Allegro A3972SB Datasheet

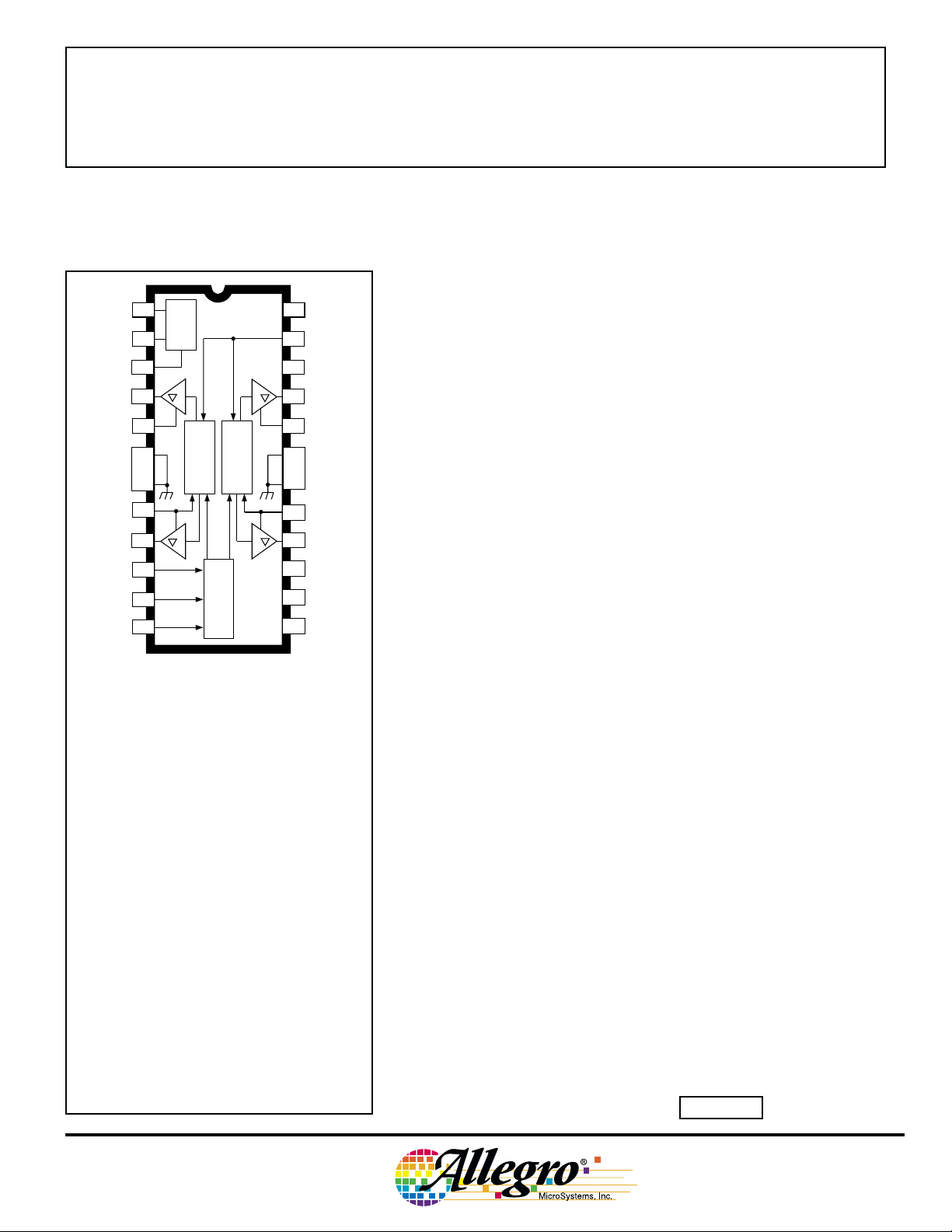

VCP

CP1

CP2

OUT

LOAD

SUPPLY

GROUND

GROUND

SENSE

OUT

STROBE

CLOCK

DATA

1

V

BB1

PUMP

CHARGE

6-BIT DAC

& LOGIC

& LOGIC

6-BIT DAC

SERIAL PORT

V

BB2

DD

V

2

3

1B

4

5

1

6

7

1

8

9

1A

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

Dwg. PP-069-3

OSC

SLEEP

V

REG

OUT

2B

LOAD

SUPPLY

GROUND

GROUND

SENSE

OUT

2A

LOGIC

SUPPLY

MUX

REF

ABSOLUTE MAXIMUM RATINGS

at TA = +25°C

Load Supply Voltage, VBB................ 50 V

Output Current, I

Logic Supply Voltage, VDD.............. 7.0 V

Logic Input Voltage Range,

VIN................ -0.3 V to V

Reference Voltage, V

Sense Voltage (dc), VS................ 500 mV

Package Power Dissipation,

PD.......................................... 3.1 W

Operating Temperature Range,

TA.......................... -20°C to +85°C

Junction Temperature, TJ............. +150°C

Storage Temperature Range,

TS......................... -55°C to +150°C

Output current rating may be limited by duty

cycle, ambient temperature, and heat sinking.

Under any set of conditions, do not exceed the

specified current rating or a junction temperature of 150°C.

...................... ±1.5 A

OUT

DD

..................... 3 V

REF

+ 0.3 V

Data Sheet

29319.33

3972

DUAL DMOS FULL-BRIDGE MICRO-

STEPPING PWM MOTOR DRIVER

Designed for pulse-width modulated (PWM) current control of

bipolar microstepping stepper motors, the A3972SB is capable of

continuous output currents to ±1.5 A and operating voltages to 50 V.

Internal fixed off-time PWM current-control timing circuitry can be

programmed via a serial interface to operate in slow, fast, and mixed

current-decay modes.

The desired load-current level is set via the serial port with two 6-bit

2

2

linear DACs in conjunction with a reference voltage. The six bits of

control allow maximum flexibility in torque control for a variety of step

methods, from microstepping to full-step drive. Load current is set in

1.56% increments of the maximum value.

Synchronous rectification circuitry allows the load current to flow

through the low r

of the DMOS output driver during the current

DS(on)

decay. This feature will eliminate the need for external clamp diodes in

most applications, saving cost and external component count, while

minimizing power dissipation.

Internal circuit protection includes thermal shutdown with hysteresis, transient-suppression diodes, and crossover-current protection.

Special power-up sequencing is not required.

The A3972SB is supplied in a 24-lead plastic DIP with a copper

batwing power tab (suffix ‘B’). The power tab is at ground potential and

needs no electrical isolation.

FEATURES

■ ±1.5 A, 50 V Continuous Output Rating

■ Low r

■ Optimized Microstepping via 6-Bit Linear DACs

■ Programmable Mixed, Fast, and Slow Current-Decay Modes

■ 4 MHz Internal Oscillator for Digital Timing

■ Serial-Interface Controls Chip Functions

■ Synchronous Rectification for Low Power Dissipation

■ Internal UVLO and Thermal Shutdown Circuitry

■ Crossover-Current Protection

■ Precision 2 V Reference

■ Inputs Compatible with 3.3 V or 5 V Control Signals

■ Sleep and Idle Modes

Always order by complete part number: A3972SB .

DMOS Output Drivers

DS(on)

3972

DUAL DMOS FULL-BRIDGE

MICROSTEPPING PWM MOTOR DRIVER

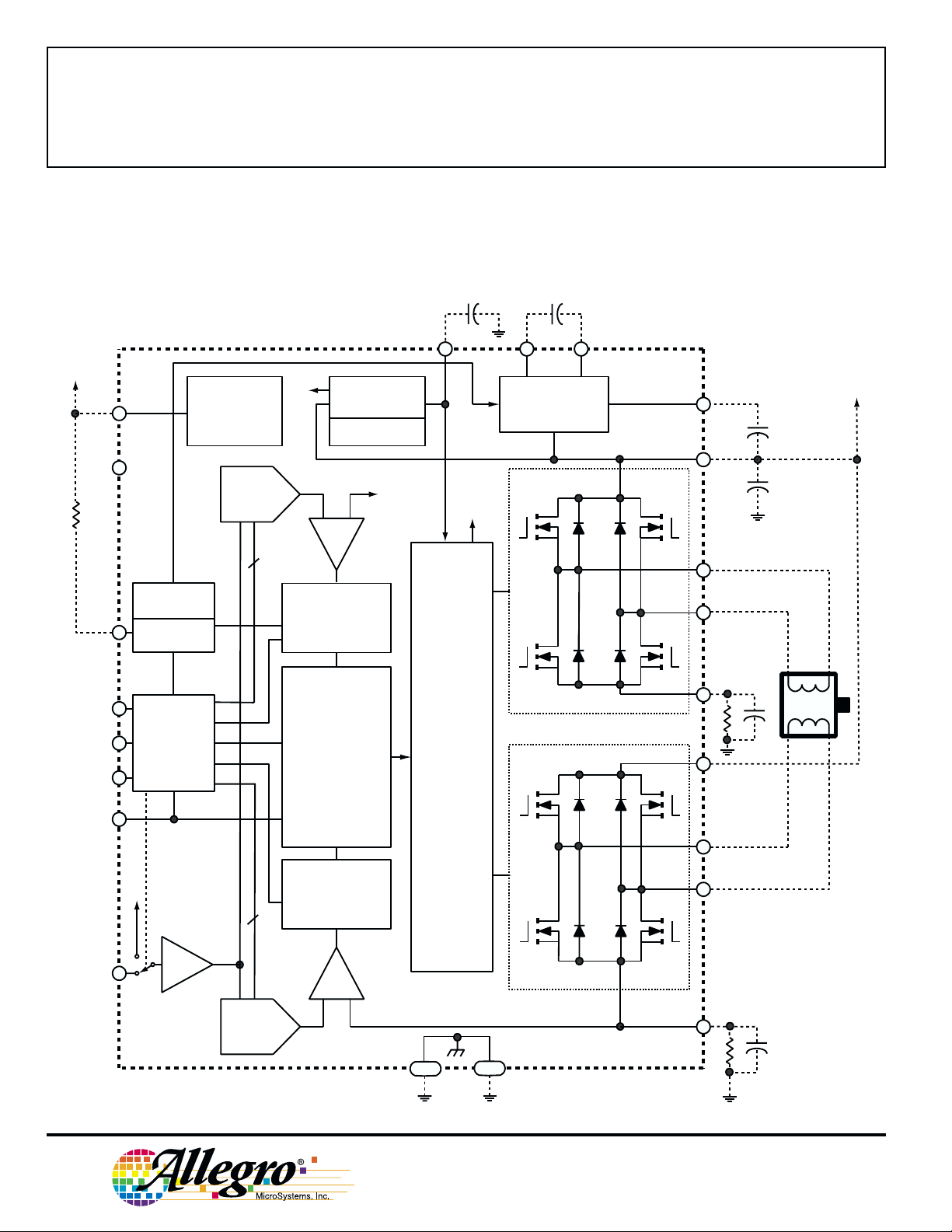

FUNCTIONAL BLOCK DIAGRAM

LOGIC

SUPPLY

CLOCK

DATA

STROBE

SLEEP

V

MUX

OSC

15

DD

14

24

11

12

10

23

OSCILATOR

OSC SELECT/

DIVIDER

SERIAL

PORT

2 V

UVLO AND

FAULT

DETECT

6-BIT

LINEAR

DAC

6

6

2 V

REGULATOR

BANDGAP

+-

PROGRAMMABLE

PWM TIMER

FIXED-OFF

BLANK

MIXED DECAY

CONTROL

LOGIC

PHASE 1/2

SYNC. RECT. MODE

SYNC. RECT. DISABLE

MODE 1/2

PROGRAMMABLE

PWM TIMER

FIXED-OFF

BLANK

MIXED DECAY

SENSE

1

V

22

GATE

DRIVE

0.22 µF

REG

V

CP

0.22 µF

3

CP1CP2

2

CHARGE PUMP

DMOS H-BRIDGE

DMOS H-BRIDGE

1

5

9

4

8

20

16

21

V

CP

V

BB1

OUT

1A

OUT

1B

SENSE

V

BB2

OUT

2A

OUT

2B

1

0.1 µF

0.22 µF

LOAD

SUPPLY

2

REF

13

Dwg. FP-050-1

BUFFER

6-BIT

LINEAR

DAC

+-

GROUND

6

18

7

19

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

Copyright © 2000, Allegro MicroSystems, Inc.

17

SENSE

2

0.1

µ

F

3972

DUAL DMOS FULL-BRIDGE

MICROSTEPPING PWM MOTOR DRIVER

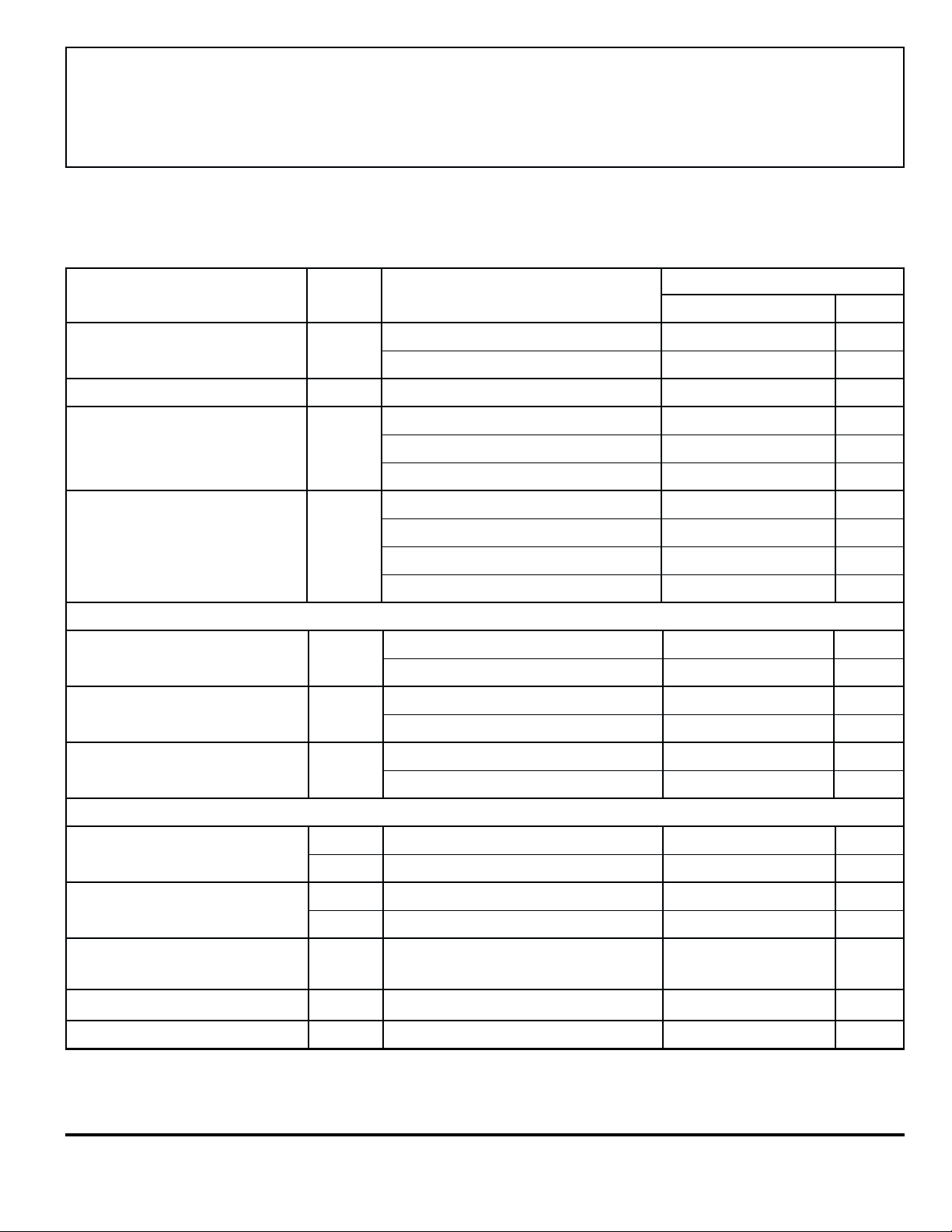

ELECTRICAL CHARACTERISTICS at TA = +25°C, VBB = 50 V, VDD = 5.0 V, VS = 0.5 V,

f

< 50 kHz (unless otherwise noted).

PWM

Limits

Characteristic Symbol Test Conditions Min. Typ. Max. Units

Load Supply Voltage Range V

Logic Supply Voltage Range V

Load Supply Current I

Logic Supply Current I

Output Drivers

Output Leakage Current I

Output On Resistance r

DS(on)

Body Diode Forward Voltage V

BB

DD

BB

DD

DSS

Operating 15 — 50 V

During sleep mode 0 — 50 V

Operating 4.5 5.0 5.5 V

f

< 50 kHz — — 8.0 mA

PWM

Operating, outputs disabled — — 6.0 mA

Sleep or idle mode — — 20 µA

f

< 50 kHz — — 12 mA

PWM

Outputs off — — 10 mA

Idle mode (D0 = 1, D18 = 0) — — 1.5 mA

Sleep mode — — 100 µA

V

= V

OUT

V

OUT

Source driver, I

Sink driver, I

F

Source diode, IF = 1.5 A — — 1.2 V

BB

= 0 V — <-1.0 -50 µA

= –1.5 A — 0.5 0.55 Ω

OUT

= 1.5 A — 0.315 0.35 Ω

OUT

— <1.0 50 µA

Sink diode, IF = 1.5 A — — 1.2 V

Control Logic

Logic Input Voltage V

Logic Input Current I

OSC Input Frequency Range f

V

I

IN(1)

IN(0)

IN(1)

IN(0)

OSC

VIN = 2.0 V — <1.0 20 µA

V

= 0.8 V — <-2.0 -20 µA

IN

Divide by one 2.5 — 6.0 MHz

2.0 — — V

——0.8 V

(D0 =1, D13 = 0, D14 = 1)

OSC Input Duty Cycle — 40 — 60 %

Input Hysterisis ∆V

IN

0.20 — 0.40 V

continued next page ...

www.allegromicro.com

3

3972

DUAL DMOS FULL-BRIDGE

MICROSTEPPING PWM MOTOR DRIVER

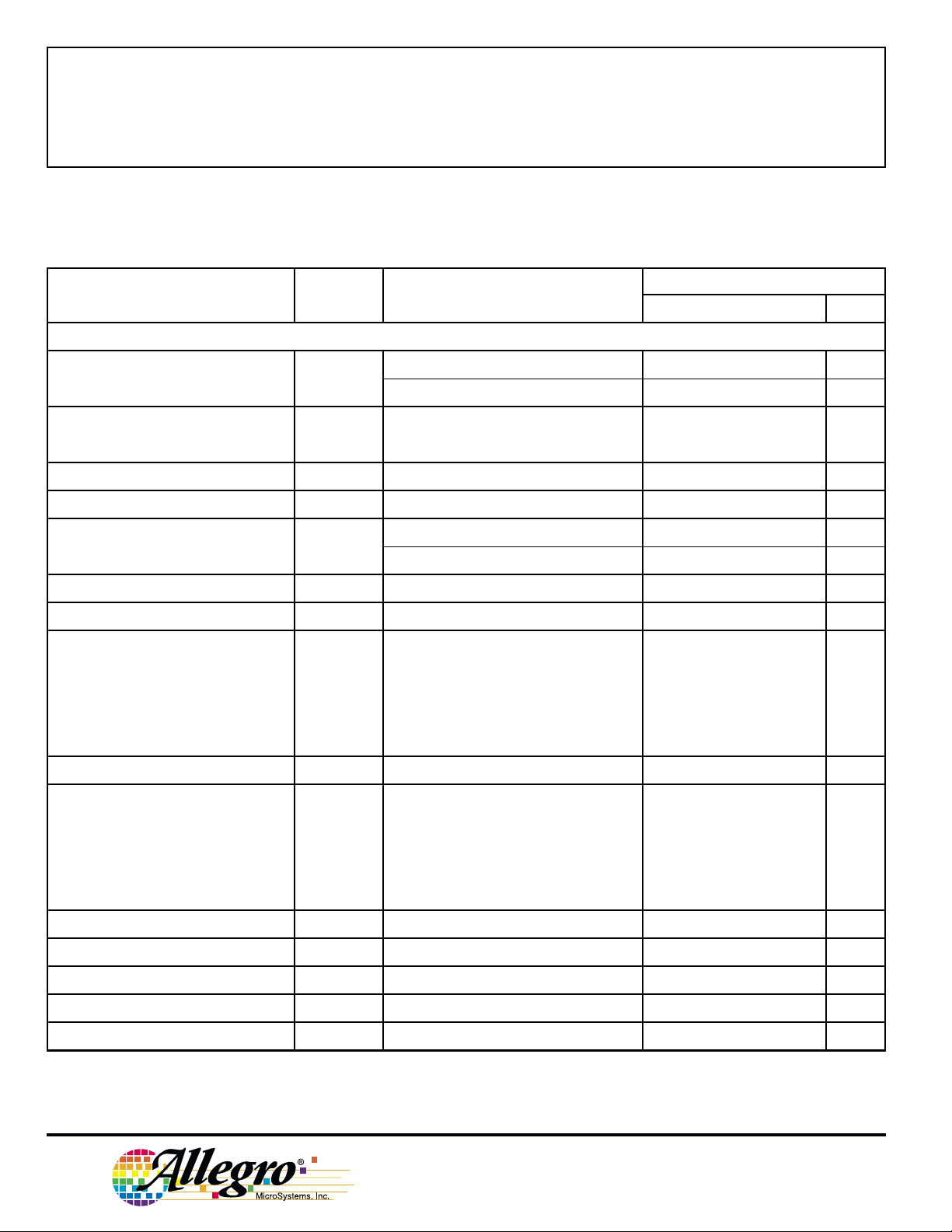

ELECTRICAL CHARACTERISTICS at TA = +25°C, VBB = 50 V, VDD = 5.0 V, VS = 0.5 V,

f

< 50 kHz (unless otherwise noted).

PWM

Limits

Characteristics Symbol Test Conditions Min. Typ. Max. Units

Control Logic (continued)

Internal Oscillator f

DAC Accuracy (total error) E

Reference Input Voltage Range V

REF(EXT)

Reference Buffer Offset V

Reference Divider Ratio V

REF/VS

Reference Input Current I

Internal Reference Voltage V

REF(INT)

Gain (Gm) Error (note 3) E

Comparator Input Offset Voltage V

Propagation Delay Times t

OSC

OS

REF

G

IO

pd

OSC shorted to ground 3.0 4.0 5.0 MHz

R

= 51 kΩ 3.4 4.0 4.6 MHz

OSC

T

Relative to DAC reference buffer

— ±1/2 — LSB

output, D0 = 0, D17 = 0

0.5 — 2.6 V

— ±10 — mV

D0 = 0, D18 = 0 — 8.0 — —

D0 = 0, D18 = 1 — 4.0 — —

V

= 2.0 V — — ±0.5 µA

REF

1.94 2.0 2.06 V

D0 = 0, D17 = 0,

D18 = 0, DAC = 63 — 0 ±6%

D18 = 0, DAC = 31 — 0 ±9%

D18 = 1, DAC = 63 — 0 ±6%

D18 = 1, DAC = 15 — 0 ±10 %

V

= 0 V — ±5.0 — mV

REF

50% to 90%:

PWM change to source on 500 800 1200 ns

PWM change to source off 50 150 350 ns

PWM change to sink on 500 800 1200 ns

Crossover Dead Time t

Thermal Shutdown Temperature T

Thermal Shutdown Hysteresis ∆T

UVLO Enable Threshold V

UVLO Hysteresis ∆V

dt

J

J

UVLO

UVLO

NOTES: 1. Typical Data is for design information only.

2. Negative current is defined as coming out of (sourcing) the specified device terminal.

3. EG = [(V

/Range) – VS]/(V

REF

/Range).

REF

4

PWM change to sink off 50 150 350 ns

300 700 900 ns

— 165 — °C

—15— °C

Increasing V

DD

3.9 4.2 4.45 V

0.05 0.10 — V

115 Northeast Cutoff, Box 15036

Worcester, Massachusetts 01615-0036 (508) 853-5000

Loading...

Loading...