ALLEGRO A3930, A3931 User Manual

A3930 and A3931

Automotive 3-Phase BLDC Controller and MOSFET Driver

Features and Benefits

High current 3-phase gate drive for N-channel MOSFETs

Synchronous rectification

Cross-conduction protection

Charge pump and top-off charge pump for 100% PWM

Integrated commutation decoder logic

Operation over 5.5 to 50 V supply voltage range

Extensive diagnostics output

Provides +5 V Hall sensor power

Low-current sleep mode

Package: 48 Lead LQFP with exposed

thermal pad (suffix JP)

Description

The A3930 and A3931 are 3-phase brushless DC (BLDC) motor

controllers for use with N-channel external power MOSFETs.

They incorporate much of the circuitry required to design a

cost effective three-phase motor drive system, and have been

specifically designed for automotive applications.

A key automotive requirement is functionality over a wide

input supply range. A unique charge pump regulator provides

adequate (>10 V) gate drive for battery voltages down to 7 V,

and allows the device to operate with a reduced gate drive at

battery voltages down to 5.5 V. Power dissipation in the charge

pump is minimized by switching from a voltage doubling mode

at low supply voltage to a dropout mode at the nominal running

voltage of 14 V.

A bootstrap capacitor is used to provide the above-battery

supply voltage required for N-channel MOSFETs. An internal

charge pump for the high-side drive allows for DC (100% duty

cycle) operation.

Internal fixed-frequency PWM current control circuitry can

be used to regulate the maximum load current. The peak

load current limit is set by the selection of an input reference

voltage and external sensing resistor. The PWM frequency is

set by a user-selected external RC timing network. For added

flexibility, the PWM input can be used to provide speed and

Approximate Scale 1:1

Continued on the next page…

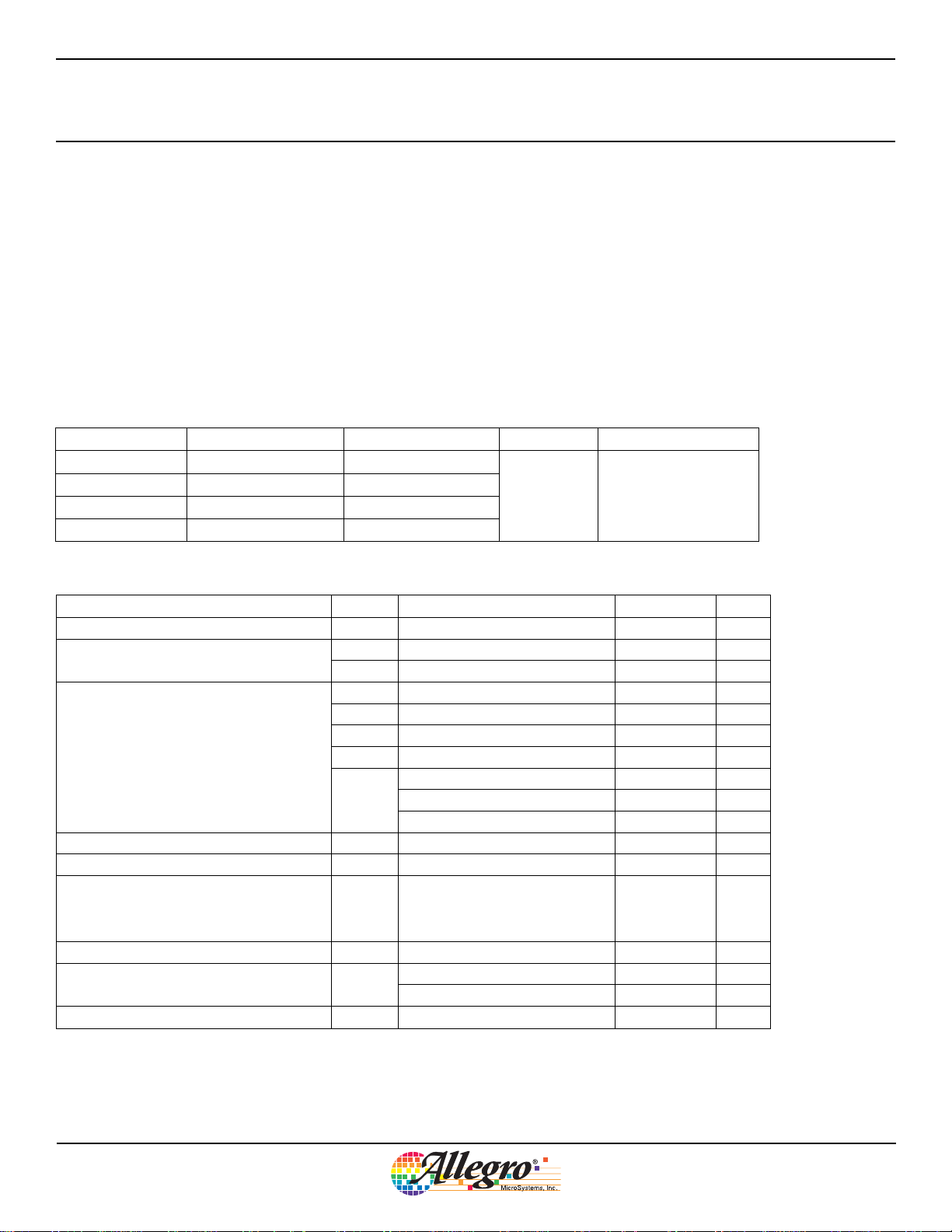

T ypical Application

3930-DS Rev. 2

A3930 and

Automotive 3-Phase BLDC Controller

A3931

Description (continued)

torque control, allowing the internal current control circuit to set

the maximum current limit.

Efficiency is enhanced by using synchronous rectification. The

power FETs are protected from shoot-through by integrated

crossover control with dead time. The dead time can be set by a

single external resistor.

The A3930 and A3931 only differ in their response to the all-zero

Selection Guide

Part Number Option Packing Terminals Package

A3930KJP-T Hall short detection 250 pieces/tray

A3930KJPTR-T Hall short detection 1500 pieces/reel

A3931KJP-T Pre-positioning 250 pieces/tray

A3931KJPTR-T Pre-positioning 1500 pieces/reel

combination on the Hall inputs. In this state, the A3930 indicates

a logic fault, but the A3931 pre-positions the motor in an unstable

starting position suitable for start-up algorithms in microprocessordriven “sensor-less” control systems.

Both devices are supplied in a 48-pin LQFP with exposed thermal

pad. This is a small footprint (81 mm2) power package, that is lead

(Pb) free, with 100% matte tin leadframe plating.

48 LQFP surface mount

and MOSFET Driver

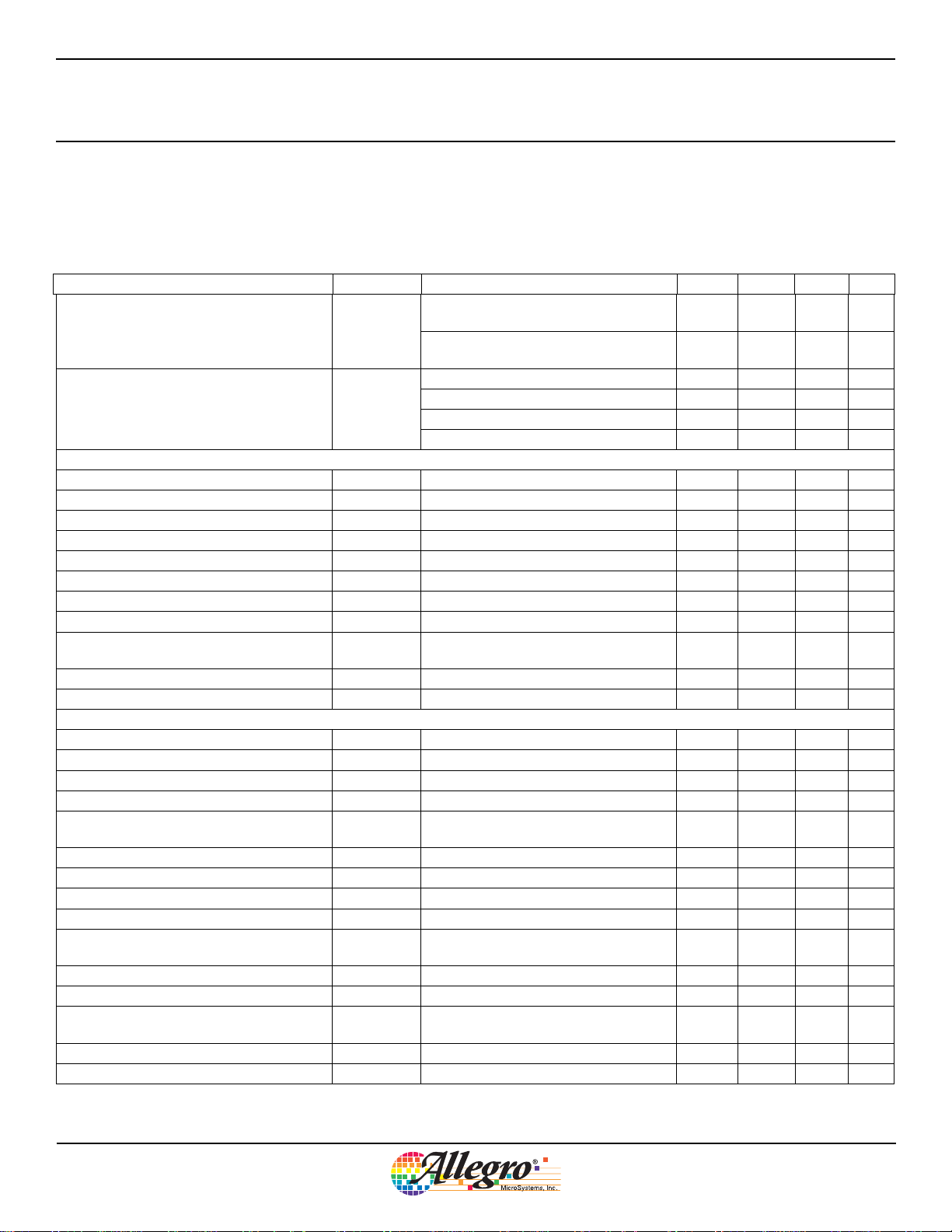

Absolute Maximum Ratings

Parameter Symbol Conditions Rating Units

Load Supply Voltage V

V

Logic Input/Output Voltage

Output Voltage Range

Operating Temperature Range (K) T

Junction Temperature T

Transient Junction Temperature T

Storage Temperature Range T

ESD Rating, Human Body Model

ESD Rating, Charged Device Model AEC-Q100-011, all pins 1050 V

RESET

V

V

V

V

VBB pin –0.3 to 50 V

BB

RESET pin input –0.3 to 6 V

Remaining logic pins –0.3 to 7 V

GHA, GHB, and GHC pins VSx to VSx+ 15 V

GHx

GLA, GLB, and GLC pins –5 to 16 V

GLx

CA, CB, and CC pins VSx+ 15 V

Cx

SA, SB, and SC pins –5 to 55 V

Sx

CSP, CSN, and LSS pins –4 to 6.5 V

CSO, VDSTH pins –0.3 to 6.5 V

VDRAIN pin –0.3 to 55 V

A

J

Overtemperature event not exceeding 1 s, lifetime duration not exceed-

tJ

ing 10 hr; guaranteed by design

characterization

S

AEC-Q100-002, all pins except CP1 2000 V

AEC-Q100-002, pin CP1 1000 V

–40 to 150 °C

–55 to 150 °C

150 °C

175 °C

Allegro MicroSystems, Inc.

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

2

A3930 and

Automotive 3-Phase BLDC Controller

A3931

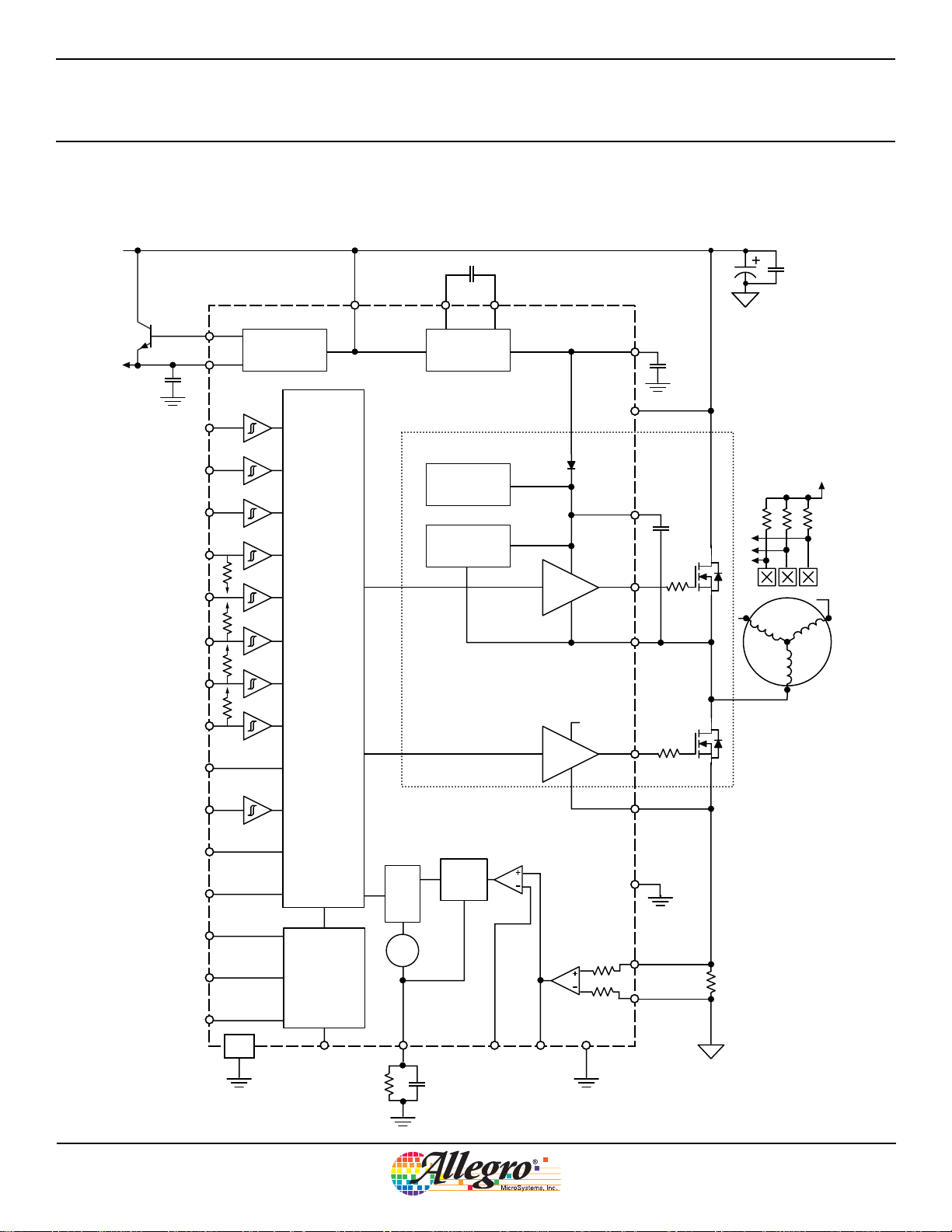

QV5

VBAT+

V5BD

CV5

MODE

COAST

BRAKE

RESET

DIR

and MOSFET Driver

Functional Block Diagram

CP

VBB

V5

H1

+5V Ref

Control

Logic

Phase A of three phases

CP1CP2

Charge

Pump

Regulator

Charge

Pump

Boostrap

Monitor

High-Side

Drive

VREG

VDRAIN

CA

GHA

SA

CREG

CBOOTA

RGHA

P

V5

H1

H2

H3

&C

&B

H2

H3

RDEAD

PWM

TACHO

DIRO

ESF

FF1

FF2

Pad

Diagnostics and

Protection

–UVLO

–TSD

–Short to Supply

–Short to Ground

–Shorted Winding

–Low Load

VDSTH

RC

Q

OSC

VREG

Low-Side

Drive

R

Blanking

S

REF

CSOUT

CTRT

AGND

GLA

RGLA

LSS

TEST

CSP

CSN

P

&A

RSENSE

Allegro MicroSystems, Inc.

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

3

A3930 and

Automotive 3-Phase BLDC Controller

A3931

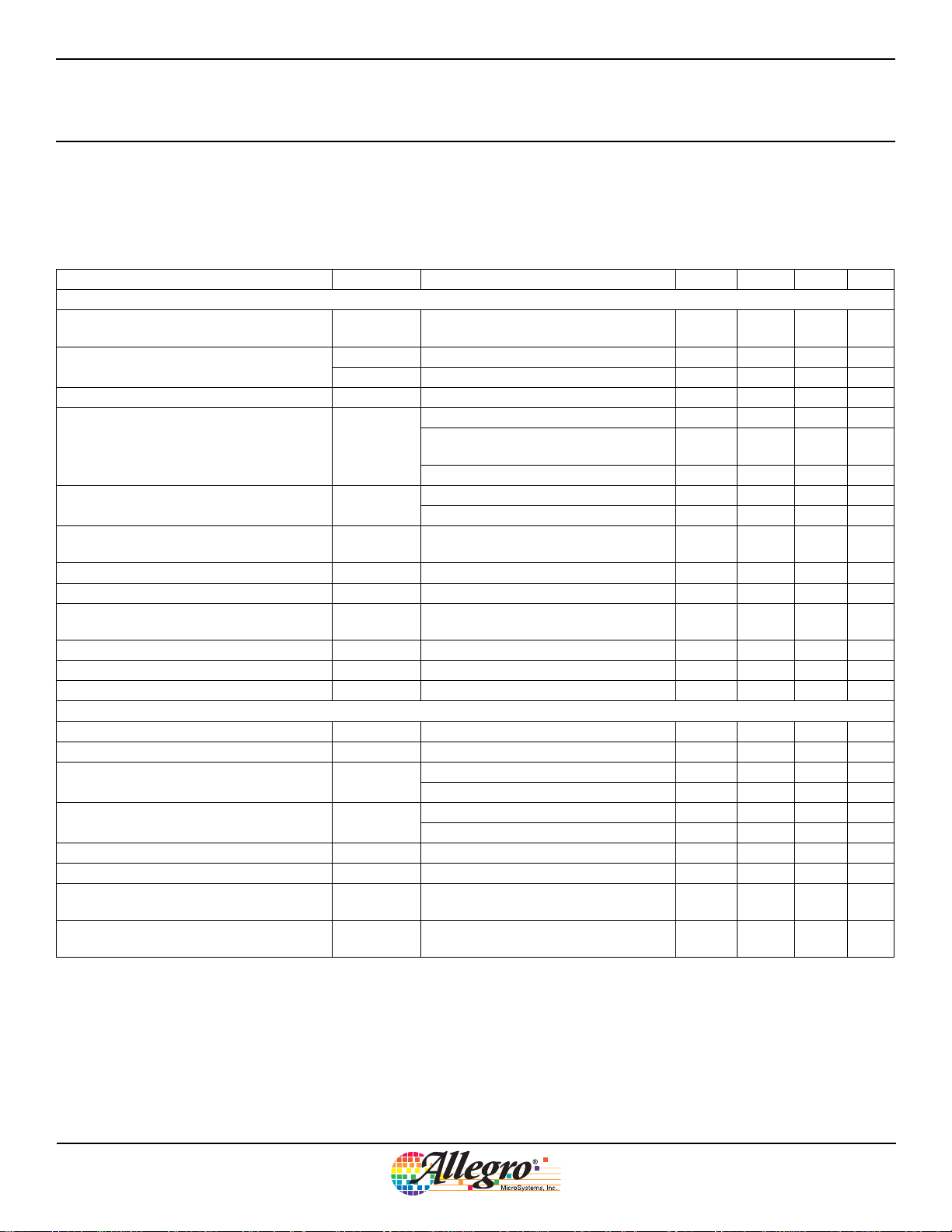

ELECTRICAL CHARACTERISTICS at T

Characteristics Symbol Test Conditions Min. Typ. Max. Units

Supply and Reference

VBB Functional Operating Range

VBB Quiescent Current

V5 Quiescent Current I

VREG Output Voltage V

Bootstrap Diode Forward Voltage V

Bootstrap Diode Resistance r

Bootstrap Diode Current Limit I

Top-off Charge Pump Current Limit I

High-Side Gate Drive Static Load

Resistance

V5 Output Voltage V

VBE of External Transistor QV5 V

V5BD Base Drive Capability for QV5

Gate Output Drive

Turn-On Rise Time t

Turn-Off Fall Time t

Pull-Up On Resistance R

Pull-Down On Resistance R

Short-Circuit Current – Source

Short-Circuit Current – Sink I

GHx Output Voltage V

GLx Output Voltage V

6

2

2

= –40°C to 150°C, V

J

DS(on)UP

DS(on)DN

I

SC(source)TJ

SC(sink)

V

BB

I

BBQ

I

BBS

V5Q

REG

fBOOT

D

DBOOT

TOCPM

R

GSH

5

BEEXT

I

5BD

r

f

GHx

GLx

and MOSFET Driver

= 7 to 45 V, unless otherwise noted

BB

Function correct, parameters not

guaranteed

RESET = High, outputs = Low – 11 14 mA

RESET = Low, sleep mode – – 10 A

RESET = High, outputs = Low – – 5 mA

V

7.4 V, I

BB

6 V < V

BB

I

= 0 to 15 mA

REG

5.5 V < VBB < 6 V, I

= 0 to 15 mA 12.10 13 13.75 V

REG

< 7.4 V

< 10 mA 9 10 – V

REG

ID = 10 mA 0.4 0.7 1.0 V

ID = 100 mA 1.5 2.2 2.8 V

r

D(100 mA)

V

C

LOAD

C

LOAD

TJ = 25°C, I

TJ = 150°C, I

TJ = 25°C, I

TJ = 150°C, I

= (V

fBOOT(150 mA)

fBOOT(50 mA)

–

) / 100 mA

= 3300 pF, 20% to 80% points – 60 – ns

= 3300 pF, 80% to 20% points – 40 – ns

= –150 mA 3 4 5

GHx

= –150 mA 4.6 5.6 6.6

GHx

= 150 mA 1 1.5 2

GLx

= 150 mA 1.5 2.3 3

GLx

= 25°C – –500 – mA

TJ = 25°C – 850 – mA

tw < 10 s

Bootstrap capacitor fully charged

1

5.5 – 50 V

2 × V

BB

–2.7

––V

61020

250 500 750 mA

– 200 – A

250 – – k

4.75 5 5.25 V

––1V

– – –2 mA

V

– 0.2 – – V

Cx

V

–

REG

0.2

––V

Continued on the next page...

Allegro MicroSystems, Inc.

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

4

A3930 and

Automotive 3-Phase BLDC Controller

A3931

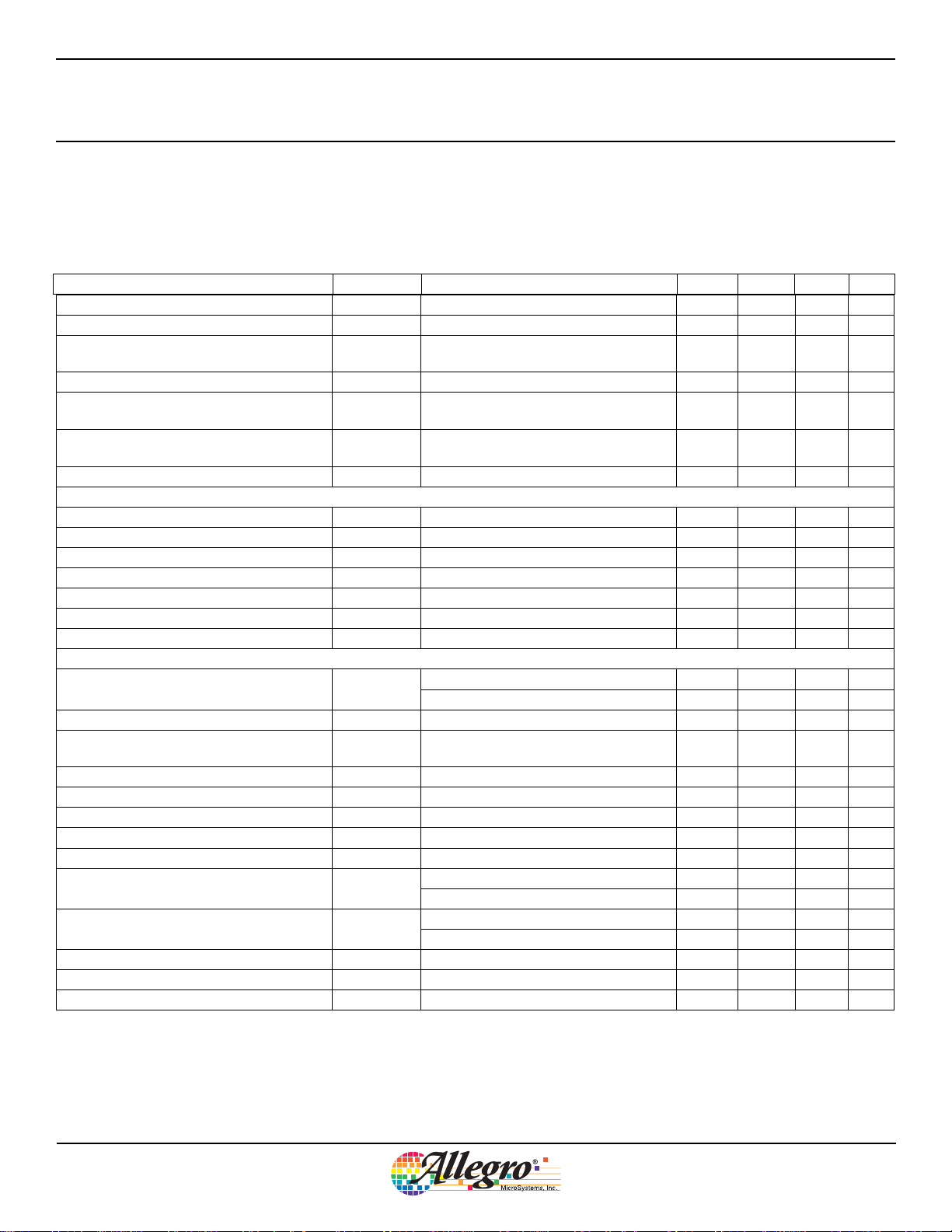

ELECTRICAL CHARACTERISTICS (continued) at T

Characteristics Symbol Test Conditions Min. Typ. Max. Units

Turn-Off Propagation Delay t

Dead Time (turn-off to turn-on delay) t

Logic Inputs and Outputs

FFx Fault Output (Open Drain) V

FFx Fault Output Leakage Current

2

TACHO and DIRO Output High Voltage V

TACHO and DIRO Output Low Voltage V

Input Low Voltage V

Input High Voltage (Except RESET) V

RESET Input High Voltage V

Input Hysteresis V

Input Current (Except H1, H2, H3, and

RESET)

2

RESET Input Pull-Down Resistor R

Hx Input Pull-Up Resistor R

Current Sense Differential Amplifier

Input Bias Current

Input Offset Current

2

2

CSP Input Resistance R

CSN Input Resistance R

Differential Input Voltage V

Output Offset Voltage V

Output Offset Voltage Drift V

Input Common Mode Range V

Differential Input Voltage Gain A

Low Output Voltage Error V

DC Common Mode Gain A

Source Resistance r

Output Dynamic Range V

Output Current – Sink I

Output Current – Source

2

p(off)

DEAD

OL

I

OH

OH

OL

IL

IH

IHR

IHys

I

IN

PD

PU

I

IBS

I

IOS

CSP

CSN

ID

OOS

OOS(t)

CM

V

err

CMdc

CSOUT

CSOUT

CSOUT(sink)VCSOUT

I

CSOUT(source)VCSOUT

and MOSFET Driver

= –40°C to 150°C, V

J

From Hall input change to unloaded

gate output change

From other control input change to

unloaded gate output change

R

= 5 k – 180 – ns

DEAD

R

= 50 k 835 960 1090 ns

DEAD

R

= 400 k – 3.3 – s

DEAD

= 7 to 45 V, unless otherwise noted

BB

300 500 700 ns

– 150 200 ns

RDEAD = tied to V5 – 6 – s

I

= 1 mA, fault asserted – – 0.4 V

OL

VO = 5 V, fault not asserted –1 – 1 A

I

= –1 mA V5 – 1 V – – V

OH

I

= 1 mA – – 0.4 V

OL

– – 0.8 V

2––V

2.2 – – V

300 500 – mV

–1 – 1 A

V

= 5 V – 50 – k

IN

V

= 0 V – 100 – k

IN

CSP = CSN = 0 V –250 –200 –150 A

CSP = CSN = 0 V –10 – 10 A

Measured with respect to AGND – 80 – k

Measured with respect to AGND – 4 – k

V

= CSP – CSN, –1.3 V < CSP < 4 V,

ID

–1.3 V < CSN < 4 V

0 – 200 mV

CSP = CSN = 0 V 100 320 550 mV

CSP = CSN = 0 V – 100 – V/°C

CSP = CSN –1.5 – 4 V

40 mV < V

0 < V

V

CSOUT

< 175 mV, VCM in range 18.5 19 19.5 V/V

ID

< 40 mV,

ID

= (19 × VID) + V

OOS

+ V

err

–20 – 20 mV

CSP = CSN = 200 mV – –30 – dB

V

–100 A < I

= 2 V, –2 mA < I

CSOUT

< 0.5 mA – 80 –

CSOUT

< 100 A 0.1 –

CSOUT

= 2 V ±5% – 1 – mA

= 2 V ±5% – –19 – mA

1

– 0.2

V5

V

Continued on the next page…

Allegro MicroSystems, Inc.

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

5

A3930 and

Automotive 3-Phase BLDC Controller

A3931

ELECTRICAL CHARACTERISTICS (continued) at T

= –40°C to 150°C, V

J

= 7 to 45 V, unless otherwise noted

BB

and MOSFET Driver

1

Characteristics Symbol Test Conditions Min. Typ. Max. Units

Supply Rejection PSRR CSP = CSN = AGND, 0 to 300 kHz – 45 – dB

Small Signal 3 dB Bandwidth Frequency f

Settling Time t

AC Common Mode Gain A

Common Mode Recovery Time t

3dB

SETTLE

CMac

CMrec

Output Slew Rate SR

Input Overload Recovery Time t

IDREC

VID=10 mV

To within 10%, V

PP

= 1 VPP square

CSOUT

wave

V

= 250 mVPP, 0 to 1 MHz – –28 – dB

ICR

To within 100 mV, V

= +4.1 to 0 V

ICR

step

10% to 90% points, VID= 0 to 175 mV

step

– 1.6 – MHz

– 400 – ns

–1–s

–20–V/s

To within 10%, VID=250 mV to 0 V step – 500 – ns

Current Limit

Reference Comparator Input Offset Voltage V

Reference Input Clamp Voltage V

Comparator Blank Time t

REF Input Bias Current I

RC Charge Current

2

RC HIgh Voltage Threshold V

RC Low Voltage Threshold V

IOC

REFC

RC

IBREF

I

RC

RCH

RCL

External pull-up to 5 V R

= 200 k 3.75 4 4.2 V

REF

RT= 56 k, CT = 470 pF – 650 – ns

–15 0 15 mV

–0–A

–1.15 –1 –0.85 mA

1.7 1.9 2.1 V

0.6 0.7 0.8 V

Protection

V

rising 7.5 8 8.5 V

VREG Undervoltage Lockout V

Bootstrap Capacitor Undervoltage Lockout V

Bootstrap Capacitor Undervoltage Lockout

Hysteresis

V5 Undervoltage Lockout V

V5 Undervoltage Lockout Hysteresis V

VDSTH Input Voltage Range V

VDSTH Input Current

2

VDRAIN Input Voltage Range V

Short-to-Ground Threshold Offset

Short-to-Battery Threshold Offset

3,5

4,5

Low Load Current Detection Voltage V

Overtemperature Flag T

Overtemperature Flag Hysteresis T

1

Parameters are tested at 135°C. Values at 150°C are guaranteed by design or correlation.

2

For input and output current specifications, negative current is defined as coming out of (sourcing) the specified device pin.

3

High side on. As VSX decreases, fault occurs if V

4

Low side on. As VSX increases, fault occurs if V

5

V

threshold is V

STG

6

Function is correct but parameters not guaranteed above or below general limits (7 to 45 V).

DTSTH

+ V

STGO

. V

STB

threshold is V

REGUV

BOOTUVVBOOT

V

BOOTUVHysVBOOTUVHys

5UV

5UVHys

DSTH

I

DSTH

DRAIN

V

STGO

V

STBO

CSOL

JF

JFHys

– V

– V

SX

LSS

DTSTH

> V

> V

BAT

SX

REG

V

falling 6.75 7.25 7.75 V

REG

falling, VCx – V

= %V

REG

Sx

59 – 69 %

–13–%

V5 falling 3.4 3.65 4.0 V

300 400 500 mV

0.3 – 4 V

–1 – 1 A

7VBB45 V

V

> 1 V – ±300 – mV

DSTH

V

1 V, 7 V V

DSTH

V

> 1 V – ±300 – mV

DSTH

V

1 V, 7 V V

DSTH

30 V –150 – 150 mV

DRAIN

30 V –150 – 150 mV

DRAIN

– 500 – mV

Temperature increasing – 170 – ºC

Recovery = T

.

STG

.

STB

+ V

STBO

.

JF

– T

JFHys

–15–ºC

Allegro MicroSystems, Inc.

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

6

A3930 and

Automotive 3-Phase BLDC Controller

A3931

and MOSFET Driver

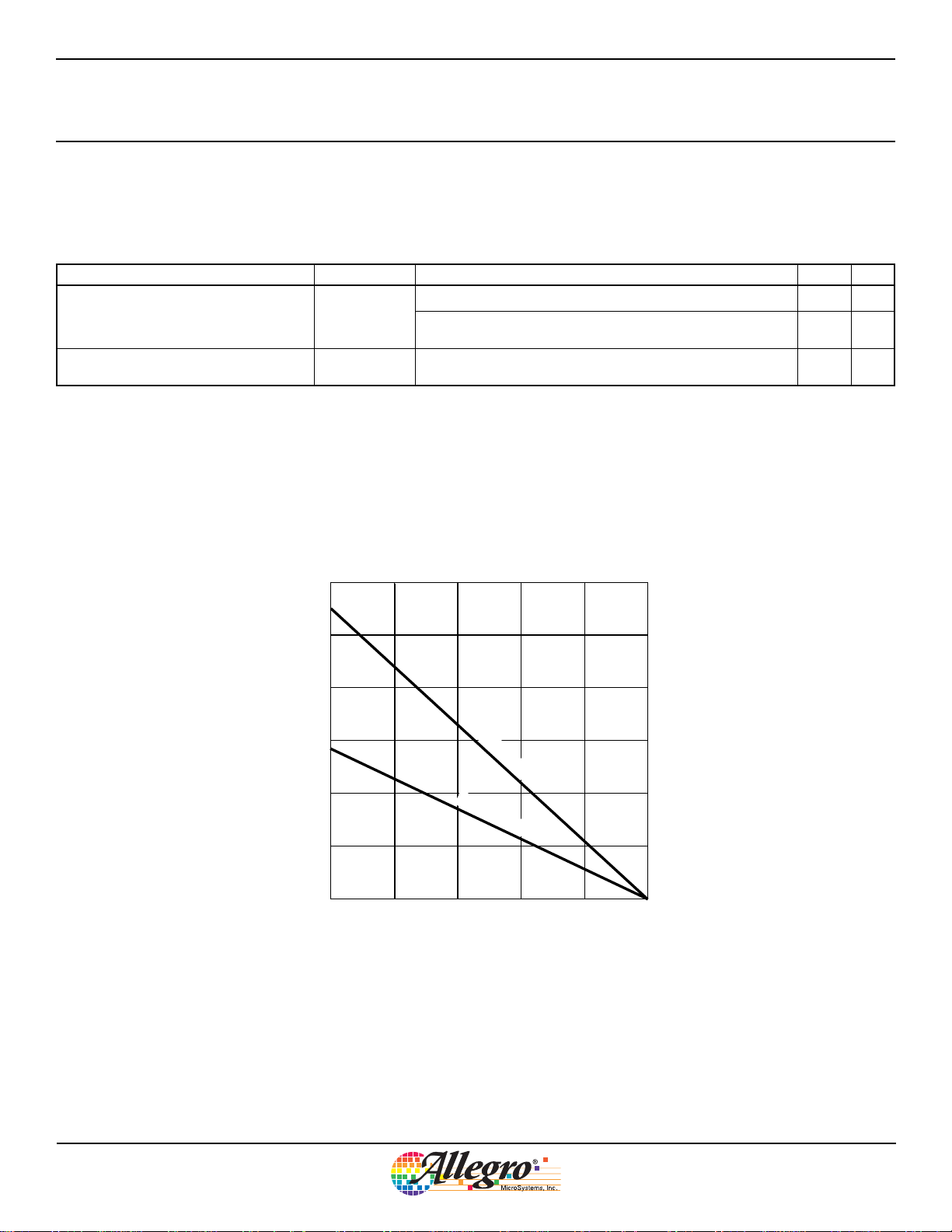

Thermal Characteristics

THERMAL CHARACTERISTICS may require derating at maximum conditions, see Applications Information section

Characteristic Symbol Test Conditions* Value Units

4-layer PCB, based on JEDEC standard 23 ºC/W

Package Thermal Resistance R

Die-to-Exposed Pad Thermal Resistance

*Additional thermal information available on Allegro Web site.

JA

R

JP

Power Dissipation versus Ambient Temperature

2-layer PCB, with 3 in.

by thermal vias

2

of copper area each side connected

44 ºC/W

2 ºC/W

6.0

5.0

4.0

R

R

QJA

Q

JA

= 23°C/W

= 44°C/W

3.0

2.0

1.0

0

ALLOWABLE PACKAGE POWER DISSIPATION IN WATTS

50 75 100 125 15025

AMBIENT TEMPERATURE IN °C

Allegro MicroSystems, Inc.

115 Northeast Cutoff

Worcester, Massachusetts 01615-0036 U.S.A.

1.508.853.5000; www.allegromicro.com

7

Loading...

Loading...