Page 1

DJ-180

DJ-1400

Service Manual

CONTENTS

SPECIFICATIONS PC BOARD VIEW

1) General 2 1) VCO Unit 24

2) Transmitter. 2 2) JACK Unit 24

3) Receiver 2 3) PTT Unit Side B 24

4) Functions for Each Version 3 4) PS Unit 25

CIRCUIT DESCRIPTION 5) ROM1 Unit Side B 25

1) Receiver System 4 6) ROM2 Unit Side B 25

2) PLL VCO Circuit. 5 7) RF Unit Side A 26

3) Transmitter System 5 8) RF Unit Side B 27

4) DTMF Encoder Circuit (option). 6 9) CPU Unit Side A. 28

5) Tone Squelch Circuit (option) 6 10) CPU Unit Side B 29

6) Microprocessor and Peripheral Circuit 6 11) RE Unit 30

7) Terminal Function of Microprocessor 7 12) CTCSS UniL 30

SEMICONDUCTOR DATA 13) DTMF Unit. 31

1) LR408721 10 PARTS LAST

2) M5218FP 10 CPU unit 32

3) M5236ML. 10 PS unit. 32

4) MB1504LPF 11 ROM1 Unit 33

5) MC3357 11 DTMF Unit 33

6) MX365 12 RF Unit 33 ~ 36

7) NJM386 13 Vco unit 37

8) RH5VA32AA. 13 CTCSS Unit 37

9) RH5VA45AA. 13 PTT SW Unit 38

10) X24C01A 14 JACK Unit 38

11) X24C04S14 14 RE Unit 38

12) X24C16S14 14 Others 38

13) Transistor, Diode and LED Outline Draw 15 ROM2 Unit. 38

14) LCD Connection. 16 PACKING 38

EXPLODED VIEW Parts Table for Each Version. 39

1) Rear Case 1 17 ADJUSTMENT

2) LCD 17 1) Required Test Equipment. 40

3) Rear Case 2 18 2) Before Adjustment 40

4) Front Case 1 19 3) Adjustment for DJ180, DJ1400 41

5) Front Case 2 20 4) Adjustment for DJ1400AN/QN 42

6) Front Case 3 and Battery Terminal 21 5) Adjustment Quick Reference 43

7) Ten Key Cover and Key Pad Panel 22 6) Adjustment Points. 43 ~ 44

8) CTCSS Unit and ROM1 Unit 23

CIRCUIT DIAGRAM 45 ~ 46

BLOCK DIAGRAM 47

ALINCO INCORPORATED

TWIN 21 M.I.D. TOWER BUILDING 23F, 1-61, 2-CHOME,

SHIROMI CHUO-KU , OSAKA, 540-8580 JAPAN

Tel (81)6-6946-8150 fax (81)6-6946-8175

e-mail: export@alinco.co.jp

Page 2

SPECIFICATIONS

DJ-180

1) General

Frequency Coverage:

RX: 137.000 ~ 173.995MHz (T, TM version)

TX: 144.000 ~ 147.995MHz (T, TM version)

RX: 137.000 ~ 173.995MHz (TA, TB, TA2, TB2 version)

TX: 137.000 ~ 173.995MHz (TA, TB, TA2, TB2 version)

RX/TX: 144.000~145.995MHz(TS, TSA, TZ, E, EA, EB version)

Frequency Resolution:

Memory Channels:

Antenna Impedance:

Signal Type:

Power Supply Requirement: DC 5.5V~13.8V (Rated 7.2V Ni-Cd)

Dimensions: Approximately 132(H) x 58(W) x 33(D) mm

Weight : Approximately 350g

2) Transmitter

Output Power.I 5.0W with Optional 12V Ni-Cd Battery

Modulation System:

Max. Frequency Deviation:

Tone Frequency:

DTMF Encoder:

Tone Burst:

5, 10, 12.5, 15, 20, 25kHz steps

10 Channels (standard)

50 ohm unbalanced

F3E(FM)

2.0W with Standard 7.2V Ni-Cd Battery

(144.000~147.995MHz)

(160.000~165.000MHz)... TA2, TB2 only

Variable Reactance Frequency Modulation

+/ -5kHz

67.0 to 250.3Hz -38 Subaudible Encoding Tones

(E, EA, EB version: option)

(TZ, EB version: option)

(E, EA, EB version only)

3) Receiver

Receiver System: Double-Conversion Superheterodyne

Intermediate Frequency.' 1st IF: 21.4MHz

2nd IF: 455kHz

Sensitivity: 12dB SINAD less than -10dBu

(144.000~17.995MHz)

(160.000~165.000MHz)... TA2, TB2 only

Page 2

Page 3

SPECIFICATIONS

DJ-1400QN / AN (The Narrow Version)

1) General

Frequency Coverage:

136.GGG ~ 155.000MHz (AN version)

150.000 ~ 173.995MHz (QN version)

Frequency Resolution:

Memory Channels:

Antenna Impedance:

Signal Type:

Power Supply Requirement: DC 5.5V~13.BV (Rated 7.2V Ni-Cd)

Dimensions:

Weight :

2) Transmitter

Output Power.I 5.GW with Optional 12V Ni-Cd Battery

Modulation System:

Max. Frequency Deviation:

Tone Frequency:

Time Out Timer

Time Out Penalty

3) Receiver

Receiver System:

Intermediate Frequency.'

Sensitivity:

AF Output

5, 10, 12.5, 15, 20, 25kHz steps

10 Channels (standard)/option 50 and 200ch

50 ohm unbalanced

F3E(FM)

Approximately 132(H) x 5B(W) x 33(D) mm

Approximately 35Gg

2.GW with Standard 7.2V Ni-Cd Battery

Variable Reactance Frequency Modulation

+/ -2.5kHz

67.0 to 250.3Hz -38 Subaudible Encoding Tones

0 to 450 sec

0 to 15 sec

Double-Conversion Superheterodyne

1st IF: 21.4MHz

2nd IF: 455kHz

12dB SINAD less than -16dBu

200mW (10% THD)

Page 2-1

Page 4

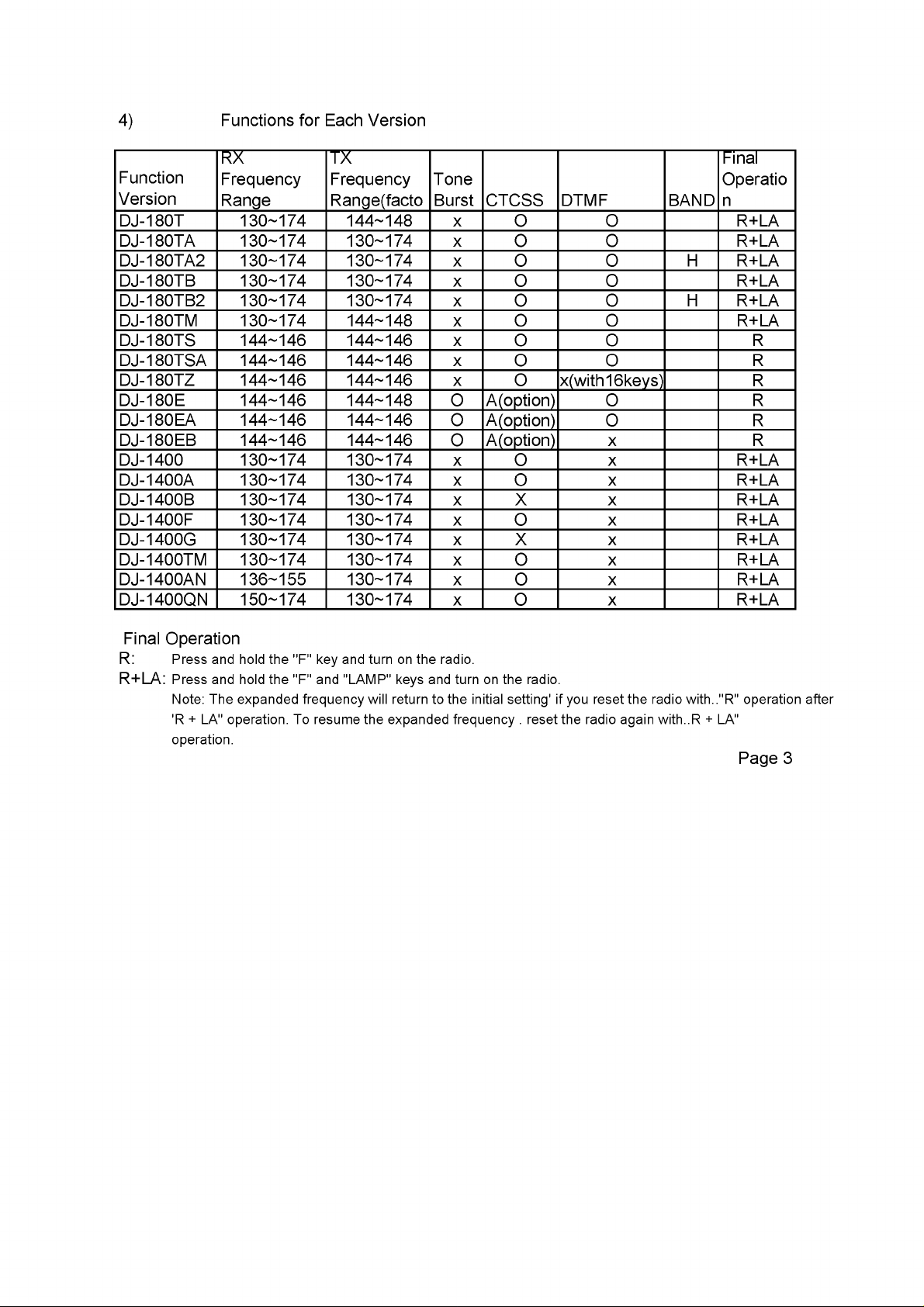

4) Functions for Each Version

RX

Function

Version

Frequency

Range

DJ-180T 130~174 144~148 x

DJ-180TA 130~174 130~174 x

DJ-180TA2 130~174 130~174 x

DJ-180TB 130~174 130~174 x

DJ-180TB2 130~174 130~174 x

DJ-180TM 130~174 144~148 x

DJ-180TS

144~146 144~146 x

DJ-180TSA 144~146 144~146 x

DJ-180TZ 144~146 144~146 x

DJ-180E 144~146 144~148

DJ-180EA 144~146 144~146

DJ-180EB 144~146 144~146

DJ-1400 130~174 130~174 x

DJ-1400A 130~174 130~174 x

TX

Frequency

Range(facto

Tone

Burst

O

CTCSS

A(option)

O A(option)

A(option) x R

O

Final

Operatio

DTMF BAND

O O

O O

O O

O O

O O

O O

n

R+LA

R+LA

H R+LA

R+LA

H R+LA

R+LA

O O

O O

O x(with16keys) R

O

O

O

O

x R+LA

x R+LA

R

R

R

R

DJ-1400B 130~174 130~174 x X x R+LA

DJ-1400F 130~174 130~174 x

DJ-1400G

130~174 130~174 x X x R+LA

DJ-1400TM 130~174 130~174 x

DJ-1400AN 136~155 130~174 x

DJ-1400QN 150~174 130~174 x

O

O

O

O

x R+LA

x R+LA

x R+LA

x R+LA

Final Operation

R: Press and hold the "F" key and turn on the radio.

R+LA: Press and hold the "F" and "LAMP" keys and turn on the radio.

Note: The expanded frequency will return to the initial setting' if you reset the radio with.."R" operation after

'R + LA'' operation. To resume the expanded frequency . reset the radio again with..R + LA"

operation.

Page 3

Page 5

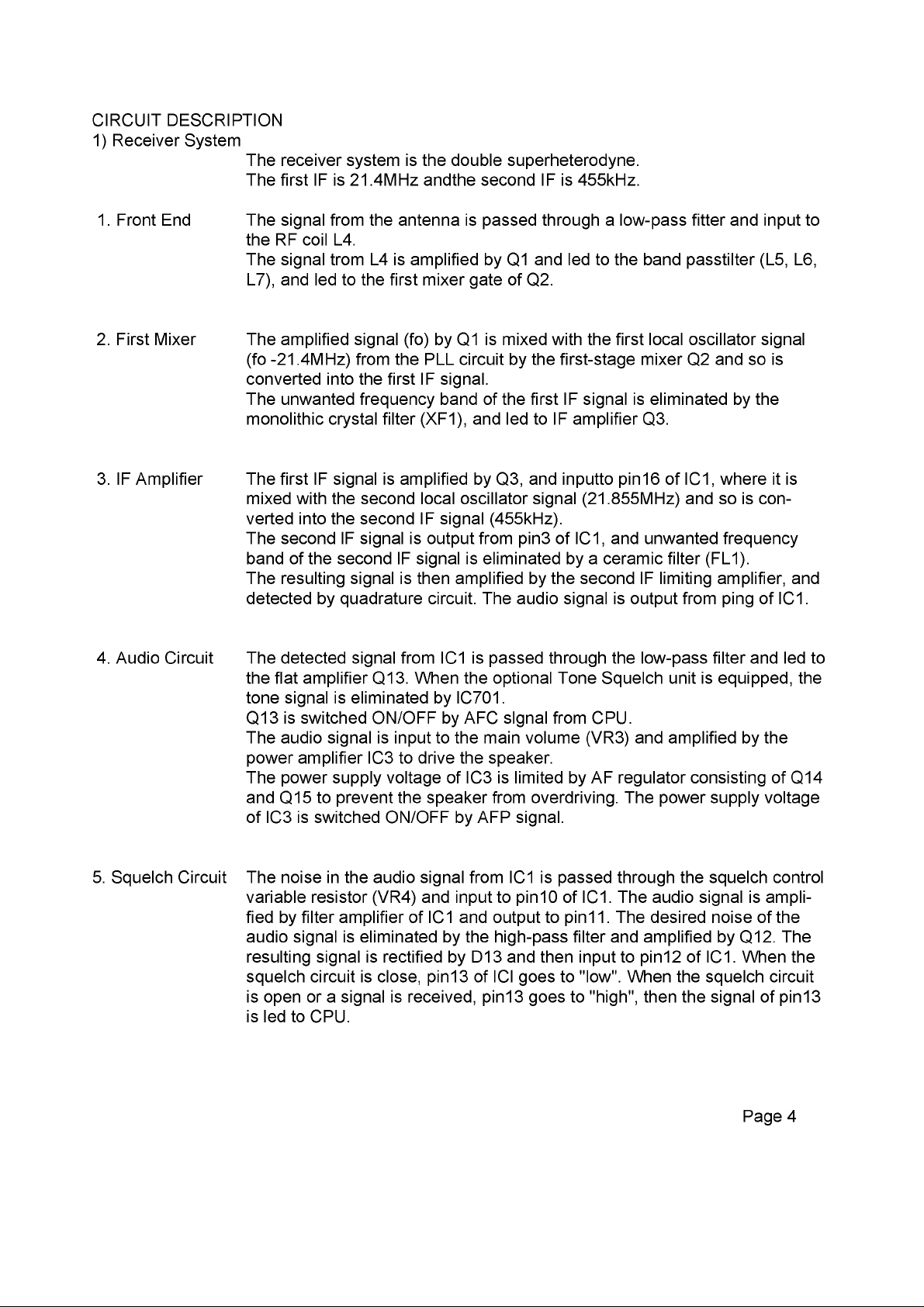

CIRCUIT DESCRIPTION

1) Receiver System

The receiver system is the double superheterodyne.

The first IF is 21.4MHz andthe second IF is 455kHz.

1. Front End

2. First Mixer

3. IF Amplifier

4. Audio Circuit

The signal from the antenna is passed through a low-pass fitter and input to

the RF coil L4.

The signal trom L4 is amplified by Q1 and led to the band passtilter (L5, L6,

L7), and led to the first mixer gate of Q2.

The amplified signal (fo) by Q1 is mixed with the first local oscillator signal

(fo -21.4MHz) from the PLL circuit by the first-stage mixer Q2 and so is

converted into the first IF signal.

The unwanted frequency band of the first IF signal is eliminated by the

monolithic crystal filter (XF1), and led to IF amplifier Q3.

The first IF signal is amplified by Q3, and inputto pin16 of IC1, where it is

mixed with the second local oscillator signal (21.855MHz) and so is con

verted into the second IF signal (455kHz).

The second lF signal is output from pin3 of IC1, and unwanted frequency

band of the second lF signal is eliminated by a ceramic filter (FL1).

The resulting signal is then amplified by the second lF limiting amplifier, and

detected by quadrature circuit. The audio signal is output from ping of IC1.

The detected signal from IC1 is passed through the low-pass filter and led to

the flat amplifier Q13. When the optional Tone Squelch unit is equipped, the

tone signal is eliminated by lC701.

Q13 is switched ON/OFF by AFC slgnal from CPU.

The audio signal is input to the main volume (VR3) and amplified by the

power amplifier IC3 to drive the speaker.

The power supply voltage of IC3 is limited by AF regulator consisting of Q14

and Q15 to prevent the speaker from overdriving. The power supply voltage

of IC3 is switched ON/OFF by AFP signal.

5. Squelch Circuit

The noise in the audio signal from IC1 is passed through the squelch control

variable resistor (VR4) and input to pin10 of IC1. The audio signal is ampli

fied by filter amplifier of IC1 and output to pin11. The desired noise of the

audio signal is eliminated by the high-pass filter and amplified by Q12. The

resulting signal is rectified by D13 and then input to pin12 of IC1. When the

squelch circuit is close, pin13 of ICl goes to "low". When the squelch circuit

is open or a signal is received, pin13 goes to "high", then the signal of pin13

is led to CPU.

Page 4

Page 6

2) PLL, VCO Circuit

Output frequency of PLL circuit is set by the serial data (pin9: clock, pin10:

data, pin11 : toad enable) from microprocessor.

PLL circuit consists of v Co Q201, buffer amplifier Q202 and Q17.

When PLL is locked, pin7 of IC2 goesto "high" and UNLOCK SW Q19

becomes OFF, then T.MUTE signal goes to "low".

The pulse wave output of charge pump is converted to DC voltage by PLL

loop filter circuit, and supplied to D201 , D202 of varicap diode in VCO unit.

The VCO tune voltage is applied to the varicaps D3, D4, D5 and D6 in the

frontend.

The frequency modulation is executed when the audio signal voltage is

supplied to the varicaps D201, D202 and D203.

3) Transmitter System

1. Microphone The voice from the internal or external microphone is led to the pre-empha-

Amplifier sis circuit, and then input to the microphone amplifier IC4, which consists of

two operational amplifiers.

The amplified signal is input to the low.pass filter lC4.

The output from the microphone amplifier is passed through variable resis

tors VR2 tor modulation adjustment to varicap diode of the VCO, contromng

the VCO frequency.

2. Power Amplifier The signal from VCO is amplified by buffer amplifiers Q4 and Q5, and input

to the buffer amplifiers Q6 and input to the power amplifier Q7. The amplified

signal is output from Q7, and then passed through the low-pass filter, the an

tenna switch circuit and the output low-pass tilter. The unwanted harmonies

frequency signal is eliminated by the low-pass fitter and input to the antenna.

The LC matching circuits located between amplifiers of the transmitting

circuit make the transmission smooth.

3. Automatic Power

Control Circuit The automatic power control(APC) circuit is used to obtain a stable transmis

sion power. This circuit detects the transmission power by D8 in the low-

pass filter consisting of L18, L19, C59, and C64. The detected DC voltage is

supplied to APC circuit. When the detected voltage goes higher than the

settled voltage, the bias voltage of APC amplifier Q9 goes to low. The

collector voltage of APC amplifier Q10 goes to low and the power supply

voltage of Q5 goes to low, and output power becomes small to prevent from

the over power.

At low power the Power Control Switch Q8 lets the base voltage of APC

DET Q11 and the collector voltage of APC AMP Q10 down, also switches

between high power and low power, and inhibits the transmission.

Page 5

Page 7

4) DTMF Encoder Circuit (option)

The DTMF signal corresponding to the combination of the column and row is

output from tone output pin17 of IC401 Encoder, producing a frequency-

modulated RF output. The Q401 switches the DTMF Encoder when lC401 is

active during DTMF transmission.

5) Tone Squelch Circuit (option)

1.Decoder

The second IF signalfrom pin11 of IC1, and input to the tone squelch

decoder lC701.

When the tone squelch decoder IC701 decodes the input tone signal fre

quency as the programmed frequency, pin13 goes to "Low". The signal is

input to pin16(DET) of lC107, and the squelch goes off.

When the Tone squelch decoder IC701 does not decode the input tone

signal frequency as the programmed frequency, pin13 goes to "High".

2. Encoder

The tone signal is output from pin16 of IC701, producing a frequency-

modulated RF output.

6) Microprocessor (CPU) and Peripheral Circuit

Refer to "Terminal Function of Microprocessor" about each terminal func

tion.

1, BS Mode When the Squelch is closed for more than 5 seconds, the radio goes into the

BS(Battery Save) mode automatically. Pin11 (R5C) and pin19 become High

or Low periodically. Open the Squelch, and the radio does not go into the

BS mode.

2. Backup Reset

When the voltage detector circuit lC303 detects a decrease in the C5V line,

CPU RAM data is stored in the EEPROM IC, IC601. IC 302 is also the

voltage detector circuit and it detects the lower voltage than IC303. The

circuit detects a increase in the C5V line when power is turned on, and then

the CPU will be initialized.

3. Reset

Press and holdthe."F" key, then turn on the power. The radio will reset to

initial factory settings.

Even if you expanded the frequency, it will return to the initial setting. To

resume the expanded frequency, press and hold the "F" and "Lamp" keys,

then turn on the power.

Page 6

Page 8

7) Terminal Function o f Microprocesser

Name I/O Description PinNo. PinName H L

TBST O 1750Hz Tone Burst Output 9 P57/PWM3 Normal:H(HiZ) Output:Pluse

BEEP O Beep Tone Output 10 P56/PW M 2 Normal:H(HiZ) Output:Pluse

R5C O RX 5V ON/OFF 11 P55/PWM1 ON OFF

T5C O TX5V ON/OFF 12 P54/PWM0 ON OFF

AFP O AF Power Amplifier ON/OFF 13 P53/SIG ON OFF

AFC O IF Mute Output 14 P52/CNT2 Mute OFF Mute ON

M.MUTE O Microphone Mute Output 15 P5l/CNT1

RE1 I Rotary Encoder Input 1 16 P50/INT3

LAMP O Lamp ON/OFF Switch 17 P37/SR DY ON OFF

BAT I Battery L ow Indicator Input 18 P36/CLK Low Normal

P5C O PLL Power ON/OFF 19 P35/SOUT ON OFF

EICD I EEPROM Unit Detection 20 P34/SIN Equipped Nothing

XW R I External EEPROM Write Cycle Detection 21 P33rr Normal Write cycle

RE2 I Rotary Encoder Input 2 22 P32/INT2

SCOM O Band Plan Scan Output 23 P3l/XCIN H(Hiz) Low Active

P.H/L O Transmit Power Switch 24 P30/XCOUT L ow Power High Power

BU I Back up Mode Input 25 INT1 Normal Negative Edge Triggered

RES I Reset Input 27 RESET at Work on Reset

TSQD I Tone Detecton Input 31 P17 Undetected Detected

TICD I Tone Unit D etection 32 P16 Nothing Equipped

BP1 I Band Plan(TX) 33 P15 Expanded Normal

BP2 I Band Plan(RX) 34 P14 Expanded Normal

BP3 I Band PIan(TX,RX) 35 P13 Expanded Normal

BP4 I Band Plan(Channelstep) 36 P12 Expanded Normal

BP5 I Band Plan(OffsetFreq.) 37 P11 Expanded Normal

CH I Band Plan(ChanneIDisp.) 38 P10 Expanded Normal

SLC O CIock for EEPROM IC 39 P07 Normal:Hiz Output: Pluse

SDA I/O Data for EEPROM IC 40 P06 Normal:Hiz Output: Pluse

CLK O Clock for PLL,TONE IC 41 P05 Output:Pluse Normal:L

DTA O Data for PLL,TONE IC 42 P04 Output:Pluse Normal:L

STB1 O Strobe for PLL IC 43 P03 Output:Pluse Normal:L

STB2 O Strobe for TONE IC 44 P02 Output:Pluse Normal:L

FUNC I Function Key Input 45 P0l OFF ON

SD I Signal Detection Input 46 P00 Received Nothing

TBST I Tone Burst Key Input 47 P27 OFF ON

CALL I CALL(APO) 48 P26 OFF ON

LAMP I LAM P (FLJPL) 49 P25 OFF ON

MONI I M ONl(P.H/L) 50 P24 OFF ON

TONE I TONE(MW ) 51 P23 OFF ON

V/M

T.SCAN I T.SCAN(CH STEP) 53 P2l OFF ON

PTT I PTT K ey Input 54 P20 OFF ON

COMO O Common Output 58 COM0

COM1 O Common Output 59 COM1

COM2 O Common Output 60 COM2

SEGO O Segment Output 62 SEGO

SEG1 O Segment Output 63 SEGl

SEG2 O Segment Output 64 SEG2

SEG3 O Segment Output 65 SEG3

SEG4 O Segment Output 66 SEG4

SEG5 O Segment Output 67 SEG5

SEG6 O Segment Output 68 SEG6

SEG7 O Segment Output 69 SEG7

SEG8 O Segment Output 70 SEG8

SEG9 O Segment Output 71 SEG9

SEG1O O Segment Output 72 SEG10

SEG11 O Segment Output 73 SEG11

SEG12 O Segment Output 74 SEG12/P43

SEG13 O Segment Output 75 SEG13/P42

SEG14 O Segment Output 76 SEGl4/P4l

SEG15 O Segment Output 77 SEG15/P40

SEG16 O Segment Output 78 SEG16/IN7

SEG17 O Segment Output 79 SEG17/IN6

SEG18 O Segment Output 80 SEG18/IN5

SEG19 O Segment Output 1 SEG19/1N4

SEG2O O Segment Output 2 SEG20/IN3

SEG2l O Segment Output 3 SEG21/IN2

SEG22 O Segment Output 4 SEG22/IN1

SEG23 O Segment Output 5 SEG23/IN0

Clock Input 3.58MHz 28 XIN

Clock Output 3.58MHz 29 XOUT

Ground 30 Vss

I V/M(OFFSET) 52 P22 OFF ON

Ground 6 AVss

+4V 7 Vref

+4V 8 Vcc

26 CNVss

55 VL3

56 VL2

57 VL1

61 COM3

during Tone Burst

Tansmission Normal

Page 7

Page 9

SEMICONDUCTOR DATA

1) LR408721 (XA0042)

Tone Dialer

V+[

1 ^ 18

1 Non Connect

Test Circuit

3.5-1 OV 0 LR408721

3.58MHz JT~

—IDhj—

X

----

1 18

2

3 16

4

5 14

6 13

7

8 11

9

17

15

12

10

2) M5218FP (XA0068)

Dual Low Noise

Operational Amplifiers

Row Tone 400mV rms

ColumnTone 500mV rms

-O

0C

f1=697Hz

f2=770Hz

f3=852Hz

f4=941 Hz

f5=1209Hz

f6=1336Hz

f/= 14 //H z

f8=1633Hz

XMRT I

Switch

COL1 d

COL2I

COL3 [

OSCin

OSCout

Output 1

V+I

1 l=

2 17

3 16

4 ^ 15

3J

5 co 14

's!

I\J

6 - 1 13

7 12

8 11

9 10 Z D COL4

1 Tone out

1 Single Tone Inhibit

Z D ROW1

Z D ROW2

Z D ROW3

Z D ROW4

I Mute Out

| 8 Power Supply Plus

3) M5236ML (XA0104)

Voltage Regulator

Test Circuit

Inverting Input 1

Non Inverting Input 1

Power Supply Minus

2 IZ Z

3 1=

4 IZ Z

r r m r

VREF GND VIN

M5236ML

| 7 Output 2

| 6 Inverting Input 2

| 5 Non Inverting Input 2

10

Page 10

4) MB1504LPF-G-BND-TF (XA0145)

Frequency Synthesizer

Function Table

FC input P.D.input

Do output

High or Low

Reference

oscillator input

terminal

Reference

oscillator output

terminal

Power supply

terminal for

r h a r n e m im n

w. y w

Power supply

terminal

3V 15mA

Charge pump

output terminal

Ground terminal

Phase detector output

terminal I D t

when locked: LD=H

Prescaler input

terminal

OSCinl— 1

OSCout I—

Vp C Z

Vcc I

noi—

GNDI

fin C ^

High

High

Low

Low

---

fr=fp HiZ

fr>fp High

fr<fp

Low

fr>fp Low

fr<fp

2

3

4

5

6

7

8

High

JoR

16

I0P

15

Ifp

14

13

Z J F C

12

11

I LE

I Data Serial data input

10

I Clock

9

Phase detector output

terminal for external

charge pump

Phase detector output

terminal for external

charge pump

Programmable

divider output

terminal

Reference divider

output terminal

Phase switch input

terminal of phase

comparator

Load enable signal

input terminal

terminal

Clock input

terminal

5) MC3357 (XA0063)

Narrow Band FM IF IC

Vcc=6V

F=10.7MHz

3mA

Icc

Limit

Vo

5|iV

350mV

-3dB

Dev=+/-3KHz

11

Page 11

6) MX365 (XA0203)

CTCSS Encoder/Decoder

---

1 I I 2

33p a P ,

1MHz

MX365ADW

Vdd

Xtal Clock inpul

---

Xtal

Load /Latch

D5

D4

D3

D2

D1

DO RX DETECT

Vss

COMP.REF

TONE IN

RX AUD IN

BIAS

TX AUD OUT

RX AUD OUT

PTL

RX/TX

TONE OUT

DECODE

COMP IN

RX DECODE

i 4

23

¥ -

21

20

19

17

16

15

14

13

0.1*iF

0

0.1 H F

0 4 7 ^ F

11 1

0 1^ F " r

0 1^F

0.1(.iF

56 0 K

~ p ° n

1 1 1 "

I s

Decode Comparator Ref: This pin is internally biased

to VDD/3 or 2VDD/3 via 1M resistors depending on the

logical state of the Rx Tone Decode Out pin. Rx Tone

Decode Out = 1 will bias bias this input 2VDD/3; a logic

"0" will bias this input VDD/3. This input provides the

decode comparator reference voltage, and switching of

bias voltages provides hysteresis to reduce "chatter"

under marginal conditions.

RX Tone Decode Out: This is the gated output of the

decode comparator. This output is used to gate the RX

Audio path. A logic "0" on this pin indicates a successful

decode and that the Decode Comparator Input pin is

more positive than the Decode Comparator Ref. input.

Decode Comparator Input: This is the inverting input

of the decode comparator. This pin is normally

connected to the integrated output of the Rx Tone Detect

line.

Rx Tone D etect: In Rx mode this pin will go to logic '11

during a successful decode. It must be externally

integrated to control response and deresponse times.

Tx Tone Out: The CTCSS sinewave output appears on

this pin under the control of the Rx/Tx pin. This pin,

when not transmitting a tone, may be biased to VDD/2 -

0.7V or O/C .

Rx/Tx: This input (in parallel mode) selects Rx or Tx

modes . In serial mode this function is serially loaded.

This pin is internally pulled to VDD via a 1 M ii resistor.

PTL: in paraiiei Rx mode this pin operates as a 'Press

To Listen' function by enabling the Rx audio path, thus

overriding the tone squelch function. In parallel Tx mode

this pin reverses the phase of the transmitted CTCSS

tone (used for squelch tail elimination). In serial mode

this function is serially loaded.

Rx Audio Out: This is the high pass filtered receive

audio output pin. This pin outputs audio when Rx TONE

DECODE = 0, or PTL = 1, or when Notone is

programmed. In Tx mode this pin is biased to VDD/2.

Tx Audio Out: This is the high pass filtered transmit

audio output pin. In Tx mode this pin outputs audio

present at the Tx Audio Input pin. In Rx mode this pin is

biased to VDD/2.

Bias: This pin is the output of an internally generated

VDD/2 bias level and would normally be externally

decoupled to Vss via C7.

Tx Audio In: This Is the Tx Audio input pin. In Tx mode

It may be prefiltered, using the Tx audio path, thus

helping to avoid talk off due to intermodulation of speech

frequencies with the transmitted CTCSS tone. This pin

is internally biased to VDD/2.

Rx Audio In: This Is the input to the audio high pass

filter in Rx mode. It is internally biased to VDD/2.

Tone Input: This is the Input to the CTCSS tone

detector. It is Internally biased to VDD/2.

12

Page 12

7) NJM386 (XA0061)

Dual Power Amplifiers

V+=9V RL=16£2 Po=500mW

V+

8) RH5VA32AA-T1 (XA0198)

C-MOS Voltage Detector

/> N

____

C\J

O

U U ..EF

OUT VDD VSS

Gain

-Input

+lnput

GND

1 1=

2 d

3 C

4 [ =

o

z

c_

2

CO

00

o>

I Z I 8

1=17

= □ 6 Vs

= □ 5

Equivalent Circuit

Gain

Bypass

Vout

RH5VA32AA

9) RH5VA45AA-T1 (XA0208)

C-MOS Voltage Detector

in

Û

u u.nr

OUT VDD VSS

RH5VA45AA

Equivalent Circuit

13

Page 13

10) X24C01A (XA0199)

EEPROM 1024Bit

Pin Names

AO Vcc

A1

X24C01A

A2

Vss

WC

SCL

SDA

11) X24C04S14 (XA0200)

EEPROM 4096Bit

NC NC

AO Vcc

A1 TEST

NC

A2

X24C04

NC

SCL

AO - A2

SDA Serial Data

SCL Serial Clock

WC

Vss

Vcc

Address inputs

Write Control

Ground

+5V

Pin Names

AO ~ A2

SDA Serial Data

SCL

TEST

Vss

Vcc

NC

Address inputs

Serial Clock

Hold at Vss

Ground

+5V

No Connect

Vss SDA

NC NC

12) X24C16S14 (XA0201)

EEPROM 16384Bit

NC NC

AO

A1

NC

A2

Vss

NC

X24C16

Vcc

TEST

NC

SCL

SDA

NC

Pin Names

AO ~ A2

SDA

SCL Serial Clock

TEST

Vss

Vcc

NC

Address inputs

Serial Data

Hold at Vss

Ground

+5V

No Connect

14

Page 14

13) Transistor, Diode and LED Outline Drawings

15

Page 15

co

m

O

S

m

z

S17

S16

S14

S13 _

S12

S10

S9

S8

S6

S5

S4

@ c o

^ 5 4 !

S18

S21

S22

S23

S19

S15

S11

S7

S3

COMO

COM1

S2

S1

^om CQ

COM2

SO

Page 16

o

o

s

s

o

z

14) LCD Connection

Page 17

EXPLODED VIEW

1) Rear Case 1

UE0029A

2) LCD Assembly

KB0038

ST0031

17

Page 18

Page 19

4) Front Case 1

FG0092(180T/E)

FG0112(1400..)

FG0129(1400AN/QN)

AK0001

V

NB0047A

Key pad panel (DJ180...) (PAGE 22)

Ten key Cover (DJ1400..)

19

Page 20

5) Front Case 2

FG0094

YZ0116

DP0063

S DP0111 (1400AN/QN)

VZ0117 (1400, A, B)

KM0141 (1400, A, B)

2 0

Page 21

6) Rear Case 3 and Battery Terminal

AK0004

(Torque =4.5kgcm)

AK0004

(Torque ;4.5kgcm ) A K m 4

* (Torque =4.5kgcm)

DS0357 (DJ180T)

DS0388

AK0001 (Torque =2.0kgcm)

• Insert the tip of the battery terminal into

the hole of battery release knob.

^ a k u u u i(I orque =z.uK g c m j /

AK0001 (Torque =1.2kgcm) r ( Battery terminal

\

AK0001 (Torque =1,2kgcm)

\

NB0047 AZ

Page 21

Page 22

7) Ten Key Cover and Key Pad Panel

Ten Key Cover (180EB, 1400 ...)

Key Pad Panel

Page 23

8) CTCSS Unit and R0M1 Unit

Model No.

Destination

CTCSS Unit

ROM1 Unit

T TA

1

1

DJ-180

TB TS TZ E

1 1 1

1 1

1 1 1

1 0 0

EA

1

DJ-1400

EB

1 1 0

0

1 1 1

A B

1

AN QN

1 1

1 1

Page 24

PC BOARD VIEW

1) VCO Unit

Side A

iRO^y

i R2 !0 IR

221 | R212 |1 0 1 1 R2Q1 | j~C2ÖT

1(»

I

-----E----

C L?01 [n 1SV217 1SV217 I ^ i

L206

2.51 Ob

(QKA2SC)

685/6.3V

C21Q |

2) Jack Unit

2SC4099

| Q202 I

Li t J

020

-1 ^ j P 20 11 g P 2 0 2 j r .ü r ,

2SC3356

n n

8 8

104

ln £

ICC I'”

c|

©

L

3

2SC40Ö1

R204 |

QA0081 S

| C203 |

102

Side A

C211

^ | R2C7 |

472

Q201

LT

X r

»

8

er

8

O CM

----1

SideB

Side B

JK502

KS Jt423-01-050

(UJ0016)

3) PTT Unit Side B

JK501

HSJ1102-01-640

(IJJ00 22)

Page 25

4) PS Unit

Side A UP0220 (1/2)

Side B

5) R0M1 Unit Side B UP0220 (1/2)

1C601

X24C01AS

-3.0T :

V_

6) R0M2 Unit Side B (EJ-14u / EJ- 15u)

X24C04S14-3.0T (EJ14U)

X24C16S14-3.0T (EJ19Ü)

UP0220 (1/2)

25

Page 26

7) RF Unit Side A (UP0221) 1/2

i R/ t I

222

26

Page 27

8) RF Unit Side B

UP0221 (1/2)

106/6.3V

105/16V

CM _

J

a:

a

__

o

a

c c

cs j

• - ■ - •

1 m

in

°

(M

223

rme

103

1C 2

MB1504L

t R85

{ C129 I

101

C128 i C127 )

101

cvi n

o J

n n

i UN2214

ÍC167

(

-

CD

102

Si

cv

£

□

3 «

5

CM

<VI

£

Q21

2SA12 ■

D

<C «a

oS

t i u

] R131 1

27

Page 28

9) CPU Unit Side A upo22o (1/2)

n n , - •

0 3 0 5 « ! ” ■ -

\ M - ■ * t - ,

SLM -13MW

NTB TB

W3O3

TX

IR3/4 I OOP

{H37§300@’

>376 l OflO

■YOOI5

KUC2223

-01-0030

Model No.

-^ - ^ D e s tin ation

Ref.

TX (TX Exp.) 0

RX (RX Exp.)

TRX (TX/RX Exp.) 1 1 1

R376

28

T TA TB

TS

0 0 0 0

0 0 0 0 0

0 0

DJ-180

TZ E EA EB TA2 TB2 TM TSA A B

1

0 0 0 0

1

0 0 0 0 0 0 0 0 0 0 0 0

0 0

0

1 1 1

0

0 0

1 1 1 1

0

DJ-1400

0 0 0 0 0

F

G

1 1

TM

AN QN

- -

-

1 1

W3O3

-

W3O3

Page 29

10) CPU Unit SideB UP0220 (1/2)

|Q3Q1_j 6Si

u U IR310

2SC4081

-------

r

o

D301

U L J

104

jC301

CO

s:

IR338

333

1R334

.

)

IC30T

M37410M4H331FP

105 f R311

681 [R319 j

l R322 l fR32i~

[R323

rn

LO

°

s

CC

n

Q302

t r u

UN2£14

Q303

t r r r

UN211H

n .

CN304

TFl608-Pi28G05

-JS.!.WO- I

C\J

102 , n n

{ R306

333

333

D309

m a r

t03

IR317 }

' ' " 8

102 "

j R313

102

t

_

:co

, . OJ

O__D 102

D308

U

1SS226

CN302

DF9A-9S-1V

5 C

Q r

CO*-1

o

11 ß

3.

I w

IR331 |

\ R332 I

-TX-

fC304

TT T TTT *

n

f*-

RH5VA32AA

03

o

j R329 l 123

474 IR345

IC303

RH5VA45ÄA

472

1R320

LJ

IR303 |

ür>

1

105

IR316 |

CN303

DF9A-11S-1V

103

• c

s

§

..cE

W302

MTCK03AA

Brown

r>

W301

MPCKH8AA

Pink

29

Page 30

11) RE Unit

Side A UP0221 (1/2)

12) CTCSS Unit (EJ-17u)

Side A UP0221 (1/2) SideB

r CN701 5 4 / ] ; % ^ i .

DF9A-11P-1V , '' " i f ] !

Side B

i

RE1

RK09710HH5RH220

(UU0007)

X701

CSB1

XB0001

Soldering

Soldering

\jSr|SWo2 <

S f C p i l

CSJ*—1

-------

—

I 'iifb'i '

l

105

: TT

•

IC 701

MX365ADW-rR

" * - = U

474/25V 1fU

C705 § . | 0703 |

1 £

-Soldering

CO

C\J h -

CM Q £

If)

o

N-

£ i

-rn

8

l i

152

f l T o T j

r i i

| Q701

■ I * ' 1

2SC2412

VR701

3 J p

| R/Otf

IS .'

s

<E>

N.

a?

o

| R708

824

I C710

30

Page 31

13) DTMF Unit (EJ-13u)

Side A

p lu g

LJ

XN1A312

J

To CPU unit CN3Q6

YeMow

Pink

Red

Brown

fflafifc

IC 401

•

LR4Q87P1

Side B

[ R401

<s

^ u °

s5®

SS8

CC

O

473

m r

U - Q j

VR401 i

w

31

Page 32

PARTS LIST

Ref No |Parts No.

C301 CU3059 Chip C. C1608JF1E104ZT-A

C302 CS0333 Chip Tantal ECST0JV686R

C303 CU3047 Chip C. C1608JB1H103KT-A

C304 CS0277 Chip Tantal ECST1CY105R

C305 CU3047 Chip C. C1608JB1H103KT-A

C306 CU3051 Chip C. C1608JB1E223KTA

C307 CU3051 Chip C. C1608JB1E223KT-A

C308 CU3085 Chip C. C1608CH1H300JT-A

C309 CU3085 Chip C. C1608CH1H300JT-A

C310 CU3035 Chip C. C1608JB1H102KT-A

CN301 UE0143 Connector AXN93030001

CN302 UE0129 Connector DF9A-9S-1 V (22)

CN303 UE0130 Connector DF9A-11S-1V (22)

CN304 UE0147 Connector TE 1608-PI28G05

CN305 UE0144 Connector TE 1208-Pl28G02

CN306 UE0147 Connector TE 1608-PI28G05

D301 XD0134 Diode RB450FT106

D302 XD0057 Diode 1SS184

D305 XL0016 LED SLM-1 3MWSFT96B

D307 XD0103 Diode 1SS226TE85L

D308 XD0103 Diode 1SS226TE85L

D309 XD0103 Diode 1SS226TE85L

IC301 XA0222 IC M37410M4H331 FP

IC301 XA0508 IC M37410M4H332 FP

IC303 XA0208 IC RH5VA45AA-T 1

IC304 XA0198 IC R H 5VA32AA-T 1

Q301 XT0095 Trangistor 2SC4081T106R

Q302 XU0038 Trangistor UN2214-TX

Q303 XU0040 Trangistor UN211H-TX

Q304 XU0038 Trangistor UN2214-TX

Q305 XT0095 Trangistor 2SC4081T106R

R301 RK3054 Chip R. ERJ3GSYJ223V

R302 RK3050 Chip R. ERJ3GSYJ103V

R303 RK3052 Chip R. ERJ3GSYJ153V

R303 RK3055 Chip R. ERJ3GSYJ273V

R304 RK3058 Chip R. ERJ3GSYJ473V

R307 RK3031 Chip R. ERJ3GSYJ271V

R309 RK3074 Chip R. ERJ3GSYJ105V

R310 RK3056 Chip R. ERJ3GSYJ333V

R311 RK3074 Chip R. ERJ3GSYJ105V

R312 RK3038 Chip R. ERJ3GSYJ102V

R313 RK3038 Chip R. ERJ3GSYJ102V

R314 RK3056 Chip R. ERJ3GSYJ333V

R315 RK3056 Chip R. ERJ3GSYJ333V

R316 RK3074 Chip R. ERJ3GSYJ105V

R317 RK3050 Chip R. ERJ3GSYJ103V

R318 RK3038 Chip R. ERJ3GSYJ102V

R319 RK3036 Chip R. ERJ3GSYJ681V

R320 RK3046 Chip R. ERJ3GSYJ472V

R321 RK3062 Chip R. ERJ3GSYJ104V

R322 RK3058 Chip R. ERJ3GSYJ473V

Q

o

e

s

CPU Unit UP0220 1/2

Parts Name Ver

niori

-

AN/QN

AN/QN

CPU Unit PS Unit

Ref No Parts No. Description Parts Name Ver

R323 RK3058 Chip R. ERJ3GSYJ473V

R324 RK3058 Chip R. ERJ3GSYJ473V

R325 RK3062 Chip R. ERJ3GSYJ104V

R326 RK3052 Chip R. ERJ3GSYJ153V

R327 E

R328 T/1400

R329 RK3070 Chip R. ERJ3GSYJ474V

R330 RK3038 Chip R. ERJ3GSYJ102V

R331 RK3038 Chip R. ERJ3GSYJ102V

R332 RK3038 Chip R. ERJ3GSYJ102V

R334 RK3052 Chip R. ERJ3GSYJ153V

R338 RK3056 Chip R. ERJ3GSYJ333V

R345 RK3051 Chip R. ERJ3GSYJ123V

R362 RK3046 Chip R. ERJ3GSYJ472V

-

R371

-

R372

-

R373

R374 RK3001 Chip R. ERJ3GSY0R00V

R375 RK3001 Chip R. ERJ3GSY0R00V

R376 RK3001 Chip R. ERJ3GSY0R00V

X301 XB0008 Crystal CSAC3.58MGC-TC

W301 MPCKH8AA Wire DJ-180 J301 (T series) T

W302 MTCK03AA Wire DJ-180 J302 (E series) E

W303 MPCK03AA Wire DJ-180 J302 (1400 series 1400

EL0020A LCD DJ145 (E/1400 series)

EY0015 Microphone KUC2223-01 -0030

FF0022 Cloth(BLIND LCD)

DH0008 Lighting plate

FG0099 Rubber Connector

ST0031 LCD Flame

PS Unit UP0220 1/2

W901 UX1034 Wire DJ145

AF0020 02+3FeNi

FM0063 Rear Case

SD0025 Plus Terminal

YZ0044 Screw Lock 1401C

E

E

T/1400

Page 32

Page 33

Ref No |Parts No. Description Parts Name Ver

ROM1 Unit UP0220 1/2 all

CN601 UE0132 Connector DF9A-9P-1V

IC601 XA0363 IC AT24C01A-10SI-2.7

R601 RK3062 Chip R. ERJ3GSYJ104V

R602 RK3062 Chip R. ERJ3GSYJ104V

DTMF Unit UP0220 1/2

C401 CS0256 Chip Tantal ECST1AY225R DJ180

C403 CU3047 Chip C. C1608JB1H103KT-A DJ180

IC401 XA0042 IC LR408721 DJ180

Q401 XU0041 Digital T. XN1A312-TX DJ180

R401 RK3058 Chip R. ERJ3GSYJ473V DJ180

R402 RK3058 Chip R. ERJ3GSYJ473V DJ180

VR401 RH0103 Trim.Pot EVM1YSX50B14 DJ180

W401 UX1036 Wire DJ-145N DJ180

X401 XB0001 Crystal FARC4CA 03580000K0 1 R DJ180

AF0020 02+3FeNi DJ180

FG0101AZ SiliconTenKey DJ180

KM0138 Keypad Panel DJ180

TW0003 Water Proof Cushion

KM0136 Keypad Panel 1400

ROM1 Unit / DTMF Unit / RF Unit

Ref No 1 Parts No. Description Parts Name Ver

RF Unit UP0221

C2 CU3004 Chip C. C1608CH1H030CT-A

C3 CU3018 Chip C. C1608CH1H390JT-A

C4 CU3003 Chip C. C1608CH1H020CT-A

C5 CU3017 Chip C. C1608CH1H330JT-A

C6 CU3023 Chip C. C1608CH1H101JT-A

C7 CU3013 Chip C. C1608CH1H150JT-A

C8 CU3025 Chip C. C1608CH1H151JT-A

C10 CU3015 Chip C. C1608CH1H220JT-A

C11 CU3017 Chip C. C1608CH1H330JT-A

C12 CU3003 Chip C. C1608CH1H020CT-A

C13 CU3035 Chip C. C1608JB1H102KT-A

C14 CU3035 Chip C. C1608JB1H102KT-A

C15 CU3017 Chip C. C1608CH1H330JT-A

C16 CU3003 Chip C. C1608CH1H020CT-A

C17 CU3017 Chip C. C1608CH1H330JT-A

C25 CU3059 Chip C. C1608JF1E104ZT-A

C26 CU3047 Chip C. C1608JB1H103KT-A

C27 CU3035 Chip C. C1608JB1H102KT-A

C28 CU3004 Chip C. C1608CH1H030CT-A Wide

C28 CU3011 Chip C. C1608CH1H100DT-A Narrow

C29 CU3047 Chip C. C1608JB1H103KT-A

C30 CU3035 Chip C. C1608JB1H102KT-A

C31 CU3006 Chip C. C1608CH1H050CT-A

C32 CU3035 Chip C. C1608JB1H102KT-A

C33 CU3035 Chip C. C1608JB1H102KT-A

C34 CU3013 Chip C. C1608CH1H150JT-A

C35 CU3013 Chip C. C1608CH1H150JT-A

C36 CU3035 Chip C. C1608JB1H102KT-A

C37 CU3035 Chip C. C1608JB1H102KT-A

C38 CU3035 Chip C. C1608JB1H102KT-A

C39 CU3035 Chip C. C1608JB1H102KT-A

C40 CU3035 Chip C. C1608JB1H102KT-A

C41 CU3035 Chip C. C1608JB1H102KT-A

C42 CU3015 Chip C. C1608CH1H220JT-A

C43 CU3013 Chip C. C1608CH1H150JT-A

C44 CU3035 Chip C. C1608JB1H102KT-A

C45 CU3035 Chip C. C1608JB1H102KT-A

C46 CU3015 Chip C. C1608CH1H220JT-A

C46 CU3013 Chip C. C1608CH1H150JT-A

C47 CU3016 Chip C. C1608CH1H270JT-A

C48 CU3019 Chip C. C1608CH1H470JT-A

C48 CU3018 Chip C. C1608CH1H390JT-A

C49 CU3035 Chip C. C1608CH1H102KT-A

C50 CU3035 Chip C. C1608JB1H102KT-A

C51 CU3035 Chip C. C1608JB1H102KT-A

C52 CU3035 Chip C. C1608JB1H102KT-A

C53 CU3035 Chip C. C1608JB1H102KT-A

C54 CU3035 Chip C. C1608JB1H102KT-A

C55 CU3035 Chip C. C1608JB1H102KT-A

C56 CU3017 Chip C. C1608CH1H330JT-A

C56 CU3016 Chip C. C1608CH1H270JT-A

C57 CU3023 Chip C. C1608CH1H101JT-A

C58 CU3035 Chip C. C1608JB1H102KT-A

C59 CU3017 Chip C. C1608CH1H330JT-A

C59 CU3016 Chip C. C1608CH1H270JT-A

C60 CU3002 Chip C. C1608CH1H010CT-A

C61 CU3002 Chip C. C1608CH1H010CT-A

C62 CU3005 Chip C. C1608CH1H040CT-A

/ c

T 2

Cö T

QN/TA

2/TB2

QN/TA

2/TB2

QN/TA

2/TB2

Page 33

M A

Page 34

RF Unit

Ref No Parts No. Description Parts Name Ver

C63 CU3005 Chip C. C1608CH1H040CT-A

C64 CU3017 Chip C. C1608CH1H330JT-A

C65 CE0204 Chip Tantal ECEA1CKA107

C67 CU3035 Chip C. C1608JB1H102KT-A

C68 CU3035 Chip C. C1608JB1H102KT-A

C69 CS0277 Chip Tantal ECST1CY105R

C70 CU3035 Chip C. C1608JB1H102KT-A

C71 CU3035 Chip C. C1608JB1H102KT-A

C72 CU3035 Chip C. C1608JB1H102KT-A

C75 CU3059 Chip C. C1608JF1E104ZT-4

C76 CU3035 Chip C. C1608JB1H102KT-A

C80 CU3021 Chip C. C1608CH1H680JT-A

C81 CU3015 Chip C. C1608CH1H220JT-A

C82 CU3059 Chip C. C1608JF1E104ZT-4

C83 CU3059 Chip C. C1608JF1E104ZT-4

C84 CU3024 Chip C. C1608CH1H121JT-A

C85 CU3035 Chip C. C1608JB1H102KT-A

C86 CU3019 Chip C. C1608CH1H470JT-A

C87 CU3035 Chip C. C1608JB1H102KT-A

C88 CU3047 Chip C. C1608JB1H103KT-A

C89 CU3047 Chip C. C1608JB1H103KT-A

C90 CU3047 Chip C. C1608JB1H103KT-A

C91 CU3059 Chip C. C1608JF1E104ZT-4

C92 CS0277 Chip Tantal ECST1CY105R

C93 CU3029 Chip C. C1608JB1H331KT-A

C94 CU3035 Chip C. C1608JB1H102KT-A

C95 CU3035 Chip C. C1608JB1H102KT-A

C96 CS0307 Chip Tantal ECST1VY104R

C97 CU3051 Chip C. C1608JB1E223KT-A

C98 CU3059 Chip C. C1608JF1E104ZT-4

C99 CU3059 Chip C. C1608JF1E104ZT-4

C100 CS0331 Chip Tantal ECST0JC336R

C101 CU3047 Chip C. C1608JB1H103KT-A

C102 CU3059 Chip C. C1608JF1E104ZT-A

C103 CU3059 Chip C. C1608JF1E104ZT-4

C104 CU3047 Chip C. C1608JB1H103KT-A

C105 CU3039 Chip C. C1608JB1H222KT-A

C106 CS0277 Chip Tantal ECST1CY105R

C107 CU3059 Chip C. C1608JF1E104ZT-4

C108 CE0307 Chip Tantal ECEV0JA476P

C109 CU3051 Chip C. C1608JB1E223KT-A

C110 CE0307 Chip Tantal ECEV0JA476P

C111 CU3035 Chip C. C1608JB1H102KT-A

C112 CU3035 Chip C. C1608JB1H102KT-A

C113 CS0277 Chip Tantal ECST1CY105R

C114 CU3035 Chip C. C1608JB1H102KT-A

C120 CS3011 Chip Tantal C1608CH1H100DTA

C121 CU3035 Chip C. C1608JB1H102KT-A

C122 CU3002 Chip C. C1608CH1H010CT-A

C124 CU3CN)2 Chip C. C1608CH1H010CT-A

C125 CS0277 Chip Tantal ECST1CY105R

C126 CU3011 Chip C. C1608CH1H100DT-A

C127 CU3023 Chip C. C1608CH1H101JT-A

C128 CU3023 Chip C. C1608CH1H101JT-A

RF Unit

Ref No Parts No. Description Parts Name Ver

C129 CU3023 Chip C. C1608CH1H101JT-A

C130 CU3035 Chip C. C1608JB1H102KT-A

C131 CS0329 Chip Tantal ECS0JX106R

C132 CU3016 Chip C. C1608CH1H270JT-A

C133 CU3017 Chip C. C1608CH1H330JT-A

C134 CS0329 Chip Tantal ECS0JX106R

C135 CS0256 Chip Tantal ECS1AY225R

C136 CU3047 Chip C. C1608JB1H103KT-A

C137 CS0258 Chip Tantal ECST1AX475R

C138 CU3047 Chip C. C1608JF1E104ZT-4

C139 CS0307 Chip Tantal ECST1VY104R

C140 CU3059 Chip C. C1608JF1E104ZTA

C141 CU3051 Chip C. C1608JB1E223KT-A

C142 CU3051 Chip C. C1608JB1E223KT-A

C143 CS0277 Chip Tantal ECST1CY105R

C144 CU3019 Chip C. C1608CH1H470JT-A

C145 CS0277 Chip Tantal ECST1CY105R

C146 CS0277 Chip Tantal ECST1CY105R

C147 CU3059 Chip C. C1608JF1E104ZTA

C148 CU3047 Chip C. C1608JB1H103KT-A

C149 CU3059 Chip C. C1608JF1E104ZT-A

C150 CU3035 Chip C. C1608JB1H102KT-A

C151 CU3035 Chip C. C1608JB1H102KT-A

C152 CU3024 Chip C. C1608CH1H121JT-A

C153 CU3039 Chip C. C1608JB1H222KT-A

C154 CU3035 Chip C. C1608JB1H102KT-A

C155 CU3035 Chip C. C1608JB1H102KT-A

C156 CU3035 Chip C. C1608JB1H102KT-A

C157 CU3047 Chip C. C1608JB1H103KT-A

C158 CU3035 Chip C. C1608JB1H102KT-A

C159 CU3035 Chip C. C1608JB1H102KTA

C160 CU3035 Chip C. C1608JB1H102KT-A

C161 CU3035 Chip C. C1608JB1H102KT-A

C162 CU3035 Chip C. C1608JB1H102KT-A

C163 CU3035 Chip C. C1608JB1H102KT-A

C164 CS0331 Chip Tantal ECST0JC336R

C165 CS0277 Chip Tantal ECST1CY105R

C166 CU3035 Chip C. C1608JB1H102KT-A

C167 CU3047 Chip C. C1608JB1H103KT-A

C168 CU3035 Chip C. C1608JB1H102KT-A

CN1 UE0143 Connector AXN93030001

D1 XD0066 Diode RLS135-TE-11

D2 XD0066 Diode RLS135-TE-11

D3 XD0233 Diode 1SV217TPH4

D4 XD0233 Diode 1SV217TPH4

D5 XD0233 Diode 1SV217TPH4

D6 XD0233 Diode 1SV217TPH4

D7 XD0066 Diode RLS135-TE-11

D8 XD0120 Diode MA704WKTX

D10 XD0057 Diode 1SS184TE85L

D11 XD0147 Diode DTZ2.4ATT11

D12 XD0129 Diode 1SS318TT11

Page-34

Page 35

RF Unit RF Unit

Ref No Parts No. Description Parts Name Ver

D13 XD0118 Diode MA716-TW

D14 XD0137 Diode DTZ6.2ATT11

D15 XD0272 Diode 1SS356 TW11

FB1 QB0008 Ferrite Bead HF30ACB201 209-T

FB2 QB0008 Ferrite Bead HF30ACB201 209-T

FL1 XC0004 Fitter CFUM455E Wide

FL1 XC0006 Fitter CFUM455G Narrow

IC1 XA0063 IC MC3357DR

IC2 XA0145 IC MB1504LPF-G-BND-TF

IC3 XA0061 IC NJM386M.T1

IC4 XA0068 IC M5218FP-TO1-1

IC5 XA0104 IC M5236 M L-T73A-36

L1 QKA35D Coil MR3.0-3.5T-0.6

L2 QKA35D Coil MR3.0-3.5T-0.6

L3 QKA45D Coil MR3.0-4.5T-0.6

L4 QA0079 RF Coil QA0079

L5 QA0078 RF Coil QA0078

L6 QA0078 RF Coil QA0078

L7 QA0078 RF Coil QA0078

L9 QC0010 Chip L. MLF3216E100M

L10 QC0009 Chip L. MLF3216DR10M

L11 QC0139 Chip L. MLF3216DR22M

L12 QKA45D Coil MR3.0-4.5T-0.6

L13 QKA35D Coil MR3.0-3.5T-0.6

L14 QKA35D Coil MR3.0-3.5T-0.6

L15 QKA15D Coil MR3.0-1.5T-0.6

L16 QKA25D Coil MR3.0-2.5T-0.6

L17 QC0003 Chip L. MLF3216A1R0M

L18 QKA25D Coil MR3.0-2.5T-0.6

L19 QKA15C Coil MR2.5-1.5T-0.5

L19 QKA15B Coil MR2.0 1.5T 0.5 QN

Q1 XE0009 FET 2SK302-GR(TE85L)

Q2 XE0009 FET 2SK302-GR(TE85L)

Q3 XT0096 Transistor 2SC4099T1 06N

Q4 XT0030 Transistor 2SC3356T1BR24/25

Q5 XT0030 Transistor 2SC3356T1BR24/25

Q6 XT0052 Transistor 2SC2053

Q7 XT0101 Transistor 2SC1971

Q8 XU0035 Transistor XN1214-TX

Q9 XU0037 Transistor UN2215-TX

Q10 XT0068 Transistor 2SA1162GRTE85L

Q11

Q12 XT0095 Transistor 2SC4081T106R

Q13 XT0095 Transistor 2SC4081T106R

Q14 XT0095 Transistor 2SC4081T106R

Q15 XT0088 Transistor 2SA1213YTE12L

Q16 XU0038 Transistor UN2214TX

Q17 XT0097 Transistor 2SC4393TE85R

Q18 XT0096 Transistor 2SC4099T1 06N

Q19 XU0039 Transistor UN211L-TX

Q20 XT0088 Transistor 2SA1213YTE12L

XU0034 Transistor XN1401-TX

Ref No Parts No. Description Parts Name Ver

Q21 XT0088 Transistor 2SA1213YTE12L

Q22 XU0038 Transistor UN2214-TX

Q23 XU0036 Transistor XN111F-TX

Q24 XU0035 Transistor XN1214-TX

R1 RK3074 Chip R. ERJ3G3YJ105V

R2 RK3074 Chip R. ERJ3G3YJ105V

R3 RK3018 Chip R. ERJ3GSYJ220V

R4 RK3018 Chip R. ERJ3GSYJ220V

R5 RK3074 Chip R. ERJ3G3YJ105V

R6 RK3074 Chip R. ERJ3G3YJ105V

R7 RK3042 Chip R. ERJ3GSYJ222V

R8 RK3022 Chip R. ERJ3GSYJ470V

R9 RK3050 Chip R. ERJ3GSYJ103V

R11 RK3038 Chip R. ERJ3GSYJ102V wide

R11 RK3037 Chip R. ERJ3GSYJ821V narrow

R12 RK3072 Chip R. ERJ3GSYJ684V

R13 RK3038 Chip R. ERJ3GSYJ102V

R15 RK3001 Chip R. ERJ3GSY0R00V

R16 RK3050 Chip R. ERJ3GSYJ103V

R17 RK3046 Chip R. ERJ3GSYJ472V

R18 RK3030 Chip R. ERJ3GSYJ221V

R19 RK3038 Chip R. ERJ3GSYJ102V

R20 RK3034 Chip R. ERJ3GSYJ471V

R21 RK3034 Chip R. ERJ3GSYJ471V

R22 RK3010 Chip R. ERJ3GSYJ4R7V

R23 RK3034 Chip R. ERJ3GSYJ471V

R24 RK3010 Chip R. ERJ3GSYJ4R7V

R25 RK3028 Chip R. ERJ3GSYJ151V

R26 RK3026 Chip R. ERJ3GSYJ101V

R27 RK1108 Chip R. ERJ8GEYJ4R7V

R28 RK3022 Chip R. ERJ3GSYJ470V

R29 RK0022 Chip R. ERJ6GEYJ221V

R30 RK3058 Chip R. ERJ3GSYJ473V

R31 RK3058 Chip R. ERJ3GSYJ473V

R33 RK3053 Chip R. ERJ3GSYJ183V

R34 RK3042 Chip R. ERJ3GSYJ222V

R36 RK3054 Chip R. ERJ3GSYJ223V

R37 RK3050 Chip R. ERJ3GSYJ103V

R38 RK3054 Chip R. ERJ3GSYJ223V

R39 RK3038 Chip R. ERJ3GSYJ102V

R40 RK3050 Chip R. ERJ3GSYJ103V

R41 RK3030 Chip R. ERJ3GSYJ221V

R50 RK3058 Chip R. ERJ3GSYJ473V

R51 RK3040 Chip R. ERJ3GSYJ152V

R52 RK3040 Chip R. ERJ3GSYJ152V

R53 RK3058 Chip R. ERJ3GSYJ473V

R54 RK3040 Chip R. ERJ3GSYJ152V

R56 RK3038 Chip R. ERJ3GSYJ102V

R57 RK3074 Chip R. ERJ3G3YJ105V

R58 RK3050 Chip R. ERJ3GSYJ103V

R59 RK3038 Chip R. ERJ3GSYJ102V

R60 RK3042 Chip R. ERJ3GSYJ222V

R61 RK3054 Chip R. ERJ3GSYJ223V

R62 RK3038 Chip R. ERJ3GSYJ102V

Page-35

Page 36

RF Unit

Ref No Parts No. Description Parts Name Ver

R63 RK3054 Chip R. ERJ3GSYJ223V

R64 RK3054 Chip R. ERJ3GSYJ223V

R65 RK3042 Chip R. ERJ3GSYJ222V

R66 RK3046 Chip R. ERJ3GSYJ472V

R67 RK3058 Chip R. ERJ3GSYJ473V

R68 RK3064 Chip R. ERJ3GSYJ154V

R69 RK3046 Chip R. ERJ3GSYJ472V

R70 RK3034 Chip R. ERJ3GSYJ471V Wide

R70 RK3034 Chip R. ERJ3GSYJ471V Narrow

R71 RK3042 Chip R. ERJ3GSYJ222V

R72 RK3065 Chip R. ERJ3GSYJ184V Wide

C182

(R72) CU3059 Chip C. C1608JF1E104ZT-N Narrow

R73 RK3006 Chip R. ERJ3GSYJ2R2V

R74 RK3046 Chip R. ERJ3GSYJ472V

R75 RK3042 Chip R. ERJ3GSYJ222V

R76 RK3046 Chip R. ERJ3GSYJ472V

R80 RK3042 Chip R. ERJ3GSYJ222V

R81 RK3064 Chip R. ERJ3GSYJ154V

R82 RK3054 Chip R. ERJ3GSYJ223V

R83 RK3054 Chip R. ERJ3GSYJ223V

R84 RK3054 Chip R. ERJ3GSYJ223V

R85 RK3050 Chip R. ERJ3GSYJ103V

R86 RK3050 Chip R. ERJ3GSYJ103V

R87 RK3050 Chip R. ERJ3GSYJ103V

R88 RK3044 Chip R. ERJ3GSYJ332V

R89 RK3042 Chip R. ERJ3GSYJ222V

R90 RK3022 Chip R. ERJ3GSYJ470V

R91 RK3034 Chip R. ERJ3GSYJ471V

R92 RK3038 Chip R. ERJ3GSYJ102V

R93 RK3074 Chip R. ERJ3G3YJ105V

R94 RK3042 Chip R. ERJ3GSYJ222V

R95 RK3026 Chip R. ERJ3GSYJ101V

R96 RK3026 Chip R. ERJ3GSYJ101V

R97 RK3026 Chip R. ERJ3GSYJ101V

R99 RK3062 Chip R. ERJ3GSYJ104V

R100 RK3054 Chip R. ERJ3GSYJ223V

R101 RK3034 Chip R. ERJ3GSYJ471V

R102 RK3038 Chip R. ERJ3GSYJ102V

R110 RK3051 Chip R. ERJ3GSYJ123V

R111 RK3058 Chip R. ERJ3GSYJ473V

R112 RK3020 Chip R. ERJ3GSYJ330V

R113 RK3057 Chip R. ERJ3GSYJ393V

R114 RK3050 Chip R. ERJ3GSYJ103V

R115 RK3062 Chip R. ERJ3GSYJ104V

R116 RK3062 Chip R. ERJ3GSYJ104V

R117 RK3050 Chip R. ERJ3GSYJ103V

R118 RK3051 Chip R. ERJ3GSYJ123V

R119 RK3062 Chip R. ERJ3GSYJ104V

R120 RK3054 Chip R. ERJ3GSYJ223V

R122 RK3050 Chip R. ERJ3GSYJ103V

R123 RK3050 Chip R. ERJ3GSYJ103V

R124 RK3056 Chip R. ERJ3GSYJ333V

R125 RK3061 Chip R. ERJ3GSYJ823V

R126 RK3061 Chip R. ERJ3GSYJ823V

R127 RK3050 Chip R. ERJ3GSYJ103V

R128 RK3066 Chip R. ERJ3GSYJ224V

R129 RK3058 Chip R. ERJ3GSYJ473V

Ref No Parts No. Description Parts Name Ver

R130 RK0105 Chip R. ERJ6GEYJ2R2V

R131 RK3030 Chip R. ERJ3GSYJ221V

R132 RK3034 Chip R. ERJ3GSYJ471V

R133 RK3050 Chip R. ERJ3GSYJ103V

R134 RK3045 Chip R. ERJ3GSYJ392V

R135 RK3051 Chip R. ERJ3GSYJ123V

R136 RK3054 Chip R. ERJ3GSYJ223V

R137 RK3042 Chip R. ERJ3GSYJ222V

R141 RK3001 Chip R. ERJ3GSY0R00V

TC1 CT0033 Trimmer ECRJA010A11W

VR1 RH0106 Trim.Pot EVM1YSX50BQ4

VR2 RH0103 Trim.Pot EVM1YSX50B14

VR3 RV0017 Trim.Pot RK09711-10KA-SW

VR4 RV0018 Trim.Pot RK09711-10KB

W1 MRCJ06AA Wire DJ145

W2 MWCK06AA Wire DJ145

W3 MKCJH3AA Wire DJ145

W4 UX1033 Wire DJ145

X1 XQ0053 Crystal UM-1 21,855MHz

X2 XK0002 Discriminator CDBM455C7

X3 XQ0052 Crystal UM-5 12.800MHz

XF0011 Crystal Filter

XF1

XF0023 Crystal Filter

XF1

TT1002 Tube

2l.400MHz 21M15B1

2l.400MHz 21M7B1

Wide

Narrow

Page-36

Page 37

Ref No |Parts No. Description Parts Name Ver

VCO Unit

C201 CU3035 Chip C. C1608JB1H102KT-A

C202 CU3047 Chip C. C1608JB1H103KT-A

C203 CU3035 Chip C. C1608JB1H102KT-A

C204 CU3035 Chip C. C1608JB1H102KT-A

C205 GU3002 Chip C. C1608CH1H010CT-A

C206 CU3047 Chip C. C1608JB1H103KT-A

C207 CU3047 Chip C. C1608JB1H103KT-A

C208 CU3047 Chip C. C1608JB1H103KT-A

C209 CU3047 Chip C. C1608JB1H103KT-A

C210 CS0328 Chip Tantal ECST0JY685R

C211 CU3035 Chip C. C1608JB1H102KT-A

C212 CU3035 Chip C. C1608JB1H102KT-A

C213 CU3003 Chip C. C1608CH1H020CT-A

C214 CU3002 Chip C. C1608CH1H010CT-A

C215 CU3047 Chip C. C1608JB1H103KT-A

C216 CU3047 Chip C. C1608JB1H103KT-A

D201 XD0233 Diode 1SV217TPH4

D202 XD0233 Diode 1SV217TPH4

D203 XD0233 Diode 1SV217TPH4

L201 QC0010 Chip L. MLF3216E100M

L202 QC0010 Chip L. MLF3216E100M

L203 QC0090 Chip L. MLF3216E4R7M

L204 QC0003 Chip L. MLF3216A1R0M

L205 QA0081 IFT QA0081

L206 QKA25C Coil MR2.5-2.5T-0.5

Q201 XT0030 Transistor 2SC3356T1BR24/25

Q202 XT0096 Transistor 2SC4099T106N

Q203 XT0095 Transistor 2SC4081T106R

Q204 XU0038 Transistor UN2214-TX

R201 RK3026 Chip R. ERJ3GSYJ101V

R202 RK3034 Chip R. ERJ3GSYJ471V

R203 RK3038 Chip R. ERJ3GSYJ102V

R204 RK3062 Chip R. ERJ3GSYJ104V

R205 RK3062 Chip R. ERJ3GSYJ104V

R206 RK3050 Chip R. ERJ3GSYJ103V

R207 RK3046 Chip R. ERJ3GSYJ472V

R208 RK3026 Chip R. ERJ3GSYJ101V

R209 RK3022 Chip R. ERJ3GSYJ470V

R210 RK3054 Chip R. ERJ3GSYJ223V

R211 RK3050 Chip R. ERJ3GSYJ103V

R212 RK3030 Chip R. ERJ3GSYJ221V

R213 RK3062 Chip R. ERJ3GSYJ104V

R214 RK3050 Chip R. ERJ3GSYJ103V

R215 RK3050 Chip R. ERJ3GSYJ103V

UT0019 CK-1-2

TS0072 VCO Case

VCO Unit / CTCSS Unit

Ref No 1 Parts No. Description Parts Name Ver

180T...

1400non

CTCSS Unit UP0221

1400A

C701 CU3027 Chip C. C1608CH1H221JT-A

C702 CU3027 Chip C. C1608CH1H221JT-A

C703 CU3059 Chip C. C1608JF1E104ZT-A

C704 CU3047 Chip C. C1608JB1H103KT-A

C705 CS0296 Chip Tantal ECST1EY474R

C706 CS0296 Chip Tantal ECST1EY474R

C707 CU3047 Chip C. C1608JB1H103KT-A

C708 CU3059 Chip C. C1608JF1E104ZT-A

C709 CU3059 Chip C. C1608JF1E104ZT-A

C710 CU3059 Chip C. C1608JF1E104ZT-A

C711 CS0296 Chip Tantal ECST1EY474R

CN701 UE0133 Connector DF9A-11P-1V

D701 XD0057 Diode 1SS184TE85L

IC701 XA0203 IC MX365ADW-TR

Q701 XT0037 Transistor 2SC2412KT146R

R701 RK3074 Chip R. ERJ3GSYJ105V

R702 RK3064 Chip R. ERJ3GSYJ154V

R703 RK3040 Chip R. ERJ3GSYJ152V

R704 RK3034 Chip R. ERJ3GSYJ471V

R705 RK3067 Chip R. ERJ3GSYJ274V

R706 RK3059 Chip R. ERJ3GSYJ563V

R707 RK3074 Chip R. ERJ3GSYJ105V

R708 RK3073 Chip R. ERJ3GSYJ824V

R709 RK3038 Chip R. ERJ3GSYJ102V

R710 RK3070 Chip R. ERJ3GSYJ474V

R711 RK3054 Chip R. ERJ3GSYJ223V

R712 RK3040 Chip R. ERJ3GSYJ152V

VR701 RH0060 Trim.Pot MVR32 HXBRN473

X701 XB0006 Crystal CSB1000J 221

YZ0042 Adhesion G17

Page-37

Page 38

PTT SW Unit/JACK Unit /RE Unit

OTHER/ROM2 Unit /PACKING

Ref No |Parts No. ¡Description |Parts Name |Ver

PTT SW Unit

SW301 UU0013 Switch SKHUAB

SW302 UU0013 Switch SKHUAB

SW303 UU0013 Switch SKHUAB

CN501 UE0147 Connector TE 1608-PI28G05

JACK Unit

JK501 UJ0022 Jack HSJ112-01-540

JK502 UJ0016 Jack HSJ1423-01-050

R501 RK4051 Chip R. ERJ-14YS101V

RE Unit

|UR0007 | 1RK09710HH5RH 220 |

OTHERS

AB0011 3+8FeNi

AK0001 0B2+4FeNi

AK0002 0B2+4FeB/C

AV0004 0B26+6FeNi

AN0012 Dial Nut

AP0016 P2+8FeB/C

C1 CC0119 CeramicC. 50V22PF CH

DP0063 LCD Panel

DP0111 LCD Panel

AN/QN

ES0011AZ Speaker 036S13D

FG0076 Battery Rubber

FG0092 Silicone Key 1 (T/E) DJ180

FG0093 Silicone Key 2 (T/E) DJ180

FG0094 Jack Cap

FG0095 PTT Rubber

FG0097 VOL Rubber

FG0100 EP/MIC Cushion

FG0112 Silicone Key 2 (1400) 1400

FG0129 Silicone Key 2 (1400AN/QN) AN/QN

FM0068 Earth Ring

FM0069 Antenna Earth

KB0038 Rear Case

KM0135 FrontCase

KM0141 Switch Cover (1400) 1400

NB0047 Release Knob

NK0028 VOL Knob

NK0029 SQL Knob

ST0032 SP Holder

TG0014 SP Net

TS0071 RF Shield

UE0193Z BNC Receptacle

UP0220A P.C.B.

W201 UX1035 Wire DJ145

YZ0044 Screw Lock 1401C

YZ0116 Acrylic Tape

YZ0117 Switch Cover Tape (1400) 1400

Ref No 1 Parts No. Description Parts Name Ver

ROM2 Unit

CN801 UE0132 Connector DF9A-9P-1V 1

IC801 XA0200 IC X24C04S14-3.0T (EJ-14u)

IC801 XA0201 IC X24C16S-3.0T (EJ.15u)

R801 RK3062 Chip R. ERF3GSYJ104V

R802 RK3062 Chip R. ERF3GSYJ104V

HK0284 Carton Box EJ-14u

HK0285 Carton Box EJ-15u

HP0029 Protection Bag

UP0220B CPU P.C.B.

YZ0121 Tape

Packing

AK0004 4PCS 0B2+3FeB/C

DS0357 Model Name Plate DJ-18 T

DS0388A Model Name Plate page39

DS0340 Model Name plate

EA57 Antenna M Low band Ea page39

EA58 Antenna M high band EA page39

EBP26N Ni-Cd(EG0016) page39

EDC-49 Charger (EJ0007) page39

EDC-50 Charger (EJ0008) page39

FG0096 Model Name Rubber

HK0280 Item Carton Box DJ-180' DJ180

HK0287 Item CartonBox DJ1400 DJ1400

HM0100 Carton Box

HU0037 Fixture

KM0137 Switch Cover DJ180

HP0016 Protection Bag 75 X 90 page39

HP0028 Protection Bag 165 X 280

HP0031 Protection Bag 100 X 200

PH0006 Registration Card

PR0022 Seal E

PR0094 Seal A

PR0157 Seal TA

PR0158 Seal TB

PR0159G Seal TS

PR0160 Seal TZ

PR0161 Seal A

PR0162 Seal B

PR0163 Seal B

PS0159G Instruction Manual

PS0161 Instruction Manual

PS0258A Instruction Manual

DJ180

DJ1400

AN/QN

PT0004A Lot Number Seal

YZ0117 Switch Cover Tape

YZ0118 Tape

YZ0121 Tape

EBC-3 Belt Ciip

BB0009Y Hand Strap

Page-38

Page 39

Model No DJ-180 DJ-180 DJ-1400

Ref. No. T TA TA2 TB TB2 TM

DS0357 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

DS0388A 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

DS0352A 1 1

EA57 1 1 0 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1

EA58 0 0 1 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0

EBP26N 1 1 1 1 1 1 1 1 1 0 0 0 0 0 1 1 1 0 0 0 1 1 1 1 1 1 0 0 0 0 0

EBP28N 1 1

EDC49 1 0 0 1 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 1 0 0 0 0

EDC50 0 1 1 0 0 1 1 0 1 0 0 0 0 0 1 1 1 0 0 0 0 1 1 0 0 1 0 0 0

FG0092 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0

FG0093 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0

FG0101 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 0 0 0 0 0 0 0 0 0 0

FG0112 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 0 0

FG0129 1 1

HK0280 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0

HK0287 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1

HP0016 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 1 1

KM0136 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1

KM0137 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0

KM0138 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0

KM0141 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1

PH0006 1 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 1 1 0 0

PR0174 0 0 0 0 0 0 0 0 0 1 1 1 1 1 0 0 0 1 1 1 0 0 0 0 0 0 1 1 1

PS0159 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0

PS0161 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 0 0

PS0258A 1 1

SEAL TA TA2 TB TB2 TM

EDH11 0 0 0 0 0 0 0 0 0 1 1 1 1 1 0 0 0 1 1 1 0 0 0 0 0 0 1 1 1

TSA TZ TD TAD TFD TSD TZD E EA EB ED EAD EBD A B F

TS

TSA TZ TA TFD

TS

TZ E EA EB E EA EB A B F

TS

TM D AD BD

G

TM A B

G

QISAN

Page 40

ADJUSTMENT

1) Required Test Equipment

1. Regulated Power Supply

Supply voltage: 2Vto15V

Current: 2A or more

Standard voltage: 13.8V

6. Oscilloscope

Measurable frequency:

7. AF Voltmeter

Measurable frequency:

DC to 30MHz

50Hz to 1MHz

2. Frequency Counter Maximum sensitivity: 1 mV or more

Measurable frequency: Up to 1 GHz

Measurements stability: 0.2ppm or so

8. Spectrum Analyzer

Measuring range: DC to 2GHz or more

3. Power Meter

Measurable frequency: Up to 500M Hz

Impedance: 50Q, unbalanced

Measuring range: Full scale of 10W or so

9. SSG

Maximum frequency: 1GHz or more

Output:

Output impedance:

-20dB/0.1nVto 120dB/1 V

50Q, unbalanced

4. Linear Detector

Measurable frequency: Up to 500MHz

Characteristics: Flat

CN: 60dBorm ore

10. Dummy Load

Impedance: 8Q

Dissipation: 2W or more

5. Digital Multimeter

Voltage range: FS = 18V or so

Input resistance: 1MQ or more

2) Before Adjustment

11. Distortion Meter

Measurable frequency: 30Hz to 100kHz

Input level: 50mV to 10V rms

40

Page 41

3) ADJUSTMENT for DJ180 DJ1400 (The Wide Version)

PLL Adjustment

Item Condition

RX VCO Frequency: 145.00MHz

Reference

Frequency

TX Adjustment

Item

Power

DEV

DTMF

88.5HzTone

Frequency: 145.00MHz

PTT: ON

Condition

Freq: ***** MHz

PTT: ON

Power: Low

Freq: ***** MHz

PTT: ON

Power: Low

AG output: 1KHz,

-30dBm

Freq: ***** MHz

PTT: ON

Power: Low

Push1"keyon"

Freq: ***** MHz

PTT: ON

Power: Low

Measurement Adjustment Speclficatlons/

Digital Multimeter TPl

Frequency Counter

Measurement Adjustment Speclficatlons/

Test-equipment Ternlinal Unit Parts Method

PowerMeter ANT RF

AF OSC

Liner Detector

ANT RF TC1

ANT

VCO

RF VR2

DTMF VR401

TONE VR701

L205

VR1

RemarksTest-equipment Ternlinal Unit Parts Method

1.5+/-0.05V

145.00MHz+/-

50Hz

Remarks

0.4+/-0.05W

4.3KHz

+/-0.2KHz/DEV

3.0KHz

+/-0.5KHz/DEV

0.8KHz+/-

0.1KHz/DEV

RX Adjustment

Item

RXFront End

Condition

Frequency: ***** MHz

SSGmod: 1KHz,

3.5kHzDEV

DJ-180 T/E/

DJ1400/A/B 145.00MHz

DJ-180TA2,TB2 162.00MHz

Measurement Adjustment Speclficatlons/

Test-equipment Ternlinal Unit Parts Method

SSG

Oscilloscope

AFVoltmeter

Distorlion Meter

SP

RF L4~L7

12dB

SINAD:

MAX

Remarks

12dB SINAD -

6.0dBuV(EMF)

Page-41

Page 42

3) ADJUSTMENT for DJ14GGAN/QN (The Narrow Version)

PLL Adjustment

Item Condition Measurement Adjustment Speclficatlons/

Test-equipment Ternlinal Unit Parts Method

RX VCO Frequency: 145.GGMHz

Reference

Frequency

TX Adjustment

Item Condition Measurement Adjustment Speclficatlons/

Power

DEV

DTMF

BB.5HzTone

Frequency: 145.GGMHz

PTT: ON

Freq: ******MHz

PTT: ON

Power: Low

Freq: ******MHz

PTT: ON

Power: Low

AG output: lKHz,

-3GdBm

Freq: ******MHz

PTT: ON

Power: Low

Freq: ******MHz

PTT: ON

Power: Low

Digital Multimeter TPl

Frequency Counter

Test-equipment Ternlinal Unit Parts Method

PowerMeter ANT RF VR1

AF OSC

Liner Detector

ANT RF

ANT

VCO

RF VR2

DTMF VR4G1

TONE VR7G1

L2G5

TC1

Remarks

1.5+/-G.G5V

145.GGMHz+/-

5GHz

Remarks

G.4+/-G.G5W

2.2KHz

+/-G.2KHz/DEV

G.BKHz

+/-

G.G5KHz/DEV

G.35KHz+/-

G.G5kHz/DEV

RX Adjustment

Item Condition Measurement Adjustment Speclficatlons/

Remarks

12dB SINAD -

6.GdBuV(EMF)

RXFront End

Test-equipment Ternlinal Unit Parts Method

Frequency:

******MHz SSGmod:

lKHz, 1.7kHzDEV

*****MHz

DJ14GGAN 145.GGMHz

DJ14GGQN 162.GGMHz

SSG

Oscilloscope

AFVoltmeter

Distorlion Meter

SP

RF L4~L7

12dB

SINAD:

MAX

Page-42

Page 43

5) Adjustment Quick Reference

Wide Version

Narrow Version

Parts

L4 RX Sensitivity

L5

L6 RX Sensitivity -6dBn.V (12dB SINAD)

L7 RX Sensitivity -6dB|iV (12dB SINAD)

L205 VCO Frequency 1.5 +/-0.05V

TC1 Reference Frequency 145MHz +/- 50Hz

VR1

VR2 Deviation 4.3kHz +/- 0.2kHz

VR401 DTMF Deviation 3.0kHz +/-0.5kHz

VR701 CTCSS Deviation 0.8kHz +/-0.1kHz

Item

RX Sensitivity -6dBp.V (12dB SINAD)

TX Low Power

Specifications

-6dB(j.V (12dB SINAD)

0.4 +/-0.05W

2.2KHz+/-0.2KHz

0.8KHz+/-0.05KHz

0.35KHz+/-0.05KHz

'Attach the DC IN unit to the radio and power

supply voltage 13.8V will be supplied.

43

Page 44

2. DTMF Unit Adjustment

3. CTCSS Unit Adjustment

44

Page 45

DJ-180TA2/TB2 Version Only

Ret. No.

Value

C3 C46

47 p

C48

15p 39p 1 Bp 62 p 27p QKA15B

C56

C57 C59 L19

CIRCUIT DIAGRAM

RF Unit

A

en

Page 46

(J)

oë«

— r

Z

o

m

i

1

1

1

8

g

Ï

*

8

g

0.

g

ÿ

Page 47

BATTERY

TERMINAL

A

Loading...

Loading...