AGERE FW801 Datasheet

FW801 PHY IEEE * 1394A

One-Cable Transceiver/Arbiter Device

Supports provisions of IEEE 1394-1995 Standard

Distinguishing Features

■

Compliant with IEEE P1394a Draft 2.0 Standard

for a High Performance Serial Bus (Supple-

ment)

Supports extended BIAS_HANDSHAKE time for

■

enhanced interoperability with camcorders

While unpowered and connected to the bus, will not

■

drive TPBIAS on a connected port even if receiving

incoming bias voltage on that port

Does not require external filter capacitors for PLL

■

Does not require a separate 5 V supply for 5 V link

■

controller interoperability

Interoperable across 1394 cable with 1394 physical

■

layers (PHY) using 5 V supplies

Interoperable with 1394 link-layer controllers using

■

5 V supplies

Device powerdown feature to conserve energy in

■

battery-powered applications

Interface to link-layer controller supports Annex J

■

electrical isolation as well as bus-keeper isolation

■

for a High Performance Serial Bus

Fully interoperable with FireWire† implementation

■

of IEEE 1394-1995

Reports cable power fail interrupt when voltage at

■

CPS pin falls below 7.5 V

Separate cable bias and driver termination voltage

■

supply for port

Other Features

48-pin TQFP package

■

Single 3.3 V supply operation

■

Data interface to link-layer controller provided

■

through 2/4/8 parallel lines at 50 Mbits/s

25 MHz crystal oscillator and PLL provide transmit/

■

receive data at 100 Mbits/s, 200 Mbits/s, and

400 Mbits/s and link-layer controller clock at

50 MHz

Multiple separate package signals provided for

■

analog and digital supplies and grounds

Data Sheet, Rev. 1

June 2001

Features

Provides one fully compliant cable port at

■

100 Mbits/s, 200 Mbits/s, and 400 Mbits/s

Fully supports Open HCI requirements

■

Supports arbitrated short bus reset to improve

■

utilization of the bus

Supports ack-accelerated arbitration and fly-by

■

concatenation

Supports connection debounce

■

Supports multispeed packet concatenation

■

Supports PHY pinging and remote PHY access

■

packets

Fully supports suspend/resume

■

Supports PHY-link interface initialization and reset

■

Supports 1394a register set

■

Supports LPS/link-on as a part of PHY-link inter-

■

face

Description

The Agere Systems Inc. FW801 device provides the

analog physical layer functions needed to implement a one-port node in a cable-based IEEE 13941995 and IEEE P1394a network.

The cable port incorporates two differential line

transceivers. The transceivers include circuitry to

monitor the line conditions as needed for determining connection status, for initialization and

arbitration, and for packet reception and transmission. The PHY is designed to interface with a linklayer controller (LLC).

* IEEE is a registered trademark of The Institute of Electrical and

Electronics Engineers, Inc.

† FireWire is a registered trademark of Apple Computer, Inc.

FW801 PHY IEEE 1394A

One-Cable Transceiver/Arbiter Device

Data Sheet, Rev. 1

June 2001

Table of Contents

Contents Page

Distinguishing Features ............................................................................................................................................ 1

Features ................................................................................................................................................................... 1

Other Features ......................................................................................................................................................... 1

Description ................................................................................................................................................................ 1

Signal Information ..................................................................................................................................................... 6

Application Information ............................................................................................................................................. 9

1394 Application Support Contact Information ....................................................................................................... 10

Absolute Maximum Ratings .................................................................................................................................... 11

Electrical Characteristics ........................................................................................................................................12

Timing Characteristics ............................................................................................................................................ 15

Timing Waveforms .................................................................................................................................................. 16

Internal Register Configuration ............................................................................................................................... 17

Outline Diagrams .................................................................................................................................................... 22

List of Figures

Figure 1. Block Diagram .......................................................................................................................................... 5

Figure 2. Pin Assignments ....................................................................................................................................... 6

Figure 3. Typical External Component Connections ............................................................................................... 9

Figure 4. Typical Port Termination Network .......................................................................................................... 10

Figure 5. Dn, CTLn, and LREQ Input Setup and Hold Times Waveforms ............................................................ 16

Figure 6. Dn, CTLn Output Delay Relative to SYSCLK Waveforms ...................................................................... 16

List of Tables

Table 1. Signal Descriptions ..................................................................................................................................... 6

Table 2. Absolute Maximum Ratings ...................................................................................................................... 11

Table 3. Analog Characteristics .............................................................................................................................. 12

Table 4. Driver Characteristics ............................................................................................................................... 13

Table 5. Device Characteristics ..............................................................................................................................14

Table 6. Switching Characteristics ......................................................................................................................... 15

Table 7. Clock Characteristics ................................................................................................................................15

Table 8. PHY Register Map for the Cable Environment ........................................................................................17

Table 9. PHY Register Fields for the Cable Environment ...................................................................................... 17

Table 10. PHY Register Page 0: Port Status Page ................................................................................................ 19

Table 11. PHY Register Port Status Page Fields ................................................................................................... 20

Table 12. PHY Register Page 1: Vendor Identification Page ...............................................................................21

Table 13. PHY Register Vendor Identification Page Fields .................................................................................... 21

22 Agere Systems Inc.

Data Sheet, Rev. 1 FW801 PHY IEEE 1394A

June 2001 One-Cable Transceiver/Arbiter Device

Description

The PHY requires either an external 24.576 MHz

crystal or crystal oscillator. The internal oscillator

drives an internal phase-locked loop (PLL), which

generates the required 400 MHz reference signal. The

400 MHz reference signal is internally divided to

provide the 49.152 MHz, 98.304 MHz, and

196.608 MHz clock signals that control transmission of

the outbound encoded strobe and data information.

The 49.152 MHz clock signal is also supplied to the

associated LLC for synchronization of the two chips

and is used for resynchronization of the received data.

The powerdown function, when enabled by the PD

signal high, stops operation of the PLL and disables all

circuitry except the cable-not-active signal circuitry.

The PHY supports an isolation barrier between itself

and its LLC. When /ISO is tied high, the link interface

outputs behave normally. When /ISO is tied low,

internal differentiating logic is enabled, and the outputs

become short pulses, which can be coupled through a

capacitor or transformer as described in the

IEEE 1394-1995 Annex J. To operate with bus-keeper

isolation, the /ISO pin of the FW801 must be tied high.

Data bits to be transmitted through the cable ports are

received from the LLC on two, four, or eight data lines

(D[0:7]), and are latched internally in the PHY in

synchronization with the 49.152 MHz system clock.

These bits are combined serially, encoded, and

transmitted at 98.304 Mbits/s, 196.608 Mbits/s, or

393.216 Mbits/s as the outbound data-strobe

information stream. During transmission, the encoded

data information is transmitted differentially on the TPA

and TPB cable pair(s).

During packet reception, the TPA and TPB

transmitters of the receiving cable port are disabled,

and the receivers for that port are enabled. The

encoded data information is received on the TPA and

TPB cable pair. The received data-strobe information

is decoded to recover the receive clock signal and the

serial data bits. The serial data bits are split into two,

four, or eight parallel streams, resynchronized to the

local system clock, and sent to the associated LLC.

The received data is also transmitted (repeated) out of

the other active (connected) cable ports.

Both the TPA and TPB cable interfaces incorporate

differential comparators to monitor the line states

during initialization and arbitration. The outputs of

these comparators are used by the internal logic to

determine the arbitration status. The TPA channel

monitors the incoming cable common-mode voltage.

The value of this common-mode voltage is used during

arbitration to set the speed of the next packet

(continued)

transmission. In addition, the TPB channel monitors

the incoming cable common-mode voltage for the

presence of the remotely supplied twisted-pair bias

voltage. This monitor is called bias-detect.

The TPBIAS circuit monitors the value of incoming

TPA pair common-mode voltage when local TPBIAS is

inactive. Because this circuit has an internal current

source and the connected node has a current sink, the

monitored value indicates the cable connection status.

This monitor is called connect-detect.

Both the TPB bias-detect monitor and TPBIAS

connect-detect monitor are used in suspend/resume

signaling and cable connection detection.

The PHY provides a 1.86 V nominal bias voltage for

driver load termination. This bias voltage, when seen

through a cable by a remote receiver, indicates the

presence of an active connection. The value of this

bias voltage has been chosen to allow interoperability

between transceiver chips operating from 5 V or 3 V

nominal supplies. This bias voltage source should be

stabilized by using an external filter capacitor of

approximately 0.33 µF.

The transmitter circuitry, the receiver circuitry, and the

twisted-pair bias voltage circuity are all disabled with a

powerdown condition. The powerdown condition

occurs when the PD input is high. The port transmitter

circuitry and the receiver circuitry are also disabled

when the port is disabled, suspended, or

disconnected.

The line drivers in the PHY operate in a highimpedance current mode and are designed to work

with external 112 Ω line-termination resistor networks.

One network is provided at each end of each twistedpair cable. Each network is composed of a pair of

series-connected 56 Ω resistors. The midpoint of the

pair of resistors that is directly connected to the

twisted-pair A (TPA) signals is connected to the

TPBIAS voltage signal. The midpoint of the pair of

resistors that is directly connected to the twisted-pair B

(TPB) signals is coupled to ground through a parallel

RC network with recommended resistor and capacitor

values of 5 kΩ and 220 pF, respectively. The value of

the external resistors are specified to meet the draft

standard specifications when connected in parallel

with the internal receiver circuits.

The driver output current, along with other internal

operating currents, is set by an external resistor. This

resistor is connected between the R0 and R1 signals

and has a value of 2.49 kΩ ± 1%.

Agere Systems Inc. 3

FW801 PHY IEEE 1394A Data Sheet, Rev. 1

One-Cable Transceiver/Arbiter Device June 2001

Description

The signal, C/LKON, as an input, indicates whether a

node is a contender for bus manager. When the

C/LKON signal is asserted, it means the node is a contender for bus manager. When the signal is not

asserted, it means that the node is not a contender.

The C bit corresponds to bit 20 in the self-ID packet

(see Table 4-29 of the IEEE 1394-1995 standard for

additional details).

The power-class bits of the self-ID packet do not have

a default value. These bits can be initialized and read/

written through the LLC using the PHY Register Map

Figure 6-1 of the IEEE P1394a Draft 2.0 standard. See

Table 8 for the address space of the Pwr_class

register.

A powerdown signal (PD) is provided to allow a powerdown mode where most of the PHY circuits are

powered down to conserve energy in battery-powered

applications. A cable status signal, CNA, provides a

high output when none of twisted-pair cable ports are

receiving incoming bias voltage. This output is not

debounced. The CNA output can be used to determine when to power the PHY down or up. In the

powerdown mode, all circuitry is disabled except the

CNA circuitry. It should be noted that when the device

is powered down, it does not act in a repeater mode.

When the power supply of the PHY is removed while

the twisted-pair cables are connected, the PHY transmitter and receiver circuitry has been designed to

present a high impedance to the cable in order to not

load the TPBIAS signal voltage on the other end of the

cable.

(continued)

For reliable operation, the TPBn signals must be terminated using the normal termination network regardless

of whether a cable is connected to a port or not connected to a port. When a port does not have a cable

connected, internal connect-detect circuitry will keep

the port in a disconnected state.

Note: All gap counts on all nodes of a 1394 bus must

be identical. This may be accomplished by using

PHY configuration packets (see Section 4.3.4.3

of IEEE 1394-1995 standard) or by using two

bus resets, which resets the gap counts to the

maximum level (3Fh).

The link power status (LPS) signal works with the

C/LKON signal to manage the LLC power usage of the

node. The LPS signal indicates that the LLC of the

node is powered up or powered down. If LPS is inactive for more than 1.2 µs and less than 25 µs, PHY/link

interface is reset. If LPS is inactive for greater than

25 µs, the PHY will disable the PHY/link interface to

save power. If the PHY then receives a link-on packet,

the C/LKON signal is activated to output a 6.114 MHz

signal, which can be used by the LLC to power itself

up. Once the LLC is powered up, the LPS signal communicates this to the PHY and the PHY/link interface

is enabled. C/LKON signal is turned off when both LPS

is active and Link_active bit (see Table 9) is set.

Two of the signals are used to set up various test conditions used in manufacturing. These signals, SE and

SM, should be connected to V

SS for normal operation.

4 Agere Systems Inc.

Data Sheet, Rev. 1

June 2001

FW801 PHY IEEE 1394A

One-Cable Transceiver/Arbiter Device

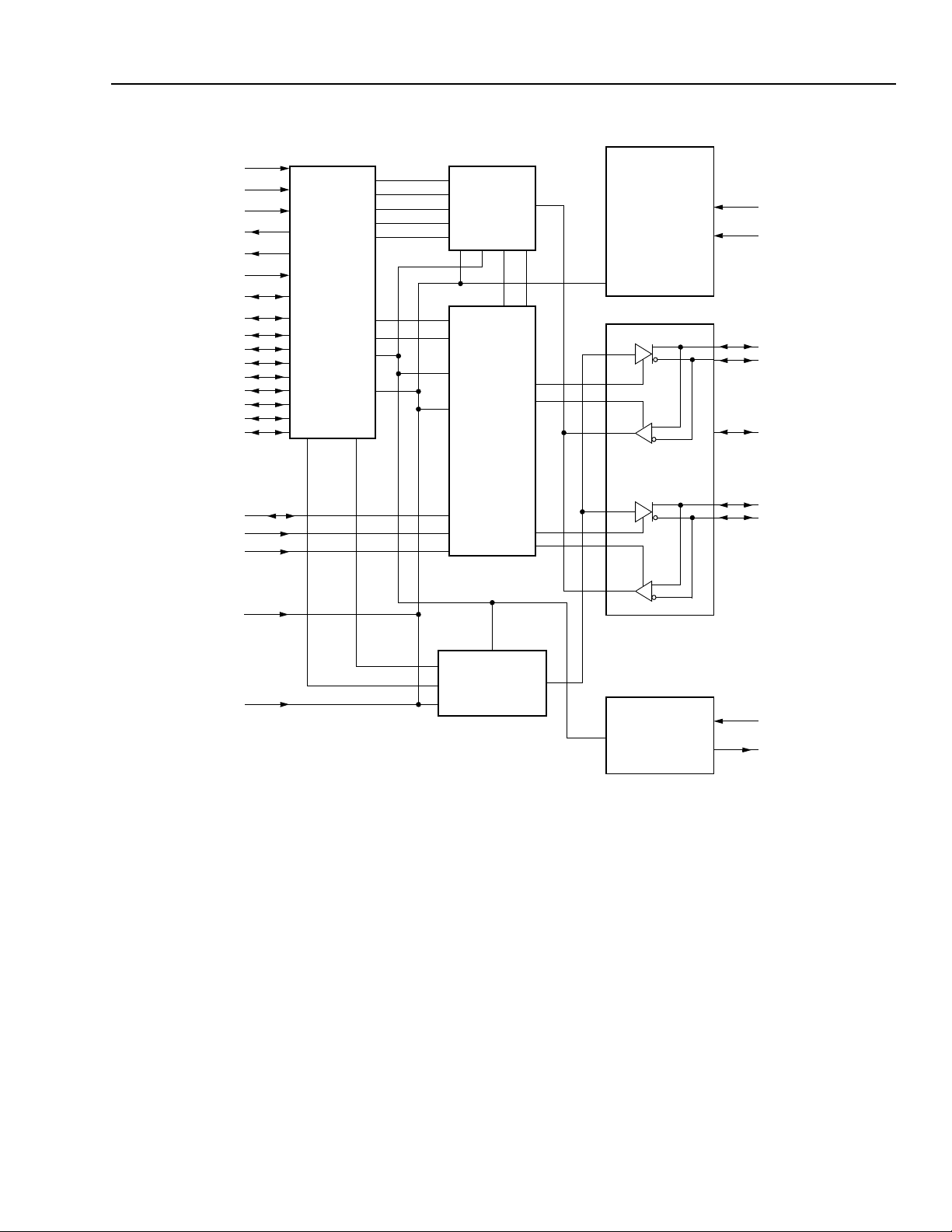

Description

SYSCLK

LREQ

CTL0

CTL1

C/LKON

(continued)

CPS

LPS

/ISO

CNA

D0

D1

D2

D3

D4

D5

D6

D7

SE

SM

LINK

INTERFACE

I/O

RECEIVED

DATA

DECODER/

RETIMER

ARBITRATION

AND

CONTROL

STATE

MACHINE

LOGIC

BIAS

VOLTAGE

AND

CURRENT

GENERATOR

CABLE PORT 0

R0

R1

TPA0+

TPA0–

TPBIAS0

TPB0+

TPB0–

PD

/RESET

TRANSMIT

DATA

ENCODER

Figure 1. Block Diagram

CRYSTAL

OSCILLATOR,

PLL SYSTEM,

AND

CLOCK

GENERATOR

XI

XO

5-5459.e (F)

Agere Systems Inc. 5

FW801 PHY IEEE 1394A

One-Cable Transceiver/Arbiter Device

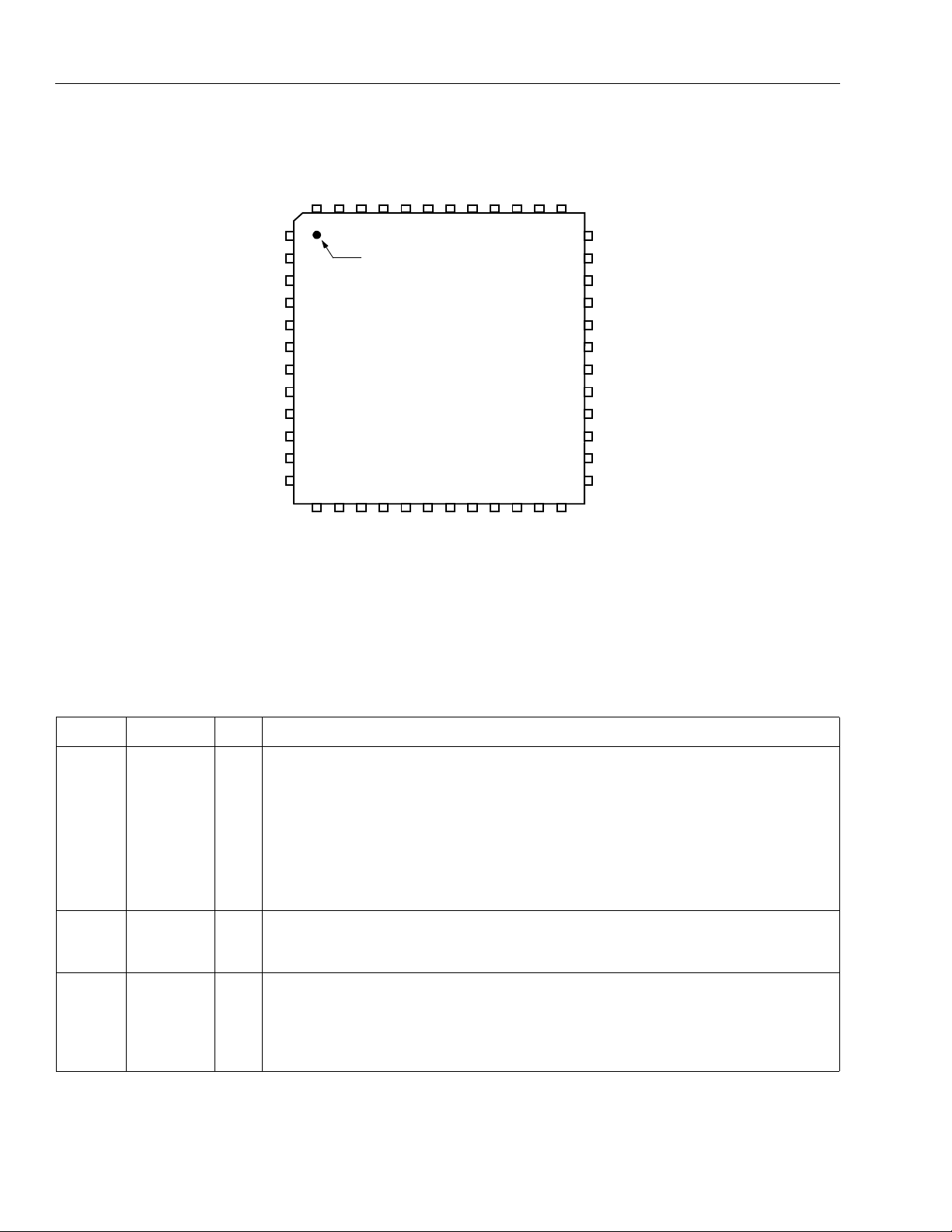

Signal Information

SYSCLK

VSSLREQ

46

47

CTL0

CTL1

D0

D1

V

D2

D3

D4

D5

D6

D7

V

DD

SS

48

1

2

3

4

5

6

7

8

9

10

11

12

13

PIN #1 IDENTIFIER

14

15

XI

XO

/RESET

43

44

45

AGERE FW801

16

17

18

Data Sheet, Rev. 1

June 2001

DD

SS

DD

R0

R1

V

VSSPLLV

PLLV

37

38

39

40

41

42

19

20

21

22

23

V

SSA

36

V

35

SSA

V

DDA

34

V

DDA

33

TPBIAS0

32

TPA0+

31

TPA0–

30

TPB0+

29

TPB0–

28

V

27

SSA

V

26

SSA

25

DDA

V

24

CNA

SS

DD

V

LPS

PD

V

C/LKON

SS

DD

SE

V

/ISO

CPS

SM

V

Note: Active-low signals are indicated by “/” at the beginning of signal names, within this document.

Figure 2. Pin Assignments

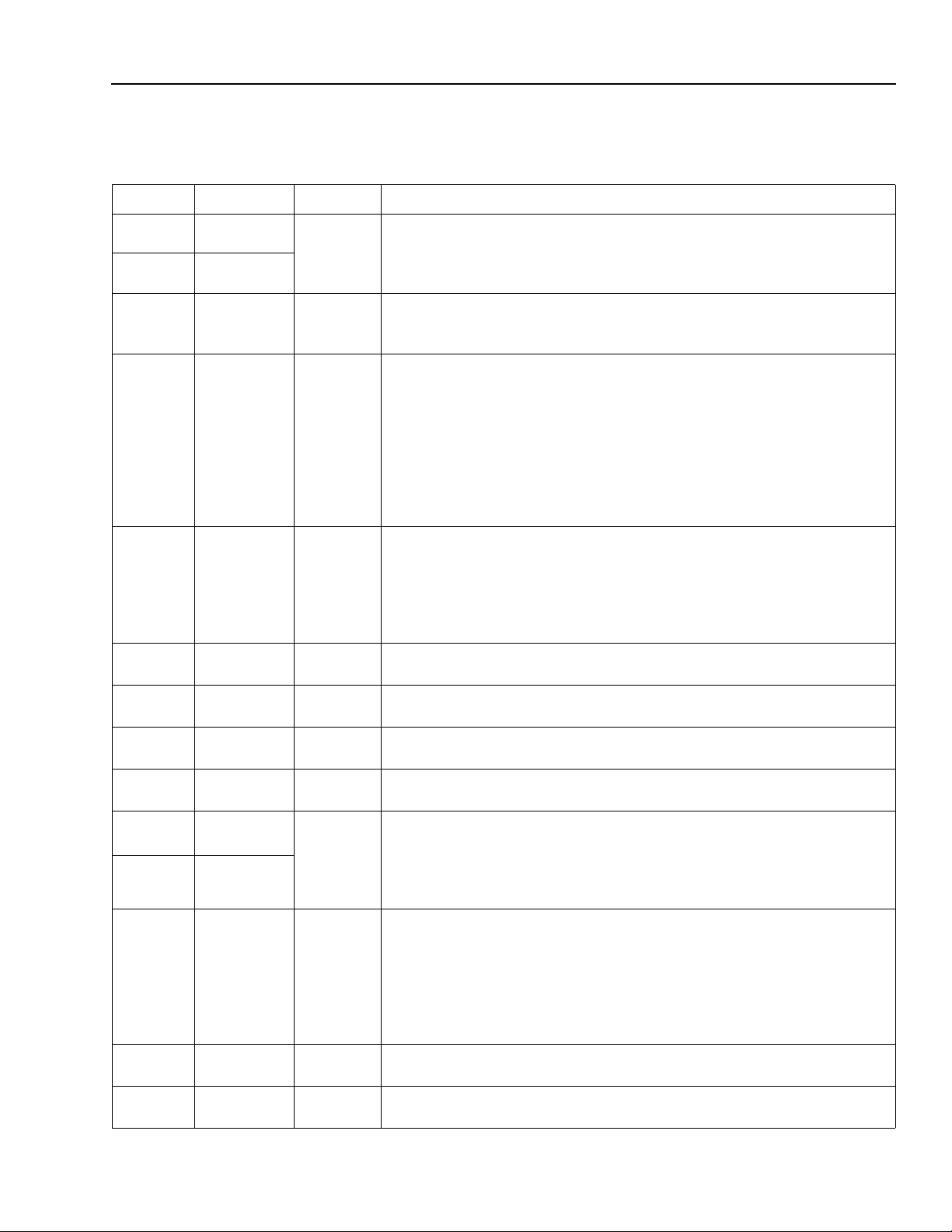

Table 1. Signal Descriptions

Pin Signal* Type Name/Description

17 C/LKON I/O Bus Manager Capable Input and Link-On Output. On hardware reset, this pin is

used to set the default value of the contender status indicated during self-ID. The

bit value programming is done by tying the signal through a 10 kΩ resistor to V

(high, bus manager capable) or to GND (low, not bus manager capable). Using

either the pull-up or pull-down resistor allows the link-on output to override the input

value when necessary.

After hardware reset, this pin is set as an output, C/LKON indicates the reception of

a link-on message by asserting a 6.114 MHz signal.

13 CNA O Cable-Not-Active Output. CNA is asserted high when none of the PHY ports are

receiving an incoming bias voltage. This circuit remains active during the powerdown mode.

20 CPS I Cable Power Status. CPS is normally connected to the cable power through a

400 kΩ resistor. This circuit drives an internal comparator that detects the presence

of cable power. This information is maintained in one internal register and is available to the LLC by way of a register read (see IEEE P1394a Draft 2.0 Standard for

a High Performance Serial Bus (Supplement)).

* Active-low signals are indicated by “/ ” at the beginning of signal names, within this document.

5-7302.b (F)

DD

66 Agere Systems Inc.

Data Sheet, Rev. 1

June 2001

FW801 PHY IEEE 1394A

One-Cable Transceiver/Arbiter Device

Signal Information

(continued)

Table 1. Signal Descriptions (continued)

Pin Signal* Type Name/Description

1 CTL0 I/O Control I/O. The CTLn signals are bidirectional communications control

signals between the PHY and the LLC. These signals control the passage

2CTL1

of information between the two devices. Bus-keeper circuitry is built into

these terminals.

3, 4, 6, 7,

8, 9, 10,

D[0:7] I/O Data I/O. The Dn signals are bidirectional and pass data between the

PHY and the LLC. Bus-keeper circuitry is built into these terminals.

11

19 /ISO I Link Interface Isolation Disable Input (Active-Low). /ISO controls the

operation of an internal pulse differentiating function used on the

PHY-LLC interface signals, CTLn and Dn, when they operate as outputs.

When /ISO is asserted low, the isolation barrier is implemented between

PHY and its LLC (as described in Annex J of IEEE 1394-1995).

/ISO is normally tied high to disable isolation differentiation. Bus-keepers

are enabled when /ISO is high (inactive) on CTL, D, and LREQ. When

/ISO is low (active), the bus-keepers are disabled. Please refer to Agere’s

application note AP98-074CMPR for more information on isolation.

14 LPS I Link Power Status. LPS is connected to either the V

DD supplying the

LLC or to a pulsed output that is active when the LLC is powered for the

purpose of monitoring the LLC power status. If LPS is inactive for more

than 1.2 µs and less than 25 µs, interface is reset. If LPS is inactive for

greater than 25 µs, the PHY will disable to save power. FW801 continues

its repeater function.

48 LREQ I Link Request. LREQ is an output from the LLC that requests the PHY to

perform some service. Bus-keeper circuitry is built into this terminal.

18 PD I Powerdown. When asserted high, PD turns off all internal circuitry except

the bias-detect circuits that drive the CNA signal.

41 PLLV

DD — Power for PLL Circuit. PLLVDD

supplies power to the PLL circuitry

portion of the device.

42 PLLV

SS — Ground for PLL Circuit. PLLVSS is tied to a low-impedance ground

plane.

37 R0 I Current Setting Resistor. An internal reference voltage is applied to a

resistor connected between R0 and R1 to set the operating current and

38 R1

the cable driver output current. A low temperature-coefficient resistor

(TCR) with a value of 2.49 kΩ ± 1% should be used to meet the

IEEE 1394-1995 standard requirements for output voltage limits.

45 /RESET I Reset (Active-Low). When /RESET is asserted low (active), a bus reset

condition is set on the active cable ports and the internal logic is reset to

the reset start state. An internal pull-up resistor, which is connected to

V

DD

, is provided, so only an external delay capacitor in parallel with a

resistor is required to ensure that the capacitor is discharged when PHY

power is removed. This input is a standard logic buffer and can also be

driven by an open-drain logic output buffer.

23 SE I Test Mode Control. SE is used during the manufacturing test and should

be tied to V

SS.

24 SM I Test Mode Control. SM is used during the manufacturing test and should

be tied to V

* Active-low signals are indicated by “/ ” at the beginning of signal names, within this document.

SS.

Agere Systems Inc. 7

Loading...

Loading...