AGERE DNC3X3625 Datasheet

Advance Data Sheet

4

March 2000

DNC3X3625

Hex 10/100 Mbits/s Ethernet Transceiver Macrocell

Features

Hex 10 Mbits/s Transceiver

■

DSP based.

■

Compatible with

for twisted-pair cable.

■

Half- and full-duplex operations.

■

Autopolarity detection and correction.

■

Adjustable squelch level for extended wire-length

capability (two levels).

■

Interfaces with

interface (MII) or a serial 10 Mbits/s 7-pin interface.

■

On-chip filtering eliminates the need for external filters.

Hex 100 Mbits/s Transceiver

■

Compatible with

PCS/PMA (clause 24), PMD (clause 25), MII management, and autonegotiation (clause 28) specifications.

■

Selectable 5-bit code-group (PDT/PDR interface)

or 4-bit data nibbles (MII interface) input/output.

■

Full- or half-duplex operations.

■

Optional carrier integrity monitor (CIM).

■

Selectable carrier sense signal generation (MCRS)

asserted during either transmis sion or reception in

half duplex (MCRS asserted during reception only

in full duplex).

■

Adaptive equalization and baseline wander correction.

IEEE

* 802.3 10Base-T standard

IEEE

802.3u media independent

IEEE

802.3u MII (clause 22),

Hex 100 Mbits/s FX Transceiver

■

Compatible with

IEEE

802.3u 100Base-FX stan-

dard.

■

Reuses existing twisted-pair I/O pins for compatible

fiber-optic transceiver pseudo-ECL (PECL) data.

■

Fiber mode automatically configures port:

— FX mode enable is pin or register selectable

— Disables autonegotiation and 10Base-T.

— Enables 100Base-FX remote fault signaling.

— Disables MLT-3 encoder/decoder.

— Disables scrambler/descrambler.

General

■

Ports individually configurable

■

Autonegotiation and management:

— Fast link pulse (FLP) burst generator.

— Arbitration function.

— Accepts preamble suppression.

— Operates up to 12.5 MHz.

■

Supports the MII station management protocol and

frame format (clause 22): basic and extended register set.

■

Supports next page.

■

Provides status signals: receive activity, transmit

activity, full duplex, collision/jabber, link integrity,

and speed indication.

■

Powerdown mode for 10 Mbits/s and 100 Mbits/s

operation.

■

Loopback testing for 10 Mbits/s and 100 Mbits/s

operation.

■

0.25 µm low-power CMOS technology.

■

Single 3.3 V power supply operation.

■

■

On-chip filtering eliminates the need for external

filters.

*

IEEE

is a registered trademark of The Institute of Electrical and

Electronics Engineers, Inc.

Note: Advisories are issued as needed to update product information. When using this data sheet for design purposes, please contact

your Lucent Technologies Microelectronics Group Account Manager to obtain the latest advisory on this product.

25 MHz XTAL oscillator input or 25 MHz/50 MHz/

125 MHz clock input.

■

Compatible with RMII (standard version) and SMII

(standard version).

DNC3X3625 Advance Data Sheet

10/100 Mbits/ s Ethernet Transceiver Macrocell March 2000

Table of Contents

Contents Page

Features ................................... .............................................. ...................................... .............................................1

Hex 10 Mbits/s Transceiver.....................................................................................................................................1

Hex 100 Mbits/s Transceiver...................................................................................................................................1

Hex 100 Mbits/s FX Transceiver..............................................................................................................................1

General ...................................................................................................................................................................1

Description ................................................................................................................................................................4

Functional Block Diagram .......................................................................................................................................4

Macrocell I/Os.........................................................................................................................................................5

Signal Information......................................................................................................................................................6

Signal Descriptions .................................... ...... ....... ...... ....... ...... ....... ...... ...... ....................................... ....... ...... ......6

MII Station Management ................. ...... ....... ...... ....... ...... ....... ...... ....... ............................................. ...... ....... ...... ....13

Basic Operation ....................................................................................................................................................13

MII Interface Design ........................ ...... ....... ...... ....... ...... ....... ...... ....... ...... ...... .............................................. ..........14

Absolute Maximum Ratings.....................................................................................................................................14

Electrical Characteristics.........................................................................................................................................15

Register Information ................................................................................................................................................19

Register Descriptions............................................................................................................................................19

Application Notes: Board Layout.............................................................................................................................31

Board Layout Considerations................................................................................................................................31

Tables Page

Table 1. MII/5-Bit Serial Interface Signals.................................................................................................................6

Table 2. MII Management Signals ............................................................................................................................7

Table 3. 10/100 Mbits/s Twisted-Pair (TP) Interface Signals.....................................................................................7

Table 4. Status Signals .............................................................................................................................................8

Table 5. Clock and Reset Signals.............................................................................................................................9

Table 6. Control/Status Signals ..............................................................................................................................10

Table 7. Testability Signals......................................................................................................................................12

Table 8. MII Management Frame Format................................................................................................................13

Table 9. MII Management Frames—Field Description............................................................................................13

Table 10 . Absolute Maximum Ratings ...................................................................................................................14

Table 11 . Operating Conditions .............................................................................................................................14

Table 12. Summary of Management Registers (MR) .............................................................................................19

Table 13. MR0—Control Register Bit Descriptions.................................................................................................20

Table 14. MR1—Status Register Bit Descriptions ..................................................................................................21

Table 15. MR2, MR3—PHY Identification Registers (1 and 2) Bit Descriptions .....................................................22

Table 16. MR4—Autonegotiation Advertisement Register Bit Descriptions............................................................22

Table 17. MR5—Autonegotiation Link Partner Ability (Base Page) Register Bit Descriptions................................23

Table 18. MR5—Autonegotiation Link Partner (LP) Ability Register (Next Page) Bit Descriptions.........................23

Table 19. MR6—Autonegotiation Expansion Register Bit Descriptions..................................................................24

Table 20. MR7—Next Page Transmit Register Bit Descriptions..............................................................................25

Table 21. MR16—PCS Control Register Bit Descriptions.......................................................................................25

Table 22. MR17—Autonegotiation Read Register A...............................................................................................26

Table 23. MR18—Autonegotiation Read Register B...............................................................................................26

Table 24. MR20—User-Defined Register ...............................................................................................................27

Table 25. MR21—RXER Counter ...........................................................................................................................27

2

Advance Data Sheet DNC3X3625

March 2000 10/100 Mbits/s Ethernet Transceiver Macrocell

Table of Contents

Tables

Table 26. MR28—Device-Specific Register 1 (Status Register) Bit Descriptions...................................................27

Table 27. MR29—Device-Specific Register 2 (100 Mbits/s Control) Bit Descriptions.............................................28

Table 28. MR30—Device-Specific Register 3 (10 Mbits/s Control) Bit Descriptions...............................................29

Table 29. MR31—Device-Specific Register 4 (Quick Status) Bit Descriptions .......................................................30

(continued)

(continued)

Page

Figures Page

Figure 1. DNC3X3625 Functional Block Diagram ....................................................................................................4

Figure 2. I/Os of the DNC3X3625 Macrocell ............................................................................................................5

Figure 3. DNC MII TX Logic ...................................................................................................................................15

Figure 4. DNC MII RX Logic...................................................................................................................................15

Figure 5. DNC Maintenance Logic .........................................................................................................................15

Figure 6. Typical Application (One Channel Shown) ..............................................................................................16

Figure 7. Pinout Assignment ..................................................................................................................................17

Figure 8. Typical Single-Channel Twisted-Pair (TP) Interface.................................................................................18

3

DNC3X3625 Advance Data Sheet

10/100 Mbits/ s Ethernet Transceiver Macrocell March 2000

Description

The DNC3X3625 is a twisted-pair transceiver macrocell that supports transmission and reception over category 3

unshielded twisted-pair (UTP) cable and category 5 UTP.

The DNC3X3625 has been designed specifically for applications that support both 10Base-T and 100Base-X, such

as network interface cards (NICs), switches.

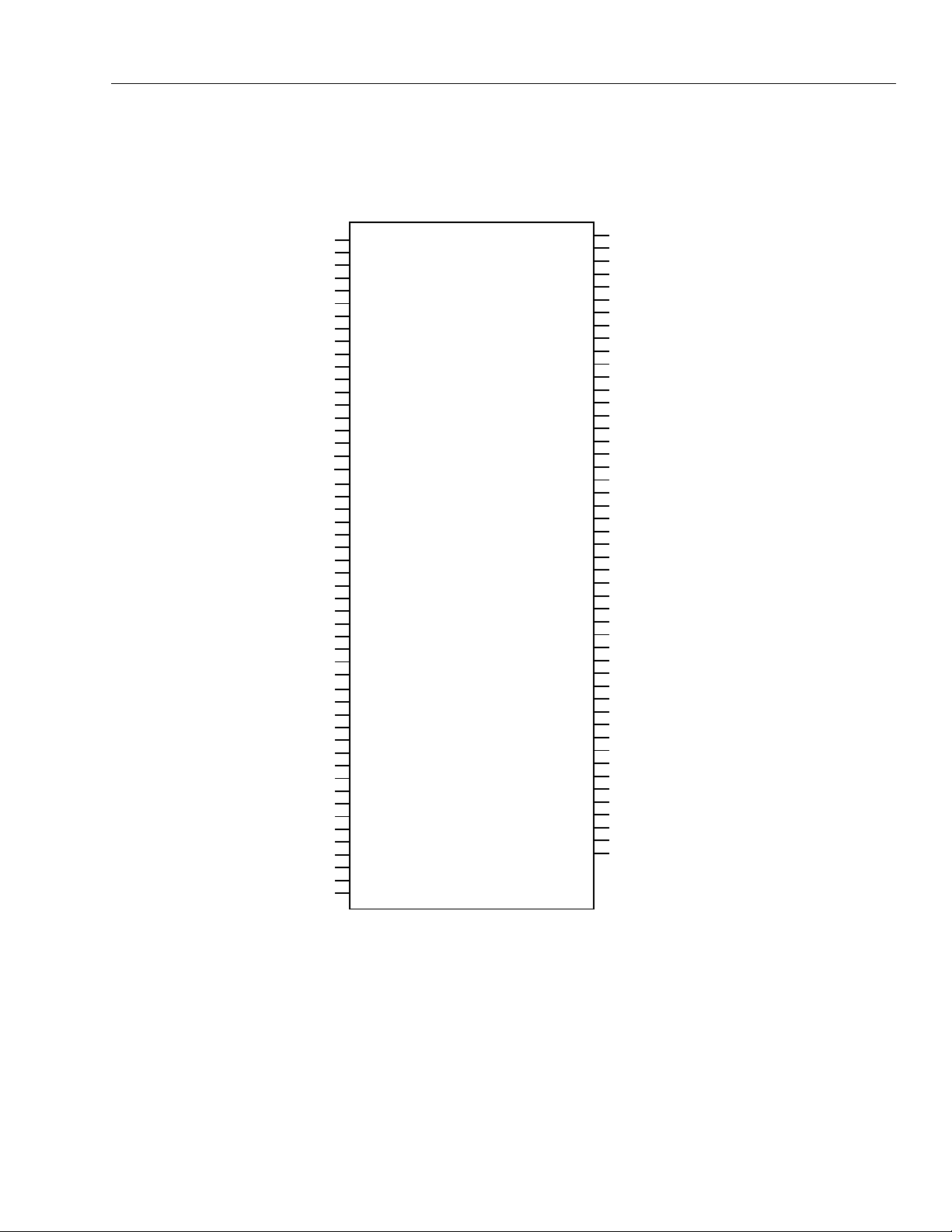

Figure 1 represents a functional block diagram of the DNC3X3625 macrocell.

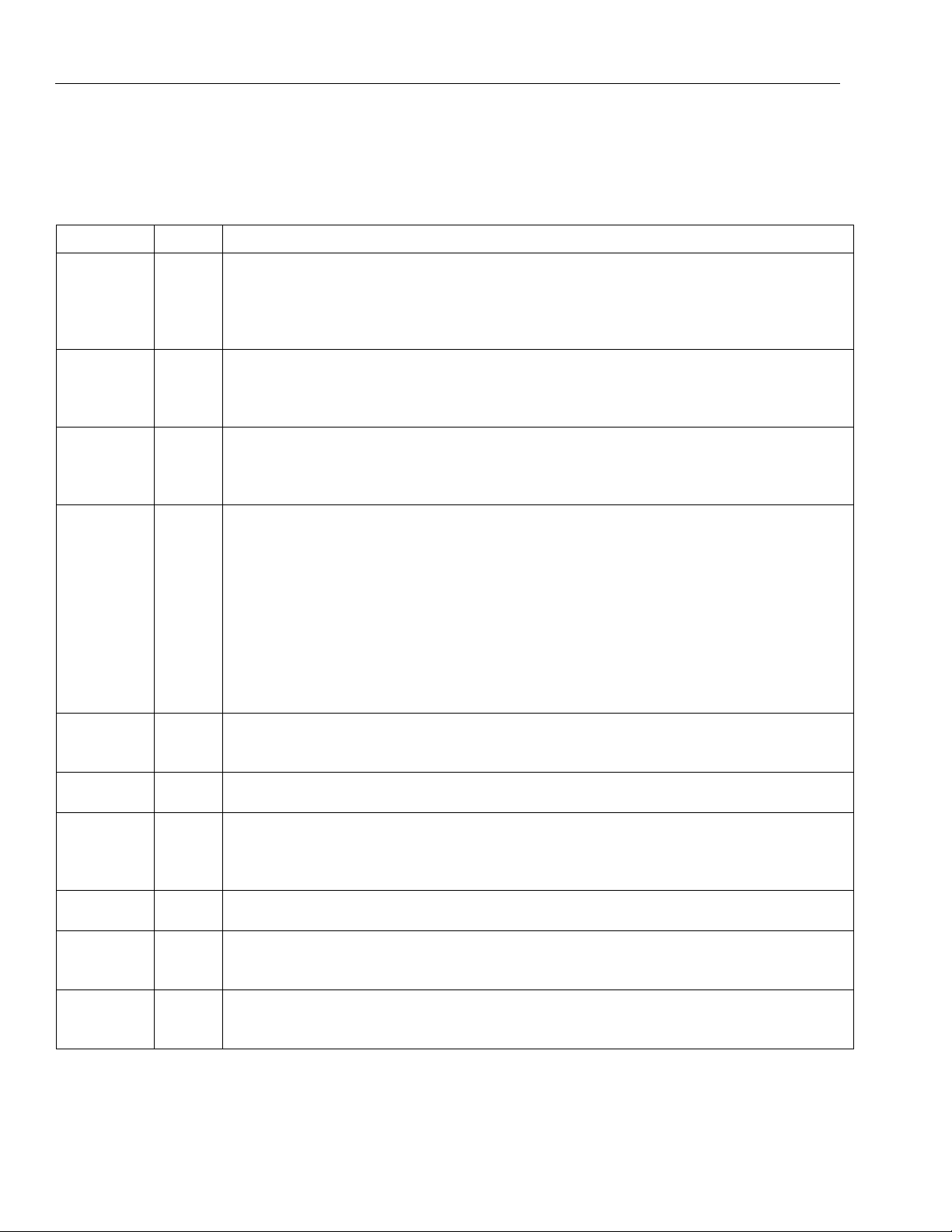

Figure 2 shows the I/Os of the DNC3X3625 macrocell.

Functional Block Diagram

100 Mbits/s TRANSCEIVER

MII

INTERFACE

INTERFACE

MANAGEMENT

RMCLK

125 MH

MTXD[3:0]

MCRS

MCOL

MRXD[3:0]

MRX_DV

MRX_ER

MRXCLK

MTXCLK

MTXD[3:0]

MTX_EN

MTX_ER

SERIAL/PARALLEL

INTERFACE

MDC

MDIO

FREQ.

SYNTH.

Z

MII

CLK20

25 MHz

125 MHz

20 MHz

4B/5B

ENCODER

TX STATE

MACHINE

CIM

5B/4B

DECODER

FAR-END

FAULT DETECT

10 Mbits/s TRANSCEIVER

MANAGEMENT

SD

CAR_STAT

RXERR_ST

MII

FAR-END

FAULT GEN.

COLLISION

DETECT

CARRIER

DETECT

ALIGNER

LC10 LS10

AUTONEGOTIATION

AND LINK MONITOR

SCRAMBLER

RX STATE

MACHINE

SD

DESCRAMBLER

LC100

LS100

SD

PDT

PDR/

DCRU

SD

PMD

TX

PMD

RX

TPO

TPI

±

±

25 MHz

CRYSTAL

5-5136(F).j

Figure 1. DNC3X3625 Functional Block Diagram (1 Channel Shown)

4

Advance Data Sheet DNC3X3625

4

March 2000 10/100 Mbits/s Ethernet Transceiver Macrocell

Description

Macrocell I/Os

(continued)

APFE_PIN[7:0]

AUTO_EN[7:0]

BYPPD125

BYPPD160

CARIN_IN[7:0]

CK125_BUF

CRS_SEL[7:0]

EDBT[7:0]

ELLE_PIN[7:0]

EN_RMCK

EN_XTL

FASTSEL[1:0]

FASTTEST

FX_MODE[7:0]

F_DUP[7:0]

HBT_PIN[7:0]

HWRESET

IN125

INT_MASK[7:0]

ISOLATE[7:0]

LED_STR_EN

LED_BLINK_EN

LITF_ENH

LPBK_PIN[7:0]

MDC

MDIO_IN

MGT_ADD[4:2]

MODEL[5:0]

MTXD[3:0][7:0]

MTX_EN[7:0]

MTX_ER[7:0]

NOLP_PIN[7:0]

OUI[24:3]

POR

PWRDN[7:0]

REV_ADD

RMCLK

SDBT[7:0]

SDFX[7:0]

SECUR[7:0]

SER_SEL_PIN[7:0]

SPEED_PIN[7:0]

TESTMDC

TESTMDIN

TESTSEL[3:0]

TESTTXD[3:0]

TESTTXEN

TESTTXER

TPI[7:0]

TPIB[7:0]

VERSION[3:0]

XLO

ATBON

AUTODONE[7:0]

FDUP_OUT[7:0]

REG20_OUT[15:0][7:0]

RST_10_BUSY[7:0]

RST_BUSY[7:0]

RST_TX_BUSY[7:0]

SERIAL_SEL[7:0]

TESTRXCK[7:0]

TESTRXDV[7:0]

TESTRXD[3:0][7:0]]

TESTRXER[7:0]

TESTTXCK[7:0]

ATBOP

CK125P

CK160

CLK25RAW

CS[7:0]

ECLN

ECLP

INT_R31[7:0]

LS100_OK[7:0]

LS10_OK[7:0]

LS_OK[7:0]

MCOL[7:0]

MCRS[7:0]

MDIO_HI_Z

MDIO_OUT

MRXCLK[7:0]

MRXD[3:0][7:0]

MRX_DV[7:0]

MRX_ER[7:0]

MTXCLK[7:0]

REXT10

REXT100

REXTBS

RMCLKRAW

RS[7:0]

SLOWCLK[7:0]

TESTCOL[7:0]

TESTCRS[7:0]

TESTMDHZ

TESTMDOUT

TPAPS[7:0]

TPJS[7:0]

TPO[7:0]

TPOB[7:0]

XHI

XS[7:0]

DNC3X3825

Figure 2. I/Os of the DNC3X3625 Macrocell

5-7541(F).a.r2

5

DNC3X3625 Advance Data Sheet

10/100 Mbits/ s Ethernet Transceiver Macrocell March 2000

Signal Information

Signal Descriptions

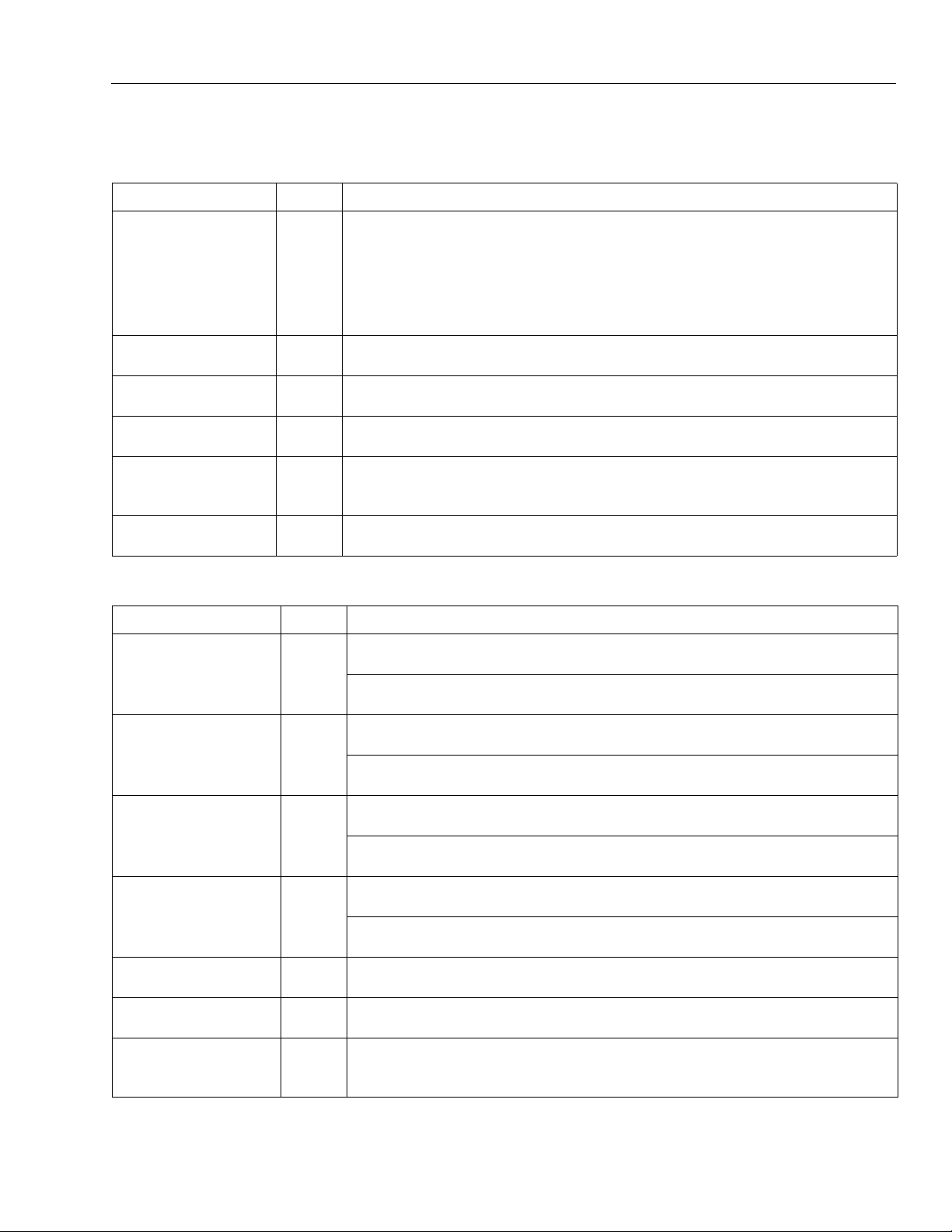

Table 1. MII/5-Bit Serial Interface Signals

Signal Type Name/Description

MCOL[5:0] O

MCRS[5:0] O

MRXCLK

[5:0]

MRXD[3:0]

[5:0]

Collision Detect.

the network. MCOL is asserted high whenever there is transmit and receive activity on the

UTP media. MCOL is the logical AND of MTX_EN and receive activity, and is an asynchronous output. When SER_SEL_PIN is high and in 10Base-T mode, MCOL indicates the

jabber timer has expired.

Carrier Sense.

transmit or receive medium is nonidle. This signal remains asserted throughout a collision

condition. When CRS_SEL is high, MCRS is asserted on receive activity only. CRS_SEL is

set via the MII management interface or the CRS_SEL signal.

Receive Clock.

O

nibble mode, and 10 MHz in 10 Mbits/s serial mode. MRXCLK has a worst-case 35/65 duty

cycle. MRXCLK provides the timing reference for the transfer of MRX_DV, MRXD, and

MRX_ER signals.

Receive Data

O

MRX_ER is asserted high in 100 Mbits/s mode, an error code will be presented on

MRXD[3:0] where appropriate. The codes are as follows:

This signal signifies in half-duplex mode that a collision has occurred on

When CRS_SEL is low, this signal is asserted high when either the

25 MHz clock output in 100 Mbits/s mode, 2.5 MHz output in 10 Mbits/s

. 4-bit parallel data outputs that are synchronous to MRXCLK. When

MRX_DV

[5:0]

MRX_ER

[5:0]

MTXCLK

[5:0]

MTXD[3:0]

[5:0]

MTX_EN

[5:0]

MTX_ER

[5:0]

Packet errors: ERROR_CODES = 2h.

Link error s: ERROR_CODES = 3h. (Packet a nd link erro r codes will only be repeated if

registers [29.9] and [29.8] are enabled.)

Premature end errors: ERROR_CODES = 4h.

Code errors: ERROR_CODES = 5h.

When SER_SEL_PIN is active-high and 10 Mbits/s mode is selected, MRXD[0] is used for

data output and MRXD[3:1] are 3-stated.

Receive Data Valid.

O

and decoding valid nibbles on MRXD[3:0], and the data is synchronous with MRXCLK.

MRX_DV is synchronous with MRXCLK. This signal is not used in serial 10 Mbits/s mode.

Receive Error.

O

error in the frame presently being received. MRX_ER is synchronous with MRXCLK.

Transmit Clock.

O

MII mode, 10 MHz output in 10 Mbits/s serial mode. MTXCLK provides timing reference for

the transfer of the MTX_EN, MTXD, and MTX_ER signals sampled on the rising edge of

MTXCLK.

Transmit Data.

I

active-high and 10 Mbits/s mode is selected, only MTXD[0] is valid.

Transmit Enable.

I

MTX_EN is synchronous with MTXCLK. When SER_SEL_PIN is active-high and

10 Mbits/s mode is selected, this signal indicates there is valid data on MTXD[0].

Transmit Coding Error.

I

corrupt the byte being transmitted across the MII (00100 will be transmitted). When in

10 Mbits/s mode, this signal is ignored.

When this signal is high, it indicates the DNC3X3625 is recovering

When high, MRX_ER indicates the DNC3X3625 has detected a coding

25 MHz clock output in 100 Mbits/s mode, 2.5 MHz output in 10 Mbits/s

4-bit parallel input synchronous with MTXCLK. When SER_SEL_PIN is

When driven high, this signal indicates there is valid data on MTXD[3:0].

When driven high, this signal causes the encoder to intentionally

6

Advance Data Sheet DNC3X3625

4

March 2000 10/100 Mbits/s Ethernet Transceiver Macrocell

Signal Information

Table 2. MII Management Signals

Signal

MDC I

MDIO_IN I

MDIO_OUT O

MDIO_HI_Z O

INT_MASK[5:0] I

INT_R31[5:0] O

(continued)

Type

Name/Description

Management Data Clock.

on the MDIO signal. This signal may be asynchronous to MRXCLK and

MTXCLK. The maximum clock rate is 12.5 MHz.

When running MDC above 6.25 MHz, MDC must be synchronous with

CLK25RAW and have a setup time of 15 ns and a hold time of 5 ns with respect

to CLK25RAW.

Management Data Input.

ment, synchronous with MDC, onto this input.

Management Data Output.

synchronous with MDC, onto this output.

Management Data Output Enable.

3-state the MDIO bidirectional buffer (external to the DNC3X3625).

Interrupt Mask.

When set low, interrupts are generated according to bit [31.7]. This signal is

ORed with bit [31.6].

Maskable Status Interrupt.

in status as defined in Table 27.

When set high, no interrupt is generated under any condition.

This is the timing reference for the transfer of data

Control information is driven by the station manage-

Status information is driven by the DNC3X3625,

When high, this signal can be used to

This signal will go high whenever there is a change

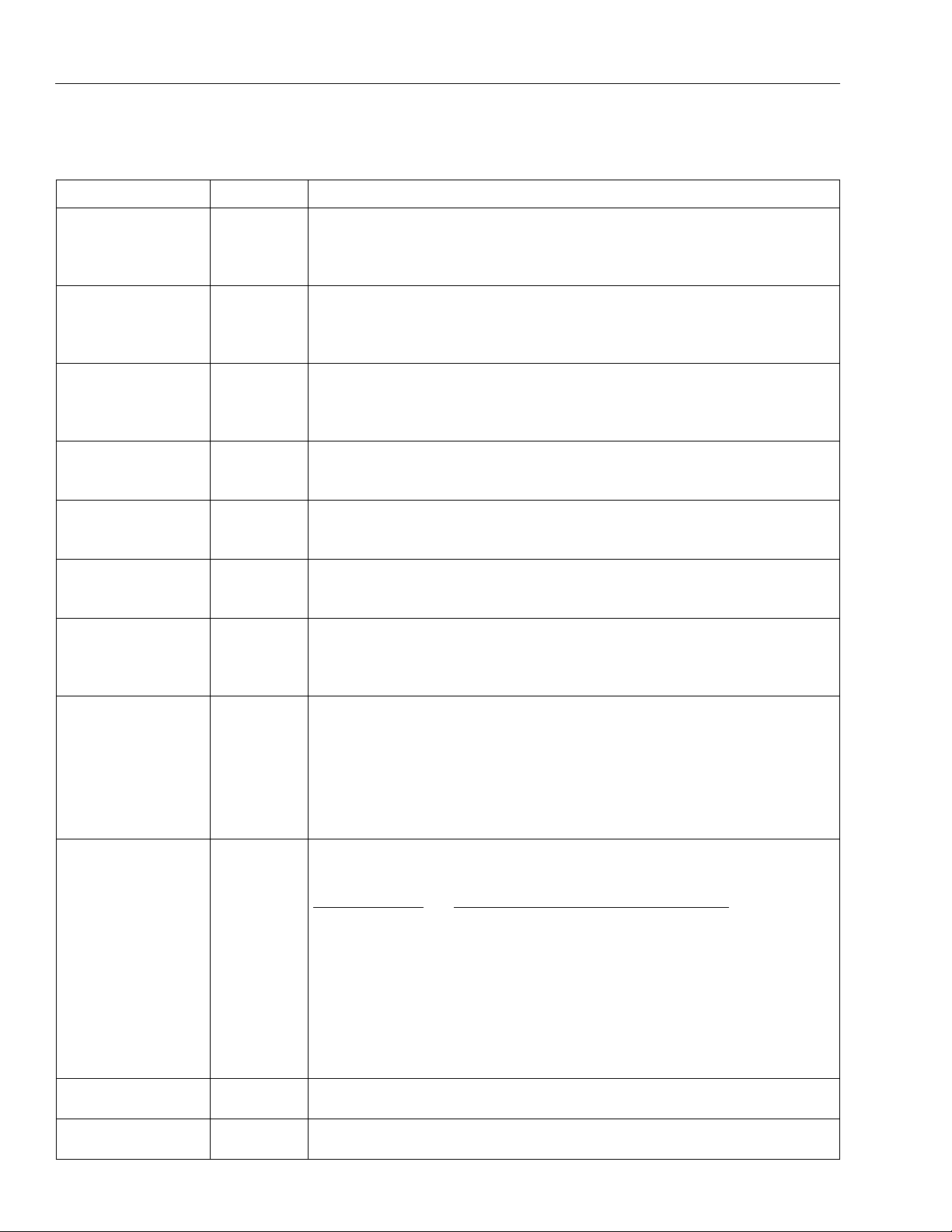

Table 3. 10/100 Mbits/s Twisted-Pair (TP) Interface Signals

Signal Type Name/Description

TPI

[5:0]

TPIB

[5:0]

TPO

[5:0]

TPOB

[5:0]

REXT10 PADO

REXT100 PADO

REXTBS PADO

PADI

PADI

PADO

PADO

Received Data.

Manchester data from magnetics.

Fiber-Optic Data Input.

data from fiber transceiver.

Received Data.

Manchester data from magnetics.

Fiber-Optic Data Input.

data from fiber transceiver.

Transmit Data.

Manchester data to magnetics.

Fiber-Optic Data Output.

compatible data to fiber transceiver.

Transmit Data.

Manchester data to magnetics.

Fiber-Optic Data Output.

ECL compatible data to fiber transceiver.

Current Setting 10 Mbits/s.

signal to ground to set the 10 Mbits/s TP driver transmit output level.

Current Setting 100 Mbits/s.

signal to ground to set the 100 Mbits/s TP driver transmit output level.

Band Gap Reference for the Receive Channel.

24.9 kΩ ± 1% resistor to ground. The parasitic load capacitance should be less

than 15 pF.

Positive differential received 125 Mbaud MLT3 or 10 Mbaud

Positive differential received 125 Mbaud pseudo-ECL

Negative differential received 125 Mbaud MLT3 or 10 Mbaud

Negative differential received 125 Mbaud pseudo-ECL

Positive differential transmit 125 Mbaud MLT3 or 10 Mbaud

Negative differential transmit 125 Mbaud MLT3 or 10 Mbaud

Positive differential transmit 125 Mbaud pseudo-ECL

Negative differential transmit 125 Mbaud pseudo-

An external resistor (21.0 kΩ) is placed from this

An external resistor (21.5 kΩ) is placed fro m this

Connect this signal to a

7

DNC3X3625 Advance Data Sheet

10/100 Mbits/ s Ethernet Transceiver Macrocell March 2000

Signal Information

LEDs operate as follows

LED_STR_EN = 0, LED_BLINK_EN = 0 => No stretching/blinking.

LED_STR_EN = 1, LED_BLINK_EN = 0 => Stretch to 42 ms, minimum.

LED_STR_EN = 0, LED_BLINK_EN = 1 => Every activity causes 42 mS ON, 42 mS OFF blink.

LED_STR_EN = 1, LED_BLINK_EN = 1 => Every activity causes 0.5 second ON, 0.5 second OFF blink.

Table 4. Status Signals

Signal Type Name/Description

XS[5:0] O

RS[5:0] O

CS[5:0] O

LS10_OK[5:0] O

LS100_OK[5:0] O

LS_OK[5:0] O

FDUP_OUT[5:0] O

TPJS[5:0] O

TPAPS[5:0] O

(continued)

:

Transmit Status.

stretched or blinked per the description given above.

Receive St atus

stretched or blinked per the description given above.

Collision Status

be stretched or blinked per the description given above.

Link10

Link100.

Link Status.

Full-Duplex Status

low, then the link is half duplex.

Jabber Status.

TP Autopolarity Status.

corrected.

This signal indicates transmit activity. This output can be

. This signal indicates receive activity . This output can be

. This signal indicates collision occurrence. This output can

. This signal indicates good link status for 10 Mbits/s.

This signal indicates good link status for 100 Mbits/s.

Indicates link status.

. If this signal is high, it indicates full-duplex link, and if it is

Indicates that there is a jabber condition (only in 10 Mbits/s).

Indicates if autopolarity has been detected and

8

Advance Data Sheet DNC3X3625

4

March 2000 10/100 Mbits/s Ethernet Transceiver Macrocell

Signal Information

Table 5. Clock and Reset Signals

Signal Type Name/Description

EN_RMCK I

RMCLK PA D I*

IN125 I

EN_XTL I

XLO PADI

XHI PADO

CLK25RAW O

RMCLKRAW O

SLOWCLK[5:0] O

HWRESET I

POR I

RST_BUSY[5:0] O

RST_10_BUSY[5:0] O

RST_TX_BUSY[5:0] O

BYPPD125 I This pin, when high, powers up the 125 MHz PLL permanently , allowing

BYPPD160 I This pin, when high, powers up the 160 MHz PLL permanently , allowing

CK125_BUF I This pin is the feedback for CK125P. Normally this will be connected to

CK160 O This is a 160 MHz output clock; this will be available if 10Base-T is enabled or

CK125P O This is a 125 MHz output clock, which must be fed back to CK125_BUF. This

(continued)

†

(optional)

Enable RMCLK

This signal and EN_XTL cannot be high simultaneously.

Primary Input Clock.

50 MHz. IN125 is used to indicate the appropriate frequency. This clock input

is used when EN_RMCK is high.

Input Clock Frequency Select

frequency of RMCLK is 125 MHz; else the clock frequency is 50 MHz.

Enable Crystal Input

(XLO) as the clock input. This signal and EN_RMCK cannot be high simultaneously.

Crystal Oscillator Input.

across XLO and XHI. Alternately, a 25 MHz external CMOS oscillator can be

connected to this input. This clock input is used when EN_XTL is high.

Crystal Oscillator Output

is not used.

CLK25RAW.

RMCLKRAW.

125 MHz, depending on RMCLK frequency.

24 Hz Clock Output.

Full-Chip Reset.

when reset is complete. 10Base-T and 100Base-TX/-FX are in reset until

enabled and take 1.3 ms to come out of reset.

Po wer-On Reset.

then tie this input low.

Reset Busy.

10Base-T in Reset.

100Base-TX Reset.

CK125P to be used for external logic at all times.

CK160 to be used for external logic at all times.

CK125P or any external chip clock buffers for CK125P.

BYPPD160 is high.

will be available when in 100Base-Tx mode or if BYPPD125 is high or if IN125

is high.

. When high, this signal selects RMCLK as the clock input.

The frequency of this clock can be either 125 MHz or

. When high, this signal will indicate that the

. This signal, when high, will select the crystal input

A 25 MHz crystal ± 25 ppm can be connected

. This pad does not have to be bonded out if crystal

25 MHz output clock.

Buffered version of the RMCLK. This is either 50 MHz or

This is a 24 Hz output signal.

Reset is active-high. The RST_BUSY signal will go low

If a powerup reset (PUR) cell from ASIC library is not used,

This signal indicates that the DNC3X3625 is in reset.

This signal indicates that the 10 Mbits/s logic is in reset.

This signal indicates that the 100 Mbits/s logic is in reset.

* Double bonded with XLO.

† Double bonded with RMCLK.

9

DNC3X3625 Advance Data Sheet

10/100 Mbits/ s Ethernet Transceiver Macrocell March 2000

Signal Information

Table 6. Control/Status Signals

Signal Type Description

AUTO_EN[5:0] I

F_DUP[5:0] I

CRS_SEL[5:0] I

SER_SEL_PIN[5:0] I

CARIN_IN[5:0] I

EDBT[5:0] I

SDBT[5:0] I

SPEED_PIN[5:0] I

(continued)

Autonegotiation Enable.

enabled. Pulsing this signal will cause autonegotiation to restart. This input

has the same function as register 0, bit 12. This input and the register bit are

ANDed together.

Full-Duplex Mode.

duplex mode. A low on this signal will put it in half-duplex mode. This signal

is ignored when autonegotiation is enabled. This is the same function as

register 0, bit 8. This input and the register bit are ORed together.

Carrier Sense Select.

MCRS operation. When this signal is pulled high, MCRS will be asserted on

receive activity only. This is the same function as register 29, bit 10. This

input and the register bit are ORed together.

Serial Mode Select.

tion of register 30, bit 1 by pulling it high, if station management is unavailable. This input and the register bit are ORed together.

Carrier Integrity Enable.

carrier integrity function of register 29, bit 3, if station management is

unavailable. This input and the register bit are ORed together.

Encoder/Decoder Bypass.

encoder/decoder bypass function of register 29, bit 6, if station management

is unavailable. This input and the register bit are ORed together.

Scrambler/Descrambler.

descrambler bypass function by pulling this signal high, if station management is unavailable. This is the same function as register 29, bit 4. This

input and the register bit are ORed together.

Speed.

same function as register 0, bit 13:

This signal can be used to select the operating speed and is the

When this signal is high, autonegotiation is

When this signal is set high, the PHY will be in full-

This signal may be used to select the mode of

This signal may be used to set the SERIAL_SEL func-

If this signal is pulled high, it will enable the

If this signal is pulled high, it will enable the

This signal may be used to enable the scrambler/

MGT_ADD[4:2] I

REV_ADD I

FX_MODE[5:0] I

10

■

If this signal is pulled high, it will enable 100 Mbits/s operation.

■

If this signal is pulled low, it will enable 10 Mbits/s operation.

This signal is ignored when autonegotiation is enabled. This signal and the

register bit are ANDed.

Management Address [4:2]

addresses and are decoded as follows:

MGT_ADD[4:2 ] PHY 0, PHY 1, PHY 2, PHY 3, PHY 4, PHY 5

000 0, 1, 2, 3, 4, 5

001 8, 9, 10, 11, 12, 13

010 16, 17, 18, 19, 20, 21

011 24, 25, 26, 27, 28, 29

100 6, 7, 8, 9, 10, 11

101 12, 13, 14, 15, 16, 17

110 18, 19, 20, 21, 22, 23

111 0, 0, 0, 0, 0, 0, 0, 0

Reverse Phy Address

Access. (PHY0 is highest address, PHY5 is lowest address)

FX_MODE

mode. This signal is ORed with register 29, bit 0 [29.0].

. When this signal is high, it puts DNC3X3625 in fiber-optic

. These signals set the management

. Reverse the order of Ports for Management

Loading...

Loading...