Aeroflex UTMC UT54ACTS193, UT54ACS193 Datasheet

137 RadHard MSI Logic

UT54ACS193/UT54ACTS193

Radiation-Hardened

Synchronous 4-Bit Up-Down Dual Clock Counters

FEATURES

Look-ahead circuitry enhances cascaded counters

Fully synchronous in count modes

Asynchronous clear

radiation-hardened CMOS

- Latchup immune

High speed

Low power consumption

Single 5 volt supply

Available QML Q or V processes

Flexible package

16-pin DIP

-

DESCRIPTION

The UT54ACS193 and the UT54ACTS193 are synchronous 4-

operation is provided by having all flip-flops clocked

simultaneously so that the outputs change coincident with each

output counting spikes normally associated with asynchronous

counters.

level transition of either count input (Up or Down). The direction of the counting is determined by which count input is pulsed

The counters are fully programmable. The outputs may be preset to either level by placing a low on the load input and entering

agree with the data inputs independently of the count pulses.

Asynchronous loading allows the counters to be used as modu-

preset inputs.

A clear input has been provided that forces all outputs to the low

pendent of the count and the load inputs.

The counter is designed for efficient cascading without the need

BO) produces a low-

Similarly, the carry output (CO

while the count is maximum

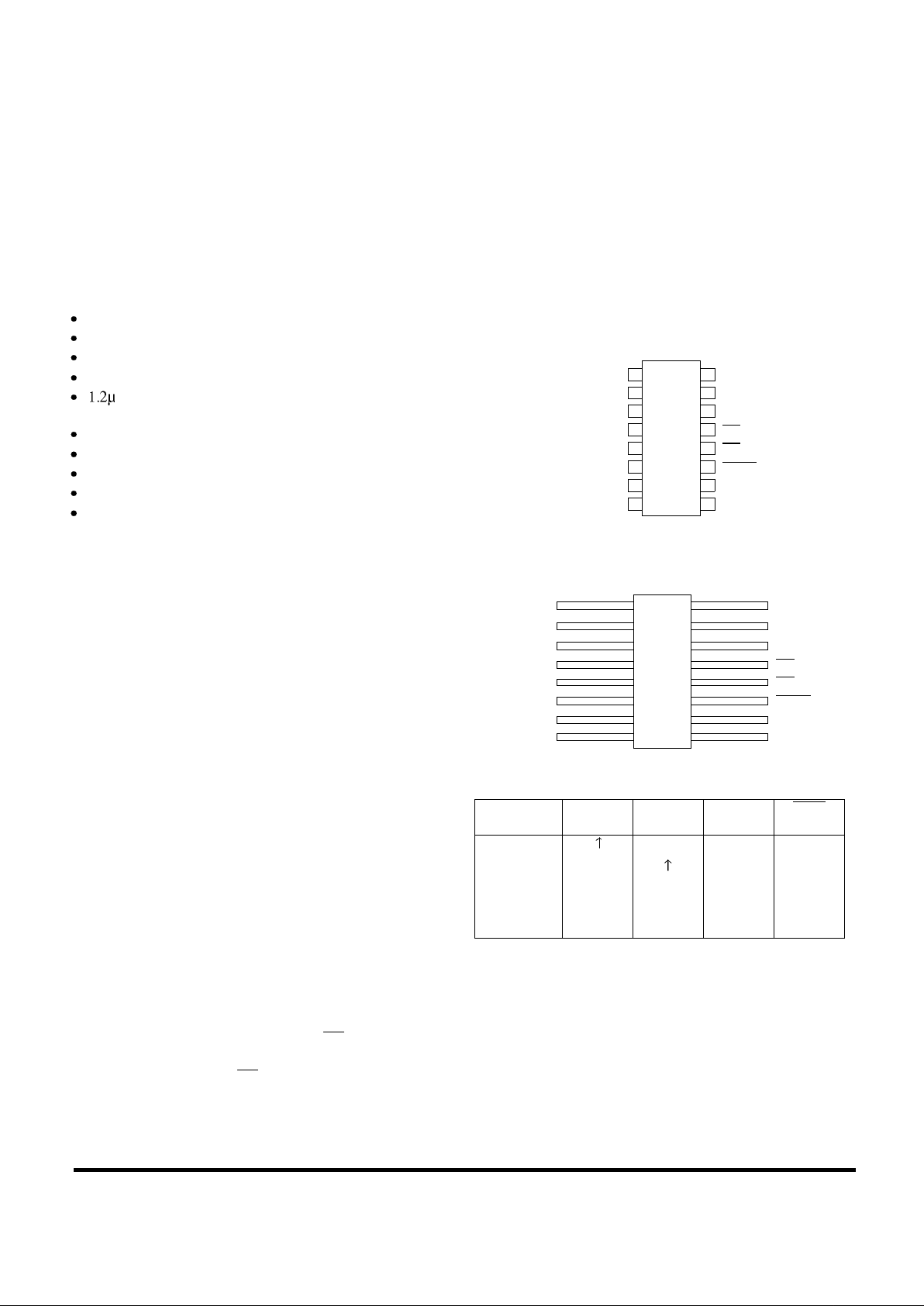

PINOUTS

Top View

16-Lead Flatpack

FUNCTION TABLE

FUNCTION CLOCK UPCLOCK

DOWN

CLR LOAD

Count Up H L H

Count Down H L H

Reset X X H X

Load Preset

Input

X X L L

1

2

3

4

5

7

6

16

15

14

13

12

10

11

B

Q

B

Q

A

DOWN

UP

Q

C

Q

D

V

DD

A

CLR

BO

CO

C

8 9

V

SS

D

LOAD

1

2

3

4

5

7

6

16

15

14

13

12

10

11

V

DD

8 9

B

Q

B

Q

A

DOWN

UP

Q

C

Q

D

A

CLR

BO

CO

LOAD

C

V

SS

D

RadHard MSI Logic 138

UT54ACS193/UT54ACTS193

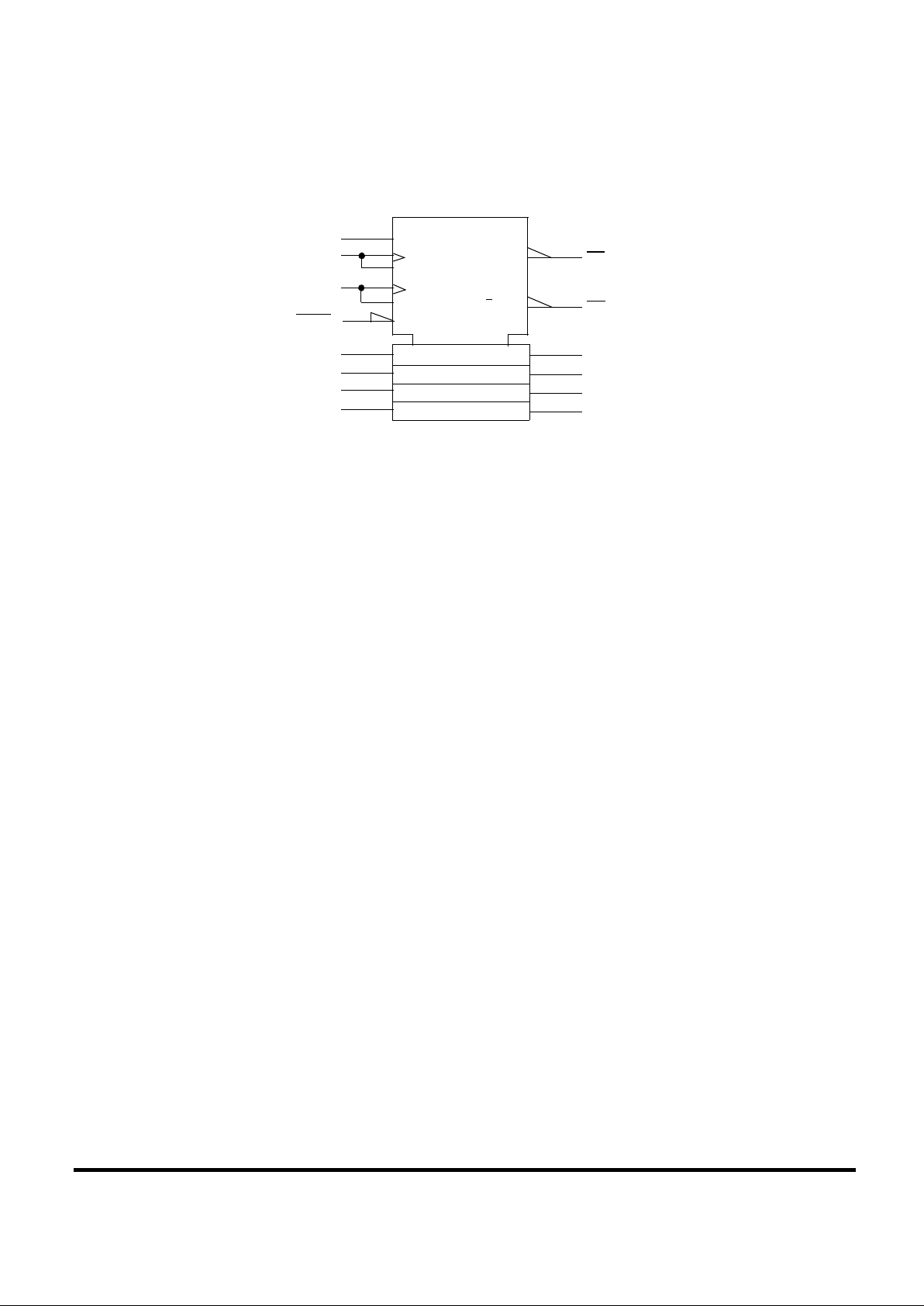

LOGIC SYMBOL

(14)

CLR

(5)

UP

G1

CT=0

CTRDIV 16

(4)

DOWN

(15)

A

(1)

B

(10)

C

(9)

D

(12)

(3)

Q

A

(7)

Q

D

(6)

Q

C

(2)

Q

B

3D

(1)

(2)

(4)

(8)

2+

G2

(11)

LOAD C3

(13)

BO

2CT=0

1-

CO

1CT=15

Note:

1. Logic symbol in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

139 RadHard MSI Logic

UT54ACS193/UT54ACTS193

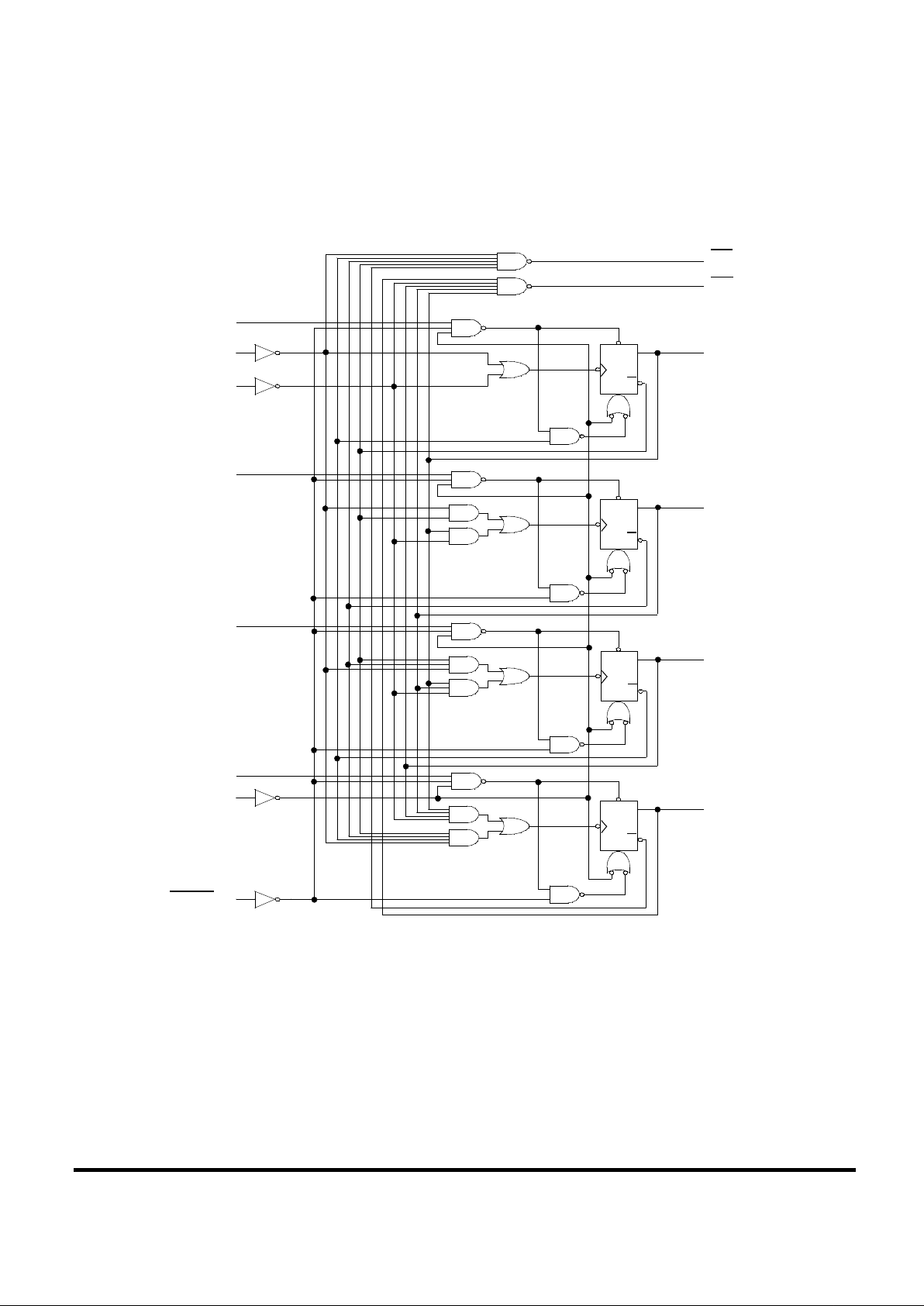

LOGIC DIAGRAM

A

DOWN

UP

CLR

LOAD

(15)

(4)

(5)

(1)

(10)

(9)

(14)

(11)

Q

(7)

(6)

(2)

(3)

(12)

(13)

B

C

D

BO

CO

D

C

B

A

Q

Q

Q

C

Q

R

S

Q

C

Q

R

S

Q

C

Q

R

S

Q

C

Q

R

S

Q

Loading...

Loading...