Aeroflex UTMC UT54ACTS165, UT54ACS165 Datasheet

113 RadHard MSI Logic

UT54ACS165/UT54ACTS165

Radiation-Hardened

8-Bit Parallel Shift Registers

FEATURES

Complementary outputs

Direct overriding load (data) inputs

Gated clock inputs

Parallel-to-serial data conversions

radiation-hardened CMOS

- Latchup immune

High speed

Low power consumption

Single 5 volt supply

Available QML Q or V processes

Flexible package

- 16-pin DIP

- 16-lead flatpack

DESCRIPTION

The UT54ACS165 and the UT54ACTS165 are 8-bit serial shift registers that, when clocked, shift the data toward serial output QH. Parallel-

in access to each stage is provided by eight individual data inputs that

are enabled by a low level at the SH/LD input. The devices feature a

clock inhibit function and a complemented serial output QH .

Clocking is accomplished by a low-to-high transition of the CLK input

while SH/LD is held high and CLK INH is held low. The functions of

the CLK and CLK INH (clock inhibit) inputs are interchangeable.

Since a low CLK input and a low-to-high transition of CLK INH will

also accomplish clocking, CLK INH should be changed to the high

level only while the CLK input is high. Parallel loading is disabled

when SH/LD is held high. Parallel inputs to the registers are enabled

while SH/LD is low independently of the levels of CLK, CLK INH or

SER inputs.

The devices are characterized over full military temperature range of

-55 C to +125 C.

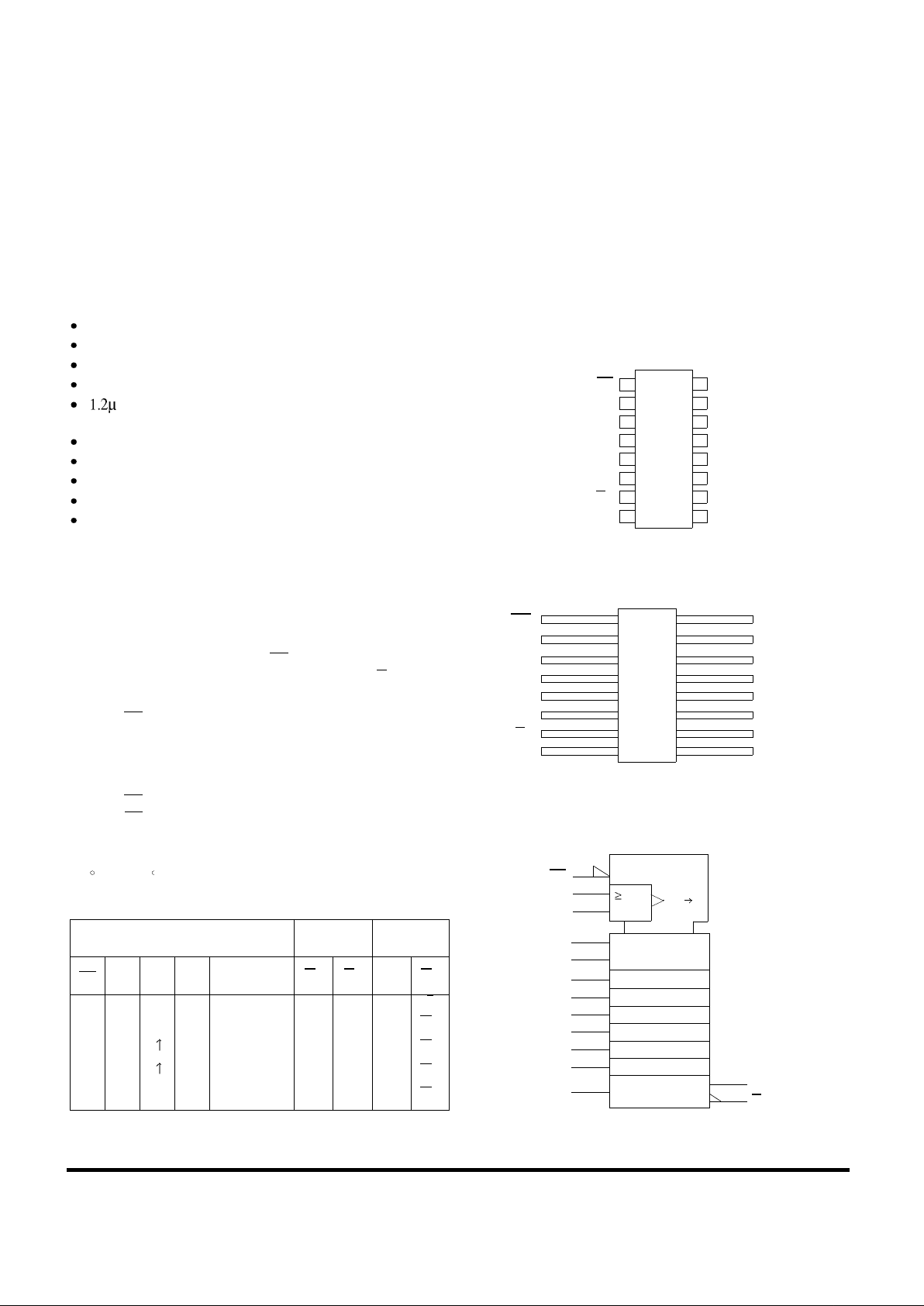

FUNCTION TABLE

Note:

1. Qn = The state of the referenced output one setup time prior to the Low-toHigh clock transition.

PINOUTS

16-Pin DIP

Top View

16-Lead Flatpack

Top View

LOGIC SYMBOL

INPUTS INTERNAL

OUTPUTS

OUTPUTS

SH/LDCLK

INH

CLK SER PARALLEL

A . . . H

QAQBQHQ

H

L X X X a . . . h a b h

h

H L L X X QAQBQHQ

H

H L H X H QAQGQ

G

H L L X L QAQGQ

G

H H X X X QAQBQHQ

H

1

2

3

4

5

7

6

16

15

14

13

12

10

11

SH/LD

CLK

E

F

G

H

Q

H

V

DD

CLK INH

D

C

B

A

SER

8

9

V

SS

Q

H

1

2

3

4

5

7

6

16

15

14

13

12

10

11

V

DD

8 9

SH/LD

CLK

E

F

G

H

Q

H

CLK INH

D

C

B

A

SER

V

SS

Q

H

(1)

SH/LD

(15)

CLK INH

C2/

C1 (LOAD)

(10)

SER

(11)

A

SRG8

(9)

Q

H

(7)

Q

H

1

(2)

CLK

2D

1D

(12)

B

(13)

C

(14)

D

(3)

E

(4)

F

(5)

G

(6)

H

1D

1D

RadHard MSI Logic 114

UT54ACS165/UT54ACTS165

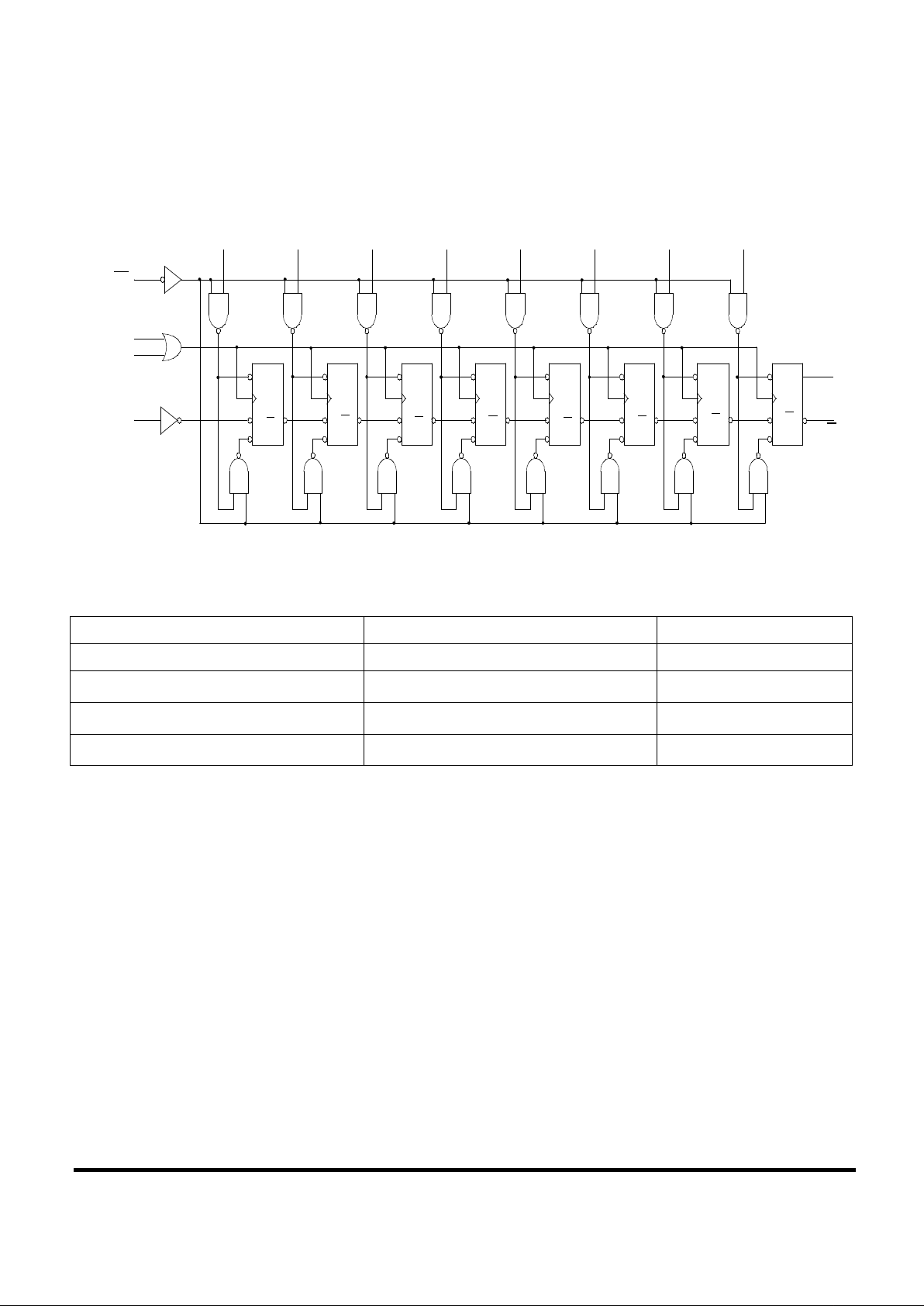

LOGIC DIAGRAM

RADIATION HARDNESS SPECIFICATIONS

1

Notes:

1. Logic will not latchup during radiation exposure within the limits defined in the table.

2. Device storage elements are immune to SEU affects.

PARAMETER LIMIT UNITS

Total Dose 1.0E6 rads(Si)

SEU Threshold

2

80

MeV-cm2/mg

SEL Threshold 120

MeV-cm2/mg

Neutron Fluence 1.0E14

n/cm

2

A B C D E F G

H

(11) (12) (13) (14) (4) (5) (6)

(3)

S

C

D

R

(1)

(15)

(2)

(10)

CLK INH

CLK

SER

Q

C

Q

D

Q

E

Q

F

Q

G

SH/LD

(9)

(7)

Q

H

Q

H

S

C

D

R

S

C

D

R

S

C

D

R

S

C

D

R

S

C

D

R

S

C

D

R

Q

A

S

C

D

R

Q

H

Q

B

Loading...

Loading...