Aeroflex UTMC UT54ACTS138, UT54ACS138 Datasheet

71 RadHard MSI Logic

UT54ACS138/UT54ACTS138

Radiation-Hardened

3-Line to 8-Line Decoders/Demultiplexers

FEATURES

• radiation-hardened CMOS

- Latchup immune

• High speed

• Low power consumption

• Single 5 volt supply

• Available QML Q or V processes

• Flexible package

- 16-pin DIP

- 16-lead flatpack

DESCRIPTION

The UT54ACS138 and the UT54ACTS138 3-line to 8-line decoders/demultiplexers are designed to be used in high-performance memory-decoding or data-routing applications requiring

very short propagation delay times.

The conditions at the binary select inputs and the three enable

inputs select one of eight output lines. Two active-low and one

active-high enable inputs reduce the need for external gates of

inverters when expanding. A 24-line decoder can be implemented without external inverters and a 32-line decoder requires only

one inverter. An enable input can be used as a data input for

demultiplexing applications.

The devices are characterized over full military temperature

range of -55 C to +125 C.

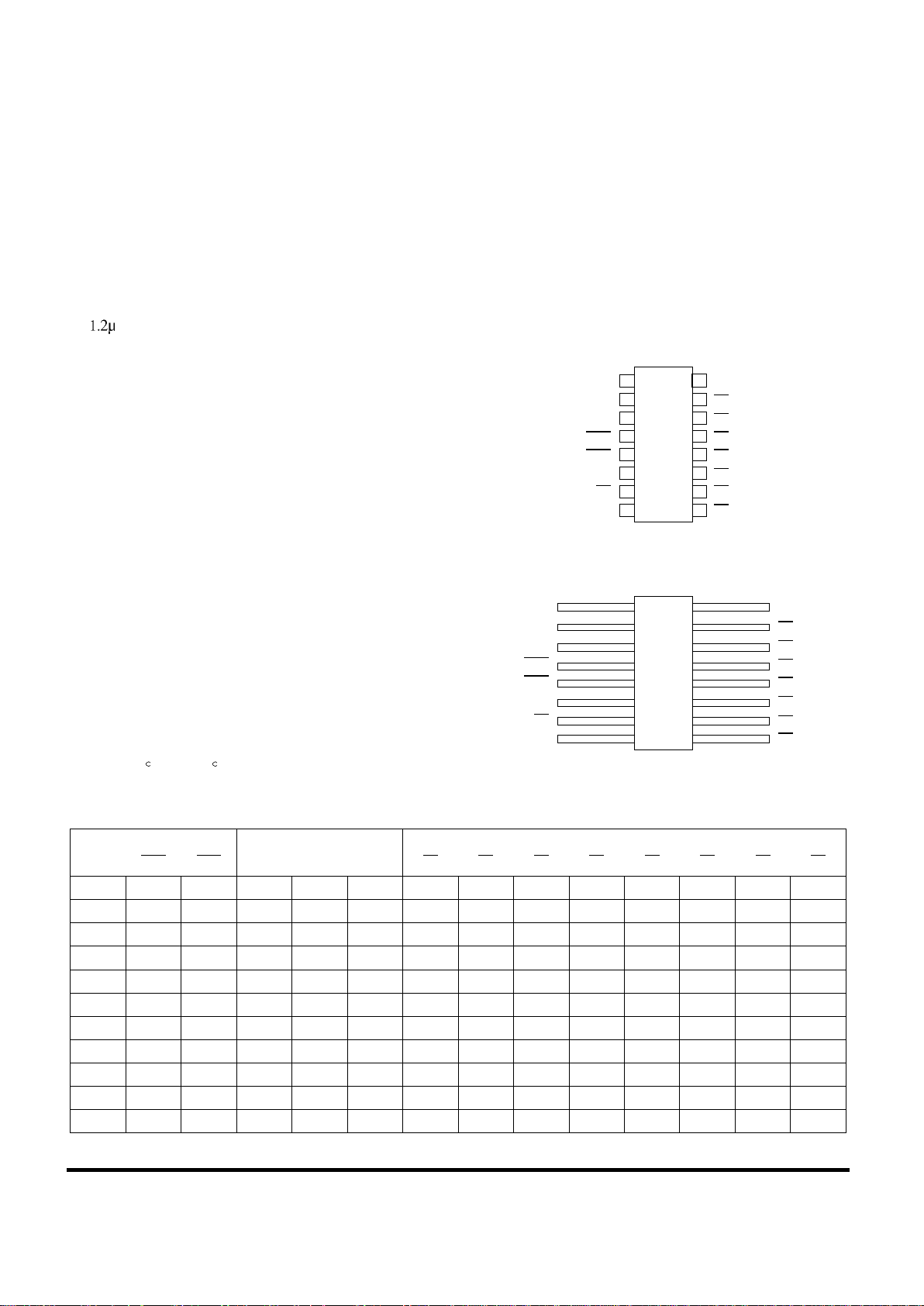

PINOUTS

16-Pin DIP

Top View

16-Lead Flatpack

Top View

FUNCTION TABLE

1

2

3

4

5

7

6

16

15

14

13

12

10

11

A

B

C

G2A

G2B

G1

Y7

V

DD

Y0

Y1

Y2

Y3

Y4

Y5

8 9V

SS

Y6

1

2

3

4

5

7

6

16

15

14

13

12

10

11

V

DD

A

B

C

G2A

G2B

G1

Y7

Y0

Y1

Y2

Y3

Y4

Y5

V

SS

Y6

8 9

ENABLE INPUTS SELECT INPUTS OUTPUT

G1 G2A G2B C B A Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

X X H X X X H H H H H H H H

L X X X X X H H H H H H H H

X H X X X X H H H H H H H H

H L L L L L L H H H H H H H

H L L L L H H L H H H H H H

H L L L H L H H L H H H H H

H L L L H H H H H L H H H H

H L L H L L H H H H L H H H

H L L H L H H H H H H L H H

H L L H H L H H H H H H L H

H L L H H H H H H H H H H L

RadHard MSI Logic 72

UT54ACS138/UT54ACTS138

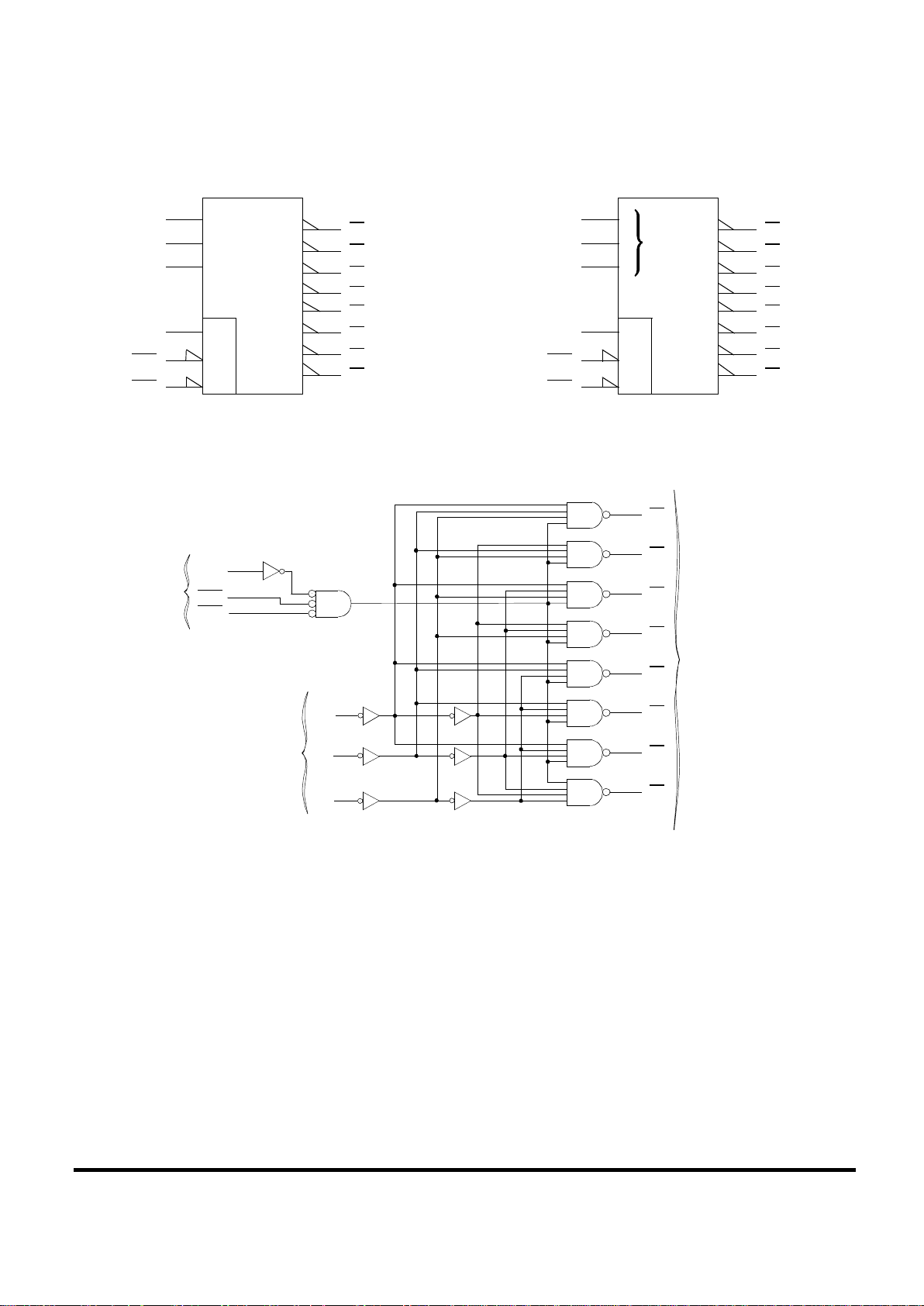

LOGIC SYMBOL

LOGIC DIAGRAM

(7)

Y7

(1)

A

(2)

B

(3)

C

(6)

G1

(4)

G2A

(5)

G2B

2

4

1

(9)

Y6

(10)

Y5

(11)

Y4

(12)

Y3

(13)

Y2

(14)

Y1

(15)

Y0

BIN/OCT

EN

&

1

2

0

4

5

3

6

7

(7)

Y7

(1)

A

(2)

B

(3)

C

(6)

G1

(4)

G2A

(5)

G2B

2

4

1

(9)

Y6

(10)

Y5

(11)

Y4

(12)

Y3

(13)

Y2

(14)

Y1

(15)

Y0

DMUX

EN

&

1

2

0

4

5

3

6

7

Note:

1. Logic symbols in accordance with ANSI/IEEE standard 91-1984 and IEC Publication 617-12.

G

0

7

---

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

DATA

SELECT

ENABLE

(15)

(14)

(13)

(12)

(11)

(10)

(9)

(7)

(3)

(2)

(1)

A

B

C

(6)

(4)

(5)

G1

G2A

G2B

Loading...

Loading...