Aeroflex Circuit Technology R4430PC-F10-MCM, R4430PC-P10-MCM, R4430SC-1M-F10-MCM Datasheet

1

SCD4430 Rev A 11/18/96

The Aeroflex “RISC TurboEngine”

©

A MIPS© R4400 RISC Microprocessor Multichip

Module

Aeroflex Circuit Technology

35 South Service Road, Plainview NY 11803

Tel:(516) 694-6700, Fax:(516) 694-6715

1.0 Description

The Aeroflex Circuit Technology “RISC TurboEngine” is a full military temperature range 64 bit, superpipelined RISC microprocessor with 1M Byte of secondary cache memory packaged in a high speed

multichip module (MCM). The module contains the following components:

• (1) R4400SC/MC, a 3.3V powered RISC microprocessor.

• (11) SRAMs, 64K by 16.

• (3) Buffers and (3) Passive components for phase lock loop operation.

A Primary cache only version, the R4400PC is also available in the same package or 179 pin PGA

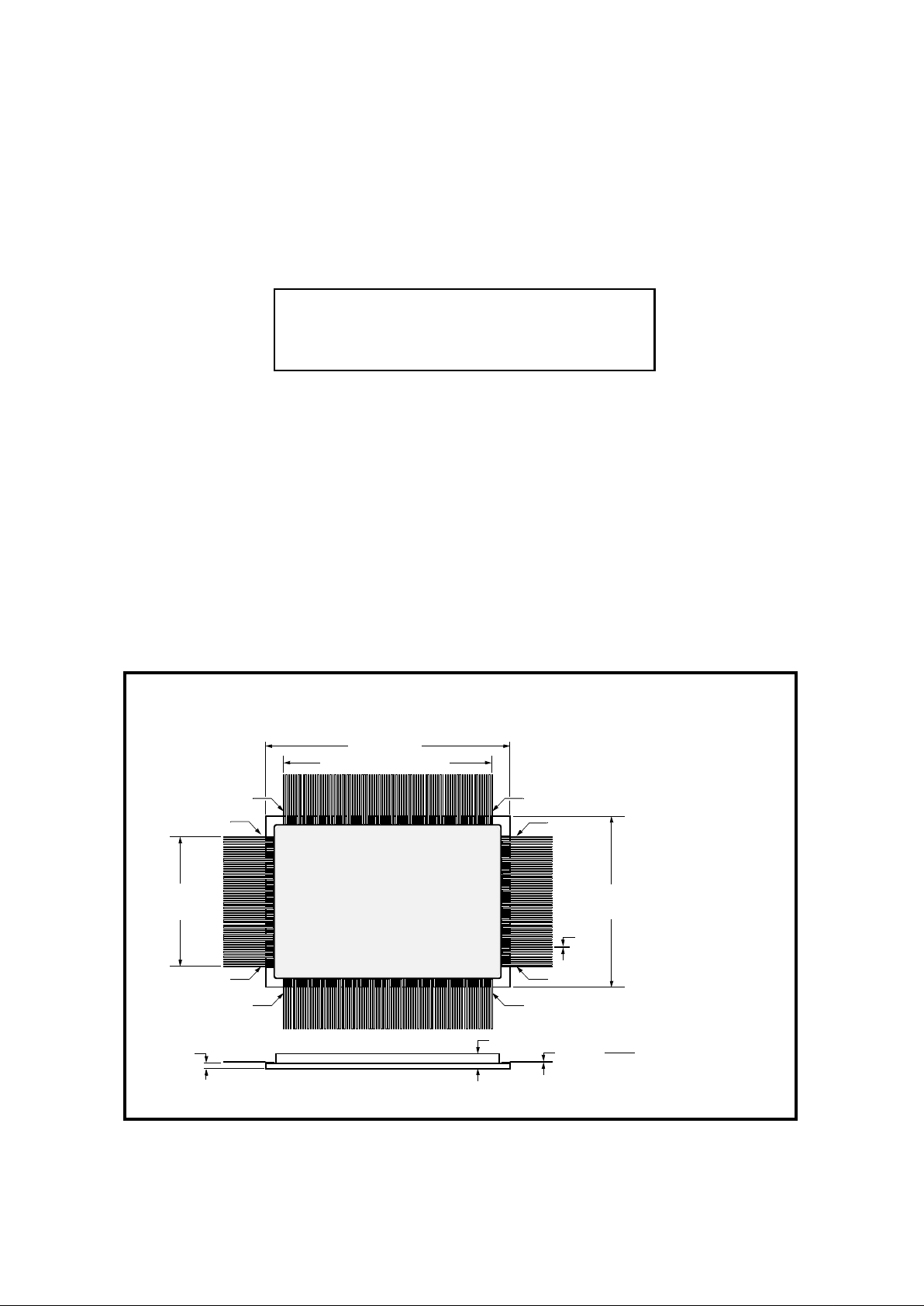

2.0 Flat Package Outline

85 Spaces at 0.025

1.768

MAX

53 Spaces

at 0.025

.010

Pin 226

Pin 141

Pin 227

Pin 140

Pin 87

Pin 86

Pin 280

Pin 1

.006

.175 MAX

.072 ±.01

2.525 MAX

R4400PC/SC

MCM

Note: Outside ceramic tie

bars not shown for clarity.

Contact factory for details

“F10” Package

(Preliminary Data Sheet, use with “MIPS R4000 Microprocessor Users Manual”© MIPS 1993)

2

SCD4430 Rev A 11/18/96

3.0 Electrical Features

• Low power dissipation, 3.3 Volt powered, 64 bit superpipelined RISC R4400 microprocessor

- Highly integrated CPU with integer unit, FPA, MMU, I&D cache

- Balanced integer & floating point performance

- Exploits 2-level instruction-level parallelism

- No issue restrictions on the instructions used

• Integer unit

- 32 entry, 64 bit wide register

- ALU

- Dedicated multiplier/divider

• Super pipelined FPA

- 32/16 entry 32/64 bit register file in a 32 bit mode

- 32 entry 64 bit register file in 64 bit mode

- Supports single and double precision.

- Supports ANSI/IEEE Standard 754-1985

• Memory management unit

- 48 entry TLB for fast virtual-to-physical address translation, software managed cntrl regstrs

- Programmable page sizes from 4K bytes to 16M bytes

- Total physical address space encompasses 64G bytes

- One pair of pages per TLB entry, each programable in size from 4K bytes to 16M bytes

• JTAG boundary scan capability for testing module interconnects.

• Internal 1M byte secondary cache SRAM configured as a split cache with instruction and data sections sepa-

rate. Can be factory configured as unified.

• Provides 16 bit ECC on secondary cache data line, 7 bit ECC on tag line.

• Minimum clock rate 50 mHz with no wait states.

• +3.3 Volt P.S.(10 Watts Max.power dissipation) operation is standard.

4.0 Mechanical Features

• Small sizes, 2.5”L X 1.75”W X 0.175”H, 280 pin surface mount flat package or alternate 1.86”LX1.86”W X

0.145”H, 179 pin PGA Package.

• Full military operating temperature range of -55 °C to +125 °C, case temperature

• Designed to meet military specifications, manufactured and tested in Aeroflex’s MIL-PRF-38534 certified

facility.

3

SCD4430 Rev A 11/18/96

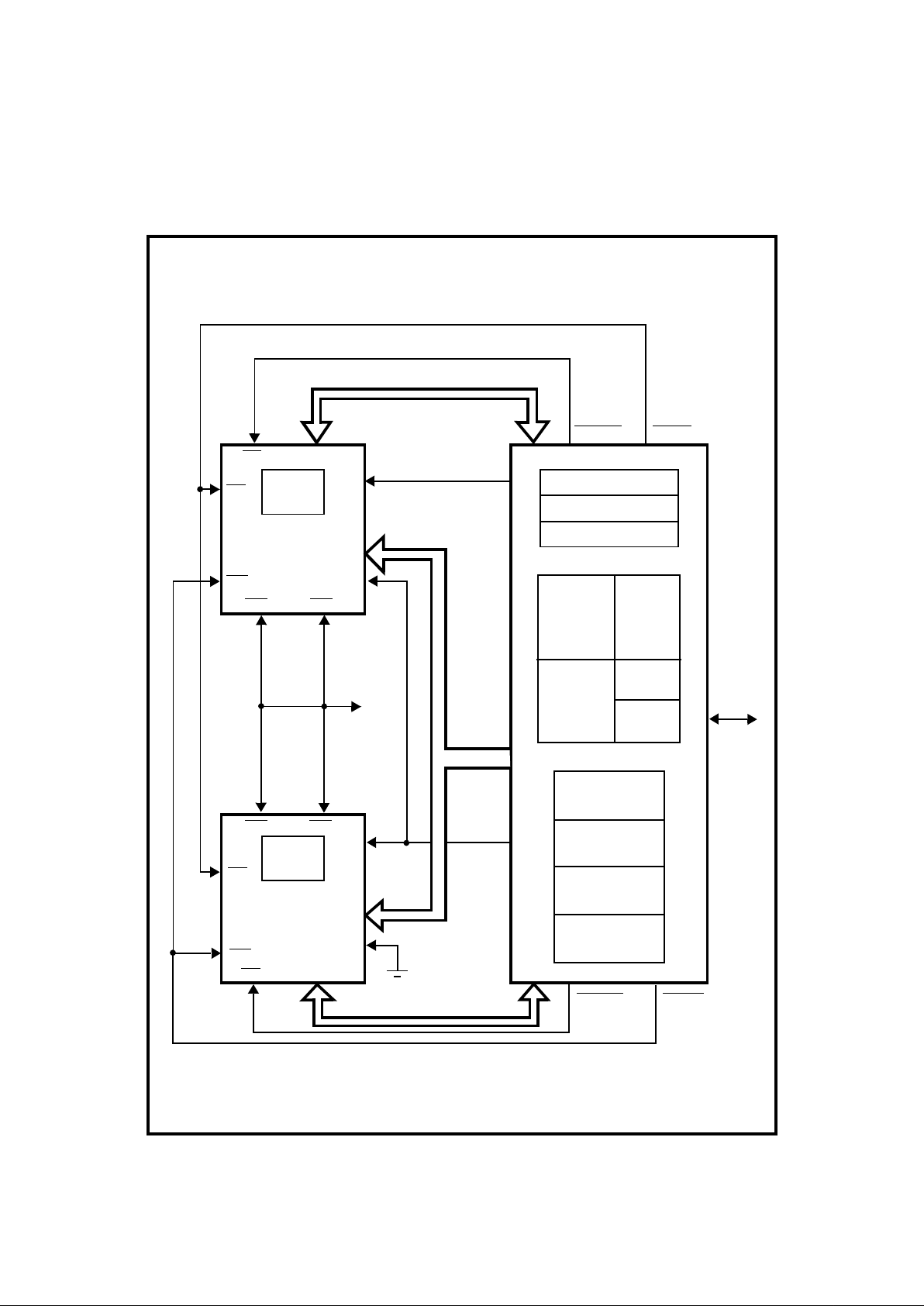

5.0 INTERNAL BLOCK DIAGRAM(SC Version)

General Registers

ALU/Multiply/Divide

Pipeline/Control

INTEGER EXECUTION UNIT

CACHE/MMU

FLOATING POINT

16K Byte

Instruction

Cache

16K Byte

Data

Cache

48 Entry

TLB

Cache

Control

MMU

FPU ALU

Multiply/Divide

Square Root

FP Register

Pipeline Control

SCOESCDCS

SCData(127:0)

SCDchk(15:0)

SCAddr0

SCAddr

SCAddr

17

SCTag(24:0)

SCTchk(6:0)

SCTCS

SCWE

A0

A15

A14:A1

CE

DQ0-DQ31

GND

BW

LBWH

A15

A0

DQ143-DQ0

CE

OE

WE

(9) 64K

by 16

SRAMs

System

Interface

R4400SC/MC Microprocessor

CACHE

CACHE TAG

OE

WE

(14:1)

BW

LBWH

DATA/INSTRUCTION

(2) 64K

by 16

SRAMs

A14:A1

4

SCD4430 Rev A 11/18/96

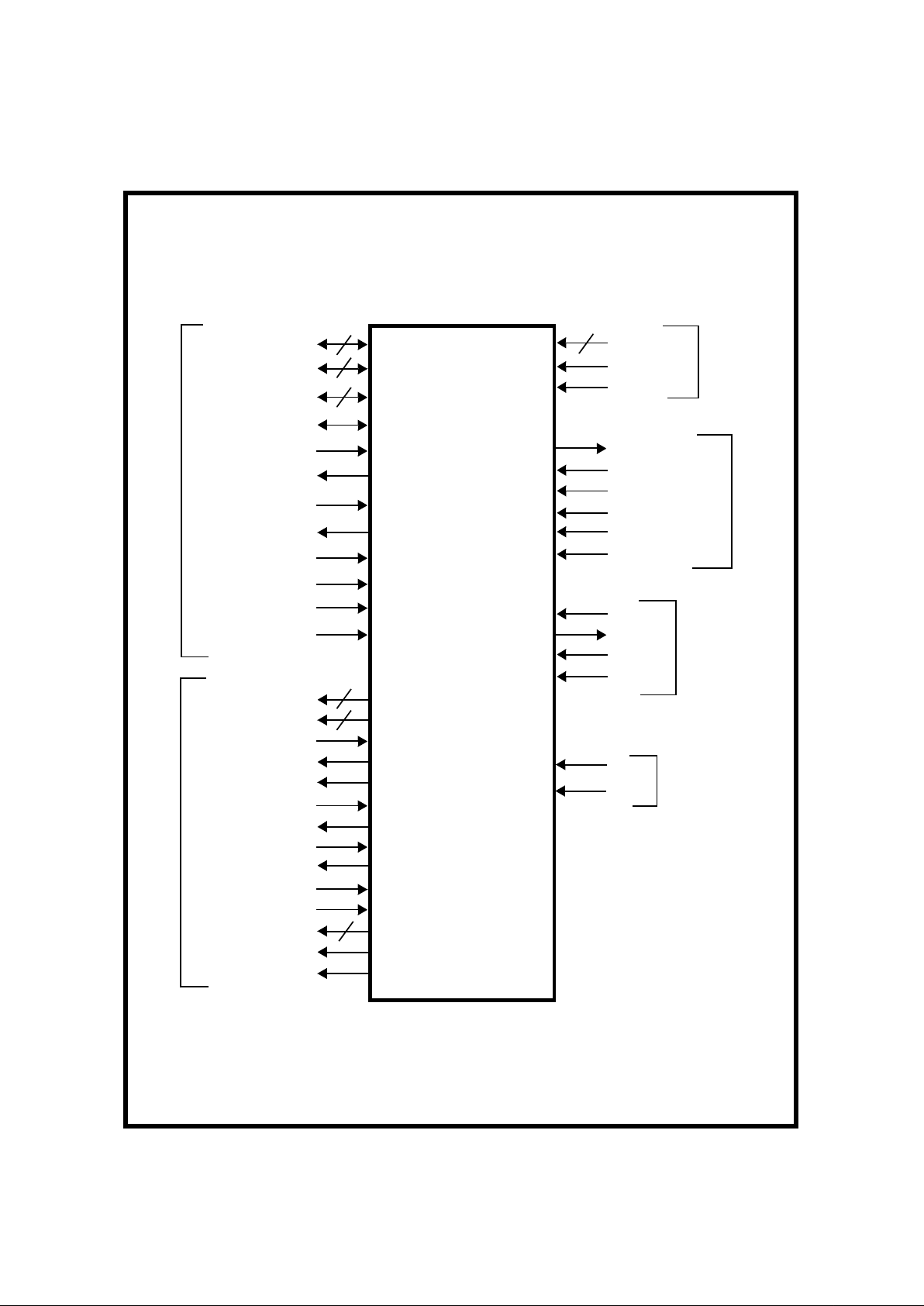

6.0 Module Symbolic Interface Connections

SysAD(63:0)

SysAD(7:0)

SysCmd(8:0)

SysCmdP

ValidIn*

ValidOut*

ExtRqst*

Release*

RdRdy*

WrRdy*

IvdAck* ‡

IvdErr* ‡

TClock(1:0)

RClock(1:0)

MasterClock

MasterOut

SyncOut

SyncIn

IOOut

IOIn

Fault*

VccP

VssP

Status(7:0)

VccSense

System Interface

Clock/Control Interface

Int(5:1)*

Int0*

NMI*

ModeClock

ModeIn

VCCOk

ColdReset*

Reset*

JTDI

JTDO

JTMS

JTCK

VssSense

Interrupt

Interface

Initialization

Interface

JTAG

Interface

64

8

9

2

2

5

R4400

Multichip

Module

8

Vcc

Gnd

Power

Note: Int(5:1)* available on R4400PC version

‡ IvdAck, IvdErr used in “MC” mode

256K/1M*

Loading...

Loading...