Page 1

ETX®-PVR

Computer-on-Module

Reference Manual

P/N 50-1Z057-1010

Page 2

Notice Page

DISCLAIMER

ADLINK Technology, Incorporated makes no representations or warranties with respect to the contents of

this manual or of the associated ADLINK products, and specifically disclaims any implied warranties of

merchantability or fitness for any particular purpose. ADLINK shall under no circumstances be liable for

incidental or consequential damages or related expenses resulting from the use of this product, even if it has

been notified of the possibility of such damages. ADLINK reserves the right to revise this publication from

time to time without obligation to notify any person of such revisions. If errors are found, please contact

ADLINK at the address shown at the bottom of this page.

TRADEMARKS

CoreModule and the Ampro logo are registered trademarks, and ADLINK, Little Board, LittleBoard,

MightyBoard, MightySystem, MilSystem, MiniModule, ReadyBoard, ReadyBox, ReadyPanel,

ReadySystem, and RuffSystem are trademarks of ADLINK Technology, Inc. All other marks are the

property of their respective companies.

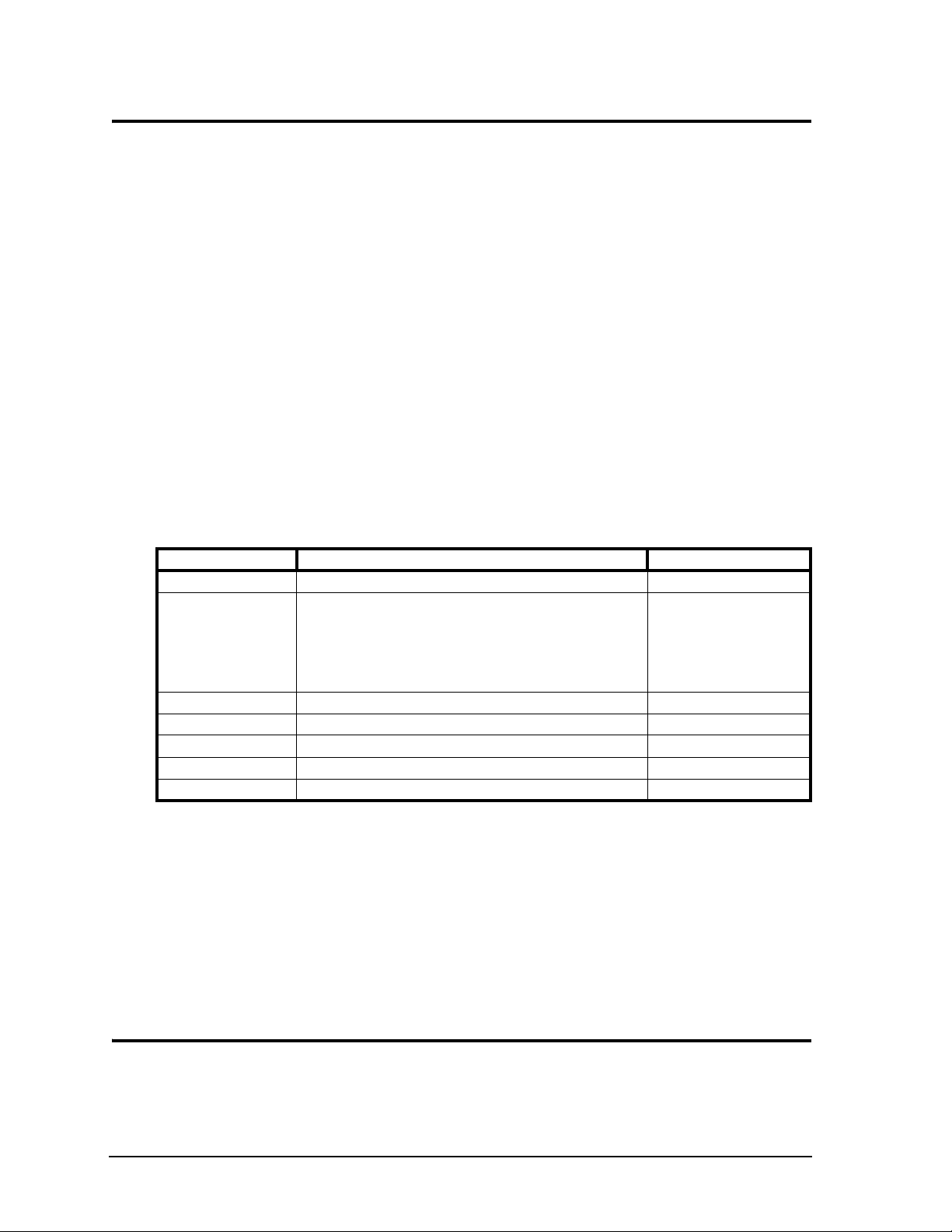

REVISION HISTORY

Revision Reason for Change Date

1000 Initial Release Nov/10

1010 Replaced N450, D410, and D510 CPUs with N455 and D525;

upgraded DDR2 memory to DDR3; revised definition of JP1 from

Clear CMOS to SSD Select; added U20 Temperature Sensor; revised

DASP and PDIAG signals in Tab le 3- 8; revised various sections of

ch 4; added Figures 2-9, 2-10, and 2-11 to illustrate In-Rush power

consumption

Aug/12

ADLINK Technology, Incorporated

5215 Hellyer Avenue, #110

San Jose, CA 95138-1007

Tel. 408 360-0200

Fax 408 360-0222

www.adlinktech.com

© Copyright 2010, 2011, 2012 ADLINK Technology, Incorporated

Audience

This manual provides reference only for computer design engineers, including but not limited to hardware

and software designers and applications engineers. ADLINK Technology, Inc. assumes you are qualified to

design and implement prototype computer equipment.

ii Reference Manual ETX-PVR

Page 3

Contents

Chapter 1 About This Manual ....................................................................................................1

Purpose of this Manual ....................................................................................................................1

References ......................................................................................................................................1

Chapter 2 Product Overview......................................................................................................3

ETX Computer-on-Module Concept.................................................................................................3

Product Description..........................................................................................................................4

Board Features ..........................................................................................................................5

Block Diagram ............................................................................................................................7

Major Components (ICs)..................................................................................................................8

Connector and Socket Definitions..................................................................................................10

Jumper Header Definition ......................................................................................................12

Specifications ................................................................................................................................13

Physical Specifications ............................................................................................................13

Mechanical Specifications ........................................................................................................13

Environmental Specifications ...................................................................................................14

Power Specifications .............................................................................................................14

Thermal/Cooling Requirements .........................................................................................17

Chapter 3 Hardware ...............................................................................................................19

Overview ........................................................................................................................................19

CPU ...............................................................................................................................................20

Graphics ........................................................................................................................................20

Memory .........................................................................................................................................20

Interrupt Channel Assignments (IRQs) ..........................................................................................21

Memory Map .................................................................................................................................22

I/O Address Map ...........................................................................................................................22

X1 PCI Bus Interface (J1) .............................................................................................................23

PCI Bus ....................................................................................................................................23

Universal Serial Bus (USB) ......................................................................................................23

Serial Interrupt Request ...........................................................................................................23

Audio Interface .........................................................................................................................24

X2 ISA Bus Interface (J2) ...........................................................................................................27

X3 Primary I/O Interface (J3) ........................................................................................................31

Floppy Interface .......................................................................................................................31

Parallel Interface ......................................................................................................................31

Serial Ports 1 and 2 .................................................................................................................31

PS/2 Keyboard .........................................................................................................................31

PS/2 Mouse .............................................................................................................................31

VGA Interface ..........................................................................................................................31

LVDS Interface ........................................................................................................................32

X4 IDE and Auxiliary Interface (J4) ...............................................................................................36

IDE Port .................................................................................................................................36

Ethernet Port Interface..............................................................................................................36

Power Control Signals .............................................................................................................37

Power Management Signals ....................................................................................................37

Speaker ...................................................................................................................................37

Real Time Clock (RTC) .........................................................................................................37

SMBus ...................................................................................................................................38

ETX-PVR Reference Manual iii

Page 4

Contents

Miscellaneous ............................................................................................................................... 42

Oops! Jumper (BIOS Recovery) ............................................................................................. 42

Remote Access ...................................................................................................................... 42

Remote Access Setup ........................................................................................................ 42

Hot (Serial) Cable .............................................................................................................. 42

Temperature Monitoring .......................................................................................................... 42

Watchdog Timer (WDT) ........................................................................................................... 43

Power Interface ............................................................................................................................. 43

Power and Sleep States................................................................................................................ 43

Power-On Switch .................................................................................................................... 43

Sleep States (ACPI) ................................................................................................................. 44

Chapter 4 BIOS Setup .............................................................................................................. 47

Introduction.................................................................................................................................... 47

Entering BIOS Setup (Local Video Display) ............................................................................. 47

Entering BIOS Setup (Remote Access) .................................................................................. 47

PCI-ISA Bridge Mapping ............................................................................................................... 48

Logo Screen Utility (Splash Screen) .............................................................................................48

Logo Screen Image Requirements ......................................................................................... 48

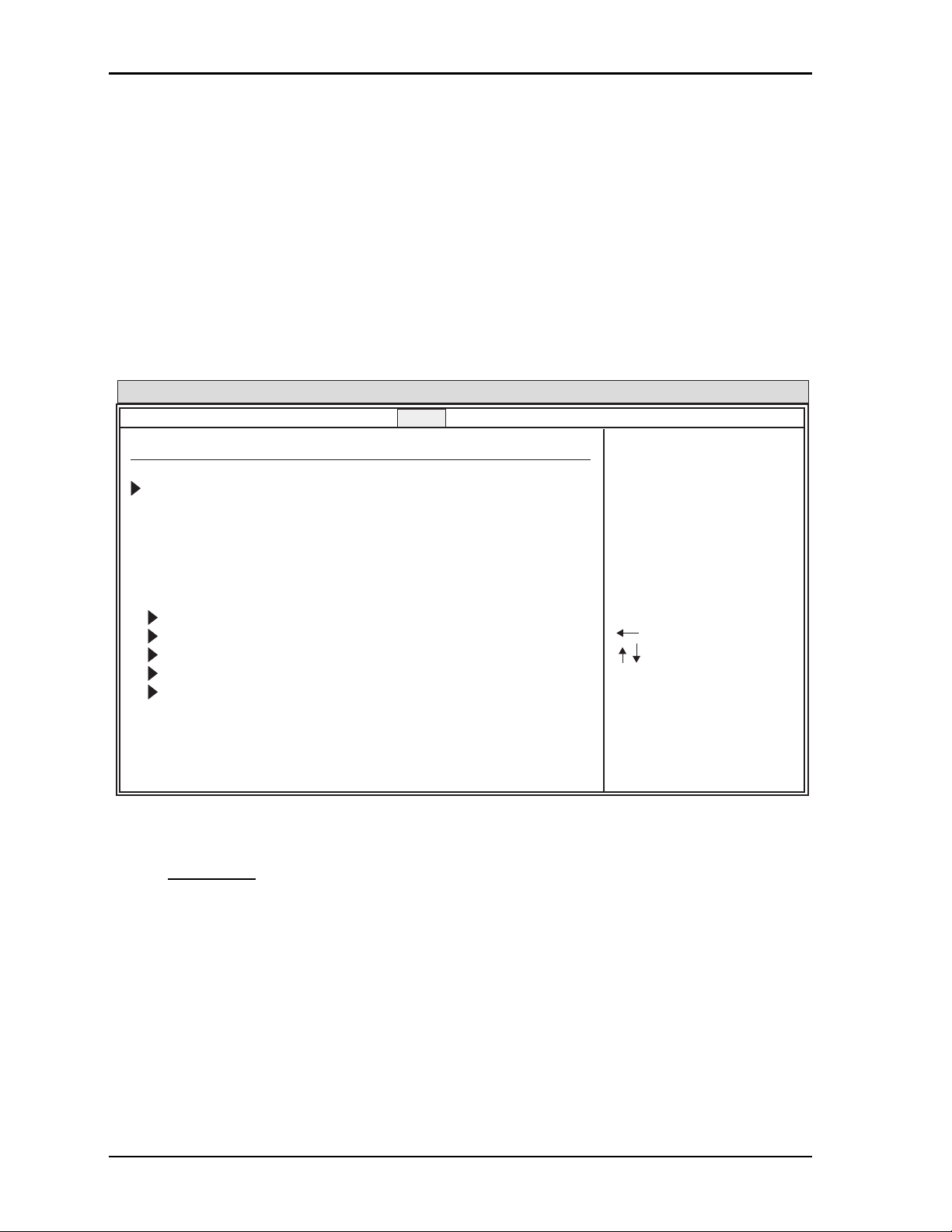

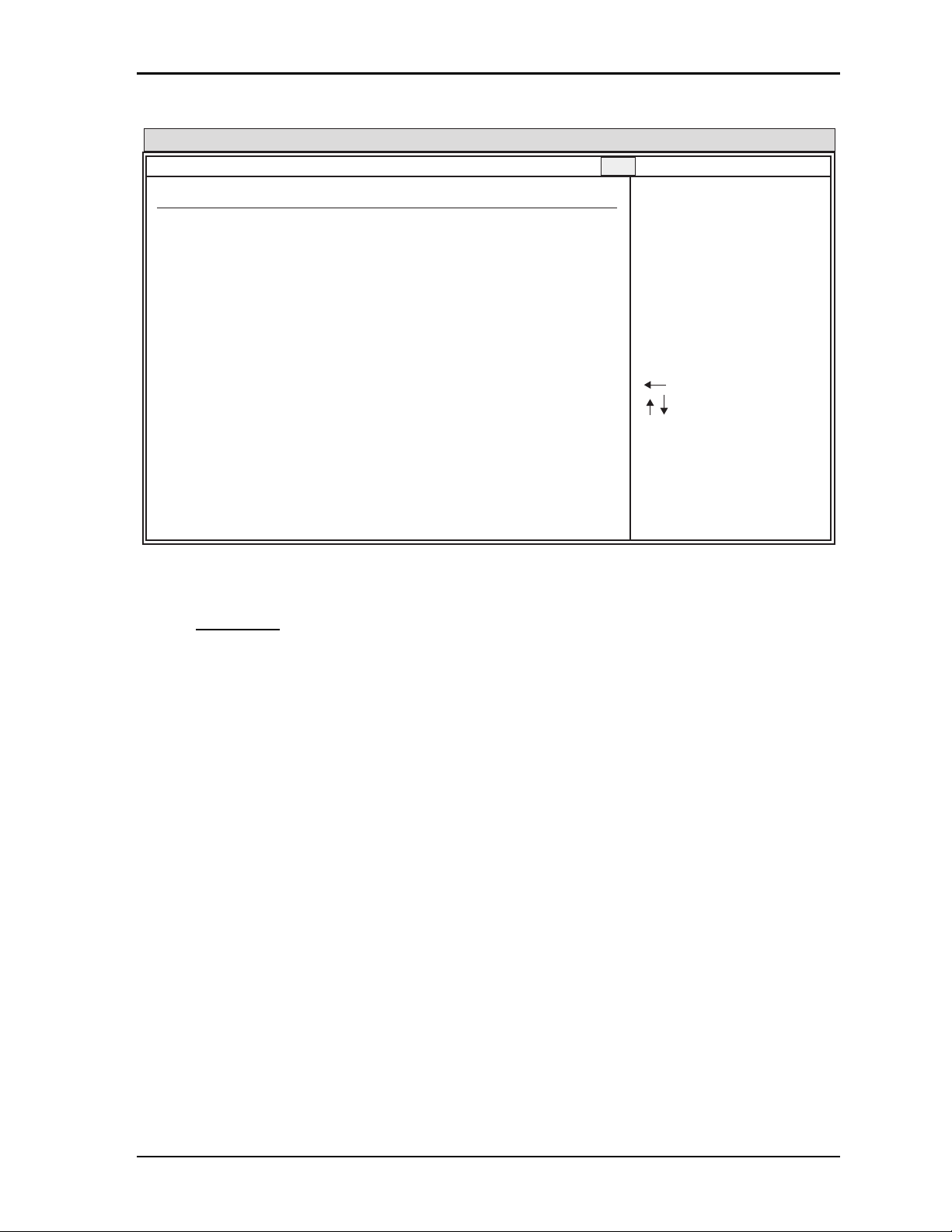

BIOS Setup Menus ....................................................................................................................... 49

BIOS Main Setup Screen ........................................................................................................ 49

BIOS Advanced Setup Screen ................................................................................................ 50

BIOS Power Management Setup Screen ................................................................................ 53

BIOS Boot Setup Screen ........................................................................................................ 54

BIOS Security Setup Screen ................................................................................................... 56

BIOS Exit Setup Screen .......................................................................................................... 57

Appendix A Technical Support ..................................................................................................59

Index .................................................................................................................................................. 61

List of Figures

Figure 2-1. ETX-PVR Module and Custom Baseboard Assembly............................................. 3

Figure 2-2. Typical ETX Design Flow ........................................................................................ 4

Figure 2-3. Functional Block Diagram ....................................................................................... 7

Figure 2-4. Component Locations (Top Side)............................................................................ 9

Figure 2-5. Component Locations (Bottom Side) .................................................................... 10

Figure 2-6. Connector and Socket Locations (Top Side)......................................................... 11

Figure 2-7. Connector Locations (Bottom Side) ...................................................................... 12

Figure 2-8. Mechanical Overview (Bottom Side) ..................................................................... 13

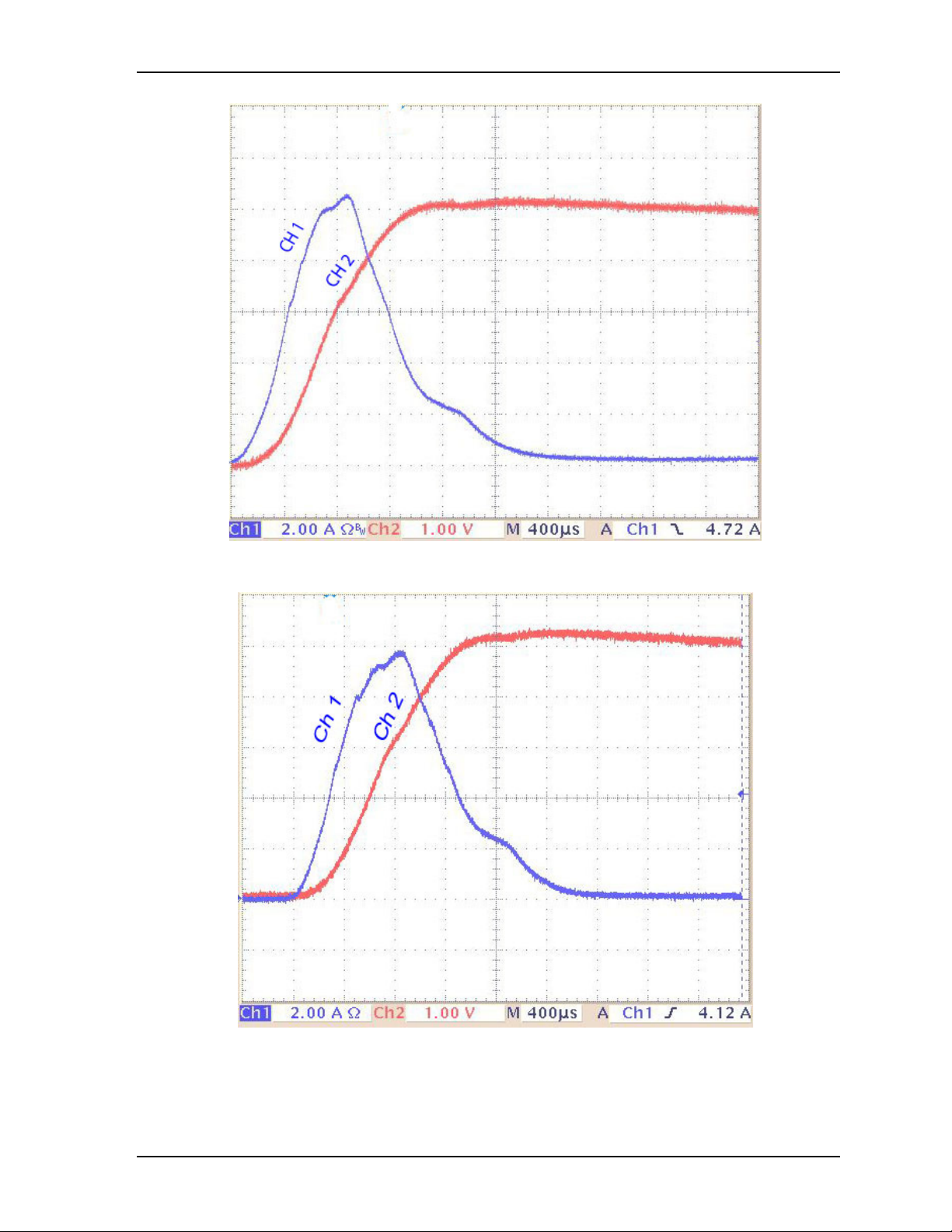

Figure 2-9. N455 (with SpeedStep disabled) Peak In-Rush Current and Duration ................. 15

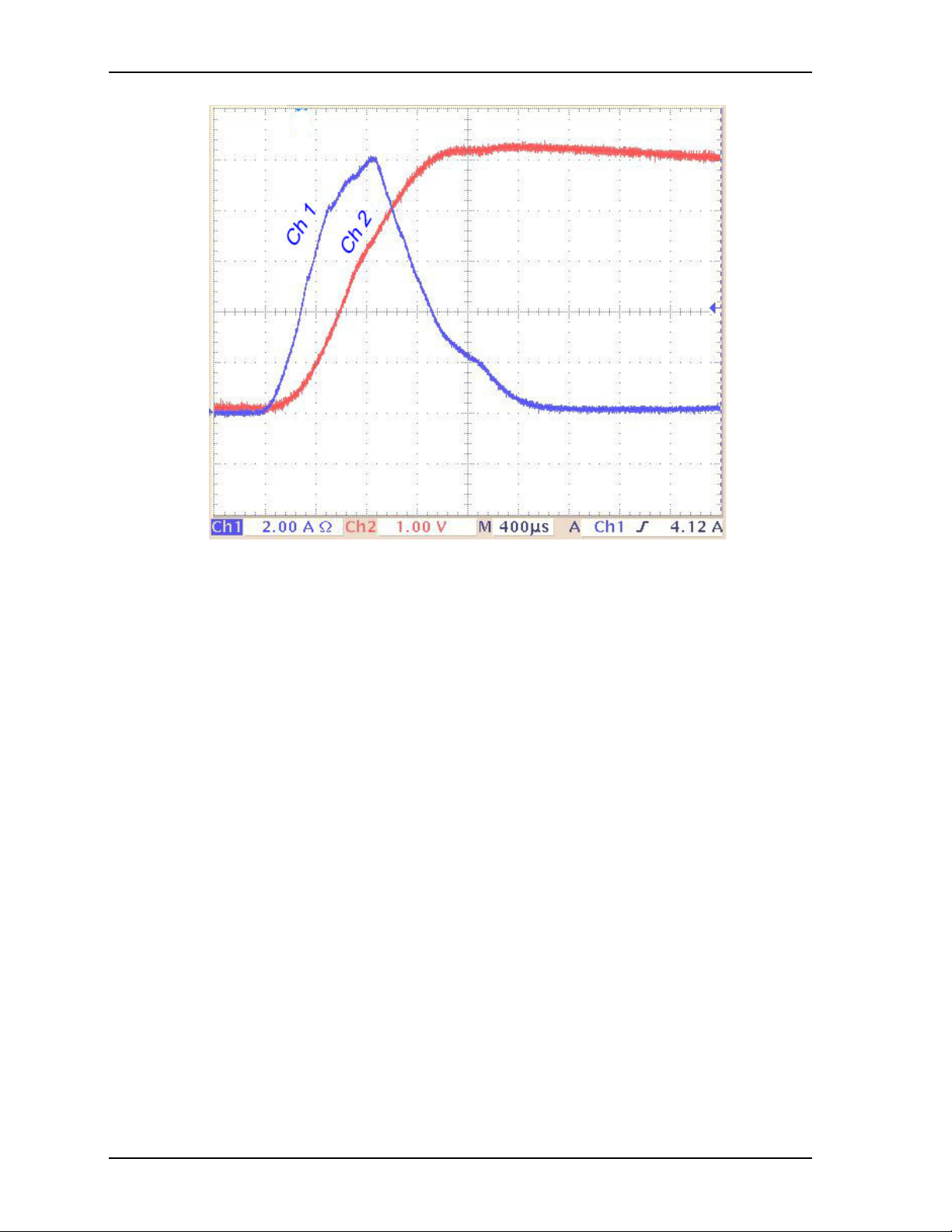

Figure 2-10. N455 Peak In-Rush Current and Duration ............................................................ 15

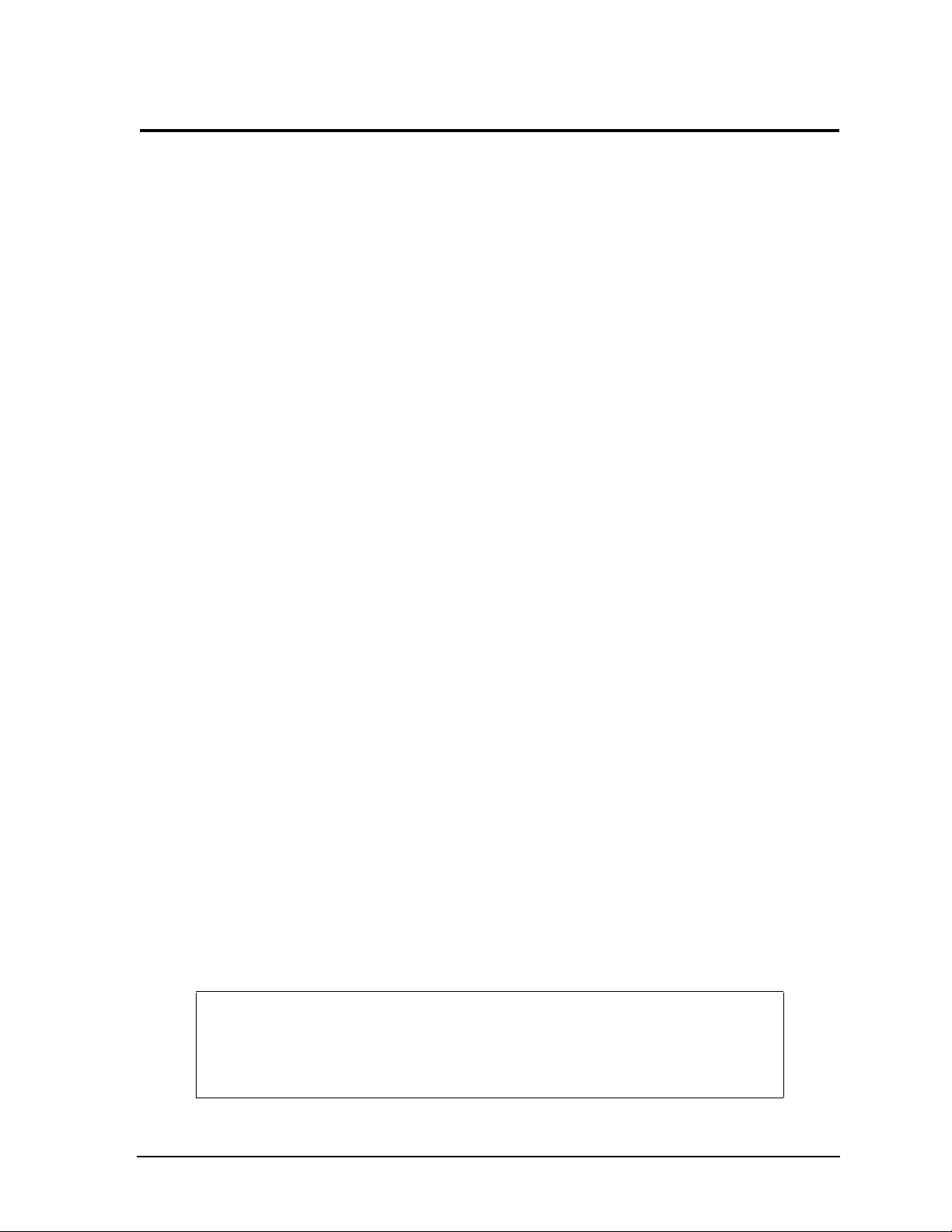

Figure 2-11. D525 Peak In-Rush Current and Duration ............................................................ 16

Figure 2-12. Stack Heights of Cooling Assemblies.................................................................... 17

Figure 3-1. Oops! Jumper Connection..................................................................................... 42

Figure 3-2. Hot Cable Jumper ................................................................................................. 42

Figure 4-1. BIOS Main Setup Screen ...................................................................................... 49

Figure 4-2. BIOS Advanced Setup Screen .............................................................................. 50

Figure 4-3. Power Management Setup Screen ....................................................................... 53

Figure 4-4. BIOS Boot Setup Screen....................................................................................... 54

Figure 4-5. BIOS Security Setup Screen ................................................................................. 56

Figure 4-6. BIOS Exit Setup Screen ........................................................................................ 57

iv Reference Manual ETX-PVR

Page 5

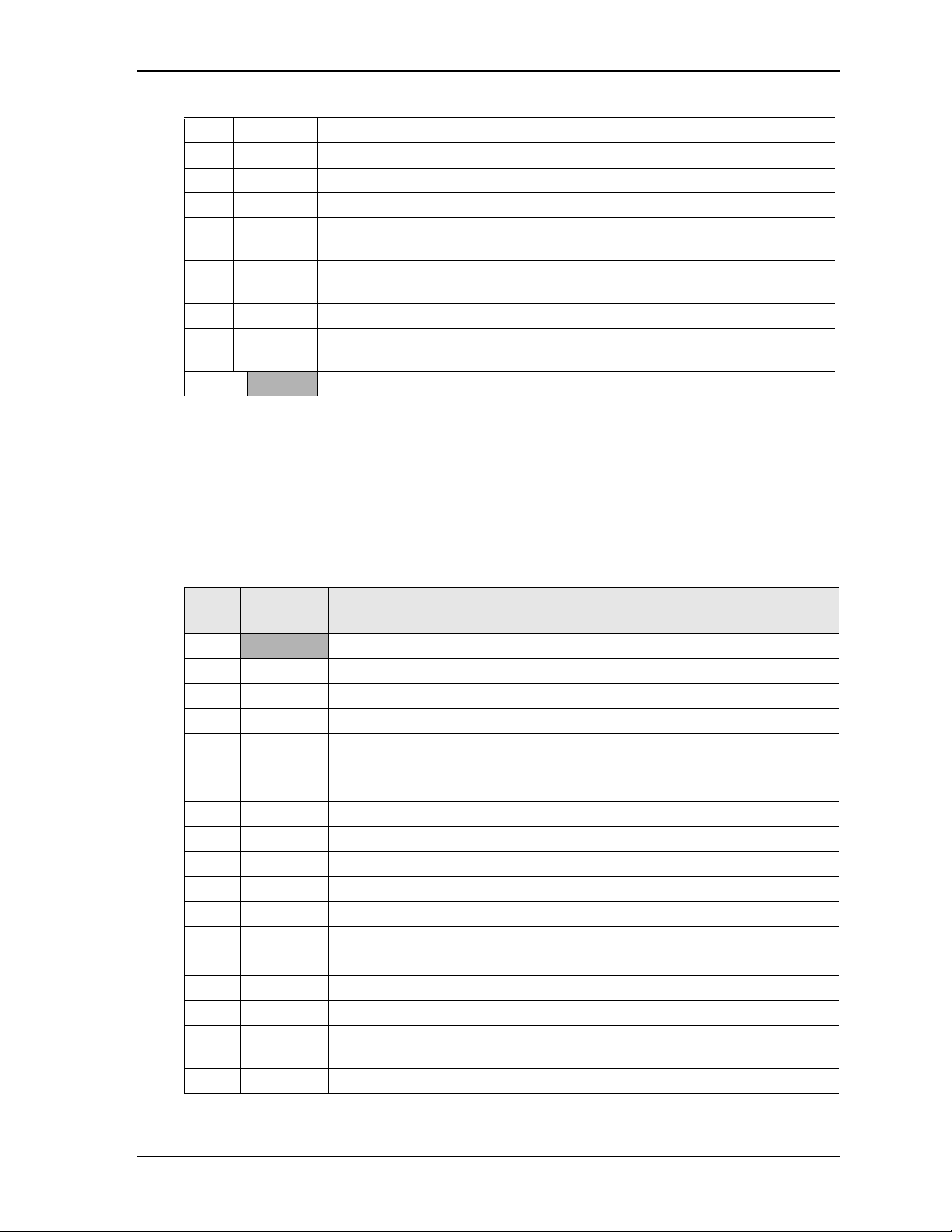

List of Tables

Table 2-1. Major Components Descriptions and Functions ......................................................8

Table 2-2. Connector and Socket Descriptions.......................................................................10

Table 2-3. Jumper Header Setting ..........................................................................................12

Table 2-4. Weight and Footprint Dimensions..........................................................................13

Table 2-5. Environmental Requirements.................................................................................14

Table 2-6. Power Supply Requirements .................................................................................14

Table 2-7. ADLINK Optional Cooling Solutions.......................................................................17

Table 3-1. Interrupt Channel (IRQs) Assignments (Typical) ...................................................21

Table 3-2. Memory Map ..........................................................................................................22

Table 3-3. I/O Address Map ....................................................................................................22

Table 3-4. Complete X1 Interface Pin Signal Descriptions (J1) ..............................................24

Table 3-5. Complete X2 ISA Bus Interface Pin Signal Descriptions (J2) ................................27

Table 3-6. Complete X3 Interface Pin Signal Descriptions (J3) ..............................................32

Table 3-7. SMBus Reserved Addresses .................................................................................38

Table 3-8. Complete X4 Interface Pin Signal Descriptions (J4) ..............................................38

Table 4-1. BIOS Setup Menus ................................................................................................49

Table A-1. Technical Support Contact Information..................................................................59

Contents

ETX-PVR Reference Manual v

Page 6

Contents

vi Reference Manual ETX-PVR

Page 7

Chapter 1 About This Manual

Purpose of this Manual

This manual is for designers of systems based on the ETX®-PVR Computer-on-Module (COM). This

manual contains information that permits designers to create an embedded system based on specific design

requirements.

Information provided in this reference manual includes:

• Product Overview

• Hardware Specifications

• Technical Support Contact Information

Information not provided in this reference manual includes:

• Detailed chip specifications

• Internal component operation

• Internal registers or signal operations

• Bus or signal timing for industry standard busses and signals

• Pinout definitions for industry standard interfaces

References

The references in the following list may help you successfully complete your custom design.

Specifications:

• ETX Spec Revision 3.02, 2007

For the latest version of the ETX specifications, use the web page at:

Web site: http://www.etx-ig.org/specs/specs.php

• PCI 2.3 Compliant Specifications

For latest revision of the PCI specifications, contact the PCI Special Interest Group Office at:

Web site: http://www.pcisig.com

• AMI BIOS Core 8 User’s Guide

Web site: http://www.ami.com/support/doc/MAN-EZP-80.pdf

Chip specifications:

• Intel Corporation and the Atom N400 and D500 series processors (with integrated Northbridge)

Web site: http://www.intel.com/p/en_US/embedded/hwsw/hardware/atom-400-500/hardware

• Intel Corporation and the ICH8-M chip, 82801HM, used for the I/O Hub (Southbridge)

Data sheet: http://www.intel.com/assets/pdf/datasheet/313056.pdf

• Intel Corporation and the 82567V chip, used as Ethernet transceiver

Data sheet: http://download.intel.com/design/network/datashts/82567.pdf

• SMSC and the SCH3112I-NU chip used for the Super I/O controller

Data sheet: http://www.smsc.com/media/Downloads_Public/Data_Briefs/311xdb.pdf

ETX-PVR Reference Manual 1

Page 8

Chapter 1 About This Manual

• Realtek and the ALC262-VD2-GR chip, used for the Audio CODEC

Web site: http://www.realtek.com/search/default.aspx?keyword=alc262

• ITE Tech. Inc. and the IT8888G-L chip, used for the PCI-to-ISA bridge conversion

Web site: http://www.ite.com.tw/EN/products_more.aspx?CategoryID=3&ID=5,76

• Greenliant and the GLS85LP1004P Solid State Drive (SSD)

Web site: http://www.greenliant.com/products/?inode=46780

• ON Semiconductor and the ADT7481ARMZ Temperature Sensor

Data sheet: http://www.onsemi.com/pub_link/Collateral/ADT7481-D.PDF

• Atmel Corporation and the ATMEGA168V-10AU micro controller, used as the board controller

Data sheet: http://www.atmel.com/dyn/resources/prod_documents/doc8025.pdf

NOTE If you are unable to locate the datasheets using the links provided, search the

internet to find the manufacturer’s web site and locate the documents you need.

2 Reference Manual ETX-PVR

Page 9

Chapter 2 Product Overview

ETX-PVR_Stack

ETX-PVR Computer -on -Module

Custom Baseboard Design

Stack Connectors

(4 pairs)

M2.5 PEM Nuts

Spacing 3 mm (4)

M2.5 Screws (4)

This introduction presents general information about the ETX Architecture and the ETX-PVR Computeron-Module (COM). After reading this chapter you should understand:

• ETX Computer-on-Module concept

• ETX-PVR product description

• ETX-PVR features

• Major components

• Connectors

• Specifications

ETX Computer-on-Module Concept

Embedded system designers face increasing pressures to bring products to market quickly. Many products

that once incorporated a custom CPU design can no longer afford the time to develop and debug a custom

CPU let alone port operating system software to it. Furthermore, CPU subsystem design usually plays a

small part in providing any uniqueness to an embedded product. The remainder of the embedded product

design adds key circuits that provide a unique product and differentiate it from other products serving the

same market. The challenge is to speed these designs to market by eliminating the need for a custom CPU

design while providing the flexibility to include all critical elements, which make the embedded product

unique.

The Embedded Technology eXtended (ETX) module provides an off-the-shelf CPU subsystem that can be

included in virtually any embedded system. An ETX module works like a high-integration chip, plugging

into your custom circuit board design to provide specific control for your logic application. See Figure 2-1.

Figure 2-1. ETX-PVR Module and Custom Baseboard Assembly

ETX provides a simple, standard interface that is independent of CPU type. The ETX interface includes the

industry-standard PCI bus, ISA bus (some models), I/O signals from the peripheral components on the ETX

module, power, and ground. Visit the ADLINK web site (www.adlinktech.com

availability and support information.

The standard ETX interface lets you try different processors in your actual product environment with the

ability to defer a processor choice until late in the project if you so choose. The interface also lets you easily

offer different versions of your product with different capabilities by either selecting different ETX modules

with the same baseboard, or by designing different baseboards for the same CPU. This simple ability to

upgrade by either selecting a more powerful CPU (without baseboard redesign) or enhancing the baseboard

without touching the CPU subsystem or the bulk of the applications software.

The ETX flexibility enables designers to take an accelerated, low risk path by using proven ETX module

designs. Your design flow might look similar to the one shown in Figure 2-2. This diagram gives a Typical

Design Flow of hardware and software functions.

) for the latest ETX processor

ETX-PVR Reference Manual 3

Page 10

Chapter 2 Product Overview

CPU and Software

Design Path

Design applicationspecific baseboard

Fabricate baseboard

Debug baseboard

Revise baseboard

if necessary

Integrate application code

Hardware

Design Path

Select CPU

Select OS & Tools

Write and Test

Application Code

Write drivers for

custom Logic

ETXdesignflw

Figure 2-2. Typical ETX Design Flow

Product Description

The ETX-PVR is an exceptionally high integration, high performance, rugged, and high quality Computeron-Module (COM), which contains all the component subsystems of an ATX motherboard plus the

equivalent of up to 2 expansion boards. Based on the Intel® Atom™ N455 and D525 processors, the

ETX-PVR provides designers a complete, high performance embedded processor that conforms to the ETX

V3.02 specification.

The Intel Atom N400 and D400/D500 series CPUs integrate processor cores with Graphics and Memory

Hubs (GMHs), providing low-power, high-performance processors, memory controllers for up to 2GB of

DDR3 memory, and graphics controllers which provide LVDS and VGA signals for most LCD video panels

and CRT monitors.

The ICH8-M chipset provides controllers for the I/O Hub (Southbridge) featuring four USB ports, one Ultra

DMA 33/66/100 IDE port supporting two IDE devices, one HD Audio link, two SATA ports, one Ethernet

interface, one PCI interface, one SMBus interface, one LPC bus, and one speaker port. The ETX-PVR

provides legacy interfaces through the SMSC SCH3112I-NU Super I/O featuring two serial ports, one

parallel/floppy port, and one PS/2 keyboard and mouse port.

Among the many embedded-PC enhancements on the ETX-PVR that ensure embedded system operation

and application versatility are a Watchdog Timer, remote access support, battery-free boot, and OEM logo

customization (Splash Screen).

The ETX-PVR is particularly well suited to either embedded or portable applications and meets the size,

power consumption, temperature range, quality, and reliability demands of embedded system applications.

The ETX-PVR requires a single +5V power supply.

4 Reference Manual ETX-PVR

Page 11

Chapter 2 Product Overview

Board Features

• CPU

Provides Intel Atom 1.66GHz N455 (6.5W) or Atom 1.80GHz D525 (13W) processor cores

DMI (Direct Media Interface) with 1 GB/s of bandwidth in each direction

Enhanced SpeedStep® technology

On die 512-kB, 8-way L2 cache

• Memory

Single standard 204-pin DDR3 SODIMM socket

Supports +1.5V DDR3, 800MHz RAM up to 2GB

Supports only non-ECC memory

Supports only unbuffered memory

• PCI Bus/ISA Bus

PCI 2.3 compliant, 32-bits wide

Supports PCI Bus speed at 33 MHz

Supports ISA bus speed at 8 MHz

• IDE Interfaces

Provides one enhanced IDE controller

Provides soldered Solid State Drive (SSD)

Supports dual bus master mode

Supports Ultra DMA 33/66/100 modes

Supports ATAPI and DVD peripherals

Supports IDE native and ATA compatibility modes

• SATA

Supports two SATA ports from the ICH8-M I/O Hub

Provides two standard SATA connectors

• Floppy Disk Interface

Supports one standard floppy disk drive interface

Supports all standard PC/AT formats: 360KB, 1.2MB, 720KB, 1.44MB, 2.88MB

• Parallel Port

Provides a standard printer interface

Supports IEEE standard 1284 protocols of EPP and ECP outputs

Supports Bi-directional data lines

• Serial Ports

Provide two buffered serial ports with full handshaking

Provide 16550-equivalent controllers, each with a built-in 16-byte FIFO buffer

Support full modem capability

Support RS232 operation

Support programmable word length, stop bits, and parity

Supports 16-bit programmable baud-rate generator and an interrupt generator

ETX-PVR Reference Manual 5

Page 12

Chapter 2 Product Overview

• USB Ports

Provide two root USB hubs

Provide up to four USB ports

Support USB boot devices

Support USB v2.0 EHCI and OHCI v1.1

Support over-current detection status

• Keyboard/Mouse Interface

Provides PS/2 keyboard interface

Provides PS/2 mouse interface

• Audio interface

Provides HD Audio CODEC on board

Supports HD Audio standard

Supports the audio amplifier on the baseboard

• Ethernet Interface

Provides one fully independent Ethernet port

Provides integrated LEDs (Link/Activity and Speed)

Provides Intel 82567V Ethernet transceiver chip

Supports IEEE 802.3 10/100BaseTX compatible physical layers

Supports Auto-negotiation for speed, duplex mode, and flow control

Supports full-duplex or half-duplex mode

• Full-duplex mode supports transmit and receive frames simultaneously

• Supports IEEE 802.3x Flow control in full duplex mode

• Half-duplex mode supports enhanced proprietary collision reduction mode

• Video Interfaces (VGA and LVDS)

Provide VGA outputs (resolutions up to 1400x1050 @ 60Hz for the N455 CPU and 2048x1536 @

60Hz for the D525 CPU)

Provide LVDS flat panel outputs (resolutions up to 1280x800 for the N455 CPU and 1366x768 for

the D525 CPU) [single channel, three differential signals]

• Miscellaneous

Real Time Clock (RTC) with replaceable battery on baseboard

Battery-free boot (Boots even if battery is dead or missing)

Supports external battery for Real Time Clock operation

Oops! Jumper (BIOS recovery) support

Remote Access

Watchdog Timer (WDT)

6 Reference Manual ETX-PVR

Page 13

Chapter 2 Product Overview

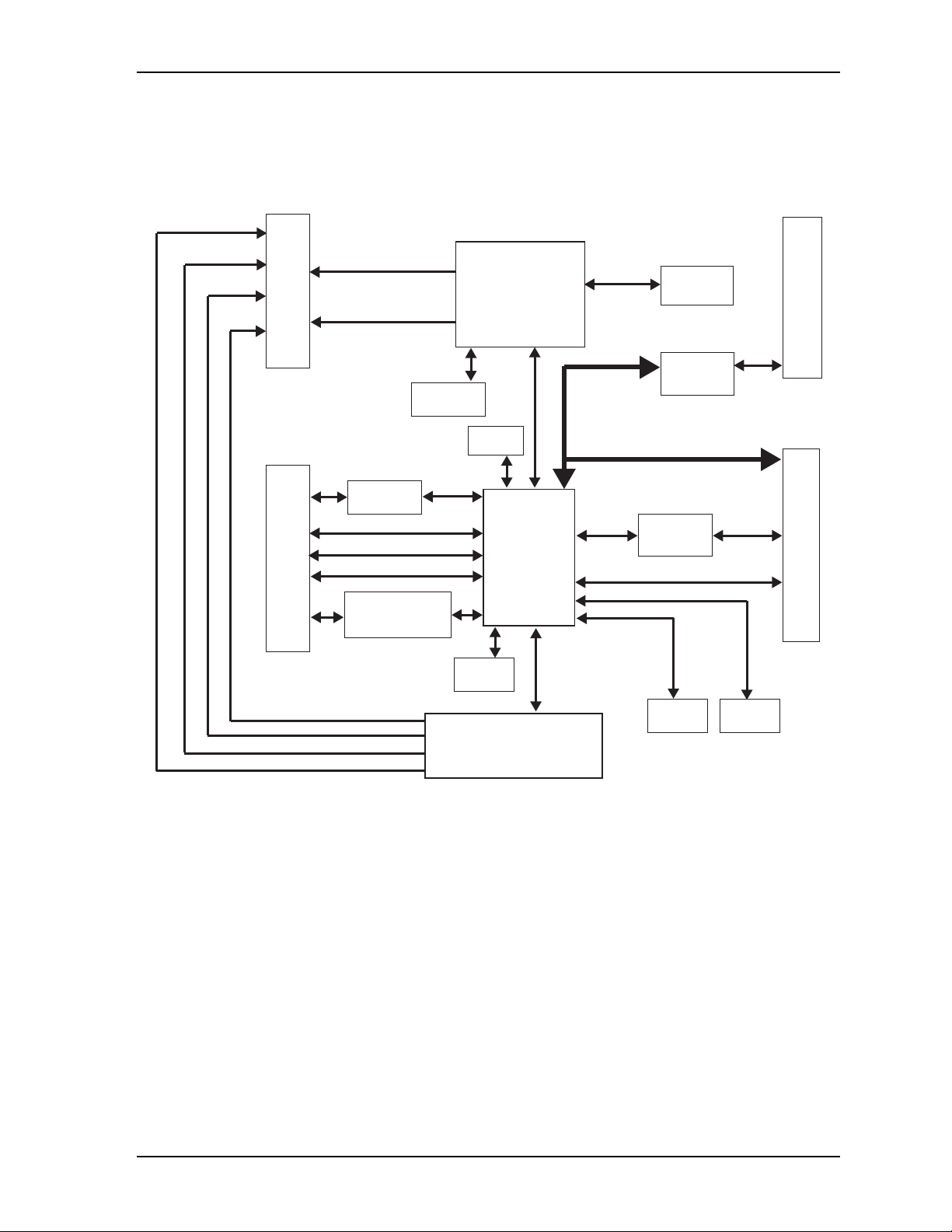

ETX-PVR_Blkdiagm_b

CPU

Intel Atom

1.66GHz N455 (6.5W)

or 1.80GHz D525 (13W)

(with Integrated

Video and Memory)

DDR3

SODIMM

PS/2 Keyboard/Mouse

PCI -to-ISA

Bridge

IT8888G-L

PCI Bus

(32bit / 33MHz)

DMI (4)

Parallel/Floppy Port

Serial Port I/F

HD Audio

ALC262

Temperature

Sensor

USB 2.0 (4)

Super I/O

SCH3112I-NU

HDA Link

Line In/Out,

MIC

X3

Connector (J3)

X2

Connector (J2)

X1

Connector (J1)

X4

Connector (J4)

Ethernet Transceiver

Intel 82567V

GbE PHY

Solid State

Drive

Board

Controller

SATA1

Connector

BIOS

SATA2

Connector

IrDA

I/O Hub

Intel

82801HM,

ICH8-M

(Southbridge)

LPC Bus

IDE

ISA

VBat

SATA 1

SATA 2

MDI

LCI

SMBus

Speaker

LVDS Video

VGA Video

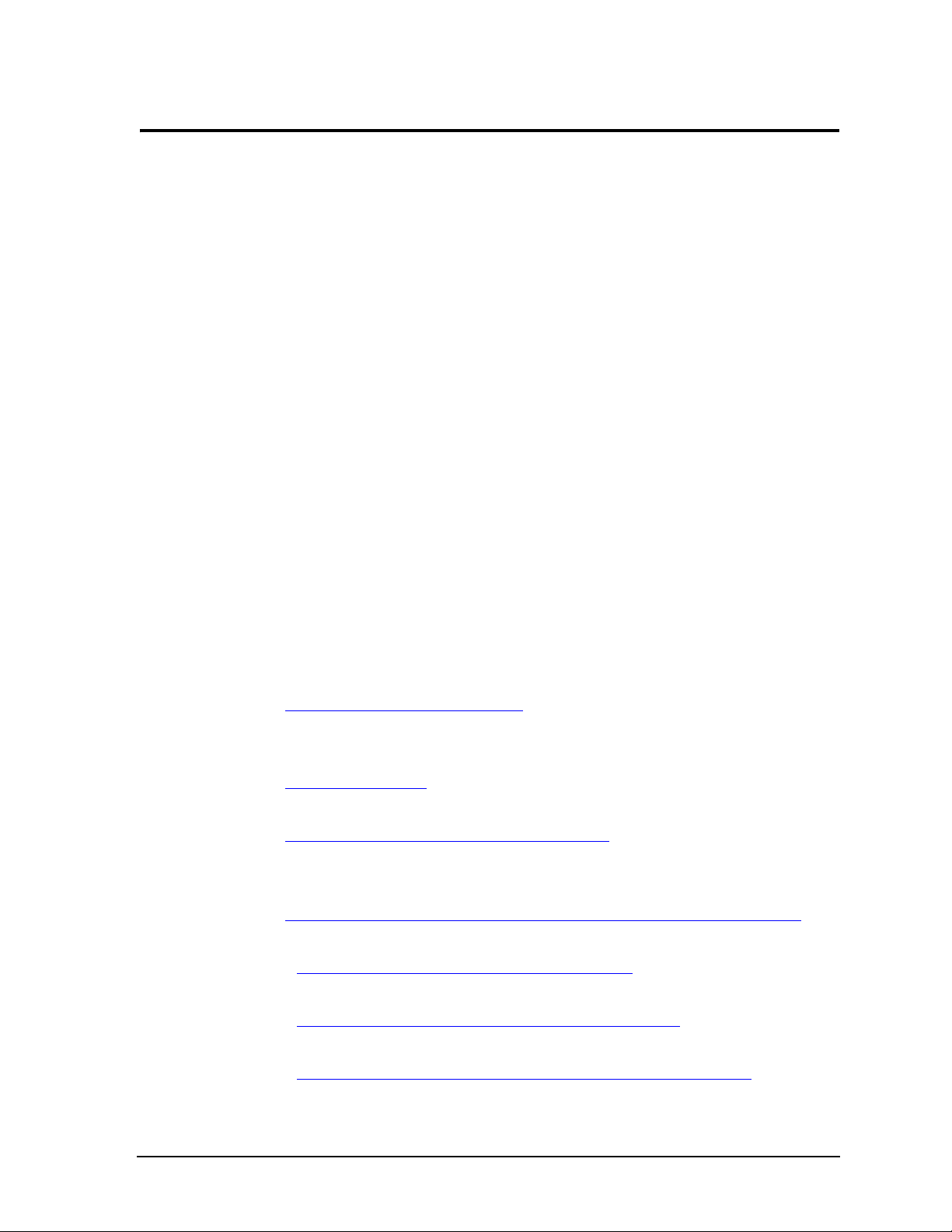

Block Diagram

Figure 2-3 illustrates the functional components of the board.

Figure 2-3. Functional Block Diagram

ETX-PVR Reference Manual 7

Page 14

Chapter 2 Product Overview

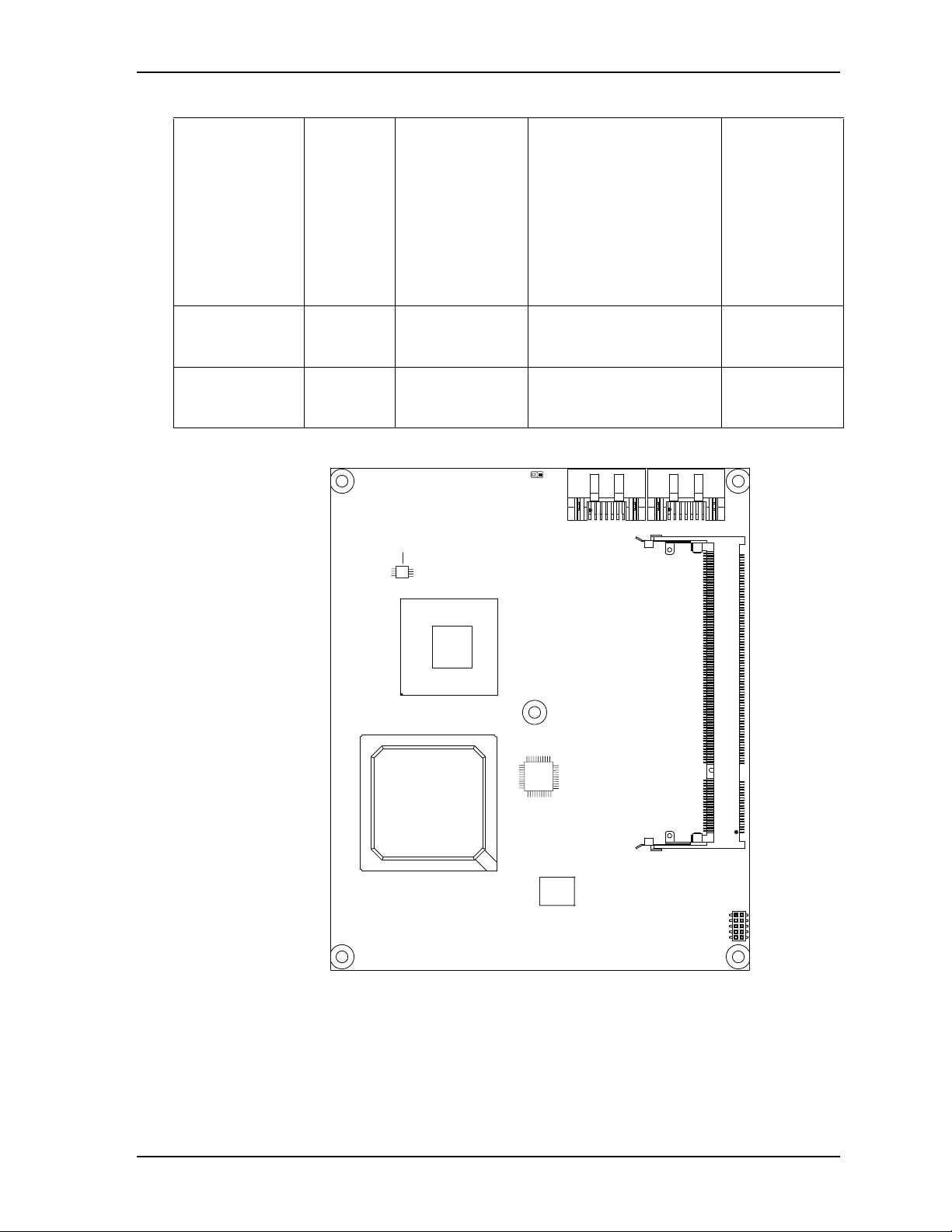

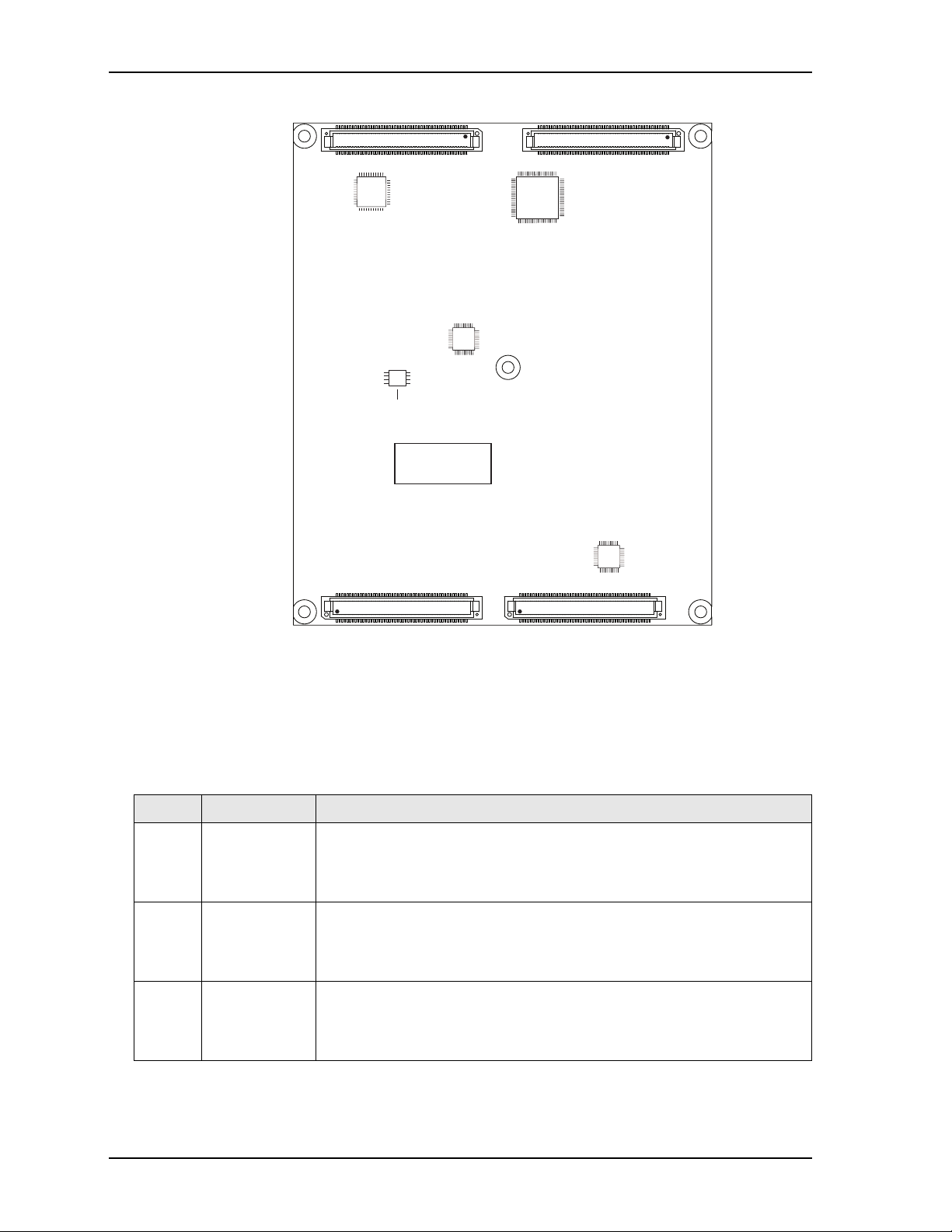

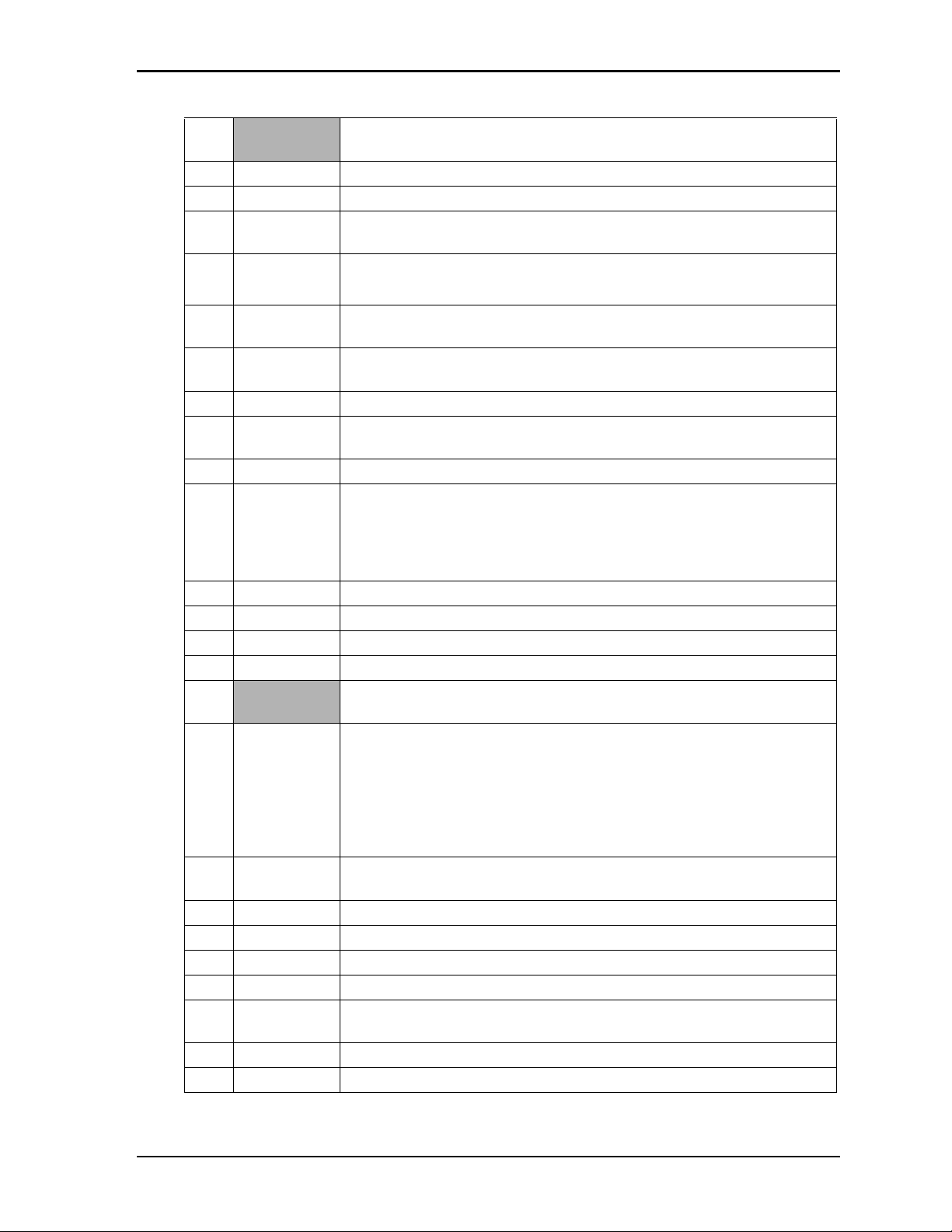

Major Components (ICs)

Table 2 - 1 lists the major ICs, including a brief description of each, on the ETX-PVR. Figures 2-4 and 2-5

show the locations of the ICs.

Table 2-1. Major Components Descriptions and Functions

Chip Type Mfg. Model Description Function

CPU (U1) Intel Atom N455 or

D525

I/O Hub (U2) Intel 82801HBM

(ICH8-M)

PCI-to-ISA

Bridge (U8)

Super I/O

(U9) [See

Figure 2-5 on

page 10.]

HD Audio

CODEC (U11)

[See Figure 2-5

on page 10]

Gigabit Ethernet

PHY Transceiver

(U12)

[See Figure 2-5

on page 10]

SSD (Solid State

Drive, U14) [see

Figure 2-5 on

page 10]

Board Controller

(U19) [see

Figure 2-5 on

page 10]

ITE ITE8888G-L Interface between PCI bus

SMSC SCH3112I-NU Super I/O controller Provides

Realtek ALC262-VD2-GR Encoder and decoder of

Intel 82567V Ethernet PHY transceiver

Greenliant GLS85LP1004P Industrial-grade, soldered

Atmel ATMEGA168 Micro controller for board

1.66GHz, 6.5W (N455) or

1.80GHz, 13W (D525)

processor with 8-way L2

cache

I/O Hub for common user

interfaces

and ISA bus

audio data for transmission,

storage, encryption,

playback, or editing

for 10T/100TX/1000T

Gigabit Ethernet function

solid-state storage module

functions including I²C,

Watchdog Timer, and Power

Button functions

Integrates

Processor Core

and Graphics

Memory

Controller Hub

Provides

Southbridge

interfaces and

off loads some

Northbridge

functions from

the CPU

Migrates legacy

ISA bus

complete legacy

Super I/O

functionality

Provides four

channels of

ADC conversion

and six channels

of DAC display

Provides a

standard IEEE

802.3 Ethernet

interface for

Ethernet transfer

rate up to 1000

Mb/s

Provides solid

state storage

through the IDE

channel

Optimizes power

consumption

versus processor

speed

8 Reference Manual ETX-PVR

Page 15

Chapter 2 Product Overview

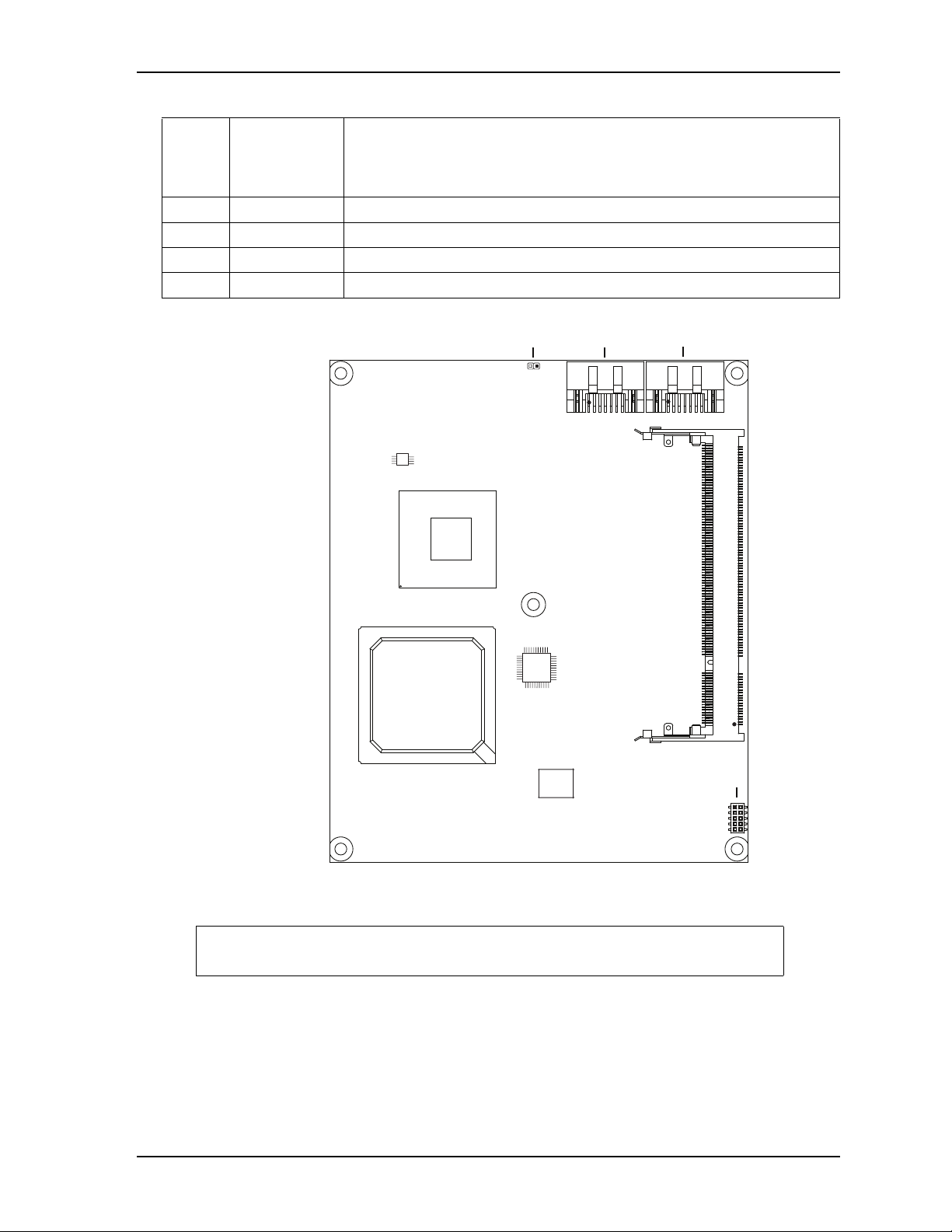

Key:

U1 - CPU

U2 - I/O Hub (Southbridge)

U8 - PCI-to-ISA Bridge

U20 - Temperature Sensor

U22 - CPLD

U1

U2

U8

ETX-PVR_Top_Comp_b

U22

U20

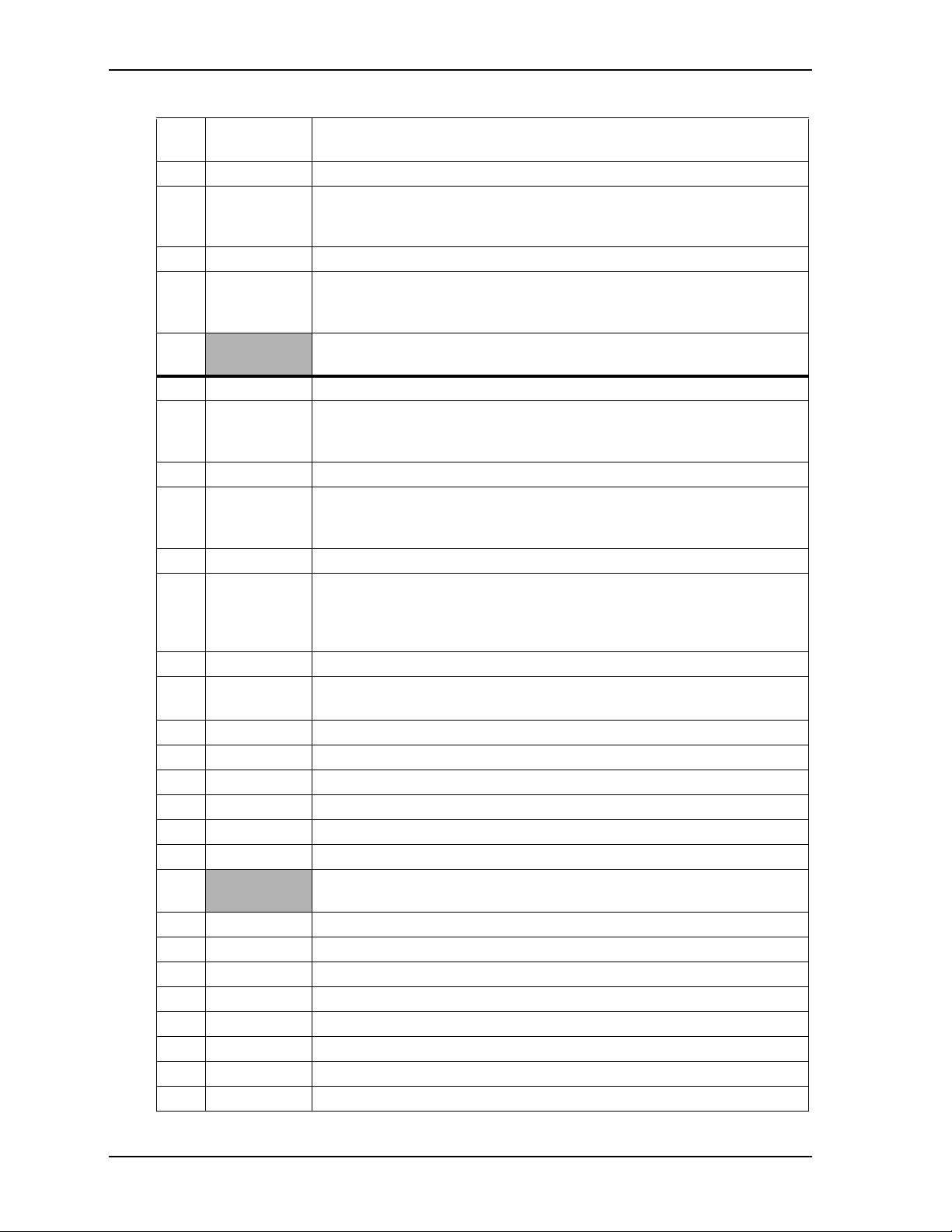

Table 2-1. Major Components Descriptions and Functions (Continued)

Temperature

Sensor (U20 - on

bottom side) [see

Figure 2-4 on

page 9]

ON Semi ADT7481ARMZ Digital thermometer and

under/over alarm for local,

CPU, and I/O Hub

temperatures

Measures its

own ambient

temperature and

the temperature

outputs of the

CPU and I/O

Hub. Provides

under/over

temperature

alarm.

CPLD (U22) Xilinx XC9536XL Complex Programmable

Logic Device (not user

programmable)

SPI Flash (U37)

[see Figure 2-5 on

page 10]

PCT PCT25VF016B Serial Peripheral Interface

Flash memory chip

(firmware)

Provides control

for Power

Sequencing

Stores BIOS in

Flash memory

Figure 2-4. Component Locations (Top Side)

ETX-PVR Reference Manual 9

Page 16

Chapter 2 Product Overview

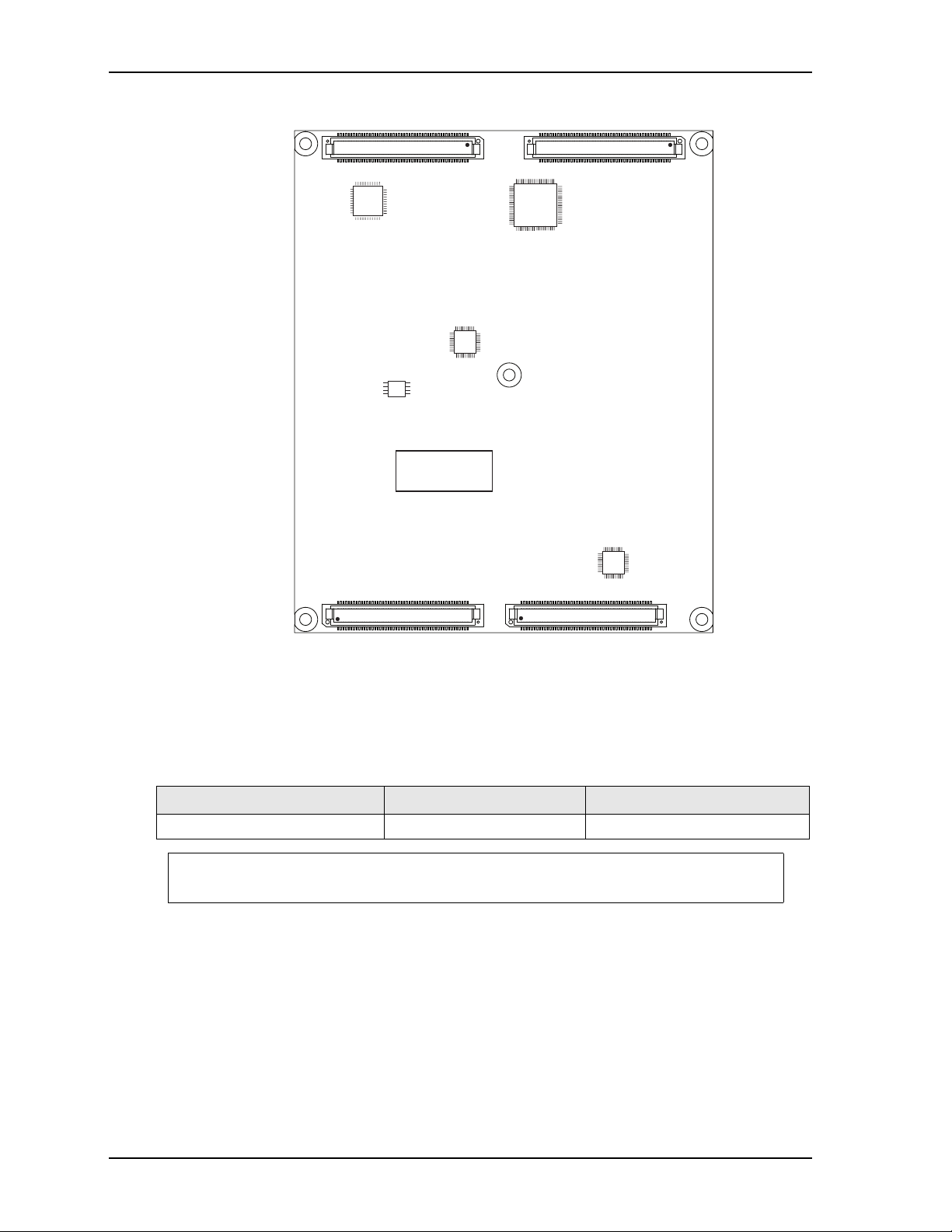

Key:

U9 - Super I/O

U11 - HD Audio

U12 - Ethernet

U14 - SSD

U19 - Board Controller

U37 - SPI Flash

U14

U9

ETX-PVR_Bottom_Comp_a

U11

U19

U37

U12

Connector and Socket Definitions

Table 2-2. Connector and Socket Descriptions

Figure 2-5. Component Locations (Bottom Side)

Table 2 - 2 describes the connectors and sockets shown in Figures 2-6 and 2-7.

Jack # Name Description

J1 ETX X1 (on

Standard 100-pin, 0.6 mm Hirose connector for PCI, Audio, and USB signals

bottom side of

the board; see

Figure 2-7.)

J2 ETX X2 (on

back of the

Standard 100-pin, 0.6 mm Hirose connector for ISA signals

board; see

Figure 2-7.)

J3 ETX X3 (on

back of the

Standard 100-pin, 0.6 mm Hirose connector for video, serial, keyboard and

mouse, and parallel/floppy drive signals

board; see

Figure 2-7.)

10 Reference Manual ETX-PVR

Page 17

Chapter 2 Product Overview

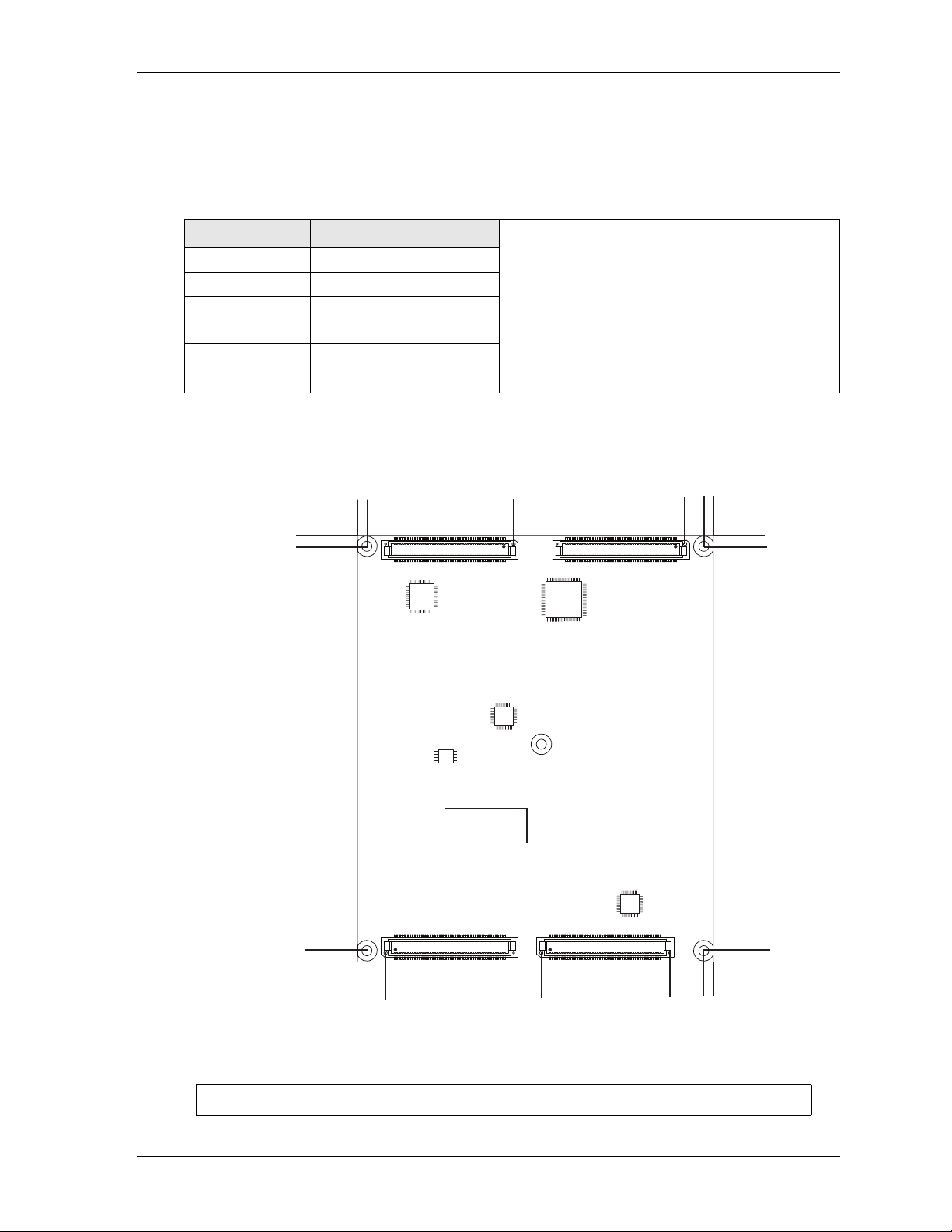

Key:

J6 - DDR3 SODIMM socket

J7 - Not supported

J8 - SATA1

J9 - SATA2

JP1 - See jumper table

ETX-PVR_Top_Conn_b

JP1

J6

J7

J8

J9

Table 2-2. Connector and Socket Descriptions (Continued)

J4 ETX X4 (on

back of the

Standard 100-pin, 0.6 mm Hirose connector for IDE, Ethernet, SMBus, I2C,

speaker, VBat, and power management signals

board; see

Figure 2-7.)

J6 SODIMM Standard un-buffered 204-pin socket for DDR3 memory

J7 LPC Not Supported

J8 SATA1 Standard 7-pin, 1.27mm right-angle connector for serial ATA signals

J9 SATA2 Standard 7-pin, 1.27mm right-angle connector for serial ATA signals

Figure 2-6. Connector and Socket Locations (Top Side)

NOTE Pin-1 is shown as a black pin (square or round) in all connectors and jumpers in

all illustrations.

ETX-PVR Reference Manual 11

Page 18

Chapter 2 Product Overview

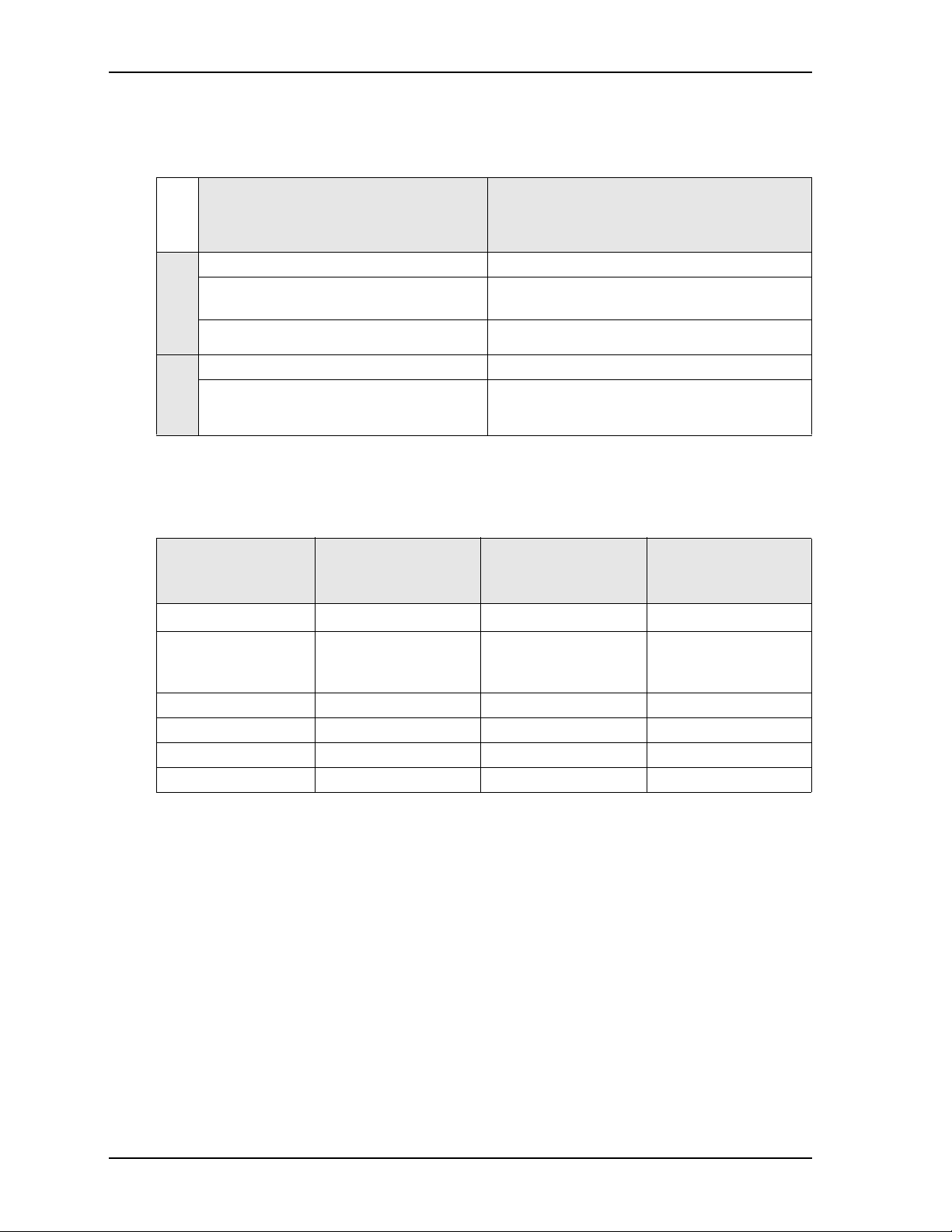

Key:

J1 - X1 ETX connector

J2 - X2 ETX connector

J3 - X3 ETX connector

J4 - X4 ETX connector

J4 J3

J1

J2

ETX-PVR_Bottom_Conn_a

Jumper Header Definition

Table 2-3. Jumper Header Setting

Figure 2-7. Connector Locations (Bottom Side)

Table 2 - 3 describes the jumper header shown in Figure 2-6 on page 11.

Jumper # Installed Removed/Installed

JP1 – SSD Select (Master/Slave) Master (Default) Slave (Removed)

NOTE Jumpers or shunts use 2mm pitch. A jumper that is removed may be placed on one of

the jumper pins for safe keeping.

12 Reference Manual ETX-PVR

Page 19

Chapter 2 Product Overview

0.00

0.12

4.38

4.26

J4 J3

J1

J2

ETX-PVR_Bottom_Dmn_a

0.00

0.100.10

0.20

2.0

3.55

3.65

0.00

0.36

1.70

3.35

0.12

0.00

4.38

4.26

Specifications

Physical Specifications

Table 2 - 4 provides the physical dimensions of the board.

Table 2-4. Weight and Footprint Dimensions

Item Dimension

Weigh t

Height (overall)

Width

0.10 kg (0.20 lb)

6.35mm (0.25")

95.25mm (3.75")

NOTE Overall height is measured from the

upper board surface to the highest

permanent component on the upper

board surface. This measurement does

not include the cooling solution.

Length

Thickness

Mechanical Specifications

114.3mm (4.5")

2.36mm (0.093")

Figure 2-8. Mechanical Overview (Bottom Side)

NOTE All dimensions are given in inches. Pin 1 is shown as a dot on each ETX connector.

ETX-PVR Reference Manual 13

Page 20

Chapter 2 Product Overview

Environmental Specifications

Table 2 - 5 provides the most efficient operating and storage environmental ranges required for this board.

Table 2-5. Environmental Requirements

Parameter 1.66GHz Atom N455,

1.80GHz Atom D525 CPUs

Environmental Ranges

Operating –20° to +70°C (-4° to +158°F)

Extended

(Optional)

Storage –55° to +85°C (–67° to +185°F)

Temperature

Operating 5% to 90% relative humidity, non-condensing

Non-operating 5% to 95% relative humidity, non-condensing

Humidity

–40° to +85°C (–40° to +185°F)

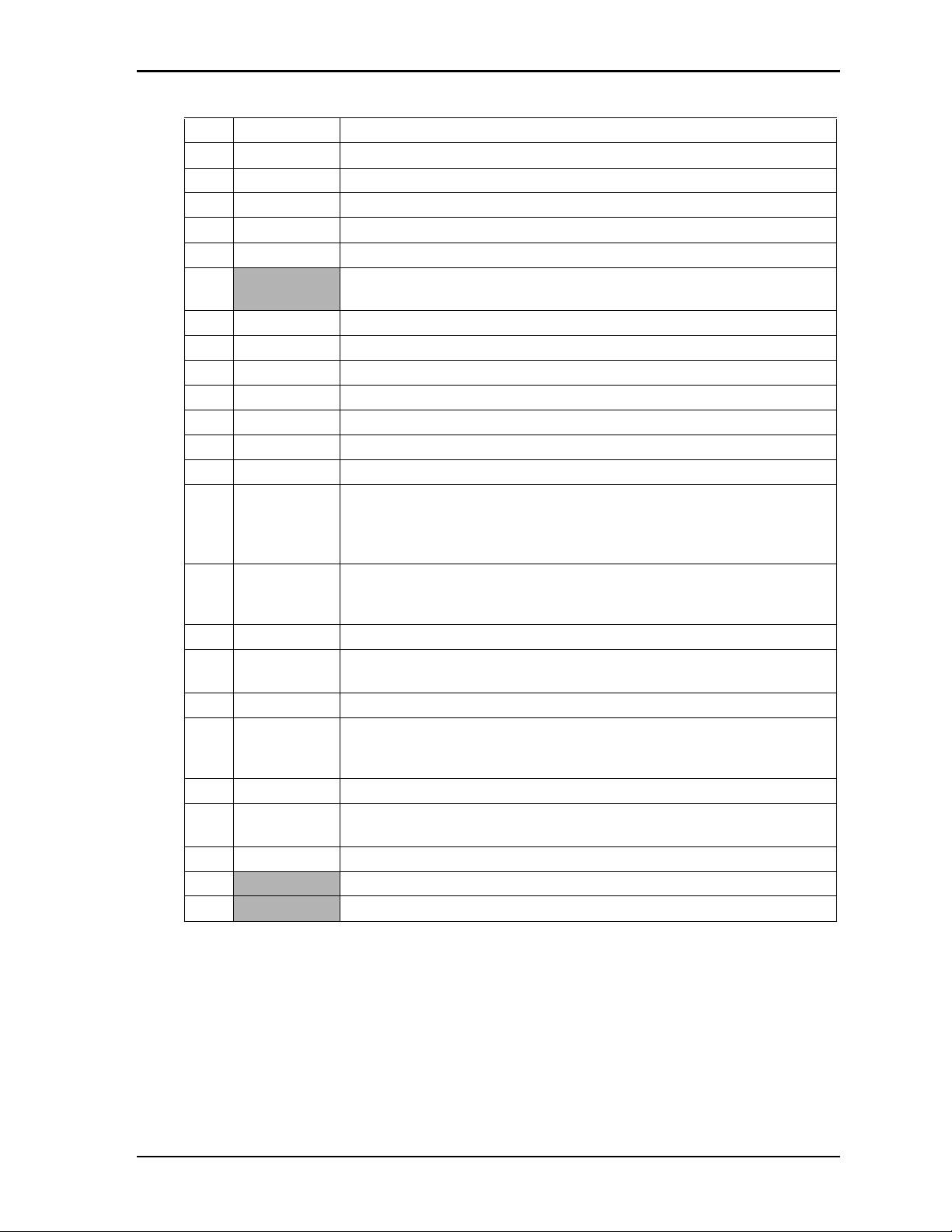

Power Specifications

Table 2 - 6 provides the power requirements for the ETX-PVR.

Table 2-6. Power Supply Requirements

Parameter 1.00GHz N455

Characteristics

(SpeedStep disabled)

Input Type Regulated DC voltages Regulated DC voltages Regulated DC voltages

In-rush Current and

Duration (Typical

Peak)

Idle Current (Typical) 1.71A (8.57W) 1.75A (8.74W) 2.27A (11.37W)

BIT Current (Typical) 2.22A (11.09W) 2.49A (12.46W) 3.31A (16.53W)

S1 Mode 0.25A (1.26W) 0.25A (1.26W) 0.25A (1.26W)

S3 Mode 0.26A (1.29W) 0.26A (1.29W) 0.26A (1.29W)

Note: All test loads include baseboard circuits.

Operating configurations:

See Figure 2-9 See Figure 2-10 See Figure 2-11

1.66GHz N455

Characteristics

1.80GHz D525

Characteristics

• In-rush operating configuration includes video, 2GB DDR3 RAM, one ET1-BBD-R-02 ETX

baseboard, and one AT power supply.

• Idle operating configuration includes the In-rush configuration as well as one SATA hard drive with

Windows XP OS, and PS/2 keyboard and mouse.

• BIT (Burn-In-Test) operating configuration includes the Idle configuration as well as two serial COM

ports with loop backs, one parallel port with loop back, four USB Compact Flash readers each with

256MB of Compact Flash, secondary SATA drive as slave, and one Ethernet connection.

• S1 (Standby) operating configuration is the same as the Idle configuration.

• S3 (Suspend-to-RAM) operating configuration is the same as the Idle configuration.

14 Reference Manual ETX-PVR

Page 21

Chapter 2 Product Overview

Figure 2-9. N455 (with SpeedStep disabled) Peak In-Rush Current and Duration

Figure 2-10. N455 Peak In-Rush Current and Duration

ETX-PVR Reference Manual 15

Page 22

Chapter 2 Product Overview

Figure 2-11. D525 Peak In-Rush Current and Duration

16 Reference Manual ETX-PVR

Page 23

Chapter 2 Product Overview

Heat Spreader

ETX-PVR

COM Board

0.52

ETX

Connector

ETX-PVR_Cooling_Ht_b

ETX-PVR with Heat Spreader

Heat

Sink

ETX-PVR

COM Board

ETX

Connector

2.23

ETX-PVR with Active Heat Sink (Fan)

Heat

Sink

ETX-PVR

COM Board

ETX

Connector

1.56

ETX-PVR with Passive Heat Sink (no Fan)

Thermal/Cooling Requirements

The CPU, I/O Hub, and voltage regulators are the main sources of heat on the board.The ETX-PVR is

designed to operate at the maximum speeds of the N455 (1.66GHz) or N525 (1.80GHz) CPUs and requires

a cooling solution. ADLINK offers two cooling solutions, as well as a heat spreader platform on which to

build a cooling solution (see Table 2-7 for descriptions of the cooling solution options.) Figure 2-12 provides

the height measurements from the bottoms of the ETX connectors to the tops of the cooling components.

NOTE The overall system design must keep the ICs within their operating temperature

specifications.

Table 2-7. ADLINK Optional Cooling Solutions

Cooling Solution Description

Passive Heat Sink

(without fan)

Active Heat Sink

(with fan)

Heat Spreader Provides a simple thermal platform on which to build a cooling solution.

Qualified to maintain optimal performance up to +70°C.

Qualified to maintain optimal performance up to +85°C.

NOTE All heights are given in inches.

Figure 2-12. Stack Heights of Cooling Assemblies

ETX-PVR Reference Manual 17

Page 24

Chapter 2 Product Overview

18 Reference Manual ETX-PVR

Page 25

Chapter 3 Hardware

Overview

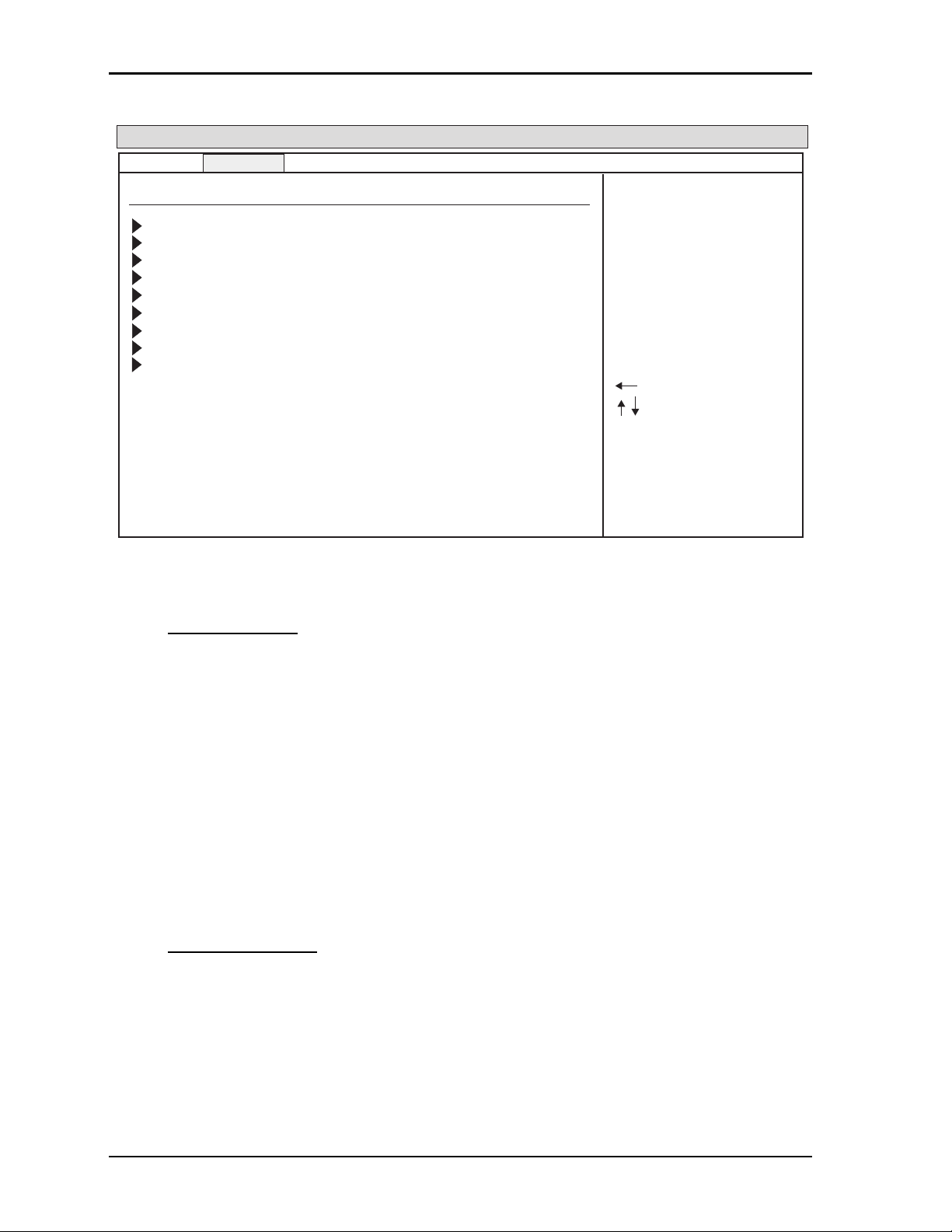

This chapter discusses the hardware features of the ETX-PVR in the following order:

• CPU

• Graphics

• Memory

• Interrupt Channel Assignments

• Memory Map

• I/O Address Map

• PCI Bus Interface (J1)

USB

Audio Interface

• ISA Bus Interface (J2 [ISA DMA not supported])

• Primary I/O Interface (J3)

Floppy/Parallel Interface

Serial Port Interfaces

Keyboard

Mouse

Video Interfaces (VGA and LVDS)

• IDE and Auxiliary Interface (J4)

Primary IDE Interface

Ethernet Interface

Power Control and Management

Real Time Clock (RTC)

Speaker

SMBus

• Miscellaneous

Oops! Jumper (BIOS recovery)

Remote Access (Serial Console)

Watchdog Timer (WDT)

Power Interface (including ACPI)

NOTE ADLINK Technology, Inc. only supports the features/options tested and listed in

this manual. The main integrated circuits used in the ETX-PVR may provide

more features or options than are listed for the ETX-PVR, but some of these chip

features or options are not supported on the board and will not function as

specified in the chip documentation.

ETX-PVR Reference Manual 19

Page 26

Chapter 3 Hardware

CPU

The ETX-PVR offers two versions of the Intel Atom™ N400/D500 series CPU—the N455 and

D525—operating at 1.66GHz with 6.5W TDP and 1.80GHz with 13W TDP, respectively. The N400/D500

integrates a low-power and high-performance x86 Processor Core with Memory Controller and 3D Graphics

Engine. This single chip is based on 45-nm, Hi-K process technology, ideal for deeply embedded

applications.

Graphics

The N400/D500 CPU provides a refresh of the Intel third generation graphics core—a 2D/3D graphics

engine that performs pixel shading and vertex shading within a single hardware accelerator, which

minimizes access to memory and improves render performance.

Memory

The ETX-PVR supports one DDR3 SODIMM for up to 2GB of RAM. One 64-bit access channel supports

single- or double-sided DIMMs, allowing for up to two device ranks. Enhanced memory technology on the

board provides optimized bandwidth and reduced latency, increased efficiency of system memory protocol,

and a near continuous data flow to the processor.

20 Reference Manual ETX-PVR

Page 27

Chapter 3 Hardware

Interrupt Channel Assignments (IRQs)

The interrupt channel assignments are listed in Table 3-1.

Table 3-1. Interrupt Channel (IRQs) Assignments (Typical)

Device vs IRQ No. 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

Timer X

Keyboard X

Secondary Cascade X

COM1 O D

COM2 D O

Floppy D

Parallel O D

RTC X

IDE D

Math Coprocessor X

PS/2 Mouse X

HD Audio CODEC D

PCI INTA Automatically Assigned

PCI INTB Automatically Assigned

PCI INTC Automatically Assigned

PCI INTD Automatically Assigned

USB Automatically Assigned

Video Automatically Assigned

Ethernet Automatically Assigned

Legend: D = Default, O = Optional, X = Fixed

NOTE The IRQs for the Ethernet, Video, USB, and PCI are automatically assigned by

the BIOS Plug and Play logic. Local IRQs assigned during initialization can not

be used by external devices.

ETX-PVR Reference Manual 21

Page 28

Chapter 3 Hardware

Memory Map

Table 3 - 2 provides the common PC/AT memory allocations. These are DOS-level addresses. The OS

typically hides these physical addresses by way of memory management.

Table 3-2. Memory Map

Base Address Function

00000000h - 0009FFFFh Conventional Memory

000A0000h - 000AFFFFh Graphics Memory

000B0000h - 000B7FFFh Mono Text Memory

000B8000h - 000BFFFFh Color Text Memory

000C0000h - 000CFFFFh Standard Video BIOS

000D0000h - 000DFFFFh DVMT Memory

000E0000h - 000EFFFFh PCI Express Base Memory

000F0000h - 000FFFFFh System Flash and PCI Resources

I/O Address Map

Table 3 - 3 provides the I/O address map. These are DOS-level addresses. The OS typically hides these

physical addresses by way of memory management.

Table 3-3. I/O Address Map

Address (hex) Subsystem

0000-00F Primary DMA Controller

0020-0021 Master Interrupt Controller

002E-002F SIO Configuration Ports

0040-0043 Programmable Interrupt Timer (Clock/Timer)

0060-006F Keyboard Controller

0070-007F CMOS RAM, NMI Mask Reg, RT Clock

0080-009F DMA Page Registers

00A0-00BF Slave Interrupt Controller

00C0-00DF Slave DMA Controller #2

00F0-00FF Math Coprocessor

01F0-01F8 Primary IDE Hard Disk Controller

0278-027F Parallel Printer

02F8-02FF Serial Port 2 (COM2)

0378-037F Parallel Port (Standard and EPP)

03C0-03DF VGA

03F0-03F7 Floppy Disk Controller

03F8-03FF Serial Port 1 (COM1)

0400-041F SMBus Configuration Ports

0500-053F ICH8 GPIO Configuration Ports

0778-077A Parallel Port (ECP Extensions) (Port 378+400)

0800-087F ICH8 Power Management Ports

22 Reference Manual ETX-PVR

Page 29

Chapter 3 Hardware

Table 3-3. I/O Address Map (Continued)

0A79h ISA PnP Ports

0B00-0B7F SIO Runtime Registers

0CF8-0CFF PCI bus Configuration Address and Data

NOTE 0A79h is the ISA PnP port used by the BIOS and an OS that supports this feature to

recognize ISA PnP (Plug and Play) cards.

The Intel I/O hub ICH-8 (ICH-6 or later) does not support ISA DMA.

X1 PCI Bus Interface (J1)

The J1, 100-pin standard connector is used for the PCI bus, USB ports, and HD Audio interface connections.

This section briefly describes each of these features.

Table 3 - 4 provides the complete pin outs for the J1 (X1) connector.

PCI Bus

The CPU integrates a PCI arbiter that supports up to four external PCI masters.

• Interface carries all of the appropriate PCI signals

• Bus operates at clock speeds up to 33 MHz

• PCI 2.3 Compliant, 32-bit +3.3V PCI interface with +5V tolerant inputs

Universal Serial Bus (USB)

The ETX-PVR module supports up to four USB ports on the baseboard, and the supported features are listed

below.

• USB v2.0 and backwards compatible to Universal UHCI v1.1

• Two root USB hubs and four USB ports

• Supports USB boot of floppy disk drives, hard disk drives, CD-ROMs, or other USB boot devices

• Integrated physical layer transceivers

• Over-current detection status on USB ports 1 and 2

Serial Interrupt Request

This SERIRQ signal is connected to the serial request input on the I/O Hub (ICH8-M) for the alternative

ISA/PCI interrupts. The ETX-PVR SERIRQ pin (pin 21) must be connected to the baseboard to use the ISA

bus on the baseboard.

NOTE The Intel ICH8 I/O Hub does not support ISA DMA.

ETX-PVR Reference Manual 23

Page 30

Chapter 3 Hardware

Audio Interface

The Realtek HD Audio CODEC (ALC262) on the ETX-PVR supports the HDA Link protocol and the

supported features in the following list.

• Supports audio amplifier on baseboard

• PC-Beep pass through to Line Out while reset is held Active Low

• True Line Level Output with volume control independent of Line Out

• Digital 3V and 5V compliant

Tab le 3-4 provides a complete list of the ETX J1 connector signals.

Table 3-4. Complete X1 Interface Pin Signal Descriptions (J1)

J1

Pin

#

1, 2

3 PCICLK3 PCI clock 3 – This signal line is one of four signal lines. These clock signals

4 PCICLK4 PCI clock 4 – Refer to J1, pin-3 for more information.

5, 6

7 PCICLK1 PCI clock 1 – Refer to J1, pin-3 for more information.

8 PCICLK2 PCI clock 2 – Refer to J1, pin-3 for more information.

9 REQ3* Bus Request 3 – This signal line is one of four signal lines. These signals indicate

10 GNT3* Grant 3 – This signal line is one of four signal lines. These signal lines indicate

11 GNT2* Grant 2 – Refer to J1, pin-10 for more information.

12

13 REQ2* Bus Request 2 – This signal line is one of four signal lines. These signals indicate

14 GNT1* Grant 1 – Refer to J1, pin-10 for more information.

15 REQ1* Bus Request 1 – Refer to J1, pin-13 for more information.

16

17 GNT0* Grant 0 – Refer to J1, pin-10 for more information.

18 NC Not Connected (Reserved)

19,

20

21 SERIRQ Serial Interrupt Request – This signal supports the serial interrupt protocol.

22 REQ0* Bus Request 0 – Refer to J1, pin-13 for more information.

23 AD0 Address/Data bus 0 – These signals <AD31 – AD0> are multiplexed on the same

Signal Description

GND Ground

provide the timing outputs for four external PCI devices and the timing for all

transactions on the PCI bus.

GND Ground

to the arbiter that the device desires use of the bus.

access has been granted to the requesting device (PCI Masters).

+3.3V +3.3 volts +/- 5% (Caution: This signal is generated by the ETX-PVR.)

[Note: This signal is not supported on ETX-PVR-R-14, R-16, and R-18 models.]

the device desires use of the bus to the arbiter.

+3.3V +3.3 volts +/- 5% (Caution: This signal is generated by the ETX-PVR.)

[Note: This signal is not supported on ETX-PVR-R-14, R-16, and R-18 models.]

VCC DC Power – +5 volts +/- 5%

PCI connector pins. During the address phase of a PCI cycle, AD31–AD0

contain a 32-bit address or other destination information. During the data phase,

AD31 – AD0 contain data.

24 Reference Manual ETX-PVR

Page 31

Chapter 3 Hardware

Table 3-4. Complete X1 Interface Pin Signal Descriptions (J1) (Continued)

24 +3.3V +3.3 volts +/- 5% (Caution: This signal is generated by the ETX-PVR.)

[Note: This signal is not supported on ETX-PVR-R-14, R-16, and R-18 models.]

25 AD1 Address/Data bus 1 – Refer to J1, pin-23 for more information.

26 AD2 Address/Data bus 2 – Refer to J1, pin-23 for more information.

27 AD4 Address/Data bus 4 – Refer to J1, pin-23 for more information.

28 AD3 Address/Data bus 3 – Refer to J1, pin-23 for more information.

29 AD6 Address/Data bus 6 – Refer to J1, pin-23 for more information.

30 AD5 Address/Data bus 5 – Refer to J1, pin-23 for more information.

31 CBE0* PCI Bus Command/Byte Enable 0 – This signal line is one of four signal lines

multiplexed on the same pins, so that during the address cycle, the command is

defined and during the data cycle, the byte enable is defined.

32 AD7 Address/Data bus 7 – Refer to J1, pin-23 for more information.

33 AD8 Address/Data bus 8 – Refer to J1, pin-23 for more information.

34 AD9 Address/Data bus 9 – Refer to J1, pin-23 for more information.

35,

GND Ground

36

37 AD10 Address/Data bus 10 – Refer to J1, pin-23 for more information.

38 AUXAL Auxiliary A Input Left – This signal is normally used for an external CD-ROM

analog output or similar live-level audio source. Minimum input impedance is 5k

Ohms and nominal input level is 1 volt RMS.

39 AD11 Address/Data bus 11 – Refer to J1, pin-23 for more information.

40 MIC Microphone reference signal – This microphone input signal has a minimum

input impedance of 5k Ohms, and the maximum input voltage is 0.15 V p-p.

41 AD12 Address/Data bus 12 – Refer to J1, pin-23 for more information.

42 AUXAR Auxiliary A Input Right – This signal is normally used for an external CD-ROM

analog output or similar live-level audio source. Minimum input impedance is 5k

Ohms and nominal input level is 1 volt RMS.

43 AD13 Address/Data bus 13 – Refer to J1, pin-23 for more information.

44 NC Not Connected

45 AD14 Address/Data bus 14 – Refer to J1, pin-23 for more information.

46 SNDL Stereo Line Output Left channel – Output signal has a nominal 1 volt RMS level

into 10k impedance load. This output signal can not drive low-impedance

speakers directly.

47 AD15 Address/Data bus 15 – Refer to J1, pin-23 for more information.

48

ASGND Analog Ground – This ground is used for the sound controller and an external

amplifier to achieved the lowest audio noise levels.

49 CBE1* Bus Command and Byte Enable 1 – Refer to J1, pin-31 for more information.

50 SNDR Stereo Line Output Right channel – This output signal has a nominal level of 1

volt RMS into 10k impedance load. This output signal can not drive lowimpedance speakers directly

51,

VCC DC Power – +5 volts +/- 5%

52

53 PAR PCI bus Parity bit – This signal is even parity bit on AD[31:0] and CBE[3:0]*.

54 SERR* System Error – This signal is for reporting address parity errors.

ETX-PVR Reference Manual 25

Page 32

Chapter 3 Hardware

Table 3-4. Complete X1 Interface Pin Signal Descriptions (J1) (Continued)

55 PERR* Parity Error – This signal is driven by the PCI target during a write to indicate a

data parity error has been detected.

56 NC Not connected (Reserved)

57 PME* Power Management Event – This signal is an optional signal that can be used by

a device to request a change in the device or system power state.

58 USB2- Universal Serial Bus Port 2 Data Negative Polarity

59 LOCK* Lock – This signal indicates an operation that may require multiple transactions

to complete.

60 DEVSEL* Device Select – Driven by the target device when its address is decoded.

61 TRDY* Target Ready – This signal indicates the selected device’s ability to complete the

current cycle of transaction. Both IRDY and TRDY must be asserted to

terminate a data cycle.

62 USB3- Universal Serial Bus Port 3 Data Negative Polarity

63 IRDY* Initiator Ready – Indicates the master’s ability to complete the current data cycle.

64 STOP* Stop – Driven by the current PCI target when requesting the master stop the

current transaction.

65 FRAME* PCI bus Frame access – Driven by the current master to indicate the start of a

transaction and will remain active until the final data cycle.

66 USB2+ Universal Serial Bus Port 2 Data Positive Polarity

67,

GND Ground

68

69 AD16 Address/Data bus 16 – Refer to J1, pin-23 for more information.

70 CBE2* Bus Command and Byte Enable 2 – Refer to J1, pin-31 for more information.

71 AD17 Address/Data bus 17 – Refer to J1, pin-23 for more information.

72 USB3+ Universal Serial Bus Port 3 Data Positive Polarity

73 AD19 Address/Data bus 19 – Refer to J1, pin-23 for more information.

74 AD18 Address/Data bus 18 – Refer to J1, pin-23 for more information.

75 AD20 Address/Data bus 20 – Refer to J1, pin-23 for more information.

76 USB0- Universal Serial Bus Port 0 Data Negative Polarity

77 AD22 Address/Data bus 22 – Refer to J1, pin-23 for more information.

78 AD21 Address/Data bus 21 – Refer to J1, pin-23 for more information.

79 AD23 Address/Data bus 23 – Refer to J1, pin-23 for more information.

80 USB1- Universal Serial Bus Port 0 Data Negative Polarity

81 AD24 Address/Data bus 24 – Refer to J1, pin-23 for more information.

82 CBE3* Bus Command and Byte Enable 3 – Refer to J1, pin-31 for more information.

83,

VCC DC Power – +5 volts +/- 5%

84

85 AD25 Address/Data bus 25 – Refer to J1, pin-23 for more information.

86 AD26 Address/Data bus 26 – Refer to J1, pin-23 for more information.

87 AD28 Address/Data bus 28 – Refer to J1, pin-23 for more information.

88 USB0+ Universal Serial Bus Port 0 Data Positive Polarity

89 AD27 Address/Data bus 27 – Refer to J1, pin-23 for more information.

90 AD29 Address/Data bus 29 – Refer to J1, pin-23 for more information.

26 Reference Manual ETX-PVR

Page 33

Chapter 3 Hardware

Table 3-4. Complete X1 Interface Pin Signal Descriptions (J1) (Continued)

91 AD30 Address/Data bus 30 – Refer to J1, pin-23 for more information.

92 USB1+ Universal Serial Bus Port 1 Data Positive Polarity

93 PCIRST* PCI Bus Reset – Signal resets entire PCI Bus. Asserted during a system reset.

94 AD31 Address/Data bus 31 – Refer to J1, pin-23 for more information.

95 INTC* Interrupt C – This signal is used to request an interrupt and only has meaning on

a multi-function device.

96 INTD* Interrupt D – This signal is used to request an interrupt and only has meaning on

a multi-function device.

97 INTA* Interrupt A – This signal is used to request an interrupt.

98 INTB* Interrupt B – This signal is used to request an interrupt and only has meaning on

a multi-function device.

99, 100

Note: The shaded areas denote power or ground. The * symbol indicates the signal is Active Low.

GND Ground

X2 ISA Bus Interface (J2)

The J2, 100-pin connector is used for standard ISA interface connections. The CPU does not directly support

an ISA expansion interface. A provision for ISA bus capabilities is provided in this connector through an onboard PCI-to-ISA bridge. Refer to Table 3-5 for pin definitions of the X2 interface.

Table 3-5. Complete X2 ISA Bus Interface Pin Signal Descriptions (J2)

J2

Pin #

1, 2

3 SD14 System Data 14 – These signals (0 to 19) provide system data bits.

4 SD15 System Data 15 – Refer to SD14, pin-3 for more information.

5 SD13 System Data 13 – Refer to SD14, pin-3 for more information.

6 MASTER* Bus Master – This signal is used by an ISA board to gain ownership of the ISA

7 SD12 System Data 12 – Refer to SD14, pin-3 for more information.

8 NS Not Supported

9 SD11 System Data 11 – Refer to SD14, pin-3 for more information.

10 NS Not Supported

11 SD10 System Data 10 – Refer to SD14, pin-3 for more information.

12 NS Not Supported

13 SD9 System Data 9 – Refer to SD14, pin-3 for more information.

14 NS Not Supported

15 SD8 System Data 8 – Refer to SD14, pin-3 for more information.

16 NS Not Supported

17 MEMW* Memory Write – This signal instructs a selected memory device to store data

18 NS Not Supported

Signal Description

GND Ground

bus.

currently on the data bus. It is active on all memory write cycles.

ETX-PVR Reference Manual 27

Page 34

Chapter 3 Hardware

Table 3-5. Complete X2 ISA Bus Interface Pin Signal Descriptions (J2) (Continued)

19 MEMR* Memory Read – This signal instructs a selected memory device to drive data

onto the data bus. It is active on all memory read cycles.

20 NS Not Supported

21 LA17 Latchable Address 17 – These signals (0-23) must be latched by the resource if

the line is required for the entire data cycle.

22 NS Not Supported

23 LA18 Latchable Address 18 – Refer to LA17, pin-21 for more information.

24 IRQ14 Interrupt Request 14 – Asserted by a device when it has pending interrupt

request. Only one device may use the request line at a time.

25 LA19 Latchable Address 19 – Refer to LA17, pin-21 for more information.

26 IRQ15 Interrupt Request 15 – Asserted by a device when it has pending interrupt

request. Only one device may use the request line at a time.

27 LA20 Latchable Address 20 – Refer to LA17, pin-21 for more information.

28 IRQ12 Interrupt Request 12 – Asserted by a device when it has pending interrupt

request. Only one device may use the request line at a time.

29 LA21 Latchable Address 21– Refer to LA17, pin-21 for more information.

30 IRQ11 Interrupt Request 11 – Asserted by a device when it has pending interrupt

request. Only one device may use the request line at a time.

31 LA22 Latchable Address 22 – Refer to LA17, pin-21 for more information.

32 IRQ10 Interrupt Request 10 – Asserted by a device when it has pending interrupt

request. Only one device may use the request line at a time.

33 LA23 Latchable Address 23 – Refer to LA17, pin-21 for more information.

34 IO16* I/O Chip Select 16 – This signal is driven low by an I/O slave device to indicate

it is capable of performing a 16-bit I/O data transfer. This signal is driven from

a decode of the SA15 to SA0 address lines.

35, 36

GND Ground

37 SBHE* System Byte High Enable – This signal is driven low to indicate a transfer of

data on the high half of the data bus (D15 to D8).

38 M16* Memory Chip Select 16 – This signal is driven low by a memory slave device to

indicates it is cable of performing a 16-bit memory data transfer. This signal is

driven from a decode of the LA23 to LA17 address lines.

39 SA0 System Address 0 – These signals (0 to 19) provide system address bits.

40 OSC Oscillator – This clock signal operates at 14.3 MHz. This signal is not

synchronous with the system clock (SYSCLK).

41 SA1 System Address 1– Refer to SA0, pin-39 for more information.

42 BALE Buffered Address Latch Enable – This signal is used to latch the LA23 to LA17

signals or decodes of these signals. Addresses are latched on the falling edge of

BALE.

43 SA2 System Address 2 – Refer to SA0, pin-39 for more information.

44 NS Not Supported

45 SA3 System Address 3 – Refer to SA0, pin-39 for more information.

46 NS Not Supported

47 SA4 System Address 4 – Refer to SA0, pin-39 for more information.

48 IRQ3 Interrupt Request 3 – Asserted by a device when it has pending interrupt

request. Only one device may use the request line at a time.

28 Reference Manual ETX-PVR

Page 35

Chapter 3 Hardware

Table 3-5. Complete X2 ISA Bus Interface Pin Signal Descriptions (J2) (Continued)

49 SA5 System Address 5 – Refer to SA0, pin-39 for more information.

50 IRQ4 Interrupt Request 4 – Asserted by a device when it has pending interrupt

request. Only one device may use the request line at a time.

51, 52

VCC DC Power – +5 volts +/- 5%

53 SA6 System Address 6 – Refer to SA0, pin-39 for more information.

54 IRQ5 Interrupt Request 5 – Asserted by a device when it has pending interrupt

request. Only one device may use the request line at a time.

55 SA7 System Address 7 – Refer to SA0, pin-39 for more information.

56 IRQ6 Interrupt Request 6 – Asserted by a device when it has pending interrupt

request. Only one device may use the request line at a time.

57 SA8 System Address 8 – Refer to SA0, pin-39 for more information.

58 IRQ7 Interrupt Request 7 – Asserted by a device when it has pending interrupt

request. Only one device may use the request line at a time.

59 SA9 System Address 9 – Refer to SA0, pin-39 for more information.

60 SYSCLK System Clock – This is a free running clock typically in the 8 MHz to 10 MHz

range, although its exact frequency is not guaranteed.

61 SA10 System Address 10 – Refer to SA0, pin-39 for more information.

62 REFSH* Memory Refresh – This signal is driven low to indicate a memory refresh cycle

is in progress. Memory is refreshed every 15.6 usec.

63 SA11 System Address 11 – Refer to SA0, pin-39 for more information.

64 NS Not Supported

65 SA12 System Address 12 – Refer to SA0, pin-39 for more information.

66 NS Not Supported

67, 68

GND Ground

69 SA13 System Address 13 – Refer to SA0, pin-39 for more information.

70 NS Not Supported

71 SA14 System Address 14 – Refer to SA0, pin-39 for more information.

72 NS Not Supported

73 SA15 System Address 15 – Refer to SA0, pin-39 for more information.

74 IOR* I/O Read – This strobe signal is driven by the owner of the bus (ISA bus master)

and instructs the selected I/O device to drive read data onto the data bus.

75 SA16 System Address 16 – Refer to SA0, pin-39 for more information.

76 IOW* I/O Write – This strobe signal is driven by the owner of the bus (ISA bus

master) and instructs the selected I/O device to capture the write data on the

data bus.

77 SA18 System Address 18 – Refer to SA0, pin-39 for more information.

78 SA17 System Address 17 – Refer to SA0, pin-39 for more information.

79 SA19 System Address 19 – Refer to SA0, pin-39 for more information.

80 SMEMR* System Memory Read – This signal is used by bus owner to request a memory

device to drive data onto the data bus and only active for lower 1 MB. Used for

legacy compatibility with 8-bit cards.

ETX-PVR Reference Manual 29

Page 36

Chapter 3 Hardware

Table 3-5. Complete X2 ISA Bus Interface Pin Signal Descriptions (J2) (Continued)

81 IOCHRDY I/O Channel Ready – This signal allows slower ISA boards to lengthen I/O or

memory cycles by inserting wait states. This signal’s normal state is active high

(ready). ISA boards drive the signal inactive low (not ready) to insert wait

states. Devices using this signal to insert wait states should drive it low

immediately after detecting a valid address decode and an active read, or write

command. The signal is released high when the device is ready to complete the

cycle.

82 NS Not Supported

83, 84

VCC DC Power – +5 volts +/- 5%

85 SD0 System Data 0 – Refer to SD14, pin-3 for more information.

86 SMEMW* System Memory Write – This signal is used by bus owner to request a memory

device to store data currently on the data bus and only active for the lower

1 MB. Used for legacy compatibility with 8-bit cards.

87 SD2 System Data 2 – Refer to SD14, pin-3 for more information.

88 SD1 System Data 1 – Refer to SD14, pin-3 for more information.

89 SD3 System Data 3 – Refer to SD14, pin-3 for more information.

90 NOWS* No Wait State – This signal is driven low by a bus slave device to indicate it is

capable of performing a bus cycle without inserting any additional wait states.

To perform a 16-bit memory cycle without wait states, this signal is derived

from an address decode.

91 NS Not Supported

92 SD4 System Data 4 – Refer to SD14, pin-3 for more information.

93 SD5 System Data 5 – Refer to SD14, pin-3 for more information.

94 IRQ9 Interrupt Request 9 – Asserted by a device when it has pending interrupt

request. Only one device may use the request line at a time.

95 SD6 System Data 6 – Refer to SD14, pin-3 for more information.

96 SD7 System Data 7 – Refer to SD14, pin-3 for more information.

97 IOCHK* I/O Channel Check – This signal may be activated by ISA boards to request that

a non-maskable interrupt (NMI) be generated to the system processor. It is

driven active to indicate an uncorrectable error has been detected.

98 RSTDRV Reset Drive – This signal is used to reset or initialize system logic on power up

or subsequent system reset.

99

100

GND Ground

GND Ground

Note: The shaded areas denote power or ground. The * symbol indicates the signal is Active Low.

30 Reference Manual ETX-PVR

Page 37

Chapter 3 Hardware

X3 Primary I/O Interface (J3)

The J3, 100-pin connector is used for Floppy or Printer (LPT1) interface, Serial interfaces (COM1 and

COM2), Mouse and Keyboard interfaces, and the video interfaces for standard VGA and LVDS video. This

section briefly describes each of these features. Refer to Table 3-6 on page 32 for pin definitions of the X3

interface.

Floppy Interface

The Floppy interface shares signal lines with the Parallel interface and is provided by the Super I/O chip

(SCH3112I-NU). The BIOS settings determine which one is operational.

• Supports two floppy drives

• Supports 16 bytes of FIFO with data rates up to 1 Mbps

Parallel Interface

Parallel interface supports standard parallel, Bi-directional, ECP and EPP protocols. The Super I/O chip

(SCH3112I-NU) provides the parallel interface signals, which are shared with the floppy drive interface.

• Shares signal lines with the Floppy interface, and the BIOS settings determine which one is operational

• Supports Standard Printer Port (SPP), Enhanced Parallel Port (EPP) and Enhanced Capabilities Port

(ECP)

Serial Ports 1 and 2

The Super I/O chip (SCH3112I-NU) provides the circuitry for two serial port UARTs. The signals for serial

ports 1 and 2 are provided to the baseboard through connector J3. However, the baseboard must provide the

serial transceivers to make use of this feature. The serial port features are:

• Two individual 16550-compatible UARTs

• Programmable word length, stop bits and parity

• 16-bit programmable baud rate generator and Interrupt generator

• Loop-back mode

• Two individual 16-bit FIFOs

PS/2 Keyboard

The signal lines for a PS/2 keyboard are provided through the J3 connector from the Super I/O chip

(SCH3112I-NU).

PS/2 Mouse

The signal lines for a PS/2 mouse are provided through the J3 connector from the Super I/O chip

(SCH3112I-NU).

VGA Interface

The N455 version of the CPU provides direct VGA outputs with a resolution up to 1400x1050 @ 60Hz. The

D525 version of the CPU provides resolutions up to 2048x1536 @ 60Hz.

The analog display output provides an RGB signal output as well as an HSYNC and a VSYNC signal. The

display function contains a RAM-based Digital-to-Analog Converter (RAMDAC) that transforms the digital

data from the graphics and video subsystems to analog data for CRT monitors.

ETX-PVR Reference Manual 31

Page 38

Chapter 3 Hardware

LVDS Interface

The CPU provides direct LVDS outputs, which support a single channel 18-bit LVDS interface with three

signal lines. The N455 CPU provides digital LVDS resolution up to 1280x800, and the D525 CPU provides

resolutions up to 1366x768.

NOTE The necessary voltages to drive a flat panel are not supplied through the J3 connector

on the ETX-PVR module. The required drive voltages for the flat panel must be

designed into the customer’s baseboard and supplied from the ATX or AT power

supply to provide drive voltages for the LVDS connector to the flat panel.

Table 3 - 6 describes the pin signals of the X3 ETX interface connector.

Table 3-6. Complete X3 Interface Pin Signal Descriptions (J3)

J3

Pin #

1, 2

3 Red Red – This is the Red analog output signal to the CRT.

4 Blue Blue – This is the Blue analog output signal to the CRT.

5 HSYNC Horizontal Sync – This signal is used for the digital horizontal sync output

6 Green Green – This is the Green analog output signal to the CRT.

7 VSYNC Vertical Sync – This signal is used for the digital vertical sync output to the

8 DDCK Display Data Channel Clock – This signal line provides the data clock signal

9 NC Not Connected

10 DDDA Display Data Channel Data – This signal line provides information to the

11 NC Not Connected

12 NC Not Connected

13 NC Not Connected

14 NC Not Connected

15, 16

17 NC Not Connected

18 NC Not Connected

19 NC Not Connected

20 NC Not Connected

21, 22

23 NC Not Connected

24 NC Not Connected

25 NC Not Connected

26 NC Not Connected

27, 28

Signal Description

GND Ground

to the CRT.

CRT.

to the Memory Hub from the monitor. This is part of the Plug and Play

standard developed by the VESA trade association.

Memory Hub about the monitor type, brand, model. This is part of the Plug

and Play standard developed by the VESA trade association.

GND Ground

GND Ground

GND Ground

32 Reference Manual ETX-PVR

Page 39

Chapter 3 Hardware

Table 3-6. Complete X3 Interface Pin Signal Descriptions (J3) (Continued)

29 LCDDO4 Data Negative Output, Line 2, Channel 1

30 LCDDO7 Clock Positive Output, Clock, Channel 1

31 LCDDO5 Data Positive Output, Line 2, Channel 1

32 LCDDO6 Clock Negative Output, Clock, Channel 1

33, 34

GND Ground

35 LCDDO1 Data Positive Output, Line 0, Channel 1

36 LCDDO3 Data Positive Output, Line 1, Channel 1

37 LCDDO0 Data Negative Output, Line 0, Channel 1

38 LCDDO2 Data Negative Output, Line 1, Channel 1

39, 40

41 JILI_DAT

VCC DC Power – +5V +/- 5%

2

Flat Panel I

C Data – This is the I2C data interface to the parameter

EEPROM used with the flat panel.

42 LTGIO0 General Purpose I/O

43 JILI_CLK

Flat Panel I

2

C Clock – This is the I2C clock interface to the parameter

EEPROM used with the flat panel.

44 BLON* Backlight On – This signal controls the external backlight power for the flat

panel.

45 BIASON

BIAS ON – This signal controls the flat panel contrast voltage.

(DNP)

46 DIGON Digital Power On – This signal controls the digital flat panel power up.

47 NC Not Connected

48 NC Not Connected

49 NC Not Connected

50 NC Not Connected

51 LPT/FLPY* Parallel/Floppy Select – This signal selects the parallel or floppy port

signals. If this signal is Low at boot time, the floppy drive is selected. If this

signal is High at boot time, the parallel port is selected. This state can not be

changed until the next boot cycle.

52 NC Not Connected (Reserved)

53

VCC DC Power – +5 volts +/- 5%

54 GND Ground

55 Strobe*

Parallel Strobe – This output signal is used to strobe data into the printer. I/O

pin in ECP/EPP mode.

DS0*

56 AFD*

Floppy Drive Select 0 – Selects drive 0.

Parallel Auto Feed – This is a output signal from the printer to

automatically feed one line after each line is printed.

DENSEL

Floppy Drive Density Select – This signal indicates if a low (250/300 kbps)

or high (500/1 kbps) data rate is selected.

57 NC Not Connected (Reserved)

58 PD7 Parallel Port Data 7 – This signal (0 to 7) provides a parallel port data signal

and is the printer data MSB.

59 NS Not Supported

ETX-PVR Reference Manual 33

Page 40

Chapter 3 Hardware

Table 3-6. Complete X3 Interface Pin Signal Descriptions (J3) (Continued)

60 ERR*

Parallel Error – This is a status output signal from the printer. A low state

indicates an error condition on the printer.

HDSEL*

Floppy Head Select – Selects floppy diskette side for Read/Write operations

(0 = side 1, 1 = side 0).

61 NS Not Supported

62 PD6

MTR0*

Parallel Port Data 6 – Refer to pin-58 and 80 for more information.

Floppy Motor Control 0 – Select motor on drive 0.

63 RXD2 Receive Data 2 – Serial port 2 receive data in.

64 INIT*

Parallel Initialize – This signal initializes the printer. Output in standard

mode, I/O in ECP/EPP mode.

DIR*

Floppy Direction – Direction of head movement (0 = inward motion,

1 = outward motion).

65, 66

GND Ground

67 RTS2* Request To Send 2 – Indicates Serial port 2 is ready to transmit data. Used as

hardware handshake with CTS2 for low level flow control.

68 PD5 Parallel Port Data 5 – Refer to pin-58 and 80 for more information.

69 DTR2* Data Terminal Ready 2 – Indicates Serial port 2 is powered, initialized, and

ready. Used as hardware handshake with DSR2 for overall readiness.

70 SLCTIN

Parallel Select In – This output signal is used to select the printer. I/O pin in

ECP/EPP mode.

STEP*

Floppy Step – Low pulse for each track-to-track movement of the head.