Page 1

cExpress-HL

User’s Manual

Manual Revision: 1.01

Revision Date: September 23, 2014

Part Number: 50-1J049-1010

Page 2

Revision History

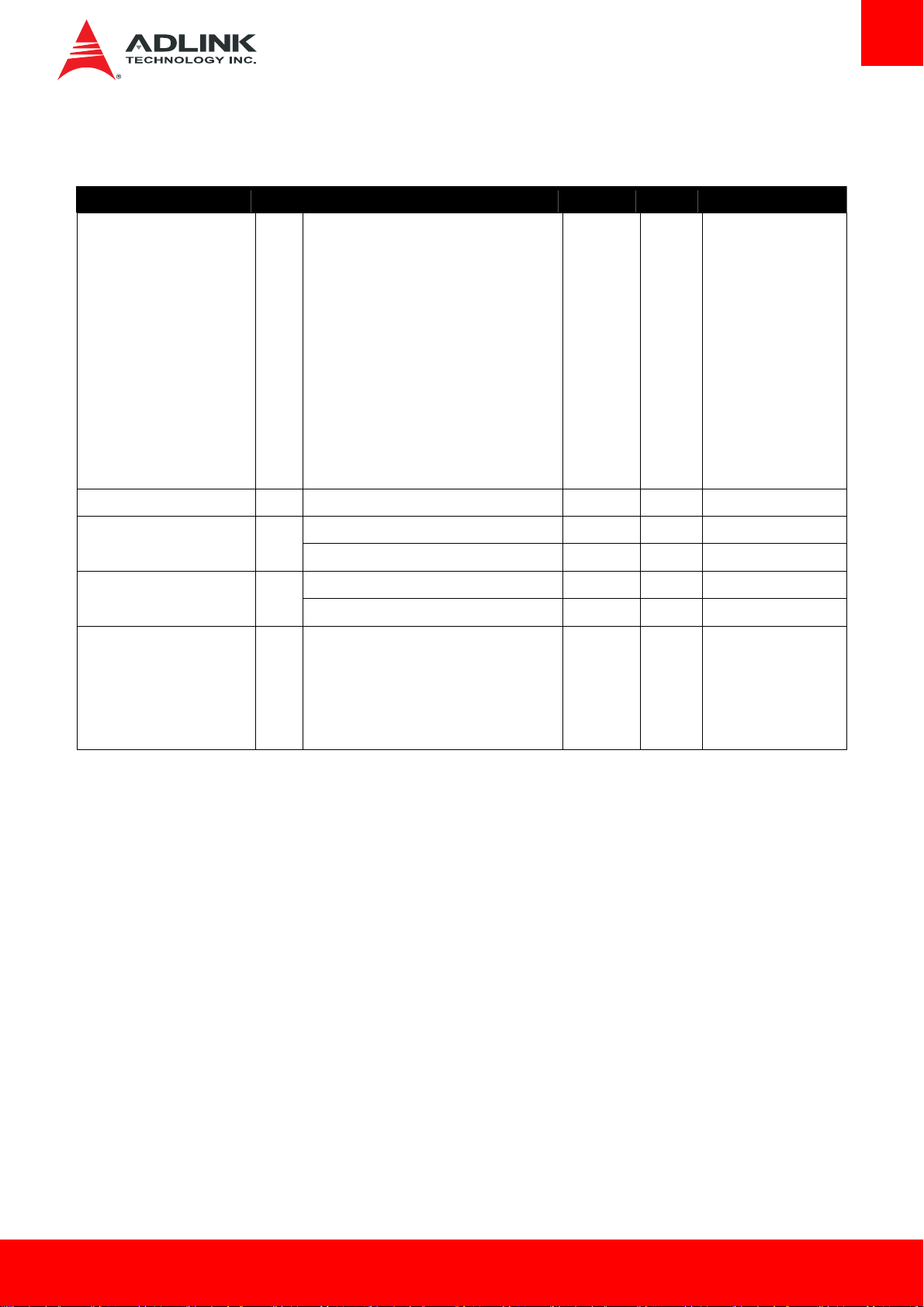

Revision Description Date By

1.00 Initial release 2014-07-28 JC

1.01 Add BIOS Checkpoints, Beep Codes; remove Industrial Temp. support 2014-09-23 JC

Page 2 cExpress-HL

Page 3

Preface

Copyright 2014 ADLINK Technology, Inc.

This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by

any mechanical, electronic, or other means in any form without prior written permission of the manufacturer.

Disclaimer

The information in this document is subject to change without prior notice in order to improve reliability, design, and function and does not

represent a commitment on the part of the manufacturer. In no event will the manufacturer be liable for direct, indirect, special, incidental, or

consequential damages arising out of the use or inability to use the product or documentation, even if advised of the possibility of such

damages.

Environmental Responsibility

ADLINK is committed to fulfill its social responsibility to global environmental preservation through compliance with the European Union's

Restriction of Hazardous Substances (RoHS) directive and Waste Electrical and Electronic Equipment (WEEE) directive. Environmental

protection is a top priority for ADLINK. We have enforced measures to ensure that our products, manufacturing processes, components, and

raw materials have as little impact on the environment as possible. When products are at their end of life, our customers are encouraged to

dispose of them in accordance with the product disposal and/or recovery programs prescribed by their nation or company.

Trademarks

Product names mentioned herein are used for identification purposes only and may be trademarks and/or registered trademarks of their

respective companies.

cExpress-HL Page 3

Page 4

Table of Contents

Revision History ............................................................................................................ 2

Preface............................................................................................................................ 3

1 Introduction............................................................................................................ 6

2 Specifications.......................................................................................................... 7

2.1 Core System ..................................................................................................................................7

2.2 Expansion Busses ..........................................................................................................................7

2.3 Video .............................................................................................................................................7

2.4 Audio.............................................................................................................................................8

2.5 LAN................................................................................................................................................8

2.6 Multi I/O and Storage ...................................................................................................................8

2.7 Serial I/O on Module.....................................................................................................................8

2.8 TPM (Trusted Platform Module)...................................................................................................8

2.9 SEMA Board Controller .................................................................................................................8

2.10 Debug ........................................................................................................................................8

2.11 Power Specifications .................................................................................................................9

2.12 Operating Temperatures...........................................................................................................9

2.13 Environmental .................................................................................................................. .........9

2.14 Specification Compliance ..........................................................................................................9

2.15 Operating Systems ....................................................................................................................9

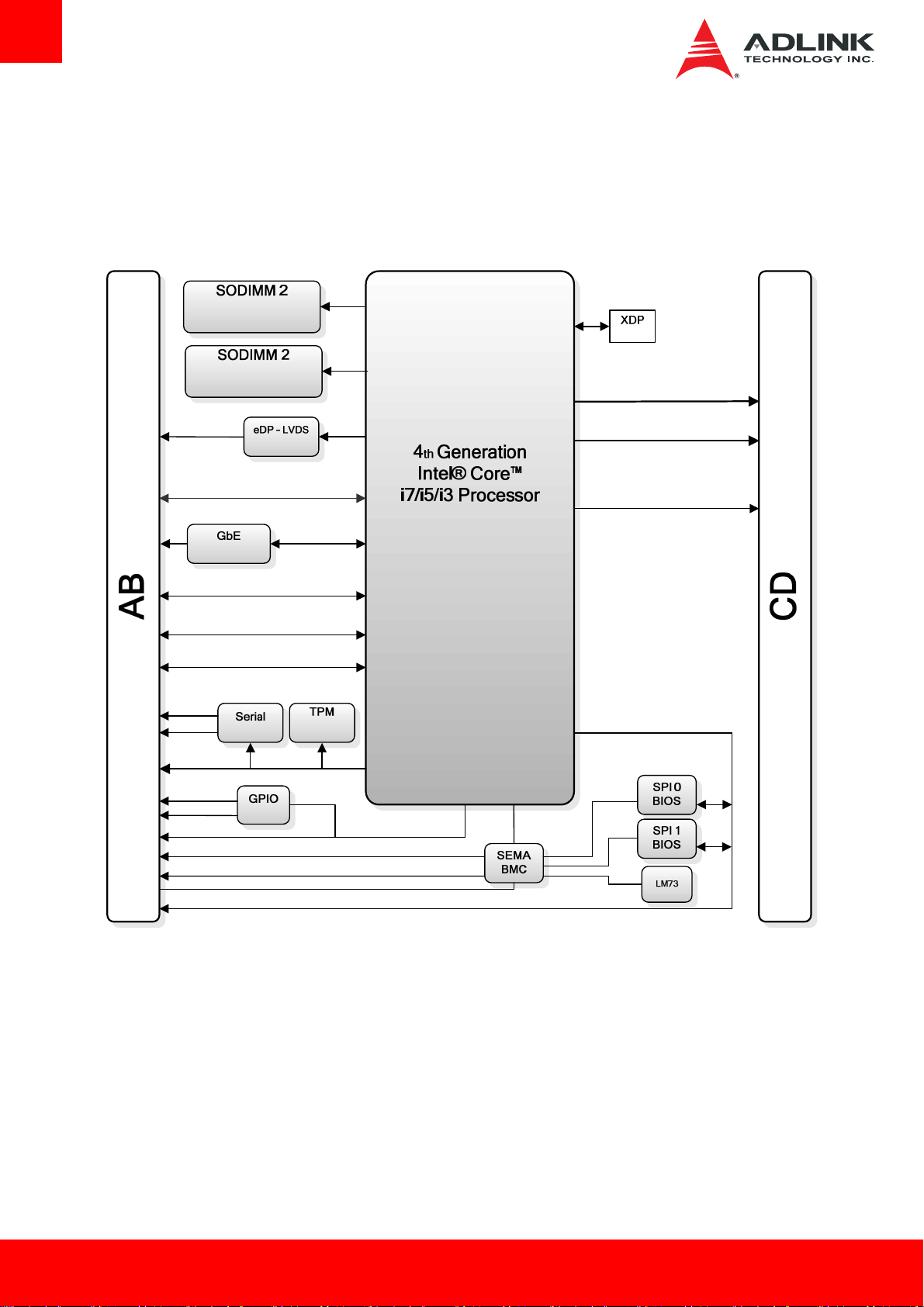

2.16 Functional Diagram ................................................................................................................ 10

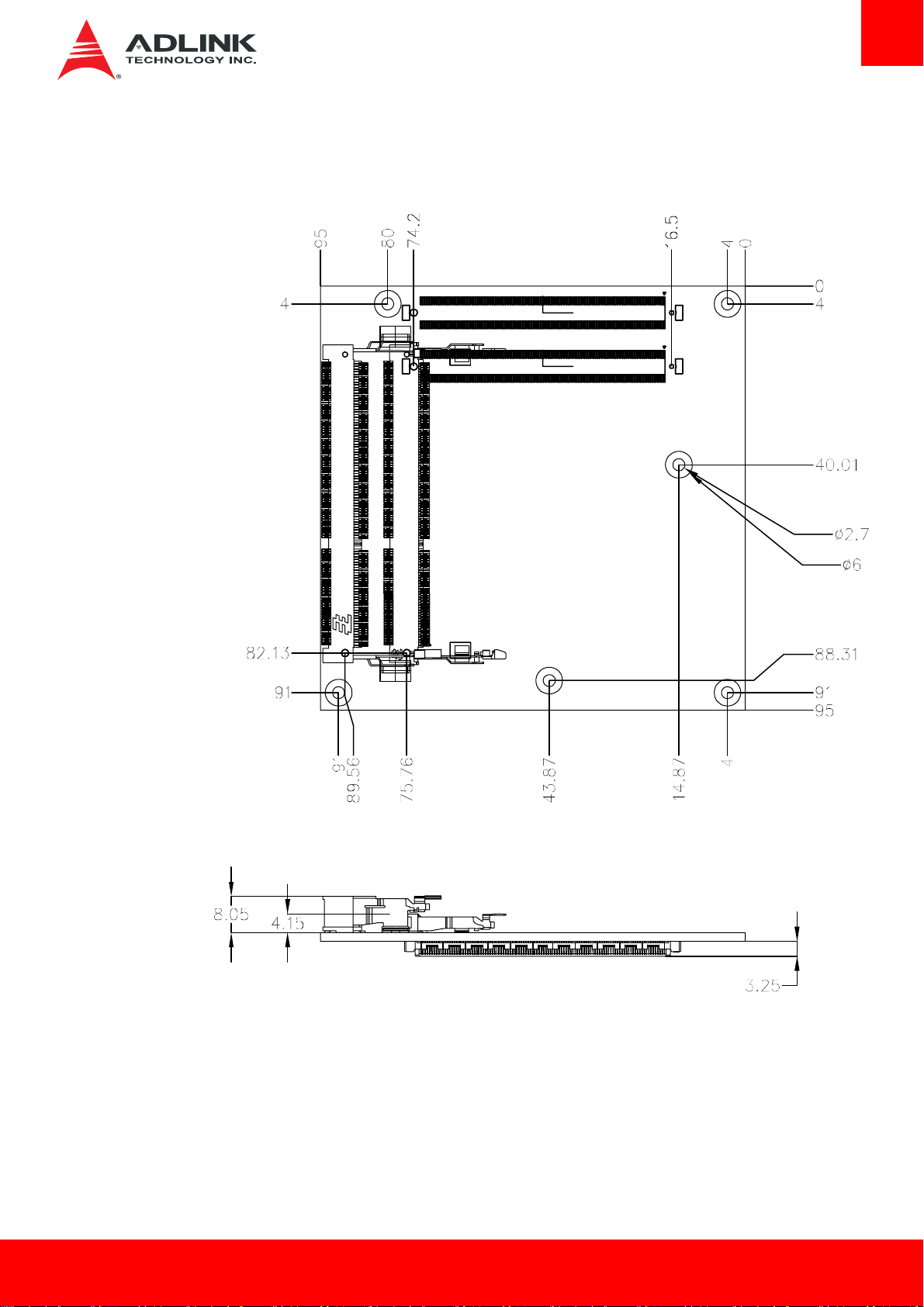

2.17 Mechanical Drawing............................................................................................................... 11

3 Pinouts and Signal Descriptions......................................................................... 12

3.1 AB / CD Pin Definitions............................................................................................................... 12

3.2 Signal Description Terminology ................................................................................................. 15

3.3 AB Signal Descriptions ............................................................................................................... 16

3.4 CD Signal Descriptions ............................................................................................................... 24

4 Connector Pinouts on Module............................................................................ 30

4.1 40-pin Debug Connector............................................................................................................ 31

4.2 Status LEDs................................................................................................................................. 33

4.3 XDP Debug header ..................................................................................................................... 34

4.4 Fan Connector............................................................................................................................ 35

4.5 BIOS Setup Defaults Reset Button ............................................................................................. 35

5 Smart Embedded Management Agent (SEMA) ................................................ 36

Page 4 cExpress-HL

Page 5

5.1 Board Specific SEMA Functions ................................................................................................. 37

6 System Resources................................................................................................. 39

6.1 System Memory Map................................................................................................................. 39

6.2 Direct Memory Access Channels ............................................................................................... 39

6.3 I/O Map...................................................................................................................................... 40

6.4 Interrupt Request (IRQ) Lines .................................................................................................... 42

6.5 PCI Configuration Space Map .................................................................................................... 44

6.6 PCI Interrupt Routing Map......................................................................................................... 45

7 BIOS Setup ............................................................................................................ 46

7.1 Menu Structure.......................................................................................................................... 46

7.2 Main ........................................................................................................................................... 47

7.3 Advanced ................................................................................................................................... 51

7.4 Boot............................................................................................................................................ 65

7.5 Security ...................................................................................................................................... 66

7.6 Save & Exit ................................................................................................................................. 67

8 BIOS Checkpoints, Beep Codes........................................................................... 68

8.1 Status Code Ranges.................................................................................................................... 69

8.2 Standard Status Codes ............................................................................................................... 69

8.3 OEM-Reserved Checkpoint Ranges............................................................................................ 75

9 Mechanical Information ...................................................................................... 76

9.1 Board-to-Board Connectors....................................................................................................... 76

9.2 Thermal Solution........................................................................................................................ 77

9.3 Mounting Methods .................................................................................................................... 79

9.4 Standoff Types ........................................................................................................................... 80

Safety Instructions ...................................................................................................... 81

Getting Service ............................................................................................................ 82

cExpress-HL Page 5

Page 6

1 Introduction

The cExpress-HL is a COM Express® COM.0 R2.1 Type 6 Compact size module supporting the 64-bit 4th Generation Intel® Core™ i7/i5/3

ULT Processors with CPU, memory controller, graphics processor and I/O hub on the same chip. Leveraging the benefits provided by the

Intel® Core™ i7/i5/3 ULT System-on-Chip, the cExpress-HL is specifically designed for customers who need optimum processing and

graphics performance with low power consumption in a long product life solution.

The cExpress-HL features the Intel® Core™ i7/i5/i3 processor supporting Intel® Hyper-Threading Technology (up to 2 cores, 4 threads) and

up to 16 GB of DDR3L dual-channel memory at 1333/1600 MHz in dual stacked SODIMM sockets to provide excellent overall performance.

Integrated Intel Generation 7.5 Graphics includes features such as OpenGL 3.1, DirectX 11, Intel® Clear Video HD Technology, Advanced

Scheduler 2.0, 1.0, XPDM support, and DirectX Video Acceleration (DXVA) support for full AVC/VC1/MPEG2 hardware decode. Graphics

outputs include dual-channel 18/24-bit LVDS and two DDI ports supporting HDMI / DVI / DisplayPort. The cExpress-HL is specifically

designed for customers with high-performance processing graphics requirements who want to outsource the custom core logic of their

systems for reduced development time.

The cExpress-HL features a single onboard Gigabit Ethernet port, two USB 3.0 ports and six USB 2.0 ports, and 4 SATA 6 Gb/s ports.

Support is provided for SMBus and I

such as remote console, CMOS backup, hardware monitor, and watchdog timer.

2

C. The module is equipped with SPI AMI EFI BIOS with CMOS backup, supporting embedded features

Page 6 cExpress-HL

Page 7

2 Specifications

2.1 Core System

¾ CPU: 4th Generation Intel® Core™ processor SoC (formerly "Haswell-ULT", Ultra Low TDP)

• Intel® Core™ i7-4650U 1.7 GHz (3.3 GHz Turbo), 15W (2C/GT3)

• Intel® Core™ i5-4300U 1.9 GHz (2.9 GHz Turbo), 15W (2C/GT2)

• Intel® Core™ i3-4010U 1.7 GHz (no Turbo) 3MB, 15W (2C/GT2)

• Intel® Celeron® 2980U 1.6 GHz (no Turbo), 15W (2C/HDG)

Supporting: Intel® VT, Intel® TXT, Intel® SSE4.2, Intel® HT Technology, Intel® 64 Architecture, Execute Disable Bit,

Intel® Turbo Boost Technology 2.0, Intel® AVX2, Intel® AES-NI, PCLMULQDQ Instruction, Intel® Secure Key and Intel® TSX

¾ L3 Cache: 4MB for Core™ i7-4650U, 3MB for Core™ i5-4300U and Core™ i3-4010U, 2MB for Celeron® 2980U

¾ Memory: Dual channel non-ECC 1600/1333 MHz DDR3L memory up to 16 GB in dual SODIMM socket

¾ BIOS: AMI EFI with CMOS backup in 8MB SPI BIOS with Intel® AMT 9.0 support

2.2 Expansion Busses

¾ 4 PCI Express x1 (AB): Lanes 0/1/2/3

¾ LPC bus, SMBus (system) , I

2

C (user)

2.3 Video

¾ Integrated in Processor: Intel® Generation 7.5 graphics core architecture

¾ GPU Feature Support:

• 3 independent and simultaneous display combinations of DisplayPort / HDMI / LVDS monitors

• Encode/transcode HD content

• Playback of high definition content including Blu-ray Disc

• Superior image quality with sharper, more colorful images

• Playback of Blu-ray disc S3D content using HDMI (1.4a spec compliant with 3D)

• DirectX Video Acceleration (DXVA) support for accelerating video processing

• Full AVC/VC1/MPEG2 HW decode

• Advanced Scheduler 2.0, 1.0, XPDM support

• Windows 8, Windows 7, OSX, Linux OS support

• DirectX 11

• Multi Display Support: 3 independent displays

¾ Display Types

• LVDS interface single/dual channel 18/24-bit LVDS through eDP (two lane) to LVDS Realtek RTD2136R

• Digital Display Ports x2

DDI1 supports DisplayPort / HDMI / DVI

DDI2 supports DisplayPort / HDMI / DVI

cExpress-HL Page 7

Page 8

2.4 Audio

¾ Integrated: Intel® HD Audio integrated in PCH QM87

¾ Codec: Realtek ALC886 on Express-BASE6

2.5 LAN

¾ Integrated: MAC integrated in SOC

¾ Intel PHY: Intel® Ethernet Controller i218LM

¾ Interface: 10/100/1000 GbE connection

2.6 Multi I/O and Storage

¾ Integrated: in SOC

¾ USB ports: 2 ports USB 3.0 (USB0,1) and 6 ports USB 2.0 (USB2,3,4,5,6,7)

¾ SATA ports: four ports SATA 6Gb/s

¾ GPIO: 4 GPO and 4 GPI with interrupt

2.7 Serial I/O on Module

¾ Chipset: Nuvoton NCT5104D

¾ Ports: two UARTs RX/TX only

¾ Console Redirection: selectable in BIOS over UART0 or UART1

2.8 TPM (Trusted Platform Module)

¾ Chipset: ATMELAT97SC3204

¾ Type: TPM 1.2

2.9 SEMA Board Controller

¾ Type: ADLINK Smart Embedded Management Agent (SEMA)

¾ Supports:

• Voltage/Current monitoring

• Power sequence debug support

• AT/ATX mode control

• Logistics and Forensic information

• Flat Panel Control

• General Purpose I2C

• Failsafe BIOS (dual BIOS )

• Watchdog Timer and Fan Control

2.10 Debug

¾ 40-pin flat cable connector to be used with DB-40 debug module

Supports: BIOS POST code LED, BMC access, SPI BIOS flashing, power testpoints, debug LEDs

¾ 60-pin XDP header for ICE debug of CPU/chipset

Page 8 cExpress-HL

Page 9

2.11 Power Specifications

¾ Power Modes: AT and ATX mode (AT mode start controlled by SMC)

¾ Standard Voltage Input: ATX = 12V±5% / 5Vsb ±5% or AT = 12V±5%

¾ Wide Voltage Input: ATX = 5~20 V / 5Vsb ±5% or AT = 5 ~20V

¾ Power Management: ACPI 4.0 compliant, Smart Battery support

¾ Power States: supporting C1-C6, S0, S1, S4, S3, S5 (Wake-on-USB S3/S4, WoL S3/S4/S5)

¾ ECO mode supports deep S5 (ECO mode)

2.12 Operating Temperatures

¾ Standard Operating Temperature: 0°C to +60°C (Wide Voltage Input)

¾ Extreme Rugged™ Operating Temperature (optional): -40°C to +85°C (Standard Voltage Input)

2.13 Environmental

¾ Humidity: 5-90% RH operating, non-condensing

5-95% RH storage (and operating with conformal coating).

¾ Shock and Vibration: IEC 60068-2-64 and IEC-60068-2-27

MIL-STD-202F, Method 213B, Table 213-I, Condition A and Method 214A, Table 214-I, Condition D

¾ HALT: Thermal Stress, Vibration Stress, Thermal Shock and Combined Test

2.14 Specification Compliance

¾ PICMG COM.0: Rev 2.1 Type 6, Basic size 125 x 95 mm

2.15 Operating Systems

¾ Standard Support: Windows 7/8 32/64-bit, Linux 32/64-bit

¾ Extended Support (BSP): WEC7/8, Linux , VxWorks

cExpress-HL Page 9

Page 10

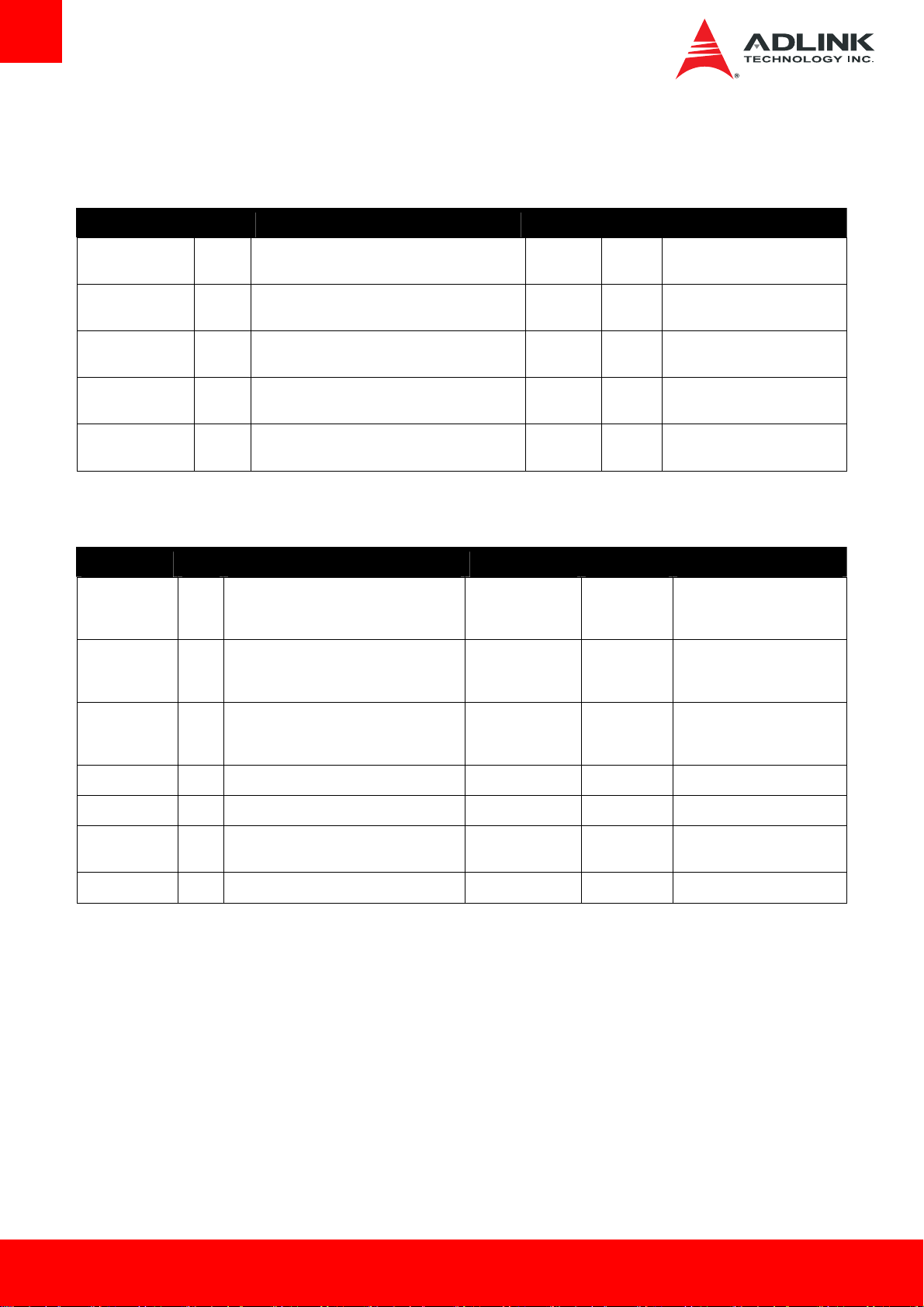

2.16 Functional Diagram

1333/1600 MHz

1~8 GB DDR3L

1333/1600 MHz

1~8 GB DDR3L

single/dual

18/24-bit LVDS

RTD2136R

2 lanes

eDP

60-pin

(

p

o

r

t

B

I

D

D

0

I / D

M

D

/ H

P

D

DDI 1 (port C)

DP / HDMI / DVI

)

I

V

4x PCIe x1 (Gen2)

i217LM

UART0

UART1

4x GP0

4x GPI

SMBus

(ports 0~3)

4x SATA 6 Gb/s

(ports 0/1/2/3)

6x USB 2.0

(ports 2~7)

HD Audio

NCT5104D

LPC bus

PCA9535

GP I2C

DDC I2C

PCIe x1

(port 4)

ATMEL

AT97SC3204

SPI_CS#

SPI

SoC

“Haswell-ULT”

SPI_CS0

SPI_CS1

2x USB 3.0 upgrade

(ports 0/1)

Page 10 cExpress-HL

Page 11

2.17 Mechanical Drawing

connectors on bottom side

Top View

Side View

All tolerances ± 0.05 mm

Other tolerances ± 0.2 mm

cExpress-HL Page 11

Page 12

3 Pinouts and Signal Descriptions

3.1 AB / CD Pin Definitions

The cExpress-HL is a Type 6 module supporting USB 3.0 and DDI channels on the CD connector

All pins in the COM Express specification are described, including those not supported on the cExpress-HL. Those not supported on the

cExpress-HL module are crossed out

Row A Row B Row C Row D

Pin Name Pin Name Pin Name Pin Name

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

GND (FIXED)

GBE0_MDI3GBE0_MDI3+

GBE0_LINK100#

GBE0_LINK1000#

GBE0_MDI2GBE0_MDI2+

GBE0_LINK#

GBE0_MDI1GBE0_MDI1+

GND (FIXED)

GBE0_MDI0GBE0_MDI0+

GBE0_CTREF

SUS_S3#

SATA0_TX+

SATA0_TX-

SUS_S4#

SATA0_RX+

SATA0_RXGND (FIXED)

SATA2_TX+

SATA2_TX-

SUS_S5#

SATA2_RX+

SATA2_RX-

BATLOW#

(S)ATA_ACT#

AC/HDA_SYNC

AC/HDA_RST#

GND (FIXED)

AC/HDA_BITCLK

AC/HDA_SDOUT

BIOS_DIS0#

THRMTRIP#

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

GND (FIXED)

GBE0_ACT#

LPC_FRAME#

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_DRQ0#

LPC_DRQ1#

LPC_CLK

GND (FIXED)

PWRBTN#

SMB_CK

SMB_DAT

SMB_ALERT#

SATA1_TX+

SATA1_TX-

SUS_STAT#

SATA1_RX+

SATA1_RXGND (FIXED)

SATA3_TX+

SATA3_TX-

PWR_OK

SATA3_RX+

SATA3_RX-

WDT

AC/HDA_SDIN2

AC/HDA_SDIN1

AC/HDA_SDIN0

GND (FIXED)

SPKR

I2C_CK

I2C_DAT

THRM#

C1

C2

C3

C4

C5

C6

C7

C8

C9

C10

C11

C12

C13

C14

C15

C16

C17

C18

C19

C20

C21

C22

C23

C24

C25

C26

C27

C28

C29

C30

C31

C32

C33

C34

C35

GND FIXED)

GND

USB_SSRX0USB_SSRX0+

GND

USB_SSRX1USB_SSRX1+

GND

USB_SSRX2USB_SSRX2+

GND (FIXED)

USB_SSRX3USB_SSRX3+

GND

DDI1_PAIR6+

DDI1_PAIR6RSVD

RSVD

PCIE_RX6+

PCIE_RX6GND (FIXED)

PCIE_RX7+

PCIE_RX7DDI1_HPD

DDI1_PAIR4+

DDI1_PAIR4RSVD

RSVD

DDI1_PAIR5+

DDI1_PAIR5GND (FIXED)

DDI2_CTRLCLK_AUX+

DDI2_CTRLDATA_AUXDDI2_DDC_AUX_SEL

RSVD

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

GND FIXED)

GND

USB_SSTX0USB_SSTX0+

GND

USB_SSTX1USB_SSTX1+

GND

USB_SSTX2USB_SSTX2+

GND (FIXED)

USB_SSTX3USB_SSTX3+

GND

DDI1_CTRLCLK_AUX+

DDI1_CTRLDATA_AUX

RSVD

RSVD

PCIE_TX6+

PCIE_TX6GND (FIXED)

PCIE_TX7+

PCIE_TX7RSVD

RSVD

DDI1_PAIR0+

DDI1_PAIR0RSVD

DDI1_PAIR1+

DDI1_PAIR1GND (FIXED)

DDI1_PAIR2+

DDI1_PAIR2-

DDI1_DDC_AUX_SEL

RSVD

Page 12 cExpress-HL

Page 13

Row A Row B Row C Row D

Pin Name Pin Name Pin Name Pin Name

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

USB6USB6+

USB_6_7_OC#

USB4USB4+

GND (FIXED)

USB2USB2+

USB_2_3_OC#

USB0USB0+

VCC_RTC

EXCD0_PERST#

EXCD0_CPPE#

LPC_SERIRQ

GND (FIXED)

PCIE_TX5+

PCIE_TX5-

GPI0

PCIE_TX4+

PCIE_TX4GND

PCIE_TX3+

PCIE_TX3GND (FIXED)

PCIE_TX2+

PCIE_TX2GPI1

PCIE_TX1+

PCIE_TX1GND

GPI2

PCIE_TX0+

PCIE_TX0GND (FIXED)

LVDS_A0+

LVDS_A0LVDS_A1+

LVDS_A1LVDS_A2+

LVDS_A2LVDS_VDD_EN

LVDS_A3+

LVDS_A3GND (FIXED)

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

USB7USB7+

USB_4_5_OC#

USB5USB5+

GND (FIXED)

USB3USB3+

USB_0_1_OC#

USB1USB1+

EXCD1_PERST#

EXCD1_CPPE#

SYS_RESET#

CB_RESET#

GND (FIXED)

PCIE_RX5+

PCIE_RX5-

GPO1

PCIE_RX4+

PCIE_RX4GPO2

PCIE_RX3+

PCIE_RX3GND (FIXED)

PCIE_RX2+

PCIE_RX2GPO3

PCIE_RX1+

PCIE_RX1-

WAKE0#

WAKE1#

PCIE_RX0+

PCIE_RX0GND (FIXED)

LVDS_B0+

LVDS_B0LVDS_B1+

LVDS_B1LVDS_B2+

LVDS_B2LVDS_B3+

LVDS_B3LVDS_BKLT_EN

GND (FIXED)

C36

C37

C38

C39

C40

C41

C42

C43

C44

C45

C46

C47

C48

C49

C50

C51

C52

C53

C54

C55

C56

C57

C58

C59

C60

C61

C62

C63

C64

C65

C66

C67

C68

C69

C70

C71

C72

C73

C74

C75

C76

C77

C78

C79

C80

DDI3_CTRLCLK_AUX+

DDI3_CTRLDATA_AUXDDI3_DDC_AUX_SEL

DDI3_PAIR0+

DDI3_PAIR0GND (FIXED)

DDI3_PAIR1+

DDI3_PAIR1DDI3_HPD

RSVD

DDI3_PAIR2+

DDI3_PAIR2RSVD

DDI3_PAIR3+

DDI3_PAIR3GND (FIXED)

PEG_RX0+

PEG_RX0-

TYPE0#

PEG_RX1+

PEG_RX1-

TYPE1#

PEG_RX2+

PEG_RX2GND (FIXED)

PEG_RX3+

PEG_RX3RSVD

RSVD

PEG_RX4+

PEG_RX4RSVD

PEG_RX5+

PEG_RX5GND (FIXED)

PEG_RX6+

PEG_RX6GND

PEG_RX7+

PEG_RX7GND

RSVD

PEG_RX8+

PEG_RX8GND (FIXED)

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

D64

D65

D66

D67

D68

D69

D70

D71

D72

D73

D74

D75

D76

D77

D78

D79

D80

DDI1_PAIR3+

DDI1_PAIR3RSVD

DDI2_PAIR0+

DDI2_PAIR0GND (FIXED)

DDI2_PAIR1+

DDI2_PAIR1DDI2_HPD

RSVD

DDI2_PAIR2+

DDI2_PAIR2RSVD

DDI2_PAIR3+

DDI2_PAIR3GND (FIXED)

PEG_TX0+

PEG_TX0-

PEG_LANE_RV#

PEG_TX1+

PEG_TX1-

TYPE2#

PEG_TX2+

PEG_TX2GND (FIXED)

PEG_TX3+

PEG_TX3RSVD

RSVD

PEG_TX4+

PEG_TX4GND

PEG_TX5+

PEG_TX5GND (FIXED)

PEG_TX6+

PEG_TX6GND

PEG_TX7+

PEG_TX7GND

RSVD

PEG_TX8+

PEG_TX8GND (FIXED)

cExpress-HL Page 13

Page 14

Row A Row B Row C Row D

Pin Name Pin Name Pin Name Pin Name

A81

A82

A83

A84

A85

A86

A87

A88

A89

A90

A91

A92

A93

A94

A95

A96

A97

A98

A99

A100

A101

A102

A103

A104

A105

A106

A107

A108

A109

A110

LVDS_A_CK+

LVDS_A_CKLVDS_I2C_CK

LVDS_I2C_DAT

GPI3

RSVD

RSVD

PCIE0_CK_REF+

PCIE0_CK_REF-

GND (FIXED)

SPI_POWER

SPI_MISO

GPO0

SPI_CLK

SPI_MOSI

TPM_PP

TYPE10#

SER0_TX

SER0_RX

GND (FIXED)

SER1_TX

SER1_RX

LID#

VCC_12V

VCC_12V

VCC_12V

VCC_12V

VCC_12V

VCC_12V

GND (FIXED)

B81

B82

B83

B84

B85

B86

B87

B88

B89

B90

B91

B92

B93

B94

B95

B96

B97

B98

B99

B100

B101

B102

B103

B104

B105

B106

B107

B108

B109

B110

LVDS_B_CK+

LVDS_B_CKLVDS_BKLT_CTRL

VCC_5V_SBY

VCC_5V_SBY

VCC_5V_SBY

VCC_5V_SBY

BIOS_DIS1#

VGA_RED

GND (FIXED)

VGA_GRN

VGA_BLU

VGA_HSYNC

VGA_VSYNC

VGA_I2C_CK

VGA_I2C_DAT

SPI_CS#

RSVD

RSVD

GND (FIXED)

FAN_PWMOUT

FAN_TACHIN

SLEEP#

VCC_12V

VCC_12V

VCC_12V

VCC_12V

VCC_12V

VCC_12V

GND (FIXED)

C81

C82

C83

C84

C85

C86

C87

C88

C89

C90

C91

C92

C93

C94

C95

C96

C97

C98

C99

C100

C101

C102

C103

C104

C105

C106

C107

C108

C109

C110

PEG_RX9+

PEG_RX9-

TPM_PP

GND

PEG_RX10+

PEG_RX10GND

PEG_RX11+

PEG_RX11GND (FIXED)

PEG_RX12+

PEG_RX12GND

PEG_RX13+

PEG_RX13GND

RSVD

PEG_RX14+

PEG_RX14GND (FIXED)

PEG_RX15+

PEG_RX15GND

VCC_12V

VCC_12V

VCC_12V

VCC_12V

VCC_12V

VCC_12V

GND (FIXED)

D81

D82

D83

D84

D85

D86

D87

D88

D89

D90

D91

D92

D93

D94

D95

D96

D97

D98

D99

D100

D101

D102

D103

D104

D105

D106

D107

D108

D109

D110

PEG_TX9+

PEG_TX9RSVD

GND

PEG_TX10+

PEG_TX10GND

PEG_TX11+

PEG_TX11GND (FIXED)

PEG_TX12+

PEG_TX12GND

PEG_TX13+

PEG_TX13GND

RSVD

PEG_TX14+

PEG_TX14GND (FIXED)

PEG_TX15+

PEG_TX15GND

VCC_12V

VCC_12V

VCC_12V

VCC_12V

VCC_12V

VCC_12V

GND (FIXED)

Page 14 cExpress-HL

Page 15

3.2 Signal Description Terminology

The following terms are used in the COM Express AB/CD Signal Descriptions below.

I Input to the Module

O Output from the Module

I/O Bi-directional input / output signal

OD Open drain output

I 3.3V Input 3.3V tolerant

I 5V Input 5V tolerant

O 3.3V Output 3.3V signal level

O 5V Output 5V signal level

I/O 3.3V Bi-directional signal 3.3V tolerant

I/O 5V Bi-directional signal 5V tolerant

I/O 3.3Vsb Input 3.3V tolerant active in standby state

P Power Input/Output

REF Reference voltage output that may be sourced from a module power plane.

PDS Pull-down strap. This is an output pin on the module that is either tied to GND or not connected.

The signal is used to indicate the PICMG module type to the Carrier Board.

PU ADLINK implemented pull-up resistor on module

PD ADLINK implemented pull-down resistor on module

cExpress-HL Page 15

Page 16

3.3 AB Signal Descriptions

3.3.1 Audio Signals

Signal Pin # Description I/O PU/PD Comment

AC_RST# /

HDA_RST#

AC_SYNC /

HDA_SYNC

AC_BITCLK /

HDA_BITCLK

AC _SDOUT /

HDA_SDOUT

AC _SDIN[2:0]

HDA_SDIN[2:0]

A30 Reset output to codec, active low. O 3.3VSB VSB because PCH uses suspend

power for RESET

A29 Sample-synchronization signal to the codec(s). O 3.3V

A32 Serial data clock generated by the external

codec(s).

A33 Serial TDM data output to the codec. O 3.3V

B28

B30

Serial TDM data inputs from up to 3 codecs. I/O 3.3V

I/O 3.3V

3.3.2 Analog VGA

Signal Pin # Description I/O PU/PD Comment

VGA_RED B89 Red for monitor.

Analog DAC output, designed to drive a

37.5-Ohm equivalent load.

VGA_GRN B91 Green for monitor

Analog DAC output, designed to drive a

37.5-Ohm equivalent load.

O Analog

O Analog

Not supported

Not supported

VGA_BLU B92 Blue for monitor.

Analog DAC output, designed to drive a

37.5-Ohm equivalent load.

VGA_HSYNC B93 Horizontal sync output to VGA monitor O 3.3V Not supported

VGA_VSYNC B94 Vertical sync output to VGA monitor O 3.3V Not supported

VGA_I2C_CK B95 DDC clock line (I²C port dedicated to identify

VGA monitor capabilities)

VGA_I2C_DAT B96 DDC data line. I/O OD 3.3V Not supported

O Analog

I/O OD 3.3V Not supported

Not supported

Page 16 cExpress-HL

Page 17

3.3.3 LVDS

Signal Pin # Description I/O PU/PD Comment

LVDS_A0+

LVDS_A0-

LVDS_A1+

LVDS_A1-

LVDS_A2+

LVDS_A2-

LVDS_A3+

LVDS_A3-

LVDS_A_CK+

LVDS_A_CK-

LVDS_B0+

LVDS_B0-

LVDS_B1+

LVDS_B1-

LVDS_B2+

LVDS_B2-

LVDS_B3+

LVDS_B3-

LVDS_B_CK+

LVDS_B_CK-

LVDS_VDD_EN A77 LVDS panel power enable O 3.3V

LVDS_BKLT_EN B79 LVDS panel backlight enable O 3.3V

LVDS_BKLT_CTRL B83 LVDS panel backlight brightness control O 3.3V PD 100K

A71

A72

A73

A74

A75

A76

A78

A79

A81

A82

B71

B72

B73

B74

B75

B76

B77

B78

B81

B82

LVDS Channel A differential pairs O LVDS

LVDS Channel A differential clock O LVDS

LVDS Channel B differential pairs O LVDS

LVDS Channel B differential clock O LVDS

Realtek ePD to LVDS

requirement

LVDS_I2C_CK A83 DDC lines used for flat panel detection and control. O 3.3V PU 2k2 3.3V

LVDS_I2C_DAT A84 DDC lines used for flat panel detection and control. I/O 3.3V PU 2k2 3.3V

3.3.4 Gigabit Ethernet

Gigabit Ethernet Pin # Description I/O PU/PD Comment

GBE0_MDI0+

GBE0_MDI0-

GBE0_MDI1+

GBE0_MDI1-

GBE0_MDI2+

GBE0_MDI2-

GBE0_MDI3+

GBE0_MDI3-

GBE0_ACT# B2 Gigabit Ethernet Controller 0 activity indicator, active low. O 3.3VSB PU 10k

GBE0_LINK# A8 Gigabit Ethernet Controller 0 link indicator, active low. O 3.3VSB

GBE0_LINK100# A4 Gigabit Ethernet Controller 0 100Mbit/sec link indicator, active low. O 3.3VSB

GBE0_LINK1000# A5 Gigabit Ethernet Controller 0 1000Mbit/sec link indicator, active low. O 3.3VSB

GBE0_CTREF A14 Reference voltage for Carrier Board Ethernet channel 1 and 2 magnetics

A13

A12

A10

A9

A7

A6

A3

A2

Gigabit Ethernet Controller 0: Media Dependent Interface Differential Pairs

0, 1, 2, 3. The MDI can operate in 1000, 100, and 10Mbit/sec modes.

Some pairs are unused in some modes according to the following:

1000BASE-T 100BASE-TX 10BASE-T

MDI[0]+/- B1_DA+/- TX+/- TX+/-

MDI[1]+/- B1_DB+/- RX+/- RX+/-

MDI[2]+/- B1_DC+/MDI[3]+/- B1_DD+/-

center tap. The reference voltage is determined by the requirements of the

Module PHY and may be as low as 0V and as high as 3.3V. The reference

voltage output shall be current limited on the Module. In the case in which

the reference is shorted to ground, the current shall be 250 mA or less.

I/O Analog Twisted pair

signals for

external

transformer.

3.3VSB

GND min

3.3V max

cExpress-HL Page 17

Page 18

3.3.5 Serial ATA

Signal Pin # Description I/O PU/PD Comment

SATA0_TX+

SATA0_TX-

SATA0_RX+

SATA0_RX-

SATA1_TX+

SATA1_TX-

SATA1_RX+

SATA1_RX-

SATA2_TX+

SATA2_TX-

SATA2_RX+

SATA2_RX-

SATA3_TX+

SATA3_TX-

SATA3_RX+

SATA3_RX-

(S)ATA_ACT# A28 ATA (parallel and serial) or SAS activity

A16

Serial ATA channel 0, Transmit Output

A17

differential pair.

A19

Serial ATA channel 0, Receive Input

A20

differential pair.

B16

Serial ATA channel 1, Transmit Output

B17

differential pair.

B19

Serial ATA channel 1, Receive Input

B20

differential pair.

A22

Serial ATA channel 2, Transmit Output

A23

differential pair.

A25

Serial ATA channel 2, Receive Input

A26

differential pair.

B22

Serial ATA channel 3, Transmit Output

B23

differential pair.

B25

Serial ATA channel 3, Receive Input

B26

differential pair.

indicator, active low.

O SATA AC coupled on Module

I SATA AC coupled on Module

O SATA AC coupled on Module

I SATA AC coupled on Module

O SATA AC coupled on Module

I SATA AC coupled on Module

O SATA AC coupled on Module

I SATA AC coupled on Module

O 3.3V

3.3.6 PCI Express

Signal Pin # Description I/O PU/PD Comment

PCIE_TX0+

PCIE_TX0-

PCIE_RX0+

PCIE_RX0-

PCIE_TX1+

PCIE_TX1-

PCIE_RX1+

PCIE_RX1-

PCIE_TX2+

PCIE_TX2-

PCIE_RX2+

PCIE_RX2-

PCIE_TX3+

PCIE_TX3-

PCIE_RX3+

PCIE_RX3-

PCIE_TX4+

PCIE_TX4-

A68

A69

B68

B69

A64

A65

B64

B65

A61

A62

B61

B62

A58

A59

B58

B59

A55

A56

PCI Express channel 0, Transmit Output differential

pair.

PCI Express channel 0, Receive Input differential

pair.

PCI Express channel 1, Transmit Output differential

pair.

PCI Express channel 1, Receive Input differential

pair.

PCI Express channel 2, Transmit Output differential

pair.

PCI Express channel 2, Receive Input differential

pair.

PCI Express channel 3, Transmit Output differential

pair.

PCI Express channel 3, Receive Input differential

pair.

PCI Express channel 4, Transmit Output differential

pair.

O PCIE AC coupled on Module

I PCIE AC coupled off Module

O PCIE AC coupled on Module

I PCIE AC coupled off Module

O PCIE AC coupled on Module

I PCIE AC coupled off Module

O PCIE AC coupled on Module

I PCIE AC coupled off Module

O PCIE Connected to LAN

PCIE_RX4+

PCIE_RX4-

PCIE_TX5+

PCIE_TX5-

B55

B56

A52

A53

PCI Express channel 4, Receive Input differential

pair.

PCI Express channel 5, Transmit Output differential

pair.

I PCIE Connected to LAN

O PCIE Not supported

Page 18 cExpress-HL

Page 19

Signal Pin # Description I/O PU/PD Comment

PCIE_RX5+

PCIE_RX5-

PCIE_CLK_REF+

PCIE_CLK_REF-

B52

B53

A88

A89

PCI Express channel 5, Receive Input differential

pair.

PCI Express Reference Clock output for all PCI

Express and PCI Express Graphics Lanes.

I PCIE Not supported

O PCIE

3.3.7 Express Card

Signal Pin # Description I/O PU/PD Comment

EXCD0_CPPE#

EXCD1_CPPE#

EXCD0_PERST#

EXCD1_PERST#

A49

B48

A48

B47

PCI ExpressCard: PCI Express capable card request I 3.3V PU 10k 3.3V

PCI ExpressCard: reset O 3.3V

3.3.8 LPC Bus

Signal Pin # Description I/O PU/PD Comment

LPC_AD[0:3] B4-B7 LPC multiplexed address, command and data bus I/O 3.3V

LPC_FRAME# B3 LPC frame indicates the start of an LPC cycle O 3.3V

LPC_DRQ0#

LPC_DRQ1#

B8

B9

LPC serial DMA request I 3.3V

LPC_SERIRQ A50 LPC serial interrupt I/O OD 3.3V PU 8k2 3.3V

LPC_CLK B10 LPC clock output - 33MHz nominal O 3.3V

3.3.9 USB

Signal Pin # Description I/O PU/PD Comment

USB0+

USB0-

USB1+

USB1-

USB2+

USB2-

USB3+

USB3-

USB4+

USB4-

USB5+

USB5-

USB6+

USB6-

A46

USB differential data pairs for Port 0 I/O 3.3VSB USB 1.1/ 2.0 compliant

A45

B46

USB differential data pairs for Port 1 I/O 3.3VSB USB 1.1/ 2.0 compliant

B45

A43

USB differential data pairs for Port 1 I/O 3.3VSB USB 1.1/ 2.0 compliant

A42

B43

USB differential data pairs for Port 2 I/O 3.3VSB USB 1.1/ 2.0 compliant

B42

A40

USB differential data pairs for Port 3 I/O 3.3VSB USB 1.1/ 2.0 compliant

A39

B40

USB differential data pairs for Port 4 I/O 3.3VSB USB 1.1/ 2.0 compliant

B39

A37

USB differential data pairs for Port 5 I/O 3.3VSB USB 1.1/ 2.0 compliant

A36

USB7+

USB7-

USB_0_1_OC# B44 USB over-current sense, USB ports 0 and 1. A pull-up

B37

USB differential data pairs for Port 6 I/O 3.3VSB USB 1.1/ 2.0 compliant

B37

I 3.3VSB PU 10k 3.3VSB Do not pull high on

for this line shall be present on the module. An open

drain driver from a USB current monitor on the carrier

board may drive this line low.

carrier

cExpress-HL Page 19

Page 20

Signal Pin # Description I/O PU/PD Comment

USB_2_3_OC# A44 USB over-current sense, USB ports 2 and 3. A pull-up

for this line shall be present on the module. An open

drain driver from a USB current monitor on the carrier

board may drive this line low. .

USB_4_5_OC# B38 USB over-current sense, USB ports 4 and 5. A pull-up

for this line shall be present on the module. An open

drain driver from a USB current monitor on the carrier

board may drive this line low.

USB_6_7_OC# A38 USB over-current sense, USB ports 6 and 7. A pull-up

for this line shall be present on the module. An open

drain driver from a USB current monitor on the carrier

board may drive this line low.

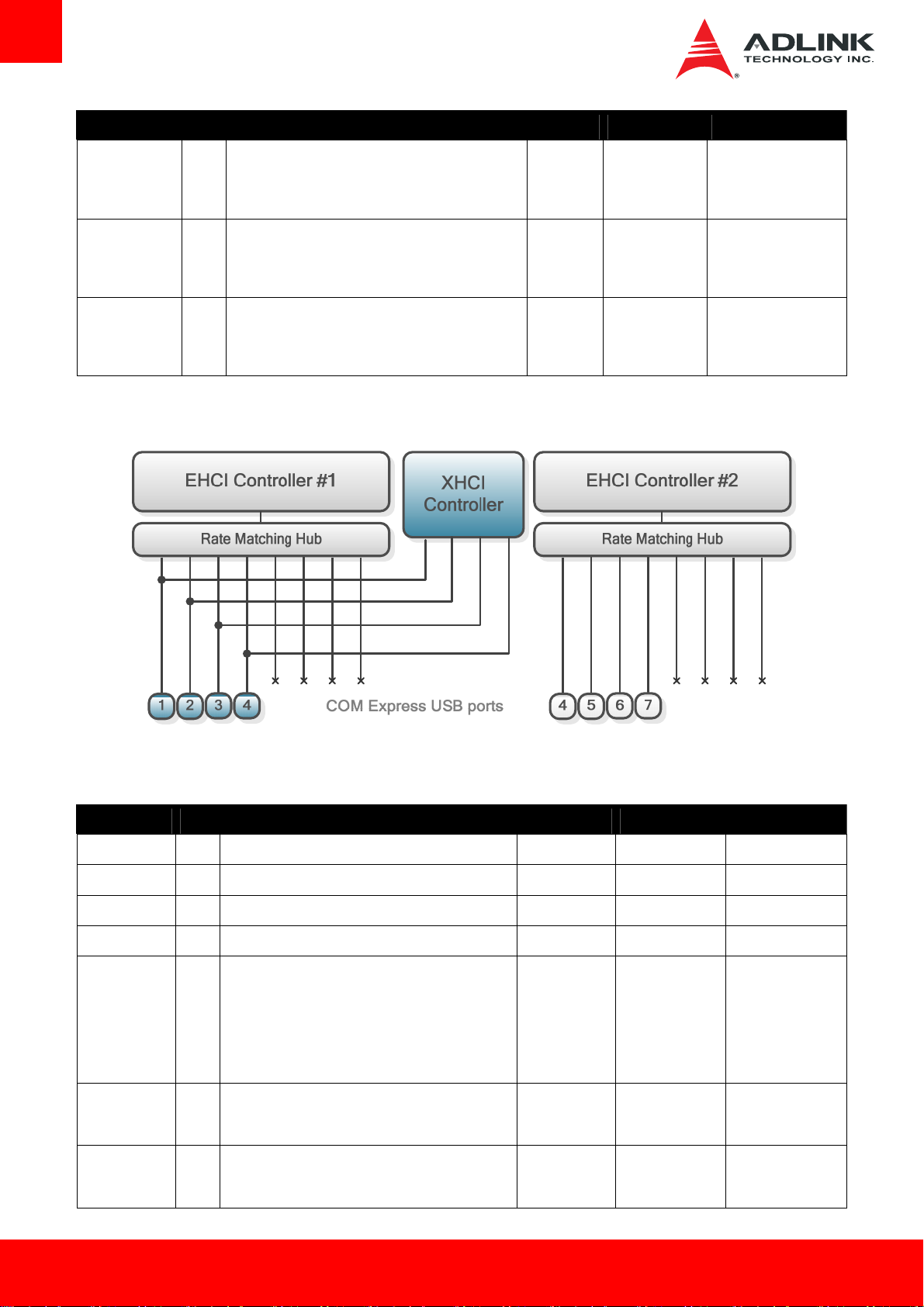

3.3.10 USB Root Segmentation

I 3.3VSB PU 10k 3.3VSB Do not pull high on

carrier

I 3.3VSB PU 10k 3.3VSB Do not pull high on

carrier

I 3.3VSB PU 10k 3.3VSB Do not pull high on

carrier

3.3.11 SPI (BIOS only)

Signal Pin # Description I/O PU/PD Comment

SPI_CS# B97 Chip select for Carrier Board SPI BIOS Flash. O 3.3VSB

SPI_MISO A92 Data in to module from carrier board SPI BIOS flash. I 3.3VSB

SPI_MOSI A95 Data out from module to carrier board SPI BIOS flash. O 3.3VSB

SPI_CLK A94 Clock from module to carrier board SPI BIOS flash. O 3.3VSB

SPI_POWER A91 Power supply for Carrier Board SPI – sourced from

Module – nominally 3.3V.

The Module shall provide a minimum of 100mA on

SPI_POWER.

Carriers shall use less than 100mA of SPI_POWER.

SPI_POWER shall only be used to power SPI devices

on the Carrier

BIOS_DIS0# A34 Selection strap to determine the BIOS boot device. I PU 10K 3.3V Carrier shall pull to

BIOS_DIS1# B88 Selection strap to determine the BIOS boot device. I PU 10K 3.3V Carrier shall pull to

O P 3.3VSB

GND or leave noconnect.

GND or leave noconnect

Page 20 cExpress-HL

Page 21

3.3.12 Miscellaneous

Signal Pin # Description I/O PU/PD Comment

SPKR B32 Output for audio enunciator, the “speaker” in PC-AT

systems

WDT B27 Output indicating that a watchdog time-out event has

occurred.

THRM# B35 Input from off-module temp sensor indicating an over-

temp situation.

THERMTRIP# A35 Active low output indicating that the CPU has entered

thermal shutdown.

FAN_PWMOUT B101 Fan speed control. Uses the Pulse Width Modulation

(PWM) technique to control the fan’s RPM.

FAN_TACHIN11 B102 Fan tachometer input for a fan with a two pulse output. I OD 3.3V PU 10k 3.3V

TPM_PP11 C83 Trusted Platform Module (TPM) Physical Presence pin.

Active high. TPM chip has an internal pull down. This

signal is used to indicate Physical Presence to the

TPM.

O 3.3V

O 3.3V

I 3.3V

O 3.3V PU 330 3.3V

O OD 3.3V

I 3.3V

PD 10k 3.3V

PD is only placed

when TPM is

installed on module

3.3.13 SMBus

Signal Pin # Description I/O PU/PD Comment

SMB_CK B13 System Management Bus bidirectional clock line.

Power sourced through 5V standby rail and main power

rails.

I/O OD 3.3VSB PU 2k2 3.3VSB

SMB_DAT# B14 System Management Bus bidirectional data line. Power

sourced through 5V standby rail and main power rails.

SMB_ALERT# B15 System Management Bus Alert – active low input can

be used to generate an SMI# (System Management

Interrupt) or to wake the system. Power sourced

through 5V standby rail and main power rails.

I/O OD 3.3VSB PU 2k2 3.3VSB

I 3.3VSB PU 10k 3.3VSB

3.3.14 I2C Bus

Signal Pin # Description I/O PU/PD Comment

I2C_CK B33 General purpose I²C port clock output/input I/O OD 3.3VSB PU 2k2 3.3VSB

I2C_DAT B34 General purpose I²C port data I/O line I/O OD 3.3VSB PU 2k2 3.3VSB

3.3.15 General Purpose I/O (GPIO)

Signal Pin # Description I/O PU/PD Comment

GPO[0] A93 General purpose output pins. O 3.3V After hardware

RESET output low

GPO[1] B54 General purpose output pins. O 3.3V After hardware

RESET output low

GPO[2] B57 General purpose output pins. O 3.3V After hardware

RESET output low

cExpress-HL Page 21

Page 22

Signal Pin # Description I/O PU/PD Comment

GPO[3] B63 General purpose output pins. O 3.3V After hardware

RESET output low

GPI[0] A54 General purpose input pins.

I 3.3V PU 10K 3.3V

Pulled high internally on the module.

GPI[1] A63 General purpose input pins.

I 3.3V PU 10K 3.3V

Pulled high internally on the module.

GPI[2] A67 General purpose input pins.

I 3.3V PU 10K 3.3V

Pulled high internally on the module.

GPI[3] A85 General purpose input pins.

I 3.3V PU 10K 3.3V

Pulled high internally on the module.

3.3.16 Serial Interface Signals

Signal Pin # Description I/O PU/PD Comment

SER0_TX A98 General purpose serial port transmitter (TTL level output) O CMOS Power rail tolerance 5V / 12V

SER0_RX A99 General purpose serial port receiver (TTL level input) I CMOS Power rail tolerance 5V / 12V

SER1_TX A101 General purpose serial port transmitter (TTL level output) O CMOS Power rail tolerance 5V / 12V

SER1_RX A102 General purpose serial port receiver (TTL level input) I CMOS Power rail tolerance 5V / 12V

3.3.17 Power and System Management

Signal Pin # Description I/O PU/PD Comment

PWRBTN# B12 Power button to bring system out of S5 (soft off), active on falling edge. I 3.3VSB PU 10k

3.3VSB

SYS_RESET# B49 Reset button input. Active low request for module to reset and reboot. May

be falling edge sensitive. For situations when SYS_RESET# is not able to

I 3.3VSB PU 10k

3.3VSB

reestablish control of the system, PWR_OK or a power cycle may be used.

CB_RESET# B50 Reset output from module to Carrier Board. Active low. Issued by module

O 3.3VSB

chipset and may result from a low SYS_RESET# input, a low PWR_OK

input, a VCC_12V power input that falls below the minimum specification, a

watchdog timeout, or may be initiated by the module software.

PWR_OK B24 Power OK from main power supply. A high value indicates that the power is

good. This signal can be used to hold off Module startup to allow carrier

I 3.3V PU 100k

3.3VSB

based FPGAs or other configurable devices time to be programmed.

SUS_STAT# B18 Indicates imminent suspend operation; used to notify LPC devices. O 3.3VSB

SUS_S3# A15 Indicates system is in Suspend to RAM state. Active-low output. An inverted

O 3.3VSB

copy of SUS_S3# on the carrier board (also known as “PS_ON”) may be

used to enable the non-standby power on a typical ATX power supply.

SUS_S4# A18 Indicates system is in Suspend to Disk state. Active low output. O 3.3VSB

SUS_S5# A24 Indicates system is in Soft Off state. O 3.3VSB

WAKE0# B66 PCI Express wake up signal. I 3.3VSB PU 10k

3.3VSB

WAKE1# B67 General purpose wake up signal. May be used to implement wake-up on

PS/2 keyboard or mouse activity.

BATLOW# A27 Battery low input. This signal may be driven low by external circuitry to

signal that the system battery is low, or may be used to signal some other

I 3.3VSB PU 10k

3.3VSB

I 3.3VSB PU 10k

3.3VSB

external power-management event.

Page 22 cExpress-HL

Page 23

Signal Pin # Description I/O PU/PD Comment

LID# LID button. Low active signal used by the ACPI operating system for a LID

switch.

SLEEP# Sleep button. Low active signal used by the ACPI operating system to bring

the system to sleep state or to wake it up again.

I OD

3.3VSB

I OD

3.3VSB

PU 10k

3.3VSB

PU 10K

3.3VSB

3.3.18 Power and Ground

Signal Pin # Description I/O PU/PD Comment

VCC_12V A104-A109

B104-B109

VCC_5V_SBY B84-B87 Standby power input: +5.0V nominal. If VCC5_SBY is used, all

VCC_RTC A47 Real-time clock circuit-power input. Nominally +3.0V. P

GND A1, A11, A21, A31,

A41, A51, A57, A66,

A80, A90, A96,

A100, A110, B1,

B11, B21 ,B31, B41,

B51, B60, B70, B80,

B90, B100, B110

Primary power input: +12V nominal (5 ~ 20V wide input).

All available VCC_12V pins on the connector(s) shall be used.

available VCC_5V_SBY pins on the connector(s) shall be used.

Only used for standby and suspend functions. May be left

unconnected if these functions are not used in the system design.

Ground - DC power and signal and AC signal return path. P

P 5~20 V

P 5Vsb ±5%

cExpress-HL Page 23

Page 24

3.4 CD Signal Descriptions

3.4.1 USB 3.0 extension

Signal Pin Description I/O PU/PD Comment

USB_SSRX0-

USB_SSRX0+

USB_SSTX0-

USB_SSTX0+

USB_SSRX1-

USB_SSRX1+

USB_SSTX1-

USB_SSTX1+

USB_SSRX2-

USB_SSRX2+

USB_SSTX2-

USB_SSTX2+

USB_SSRX3-

USB_SSRX3+

USB_SSTX3-

USB_SSTX3+

C3

C4

D3

D4

C6

C7

D6

D7

C9

C10

D9

D10

C12

C13

D12

D13

Additional Receive signal differential pairs for the

SuperSpeed USB data path on USB0

Additional Transmit signal differential pairs for the

SuperSpeed USB data path on USB0

Additional Receive signal differential pairs for the

SuperSpeed USB data path on USB1

Additional Transmit signal differential pairs for the

SuperSpeed USB data path on USB1

Additional Receive signal differential pairs for the

SuperSpeed USB data path on USB2

Additional Transmit signal differential pairs for the

SuperSpeed USB data path on USB2

Additional Receive signal differential pairs for the

SuperSpeed USB data path on USB3

Additional Transmit signal differential pairs for the

SuperSpeed USB data path on USB3

I PCIE

O PCIE AC coupled on Module

I PCIE

O PCIE AC coupled on Module

I PCIE Not supported

O PCIE Not supported

I PCIE Not supported

O PCIE Not supported

3.4.2 PCI Express x1

Signal Pin # Description I/O PU/PD Comment

PCIE_TX6+

PCIE_TX6-

PCIE_RX6+

PCIE_RX6-

PCIE_TX7+

PCIE_TX7-

PCIE_RX7+

PCIE_RX7-

D19

D20

C19

C20

D22

D23

C22

C23

PCI Express channel 6, Transmit Output differential pair. O PCIE

PCI Express channel 6, Receive Input differential pair. I PCIE

PCI Express channel 7, Transmit Output differential pair. O PCIE

PCI Express channel 7, Receive Input differential pair. I PCIE

Not supported

Not supported

Not supported

Not supported

Page 24 cExpress-HL

Page 25

3.4.3 DDI Channels

DDI 1

Signal Pin Description I/O PU/PD Comment

DDI1_PAIR0+

DDI1_PAIR0DDI1_PAIR1+

DDI1_PAIR1DDI1_PAIR2+

DDI1_PAIR2DDI1_PAIR3+

DDI1_PAIR3DDI1_PAIR4+

DDI1_PAIR4DDI1_PAIR5+

DDI1_PAIR5DDI1_PAIR6+

DDI1_PAIR6-

DDI1_HPD C24 Digital Display Interface Hot-Plug Detect I PCIE

DDI1_DDC_AUX_SEL D34 Selects the function of DDI1_CTRLCLK_AUX+

D26

D27

D29

D30

D32

D33

D36

D37

C25

C26

C29

C30

C15

C16

Digital Display Interface1 differential pairs O PCIE

IF DDI1_DDC_AUX_SEL is floating I/O PCIe DP1_AUX+ DDI1_CTRLCLK_AUX+ D15

IF DDI1_DDC_AUX_SEL pulled high I/O OD 3.3V HDMI1_CTRLCLK

IF DDI1_DDC_AUX_SEL is floating I/O PCIe DP1_AUX+ DDI1_CTRLCLK_AUX- D16

IF DDI1_DDC_AUX_SEL pulled high I/O OD 3.3V HDMI1_CTRLDATA

I/O OD 3.3V PD 1M

and DDI1_CTRLDATA_AUX-. This pin shall

have a 1M pull-down to logic ground on the

Module. If this input is floating the AUX pair is

used for the DP AUX+/- signals. If pulled-high

the AUX pair contains the CRTLCLK and

CTRLDATA signals.

Pair 4 to Pair 6

Not supported

cExpress-HL Page 25

Page 26

DDI 2

Signal Pin Description I/O PU/PD Comment

DDI2_PAIR0+

DDI2_PAIR0DDI2_PAIR1+

DDI2_PAIR1DDI2_PAIR2+

DDI2_PAIR2DDI2_PAIR3+

DDI2_PAIR3-

DDI2_HPD D44

DDI2_DDC_AUX_SEL C34 Selects the function of DDI2_CTRLCLK_AUX+ and

D39

D40

D42

D43

D46

D47

D49

D50

Digital Display Interface2 differential pairs

IF DDI2_DDC_AUX_SEL is floating I/O PCIe DP2_AUX+ DDI2_CTRLCLK_AUX+ C32

IF DDI2_DDC_AUX_SEL pulled high I/O OD 3.3V HDMI2_CTRLCLK

IF DDI2_DDC_AUX_SEL is floating I/O PCIe DP2_AUX+ DDI2_CTRLCLK_AUX- C33

IF DDI2_DDC_AUX_SEL pulled high I/O OD 3.3V HDMI2_CTRLDATA

PD 1M

DDI2_CTRLDATA_AUX-. This pin shall have a 1M pulldown to logic ground on the Module. If this input is

floating the AUX pair is used for the DP AUX+/- signals. If

pulled-high the AUX pair contains the CRTLCLK and

CTRLDATA signals.

DDI 3

Signal Pin Description I/O PU/PD Comment

DDI3_PAIR0+

DDI3_PAIR0DDI3_PAIR1+

DDI3_PAIR1DDI3_PAIR2+

DDI3_PAIR2DDI3_PAIR3+

DDI3_PAIR3-

DDI3_HPD C44

DDI3_CTRLCLK_AUX+ C36

DDI3_CTRLCLK_AUX- C37

DDI3_DDC_AUX_SEL C38 Selects the function of DDI3_CTRLCLK_AUX+ and

C39

C40

C42

C43

C46

C47

C49

C50

Digital Display Interface3 differential pairs

IF DDI3_DDC_AUX_SEL is floating I/O PCIe

IF DDI3_DDC_AUX_SEL pulled high I/O OD 3.3V

IF DDI3_DDC_AUX_SEL is floating I/O PCIe

IF DDI3_DDC_AUX_SEL pulled high I/O OD 3.3V

PD 1M

DDI3_CTRLDATA_AUX-. This pin shall have a 1M pulldown to logic ground on the Module. If this input is

floating the AUX pair is used for the DP AUX+/- signals. If

pulled-high the AUX pair contains the CRTLCLK and

CTRLDATA signals.

Not supported

Not supported

Not supported

Not supported

Not supported

Not supported

Not supported

Page 26 cExpress-HL

Page 27

3.4.4 DDI to DP/HDMI/SDVO Mapping

Pin Pin Name DP HDMI \ DVI

D26 DDI1_PAIR0+ DP1_LANE0+ TMDS1_DATA2+

D27 DDI1_PAIR0- DP1_LANE0- TMDS1_DATA2-

D29 DDI1_PAIR1+ DP1_LANE1+ TMDS1_DATA1+

D30 DDI1_PAIR1- DP1_LANE1- TMDS1_DATA1-

D32 DDI1_PAIR2+ DP1_LANE2+ TMDS1_DATA0+

D33 DDI1_PAIR2- DP1_LANE2- TMDS1_DATA0-

D36 DDI1_PAIR3+ DP1_LANE3+ TMDS1_CLK+

D37 DDI1_PAIR3- DP1_LANE3- TMDS1_CLK-

C25 DDI1_PAIR4+ Not supported Not supported

C26 DDI1_PAIR4- Not supported Not supported

C29 DDI1_PAIR5+ Not supported Not supported

C30 DDI1_PAIR5- Not supported Not supported

C15 DDI1_PAIR6+ Not supported Not supported

C16 DDI1_PAIR6- Not supported Not supported

C24 DDI1_HPD DP1_HPD HDMI1_HPD

D15 DDI1_CTRLCLK_AUX+ DP1_AUX+ HMDI1_CTRLCLK

D16 DDI1_CTRLDATA_AUX- DP1_AUX- HMDI1_CTRLDATA

D34 DDI1_DDC_AUX_SEL

D39 DDI2_PAIR0+ DP2_LANE0+ TMDS2_DATA2+

D40 DDI2_PAIR0- DP2_LANE0- TMDS2_DATA2-

D42 DDI2_PAIR1+ DP2_LANE1+ TMDS2_DATA1+

D43 DDI2_PAIR1- DP2_LANE1- TMDS2_DATA1-

D46 DDI2_PAIR2+ DP2_LANE2+ TMDS2_DATA0+

D47 DDI2_PAIR2- DP2_LANE2- TMDS2_DATA0-

D49 DDI2_PAIR3+ DP2_LANE3+ TMDS2_CLK+

D50 DDI2_PAIR3- DP2_LANE3- TMDS2_CLK-

D44 DDI2_HPD DP2_HPD HDMI2_HPD

C32 DDI2_CTRLCLK_AUX+ DP2_AUX+ HDMI2_CTRLCLK

C33 DDI2_CTRLDATA_AUX- DP2_AUX- HDMI2_CTRLDATA

C34 DDI2_DDC_AUX_SEL

cExpress-HL Page 27

Page 28

3.4.5 PCI Express Graphics x16 (PEG)

Signal Pin Description I/O PU/PD Comment

PEG_RX0+

PEG_RX0-

PEG_RX1+

PEG_RX1-

PEG_RX2+

PEG_RX2-

PEG_RX3+

PEG_RX3-

PEG_RX4+

PEG_RX4-

PEG_RX5+

PEG_RX5-

PEG_RX6+

PEG_RX6-

PEG_RX7+

PEG_RX7-

PEG_RX8+

PEG_RX8-

PEG_RX9+

PEG_RX9-

PEG_RX10+

PEG_RX10-

PEG_RX11+

PEG_RX11-

PEG_RX12+

PEG_RX12-

PEG_RX13+

PEG_RX13-

PEG_RX14+

PEG_RX14-

PEG_RX15+

PEG_RX15

C52

C53

C55

C56

C58

C59

C61

C62

C65

C66

C68

C69

C71

C72

C74

C75

C78

C79

C81

C82

C85

C86

C88

C89

C91

C92

C94

C95

C98

C99

C101

C102

PCI Express Graphics transmit differential pairs. I PCIE Not supported

PEG_TX0+

PEG_TX0-

PEG_TX1+

PEG_TX1-

PEG_TX2+

PEG_TX2-

PEG_TX3+

PEG_TX3-

PEG_TX4+

PEG_TX4-

PEG_TX5+

PEG_TX5-

PEG_TX6+

PEG_TX6-

PEG_TX7+

PEG_TX7-

PEG_TX8+

PEG_TX8-

PEG_TX9+

PEG_TX9-

PEG_TX10+

PEG_TX10-

PEG_TX11+

PEG_TX11-

PEG_TX12+

PEG_TX12-

PEG_TX13+

PEG_TX13-

PEG_TX14+

PEG_TX14-

D52

D53

D55

D56

D58

D57

D61

D62

D65

D66

D68

D69

D71

D72

D74

D75

D78

D79

D81

D82

D85

D86

D88

D89

D91

D92

D94

D95

D98

D99

PCI Express Graphics receive differential pairs. O PCIE Not supported

Page 28 cExpress-HL

Page 29

Signal Pin Description I/O PU/PD Comment

PEG_TX15+

PEG_TX15-

D101

D102

PEG_LANE_RV# D54 PCI Express Graphics lane reversal input strap.

Pull low on the Carrier board to reverse lane order.

I 1.05V Not supported

3.4.6 Module Type Definition

Signal Pin # Description I/O Comment

TYPE0#

TYPE1#

TYPE2#

C54

C57

D57

The TYPE pins indicate to the Carrier Board the Pin-out Type that is implemented

on the module. The pins are tied on the module to either ground (GND) or are noconnects (NC). For Pinout Type 1, these pins are don’t care (X).

TYPE2# TYPE1# TYPE0#

X X X Pinout Type 1

NC NC NC Pinout Type 2

NC NC GND Pinout Type 3 (no IDE)

NC GND NC Pinout Type 4 (no PCI)

NC GND GND Pinout Type 5 (no IDE, no PCI)

GND NC NC Pinout Type 6 (no IDE, no PCI)

The Carrier Board should implement combinatorial logic that monitors the module

TYPE pins and keeps power off (e.g deactivates the ATX_ON signal for an ATX

power supply) if an incompatible module pin-out type is detected. The Carrier

Board logic may also implement a fault indicator such as an LED.

Type 6

3.4.7 Power and Ground

Signal Pin # Description I/O PU/PD Comment

VCC_12V C104-C109

D104-D109

GND C1, C11, C21, C31, C41,

C51, C60, C70, C76, C80,

C84, C87, C90, C93, C96,

C100, C103, C110, D1,

D11, D21, D31, D41, D51,

D60, D67, D70, D76, D80,

D84, D87, D90, D93, D96,

D100, D103, D110

Primary power input: +12V nominal (5 ~ 20V wide input).

All available VCC_12V pins on the connector(s) shall be used.

Ground - DC power and signal and AC signal return path.

All available GND connector pins shall be used and tied to carrier

board GND plane.

P 5~20 V

P

cExpress-HL Page 29

Page 30

4 Connector Pinouts on Module

This chapter describes connectors and pinouts, LEDs and switches that are used on the module but are not included in the PICMG standard

specification

¾ Connector and LED Locations

XDP

60-pin

to CPU

CPU

Keep out

BIOS

Defaults

Reset

Switch

CD

AB

FAN

LED2

LED3

40-pin Debug

Connector

4-pin

Fan

Page 30 cExpress-HL

LED1

Page 31

4.1 40-pin Debug Connector

¾ FPC Connector Type: FCI 59GF Flex 10042867

¾ Pin Orientation

¾ cExpress-HL and the DB40 Debug Module

cExpress-HL Page 31

Page 32

¾ 40-pin Debug Connector Pin Definition on the COM Express Module

Pin Interface Signal Remark Pin Interface Signal Remark

SPI

1 VCC_SPI_IN SPI Power Input from flash tool

Program

interface

2 GND 22 RXD6

3 SPI_BIOS_CS0# 23 FUMD0

4 SPI_BIOS_CS1# 24 RESET_IN#

5 SPI_BIOS_MISO 25 DATA

6 SPI_BIOS_MOSI 26 CLK

7

8 3V3_LPC System power 3.3V provide from

LPC Bus

9 GND 29 PWRBTN#

10 BIOS_DIS0 30 SYS_RESET#

11 RST# 31 CB_RESET#

12 CLK33_LPC 32 CB_PWROK

13 LPC_FRAME# 33 SUS_S3#

SPI_BIOS_CLK 27 OCD0A Include a jumper to connect

to module. HW need add MOS

FET to switch SPI power for SPI

ROM

COM module

21 TXD6

28

BMC Program

interface

(continued)

OCD0A via 1K0 pull-up to

3.3V_BMC

OCD0B Include a jumper to connect

OCD0A via 1K0 pull-up to

3.3V_BMC

Test points

14 LPC_AD3 34 SUS_S4#

15 LPC_AD2 35

16 LPC_AD1 always power 3.3V provide from

COM module

17

BMC

18

Program

interface

19 3.3V_BMC always power 3.3V provide from

20

LPC_AD0 37 SEL_BIOS Connect to Jumper for

3.3V_BMC always power 3.3V provide from

COM module

COM module

GND 40 Reserved

36 POSTWDT_DIS# Connect to Jumper for

38 BIOS_MODE Connect to Jumper for

39

BMC Debug

signals

SUS_S5#

Debug

Debug

Debug

BMC_STATUS

Note: The pin definition on the debug module is the inverse of that on the COM Express module.

Page 32 cExpress-HL

Page 33

4.2 Status LEDs

To facilitate easier maintenance, status LED’s are mounted on the board.

¾ LED Descriptions

Name Color Connection Function

LED1 Blue BMC output Power Sequence Status Code (BMC)

Power Changes, RESET

(see 5.1.4 Exception Codes below)

LED2 Green Power Source 3Vcc S0 LED ON

S3/S4/S5 LED OFF

ECO mode LED OFF

LED3 Red BMC output

and same signal as WDT

(B27) on BtB connector

Module power up WD LED = LED OFF

Watchdog counting WD LED = LED OFF

Watchdog timed out WD LED = LED ON

Watchdog RESET WD LED = LED ON

Rebooted after WD RESET WD LED = LED ON

Rebooted after PWRBTN WD LED = LED ON

Rebooted after RESET BTN WD LED = LED OFF

Note: only a RESET not initiated by the BMC can clear the WD LED (user action)

cExpress-HL Page 33

Page 34

4.3 XDP Debug header

The debug port is a connection into a target-system environment that provides access to JTAG, run control, system control, and observation

resources. The XDP target system connector is a Samtec™ 60-pin BSH-030-01 series connector.

Pin XDP Signal Target Signal I/O Device Pin XDP Signal Target Signal I/O Device

1 GND GND NA 2 GND GND NA

3 OBSFN_A0 PREQ# I/O Processor 4 OBSFN_C0 CFG[17]2 I Processor

5 OBSFN_A1 PRDY# I/O Processor 6 OBSFN_C1 CFG[16]2 I Processor

7 GND GND NA 8 GND GND NA

9 OBSDATA_A0 CFG[0]2 I/O Processor 10 OBSDATA_C0 CFG[8]2 I/O Processor

11 OBSDATA_A1 CFG[1]2 I/O Processor 12 OBSDATA_C1 CFG[9]2 I/O Processor

13 GND GND NA 14 GND GND NA

15 OBSDATA_A2 CFG[2]2 I/O Processor 16 OBSDATA_C2 CFG[10]2 I/O Processor

17 OBSDATA_A3 CFG[3]2 I/O Processor 18 OBSDATA_C3 CFG[11]2 I/O Processor

19 GND GND NA 20 GND GND NA

21 OBSFN_B0 BPM#[0]1 I/O Processor 22 OBSFN_D0 CFG[19]2 I/O Processor

23 OBSFN_B1 BPM#[1]1 I/O Processor 24 OBSFN_D1 CFG[18]2 I/O Processor

25 GND GND NA 26 GND GND NA

27 OBSDATA_B0 CFG[4]2 I/O Processor 28 OBSDATA_D0 CFG[12]2 I Processor

29 OBSDATA_B1 CFG[5]2 I/O Processor 30 OBSDATA_D1 CFG[13]2 I Processor

31 GND GND NA 32 GND GND NA

33 OBSDATA_B2 CFG[6]2 I/O Processor 34 OBSDATA_D2 CFG[14]2 I/O Processor

35 OBSDATA_B3 CFG[7]2 I/O Processor 36 OBSDATA_D3 CFG[15]2 I/O Processor

37 GND GND NA 38 GND GND NA

39 HOOK0 PWRGOOD I System 40 ITPCLK/HOOK4 Open NA

41 HOOK11 BP_PWRGD_RST# O System 42 ITPCLK#/HOOK5 Open NA

43 VCC_OBS_AB VCCIO_OUT I System 44 VCC_OBS_CD VCCIO_OUT I System

45 HOOK2 PWR_DEBUG O Processor 46 HOOK6/RESET# PLTRSTIN# I System

47 HOOK3 PCH_SYS_PWROK O System 48 HOOK7/DBR# DBR# O System

49 GND GND NA 50 GND GND NA

51 SDA1 SDA I/O System 52 TDO TDO I Processor

53 SCL1 SCL I/O System 54 TRSTn TRST# O Processor

55 TCK1 Open NA 56 TDI TDI O Processor

57 TCK0 TCK O Processor 58 TMS TMS O Processor

59 GND GND NA 60 GND GND (or XDP_PRESENT#

if required)

NA

Notes:

1. These signals are optional, can be left as OPEN/No-Connect if debug by Intel will not be needed.

2. These CFG signals can be left as Open/No Connect if not used as a strapping signal and top side probe will be used to debug

processor.

Refer to the "Shark Bay, Denlow and Broadwell U/Y Platforms Debug Port Design Guide", Document Number: 479493, Revision: 2.0

Page 34 cExpress-HL

Page 35

4.4 Fan Connector

¾ Connector Type: JVE 24W1125A-04M00

¾ Pin Assignment

Name Signal Description

1 BMC_FAN_OUT FAN_PWMOUT

2 BMC_FAN_PWM_IN FAN_TACHIN

3 GND Ground

4 P5V_S 5V

4.5 BIOS Setup Defaults Reset Button

To perform a hardware reset of BIOS default settings, perform the following steps:

1. Shut down the system.

2. Press the BIOS Setup Defaults RESET Button continuously and boot up the system. You can release the button when the BIOS

prompt screen appears

3. The BIOS prompt screen will display a confirmation that BIOS defaults have been reset and request that you reboot the system.

cExpress-HL Page 35

Page 36

5 Smart Embedded Management Agent (SEMA)

The onboard microcontroller (BMC) implements power sequencing and Smart Embedded Management Agent (SEMA) functionality. The

microcontroller communicates via the System Management Bus with the CPU/chipset. The following functions are implemented:

‧ Total operating hours counter. Counts the number of hours the module has been run in minutes.

‧ On-time minutes counter. Counts the seconds since last system start.

‧ Temperature monitoring of CPU and board temperature. Minimum and maximum temperature values of CPU and board are

stored in flash.

‧ Power cycles counter

‧ Boot counter. Counts the number of boot attempts.

‧ Watchdog Timer (Type-II). Set / Reset / Disable Watchdog Timer. Features auto-reload at power-up.

‧ System Restart Cause. Power loss / BIOS Fail / Watchdog / Internal Reset / External Reset

‧ Fail-safe BIOS support. In case of a boot failure, hardware signals tells external logic to boot from fail-safe BIOS.

‧ Flash area. 1kB Flash area for customer data

‧ 128 Bytes Protected Flash area. Keys, IDs, etc. can be stored in a write- and clear-protectable region.

‧ Board Identify. Vendor / Board / Serial number / Production Date

‧ Main-current & voltage. Monitors drawn current and main voltages

For a detailed description of SEMA features and functionality, please refer to SEMA Technical Manual and SEMA Software Manual,

downloadable at:

http://www.adlinktech.com/sema/.

Page 36 cExpress-HL

Page 37

5.1 Board Specific SEMA Functions

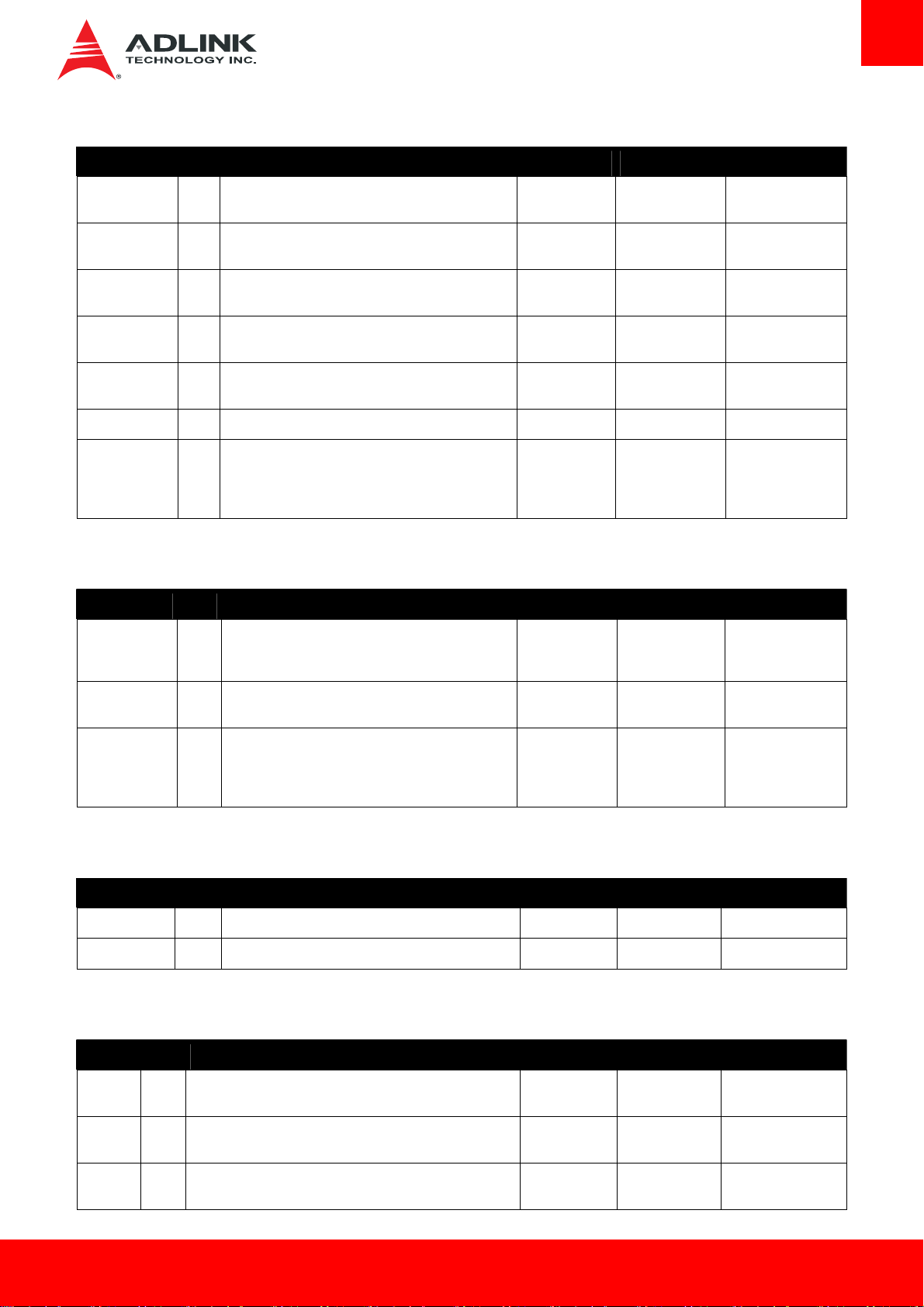

5.1.1 Voltages

The BMC of the cExpress-HL implements a voltage monitor and samples several onboard voltages. The voltages can be read by calling the

SEMA function “Get Voltages”. The function returns a 16-bit value divided into high-byte (MSB) and low-byte (LSB).

ADC Channel Voltage Name Voltage Formula [V]

0

1

2 +V1.05S (MSB<<8 + LSB) x 3.3 / 1024

3 +V3.3A (MSB<<8 + LSB) x 1.100 x 3.3 / 1024

4 +VDDQ (V1.35 ~ V1.5) (MSB<<8 + LSB) x 3.3 / 1024

5 +V5A_DUAL (MSB<<8 + LSB) x 1.833 x 3.3 / 1024

6 +VIN (MSB<<8 + LSB) x 6.000 x 3.3 / 1024

+V1.05S (MSB<<8 + LSB) x 3.3 / 1024

+VCORE (MSB<<8 + LSB) x 3.3 / 1024

7 (MAIN CURRENT) Use Main Current Function

5.1.2 Main Current

The BMC of the cExpress-HL implements a current monitor. The current can be read by calling the SEMA function “Get Main Current”. The

function returns four 16-bit values divided in high-byte (MSB) and low-byte (LSB). These 4 values represent the last 4 currents drawn by the

board. The values are sampled every 250ms. The order of the 4 values is NOT in chronological order. Access by the BMC may increase the

drawn current of the whole system. In this case, there are still 3 samples not influenced by the read access.

Main Current = (MSB_n<<8 + LSB_n) x 8.06mA

5.1.3 BMC Status

This register shows the status of BMC controlled signals on the cExpress-HL.

Status Bit Signal

0 WDT_OUT

1 LVDS_VDDEN

2 LVDS_BKLTEN

3 BIOS_MODE

4 POSTWDT_DISn

5 SEL_BIOS

6 BIOS_DIS0n

7 BIOS_DIS1n

cExpress-HL Page 37

Page 38

5.1.4 Excep tion Codes

In case of an error, the BMC drives a blinking code on the blue Status LED (LED1). The same error code is also reported by the BMC Flags

register. The Exception Code is not stored in the Flash Storage and is cleared when the power is removed. Therefore, a “Clear Exception

Code” command is not needed or supported.

Exception Code Error Message

0 NOERROR

2 NO_SUSCLK

3 NO_SLP_S5

4 NO_SLP_S4

5 NO_SLP_S3

6 BIOS_FAIL

7 RESET_FAIL

8 POWER_FAIL

9 LOW_VIN

11 VCORE

12 +P1V05_S

13 +P3V3_A

14 +VDDQ

15 +P5V_A

16 +P12V

18 CRITICAL_TEMP

19 NO_CB_PWROK

20 NO_SYS_GD

21 NO_VCORE_GD

22 NO_XDP_PIN47

5.1.5 BMC Flags

The BMC Flags register returns the last detected Exception Code since power-up and shows the BIOS in use and the power mode.

Bit Description

[ 0 ~ 4 ] Exception Code

[ 6 ] 0 = AT mode

1 = ATX mode

[ 7 ] 0 = Standard BIOS

1 = Fail-safe BIOS.

Page 38 cExpress-HL

Page 39

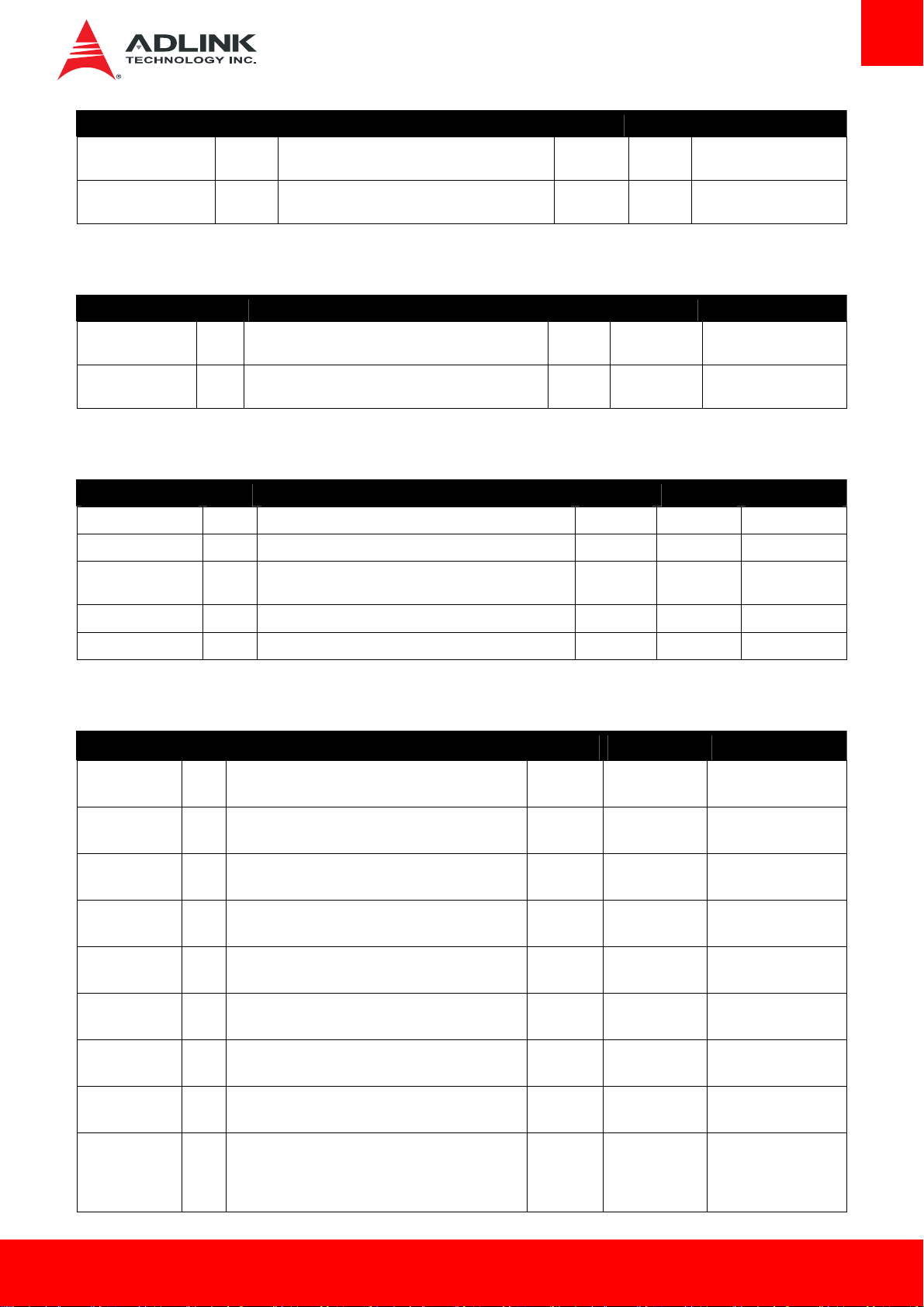

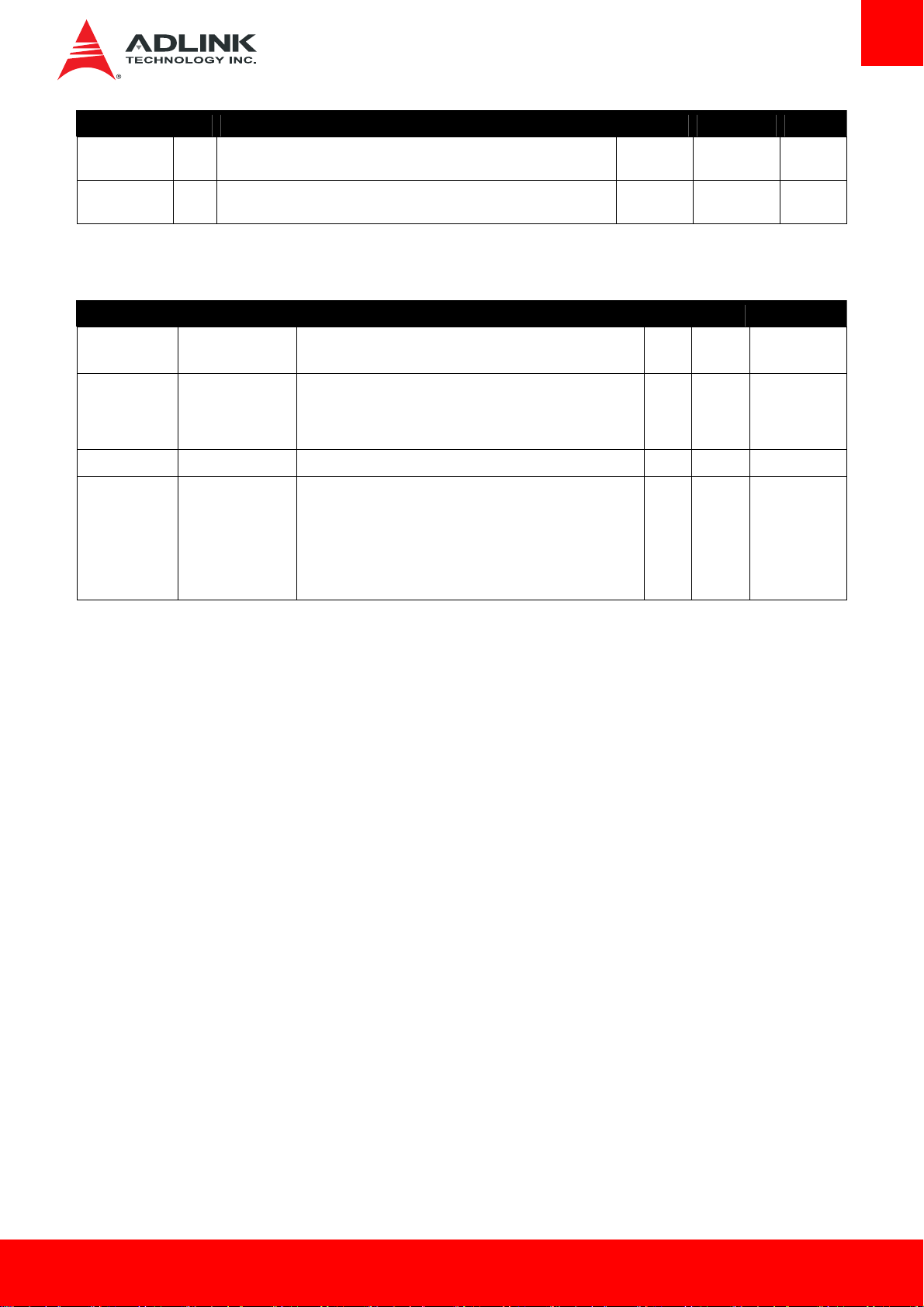

6 System Resources

6.1 System Memory Map

Address Range (decimal) Address Range (hex) Size Description

(4GB-2MB) FFE00000 – FFFFFFFF 2 MB High BIOS Area

(4GB-18MB) – (4GB-17MB-1) FEE00000 – FEEFFFFF 1 MB MSI Interrupts

(4GB-20MB) – (4GB-19MB-1) FEC00000 – FECFFFFF 1 MB APIC Configuration Space

1MB -15MB 100000 - EFFFFF 14MB Main Memory

0K –1MB 00000 – FFFFFF 1MB DOS Compatibility Memory

6.2 Direct Memory Access Channels

Channel Number Data Width System Resource

0 8-bits Generic

1 8-bits Generic

2 8-bits Generic

3 8-bits Generic

4 Reserved - cascade channel

5 16-bits Generic

6 16-bits Generic

7 16-bits Generic

cExpress-HL Page 39

Page 40

6.3 I/O Map

Hex Range Device

000-01F DMA controller 1, 8237A-5 equivalent

020-02D and 030-03F Interrupt controller 1, 8259 equivalent

02E-02F LPC SIO () configuration index/data registers

040-05F Timer, 8254-2 equivalent

060, 062, 064, 066, 068-06F 8742 equivalent (keyboard)

061, 063, 065, 067 NMI control and status

070-07F Real Time Clock Controller( bit 7 -NMI mask)

080-091 DMA page register

092 Reset (Bit 0)/ Fast Gate A20 (Bit 1)

93-9F DMA page registers continued

0A0-0B1 and 0B4-0BF Interrupt controller 2, 8259 equivalent

0B2 and 0B3 APM control and status port respectively

0C0-0DF DMA controller 2, 8237A-5 equivalent

0E0-0EF Available

0F0 Co-processor error register

0F1 N/A

0F2-0F3 N/A

0F4 IDE ID port

0F5-0F7 N/A

0F8 IDE Index port

0F9-0FB N/A

0FC IDE Data port

0FD-0FF N/A

100-179 Available

180-181 Default AIM4 SRAM control register (May be remapped)

182-1EF Available

1F0-1F7 Primary IDE Controller (AT Drive)

1FB-22F Available

230 -23F Available

240 -25F Serial Port 3/4

260-2F7 Available

2F8-2FF Serial Port 2

300-36F Available

370-377 Alt. Floppy Disk Controller

378-37F Available

380-3AF Available

3B0-3BB and 3BF Mono/VGA mode video

Page 40 cExpress-HL

Page 41

Hex Range Device

3BC-3BE Reserved for parallel port

3C0-3DF VGA registers

3E0-3EF Available

3F0-3F7 Available

3F8-3FF Serial port 1

4D0 Master PIC Edge/Level Trigger register

4D1 Slave PIC Edge/Level Trigger register

CF8-CFB PCI configuration address register (32 bit I/O only)

CF9 Reset Control register (8 bit I/O)

CFC-CFF PCI configuration data register

F040 Smbus base address for SB.

1C00 GPIO Base Address for SB

1800 PM (ACPI) Base Address for SB

1860 Alias for ICH TCO base address.

0A00~0AFF Reserved for SIO functions base address (ex: PME /GPIO etc)

cExpress-HL Page 41

Page 42

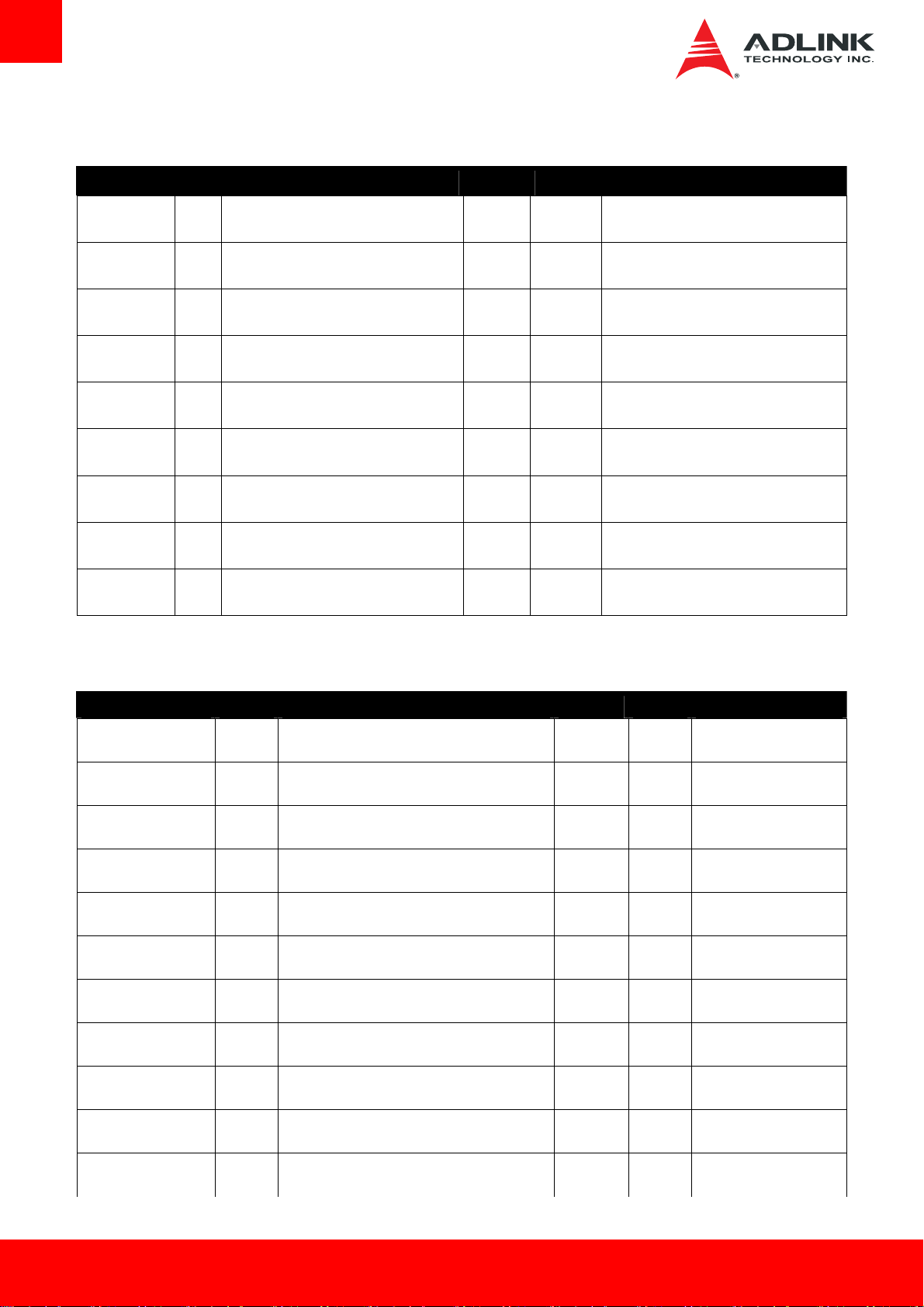

6.4 Interrupt Request (IRQ) Lines

PIC Mode

IRQ# Typical Intterupt Resource Connected to Pin Available

0 Counter 0 N/A No

1 Keyboard controller N/A No

2 Cascade interrupt from slave PIC N/A No

3 Serial Port 2 (COM2) IRQ3 via SERIRQ / PIRQ Note (1)

4 Serial Port 1 (COM1) IRQ4 via SERIRQ / PIRQ Note (1)

5 Parallel Port 2 (LPT2) IRQ5 via SERIRQ / PIRQ Note (1)

6 Generic IRQ6 via SERIRQ / PIRQ No

7 Generic IRQ7 via SERIRQ / PIRQ Note (1)

8 Real-time clock N/A No

9 Generic N/A Note (1)

10 Serial Port 3 (COM3) IRQ10 via SERIRQ / PIRQ Note (1)

11 Serial Port 4 (COM4) IRQ11 via SERIRQ / PIRQ Note (1)

12 PS/2 Mouse IRQ12 via SERIRQ / PIRQ Note (1)

13 Math Processor N/A Note (1)

14 Primary IDE controller IRQ14 via SERIRQ / PIRQ Note (1)

15 Secondary IDE controller IRQ15 via SERIRQ / PIRQ Note (1)

Note (1): These IRQs can be used for PCI devices when onboard device is disabled.

APIC Mode

IRQ# Typical Intterupt Resource Connected to Pin Available

0 Counter 0 N/A No

1 Keyboard controller N/A No

2 Cascade interrupt from slave PIC N/A No

3 Serial Port 2 (COM2) IRQ3 via SERIRQ / PIRQ Note (1)

4 Serial Port 1 (COM1 IRQ4 via SERIRQ / PIRQ Note (1)

5 N/A N/A Note (1)

6 N/A N/A Note (1)

7 N/A N/A Note (1)

8 Real-time clock N/A No

9 N/A IRQ9 via SERIRQ / PIRQ Note (1)

10 Serial Port 3 (COM3) IRQ10 via SERIRQ / PIRQ Note (1)

11 Serial Port 4 (COM4) IRQ11 via SERIRQ / PIRQ Note (1)

12 PS/2 Mouse IRQ12 via SERIRQ / PIRQ Note (1)

13 Math Processor N/A Note (1)

14 Primary IDE controller IRQ14 via SERIRQ / PIRQ Note (1)

15 Secondary IDE controller IRQ15 via SERIRQ / PIRQ Note (1)

Page 42 cExpress-HL

Page 43

IRQ# Typical Intterupt Resource Connected to Pin Available

16 N/A Intel HDA, PCIE Port 0/1/2/3 EHCI Conterller #2 ,

I.G.D ,XHCI Controller

17 N/A PCIE Port 0/1/2/3 Note (1)

18 N/A PCIE Port 0/1/2/3 SMBus Controller, Note (1)

19 N/A PCIE Port 0/1/2/3 Note (1)

20 N/A Gbe Controller Note (1)

21 N/A Note (1)

22 N/A Intel HDA Note (1)

23 N/A EHCI Controller #1 Note (1)

Note (1)

Note (1): These IRQs can be used for PCI devices when onboard device is disabled.

cExpress-HL Page 43

Page 44

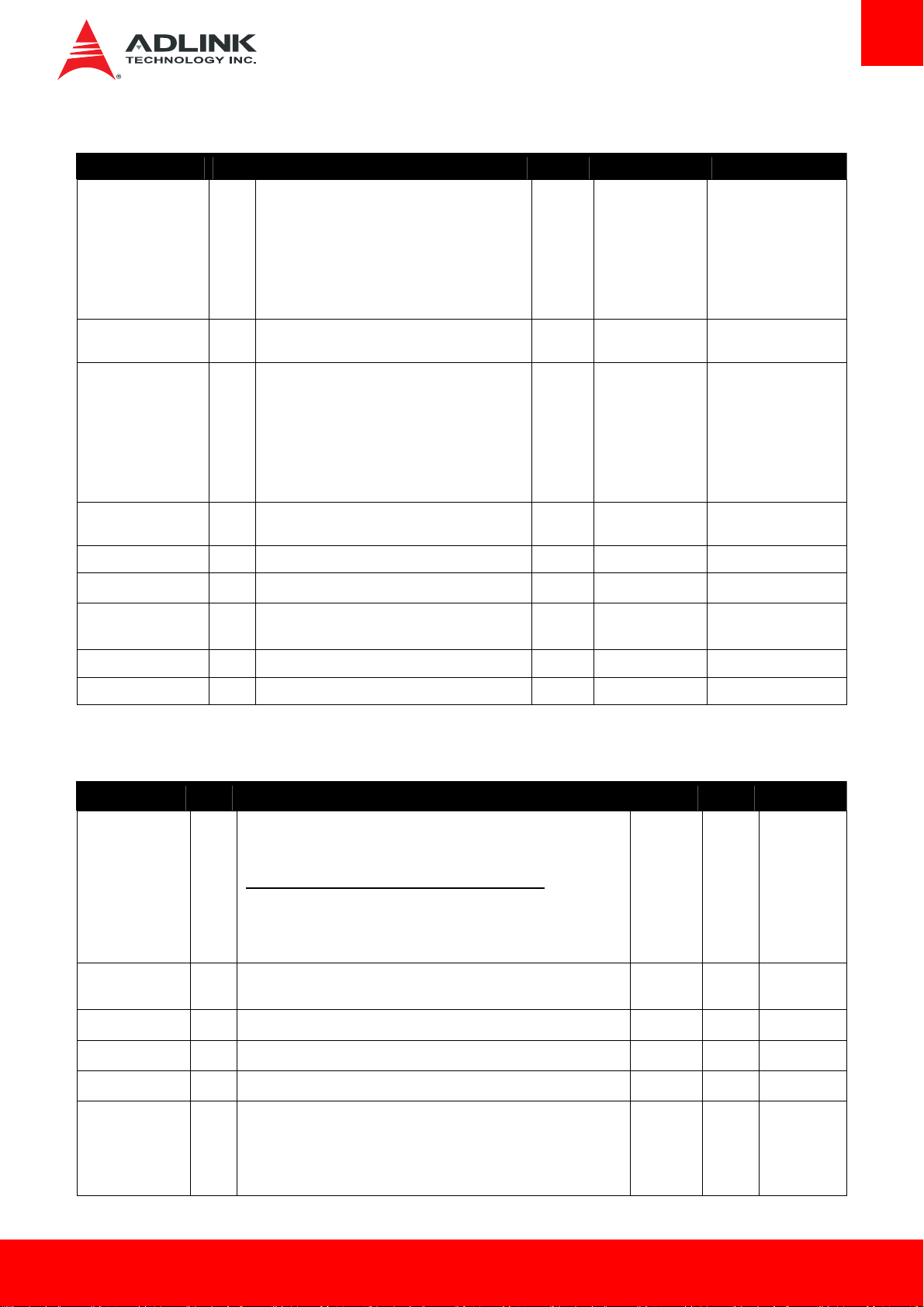

6.5 PCI Configuration Space Map

Bus

Number

00h 00h 00h N/A Intel host Bridge

00h 02h 00h Internal Intel I.G.D

00h 03h 00h Internal HD Audio Device

00h 14h 00h Internal xHCI Controller

00h 16h 00h Internal Intel Management Engine Interfaxe #1

00h 19h 00h Internal Gigabit Etherent Controller

00h 1Bh 00h Internal High Definition Audio controller

00h 1Ch 00h Internal Intel PCI Express Root port 1

00h 1Ch 01h Internal Intel PCI Express Root port 2

00h 1Ch 02h Internal Intel PCI Express Root port 3

00h 1Ch 03h Internal Intel PCI Express Root port 4

00h 1Dh 00h Internal Intel USB EHCI Controller #1

00h 1Fh 00h N/A Intel LPC Interface Bridge

00h 1Fh 02h Internal SATA Host Controller #1

00h 1Fh 03h Internal SMBus Controller

Device

Number

Function

Number

Routing Description

Page 44 cExpress-HL

Page 45

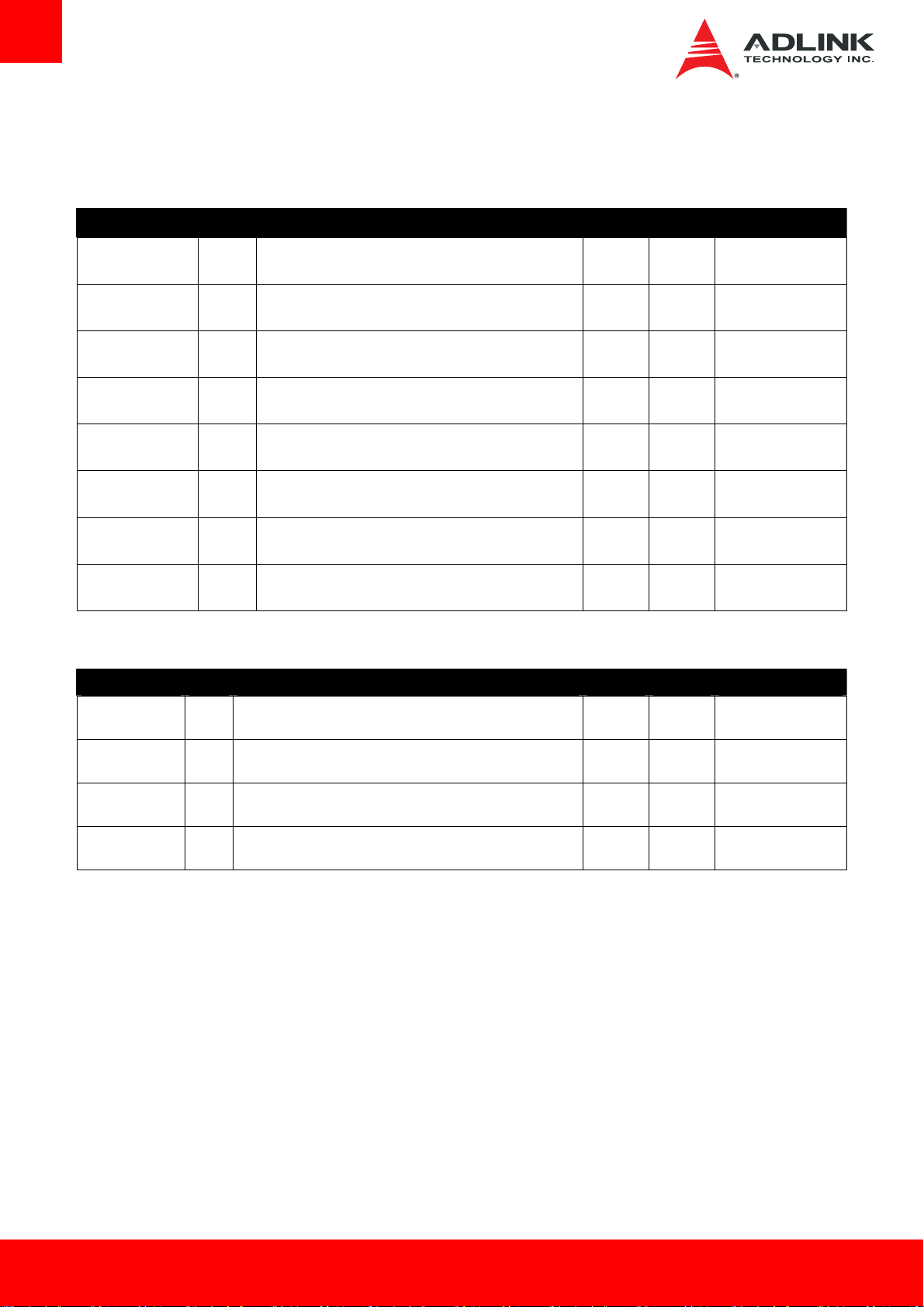

6.6 PCI Interrupt Routing Map

INT

Audio

Line

Controller

Int0 INTA:16 INTA:16 INTA:16 INTE:20 INTG:22

Int1 INTD:19

Int2 INTC:18

Int3 INTB:17

INT

PCIE port1 PCIE port 2 PCIE port 3 PCIE port 4 EHCI

Line

Int0 INTA:16 INTB:17 INTC:18 INTD:19 INTH:23 INTF:21

xHCI

Controller

ME

Controller #1

GbEt

Controller

HDA

Controller

#1

LPC

Controller

SATA

Controller

#1

SMBus

Controller

Int1 INTB:17 INTC:18 INTD:19 INTA:16 INTD:19 INTD:19

Int2 INTC:18 INTD:19 INTA:16 INTB:17 INTC:18 INTC:18

Int3 INTD:19 INTA:16 INTB:17 INTC:18 INTA:16

cExpress-HL Page 45

Page 46

7 BIOS Setup

7.1 Menu Structure