Page 1

aTCA-6155

Dual Intel® Xeon® 5600 Series Processor

10GbE ATCA Processor Blade

User’s Manual

Manual Rev.: 2.00

Revision Date: November 22, 2012

Part No: 50-1G019-1000

Advance Technologies; Automate the World.

Page 2

Revision History

Revision Release Date Description of Change(s)

2.00 2012/11/22 Initial Release

Page 3

aTCA-6155

Preface

Copyright 2012 ADLINK Technology Inc.

This document contains proprietary infor mation protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form

without prior written permission of the manufacturer.

Disclaimer

The information in this document is subject to change without prior

notice in order to improve reliability, design, and function and does

not represent a commitment on the part of the manufa cturer.

In no event will the manufacturer be liable for direct, indirect, special, incidental, or consequential damages arising out of the use or

inability to use the product or documentation, even if advised of

the possibility of such damages.

Environmental Responsibility

ADLINK is committed to fulfill its social responsibility to global

environmental preservation through compliance with the European Union's Restriction of Hazardous Substances (RoHS) directive and Waste Electrical and Electronic Equipment (WEEE)

directive. Environmental protection is a top priority for ADLINK.

We have enforced measures to ensure that our products, manufacturing processes, components, and raw materials have as little

impact on the environment as possible. When products are at their

end of life, our customers are encouraged to dispose of them in

accordance with the product disposal and/or recovery programs

prescribed by their nation or company.

Trademarks

Product names mentioned herein are used for identification purposes only and may be trademarks and/or registered trademarks

of their respective companies.

Preface iii

Page 4

Using this Manual

Audience and Scope

The aTCA-6155 User’s Manual is intended for hardware

technicians and systems operators with knowledge of installing,

configuring and operating ATCA systems.

Manual Organization

This manual is organized as follows:

Chapter 1, Introduction: Introduces the aTCA-6155, its features,

block diagrams, and package contents.

Chapter 2, Specifications: Presents detailed specification infor-

mation, power consumption, and board layout drawings.

Chapter 3, Functional Description: Describes the aTCA-6155’s

functional components and board interfaces.

Chapter 4, Hardware Platform Management: Describes the

hardware platform management system, including IPMI sensors,

commands, and firmware upgrade procedure.

Chapter 5, Getting Started: Describes the installation of components to the aTCA-6155.

Chapter 6, Driver Installation: Provides information on how to

install the aTCA-6155 device drivers.

Chapter 7, Watchdog Timer: Describes the watchdog functionality of the aTCA-6155.

Chapter 8, BIOS Setup: Describes basic navigation for the

AMIBIOS®8 BIOS setup utility.

Important Safety Instructions: Presents safety instructions all

users must follow for the proper setup, installation and usage of

equipment and/or software.

Getting Service: Contact information for ADLINK’s worldwide

offices.

iv Preface

Page 5

aTCA-6155

Conventions

Take note of the following conventions used throughout this

manual to make sure that users perform certain tasks and

instructions properly.

Additional information, aids, and tips that help users perform

tasks.

NOTE:

NOTE:

Information to prevent minor physical injury, component damage, data loss, and/or program corruption when trying to com-

CAUTION:

WARNING:

plete a task.

Information to prevent serious physical injury, component

damage, data loss, and/or program corruption when trying to

complete a specific task.

Preface v

Page 6

This page intentionally left blank.

vi Preface

Page 7

aTCA-6155

Table of Contents

aTCA-6155..................................................................................i

Revision History...................................................................... ii

Preface.................................................................................... iii

List of Figures........................................................................ xi

List of Tables........................................................................ xiii

1 Introduction ........................................................................ 1

1.1 Overview.............................................................................. 1

1.2 Block Diagram ..................................................................... 2

1.3 Package Contents ............................................................... 3

2 Specifications..................................................................... 5

2.1 CPU, Chipset, Memory........................................................ 5

2.2 Standards and Interface ...................................................... 6

2.3 Software............................................................................... 7

2.4 Mechanical & Environmental ............................................... 7

2.5 Power Consumption ............................ ... ............................. 8

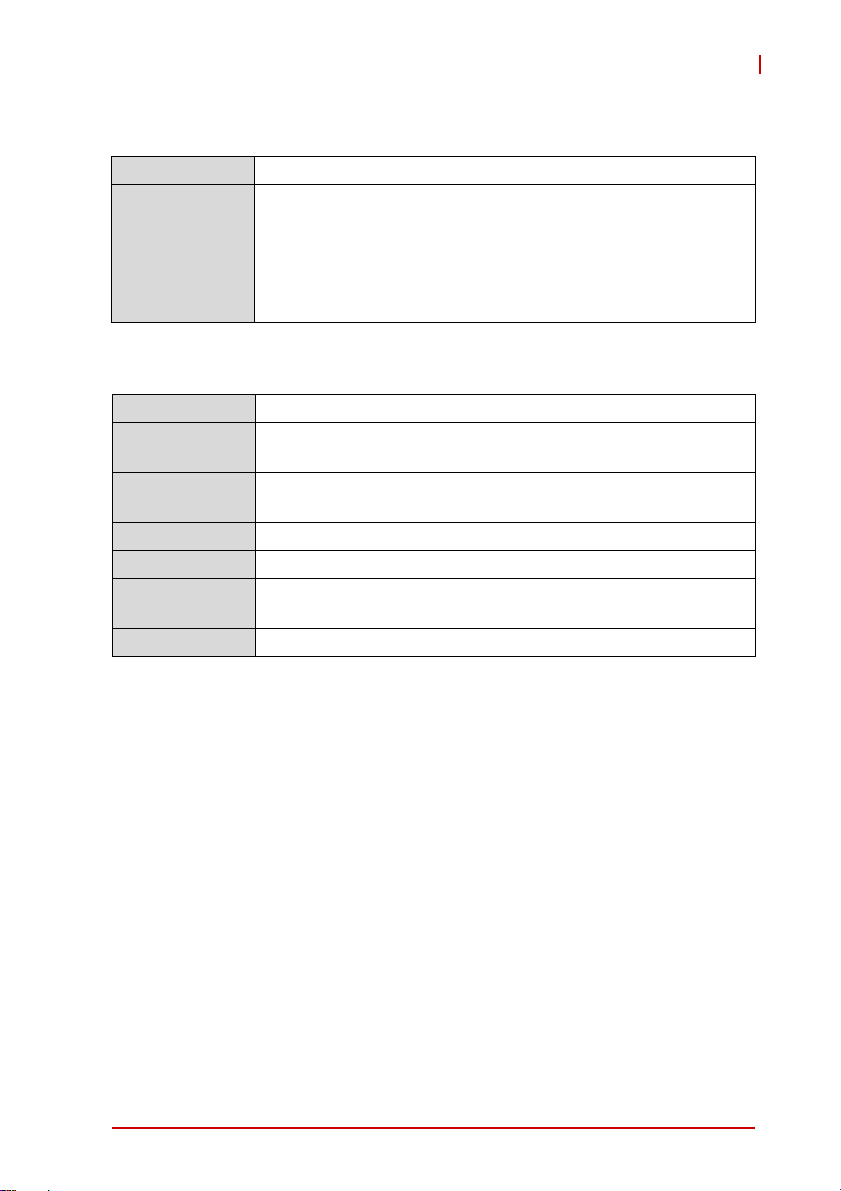

2.6 aTCA-6155 Board Layout.................................................... 9

2.7 aTCA-6155 Front Panel..................................................... 10

2.8 Compliance........................................................................ 12

3 Functional Description .................................................... 13

3.1 CPU, Memory and Chipset................................................ 13

3.2 Peripherals......................................................................... 17

3.3 I/O Interfaces ..................................................................... 21

3.4 Switches ............................................................................ 24

Table of Contents vii

Page 8

4 Hardware Platform Management..................................... 29

4.1 Platform Management Overview........................................ 29

4.2 IPMI Sensors ..................................................................... 29

4.2.1 Get Sensor Reading (FRU Hotswap Sensor)................33

4.2.2 Get Sensor Reading (Physical IPMB-0 Sensor)............34

4.2.3 Watchdog Timer Sensor...................................... ... ... ... .35

4.2.4 Version Change Sensor.................................................36

4.2.5 Get Sensor Reading Command.....................................38

4.3 IPMI Commands................................................................ 40

4.4 IPMI Firmware Upgrade Procedure................................... 43

5 Getting Started.................................................................. 47

5.1 Safety Requirements ................................................ ... ... ... 47

5.2 Installing the aTCA-6155 ................................................... 48

5.3 Removing the aTCA-6155 ................................................. 51

6 Driver Installation.............................................................. 53

6.1 Chipset Driver Installation.................................................. 53

6.2 LAN Driver Installation....................................................... 54

6.3 LAN Driver Installation....................................................... 55

6.4 VGA Driver Installation....................................................... 58

7 Watchdog Timer................................................................ 59

7.1 Overview............................................................................ 59

7.2 Sample Code..................................................................... 60

8 BIOS Setup........................................................................ 63

8.1 Starting the BIOS............................................................... 63

8.2 Main Setup......................................................................... 67

8.3 Advanced BIOS Setup....................................................... 68

8.3.1 CPU Configuration.........................................................69

8.3.2 Super IO Configuration..................................................71

8.3.3 Hardware Health Configuration .....................................72

viii Table of Contents

Page 9

aTCA-6155

8.3.4 USB Configuration.........................................................73

8.3.5 AHCI Configuration........................................................76

8.3.6 Remote Access Configuration....................................... 77

8.4 Advanced PCI/PnP Settings.............................................. 79

8.5 Boot Settings ..................................................................... 81

8.5.1 Boot Settings Configuration........ .... ... ... ... ... .... ... ... ... .... .. 82

8.6 Security Setup ................................................................... 84

8.7 Chipset Setup.................................................................... 87

8.8 Exit Menu........................................................................... 91

8.9 BIOS Update Procedure.................................................... 93

Important Safety Instructions.............................................. 95

Getting Service...................................................................... 97

Table of Contents ix

Page 10

This page intentionally left blank.

xTable of Contents

Page 11

aTCA-6155

List of Figures

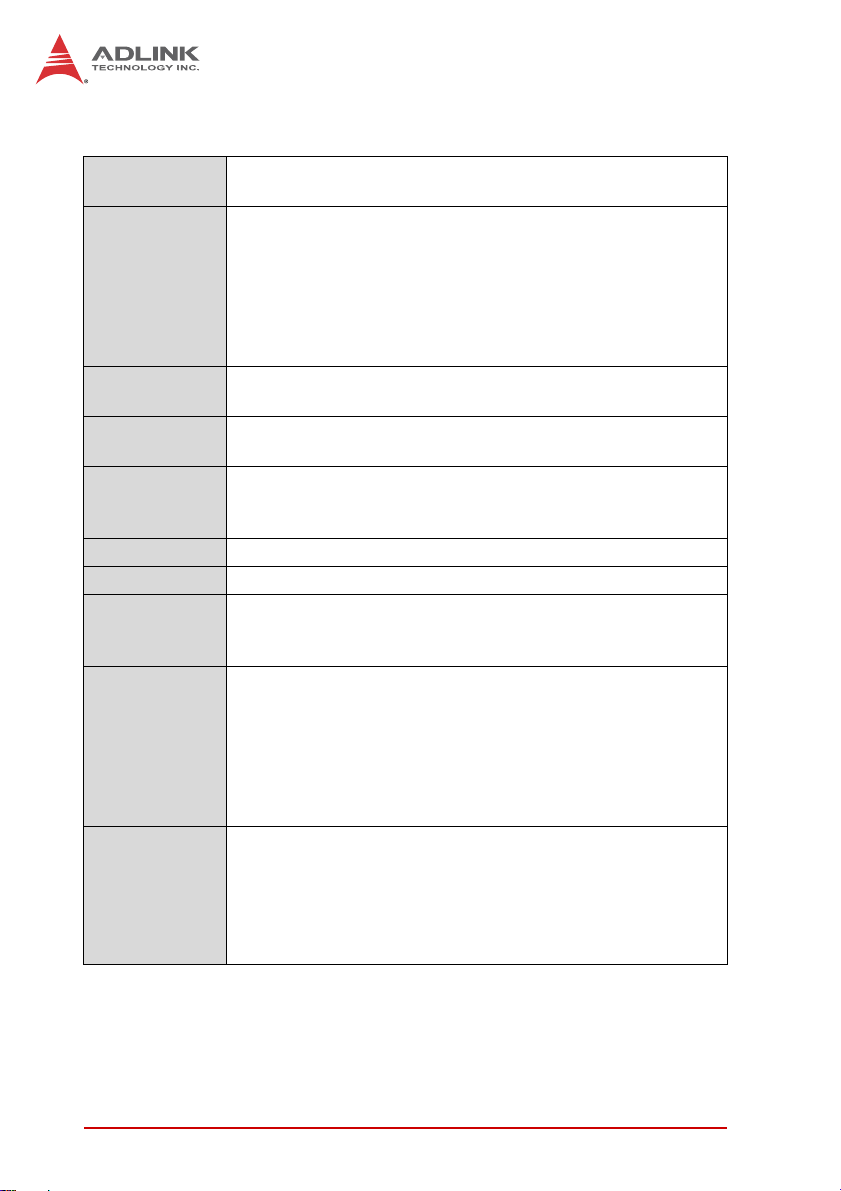

Figure 1-1: aTCA-6155 Functional Block Diagram ............................ 2

Figure 2-1: aTCA-6155 Board Layout................................................9

Figure 2-2: aTCA-6155 Front Panel..................................... ... ... .... .. 10

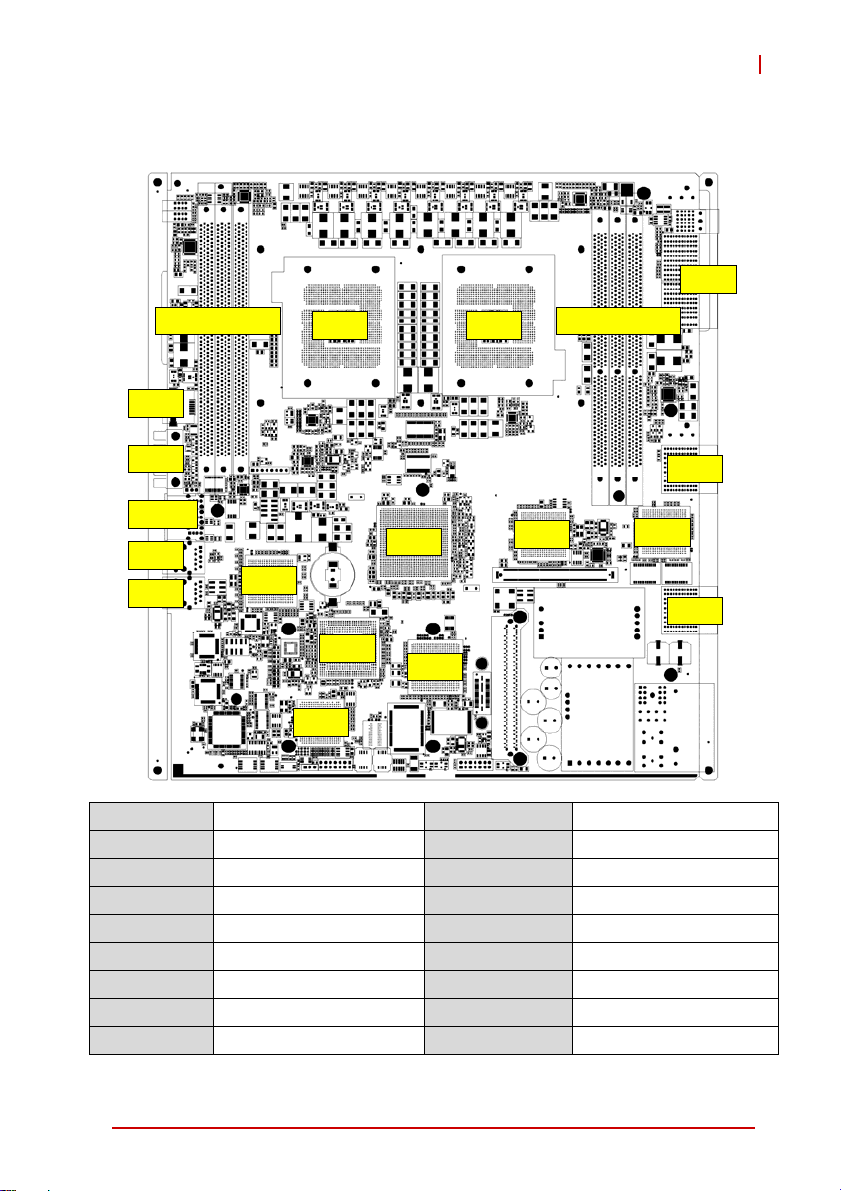

Figure 3-1: aTCA-6155 Switch Locations ...................................... .. 24

List of Figures xi

Page 12

This page intentionally left blank.

xii List of Figures

Page 13

aTCA-6155

List of Tables

Table 3-1: Front Panel USB Connector Pin Definition.................... 21

Table 3-2: VGA Connector Pin Definition........... ... ... ... .... ... ... ... .... .. 22

Table 3-3: COM1 Serial Port Connector Pin Definition...................23

Table 3-4: IPMC Debug Port Connector Pin Definition...................23

Table 3-5: Blade Operation Mode Switch Settings (Rev. A2)......... 25

Table 3-6: Blade Operation Mode Switch Settings (Rev. A3+).......25

Table 3-7: COM Mode Switch Settings (Rev. A2)...........................26

Table 3-8: COM Mode Switch Settings (Rev. A3 and higher).........26

Table 4-1: aTCA-6155 IPMI Sensors........... .... ... ... ... ....... ... ... ... .... .. 32

Table 4-2: Get Sensor Reading (FRU Hotswap Sensor)................33

Table 4-3: Get Sensor Reading (Physical IPMB-0 Sensor)............34

Table 4-4: Watchdog Timer Sensor................................................ 35

Table 4-5: Version Change Sensor................................................. 36

Table 4-6: Get Sensor Reading Command..................................... 39

Table 4-7: Supported IPMI Commands....... .... ... ... ... ... .... ... ... ....... .. 40

List of Tables xiii

Page 14

This page intentionally left blank.

xiv List of Tables

Page 15

1 Introduction

1.1 Overview

The aTCA-6155 is a highly integrated multi-core dual-processor

AdvancedTCA processor blade supporting six sockets for

DDR3-1066 VLP RDIMM up to 48GB maximum system mem ory

capacity. IO features include two 10Gigabit Ethernet ports (XAUI,

1000BASE-KX4) compliant with PICMG 3.1 option 1/9, four Gigabit Ethernet 10/100/1000BASE-T ports to the face plate and

AdvancedTCA Base Interface channels. More detailed features

are outlined below and a functional block diagram is shown in the

next section.

X Two Six-Cor e Intel® Xeon® Processor L5638 or Quad -Core

Intel® Xeon® Processor L5618

X Server-class Intel® 5520/ICH10R chipset

X DDR3-1066 JEDEC standard VLP RDIMM (REG/ECC),

up to 48GB

X Onboard 4GB bootable USB interface NAND flash

X Three Intel® 82576EB PCI-Express Gigabit Ethernet con-

trollers

X Intel® 82599EB PCI-Express 10Gigabit Ethernet (XAUI)

controller

X Dual PICMG 3.1 option 1/9 Fabric Interface channels

X Modular Fabric riser card for other PICMG Fabric Interface

protocols

X Failover system BIOS

X Analog UXGA high color graphics

aTCA-6155

Introduction 1

Page 16

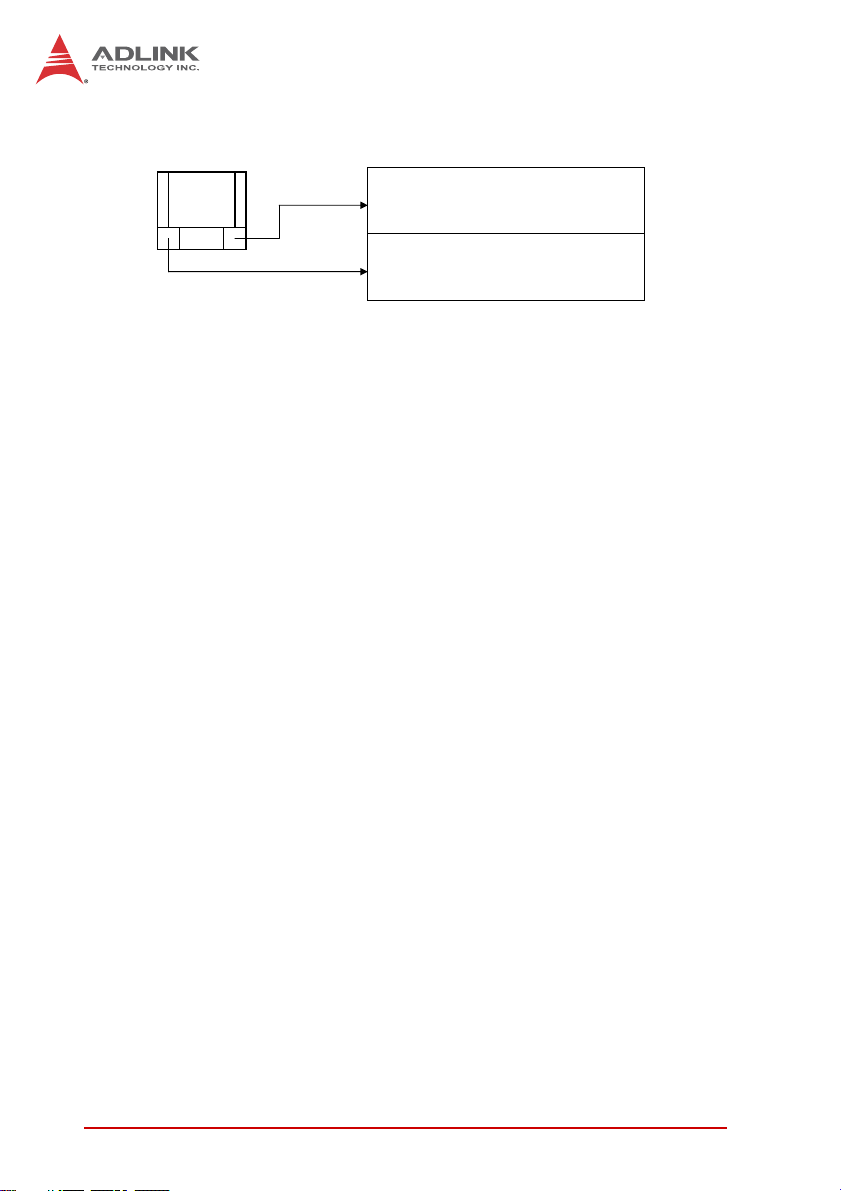

1.2 Block Diagram

DDR3Ͳ1066 RDIMM

DDR3Ͳ1066 RDIMM

DDR3Ͳ1066 RDIMM

MidͲSize

AMC

SAS 1/2/3 to RTM

F

R

O

N

T

P

A

N

E

L

RGB

USB1/2/3

COM1

SAS 0

To RTM

RTM

AMC.2 E2

AMC.2 T4

SAS1064E

PCI 32bit/33Mhz

ATI

ES1000

2.5" HDD

4GB NAND Flash

SATA x4,

USB5/6/7/8

NehalemͲEP

(5638/5618)

PCIͲE x4

PCIͲE x4

PCIͲE x4

Intel

CPU

QPI QPI

SATA

USB4

USB Header

USB Header

Intel

TylersburgͲ36D

(5520)

IOH

Intel

ICH10R

USB9

USB10

Intel

NehalemͲEP

(5638/5618)

CPU

PCIͲE x4

PCIͲE x8

PCIͲE x4

LPC

To RTM

Static

Switch

AMC.2 E2

AMC.2 T4

AMC.2 T4

Copper SerDes

Intel

82576EB

Copper SerDes

GbE 1/2 to Front Panel

BIOS BIOS

TPM

LPC

Super

I/O

COM2

COM3

COM4

DDR3Ͳ1066 RDIMM

DDR3Ͳ1066 RDIMM

DDR3Ͳ1066 RDIMM

SAS x3, SATA x4, USB5/6/7/8,

COM3, PCIͲE x4, SerDes x2

Intel

82576EB

Copper

SerDes

C

Port0

H

1

Port1

/

FRC

C

Port2

H

Port3

2

Intel

82576EB

UCH 1/2 SerDes

BCH 1/2

IPMC

BMRͲH8S

IPMB 0/1

RTM

Telecom Clock

FCH1/2

Z

O

N

E

3

Z

O

N

E

2

Z

O

N

E

1

Figure 1-1: aTCA-6155 Functional Block Diagram

2Introduction

Page 17

aTCA-6155

1.3 Package Contents

Before opening the product box, please check the shipping carton

for any damage. If the shipping carton and contents are damaged,

notify the dealer for a replacement. Retain the shipping carton and

packing material for inspection by the dealer. Obtain authorization

before returning any product to ADLINK.

Check that the following items are included in the package. If there

are any missing items, contact your dealer:

X aTCA-6155 AdvancedTCA processor blade (CPU, RAM

specifications will differ depending on options selected)

X RJ-45 to DB9 cable

This product must be protected from static discharge and physical shock. Never remove any of the components except at a

CAUTION:

static-free workstation. Use the anti-static bag shipped with the

product when putting the board on a surface. Wear an anti-static

wrist strap properly grounded on one of the system's ESD ground

jacks when installing or servicing system components.

Introduction 3

Page 18

This page intentionally left blank.

4Introduction

Page 19

2 Specifications

2.1 CPU, Chipset, Memory

CPU • SIx-core Intel® Xeon® Processor L5638 (2.00GHz

QPI 5.86GT/s, 12MB L2 cache, LGA1366 package)

• Quad-core Intel® Xeon® Processor L5618 (1.87GHz

QPI 5.86GT/s, 12MB L2 cache, LGA1366 package)

Chipset • Intel® 5520/ICH10R chipset

Memory • Registered ECC DDR3-1066 SDRAM

• Six RDIMM sockets

• Up to 48GB

aTCA-6155

Specifications 5

Page 20

2.2 Standards and Interface

Standards • PICMG 3.0 R2.0 AdvancedTCA

• PICMG 3.1 AdvancedTCA Ethernet option 1/9

Networking • Three dual-port Intel® 82576EB Gigabit Ethernet

controllers

• Four 10/100/1000BASE-T ports (2 on face plate and

2 on Base Interface channels 1-2)

• Two SerDes ports on Zone 3 to RTM

• Dual 10GBASE-KX4 Fabric Interface Channels via

Intel® 82599EB on aDB-6100 riser card

Serial ATA • Five Serial ATA II ports from ICH10R, one onboard,

four to RTM

Serial Attached

SCSI

Display • ATI ES1000 graphics controller with 2D accelerator

USB • Three USB 2.0 ports on front panel, four ports to RTM

Serial • One RJ-45 RS-232 port

Storage • On-board 4GB USB NAND Flash

Front Panel I/O • 1x VGA port (DB-15)

Rear I/O • PCI-E x4 from Intel 5520

• Four SAS ports from LSISAS1064E, one to AMC, three to

RTM

• DDR2-533 64MB memory

• Analog RGB up to 1600x1200@75Hz refresh rate

• AMC.3 SAS

• Four SATA and three SAS ports on RTM

• 3x USB 2.0 port (Type-A)

• 1x RS-232 port (RJ45)

• 2x GbE ports (RJ45)

• 1x AMC bay (aTCA-6155A only)

• LEDs: OOS, Media, User and Hotswap

• Recessed reset button

• 1x COM port

• 4x USB 2.0 ports

• 4x SATA ports from ICH10R

• 3x SAS/SATA ports from LSISAS1064E

• 2x SerDes ports

6 Specifications

Page 21

aTCA-6155

2.3 Software

BIOS • AMI® BIOS with 8Mbit flash memory

Supported OS • Microsoft® Windows® Server 2003

• Microsoft® Windows® Server 2008

• Microsoft® Windows® Server 2008 R2

• RedHat Enterprise Linux Release 5.4

• MontaVista Linux Carrier Grade Edition 4.0

• Contact ADLINK for other OS availability

2.4 Mechanical & Environmental

Dimensions • 322.25mm x 280mm x 30.48mm (H x D x W) - 6HP slot

Operating

T emperature

Storage

T emperature

Humidity • 5% to 90% non-condensing

Shock • 15G peak-to-peak, 11ms duration, non-operation

Vibration • Non-operating: 1.88G rms, 5 to 500 Hz, each axis

Compliance • CE, FCC Class A, CUL, NEBS Level 3 (design)

• Standard: 0°C to 50°C

• NEBS short-term: 0°C to 55°C

• -40°C to 85°C

• Operating: 0.5G rms. 5 to 500Hz, each axis

Specifications 7

Page 22

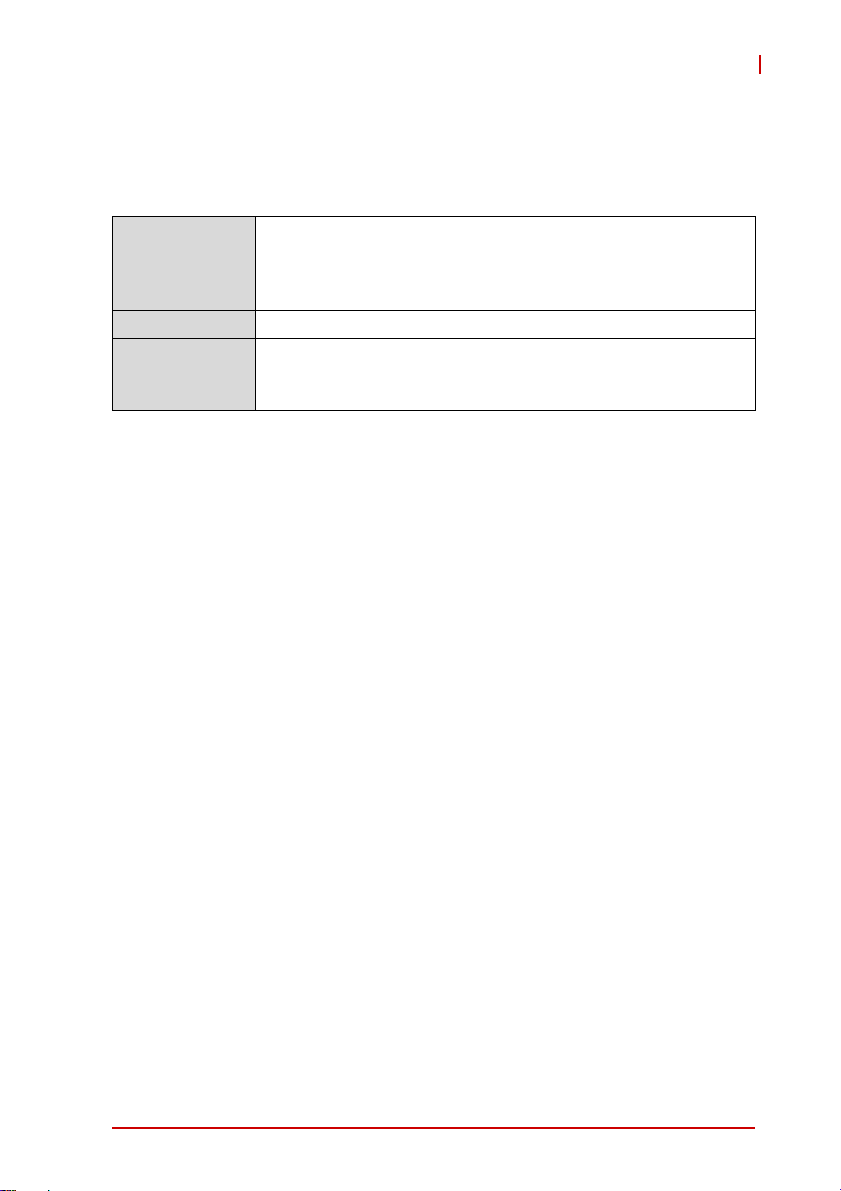

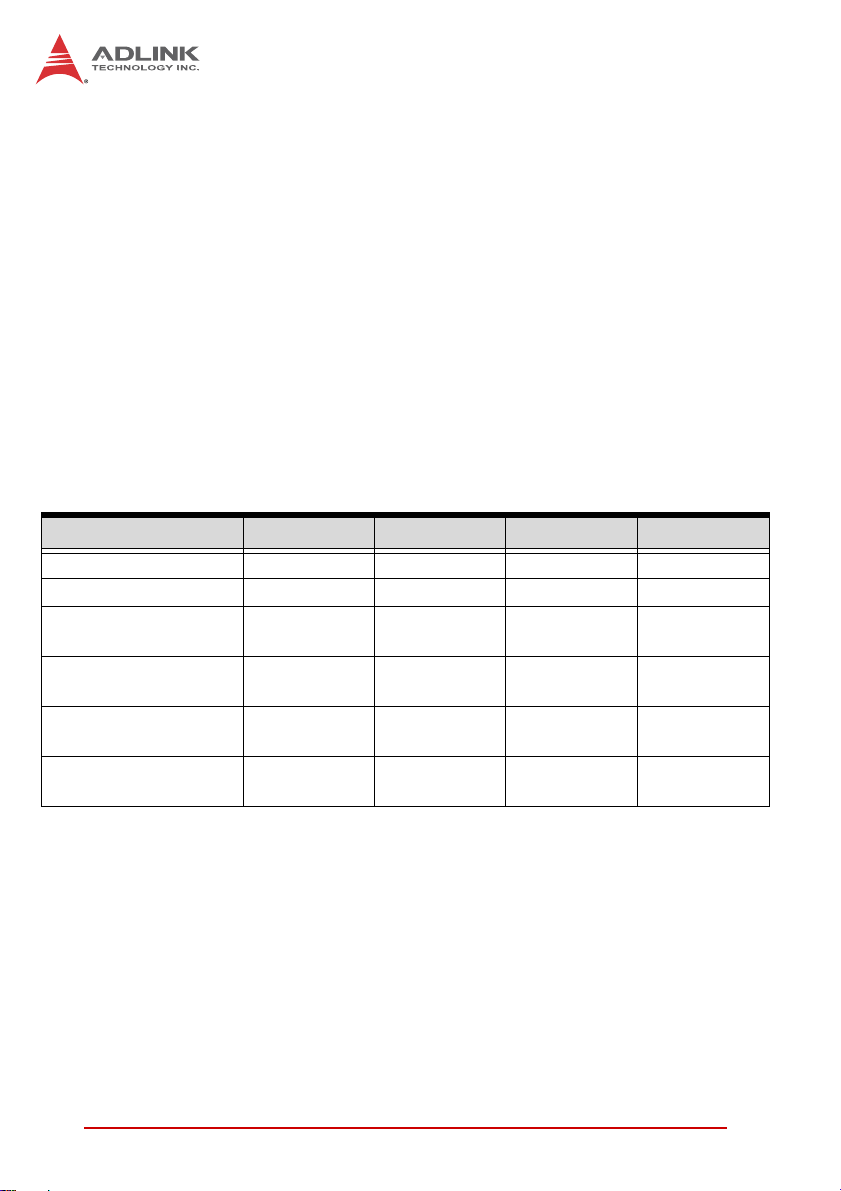

2.5 Power Consumption

This section provides information on the power consumption of

aTCA-6155.

System Configuration

X Memory: 2G DDR3-1066 ECC REG x6

X Graphics: ATI ES1000

X Power Supply: Sunpower SPS-600P-48

X CPU:

Z Six-core Intel® Xeon® processor L5638

Z Quad-core Intel® Xeon® process or L56 1 8

The following table describes power consumption of the

aTCA-6155 using real applications with a 48V power rail under

various operating systems.

OS vs. CPU L5638 CPU x1 L5638 CPU x2 L5618 CPU x1 L5618 CPU x2

DOS 89.7 W 138.6 W 80.8 W 121.1 W

Linux, Idle 65.9 W 108.1 W 64.3 W 101.7 W

Windows Server 2003,

Idle

Windows Server 2003,

CPU 100% Usage

Windows Server 2008,

Idle

Windows Server 2008,

CPU 100% Usage

76.1 W 109.2 W 72. 2 W 104.1 W

105.6 W 174. 4 W 88.4 W 136.3 W

53.6 W 106.5 W 55.0 W 99.4 W

104.2 W 171.2 W 89.6 W 134.4 W

8 Specifications

Page 23

2.6 aTCA-6155 Board Layout

aTCA-6155

J3-J4

DIMM C/B/A

CPU0 CPU1

DIMM D/E/F

CN8

CN10

J2

CN2-4

U27

CN16

CN15

U23

U4

U174

J1

U9

U29

U41

CPU1, CPU2 CPU1/2 processors CN16 1GbE Ethernet port

DIMM A/B/C DDR3-1066MHz (CPU0) CN15 1GbE Ethernet port

DIMM D/E/F DDR3-1066MHz (CPU1) U23 Intel 82576EB

J1 Base Interface U4 Intel 5520

J2 Fabric Interface U174 Intel 82576EB

J3-J4 Zone 3 to RTM U27 Intel 82576EB

CN8 COM port U9 Intel ICH10R

CN10 DB-15 VGA connector U29 LSISAS1064E controller

CN2-4 USB ports U41 ATI ES1000 graphics

Figure 2-1: aTCA-6155 Board Layout

Specifications 9

Page 24

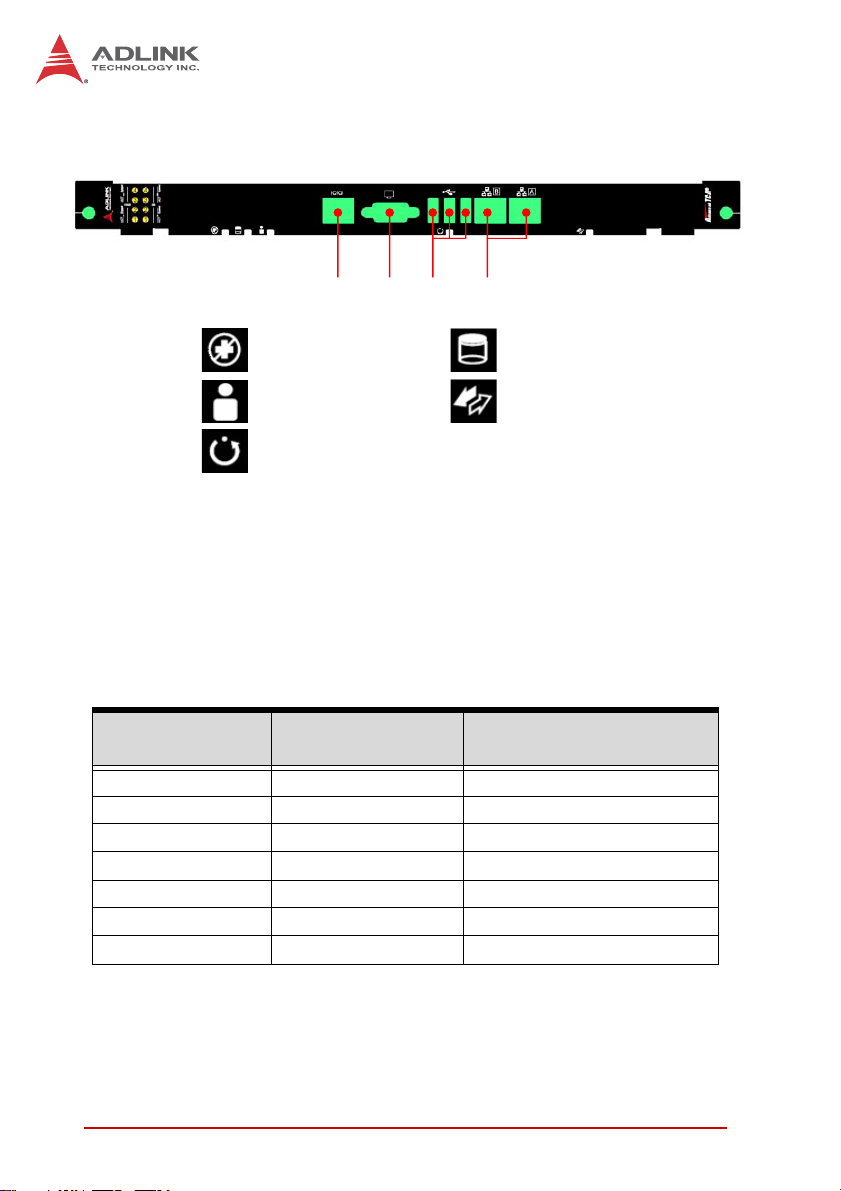

2.7 aTCA-6155 Front Panel

VGA

USB

GbE

COM

Out of Service LED (Red) Media LED (Green)

User LED (Amber) Hot-swap LED (Blue)

Reset buon

Figure 2-2: aTCA-6155 Front Panel

LED Definitions

The following shows the LED in the front panel which included the

Hot-swap LED, User LED, Media LED, and OOS LED.

Hot-swap LED

Hot-swap LED

(Blue)

Off M0 FRU not installed

On M1 FRU inactive

Long blink M2 FRU activation request

Off M3 FRU activation in process

Off M4 FRU active

Short blink M5 FRU deactivation reque st

Short blink M6 FRU deactivation in process

FRU State number FRU State Name

10 Specifications

Page 25

Out of Service LED

OOS LED (Red) State Remark

Blink During BIOS POST FRU State M4

Off BIOS POST OK FRU State M4

On After OS shutdown FRU State M1

Media LED

Media LED (Green) State Remark

Blink Accessing Disk I/O

Off Disk I/O idle

User LED

User LED (Amber) State Remark

This LED is reserved for

On Default On

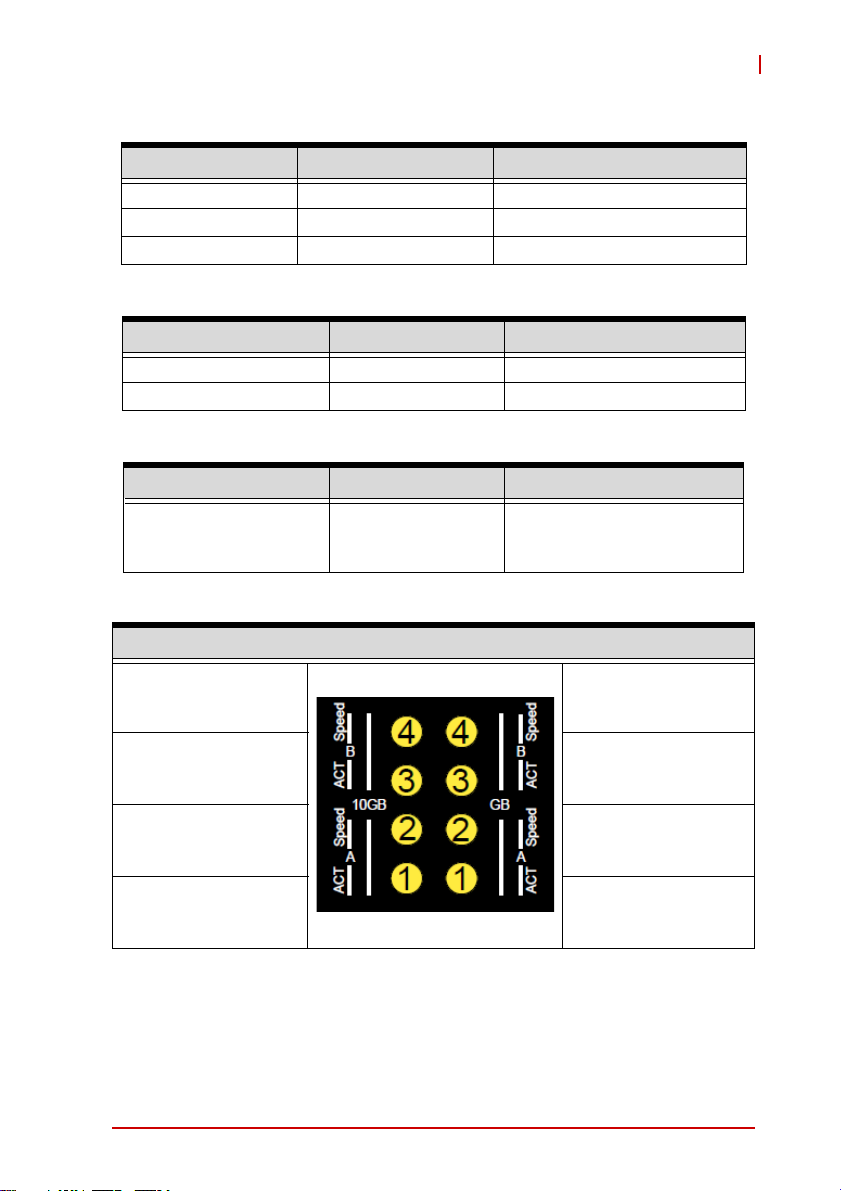

Base Fabric Channel LED

BASE Channel and Fabric Channel LED

Fabric 2 Speed/Link

1Gbps – OFF

10Gbps – ON (Amber)

Fabric 2 ACT (Amber)

Blink when accessing

Ethernet I/O

Fabric 1 Speed/Link

1Gbps - OFF

10Gbps – ON (Amber)

Fabric 1 ACT (Amber)

Blink when accessing

Ethernet I/O

customer applications and

can be controlled via GPIO.

BCH2 Speed/Link

100 Mbps: Green

1Gbps: Amber

BCH2 ACT (Amber)

Blink when accessing

Ethernet I/O

BCH1 Speed/Link

100 Mbps: Green

1Gbps: Amber

BCH1 ACT (Amber)

Blink when accessing

Ethernet I/O

aTCA-6155

Specifications 11

Page 26

GbE LED

LED2: Speed and Link

RJ-45

1Gbps: Amber,

100Mbps: Green

LED1: ACT

Blinking when accessing I/O

Color: Amber

2.8 Compliance

The aTCA-6155 conforms to the following specifications:

X PICMG 3.0 R2.0 ECN0002 AdvancedTCA

X PICMG 3.1 Ethernet over AdvancedTCA option 1 and 9

X AMC.0 Advanced Mezzanine Card R2.0 Midsize

X AMC.1 PCI Express R1.0

X AMC.2 E2 / Type 4

X AMC.3 Storage R1.0

12 Specifications

Page 27

3 Functional Description

3.1 CPU, Memory and Chipset

Supported Processors

Six-core Intel® Xeon Processor L5638

Quad-core Intel® Xeon Processor L5618

The Intel Xeon® processor 5600 series is the first generation

dual-processor server/workstation solution to implement key new

technologies:

X Integrated Memory controller

X Point-to-point link interface based on Int el® QuickPath

Interconnect (Intel® QPI)

The processor is optimized for performance with the power efficiencies of a low-power micro-architecture to enable smaller, quieter systems.

The Intel® Xeon processors L5638 and L5618 are multi-core processors based on 32 nm process technology. Processor features

include two Intel® QPI point-to-point links with 5.86GT/s, 12MB of

shared cache, and an integrated memory controller. The processors support all the existing Streaming SIMD Extensions 2 (SSE2),

Streaming SIMD Extensions 3 (SSE3) and Streaming SIMD

Extensions 4 (SEE4). Also supported are: Execute Disable Bit,

Intel® 64 Technology, Enhanced Intel® SpeedStep Technology,

Intel® Virtualization Technology (Intel® VT), and Intel®

Hyper-Threading Technology.

aTCA-6155

The Intel® Xeon® Processor L5638 has a max. TDP of 60 W and

the Intel® Xeon® Processor L5618 has a max. TDP of 40 W. Both

processors have an elevated case temperature specification. The

elevated case temperatures are intended to meet the short-term

thermal profile requirements of NEBS Level 3. These 2-socket

processors are ideal for thermally constrained form factors in

embedded servers, communications and storage markets.

Functional Description 13

Page 28

Supported Processors, Maximum Power Dissip ation

The following tables describe the processors supported on the

aTCA-6155 and their maximum power dissipation.

Intel® L5638 Intel® L5618

L2 cache 12 MB 12 MB

Clock 2.00 GHz 1.87 GHz

QPI 5.86 GT/s 5.86 GT/s

Max. Power 60 W 40 W

Memory

The aTCA-6155 supports DDR3-1066 RDIMM in six sockets

(3 per processor) up to 48GBytes. The available COTS

DDR3-1066 RDIMM densities are 1 GB, 2GB, 4GB and 8GB.

Memory configuration changes can only be performed at the

factory. Failure to comply with the above may result in damage

NOTE:

NOTE:

to your board or improper operation.

14 Functional Description

Page 29

aTCA-6155

Chipset

Intel® 5520/ICH10R Chipset Overview

The Intel® 5520 Chipset I/O Hub (IOH) provides a connection

point between various I/O components and Intel® QuickPath In terconnect (Intel® QPI) based processors. The Intel® 5520 Chipset

is combined with Intel® Xeon® Processor 5500 in their respectiv e

two socket platforms. The Intel® Xeon® 5500 Platform consists of

the Intel Xeon Processor 5500 Series, the Intel 5520 Chipset I/O

Hub (IOH), the I/O Controller Hub (Intel® ICH10), and the I/O subsystem. The processor includes an integrated Memory Controller

(IMC) that resides within the proc essor package. This platform is

the first single processing platform that introduces the Intel QuickPath Interconnect. Intel QuickPath Interconnect is Intel’s next generation point-to-point system interconnect interface and replaces

the Front Side Bus.

The term IOH refers to the Intel 5520 Chipset I/O Hub (IOH)

and ICH10R refers to the Intel® 82801JIR ICH10R I/O

NOTE:

NOTE:

The IOH provides the interface between the processor Intel QuickPath Interconnect and industry-standard PCI Express components. The two Intel QuickPath Interconnect interfaces are

full-width links (20 lanes in each direction). The two x16 PCI

Express Gen2 ports are also configurable as x8 and x 4 links com pliant to the PCI Express Base Specification, Revision 2.0. The

single x4 PCI Express Gen2 port can bifurcate into two independent x2 interfaces.In addition, the legacy IOH supports a x4 ESI

link interface for the legacy bridge. The IOH supports the following

features and technologies:

Controller Hub 10 components.

X Intel® QuickPath Interconnect profile

X Interface to CPU or other IOH (limited configurations) PCI

Express Gen2

X Intel® I/O Accelerated Technology (In tel® I/OAT) and Intel®

Quick Data Technology (updated DMA engine with virtualization enhancements)

X Integrated Intel® Management Engine (Intel® ME)

Functional Description 15

Page 30

ATI ES1000 Graphics Controller

The aTCA-6155 provides an analog VGA port on the front panel

powered by an AMD ES1000 2D graphics controller with the following features:

X 32-bit PCI bus (Rev 2.2), 3.3 V with bus mastering support

X Support for SPI Serial and Flash Memory video BIOS

X One CRT controller capable of supporting two identical

simultaneous display paths

X Dual integrated DACs for CRT display support

X Support for external TMDS transmitter via 24-bit digital out-

put to drive most popular TMDS transmitters up to 165MHz

frequency

X Independent DDC lines for both DACs and TMDS connec-

tions; also full AppleSense support on DAC connection

X Static and dynamic Power Management support (APM as

well as ACPI) with full VESA DPMS and Energy Star com-

pliance

X Comprehensive testability including full internal scan, mem-

ory BIST, I/O xor tree and Iddq

X Full ACPI 1.0b, OnNow, and IAPC (Instantly Available PC)

power management, including PCI power management reg-

isters

X Bi-endian support for compliance on a variety of processor

platforms

X Bus mastering of 2D display lists

X Triple 10-bit palette DAC supports pixel rates to 350MHz

X DDC1 and DDC2 for plug and play monitors

X Flexible memory support:

Z DDR1 and DDR2 SDRAM and SGRAM

Z 16-bit interface

Z 8MB to 256MB

X Up to 1GB/s bandwidth.

X Single chip solution in 0.13 micron process, 1.2V CMOS

technology in a BGA package

16 Functional Description

Page 31

aTCA-6155

3.2 Peripherals

The following standard peripherals are available on the

aTCA-6155 blade:

Timer

The aTCA-6155 is equipped with the following timers:

X Real-Time Clock: The ICH10R contains a real-time clock

that performs timekeeping functions and includes 256 bytes

of general purpose battery-backed CMOS RAM. Features

include an alarm function, programm abl e pe r iod ic inte rr up t

and a 100-year calendar. All battery-backed CMOS RAM

data remains stored in an additional EEPROM. This prevents data loss in case the aTCA-6155 is operated without

battery.

X Counter/Timer: Three 8254-style counter/timers are

included on the aTCA-6155 as defined for the PC/AT (System Timer, Refresh Request, Speaker Tone Output).

X High Precision Event Timers (HPET): In addition to the

three 8254-style counters, the ICH10R includes three High

Precision Event Timers (HPET) that may be used by the

operating system. They can be used in one-shot and periodic modes to generate an interrupt when the counter

reaches a pre-programmed value.

Watchdog Timer

The aTCA-6155 provides a Watchdog Timer that is programmable

for a timeout period ranging from 1 to 255 minutes, or 1 to 255

seconds. Please refer to “Watchdog Timer” on page 59 for a

detailed programming guide.

Functional Description 17

Page 32

Battery

The aTCA-6155 is equipped with a 3.0 V “coin cell” lithium battery

for the RTC. To replace the battery, proceed as follows:

X Turn off power

X Remove the battery

X Place the new battery in the socket

Make sure that you insert the battery with the correct orientation.

The positive pole must be on the top

The lithium battery must be replaced with an id entical b attery

or a battery type recommended by the manufacturer. A suitable

battery is the Panasonic CR2032.

The user must be aware that the battery’s operational temperature range is less than that of the aTCA-6155’s storage temper-

NOTE:

NOTE:

NOTE:

NOTE:

ature range. For exact temperature range information, refer to

the battery manufacturer’s specifications.

Care must be taken to ensure that the battery is correctly

replaced. The battery should be replaced only with an identical

or equivalent type recommended by the manufacturer. Dispose

of used batteries according to the manufacturer’s instructions.

The typical life expectancy of a 225mAh battery is 4-5 years

with an average on-time of 8 hours per working day at an operating temperature of 30°C. However, this typical value varies

considerably because the life expectancy is dependent on the

operating temperature and standby (shutdown) time of the system in which it operates. To ensure that the lifetime of the battery has not been exceeded, it is recommended to change the

battery after 3-4 years.

18 Functional Description

Page 33

aTCA-6155

Reset

The aTCA-6155 is automatically reset by a precision voltage monitoring circuit that detects a drop in voltage below the acceptable

operating limit of 4.85V for the 5V line and below 3.2V for the 3.3V

line. Other reset sources include the Watchdog Timer, the face

plate push-button switch and also the RESET signal from the

IPMC. The aTCA-6155 responds to any of these sources by initializing local peripherals.

A reset will be generated by the following conditions:

X Power failure, +5 V supply falls below 4.1 V (typ.) or +3.3 V

supply falls below 2.93 V (typ.)

X Pushbutton ´RESET" pressed

X Watchdog time-out

X IPM controller reset

SMBus and I2C Devices

The aTCA-6155 provides a System Management Bus (SMBus)

hosted by the ICH10R and an I2C bus hosted by the IPM controller, H8S/2168. The following table describes the function and

address of the devices.

SMBus Device Address (HEX) I2C Device Address (HEX)

DIMM A 0xA0 PECI-to-I2C 0x92

DIMM B 0xA4 LM75 0x9E

DIMM C 0xA8 PCA9555PW 0x40

DIMM D 0xA0 Fabric Riser Card 0xAE

DIMM E 0xA4

DIMM F 0xA8

Clock Gen 0xD2

Clock Buffer 0xDC

Functional Description 19

Page 34

GPIO List

The following table summarizes GPIO usage on ICH10R:

ICH10R I/O Signal Description

GPI[2] Input IOH_ERR-L

GPI[8] Input QPI_TTL_CATERR-L

GPI[23] Output USR_LED

GPI[27] Output QPI_FREQSEL0

GPI[28] Output QPI_FREQSEL1

GPI[29] Output FM_CPU0_LVDDR3_EN

GPI[30] Output FM_CPU1_LVDDR3_EN

GPI[32] Output POSTOK-L

GPI[52] Output ICH_SMBUS_MUX0

GPI[53] Output ICH_SMBUS_MUX1

GPI[56] Output QPI_FSEL_PWRGD-L

IOH Error output signals

CPU Indicates that the system

has experienced a catastrophic

error and cannot continue to

operate

User defined LED

QuickPath Interconnect

Frequency Strapping Options

QuickPath Interconnect

Frequency Strapping Options

DDR3L DIMM voltage control

(DIMM A/B/C)

DDR3L DIMM voltage control

(DIMM D/E/F)

POST OK to IPMC

DDR SMBUS Multiplier control

DDR SMBUS Multiplier control

IOH Hard Reset Triggers a

Power-Up Reset control

20 Functional Description

Page 35

aTCA-6155

3.3 I/O Interfaces

USB

The aTCA-6155 supports eight USB 2.0 ports:

X three Type-A ports on front panel

X four ports routed to RTM

X one channel for 4GB on-board NAND flash

On the USB 2.0 front panel port, a USB cable with up to 5 meters

in length can be used.

On the USB 2.0 Rear I/O ports, it is strongly recommended to use

a cable below 3 meters in length for USB 2.0 devices.

The USB 2.0 ports are high-speed, full-speed, and low-speed

capable. Hi-speed USB 2.0 allows data transfers of up to

480 Mb/s, 40 times faster than a full-speed USB (USB 1.1). One

USB peripheral may be connected to each port.

Front Panel USB Connector (CN9-11)

Pin # Signal Name

1Vcc

2 Data3 Data+

4GND

Ta ble 3-1: Front Panel USB Connector Pin Definition

The aTCA-6155 host interfaces can be used with maximum

500mA continuous load current as specified in the Universal

NOTE:

NOTE:

Functional Description 21

Serial Bus Specification, Revision 2.0. Short circuit protection

is provided. All the signal lines are EMI filtered.

Page 36

VGA Analog Interface

The DB-15 female connector CN10 is for analog display output.

DB-15 VGA Connector (CN10)

Signal Name Pin # Pin # Signal Name

Red 1 9 +5 V

Green 2 10 Ground

Blue 3 11 NC

NC 4 12 DDC_DATA

Ground 5 13 HSYNC

Ground 6 14 VSYNC

Ground 7 15 DDC CLK

Ground 8

Table 3-2: VGA Connector Pin Definition

Gigabit Ethernet

The aTCA-6155 is equipped with three dual-port Intel® 82571EB

Gigabit Ethernet controllers, which provide a total of six GbE ports

onboard. In default configuration, two ports are connected to the

front panel and two ports are connected to the Base Interface

channels. The third controller provides two 1GB Fiber Channels

(routed to SERDES links to the RTM if no riser card installed).

The aDB-6155-A Fabric riser card provides the capability to support different configurations for Fabric Channels 1 and 2. An

aDB-6155-A will be installed on the aTCA-6155 by default. An

Intel 82599EB Ethernet controller on the riser card connects to the

IOH via a PCI-E x8 interface and provides 10GbE link s to Fabric

Channels 1 and 2 (FCH1/FCH2).

22 Functional Description

Page 37

aTCA-6155

Serial Port

One PC-compatible serial RS-232, RJ45 port is provided on the

front panel with DIP switches SWX1 and SWX2 on the board that

are used to set the COM port function to RS-232 mode or IPMC

debug mode. A complete set of handshaking and modem control

signals are supported, with data transfer rates up to 115.2 kB/sec.

The Front Panel RJ45 COM connector CN8 pin-assignment is

listed below.

COM Serial Port Connector (RJ45)

Pin # Signal Function

1 DCD# Data Carrier Detect

2 RTS# Request to Send

3 DSR# Data Set Ready

4 TXD Transmit Data

5 RXD Receive Data

6 GND Ground

7 CTS# Clear to Send

8 DTR# Data Terminal Ready

Table 3-3: COM1 Serial Port Connector Pin Definition

When the Front Panel RJ45 COM connecto r is se t to IPMC debug

mode, the pin assignment of the RJ45 connector is as below.

Pin # Signal Function

1 NC Not connected

2 NC Not connected

3 NC Not connected

4 DBG_TX IPMC Transmit Data

5 DBG_RX I PMC Receive Data

6 GND Ground

7 NC Not connected

8 NC Not connected

T able 3-4: IPMC Debug Port Connector Pin Definition

See “COM Mode Switch Settings (SWX1 and SWX2)” on page 26

for DIP switch settings.

Functional Description 23

Page 38

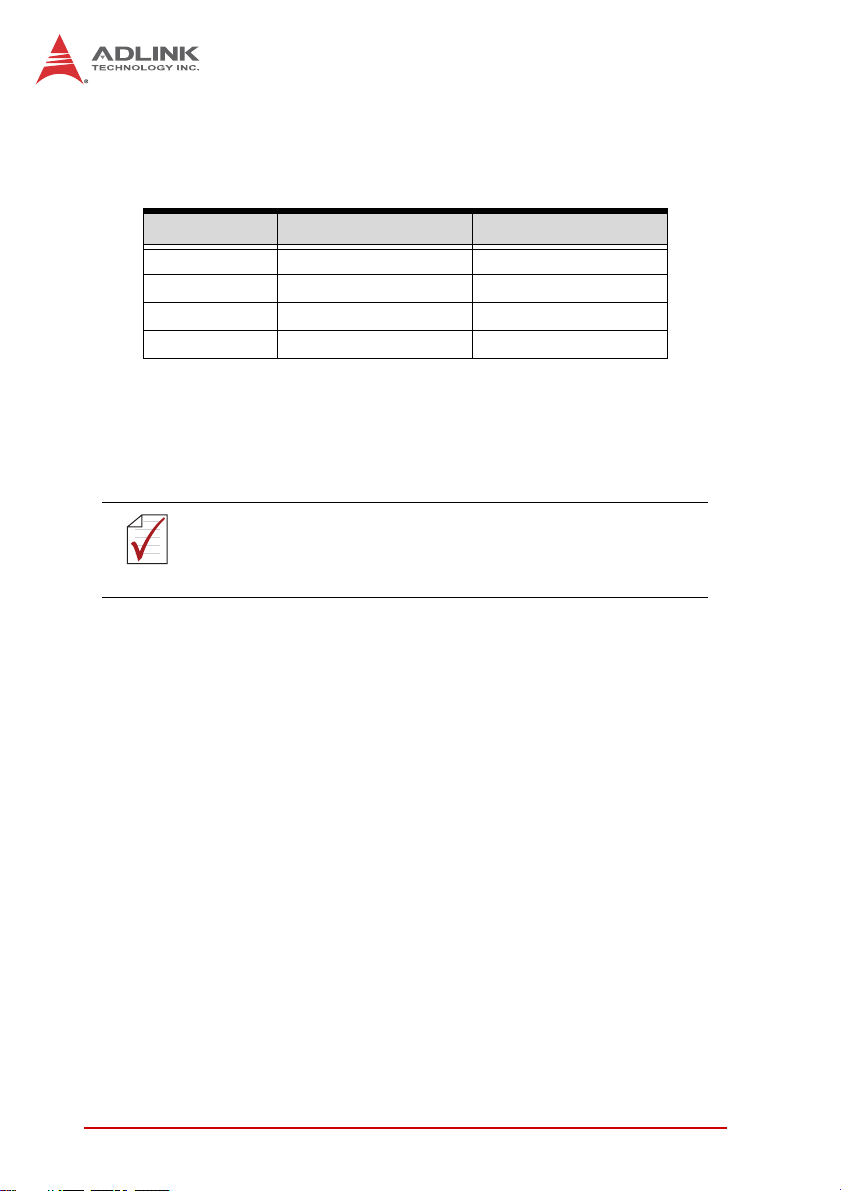

3.4 Switches

Switch SW1 is for Blade Operation Mode Control (Pins 1 & 2) and

PICMG 3.1 Option Control (Pins 3 & 4). Switch SW2 is for debugging purposes. Switches SWX1 and SWX2 are used to set the

COM port function to RS-232 mode or IPMC debug mode. SW7 is

provided to clear CMOS.

SWX1

SW2 SW1 SWX2 SW7

Figure 3-1: aTCA-6155 Switch Locations

24 Functional Description

Page 39

aTCA-6155

SW1 - Blade Operation Mode Control

Normal operation requires a shelf manager for the blade to

boot. Standalone mode allows the blade to boot without a shelf

manager. There are different switch settings for PCB Revisions

A2 and A3 onwards.

Options Pin 1 Pin 2

Normal mode* OFF OFF

Standalone mode OFF ON

Table 3-5: Blade Operation Mode Switch Settings (Rev. A2)

Options Pin 1 Pin 2

Normal mode* ON OFF

Standalone mode ON ON

Table 3-6: Blade Operation Mode Switch Settings (Rev . A3 and higher)

* Default

Pin 1 on SW1 is used to identify the PCB version to the IPMC.

On PCB Rev. A2, the IPMC can only detect the processor

NOTE:

NOTE:

nearest the front panel for temperature and voltage monitoring.

From PCB Rev. A3 onwards, the IPMC can detect both processors automatically.

SW1 - PICMG 3.1 Option Control

Options Pin 3 Pin 4

PICMG 3.1 Opt. 1 OFF OFF

PICMG 3.1 Opt. 9* ON OFF

* Default

Functional Description 25

Page 40

SW2 - Debug use only

Switch SW2 is for debugging purposes. For normal operation,

leave the switch in the default settings.

SW2 Pin 1 Pin 2 Pin 3 Pin 4

Default Setting OFF OFF OFF OFF

X Pin 1: ON for FWE pin protection; OFF for Normal operation

X Pin 2: ON for Slave SPI; OFF for Master SPI

IPMC Mode Select:

Z Pin 3: ON for Program mode; OFF for Normal mode

Z Pin 4: ON for Program mode; OFF for Normal mode

COM Mode Switch Settings (SWX1 and SWX2)

Switches SWX1 and SWX2 are used to set the COM port function to RS-232 mode or IPMC debug mode. There are different

switch settings for PCB Revisions A2 and A3 onwards.

Mode Switch Pin 1 Pin 2 Pin 3 Pin 4

RS-232 port

(default)

IPMC debug port

SWX1 ON ON OFF OFF

SWX2 OFF ON N/A

SWX1 OFF OFF ON ON

SWX2 ON OFF N/A

Table 3-7: COM Mode Switch Settings (Rev. A2)

Mode Switch Pin 1 Pin 2 Pin 3 Pin 4

RS-232 port

(default)

IPMC debug port

T able 3-8: COM Mode Switch Settings (Rev. A3 and higher)

26 Functional Description

SWX1 ON ON OFF OFF

SWX2 ON OFF N/A

SWX1 OFF OFF ON ON

SWX2 OFF ON N/A

Page 41

aTCA-6155

SW7 - Clear CMOS

SW7 is provided to clear CMOS. Press the switch to clear the

CMOS and reset the BIOS values to default.

Functional Description 27

Page 42

This page intentionally left blank.

28 Functional Description

Page 43

4 Hardware Platform Management

4.1 Platform Management Overview

The purpose of the hardware platform management system is to

monitor, control, and assure proper operation of AdvancedTCA®

Boards and other Shelf components. The hardware platform management system watches over the basic health of the system,

reports anomalies, and takes corrective action when needed. The

hardware platform management system can retrieve inventory

information and sensor readings as well as receive event reports

and failure notifications from Boards and other Intelligent FRUs.

The hardware platform management system can also perform

basic recovery operations such as power cycle or reset of managed entities.

The IPMC controller on the aTCA-6155 supports an “intelligent”

hardware management system, based on the Intelligent Platform

Management Interface Specification. The hardware management

system provides the ability to manage the power, cooling, and

interconnect needs of intelligent devices; to monitor events; and to

log events to a central repository.

aTCA-6155

4.2 IPMI Sensors

Following table lists all the sensors supported by the aTCA-6155.

Item

(1) Hotswap (0x0) FRU Hotswap Sensor. Please refer to section 4.2.1

(2)

(3)

(4)

(5)

(6)

Sensor

Name

Shelf FRU

Hotswap

Hotswap

AMC 1

RTM

Hotswap

IPMB

Physical

BMC

Watchdog

Hardware Platform Management 29

Sensor

Address

(0x1) FRU Hotswap Sensor. Please refer to section 4.2.1

(0x2)

(0x3) RTM Hotswap Sensor. Please refer to section 4.2.1

(0x5) Physical IPMB Sensor. Please refer to section 4.2.2

(0x6)

AMC#1 Hotswap Sensor. Please refer to section

4.2.1

Watchdog Timer Sensor. Please refer to section

4.2.3

Description

Page 44

Item

(7)

(8)

(9) +1.8V CPU (0x8)

(10) +5.0V (0x9)

(11) +3.3V (0xA)

(12) +12V (0xB)

Sensor

Name

Version

change

+1..5V

DDR-CPU

Sensor

Address

(0x4)

(0x7)

Description

Version Change Sensor. Please refer to section

4.2.4

Voltage Sensor. Please refer to section 4.2.5

Upper Non-Recoverable Threshold = 1.65 Volts

Upper Critical Threshold = 1.62 Volts

Upper Non-Critical Threshold = 1.59 Volts

Lower Non-Critical Threshold = 1.41 Volts

Lower Critical Threshold = 1.38 Volts

Lower Non-Recoverable Threshold = 1.35 Volts

Voltage Sensor. Please refer to section 4.2.5

Upper Non-Recoverable Threshold = 1.98 Volts

Upper Critical Threshold = 1.944 Volts

Upper Non-Critical Threshold = 1.908 Volts

Lower Non-Critical Threshold = 1.692 Volts

Lower Critical Threshold = 1.656 Volts

Lower Non-Recoverable Threshold = 1.62 Volts

Voltage Sensor. Please refer to section 4.2.5

Upper Non-Recoverable Threshold = 5.5 Volts

Upper Critical Threshold = 5.4 Volts

Upper Non-Critical Threshold = 5.3 Volts

Lower Non-Critical Thresh o l d = 4.7 Volts

Lower Critical Threshold = 4.6 Volts

Lower Non-Recoverable Threshold = 4.5 Volts

Voltage Sensor. Please refer to section 4.2.5

Upper Non-Recoverable Threshold = 3.63 Volts

Upper Critical Threshold = 3.564 Volts

Upper Non-Critical Threshold = 3.498 Volts

Lower Non-Critical Threshold = 3.102 Volts

Lower Critical Threshold = 3.036 Volts

Lower Non-Recoverable Threshold = 2.97 Volts

Voltage Sensor. Please refer to section 4.2.5

Upper Non-Recoverable Threshold = 13.2 Volts

Upper Critical Threshold = 12.96 Volts

Upper Non-Critical Threshold = 12.72 Volts

Lower Non-Critical Threshold = 11.28 Volts

Lower Critical Threshold = 11.04 Volts

Lower Non-Recoverable Threshold = 10.8 Volts

30 Hardware Platform Management

Page 45

aTCA-6155

Item

(13)

(14) CPU0 Temp (0x11)

(15) CPU1 Temp (0x12)

(16)

(17) SIO_THERM (0xD)

(18) SIO_WDT (0xE)

(19) ICH_THEM (0xF)

(20)

Sensor

Name

LM75 SYS

Temp

W83627_OVT

FSB_GPIO_

FERR

Sensor

Address

(0x13)

(0xC)

(0x10)

Description

System Temperature. Please refer to section 4.2.5

Upper Non-Recoverable Threshold = 95 °C

Upper Critical Threshold = 75 °C

Upper Non-Critical Threshold = 60 °C

CPU Temperature. Please refer to section 4.2.5

Upper Non-Recoverable Threshold = 100 °C

Upper Critical Threshold = 80 °C

Upper Non-Critical Threshold = 65 °C

CPU Temperature. Please refer to section 4.2.5

Upper Non-Recoverable Threshold = 100 °C

Upper Critical Threshold = 80 °C

Upper Non-Critical Threshold = 65 °C

Discrete Sensor

OVT#/SMI#: Can create interrupts that depend on

the temperatures measured by SYSTIN and

CPUTIN. This mode is enabled by setting THYST

(Temperature Hysteresis) to 127 °C.

Discrete Sensor

Same as W83627 OVT.

Discrete Sensor(Normal:0x0001, Abnormal:0x0002)

Watchdog timer output signal. The time-out counter

ranges from 1 to 255 minutes in the minute mode,

or 1 to 255 seconds in the second mode.

Discrete Sensor

Thermal Alarm: Active low signal generated by

external hardware to generate an SMI# or SCI.

Discrete Sensor

FERR# (floating-point error) is qualified by

STPCLK#. When STPCLK# is not asserted, FERR#

indicates a floating-point error and will be asserted

when the processor detects an unmasked

floating-point error. When STPCLK# is not asserted,

FERR# is similar to the ERROR# signal on the Intel

387 coprocessor, and is included for compatibility

with systems using MS-DOS*-type floating-point

error reporting. When STPCLK# is asserted, an

assertion of FERR# indicates that the processor has

a pending break event waiting for service. The

assertion of FERR# indicates that the processor

should be returned to the Normal state.

(Normal:0x0001, Abnormal:0x0002)

(Normal:0x0001, Abnormal:0x0002)

(Normal:0x0001, Abnormal:0x0002)

(Normal:0x0001, Abnormal:0x0002)

Hardware Platform Management 31

Page 46

Item

(21)

(22)

Sensor

Name

BIOS

CHANGE

BIOS POST

ERROR

Sensor

Address

(0x15)

(0x16)

Table 4-1: aTCA-6155 IPMI Sensors

Discrete Sensor

Dual Bios function.

Discrete Sensor

Dual Bios function.

Description

32 Hardware Platform Management

Page 47

4.2.1 Get Sensor Reading (FRU Hotswap Sensor)

Byte Data field

Request

data

Response

data

Sensor Number (FFh = reserved)

1

1 Completion Code

Sensor Reading.

2

[7:0] - Not used. Write as 00h.

Standard IPMI byte (See “Get Sensor Reading” in IPMI specification):

[7] - 0b = All Event Messages disabled from this sensor

[6] - 0b = sensor scanning disabled

[5] - 1b = initial update in progress. This bit is set to indicate that a

“Re-arm Sensor Events” or “Set Event Receiver” command has

been used to request an update of the sensor status, and that

update has not occurred yet. Soft w are sho uld use this bit to avoid

3

getting an incorrect status while the first sensor update is in

progress. This bit is only required if it is possible for the IPM

Controller to receive and process a “Get Sensor Reading or Get

Sensor Event Status” command for the sensor before the update

has completed. This is most likely to be the case for sensors, such

as fan RPM sensors, that may require seconds to accumulate the

first reading after a re-arm.

[4:0] – reserved. Ignore on read.

Current State Mask

[7] – 1b = FRU Operational State M7 - Communication Lost

[6] – 1b = FRU Operational State M6 - FRU De a c ti v at i o n I n P r o gr e ss

[5] – 1b = FRU Operational State M5 - FRU Deactivation Request

4

[4] – 1b = FRU Operational State M4 - FRU Active

[3] – 1b = FRU Operational State M3 - FRU Activation in Progress

[2] – 1b = FRU Operational State M2 - FRU Activation Request

[1] – 1b = FRU Operational State M1 - FRU Inactive

[0] – 1b = FRU Operational State M0 - FRU Not Installed

[7:0] – Optional/Reserved. If provided, write as 80h (IPMI

5

restriction). Ignore on read.

Table 4-2: Get Sensor Reading (FRU Hotswap Sensor)

aTCA-6155

Hardware Platform Management 33

Page 48

4.2.2 Get Sensor Reading (Physical IPMB-0 Sensor)

Byte Data field

Request

data

Response

data

Table 4-3: Get Sensor Reading (Physical IPMB-0 Sensor)

Sensor Number (FFh = reserved)

1

1 Completion Code

Sensor Reading.

2

[7:0] - Not used. Write as 00h.

Standard IPMI byte (See “Get Sensor Readin g” in IPMI specification):

[7] - 0b = All Event Messages disabled from this sensor

[6] - 0b = sensor scanning disabled

[5] - 1b = initial update in progress. This bit is set to indicate that a

“Re-arm Sensor Events” or “Set Event Receiver” command has

been used to request an update of the sensor status, and that

update has not occurred yet. Software should use this bit to avoid

3

getting an incorrect status while the first sensor update is in

progress. This bit is only required if it is possible for the IPM

Controller to receive and process a “Get Sensor Reading or Get

Sensor Event Status” command for the sensor before the update

has completed. This is most likely to be the case for sensors, such

as fan RPM sensors, that may require seconds to accumulate the

first reading after a re-arm.

[4:0] – reserved. Ignore on read.

Current State Mask

[7] – 1b = FRU Operational State M7 - Communication Lost

[6] – 1b = FRU Operational State M6 - FRU Deactivation In

Progress

[5] – 1b = FRU Operational State M5 - FRU Deactivation Request

4

[4] – 1b = FRU Operational State M4 - FRU Active

[3] – 1b = FRU Operational State M3 - FRU Activation in Progress

[2] – 1b = FRU Operational State M2 - FRU Activation Request

[1] – 1b = FRU Operational State M1 - FRU Inactive

[0] – 1b = FRU Operational State M0 - FRU Not Installed

[7:0] – Optional/Reserved. If provided, write as 80h (IPMI

5

restriction). Ignore on read.

34 Hardware Platform Management

Page 49

4.2.3 Watchdog Timer Sensor

aTCA-6155

Sensor Type

Watchdog 2 23h

Sensor

Type Code

Sensor

Specific Offset

This sensor is recommended for new

IPMI v1.0 and later implementations.

00h

01h Hard Reset

02h Power Down

03h Power Cycle

04h-07h reserved

08h Timer interrupt

Timer expired, status only (no action, no

interrupt)

The Event Data 2 field for this command

can be used to provide an

event extension code, with the following

definition:

7:4 interrupt type

3:0 timer use at expiration:

Event

0h = none

1h = SMI

2h = NMI

3h = Messaging Interrupt

Fh = unspecified

all other = reserved

0h = reserved

1h = BIOS FRB2

2h = BIOS/POST

3h = OS Load

4h = SMS/OS

5h = OEM

Fh = unspecified

all other = reserved

T able 4-4: Watchdog Timer Sensor

Hardware Platform Management 35

Page 50

4.2.4 Version Change Sensor

Sensor

Type

Version

Change

Sensor

Type Code

2Bh

Sensor

Specific Offset

00h Hardware change detected with

associated Entity. Informational. This offset

00h

01h

02h

03h

04h

05h

06h

07h

Table 4-5: Version Change Sensor

does not imply whether the hardware change

was successful or not. Only that a change

occurred.

01h Firmware or software change detected

with associated Entity.Informational. Success

or failure not implied.

02h Hardware incompatibility detected with

associated Entity.

03h Firmware or software incompatibility

detected with associated Entity.

04h Entity is of an invalid or unsupported

hardware version.

05h Entity contains an invalid or unsupported

firmware or software version.

06h Hardware Change detected with

associated Entity was successful.

(deassertion event means unsuccessful’).

07h Software or F/W Change detected with

associated Entity was successful.

(deassertion event means ‘unsuccessful’)

Event data 2 can be used for additional event

information on the type of version change see definition below

Event

36 Hardware Platform Management

Page 51

aTCA-6155

Event Data 2

7:0 Version cha nge type

X 00h unspecified

X 01h management controller device ID (change in one or

more fields from ‘Get Device ID’)

X 02h management controller firmware revision

X 03h management controller device revision

X 04h management controller manufacturer ID

X 05h management controller IPMI version

X 06h management controller auxiliary firmware ID

X 07h management controller firmware boot block

X 08h other management controller firmware

X 09h system firmware (EFI / BIOS) change

X 0Ah SMBIOS change

X 0Bh operating system change

X 0Ch operating system loader change

X 0Dh service or diagnostic partition change

X 0Eh management software agent change

X 0Fh management software application change

X 10h management software middleware change

X 11h programmable hardware change (e.g. FPGA)

X 12h board/FRU module change (change of a module

plugged into associated entity)

X 13h board/FRU component change (a dd itio n or rem o val of

a replaceable component on the board/FRU that is not

tracked as a FRU)

X 14h board/FRU replaced with equivalent version

X 15h board/FRU replaced with newer version

X 16h board/FRU replaced with older version

X 17h board/FRU hardware configuration change (e.g. strap,

jumper, cable change, etc.)

Hardware Platform Management 37

Page 52

4.2.5 Get Sensor Reading Command

Byte Data field

Request

data

Response

data

1 Sensor Number (FFh = reserved)

1 Completion Code

Sensor reading

2

Byte 1: byte of reading. Ignore on read if sensor does not return an

numeric (analog) reading.

[7] - 0b = All Event Messages disabled from this sensor

[6] - 0b = sensor scanning disabled

[5] - 1b = reading/state unavailable (formerly “initial update in

progress”).

This bit is set to indicate that a ‘re-arm’ or ‘Set Event Receiver’

command has been used to request an update of the sensor

status, and that update has not occurred yet. Software should use

this bit to avoid getting an incorrect status while the first sensor

update is in progress. This bit is only required if it is possible for

the controller to receive and process a ‘Get Sensor Reading’ or

3

‘Get Sensor Event Status’ command for the sensor before the

update has completed. This is most likely to be the case for

sensors, such as fan RPM sensors, that may require seconds to

accumulate the first reading after a re-arm. The bit is also used to

indicate when a reading/state is unavailable because the

management controller cannot obtain a valid reading or state for

the monitored entity, typically because the entity is not present.

See PICMG Specification 3.0, Section 16.4, Event Status, Event

Conditions, and Present State and Section 16.6, Re-arming for

more information.

[4:0] - reserved. Ignore on read.

38 Hardware Platform Management

Page 53

Response

data

(cont’d)

Byte Data field

For threshold-based sensors

Present threshold comparison status

[7:6] - reserved. Returned as 1b. Ignore on read.

[5] - 1b = at or above () upper non-recoverable threshold

[4] - 1b = at or above () upper critical threshold

[3] - 1b = at or above () upper non-critical threshold

[2] - 1b = at or below () lower non-recoverable threshold

[1] - 1b = at or below () lower critical threshold

[0] - 1b = at or below () lower non-critical threshold

4

For discrete reading sensors

[7] - 1b = state 7 asserted

[6] - 1b = state 6 asserted

[5] - 1b = state 5 asserted

[4] - 1b = state 4 asserted

[3] - 1b = state 3 asserted

[2] - 1b = state 2 asserted

[1] - 1b = state 1 asserted

[0] - 1b = state 0 asserted

For discrete reading sensors only. (Optional)

(00h Otherwise)

[7] - reserved. Returned as 1b. Ignore on read.

[6] - 1b = state 14 asserted

[5] - 1b = state 13 asserted

(5)

[4] - 1b = state 12 asserted

[3] - 1b = state 11 asserted

[2] - 1b = state 10 asserted

[1] - 1b = state 9 asserted

[0] - 1b = state 8 asserted

Table 4-6: Get Sensor Reading Command

aTCA-6155

Hardware Platform Management 39

Page 54

4.3 IPMI Commands

Following table presents all the commands which are supported

by the aTCA-6155 in different interfaces and compatible with IPMI

v1.5 and PICMG 3.0 R2.0 ECN001. There are two interfaces

implemented with IPMI command support.

(1) KCS: OpenIPMI

(2) IPMB0: IPMBa & IPMBb

KCS IPMB0

IPMI Commands

IPM Device “Global” Commands

Get Device ID x x

Cold Reset x x

Warm Reset x x

Get Self Test Results x x

Get Device GUID x x

IPMI Messaging Support Commands

Set BMC Global Enables x x

Get BMC Global Enables x x

Clear Message Flags x x

Get Message Flags x x

Get Message x x

Send Message x x

Master Write-Read x x

BMC Watchdog Timer

Reset Watchdog Timer x x

Set Watchdog Timer x x

Get Watchdog Timer x x

Event Commands

Set Event Receiver x x

Get Event Receiver x x

Platform Event x x

Table 4-7: Supported IPMI Commands

40 Hardware Platform Management

Page 55

KCS IPMB0

Sensor Device Commands

Get Device SDR Info x x

Get Device SDR x x

Reserve Device SDR

Repository

Get Sensor Reading Factors x x

Set Sensor Hysteresis x x

Get Sensor Hysteresis x x

Set Sensor Threshold x x

Get Sensor Threshold x x

Set Sensor Event Enable x x

Get Sensor Event Enable x x

Rearm Sensor Events x x

Get Sensor Event Status x x

Get Sensor Reading x x

xx

FRU Device Commands

Get FRU Inventory Area Info x x

Read FRU Data x x

Write FRU Data x x

PICMG Commands

aTCA-6155

HPM.1 Upgrade Commands (HPM.1)

Get target upgrade capabilities x x

Get component properties x x

Abort Firmware Upgrade x x

Initiate upgrade action x x

Upload firmware block x x

Finish firmware upload x x

Get upgrade status x x

Activate firmware x x

Query Self-test Results x x

Query Rollback status x x

Initiate Manual Rollback x x

Table 4-7 (cont’d): Supported IPMI Commands

Hardware Platform Management 41

Page 56

KCS IPMB0

AdvancedTCA

Get PICMG Properties x x

Get Address Info x x

FRU Control x x

FRU Control Capabilities x x

Get FRU LED Properties x x

Get LED Color Capabilities x x

Set FRU LED State x x

Get FRU LED State x x

Set IPMB State x

Set FRU Activation Policy x x

Get FRU Activation Policy x x

Set FRU Activation x x

Get Device Locator Record ID x x

Get Port State x x

Set Port State x

Compute Power Properties x

Set Power Level x

Get Power Level x x

Bused Resource Control x

Get IPMB Link Info x x

SET_CLOCK_STATE x x

GET_CLOCK_STATE x x

Get AMC-Port State x

Set AMC-Port State x

T able 4-7 (cont’d): Supported IPMI Commands

42 Hardware Platform Management

Page 57

aTCA-6155

4.4 IPMI Firmware Upgrade Procedure

The processor can communicate with the IPMC by Keyboard Co ntroller Style (KCS), and an upgrade tool for DOS environment to

upgrade the IPMC firmware is provided on the ADLINK All-in-One

CD or can be downloaded from the ADLINK website. Please follow the procedures below to upgrade the IPMC firmware.

1. Copy the upgrade tool for DOS onto a bootable USB

flash drive, and change the boot order setting in BIOS so

that the USB flash drive is the first boot device.

C:\IPMC\AT6155>dir/w

Volume in drive C has no label

Volume Serial Number is 0065-1CB9

Directory of C:\IPMC\AT6155

[.] [..] README.DOC [TESTTOOL] [UPGRADE]

1 file(s) 2,185,216 bytes

4 dir(s) 863,748,096 bytes free

C:\IPMC\AT6155>cd upgrade

C:\IPMC\AT6155\UPGRADE>dir/w

Volume in drive C has no label

Volume Serial Number is 0065-1CB9

Directory of C:\IPMC\AT6155\UPGRADE

[.] [..] A203.IMG CWSDPMI.EXE CWSDPR0.EXE

CWSPARAM.EXE HPMDOS.EXE UPGRADE.BAT

7 file(s) 884,350 bytes

2 dir(s) 863,748,096 bytes free

C:\IPMC\AT6155\UPGRADE>

Hardware Platform Management 43

Page 58

2. Execute upgrade.bat. This tool will upgrade the IPMC

firmware automatically. After the firmware has been

upgraded successfully, please do a power cycle or

remove the blade from the chassis and reinsert.

C:\IPMC\AT6155\UPGRADE>upgrade.bat

C:\IPMC\AT6155\UPGRADE>CWSDPMI.EXE -sCWSDPMI V0.90+ (r4) Copyright (C) 1997 CW Sandmann

ABSOLUTELY NO WARRANTY

C:\IPMC\AT6155\UPGRADE>hpmdos.exe -I KCS -F A203.img

upgrade

Adlink HPH.1 DOS Upgrade Agent

Update HPM.1 components using PICMG HPM.1 file

Validating firmware image integrity...OK

Performing preparation stage...OK

Services may be affected during upgrade. Do you wish

to continue? y/n

Target Product ID : 6155

Target Manufacturer ID: 005f13

Performing upgrade stage: Upgrading H8S-AMCc F/W

with Version: Major: 1

Minor: 51

Aux : a2 00 00 03

Writing firmware: 100 % completed

Firmware upgrade procedure successful

Upgrade successful, please shutdown and boot system

HPM.1 upgrade succeed!!

3. Go to the \TESTTOOL directory and execute TEST.BAT.

This tool will list all the sensors on the aTCA-6155, and

“Auxiliary Firmware Revision Information: a2000003”

indicates the firmware version is a2000003.

C:\IPMC\AT6155\TESTTOOL>dir/w

Volume in drive C has no label

Volume Serial Number is 0065-1CB9

Directory of C:\IPMC\AT6155\TESTTOOL

[.] [..] INFO.INI IPMITEST.EXE TEST.BAT

44 Hardware Platform Management

Page 59

aTCA-6155

IPMITOOL v 2.0.1 03/17/2008 - IPMI toolkit for Terminal

mode.

Copyright(c) 2006. All Rights Reserved

FOR PRODUCTS WITH PICMG 2.9(CPCI) CAPABILITY ONLY.

DO NOT RUN THIS PROGRAM UNDER WINDOWS NT, 2000, OR XP.

Please Press any key to continue.

########################################################

[#]Check IPMC status .....[OK]

Product Name: aTCA-6155

Firmware Version: V1.51

[#]Check Development status .....OK

Auxiliary Firmware Revision Information : a2000003

[#]Check KCS status .....OK

[#] Check IPMB addr ..... (IPMB addr: 0x80)

[#] FRU Information .....

Board product Name: aTCA6155

Board FRU ID: FRU-OP1 V1.1

###### Press any key to continue ######

01.Hot Swap [00] .....Status OK

02.ShelfFRU HotSwap [01] .....Status OK

03.Hot Swap AMC 1 [02] .....Status OK

04.IPMB Physical [0A] .....Status OK

05.BMC Watchdog [14] .....Status OK

06.Version change [15] .....Status OK

07.+5.0V [05] .....RAW Data(D1) 5.104 V ....Status OK

08.+3.3V [06] .....RAW Data(D1) 3.367 V ....Status OK

09.+1.8V [07] .....RAW Data(B7) 1.789 V ....Status OK

10.+1.5V [08] .....RAW Data(98) 1.485 V ....Status OK

10.+1.5V [08] .....RAW Data(98) 1.485 V ....Status OK

12.LM75 SYS Temp [16] .....RAW Data(A0) 32.000 C

....Status OK

13.W83627 OVT [0B] .....Status OK

14.SIO THERM [0C] .....Status OK

15.SIO WDT [0D] .....Status OK

16.ICH THRM [0E] .....Status OK

17.CPU THERMTRIP [0F] .....Status OK

18.FSB FERR [10] .....Status OK

19.FSB IERR [11] .....Status OK

20.SYS PWROK [12] .....Status OK

21.CPU0 Temp [17] .....RAW Data(21) 33.000 C ...Status OK

22.CPU1 Temp [18] .....RAW Data(1C) 28.000 C ...Status OK

23.Hot Swap [00] .....Status OK

Hardware Platform Management 45

Page 60

This page intentionally left blank.

46 Hardware Platform Management

Page 61

5 Getting Started

The aTCA-6155 has been designed for easy inst allatio n. However,

the following standard precautions, installation procedures, and

general information must be observed to ensure p roper inst allation

and to preclude damage to the board, other system components,

or injury to personnel.

5.1 Safety Requirements

The following safety precautions must be observed when installing

or operating the aTCA-6155. ADLINK assumes no responsibility for

any damage resulting from failure to comply with these requirements.

Exercised due care when handling the board as the heat sink can

get very hot. Do not touch the heat sink when installing or removing

the board. The board should not be placed on any surface or in any

form of storage container until the board and heat sink have cooled

down to room temperature.

If your board type is not specifically qualified as being hot swap

capable, switch off the system power before installing the board in a

free slot. Failure to do so could endanger your life or health and may

damage your board or system.

aTCA-6155

Certain blades require bus master and/or Rear I/O capability. If you

are in doubt whether such features are required for the board you

intend to install, please check your specific board and/or system

documentation to make sure that your system is provided with an

appropriate free slot in which to insert the board.

This ATCA blade contains electrostatic sensitive devices. Please

observe the necessary precautions to avoid damage to your board:

X Discharge your clothing before touching the assembly.

Tools must be discharged before use.

X Do not touch components, connector-pins or traces.

X If working at an anti-static workbench with professional dis-

charging equipment, please do not omit to use it.

Getting Started 47

Page 62

5.2 Installing the aTCA-6155

Follow these steps to install the aTCA-6155 to the chassis.

1. Carefully align the board edges with the chassis guide

rails and insert the blade into the chassis guide rail.

2. Check that the catch hooks and alignment pins at either

end of the blade are correctly inserted into the proper

openings. Push inwards on the handles until the blade is

firmly seated in the chassis. (Do not force the handles if

there is resistance as this may damage the connectors

and/or backplane.)

48 Getting Started

Page 63

aTCA-6155

Getting Started 49

Page 64

3. Pinch the ejector to unlock the handle and insert the

catch into the faceplate.

50 Getting Started

Page 65

4. Secure the blade by tightening the captive screws.

aTCA-6155

5.3 Removing the aTCA-6155

To remove the aTCA-6155 blade, undo the captive screws, pinch

the ejector handle release mechanisms and pull outwards on the

ejector handles to eject the blade from the backplane. Pull the

blade towards you until it is free of the chassis.

Getting Started 51

Page 66

This page intentionally left blank.

52 Getting Started

Page 67

6 Driver Installation

The drivers for the aTCA-6155 are available on the ADLINK website. Please visit the product website for details:

http://www.adlinktech.com.

The following describes the driver installation procedures for Windows® Server 2003

1. Install the Windows operating system before installing

any driver. Most standard I/O device drivers are installed

during Windows installation.

2. Download the drive rs from the website:

Z Chipset - Intel® Chipset Installation Utility Version

Z LAN Controller - Intel® PRO/1000 PT Dual Port Server

Adapter

Z SAS Controller - LSI Adapter, SAS 3000 series, 4-port with

1064E

Z VGA Controller - ATI ES1000, 6.14.10.6553

We recommend using all the drivers provided on the ADLINK

All-in-One CD or downloaded from the ADLINK website to ensure

driver compatibility. Contact ADLINK to get support for other operating systems.

aTCA-6155

6.1 Chipset Driver Installation

To install the chipset driver for Windows® Server 2003:

1. Run the InstallShield installation program:

Z Self-extracting .EXE distribution: INFINST_AUTOL.EXE

Z Compressed .ZIP distribution: SETUP.EXE

2. You will be prompted to agree to the license agreement.

If you do not agree, the installation program will exit

before extracting any files.

3. Once the operating system reboot s, follow the on-scree n

instructions and accept default settings to complete the

setup.

Driver Installation 53

Page 68

6.2 LAN Driver Installation

Download the archive Intel_Network_Adapter_Win2003_v14.3.zip

then extract and run the installation wizard. All language files are

embedded in this archive. You do not need to download an extra

language pack.

After installing the Intel LAN driver, you will see the following Network Adapters in the Device Manager:

X Intel 10 Gigabit KX4 Dual Port Server Adapter x2

X 82576EB Intel PRO/1000 PB Dual Port Server Connection x6.

,

54 Driver Installation

Page 69

aTCA-6155

6.3 LAN Driver Installation

Right-click the mouse on the SCSI Controller in the Device Manager and select Update Driver.

Select Install from a list or specific location (Advanced).

Driver Installation 55

Page 70

Navigate to the location lsimpt_sas_srv03_x86.

Select Continue Anyway when this message pops up.

56 Driver Installation

Page 71

aTCA-6155

The LSI adapter, SAS 3000 series, 4-port with 1064E–StorPort

driver will be installed.

Click Finish to complete the installation.

Driver Installation 57

Page 72

6.4 VGA Driver Installation

Right-click the mouse on the VGA Controller in the Device Manager and select Update Driver. Navigate to the directory

2KXP_INF for the VGA driver.

Check if the ATI ES1000 driver was installed properly.

58 Driver Installation

Page 73

7 Watchdog Timer

7.1 Overview

The aTCA-6155 supports a Watchdog Timer function which is b uilt

into the Winbond W83627UHG to protect the system from specific

software or hardware failures that may cause the system stop

responding. The application is first registered with the watchdog

device. Once the watchdog device is enabled, the application

must periodically send a signal to the watchdog device. If the

watchdog device doesn’t receive this signal within the set period of

time, it will reboot the system or restart the application.

The Watchdog Timer of the W83627UHG consists of an 8-bit programmable time-out counter and a control and status register. The

time-out counter ranges from 1 to 255 minutes in the minutes

mode, or 1 to 255 seconds in the seconds mode. The mode of the

Watchdog Timer counter are selected at Logical Device 8,

CR[F5h], bit[3]. The time-out value is set at Logical Device 8,

CR[F6]. Writing zero disables the Watchdog Timer function. Writing any non-zero value to this register causes the counter to load

this value into the Watchdog Timer counter and start counting

down.

The W83627UHG outputs a low signal to the WDTO# (pin 77)

when a time-out event occurs. In other words, when the value is

counted down to zero, the timer stops, and the W83627UHG sets

the WDTO# status bit in Logic Device 8, CR[F7h], bit[4], outputting

a low signal to the WDTO# pin (pin 77). Writing a zero will clear

the status bit and the WDTO# pin returns to high. This bit will also

be cleared if LRESET# or PWROK# signal is asserted.

aTCA-6155

Watchdog Timer 59

Page 74

7.2 Sample Code

This sample code is provided for testing the Watchdog Timer fun ction of the W83627UHG on the aTCA-6155.

#include<stdlib.h>

#include<stdio.h>

#include<string.h>

#include<dos.h>

void WDTRUN(int config_port,int count_value);

void Enter_W627UHG_Config(int config_port);

void Exit_W627UHG_Config(int config_port);

void main(int argc,char *argv[])

{

int number,DevID1,DevID2,chipflag=0;

int ioport = 0x4E;//Default config_port = 0x4E

if((argc==1) || ((argc == 3)&& (*argv[2] != 'i')) ||

(argc>3))

{

printf("ADLINK Watchdog Timer Utility of aTCA-

6155.\n\n");

printf(" Usage: WDT6155 value [i]\n");

printf(" value is from 1 to 15300, the unit is

second.\n");

printf(" Write 0 will disable watchdog

timer.\n\n");

printf(" i - change IO port to 0x2E. Default

is 0x4E.\n");

exit(1);

}

else

{

if(argc==3) ioport=0x2E;

//Detect W83627UHG.

Enter_W627UHG_Config(ioport);

//Get Chip ID Hi Byte = 0xA2, Chip ID LO Byte = 0x3x

outportb(ioport, 0x20);

DevID1 = inportb(ioport+1);

outportb(ioport, 0x21);

DevID2 = inportb(ioport+1);

if((DevID1 == 0xA2) && ((DevID2 & 0xF0) == 0x30))

chipflag = 1;

60 Watchdog Timer

Page 75

if(chipflag == 0)

{

printf("ADLINK Watchdog Timer Utility of aTCA-

6155.\n\n");

printf("Can't find any Winbond W83627UHG on

system!\n");

Exit_W627UHG_Config(ioport);

exit(1);

}

else

{

printf("ADLINK Watchdog Timer Utility of aTCA-

6155.\n\n");

number=atoi(argv[1]);

WDTRUN(ioport,number);

Exit_W627UHG_Config(ioport);

}

}

}

void Enter_W627UHG_Config(int config_port)

{

outportb(config_port, 0x87);

outportb(config_port, 0x87);

}

void Exit_W627UHG_Config(int config_port)

{

outportb(config_port, 0xAA);

}

void WDTRUN(int config_port,int count_value)

{

int temp;

int counter;

//Select WDT device

outportb(config_port, 0x07);

outportb(config_port+1, 0x08);//device 8

aTCA-6155

//Activate WDT device

outportb(config_port, 0x30);

temp = inportb(config_port+1);

temp = temp | 0x01;

outportb(config_port+1, temp);

//Set second/minute mode

outportb(config_port, 0xF5);

Watchdog Timer 61

Page 76

temp = inportb(config_port+1);

temp = temp & 0xFD;//disable WDTO to KBRST#.

if(count_value <= 60)

temp = temp & 0xF7;//second.

//Count the timeout value

if(((count_value>60) && (count_value<=15300)) ||

(count_value > 15300))

{