Page 1

NuDAQ

ACL-8454

Multi-Functions

Counter/Timer Card

User’s Manual

Recycled Paper

Page 2

Page 3

Copyright 1997~2001 ADLINK Technology Inc.

All Rights Reserved.

Manual Rev. 1.40: March 21, 2001

Part No. 50-11017-101

The information in this document is subject to change without prior notice in

order to improve reliability, design and function and does not represent a

commitment on the part of the manufacturer.

In no event will the manufacturer be liable for direct, indirect, special,

incidental, or consequential damages arising out of the use or inability to

use the product or documentation, even if advised of the possibility of such

damages.

This document contains proprietary information protected by copyright. All

rights are reserved. No part of this manual may be reproduced by any

mechanical, electronic, or other means in any form without prior written

permission of the manufacturer.

Trademarks

NuDAQ

, NuIPC, NuDAM, NuPRO are registered trademarks of

ADLINK Technology Inc. Other product names mentioned herein are used

for identification purposes only and may be trademarks and/or registered

trademarks of their respective companies.

Page 4

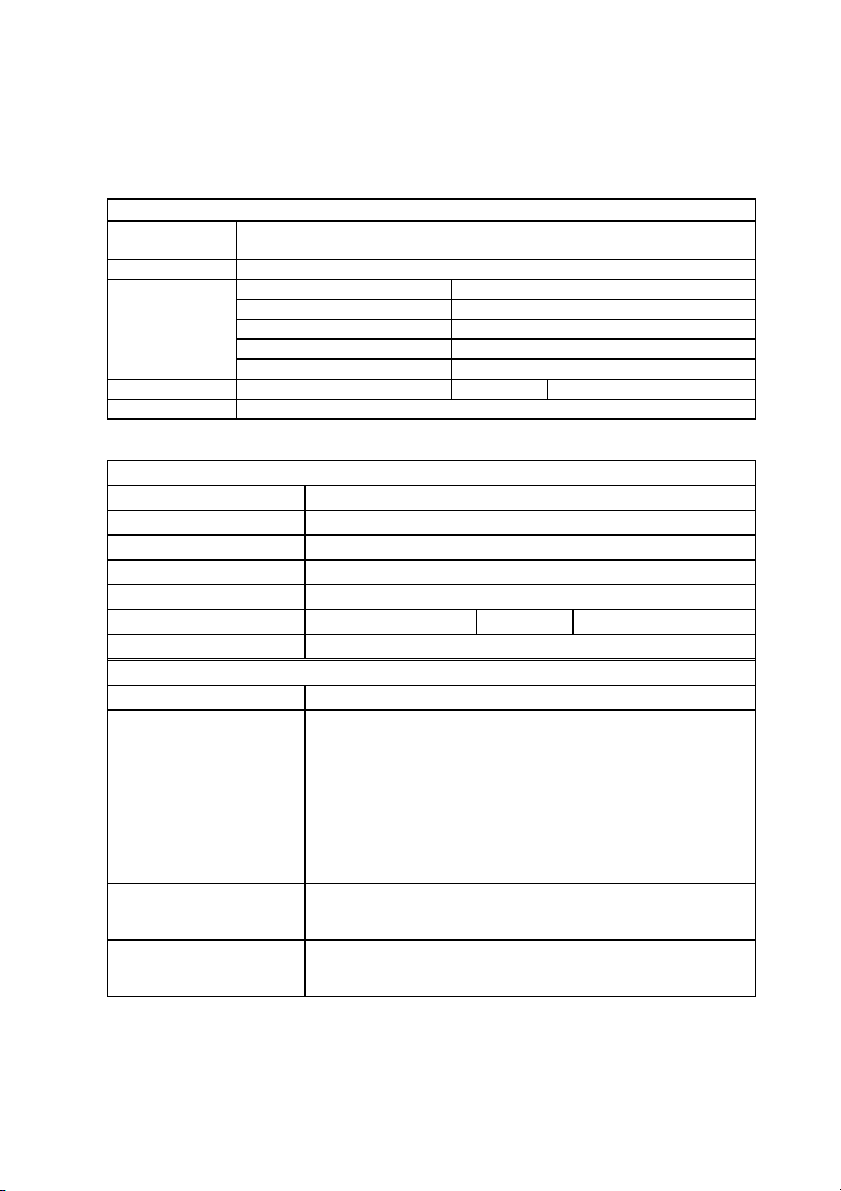

Getting service from ADLINK

Customer Satisfaction is always the most important thing for ADLink Tech

Inc. If you need any help or service, please contact us and get it.

ADLINK Technology Inc.

Web Site http://www.adlinktechnology.com

Sales & Service service@adlink.com.tw

Technical

Support

TEL +886-2-82265877 FAX +886-2-82265717

Address 9F, No. 166, Jian Yi Road, Chungho City, Taipei, 235 Taiwan, R.O.C.

Please inform or FAX us of your detailed information for a prompt,

satisfactory and constant service.

http://www.adlink.com.tw

NuDAQ nudaq@adlink.com.tw

NuDAM nudam@adlink.com.tw

NuIPC nuipc@adlink.com.tw

NuPRO nupro@adlink.com.tw

Software sw@adlink.com.tw

Detailed Company Information

Company/Organization

Contact Person

E-mail Address

Address

Country

TEL

Web Site

FAX

Questions

Product Model

Environment to Use

OS

Computer Brand

M/B :

Chipset :

Video Card :

Network Interface Card :

Other :

CPU :

BIOS :

Challenge Description

Suggestions for ADLINK

Page 5

Table of Contents

Chapter 1 INTRODUCTION............................................. 1

1.1 Features................................................................................... 3

1.2 Applications .............................................................................3

1.3 Specifications........................................................................... 4

Chapter 2 INSTALLATION & CONFIGURATIONS......... 5

2.1 What You Have........................................................................5

2.2 Unpacking................................................................................6

2.3 PCB Layout of ACL-8454 ........................................................6

2.4 Default Configurations .............................................................7

2.5 Base Address Setting ..............................................................8

2.6 Pin Assignment of Connector ................................................ 10

2.7 Clock System.........................................................................11

2.8 Counters Architecture ............................................................ 13

2.9 Clock Source Configurations .................................................16

2.10 Gate Control Configurations...............................................19

2.11 Counter Outputs .................................................................19

2.12 Interrupt System .................................................................20

2.13 Digital Input and Output......................................................21

2.14 Summary of Default Setting ...............................................22

2.15 Notes for Installing More 8254 Chips .................................23

Chapter 3 REGISTERS FORMAT ................................. 24

3.1 I/O Port Address ....................................................................24

3.2 Timer/Counter Registers .......................................................25

3.3 Chip Select Register .............................................................. 25

3.4 Digital Input Registers............................................................26

3.5 Digital Output Register ..........................................................26

3.6 Low-level Programming......................................................... 27

Chapter 4 SIGNAL CONNECTIONS & APPLICATIONS

....................................................................................... 29

4.1 Connectors Pin Assignment ..................................................29

4.2 Daughter Board Connection ..................................................29

4.3 Digital I/O Connection............................................................ 30

4.4 Timer / Counter Connection ..................................................30

4.5 Frequency Generator.............................................................31

Table of Concents i

Page 6

4.6 Pulse Width Measurement ....................................................33

4.7 Frequency Measurement....................................................... 34

4.8 Event Counter........................................................................36

4.9 Double Interrupt System........................................................ 37

Chapter 5 HIGH-LEVEL PROGRAMMING ................... 38

5.1 Installation..............................................................................38

5.2 W_8454_Initial ....................................................................... 42

5.3 Set_Chip ................................................................................43

5.4 W_8454_Write_Counter ........................................................43

5.5 W_8454_Read_Counter........................................................44

5.6 W_8454_Stop_Counter .........................................................45

5.7 W_8454_DO .......................................................................... 46

5.8 W_8454_DI............................................................................46

5.9 8454 Mode Functions ............................................................47

5.10 W_8454_INT_Enable ......................................................... 48

5.11 W_8454_INT_Disable ........................................................ 49

Appendix A Using of IRQ Channels............................ 50

Appendix B Timer/Counter Operation ........................ 51

Warranty Policy ............................................................ 54

ii Table of Concents

Page 7

How to Use This Guide

This manual is designed to help you use the ACL-8454. The manual

describes how to modify various settings on the ACL-8454 card to meet

your requirements. It is divided into 5 chapters:

Chapter 1,

features, applications and specifications.

Chapter 2,

operation method and multi-functions of the ACL-8454. Users

should read through this chapter to understand the configurations of

the ACL-8454. The chapter will also teach user how to install the

ACL-8454.

Chapter 3,

format of the ACL-8454, this information is very useful for the

programmers who want to control the hardware by low-level

programming.

Chapter 4,

connectors' pin assignment and how to connect the outside signal

and devices to / from the ACL-8454. Some applications are also

introduced.

Chapter 5,

library for operating the ACL-8454. Some examples are shown too.

"Introduction" gives an overview of the product

"Installation & Configurations" describes the

"Register Format" describes the details of register

"Signal Connection & Applications” describes the

"High-level Programming" introduces the C-language

Page 8

Page 9

1

Introduction

The ACL-8454 is a general purpose counter/timer and digital I/O card. It is a

compact-size add-on card for IBM AT compatible PC in control, monitoring

and sensing applications. There are two version of ACL-8454: ACL-8454/6

and ACL-8454/12. ACL-8454/6 has two 8254 chips (6 counters) on board.

ACL-8454/12 has four 8254 chips (12 counters).

On ACL-8454/6, four counters are used for external signal, two counters are

cascaded as 32-bit timer. On ACL-8454/12, eight counters are used for

external signal, the rest of the four counters are designed as two 32-bit

cascaded counters.

This card has multi-configurations. The counters can be set as independent

counters or cascaded counters. The gate control of every counter comes

from either external source or internal cascaded counter. The clock source

comes from either internal or external can be selected by jumper setting. A

10 MHz oscillator is used as the base clock of internal clock sources.

It is possible to use this card on variety of powerful counter/timer functions

to match your industry and laboratory applications. Users can set the

configuration to fit the variety of applications, such as timer, event counter,

frequency generator, pulse width measurement, and frequency

measurement.

Introduction 1

Page 10

The card also provides digital output and input port. There are 8 digital

output channels and these channels can be used to control the external

devices. There are digital input channels and these channels are shared the

same signal lines with the external clock and the external gate signals.

Whenever the external clock or gate signals are not used, they can be

dedicatedly used as D/I. There are at least 8 D/I bits under default setting of

the ACL-8454 because only two 8254 chips are used.

ACL-8454 provides one interrupt signal which comes from one of four

internal or external interrupt sources. Three internal interrupt sources come

from the counter output. One external interrupt source shares with one D/I

pin. The interrupt can be used for watchdog timer or other applications. One

of the 11 interrupt levels on the AT-bus can be selected by setting jumper.

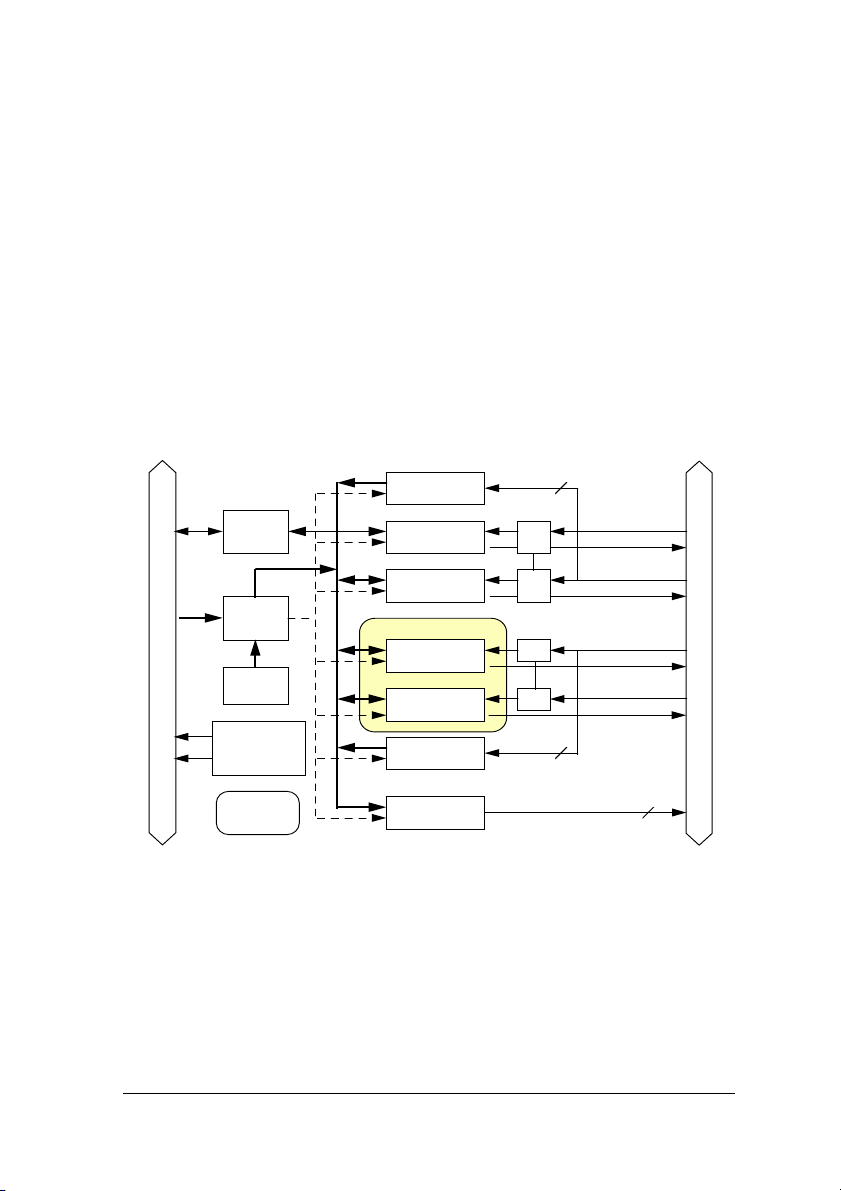

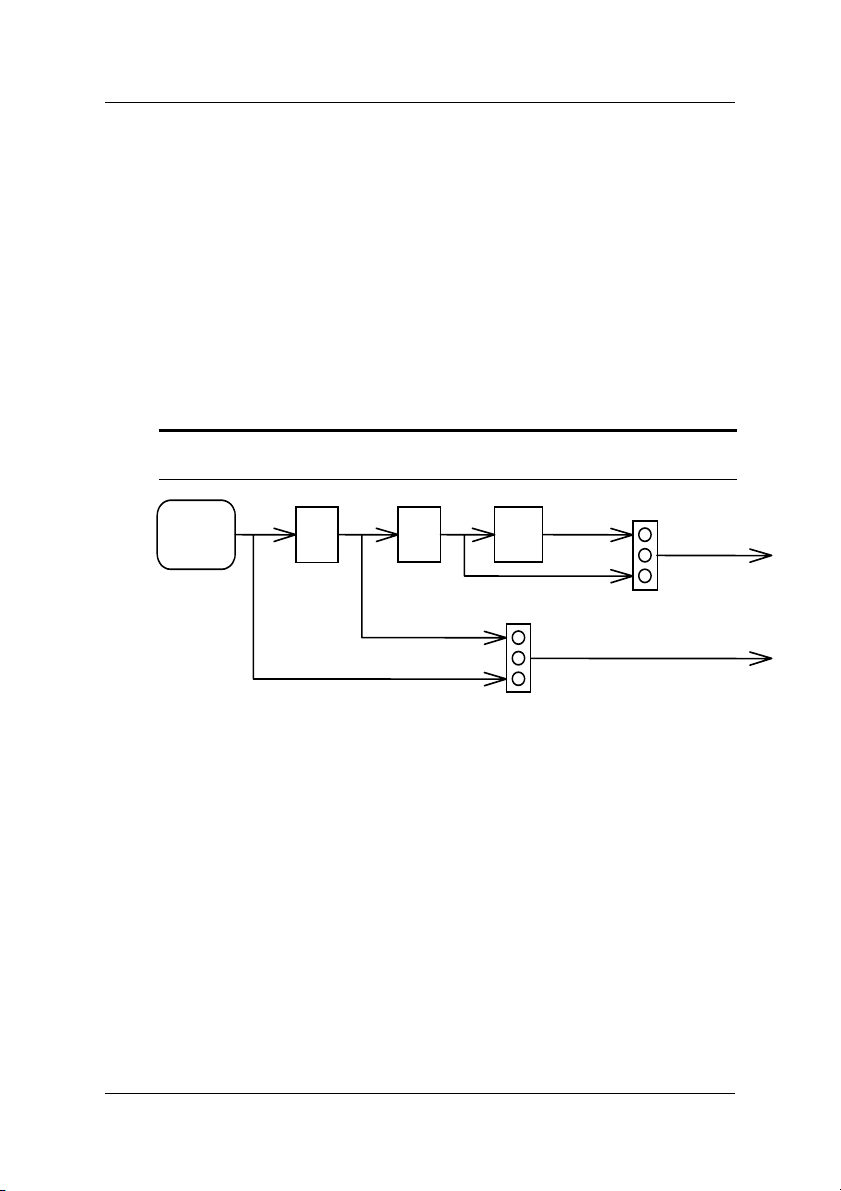

Figure 1.1 shows the block diagram of the ACL-8454.

8 bits

Digital Input

data bus

buffer

8254

chip #1

8254

chip #2

address

PC bus

decoder

address

switch

Double

interrupt

level selector

Clock

System

Optional

8254

chip #3

8254

chip #4

8 bits

Digital Input

8 bits

Digital O utput

Figure 1.1. Block diagram of the ACL-8454

8

jumpers

8

(CLK,GATE) 6

(OUT) 3

(CLK,GATE) 2

(OUT) 2

(CLK,GATE) 6

(OUT) 3

(CLK,GATE) 2

(OUT) 2

8

37 pin D-type connector

2 Introduction

Page 11

1.1 Features

The ACL-8454 Counter/Timer and digital I/O Card provides the following

advanced features:

Default 6 counters/timers are installed and it is expandable to 12

counters/timers at most

Multi-configurations of counters/timers:

Flexible setting for each independent counter, the clock source

could be external, internal or cascaded. The gate signal is external

controlled or internal cascaded signal.

8 digital output channels

16 digital input channels shared with the same signal lines with

external gate control and external clock input

Two interrupt sources

The first interrupt source comes from output of counter #6 and this

signal is jumper selectable to one of 4 IRQ channels

The second interrupt source comes from either internal periodic or

external source. This signal is jumper selectable to one of 5 IRQ

channels.

Synchronized 4 channels frequency measurement is possible

37-pin D-type female connector

AT-Bus and compact size (Half-size only)

1.2 Applications

Event counter

Frequency generator

Frequency synthesizer

Pulse width measurement

Low level pulse generator

Time delay

Industry automation

Watchdog timer

Laboratory and Industrial automation

Introduction 3

Page 12

1.3 Specifications

Programmable Counter/Timer

Device :

Counters :

Clock source :

Gate control :

Digital I/O (DIO)

# of input channels : 16 channels

# of output channels :

Electronics characteristics : TTL compatible signal

General Specifications

I/O Base Address :

Interrupt IRQ :

Connector :

Operating Temperature : 0 C ~ 60 C

Storage Temperature : -20 C ~ 80 C

Humidity :

Power Consumption :

Dimension :

8254 x 2 (default), or 8254 x 4 (at most)

16-bit down counter

internal clock, external source or cascaded

default enable or external control

8 channels (dedicated output)

8 consecutive address space

IRQ 3, ..., IRQ 15 (9 levels jumper selectable)

37-pin D-type female connector

5 ~ 95, non-condensing

+5 V @ 210 mA maximum

163mm(L) X 108mm(W)

4 Introduction

Page 13

2

Installation & Configurations

This chapter describes the configuration and function of the ACL-8454 and

the steps to install the ACL-8454. At first, the contents in the package and

unpacking information that you should care about are described. The

versatile configurations of ACL-8454 are introduced so that you can

configure it according to your applications. The default setting of ACL-8454

is shown at the end of this chapter.

2.1 What You Have

In addition to this User's Manual, the package includes the following items:

ACL-8454 Enhanced Multi-function Counter/Timer Card

Utility Library Diskette or Manual & Software Utility CD

If any of these items is missing or damaged, contact the dealer from whom

you purchased the product. Save the shipping materials and carton in case

you want to ship or store the product in the future.

Installation & Configurations 5

Page 14

2.2 Unpacking

Your ACL-8454 card contains sensitive electronic components that can be

easily damaged by static electricity. The card should be unpacked on a

grounded anti-static mat. The operator should be wearing an anti-static

wristband, grounded at the same point as the anti-static mat.

Inspect the card module carton for obvious damage. Shipping and handling

may cause damage to your module. Be sure there are no shipping and

handing damages on the module before processing.

After opening the card module carton, extract the system module and place

it only on a grounded anti-static surface component side up.

Again inspect the module for damage. Press down on all the socketed IC's

to make sure that they are properly seated. Do this only with the module

place on a firm flat surface.

Note :

You are now ready to install your ACL-8454.

DO NOT APPLY POWER TO THE CARD IF IT HAS BEEN

DAMAGED.

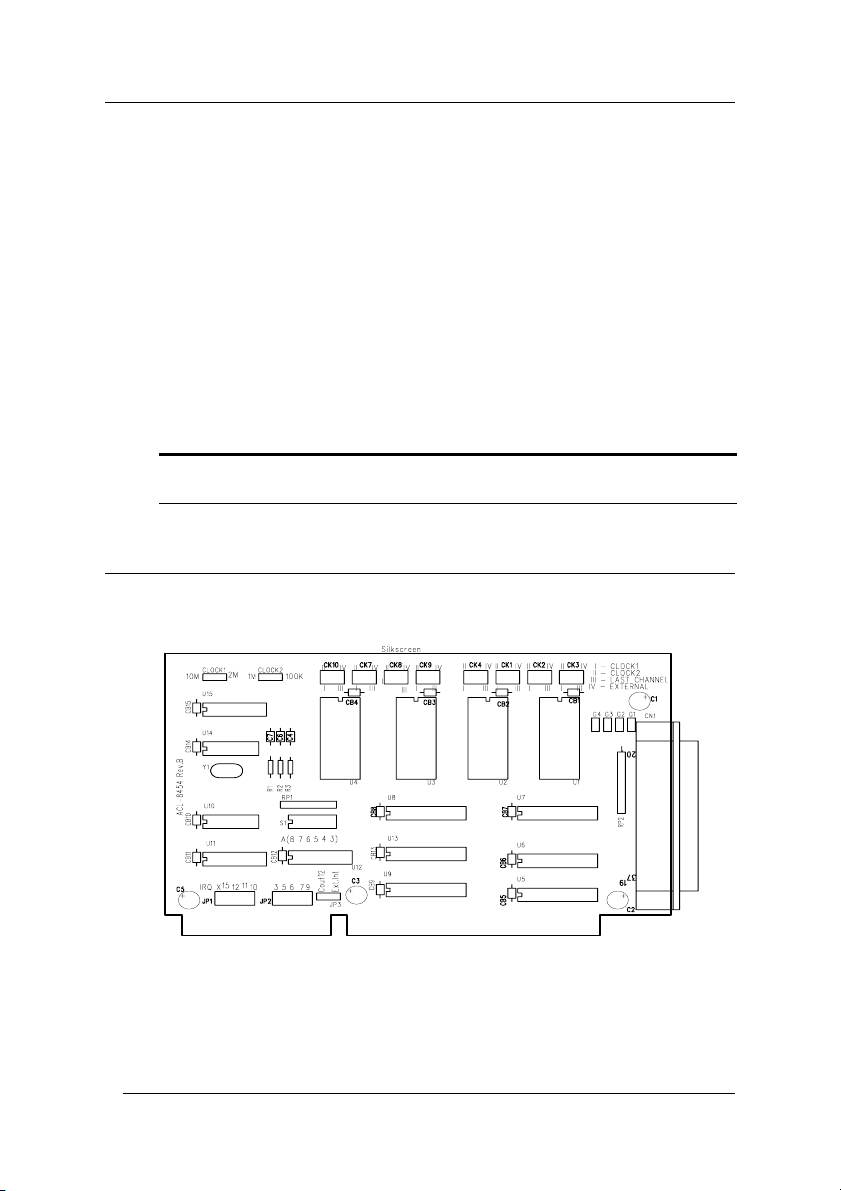

2.3 PCB Layout of ACL-8454

Figure 2.1 PCB Layout of the ACL-8454

6 Installation & Configurations

Page 15

2.4 Default Configurations

To operate the ACL-8454 correctly, users should understand the structure

of ACL-8454 and details of the possible configurations. The block diagram

of the ACL-8454 is shown in chapter 1. It contains the clock system, counter

system, interrupt system and address decoder etc. The following sections

describe the details and the default setting is list in Table 2.1.

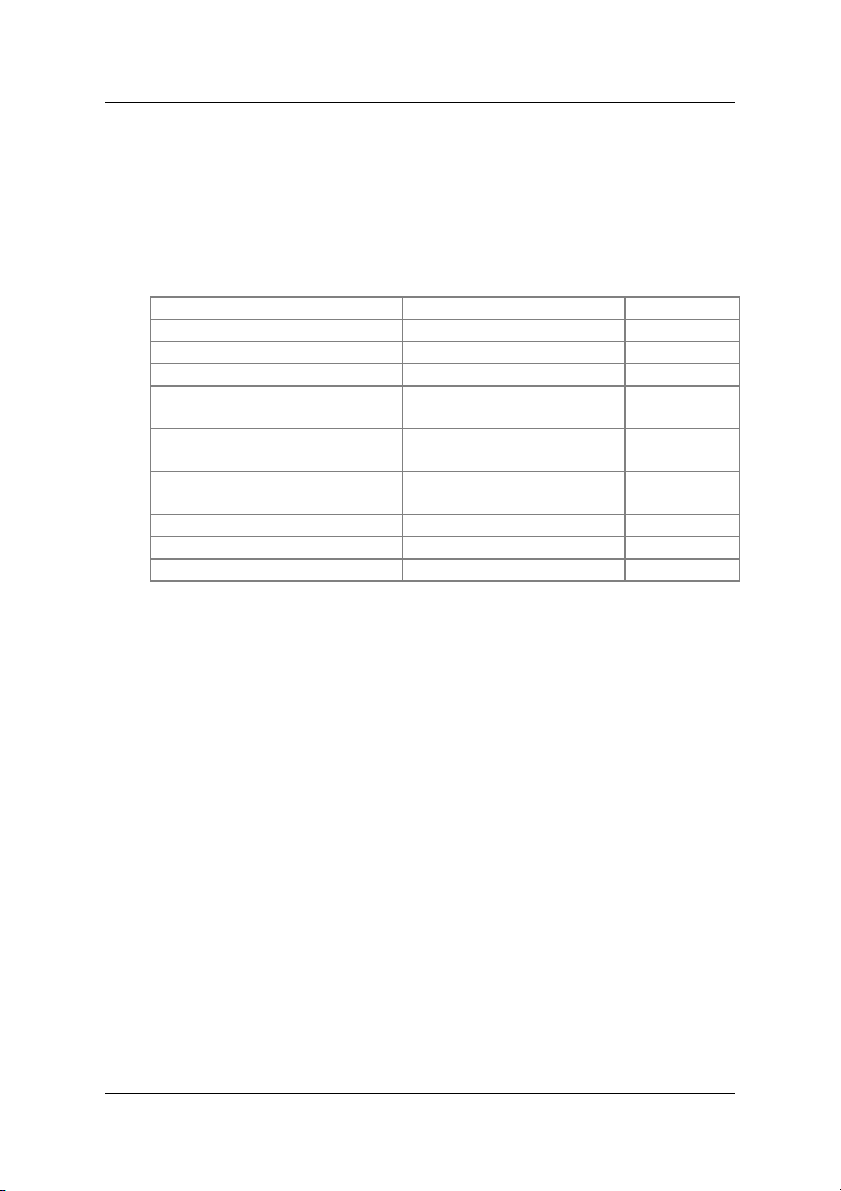

Items Default Configuration Setting by

Base Address 0x240 S1

Clock Source #1 2M Hz CLOCK1

Clock Source #2 100K Hz CLOCK2

8254 chips

Clock Sources of Counters

Gate Sources of

Counter 1~4

Interrupt Level #1 IRQ 15 JP1

Interrupt Level #2 No Connection JP2

Source of Interrupt Level #2 External Interrupt Sources JP3

Table 2.1 Default Configuration of ACL-8454

U1, U2 installed

U3, U4 not installed

Internal Clock Source #1

(=2M Hz)

External Gate G1 ~ G4

--

CK n

You can change the ACL-8454's default configuration by setting jumpers

and DIP switches on the card for your own applications. The card's jumpers

and switches are preset at the factory. A jumper switch is closed

(sometimes referred to as "shorted") with the plastic cap inserted over two

pins of the jumper. A jumper is open with the plastic cap inserted over one

or no pin(s) of the jumper.

Before changing the default configuration, users must fully understand the

operation of the ACL-8454. The setting and the basic operation theorem are

discussed in this chapter. It is recommended to refer chapter 3 for details of

the registers and to refer chapter 4 for application notes.

Installation & Configurations 7

Page 16

A

2.5 Base Address Setting

The ACL-8454 requires 8 consecutive address locations in the I/O address

space. The base address of the ACL-8454 is restricted by the following

conditions.

1.

The base address must be within the range Hex 200 to Hex 3FF.

2.

The base address should not conflict with any reserved I/O address.

3.

The base address must not conflict with any add-on card on your

own PC. Please check your PC before installing the ACL-8454.

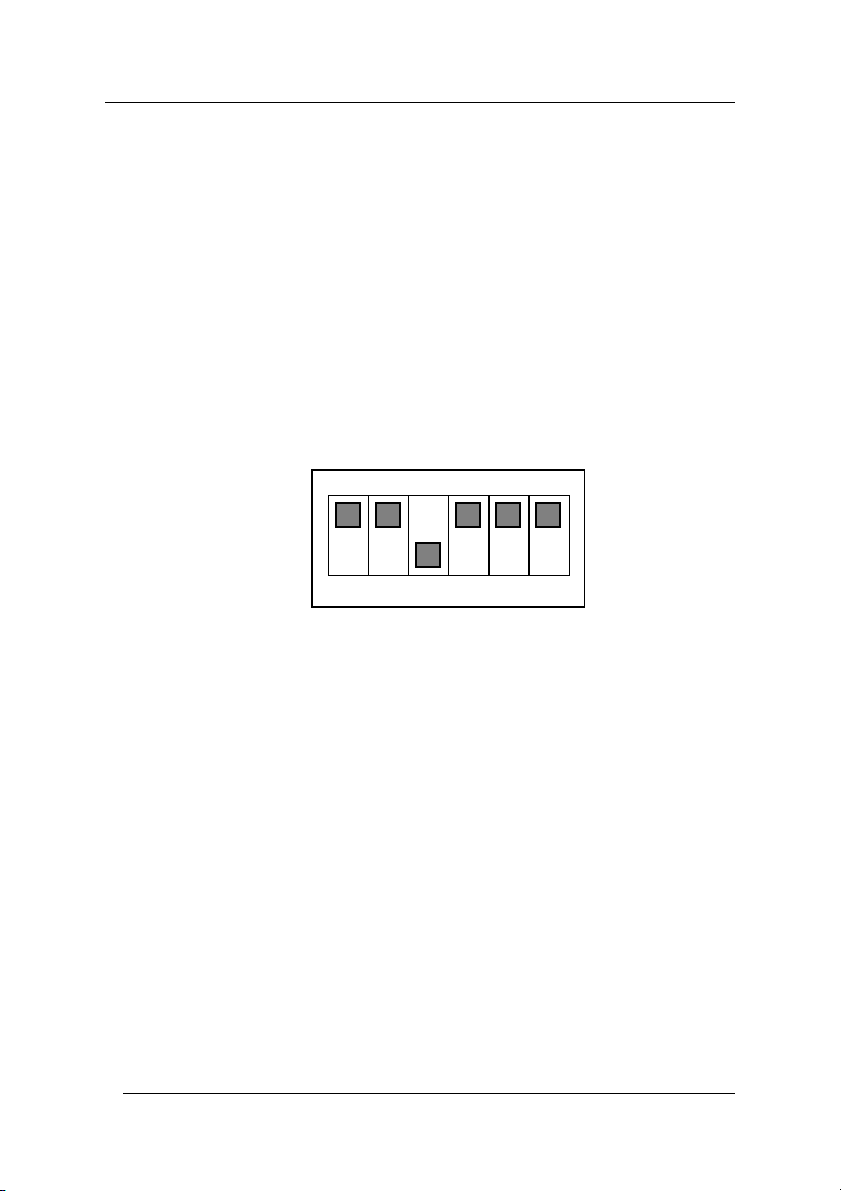

The base address of ACL-8454 is selected by a 6 positions DIP switch S1.

The default setting of base address is set to be HEX 240. All possible base

address combinations are listed as Table 2.2. You may modify the base

address if the default address has been occupied by another add-on card.

ON

S1

1 2 3 4 5 6

( 8 7 6 5 4 3 )

A3 ~ A8 control the BASE I/O address.

Figure 2.2 Default Base Address Setting

8 Installation & Configurations

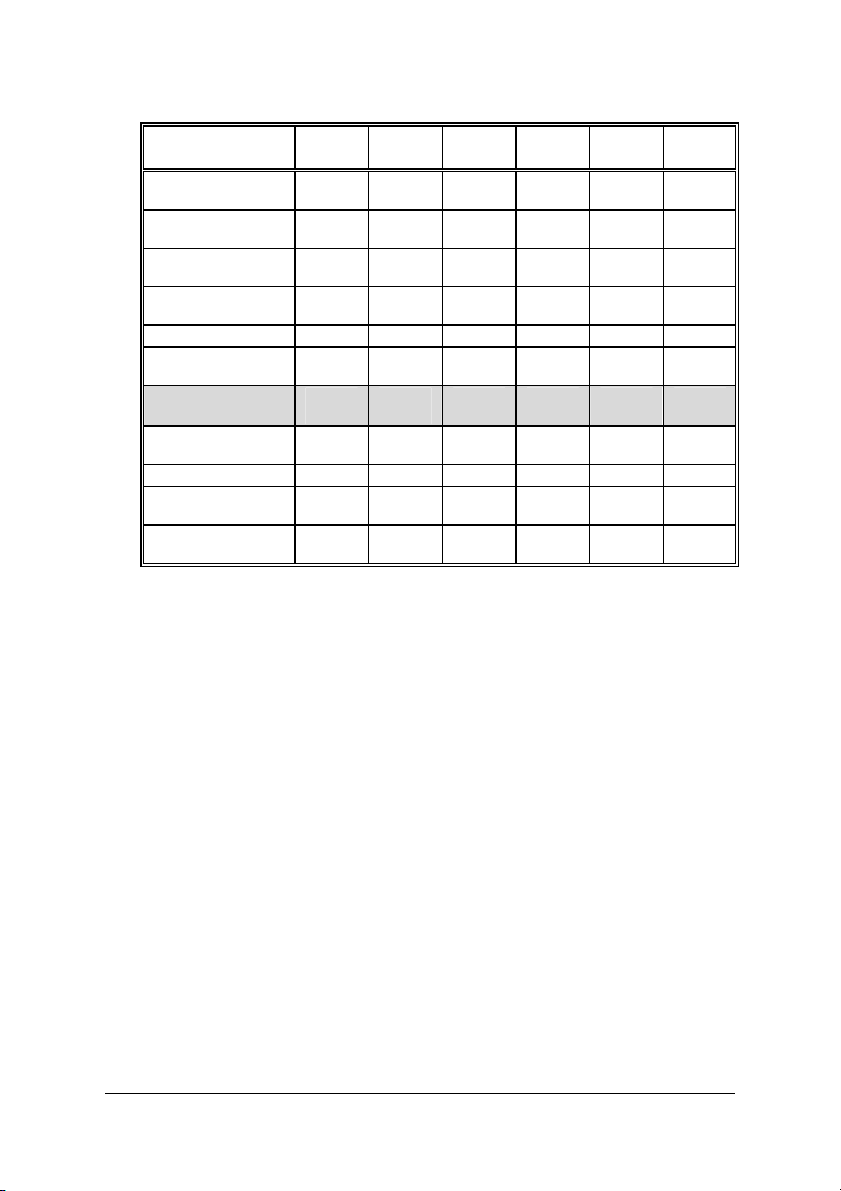

Page 17

I/O port

Address (Hex) 1 A8

200-207

208-20F

210-217

218-21F

:

237-23F

240-247

(default)

248-24F

:

3F0-3F7

3F8-3FF

ON

(0)

ON

(0)

ON

(0)

ON

(0)

: : : : : :

ON

(0)

ON

(0)

ON

(0)

: : : : : :

OFF

(1)

OFF

(1)

2

A7

ON

(0)

ON

(0)

ON

(0)

ON

(0)

ON

(0)

ON

(0)

ON

(0)

OFF

(1)

OFF

(1)

3

A6

ON

(0)

ON

(0)

ON

(0)

ON

(0)

ON

(0)

OFF

(1)

OFF

(1)

OFF

(1)

OFF

(1)

* A3, ..., A8 is corresponding to PC Bus address lines

Table 2.2. Possible Base Address Combinations

4

A5

ON

(0)

ON

(0)

ON

(0)

ON

(0)

OFF

(1)

ON

(0)

ON

(0)

OFF

(1)

OFF

(1)

5

A4

ON

(0)

ON

(0)

OFF

(1)

OFF

(1)

OFF

(1)

ON

(0)

ON

(0)

OFF

(1)

OFF

(1)

6

A3

ON

(0)

OFF

(1)

ON

(0)

OFF

(1)

OFF

(1)

ON

(0)

OFF

(1)

ON

(0)

OFF

(1)

Installation & Configurations 9

Page 18

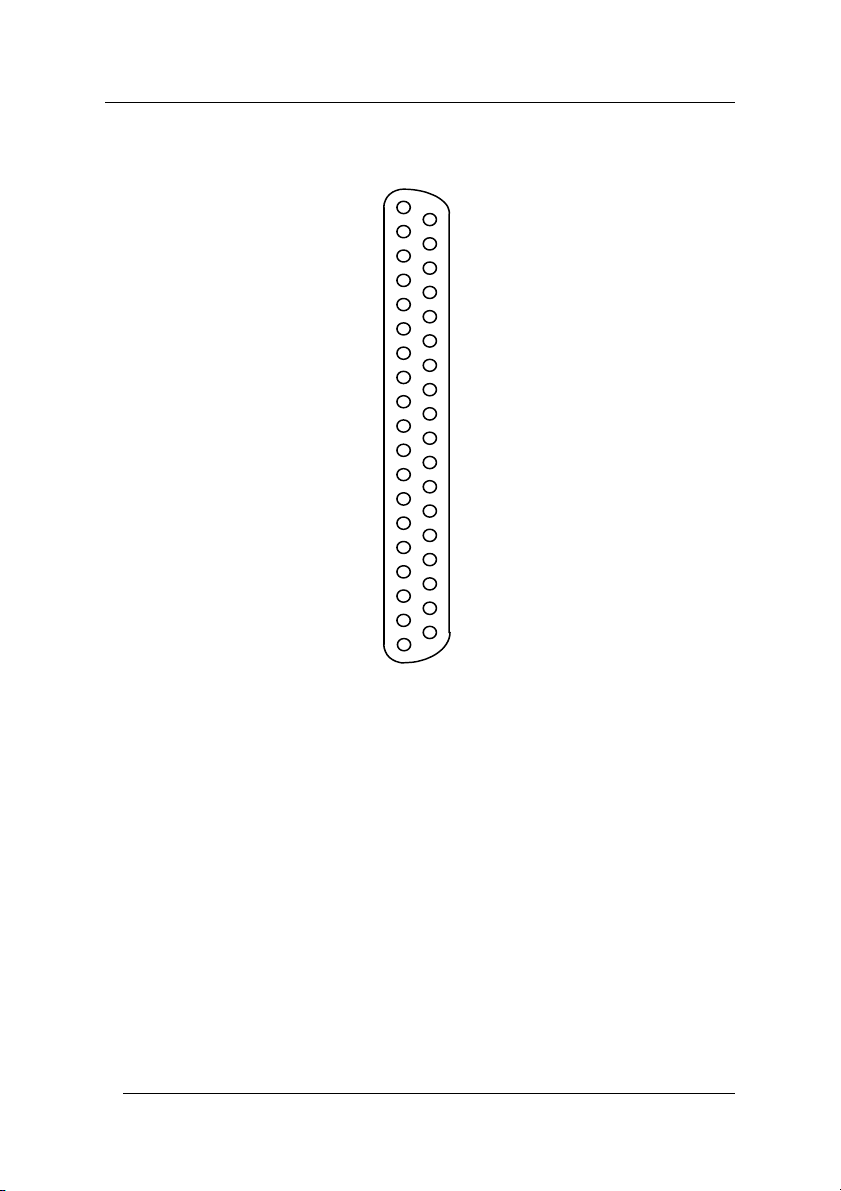

2.6 Pin Assignment of Connector

CN1

(1)

GND

ECLK1(DI0)

COUT1

ECLK2(DI1)

ECLK3(DI2)

COUT3

ECLK4(DI3)

ECLK7(DI8)

COUT7

ECLK8(DI9)

ECLK9(DI10)

COUT9

ECLK10(DI11/EInt)

COUT6

DO0

DO2

DO4

DO6

+5V

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)

(10)

(11)

(12)

(13)

(14)

(15)

(16)

(17)

(18)

(19)

Legend:

ECLK n : External clock source for counter #n

ExtG n : External gate signal for counter #n

COUT n : Counter/Timer output of counter #n

DO m : Digital output port channel #m

DI m : Digital input port channel #m

Eint : External interrupt signal input

(20)

(21)

(22)

(23)

(24)

(25)

(26)

(27)

(28)

(29)

(30)

(31)

(32)

(33)

(34)

(35)

(36)

(37)

GND

ExtG1(DI4)

ExtG2(DI5)

COUT2

ExtG3(DI6)

ExtG4(DI7)

COUT4

ExtG7(DI12)

ExtG8(DI13)

COUT8

ExtG9(DI14)

ExtG10(DI15)

COUT10

COUT12(EInt)

DO1

DO3

DO5

DO7

Figure 2.3 Pin Assignment of Connector CN1

The pin assignment of the 37 pins D-type connector (CN1) is shown in

Figure 2.3. The abbreviations of signal names are listed in Table 2.3. The

signal name conventions are used through this manual. Some signal pins

are multi-function signals. For example, the ECLK10 are not only used as

clock source of counter #10, but also be used as external interrupt source

and be connected to digital input channel.

10 Installation & Configurations

Page 19

2.7 Clock System

The clock system of ACL-8454 provides the internal clock source for the

8254 chips. The block diagram of the clock system is shown in the Figure

2.4. Two clock sources, which named as CLOCK1 and CLOCK2, are

divided from the internal 10Mhz signal. The clock of every counter/timer can

be one of the 4 sources: CLOCK1, CLOCK2, external clock source or

cascaded source from the ‘last’ channel. Refers to next section for details

of setting clock for each counter/timer.

The crystal on ACL-8454 is 10 MHz which is the highest frequency of the

card. The maximum speed of the 8254 chips can run under 10 MHz. As

users plug the lower speed 8254 chips into ACL-8454, the lower frequency

clock source should be used. A frequency divider is used to generate 2MHz

for such circumstance.

Note:

OSC

10 MHz

Certain versions of 8254 or 8253 chips, such as 8254-5, can

run under only 2 MHz.

÷5

2M Hz

10M Hz

100K Hz

÷10÷2

1M Hz

CLOCK2

CLOCK1

Figure 2.4 Clock system of ACL-8454

Installation & Configurations 11

Page 20

M

M

CLOCK1 (High Frequency)

The clock source of CLOCK1 can be set by jumper ‘CLOCK1’. The

frequency could be

10 MHz

or

2 MHz

. Figure 2.5 shows the jumper setting

and the corresponding frequency. The default setting of CLOCK1 is using 2

MHz.

CLOCK1= 2 MHz

CLOCK1

10

2M

CLOCK1= 10 MHz

CLOCK1

10M

2M

(Default)

Figure 2.5 Jumper setting of CLOCK1

CLOCK2 (Low Frequency)

The clock source of CLOCK2 can be set by jumper ‘CLOCK2’. The

frequency could be

1 MHz

or

100 KHz

which are divided from CLOCK1.

The CLOCK2 is provided for low frequency applications. Figure 2.6 shows

the jumper setting and the corresponding frequency. The default setting of

CLOCK2 is using 100 KHz.

CLOCK2= 100 KHz

CLOCK2

1

100K

CLOCK2= 1 MHz

CLOCK2

1M

100K

(Default)

Figure 2.6 Jumper setting of CLOCK2

If user‘s application need a clock frequency lower than 100 KHz, the first

method is to use external clock source, the second method is to use one

counter to generate a frequency lower than 100 Khz then cascaded the low

frequency signal to the other counter’s clock source. This cascaded

counter configuration is feasible on the ACL-8454 by jumper setting. See

the next section for details of how to set cascaded counter.

12 Installation & Configurations

Page 21

2.8 Counters Architecture

There are at most four 8254 chips on the ACL-8454 card. The chip #1 (U1)

and chip #2 (U2) are default mounted on the card, therefore 6 counters are

default on board. It is possible to expand to four 8254 chips by plugging the

additional chip #3 (U3) and chip #4 (U4) into ACL-8454 and totally 12

counters are available. The default counters on chip #1 and #2 are labeled

as counter #1 to counter #6. The expandable counters on chip #3 and #4

are labeled as counter #7 to counter #12. Some counters are default

configured as

cascaded counters

as

reference number of chips and the counters number.

8254 Chip

Number

Chip #1 U1 Counter #2 Independent Installed

Chip #2 U2 Counter #5 Installed

Chip #3 U3 Counter #8 Independent Not installed

Chip #4 U4 Counter #11 Not Installed

independent counters

. Table 2.3 illustrates the relationship between the

Reference

Number

Counter #1 Independent

Counter #3 Independent

Counter #4 Independent

Counter #6 Cascaded

Counter #7 Independent

Counter #9 Independent

Counter #10 Independent

Counter #12 Cascaded

Table 2.3 Default Counters Architecture

and the others are default configured

Counter

Number

Type of

Counter

Installed

Default

Installation & Configurations 13

Page 22

There are three signals (2 input,1 output) for each counter, a clock input

signal, a gate control signal, and an output signal. The Figure 2.7 illustrates

the block diagram of the 8254 counter. CLK1 ~ CLK12 are clock sources

and GATE1 ~ GATE12 are gate control signals. The COUT1 ~ COUT12

are outputs of the counters. The Figure 2.8 shows all the labels and the

inter-connection of the 8254 counters when all the 4 chips are installed. The

COUT5 and COUT11 are used only for internal.

Clock Source Input

Gate Control Input

8254 Chip

C

G

Counter

Counter / Timer Output

O

Figure 2.7 Block Diagram of the 8254 Counter

CLK4

GATE4

1 MHz COUT5

COUT5

CLK10

GATE10

1M Hz

COUT11

8254 Chip #2

C

Counter #4

G

C

Counter #5

G

'H'

C

Counter #6

G

'H'

8254 Chip #4

C

Counter #10

G

C

Counter #11

G

'H'

C

Counter #12

G

'H'

Figure 2.8 Counters Architectural

O

O

O

O

COUT11

O

O

COUT4

COUT6

COUT10

COUT12

CLK1

GATE1

CLK2

GATE2

CLK3

GATE3

CLK7

GATE7

CLK8

GATE8

CLK9

GATE9

8254 Chip #1

C

Counter #1

G

C

Counter #2

G

C

Counter #3

G

8254 Chip #3

C

Counter #7

G

C

Counter #8

G

C

Counter #9

G

O

O

O

O

O

O

COUT1

COUT2

COUT3

COUT7

COUT8

COUT9

14 Installation & Configurations

Page 23

Independent Counters

(Counter #1~#4, & Counter #7~#10)

The Counter #1 to Counter #4 and Counter #7 to Counter #10 are

independent because the clock source and gate control of those counters

can be set independently. These 8 counters are named as independent

counters.

CLK1

GATE1

8254 Chip #1

C

Counter #1

G

COUT1

O

Figure 2.9 Example of ‘independent counters’

Cascaded Counters

The connection of Counter #5, #6 and Counter #11, #12 are different with

other independent counters. These four counters are named as cascaded

counters because the clock sources of counter #5 and #11 come from fixed

1 MHz

and their output are cascaded to counter #6 and #12 respectively. In

fact, counter #5, #6 and counter #11, #12 are designed for frequency

divider by using 8254's square wave generator mode. The gates of these

counters keep at 'H' level for enabling counters all the time. The COUT6

and COUT12 can precisely generate frequency upper to 250 KHz and lower

to 0.000233 Hz. Note that the signals COUT6 and COUT12 can also be

used as interrupt source. See ‘Interrupt Sources’ section for details. The

following figure demonstrates a set of cascaded counter - counter #5 and

#6.

8254 Chip #2

C

1 MHz COUT5

COUT5

G

'H'

C

G

'H'

Counter #5

Counter #6

O

COUT6

O

Figure 2.10 Example of ‘cascaded counter’

User Configurable Cascaded Counters

Although there are two cascaded counter on board, users may need more

cascaded counters. User can configure the jumper for the clock source of

every independent counter. Therefore, the independent counter output can

be cascaded to the next counter's clock source by jumper setting. Figure

2.11 demonstrates an example of the user configurable cascaded counter.

Refer to next section for details of the clock source setting.

Multi-Configurations

Installation & Configurations 15

Page 24

The ACL-8454 provides multi-configurations for many situations. Users may

need more independent counters for some applications. Users can installed

one more 8254 to chip #3(U3) by yourself to get 3 more independent

counters. It is also possible to install one more 8254 chip to #4(U4) and get

one more set of cascaded counter or to get another internal interrupt

source(refer to section 2.11).

The versatile configurations of ACL-8454 depend on user‘s applications.

You may also order the extent version named as ACL8454/12. On which all

four chips are installed when shipping.

8254 Chip #1

C

Counter #1

G

C

Counter #2

G

COUT1

O

COUT2

O

Cascaded

Counters

Output

CLOCK1

VCC

VCC

Jumper 'CK2'

CLK1

GATE1

CLK2

GATE2

Figure 2.11 Example of ‘user configurable cascaded counters’

2.9 Clock Source Configurations

For every independent counter, four signals can be chosen as clock source

by jumper setting. The clock source of counter #n comes from either

CLOCK1, CLOCK2, the external clock source (ECLK n), or the cascaded

counter output. Note that the clock sources of the cascaded counters

(counter #5, #6, #11 and #12) are fixed.

CLOCK1

CLOCK2

ECLK n

COUT x

Figure 2.12 Clock Source of Counter #n

CLK n

16 Installation & Configurations

Page 25

The two internal clock sources, CLOCK1 and CLOCK2 come from the

clock system (see 'Clock System section'). The cascaded clock source

comes from the output of the counter with smaller channel number. For

example, the COUT1 is cascaded to source of CLK2; the COUT3 is

cascaded to source of CLK4. The exceptions are the cascaded source of

CLK1 comes from COUT4 and the cascaded source of CLK7 comes from

COUT10.

The external clock source named as ECLK n comes from the 37-pins

connector. Figure 2.13 demonstrates the clock source jumper setting

counter channel 1 (CLK1) by jumper ‘ CK1 ’. In this figure, the clock source

comes from the internal source CLOCK1.

I

II

CK1

IVIII

Figure 2.13 Setting the Clock Source of Counter #1

The jumper setting is flexible for user applications. There are four kinds of

configurations for every clock source jumper.

(1) Use internal clock source CLOCK1.

I

CK n

(2) Use internal clock source CLOCK2.

I

CK n

Sources of CLK1 (by setting jumper CK1)

CLOCK1

I:

CLOCK2

II:

LAST CHANNEL (COUT4)

III:

EXTERNAL (ECLK 1)

IV:

II

CLOCK1

I:

CLOCK2

II:

LAST CHANNEL

CLK n

III:

EXTERNAL

IV:

IVIII

II

CLOCK1

I:

CLOCK2

II:

LAST CHANNEL

CLK n

III:

EXTERNAL

IV:

IVIII

Installation & Configurations 17

Page 26

(3) Use cascaded clock source from the last channel.

I

II

CK n

CLK n

IVIII

(4) Use external clock source ECLK n.

I

II

CK n

CLK n

IVIII

The Table 2.4 shows the reference number of the clock source jumpers and

its corresponding counter/timer channels number. The default setting of

every jumper is also shown. The clock sources of CLK1~4 come from

internal source ‘

external sources.

Clock source of

counter/timer

CLK1 CK1 CLOCK1

CLK2 CK2 CLOCK1

CLK3 CK3 CLOCK1

CLK4 CK4 CLOCK1

CLK7 CK7 ECLK7

CLK8 CK8 ECLK8

CLK9 CK9 ECLK9

CLK10 CK10 ECLK10

Table 2.4 Reference Numbers of Clock Setting Jumpers

CLOCK1’

and the clock sources of CLK7~10 come from

Reference number

of jumper

CLOCK1

I:

CLOCK2

II:

LAST CHANNEL

III:

EXTERNAL

IV:

CLOCK1

I:

CLOCK2

II:

LAST CHANNEL

III:

EXTERNAL

IV:

Default clock source

18 Installation & Configurations

Page 27

2.10 Gate Control Configurations

The gate control signals of the independent counters are internally pulled

high hence they are default enabled if no external gate used. When the

external gate signals are used, the counters can be used to measure pulse

width. Moreover, the gate of counter #1 ~ #4 come from the reverse of

counter #6 output by jumper selecting. Therefore, the time interval of the

counter gate can be precisely controlled and frequency measurement is

possible. Figure 2.14 shows the jumper setting of gate control of counter

#1~ #4.

ExtG n

VCC

/COUT 6

(1) Jumper NOT installed : External gate control

ExtG n

/COUT 6

(2) Jumper installed : Cascaded gate control

GATE n

VCC

GATE n

Figure 2.14 Gate source of counter #1 ~#4

The jumper setting is flexible for users‘ applications. There are two

configurations: jumper installed or NOT installed. The default state of

jumper is not installed and the counter can be controlled externally or just

pull-high enable. When the jumper installed, the gate is cascaded from

counter #6 output and the ExtG n signal is an output signal.

Note that the external gate source must NOT be used when cascaded gate

source is used. Table 2.5 shows the reference number of the gate control

jumpers and its corresponding counter/timer channels number. The default

setting of every jumper is also shown.

Jumper Label Gate source of counter/timer Default gate ource

G1 GATE1 ExtG1

G2 GATE2 ExtG2

G3 GATE3 ExtG3

G4 GATE4 ExtG4

Table 2.5 Reference number of clock setting jumpers

2.11 Counter Outputs

Installation & Configurations 19

Page 28

The timer/counter output signals (COUT n) of 8254 are controlled by clock

source, gate control and software program. All the outputs of the 8

independent counters are sent to the 37 pins connector directly. The

COUT6 and COUT12 of the two pairs of cascaded counters are also sent to

connector. Therefore, totally 10 counter outputs are sent to connector, see

'Pin assignment' for corresponding signal pin number.

In addition, the output-signals may be used as clock sources or gate

controls of the cascaded counters, see the above sections. It is possible to

cascaded two counters by jumpers. The counters output COUT6, COUT12

are also used as internal interrupt source (refers to 'Interrupt System').

2.12 Interrupt System

The ACL-8454 has two interrupt sources on board. That means the two

interrupt levels or two IRQ lines can be used by this board. The block

diagram of the interrupt system is shown in Figure 2.15.

The two IRQ channels can be set by jumper

high IRQ level is jumper wired to IRQ 10~15 and the low IRQ level is jumper

wired to IRQ 3~9. The source of the high IRQ level comes from /COUT6

which is the

The reversed COUT6 interrupt is very useful because the /COUT6 is also

send to the gate control of counter #1 ~ #4 for frequency measurement.

While /COUT6 is high, the frequency measurement is counting. When

/COUT6 goes low, the counting is ending and an interrupt is generated from

interrupt system so that the software can sample and memorize the result of

frequency measurement. In watchdog application, using reversed COUT6

has no problems because the frequency of COUT6 and reversed COUT6 is

the same.

The sources of the low IRQ level come from internal (COUT12) or external

(ECLK10) source which are jumper selectable by

not reversed counter output.

reversed output

of cascaded counters.

JP1

JP2

and

JP3

respectively. The

. Note the COUT12 is

Note:

20 Installation & Configurations

The IRQ channels must not conflict with other add-on cards on

your PC.

Page 29

/

6

COUT

IRQ 101112 15X

High IRQ Level

JP1

Ext.Int.

(ECLK10)

IRQ356 79

COUT12

Low IRQ Level

JP3

JP2

Figure 2.15 Block diagram of interrupt system

The default setting of the high and the low IRQ levels come from /COUT6

and ECLK10 respectively. The interrupt system on ACL-8454 is very

flexible to use. No matter under any system configuration, it is possible to

generate interrupt internally or externally.

In fact, when chip #4 are not installed, the COUT12 are floating and its

corresponding pin in the connector can be used as digital input pin or

external interrupt source. Whenever 8254 chip #4 is installed, it is an

internal interrupt source, otherwise, it is used as an external clock source or

just a digital input signal. The following table lists the combinations of the

interrupt sources. The label ‘I’ means ‘internal’ source and the label ‘e’

means ‘external’ source. The label ‘DI’ means the signal can be used as

digital input pin dedicatedly.

Chip

Chip

Chip

#1

#2

1

2

3

4

#3

Chip

/COUT6 COUT12 ECLK10 Remarks

#4

i e DI

i i e

i e DI

i i e

ACL-8454 / 6

ACL-8454 / 12

user installed

user installed

Table 2.6 Chips installation and interrupt sources

When 2 default chips (#1 and #2) are installed on ACL-8454, /COUT6 is

internal but COUT12 can be used as external interrupt source. ECK10 is

still used as digital input pin. If user installs the chip #3 by yourself, the

interrupt sources are in the same configuration as condition 1.

When all 4 chips are installed, /COUT6, COUT12 are internal interrupt

sources, only ECLK10 can be used as external. If user installs the chip #4

by yourself, the interrupt sources are the same configuration as condition 2.

2.13 Digital Input and Output

Installation & Configurations 21

Page 30

To program digital I/O operation is fairly straightforward. The digital input

operation is just to read data from the corresponding registers, and the

digital output operation is to write data to the corresponding registers. The

digital I/O registers‘ format are shown in section 3.11. It is not necessary to

set any jumper for digital I/O.

2.14 Summary of Default Setting

Chip #1 and chip #2 are installed. Counter #1 ~ counter #6 are

available. Chip #3 and chip #4 are not installed.

Counter #1~ #4 and counter #7~#10

CLK n = CLOCK1 n

GATE n = ExtG n

Counter #5 and Counter #6

CLK5 = 1 MHz

CLK6 = COUT5

GATE11,12 are default enable

Counter #11 and Counter #12

CLK11 = 1 MHz

CLK12 = COUT11

GATE11,12 are default enable

22 Installation & Configurations

Page 31

2.15 Notes for Installing More 8254 Chips

The user can install 8254 chips to ACL-8454 card by yourself. Before install

the additional 8254 chip, please make sure the ACL-8454 card is removed

from the PC slot, no power is applied and no external daughter board is

attached.

When plugging 8254 chips, please check the pin of chips must not be fold

and install the chip into the socket carefully. After installing the chip, please

configure the jumper setting of the ACL-8454 card according to your

application. At first the clock source of counter #7 ~ #10 should be set. The

gate source of counter #7~#10 cannot be configured, however, user should

notice whether if any external gate source or digital signal is connected to

the signals. The un-wanted signal may control the gate source of the

counters can cause your application fail.

The low IRQ source should also be checked because the counter #12 is

installed and COUT12 can only be used as internal interrupt source if 8254

chip #4 is installed. Please take care the issues mentioned above.

Installation & Configurations 23

Page 32

3

Registers Format

This chapter describes details of the register format of the ACL-8454. This

information is quite useful for the programmers who wish to handle the card

by low-level program.

In addition, the low level programming is introduced. This information can

help the beginners to manipulate the ACL-8454 in the shortest learning time.

3.1 I/O Port Address

The ACL-8454 requires 6 consecutive addresses in the PC I/O address

space. There are four 8254 chips in ACL-8454, however, these 8254 chips

use the same I/O address. Two chip select bits are used to select active

chip. The Table 3.1 shows the I/O address of each register with respect to

the base address.

I/O Address Write Read

Base + 0 Counter 0 Counter 0

Base + 1 Counter 1 Counter 1

Base + 2 Counter 2 Counter 2

Base + 3 Mode Control No use

Base + 4 Chips select DI low byte

ECLK1~4, ExtG1~4

Base + 5 Digital Output DI high byte

ECLK7~10, ExtG7~10

Table 3.1 I/O Address Map of ACL-8454

24 Registers Format

Page 33

3.2 Timer/Counter Registers

Every 8254 occupies 4 I/O address locations in the ACL-8454 as shown

below. Condensed information is specified in Appendix B Timer/Counter

Operation. Users can refer to Tundra’s website (“http://www.tundra.com”) or

Intel's data sheet for a fully descriptions of the 8254 features (see

“http://support.intel.com/support/controllers/peripheral/231164.htm”). Note

that only one 8454 chip can be enabled at the same time.

Address : BASE + 0 ~ BASE + 3

Attribute :

Data Format :

Base + 0 Counter 0 Register ( R/W)

Base + 1 Counter 1 Register ( R/W)

Base + 2 Counter 2 Register ( R/W)

Base + 3 8254 Mode Control Register (W)

read / write

8254 Read Back Register (R)

3.3 Chip Select Register

Although there are at most four 8254 chips can be installed on board,

however, only one 8254 can be selected at the same time. The bits 0, 1 of

the chip select register (CS1 and CS0) are used to select 8254 chips.

Whenever a chip is selected (active), the 8254 I/O address (BASE+0 ~

BASE+3) is selected by this chip. The active chip is enabled by CS0 and

CS1 according the following table.

Address : BASE + 4

Attribute :

Data Format :

Base + 4 -- -- -- -- -- -- CS1 CS0

8254 Chip # CS1

write only

Bit 7 6 5 4 3 2 1 0

Chip #1

Chip #2

Chip #3

Chip #4

0 0

0 1

1 0

1 1

CS0

Registers Format 25

Page 34

3.4 Digital Input Registers

There are 16 digital input channels on the ACL-8454. The digital input

channels are common with the external gate signals (ExtG 1~3 & ExtG

7~10) and the external clock signals (ECLK 1~3 & ECLK 7~10).The

external clock source ECLK n and external gate control ExtG n can be read

back from the DI ports. When the external clock sources and the external

gate signals are not used for counters, these channels can be used as

digital input signal dedicatedly. For example, the chip #3 and #4 are not

installed under default configuration, ECLK7~10 and external gate

ExtG7~10 are not used hence the port (BASE+5) can be used as a digital

input port dedicatedly. Even if these external clock or gate signals are used

for counters, the input port can still monitor their signal level.

Address : BASE + 4 & BASE + 5

Attribute :

Data Format :

Bit 7 6 5 4 3 2 1 0

Base + 4

Base + 5

or

Bit 7 6 5 4 3 2 1 0

Base + 4 ExtG4 ExtG3 ExtG2 ExtG1 ECLK4 ECLK3 ECLK2 ECLK1

Base + 5 ExtG10 ExtG9 ExtG8 ExtG7 ECLK10 ECLK9 ECLK8 ECLK7

read only

DI15 DI14 DI13 DI12 DI11 DI10 DI9 DI8

DI7 DI6 DI5 DI4 DI3 DI2 DI1 DI0

3.5 Digital Output Register

The register is a general purpose 8 bits digital output port. These signals

can be used to control external devices.

Address : BASE + 5

Attribute :

Data Format :

Base + 5

26 Registers Format

write only

Bit 7 6 5 4 3 2 1 0

DO7 DO6 DO5 DO4 DO3 DO2 DO1 DO0

Page 35

3.6 Low-level Programming

To manipulate the ACL-8454, users may understand how to write a

hardware dependent low-level program. Using either assembly or high-level

language such as BASIC or C language can carry out the low-level

programming. The following gives examples to show how to use

programming language to access an add-on I/O card.

Getting Start

Before programming, the add-on card should be correctly installed. After

installing the card, the users should already understand how much system

(PC) resources are used by this card, such as I/O address, IRQ channels,

and even DMA channel, etc.

The second step is to study the register format and the operation theorem

of the card. Then users can try to write low-level programs to operate it.

Although the high-level program library is available, the low-level

programming can improve the efficiency and perform functions which the

library does not support. The low level programming is not difficult and may

be necessary to understand.

Programming Language

The programming language to be used is dependent on users' familiarity

and the system requirement. No matter what kind of language is used, the

user must understand the syntax of the I/O instructions to access the I/O

card. The following sections introduce the syntax of the often used

programming language. In each section, the write (output) port instruction

and the read (input) port instruction are shown. In the examples, the base

address of the I/O card is assumed as HEX 240 and the port of the register

to be access is BASE+2.

Assembly

To write an output port:

out 240h,value

out 240h,register

To read an input port

in A, 240h

Registers Format 27

Page 36

BASIC language

To write an output port:

10 BASE=&H240

20 VALUE% = &H2F

30 OUT( BASE+2), VALUE %

or

10 OUT( &H242 ), &H20

To read an input port

10 BASE=&H240

20 VALUE=INP( BASE+2)

or

10 VALUE=INP( &H242 )

C language (Borland C++)

To write an output port:

#define BASE 0x240

unsigned int Value=0x2F;

outportb( BASE+2 , Value );

or

outportb( 0x242 , 0x2F );

To read an input port

#define BASE 0x240

unsigned int Value;

Value = inp

or

Value = inportb( 0x242 );

Perform Functions

Users should study the operation theorem and the relative data sheet to

understand how to operate this card, and then use the low-level

programming to perform those functions. Generally, the DIO control can be

easily performed by only a few instructions, it is very suitable to use the low

level programming.

As to the higher-level functions such as the interrupt service routines, pulse

width measurement, frequency measurement, etc, user may use the library

or modify the examples to carry them out. However, fully understanding of

the PC system is necessary for certain applications.

ortb( BASE+2 );

28 Registers Format

Page 37

4

Signal Connections &

Applications

This chapter describes the connectors and some application wiring of the

ACL-8454. Including the signal connection between the ACL-8454 and

external devices, such as daughter boards or other devices.

4.1 Connectors Pin Assignment

The ACL-8454 comes equipped with a D-type 37 pin female connector

(CN1). The CN1 is located at the rear plate. The pin assignment of the

connector is illustrated in the Figure 2.1. Refer to section 2.1 for details of

pin assignment.

4.2 Daughter Board Connection

The ACL-8454 can be connected with daughter boards ACLD-9137, ACLD9138, ACLD-9188, and DIN-37D to extend the bus.

Signal Connections & Applications 29

Page 38

4.3 Digital I/O Connection

The ACL-8454 provides 16 digital input and 8 digital output channels

through the connector CN1. The digital I/O signals are fully TTL/DTL

compatible.

Digital Input(DI)

From TTL Devices

Digital Output (DO)

To TTL Devices

GND

ACL-8454

Outside Device

Figure 4.1 Digital I/O Connections

4.4 Timer / Counter Connection

The ACL-8454 has four 8254 chips on board. It offers 8 independent 16-bit

programmable down counters and two pairs of cascaded counters. To

implement your applications, you can follow the procedure to design your

applications and connect the signals.

1. Check if the frequencyof the clock source is fixed, if answer is ‘No’

then go to step 7.

2. Calculate the frequency of clock according to your application and

decide the clock source: internal, external, or cascaded. Then

decided which counter is used.

3. If internal clock source is used, configure the CK n jumpers

according the calculation in step 2.

4. If external clock source is used, to generate a clock source outside

the board and check the frequency.

5. If cascaded clock source is used, to configure and program the

cascaded timer to generate the desired clock source.

6. If frequency of the clock is not fixed, only external source can be

used and then connect the external jump wires according your

application.

7. Decide the gate control source: always enable, externally control, or

cascaded controlled.

8. To connect or configure the gate signal of counter/timers.

9. To program the counter/timers using desired mode.

30 Signal Connections & Applications

Page 39

4.5 Frequency Generator

Example 1 : To generate a 250 KHz Square Wave.

step 1: To use

frequency.

step 2: Internal 2 MHz clock source is suitable to generate a 250 KHz

square wave. Use Counter #4 for this application.

step 3: Set jumper ‘CK4’. The clock source is coming from internal

‘CLOCK1’. Note that the CLOCK1 must be set as 2 MHz.

However, the CLOCK1 is shared with other counters. You must

consider the clock source of other counters which using

CLOCK1 in the same time.

step 4 ~ 6 : Skip these steps.

step 7: The gate source is always enabled. Note the jumper ‘G4’

should be removed and no external gate is used.

step 8: Connect the counter output to external device. The following

block diagram illustrates the application.

step 9: Write the control program. Please refer the ‘DEMO1.C’ source

code.

Figure 4.2 Example of frequency generator (1)

Example 2 : To generate a very low frequency of 1 pulse / 1 hour

step 1: To use

frequency.

step 2: Because the desired frequency (1/3600sec=0.000278Hz) is too

slow to use one counter to generate. Even if using cascaded

counter architecture, the clock frequency of the first stage

counter must be as low as possible. At first, try to use

clock. Assume the clock of the first stage is 100 K Hz. then the

frequency divider value of the two cascaded counters is:

It is really a large number. Share the divider value to the two

counters, for example, the divider of the first stage can be

60000 and the divider of the second stage is 6000.

fixed

clock source because the output is a fixed

50 KHz = 2 MHz / 8

Jumper

CLOCK1

Jumper

CK4

2 M Hz

fixed

clock source because the output is a fixed

'H'

8254 Chip #2

C

Counter #4

G

100 K Hz / 0.000278 Hz = 360,000,000

O

COUT4

internal

Signal Connections & Applications 31

Page 40

360,000,000 = 60000 x 6000

Therefore, ‘user configurable cascaded counters’ can be used

to solve this problem. The counter #1 and #2 are used in this

example.

step 3: Set jumper ‘CK1’. The clock source is internal ‘CLOCK2’ and it

is set as 100 KHz in default. Then set jumper ‘CK2’ and the

clock source is coming for the output of the ‘Last channel (#1)‘.

step 4: Skip these steps.

step 5: Write and verify the control program for counter #1.

step 6: Skip these steps.

step 7: The gate source of the two counters is enable always. Note the

jumper ‘G1’ and ‘G2’ should be removed and no external gate

signals are used.

step 8: Connect the counter #2 output to external device. The following

block diagram illustrates the application

step 9: Write and verify the control program. Please refer the

‘DEMO2.C’ source code.

Jumper

CLOCK2

Jumper

CK1

100 K Hz

'H'

8254 Chip #1

C

Counter #1

G

O

COUT1

Jumper

CK2

'H'

Figure 4.3 Example of frequency generator (2)

32 Signal Connections & Applications

8254 Chip #1

C

Counter #2

G

O

COUT2

Page 41

4.6 Pulse Width Measurement

Example : To measure pulse width (with T < 32ms)

Jumper

CK3

fixed

clock source as base time interval (or base

nternal 2M Hz

t = 1/2M=5x10e-7 sec

t < pulse width < t *65535 (=32.768 msec)

2 M Hz

clock is used. The time base is

8254 Chip #1

C

Counter #3

G

Pulse Width

O

COUT3

Polling D/I for checking the

end of a pulse

step 1: To use

frequency).

step 2: Assume I

The count range for measuring pulse width is:

If the specification of the pulse width to be measured is in the

range, the 2M Hz can be used. Otherwise changing the base

frequency of the counter. The counter #3 is used in this

example.

step 3: Set jumper ‘CK3’ for internal 2 M Hz clock source.

step 4 ~ 6 : Skip these steps.

step 7: The external gate source is just the signal to be measured. The

width of the high pulse can be measured. Note that if the pulse

is shorter, the time resolution is worse. If the pulse is wider, the

limitation of the maximum pulse width should be care.

step 8: The following block diagram illustrates the application.

step 9: Write the control program. Please refer the ‘DEMO3.C’ source

code.

Jumper

CLOCK1

Signal to be measured

Figure 4.4 Example of pulse width measurement

Signal Connections & Applications 33

Page 42

4.7 Frequency Measurement

Example : To measure frequency around 1~100 K Hz

step 1: This application needs two counters. One counter is used to

generate a pulse whose time interval is very precise. The pulse

is used to enable the other counter (counting counter) by gate

control. On ACL-8454, internal gate control is possible. The

internal gate is coming from /COUT6. In this example, the

pulse generate is counter #6 and the counter #1 is used to

measure frequency.

step 2: The maximum value of counting counter is no more than

65535. For measuring 100 K Hz frequency, the time interval

should be within 1/100 K Hz x 65535 = 0.655 sec. If the time

interval is wider then the measurement resolution is better,

however, if time interval is too long the counting value will be

overflow. That means the low pulse width of counter #6 output

should shorter than 0.655 sec. User can try to generate the

pulse by counter #6 by yourself.

step 3: Configure jumper ‘CK1’. The clock source is the signal to be

measured.

step 4~6: Skip these steps.

step 7: Set the internal jumper ‘G1’. The gate is controlled internally.

step 8: The following block diagram illustrates the application

step 9: Write and verify the control program. The frequency of the

signal is :

frequency = counting value of counter #1 / precise time

interval

Please refer the ‘DEMO4.C’ source code.

34 Signal Connections & Applications

Page 43

frequency to

be measured

Jumper

G1

Jumper

CK1

COUT5

'H'

/COUT6

8254 Chip #2

C

Counter #6

G

8254 Chip #1

C

Counter #1

G

O

O

COUT6

COUT1

Precise

Time

Interval

'H' enable counter #1

Figure 4.5 Example of frequency measurement (1)

The ACL-8454 can

synchronously

measure frequency from

four

channels

because the internal gate control is connected to 4 counters (#1~4) in the

same time. Furthermore, as the gate signal goes low, an interrupt is

generated. The user can write an ISR to sample and calculate the

frequency of all the 4 channels. This feature is very useful in control system.

Jumper

'H'

frequency to

be measured

8254 Chip #m

C

Counter #n

G

O

COUT n

CK1

8254 Chip #1

C

Counter #1

G

external gate control

O

COUT1

Figure 4.6 Example of frequency measurement (2)

Note that the precise gate signal is not necessarily coming from the internal

source. The gate can be generated by any counter and route to gate of

counters externally (refer Figure 4.6.). The frequency measurement

application is quit complicate. User should also be care of the frequency

range to be measured then design a system according to the system

specification.

Signal Connections & Applications 35

Page 44

4.8 Event Counter

Example : To count external event in 1 sec

step 1: This application needs one counter to generate a time base of

1 sec and the second counter to count the event. The

cascaded counter #5, #6 can perform the watchdog timer.

Counter #1 is used as an example to count external event. The

clock source of counter #1 is the event signal and the

frequency is not fixed.

step 2~6: Skip these steps.

step 7: The gate source is always enabled and the external gate must

be removed.

step 8: Connect the signal according to Figure 4.7.

step 9: Write the control program. Please refer the ‘DEMO5.C’ source

code.

Event signal

Jumper

CK1

'H'

8254 Chip #2

C

Counter #1

G

O

COUT1

8254 Chip #2

C

Counter #6

G

O

COUT6

JP1

Figure 4.7 Example of event counter

36 Signal Connections & Applications

IRQ channel : Watchdog Interrupt

Page 45

4.9 Double Interrupt System

One Internal plus one external interrupt sources

The ACL-8454 provides double interrupt sources which are very useful in

some application. For example, most of the application needs a watchdog

timer to monitor the system periodically, hence, an IRQ channel is used. In

addition, the emergency control may be necessary, hence, an additional

external IRQ channel is helpful to handle the situation. Therefore, double

interrupt level is necessary. The external interrupt source can be routed to

COUT12 if 8254 chip #4 is not installed.

8254 Chip #2

C

Counter #6

G

O

/COUT6

JP1

IRQ channel : Watchdog Interrupt

COUT12

Ext.Clk

JP3

COUT12

JP2

IRQ channel : External Interrupt

Figure 4.8 Example of double interrupt system

Two internal interrupt sources

For certain application, /COUT6 is used to generate gate control pulse for

measuring frequency and to generate interrupt too. This internal IRQ

channel is used to calculate frequency data. However, another internal

watchdog timer interrupt may be still necessary. Users can install 8254 chip

#4 to get one more pair of cascaded counters (#11, #12). The COUT12 can

be used as watchdog interrupt source. Therefore, two internal interrupt

sources are available.

Signal Connections & Applications 37

Page 46

5

High-Level Programming

There are more than 10 functions provided by the C language library. By

using the C language library, it saves a lot of programming time.

If you need to perform some special functions which are not provided in the

library, you can modify the library according to your requirement. The fully

commented C source of the library is also included in your software library

diskette. It is a good starting point for C language programmers who wish to

modify the functions in the library.

In addition to library and source code, some demonstrating programs are

also included in the disk. It will help you to understand the library more

quickly.

Please refer to the demonstration examples in the software to get examples

of the using of the library

5.1 Installation

MS-DOS/Windows 3.1 Software Installation

With "ACL-8454 Library & Utility" diskette:

1. Turn your PC's power switch on.

2. Put the " ACL-8454 Library &Utility" diskette into your floppy drive A:

or B:

for DOS

for Win 3.1

38 High-Level Programming

: A:\DOS\SETUP.BAT

: A:\WIN31\SETUP.BAT

Page 47

With CD-ROM:

1. Turn your PC's power switch on.

2. Put the CD-ROM into your CD-ROM drive.

3. Type the commands:

Dos:

X:\> CD\NuDAQISA\8454\DOS

X:\NuDAQISA\8454\DOS> SETUP

(x identifies the drive that contains the CD-ROM)

After installation, all the files of ACL-8454 Library & Utility for DOS

are stored in C:\ADLink\8454\DOS directory.

Windows 3.1:

X:\> CD\NuDAQISA\8454\WIN31

X:\NuDAQISA\8454\DOS> SETUP

(x identifies the drive that contains the CD-ROM)

After installation, all the files of ACL-8454 Library & Utility for

Windows 3.1 are stored in C:\ADLink\8454\W31 directory.

Win-95/Win-NT Software Installation

With "ACL-8454 Library & Utility" diskette:

1. Turn your PC's power switch on.

2. Put the " ACL-8454 Library &Utility" diskette into your floppy drive A:

or B:

for Win-95

for Win-NT

With CD-ROM:

step 1:

Place the ADLink CD-ROM into the appropriate CD drive.

step 2:

If auto-run setup program is not invoked automatically,

step 3:

: A:\Win95\SETUP.EXE

: A:\WinNT\SETUP.EXE

please execute X:\setup.exe. (X indicates the CD-ROM

drive)

Select NuDAQISAÆACL-8454ÆWin95DLL or NuDAQISA

ÆACL-8454ÆWinNT DLL to install software.

High-Level Programming 39

Page 48

[Win-NT only]

When the software component installation process is completed and the

system that ACL-8454 Library is installed on is Windows NT, Setup will

launch the Driver Registry Utility (8454Util.exe) for you to make the registry

of the drivers that you want to perform interrupt operation.

The Driver Registry Utility first shows the following window. If 8454 driver

has been registered, it will be shown on the Registered Driver list.

If the ACL-8454 device

please click “Done” or “Exit!” to exit this utility. Click “New…” button and a

Driver Configuration window appears for you to set IRQ levels and base

address.

ACL-8454

/COUT6 which is the reversed output of internal cascaded counters and the

other is IRQ2 (low IRQ) from COUT12 which is from internal timer or

external source (ECLK10). The “Driver Configuration” window for ACL-8454

is:

40 High-Level Programming

can support two interrupt lines. One is IRQ1 (high IRQ) from

DOES NOT

want to perform interrupt operation’,

Page 49

If you don’t need to use both of these two IRQ lines, set the unused IRQ

level as “0”. Then you can save one IRQ level for your system.

After the setting for IRQs level and base address, click “OK” to register the

driver.

When you finish the driver register, select “Done” or “Exit!” to exit this utility.

To make the registered drivers work, you have to re-start Windows NT

system.

Note :

If your device driver can not be started, please check if the

resources ( I/O Port Address or IRQ Level) conflict with other

hardware device. You can use 8454Util utility to change the

resource setting. After the ACL-8454 DLL for Win-NT is

installed, this utility is located in <InstallDir>\Util directory.

[Win-95 & Win-NT]

After you complete the installation of ACL-8454 Library, ACL-8454’s DLL

(8454.DLL) is copied to Windows System directory (default is

C:\Windows\System for Win95 or C:\Winnt\System32 for Win-NT). The

driver files for Win-95 (w95_8454.VXD) are copied to the Windows System

directory (default is C:\ Windows\System) or the driver files for Win-NT

(DIO.SYS and 8454.SYS) are copied to the Windows NT System Drivers

directory (the default directory is C:\Winnt\System32\Drivers).

High-Level Programming 41

Page 50

5.2 W_8454_Initial

@ Description

To initial the base address used which used by the following

functions. The default base address set in the library is 0x240.

However, you should call this function before using others functions.

@ Syntax

Microsoft C/C++ (Windows, Win95 & Win-NT)

int W_8454_Initial(int base_address)

Visual Basic

Windows 3.11 Version:

W_8454_Initial (ByVal base_address As Integer) As Integer

Win-95 or Win-NT Version:

W_8454_Initial (ByVal base_address As Long) As Long

C/C++ (DOS)

int _8454_Initial( int base_address )

@ Arguments

int base_address : base address of the card

@ Return Value

No_Error : No error

Base_Address_Error : When the base address is illegal

42 High-Level Programming

Page 51

5.3 Set_Chip

@ Description

This is a macro which is used to select or active one of the four 8254

chips. Refer the 8454.H for the definition of the Set_Chip macro. This

macro is used by other functions in this library, it may not necessary

be used by users.

@ Syntax

Microsoft C/C++ (DOS, Windows, Win95 & Win-NT)

Set_Chip( int ChipNo )

@ Arguments

int ChipNo : chip number, equal 1 to 4.

@ Return Value

No return value

5.4 W_8454_Write_Counter

@ Description

To write a command to a counter. The user can directly assign the

counter number 1~12, therefore it is not necessary to care about the

chips number and other details. The output and response of the

counter is dependent on the ‘Mode’ argument and the configuration

on hardware.

@ Syntax

Microsoft C/C++ (Windows, Win95 & Win-NT)

int W_8454_Write_Counter(int CntrNo,int Mode,unsigned int

CntrVal)

Visual Basic

Windows 3.11 Version:

W_8454_Write_Counter (ByVal CntrNo As Integer, ByVal

Mode As Integer, ByVal CntrVal As Integer) As Integer

Win-95 or Win-NT Version:

W_8454_Write_Counter (ByVal CntrNo As Long, ByVal Mode

As Long, ByVal CntrVal As Long) As Long

C/C++ (DOS)

int _8454_Write_Counter(int CntrNo,int Mode,unsigned int

CntrVal )

High-Level Programming 43

Page 52

@ Arguments

int CntrNo : Counter number, equals to 1~12

int Mode : Operation mode of counter, equals to 1 ~6

unsigned int CntrVal :The 16 bits counter value to write to the

counter.

@ Return Value

No_Error : No error

Invalid_Counter_No : CntrNo is out of range.

Invalid_Timer_Mode : Mode is out of range

5.5 W_8454_Read_Counter

@ Description

To read the counter value from a counter. The user can directly

assign the counter number 1~12, therefore it is not necessary to care

about the chips number and other details.

@ Syntax

Microsoft C/C++ (Windows, Win95 & Win-NT)

int W_8454_Read_Counter (int CntrNo, int *Mode, unsigned

int *CntrVal)

Visual Basic

Windows 3.11 Version:

W_8454_Read_Counter (ByVal CntrNo As Integer, Mode As

Integer, CntrVal As Integer) As Long

Win-95 or Win-NT Version:

W_8454_Read_Counter (ByVal CntrNo As Long, Mode As

Long, CntrVal As Long) As Long

C/C++ (DOS)

int _8454_Read_Counter(int CntrNo, int *Mode, unsigned int

*CntrVal)

@ Arguments

int CntrNo : Counter number, equals to 1~12

int *Mode : Operation mode of counter, equals to 1 ~6

UINT *CntrVal : address to save the read back counter value

@ Return Value

No_Error : No error

Invalid_Counter_No : CntrNo is out of range.

44 High-Level Programming

Page 53

5.6 W_8454_Stop_Counter

@ Description

This function is used to stop a specified counter. The user can

directly assign the counter number 1~12, therefore it is not necessary

to care about the chips number and other details.

@ Syntax

Microsoft C/C++ (Windows, Win95 & Win-NT)

int W_8454_Stop_Counter (int CntrNo, unsigned int *CntrVal)

Visual Basic

Windows 3.11 Version:

W_8454_Stop_Counter (ByVal CntrNo As Integer, CntrVal As

Integer) As Long

Win-95 or Win-NT Version:

W_8454_Stop_Counter (ByVal CntrNo As Long, CntrVal As

Long) As Long

C/C++ (DOS)

int _8454_Stop_Counter(int CntrNo, unsigned int *CntrVal)

@ Arguments

int CntrNo : Counter number, equals to 1~12

UINT *CntrVal : address to save the read back counter value

@ Return Value

No_Error : No error

Invalid_Counter_No : CntrNo is out of range.

High-Level Programming 45

Page 54

5.7 W_8454_DO

@ Description

To write an 8 bits data to the digital output port.

@ Syntax

Microsoft C/C++ (Windows, Win95 & Win-NT)

int W_8454_DO (int DO_Value)

Visual Basic

Windows 3.11 Version:

W_8454_DO (ByVal DO_Value As Integer) As Integer

Win-95 or Win-NT Version:

W_8454_DO (ByVal DO_Value As Long) As Long

C/C++ (DOS)

int _8454_DO(int DO_Value )

@ Arguments

DO_Value : the value to write to digital output port, only the 8 LSBs

of the value are effective.

@ Return Value

Always no error

5.8 W_8454_DI

@ Description

To read the data of the digital input port. It is possible to read the 8

LSBs, 8 MSBs, or read only one bit channel by the DI relative

functions.

@ Syntax

Microsoft C/C++ (Windows, Win95 & Win-NT)

int W_8454_DI( UINT *DI_Value )

int W_8454_DI_L( UINT *DI_LValue )

int W_8454_DI_H( UINT *DI_HValue )

int W_8454_DI_bit( int Bit_No )

Visual Basic

Windows 3.11 Version:

W_8454_DI (DI_Value As Integer) As Integer

W_8454_DI_L (DI_LValue As Integer) As Integer

W_8454_DI_H (DI_HValue As Integer) As Integer

W_8454_DI_bit (ByVal Bit_No As Integer) As Integer

Win-95 or Win-NT Version:

W_8454_DI (DI_Value As Long) As Long

46 High-Level Programming

Page 55

W_8454_DI_L (DI_LValue As Long) As Long

W_8454_DI_H (DI_HValue As Long) As Long

W_8454_DI_bit (ByVal Bit_No As Long) As Long

C/C++ (DOS)

int _8454_DI( UINT *DI_Value )

int _8454_DI_L( UINT *DI_LValue )

int _8454_DI_H( UINT *DI_HValue )

int _8454_DI_bit( int Bit_No )

@ Arguments

UINT *DI_Value : the 16 bits digital input value of port BASE+4 and

BASE+5

UINT *DI_LValue : the digital input value of port BASE+4, note that

only the low 8 bits is effective

UINT *DI_HValue : the digital input value of port BASE+5, note that

only the low 8 bits is effective

int Bit_No : the bit channel number to be read back, the value should

be in the range of 0 ~ 15

@ Return Value

Always no error for _8454_DI(), _8454_DI_L(), _8454_DI_H()

For _8454_DI_bit():

Invalid_Bit_Number (0xFF) : argument out of range

0 or 1 : the return value of the digital input channel

5.9 8454 Mode Functions

@ Description

This is a macro, instead of using function, which is used to program the

mode of the counters. Refer the 8454.H for the definition of these macros.

The macro names are designed for easy to memorize or to be referenced.

User can use these macros instead of using the ‘_8454_Write_Counter()’

function.

High-Level Programming 47

Page 56

@ Syntax

Microsoft C/C++ (Windows, Win95 & Win-NT)

W_8454_Interrupt_on_TC(CN,Val) == W_8454_Write_Counter( CN, 0, Val )

W_8454_One_Shoot(CN,Val) == W_8454_Write_Counter( CN, 1, Val )

W_8454_Square_Wave(CN,Val) == W_8454_Write_Counter( CN, 2, Val )

W_8454_Rate_Generator(CN,Val) == W_8454_Write_Counter( CN, 3, Val )

W_8454_SW_Strobe(CN,Val) == W_8454_Write_Counter( CN, 4, Val )

W_8454_HW_Strobe(CN,Val) == W_8454_Write_Counter( CN, 5, Val )

C/C++ (DOS)

_8454_Interrupt_on_TC(CN,Val) == _8454_Write_Counter( CN, 0, Val )

_8454_One_Shoot(CN,Val) == _8454_Write_Counter( CN, 1, Val )

_8454_Square_Wave(CN,Val) == _8454_Write_Counter( CN, 2, Val )

_8454_Rate_Generator(CN,Val) == _8454_Write_Counter( CN, 3, Val )

_8454_SW_Strobe(CN,Val) == _8454_Write_Counter( CN, 4, Val )

_8454_HW_Strobe(CN,Val) == _8454_Write_Counter( CN, 5, Val )

@ Arguments

int CN : Counter number, equals to 1~12

UINT Val : The 16 bits counter value to write to the counter.

@ Return Value

No_Error : No error

Invalid_Counter_No : CntrNo is out of range.

Invalid_Timer_Mode : Mode is out of range

@ Example

See ‘DEMO.C’ in library diskette

5.10 W_8454_INT_Enable

@Description

This function is only available in Window 95 driver and Windows

NT driver. The function is used to initialize and start up the interrupt

control. After calling this function, every time an interrupt request

signal generated, a software event is signaled. So that in your

program, your can use wait operation to wait for the event. When

the event is signaled, it means an interrupt is generated. Please

refer to the samples program 8454int.c.

Note :

48 High-Level Programming

The W_8454_INT_Enable and W_8454_INT_Disable are a pair

of functions. That is, as the W_8454_INT_Enable is called, the

W_8454_INT_Disable has to follow up behind it. Otherwise, the

interrupt operation will not stop.

Page 57

@ Syntax

Microsoft C/C++ (Win95 & Win-NT)

int W_8454_INT_Enable(int irq_no, int irql, HANDLE *phEvent)

Visual Basic (Win95 & Win-NT)

W_8454_INT_Enable (ByVal irq_no As Long, ByVal irql As

Long, phEvent As Long) As Long

@ Arguments

irq_no : IRQ channel selected

1: Higher IRQ (From /COUT6)

2: Lower IRQ (From COUT12 or Ext. Int)

irql : The IRQ level of the IRQ channel specified in argument irq_no.

phEvent: The handle of the event for interrupts signals.

@ Return Value

NoError

INT_Not_Set