FEATURES

ACT8846

Rev 1, 15-May-13

Advanced PMU for Multi-core Application Processors

GENERAL DESCRIPTION

INTEGRATED POWER SUPPLIES

• Four DC/DC Step-Down (Buck) Regulators

− 2 x 2.8A, 2 x 1.5A

• Five Low-Noise LDOs

− 2 x 150mA, 3 x 350mA

• Three Low-Input Voltage LDOs

− 1 x 150mA, 2 x 350mA

• One Low IQ Keep-Alive LDO

• Backup Battery Charger

SYSTEM CONTROL AND INTERFACE

• Four General Purpose I/O with PWM Drivers

2

• I

C Serial Interface

• Interrupt Controller

SYSTEM MANAGEMENT

• Reset Interface and Sequencing Controller

− Power on Reset

− Soft / Hard Reset

− Watchdog Supervision

− Multiple Sleep Modes

• Thermal Management Subsystem

APPLICATIONS

• Tablet PC

• Mobile Internet Devices (MID)

• E-books

• Personal Navigation Devices

• Smart Phones

The ACT8846 is a complete, cost effective, and

highly-efficient ActivePMU

solution optimized for the power, voltage

sequencing and control requirements of Rockchip

RK31x8 application processor family.

The ACT8846 features four fixed-frequency,

current-mode, synchronous PWM step-down

converters that achieve peak efficiencies of up to

97%. These regulators operate with a fixed

frequency of 2.25MHz, minimizing noise in sensitive

applications and allowing the use of small external

components. These buck regulators supply up to

2.8A of output current and can fully satisfy the

power and control requirements of the multi-core

application processor. Dynamic Voltage Scaling

(DVS) is supported either by dedicated control pins,

or through I2C interface to optimize the energy-pertask performance for the processor. This device

also include eight low-noise LDOs (up to 350mA

per LDO), one always-on LDO and an integrated

backup battery charger to provide a complete

power system for the processor.

The power sequence and reset controller provides

power-on reset, SW-initiated reset, and power cycle

reset for the processor. It also features the

watchdog supervisory function. Multiple sleep

modes with autonomous sleep and wake-up

sequence control are supported.

The thermal management and protection

subsystem allows the host processor to manage the

power dissipation of the PMU and the overall

system dynamically. The PMU provides a thermal

warning to the host processor when the

temperature reaches a certain threshold such that

the system can turn off some of the non-essential

functions, reduce the clock frequency and etc to

manage the system temperature.

The ACT8846 is available in a compact, Pb-Free

and RoHS-compliant TQFN66-48 package.

TM

power management

Innovative PowerTM - 1 - www.active-semi.com

Active-Semi Proprietary―For Authorized Recipients and Customers

ActivePMU

I2CTM is a trademark of NXP.

TM

is a trademark of Active-Semi.

Copyright © 2013 Active-Semi, Inc.

ACT8846

Rev 1, 15-May-13

TABLE OF CONTENTS

General Information ..................................................................................................................................... p. 01

Functional Block Diagram ............................................................................................................................ p. 03

Ordering Information .................................................................................................................................... p. 04

Pin Configuration ......................................................................................................................................... p. 04

Pin Descriptions ........................................................................................................................................... p. 05

Absolute Maximum Ratings ......................................................................................................................... p. 07

2

C Interface Electrical Characteristics ........................................................................................................ p. 08

I

Global Register Map .................................................................................................................................... p. 09

Register and Bit Descriptions ...................................................................................................................... p. 11

System Control Electrical Characteristics .................................................................................................... p. 17

Step-Down DC/DC Electrical Characteristics .............................................................................................. p. 18

Low-Noise LDO Electrical Characteristics ................................................................................................... p. 19

Low-Input Voltage LDO Electrical Characteristics ....................................................................................... p. 20

Low-Power (Always-On) LDO Electrical Characteristics ............................................................................. p. 21

PWM LED Driver Electrical Characteristics ................................................................................................. p. 21

Typical Performance Characteristics……………………………………………………………………………..p. 22

System Control Information ......................................................................................................................... p. 28

Interfacing with the Rockchip RK31x8 Processors .......................................................................... p. 28

Control Signals ................................................................................................................................. p. 29

Push-Button Control ......................................................................................................................... p. 30

Control Sequences ........................................................................................................................... p. 30

Watch-Dog Supervision ................................................................................................................... p. 31

Software-Initiated Power Cycle ........................................................................................................ p. 31

Functional Description ................................................................................................................................. p. 32

2

C Interface ..................................................................................................................................... p. 32

I

Housekeeping Functions .................................................................................................................. p. 32

Thermal Protection ........................................................................................................................... p. 32

Step-Down DC/DC Regulators .................................................................................................................... p. 33

General Description .......................................................................................................................... p. 33

100% Duty Cycle Operation ............................................................................................................. p. 33

Operating Mode ................................................................................................................................ p. 33

Synchronous Rectification ................................................................................................................ p. 33

Soft-Start .......................................................................................................................................... p. 33

Compensation .................................................................................................................................. p. 33

Configuration Options ....................................................................................................................... p. 33

OK[ ] and Output Fault Interrupt ....................................................................................................... p. 34

PCB Layout Considerations ............................................................................................................. p. 34

Low-Noise, Low-Dropout Linear Regulators ................................................................................................ p. 35

General Description .......................................................................................................................... p. 35

Output Current Limit ......................................................................................................................... p. 35

Compensation .................................................................................................................................. p. 35

Configuration Options ....................................................................................................................... p. 35

OK[ ] and Output Fault Interrupt ....................................................................................................... p. 35

PCB Layout Considerations ............................................................................................................. p. 35

Always-On LDO (REG13) ............................................................................................................................ p. 36

General Description .......................................................................................................................... p. 36

Reverse-Current Protection ............................................................................................................. p. 36

Typical Application ........................................................................................................................... p. 36

PWM LED Drivers ........................................................................................................................................ p. 37

PWM Frequence Selection .............................................................................................................. p. 37

PWM Duty Cycle Selection .............................................................................................................. p. 37

TQFN66-48 Package Outline and Dimensions ........................................................................................... p. 38

Revision History ........................................................................................................................................... p. 39

Innovative PowerTM - 2 - www.active-semi.com

Active-Semi Proprietary―For Authorized Recipients and Customers

ActivePMU

I2CTM is a trademark of NXP.

TM

is a trademark of Active-Semi.

Copyright © 2013 Active-Semi, Inc.

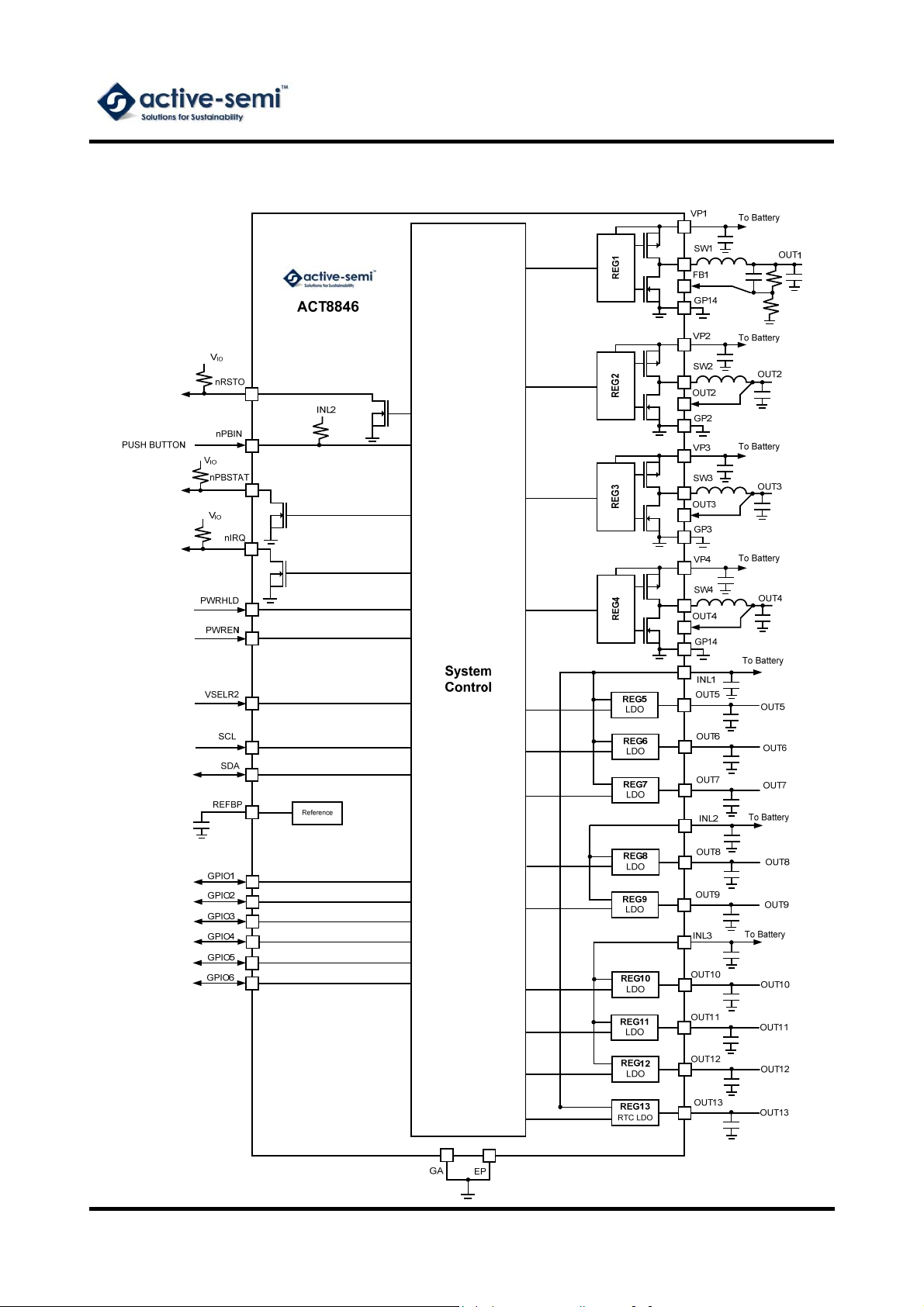

FUNCTIONAL BLOCK DIAGRAM

ACT8846

Rev 1, 15-May-13

Innovative PowerTM - 3 - www.active-semi.com

Active-Semi Proprietary―For Authorized Recipients and Customers

ActivePMU

I2CTM is a trademark of NXP.

TM

is a trademark of Active-Semi.

Copyright © 2013 Active-Semi, Inc.

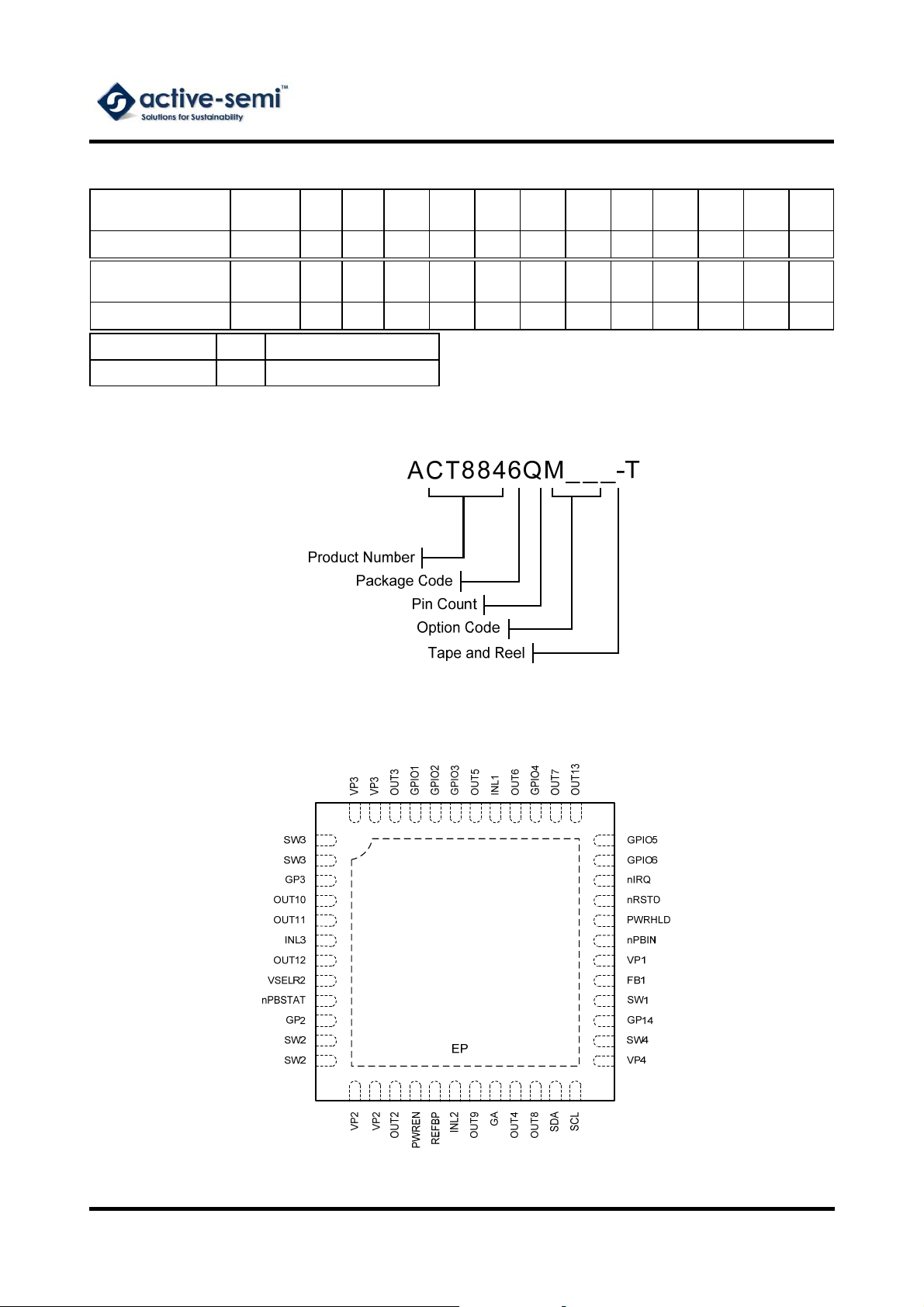

ORDERING INFORMATIONc

ACT8846

Rev 1, 15-May-13

PART NUMBER V

ACT8846QM460-T Adjustable 1.0V 1.0V 3.0V 1.0V 1.2V 1.8V 3.3V 3.3V 3.3V 1.8V 2.8V 1.8V

PART NUMBER V

d

ACT8846QM468-T

PACKAGE PINS TEMPERATURE RANGE

TQFN66-48 48 -40°C to +85°C

c: All Active-Semi components are RoHS Compliant and with Pb-free plating unless specified differently. The term Pb-free means

semiconductor products that are in compliance with current RoHS (Restriction of Hazardous Substances) standards.

d: Push button 10s shut down function is supported in ACT8846QM468 only.

Adjustable 1.0V 1.0V 3.0V 1.0V 1.2V 1.8V 3.3V 3.3V 3.3V 1.8V 2.8V 1.8V

OUT1

OUT1

V

OUT2 VOUT3 VOUT4 VOUT5 VOUT6 VOUT7 VOUT8 VOUT9 VOUT10 VOUT11 VOUT12 VOUT13

V

OUT2 VOUT3 VOUT4 VOUT5 VOUT6 VOUT7 VOUT8 VOUT9 VOUT10 VOUT11 VOUT12 VOUT13

PIN CONFIGURATION

TOP VIEW

ACTIVE

8846QM

DATE CODE

Thin - QFN (TQFN66-48)

Innovative PowerTM - 4 - www.active-semi.com

Active-Semi Proprietary―For Authorized Recipients and Customers

ActivePMU

I2CTM is a trademark of NXP.

TM

is a trademark of Active-Semi.

Copyright © 2013 Active-Semi, Inc.

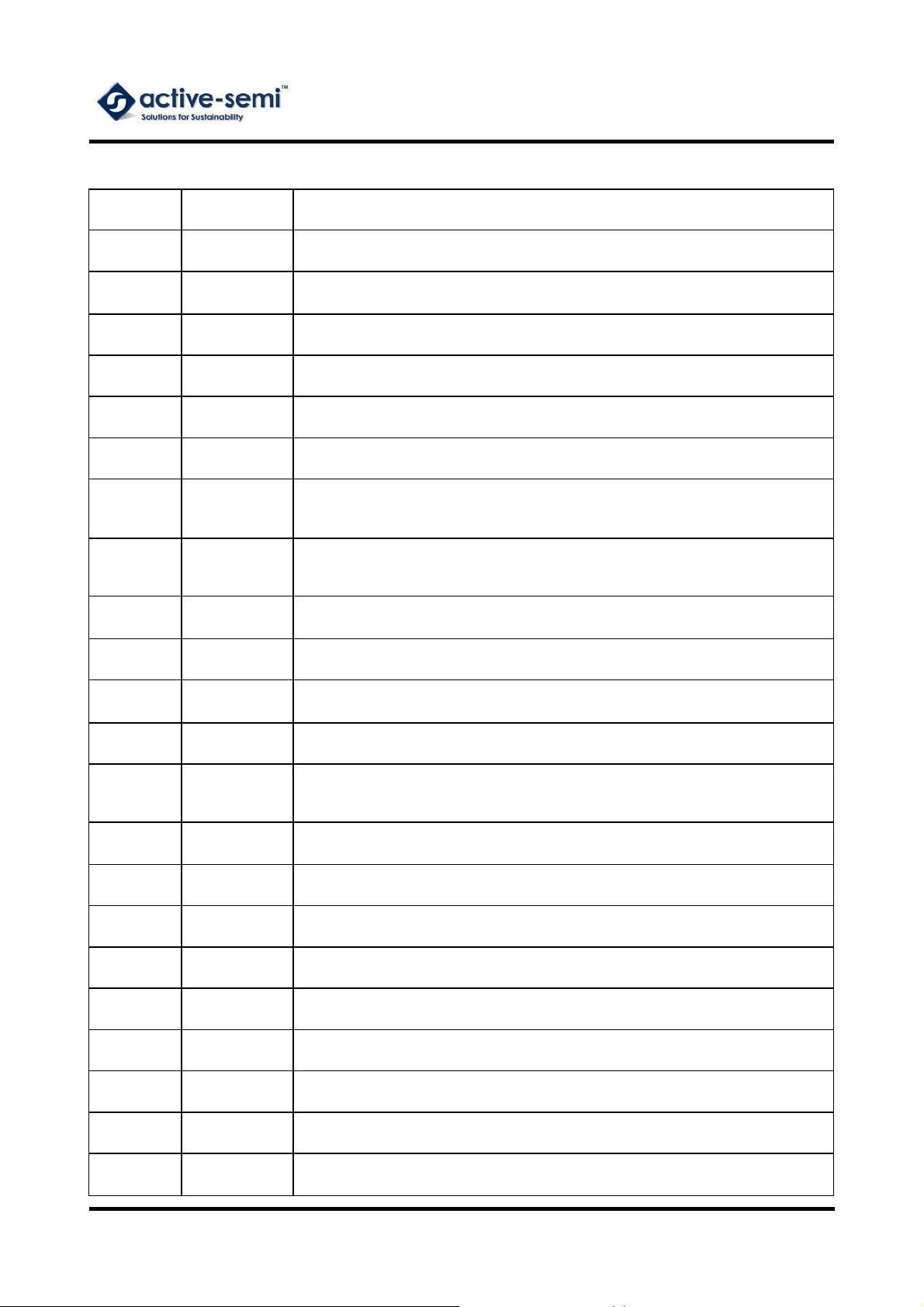

PIN DESCRIPTIONS

PIN NAME DESCRIPTION

1, 2 SW3 Switch Node for REG3.

ACT8846

Rev 1, 15-May-13

3 GP3

4 OUT10 REG10 output. Bypass it to ground with a 2.2µF capacitor.

5 OUT11 REG11 output. Bypass it to ground with a 2.2µF capacitor.

6 INL3 Power input for REG10, REG11 and REG12.

7 OUT12 REG12 output. Bypass it to ground with a 2.2µF capacitor.

8 VSELR2

9 nPBSTAT

10 GP2

11, 12 SW2 Switch Node for REG2.

13, 14 VP2

Power Ground for REG3. Connect GP14, GP2, GP3, and GA together at a single

point as close to the IC as possible.

Output Voltage Selection for REG2. Drive to logic low to select default output voltage.

Drive to logic high to select secondary output voltage.

Active-Low Open-Drain Push-Button Status Output. nPBSTAT is asserted low

whenever the

Power ground for REG2. Connect GP14, GP2, GP3, and GA together at a single

point as close to the IC as possible.

Power input for REG2. Bypass to GP2 with a high quality ceramic capacitor placed as

close to the IC as possible.

nPBIN is pushed, and is high-Z otherwise.

15 OUT2 Output Voltage Sense for REG2.

Power Enable Input for REG3. PWREN is functional only when PWRHLD is driven

16 PWREN

17 REFBP

18 INL2 Power Input for REG8, REG9.

19 OUT9 REG9 output. Bypass it to ground with a 2.2µF capacitor.

20 GA Analog Ground.

21 OUT4 Output voltage sense for REG4.

22 OUT8 REG8 output. Bypass it to ground with a 2.2µF capacitor.

23 SDA Data Input for I

24 SCL Clock Input for I

25 VP4

high. Drive PWREN to a logic high to turn on the REG3. Drive PWREN to a logic low

to turn off the REG3.

Reference Bypass. Connect a 0.047F ceramic capacitor from REFBP to GA. This

pin is discharged to GA in shutdown.

2

C Serial Interface. Data is read on the rising edge of SCL.

2

C Serial Interface.

Power input for REG4. Bypass to GP14 with a high quality ceramic capacitor placed

as close to the IC as possible.

Innovative PowerTM - 5 - www.active-semi.com

Active-Semi Proprietary―For Authorized Recipients and Customers

ActivePMU

I2CTM is a trademark of NXP.

TM

is a trademark of Active-Semi.

Copyright © 2013 Active-Semi, Inc.

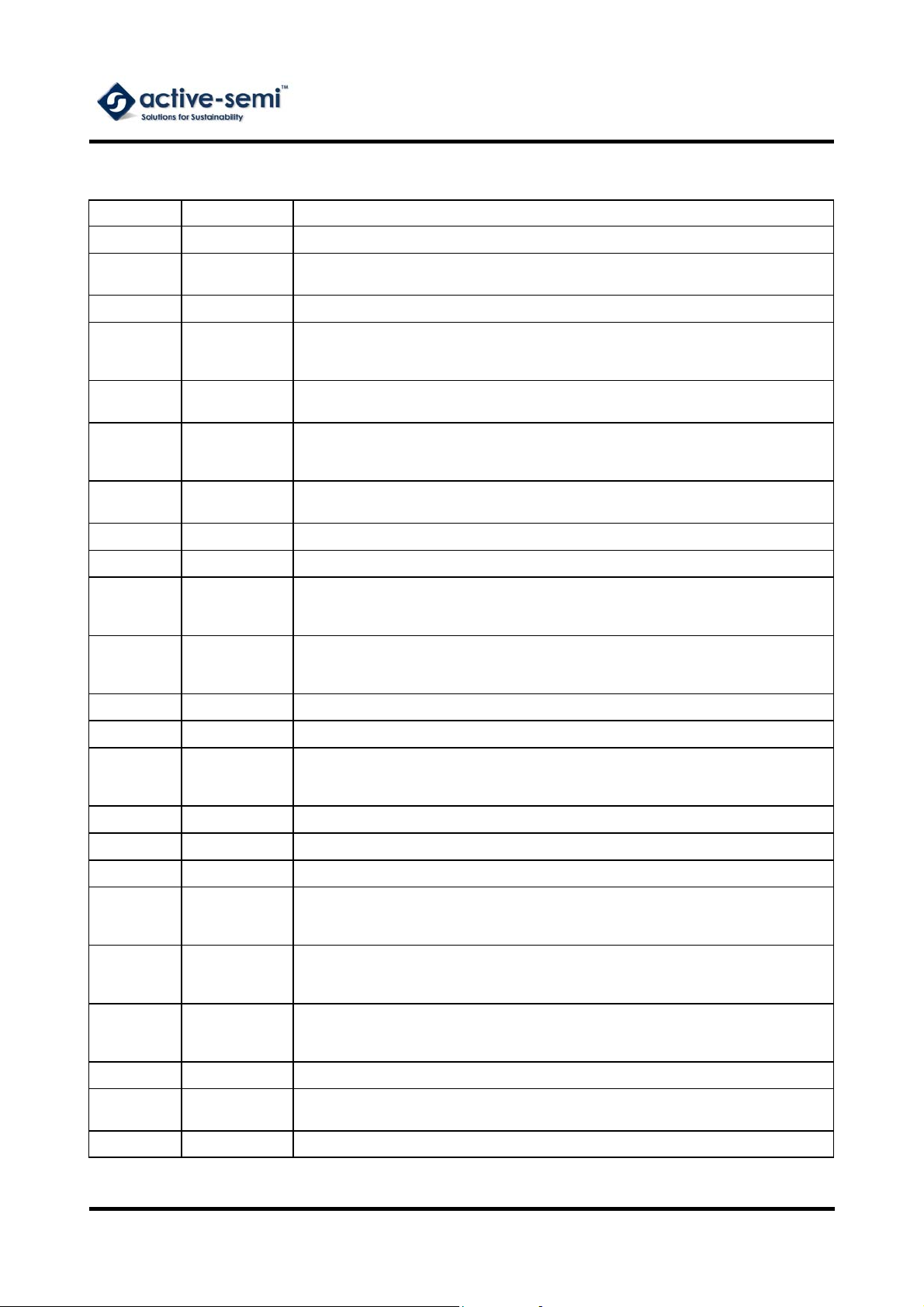

PIN DESCRIPTIONS CONT’D

PIN NAME DESCRIPTION

ACT8846

Rev 1, 15-May-13

26 SW4

27 GP14

28 SW1

29

FB1

30

VP1

31 nPBIN

32 PWRHLD

33 nRSTO

34 nIRQ

35

GPIO6

36 GPIO5

Switch Node for REG4.

Power Ground for REG1 and REG4. Connect GP14, GP2, GP3, and GA together at a

single point as close to the IC as possible.

Switch Node for REG1.

Output Feedback Sense for REG1. For the adjustable output voltage options, connect

this pin to the center of the output feedback resistor divider for voltage setting,

connect this pin to the output directly to regulate the output voltage at 1.2V.

Power Input for REG1. Bypass to GP14 with a high quality ceramic capacitor placed

as close to the IC as possible.

Master Enable Input. Drive nPBIN to GA through a 50k resistor for 32ms to enable

the IC. Drive nPBIN to GA through a 50k resistor for 10 seconds to disable the IC.

Drive nPBIN

Power Hold Input, enable input for REG1, REG2, REG4, REG5, REG6, REG8 and

REG10. PWRHLD is internally pulled down to GA through a 900k resistor.

Open-Drain Reset Output.

Open-Drain Interrupt Output.

General Purpose I/O #6. Configured as PWM LED driver output for up to 6mA current

with programmable frequency and duty cycle. See the PWM LED Drive section for

more information.

General Purpose I/O #5. Configured as PWM LED driver output for up to 6mA current

with programmable frequency and duty cycle. See the PWM LED Driver section for

more information.

directly to GA to assert a Manual-Reset condition.

1

37 OUT13

38 OUT7

39

GPIO4

40 OUT6

41 INL1

42

OUT5

43

GPIO3

44 GPIO2

45 GPIO1

46 OUT3

47,48 VP3

EP EP Exposed Pad. Must be soldered to ground on PCB.

REG13 output. Bypass it to ground with a 0.47µF capacitor.

REG7 output. Bypass it to ground with a 2.2µF capacitor.

General Purpose I/O #4. Configured as PWM LED driver output for up to 6mA current

with programmable frequency and duty cycle. See the PWM LED Driver section for

more information.

REG6 output. Bypass it to ground with a 2.2µF capacitor.

Power Input for REG5, REG6, REG7.

REG5 output. Bypass it to ground with a 2.2µF capacitor.

General Purpose I/O #3. Configured as PWM LED driver output for up to 6mA current

with programmable frequency and duty cycle. See the PWM LED Drier section for

more information.

General Purpose I/O #2. Configured as VSELR4 for Voltage Selection of REG4. Drive

to logic low to select default output voltage.

output voltage.

General Purpose I/O #1. Configured as VSELR3 for Voltage Selection of REG3. Drive

to logic low to select default output voltage.

output voltage.

Output Voltage Sense for REG3.

Power input for REG3. Bypass to GP3 with a high quality ceramic capacitor placed as

close to the IC as possible.

Drive to logic high to select secondary

Drive to logic high to select secondary

1: Only for ACT8846QM468.

Innovative PowerTM - 6 - www.active-semi.com

Active-Semi Proprietary―For Authorized Recipients and Customers

ActivePMU

I2CTM is a trademark of NXP.

TM

is a trademark of Active-Semi.

Copyright © 2013 Active-Semi, Inc.

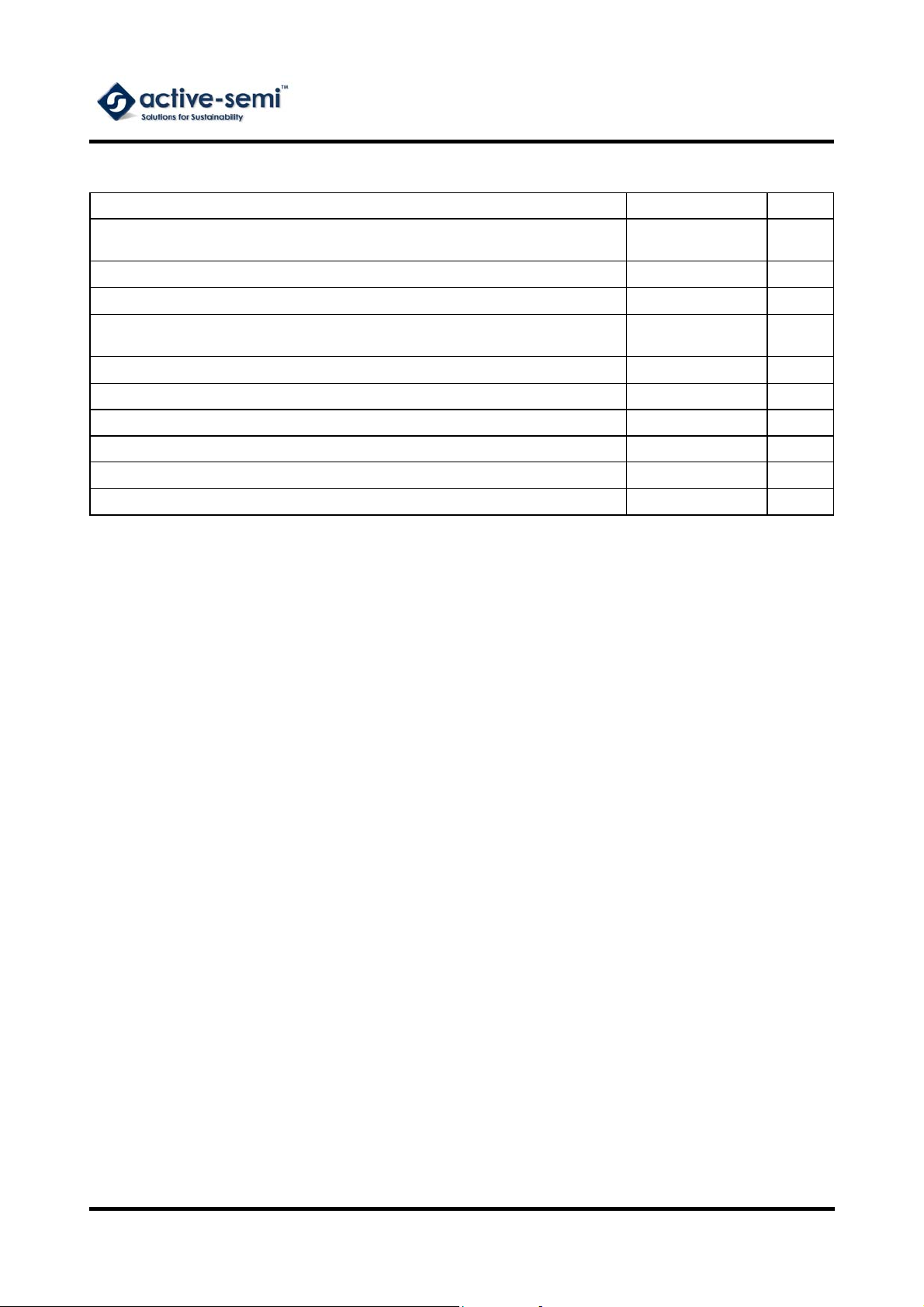

ABSOLUTE MAXIMUM RATINGS

PARAMETER VALUE UNIT

INL1, INL2, INL3 to GA; VP1, SW1, FB1 to GP14; VP2, SW2, OUT2 to GP2; VP3,

SW3, OUT3 to GP3; VP4, SW4, OUT4 to GP14

GP14, GP2, GP3 to GA -0.3 to + 0.3 V

OUT5, OUT6, OUT7, OUT13 TO GA -0.3 to INL1 + 0.3 V

c

ACT8846

Rev 1, 15-May-13

-0.3 to 6 V

OUT8, OUT9, GPIO1, GPIO2, GPIO3, GPIO4, GPIO5, GPIO6, VSELR2, nPBIN,

nRSTO, nIRQ, nPBSTAT, PWREN, PWRHLD, REFBP, SCL, SDA to GA

OUT10, OUT11, OUT12 to GA -0.3 to INL3 + 0.3 V

Junction to Ambient Thermal Resistance 21 °C/W

Operating Ambient Temperature Range -40 to 85 °C

Operating Junction Temperature -40 to 125 °C

Storage Temperature -55 to 150 °C

Lead Temperature (Soldering, 10 sec) 300 °C

c: Do not exceed these limits to prevent damage to the device. Exposure to absolute maximum rating conditions for long periods may

affect device reliability.

-0.3 to INL2 + 0.3 V

Innovative PowerTM - 7 - www.active-semi.com

Active-Semi Proprietary―For Authorized Recipients and Customers

ActivePMU

I2CTM is a trademark of NXP.

TM

is a trademark of Active-Semi.

Copyright © 2013 Active-Semi, Inc.

ACT8846

Rev 1, 15-May-13

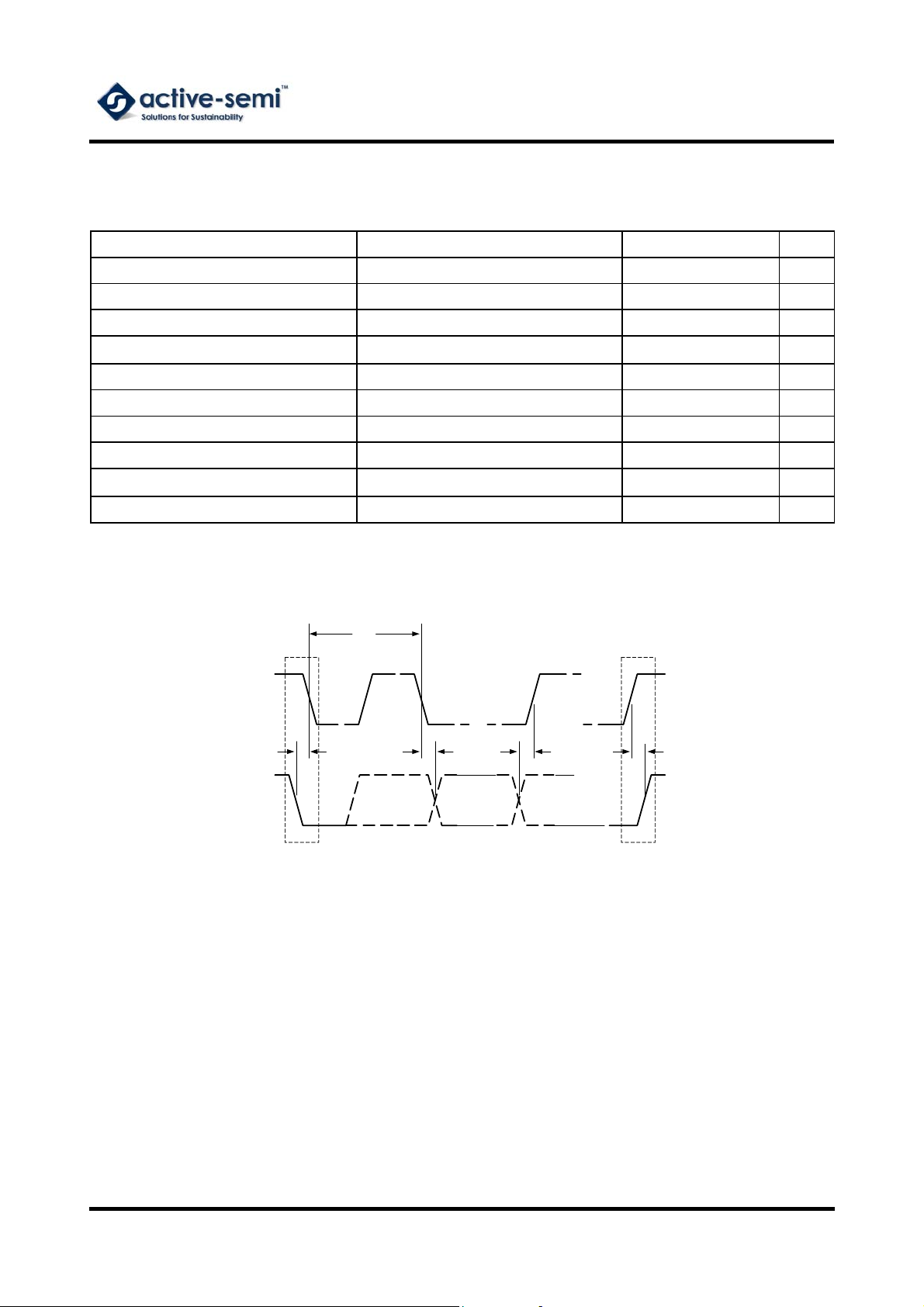

I2C INTERFACE ELECTRICAL CHARACTERISTICS

(V

= 3.6V, TA = 25°C, unless otherwise specified.)

INL2

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

SCL, SDA Input Low V

SCL, SDA Input High V

SDA Leakage Current 1 µA

= 3.1V to 5.5V, TA = -40ºC to 85ºC 0.35 V

INL2

= 3.1V to 5.5V, TA = -40ºC to 85ºC 1.55 V

INL2

SCL Leakage Current

SDA Output Low I

SCL Clock Period, t

SDA Data Setup Time, t

SDA Data Hold Time, t

1.5 µs

SCL

100 ns

SU

300 ns

HD

= 5mA 0.35 V

OL

1 µA

Start Setup Time, tST For Start Condition 100 ns

Stop Setup Time, t

For Stop Condition 100 ns

SP

Figure 1:

2

I

C Compatible Serial Bus Timing

t

SCL

SCL

t

ST

t

HD

t

SU

t

SP

SDA

Start

condition

Innovative PowerTM - 8 - www.active-semi.com

Active-Semi Proprietary―For Authorized Recipients and Customers

ActivePMU

I2CTM is a trademark of NXP.

TM

is a trademark of Active-Semi.

Stop

condition

Copyright © 2013 Active-Semi, Inc.

ACT8846

Rev 1, 15-May-13

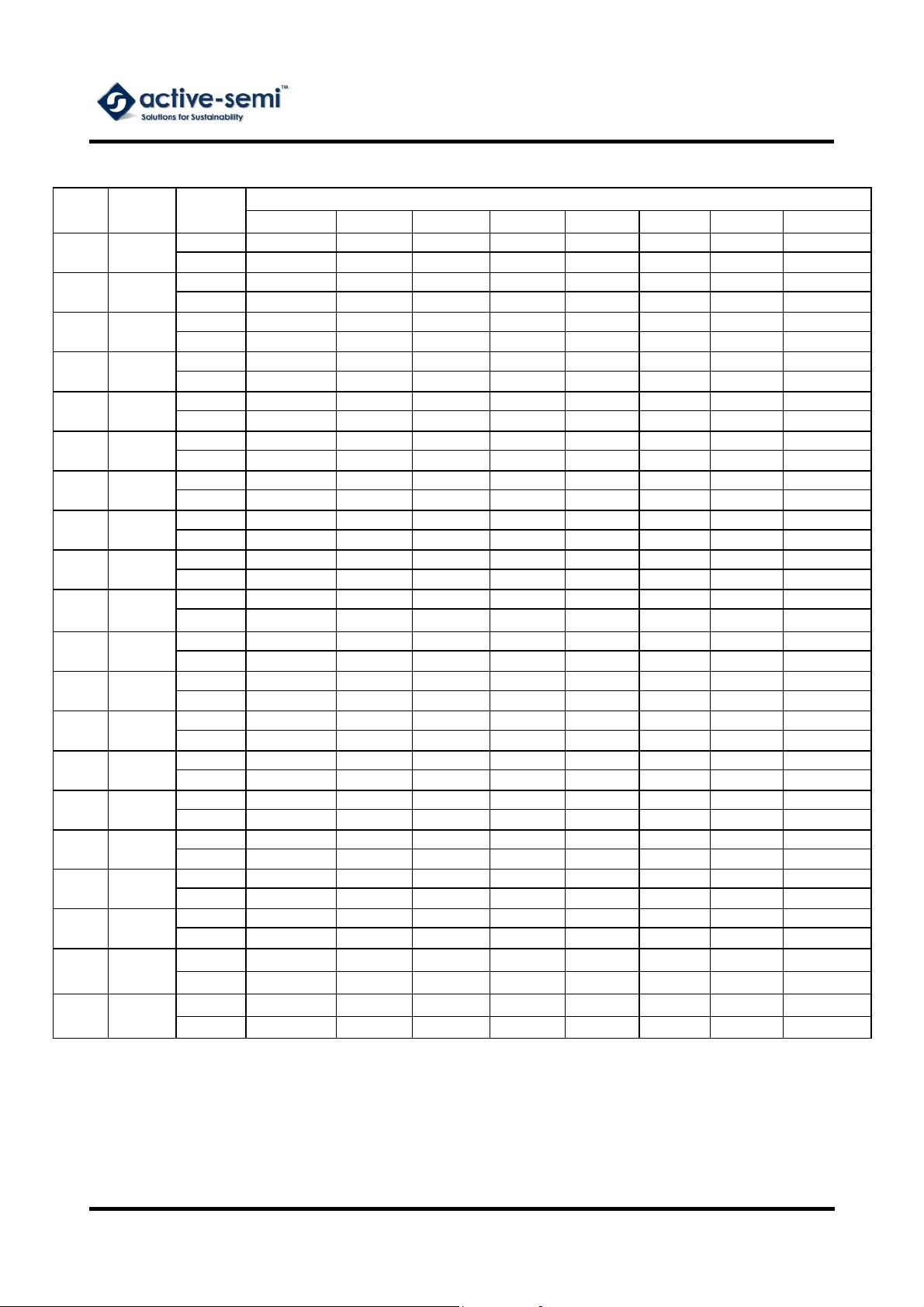

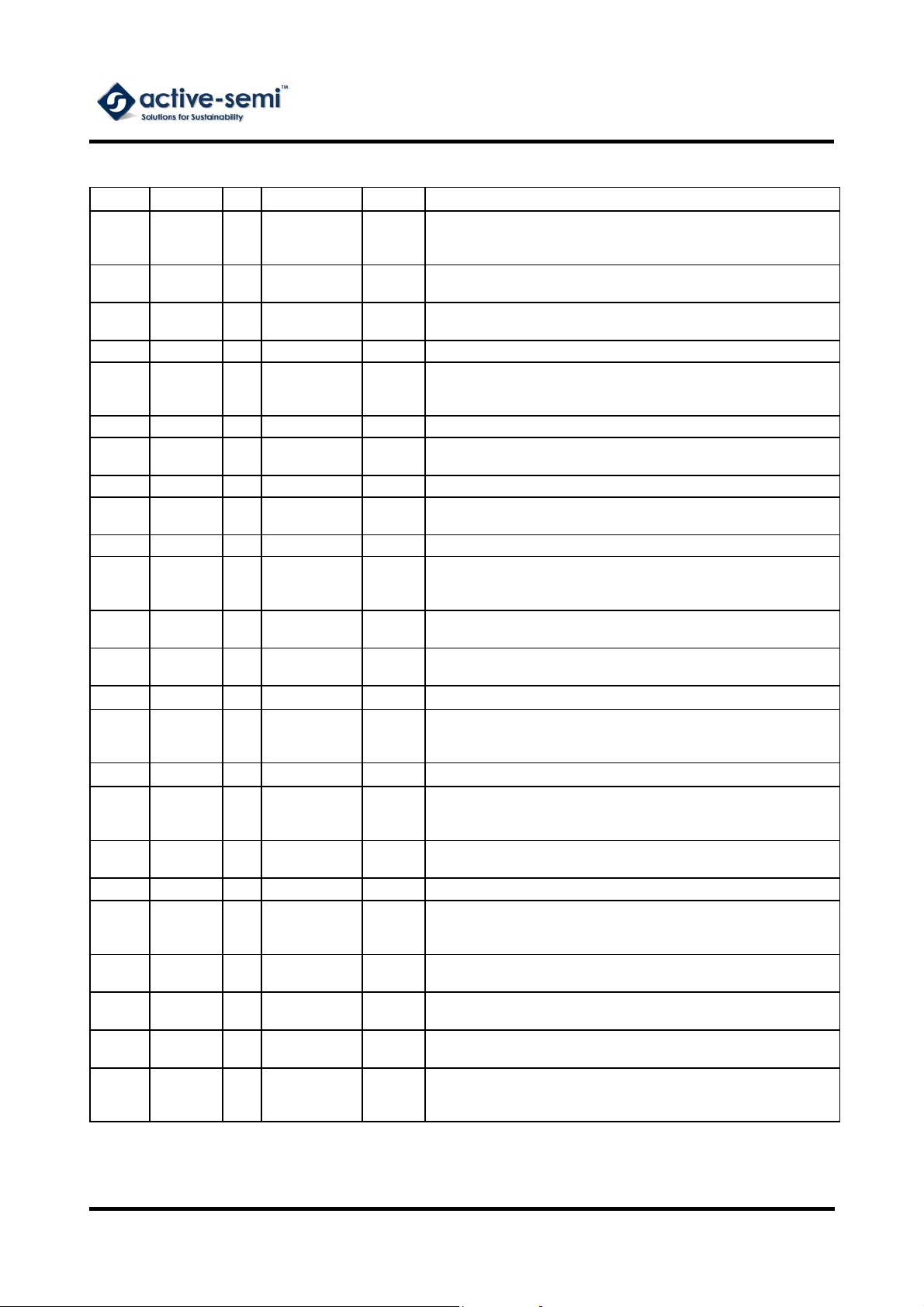

GLOBAL REGISTER MAP

BLOCK ADDRESS

SYS 0x00

SYS 0x01

REG1 0x12

REG2 0x20

REG2 0x21

REG2 0x22

REG3 0x30

REG3 0x31

REG3 0x32

REG4 0x40

REG4 0x41

REG4 0x42

REG5 0x50

REG5 0x51

REG6 0x58

REG6 0x59

REG7 0x60

REG7 0x61

REG8 0x68

REG8 0x69

NAME nBATLEVMSK nBATSTAT VBATDAT Reserved BATLEV[3] BATLEV[2] BATLEV[1] BATLEV[0]

DEFAULTc

NAME nTMSK TSTAT Reserved Reserved Reserved Reserved Reserved Reserved

DEFAULTc

NAME ON Reserved Reserved Reserved Reserved PHASE nFLTMSK OK

DEFAULTc

NAME Reserved Reserved VSET0[5] VSET0[4] VSET0[3] VSET0[2] VSET0[1] VSET0[0]

DEFAULTc

NAME Reserved Reserved VSET1[5] VSET1[4] VSET1[3] VSET1[2] VSET1[1] VSET1[0]

DEFAULTc

NAME ON Reserved Reserved Reserved Reserved PHASE nFLTMSK OK

DEFAULTc

NAME Reserved Reserved VSET0[5] VSET0[4] VSET0[3] VSET0[2] VSET0[1] VSET0[0]

DEFAULTc

NAME Reserved Reserved VSET1[5] VSET1[4] VSET1[3] VSET1[2] VSET1[1] VSET1[0]

DEFAULTc

NAME ON Reserved Reserved Reserved Reserved PHASE nFLTMSK OK

DEFAULTc

NAME Reserved Reserved VSET0[5] VSET0[4] VSET0[3] VSET0[2] VSET0[1] VSET0[0]

DEFAULTc

NAME Reserved Reserved VSET1[5] VSET1[4] VSET1[3] VSET1[2] VSET1[1] VSET1[0]

DEFAULTc

NAME ON Reserved Reserved Reserved Reserved PHASE nFLTMSK OK

DEFAULTc

NAME Reserved Reserved VSET[5] VSET[4] VSET[3] VSET[2] VSET[1] VSET[0]

DEFAULTc

NAME ON Reserved Reserved Reserved Reserved DIS nFLTMSK OK

DEFAULTc

NAME Reserved Reserved VSET[5] VSET[4] VSET[3] VSET[2] VSET[1] VSET[0]

DEFAULTc

NAME ON Reserved Reserved Reserved Reserved DIS nFLTMSK OK

DEFAULTc

NAME Reserved Reserved VSET[5] VSET[4] VSET[3] VSET[2] VSET[1] VSET[0]

DEFAULTc

NAME ON Reserved Reserved Reserved Reserved DIS nFLTMSK OK

DEFAULTc

NAME Reserved Reserved VSET[5] VSET[4] VSET[3] VSET[2] VSET[1] VSET[0]

DEFAULTc

NAME ON Reserved Reserved Reserved Reserved DIS nFLTMSK OK

DEFAULTc

D7 D6 D5 D4 D3 D2 D1 D0

BITS

0 R R R 0 1 0 0

0 R 0 0 0 0 0 0

1 1 0 0 1 0 0 R

0 0 0 1 0 0 0 0

0 0 0 1 0 0 0 0

1 1 0 0 1 0 0 R

0 0 0 1 0 0 0 0

0 0 0 1 0 0 0 0

1 1 0 1 1 1 0 R

0 0 1 1 0 1 1 0

0 0 1 1 0 1 1 0

1 1 0 0 1 1 0 R

0 1 0 1 0 0 0 0

1 1 0 0 1 1 0 R

0 1 0 1 1 0 0 0

0 1 0 0 1 1 0 R

0 1 1 0 0 1 0 0

0 1 0 0 1 1 0 R

0 1 1 1 1 0 0 1

0 1 0 0 1 1 0 R

c: Default values of ACT8846QM468-T.

Innovative PowerTM - 9 - www.active-semi.com

Active-Semi Proprietary―For Authorized Recipients and Customers

ActivePMU

I2CTM is a trademark of NXP.

TM

is a trademark of Active-Semi.

Copyright © 2013 Active-Semi, Inc.

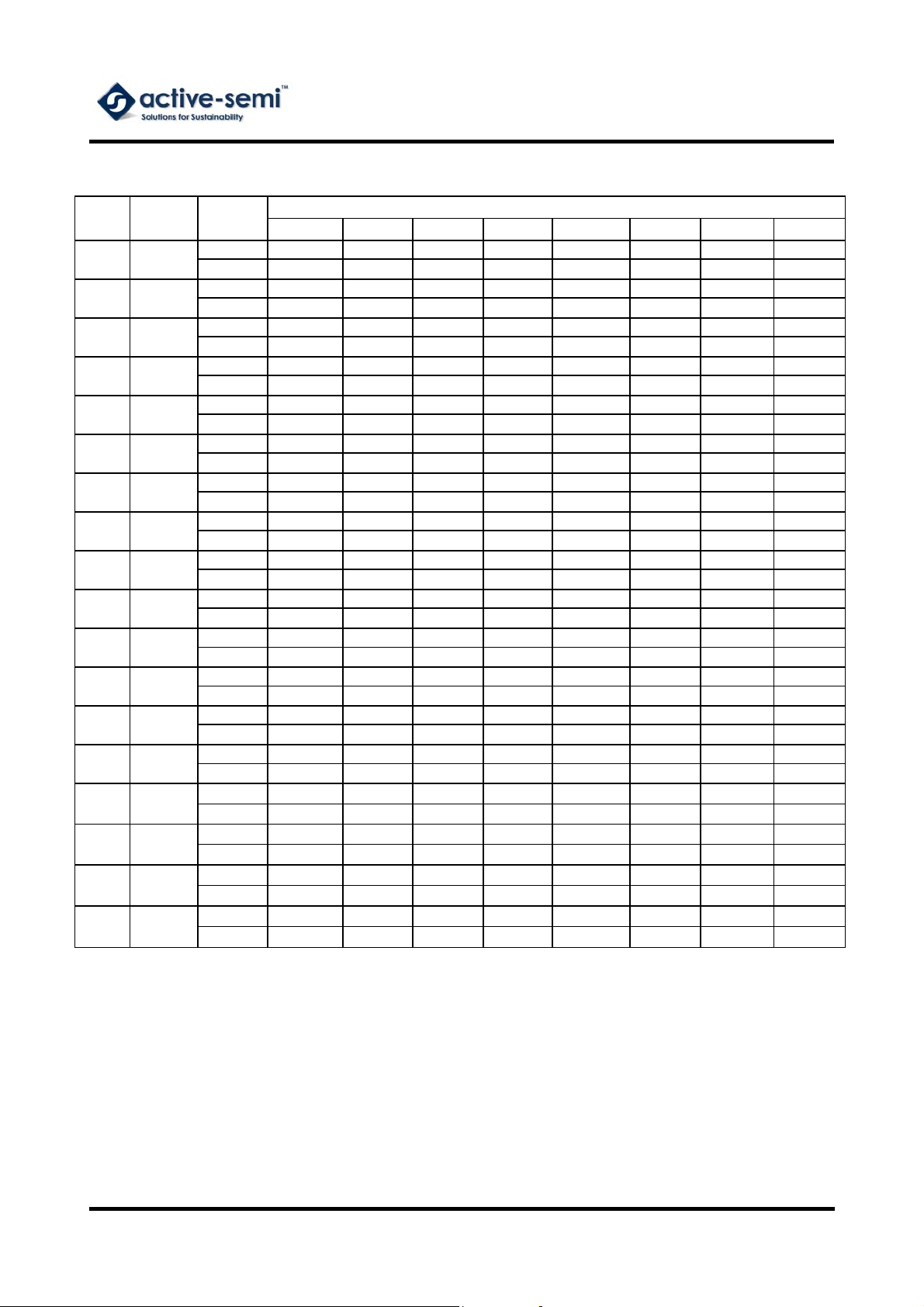

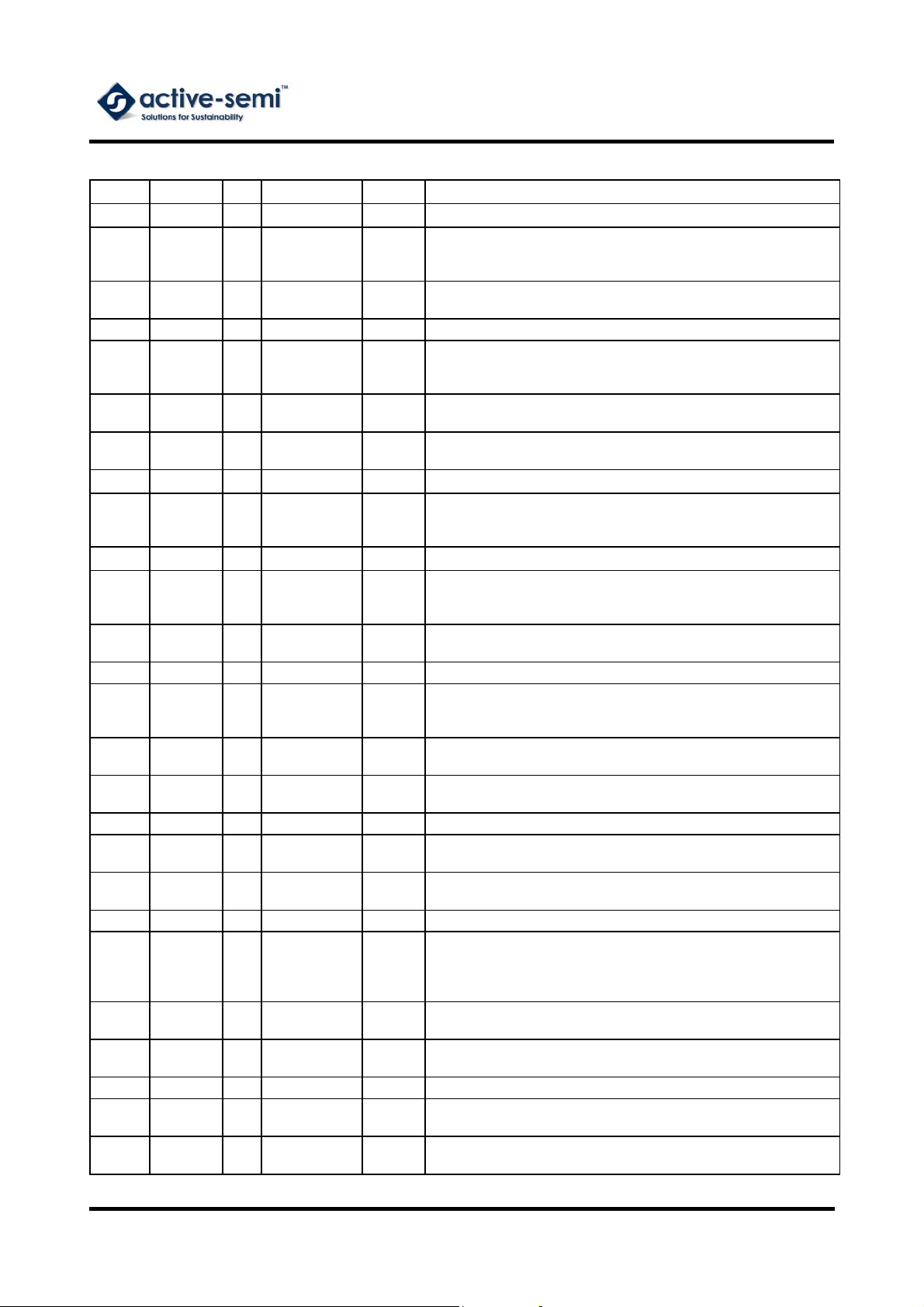

GLOBAL REGISTER MAP CONT’D

BLOCK ADDRESS

REG9 0x70

REG9 0x71

REG10 0x80

REG10 0x81

REG11 0x90

REG11 0x91

REG12 0xA0

REG12 0xA1

REG13 0xB1

PB 0xC0

PB 0xC1

PB 0xC2

PB 0xC3

PB 0xC5

GPIO6 0xE3

GPIO5

0xE4

GPIO3 0xF4

GPIO4 0xF5

NAME Reserved Reserved VSET[5] VSET[4] VSET[3] VSET[2] VSET[1] VSET[0]

DEFAULTc

NAME ON Reserved Reserved Reserved Reserved DIS nFLTMSK OK

DEFAULTc

NAME Reserved Reserved VSET[5] VSET[4] VSET[3] VSET[2] VSET[1] VSET[0]

DEFAULTc

NAME ON Reserved Reserved Reserved Reserved DIS nFLTMSK OK

DEFAULTc

NAME Reserved Reserved VSET[5] VSET[4] VSET[3] VSET[2] VSET[1] VSET[0]

DEFAULTc

NAME ON Reserved Reserved Reserved Reserved DIS nFLTMSK OK

DEFAULTc

NAME Reserved Reserved VSET[5] VSET[4] VSET[3] VSET[2] VSET[1] VSET[0]

DEFAULTc

NAME ON Reserved Reserved Reserved Reserved DIS nFLTMSK OK

DEFAULTc

NAME ON Reserved Reserved Reserved Reserved Reserved Reserved Reserved

DEFAULTc

NAME PBAMSK PBDMSK Reserved Reserved Reserved Reserved WDSREN WDPCEN

DEFAULTc

NAME INTADR [7] INTADR [6] INTADR [5] INTADR [4] INTADR [3] INTADR [2] INTADR [1] INTADR [0]

DEFAULTc

NAME PBASTAT PBDSTAT PBDAT Reserved Reserved Reserved Reserved Reserved

DEFAULTc

NAME Reserved Reserved Reserved OFFSYS OFFSYSCLR Reserved Reserved SIPC

DEFAULTc

NAME Reserved Reserved Reserved Reserved Reserved Reserved PCSTAT SRSTAT

DEFAULTc

NAME PWM6EN FRE6[2] FRE6[1] FRE6[0] DUTY6[3] DUTY6[2] DUTY6[1] DUTY6[0]

DEFAULTc 0 0 0 0 0 0 0 0

NAME PWM5EN FRE5[2] FRE5[1] FRE5[0] DUTY5[3] DUTY5[2] DUTY5[1] DUTY5[0]

DEFAULTc 0 0 0 0 0 0 0 0

NAME PWM3EN FRE3[2] FRE3[1] FRE3[0] DUTY3[3] DUTY3[2] DUTY3[1] DUTY3[0]

DEFAULTc 1 1 0 1 0 1 1 1

NAME PWM4EN FRE4[2] FRE4[1] FRE4[0] DUTY4[3] DUTY4[2] DUTY4[1] DUTY4[0]

DEFAULTc 0 0 0 0 0 0 0 0

D7 D6 D5 D4 D3 D2 D1 D0

0 1 1 1 1 0 0 1

0 1 0 0 1 1 0 R

0 1 1 1 1 0 0 1

0 1 0 0 1 1 0 R

0 1 1 0 0 1 0 0

1 1 0 0 1 1 0 R

0 1 1 1 0 1 0 0

0 1 0 0 1 1 0 R

1 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

R R R R R R R R

R R R R R R R R

0 0 0 0 0 0 0 0

0 0 0 0 0 0 R R

ACT8846

Rev 1, 15-May-13

BITS

c: Default values of ACT8846QM468-T.

Innovative PowerTM - 10 - www.active-semi.com

Active-Semi Proprietary―For Authorized Recipients and Customers

ActivePMU

I2CTM is a trademark of NXP.

TM

is a trademark of Active-Semi.

Copyright © 2013 Active-Semi, Inc.

ACT8846

Rev 1, 15-May-13

REGISTER AND BIT DESCRIPTIONS

BLOCK ADDRESS BIT NAME ACCESS DESCRIPTION

Battery Voltage Level Interrupt Mask. Set this bit to 1 to unmask

SYS 0x00 [7] nBATLEVMSK R/W

SYS 0x00 [6] nBATSTAT R

SYS 0x00 [5] VBATDAT R

SYS 0x00 [4] - R/W Reserved.

SYS 0x00 [3:0] BATLEV R/W

SYS 0x01 [7] nTMSK R/W Thermal Interrupt Mask. Set this bit to 1 to unmask the interrupt.

SYS 0x01 [6] TSTAT R

SYS 0x01 [5:0] - R/W Reserved.

REG1 0x12 [7] ON R/W

REG1 0x12 [6:3] - R Reserved.

REG1 0x12 [2] PHASE R/W

REG1 0x12 [1] nFLTMSK R/W

REG1 0x12 [0] OK R

REG2 0x20 [7:6]

REG2 0x20 [5:0] VSET0 R/W

REG2 0x21 [7:6]

REG2 0x21 [5:0] VSET1 R/W

REG2 0x22 [7] ON R/W

REG2 0x22 [6:3] - R Reserved.

REG2 0x22 [2] PHASE R/W

REG2 0x22 [1] nFLTMSK R/W

REG2 0x22 [0] OK R

-

-

the interrupt. See the Programmable Battery Voltage Monitor

section for more information

Battery Voltage Status. Value is 1 when BATLEV interrupt is

generated, value is 0 otherwise.

Battery Voltage Monitor real time status. Value is 1 when VBAT <

BATLEV, value is 0 otherwise.

Battery Voltage Detect Threshold. Defines the BATLEV voltage

threshold. See the Programmable Battary Voltage Monitor

section for more information.

Thermal Interrupt Status. Value is 1 when a thermal interrupt is

generated, value is 0 otherwise.

Regulator Enable Bit. Set bit to 1 to enable the regulator, clear bit

to 0 to disable the regulator.

Regulator Phase Control. Set bit to 1 for the regulator to operate

180° out of phase with the oscillator, clear bit to 0 for the

regulator to operate in phase with the oscillator.

Regulator Fault Mask Control. Set bit to 1 enable fault-interrupts,

clear bit to 0 to disable fault-interrupts.

Regulator Power-OK Status. Value is 1 when output voltage

exceeds the power-OK threshold, value is 0 otherwise.

R Reserved.

Primary Output Voltage Selection. Valid when VSEL is driven low.

See the Output Voltage Programming section for more

information

R Reserved.

Secondary Output Voltage Selection. Valid when VSEL is driven

high. See the Output Voltage Programming section for more

information.

Regulator Enable Bit. Set bit to 1 to enable the regulator, clear bit

to 0 to disable the regulator.

Regulator Phase Control. Set bit to 1 for the regulator to operate

180° out of phase with the oscillator, clear bit to 0 for the

regulator to operate in phase with the oscillator.

Regulator Fault Mask Control. Set bit to 1 enable fault-interrupts,

clear bit to 0 to disable fault-interrupts.

Regulator Power-OK Status. Value is 1 when output voltage

exceeds the power-OK threshold, value is 0 otherwise.

REG3 0x30 [7:6]

REG3 0x30 [5:0] VSET0 R/W

Innovative PowerTM - 11 - www.active-semi.com

Active-Semi Proprietary―For Authorized Recipients and Customers

ActivePMU

I2CTM is a trademark of NXP.

TM

is a trademark of Active-Semi.

-

R Reserved.

Primary Output Voltage Selection. Valid when VSEL is driven low.

See the Output Voltage Programming section for more

information

Copyright © 2013 Active-Semi, Inc.

ACT8846

Rev 1, 15-May-13

REGISTER AND BIT DESCRIPTIONS CONT’D

BLOCK ADDRESS BIT NAME ACCESS DESCRIPTION

REG3 0x31 [7:6]

REG3 0x31 [5:0] VSET1 R/W

REG3 0x32 [7] ON R/W

REG3 0x32 [6:3] - R Reserved.

REG3 0x32 [2] PHASE R/W

REG3 0x32 [1] nFLTMSK R/W

REG3 0x32 [0] OK R

REG4 0x40 [7:6]

REG4 0x40 [5:0] VSET0 R/W

REG4 0x41 [7:6]

REG4 0x41 [5:0] VSET1 R/W

REG4 0x42 [7] ON R/W

REG4 0x42 [6:3] - R Reserved.

REG4 0x42 [2] PHASE R/W

REG4 0x42 [1] nFLTMSK R/W

REG4 0x42 [0] OK R

REG5 0x50 [7:6] - R Reserved.

REG5 0x50 [5:0] VSET R/W

REG5 0x51 [7] ON R/W

REG5 0x51 [6:3] - R Reserved.

REG5 0x51 [2] DIS R/W

REG5 0x51 [1] nFLTMSK R/W

REG5 0x51 [0] OK R

REG6 0x58 [7:6] - R Reserved.

REG6 0x58 [5:0] VSET R/W

REG6 0x59 [7] ON R/W

-

-

-

R Reserved.

R Reserved.

R Reserved.

Secondary Output Voltage Selection. Valid when VSEL is driven

high. See the Output Voltage Programming section for more

information.

Regulator Enable Bit. Set bit to 1 to enable the regulator, clear bit

to 0 to disable the regulator.

Regulator Phase Control. Set bit to 1 for the regulator to operate

180° out of phase with the oscillator, clear bit to 0 for the

regulator to operate in phase with the oscillator.

Regulator Fault Mask Control. Set bit to 1 enable fault-interrupts,

clear bit to 0 to disable fault-interrupts.

Regulator Power-OK Status. Value is 1 when output voltage

exceeds the power-OK threshold, value is 0 otherwise.

Primary Output Voltage Selection. Valid when VSEL is driven low.

See the Output Voltage Programming section for more

information

Secondary Output Voltage Selection. Valid when VSEL is driven

high. See the Output Voltage Programming section for more

information.

Regulator Enable Bit. Set bit to 1 to enable the regulator, clear bit

to 0 to disable the regulator.

Regulator Phase Control. Set bit to 1 for the regulator to operate

180° out of phase with the oscillator, clear bit to 0 for the

regulator to operate in phase with the oscillator.

Regulator Fault Mask Control. Set bit to 1 enable fault-interrupts,

clear bit to 0 to disable fault-interrupts.

Regulator Power-OK Status. Value is 1 when output voltage

exceeds the power-OK threshold, value is 0 otherwise.

Output Voltage Selection. See the Output Voltage Programming

section for more information.

Regulator Enable Bit. Set bit to 1 to enable the regulator, clear bit

to 0 to disable the regulator.

Output Discharge Control. When activated, LDO output is

discharged to GA through 1.5k resistor when in shutdown. Set

bit to 1 to enable output voltage discharge in shutdown, clear bit

to 0 to disable this function.

Regulator Fault Mask Control. Set bit to 1 enable fault-interrupts,

clear bit to 0 to disable fault-interrupts.

Regulator Power-OK Status. Value is 1 when output voltage

exceeds the power-OK threshold, value is 0 otherwise.

Output Voltage Selection. See the Output Voltage Programming

section for more information.

Regulator Enable Bit. Set bit to 1 to enable the regulator, clear bit

to 0 to disable the regulator.

Innovative PowerTM - 12 - www.active-semi.com

Active-Semi Proprietary―For Authorized Recipients and Customers

ActivePMU

I2CTM is a trademark of NXP.

TM

is a trademark of Active-Semi.

Copyright © 2013 Active-Semi, Inc.

Loading...

Loading...