ACT ACT-5231PC-200F22M, ACT-5231PC-150F22T, ACT-5231PC Datasheet

ACT5231

32-Bit Superscaler Micropr ocessor

Features

Full militarized QED RM5231 microprocessor

■

Pinout compatibl e wit h popular RM5230 with split power sup

■

plies (2.5V and 3.3V)

Dual Issue superscalar microprocessor - can issue one

■

integer and one floating-point instruction per cyc le

133, 150 and 200 MHz operating frequencies – Consult Factory for

●

lates t speeds

325 Dhrystone2.1 MIPS

●

SPECInt95 5.0, SPECfp95 5.25

●

System interface optimized for embedded applications

■

32-bit system interface lowers total system cost

●

High performance write protocols maximize uncached write

●

bandwidth with 600 MB per second peak throughput

Operates at processor clock divisors 2, 2.5, 3, 3.5,4, 4.5, 5, 6, 7, 8, 9

●

IEEE 1149.1 JTA G boundary scan

●

Integrated on-c hip caches

■

32KB instruction and 32KB data - 2 way set associative and per

●

set locking

Virtually indexed, physically tagged

●

Write-back and write-through on per page basis

●

Pipeline restart on first double for data cache misses

●

Integrated memory management unit

■

Fully associative joint TLB (shared by I and D translations)

●

48 dual entries map 96 pa ges

●

Variable page size (4KB to 16MB in 4x increments)

●

High-performance floating point unit

■

532 MFLOPS single-precision performance

●

Single cycle repeat rate for common single precision opera-tions

●

and some double precision operations

Two cycle repeat rate for double precision multiply and double

●

precision combined multiply-add operations

Single cycle repeat rate for single precision combined multiply-

●

add operation

MIPS IV instructi on set

■

Floating point multiply-add instruction increases performance in

●

signal processing and graphics applications

Conditional moves to reduce branch frequency

●

Index address modes (register + register)

●

Embedded application enhancements

■

Specialized DSP integer Multiply-Accumulate instruction and 3

●

operand multiply instruction

I and D cache locking by set

●

Optional dedicated exception vector for interrupts

●

Fully static CMOS design with power down logic

■

Standby reduced power mode with WAIT instruction

●

2.7 W typical power @ 200MHz

●

2.5V core with 3.3V IO’s

●

■

128-pin Power Quad-4 package (F22),

Consult Fac tory for

package conf iguration

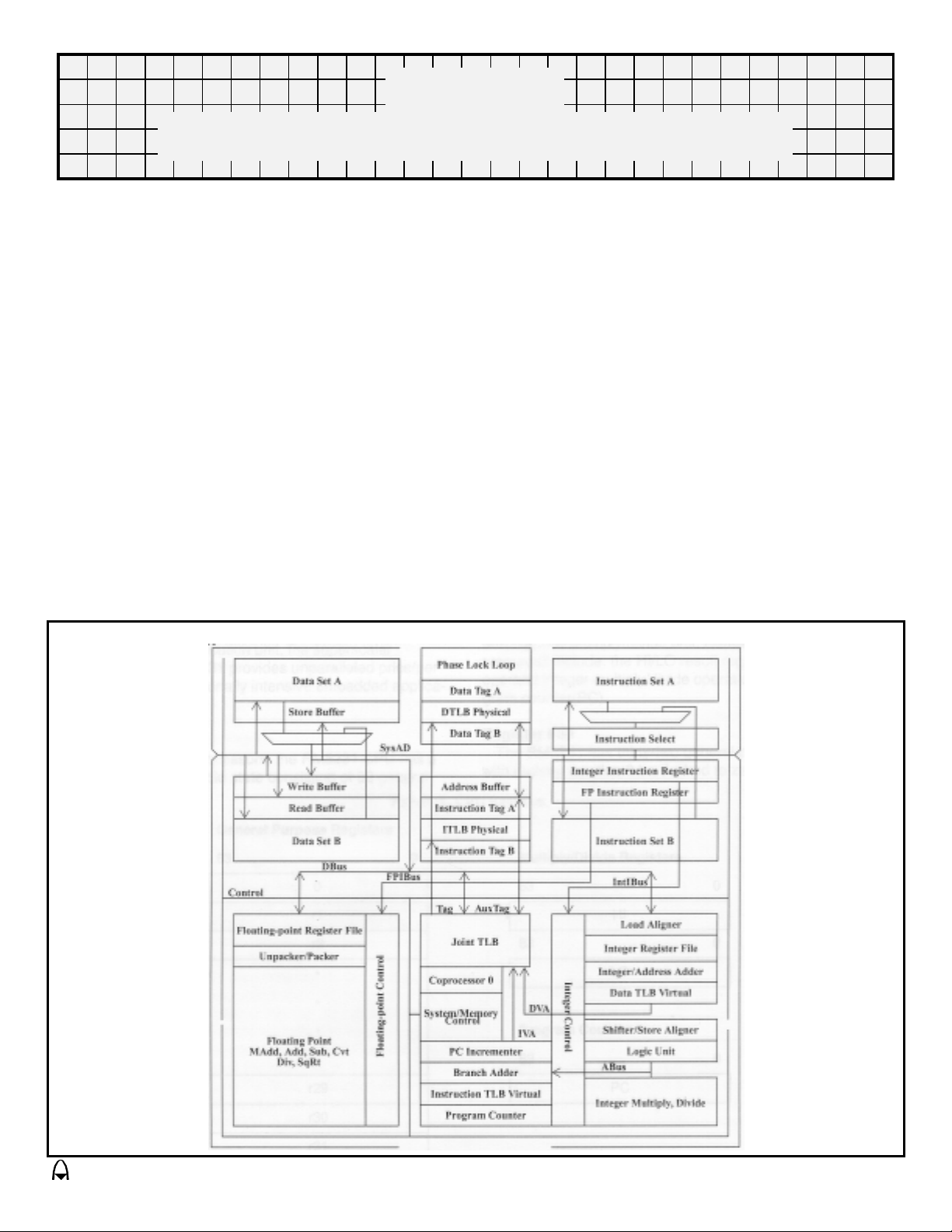

Block Diagram

eroflex Circuit

Technology

Preliminary

– RISC TurboEngines For The Future © SCD5231 REV 1 12/22/98

DESCRIPTION

Integer Unit

The AC T5231 is a hig hly inte grated supers calar

micropro cessor that imp lements a sup erset of the

MIPS IV I nstruc tion Se t Archit ecture(I SA). It has a

high performance 64-bit integer unit, a high

throughpu t, ful ly pip elin ed 64 -bit f loat ing po int un it,

an operating system friendly memory management

unit with a 48-entry fully associative TLB, a 32KB

2-way set associative instruction cache, a 32KB

2-way set a ssociative da ta cache, and a n efficient

32-bit system interface. The ACT5231 can issue

both an integer and a floating point instruction in the

same cycle.

The ACT5231 is ideally suited for high-end

embedded control applications such as

internetworking, high performance image

manipulation, high speed printing, and 3-D

visualization.

HARDWARE OVERVIEW

The ACT5231 offers a high-level of integration

targeted at high-performance embedded

applications. The key elements of the ACT5231 are

briefly desc ribed below .

Superscalar Dispatch

The ACT5231 has an efficient asymmetric

superscalar dispatch unit which allows it to issue an

integer ins t ruction and a floa tin g-point com putatio n

instruction simultaneously. With respect to

superscal ar issue, i nteger ins tructions in clude alu ,

branch, load/store, and floating-point load/ store,

while floating-point computation instructions

include floating-point add, subtract, combined

multiply-a dd, conver ts, etc. In c ombinatio n with its

high throughput fully pipelined floating-point

execution unit, the superscalar capability of the

ACT523 1 pro vide s un pa rallele d p rice /perfo rman ce

in computationally intensive embedded

applications.

The ACT5231 implements the MIPS IV

Instruction Set Architecture, and is ther efore fully

upward compatible with applications that run on

processors implementing the earlier generation

MIPS I-III instruction sets. Additionally, the

ACT5231 includes two implementation specific

instruct ions no t found in t he base line MIPS IV ISA

but tha t are u seful in t he em bedded marke t place.

Described in det ail in the QE D R M 5231 dat as heet,

these instructions are integer multipl y-accumulate

and 3-operand integer multiply.

The ACT5231 integer unit includes thirty-two

general purpose 64-bit registers, a load/store

architecture with single cycle ALU operations (add,

sub, logical, shift) and an autonomous multiply/

divide unit. Additional register resources include:

the HI/LO result registers for the two-operand

integer m ultiply/divide operat ions, and the program

counte r(PC).

Register File

The ACT5231 has thirty-two general purpose

registers with register location 0 hard wired to zero.

These registersi ch allo are used for s calar in teger

operations and address calculation. The register

file has two read ports and one write port and is fully

bypassed to minimize operation latency in the

pipeline.

ALU

The ACT5231 ALU consists of the integer adder/

subtractor, the logic unit, and the shifter. The adder

performs address calculations in addition to

arithmetic operations, the logic unit performs all

logical and zero shift data moves, and the shifter

performs shifts and store alignment operations.

Each of these units is optimized to perf orm all ti o ns

in a single processo r c y cl e.

CPU Registers

Like all MIPS ISA processors, the ACT5231 CPU

has a simple, clean user visible state consisting of

32 gene ral purpo se regi sters, two sp ecial pu rpose

registers for integer multiplication and division, a

program c ounter, and no condition code bits .

For additional Detail Information regarding the

operation of the Quantum Effect Design (QED)

RISCMark RM 5231, 32-Bit Superscalar

Microp roc essor see th e lat est QED da ta s heet.

Pipeline

For integ er operations, loa ds, stores, and oth er

non-floating-point operations, the ACT5231 uses

the simple 5-stage pipeline also found in the

ACT52xx family, R4600, R4700, and R5000. In

addition to this standard pipeline, the ACT5231

uses an extended seven stage pipeline for

floating-point operations. The ACT5231 does

virtual to ph ysical t ranslatio n in par allel with c ache

access.

Aeroflex Circuit Technology SCD5231 REV 1 12/22/98 Plainview NY (516) 694-6700

2

Loading...

Loading...