Page 1

ACE User Guide

For ACE Version 5.0

UG001 v5.0 - 5th December 2012

http://www.achronix.com

Page 2

Copyright Info

Copyright © 2006 - 2012 Achronix Semiconductor Corporation; certain portions of this guide are Copyright

© 2000, 2006 IBM Corporation and others. All rights reserved. Achronix and Speedster are trademarks of

Achronix Semiconductor Corporation. All other trademarks are the property of their prospective owners.

All specifications subject to change without notice.

NOTICE of DISCLAIMER: The information given in this document is believed to be accurate and reliable.

However, Achronix Semiconductor Corporation does not give any representations or warranties as to the

completeness or accuracy of such information and shall have no liability for the use of the information

contained herein. Achronix Semiconductor Corporation reserves the right to make changes to this document

and the information contained herein at any time and without notice. All Achronix trademarks, registered

trademarks, disclaimers and patents are listed at http://www.achronix.com/legal.

Achronix Semiconductor Corporation

2953 Bunker Hill Lane, Suite 101 Phone : 877.GHZ.FPGA (877.449.3742)

Santa Clara, CA, 95054 Fax : 408.286.3645

USA E-mail : info@achronix.com

i http://www.achronix.com UG001 Rev. 5.0 - 5th December 2012

Page 3

CONTENTS CONTENTS

Contents

1 Preface 1

1.1 About This Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.2 Related Documents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.3 Conventions Used in this Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2 Getting Started 2

2.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2.2 ACE Quickstart Tutorial . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3 Concepts 4

3.1 Workbench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.2 Perspectives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.3 Editors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.3.1 Text Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.3.2 HTML Report Browser . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3.3.3 Advanced PLL Configuration Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.3.4 Basic PLL Configuration Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.3.5 BRAM Configuration Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.3.6 DDR3 Configuration Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.3.7 Ethernet Configuration Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.3.8 FIFO Configuration Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.3.9 Interlaken Configuration Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.3.10 LRAM Configuration Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

3.3.11 LRAM FIFO Configuration Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

3.3.12 PCI Express Configuration Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

3.3.13 ROM Configuration Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

3.3.14 SerDes Configuration Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

3.3.15 VCD Waveform Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

3.4 Views . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

3.4.1 Fast views . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

3.4.2 Projects View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

3.4.3 Flow View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

3.4.4 Options View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

3.4.5 Multiprocess View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

3.4.6 Tcl Console View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

3.4.7 Search View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

3.4.8 Selection View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

UG001 Rev. 5.0 - 5th December 2012 http://www.achronix.com ii

Page 4

CONTENTS CONTENTS

3.4.9 Critical Paths View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

3.4.10 Critical Path Diagram View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

3.4.11 Package View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

3.4.12 IO Assignment View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

3.4.13 Clock Regions View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

3.4.14 Netlist Browser View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

3.4.15 Placement Regions View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

3.4.16 Outline View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

3.4.17 IP Libraries View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

3.4.18 IP Diagram View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

3.4.19 IP Problems View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

3.4.20 Download View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

3.5 Dialogs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

3.5.1 Create Project Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

3.5.2 Load Project Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

3.5.3 Create Implementation Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

3.5.4 Restore Implementation Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

3.5.5 Save Implementation Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180

3.5.6 Create a New Constraints File Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

3.5.7 Create a New Text File Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

3.5.8 Add Source Files Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

3.5.9 Save Placement Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

3.5.10 Save Script File Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

3.5.11 New IP Configuration Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

3.5.12 Generate IP Design Files Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

3.5.13 Configure Selected IOs Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

3.5.14 Save Changed Properties Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

3.5.15 Generate a Pin Assignment Report Dialog . . . . . . . . . . . . . . . . . . . . . . . . . 194

3.5.16 Configure Table Columns Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

3.5.17 Add Signals to Waveform Viewer Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . 196

3.5.18 Assign Bussed Signal Names Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

3.5.19 Search Filter Builder Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

3.5.20 Create Placement Region Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

3.5.21 Save Placement Regions Dialog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

3.6 Toolbars . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

3.7 Preferences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

3.7.1 Critical Path Diagram View Preference Page . . . . . . . . . . . . . . . . . . . . . . . . 206

3.7.2 Floorplanner View Colors Preference Page . . . . . . . . . . . . . . . . . . . . . . . . . 208

3.7.3 Floorplanner View Optimizations Preference Page . . . . . . . . . . . . . . . . . . . . . 209

3.7.4 IP Diagram Preference Page . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

iii http://www.achronix.com UG001 Rev. 5.0 - 5th December 2012

Page 5

CONTENTS CONTENTS

3.7.5 Multiprocess View Preference Page . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

3.7.6 Other Colors and Fonts Preference Page . . . . . . . . . . . . . . . . . . . . . . . . . . . 217

3.7.7 Package View Preference Page . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

3.7.8 Placement Regions Preference Page . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

3.7.9 Project Management Preference Page . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

3.7.10 Tcl Console View Preference Page . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

3.7.11 Text Editors Preference Page . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

3.8 Projects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

3.8.1 Implementations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

3.8.2 Project File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

3.8.3 Source Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

3.8.4 IP Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

3.8.5 Output Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

3.8.6 Log Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

3.8.7 Active Project and Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

3.9 Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

3.9.1 Flow Steps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

3.9.2 Flow Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

3.10 Reports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

3.10.1 Clock Report . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

3.10.2 Utilization Report . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

3.10.3 Pin Assignment Report . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

3.10.4 Timing Report . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 232

3.10.5 I/O Timing Report . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

3.10.6 Routing Report . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

3.10.7 Power Dissipation Report . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

3.10.8 Multiprocess Summary Report . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

3.11 Advanced Concepts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

3.11.1 Clock Regions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

4 Tasks 236

4.1 Running ACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

4.2 Working With Perspectives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

4.2.1 Switching Between Perspectives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

4.2.2 Opening Perspectives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

4.2.3 Resetting Perspectives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

4.3 Working with Views and Editors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

4.3.1 Opening Views . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

4.3.2 Moving and Docking Views . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

4.3.3 Rearranging Tabbed Views . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

4.3.4 Creating Fast Views . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

UG001 Rev. 5.0 - 5th December 2012 http://www.achronix.com iv

Page 6

CONTENTS CONTENTS

4.3.5 Tiling Editors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

4.3.6 Maximizing a View or Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

4.4 Working with Projects and Implementations . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

4.4.1 Creating Projects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

4.4.2 Loading Projects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

4.4.3 Removing Projects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

4.4.4 Saving Projects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

4.4.5 Opening Project Files in an Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

4.4.6 Adding Source Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

4.4.7 Removing Source Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

4.4.8 Opening Source Files in an Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

4.4.9 Creating Implementations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

4.4.10 Saving Implementations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244

4.4.11 Restoring Implementations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244

4.4.12 Copying Implementations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

4.4.13 Setting the Active Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

4.4.14 Removing Implementations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

4.4.15 Configuring Implementation Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

4.4.16 Opening Output Files in an Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

4.4.17 Opening Report Files in an Editor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 246

4.5 Running the Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

4.5.1 Running the Entire Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

4.5.2 Running a Sub-Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

4.5.3 Prepare Steps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

4.5.4 Place and Route Steps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248

4.5.5 Design Completion Steps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248

4.5.6 FPGA Programming Steps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 249

4.5.7 Running Multiple Flows in Parallel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 249

4.6 Using the Tcl Console . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255

4.6.1 Sending Commands from GUI Actions . . . . . . . . . . . . . . . . . . . . . . . . . . . 255

4.6.2 Sending Commands from the Console . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255

4.6.3 Command Highlighting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255

4.6.4 Command Auto-Completion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255

4.6.5 Command Help . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

4.6.6 Text Limit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

4.6.7 Clearing the Console . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

4.6.8 Viewing the ACE Log File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

4.6.9 Object Type Prefixes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

4.7 Creating an IP Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 259

4.7.1 Creating and Naming an IP Configuration . . . . . . . . . . . . . . . . . . . . . . . . . 259

v http://www.achronix.com UG001 Rev. 5.0 - 5th December 2012

Page 7

CONTENTS CONTENTS

4.7.2 Setting the IP Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260

4.7.3 Generating the IP Design Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260

4.7.4 Adding Configuration Files to a Project . . . . . . . . . . . . . . . . . . . . . . . . . . . 260

4.8 Viewing the Floorplanner . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

4.8.1 Opening and Closing the Fly-Out Palette . . . . . . . . . . . . . . . . . . . . . . . . . . 261

4.8.2 Zooming In and Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

4.8.3 Panning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

4.8.4 Selecting Objects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

4.8.5 Deselecting Objects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

4.8.6 Toggling Mouse Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 263

4.8.7 Filtering the View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 263

4.8.8 Getting Object Tooltips . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 263

4.8.9 Viewing Object Labels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 264

4.9 Viewing the Package Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 265

4.9.1 Opening and Closing the Fly-Out Palette . . . . . . . . . . . . . . . . . . . . . . . . . . 265

4.9.2 Zooming In and Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 265

4.9.3 Panning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 266

4.9.4 Selecting Objects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 266

4.9.5 Deselecting Objects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 266

4.9.6 Toggling Mouse Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

4.9.7 Filtering the View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

4.9.8 Getting Object Tooltips . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

4.9.9 Viewing Object Labels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

4.10 Pre-Placing a Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 269

4.10.1 Placing an Object . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 269

4.10.2 Changing Between Fixed and Soft Placement . . . . . . . . . . . . . . . . . . . . . . . . 270

4.10.3 Removing Placement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

4.10.4 Saving Pre-Placement Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

4.10.5 Using Pre-Placement in the Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

4.11 Analyzing Critical Paths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 272

4.11.1 Generating Timing Reports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 272

4.11.2 Highlighting Critical Paths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 272

4.11.3 Selecting Critical Path Objects . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

4.11.4 Zooming to Critical Paths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274

4.11.5 Printing Critical Path Details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274

4.11.6 Using Critical Path Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274

4.11.7 Viewing Critical Paths in the Schematic Viewer . . . . . . . . . . . . . . . . . . . . . . 281

4.12 Managing I/Os . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

4.13 Running the SnapShot Debugger . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

4.13.1 General SnapShot Description and Architecture . . . . . . . . . . . . . . . . . . . . . . 284

UG001 Rev. 5.0 - 5th December 2012 http://www.achronix.com vi

Page 8

CONTENTS CONTENTS

4.13.2 Using the SnapShot Macro . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 285

4.13.3 Setting Up the Bitporter Pod Connection . . . . . . . . . . . . . . . . . . . . . . . . . . 289

4.13.4 Setting Up the Scan Chain . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

4.13.5 Entering a Trigger Pattern . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

4.13.6 Configuring Test Stimulus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 291

4.13.7 Setting Triggering Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 292

4.13.8 Configuring the Samples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 292

4.13.9 Collecting Samples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 292

4.13.10 Saving/Loading SnapShot Configurations . . . . . . . . . . . . . . . . . . . . . . . . . 293

4.13.11 Batch Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 293

4.14 Playing a STAPL File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

4.14.1 Selecting a STAPL File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

4.14.2 Selecting Actions and Procedures to be Played . . . . . . . . . . . . . . . . . . . . . . . 294

4.14.3 Specifying the Bitporter Pod . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

4.14.4 Playing an Action . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

4.15 Optimizing a Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 295

4.15.1 Attempting Likely Optimizations Using Option Sets . . . . . . . . . . . . . . . . . . . 295

4.16 Placement Regions and Placement Region Constraints . . . . . . . . . . . . . . . . . . . . . . . 297

4.16.1 Placement Region Preferences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 297

4.16.2 Creating a new placement region . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 297

4.16.3 Resizing an existing placement region . . . . . . . . . . . . . . . . . . . . . . . . . . . . 298

4.16.4 Moving an existing placement region . . . . . . . . . . . . . . . . . . . . . . . . . . . . 298

4.16.5 Assigning placement region constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . 299

4.16.6 Listing all objects constrained to a placement region . . . . . . . . . . . . . . . . . . . . 300

4.16.7 Removing a placement region constraint from an object . . . . . . . . . . . . . . . . . . 300

4.16.8 Saving placement region definitions and placement region constraints . . . . . . . . . 300

4.16.9 Deleting Placement Regions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 301

5 Tcl Command Reference 302

5.1 add project constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 302

5.2 add project ip . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 302

5.3 add project netlist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 302

5.4 add region insts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 303

5.5 all clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 303

5.6 all inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 303

5.7 all outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 303

5.8 apply extra pipeline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 303

5.9 apply placement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 304

5.10 clear arcs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 304

5.11 clear drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 304

5.12 clear lines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 304

vii http://www.achronix.com UG001 Rev. 5.0 - 5th December 2012

Page 9

CONTENTS CONTENTS

5.13 clear ovals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 305

5.14 clear polygons . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 306

5.15 clear rectangles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 306

5.16 clear strings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 306

5.17 clock info . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 306

5.18 clock relation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 307

5.19 create clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 308

5.20 create flow step . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 308

5.21 create generated clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 309

5.22 create impl . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 310

5.23 create path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 310

5.24 create project . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 311

5.25 create region . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 311

5.26 deselect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 312

5.27 disable flow step . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 312

5.28 disable project constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 312

5.29 display file . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 313

5.30 display rtl . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 313

5.31 draw arc . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 313

5.32 draw line . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 315

5.33 draw oval . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316

5.34 draw polygon . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 317

5.35 draw rectangle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 318

5.36 draw string . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 319

5.37 enable flow step . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 320

5.38 enable project constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 320

5.39 find . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 320

5.40 generate ip design files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 323

5.41 get ace cputime . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 323

5.42 get ace current memory usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 323

5.43 get ace peak memory usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 323

5.44 get ace version . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 323

5.45 get active impl . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 323

5.46 get active project . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 323

5.47 get cells . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 324

5.48 get clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 324

5.49 get current design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 325

5.50 get current partname . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 325

5.51 get efd file path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 325

5.52 get enabled constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 325

UG001 Rev. 5.0 - 5th December 2012 http://www.achronix.com viii

Page 10

CONTENTS CONTENTS

5.53 get extra pipeline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 326

5.54 get fabricdb path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 326

5.55 get impl names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 326

5.56 get impl option . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 327

5.57 get installation directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 327

5.58 get location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 327

5.59 get nets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 327

5.60 get part names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 328

5.61 get path property . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 328

5.62 get pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 329

5.63 get placement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 329

5.64 get pod names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 330

5.65 get ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 330

5.66 get project constraint files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 330

5.67 get project directory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 330

5.68 get project ip files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 331

5.69 get project names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 331

5.70 get project netlist files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 331

5.71 get properties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 331

5.72 get property . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 332

5.73 get region insts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 332

5.74 get selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 332

5.75 get stapl actions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 333

5.76 get techlib name . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 334

5.77 get techlib path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 334

5.78 get techlibdb path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 334

5.79 get techlibt name . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 334

5.80 get techlibt path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 335

5.81 get techlibx name . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 335

5.82 get techlibx path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 335

5.83 highlight . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 336

5.84 ignore cancel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 336

5.85 load place and route . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 336

5.85.1 Usage Notes: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 337

5.86 load project . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 337

5.87 message . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 337

5.88 prepare sta . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 338

5.89 refresh drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 338

5.90 remove flow step . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 338

5.91 remove impl . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 338

ix http://www.achronix.com UG001 Rev. 5.0 - 5th December 2012

Page 11

CONTENTS CONTENTS

5.92 remove path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 339

5.93 remove project . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 339

5.94 remove project constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 339

5.95 remove project ip . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 339

5.96 remove project netlist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 340

5.97 remove region . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 340

5.98 remove region insts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 340

5.99 rename impl . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 341

5.100report clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 341

5.101report clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 341

5.102report impl options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 341

5.103report pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 342

5.104report placement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 343

5.105report power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 343

5.106report regions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 344

5.107report routing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 345

5.108report utilization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 345

5.109reset impl option . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 346

5.110reset sta . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 346

5.111restore impl . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 346

5.111.1 Usage Notes: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 347

5.112restore project . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 347

5.113run . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 348

5.114run fanout control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 348

5.115run final drc checks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 349

5.116run fpga download . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 349

5.117run gate balance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 349

5.118run generate bitstream . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 350

5.119run generate netlist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 351

5.120run insert reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 351

5.121run place . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 351

5.122run post process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 352

5.123run prepare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 352

5.124run remove reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 353

5.125run route . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 353

5.126run stapl action . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 354

5.127run timing analysis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 354

5.128run un post process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 355

5.129run unplace . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 355

5.130run unroute . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 356

UG001 Rev. 5.0 - 5th December 2012 http://www.achronix.com x

Page 12

CONTENTS CONTENTS

5.131save place and route . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 356

5.131.1 Usage Notes: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 356

5.132save placement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 356

5.133save impl . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 358

5.133.1 Usage Notes: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 358

5.134save project . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 358

5.135save properties . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 359

5.136save regions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 359

5.137select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 359

5.138set active impl . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 360

5.139set clock groups . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 360

5.140set clock type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 361

5.141set cluster . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 361

5.142set default relation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 362

5.143set extra delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 362

5.144set extra pipeline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 363

5.145set false path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 364

5.146set flyline direction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 364

5.147set impl option . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 364

5.148set input delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366

5.149set input transition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366

5.150set load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367

5.151set max flyline fanout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367

5.152set output delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367

5.153set placement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 368

5.154set property . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 369

5.155set region bounds . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 369

5.156set units . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 370

5.157timing summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 370

5.158write bitstream . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 370

5.159write critical paths script . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 371

5.160write netlist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 371

5.161write tcl history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 372

6 Revision History 373

6.0.1 Version 5.0.0: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 373

6.0.2 Version 4.2.0: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 375

6.0.3 Version 3.2.0: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 376

xi http://www.achronix.com UG001 Rev. 5.0 - 5th December 2012

Page 13

Conventions Used in this Guide Chapter 1. Preface

Preface

About This Guide

This guide is a reference manual for the Achronix CAD Environment (ACE), used for placing, routing,

configuring, and debugging Achronix FPGAs. ACE works in conjunction with 3rdParty Synthesis and

Simulation tools to provide a complete design environment for Achronix FPGAs.

This guide consists of the following chapters:

Getting Started includes an Introduction to ACE and a quick Tutorial.

Concepts covers all the basic concepts of ACE, and can be considered a reference manual for the various

GUI elements.

Tasks details how to complete various tasks within the GUI, plus provides the related TCL commands.

TCL Command Reference provides a complete TCL command reference including syntax.

Related Documents

ACE Installation and Licensing Guide (UG002)

ACE Quick Start Guide (UG003)

Bitporter User Guide (UG004)

Using Verilog Libraries Available In ACE (found at <ace install dir>/libraries/README.pdf)

Conventions Used in this Guide

Item Format

Command-line entries

File Names

GUI buttons, menus, and

radio buttons

Variables Formatted with italic emphasis.

Window and dialog box

headings and

sub-headings

Window and dialog box

names

Formatted with a bold

fixed-width font.

Formatted with a fixed-width

font.

Formatted with a

variable-width bold font.

Heading formatted in

quotation marks.

Name uses initial caps.

Examples

$ Open top level name.log

filename.ext

Select File→Open, select the desired

file, then click OK to continue.

design dir/output.log

Under ”Output Files”, select . . .

From the Add Files dialog box, . . .

1 http://www.achronix.com UG001 Rev. 5.0 - 5th December 2012

Page 14

Chapter 2. Getting Started

Getting Started

Introduction

The Achronix implementation flow uses an industry standard RTL synthesis flow based on Synplify-Pro

from Synplicity and Precision Synthesis from Mentor Graphics. Working in conjunction with the synthesis

tool, Achronix CAD Environment (ACE) provides

• Placement

• Routing

• Timing Analysis

• Bitstream Generation

• FPGA Configuration

• On-chip Debugging

UG001 Rev. 5.0 - 5th December 2012 http://www.achronix.com 2

Page 15

ACE Quickstart Tutorial Chapter 2. Getting Started

ACE Quickstart Tutorial

Start by copying all the files from <install dir>/Achronix/examples/quickstart into a new

empty directory (<test dir>). Now click the ( ) icon in the upper right corner. Then follow these

simple steps to complete your first design in ACE.

1. Create your Project

In the Projects view, click the Create Project ( ) toolbar button. In the Create a New Project dialog, enter

(or browse to) the path to <test dir> in the Project Directory field. Enter ”quickstart” in the Project

Name field and click OK. You should now see your new project show up in the Projects view.

See Creating Projects or Working with Projects for more details.

2. Add your Design Files

In the Projects view, click on the ”quickstart” project to select it. Now click on the Add Files ( ) toolbar

button. In the Add Source Files dialog, select both quickstart.vma and quickstart.sdc by holding

down the CTRL key and clicking on them. Now click the Open button. You now have a project that is ready

to run through the flow!

See Adding Source Files or Working with Projects for more details.

3. Run the Flow

In the Flow view, click on the Run Flow ( ) toolbar button. Output from the flow will be shown in the

TCL Console view. When the flow is finished running, you will see the flow steps in the Flow view updated

with a green check mark ( ) to indicate success and all newly generated reports will be displayed in the

editor area.

See the Flow concept or Running the Flow for more details.

4. Analyze the Results

On the main toolbar, click the Floorplanner Perspective ( ) toolbar button. Use the Critical Paths view to

analyze critical paths and highlight them in the Floorplanner view. Clicking the Zoom To Path ( ) toolbar

button will zoom the Floorplanner view to the path currently selected in the Critical Paths view. Use the

Search view and Selection view to locate objects of interest. Clicking the Zoom To Selection ( ) toolbar

button in the Selection view will zoom the Floorplanner view to the objects in the current selection set.

Congratulations!!!

You have successfully completed a design in ACE!

3 http://www.achronix.com UG001 Rev. 5.0 - 5th December 2012

Page 16

Perspectives Chapter 3. Concepts

Concepts

Workbench

The term Workbench refers to the desktop development environment within ACE. The Workbench aims to

achieve seamless tool integration and controlled openness by providing a common platform for the creation,

management, and navigation of workspace resources.

Each Workbench window contains one or more perspectives. Perspectives contain views and editors and

control what appears in certain menus and tool bars. More than one Workbench window can exist on the

desktop at any given time.

Perspectives

There are many different kinds of information a user must view within ACE. Perspectives are used to filter

the information into usable logically consistent groupings. A perspective provides a set of functionality

aimed at accomplishing a specific type of task or works with specific types of resources. A perspective

defines the initial set and layout of views, editors, menus, and toolbars in the Workbench window.

For example, the Projects perspective combines views commonly used while managing project source

files, while the Floorplanner perspective contains the views that are used while viewing chip layout and

floorplanning information. Users often switch perspectives frequently while working inside the Workbench.

Note: Within the Workbench window, all perspectives share the same set of editors. All editors are

usable/visible from all perspectives1. Likewise, each of the views may optionally be used within any

perspective, but they’re most useful when grouped with the other views from their native perspective.

Projects Perspective

The Projects Perspective allows the user to select an active project and implementation, manage the

contents and configuration of the active project/implementation, run the Flow, and view the reports

generated by the Flow.

By default, this perspective contains the ”Projects View”, ”Flow View”, ”Options View”, ”TCL Console

View”, and the Editor area, which can contain any ACE Editor or Report.

For more information, see Working with Projects, Running the Flow, and Using the Tcl Console.

Floorplanner Perspective

The Floorplanner Perspective allows the user to view and edit the placement and routing of their active

project/implementation.

By default, this perspective contains the ”Floorplanner View”, ”Package View”, ”Search View”, ”Selection

View”, ”Critical Paths View”, ”IO Assignment View”, ”Netlist Browser View”, ”Clock Regions View”,

”Placement Regions View”, and ”TCL Console View”.

For more information on using the views in this perspective, see Viewing the Floorplanner, Viewing the

Package Layout, Pre-Placing a Design, Analyzing Critical Paths, and Managing I/Os.

NOTE:

Unlike all other perspectives, the Floorplanner perspective hides the Editor area. To view

Editors and reports, a different perspective must be selected.

IP Configuration Perspective

The IP Configuration Perspective is used to create and edit IP configuration files (.acxip) through the IP

Editors (like the ”SerDes IP Configuration Editor” and ”Basic PLL IP Configuration Editor”).

1

except the Floorplanner perspective, which disallows the display of editors

UG001 Rev. 5.0 - 5th December 2012 http://www.achronix.com 4

Page 17

Perspectives Chapter 3. Concepts

By default, this perspective contains the ”Projects View”, ”IP Libraries View”, ”IP Diagram View”, ”IP

Problems View”, ”Outline View”, ”TCL Console View”, and the Editor Area, which can contain any ACE

Editor or Report.

See Creating an IP Configuration for more details.

Bitporter Perspective

The Bitporter Perspective allows interaction with Achronix FPGAs via JTAG through a Bitporter pod.

Downloading the device configuration and debugging will typically happen from here.

By default, this perspective contains the ”SnapShot Debugger View”, ”Download View”, ”TCL Console

View”, and the Editor area, which can contain any ACE Editor or Report.

For more information on using this perspective, see Running the SnapShot Debugger and Playing a STAPL

File

5 http://www.achronix.com UG001 Rev. 5.0 - 5th December 2012

Page 18

Editors Chapter 3. Concepts

Editors

Most perspectives in the Workbench are comprised of an editor area and one or more views. Different

editors are associated with different types of files. For example, when a file is opened by double-clicking for

editing in the Projects View, the associated editor opens in the Workbench. If there is no associated editor

for a resource, the Workbench attempts to launch an external editor outside the Workbench. Any number

of editors can be open at once, but only one can be active at a time. The main menu bar and toolbar for the

Workbench window contain operations that are applicable to the active editor.

Tabs in the editor area indicate the names of resources that are currently open for editing (usually the

filename, and the tab’s tooltip will provide the full path to the file). An asterisk (*) indicates that an editor

has unsaved changes. By default, editors are stacked in the editor area, but users may choose to tile them

in order to view multiple editors simultaneously. The gray border at the left margin of the editor area may

contain icons that flag errors, warnings, or problems detected by the system.

In ACE, the editor area is also used to view the Reports generated by ACE. By default, ACE will open HTML

versions of the reports in the HTML Report Browser as soon as the report data is generated/updated2.

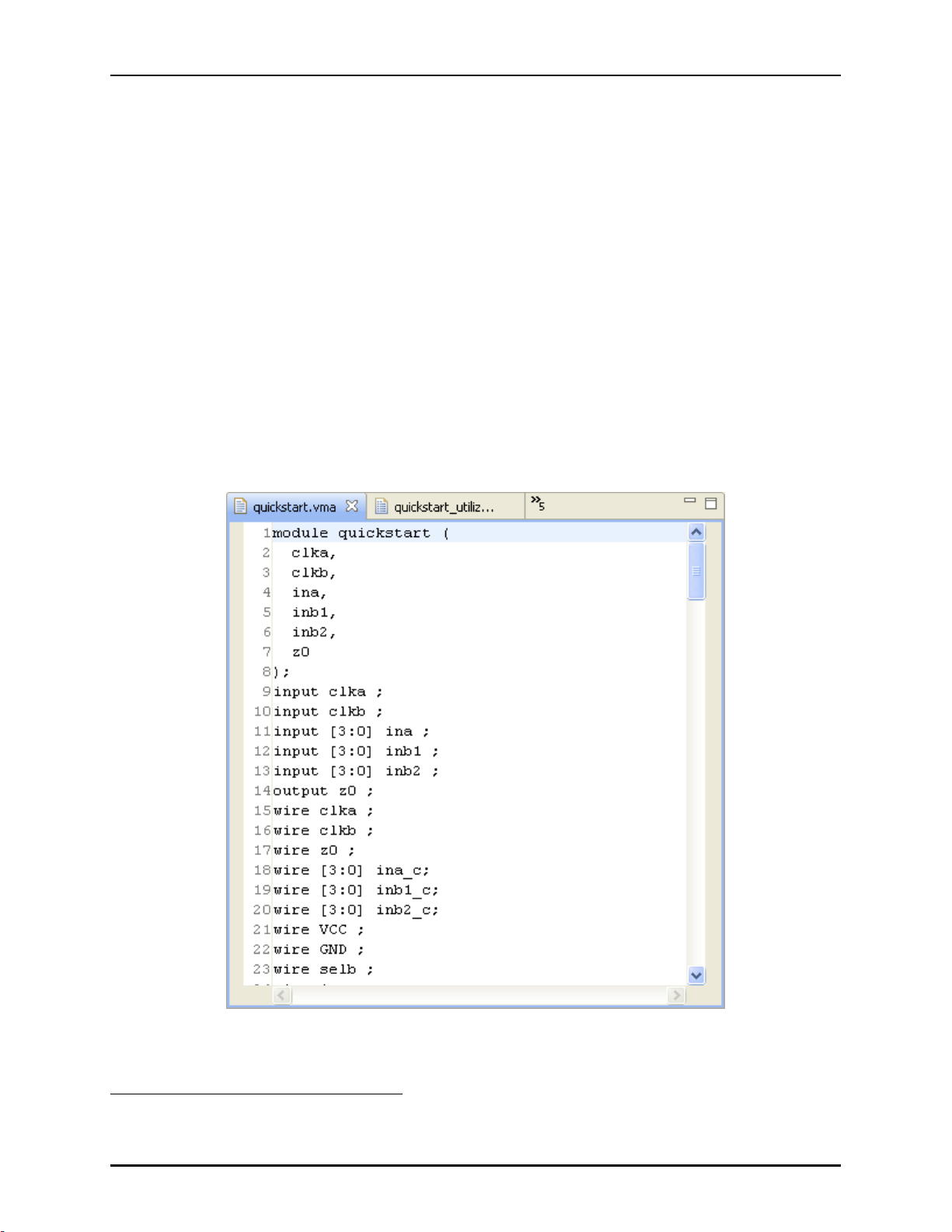

Text Editor

Reports, source files, and scripts open in the text editor. The text editor supports typical editing functions,

such as insert, delete, copy, cut, and paste.

Figure 3.1: Text Editor Window

2

This is only true when running the Flow in single-process mode. In Multiprocess mode (via the Multiprocess View), only the

Multiprocess Summary Report is automatically opened in the editor area the other reports must be opened manually through the

Projects View.

UG001 Rev. 5.0 - 5th December 2012 http://www.achronix.com 6

Page 19

Editors Chapter 3. Concepts

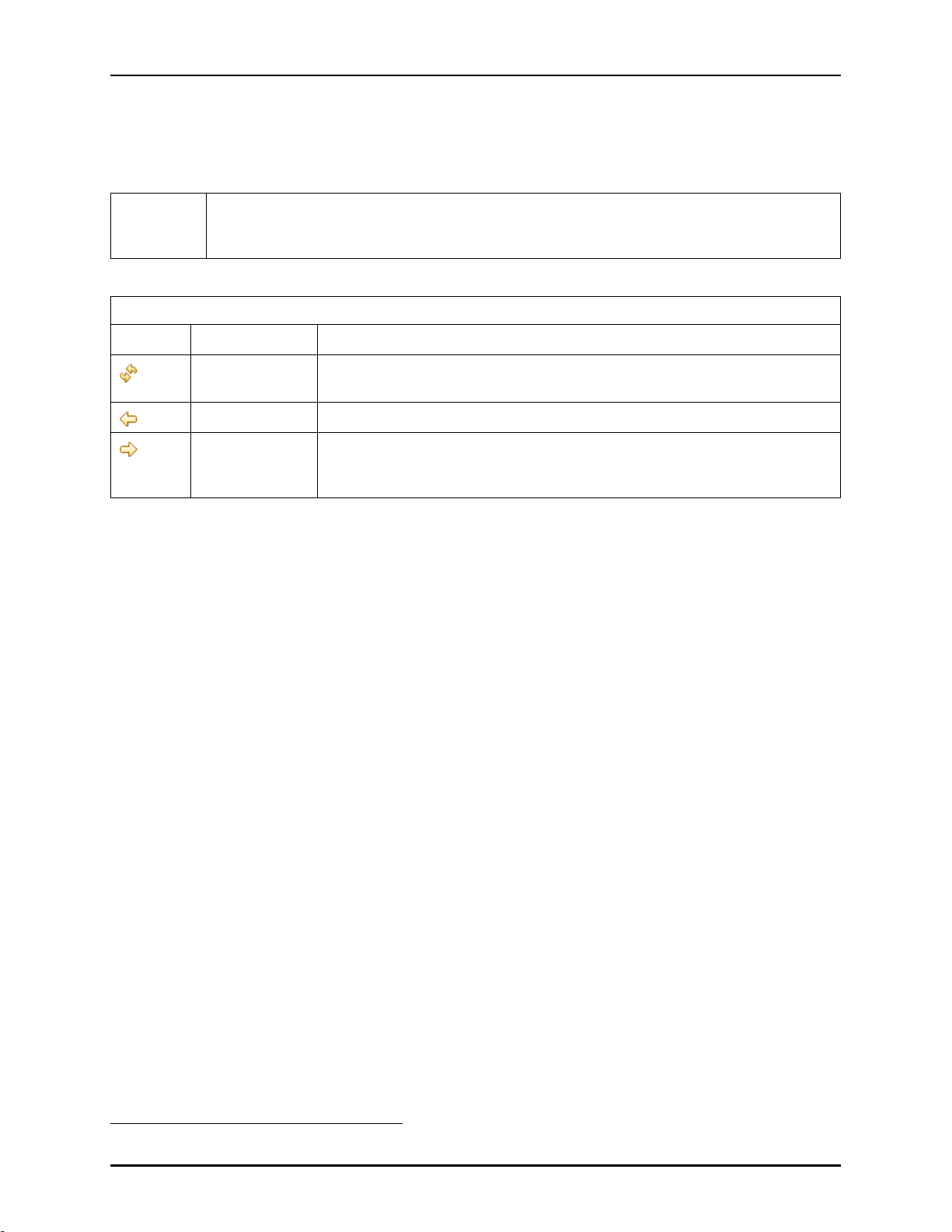

HTML Report Browser

When HTML versions of generated Reports are opened within ACE, they are displayed within the Editor

area using the HTML Report Browser. This is a very limited form of a web browser - it only allows hyperlink

traversal, refresh, forward, and back operations.

Note:

The HTML Report Browser should typically not be used to browse the Internet - a

dedicated web browser like Firefox would be a much better choice for both security and

performance reasons.

Icon Action

Refresh

Back

Forward

HTML Report Browser Toolbar Buttons

3

Description

Refreshes the displayed HTML report to show the current contents of the

report file on disk.

Returns to the last HTML location viewed.

Returns to the HTML location viewed before the Back button was

selected. (The Forward button remains disabled until the Back button has

been pressed.)

3

These buttons are displayed in the topmost button-bar of ACE, not within the Editor area itself.

7 http://www.achronix.com UG001 Rev. 5.0 - 5th December 2012

Page 20

Editors Chapter 3. Concepts

Advanced PLL Configuration Editor

The Advanced PLL Configuration Editor provides a graphical wizard for creating a PLL configuration

file (.acxip). This editor allows the user to generate the required configuration files for design with the

embedded PLLs. See Creating an IP Configuration. Unlike the much simpler Basic PLL Configuration

Editor, the Advanced PLL Configuration Editor allows the user to access the complete functionality of the

PLL.

By default, the Advanced PLL Configuration Editor is included in the IP Configuration perspective

(Window → Open Perspective → IP Configuration) ( ). The Advanced PLL configuration information is

broken up into several pages, organized by concept. While some pages are always available, many pages of

configuration options may appear or disappear depending upon whether they are relevant, based upon the

users current choices for configuration options.

Once the user has configured the PLL to meet their requirements, and the Advanced PLL Editor has

determined that there are no errors in the configuration, the user may choose to generate their IP design

files (see Generating the IP Design Files).

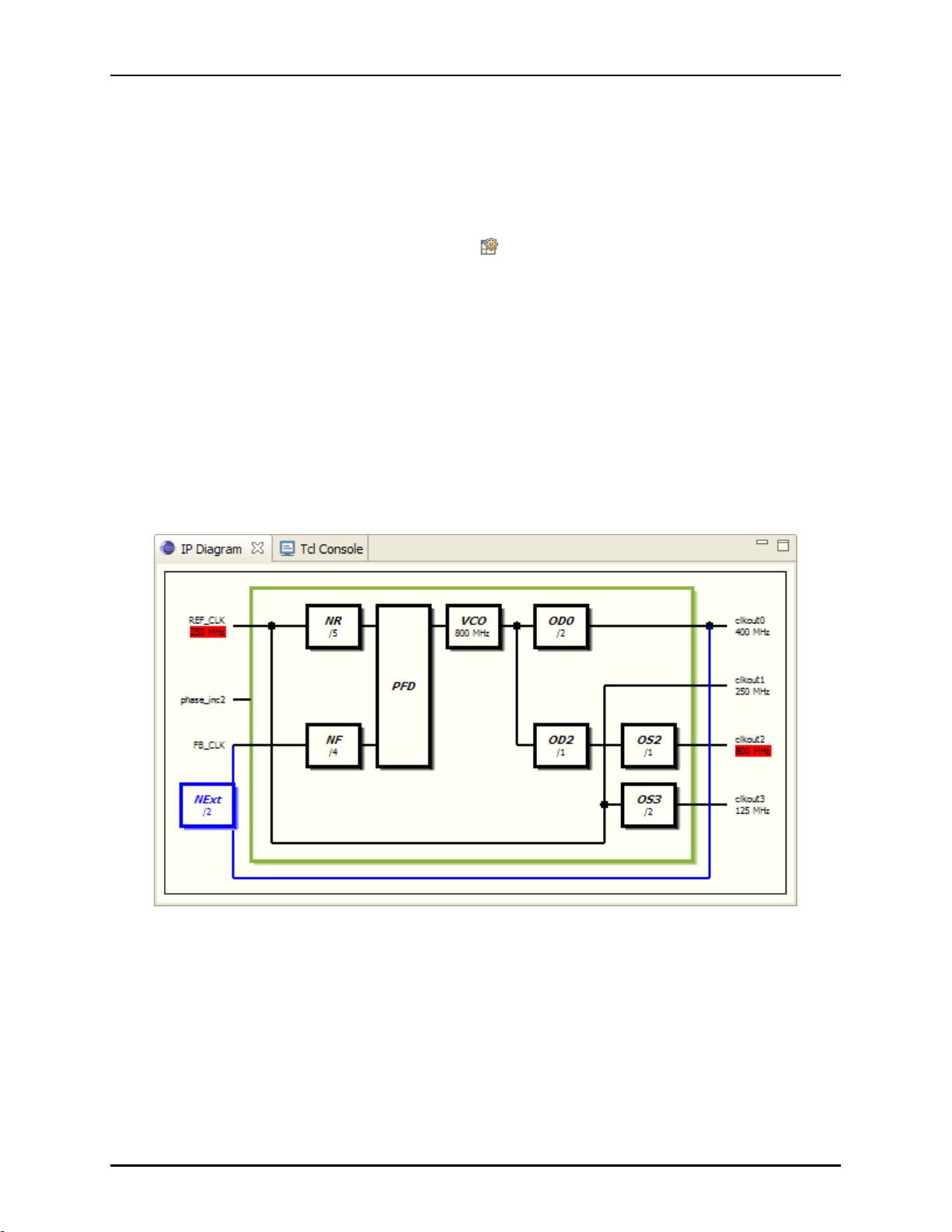

IP Diagram

The IP Diagram View for the PLL shows live information about the current configuration in the Editor,

including which logic blocks are currently active, which inputs and outputs are currently active, and what

the various frequencies are within the PLL. Additionally, configuration errors will be shown with a red

background, and configuration warnings will be shown with a yellow background (these are the default IP

Diagram colors, and may be modified in the Preferences).

Figure 3.2: Example IP Diagram for Advanced PLL Editor with some errors in red

UG001 Rev. 5.0 - 5th December 2012 http://www.achronix.com 8

Page 21

Editors Chapter 3. Concepts

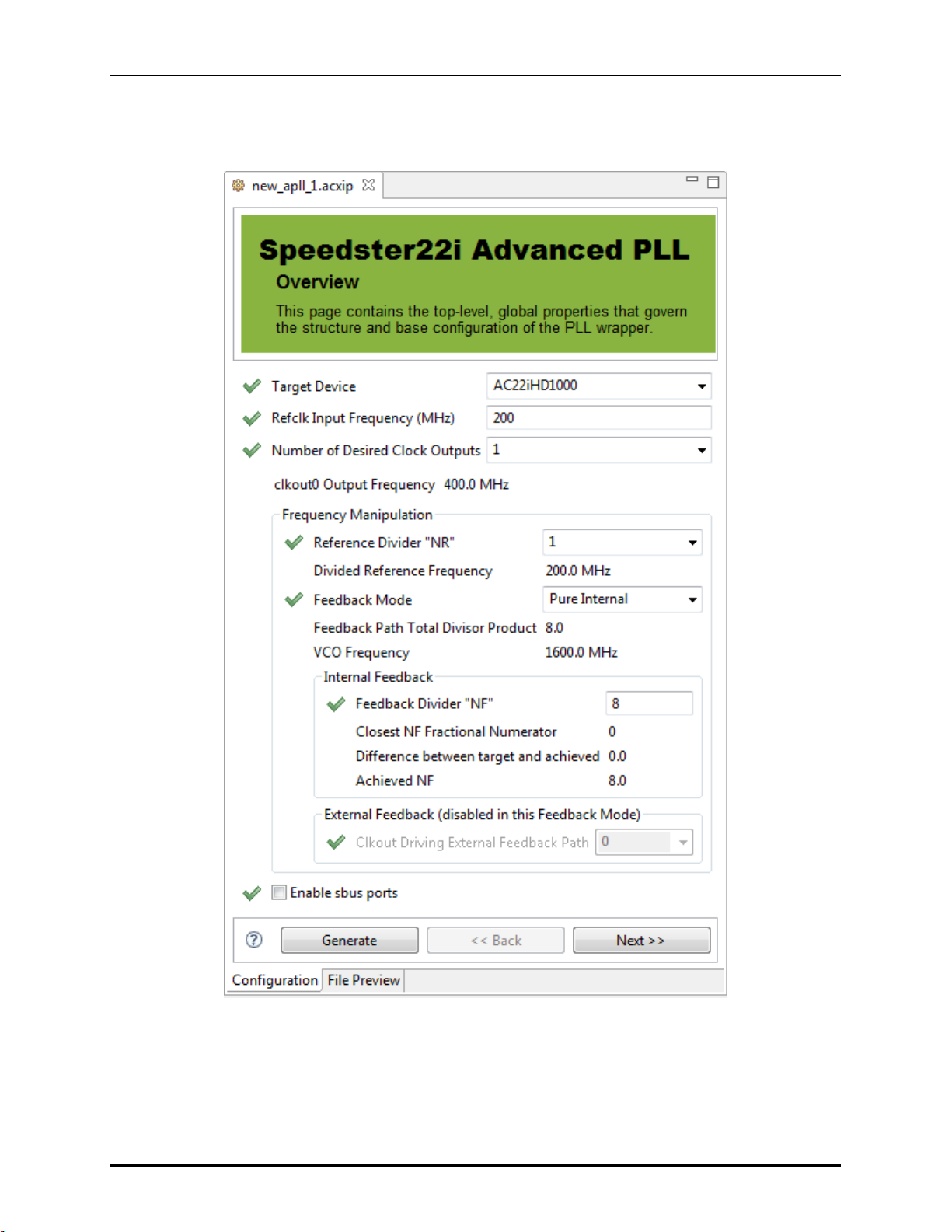

Overview Page

The Overview page contains the top-level, global properties that govern the structure and base

configuration of the PLL. Changes made on this page affect all the outputs for this PLL.

Figure 3.3: Advanced PLL IP Editor Overview Page

9 http://www.achronix.com UG001 Rev. 5.0 - 5th December 2012

Page 22

Editors Chapter 3. Concepts

PLL Editor Overview Page Options

Option Editable

Target Device Y

Refclk Input

Frequency (MHz)

Number of Desired

Clock Outputs

Y

Y

clkout Output

Frequency

Reference Divider

”NR”

Y

Divided Reference

Frequency

Feedback Mode Y

Description

The Speedster22i device this PLL is intended to target.

The frequency of the PLL reference clock input.

The number of desired clock output signals for this PLL.

Changing this will alter the number of active pages of

Clock Output configuration options.

The calculated output frequency of the named clock

output signal. The number of outputs listed will match

the ”Number of Desired Clock Outputs”.

The amount by which the reference clock frequency

should be divided before entering the PLLs Phase

Frequency Detector. As this value increases, the ”VCO

Frequency” decreases.

The calculated reference clock frequency after having

been divided by the ”Reference Divider ’NR’”.

Selects one of the three allowed feedback modes, and

enables/disables related options on this page according

to the selected mode. See Feedback Modes below for

more details.

Feedback Path Total

Divisor Product

VCO Frequency

Feedback Divider

”NF”

Closest NF Fractional

Numerator

Difference between

target and achieved

The calculated total product of all divisors in the present

feedback path.

The calculated VCO output frequency. The algorithm

used will vary depending upon the selected Feedback

Mode.

Y

The amount by which the feedback signal should be

divided before entering the PLLs Phase Frequency

Detector. As this value increases, the ”VCO Frequency”

increases. When in Pure Internal Feedback Mode, this

may be a floating-point value; in Mixed feedback mode

this must be an integer value. In Pure External Feedback

Mode, this option will be disabled.

This calculated values represents the fractional portion of

the entered ”Feedback Value ’NF’” used to configure the

PLL. When floating point values are entered for the

”Feedback Divider ’NF’”, they must be represented as

fractions of 65536 (a 16-bit representation of the fraction is

used). The value displayed provides the closest possible

fraction to that requested by the user.

This calculated value shows how close the PLL can come

to the requested ”Feedback Divider ’NF’” value. (Some

requested fractional values are impossible to exactly

represent within the 16 bits available in the PLL.)

UG001 Rev. 5.0 - 5th December 2012 http://www.achronix.com 10

Page 23

Editors Chapter 3. Concepts

Achieved NF

This calculated value shows the exact ”Feedback Divider

’NF’” value which will be used by the PLL. This may

differ slightly from the requested value; the closest

approximate value will be chosen if an exact match is not

possible.

Clkout Driving

External Feedback

Path

Y

Selects which of the currently-enabled clock outputs will

drive the external feedback path. Note that Phase

Adjustment is not allowed in the Feedback Path.

Enable sbus ports Y

When selected, the sbus ports will be exposed in the

generated HDL file(s).

Feedback Modes There are three feedback modes available to the PLL. Some allow fractional feedback,

others allow deskew.

PLL Feedback Modes

Mode Fractional Feedback? Deskew?

Pure Internal Y N

Pure External N Y

Mixed N Y

Algorithm

F

=(NF/NR)*F

V CO

F

=(ODn*OSn/NR)*F

V CO

F

=(NF*ODn*OSn/NR)*F

V CO

ref

ref

ref

Pure Internal Feedback

When internal feedback mode is selected, the VCO clock is divided by the ”Feedback Divider ’NF’” only.

In this mode, the PLL can have both integer and fractional feedback divider values. The ”Clkout Driving

External Feedback Path” option becomes disabled in this mode, since it is irrelevant. Deskewing is not

possible in this mode.

Pure External Feedback

When external feedback mode is selected, the VCO clock is divided by the Output Divider (ODn) and

(optionally) the Output Synthesizer (OSn). The ”Clkout Driving External Feedback Path” option becomes

enabled in this mode, and the ”Feedback Divider ’NF’” option becomes disabled. In this mode, it is not

allowed to feedback a clock output that has Phase Adjustment enabled.

4

Mixed Feedback

Mixed feedback mode is a modified version of Pure External feedback mode, in that the Feedback Divider

integer value is also in the deskew feedback path. As with Pure External mode, Phase Adjustment is not

allowed in the feedback path. The ”Clkout Driving External Feedback Path” option becomes enabled in this

mode, as does ”Feedback Divider ’NF’”.

4

Phase rotation in the feedback path will cause the PLL to unlock. If Phase Adjustment is required on any output clocks, it must be

used on outputs which are not in the feedback path.

11 http://www.achronix.com UG001 Rev. 5.0 - 5th December 2012

Page 24

Editors Chapter 3. Concepts

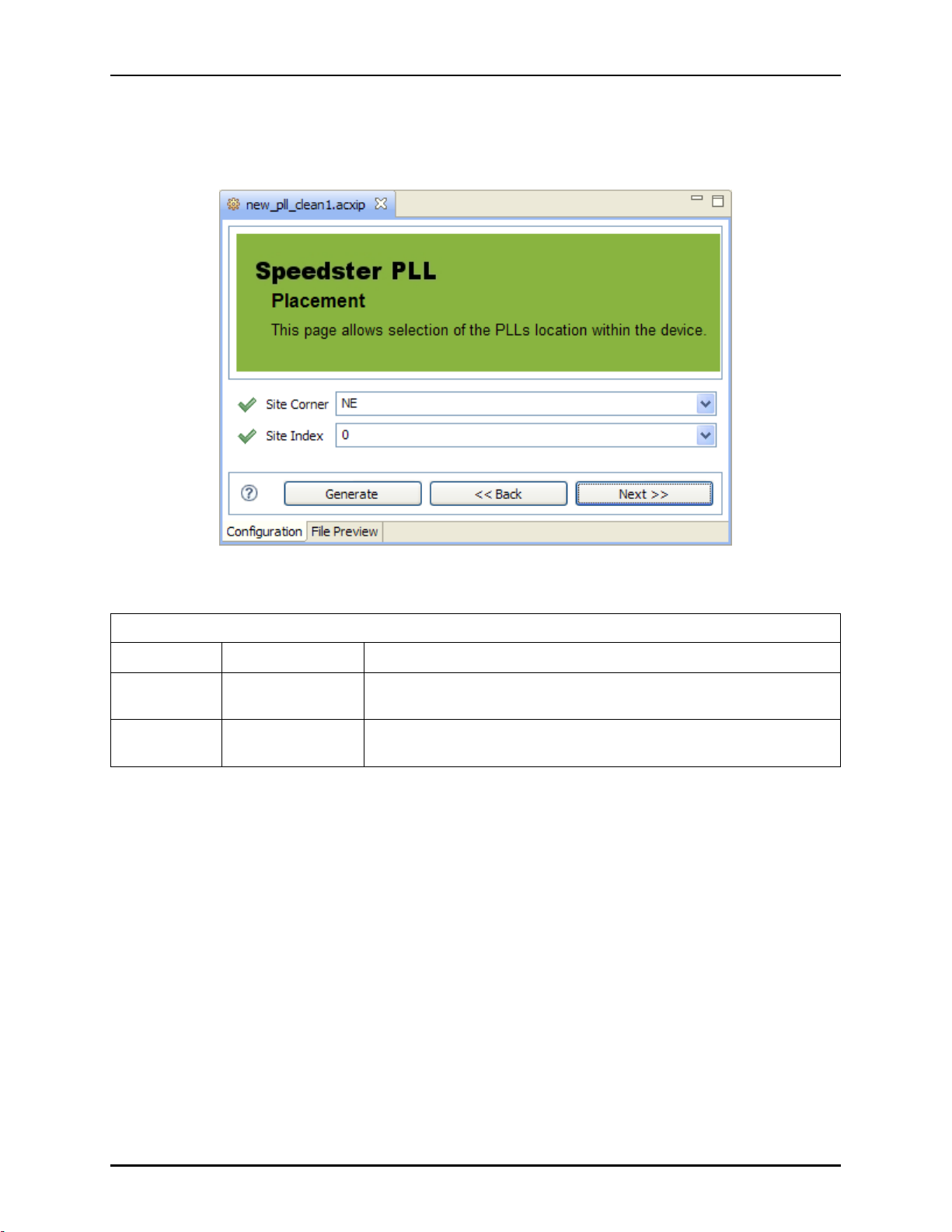

Placement Page

The Placement page contains configuration information relating to the PLLs placement in the Speedster

device. The site chosen will be exported in a placement constraints (.pdc) file when the user chooses to

generate their PLL design files.

Option Editable

Site Corner Y

Site Index Y

Figure 3.4: Advanced PLL IP Editor Placement Page

PLL Editor Placement Page Options

Description

The corner of the Speedster22i device where this PLL instance

should be placed. The four choices are NE, SE, SW, and NW.

The site index within the corner where this PLL instance should be

placed.

UG001 Rev. 5.0 - 5th December 2012 http://www.achronix.com 12

Page 25

Editors Chapter 3. Concepts

Clock Output [0,1,2,3] Pages

The Clock Output pages each contain general configuration information relating to a single PLL output

signal. Since there are one-to-four PLL output signals per PLL (as configured on the Overview Page),

between one and four Clock Output pages will be enabled.

Figure 3.5: IP Advanced PLL Editor Clock Output 0 Page

Option Editable

clkout Output

Frequency

Bypass PLL and

Output Divider

(OD[0-3])

Enable Output

Synthesizer

(OS[0-3])

Y

Y

PLL Editor Clock Output Page Options

Description

The calculated frequency of this clock output signal as it

exits the PLL.

Enabling this will bypass the NR, PFD, VCO, and OD,

sending the reference clock input signal directly to the OS

input. Disabling this allows normal PLL behavior. Note that

when this is enabled, the IP Editor configuration page for

the Output Divider (OD) associated with this clock output is

disabled. In addition, when enabled, it becomes illegal to

use this output in an external feedback path, as the PLL will

lose lock.

Allows this clock output to use its Output Synthesizer (OS).

When enabled, this activates the IP Editor configuration

page for the OS associated with this clock output. When

disabled, the associated OS configuration page is hidden.

13 http://www.achronix.com UG001 Rev. 5.0 - 5th December 2012

Page 26

Editors Chapter 3. Concepts

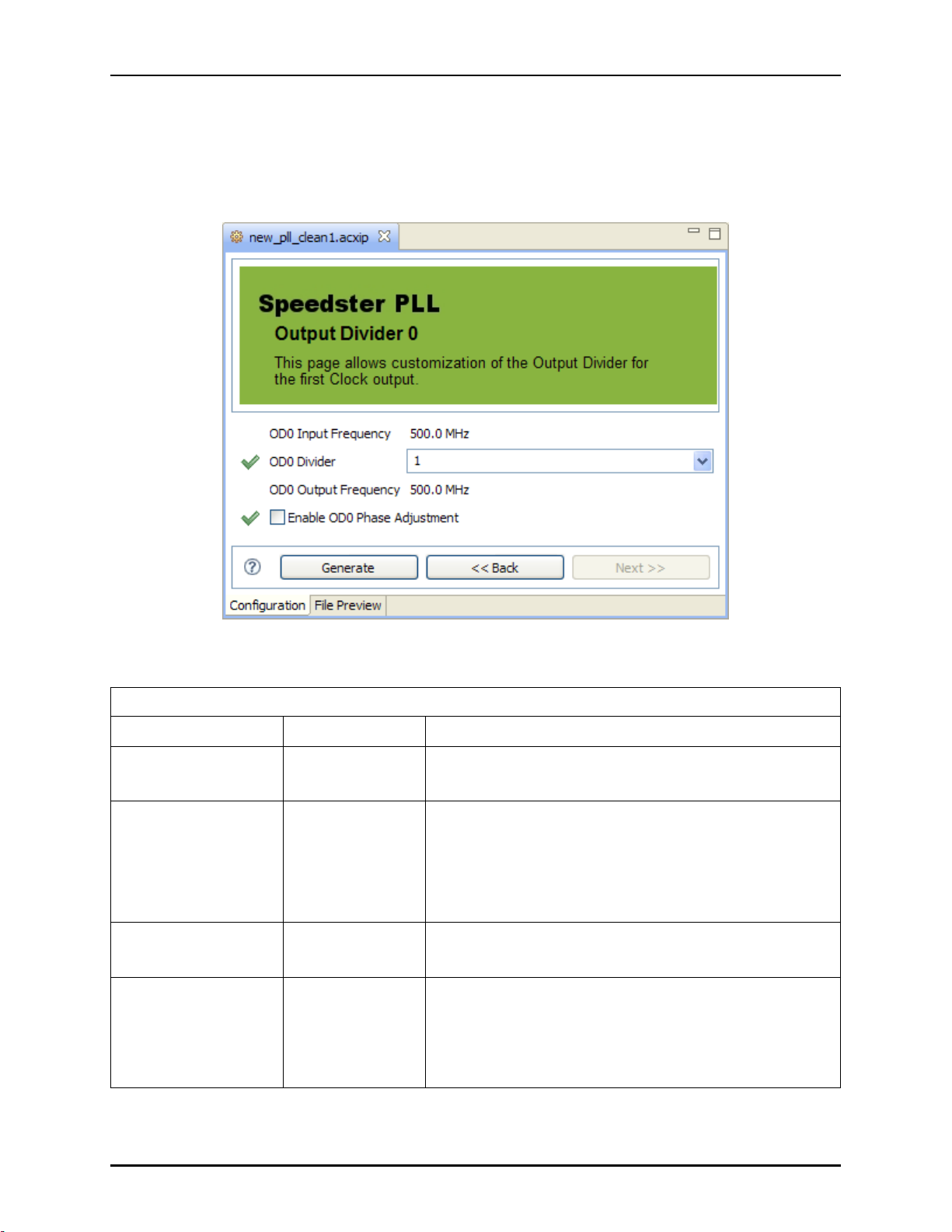

Output Divider [0,1,2,3] Pages

The Output Divider pages contain configuration information relating to the output divider (OD) of one of

the PLLs clock output signals. Since there are one-to-four PLL output signals per PLL, there are also up to

four of these pages. Because the PLL and OD logic may be bypassed on a per-output basis (as configured

on the Clock Output [0,1,2,3] Pages), this page may sometimes be hidden, even if the related clock output is

enabled.

Figure 3.6: IP Advanced PLL Editor Output Divider 0 Page

PLL Editor Output Divider Page Options

Option Editable

OD[0-3] Input

Frequency

OD[0-3] Divider Y

OD[0-3] Output

Frequency

Enable OD[0-3] Phase

Adjustment

Y

Description

The calculated frequency of the input signal as it enters

this OD logic block.

The factor by which the signal entering the OD should be

divided before it exits the OD. As this increases, the OD

output frequency decreases. (Unless this OD is in the

external feedback path, in which case increasing this

value does not affect the OD output frequency, but

increases the VCO output frequency.)

The calculated frequency of the output signal as it exits

this OD logic block.

Enabling this will allow this OD to perform phase

adjustments on the OD output signal. When enabled, this

activates the related OD [0,1,2,3] Phase Adjustment Pages.

When disabled, the phase adjustment configuration

options remain hidden.

UG001 Rev. 5.0 - 5th December 2012 http://www.achronix.com 14

Page 27

Editors Chapter 3. Concepts

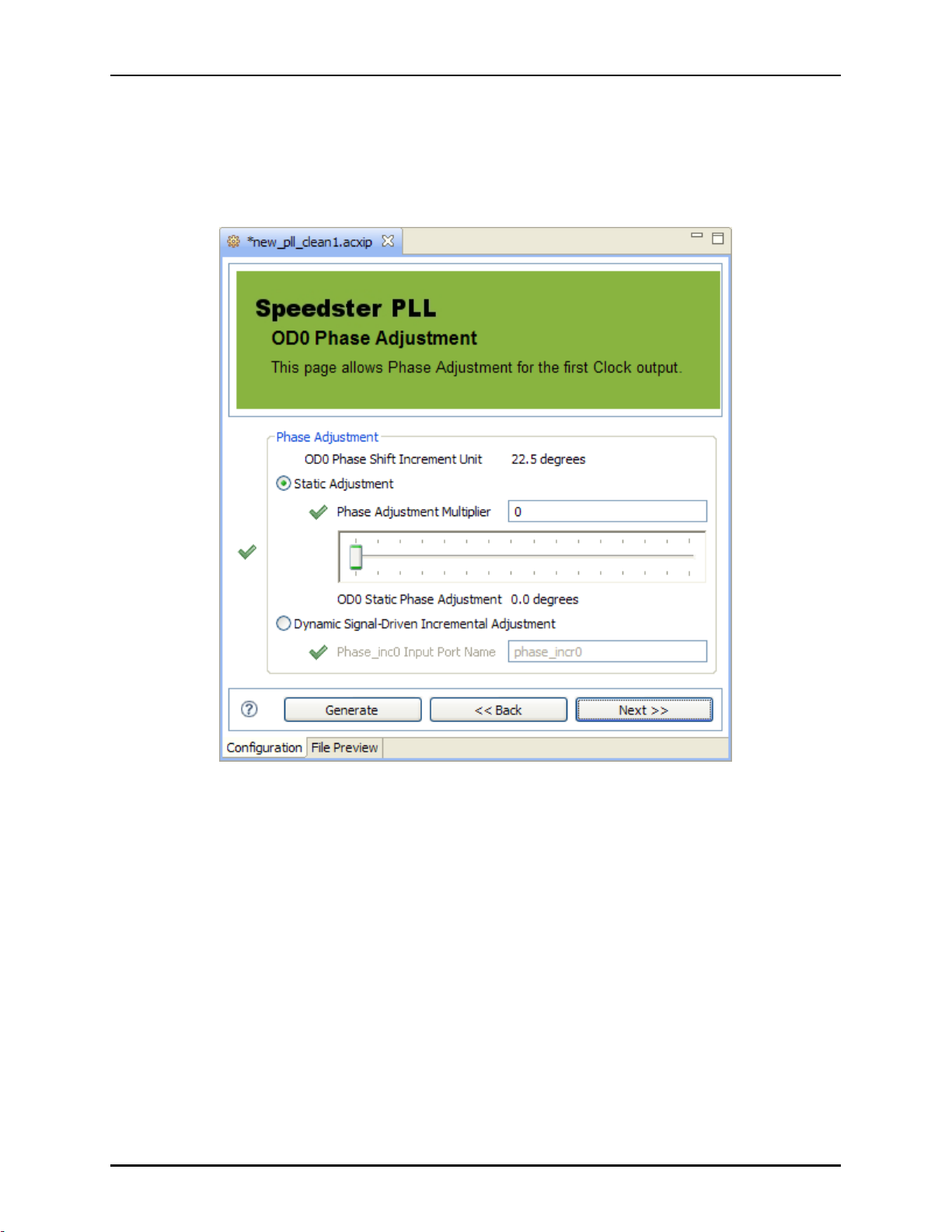

OD [0,1,2,3] Phase Adjustment Pages

The Output Divider (OD) Phase Adjustment pages contain configuration information about the potential

phase adjustment performed in an OD for one of the PLLs clkout signals. This page will only be visible

when the associated Output Divider [0,1,2,3] Pages are enabled, and the setting ”Enable OD[0-3] Phase

Adjustment” is selected. There is potentially one of these pages associated with every OD, so there will be

between zero and four of these pages for a given IP configuration.

Figure 3.7: IP Advanced PLL Editor OD0 Phase Adjustment Page

15 http://www.achronix.com UG001 Rev. 5.0 - 5th December 2012

Page 28

Editors Chapter 3. Concepts

PLL Editor OD Phase Adjustment Options

Option Editable

OD[0-3] Phase Shift

Increment Unit

Static Adjustment Y

Phase Adjustment Multiplier Y

OD[0-3] Static Phase

Adjustment

Dynamic Signal-Driven

Incremental Adjustment

Y

Description

The incremental step, always 45 degrees, by which

the OD output signal will be shifted relative to the

VCO output signal. This is a fixed value, displayed

for user convenience.

When selected, a single, unchanging phase

adjustment must be chosen for this OD. When this

is enabled, the ”Phase Adjustment Multiplier” field

will also be enabled.

This value is multiplied by the ”OD[0-3] Phase

Shift Increment Unit” to determine the total

”OD[0-3] Static Phase Adjustment”.

The calculated total phase shift, in degrees,

performed by this OD.

When selected, this enables dynamic phase

adjustment mode, where the phase of the OD

output signal will advance by ”OD[0-3] Phase Shift

Increment Unit” degrees each time a rising edge is

applied to the associated phase inc input signal.

When this mode is enabled, the ”Phase

Adjustment Multiplier” field will be disabled.

UG001 Rev. 5.0 - 5th December 2012 http://www.achronix.com 16

Page 29

Editors Chapter 3. Concepts

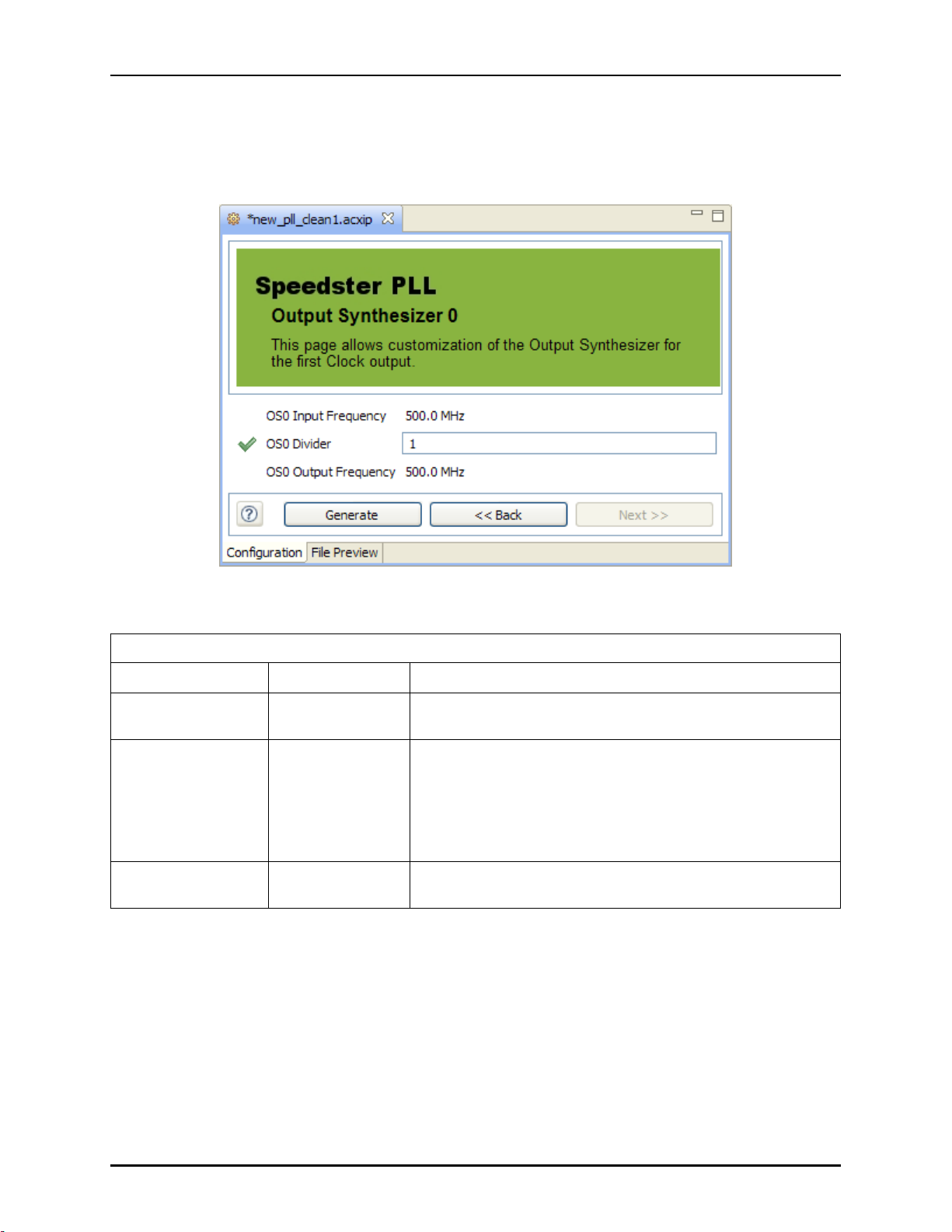

Output Synthesizer [0,1,2,3] Pages

The Output Synthesizer (OS) pages contain configuration information relating to the OS associated with

the PLLs selected clock output. Because the OS can be disabled for a PLL clock output, this page is only

visible when the ”Enable Output Synthesizer (OS[0-3])” field on the appropriate Clock Output [0,1,2,3] Page

is enabled.

Figure 3.8: IP Advanced PLL Editor Output Synthesizer 0 Page

PLL Editor Output Synthesizer Page Options

Option Editable

OS[0-3] Input

Frequency

OS[0-3] Divider Y

OS[0-3] Output

Frequency

Description

The calculated frequency of the OS input signal.

The factor by which the signal entering the OS should be

divided before it exits the OS. As this increases, the OS

output frequency decreases. (Unless this OS is in the

external feedback path, in which case increasing this value

does not affect the OS output frequency, but instead

increases the VCO output frequency.)

The calculated frequency of the OS output signal.

17 http://www.achronix.com UG001 Rev. 5.0 - 5th December 2012

Page 30

Editors Chapter 3. Concepts

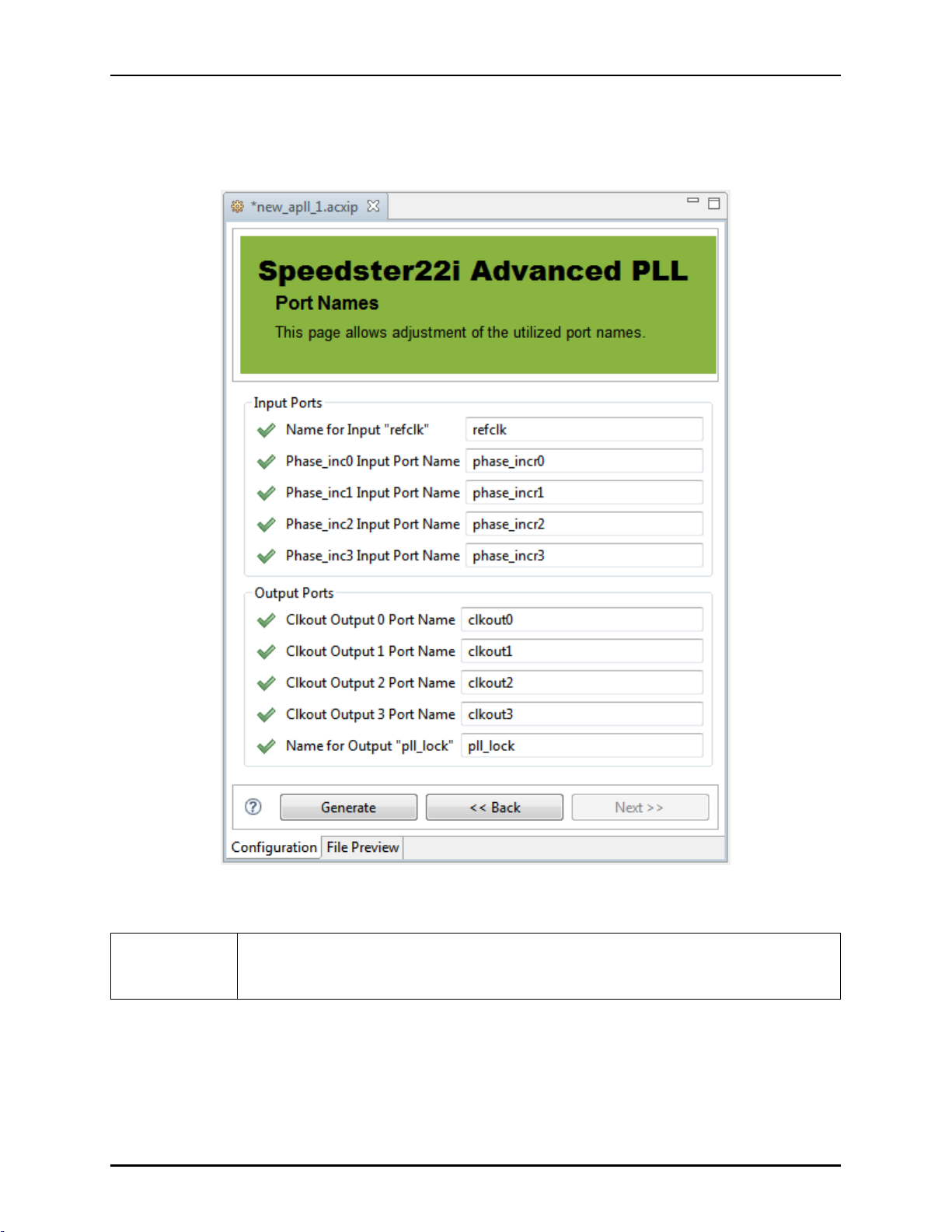

Port Names Page

The Port Names page contains all the input and output ports which will be used by the PLL in its current

configuration. (Changing options on other pages will show and hide port names on this page, as the need

for the ports changes.)

Figure 3.9: IP Advanced PLL Editor Port Names Page

NOTE:

UG001 Rev. 5.0 - 5th December 2012 http://www.achronix.com 18

All port names entered on this page must adhere to Verilog and VHDL naming

standards. Illegal names will be caught as errors, and will prohibit RTL wrapper file

generation.

Page 31

Editors Chapter 3. Concepts

Advanced PLL Editor Port Names Page Options

Option Description

Input Ports

Name for Input ”refclk” The desired name for the reference clock input

signal in the generated RTL.

Name for Input ”fbclk” The desired name for the feedback clock input

signal in the generated RTL. This option is not

available when the PLL is in Pure Internal

Feedback Mode.

Phase inc[0-3] Input Port Name The desired name for the phase inc input signal

(for the appropriately numbered clock output) in

the generated RTL.

Output Ports

Clkout Output [0-3] Port Name The desired name for the PLL clock output in the

generated RTL.

Name for Output ”pll lock” The desired name for the PLL’s lock indication

output signal in the generated RTL.

19 http://www.achronix.com UG001 Rev. 5.0 - 5th December 2012

Page 32

Editors Chapter 3. Concepts

Basic PLL Configuration Editor

The Basic PLL Configuration Editor provides a simplified graphical wizard for creating a PLL configuration

file (.acxip). This editor allows the user to generate the required configuration files for design with the

embedded PLLs. See Creating an IP Configuration. Unlike the much more complicated Advanced PLL

Configuration Editor, the Basic PLL Configuration Editor allows the user to access only the most-often used

functionality of the PLL.

By default, the Basic PLL Configuration Editor is included in the IP Configuration perspective

(Window→Open Perspective→IP Configuration) ( ). The Basic PLL configuration information fits into a

single page.

Once the user has configured the PLL to meet their requirements, and the Basic PLL Configuration Editor

has determined that there are no errors in the configuration, the user may choose to generate their IP design

files (see Generating the IP Design Files).

NOTE:

IP Diagram

The IP Diagram View for the Basic PLL shows live information about the current configuration in the Editor,

including which logic blocks are currently active, which inputs and outputs are currently active, and what

the various frequencies are within the PLL. Additionally, configuration errors will be shown with a red

background, and configuration warnings will be shown with a yellow background (these are the default IP

Diagram colors, and may be modified in the Preferences).

The Basic PLL only supports Pure Internal Feedback Mode, and thus hides feedback path

modes from the user. This allows fractional feedback dividers (so any desired clkout0

output frequency is achievable), but prohibits deskew functionality. For simplification,

output phase adjustment is also disabled. If deskew or phase adjustment functionality are

required, the Advanced PLL must be used instead of the Basic PLL.

Figure 3.10: Example IP Diagram for PLL

UG001 Rev. 5.0 - 5th December 2012 http://www.achronix.com 20

Page 33

Editors Chapter 3. Concepts

Overview Page

The Overview page contains all the properties that govern the structure and configuration of the basic PLL.

Figure 3.11: Basic PLL IP Editor Overview Page

PLL Editor Overview Page Options

Option Editable

Target Device Y

Number of

Desired Clock

Outputs

Refclk Input

Frequency

(MHz)

21 http://www.achronix.com UG001 Rev. 5.0 - 5th December 2012

Y

Y

Description

The Speedster22i device this PLL is intended to target.

The number of desired clock output signals for this PLL.

Changing this will alter the number of active pages of Clock

Output configuration options.

The frequency of the PLL reference clock input.

Page 34

Editors Chapter 3. Concepts

clkout0 Desired

Frequency

Y

clkout0

Achieved