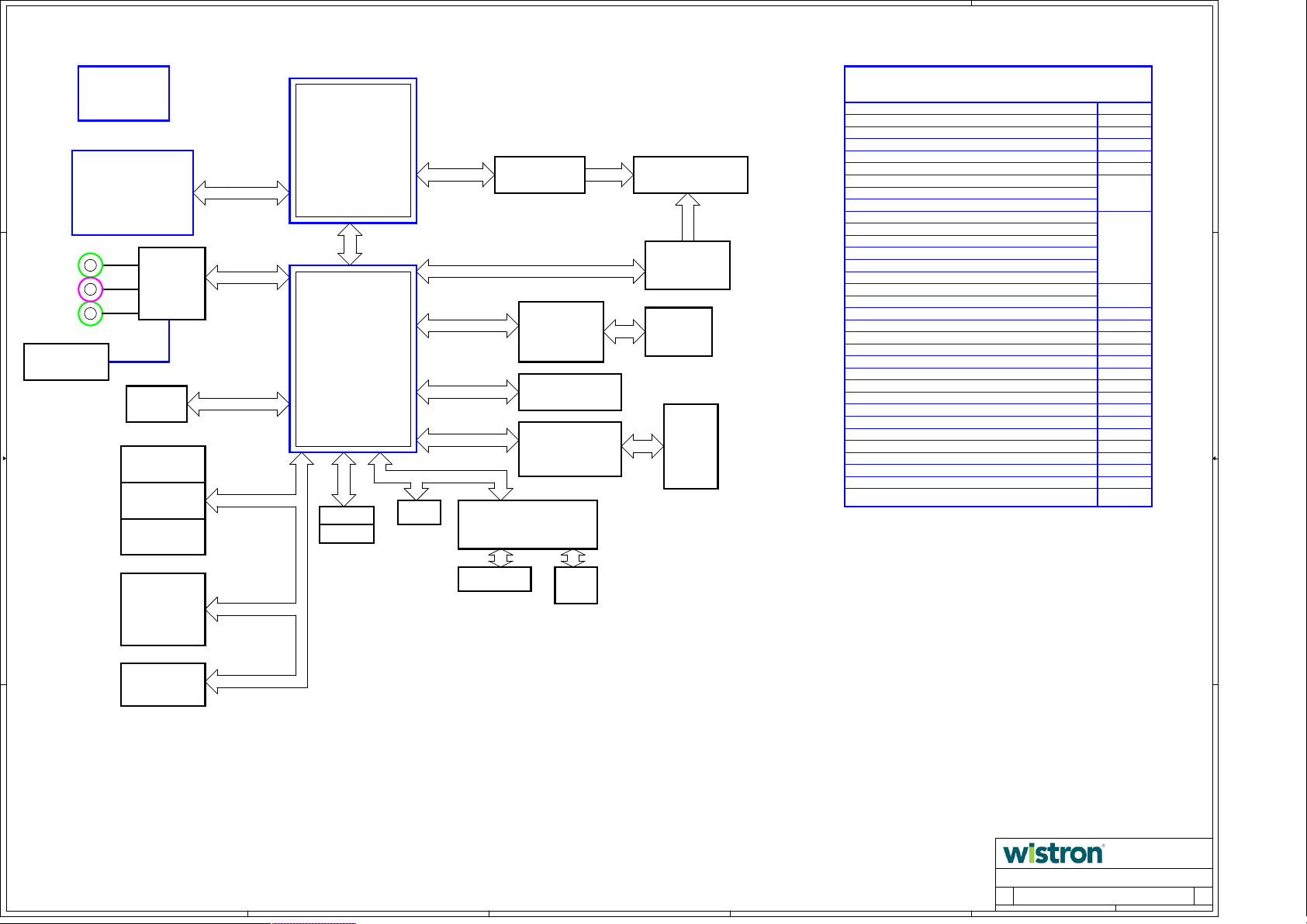

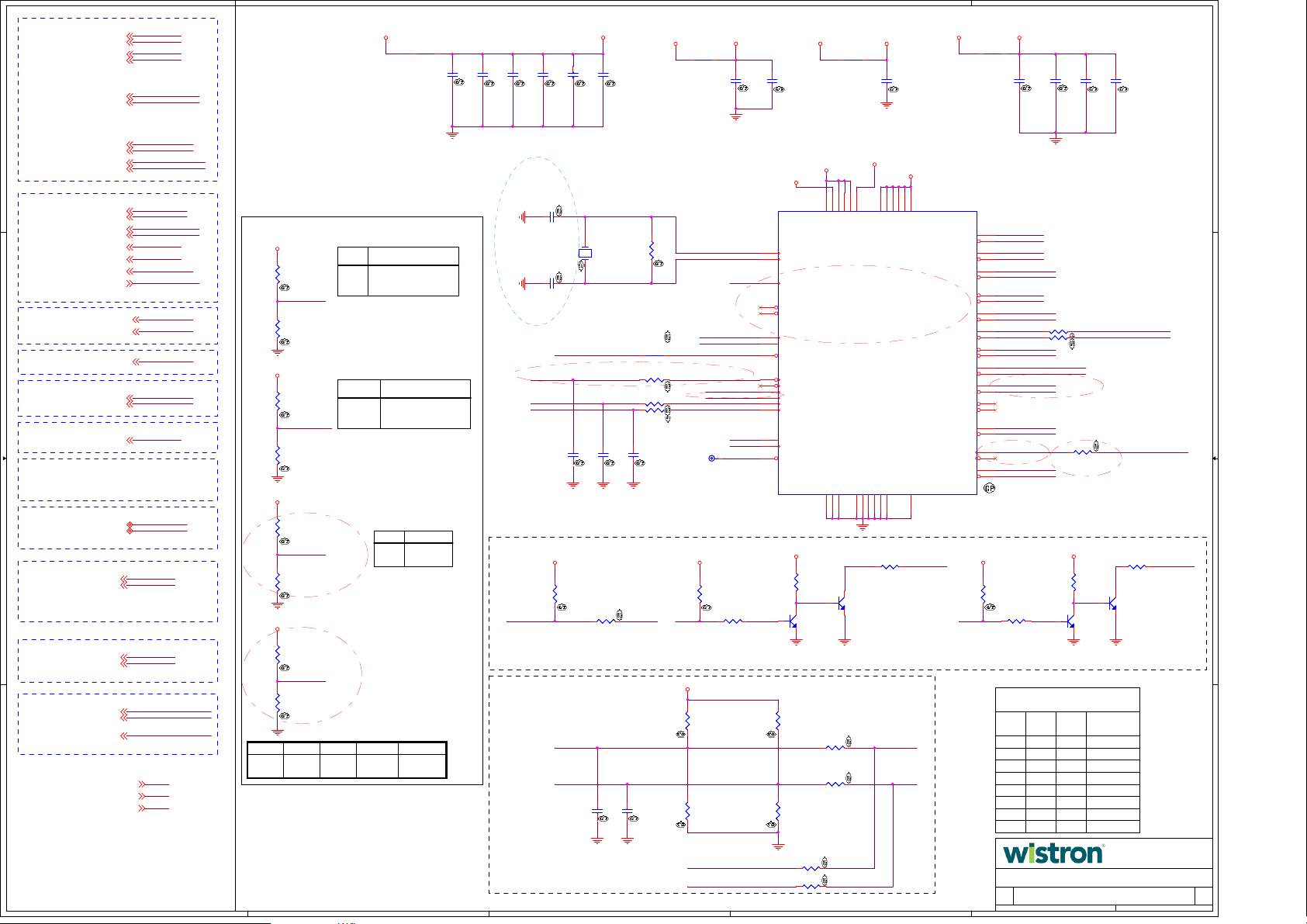

Acer Veriton Z291G, Emachines EZ171 Schematic

5

4

3

2

1

E/VMARR_Pine trail-D Block Diagram

Clock Generator

CK-505

RTM875N-606

D D

Intel

PINEVIEW-D

Atom D525

(1.8G 1M)

DDR3 800MHz

INTEGRATED GRAHPICS

LVDS

CRT I/F

DMI BUS

Intel

TIGERPOINT

USB 2.0 (2+2+2+2)

LAN Connect I/F (LCI)

AC97 2.3/Azalia Interface

Ultra ATA/100/66/33

Serial ATA 150MB/s

ACPI 2.0

LPC I/F

PCI Rev 2.3

PCI Express

INT. RTC

SATA

SATA1

SATA2

RGB CRT

PCI_E

PCI_E

PCI_E

PCI_E

LPC Bus / 33MHz

TPM

Line OUT

C

INTERNAL SPK

B

HP OUT

MIC IN

2W x 2

SINGLE CHANNEL 2 x

SO-DIMM

DDR3

Support memory type only

1R x8

2Rx16

AUDIO

CODEC

ALC269 VB2

Flash ROM

8Mb

INTERNAL

USB 0

(WEBCAM)

INTERNAL

USB 1 (TOUCH

PANEL)

INTERNAL

USB 2 (mini-PCIE

SLOT)

Rear IO

USB x 2

CONN(3,4)

USB x 1

CONN(5)

Side I/O

USB x 2

CONN(6,7)

SPI

Channel A

DDR3

HDA

USB 2.0

USB 2.0

USB 2.0

PI010L/Marr-AIO

BOARD NO: 09194-1

DATE: 2010/06/24

CPU FAN

SCALAR

Realtek RTD2270

Giga LAN

RTL 8111E

mini-PCIE SLOT X 1

Card Reader

Controller

JMB385

SIO

ITE IT8758E

PS2

KB/MS

LVDS

LCD Panel

LVDS

PCIE SLOT X 1

NVIDIA

GT218-ILV

Rear IO

RJ45 CONN.

SD

SDHC

MMC

MS

MS PRO

MS HG

BOM PARAMETER

G: GPU GT218-ILV

S: SCALAR RTD2270

A: SUPPORT ASF 2.0

N: Non SUPPORT ASF 2.0

R: Unmount

E: EUP

V: V-Marr

PAGE

TITLE

01

COVER PAGE

POWER DELIVERY CHART

02

CLOCK/RESET MAP

03

04

POWER MAP

05

GPIO TABLE

06

CLOCK GENERATOR

CPU PINEVIEW:DMI&EXP/ VGA/VSS

07

CPU PINEVIEW:DDR3

08

CPU PINEVIEW:LVDS/CPU SB/DEBUG

09

CPU PINEVIEW:POWER

10

11

DDR3 DIMMA & B

12

DDR3 DECOPULING

13

LVDS RTD2270

GPU NV GT218-ILV

14

15

TP DMI/ PCIE/ USB

TP HOST/ SATA

16

TP GPIO/ SPI/ LPC/ RTC

17

18

TP POWER/ GND

19

USB CONNECTOR

20

LAN_RTL8111E

21

AUDIO CODEC ALC269

SATA/ XPD-SSA/DEBUG PORT

22

23

SIO ITE8758/FAN/PS2 KBMS

MINI-PCIE SLOT

24

25

CARD READER JMB385C

19VDC POWER JACK

26

27

S5_1W/ LED/ HOLES

RT8205A_3V&5V

28

29

RT8209A_DDR1D5V/1D05V

30

RT8209A_GPU CORE

31

NCP5380_VCORE

EMARR_H: G, N

EMARR_L: S, N

VMARR: S, A, V

Quantity

Total:

D: D-SUB

C

B

A

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Sec.1,Hs in Tai Wu Rd

21F, 88, Sec.1,Hs in Tai Wu Rd

21F, 88, Sec.1,Hs in Tai Wu Rd

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

Title

Title

Title

COVER PAGE

COVER PAGE

COVER PAGE

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

AIO eMARR

AIO eMARR

AIO eMARR

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Hsichih, Taipei Hsien

of

131Tuesday, June 29, 2010

of

131Tuesday, June 29, 2010

of

1

131Tuesday, June 29, 2010

A

1A

1A

1A

5

Vinafix

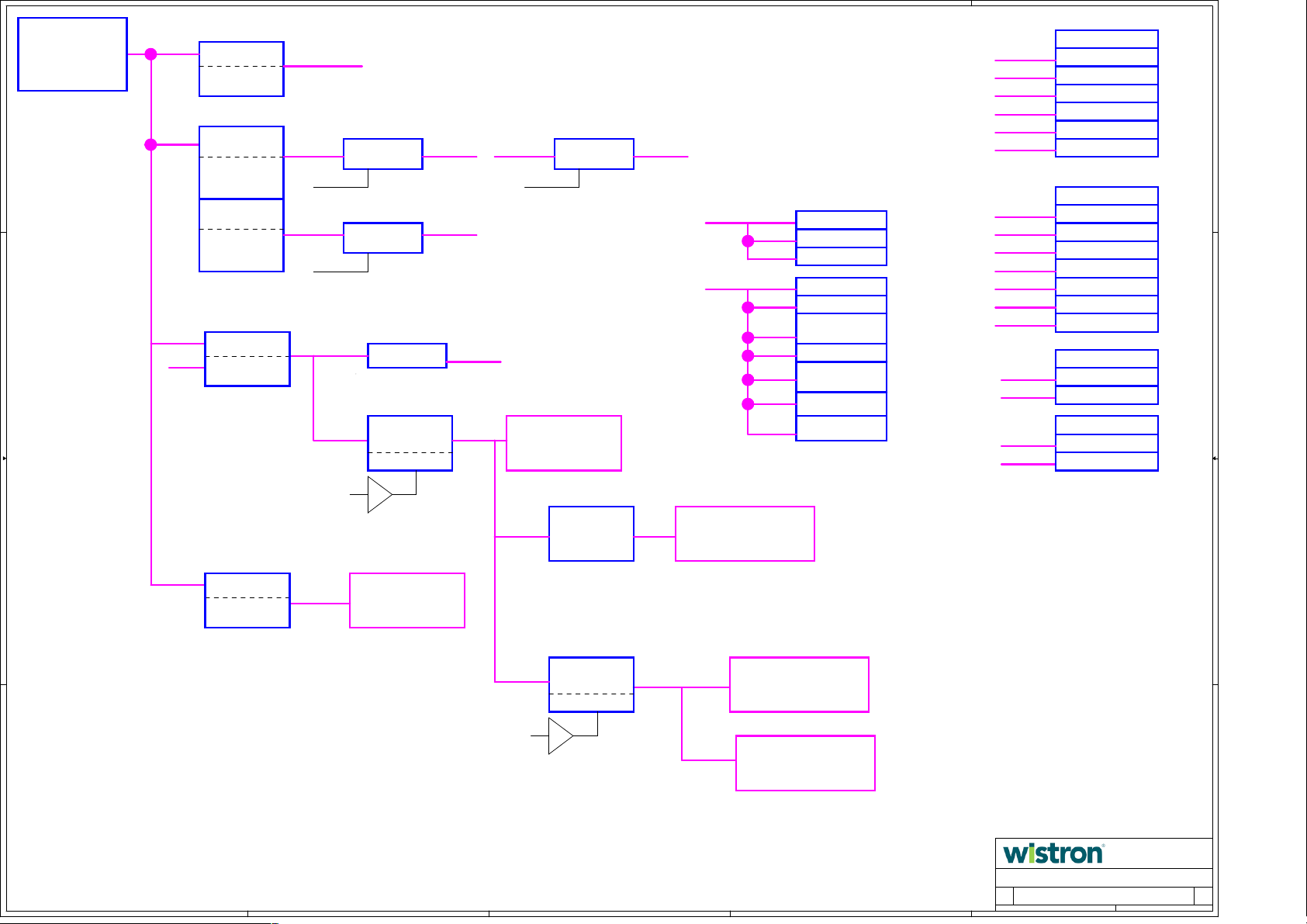

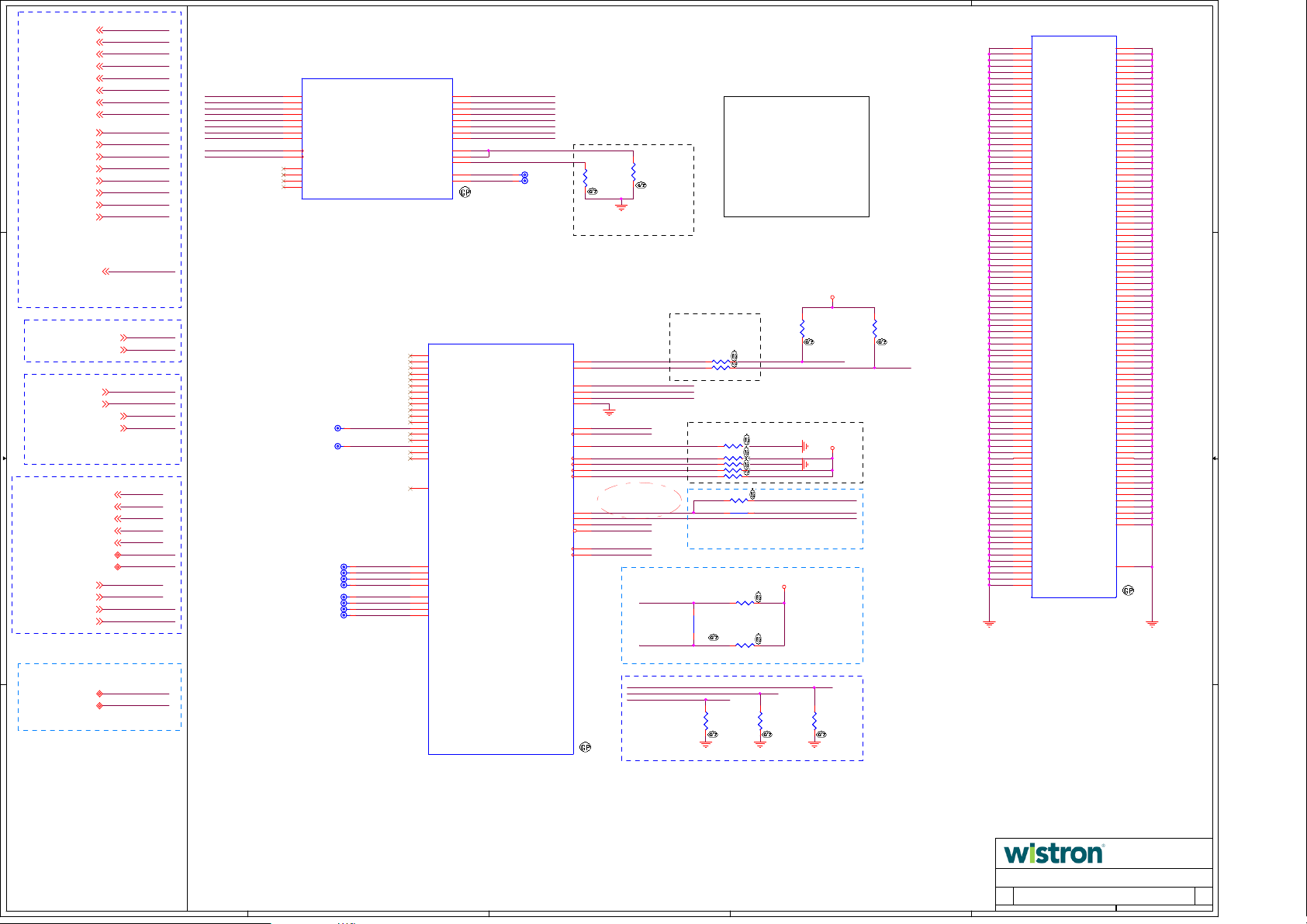

ADP_19V

ADP_19V

5V_S5

VCORE

+1.1V

(8A)

NCP5380

Phase 1

NTD4809N NMOS

TO-252 14m ohm

NTD4806N NMOS

TO-252 9.4m ohm

RT8205A

5V_S5

AO4468 NMOS

SO-8 22m ohm

AO4718 NMOS

SO-8 14m ohm

3D3V_S5

AO4468 NMOS

SO-8 22m ohm

AO4718 NMOS

SO-8 14m ohm

MEMORY POWER

+1.8V

RT8209A

NTD4809N NMOS

TO-252 14m ohm

NTD4806N NMOS

TO-252 9.4m ohm

VCORE

5V_S5

SLP_S3_N

3D3V_S5

SLP_S3_N

(18A)

VCC_MEM_1P5

POWER ADAPTER

DCBATOUT

ADP_19V

D D

C

4

VCC5

(6.5A)

AO4468

NMOS SO-8

14mohm 9.2A

VCC3_3

AO4468

NMOS SO-8

14mohm 9.2A

+0.9V

APL5336

LDO SO-8 1.5A

CORE POWER

+1.5V

AO4468

NMOS SO-8

14mohm 9.2A

(4A)

(1A)

OP

5V_S0

3D3V_S0

MEM_VTT

VCC5

5V_S5

SLP_S4_N

(2.5A)

NM10

V_1P5_CORE

AO4468

NMOS SO-8

14mohm 9.2A

3

VCC5_USB

5V_S0

3D3V_S0

CPU Fan

WEBCAM

Touch Panel (Option)

SIO ITE8755

LAN RTL8111E

CLK GEN

RTM875N-605

2

VCORE

V_1P05_CORE

VCCA

V_SM

V_1P8_PLLSFR

VCC_GIO

Vcc1.05V

Vcc1_5_V

VCC3_3

V5REF

VCCSus3_3

V5REF_Sus

VccRTC

BIOS ROM

1394/Card reader

VT6325

VCC_MEM_1P8

MEM_VTT

LVDS RTL2270

AUDIO ALC269

3D3V_S0

V_1P5_CORE

1

CPU

VCORE +1.1V 8A

V_1P05_CORE 5.34A

VCCA 1.5V 0.11A

V_SM 2.27A

V_1P8_PLLSFR 0.43A

VCC_GIO 0.01A

SB

Vcc1.05V 0.98A

Vcc1_5_V 1.41A

VCC3_3 0.29A

V5REF 0.006A

VCCSus3_3 0.13A

V5REF_Sus 0.01A

VccRTC 0.014A

DDR2 2 DIMM

V_SM 1.0A

V_SM_VTT 0.3A

Mini PCI Express Slot x 1

V_SM 1.0A

V_SM_VTT 0.3A

C

B

A

GT218 CORE POWER

0.9V

ADP_19V

NTD4809N NMOS

TO-252 14m ohm

NTD4806N NMOS

TO-252 9.4m ohm

RT8209A

(11.3A)

GPU GT218-ILV

V_0P9_CORE

AO4468

NMOS SO-8

14mohm 9.2A

(2A)

GPU GT218-ILV

V_1P5_MEM

B

+1.05V

AO4468

NMOS SO-8

14mohm 9.2A

V_1P05_CORE

OP

5

4

3

(6.5A)

NM10

V_1P05_CORE

(0.72A)

GPU GT218-ILV

V_1P05

A

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Sec.1,Hs in Tai Wu Rd

21F, 88, Sec.1,Hs in Tai Wu Rd

21F, 88, Sec.1,Hs in Tai Wu Rd

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

Title

Title

Title

POWER DELIVERY C HART

POWER DELIVERY C HART

POWER DELIVERY C HART

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

AIO eMARR

AIO eMARR

AIO eMARR

Date: Sheet

Date: Sheet

2

Date: Sheet

Hsichih, Taipei Hsien

1A

1A

1A

of

231Thursday, June 24, 2010

of

231Thursday, June 24, 2010

of

1

231Thursday, June 24, 2010

5

4

3

2

1

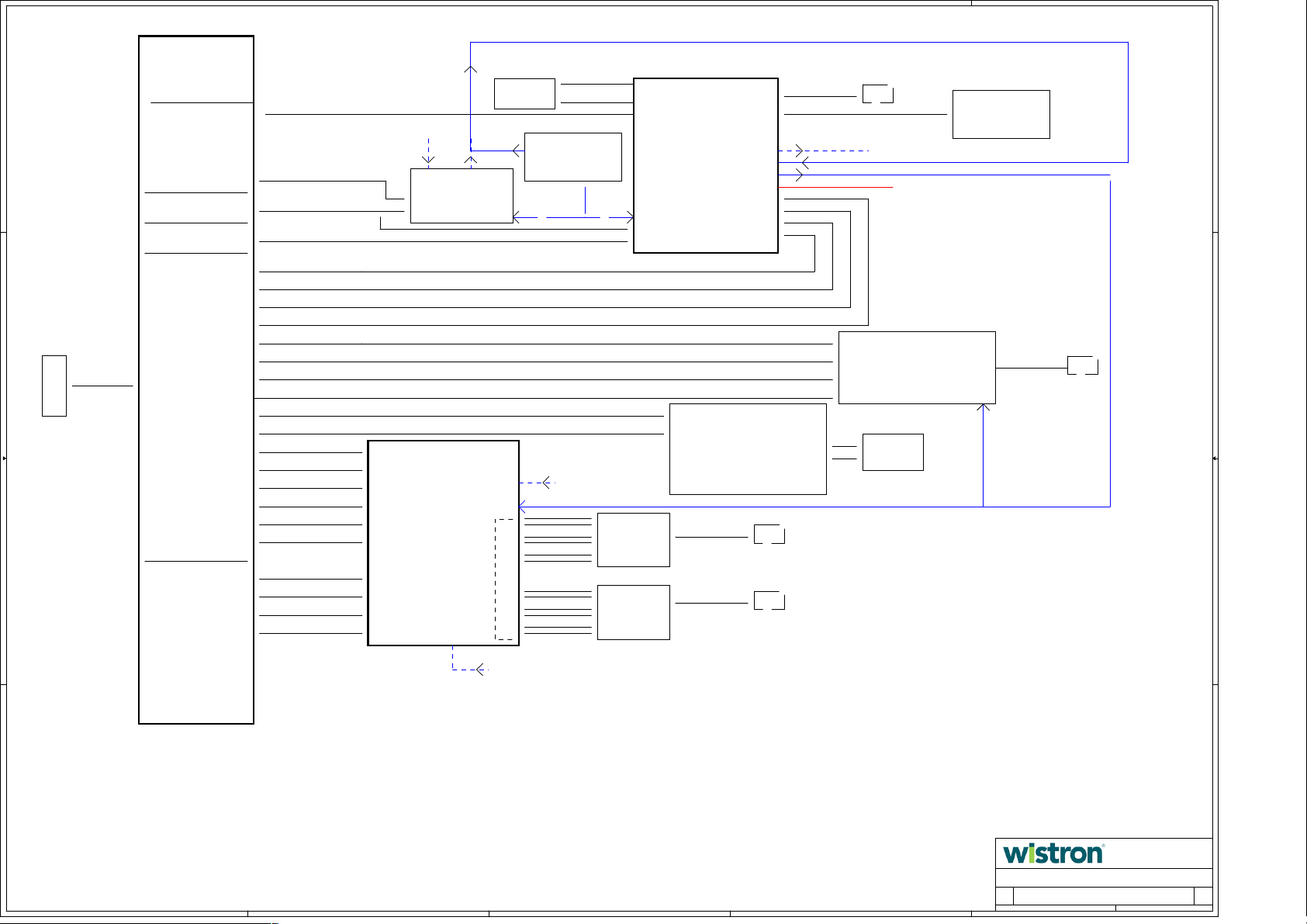

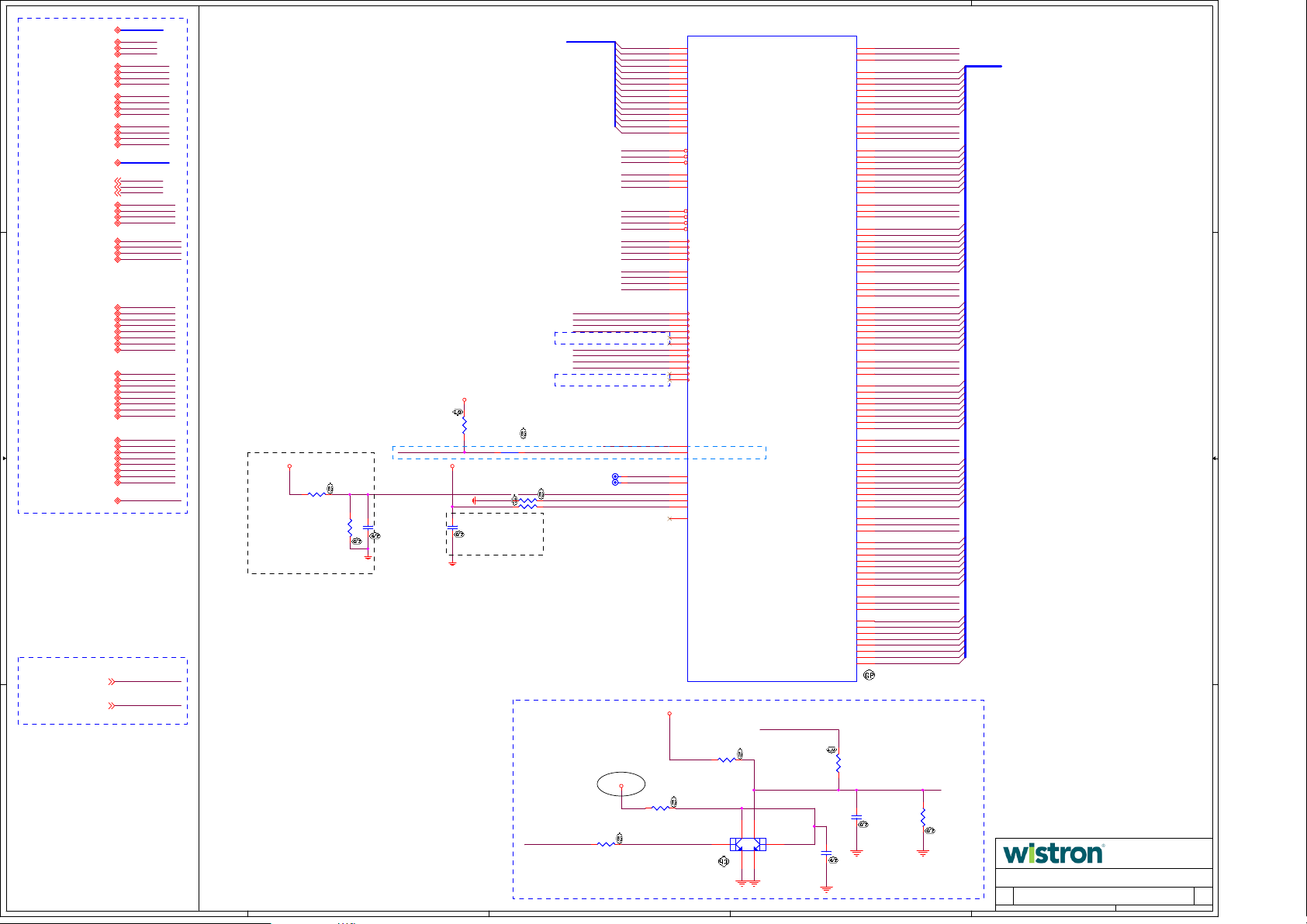

CK 505

3.3 VOLT

CK_PWRGD

CRYSTAL

D D

PCI

USB

REF

C

14.318 MHZ

SRC

CRYSTAL

B

HOST

PCIF5

33MHZ

PCI0

33MHZ

48MHZ

UCB48

14MHZ

REF

100MHZ

SRC2

100MHZ

SRC2*

100MHZ

SRC3

100MHZ

SRC3*

100MHZ

SRC5

100MHZ

SRC5*

100MHZ

SRC7

100MHZ

SRC7*

100MHZ

SRC6

100MHZ

SRC6*

96MHZ

SRC0

96MHZ

SRC0*

100MHZ

SRC1

100MHZ

SRC1*

100MHZ

SRC4

100MHZ

SRC4*

100/133/166/200 MHZ

CPU0*

100/133/166/200 MHZ

CPU0

100/133/166/200 MHZ

CPU1*

100/133/166/200 MHZ

CPU1

PLTRST_N

LRESET#

PCICLK

CLKIN

DPL_REFCLKINP

DPL_REFCLKINN

DPL_REFSSCLKINP

DPL_REFSSCLKINN

EXP_CLKINP

EXP_CLKINN

BCLKN

BCLKP

HPL_CLKINN

HPL_CLKINP

ICH_RSMRST_N

RSMRST#

SIO

PWROK PWROK

RSTIN#

CPUPWRGOOD

PNV

667/800

PWROK

32.768KHZ

32.768KHZ

GLUE LOGIC

PWRGD_3V

PWRGD_3V

PLTRST_N

H_PWRGD

RTCX1

RTCX2

PCICLK

TIGERTPOINT

CLK48

CLK14

CHAN A

DIMM0

CHAN A

DIMM1

REFCLKP

REFCLKN

SMBCLK

PLTRSTB

RSMRST#

24MHZ

ACZ_BCLK

CPUPWRGOOD

VRMPWRGD VCC3

DMICLK100N

DMICLK100P

SATACLKN

SATACLKP

SCLK

PLTRST_N

CK_100M_XDP_DP

CK_100M_XDP_DPN

XDP_H_CLK_DP

XDP_H_CLK_DN

LAN

RTL8111E

XTAL1

XTAL2

CRYSTAL

25MHZ

SCLK

SCLK

XDP_SSA

XDP_PWRGD

AUDIO CODEC

BCLK

SCLK

C

B

CPU_ITP*

CPU_ITP

A

5

100/133/166/200 MHZ

100/133/166/200 MHZ

4

PWRGD_3V

A

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Sec.1,Hs in Tai Wu Rd

21F, 88, Sec.1,Hs in Tai Wu Rd

21F, 88, Sec.1,Hs in Tai Wu Rd

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

Title

Title

Title

CLOCK/RESET MAP

CLOCK/RESET MAP

CLOCK/RESET MAP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

AIO eMARR

AIO eMARR

AIO eMARR

Date: Sheet

Date: Sheet

3

2

Date: Sheet

Hsichih, Taipei Hsien

1A

1A

1A

of

331Thursday, June 24, 2010

of

331Thursday, June 24, 2010

of

1

331Thursday, June 24, 2010

5

4

3

2

1

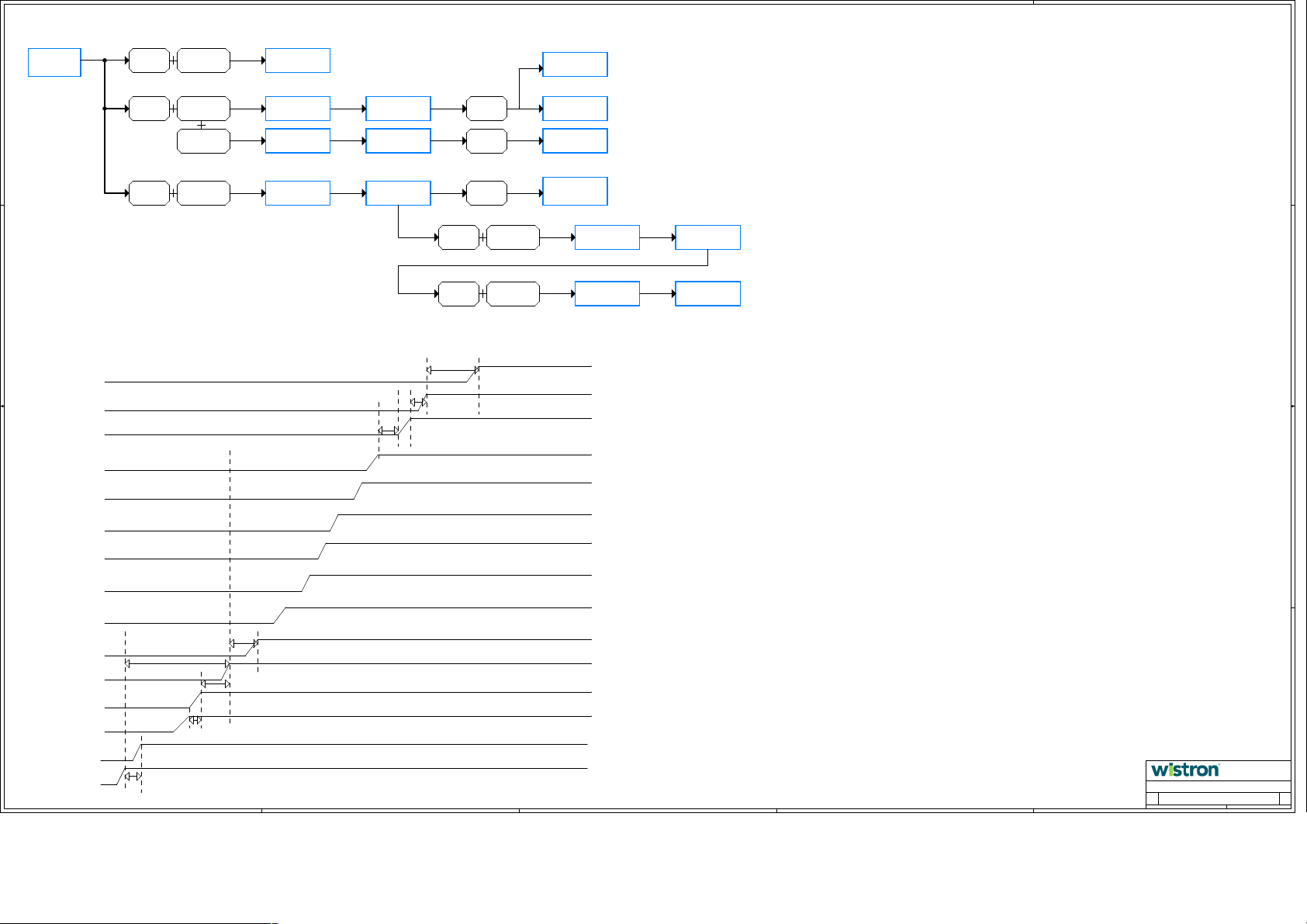

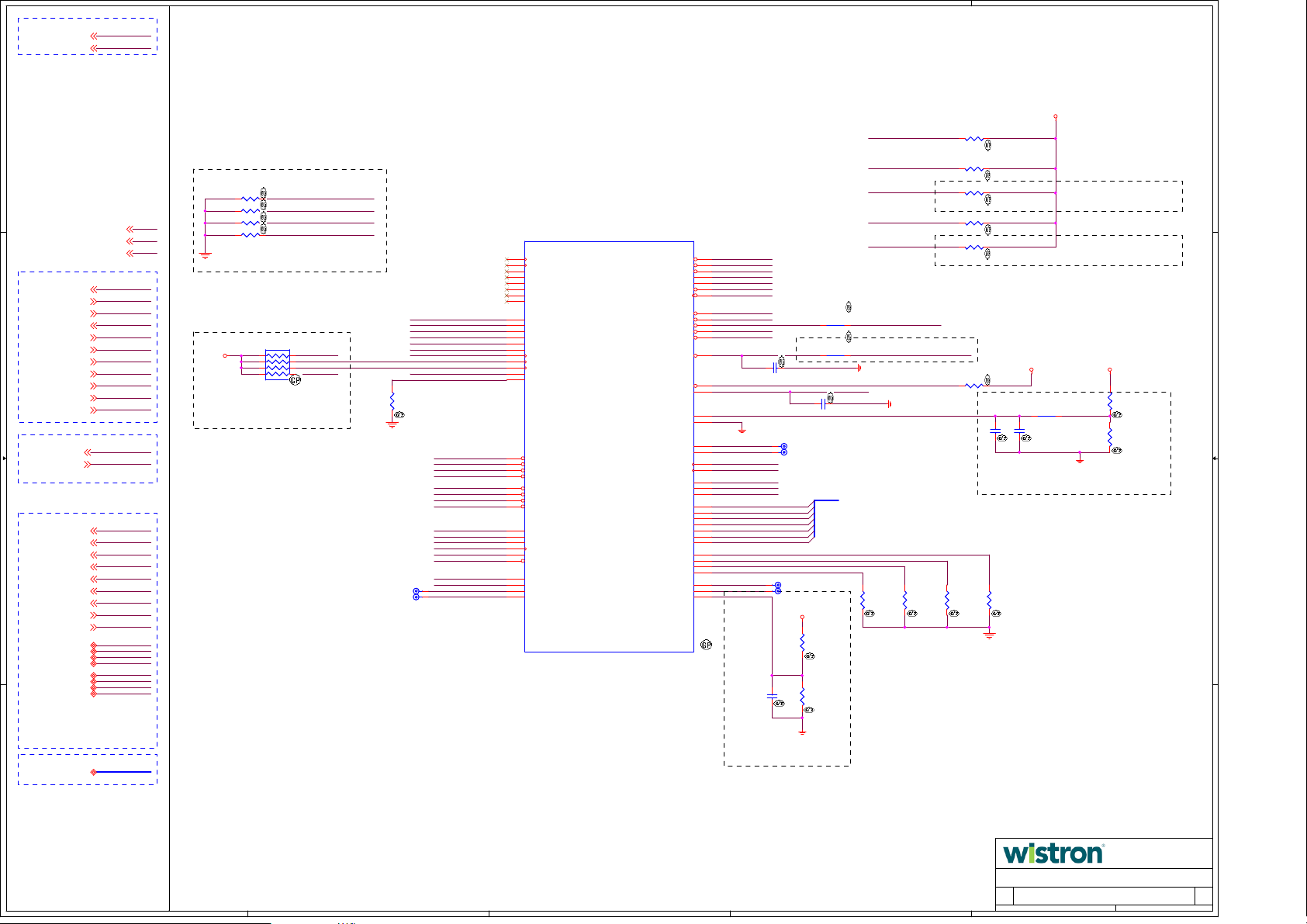

CPU POWER CONN

NTD4809*1

DC_19_IN

PWM

NCP5380

NTD4806*1

1 Phase Design

PWM

D D

AO4468*1 5V_S0

AO4718*1

RT8205A

AO4468*1

AO4718*1

1 Phase Design

NTD4809*1

PWM 1.8V

RT8209AGQW

NTD4806*1

1 Phase Design

VCORE

Imax=8A

5V_PWR

Imax=6.5A

3D3V_PWR

Imax=4A

Imax=17A

5V_S5

Imax=6.5A

3D3V_S5

Imax=4A

1D8V_S3

Imax=17A

N-MOS

AO4468

N-MOS 3D3V_S0

AO4468

LDO

APL5336

AO4468*1

OP

5V_USB

Imax=4.0A

Imax=6.5A

Imax=4A

VCC_MEM_1P8

MEM_VTT

Imax=1A

1.5V

Imax=2.5A

V_1P5_CORE

Imax=2.5A

AO4468*1

C

OP

1.05V

Imax=6.5A

V_1P05_CORE

Imax=6.5A

C

POWER ON SEQUENCE

PWROK

VRMOK

VCORE

110us

V_1P1_VTT

B

ICH1.5V

V_SM

+12/VCC/VCC3

SLP_S3_N

SLP_S4_N

RSMRST#

VccSus1_05

A

VccSus3_3

V5REF_Sus

0ms

0ms

10ms

0ms

99ms

20ms

B

A

RTCRST#

VccRTC

18ms

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

Hsichih, Taipe i Hsien

Hsichih, Taipe i Hsien

Title

Title

Title

RESET & POWER MAP

RESET & POWER MAP

RESET & POWER MAP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

D

D

D

AIO eMARR

AIO eMARR

AIO eMARR

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

1

Hsichih, Taipe i Hsien

431Thursday, June 24, 2010

431Thursday, June 24, 2010

431Thursday, June 24, 2010

1A

1A

1A

of

of

of

5

4

3

2

1

PCH TIGERPOINT

PIN

NAME

GPIO0

D D

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

C

GPIO16

GPIO17

GPIO18

GPIO19

GPIO20

GPIO21

GPIO22

GPIO23

GPIO24

GPIO25

GPIO26

GPIO27

GPIO28

GPIO29

B

GPIO30

GPIO31

GPIO32

GPIO33

GPIO34

GPIO35

GPIO36

GPIO37

GPIO38

GPIO39

GPIO40

GPIO41

GPIO42

GPIO43

GPIO44

A

GPIO45

GPIO46

GPIO47

GPIO48

GPIO49

PIN#

T15

C9

E8

D6

H8

F8

W16

W14

K18

H19

M17

E20

A24

C23

P5

E24

A2

C15

AA5

R3

C24

D19

D20

F22

E6

C2

C3

U14

AC1

AD23

AC23

AC24

G14

AB22

POWER

WELL

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

N/A

MAIN

N/A

N/A

N/A

N/A

MAIN

MAIN

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

N/A

MAIN

MAIN

N/A

MAIN

N/A

MAIN

MAIN

N/A

N/A

N/A

N/A

N/A

N/A

N/A

N/A

MAIN

CPU

5

USAGE

PANEL_DET

SPK_MUTE_N

P_INTE_N

P_INTF_N

P_INTG_N

P_INTH_N

W1_DETECT_N

W2_DETECT_N

PANEL_SEL1

PANEL_SEL2

PANEL_SEL3

SMB_ALERT_PU

P_GPIO12

PME_N

TS_RADY

P_GPIO15

P_GPIO17

Panel_FB

L_DRQ1_N

LAN_PWR_ON

TPEV_P_GPIO25

ISPWT_EN_R

SUSLED_N

PWRLED_N

–USB_OC57

–USB_OC36

–USB_OC57

W1_DISABLE_N

W2_DISABLE_N

AUTO_COLOR_SIO

TOUCH_EN

CAMERA_EN

P_GPIO48

H_PWRGD

Default

Type

I/O

I/O

I/OD

I/OD

I/OD

I/OD

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

N/A

I/O

N/A

N/A

N/A

N/A

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

N/A

I/O

I/O

N/A

I/O

N/A

I/O

I/O

N/A

N/A

N/A

N/A

N/A

N/A

N/A

N/A

I/O

I/O

DURING

RESET

4

Default

Setting

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

L

L

H

H

L

H

H

H

H

H

H

H

H

L

H

NOTES

Multiplexed with BM_BUSY#.

Unmultiplexed.

Multiplexed with PIRQ[H:E]#.

Multiplexed with PIRQ[H:E]#.

Multiplexed with PIRQ[H:E]#.

Multiplexed with PIRQ[H:E]#.

Unmultiplexed.

Unmultiplexed.

Unmultiplexed.

Unmultiplexed.

Unmultiplexed.

Multiplexed with SMBALERT#

Unmultiplexed.

Unmultiplexed.

Unmultiplexed.

Unmultiplexed.

Not Implemented

Multiplexed with BM_BUSY#.

Not Implemented

Not Implemented

Not Implemented

Not Implemented

Unmultiplexed.

Multiplexed with LDRQ1#

Unmultiplexed. Not cleared by CF9h reset event.

Unmultiplexed.

Unmultiplexed.

Unmultiplexed.

Unmultiplexed.

Multiplexed with OC5#

Multiplexed with OC6#

Multiplexed with OC7#

Not Implemented

Unmultiplexed.

Unmultiplexed.

Not Implemented

Unmultiplexed.

Not Implemented

Unmultiplexed.

Unmultiplexed.

Not Implemented.

Not Implemented.

Not Implemented.

Not Implemented.

Not Implemented.

Not Implemented.

Not Implemented.

Not Implemented.

Multiplexed with STRAP1#

Multiplexed with CPUPWRGD

7/9

3

S5 -> LAN_PWR_ON -> LOW

S4, S3, S0 -> LAN_PWR_ON -> HIGH

Title

Title

Title

GPIO TABLE

GPIO TABLE

GPIO TABLE

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

AIO eMARR

AIO eMARR

AIO eMARR

Date: Sheet

Date: Sheet

2

Date: Sheet

Wistron I ncorporat ed

Wistron I ncorporat ed

Wistron I ncorporat ed

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

21F, 88, Sec.1,Hsin Tai Wu Rd

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

of

531Thursday, June 24, 2010

of

531Thursday, June 24, 2010

of

531Thursday, June 24, 2010

1

1A

1A

1A

C

B

A

A

PINEVIEW

CK_H_MCH_DP7

CK_H_MCH_DN7

CK_H_CPU_DP9

CK_H_CPU_DN9

CK_PE_100M_MCH_DP7

CK_PE_100M_MCH_DN7

4 4

CK_96M_DREF_DP7

CK_96M_DREF_DN7

CK_DPL_REFSSCLKIN_DP7

CK_DPL_REFSSCLKIN_DN7

Tigerpoint

CK_ICHSATA_DP16

CK_ICHSATA_DN16

CK_PE_100M_ICH_DP15

CK_PE_100M_ICH_DN15

CK_P_33M_ICH15

CK_14M_ICH17

CK_48M_USB_ICH15

ICH_VRMPWRGD_PU17,31

SIO

3

SCALAR

LAN

CK_33M_SIO23

CK_48M_SIO23

CK_14M_SCALAR13

CLK_PCIE_LAN_DP20

CLK_PCIE_LAN_DN20

DebugPort

CLK_33_DBP22

XDP-SSA

SMBUS

SMB_DATA_MAIN11,13,17,24

SMB_CLK_MAIN11,13,17,24

MINI CARD

2

CLK_PCIE_MINI1_DP24

CLK_PCIE_MINI1_DN24

CARD READER JMB385C

CLK_PCIE_CR_DP25

CLK_PCIE_CR_DN25

GPU GT218

CLK_PCIE_GPU_DP14

CLK_PCIE_GPU_DN14

CK_GPU_27M14

Frequency select

1

CK_H_MCH_DP

CK_H_MCH_DN

CK_H_CPU_DP

CK_H_CPU_DN

CK_PE_100M_MCH_DP

CK_PE_100M_MCH_DN

CK_96M_DREF_DP

CK_96M_DREF_DN

CK_DPL_REFSSCLKIN_DP

CK_DPL_REFSSCLKIN_DN

CK_ICHSATA_DP

CK_ICHSATA_DN

CK_PE_100M_ICH_DP

CK_PE_100M_ICH_DN

CK_P_33M_ICH

CK_14M_ICH

CK_48M_USB_ICH

ICH_VRMPWRGD_PU

CLK_PCIE_LAN_DP

CLK_PCIE_LAN_DN

CLK_33_DBP

SMB_DATA_MAIN

SMB_CLK_MAIN

CLK_PCIE_MINI1_DP

CLK_PCIE_MINI1_DN

CLK_PCIE_CR_DP

CLK_PCIE_CR_DN

BSEL09

BSEL19

BSEL29

A

CK_33M_SIO

CK_48M_SIO

CK_14M_SCALAR

CLK_PCIE_GPU_DP

CLK_PCIE_GPU_DN

CK_GPU_27M

Clock Generator Strapping

3D3V_S0_CK505

12

R552

R552

10KR2J-3-GP

10KR2J-3-GP

PCI2_TME

12

R553

R553

10KR2J-3-GP

10KR2J-3-GP

(R)

(R)

3D3V_S0_CK505

1

R547

R547

10KR2J-3-GP

10KR2J-3-GP

2

SRC-5_EN/PCI-3

1

R551

R551

10KR2J-3-GP

10KR2J-3-GP

(R)

(R)

2

3D3V_S0_CK505

1

R544

R544

10KR2J-3-GP

10KR2J-3-GP

(R)

(R)

2009/12/28

2

ITP_EN

1

R554

R554

10KR2J-3-GP

10KR2J-3-GP

2

3D3V_S0_CK505

1

R546

R546

10KR2J-3-GP

10KR2J-3-GP

(G)

(G)

2

27_SEL

1

(S)

R555

R555

(S)

10KR2J-3-GP

10KR2J-3-GP

2

27_SEL PIN 20 PIN 21 PIN 24 PIN 25

0 DOT96 DOT96# SRC1 SRC1#

1 SRC0 SRC0 27M_NSS 27M_SS

B

PCI-2/

PIN3,4,5,6,7

TME

01Normal Operation

No Overclocking

SRC-5EN/

PIN29,30

PCI-3

01PCI STOP#/CPU_STOP#

SRC5

ITP_EN PIN38,39

0 SRC8

1 CPU_ITP

2009/11/21

B

R268

R268

0R0603-PAD

0R0603-PAD

1

C

3D3V_S0_CLKIO3D3V_S0

2

1

C381

C381

2

1

1

C383

C383

C376

C376

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

2

2

20100115

BSEL1

12

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

C373

C373

1

C374

C374

1

CLK_33_DBP

CK_33M_SIO

CK_P_33M_ICH

V_1P05_CORE

1

C382

C382

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

2

2009/11/09

2

SC27P50V2JN-2-GP

SC27P50V2JN-2-GP

2

SC27P50V2JN-2-GP

SC27P50V2JN-2-GP

ICH_VRMPWRGD_PU

1

EC6

EC6

2

1

R589

R589

2

470R2J-2-GP

470R2J-2-GP

CK_48M_USB_ICH

CK_14M_ICH

1

C139

C139

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

2

1

X5

X5

X-14D31818M-23GP

X-14D31818M-23GP

2

(23.30001.331)

(23.30001.331)

2010/04/02

1

(R)

(R)

SC4D7P50V2CN-1GP

SC4D7P50V2CN-1GP

2

R627

R627

1

1KR2J-1-GP

1KR2J-1-GP

1

EC8

EC8

2

EC5

EC5

(R)

(R)

SC4D7P50V2CN-1GP

SC4D7P50V2CN-1GP

C

3D3V_S0_CK505

C380

C380

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

1

(R)

(R)

R557

R557

1MR3J-L-GP

1MR3J-L-GP

2

R565

R565

1 2

0R0402-PAD-1-GP

0R0402-PAD-1-GP

R542 33R2J-2-GP

R542 33R2J-2-GP

2

1

R545 33R2J-2-GP

R545 33R2J-2-GP

1

2

R543 33R2J-2-GP

R543 33R2J-2-GP

1 2

1

EC4

EC4

(R)

(R)

(R)

(R)

TP47 TPAD28

12

SC4D7P50V2CN-1GP

SC4D7P50V2CN-1GP

2

FSB

47KR2J-2-GP

47KR2J-2-GP

EC7

EC7

(R)

(R)

SC4D7P50V2CN-1GP

SC4D7P50V2CN-1GP

R563

R563

33KR2J-3-GP

33KR2J-3-GP

TP47 TPAD28

BSEL0

3D3V_S0_CLKIO

R560

R560

(R)

(R)

SC4D7P50V2CN-1GP

SC4D7P50V2CN-1GP

2

R568

R568

0R0603-PAD

0R0603-PAD

1

SMB_CLK_MAIN

SMB_DATA_MAIN

V_1P05_CORE

1

R564

R564

2

1

2

1

2

CK_48M_SIO

CK_14M_SCALAR

3D3V_S0_CLKPLL

2

1

2

CLK_XTAL_IN

CLK_XTAL_OUT

CK_PWRGD_R

PCI0

PCI2_TME

SRC-5_EN/PCI-3

27_SEL

ITP_EN

CLKRESET-

R385

R385

470R2J-2-GP

470R2J-2-GP

1

4K7R2J-2-GP

4K7R2J-2-GP

C378

C378

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

FSA

FSB

FSC

RTM875N-606-VD-GRT-GP

RTM875N-606-VD-GRT-GP

BSEL0_2

2

47KR2J-2-GP

47KR2J-2-GP

33KR2J-3-GP

33KR2J-3-GP

3D3V_S0_CK505

12

C379

C379

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

3D3V_S0_CK505

3D3V_S0_CLKUSB

U25

U25

3

XIN

2

XOUT

17

FSLA/USB48

45

PCI_STOP#/SRC-5

44

CPU_STOP#/SRC-5#

7

SCLK

6

SDATA

63

CK_PWRGD/PD#

8

CR#_A/PCI-0

10

CR#_B/PCI-1

11

TME/PCI-2

12

SRC-5_EN/PCI-3

13

27M_SEL/PCI-4

14

ITP_EN/ PCIF-5

64

FSLB/TEST_MODE

5

FSLC/TEST_SEL/REF

55

RESET#

3D3V_S5

1

R556

R556

1KR2J-1-GP

1KR2J-1-GP

2

BSEL0_3

3

Q26

Q26

1

MMBT3904-7-F-GP

MMBT3904-7-F-GP

(84.03904.L06)

(84.03904.L06)

2

1

R540

R540

(R)

(R)

2

R332 22R2J-2-GPR332 22R2J-2-GP

R354 22R2J-2-GP

R354 22R2J-2-GP

R541

R541

12

R359 22R2J-2-GP

R359 22R2J-2-GP

1

R360 22R2J-2-GP

R360 22R2J-2-GP

1

D

3D3V_S0_CLKIO

56

33

VDD_CPU_IO

VDD_SRC_IO

SRC-8#/CPU_ITP#

GND

65

FSA

3D3V_S0

SRC-8/CPU_ITP

SRC-7/CR#_F

SRC-7#/CR#_E

CR#_H/SRC-11

CR#_G/SRC-11#

CR#_C/SRC-3

CR#_D/SRC-3#

SRC-2/SATA

SRC-2#/SATA#

SRC-1/SE1

SRC-1#/SE2

SRC-0/DOT96

SRC-0#/DOT96 #

3D3V_S0_CLKUSB

R264

R264

0R0603-PAD

0R0603-PAD

2

1

16

4

9

VDD_48

VDD_REF

GND_48

GND_PCI

1

18

15

1

1

1

2

(S)

(S)

2

3D3V_S0_CLKPLL

23

46

62

VDD_PCI

VDD_SRC

VDD_CPU

VDD_PLL3

GND_IO

GND_REF

22

30

BSEL0_4

3

Q49

Q49

MMBT3904-7-F-GP

MMBT3904-7-F-GP

(84.03904.L06)

(84.03904.L06)

2

2

2

D

GND_SRC

GND_SRC

49

36

1 2

1KR2J-1-GP

1KR2J-1-GP

1

C130

C130

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

2

19

52

27

43

VDD_IO

VDD_SRC_IO

VDD_SRC_IO

VDD_PLL3_IO

GND_SRC

GND_PLL3

GND_CPU

26

59

R422

R422

FSA

FSC

3D3V_S0_CK505

R265

R265

0R0603-PAD

0R0603-PAD

1

2

1

C133

C133

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

2

CK_H_CPU_DP

61

CPU-0

CK_H_CPU_DN

60

CPU-0#

CPU-1#

SRC-6#

SRC-10

SRC-10#

SRC-9#

SRC-4#

CK_H_MCH_DP

58

CPU-1

CK_H_MCH_DN

57

CK_PE_100M_ICH_DP

54

CK_PE_100M_ICH_DN

53

CLK_PCIE_LAN_DP

51

CLK_PCIE_LAN_DN

50

CLK_PCIE_MINI1_DP

48

SRC-6

CLK_PCIE_MINI1_DN

47

CK_DPL_REF_DP

41

42

40

39

37

SRC-9

38

34

SRC-4

35

31

32

28

29

24

25

20

21

V_1P05_CORE

1

R587

R587

2

BSEL2

4K7R2J-2-GP

4K7R2J-2-GP

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet of

1 2

CK_DPL_REF_DN

1

CK_PE_100M_MCH_DP

CK_PE_100M_MCH_DN

CLK_PCIE_GPU_DP

CLK_PCIE_GPU_DN

CLK_PCIE_CR_DP

CLK_PCIE_CR_DN

CK_ICHSATA_DP

CK_ICHSATA_DN

CK_GPU_27M_R

2009/11/17

CK_96M_DREF_DP

CK_96M_DREF_DN

R395

R395

1KR2J-1-GP

1KR2J-1-GP

R408

R408

470R2J-2-GP

470R2J-2-GP

BSEL2_2

2

1

CPU, MCH and XDP BCLK

FREQUENCY SELECTION TABLE

FSC

FSB

BSEL2

BSEL1

101

001

1

0

1

0

00

1

0

1

1

11

CLOCK GENERATOR

CLOCK GENERATOR

CLOCK GENERATOR

C

C

C

AIO eMARR

AIO eMARR

AIO eMARR

E

1

1

SC1U10V3ZY-6GP

SC1U10V3ZY-6GP

2

R569

0R2J-2-GP

0R2J-2-GP

0R2J-2-GP

0R2J-2-GP

2

R570

R570

(G)

(G)

2009/12/28

1

2

BSEL2_3

3

Q50

Q50

MMBT3904-7-F-GP

MMBT3904-7-F-GP

(84.03904.L06)

(84.03904.L06)

2

Host Clock

frequency MHz

12

C377

C377

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

(R)R569

(R)

CK_DPL_REFSSCLKIN_DP

CK_DPL_REFSSCLKIN_DN

(R)

(R)

BSEL2_4

3

1

2

C384

C384

2

2009/11/25

2009/11/25

R333 22R2J-2-GP

R333 22R2J-2-GP

1 2

3D3V_S5

1

FSA

BSEL0

100

133

166

1

200

0

266

0

333

0

400

0

Reserved

1

E

C132

C132

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

CK_GPU_27M

R394

R394

FSC

1

2

1KR2J-1-GP

1KR2J-1-GP

Q51

Q51

MMBT3904-7-F-GP

MMBT3904-7-F-GP

(84.03904.L06)

(84.03904.L06)

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Sec.1,Hs in Tai Wu Rd

21F, 88, Sec.1,Hs in Tai Wu Rd

21F, 88, Sec.1,Hs in Tai Wu Rd

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

631Thursday, June 24, 2010

of

631Thursday, June 24, 2010

of

631Thursday, June 24, 2010

1A

1A

1A

3

2

1

TPT

DMI_MCH_IT_MR_0_DP15

DMI_MCH_IT_MR_0_DN15

DMI_MCH_IT_MR_1_DP15

DMI_MCH_IT_MR_1_DN15

DMI_MCH_IT_MR_2_DP15

DMI_MCH_IT_MR_2_DN15

DMI_MCH_IT_MR_3_DP15

DMI_MCH_IT_MR_3_DN15

D D

DMI_MCH_MT_IR_0_DP15

DMI_MCH_MT_IR_0_DN15

DMI_MCH_MT_IR_1_DP15

DMI_MCH_MT_IR_1_DN15

DMI_MCH_MT_IR_2_DP15

DMI_MCH_MT_IR_2_DN15

DMI_MCH_MT_IR_3_DP15

DMI_MCH_MT_IR_3_DN15

PM_DPRSLPVR17

SIO

CLOCK

CK_PE_100M_MCH_DP6

CK_PE_100M_MCH_DN6

PWRGD_3V17

PLTRST_N14,17,22,23

CK_H_MCH_DN6

CK_H_MCH_DP6

C

VGA

HSYNC13

VSYNC13

VGA_RED13

VGA_GREEN13

VGA_BLUE13

MCH_DDC_DATA13

B

MCH_DDC_CLK13

CK_96M_DREF_DP6

CK_96M_DREF_DN6

CK_DPL_REFSSCLKIN_DP6

CK_DPL_REFSSCLKIN_DN6

5

DMI_MCH_IT_MR_0_DP

DMI_MCH_IT_MR_0_DN

DMI_MCH_IT_MR_1_DP

DMI_MCH_IT_MR_1_DN

DMI_MCH_IT_MR_2_DP

DMI_MCH_IT_MR_2_DN

DMI_MCH_IT_MR_3_DP

DMI_MCH_IT_MR_3_DN

DMI_MCH_MT_IR_0_DP

DMI_MCH_MT_IR_0_DN

DMI_MCH_MT_IR_1_DP

DMI_MCH_MT_IR_1_DN

DMI_MCH_MT_IR_2_DP

DMI_MCH_MT_IR_2_DN

DMI_MCH_MT_IR_3_DP

DMI_MCH_MT_IR_3_DN

PM_DPRSLPVR

PWRGD_3V

PLTRST_N

CK_PE_100M_MCH_DP

CK_PE_100M_MCH_DN

CK_H_MCH_DN

CK_H_MCH_DP

HSYNC

VSYNC

VGA_RED

VGA_GREEN

VGA_BLUE

MCH_DDC_DATA

MCH_DDC_CLK

CK_96M_DREF_DP

CK_96M_DREF_DN

CK_DPL_REFSSCLKIN_DP

CK_DPL_REFSSCLKIN_DN

DMI_MCH_IT_MR_0_DP

DMI_MCH_IT_MR_0_DN

DMI_MCH_IT_MR_1_DP

DMI_MCH_IT_MR_1_DN

DMI_MCH_IT_MR_2_DP

DMI_MCH_IT_MR_2_DN

DMI_MCH_IT_MR_3_DP

DMI_MCH_IT_MR_3_DN

CK_PE_100M_MCH_DN

CK_PE_100M_MCH_DP

F3

F2

H4

G3

K2

J1

M4

L3

N7

N6

R10

R9

N10

N9

TP4 TPAD28

TP4 TPAD28

TP3 TPAD28

TP3 TPAD28

U4A

U4A

DMI_RXP_0

DMI_RXN_0

DMI_RXP_1

DMI_RXN_1

DMI_RXP_2

DMI_RXN_2

DMI_RXP_3

DMI_RXN_3

EXP_CLKINN

EXP_CLKINP

RSVD#R10

RSVD#R9

RSVD#N10

RSVD#N9

PINEVIEW-1-GP

PINEVIEW-1-GP

(71.0ATOM.AHU)

(71.0ATOM.AHU)

TP43 TPAD28

TP43 TPAD28

TP40 TPAD28

TP40 TPAD28

TP32 TPAD28

TP32 TPAD28

TP33 TPAD28TP33 TPAD28

TP39 TPAD28

TP39 TPAD28

TP38 TPAD28

TP38 TPAD28

TP37 TPAD28

TP37 TPAD28

TP36 TPAD28

TP36 TPAD28

DIMM

PM_EXTTS0_N11

PM_EXTTS1_N11

PM_EXTTS0_N

PM_EXTTS1_N

4

TP_CPU_C10

TP_CPU_B10

TP_CPU_AA7

TP_CPU_AA6

TP_CPU_R5

TP_CPU_R6

TP_CPU_AA21

TP_CPU_W21

TP_CPU_T21

TP_CPU_V21

DMI_TXP_0

DMI_TXN_0

DMI_TXP_1

DMI_TXN_1

DMI_TXP_2

DMI_TXN_2

DMI_TXP_3

DMI_TXN_3

EXP_RCOMPO

EXP_ICOMPI

EXP_RBIAS

RSVD_TP#N11

RSVD_TP#P11

U4C

U4C

D12

XDP_RSVD_0

A7

XDP_RSVD_1

D6

XDP_RSVD_2

C5

XDP_RSVD_3

C7

XDP_RSVD_4

C6

XDP_RSVD_5

D8

XDP_RSVD_6

B7

XDP_RSVD_7

A9

XDP_RSVD_8

D9

XDP_RSVD_9

C8

XDP_RSVD_10

B8

XDP_RSVD_11

C10

XDP_RSVD_12

D10

XDP_RSVD_13

B11

XDP_RSVD_14

B10

XDP_RSVD_15

B12

XDP_RSVD_16

C11

XDP_RSVD_17

L11

RSVD#L11

AA7

RSVD_TP#AA7

AA6

RSVD_TP#AA6

R5

RSVD_TP#R5

R6

RSVD_TP#R6

AA21

RSVD_TP#AA21

W21

RSVD_TP#W21

T21

RSVD_TP#T21

V21

RSVD_TP#V21

PINEVIEW-1-GP

PINEVIEW-1-GP

(71.0ATOM.AHU)

(71.0ATOM.AHU)

1 OF 6

1 OF 6

G2

G1

H3

J2

K3

L2

M2

N2

L10

L9

L8

N11

P11

DMI_MCH_MT_IR_0_DP

DMI_MCH_MT_IR_0_DN

DMI_MCH_MT_IR_1_DP

DMI_MCH_MT_IR_1_DN

DMI_MCH_MT_IR_2_DP

DMI_MCH_MT_IR_2_DN

DMI_MCH_MT_IR_3_DP

DMI_MCH_MT_IR_3_DN

GIRCOMP

GRBIAS

TP_CPU_N11

TP_CPU_P11

PM_EXTTS#_0

TP35 TPAD28

TP35 TPAD28

TP34 TPAD28

TP34 TPAD28

3 OF 6

3 OF 6

CRT_HSYNC

CRT_VSYNC

CRT_RED

CRT_GREEN

CRT_BLUE

CRT_IRTN

CRT_DDC_DATA

CRT_DDC_CLK

DAC_IREF

DPL_REFCLKINP

DPL_REFCLKINN

DPL_REFSSCLKINP

DPL_REFSSCLKINN

RSVD#K29

RSVD#J30

PWROK

RSTIN#

HPL_CLKINN

HPL_CLKINP

M30

M29

N31

P30

P29

N30

L31

L30

P28

Y30

Y29

AA30

AA31

K29

J30

L5

AA3

W8

W9

1

2

3

12

R464

R464

49D9R2F-GP

R467

R467

750R3F-GP

750R3F-GP

49D9R2F-GP

FROM V0.7/ P15

NOTE: PCIE

COMP SIGNAL

TERMINATION

Hsync & Vsync level shift

PLACE 10 OHM CLOSE

TO CPU <750 MILS

R55

R55

10R2F-L-GP

HSYNC_L

VSYNC_LVSYNC_L

VGA_RED

VGA_GREEN

VGA_BLUE

MCH_DDC_DATAMCH_DDC_DATA

MCH_DDC_CLKMCH_DDC_CLK

DACREFSETDACREFSET

CK_96M_DREF_DPCK_96M_DREF_DP

CK_96M_DREF_DNCK_96M_DREF_DN

CK_DPL_REFSSCLKIN_DPCK_DPL_REFSSCLKIN_DP

CK_DPL_REFSSCLKIN_DNCK_DPL_REFSSCLKIN_DN

PM_DPRSLPVR_R

PWRGD_3V

PLTRST_N

CK_H_MCH_DN

CK_H_MCH_DP

2010/01/17

PM_EXTTS1_N

PM_EXTTS0_N

10R2F-L-GP

1 2

1

R61

R61

10R2F-L-GP

10R2F-L-GP

FROM V0.7 SCHEMATIC P15

NOTE: COLSE TO CPU <500MILS TO CPU BALL

R88 665R2F-2-GPR88 665R2F-2-GP

1 2

R97 10KR2J-3-GP(R)R97 10KR2J-3-GP

1

R92 10KR2J-3-GP(R)

R92 10KR2J-3-GP

1

R103 10KR2J-3-GP

R103 10KR2J-3-GP

1

R109 10KR2J-3-GPR109 10KR2J-3-GP

1 2

R969 0R2J-2-GP(R)

R969 0R2J-2-GP

1

R53 0R0402-PAD-1-GP

R53 0R0402-PAD-1-GP

1 2

10KR2J-3-GP

10KR2J-3-GP

(R)

(R)

12

R968

R968

0R0402-PAD-1-GP

0R0402-PAD-1-GP

(R)

(R)

10KR2J-3-GP

10KR2J-3-GP

VGA_RED

VGA_GREEN

VGA_BLUE

12

R85

R85

150R2J-L1-GP-U

150R2J-L1-GP-U

(R)

(R)

Layout: Please close to Pinview.

SIGNAL NAMING CONVENTION

DMI: DIRECT MEDIA INTERFACE

EXP: PCI EXPRESS

IRP: ICH RECEIVE POSITIVE

IRN: ICH RECEIVE NEGATIVE

MTP: MCH TRANSMIT POSITIVE

MRP: MCH RECEIVE POSITIVE

MRN: MCH RECEIVE NEGATIVE

MTN: MCH TRANSMIT NEGATIVE

ITP: ICH TRANSMIT POSITIVE

ITN: ICH TRANSMIT NEGATIVE

3D3V_S0

1

R56

R56

1KR2J-1-GP

1KR2J-1-GP

(R)

(R)

2

DY

DY

3D3V_S0

R76

R76

150R2J-L1-GP-U

150R2J-L1-GP-U

(R)

(R)

HSYNC

V_1P05_CORE

PM_DPRSLPVR

PM_EXTTS1_N

PM_EXTTS0_N

2010/05/05

2010/05/05

1

R65

R65

150R2J-L1-GP-U

150R2J-L1-GP-U

(R)

(R)

2

2

(R)

2

(R)

2

2

(R)

R95

R95

1

R98

R98

1 2

2

2

1

2

2

U4F

U4F

A11

VSS

A16

VSS

A19

VSS

A29

RSVD_NCTF#A29

A3

RSVD_NCTF#A3

A30

RSVD_NCTF#A30

A4

RSVD_NCTF#A4

AA13

VSS

AA14

VSS

AA16

VSS

AA18

VSS

AA2

VSS

AA22

VSS

AA25

VSS

AA26

VSS

AA29

VSS

AA8

VSS

AB19

VSS

AB21

VSS

AB28

VSS

AB29

VSS

AB30

VSS

AC10

VSS

AC11

VSS

AC19

VSS

AC2

VSS

AC21

VSS

AC28

VSS

AC30

VSS

AD26

VSS

AD5

VSS

AE1

VSS

AE11

VSS

AE13

VSS

AE15

VSS

AE17

VSS

AE22

VSS

AE31

VSS

AF11

VSS

AF17

VSS

AF21

VSS

AF24

VSS

AF28

VSS

AG10

VSS

12

R62

R62

1KR2J-1-GP

1KR2J-1-GP

(R)

(R)

VSYNC

DY

DY

AH18

AH23

AH28

AJ16

AJ31

AK23

AK30

AK31

AL13

AL19

AL23

AL29

AL30

AG3

AH4

AH6

AH8

AJ1

AK1

AK2

AL2

AL3

AL9

B13

B16

B19

B22

B30

B31

B5

B9

C1

C12

C21

C22

C25

C31

D22

E1

E10

E19

E21

E25

E8

F17

F19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

RSVD_NCTF#AJ1

VSS

VSS

RSVD_NCTF#AK1

RSVD_NCTF#AK2

VSS

RSVD_NCTF#AK30

RSVD_NCTF#AK31

VSS

VSS

RSVD_NCTF#AL2

VSS

RSVD_NCTF#AL29

RSVD_NCTF#AL3

RSVD_NCTF#AL30

VSS

VSS

VSS

VSS

VSS

RSVD_NCTF#B30

RSVD_NCTF#B31

VSS

VSS

RSVD_NCTF#C1

VSS

VSS

VSS

VSS

RSVD_NCTF#C31

VSS

RSVD_NCTF#E1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

PINEVIEW-1-GP

PINEVIEW-1-GP

(71.0ATOM.AHU)

(71.0ATOM.AHU)

1

6 OF 6

6 OF 6

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F24

F28

F4

G15

G17

G22

G27

G31

H11

H15

H2

H21

H25

H8

J11

J13

J15

J4

K11

K13

K19

K26

K27

K28

K30

K4

K8

L1

L13

L18

L22

L24

L25

L29

M28

M3

N1

N13

N18

N24

N25

N28

N4

N5

N8

P13

P14

P16

P18

P19

P21

P3

P4

R25

R7

R8

T11

U22

U23

U24

U27

V14

V16

V18

V28

V29

W13

W2

W23

W25

W26

W28

W30

W4

W5

W6

W7

Y28

Y3

Y4

T29

C

B

A

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Sec.1,Hs in Tai Wu Rd

21F, 88, Sec.1,Hs in Tai Wu Rd

21F, 88, Sec.1,Hs in Tai Wu Rd

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

Title

Title

Title

PINEVIEW:DMI&EXP/ VSS/ VGA

PINEVIEW:DMI&EXP/ VSS/ VGA

PINEVIEW:DMI&EXP/ VSS/ VGA

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

AIO eMARR

AIO eMARR

AIO eMARR

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet of

Hsichih, Taipei Hsien

of

731Thursday, June 24, 2010

of

731Thursday, June 24, 2010

1

731Thursday, June 24, 2010

A

1A

1A

1A

5

DIMM

M_MAA_A[14..0]11

M_SBS_A211

M_SBS_A111

M_SBS_A011

M_SCS_A_N311

M_SCS_A_N211

M_SCS_A_N111

M_SCS_A_N011

M_SCKE_A311

M_SCKE_A211

M_SCKE_A111

MISC

M_SCKE_A011

M_ODT_A311

M_ODT_A211

M_ODT_A111

M_ODT_A011

M_DATA_A[63..0]11

M_WE_A_N11

M_CAS_A_N11

M_RAS_A_N11

CK_M_DDR0_A_DP11

CK_M_DDR0_A_DN11

CK_M_DDR1_A_DP11

CK_M_DDR1_A_DN11

CK_M_DDR3_A_DP11

CK_M_DDR3_A_DN11

CK_M_DDR4_A_DP11

CK_M_DDR4_A_DN11

M_DQS_A_DP011

M_DQS_A_DP111

M_DQS_A_DP211

M_DQS_A_DP311

M_DQS_A_DP411

M_DQS_A_DP511

M_DQS_A_DP611

M_DQS_A_DP711

M_DQS_A_DN011

M_DQS_A_DN111

M_DQS_A_DN211

M_DQS_A_DN311

M_DQS_A_DN411

M_DQS_A_DN511

M_DQS_A_DN611

M_DQS_A_DN711

M_DQM_A011

M_DQM_A111

M_DQM_A211

M_DQM_A311

M_DQM_A411

M_DQM_A511

M_DQM_A611

M_DQM_A711

DDR_DRAM_RST_N11

SLP_S4_N17,23,28,29

8209A_PGOOD29

D D

C

B

A

M_MAA_A[14..0]

M_SBS_A2

M_SBS_A1

M_SBS_A0

M_SCS_A_N3

M_SCS_A_N2

M_SCS_A_N1

M_SCS_A_N0

M_SCKE_A3

M_SCKE_A2

M_SCKE_A1

M_SCKE_A0

M_ODT_A3

M_ODT_A2

M_ODT_A1

M_ODT_A0

M_DATA_A[63..0]

M_WE_A_N

M_CAS_A_N

M_RAS_A_N

CK_M_DDR0_A_DP

CK_M_DDR0_A_DN

CK_M_DDR1_A_DP

CK_M_DDR1_A_DN

CK_M_DDR3_A_DP

CK_M_DDR3_A_DN

CK_M_DDR4_A_DP

CK_M_DDR4_A_DN

M_DQS_A_DP0

M_DQS_A_DP1

M_DQS_A_DP2

M_DQS_A_DP3

M_DQS_A_DP4

M_DQS_A_DP5

M_DQS_A_DP6

M_DQS_A_DP7

M_DQS_A_DN0

M_DQS_A_DN1

M_DQS_A_DN2

M_DQS_A_DN3

M_DQS_A_DN4

M_DQS_A_DN5

M_DQS_A_DN6

M_DQS_A_DN7

M_DQM_A0

M_DQM_A1

M_DQM_A2

M_DQM_A3

M_DQM_A4

M_DQM_A5

M_DQM_A6

M_DQM_A7

DDR_DRAM_RST_N

SLP_S4_N

8209A_PGOOD

5

R138

R138

1KR2F-3-GP

1KR2F-3-GP

1

1KR2F-3-GP

CAD NOTE: PLACE R

CLOSE TO PINS ON

MCH_VREF

1KR2F-3-GP

4

1D5V_S3

2

R166

R166

10KR2J-3-GP

10KR2J-3-GP

(R)

(R)

1

R967 0R0402-PAD-1-GP

DDR_DRAM_RST_N

2

1

1

R136

R136

2

C76

C76

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

2

R967 0R0402-PAD-1-GP

1D5V_S31D5V_S3

12

C291

C291

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

CAD NOTE: PLACE C

CLOSE TO RPU

2

1

2010/01/17

R140 80D6R2F-L-GP

R140 80D6R2F-L-GP

1 2

R141 80D6R2F-L-GP

R141 80D6R2F-L-GP

2

1

FROM V_0.7 P 10

Base on Power rail

layout

SLP_S4_N

4

3

M_MAA_A[14..0]

CK_M_DDR0_A_DP

CK_M_DDR0_A_DN

CK_M_DDR1_A_DP

CK_M_DDR1_A_DN

CK_M_DDR3_A_DP

CK_M_DDR3_A_DN

CK_M_DDR4_A_DP

CK_M_DDR4_A_DN

TP42 TPAD28

TP42 TPAD28

TP41 TPAD28

TP41 TPAD28

R160 1KR2J-1-GP

R160 1KR2J-1-GP

DDR_DRAM_PWROK

DDR_DRAM_RST_R

1

3

M_MAA_A0

M_MAA_A1

M_MAA_A2

M_MAA_A3

M_MAA_A4

M_MAA_A5

M_MAA_A6

M_MAA_A7

M_MAA_A8

M_MAA_A9

M_MAA_A10

M_MAA_A11

M_MAA_A12

M_MAA_A13

M_MAA_A14

M_WE_A_N

M_CAS_A_N

M_RAS_A_N

M_SBS_A0

M_SBS_A1

M_SBS_A2

M_SCS_A_N0

M_SCS_A_N1

M_SCS_A_N2

M_SCS_A_N3

M_SCKE_A0

M_SCKE_A1

M_SCKE_A2

M_SCKE_A3

M_ODT_A0

M_ODT_A1

M_ODT_A2

M_ODT_A3

MCH_DDR_RPD

MCH_DDR_RPU

5V_S5

2

TP_CPU_AB11

TP_CPU_AB13

MCH_VREF

R167 1KR2J-1-GP

R167 1KR2J-1-GP

1

1D5V_S3

SLP_S4_N_BJT

AH19

AK18

AK16

AH14

AK14

AH13

AK12

AK20

AH12

AK22

AK21

AH20

AK11

AH22

AK25

AH10

AK10

AK24

AH26

AH24

AK27

AG15

AF15

AD13

AC13

AD17

AC17

AC15

AD15

AF13

AG13

AB15

AB17

AB11

AB13

AK28

AK29

AJ18

AJ14

AJ12

AJ11

AJ24

AJ10

AJ22

AJ20

AJ21

AJ25

AH9

AJ8

AB4

AK8

AL28

AJ26

2

U4B

U4B

DDR_A_MA_0

DDR_A_MA_1

DDR_A_MA_2

DDR_A_MA_3

DDR_A_MA_4

DDR_A_MA_5

DDR_A_MA_6

DDR_A_MA_7

DDR_A_MA_8

DDR_A_MA_9

DDR_A_MA_10

DDR_A_MA_11

DDR_A_MA_12

DDR_A_MA_13

DDR_A_MA_14

DDR_A_WE#

DDR_A_CAS#

DDR_A_RAS#

DDR_A_BS_0

DDR_A_BS_1

DDR_A_BS_2

DDR_A_CS#_0

DDR_A_CS#_1

DDR_A_CS#_2

DDR_A_CS#_3

DDR_A_CKE_0

DDR_A_CKE_1

DDR_A_CKE_2

DDR_A_CKE_3

DDR_A_ODT_0

DDR_A_ODT_1

DDR_A_ODT_2

DDR_A_ODT_3

DDR_A_CK_0

DDR_A_CK#_0

DDR_A_CK_1

DDR_A_CK#_1

DDR_A_CK_2

DDR_A_CK#_2

DDR_A_CK_3

DDR_A_CK#_3

DDR_A_CK_4

DDR_A_CK#_4

DDR_A_CK_5

DDR_A_CK#_5

VSS

DDR3_DRAMRST

RSVD#AK8

RSVD_TP#AB11

RSVD_TP#AB13

DDR_VREF

DDR_RPD

DDR_RPU

RSVD#AK29

PINEVIEW-1-GP

PINEVIEW-1-GP

(71.0ATOM.AHU)

(71.0ATOM.AHU)

R162 10KR2J-3-GP

R162 10KR2J-3-GP

2

1

6

3

5

1

4

8209A_PGOOD

DRAM_PWROK_BJT

2

Q13

Q13

MMDT3904-7-F-GP

MMDT3904-7-F-GP

2 OF 6

2 OF 6

DDR_A_DQS_0

DDR_A_DQS#_0

DDR_A_DM_0

DDR_A_DQ_0

DDR_A_DQ_1

DDR_A_DQ_2

DDR_A_DQ_3

DDR_A_DQ_4

DDR_A_DQ_5

DDR_A_DQ_6

DDR_A_DQ_7

DDR_A_DQS_1

DDR_A_DQS#_1

DDR_A_DM_1

DDR_A_DQ_8

DDR_A_DQ_9

DDR_A_DQ_10

DDR_A_DQ_11

DDR_A_DQ_12

DDR_A_DQ_13

DDR_A_DQ_14

DDR_A_DQ_15

DDR_A_DQS_2

DDR_A_DQS#_2

DDR_A_DM_2

DDR_A_DQ_16

DDR_A_DQ_17

DDR_A_DQ_18

DDR_A_DQ_19

DDR_A_DQ_20

DDR_A_DQ_21

DDR_A_DQ_22

DDR_A_DQ_23

DDR_A_DQS_3

DDR_A_DQS#_3

DDR_A_DM_3

DDR_A_DQ_24

DDR_A_DQ_25

DDR_A_DQ_26

DDR_A_DQ_27

DDR_A_DQ_28

DDR_A_DQ_29

DDR_A_DQ_30

DDR_A_DQ_31

DDR_A_DQS_4

DDR_A_DQS#_4

DDR_A_DM_4

DDR_A_DQ_32

DDR_A_DQ_33

DDR_A_DQ_34

DDR_A_DQ_35

DDR_A_DQ_36

DDR_A_DQ_37

DDR_A_DQ_38

DDR_A_DQ_39

DDR_A_DQS_5

DDR_A_DQS#_5

DDR_A_DM_5

DDR_A_DQ_40

DDR_A_DQ_41

DDR_A_DQ_42

DDR_A_DQ_43

DDR_A_DQ_44

DDR_A_DQ_45

DDR_A_DQ_46

DDR_A_DQ_47

DDR_A_DQS_6

DDR_A_DQS#_6

DDR_A_DM_6

DDR_A_DQ_48

DDR_A_DQ_49

DDR_A_DQ_50

DDR_A_DQ_51

DDR_A_DQ_52

DDR_A_DQ_53

DDR_A_DQ_54

DDR_A_DQ_55

DDR_A_DQS_7

DDR_A_DQS#_7

DDR_A_DM_7

DDR_A_DQ_56

DDR_A_DQ_57

DDR_A_DQ_58

DDR_A_DQ_59

DDR_A_DQ_60

DDR_A_DQ_61

DDR_A_DQ_62

DDR_A_DQ_63

2

1

1

C92

C92

2

SC1U10V3ZY-6GP

SC1U10V3ZY-6GP

2

AD3

AD2

AD4

AC4

AC1

AF4

AG2

AB2

AB3

AE2

AE3

AB8

AD7

AA9

AB6

AB7

AE5

AG5

AA5

AB5

AB9

AD6

AD8

AD10

AE8

AG8

AG7

AF10

AG11

AF7

AF8

AD11

AE10

AK5

AK3

AJ3

AH1

AJ2

AK6

AJ7

AF3

AH2

AL5

AJ6

AG22

AG21

AD19

AE19

AG19

AF22

AD22

AG17

AF19

AE21

AD21

AE26

AG27

AJ27

AE24

AG25

AD25

AD24

AC22

AG24

AD27

AE27

AE30

AF29

AF30

AG31

AG30

AD30

AD29

AJ30

AJ29

AE29

AD28

AB27

AA27

AB26

AA24

AB25

W24

W22

AB24

AB23

AA23

W27

R157

R157

10KR2J-3-GP

10KR2J-3-GP

(R)

(R)

1

2

(R)

(R)

2

M_DQS_A_DP0

M_DQS_A_DN0

M_DQS_A_DP1

M_DQS_A_DN1

M_DQS_A_DP2

M_DQS_A_DN2

M_DQS_A_DP3

M_DQS_A_DN3

M_DQS_A_DP4

M_DQS_A_DN4

M_DQS_A_DP5

M_DQS_A_DN5

M_DQS_A_DP6

M_DQS_A_DN6

DDR_DRAM_PWROK

C90

C90

SC1U10V3ZY-6GP

SC1U10V3ZY-6GP

M_DQM_A0

M_DATA_A0

M_DATA_A1

M_DATA_A2

M_DATA_A3

M_DATA_A4

M_DATA_A5

M_DATA_A6

M_DATA_A7

M_DQM_A1

M_DATA_A8

M_DATA_A9

M_DATA_A10

M_DATA_A11

M_DATA_A12

M_DATA_A13

M_DATA_A14

M_DATA_A15

M_DQM_A2

M_DATA_A16

M_DATA_A17

M_DATA_A18

M_DATA_A19

M_DATA_A20

M_DATA_A21

M_DATA_A22

M_DATA_A23

M_DQM_A3

M_DATA_A24

M_DATA_A25

M_DATA_A26

M_DATA_A27

M_DATA_A28

M_DATA_A29

M_DATA_A30

M_DATA_A31

M_DQM_A4

M_DATA_A32

M_DATA_A33

M_DATA_A34

M_DATA_A35

M_DATA_A36

M_DATA_A37

M_DATA_A38

M_DATA_A39

M_DQM_A5

M_DATA_A40

M_DATA_A41

M_DATA_A42

M_DATA_A43

M_DATA_A44

M_DATA_A45

M_DATA_A46

M_DATA_A47

M_DQM_A6

M_DATA_A48

M_DATA_A49

M_DATA_A50

M_DATA_A51

M_DATA_A52

M_DATA_A53

M_DATA_A54

M_DATA_A55

M_DQS_A_DP7

M_DQS_A_DN7

M_DQM_A7

M_DATA_A56

M_DATA_A57

M_DATA_A58

M_DATA_A59

M_DATA_A60

M_DATA_A61

M_DATA_A62

M_DATA_A63

1

2

R158

R158

0R2J-2-GP

0R2J-2-GP

(R)

(R)

1

M_DATA_A[63..0]

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Sec.1,Hs in Tai Wu Rd

21F, 88, Sec.1,Hs in Tai Wu Rd

21F, 88, Sec.1,Hs in Tai Wu Rd

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

Title

Title

Title

PINEVIEW: DDR2

PINEVIEW: DDR2

PINEVIEW: DDR2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

AIO eMARR

AIO eMARR

AIO eMARR

Date: Sheet

Date: Sheet of

Date: Sheet

Hsichih, Taipei Hsien

1

1A

1A

1A

of

831Thursday, June 24, 2010

831Thursday, June 24, 2010

of

831Thursday, June 24, 2010

C

B

A

CLOCK

6/22

5

CK_H_CPU_DN6

CK_H_CPU_DP6

CK_H_CPU_DN

CK_H_CPU_DP

4

3

2

1

D D

R370 1KR2J-1-GP

Frequency select

TPT

H_THERMTRIP_N16

H_SMI_N16

H_A20M_N16

H_FERR_N16

H_INTR16

C

H_NMI16

H_IGNNE_N16

H_STPCLK_N16

PM_DPRSTP_N17

H_DPSLP_N17

H_INIT_N16

SIO

CPU_THERMDA23

CPU_THERMDC23

XDP-SSA

H_PWRGD17

XDP_TESTIN_N22

H_TDI22

H_TDO22

B

H_TCK22

H_TMS22

H_TRST_N22

H_BPM4_PRDY_N22

H_BPM5_PREQ_N22

H_BPM_N022

H_BPM_N122

H_BPM_N222

H_BPM_N322

H_BPM_2_N022

H_BPM_2_N122

H_BPM_2_N222

H_BPM_2_N322

BSEL06

BSEL16

BSEL26

H_THERMTRIP_N

H_SMI_N

H_A20M_N

H_FERR_N

H_INTR

H_NMI

H_IGNNE_N

H_STPCLK_N

PM_DPRSTP_N

H_DPSLP_N

H_INIT_N

CPU_THERMDA

CPU_THERMDC

H_PWRGD

XDP_TESTIN_N

H_TDI

H_TDO

H_TCK

H_TMS

H_TRST_N

H_BPM4_PRDY_N

H_BPM5_PREQ_N

H_BPM_N0

H_BPM_N1

H_BPM_N2

H_BPM_N3

H_BPM_2_N0

H_BPM_2_N1

H_BPM_2_N2

H_BPM_2_N3

R370 1KR2J-1-GP

R358 1KR2J-1-GP

R358 1KR2J-1-GP

R416 1KR2J-1-GP

R416 1KR2J-1-GP

R421 1KR2J-1-GP

R421 1KR2J-1-GP

3D3V_S0

2

1

1 2

1 2

1

2

NOTE: MOUNT 1K OHM IF

NO LVDS

1

2

3

4 5

(R)

(R)

RN12

RN12

SRN2K2J-2-GP

SRN2K2J-2-GP

LDDC_DATA

8

7

6

LCTLA_CLK

LVD_VBG

LVD_IBG

LVD_VREFH_OUT_R

LVD_VREFL_OUT_R

4 OF 6

U4D

U4D

U25

LVD_A_CLKM

U26

LVD_A_CLKP

R23

LVD_A_DATAM_0

R24

LVD_A_DATAP_0

N26

LVD_A_DATAM_1

N27

LVD_A_DATAP_1

R26

LVD_A_DATAM_2

R27

LVD_IBG

LVD_VBG

LVD_VREFH_OUT_R

LVD_VREFL_OUT_R

LBKLT_EN

LBKLT_CTL

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

12

R374

R374

100KR2J-1-GP

100KR2J-1-GP

(R)

(R)

H_BPM_N0

H_BPM_N1

H_BPM_N2

H_BPM_N3

H_BPM_2_N0

H_BPM_2_N1

H_BPM_2_N2

H_BPM_2_N3

XDP_TESTIN_N

H_TDI

H_TDO

H_TCK

H_TMS

H_TRST_N

CPU_THERMDA

TP5 TPAD28

TP5 TPAD28

TP6 TPAD28TP6 TPAD28 R462

CPU_THERMDC

CPU2_THERMDA

CPU2_THERMDC

R22

J28

N22

N23

L27

L26

L23

K25

K23

K24

H26

G11

E15

G13

F13

B18

B20

C20

B21

G5

D14

D13

B14

C14

C16

D30

E30

C30

D31

PINEVIEW-1-GP

PINEVIEW-1-GP

(71.0ATOM.AHU)

(71.0ATOM.AHU)

LVD_A_DATAP_2

LVD_IBG

LVD_VBG

LVD_VREFH

LVD_VREFL

LBKLT_EN

LBKLT_CTL

LCTLA_CLK

LCTLB_CLK

LDDC_CLK

LDDC_DATA

LVDD_EN

BPM_1#_0

BPM_1#_1

BPM_1#_2

BPM_1#_3

BPM_2#_0

BPM_2#_1

BPM_2#_2

BPM_2#_3

RSVD#G5

TDI

TDO

TCK

TMS

TRST#

THRMDA_1

THRMDC_1

THRMDA_2

THRMDC_2

4 OF 6

A20M#

FERR#

LINT00

LINT10

IGNNE#

STPCLK#

DPRSTP#

DPSLP#

PRDY#

PREQ#

THERMTRIP#

PROCHOT#

CPUPWRGOOD

GTLREF

RSVD#L6

RSVD#E17

BCLKN

BCLKP

BSEL_0

BSEL_1

BSEL_2

VID_0

VID_1

VID_2

VID_3

VID_4

VID_5

VID_6

RSVD#L7

RSVD#D20

RSVD#H13

RSVD#D18

RSVD_TP#K9

RSVD_TP#D19

EXTBGREF

SMI#

INIT#

H_SMI_N

E7

H_A20M_N

H7

H_FERR_N

H6

H_INTR

F10

H_NMI

F11

H_IGNNE_N

E5

H_STPCLK_N

F8

PM_DPRSTP_N

G6

H_DPSLP_N

G10

H_SB_INIT_N

G8

H_BPM4_PRDY_N

E11

H_BPM5_PREQ_N

F15

H_SB_THERMTRIP_N

H_SB_THERMTRIP_N

E13

C18

W1

A13

H27

VSS

L6

E17

H10

J10

K5

H5

K6

H30

H29

H28

G30

G29

F29

E29

L7

D20

H13

D18

K9

D19

K7

C23 SC1U10V3ZY-6GP

C23 SC1U10V3ZY-6GP

H_PROCHOT_N_R

CPU_GTLREF

TP_HFPLL_1

TP_HFPLL_2

CK_H_CPU_DN

CK_H_CPU_DP

BSEL0

BSEL1

BSEL2

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

TPEV_H_DCLKPH_1

TPEV_H_DCLKPH_2

TPEV_H_ACLKPH_1

TPEV_H_ACLKPH_2

TP_CPU_K9

TP_CPU_D19

H_EXT_BGREF_1

C268

C268

SC1U10V3ZY-6GP

SC1U10V3ZY-6GP

R426 0R0402-PAD-1-GP

R426 0R0402-PAD-1-GP

R31 0R0402-PAD-1-GP

R31 0R0402-PAD-1-GP

1 2

C281 SC1U10V3ZY-6GP

C281 SC1U10V3ZY-6GP

TP30TPAD28

TP30TPAD28

TP25TPAD28

TP25TPAD28

V_1P05_CORE

1

R451

R451

976R2F-3-GP

976R2F-3-GP

2

1

1

2

2

1 2

NOTE: PLACE NEAR TO TIGERPOINT

1

1

TP31TPAD28

TP31TPAD28

TP29TPAD28

TP29TPAD28

H_VID[6..0]

R458

R458

3K32R2F-GP

3K32R2F-GP

H_PWRGD

2

2

1

2

H_PWRGD

PM_DPRSTP_N

H_FERR_N

H_DPSLP_N

H_SB_THERMTRIP_N

12

R36

R36

1KR2F-3-GP

1KR2F-3-GP

(R)

(R)

H_INIT_N

H_THERMTRIP_N

R462

1KR2F-3-GP

1KR2F-3-GP

(R)

(R)

(R)

(R)

R469 1KR2F-3-GP

R469 1KR2F-3-GP

2

1

(R)

(R)

R431 1KR2F-3-GP

R431 1KR2F-3-GP

1

2

R430 56R2J-4-GP

R430 56R2J-4-GP

1 2

(R)

(R)

R427 1KR2F-3-GP

R427 1KR2F-3-GP

2

1

R30 56R2J-4-GP

R30 56R2J-4-GP

1

2

R37 1KR2F-3-GP

R37 1KR2F-3-GP

2

1

1

C25

C25

SC220P50V2KX-3GP

SC220P50V2KX-3GP

1

2

2

(R)

(R)

DESIGN CAD: PLACE NEAR TO CPU < 1500 MILS

12

R38

R38

R428

R428

1KR2F-3-GP

1KR2F-3-GP

(R)

(R)

1KR2F-3-GP

1KR2F-3-GP

(R)

(R)

V_1P05_CORE

CAD NOTE: PLACE R NEAR TO

TIGER POINT

CAD NOTE: PLACE R NEAR TO

PINEVIEW

V_1P05_CORE

R28

R28

0R0402-PAD

0R0402-PAD

CPU_GTLREF_R

1

2

1

C17

C17

SC1U10V3ZY-6GP

SC1U10V3ZY-6GP

2

V_1P05_CORE

12

R17

R17

1KR2F-3-GP

1KR2F-3-GP

1

R24

R24

2KR2F-3-GP

2KR2F-3-GP

2

C

B

VCCP VREG CONTROLLER

H_VID[6..0]31

A

H_VID[6..0]

CAD NOTE:GTLREF MAX TRACE

LENGTH OF 500 MIL AND 5 MIL

SPACING

A

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Sec.1,Hs in Tai Wu Rd

21F, 88, Sec.1,Hs in Tai Wu Rd

21F, 88, Sec.1,Hs in Tai Wu Rd

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

Title

Title

Title

PINEVIEW: LVDS/ CPU SB/DEBUG

PINEVIEW: LVDS/ CPU SB/DEBUG

PINEVIEW: LVDS/ CPU SB/DEBUG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

AIO eMARR

AIO eMARR

AIO eMARR

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet of

Hsichih, Taipei Hsien

1A

1A

931Thursday, June 24, 2010

931Thursday, June 24, 2010

1

931Thursday, June 24, 2010

1A

of

of

5

4

3

2

1

VCCP VERG CONTROLLER

SLP_S3_N17,23,28,29,30

VCC_SENSE_CPU_SKT

VSS_SENSE_CPU_SKT

SLP_S3_N

1D5V_S3

1

2

V_1P05_CORE

C294

C294

R472

R472

1

2

0R0805-PAD-1-GP

0R0805-PAD-1-GP

DESIGN NOTE:

EDGE CAP FOR VCCGFX

MEMORY DECOUPLING

DESIGN NOTE :

EDGE CAP/ DECOUPLING FOR VCC_DDR

1

1

C290

C290

SC2D2U10V3KX-1GP

SC2D2U10V3KX-1GP

SC2D2U10V3KX-1GP

SC2D2U10V3KX-1GP

2

2

DESIGN NOTE: FOR DEBUG

PURPOSES

V_1P8_PLLSFR

L6 HCB1608KF-601T 10-GP

L6 HCB1608KF-601T 10-GP

1 2

C60 SC1U10V3KX-3GP(R)

C60 SC1U10V3KX-3GP(R)

1 2

1

V_1P8_PLLSFR

L3 HC B1608KF-601T10-GP

L3 HC B1608KF-601T10-GP

1

BOM NOTE: DEFAULT

DESIGN NOTE:

EDGE CAP FOR

VCCA_DDR,VCCACK_DDR,VCCD_HMPL,VCCD_AB_DPL

V_1P05_CORE

12

C259

C259

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

(78.10620.51L)

(78.10620.51L)

(R)

(R)

C293

C293

SC2D2U10V3KX-1GP

SC2D2U10V3KX-1GP

C65

C65

1

C32

C32

2

(78.10620.51L)

(78.10620.51L)

2010/01/17

2

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

1

C292

C292

SC2D2U10V3KX-1GP

SC2D2U10V3KX-1GP

2

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

2

12

C4

C4

SC4D7U10V3KX-GP

SC4D7U10V3KX-GP

5 OF 6

U4E

U4E

DESIGN NOTE:

DMI STITCHING CAP

V_1P05_PCIEXPRESS

12

12

C273

C273

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

1D5V_S3

1

2

C276

C276

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

1 2

L30

L30

FCM1608KFG-301T05-GP

FCM1608KFG-301T05-GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C47

C47

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

DESIGN NOTE:

VCCRING_EAST EDGE CAP

DEFENSIVE DESIGN

12

C279

C279

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

V_1P05_CORE

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

C282

C282

1

1

C278

C278

C275

C275

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

2

2

1

C296

C296

2

1 2

L29

L29

HCB1608KF-601T10-GP

HCB1608KF-601T10-GP

2009/11/30

R470

R470

1

0R0603-PAD-1-GP

0R0603-PAD-1-GP

DESIGN NOTE:

VCC_LGI_VID EDGE CAP

DEFENSIVE DESIGN

12

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

VCCCK_DDR

1

2

2

C285

C285

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

2

V_1P05_COREV_1P05_CORE

1

C274

C274

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

2

C295

C295

SCD1U10V2MX-3GP

SCD1U10V2MX-3GP

V_1P05_CORE

VCC_AB_DPL

1

(R)

(R)

VCC_HMPL

VCCSFR_AB_DPL

VCCACRTDAC_M

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

C284

C284

(R)

(R)

C277

C277

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

1D5V_S3

3D3V_S0

AK13

AK19

AA10

AA11

AA19

AC31

T13

T14

T16

T18

T19

V13

V19

W14

W16

W18

W19

AK9

AL11

AL16

AL21

AL25

AK7

AL7

U10

U5

U6

U7

U8

U9

V2

V3

V4

W10

W11

V11

T30

T31

J31

C3

B2

C2

A21

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCCK_DDR

VCCCK_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCACK_DDR

VCCACK_DDR

VCCD_AB_DPL

VCCD_HMPLL

VCCSFR_AB_DPL

VCCACRTDAC

VCC_GIO

VCCRING_EAST

VCCRING_WEST

VCCRING_WEST

VCCRING_WEST

VCC_LGI_VID

PINEVIEW-1-GP

PINEVIEW-1-GP

(71.0ATOM.AHU)

(71.0ATOM.AHU)

5 OF 6

VCCSENSE

VSSSENSE

VCCA

VCCP

VCCP

VCCALVD

VCCDLVD

VCCA_DMI

VCCA_DMI

VCCA_DMI

RSVD#P2

VCCSFR_DMIHMPLL

VCCP

A23

VCC

A25

VCC

A27

VCC

B23

VCC

B24

VCC

B25

VCC

B26

VCC

B27

VCC

C24

VCC

C26

VCC

D23

VCC

D24

VCC

D26

VCC

D28

VCC

E22

VCC

E24

VCC

E27

VCC

F21

VCC

F22

VCC

F25

VCC

G19

VCC

G21

VCC

G24

VCC

H17

VCC

H19

VCC

H22

VCC

H24

VCC

J17

VCC

J19

VCC

J21

VCC

J22

VCC

K15

VCC

K17

VCC

K21

VCC

L14

VCC

L16

VCC

L19

VCC

L21

VCC

N14

VCC

N16

VCC

N19

VCC

N21

VCC

C29

B29

Y2

D4

VCC

B4

B3

V30

W31

T1

T2

T3

P2

AA1

E2

VCC_SENSE_CPU_SKT31

VSS_SENSE_CPU_SKT31

MISC

D D

C

B

VCC_SENSE_CPU_SKT

VSS_SENSE_CPU_SKT

V_1P05_CORE

VCCALVD_R

VCCDLVD_R

VCCA_DMI

V_1P05_CORE

VCORE

NOTE: DECOUPLING FOR PROCESSOR CORE

VOLTAGE

1

C15

C15

SC1U10V3ZY-6GP

SC1U10V3ZY-6GP

2

1

C20

C20

SC1U10V3ZY-6GP

SC1U10V3ZY-6GP

2

2009/11/20

VCCA_DMI (This circuit is defensive

design for Pineview A0 only, you don’t

need it for currently B0 state)

V_1P5_CORE

1

C286

C286

SCD1U10V2MX-3GP

SCD1U10V2MX-3GP

2

Pull- down : Pineview's

LVDS unmount

6/22

R87 0R0402-PAD

R87 0R0402-PAD

1

R90 0R0402-PAD

R90 0R0402-PAD

1 2

VCCA_DMI

(R)

(R)

2

(R)

(R)

VCCAPLL_DMI

1

C19

C19

SC1U10V3ZY-6GP

SC1U10V3ZY-6GP

2

HCB1608KF-601T10-GP

HCB1608KF-601T10-GP

1

2

12

C14

C14

SC1U10V3ZY-6GP

SC1U10V3ZY-6GP

C287

C287

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

DESIGN NOTE:

EDGE CAP FOR

VCCRING,VCC FUSE

AND VCCPC6

V_1P05_CORE

SC1U6D3V2ZY-GP

SC1U6D3V2ZY-GP

1

C2

C2

2

2009/11/20

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2ZY-GP

SC1U6D3V2ZY-GP

1

C283

C283

2

12

C271

C271

(R)

(R)

L28

L28

12

2009/11/30

C576

C576

SC10U25V6KX-1GP

SC10U25V6KX-1GP

(R)

(R)

V_1P05_CORE

2009/11/30

12

V_1P8_PLLSFR

2010/01/17

1

C577

C577

SC10U25V6KX-1GP

SC10U25V6KX-1GP

2

(R)

(R)

1

R466

R466

0R0603-PAD-1-GP

0R0603-PAD-1-GP

2

1

C272

C272

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

2

C

B

A

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Sec.1,Hs in Tai Wu Rd

21F, 88, Sec.1,Hs in Tai Wu Rd

21F, 88, Sec.1,Hs in Tai Wu Rd

Hsichih, Taipei Hsien

Hsichih, Taipei Hsien

Title

Title

Title

PINEVIEW: POWERS

PINEVIEW: POWERS

PINEVIEW: POWERS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

AIO eMARR

AIO eMARR

AIO eMARR

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Hsichih, Taipei Hsien

of

10 31Thursday, June 24, 2010

of

10 31Thursday, June 24, 2010

of

1

10 31Thursday, June 24, 2010

A

1A

1A

1A

Loading...

Loading...