Acer TRAVELMATE X349-M Schematic

YSTEM PAGE REF.

V

www.schematic-x.blogspot.com

S

5

4

3

2

1

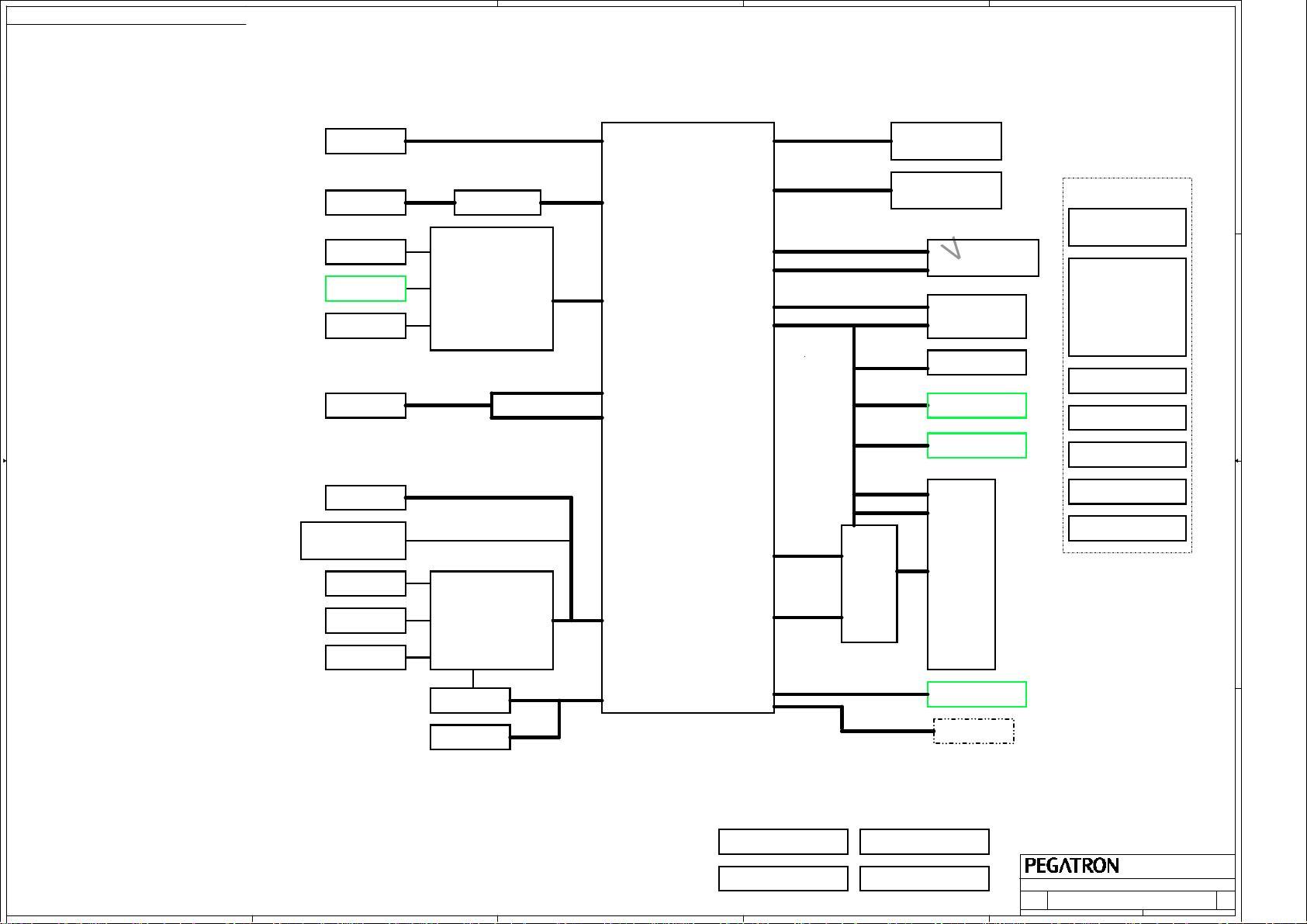

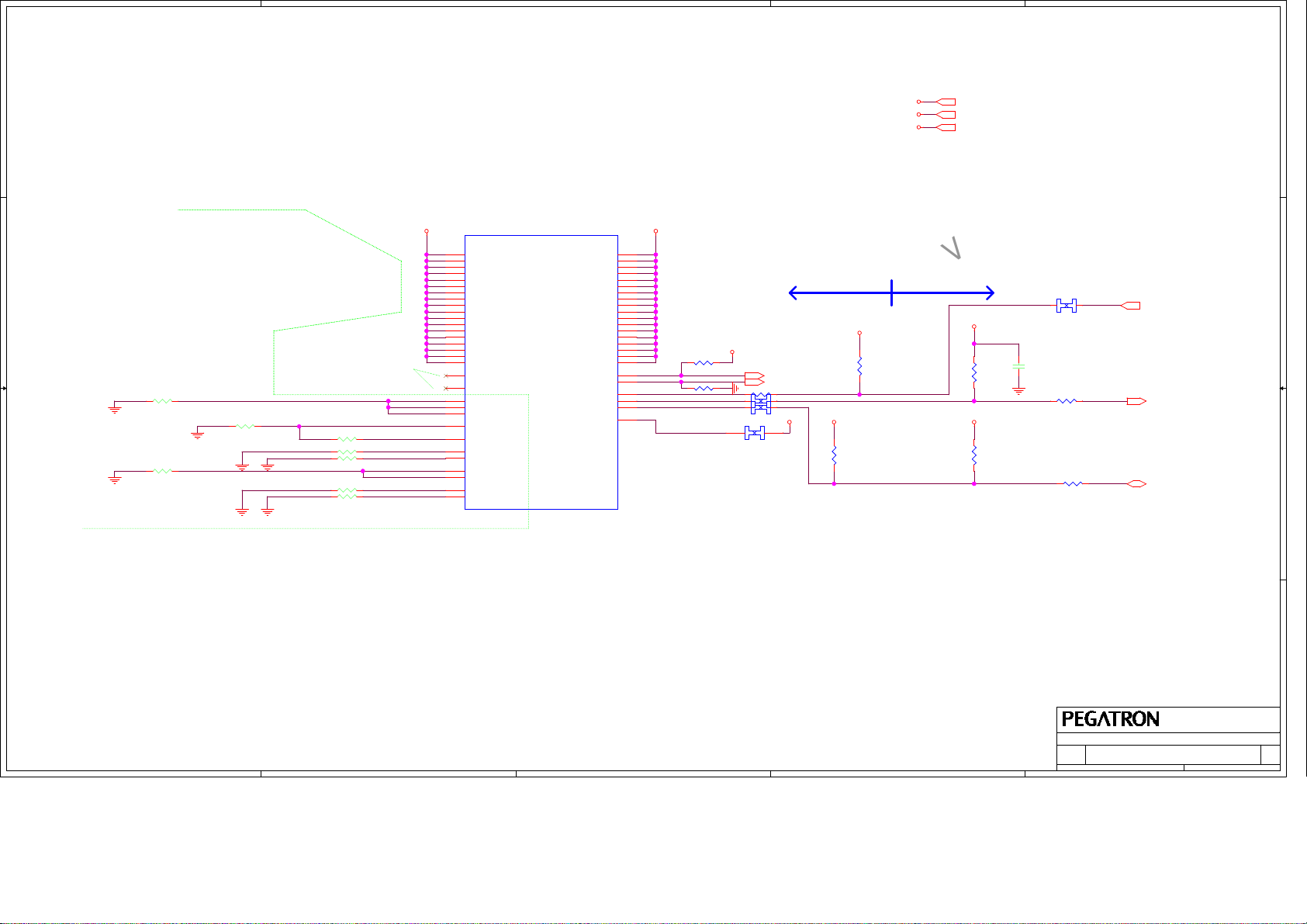

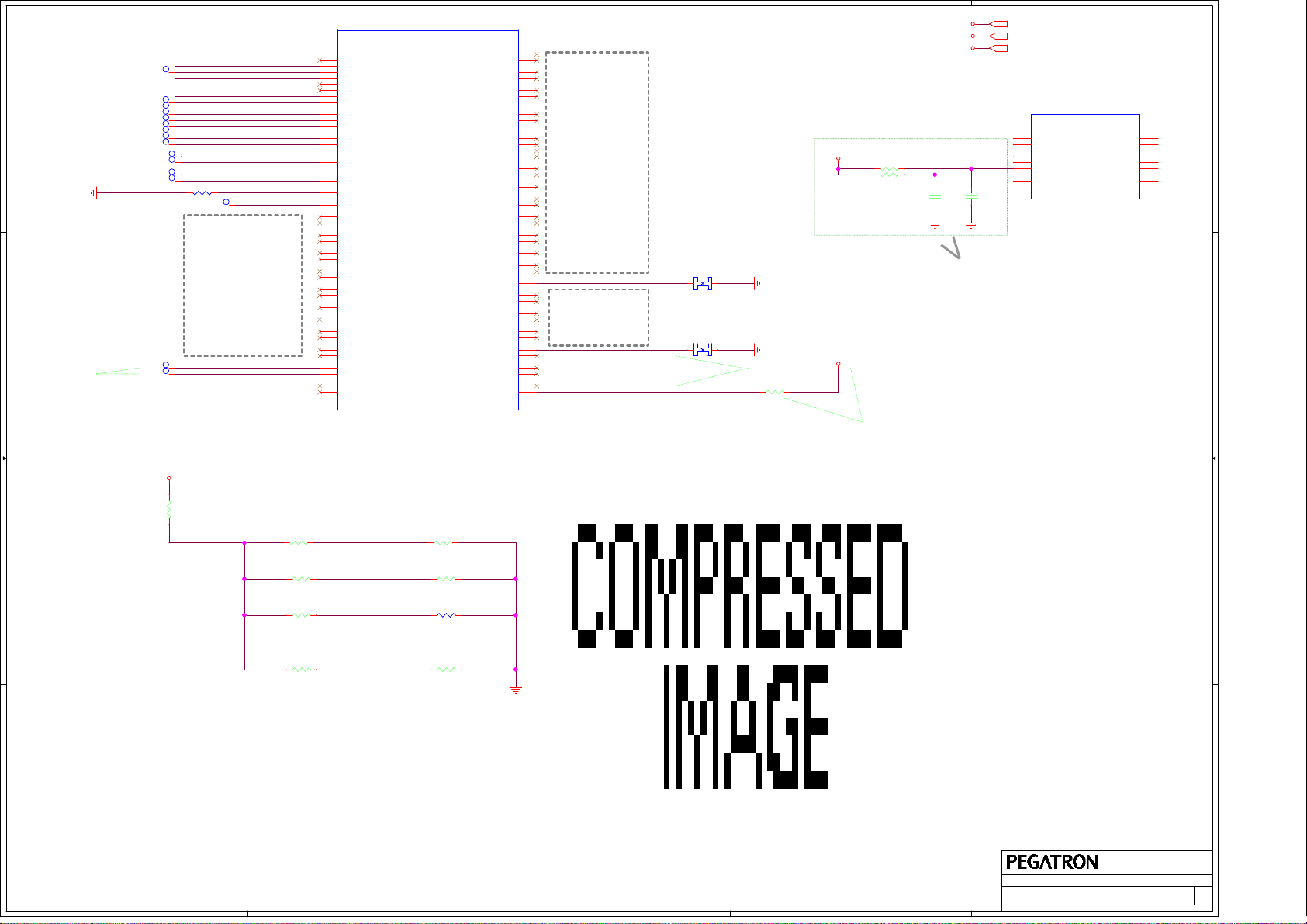

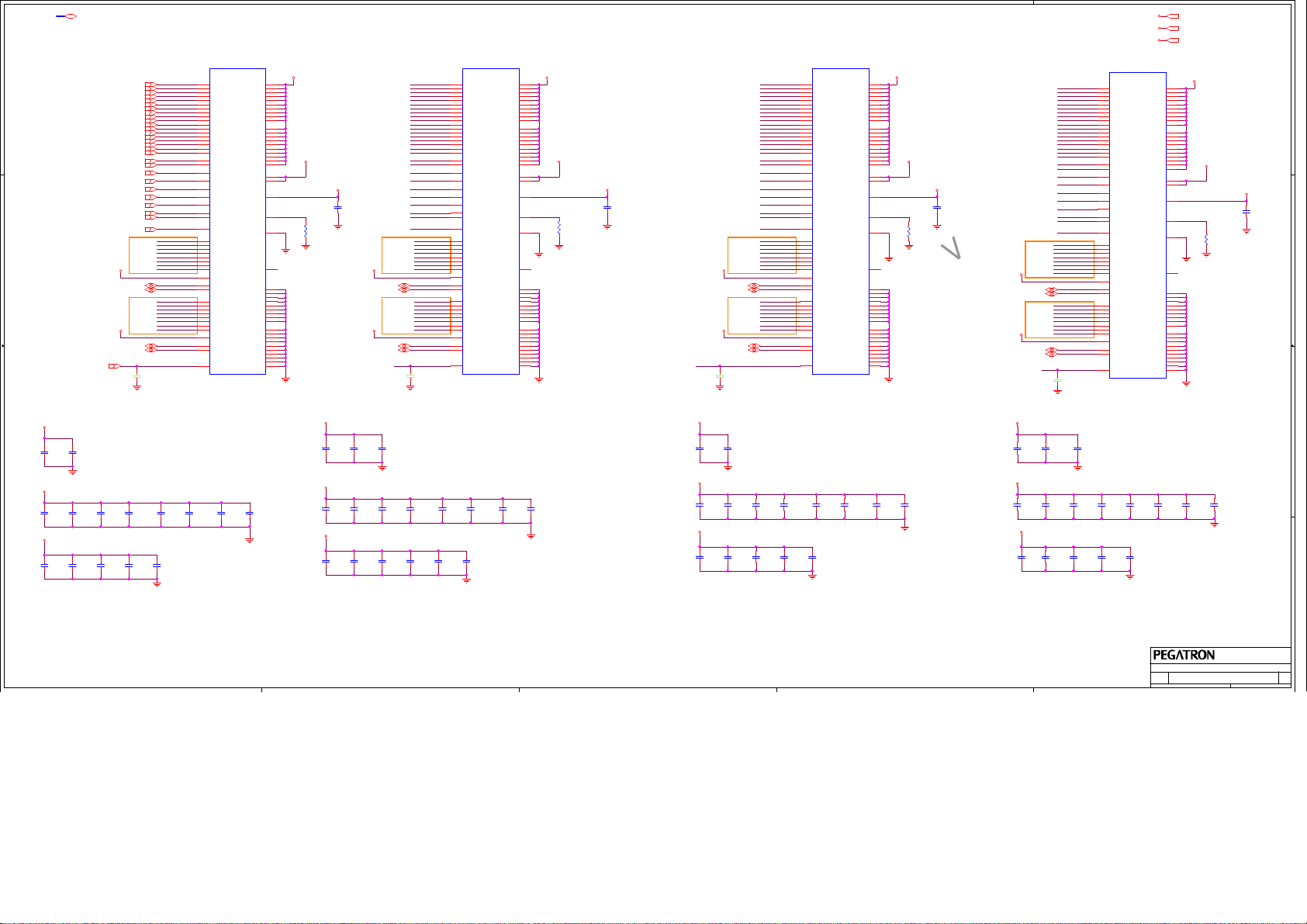

01. Block Diagram

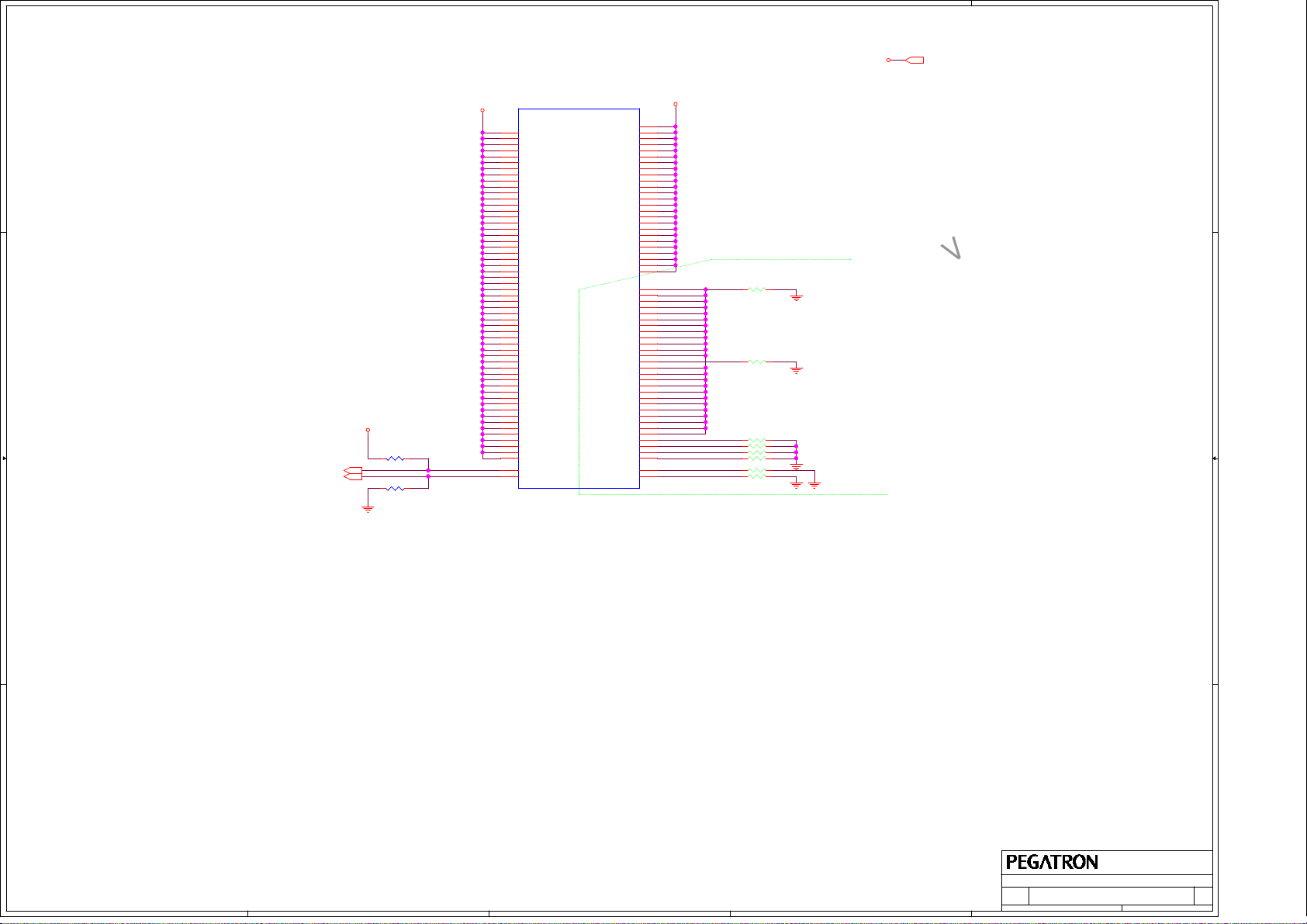

02. GPIO Setting

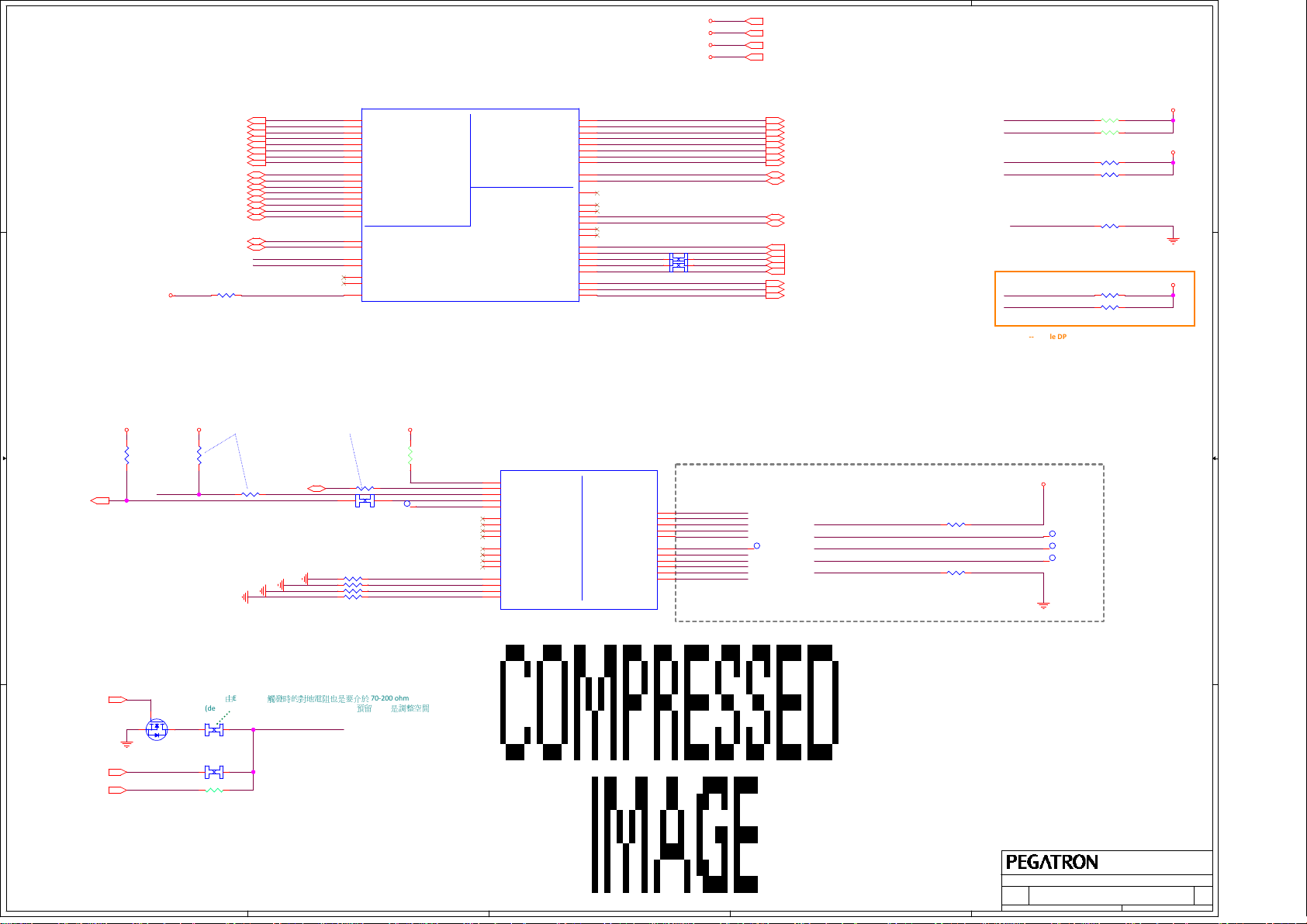

03. CPU(1)_DDI/eDP

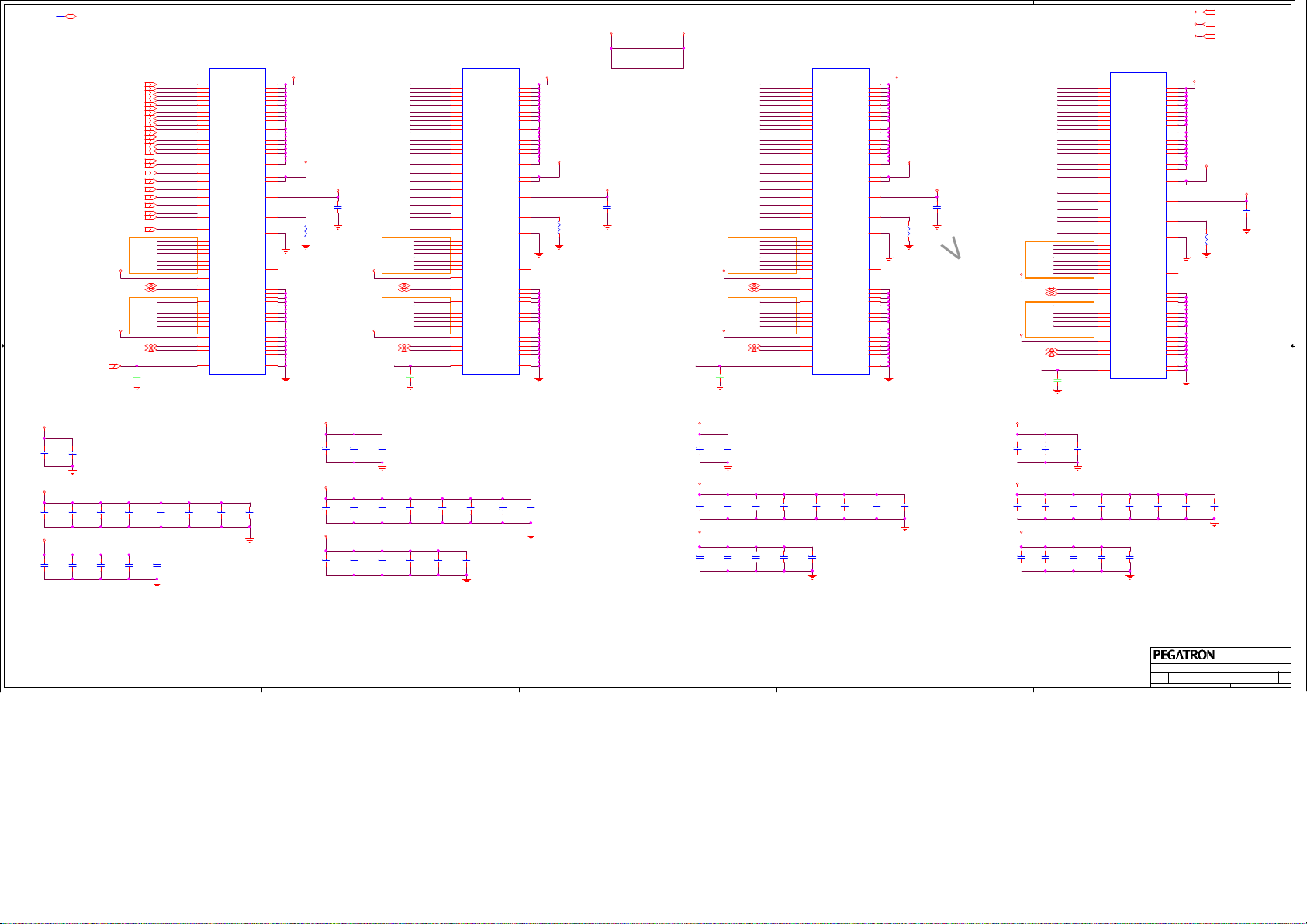

04. CPU(2)_DDR4

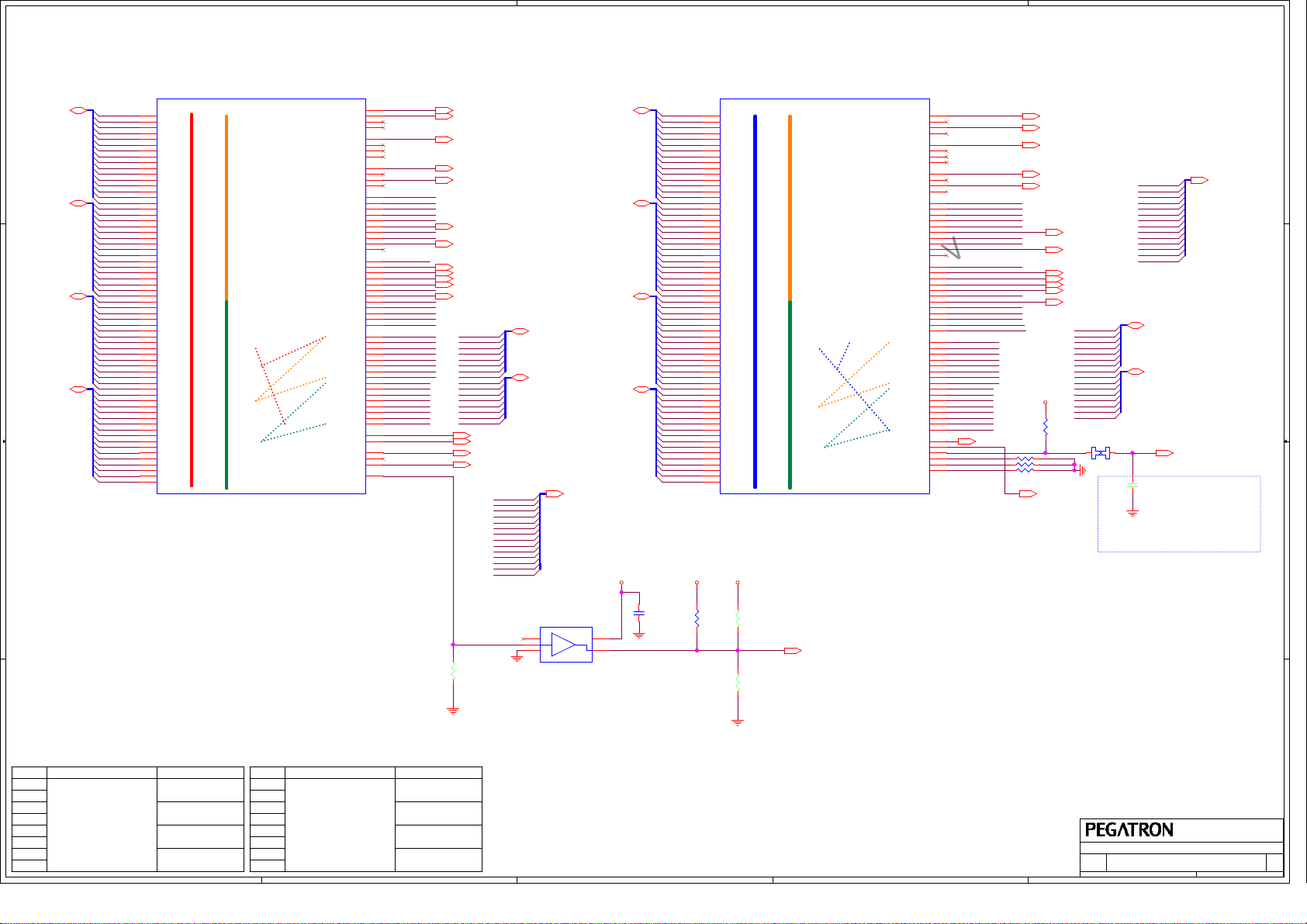

05. CPU(3)_+VCCCORE

06. CPU(4)_+VCCGT

D D

07. CPU(5)_+VDDQ/IO/SA

08. CPU(6)_CPU GND

09. CPU(7)_CFG/RSVD

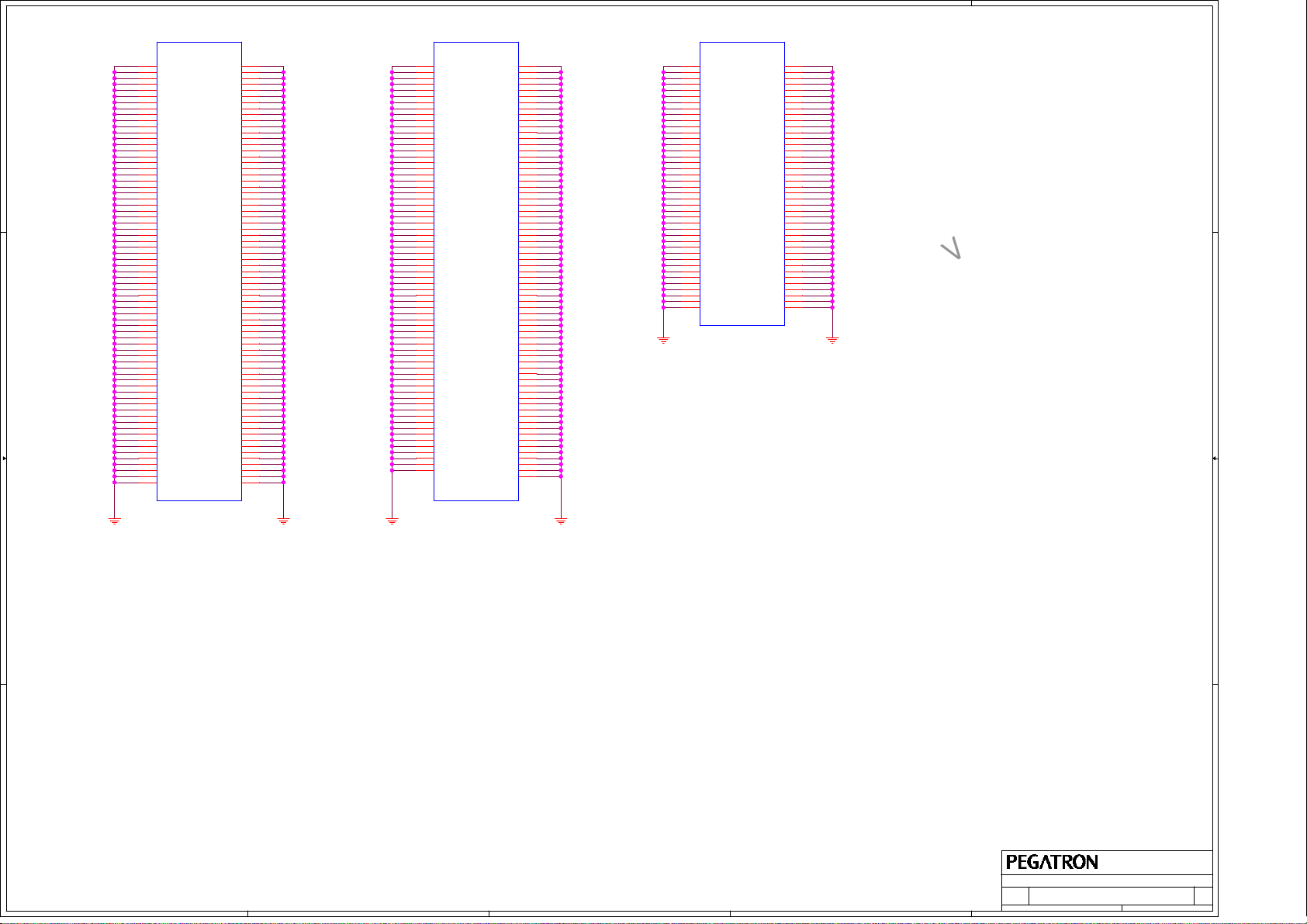

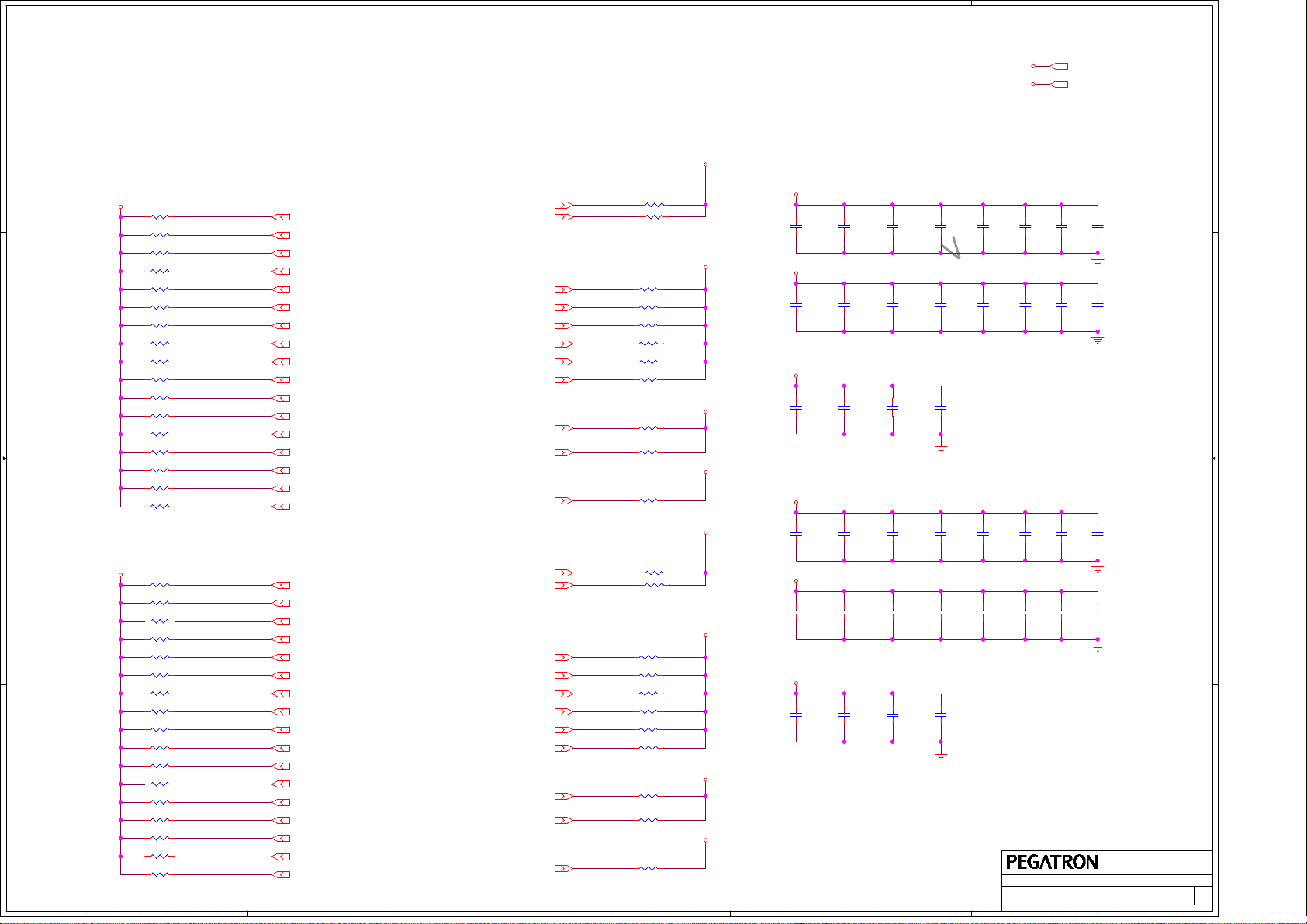

15. DDR4(0)_Termination

16. DDR4(1)_CH0

17. DDR4(2)_CH1

19. DDR4(4)_CA/DQ Voltage

20. PCH(1)_SPI/LPC

21. PCH(2)_ISH

22. PCH(3)_HDA/SDIO

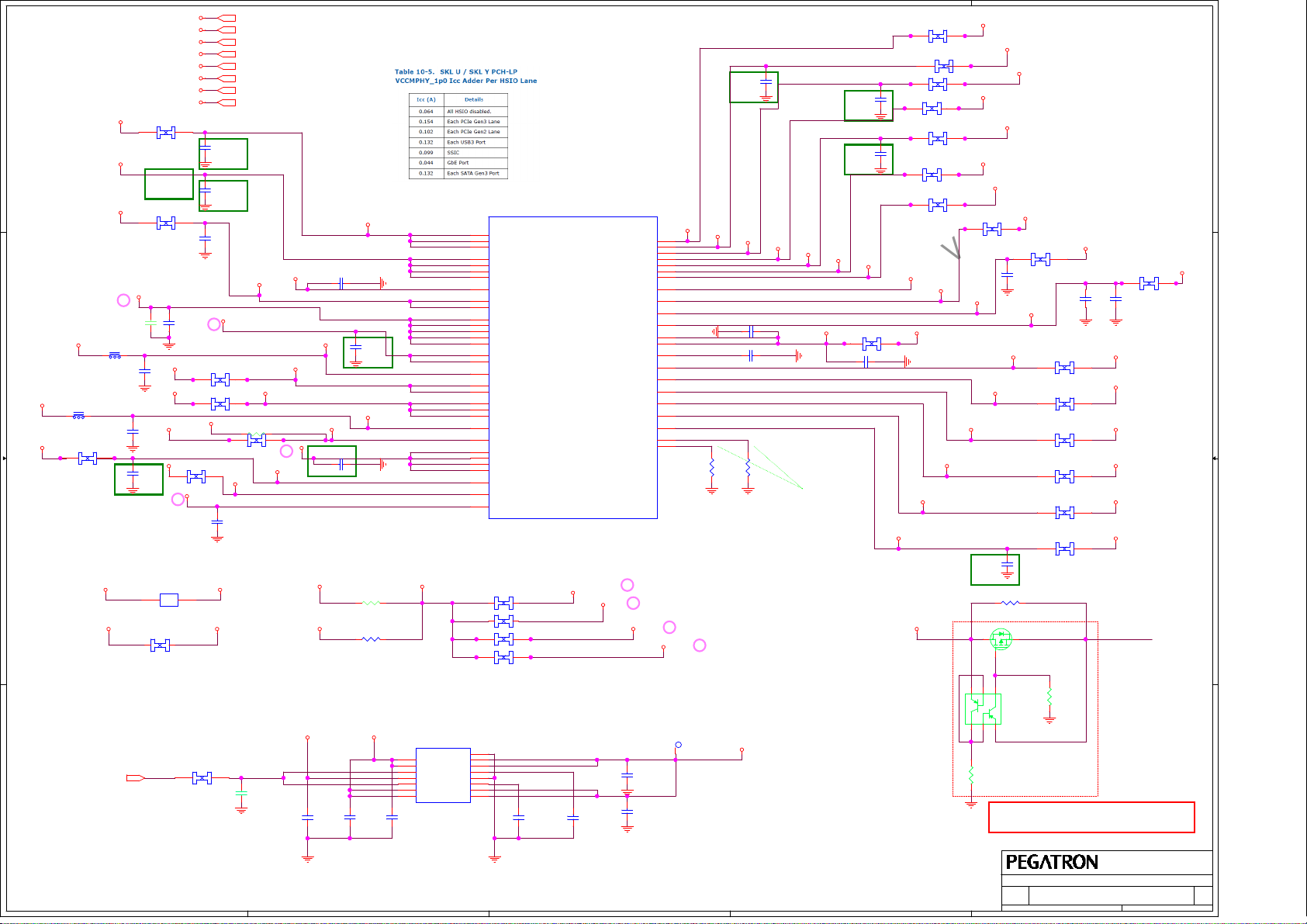

23. PCH(4)_USB/PCIE/SATA

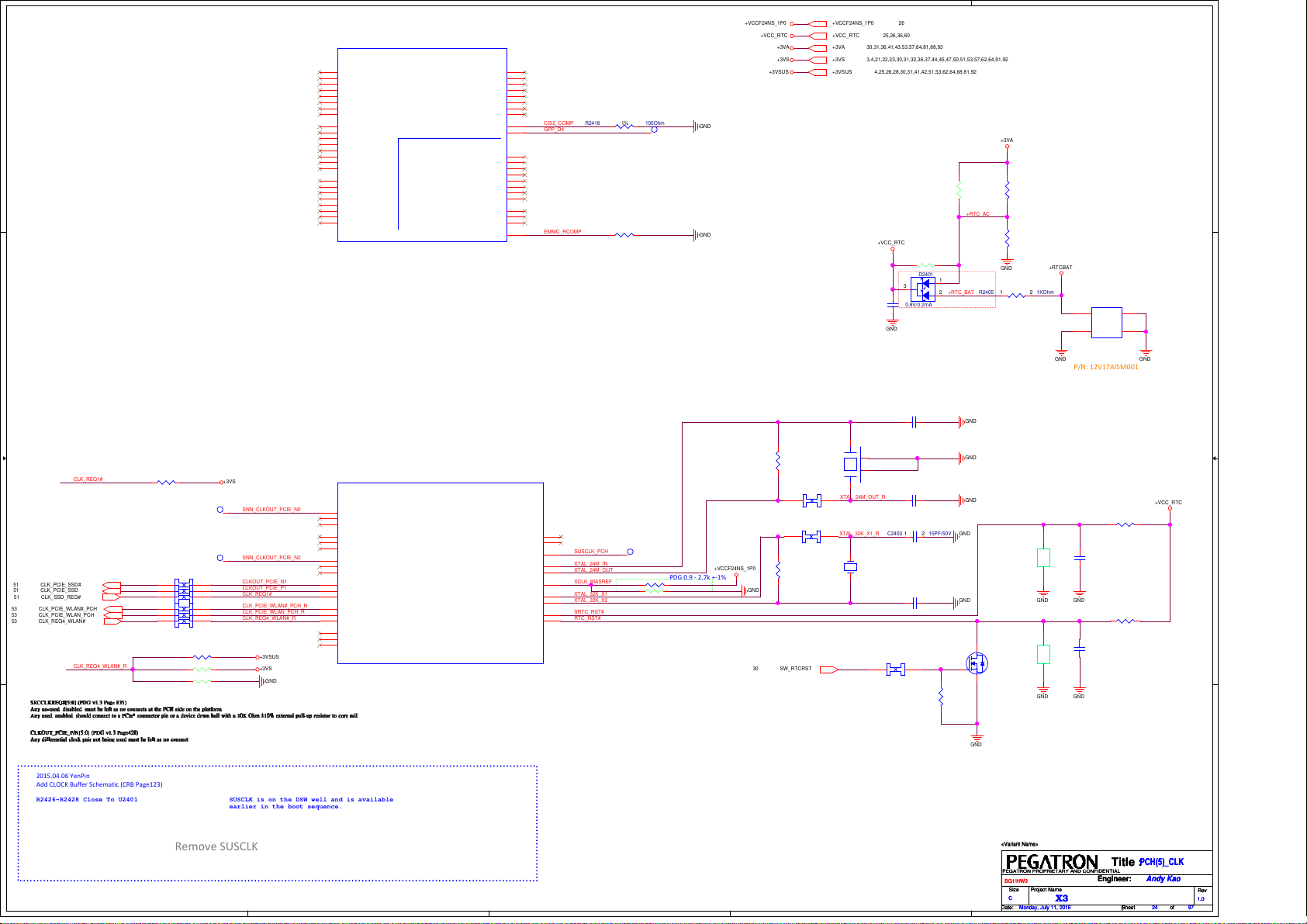

24. PCH(5)_CLK/RTC

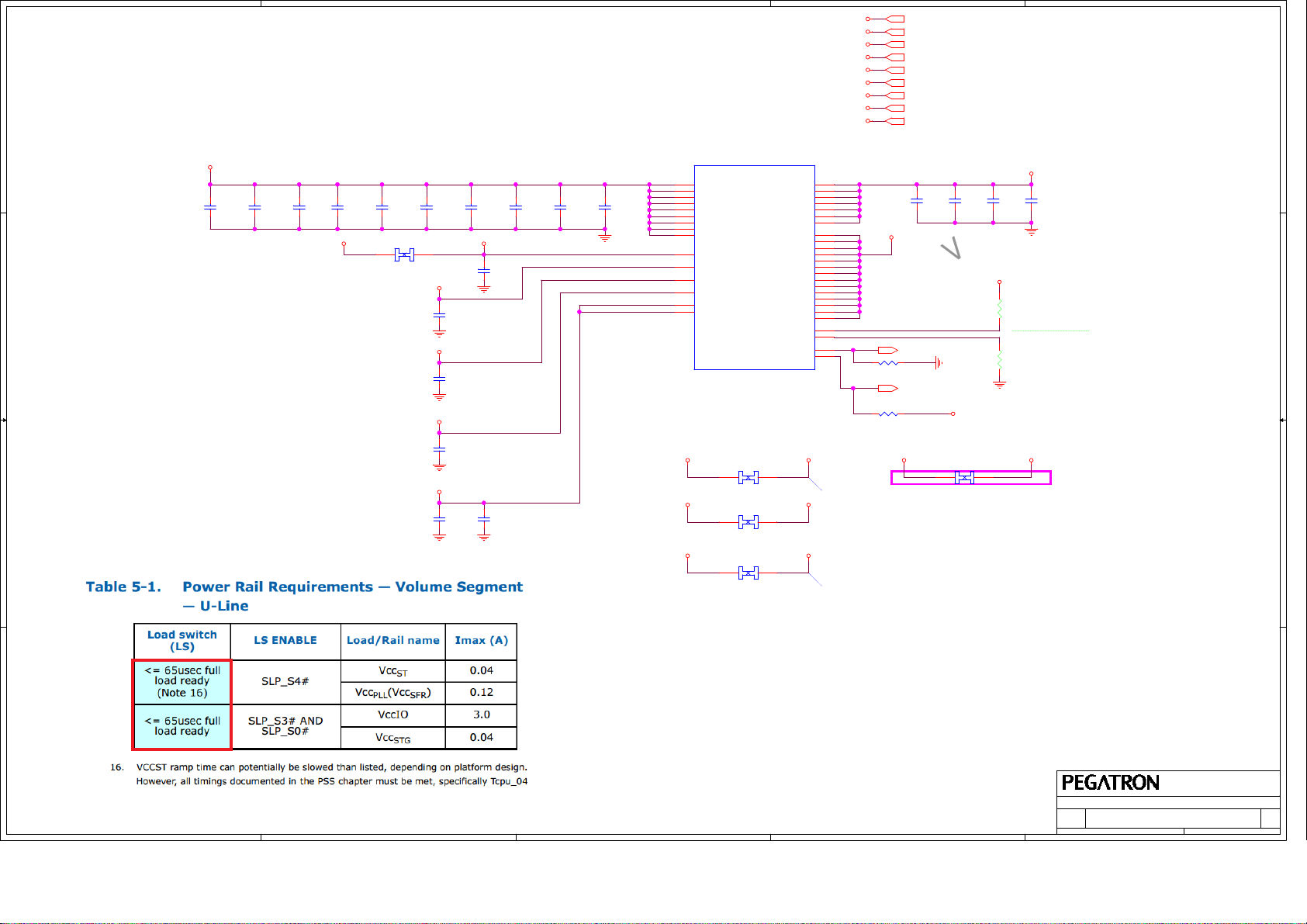

25. PCH(6)_POWER MANAGEMENT

26. PCH(7)_POWER

28. PCH(9)_SPI/SMB

30. EC_IT8587/FX

31. EC_IT8587E/FX_KB/TP/KBBL

32. RST_Reset Circuit

36. AUD_ALC255

37. AUD(2)_SPK/DMIC

C

41. USB_Type-C ANX7428

42. USB Type-C Receptacle

43. USB Type-C Dead Battery

44. Debug CONN

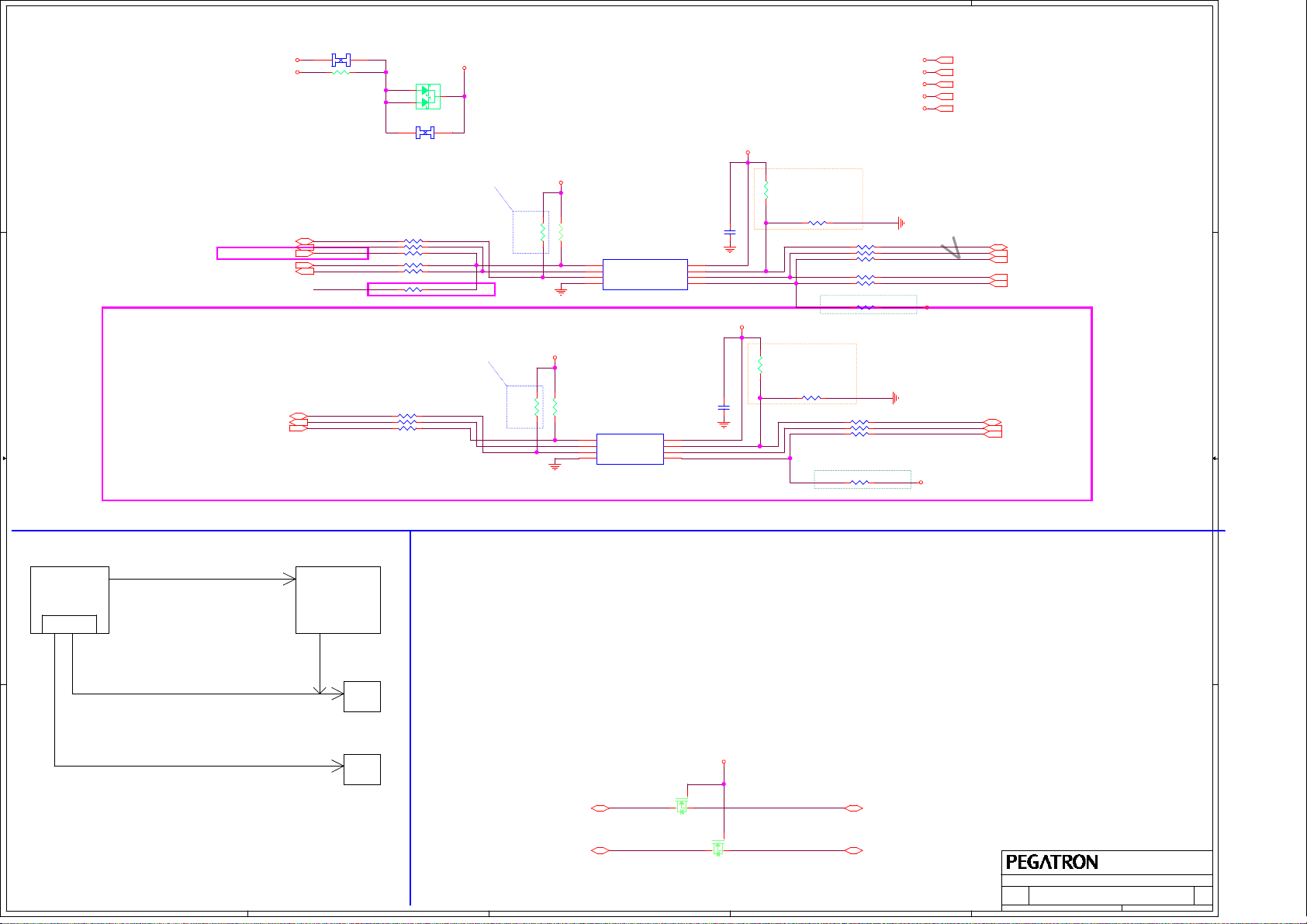

45. CRT(1)_eDP,CAMERA,TSN

47. HDMI Repeater PS8201A

48. HDMI OUT

50. THERMAL / FAN

51. NGFF PCIE*4/SATA SSD

52. USB 3.0/Sleep Charge IC

53. NGFF PCIE WLAN/BT

56. LED

57. Discharge

60. DC_DC/BAT CONN

62 TPM NPCT650

64. IO Board

65. ME_CONN / Skew Hole

68. BYPASS EC SEQUENCE

80_POWER_VCORE for U22

B

81_POWER_SYSTEM

82_POWER_+1.0VSUS

83_POWER_ DDR & VTT_UMA

84_POWER_ 1.8VSUS

85_POWER_ 1.5VS

86_POWER_XXX

87_POWER_XXX

88_POWER_CHARGER

89_POWER_AC_PD_WC Input

90_POWER_DETECT

91_POWER_LOAD SWITCH

92_POWER_PROTECT

93_POWER_SIGNAL

94_POWER_FLOWCHART

A02. AUD(2)_JACK

A03. USB20

A04. CB_RTS5170_GR

1

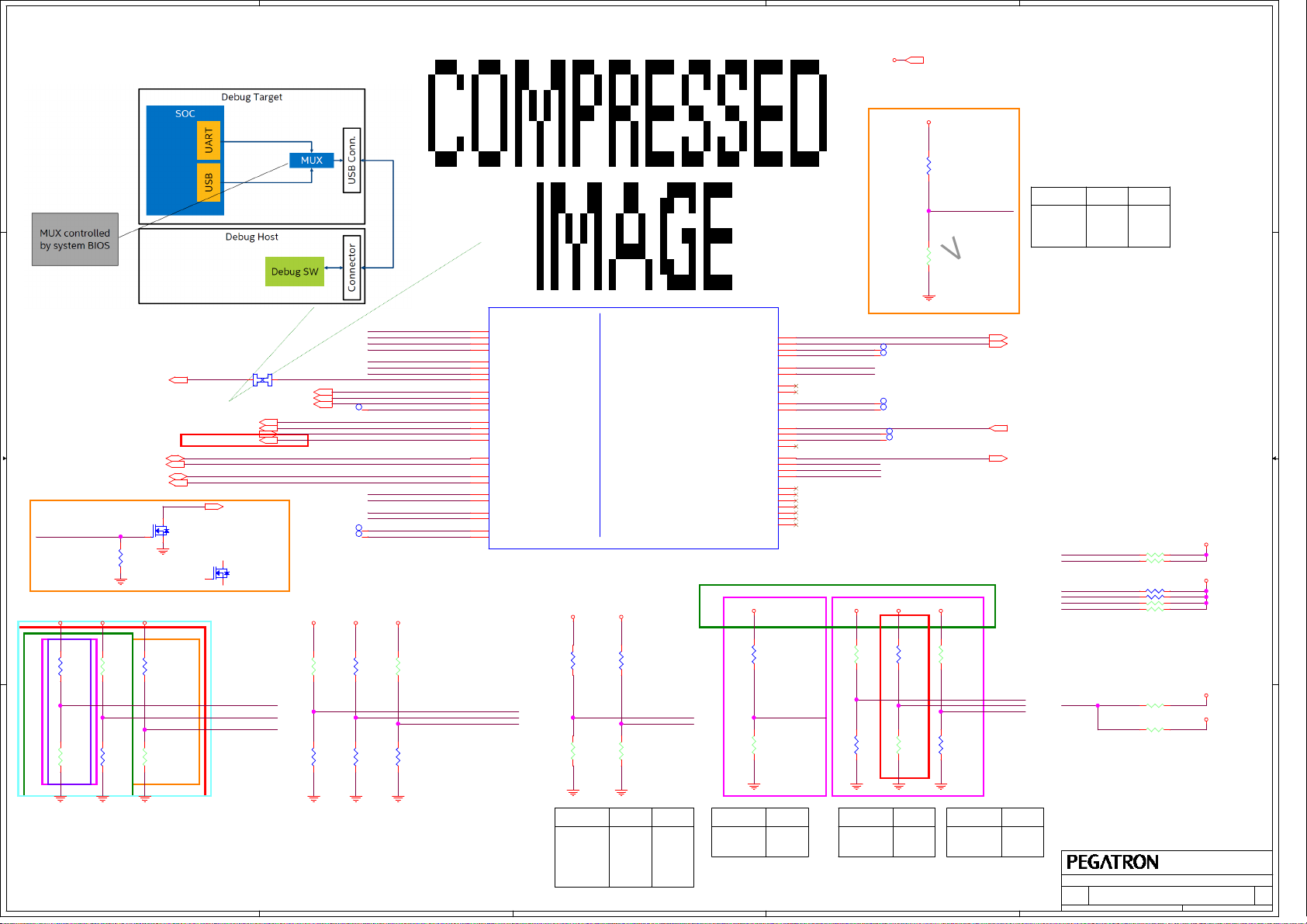

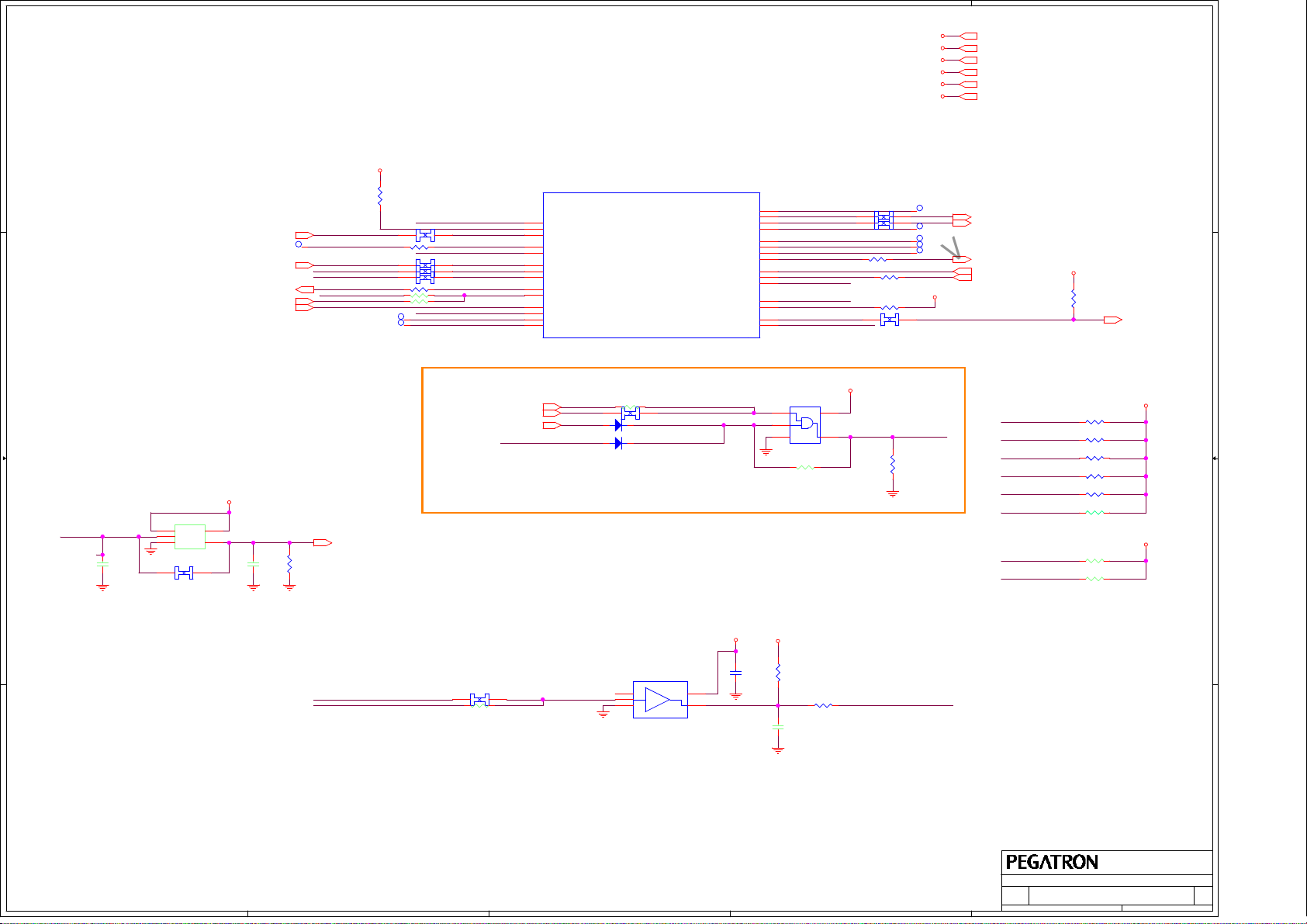

4" Cassiopeia (X3) for Skylake U Platform Block Diagram

PANEL

HDMI

page48

SPEAKER X 2

page37

COMBO JACK

pageA02

DMIC X 1

page37

NGFF SSD

p

age51

DEBUG CONN.

page44

T

PM

NUVOTON/NPCT650

page62

KB

page31

Click Pad

page31

Thermal

page50

H

DMI Repeater

PS8201A

Audio Codec

REALTEK/ ALC255

EC

I

T8987E/BX

S

PI ROM (16M)

page28

S

PI ROM (8M)

p

age28

page36

page30

eDP

DDI 1/2

HDA

PCIE

SATA

L

SPI

PC

I

NTEL

S

kylake U

T

DP 15W

DDR4 2133MHz

C

hannel A

Channel B

USB 3.0 3/4

DDI 2

PCI-E 6/10

U

SB 2.0 5/10

USB 3.0 1/4

USB 2.0 1/10

USB 2.0 7/10

USB 2.0 2/10

USB 2.0 6/10

U

SB 2.0 3/10

USB 2.0 4/10

A

nalogix

A

NX7428

M

UX

p

age41

USB2.0 8/10

U

SB2.0 9/10

DDR4

Memory Down x4

Memory Down x4

page16

DDR4DDR4 2133MHz

page17

NGFF

WLAN / BT

USB 3.0 Conn x1

W/charger

Front Camera /0.3M

USB2.0 Conn x1

Fingerprinter

T

ype C

p

age42

C

ard Reader

R

ealtek/RTS5170

Touch Panel

pageA03

p

P

p

age45

page52

page45

ageA05

ageA04

page53

P

ower

+

VCORE

+VCCGT

+

VCCSA

P

PMIC

S

ystem (5V & 3.3V)

+1.0VSUS

VCCPRIM_CORE

DDR & VTT

Page 81

+

1.5VS

+1.8VSUS

B

ATTERY CHARGER

D

L

OAD SWITCH

P

ower Protect

P

P

ETECT

P

P

P

age 80

age 84

age 88

age 90

age 91

age 92

C

B

A

5

A

D

D

ischarge Circuit

R

eset Circuit

4

3

P

age 57

P

age 32

C & BATT. Conn.

S

kew Holes

2

P

age 60

P

age 65

<

<

<

Variant Name>

Variant Name>

Variant Name>

T

T

T

itle :

itle :

1

E

E

E

ngineer:

ngineer:

ngineer:

itle :

P

P

P

EGATRON PROPRIETARY AND CONFIDENTIAL

EGATRON PROPRIETARY AND CONFIDENTIAL

EGATRON PROPRIETARY AND CONFIDENTIAL

BG1/HW3

BG1/HW3

BG1/HW3

S

ize Project Name

Size Project Name

Size Project Name

C

C

C

ustom

ustom

ustom

X3

X3

Date: Sheet

Date: Sheet

Date: Sheet

X3

Block Diagram

Block Diagram

Block Diagram

A

A

A

ndy Kao

ndy Kao

ndy Kao

1 97Monday, July 11, 2016

1 97Monday, July 11, 2016

1 97Monday, July 11, 2016

Rev

Rev

Rev

1

1

1

.0

.0

.0

o

o

o

f

f

f

5

V

4

3

2

1

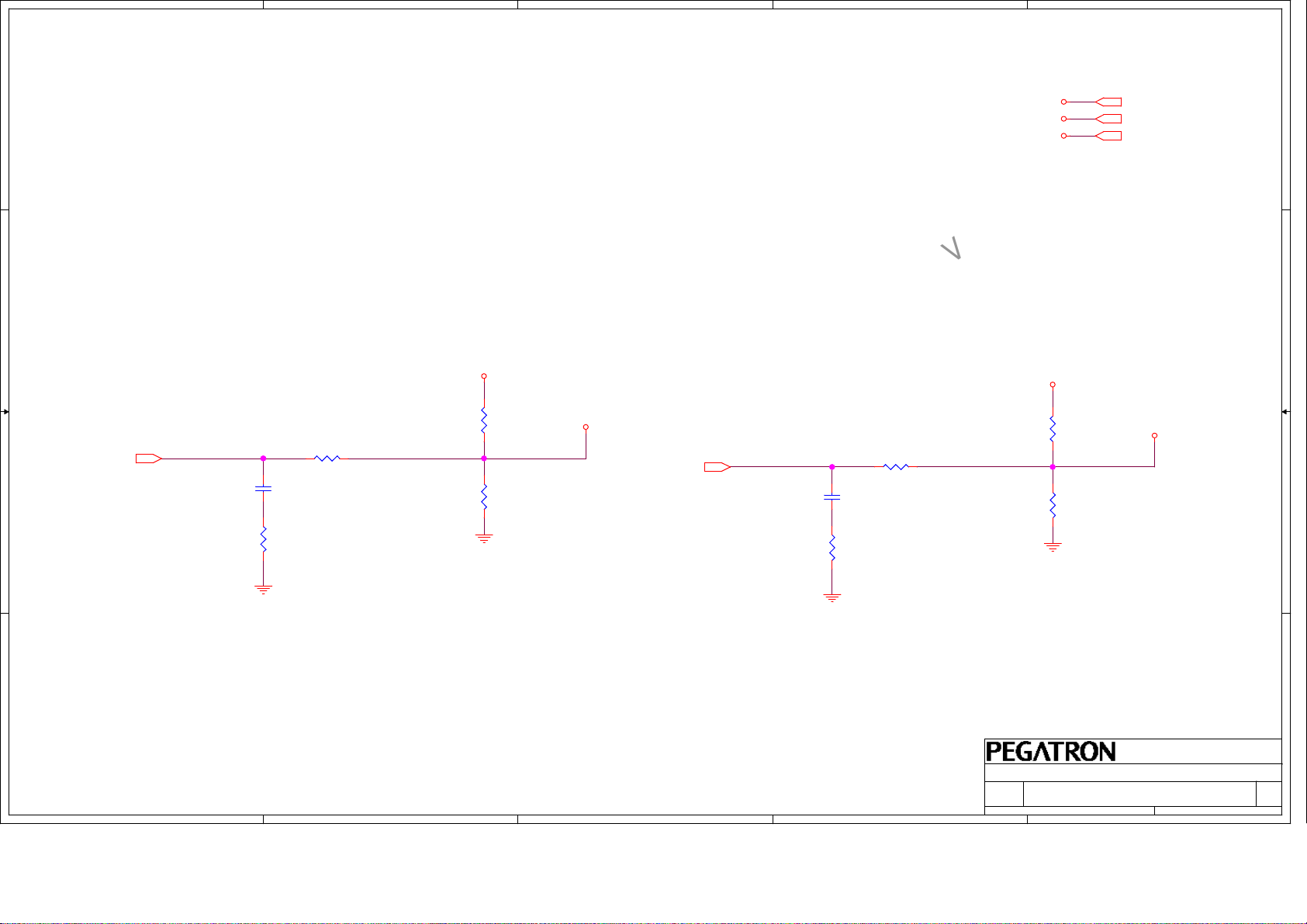

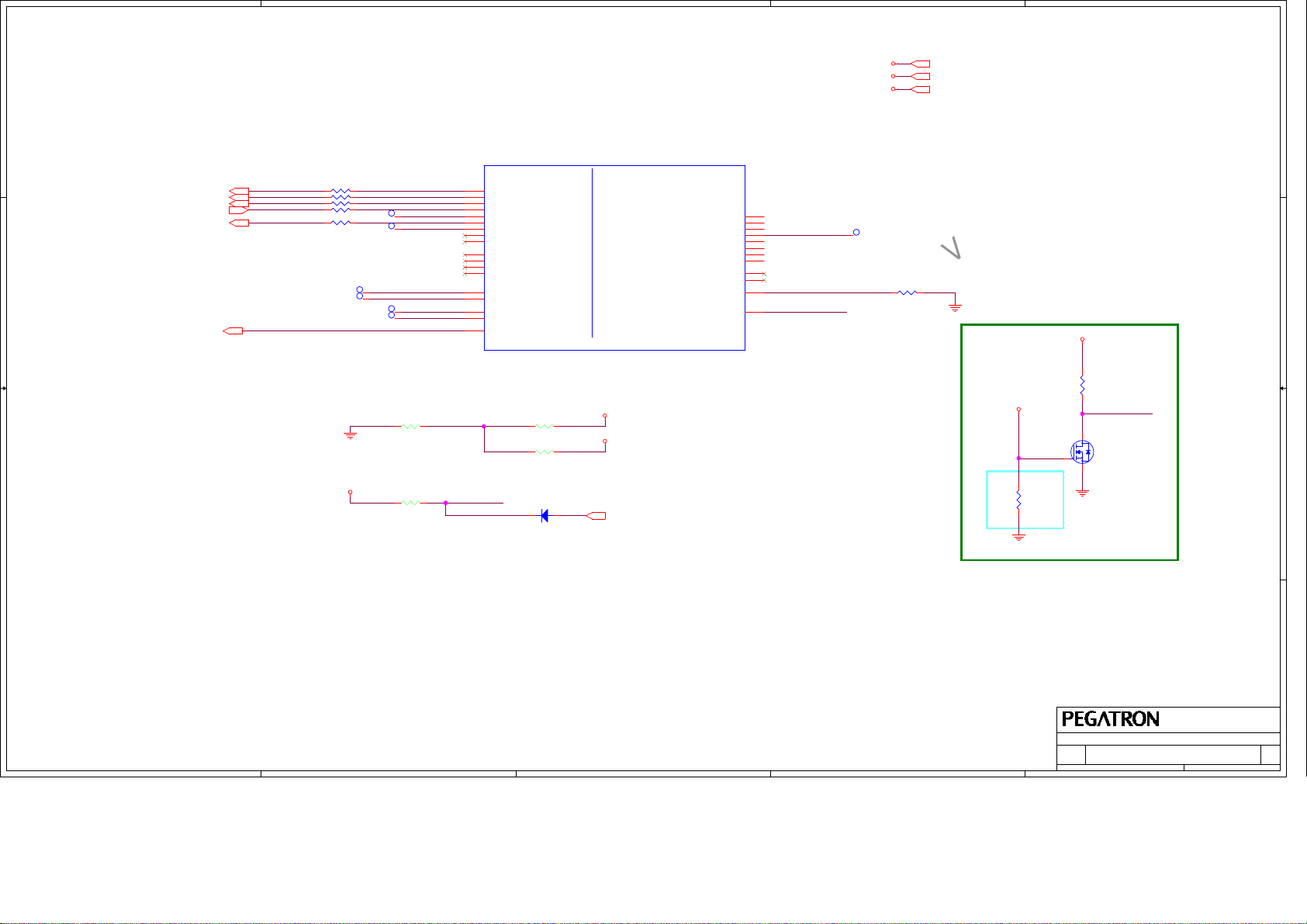

Use As Signal NameEC GPIO EC GPIO Use As Signal NameUse As Signal NameEC GPIO Use As Signal NameEC GPIO

D D

C C

B B

A A

Title :

Title :

Title :

GPIO Setting

GPIO Setting

GPIO Setting

Andy Kao

Andy Kao

Andy Kao

2 97Monday, July 11, 2016

2 97Monday, July 11, 2016

2 97Monday, July 11, 2016

Rev

Rev

Rev

1.0

1.0

1.0

PEGATRON PROPRIETARY AND CONFIDENTI AL

PEGATRON PROPRIETARY AND CONFIDENTI AL

PEGATRON PROPRIETARY AND CONFIDENTI AL

BG1/HW3

BG1/HW3

BG1/HW3

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

X3

X3

X3

Engineer:

Engineer:

Engineer:

1

5

V

4

3

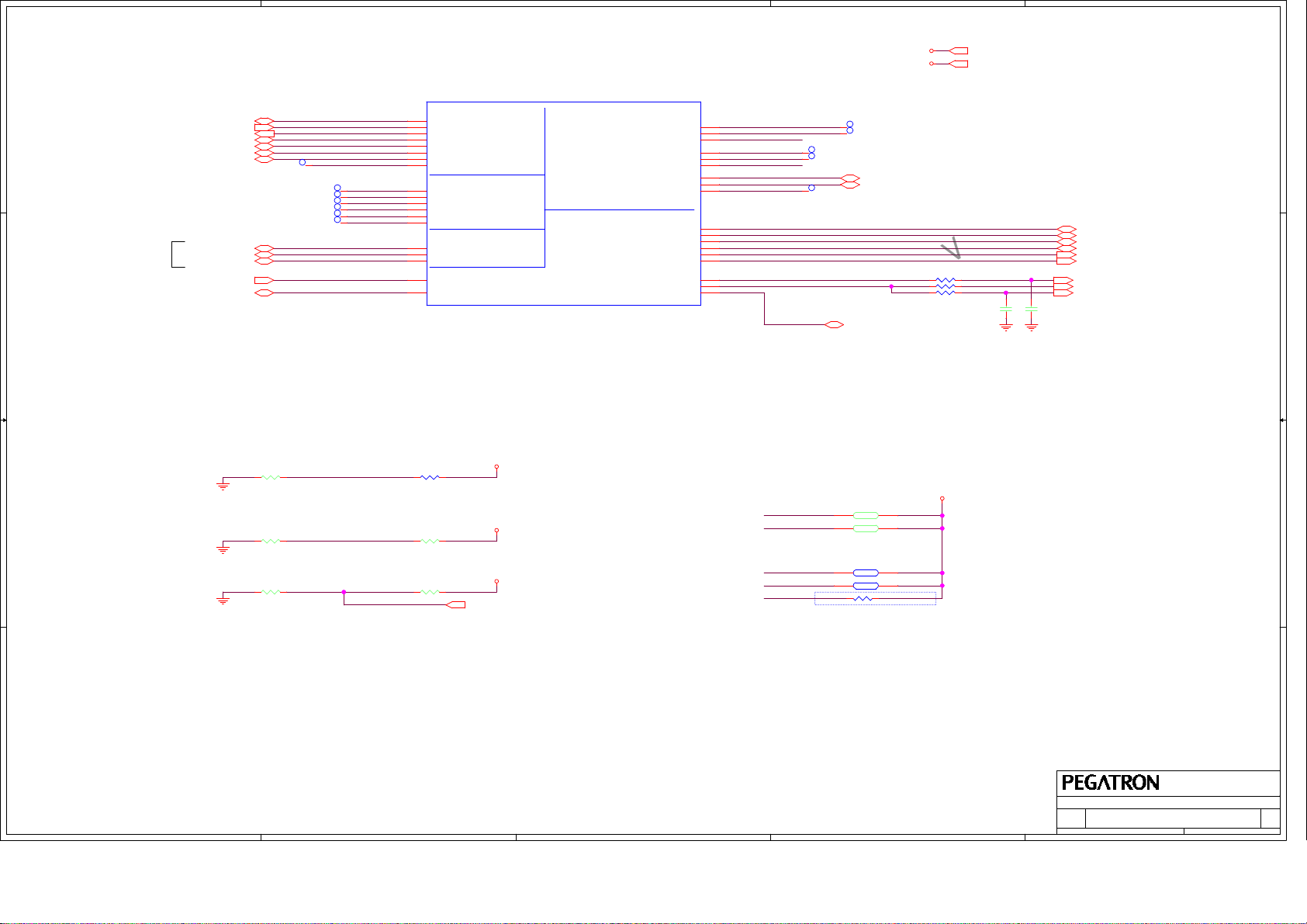

+VCCIO

+VCCST_CPU

+VCCSTG

+3VS

+VCCIO 7,9,57,91

+VCCST_CPU 5,7,9,25,32

+VCCSTG 5,7

+3VS 4,21,22,23,24,30,31,32,36,37,44,45,47,50,51,53,57,62,64,91,92

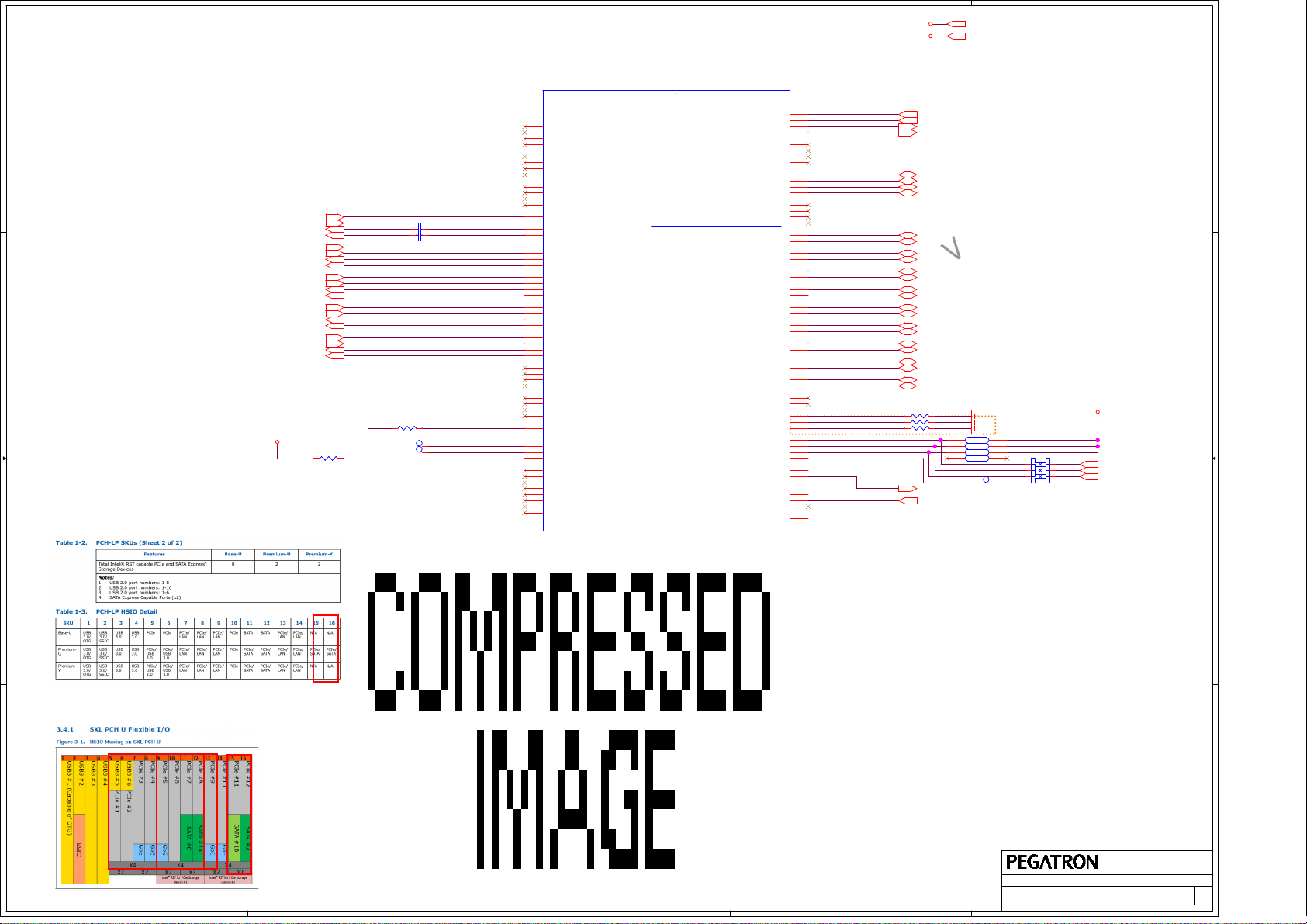

SKYLAKE-U symbol ReV0.53 #545316 / Ballout_Rev0_71 #543787 / PEGA local PN is 4201-0062000

U0301A

D D

DDI Port 1: HDMI eDP x 4

DDI Port 2: TYPE-C DP

+VCCIO

C C

DDI1_TXN247

DDI1_TXP247

DDI1_TXN147

DDI1_TXP147

DDI1_TXN047

DDI1_TXP047

DDI1_CLKN47

DDI1_CLKP47

DDI2_TXN041

DDI2_TXP041

DDI2_TXN141

DDI2_TXP141

DDI2_TXN241

DDI2_TXP241

DDI2_TXN341

DDI2_TXP341

DDPB_CTRLCLK47

DDPB_CTRLDATA47

R0301 24.9Ohm1%

12

DDPC_CTRLCLK

DDPC_CTRLDATA

DP_COMP

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22

N12

GPP_E23

E52

eDP_RCOMP

940432

01V010000015

DDI

DISPLAY SIDEBANDS

EDP

EDP_DISP_UTIL

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

RSVD_1

RSVD_2

eDP_BKLTEN

eDP_BKLTCTL

eDP_VDDEN

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

EXT_SMI#_R

EXT_SCI#_R

eDP_HPD

1 2

R0302 0Ohm

1 2

R0303 0Ohm

EXT_SMI#

EXT_SCI#

EDP_TXN0 45

EDP_TXP0 45

EDP_TXN1 45

EDP_TXP1 45

EDP_TXN2 45

EDP_TXP2 45

EDP_TXN3 45

EDP_TXP3 45

EDP_AUXN 45

EDP_AUXP 45

DDI2_AUXN 41

DDI2_AUXP 41

DDI1_HPD 47

DDI2_HPD 41

EXT_SMI# 30,44

EXT_SCI# 30

eDP_HPD 45

LCD_BKLTEN_PCH 21,45

LCD_BL_PWM_PCH 45

EDP_VDD_EN 45

2

-- WQHD 4 Lane

-- FHD 2 Lane

Pull down at connector side

DDPB_CTRLDATA

DDPC_CTRLDATA

DDPD_CTRLDATA

- Internal weak pull down 20k ohm

- 0 : port is not detected

1 : port is deteccted

DDPB_CTRLDATA

DDPB_CTRLCLK

EXT_SCI#

EXT_SMI#

DDPC_HPD

DP: 100Kohm pull down on PCH Side

HDMI: 20Kohm pull down

DDI2_HPD

DDPC_CTRLDATA

DDPC_CTRLCLK

R1.0_10L ---Enable DP port

1

1 2

R0304 2.2KOhm@

1 2

R0338 2.2KOhm@

1 2

R0307 10KOhm

1 2

R0308 10KOhm

1 2

R0337 100KOhm

1 2

R0342 2.2KOhm

1 2

R0343 2.2KOhm

+3VS

+3VS

+3VS

+VCCST_CPU

12

R0311

1KOhm

H_THRMTRIP#32

B B

THRO_CPU30

PROCHOT#88

A A

VR_HOT#80

H_PROCHOT#

1

1

G

3

2

32

D

S

Q0301

2N7002

SP0325 0Ohm

5

141024 follow PDG V1.0 Table 10-4

Rpu = 1K ohm 5%

Rs = 500 ohm 5%

12

R0312

1KOhm

5%

H_PECI_EC30

1 2

R0314 499Ohm1%

R0341由EC control

(depends on under-shoot measurement result),預預0ohm

R0341 0Ohm

R0320 0Ohm@

觸觸觸觸觸觸觸觸觸觸觸觸觸

12

H_PROCHOT#

12

12

R0315 43Ohm5%

SP0301

R0316 49.9Ohm1%

R0317 49.9Ohm1%

R0318 49.9Ohm1%

R0319 49.9Ohm1%

Closeer EC

1 2

1 2

1 2

1 2

1 2

1 2

+VCCST_CPU+VCCSTG

T0306

70-200 ohm

觸是是是是

4

12

R0313

49.9Ohm

1%

@

TP_CATERR#_R

H_PECI

PROCHOT#_R

H_THRMTRIP#_R

1

SKTOCC#

CPU_POPIRCOMP

PCH_POPIRCOMP

EDRAM_OPIO_RCOMP

EOPIO_RCOMP

AT16

AU16

D63

A54

C65

C63

A65

C55

D55

B54

C56

BA5

AY5

H66

H65

A6

A7

01V010000015

U0301D

CATERR#

PECI

PROCHOT#

THERMTRIP#

SKTOCC#

CPU MISC

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

OPCE_RCOMP

OPC_RCOMP

940432

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

3

JTAGX

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

XDP_TCLK

XDP_TDI_CPU

XDP_TDO_CPU

XDP_TMS_CPU

XDP_TRST_CPU_N

PCH_JTAG_TCLK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST_CPU_N

XDP_TCLK_JTAGX

+VCCSTG

XDP_TDO_CPUPCH_JTAG_TDO

1

T0315

PCH_JTAG_TMS XDP_TMS_CPU

XDP_TRST_CPU_NPCH_TRST_CPU_N

XDP_TDI_CPUPCH_JTAG_TDI

XDP_TCLKXDP_TCLK_JTAGX

R0323 51Ohm

R0324 51Ohm

12

12

1

T0316

1

T0317

1

T0318

Modify to XDP less

<Variant Name>

<Variant Name>

<Variant Name>

CPU(1)_DDI/eDP

CPU(1)_DDI/eDP

CPU(1)_DDI/eDP

Title :

Title :

PEGATRON PROPRIETARY AND CONFIDENTI AL

PEGATRON PROPRIETARY AND CONFIDENTI AL

PEGATRON PROPRIETARY AND CONFIDENTI AL

BG1/HW3

BG1/HW3

BG1/HW3

Size Project Name

Size Project Name

Size Project Name

C

C

C

X3

X3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

X3

Engineer:

Engineer:

Engineer:

1

Title :

Andy Kao

Andy Kao

Andy Kao

3 97Monday, July 11, 2016

3 97Monday, July 11, 2016

3 97Monday, July 11, 2016

Rev

Rev

Rev

1.0

1.0

1.0

5

V

4

3

2

1

U0301B

M_A_D[15 ..0]16

D D

M_A_D[47 ..32]16

M_B_D[15 ..0]17

C C

M_B_D[47 ..32]17

B B

M_A_D0

M_A_D1

M_A_D2

M_A_D3

M_A_D4

M_A_D5

M_A_D6

M_A_D7

M_A_D8

M_A_D9

M_A_D10

M_A_D11

M_A_D12

M_A_D13

M_A_D14

M_A_D15

M_A_D32

M_A_D33

M_A_D34

M_A_D35

M_A_D36

M_A_D37

M_A_D38

M_A_D39

M_A_D40

M_A_D41

M_A_D42

M_A_D43

M_A_D44

M_A_D45

M_A_D46

M_A_D47

M_B_D0

M_B_D1

M_B_D2

M_B_D3

M_B_D4

M_B_D5

M_B_D6

M_B_D7

M_B_D8

M_B_D9

M_B_D10

M_B_D11

M_B_D12

M_B_D13

M_B_D14

M_B_D15

M_B_D32

M_B_D33

M_B_D34

M_B_D35

M_B_D36

M_B_D37

M_B_D38

M_B_D39

M_B_D40

M_B_D41

M_B_D42

M_B_D43

M_B_D44

M_B_D45

M_B_D46

M_B_D47

AW65

AW63

AW61

AW59

AW39

AW37

AW35

AW33

AW31

AW29

AW27

AW25

AL71

DDR0_DQ[0 ]

AL68

DDR0_DQ[1 ]

AN68

DDR0_DQ[2 ]

AN69

DDR0_DQ[3 ]

AL70

DDR0_DQ[4 ]

AL69

DDR0_DQ[5 ]

AN70

DDR0_DQ[6 ]

AN71

DDR0_DQ[7 ]

AR70

DDR0_DQ[8 ]

AR68

DDR0_DQ[9 ]

AU71

DDR0_DQ[1 0]

AU68

DDR0_DQ[1 1]

AR71

DDR0_DQ[1 2]

AR69

DDR0_DQ[1 3]

AU70

DDR0_DQ[1 4]

AU69

DDR0_DQ[1 5]

BB65

DDR0_DQ[1 6]/DDR0_DQ[32 ]

DDR0_DQ[1 7]/DDR0_DQ[33 ]

DDR0_DQ[1 8]/DDR0_DQ[34 ]

AY63

DDR0_DQ[1 9]/DDR0_DQ[35 ]

BA65

DDR0_DQ[2 0]/DDR0_DQ[36 ]

AY65

DDR0_DQ[2 1]/DDR0_DQ[37 ]

BA63

DDR0_DQ[2 2]/DDR0_DQ[38 ]

BB63

DDR0_DQ[2 3]/DDR0_DQ[39 ]

BA61

DDR0_DQ[2 4]/DDR0_DQ[40 ]

DDR0_DQ[2 5]/DDR0_DQ[41 ]

BB59

DDR0_DQ[2 6]/DDR0_DQ[42 ]

DDR0_DQ[2 7]/DDR0_DQ[43 ]

BB61

DDR0_DQ[2 8]/DDR0_DQ[44 ]

AY61

DDR0_DQ[2 9]/DDR0_DQ[45 ]

BA59

DDR0_DQ[3 0]/DDR0_DQ[46 ]

AY59

DDR0_DQ[3 1]/DDR0_DQ[47 ]

AY39

DDR0_DQ[3 2]/DDR1_DQ[0]

DDR0_DQ[3 3]/DDR1_DQ[1]

AY37

DDR0_DQ[3 4]/DDR1_DQ[2]

DDR0_DQ[3 5]/DDR1_DQ[3]

BB39

DDR0_DQ[3 6]/DDR1_DQ[4]

BA39

DDR0_DQ[3 7]/DDR1_DQ[5]

BA37

DDR0_DQ[3 8]/DDR1_DQ[6]

BB37

DDR0_DQ[3 9]/DDR1_DQ[7]

AY35

DDR0_DQ[4 0]/DDR1_DQ[8]

DDR0_DQ[4 1]/DDR1_DQ[9]

AY33

DDR0_DQ[4 2]/DDR1_DQ[10 ]

DDR0_DQ[4 3]/DDR1_DQ[11 ]

BB35

DDR0_DQ[4 4]/DDR1_DQ[12 ]

BA35

DDR0_DQ[4 5]/DDR1_DQ[13 ]

BA33

DDR0_DQ[4 6]/DDR1_DQ[14 ]

BB33

DDR0_DQ[4 7]/DDR1_DQ[15 ]

AY31

DDR0_DQ[4 8]/DDR1_DQ[32 ]

DDR0_DQ[4 9]/DDR1_DQ[33 ]

AY29

DDR0_DQ[5 0]/DDR1_DQ[34 ]

DDR0_DQ[5 1]/DDR1_DQ[35 ]

BB31

DDR0_DQ[5 2]/DDR1_DQ[36 ]

BA31

DDR0_DQ[5 3]/DDR1_DQ[37 ]

BA29

DDR0_DQ[5 4]/DDR1_DQ[38 ]

BB29

DDR0_DQ[5 5]/DDR1_DQ[39 ]

AY27

DDR0_DQ[5 6]/DDR1_DQ[40 ]

DDR0_DQ[5 7]/DDR1_DQ[41 ]

AY25

DDR0_DQ[5 8]/DDR1_DQ[42 ]

DDR0_DQ[5 9]/DDR1_DQ[43 ]

BB27

DDR0_DQ[6 0]/DDR1_DQ[44 ]

BA27

DDR0_DQ[6 1]/DDR1_DQ[45 ]

BA25

DDR0_DQ[6 2]/DDR1_DQ[46 ]

BB25

DDR0_DQ[6 3]/DDR1_DQ[47 ]

940432

01V0100 00015

IL Channel A[0..63]

NIL Channel A[0..15]

NIL Channel A[32..47]

NIL Channel B[0..15]

NIL Channel B[32..47]

IL Channel A DQS[0..7]

NIL Channel A

DQS[0,1,4,5]

NIL Channel B

DQS[0,1,4,5]

DDR CH - A

DDR0_MA[5 ]/DDR0_CAA[0] /DDR0_MA[5]

DDR0_MA[9 ]/DDR0_CAA[1] /DDR0_MA[9]

DDR0_MA[6 ]/DDR0_CAA[2] /DDR0_MA[6]

DDR0_MA[8 ]/DDR0_CAA[3] /DDR0_MA[8]

DDR0_MA[7 ]/DDR0_CAA[4] /DDR0_MA[7]

DDR0_BA[2 ]/DDR0_CAA[5 ]/DDR0_BG[0]

DDR0_MA[1 2]/DDR0_CAA[6 ]/DDR0_MA[12 ]

DDR0_MA[1 1]/DDR0_CAA[7 ]/DDR0_MA[11 ]

DDR0_MA[1 5]/DDR0_CAA[8 ]/DDR0_ACT#

DDR0_MA[1 4]/DDR0_CAA[9 ]/DDR0_BG[1]

DDR0_MA[1 3]/DDR0_CAB[0 ]/DDR0_MA[13 ]

DDR0_CAS# /DDR0_CAB[1] /DDR0_MA[15]

DDR0_WE #/DDR0_CAB[2 ]/DDR0_MA[14 ]

DDR0_RAS# /DDR0_CAB[3] /DDR0_MA[16]

DDR0_BA[0 ]/DDR0_CAB[4 ]/DDR0_BA[0]

DDR0_MA[2 ]/DDR0_CAB[5] /DDR0_MA[2]

DDR0_BA[1 ]/DDR0_CAB[6 ]/DDR0_BA[1]

DDR0_MA[1 0]/DDR0_CAB[7 ]/DDR0_MA[10 ]

DDR0_MA[1 ]/DDR0_CAB[8] /DDR0_MA[1]

DDR0_MA[0 ]/DDR0_CAB[9] /DDR0_MA[0]

DDR0_DQSN[ 2]/DDR0_DQSN[ 4]

DDR0_DQSP [2]/DDR0_DQS P[4]

DDR0_DQSN[ 3]/DDR0_DQSN[ 5]

DDR0_DQSP [3]/DDR0_DQS P[5]

DDR0_DQSN[ 4]/DDR1_DQSN[ 0]

DDR0_DQSP [4]/DDR1_DQS P[0]

DDR0_DQSN[ 5]/DDR1_DQSN[ 1]

DDR0_DQSP [5]/DDR1_DQS P[1]

DDR0_DQSN[ 6]/DDR1_DQSN[ 4]

DDR0_DQSP [6]/DDR1_DQS P[4]

DDR0_DQSN[ 7]/DDR1_DQSN[ 5]

DDR0_DQSP [7]/DDR1_DQS P[5]

DDR0_VREF_ DQ

DDR1_VREF_ DQ

DDR_VTT_CNTL

DDR0_CKN[0 ]

DDR0_CKP[ 0]

DDR0_CKN[1 ]

DDR0_CKP[ 1]

DDR0_CKE[ 0]

DDR0_CKE[ 1]

DDR0_CKE[ 2]

DDR0_CKE[ 3]

DDR0_CS#[ 0]

DDR0_CS#[ 1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[3 ]

DDR0_MA[4 ]

DDR0_DQSN[ 0]

DDR0_DQSP [0]

DDR0_DQSN[ 1]

DDR0_DQSP [1]

DDR0_ALE RT#

DDR0_PAR

DDR_VREF_C A

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

AW50

AT52

AY67

AY68

BA67

AW67

M_A_A5

M_A_A9

M_A_A6

M_A_A8

M_A_A7

M_A_A12

M_A_A11

M_A_A13

M_A_A2

M_A_A10

M_A_A1

M_A_A0

M_A_A3

M_A_A4

M_A_DQS# 0

M_A_DQS0

M_A_DQS# 1

M_A_DQS1

M_A_DQS# 4

M_A_DQS4

M_A_DQS# 5

M_A_DQS5

M_B_DQS# 0

M_B_DQS0

M_B_DQS# 1

M_B_DQS1

M_B_DQS# 4

M_B_DQS4

M_B_DQS# 5

M_B_DQS5

DDR_VTT_CTRL

M_A_DIM0_ CK_DDR0_DN 15,16

M_A_DIM0_ CK_DDR0_DP 15,16

M_A_DIM0_ CKE0 15,16

M_A_DIM0_ CS0_N 15,16

M_A_DIM0_ ODT0 15,16

M_A_BG0 15,16

M_A_ACT_N 15,16

M_A_A15 _CAS_N 15,16

M_A_A14 _WE_N 15,16

M_A_A16 _RAS_N 15,16

M_A_BA0 15,16

M_A_BA1 15,16

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_DQS[ 7:0] 16

M_A_DQS# [7:0] 16

M_A_DQS7

M_A_DQS6

M_A_DQS5

M_A_DQS4

M_A_DQS3

M_A_DQS2

M_A_DQS1

M_A_DQS0

M_A_DQS# 7

M_A_DQS# 6

M_A_DQS# 5

M_A_DQS# 4

M_A_DQS# 3

M_A_DQS# 2

M_A_DQS# 1

M_A_DQS# 0

DDR0_A_A LERT_N 15,1 6

DDR0_A_P ARITY 1 5,16

DDR_VREF_C A 19

DDR_VREF_D Q 19

M_A_D[31 ..16]16

M_A_D[63 ..48]16

M_B_D[31 ..16]17

M_B_D[63 ..48]17

M_A_A[13 :0] 15,16

+1.2V

M_A_D16

M_A_D17

M_A_D18

M_A_D19

M_A_D20

M_A_D21

M_A_D22

M_A_D23

M_A_D24

M_A_D25

M_A_D26

M_A_D27

M_A_D28

M_A_D29

M_A_D30

M_A_D31

M_A_D48

M_A_D49

M_A_D50

M_A_D51

M_A_D52

M_A_D53

M_A_D54

M_A_D55

M_A_D56

M_A_D57

M_A_D58

M_A_D59

M_A_D60

M_A_D61

M_A_D62

M_A_D63

M_B_D16

M_B_D17

M_B_D18

M_B_D19

M_B_D20

M_B_D21

M_B_D22

M_B_D23

M_B_D24

M_B_D25

M_B_D26

M_B_D27

M_B_D28

M_B_D29

M_B_D30

M_B_D31

M_B_D48

M_B_D49

M_B_D50

M_B_D51

M_B_D52

M_B_D53

M_B_D54

M_B_D55

M_B_D56

M_B_D57

M_B_D58

M_B_D59

M_B_D60

M_B_D61

M_B_D62

M_B_D63

U0301C

AF65

DDR1_DQ[0 ]/DDR0_DQ[16]

AF64

DDR1_DQ[1 ]/DDR0_DQ[17]

AK65

DDR1_DQ[2 ]/DDR0_DQ[18]

AK64

DDR1_DQ[3 ]/DDR0_DQ[19]

AF66

DDR1_DQ[4 ]/DDR0_DQ[20]

AF67

DDR1_DQ[5 ]/DDR0_DQ[21]

AK67

DDR1_DQ[6 ]/DDR0_DQ[22]

AK66

DDR1_DQ[7 ]/DDR0_DQ[23]

AF70

DDR1_DQ[8 ]/DDR0_DQ[24]

AF68

DDR1_DQ[9 ]/DDR0_DQ[25]

AH71

DDR1_DQ[1 0]/DDR0_DQ[26 ]

AH68

DDR1_DQ[1 1]/DDR0_DQ[27 ]

AF71

DDR1_DQ[1 2]/DDR0_DQ[28 ]

AF69

DDR1_DQ[1 3]/DDR0_DQ[29 ]

AH70

DDR1_DQ[1 4]/DDR0_DQ[30 ]

AH69

DDR1_DQ[1 5]/DDR0_DQ[31 ]

AT66

DDR1_DQ[1 6]/DDR0_DQ[48 ]

AU66

DDR1_DQ[1 7]/DDR0_DQ[49 ]

AP65

DDR1_DQ[1 8]/DDR0_DQ[50 ]

AN65

DDR1_DQ[1 9]/DDR0_DQ[51 ]

AN66

DDR1_DQ[2 0]/DDR0_DQ[52 ]

AP66

DDR1_DQ[2 1]/DDR0_DQ[53 ]

AT65

DDR1_DQ[2 2]/DDR0_DQ[54 ]

AU65

DDR1_DQ[2 3]/DDR0_DQ[55 ]

AT61

DDR1_DQ[2 4]/DDR0_DQ[56 ]

AU61

DDR1_DQ[2 5]/DDR0_DQ[57 ]

AP60

DDR1_DQ[2 6]/DDR0_DQ[58 ]

AN60

DDR1_DQ[2 7]/DDR0_DQ[59 ]

AN61

DDR1_DQ[2 8]/DDR0_DQ[60 ]

AP61

DDR1_DQ[2 9]/DDR0_DQ[61 ]

AT60

DDR1_DQ[3 0]/DDR0_DQ[62 ]

AU60

DDR1_DQ[3 1]/DDR0_DQ[63 ]

AU40

DDR1_DQ[3 2]/DDR1_DQ[16 ]

AT40

DDR1_DQ[3 3]/DDR1_DQ[17 ]

AT37

DDR1_DQ[3 4]/DDR1_DQ[18 ]

AU37

DDR1_DQ[3 5]/DDR1_DQ[19 ]

AR40

DDR1_DQ[3 6]/DDR1_DQ[20 ]

AP40

DDR1_DQ[3 7]/DDR1_DQ[21 ]

AP37

DDR1_DQ[3 8]/DDR1_DQ[22 ]

AR37

DDR1_DQ[3 9]/DDR1_DQ[23 ]

AT33

DDR1_DQ[4 0]/DDR1_DQ[24 ]

AU33

DDR1_DQ[4 1]/DDR1_DQ[25 ]

AU30

DDR1_DQ[4 2]/DDR1_DQ[26 ]

AT30

DDR1_DQ[4 3]/DDR1_DQ[27 ]

AR33

DDR1_DQ[4 4]/DDR1_DQ[28 ]

AP33

DDR1_DQ[4 5]/DDR1_DQ[29 ]

AR30

DDR1_DQ[4 6]/DDR1_DQ[30 ]

AP30

DDR1_DQ[4 7]/DDR1_DQ[31 ]

AU27

DDR1_DQ[4 8]

AT27

DDR1_DQ[4 9]

AT25

DDR1_DQ[5 0]

AU25

DDR1_DQ[5 1]

AP27

DDR1_DQ[5 2]

AN27

DDR1_DQ[5 3]

AN25

DDR1_DQ[5 4]

AP25

DDR1_DQ[5 5]

AT22

DDR1_DQ[5 6]

AU22

DDR1_DQ[5 7]

AU21

DDR1_DQ[5 8]

AT21

DDR1_DQ[5 9]

AN22

DDR1_DQ[6 0]

AP22

DDR1_DQ[6 1]

AP21

DDR1_DQ[6 2]

AN21

DDR1_DQ[6 3]

940432

01V0100 00015

+3VSUS+3VS

IL Channel B[0..63]

SKL_ULT

NIL Channel A[16..31]

NIL Channel A[48..63]

DDR1_MA[5 ]/DDR1_CAA[0] /DDR1_MA[5]

DDR1_MA[9 ]/DDR1_CAA[1] /DDR1_MA[9]

DDR1_MA[6 ]/DDR1_CAA[2] /DDR1_MA[6]

DDR1_MA[8 ]/DDR1_CAA[3] /DDR1_MA[8]

DDR1_MA[7 ]/DDR1_CAA[4] /DDR1_MA[7]

DDR1_BA[2 ]/DDR1_CAA[5 ]/DDR1_BG[0]

DDR1_MA[1 2]/DDR1_CAA[6 ]/DDR1_MA[12 ]

DDR1_MA[1 1]/DDR1_CAA[7 ]/DDR1_MA[11 ]

DDR1_MA[1 5]/DDR1_CAA[8 ]/DDR1_ACT#

DDR1_MA[1 4]/DDR1_CAA[9 ]/DDR1_BG[1]

DDR1_MA[1 3]/DDR1_CAB[0 ]/DDR1_MA[13 ]

DDR1_CAS# /DDR1_CAB[1] /DDR1_MA[15]

DDR1_WE #/DDR1_CAB[2 ]/DDR1_MA[14 ]

DDR1_RAS# /DDR1_CAB[3] /DDR1_MA[16]

DDR1_BA[0 ]/DDR1_CAB[4 ]/DDR1_BA[0]

DDR1_MA[2 ]/DDR1_CAB[5] /DDR1_MA[2]

DDR1_BA[1 ]/DDR1_CAB[6 ]/DDR1_BA[1]

DDR1_MA[1 0]/DDR1_CAB[7 ]/DDR1_MA[10 ]

DDR1_MA[1 ]/DDR1_CAB[8] /DDR1_MA[1]

DDR1_MA[0 ]/DDR1_CAB[9] /DDR1_MA[0]

NIL Channel B[16..31]

NIL Channel B[48..63]

IL Channel B DQS[0..7]

NIL Channel A

DQS[2,3,6,7]

NIL Channel B

DQS[2,3,6,7]

DDR CH - B

DDR1_DQSN[ 0]/DDR0_DQSN[ 2]

DDR1_DQSP [0]/DDR0_DQS P[2]

DDR1_DQSN[ 1]/DDR0_DQSN[ 3]

DDR1_DQSP [1]/DDR0_DQS P[3]

DDR1_DQSN[ 2]/DDR0_DQSN[ 6]

DDR1_DQSP [2]/DDR0_DQS P[6]

DDR1_DQSN[ 3]/DDR0_DQSN[ 7]

DDR1_DQSP [3]/DDR0_DQS P[7]

DDR1_DQSN[ 4]/DDR1_DQSN[ 2]

DDR1_DQSP [4]/DDR1_DQS P[2]

DDR1_DQSN[ 5]/DDR1_DQSN[ 3]

DDR1_DQSP [5]/DDR1_DQS P[3]

DDR1_CKN[0 ]

DDR1_CKN[1 ]

DDR1_CKP[ 0]

DDR1_CKP[ 1]

DDR1_CKE[ 0]

DDR1_CKE[ 1]

DDR1_CKE[ 2]

DDR1_CKE[ 3]

DDR1_CS#[ 0]

DDR1_CS#[ 1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3 ]

DDR1_MA[4 ]

DDR1_DQSN[ 6]

DDR1_DQSP [6]

DDR1_DQSN[ 7]

DDR1_DQSP [7]

DDR1_ALE RT#

DDR1_PAR

DRAM_RESE T#

DDR_RCOMP[0 ]

DDR_RCOMP[1 ]

DDR_RCOMP[2 ]

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

M_A_DQS# 2

M_A_DQS2

M_A_DQS# 3

M_A_DQS3

M_A_DQS# 6

M_A_DQS6

M_A_DQS# 7

M_A_DQS7

M_B_DQS# 2

M_B_DQS2

M_B_DQS# 3

M_B_DQS3

M_B_DQS# 6

M_B_DQS6

M_B_DQS# 7

M_B_DQS7

CPUDRAMRST#

SM_RCOMP_ 0

SM_RCOMP_ 1

SM_RCOMP_ 2

M_B_DIM0_ CK_DDR0_DN 15,17

M_B_DIM0_ CK_DDR0_DP 15,17

M_B_DIM0_ CKE0 15,17

M_B_DIM0_ CS0_N 15,17

M_B_DIM0_ ODT0 15,17

M_B_A5

M_B_A9

M_B_A6

M_B_A8

M_B_A7

M_B_A12

M_B_A11

M_B_A13

M_B_A2

M_B_A10

M_B_A1

M_B_A0

M_B_A3

M_B_A4

+1.2V

12

DDR0_B_A LERT_N 15,1 7

1 2

R0402 200Ohm1%

1 2

R0403 80.6Ohm1%

1 2

R0404 100Ohm1%

DDR0_B_P ARITY 1 5,17

M_B_BG0 15,17

M_B_ACT_N 15,17

M_B_A15 _CAS_N 15,17

M_B_A14 _WE_N 15,17

M_B_A16 _RAS_N 15,17

M_B_BA0 15,17

M_B_BA1 15,17

M_B_DQS7

M_B_DQS6

M_B_DQS5

M_B_DQS4

M_B_DQS3

M_B_DQS2

M_B_DQS1

M_B_DQS0

M_B_DQS# 7

M_B_DQS# 6

M_B_DQS# 5

M_B_DQS# 4

M_B_DQS# 3

M_B_DQS# 2

M_B_DQS# 1

M_B_DQS# 0

R0405

470Ohm

R0401

2

0Ohm

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_DQS[ 7:0] 17

M_B_DQS# [7:0] 17

1

12

C0402

@

0.1UF/25V

Controls reset to the memory

subsystems, and is used on

DDR3L, DDR4

546765_SKL_MOW

DDR4/3L Reset signal - DRAMRST

It is recommended not to install any capacitor

on DDR Reset signal (DRAMRST).

(not applicable to LPDDR3).

M_B_A[13 :0] 15,17

DDR4_DRAMRS T_R_N 16,17

12

12

C0401

U0401

1

NC

2

A

3

12

R0406

10KOhm@

Symbol U0301 B

A A

BYTE 0

BYTE 1

BYTE 2

BYTE 3

BYTE 4

BYTE 5

BYTE 6

BYTE 7

ChannelA DQ[0..63]

DQS/DQS#[0..7]

Non-interleavedinterleaved(Symbol default)

ChannelA DQ[0..15]

DQS/DQS#[0,1]

ChannelADQ[32..47]

DQS/DQS#[4,5]

ChannelB DQ[0..15]

DQS/DQS#[0,1]

ChannelB DQ[32..47]

DQS/DQS#[4,5]

5

Symbol U0301 C

BYTE 0

BYTE 1

BYTE 2

BYTE 3

BYTE 4

BYTE 5

BYTE 6

BYTE 7

ChannelB DQ[0..63]

DQS/DQS#[0..7]

Non-interleavedinterleaved(Symbol default)

ChannelA DQ[16..31]

DQS/DQS#[2,3]

ChannelADQ[48..63]

DQS/DQS#[6,7]

ChannelB DQ[16..31]

DQS/DQS#[2,3]

ChannelB DQ[48..63]

DQS/DQS#[6,7]

4

GND

74AUP1G 07GW

5

VCC

Y

4

0.1UF/16V

3

12

R0412

220KOhm

12

R0407

220KOhm

@

R0411

2MOHM

@

DDR_PG_CTRL 83

DDR_VTT_CNTL to VTT

power ready < 35us (tCPU18)

<Variant Name>

<Variant Name>

<Variant Name>

CPU(2)_DDR4

CPU(2)_DDR4

CPU(2)_DDR4

Title :

Title :

1

Title :

Engineer:

Engineer:

Engineer:

Andy Kao

Andy Kao

Andy Kao

4 97Monday, July 11, 2016

4 97Monday, July 11, 2016

4 97Monday, July 11, 2016

Rev

Rev

Rev

1.0

1.0

1.0

of

PEGATRON PROPRIETARY AND CONFIDENTI AL

PEGATRON PROPRIETARY AND CONFIDENTI AL

PEGATRON PROPRIETARY AND CONFIDENTI AL

BG1/HW 3

BG1/HW 3

BG1/HW 3

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

X3

X3

Date: Sheet of

Date: Sheet of

2

Date: Sheet

X3

5

V

4

3

2

1

D D

+VCORE

+VCCSTG

+VCCST_CPU

+VCORE 80

+VCCSTG 3,7

+VCCST_CPU 3,7,9,25,32

29A

+VCORE

C C

SKL 2+2, +V1.8VS_EDRAM / +V_EDRAM_VR / +V_EOPIO_VR

From Intel, SKL-U 2+2 reserve these pins PD to GND Pull H/L at EE side

1 2

R0528 0Ohm@

1 2

R0529 0Ohm@

1 2

R0530 0Ohm@

B B

R0535 0Ohm@

R0531 0Ohm@

R0532 0Ohm@

R0533 0Ohm@

R0534 0Ohm@

1 2

1 2

1 2

1 2

1 2

RSVD NC

AK33

AK35

AK37

AK38

AK40

AL33

AL37

AL40

AM32

AM33

AM35

AM37

AM38

G30

AK32

AB62

G61

AC63

AE63

AE62

AG62

AL63

AJ62

A30

A34

A39

A44

K32

P62

V62

H63

01V01000001 5

U0301L

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6

VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

RSVD_3

RSVD_4

VCCOPC_1

VCCOPC_2

VCCOPC_3

VCC_OPC_1P8_1

VCC_OPC_1P8_2

VCCOPC_SENSE

VSSOPC_SENSE

VCCEOPIO_1

VCCEOPIO_2

VCCEOPIO_SENSE

VSSEOPIO_SENSE

940432

CPU POWER 1 OF 4

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_SENSE

VSS_SENSE

VIDALERT#

VIDSCK

VIDSOUT

VCCSTG

+VCORE

G32

G33

G35

G37

G38

G40

G42

J30

J33

J37

J40

K33

K35

K37

K38

K40

K42

K43

E32

E33

B63

VIDALERT#

A63

VIDSCK

D64

VIDSOUT

G20

+VCCFUSEPRG

+VCORE

12

R0536

100Ohm 1%

12

R0537

100Ohm

R0518 0Ohm

R0519 0Ohm

SP0505

NB_R0402_ 20MIL_SMALL

VCORE_VCCSENSE 8 0

VCORE_VSSSENSE 80

1 2

R0517 220Oh m 1%

12

12

+VCCSTG

1 2

CPU side VR side

+VCCST_CPU

12

R0520

56Ohm

1%

VIDALERT#_R

1%

+VCCST_CPU

VIDSCK_R

12

R0521

100Ohm1%

VIDSOUT_R

+VCCST_CPU

12

+VCCST_CPU

12

R0522

45.3Ohm

1%

R0523

100Ohm

1%

R0524 0Ohm

12

C0505

0.1UF/16V

@

1 2

R0525 51Ohm1%

1 2

R0526 10Ohm1%

12

VR_SVID_ALERT# 8 0

VR_SVID_CLK 80

VR_SVID_DATA 80

A A

CPU(3)_+VCCCORE

CPU(3)_+VCCCORE

CPU(3)_+VCCCORE

Title :

Title :

PEGATRON PROPRIETARY AND CONFIDENTIAL

PEGATRON PROPRIETARY AND CONFIDENTIAL

PEGATRON PROPRIETARY AND CONFIDENTIAL

BG1/HW3

BG1/HW3

BG1/HW3

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

X3

X3

X3

Engineer:

Engineer:

Engineer:

1

Title :

Andy Kao

Andy Kao

Andy Kao

5 97Monday, July 11, 2016

5 97Monday, July 11, 2016

5 97Monday, July 11, 2016

Rev

Rev

Rev

1.0

1.0

1.0

5

V

4

3

2

1

+VCCGT

+VCCGT 80

31A

N70

N71

R63

R64

R65

R66

R67

R68

R69

R70

R71

T62

U65

U68

U71

W63

W64

W65

W66

W67

W68

W69

W70

W71

Y62

AK42

AK43

AK45

AK46

AK48

AK50

AK52

AK53

AK55

AK56

AK58

AK60

AK70

AL43

AL46

AL50

AL53

AL56

AL60

AM48

AM50

AM52

AM53

AM56

AM58

AU58

AU63

BB57

BB66

AK62

AL61

+VCCGT

1 2

R0601 0Ohm@

1 2

R0608 0Ohm@

1 2

R0604 0Ohm@

1 2

R0605 0Ohm@

1 2

R0606 0Ohm@

1 2

R0607 0Ohm@

1 2

R0602 0Ohm@

1 2

R0603 0Ohm@

From Intel, SKL-U 2+2 reserve these pins PD to GND

VccGTx power rail is unconnected for Processors without GT3/4.

+VCCGT

D D

C C

+VCCGT

R0609

100Ohm 1%

R0610

100Ohm 1%

12

12

VCCGT_VCCSENSE80

VCCGT_VSSSENSE80

AA63

AA64

AA66

AA67

AA69

AA70

AA71

AC64

AC65

AC66

AC67

AC68

AC69

AC70

AC71

A48

A53

A58

A62

A66

J43

J45

J46

J48

J50

J52

J53

J55

J56

J58

J60

K48

K50

K52

K53

K55

K56

K58

K60

L62

L63

L64

L65

L66

L67

L68

L69

L70

L71

M62

N63

N64

N66

N67

N69

J70

J69

U0301M

CPU POWER 2 OF 4

VCCGT_1

VCCGT_2

VCCGT_3

VCCGT_4

VCCGT_5

VCCGT_6

VCCGT_7

VCCGT_8

VCCGT_9

VCCGT_10

VCCGT_11

VCCGT_12

VCCGT_13

VCCGT_14

VCCGT_15

VCCGT_16

VCCGT_17

VCCGT_18

VCCGT_19

VCCGT_20

VCCGT_21

VCCGT_22

VCCGT_23

VCCGT_24

VCCGT_25

VCCGT_26

VCCGT_27

VCCGT_28

VCCGT_29

VCCGT_30

VCCGT_31

VCCGT_32

VCCGT_33

VCCGT_34

VCCGT_35

VCCGT_36

VCCGT_37

VCCGT_38

VCCGT_39

VCCGT_40

VCCGT_41

VCCGT_42

VCCGT_43

VCCGT_44

VCCGT_45

VCCGT_46

VCCGT_47

VCCGT_48

VCCGT_49

VCCGT_50

VCCGT_51

VCCGT_52

VCCGT_53

VCCGT_54

VCCGT_55

VCCGT_SENSE

VSSGT_SENSE

940432

01V010000015

VCCGT_56

VCCGT_57

VCCGT_58

VCCGT_59

VCCGT_60

VCCGT_61

VCCGT_62

VCCGT_63

VCCGT_64

VCCGT_65

VCCGT_66

VCCGT_67

VCCGT_68

VCCGT_69

VCCGT_70

VCCGT_71

VCCGT_72

VCCGT_73

VCCGT_74

VCCGT_75

VCCGT_76

VCCGT_77

VCCGT_78

VCCGT_79

VCCGT_80

VccGTx_1

VccGTx_2

VccGTx_3

VccGTx_4

VccGTx_5

VccGTx_6

VccGTx_7

VccGTx_8

VccGTx_9

VccGTx_10

VccGTx_11

VccGTx_12

VccGTx_13

VccGTx_14

VccGTx_15

VccGTx_16

VccGTx_17

VccGTx_18

VccGTx_19

VccGTx_20

VccGTx_21

VccGTx_22

VccGTx_23

VccGTx_24

VccGTx_25

VccGTx_26

VccGTx_27

VccGTx_28

VccGTx_29

VCCGTx_SENSE

VSSGTx_SENSE

B B

A A

CPU(4)_+VCCGT

CPU(4)_+VCCGT

CPU(4)_+VCCGT

Title :

Title :

Engineer:

Engineer:

Engineer:

1

Title :

Andy Kao

Andy Kao

Andy Kao

6 97Monday, July 11, 2016

6 97Monday, July 11, 2016

6 97Monday, July 11, 2016

Rev

Rev

Rev

1.0

1.0

1.0

PEGATRON PROPRIETARY AND CONFIDENTI AL

PEGATRON PROPRIETARY AND CONFIDENTI AL

PEGATRON PROPRIETARY AND CONFIDENTI AL

BG1/HW3

BG1/HW3

BG1/HW3

Size Project Name

Size Project Name

Size Project Name

C

C

C

X3

X3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

X3

5

V

D D

4

3

+1.2V

+VCCST_CPU

+VCCSTG

+VCCIO

+VCCSA

+5VSUS

+12VSUS

+1.0VSUS

+1.0V

2

+1.2V 4,15,16,17,19,57 ,83

+VCCST_CPU 3,5,9,25,32

+VCCSTG 3,5

+VCCIO 3 ,9,57,91

+VCCSA 80

+5VSUS 41,42,52,5 6,64,81

+12VSUS 28,81,91

+1.0VSUS 26 ,82

+1.0V 57,91

1

+1.2V

12

C0703

10UF/6.3V

12

12

C0704

C0705

10UF/6.3V

10UF/6.3V

+1.2V

1 2

R0701 NB_R0402_2 0MIL_SMALL

12

12

C C

B B

C0701

10UF/6.3V

C0702

10UF/6.3V

C0701 - C0704 : Near by package

C0705 - C0710 : Underneath the package

12

12

C0706

C0707

10UF/6.3V

1UF/6.3V

+VDDQ_CPU_C LK

12

C0711

C0712

1UF/6.3V

C0713

1UF/6.3V

C0714

0.1UF/16V

C0715

0.1UF/16V

0.1UF/16V

12

C0716

0.1UF/16V

+VCCST_CPU

12

+VCCSTG

12

+VCCSFR_OC

12

+VCCSFR

12

12

C0708

1UF/6.3V

12

C0709

1UF/6.3V

12

C0710

1UF/6.3V

60mA

20mA

100mA

130mA

AU23

AU28

AU35

AU42

BB23

BB32

BB41

BB47

BB51

AM40

A18

A22

AL23

K20

K21

+1.0V

+1.0V

+VCCIO

U0301N

CPU POWER 3 OF 4

VDDQ_1

VDDQ_2

VDDQ_3

VDDQ_4

VDDQ_5

VDDQ_6

VDDQ_7

VDDQ_8

VDDQ_9

VDDQC

VCCST

VCCSTG

VCCPLL_OC

VccPLL_1

VccPLL_2

940432

01V01000001 5

VCCSA_10

VCCSA_11

VCCSA_12

VCCSA_13

VCCSA_14

VCCIO_SENSE

VSSIO_SENSE

VSSSA_SENSE

VCCSA_SENSE

R0710

nb_r0603_s hort_32mil_small

1 2

R0711

nb_r0603_s hort_32mil_small

1 2

R0713

nb_r0603_s hort_32mil_small

1 2

AK28

VCCIO_1

AK30

VCCIO_2

AL30

VCCIO_3

AL42

VCCIO_4

AM28

VCCIO_5

AM30

VCCIO_6

AM42

VCCIO_7

AK23

VCCSA_1

AK25

VCCSA_2

G23

VCCSA_3

G25

VCCSA_4

G27

VCCSA_5

G28

VCCSA_6

J22

VCCSA_7

J23

VCCSA_8

J27

VCCSA_9

K23

K25

K27

K28

K30

AM23

AM22

H21

H20

+VCCST_CPU

141127 65u sec full load ready

+VCCSFR

+VCCSTG

141030 Merge Power PDDG0.91 Table5-1

141127 65u sec full load ready

3.1A2.8A

4.5A

VCCIO_VR_FB

VSSIO_VR_FB

1%

+VCCSA

VCCSA_VSSSENSE 80

1 2

R0702

100Ohm1%

VCCSA_VCCSENSE 80

1 2

R0703

100Ohm

+1.2V

+VCCIO

12

12

C0717

1UF/6.3V

C0718

1UF/6.3V

12

+VCCIO

C0719

1UF/6.3V

12

12

R0714

100Ohm

1%

@

R0715

100Ohm

1%

@

+VCCSA

+VCCSFR_OC

1 2

R0709 NB_R0402_2 0MIL_SMALL

R1.1_10L

12

C0720

1UF/6.3V

Reserved PH/PD

A A

CPU(5)_+VDDQ/IO/SA

CPU(5)_+VDDQ/IO/SA

CPU(5)_+VDDQ/IO/SA

Title :

Title :

PEGATRON PROPRIETARY AND CONFIDENTIAL

PEGATRON PROPRIETARY AND CONFIDENTIAL

PEGATRON PROPRIETARY AND CONFIDENTIAL

BG1/HW3

BG1/HW3

BG1/HW3

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

X3

X3

X3

Engineer:

Engineer:

Engineer:

1

Title :

Andy Kao

Andy Kao

Andy Kao

7 97Monday, July 11, 2016

7 97Monday, July 11, 2016

7 97Monday, July 11, 2016

Rev

Rev

Rev

1.0

1.0

1.0

reference 543977_543977_SKL_PDDG_Rev0_91

5

V

4

3

2

1

AT63

AT68

AT71

AU10

AU15

AU20

AU32

AU38

AV68

AV69

AV70

AV71

AW10

AW12

AW14

AW16

AW18

AW21

AW23

AW26

AW28

AW30

AW32

AW34

AW36

AW38

AW41

AW43

AW45

AW47

AW49

AW51

AW53

AW55

AW57

AW60

AW62

AW64

AW66

AY66

BA10

BA14

BA18

BA23

BA28

BA32

BA36

BA45

AV1

AW6

AW8

B10

B14

B18

B22

B30

B34

B39

B44

B48

B53

B58

B62

B66

B71

BA1

BA2

F68

U0301Q

GND 2 OF 3

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

940432

01V010000015

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

VSS_243

VSS_244

VSS_245

VSS_246

VSS_247

VSS_248

VSS_249

VSS_250

VSS_251

VSS_252

VSS_253

VSS_254

VSS_255

VSS_256

VSS_257

VSS_258

VSS_259

VSS_260

VSS_261

VSS_262

VSS_263

VSS_264

VSS_265

VSS_266

VSS_267

VSS_268

VSS_269

VSS_270

VSS_271

VSS_272

VSS_273

VSS_274

VSS_275

VSS_276

VSS_277

BA49

BA53

BA57

BA6

BA62

BA66

BA71

BB18

BB26

BB30

BB34

BB38

BB43

BB55

BB6

BB60

BB64

BB67

BB70

C1

C25

C5

D10

D11

D14

D18

D22

D25

D26

D30

D34

D39

D44

D45

D47

D48

D53

D58

D6

D62

D66

D69

E11

E15

E18

E21

E46

E50

E53

E56

E6

E65

E71

F1

F13

F2

F22

F23

F27

F28

F32

F33

F35

F37

F38

F4

F40

F42

BA41

F8

G10

G22

G43

G45

G48

G5

G52

G55

G58

G6

G60

G63

G66

H15

H18

H71

J11

J13

J25

J28

J32

J35

J38

J42

J8

K16

K18

K22

K61

K63

K64

K65

K66

K67

K68

K70

K71

L11

L16

L17

U0301R

GND 3 OF 3

VSS_278

VSS_279

VSS_280

VSS_281

VSS_282

VSS_283

VSS_284

VSS_285

VSS_286

VSS_287

VSS_288

VSS_289

VSS_290

VSS_291

VSS_292

VSS_293

VSS_294

VSS_295

VSS_296

VSS_297

VSS_298

VSS_299

VSS_300

VSS_301

VSS_302

VSS_303

VSS_304

VSS_305

VSS_306

VSS_307

VSS_308

VSS_309

VSS_310

VSS_311

VSS_312

VSS_313

VSS_314

VSS_315

VSS_316

VSS_317

VSS_318

940432

01V010000015

VSS_319

VSS_320

VSS_321

VSS_322

VSS_323

VSS_324

VSS_325

VSS_326

VSS_327

VSS_328

VSS_329

VSS_330

VSS_331

VSS_332

VSS_333

VSS_334

VSS_335

VSS_336

VSS_337

VSS_338

VSS_339

VSS_340

VSS_341

VSS_342

VSS_343

VSS_344

VSS_345

VSS_346

VSS_347

VSS_348

VSS_349

VSS_350

VSS_351

VSS_352

VSS_353

VSS_354

VSS_355

VSS_356

VSS_357

VSS_358

VSS_359

L18

L2

L20

L4

L8

N10

N13

N19

N21

N6

N65

N68

P17

P19

P20

P21

R13

R6

T15

T17

T18

T2

T21

T4

U10

U63

U64

U66

U67

U69

U70

V16

V17

V18

W13

W6

W9

Y17

Y19

Y20

Y21

U0301P

GND 1 OF 3

A5

VSS_1

A67

VSS_2

A70

VSS_3

AA2

VSS_4

AA4

VSS_5

AA65

VSS_6

AA68

VSS_7

AB15

VSS_8

AB16

VSS_9

AG16

AG17

AG18

AG19

AG20

AG21

AG71

AB18

AB21

AD13

AD16

AD19

AD20

AD21

AD62

AE64

AE65

AE66

AE67

AE68

AE69

AF10

AF15

AF17

AF63

AH13

AH63

AH64

AH67

AJ15

AJ18

AJ20

AK11

AK16

AK18

AK21

AK22

AK27

AK63

AK68

AK69

AL28

AL32

AL35

AL38

AL45

AL48

AL52

AL55

AL58

AL64

AB8

AD8

AF1

AF2

AF4

AH6

AJ4

AK8

AL2

AL4

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

940432

01V010000015

D D

C C

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

AL65

AL66

AM13

AM21

AM25

AM27

AM43

AM45

AM46

AM55

AM60

AM61

AM68

AM71

AM8

AN20

AN23

AN28

AN30

AN32

AN33

AN35

AN37

AN38

AN40

AN42

AN58

AN63

AP10

AP18

AP20

AP23

AP28

AP32

AP35

AP38

AP42

AP58

AP63

AP68

AP70

AR11

AR15

AR16

AR20

AR23

AR28

AR35

AR42

AR43

AR45

AR46

AR48

AR5

AR50

AR52

AR53

AR55

AR58

AR63

AR8

AT2

AT20

AT23

AT28

AT35

AT4

AT42

AT56

AT58

B B

A A

CPU(6)_CPU GND

CPU(6)_CPU GND

CPU(6)_CPU GND

Title :

Title :

Engineer:

Engineer:

Engineer:

1

Title :

Andy Kao

Andy Kao

Andy Kao

8 97Monday, July 11, 2016

8 97Monday, July 11, 2016

8 97Monday, July 11, 2016

Rev

Rev

Rev

1.0

1.0

1.0

PEGATRON PROPRIETARY AND CONFIDENTI AL

PEGATRON PROPRIETARY AND CONFIDENTI AL

PEGATRON PROPRIETARY AND CONFIDENTI AL

BG1/HW3

BG1/HW3

BG1/HW3

Size Project Name

Size Project Name

Size Project Name

C

C

C

X3

X3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

X3

SPARE

V

1

F6

RSVD_51

E3

RSVD_52

C11

RSVD_53

B11

RSVD_54

A11

RSVD_55

D12

RSVD_56

C12

RSVD_57

F52

RSVD_58

2

+VCCIO

+VCCST_CPU

+1.8VSUS

+1.8VSUS

PDG 1.2

Placeholder only. Does not need to be stuffed.

Placement are required for future platform compatibility purpose only.

+VCCST_CPU

1 2

R0930 0Ohm@

1 2

R0931 0Ohm@

VCC_1P8_U12

VCC_1P8_U11

12

C0901

@

0.1UF/25V

@

12

C0902

0.1UF/25V

+VCCIO 3,7,57,91

+VCCST_CPU 3,5,7,25,32

+1.8VSUS 21,22,26,84

AW69

AW68

AU56

AW48

C7

U12

U11

H11

U0301T

RSVD_43

RSVD_44

RSVD_45

RSVD_46

RSVD_47

RSVD_48

RSVD_49

RSVD_50

940432

01V010000015

Remove SNN

RSVD_AY3

Remove SNN

VSS_AY71

SKL_CNL#

3

1 2

R0902 0Ohm

1 2

R0903 0Ohm

From Intel, SKL-U 2+2 remove these pins.

1 2

R0904 100KOhm@

MOW WW48

1. Ball C64 which is PROC_SELECT# needs to be pulled to VCCST for

Cannonlake support via 100K ohm resistor and with no resistor populated

(floating pin) for Skylake.

E68

B67

D65

D67

E70

C68

D68

C67

F71

G69

F70

G68

H70

G71

H69

G70

E63

F63

E66

F66

E60

E8

AY2

AY1

D1

D3

K46

K45

C71

B70

F60

A52

J71

J68

F65

G65

F61

E61

U0301S

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

CFG[18]

CFG[19]

CFG_RCOMP

ITP_PMODE

RSVD_5

RSVD_6

RSVD_7

RSVD_8

RSVD_9

RSVD_10

RSVD_11

RSVD_12

RSVD_13

RSVD_14

RSVD_15

RSVD_16

RSVD_TP_1

RSVD_TP_2

RSVD_17

RSVD_18

VSS_360

VSS_361

RSVD_19

RSVD_20

940432

01V010000015

4

RESERVED SIGNALS-1

CFG0

1 2

R0922 1KOhm@

RSVD_TP_3

RSVD_TP_4

RSVD_TP_5

RSVD_TP_6

RSVD_21

RSVD_22

RSVD_23

RSVD_24

RSVD_25

RSVD_26

RSVD_27

RSVD_28

RSVD_29

RSVD_30

RSVD_31

RSVD_32

RSVD_33

RSVD_34

RSVD_35

RSVD_36

RSVD_37

RSVD_38

RSVD_39

RSVD_40

RSVD_41

RSVD_42

VSS_362

ZVM#

RSVD_TP_7

RSVD_TP_8

MSM#

PROC_SELECT#

BB68

BB69

AK13

AK12

BB2

BA3

AU5

TP5

AT5

TP6

D5

D4

B2

C2

B3

A3

AW1

E1

E2

BA4

BB4

A4

C4

BB5

TP4

A69

B69

AY3

D71

C70

C54

D54

AY4

TP1

BB3

TP2

AY71

AR56

AW71

Remove SNN

AW70

AP56

C64

5

CFG0

T0901

1

CFG2

CFG3

CFG4

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG_RCOMP

ITP_PMODE

1

T0923

1

T0924

1

T0925

1

T0926

1

D D

T0927

T0928

T0929

T0930

T0931

T0919

T0920

T0921

T0922

1

1

1

1

1

1

1

1

1 2

R0901 49.9Ohm1%

Reserve TP for XDP

Remove SNN

AL25

AL27

BA70

C C

Intel confirm NC

T0917

T0918

1

1

RSVD_VSS_F65

RSVD_VSS_G65

BA68

Remove SNN

+VCCIO

12

R0905

0Ohm

@

R0906

1 2

10KOhm

+VCCIO_OUT_CFG_PU

@

1%

B B

A A

5

1 2

R0908 10KOhm

@

1%

1 2

R0910 10KOhm

@

1%

1 2

R0913 10KOhm

@

1%

CFG2

CFG4

CFG7

4

1 2

R0924 1KOhm@

1 2

R0926 1KOhm

1 2

R0929 1KOhm@

CPU(7)_CFG/RSVD

CPU(7)_CFG/RSVD

CPU(7)_CFG/RSVD

Title :

Title :

PEGATRON PROPRIETARY AND CONFIDENTI AL

PEGATRON PROPRIETARY AND CONFIDENTI AL

PEGATRON PROPRIETARY AND CONFIDENTI AL

BG1/HW3

BG1/HW3

BG1/HW3

Size Project Name

Size Project Name

Size Project Name

C

C

C

X3

X3

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

X3

Engineer:

Engineer:

Engineer:

1

Title :

Andy Kao

Andy Kao

Andy Kao

9 97Monday, July 11, 2016

9 97Monday, July 11, 2016

9 97Monday, July 11, 2016

Rev

Rev

Rev

1.0

1.0

1.0

5

V

D D

C C

4

3

2

1

B B

A A

PEGATRON PROPRIETARY AND CONFIDENTIAL

PEGATRON PROPRIETARY AND CONFIDENTIAL

PEGATRON PROPRIETARY AND CONFIDENTIAL

BG1/HW3

BG1/HW3

BG1/HW3

Size Project Name

Size Project Name

Size Project Name

A

A

A

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

X3

X3

X3

2

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

<Title>

<Title>

<Title>

Andy Kao

Andy Kao

Andy Kao

10 97Monday, July 11, 2016

10 97Monday, July 11, 2016

10 97Monday, July 11, 2016

1

Rev

Rev

Rev

1.0

1.0

1.0

5

V

D D

C C

4

3

2

1

B B

A A

PEGATRON PROPRIETARY AND CONFIDENTIAL

PEGATRON PROPRIETARY AND CONFIDENTIAL

PEGATRON PROPRIETARY AND CONFIDENTIAL

BG1/HW3

BG1/HW3

BG1/HW3

Size Project Name

Size Project Name

Size Project Name

A

A

A

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

X3

X3

X3

2

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

<Title>

<Title>

<Title>

Andy Kao

Andy Kao

Andy Kao

11 97Monday, July 11, 2016

11 97Monday, July 11, 2016

11 97Monday, July 11, 2016

1

Rev

Rev

Rev

1.0

1.0

1.0

5

V

D D

C C

4

3

2

1

B B

A A

PEGATRON PROPRIETARY AND CONFIDENTIAL

PEGATRON PROPRIETARY AND CONFIDENTIAL

PEGATRON PROPRIETARY AND CONFIDENTIAL

BG1/HW3

BG1/HW3

BG1/HW3

Size Project Name

Size Project Name

Size Project Name

A

A

A

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

X3

X3

X3

2

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

<Title>

<Title>

<Title>

Andy Kao

Andy Kao

Andy Kao

12 97Monday, July 11, 2016

12 97Monday, July 11, 2016

12 97Monday, July 11, 2016

1

Rev

Rev

Rev

1.0

1.0

1.0

5

V

D D

C C

4

3

2

1

B B

A A

PEGATRON PROPRIETARY AND CONFIDENTIAL

PEGATRON PROPRIETARY AND CONFIDENTIAL

PEGATRON PROPRIETARY AND CONFIDENTIAL

BG1/HW3

BG1/HW3

BG1/HW3

Size Project Name

Size Project Name

Size Project Name

A

A

A

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

X3

X3

X3

2

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

<Title>

<Title>

<Title>

Andy Kao

Andy Kao

Andy Kao

13 97Monday, July 11, 2016

13 97Monday, July 11, 2016

13 97Monday, July 11, 2016

1

Rev

Rev

Rev

1.0

1.0

1.0

5

V

D D

C C

4

3

2

1

B B

A A

PEGATRON PROPRIETARY AND CONFIDENTIAL

PEGATRON PROPRIETARY AND CONFIDENTIAL

PEGATRON PROPRIETARY AND CONFIDENTIAL

BG1/HW3

BG1/HW3

BG1/HW3

Size Project Name

Size Project Name

Size Project Name

A

A

A

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

X3

X3

X3

2

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

<Title>

<Title>

<Title>

Andy Kao

Andy Kao

Andy Kao

14 97Monday, July 11, 2016

14 97Monday, July 11, 2016

14 97Monday, July 11, 2016

1

Rev

Rev

Rev

1.0

1.0

1.0

5

V

4

3

2

1

15

D D

+0.6VS

1 2

1 2

1 2

1 2

1 2

1 2

1 2

C C

B B

A A

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

+0.6VS

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

5

R150134.8Ohm 1%

R150234.8Ohm 1%

R150334.8Ohm 1%

R150434.8Ohm 1%

R150534.8Ohm 1%

R150634.8Ohm 1%

R150734.8Ohm 1%

R150834.8Ohm 1%

R150934.8Ohm 1%

R151034.8Ohm 1%

R151134.8Ohm 1%

R151234.8Ohm 1%

R151334.8Ohm 1%

R151434.8Ohm 1%

R151534.8Ohm 1%

R151634.8Ohm 1%

R152934.8Ohm 1%

R155534.8Ohm 1%

R156034.8Ohm 1%

R156334.8Ohm 1%

R154034.8Ohm 1%

R154334.8Ohm 1%

R154434.8Ohm 1%

R154534.8Ohm 1%

R154734.8Ohm 1%

R155234.8Ohm 1%

R155834.8Ohm 1%

R155934.8Ohm 1%

R156234.8Ohm 1%

R156534.8Ohm 1%

R155134.8Ohm 1%

R155634.8Ohm 1%

R155034.8Ohm 1%

R156434.8Ohm 1%

M0_MA0

M0_MA1

M0_MA2

M0_MA3

M0_MA4

M0_MA5

M0_MA6

M0_MA7

M0_MA8

M0_MA9

M_A_A10

M0_MA11

M0_MA12

M0_MA13

M_A_A14_WE_N

M_A_A15_CAS_N

M_A_A16_RAS_N

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14_WE_N

M_B_A15_CAS_N

M_B_A16_RAS_N

M_A_A0 4,16

M_A_A1 4,16

M_A_A2 4,16

M_A_A3 4,16

M_A_A4 4,16

M_A_A5 4,16

M_A_A6 4,16

M_A_A7 4,16

M_A_A8 4,16

M_A_A9 4,16

M_A_A10 4,16

M_A_A11 4,16

M_A_A12 4,16

M_A_A13 4,16

M_A_A14_WE_N 4, 16

M_A_A15_CAS_N 4,16

M_A_A16_RAS_N 4,16

M_B_A0 4,17

M_B_A1 4,17

M_B_A2 4,17

M_B_A3 4,17

M_B_A4 4,17

M_B_A5 4,17

M_B_A6 4,17

M_B_A7 4,17

M_B_A8 4,17

M_B_A9 4,17

M_B_A10 4,17

M_B_A11 4,17

M_B_A12 4,17

M_B_A13 4,17

M_B_A14_WE_N 4, 17

M_B_A15_CAS_N 4,17

M_B_A16_RAS_N 4,17

4

DDR4(0)_Termination

M_A_DIM0_CS0_N4,16

M_A_DIM0_CKE04,16

M_A_BG04,16

M_A_BA04,16

M_A_BA14,16

M_A_DIM0_ODT04,16

M_A_ACT_N4,16

DDR0_A_PARITY4,16

M_A_DIM0_CK_DDR0_DN4,16

M_A_DIM0_CK_DDR0_DP4,16

DDR0_A_ALERT_N4,16

M_B_DIM0_CS0_N4,17

M_B_DIM0_CKE04,17

M_B_BG04,17

M_B_BA04,17

M_B_BA14,17

M_B_DIM0_ODT04,17

M_B_ACT_N4,17

DDR0_B_PARITY4,17

M_B_DIM0_CK_DDR0_DN4,17

M_B_DIM0_CK_DDR0_DP4,17

DDR0_B_ALERT_N4,17

R1521 34.8Ohm1%

R1522 34.8Ohm1%

R1523 34.8Ohm1%

R1524 34.8Ohm1%

R1525 34.8Ohm1%

R1530 34.8Ohm1%

R1532 34.8Ohm1%

R1534 34.8Ohm1%

R1536 36Ohm5%

R1537 36Ohm5%

R1535 49.9Ohm1%

R1554 34.8Ohm1%

R1542 34.8Ohm1%

R1546 34.8Ohm1%

R1549 34.8Ohm1%

R1553 34.8Ohm1%

R1561 34.8Ohm1%

R1557 34.8Ohm1%

R1548 34.8Ohm1%

R1538 36Ohm5%

R1541 36Ohm5%

R1539 49.9Ohm1%

3

vx_r0402_small

1 2

1 2

vx_r0402_small

vx_r0402_small

vx_r0402_small

vx_r0402_small

vx_r0402_small

vx_r0402_small

vx_r0402_small

vx_r0402_small

1 2

vx_r0402_small

1 2

vx_r0402_small

1 2

vx_r0402_small

1 2

1 2

vx_r0402_small

vx_r0402_small

vx_r0402_small

vx_r0402_small

vx_r0402_small

vx_r0402_small

vx_r0402_small

vx_r0402_small

1 2

vx_r0402_small

1 2

vx_r0402_small

1 2

+0.6VS

+1.2V_DDR4

+0.6VS

+0.6VS

12

12

12

12

12

12

+0.6VS

+1.2V_DDR4

+0.6VS

+0.6VS

12

12

12

12

12

12

+0.6VS

+1.2V_DDR4

Average placed close to +VDDQ_VTT power plane

+0.6VS

12

C1501

1UF/6.3V

X5R/10%

vx_c0402_small

+0.6VS

12

C1513

1UF/6.3V

X5R/10%

vx_c0402_small

+0.6VS

12

C1509

10UF/6.3V

X5R/20%

vx_c0603_small

+0.6VS

12

C1541

1UF/6.3V

X5R/10%

vx_c0402_small

+0.6VS

12

C1524

1UF/6.3V

X5R/10%

vx_c0402_small

+0.6VS

12

C1522

10UF/6.3V

X5R/20%

vx_c0603_small

12

vx_c0402_small

12

vx_c0402_small

12

vx_c0603_small

12

vx_c0402_small

12

vx_c0402_small

12

vx_c0603_small

C1502

1UF/6.3V

X5R/10%

C1514

1UF/6.3V

X5R/10%

C1510

10UF/6.3V

X5R/20%

C1540

1UF/6.3V

X5R/10%

C1525

1UF/6.3V

X5R/10%

C1534

10UF/6.3V

X5R/20%

2

12

C1521

1UF/6.3V

X5R/10%

vx_c0402_small

12

C1515

1UF/6.3V

X5R/10%

vx_c0402_small

12

C1511

10UF/6.3V

X5R/20%

vx_c0603_small

12

C1539

1UF/6.3V

X5R/10%

vx_c0402_small

12

C1526

1UF/6.3V

X5R/10%

vx_c0402_small

12

C1523

10UF/6.3V

X5R/20%

vx_c0603_small

12

C1504

1UF/6.3V

X5R/10%

vx_c0402_small

12

C1516

1UF/6.3V

X5R/10%

vx_c0402_small

12

C1512

10UF/6.3V

X5R/20%

vx_c0603_small

12

C1538

1UF/6.3V

X5R/10%

vx_c0402_small

12

C1528

1UF/6.3V

X5R/10%

vx_c0402_small

12

C1536

10UF/6.3V

X5R/20%

vx_c0603_small

12

12

C1505

1UF/6.3V

X5R/10%

vx_c0402_small

vx_c0402_small

12

12

C1517

1UF/6.3V

X5R/10%

vx_c0402_small

vx_c0402_small

12

12

C1537

1UF/6.3V

X5R/10%

vx_c0402_small

vx_c0402_small

12

12

C1535

1UF/6.3V

X5R/10%

vx_c0402_small

vx_c0402_small

PEGATRON PROPRIETARY AND CONFIDENTI AL

PEGATRON PROPRIETARY AND CONFIDENTI AL

PEGATRON PROPRIETARY AND CONFIDENTI AL

BG1/HW3

BG1/HW3

BG1/HW3

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet

+0.6VS 57,83

+1.2V_DDR4 4,7,16,17,19,57,83

12

C1507

C1506

1UF/6.3V

1UF/6.3V

X5R/10%

X5R/10%

vx_c0402_small

12

C1519

C1518

1UF/6.3V

1UF/6.3V

X5R/10%

X5R/10%

vx_c0402_small

12

C1533

C1531

1UF/6.3V

1UF/6.3V

X5R/10%

X5R/10%

vx_c0402_small

12

C1530

C1532

1UF/6.3V

1UF/6.3V

X5R/10%

X5R/10%

vx_c0402_small

X3

X3

X3

12

C1508

1UF/6.3V

X5R/10%

vx_c0402_small

12

C1520

1UF/6.3V

X5R/10%

vx_c0402_small

12

C1529

1UF/6.3V

X5R/10%

vx_c0402_small

12

C1527

1UF/6.3V

X5R/10%

vx_c0402_small

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

DDR4(0)_Termination

DDR4(0)_Termination

DDR4(0)_Termination

Andy Kao

Andy Kao

Andy Kao

15 97Monday, July 11, 2016

15 97Monday, July 11, 2016

15 97Monday, July 11, 2016

of

Rev

Rev

Rev

1.0

1.0

1.0

16

V

M_A_D[0:6 3] 4

5

4

DDR4(1)_CH0

3

+1.2V

4.4A

+1.2V_DD R4

2

1

+1.2V_DD R4

+V_DDR_ VREFC A_CHA_D IMM

+2P5VPP

+1.2V_DD R4 4,7,1 5,17,19,5 7,83

+V_DDR_ VREFC A_CHA_D IMM 19

+2P5VPP 17,57 ,82

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14 _WE_N

M_A_A15 _CAS_N

M_A_A16 _RAS_N

M_A_ACT _N

M_A_BA0

M_A_BA1

M_A_BG0

DDR0_A _PARIT Y

M_A_DIM0 _CS0_N

M_A_DIM0 _ODT0

M_A_DIM0 _CKE0

DDR0_A _ALERT _N

M_A_D16

M_A_D22

M_A_D20

M_A_D18

M_A_D21

M_A_D23

M_A_D17

M_A_D19

M_A_DQS 2

M_A_DQS #2

M_A_D28

M_A_D26

M_A_D25

M_A_D30

M_A_D24

M_A_D29

M_A_D31

M_A_D27

M_A_DQS 3

M_A_DQS #3

12

12

C1645

1UF/6.3V

C1638

1UF/6.3V

U1602

P3

A0

P7

A1

R3

A2

N7

A3

N3

A4

P8

A5

P2

A6

R8

A7

R2

A8

R7

A9

M3

A10/AP

T2

A11

M7

A12/BC_n

T8

A13

L2

WE_n/A14

M8

CAS_n/A15

L8

RAS_n/A16

L3

ACT_n

N2

BA0

N8

BA1

M2

BG0

T3

PAR

L7

CS_n

K3

ODT

K2

CKE

K7

CK_t

K8

CK_c

P9

ALERT_n

G2

DQL0

F7

DQL1

H3

DQL2

H7

DQL3

H2

DQL4

H8

DQL5

J3

DQL6

J7

DQL7

E7

DML_N/DBIL_N

G3

DQSL_t

F3

DQSL_c

A3

DQU0

B8

DQU1

C3

DQU2

C7

DQU3

C2

DQU4

C8

DQU5

D3

DQU6

D7

DQU7

E2

DMU_N/DBIU_N

B7

DQSU_t

A7

DQSU_c

P1

RESET_n

K4A8G1 65WB-B CPB

12

12

DDR4

256M x 16 (4Gbit)

C1639

1UF/6.3V

C1646

1UF/6.3V

VDD_1

VDD_2

VDD_3

VDD_4

VDD_5

VDD_6

VDD_7

VDD_8

VDD_9

VDD_10

VDDQ_1

VDDQ_2

VDDQ_3

VDDQ_4

VDDQ_5

VDDQ_6

VDDQ_7

VDDQ_8

VDDQ_9

VDDQ_10

VREFCA

VSSQ_1

VSSQ_2

VSSQ_3

VSSQ_4

VSSQ_5

VSSQ_6

VSSQ_7

VSSQ_8

VSSQ_9

VSSQ_10

12

VPP_1

VPP_2

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

TEN

C1640

1UF/6.3V

U1603

C1659

1UF/6.3V

C1677

1UF/6.3V

P3

A0

P7

A1

R3

A2

N7

A3

N3

A4

P8

A5

P2

A6

R8

A7

R2

A8

R7

A9

M3

A10/AP

T2

A11

M7

A12/BC_n

T8

A13

L2

WE_n/A14

M8

CAS_n/A15

L8

RAS_n/A16

L3

ACT_n

N2

BA0

N8

BA1

M2

BG0

T3

PAR

L7

CS_n

K3

ODT

K2

CKE

K7

CK_t

K8

CK_c

P9

ALERT_n

G2

DQL0

F7

DQL1

H3

DQL2

H7

DQL3

H2

DQL4

H8

DQL5

J3

DQL6

J7

DQL7

E7

DML_N/DBIL_N

G3

DQSL_t

F3

DQSL_c

A3

DQU0

B8

DQU1

C3

DQU2

C7

DQU3

C2

DQU4

C8

DQU5

D3

DQU6

D7

DQU7

E2

DMU_N/DBIU_N

B7

DQSU_t

A7

DQSU_c

P1

RESET_n

K4A8G1 65WB-B CPB

12

12

C1678

1UF/6.3V

DDR4

256M x 16 (4Gbit)

C1660

1UF/6.3V

12

+1.2V_DD R4

B3

B9

D1

G7

J1

J9

L1

L9

R1

T9

A1

A9

C1

D9

F2

F8

G1

G9

+2P5VPP

J2

J8

B1

R9

M1

F9

DDR4_Z Q_23

ZQ

N9

T7

NC

B2

E1

E9

G8

K1

K9

M9

N1

T1

A2

A8

C9

D2

D8

E3

E8

F1

H1

H9

12

C1641

1UF/6.3V

12

R1687

240Ohm

+V_DDR_ VREFC A_CHA_D IMM

12

C1648

0.047UF/1 6V

+1.2V_DD R4

12

12

C1656

1UF/6.3V

+2P5VPP

12

C1652

10UF/6.3V

C1674

10UF/6.3V

+1.2V_DD R4

M_A_DQS 44

M_A_DQS #44

+1.2V_DD R4

M_A_DQS 54

M_A_DQS #54

12

C1650

0.1UF/25V

@

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14 _WE_N

M_A_A15 _CAS_N

M_A_A16 _RAS_N

M_A_ACT _N

M_A_BA0

M_A_BA1

M_A_BG0

DDR0_A _PARIT Y

M_A_DIM0 _CS0_N

M_A_DIM0 _ODT0

M_A_DIM0 _CKE0

M_A_DIM0 _CK_DD R0_DP

M_A_DIM0 _CK_DD R0_DN

DDR0_A _ALERT _N

M_A_D39

M_A_D32

M_A_D38

M_A_D36

Byte_4Byte_2 Byte_6

M_A_D35

M_A_D37

M_A_D33

M_A_D34

M_A_DQS 4

M_A_DQS #4

M_A_D43

M_A_D44

M_A_D46

M_A_D45

Byte_5

M_A_D47

M_A_D40

M_A_D42

M_A_D41

M_A_DQS 5

M_A_DQS #5

DDR4_D RAMRST_ R_N

12

C1653

10UF/6.3V

12

12

12

C1658

C1657

1UF/6.3V

1UF/6.3V

12

12

12

C1676

C1675

1UF/6.3V

1UF/6.3V

VDDQ_1

VDDQ_2

VDDQ_3

VDDQ_4

VDDQ_5

VDDQ_6

VDDQ_7

VDDQ_8

VDDQ_9

VDDQ_10

VREFCA

VSSQ_10

C1661

1UF/6.3V

VDD_1

VDD_2