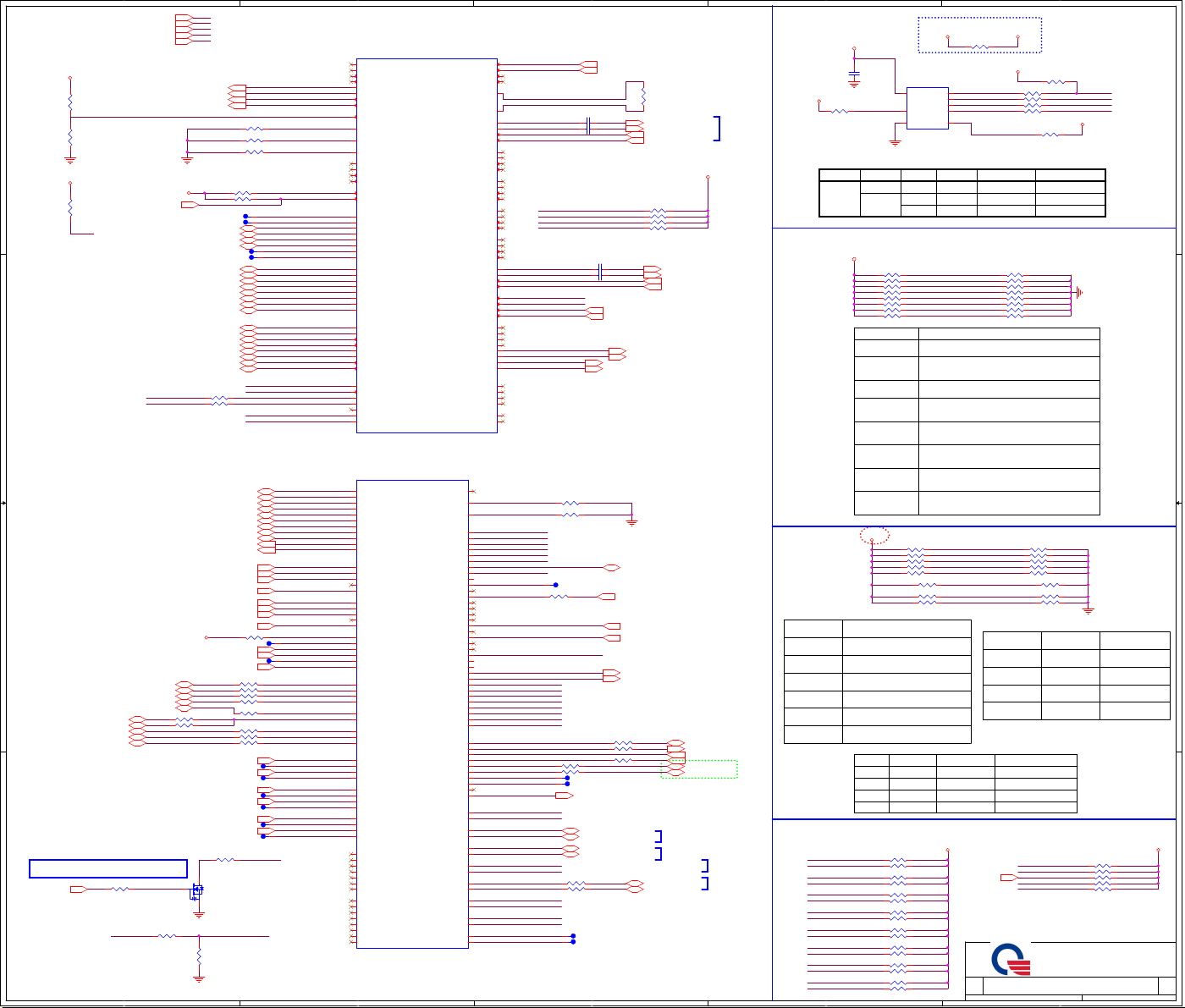

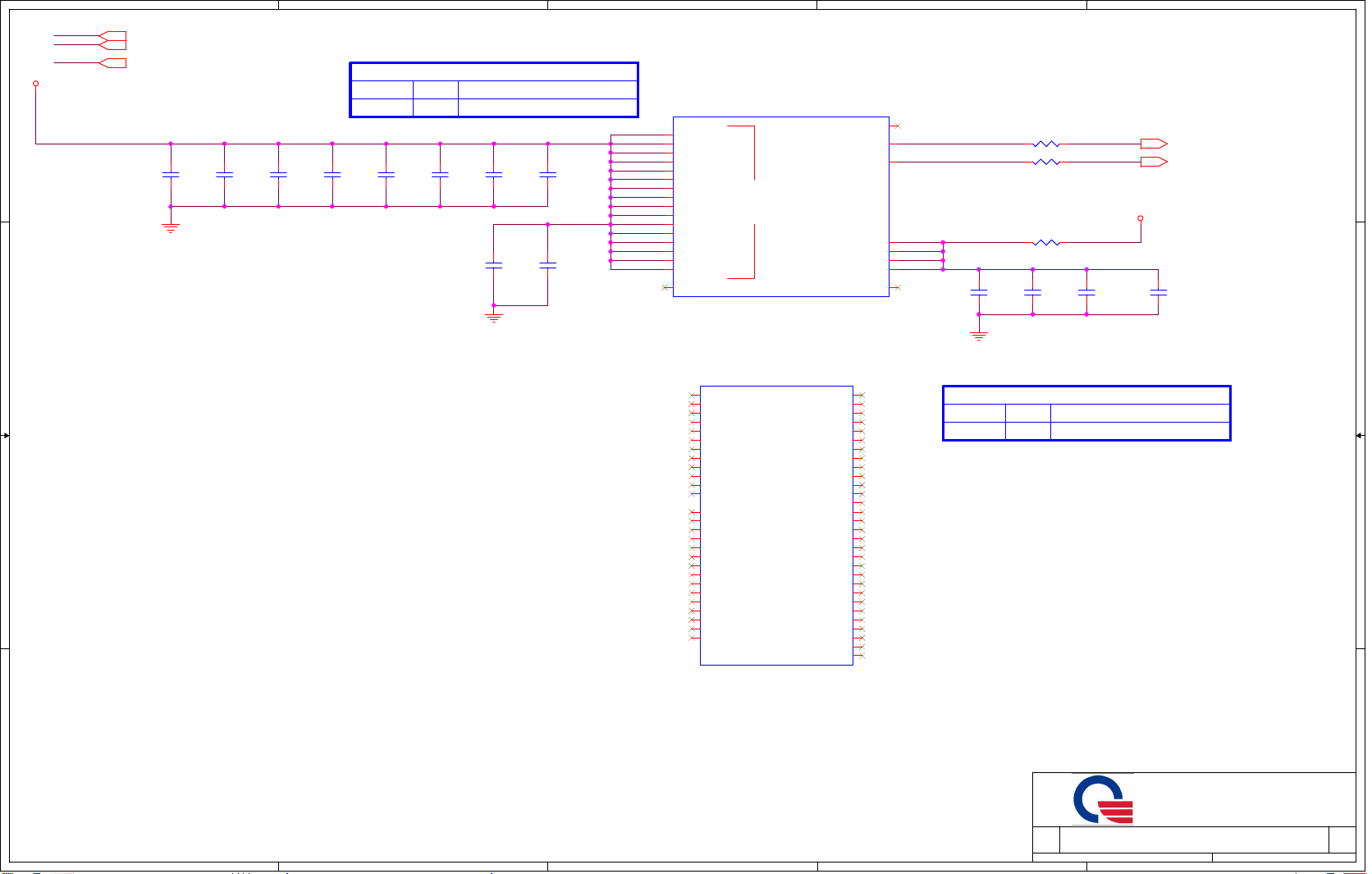

Acer TRAVELMATE SPIN B118-RN Schematics

5

www.schematic-x.blogspot.com

4

3

2

1

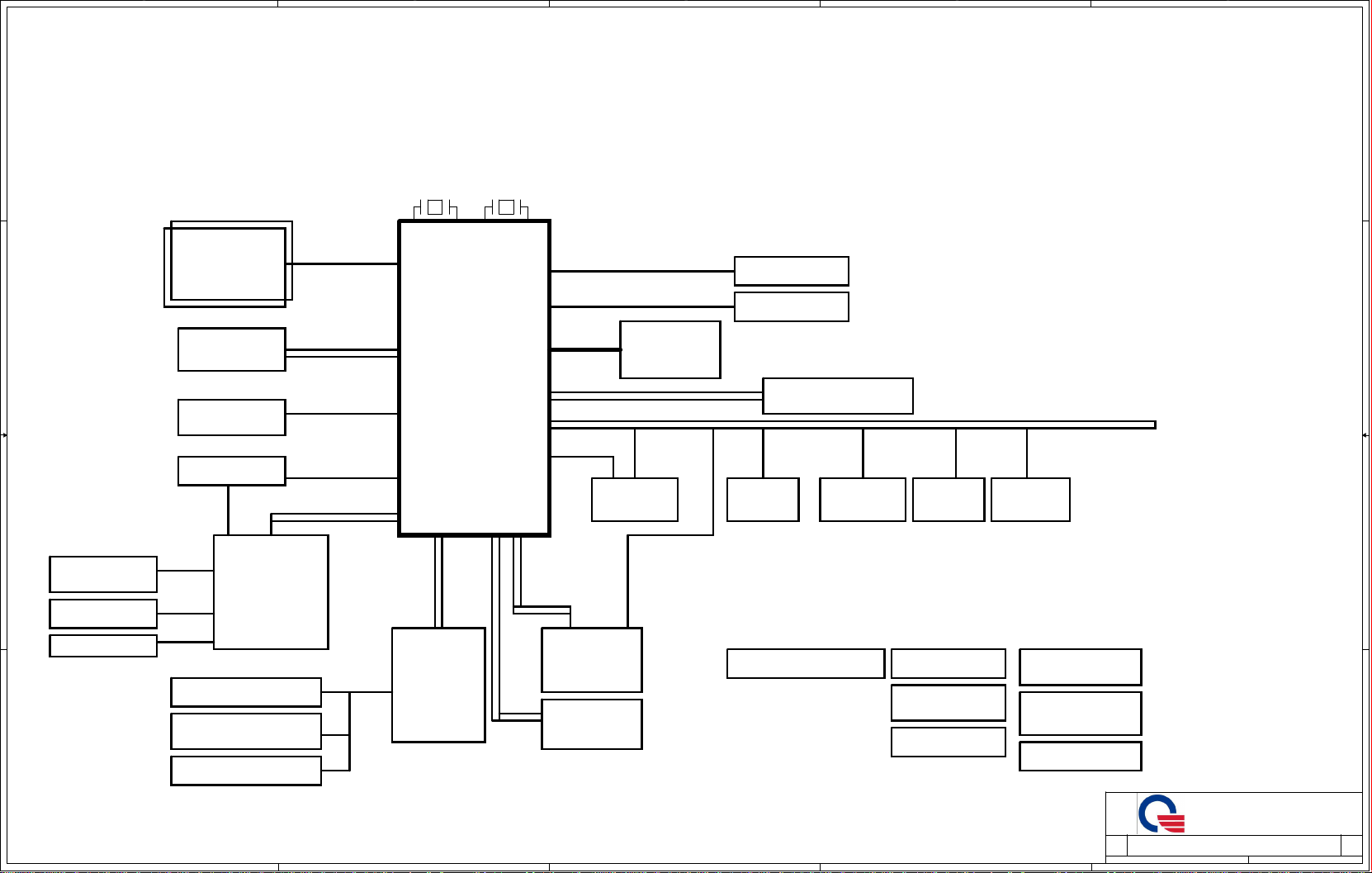

ZHV UMA(11.6")

01

D D

C C

B B

3.3V EC code

SPI ROM(8Mb)

PAGE 13

Thermal senser

PAGE 16

Keyboard

A A

PAGE 15

Intel Apollo Lake Platform Block Diagram

DDR3L 1600

Memory down

2 Channel 1Rx16

PAGE 11,12

SATA - 1st HDD

Package : 9.5 (mm)

Power :

1.8V BIOS+TXE

SPI ROM(64Mb)

PAGE 17

PAGE 5

Touch Pad

PAGE 15

PS2

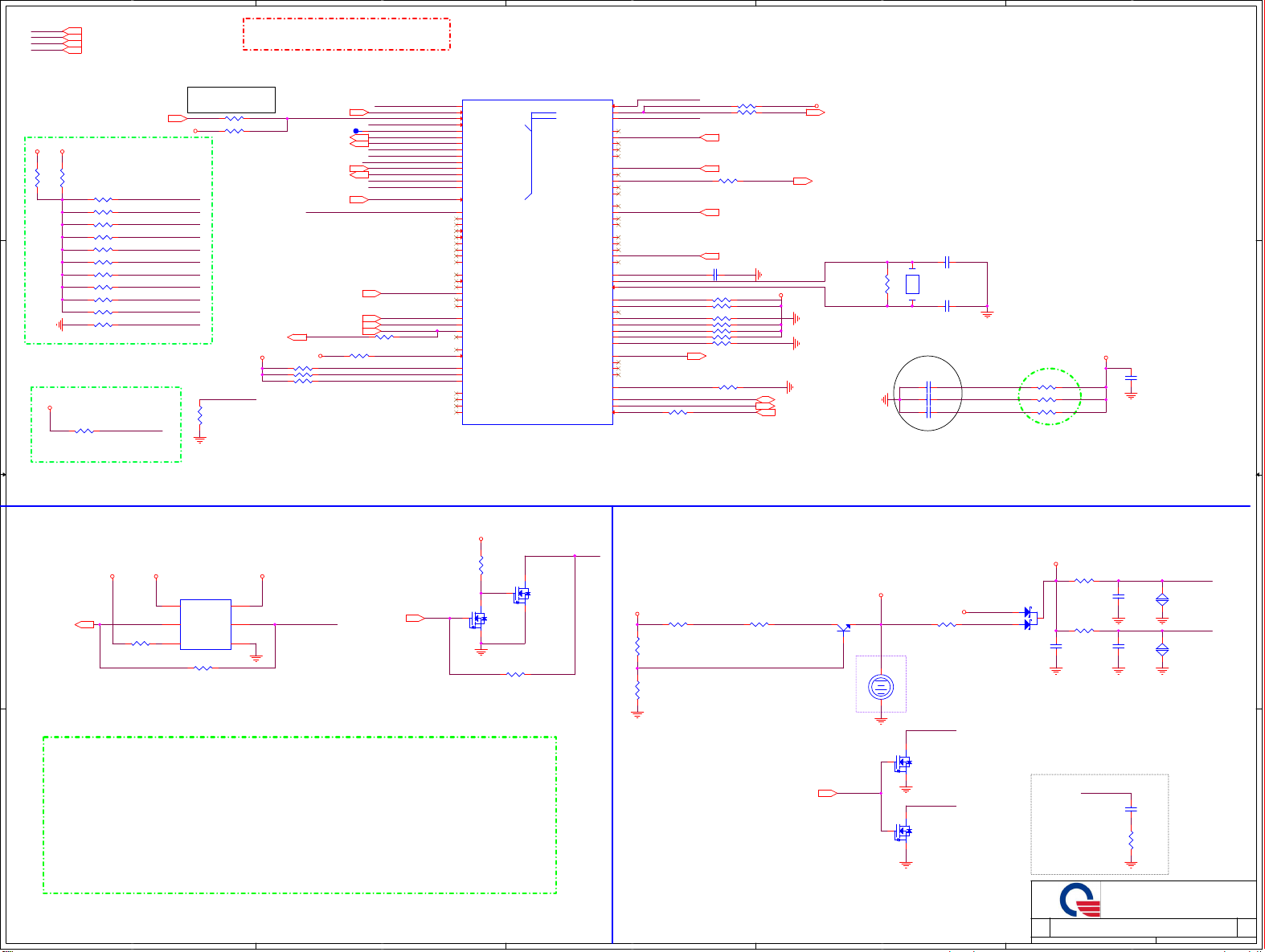

Embedded Controller

IT8987

Power :

Package : LQPF128

Size : 14 x 14 (mm)

Speaker

Combo Jack

Headphone + MIC

Digital -MIC

SATA0 3GB/s

SPI Interface

PAGE 13

PAGE 19

PAGE 19

PAGE 19

DDR3L

LPC Interface

I2C

32.768KHz

PAGE 6

Intel Apollo Lake

Package : FCBG 1170

Size : 24 x 31 (mm)

PAGE 2~10

Audio Codec

ALC255

Power :

Package : QFN

Size : 6 x 6 (mm)

Azalia

PAGE 19

PCIE2

19.2MHz

PAGE 4

DDI 0

x8

SMBus

USB 2.0 Interface

USB 3.0

Port0

PAGE 18

PCIE3

PCIE Gen 2 x 1 Lane

M.2 NGFF

WLAN / BT Combo

PAGE 21

LAN sub board

RTL8111H

PAGE 22

EMM C 5.0

SDIN7DP4

32GB/64GB

Port0

HDMI Conn

eDP

PAGE 14

PAGE 14

P17

G sensor/sensor HUB

Port4 Port7Port5

Port2

USB2.0 Port

PAGE 17

PAGE 20

Touch Screen

PAGE 14 PAGE 18

USB Board

DDR3L 1.35V(RT8231BGQW)

PAGE 27

Port6

CameraUSB3.0 Port

PAGE 14

Charger(BQ24737RGRR)

PAGE 24

SYSTEM 3V/5V

(SY8286B&8288)

PAGE 25

+1.05V (M5671RE1U)

PAGE 26

Card reader

RTS51 70

USB Board

+VNN (ISL95859)

+VCC (ISL95859)

PAGE 28

+VCC (ISL95808HRZ-T)

+VNN (ISL95808HRZ-T)

PAGE 29

Thermal / Discharge

PAGE 31

5

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, Mar ch 02, 2017

Date: Sheet of

Thursday, Mar ch 02, 2017

Date: Sheet of

4

3

2

Thursday, Mar ch 02, 2017

PROJECT :

Intel Block Diagram

Intel Block Diagram

Intel Block Diagram

ZHV

ZHV

ZHV

3A

3A

3A

341

341

1

341

5

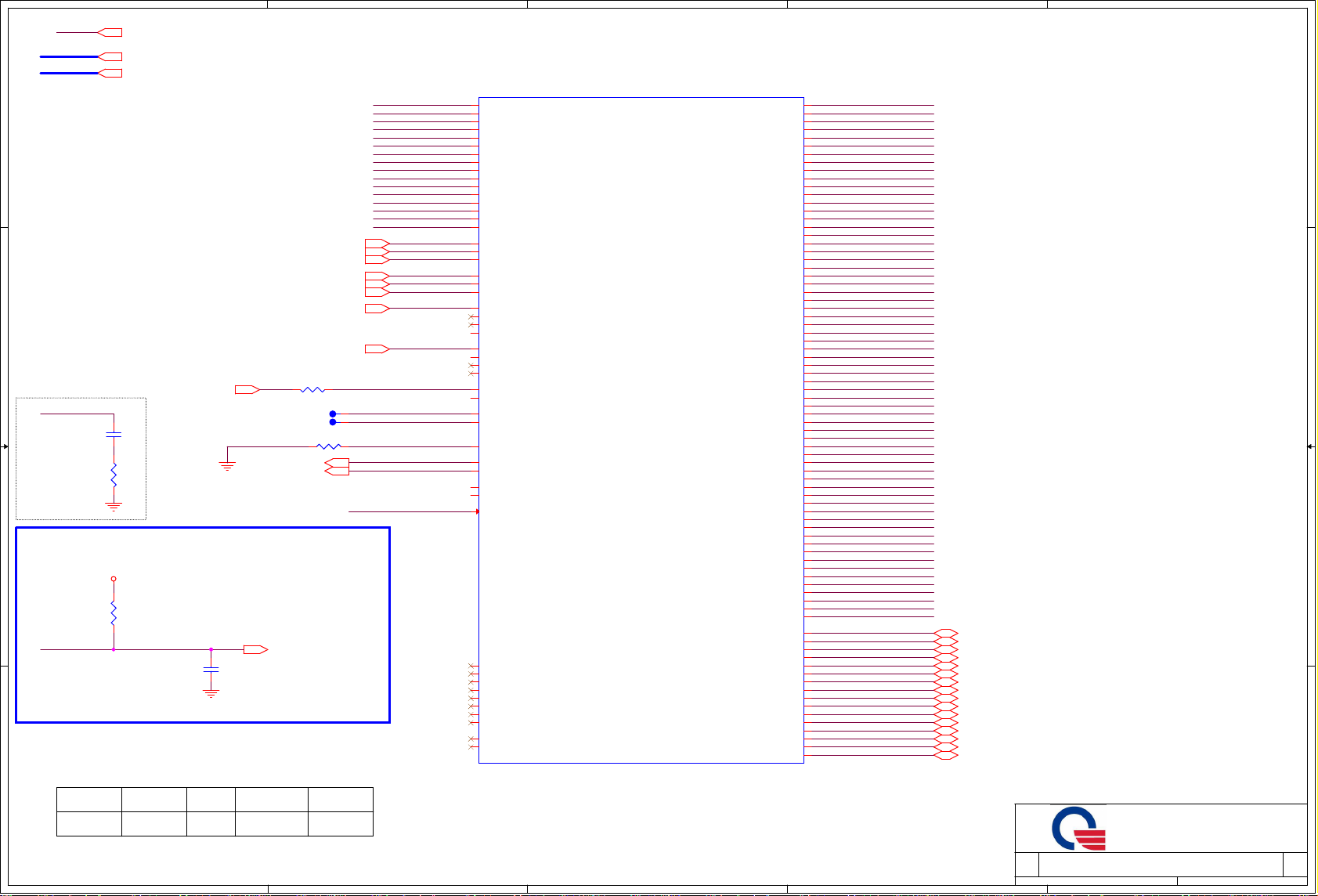

+1.35VSUS {3,9,11,12,27}

M_A_A[15:0]

M_A_DQ[63:0]

D D

VREFQD/VREFCA 0 Ohm resistor

should be un-s tuffe d by defa ult. PDG 0.9

C C

For ESD

M_A_DRAMRST#

C420

0.1u/16V_4

R578

10_5%_4

B B

A A

DRAMRST

M_A_DRAMRST#

GND

+1.35VSUS

1333/160 0/1867

M_A_A[15:0] {11}

M_A_DQ[63:0] { 11}

M_A_ODT0{11}

12/23 fol low I ntel PDG

1.0 chang e R3 22 to 0

R81

ohm.

1K_1%_4

Speed (M T/s)Configur ation

5

Channels

2 32SODIMM

R98 *0_5%_4

GND

R105 105_1%_4

M_A_CLKP0{11}

M_A_CLKN0{11}

DRAMCPU

M_A_DRAMRST# {11}

C93

*0.1u/16V_4

Raw Card Maximum Total

C(1Rx16)

A(2Rx16)

F(2Rx8)

B(1Rx8)

M_A_BS0{11}

M_A_BS1{11}

M_A_BS2{11}

M_A_CAS#{11}

M_A_RAS#{11}

M_A_WE#{11}

M_A_CS#0{ 11}

M_A_CKE0{11}

12

T6

T8

Capacity (GB)

4

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_CAS#

M_A_RAS#

M_A_WE#

M_A_CS#0

M_A_CKE0

M_A_ODT0_R

MEM_CH0_VREFDQ

MEM_CH0_VREFCA

DRAM_RCOMP0

M_A_CLKP0

M_A_CLKN0

M_A_DRAMRST#

4

BG50

DDR3L _CH0_MA0 _LPDDR3_CH 0_CAB7

BG51

DDR3L _CH0_MA1 _LPDDR3_CH 0_CAB9

BH51

DDR3L _CH0_MA2 _LPDDR3_CH 0_CAB5

BD41

DDR3L _CH0_MA3 _LPDDR3_NC

BE41

DDR3L _CH0_MA4 _LPDDR3_NC

BJ52

DDR3L _CH0_MA5 _LPDDR3_CH 0_CAA2

BG53

DDR3L _CH0_MA6 _LPDDR3_CH 0_CAA0

BG55

DDR3L _CH0_MA7 _LPDDR3_CH 0_CAA3

BH53

DDR3L _CH0_MA8 _LPDDR3_CH 0_CAA1

BG52

DDR3L _CH0_MA9 _LPDDR3_CH 0_CAA4

BH49

DDR3L _CH0_MA1 0_LPDDR3_ CH0_CAB6

BH55

DDR3L _CH0_MA1 1_LPDDR3_ CH0_CAA6

BG54

DDR3L _CH0_MA1 2_LPDDR3_ CH0_CAA5

BG46

DDR3L _CH0_MA1 3_LPDDR3_ CH0_CAB0

BG56

DDR3L _CH0_MA1 4_LPDDR3_ CH0_CAA8

BG57

DDR3L _CH0_MA1 5_LPDDR3_ CH0_CAA9

BJ48

DDR3L _CH0_BA0_ LPDDR3_CH 0_CAB2

BG49

DDR3L _CH0_BA1_ LPDDR3_CH 0_CAB8

BH57

DDR3L _CH0_BA2_ LPDDR3_CH 0_CAA7

BH47

DDR3L _CH0_CAS_ N_LPDDR3_ CH0_CAB1

BG47

DDR3L _CH0_RAS_ N_LPDDR3_ CH0_CAB3

BG48

DDR3L _CH0_WE_ N_LPDDR3_ CH0_CAB4

AR43

DDR3L _CH0_CS0_ N_LPDDR3_ CH0_CS0A_ N

AT43

DDR3L _NC_LPDDR 3_CH0_CS1 A_N

BB41

DDR3L _NC_LPDDR 3_CH0_CS0 B_N

BA41

DDR3L _CH0_CS1_ N_LPDDR3_ CH0_CS1B_ N

BH61

DDR3L _CH0_CKE0 _LPDDR3_C H0_CKE0A

BH60

DDR3L _CH0_CKE1 _LPDDR3_C H0_CKE1A

BH58

DDR3L _NC_LPDDR 3_CH0_CKE 0B

BJ58

DDR3L _NC_LPDDR 3_CH0_CKE 1B

AW43

DDR3L _CH0_ODT0_ LPDDR3_CH 0_ODTA

AW41

DDR3L _CH0_ODT1_ LPDDR3_CH 0_ODTB

AT34

MEM_ CH0_VREFD Q

AR35

MEM_ CH0_VREFC A

AV34

MEM_ CH0_RCOM P

BD45

DDR3L _CH0_CLKP 0_LPDDR3_ CH0_CLKP_ B

BE45

DDR3L _CH0_CLKN 0_LPDDR3_ CH0_CLKN_ B

BB48

DDR3L _CH0_CLKP 1_LPDDR3_ CH0_CLKP_ A

BD48

DDR3L _CH0_CLKN 1_LPDDR3_ CH0_CLKN_ A

AR34

DDR3L _CH0_RESE T_N_LPDDR3 _NC

Section 1 of 12

AW48

DDR3L _CH0_CB0_ LPDDR3_NC

AW47

DDR3L _CH0_CB1_ LPDDR3_NC

BB43

DDR3L _CH0_CB2_ LPDDR3_NC

AW45

DDR3L _CH0_CB3_ LPDDR3_NC

AV48

DDR3L _CH0_CB4_ LPDDR3_NC

AV47

DDR3L _CH0_CB5_ LPDDR3_NC

BD43

DDR3L _CH0_CB6_ LPDDR3_NC

BA45

DDR3L _CH0_CB7_ LPDDR3_NC

BD47

DDR3L _CH0_DQSP 8_LPDDR3_ NC

BB47

DDR3L _CH0_DQSN8 _LPDDR3_ NC

3

DDR3L _CH0_DQ0_ LPDDR3_CH 0_DQA0

DDR3L _CH0_DQ1_ LPDDR3_CH 0_DQA1

DDR3L _CH0_DQ2_ LPDDR3_CH 0_DQA2

DDR3L _CH0_DQ3_ LPDDR3_CH 0_DQA3

DDR3L _CH0_DQ4_ LPDDR3_CH 0_DQA4

DDR3L _CH0_DQ5_ LPDDR3_CH 0_DQA5

DDR3L _CH0_DQ6_ LPDDR3_CH 0_DQA6

DDR3L _CH0_DQ7_ LPDDR3_CH 0_DQA7

DDR3L _CH0_DQ8_ LPDDR3_CH 0_DQA8

DDR3L _CH0_DQ9_ LPDDR3_CH 0_DQA9

DDR3L _CH0_DQ10 _LPDDR3_C H0_DQA10

DDR3L _CH0_DQ11 _LPDDR3_C H0_DQA11

DDR3L _CH0_DQ12 _LPDDR3_C H0_DQA12

DDR3L _CH0_DQ13 _LPDDR3_C H0_DQA13

DDR3L _CH0_DQ14 _LPDDR3_C H0_DQA14

DDR3L _CH0_DQ15 _LPDDR3_C H0_DQA15

DDR3L _CH0_DQ16 _LPDDR3_C H0_DQA16

DDR3L _CH0_DQ17 _LPDDR3_C H0_DQA17

DDR3L _CH0_DQ18 _LPDDR3_C H0_DQA18

DDR3L _CH0_DQ19 _LPDDR3_C H0_DQA19

DDR3L _CH0_DQ20 _LPDDR3_C H0_DQA20

DDR3L _CH0_DQ21 _LPDDR3_C H0_DQA21

DDR3L _CH0_DQ22 _LPDDR3_C H0_DQA22

DDR3L _CH0_DQ23 _LPDDR3_C H0_DQA23

DDR3L _CH0_DQ24 _LPDDR3_C H0_DQA24

DDR3L _CH0_DQ25 _LPDDR3_C H0_DQA25

DDR3L _CH0_DQ26 _LPDDR3_C H0_DQA26

DDR3L _CH0_DQ27 _LPDDR3_C H0_DQA27

DDR3L _CH0_DQ28 _LPDDR3_C H0_DQA28

DDR3L _CH0_DQ29 _LPDDR3_C H0_DQA29

DDR3L _CH0_DQ30 _LPDDR3_C H0_DQA30

DDR3L _CH0_DQ31 _LPDDR3_C H0_DQA31

DDR3L _CH0_DQ32 _LPDDR3_C H0_DQB0

DDR3L _CH0_DQ33 _LPDDR3_C H0_DQB1

DDR3L _CH0_DQ34 _LPDDR3_C H0_DQB2

DDR3L _CH0_DQ35 _LPDDR3_C H0_DQB3

DDR3L _CH0_DQ36 _LPDDR3_C H0_DQB4

DDR3L _CH0_DQ37 _LPDDR3_C H0_DQB5

DDR3L _CH0_DQ38 _LPDDR3_C H0_DQB6

DDR3L _CH0_DQ39 _LPDDR3_C H0_DQB7

DDR3L _CH0_DQ40 _LPDDR3_C H0_DQB8

DDR3L _CH0_DQ41 _LPDDR3_C H0_DQB9

DDR3L _CH0_DQ42 _LPDDR3_C H0_DQB10

DDR3L _CH0_DQ43 _LPDDR3_C H0_DQB11

DDR3L _CH0_DQ44 _LPDDR3_C H0_DQB12

DDR3L _CH0_DQ45 _LPDDR3_C H0_DQB13

DDR3L _CH0_DQ46 _LPDDR3_C H0_DQB14

DDR3L _CH0_DQ47 _LPDDR3_C H0_DQB15

DDR3L _CH0_DQ48 _LPDDR3_C H0_DQB16

DDR3L _CH0_DQ49 _LPDDR3_C H0_DQB17

DDR3L _CH0_DQ50 _LPDDR3_C H0_DQB18

DDR3L _CH0_DQ51 _LPDDR3_C H0_DQB19

DDR3L _CH0_DQ52 _LPDDR3_C H0_DQB20

DDR3L _CH0_DQ53 _LPDDR3_C H0_DQB21

DDR3L _CH0_DQ54 _LPDDR3_C H0_DQB22

DDR3L _CH0_DQ55 _LPDDR3_C H0_DQB23

DDR3L _CH0_DQ56 _LPDDR3_C H0_DQB24

DDR3L _CH0_DQ57 _LPDDR3_C H0_DQB25

DDR3L _CH0_DQ58 _LPDDR3_C H0_DQB26

DDR3L _CH0_DQ59 _LPDDR3_C H0_DQB27

DDR3L _CH0_DQ60 _LPDDR3_C H0_DQB28

DDR3L _CH0_DQ61 _LPDDR3_C H0_DQB29

DDR3L _CH0_DQ62 _LPDDR3_C H0_DQB30

DDR3L _CH0_DQ63 _LPDDR3_C H0_DQB31

DDR3L _CH0_DQSP 0_LPDDR3_ CH0_DQSPA0

DDR3L _CH0_DQSN0 _LPDDR3_ CH0_DQSNA0

DDR3L _CH0_DQSP 1_LPDDR3_ CH0_DQSPA1

DDR3L _CH0_DQSN1 _LPDDR3_ CH0_DQSNA1

DDR3L _CH0_DQSP 2_LPDDR3_ CH0_DQSPA2

DDR3L _CH0_DQSN2 _LPDDR3_ CH0_DQSNA2

DDR3L _CH0_DQSP 3_LPDDR3_ CH0_DQSPA3

DDR3L _CH0_DQSN3 _LPDDR3_ CH0_DQSNA3

DDR3L _CH0_DQSP 4_LPDDR3_ CH0_DQSPB0

DDR3L _CH0_DQSN4 _LPDDR3_ CH0_DQSNB0

DDR3L _CH0_DQSP 5_LPDDR3_ CH0_DQSPB1

DDR3L _CH0_DQSN5 _LPDDR3_ CH0_DQSNB1

DDR3L _CH0_DQSP 6_LPDDR3_ CH0_DQSPB2

DDR3L _CH0_DQSN6 _LPDDR3_ CH0_DQSNB2

DDR3L _CH0_DQSP 7_LPDDR3_ CH0_DQSPB3

DDR3L _CH0_DQSN7 _LPDDR3_ CH0_DQSNB3

3

BXT_P_SOC_BGA1296U22A

AY62

AY61

BE62

BG62

BD63

AW62

AW63

BD62

AV59

AU63

AU62

AV58

AV57

AT55

AT54

AY59

AY57

BB57

BD59

BF59

AV54

AY55

AV52

BD58

BE56

BD54

BF58

BE50

BD50

BB50

BA50

BB54

AR39

AV37

AW37

AR37

AT37

AT41

AR41

AW35

BJ44

BG39

BG40

BJ40

BG43

BG44

BH45

BH41

BA34

BE34

BD34

BD37

BB37

BE39

BD39

BB34

BJ38

BG34

BG33

BH33

BG38

BH37

BG37

BJ34

BB63

BC62

AT59

AT58

BB59

BB58

BD52

BB52

AV39

AW39

BJ42

BG42

BB35

BD35

BG36

BH35

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_DQSP0

M_A_DQSN0

M_A_DQSP1

M_A_DQSN1

M_A_DQSP2

M_A_DQSN2

M_A_DQSP3

M_A_DQSN3

M_A_DQSP4

M_A_DQSN4

M_A_DQSP5

M_A_DQSN5

M_A_DQSP6

M_A_DQSN6

M_A_DQSP7

M_A_DQSN7

2

2

M_A_DQSP0 {11}

M_A_DQSN0 {11}

M_A_DQSP1 {11}

M_A_DQSN1 {11}

M_A_DQSP2 {11}

M_A_DQSN2 {11}

M_A_DQSP3 {11}

M_A_DQSN3 {11}

M_A_DQSP4 {11}

M_A_DQSN4 {11}

M_A_DQSP5 {11}

M_A_DQSN5 {11}

M_A_DQSP6 {11}

M_A_DQSN6 {11}

M_A_DQSP7 {11}

M_A_DQSN7 {11}

1

02

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

Date: Sheet of

Thursday, March 02, 2017

Date: Sheet of

Thursday, March 02, 2017

Date: Sheet of

Thursday, March 02, 2017

PROJECT :

Valley 1/9 (DDRA)

Valley 1/9 (DDRA)

Valley 1/9 (DDRA)

ZHV

ZHV

ZHV

342

342

1

342

3A

3A

3A

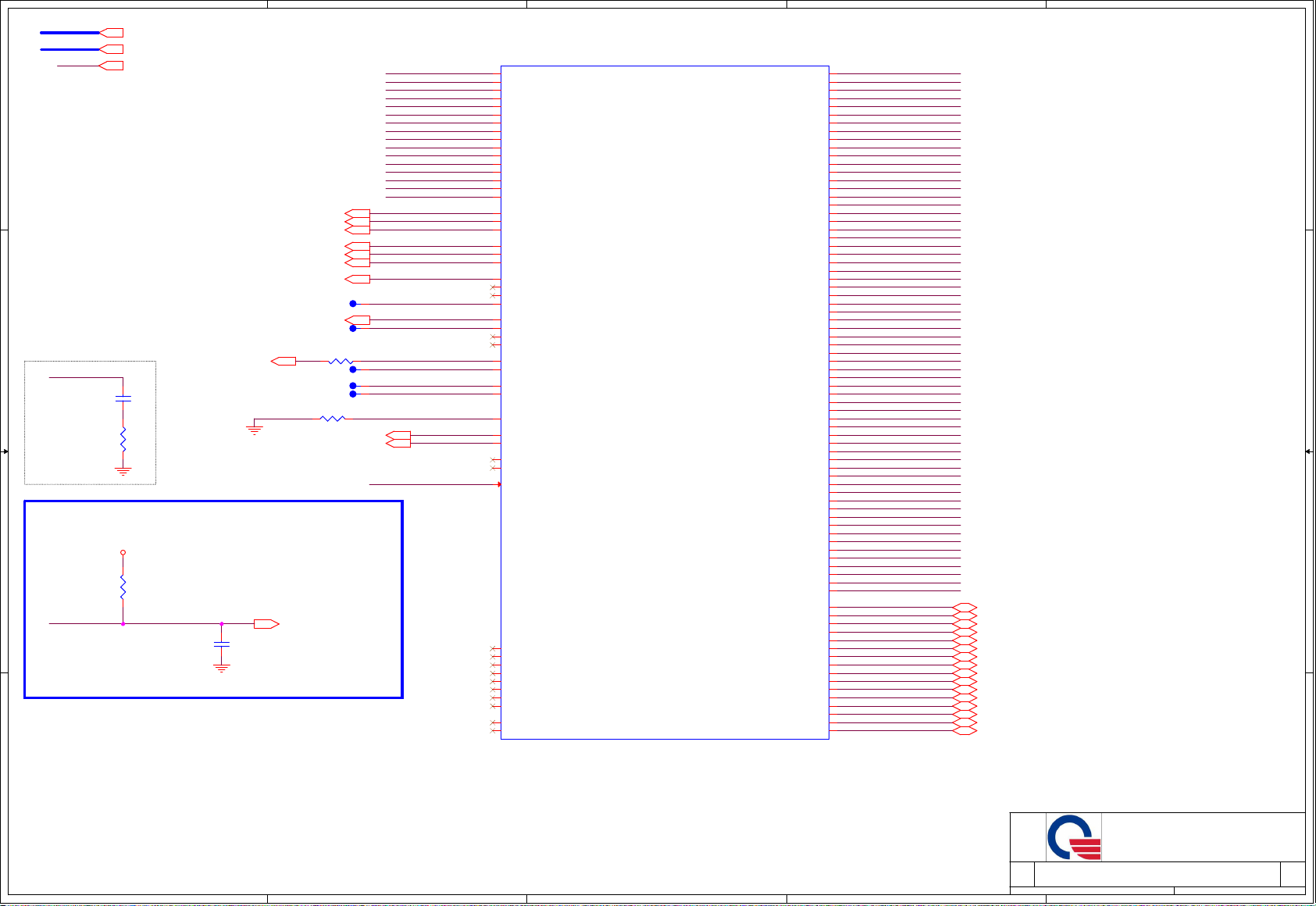

5

M_B_ A[15:0]

M_B_ DQ[63:0]

D D

VREFQD/VREFCA 0 Ohm resistor

should be un-s tuffe d by defa ult. PDG 0.9

C C

For ESD

M_B_ DRAMRST#

0.1u/1 6V_4

10_5% _4

M_B_ A[15:0] {12}

M_B_ DQ[63:0] {12}

+1.35 VSUS {2,9,1 1,12,27}

C421

R579

GND

Modify i t 10/17

M_B_ ODT0{12}

GND

M_B_ BS0{12}

M_B_ BS1{12}

M_B_ BS2{12}

M_B_ CAS#{12}

M_B_ RAS#{12}

M_B_ WE#{12}

M_B_ CS#0{12}

T4

M_B_ CKE0{12}

T3

R95 *OB@0 _5%_4

T5

T9

T7

R112

105_1 %_4

M_B_ CLKP0{12}

M_B_ CLKN0{12}

DRAMRST

+1.35 VSUS

B B

CPU DRAM

M_B_ DRAMRST#

DDR3L SO DIMM/Memo ry Down: Populating CH1 on ly

Note: No t support ed on A-step. Only support ed on

B-step.

12

R101

1K_1% _4

C104

*OB@0 .1u/16V_4

M_B_ DRAMRST# {1 2}

12

12

4

M_B_ A0

M_B_ A1

M_B_ A2

M_B_ A3

M_B_ A4

M_B_ A5

M_B_ A6

M_B_ A7

M_B_ A8

M_B_ A9

M_B_ A10

M_B_ A11

M_B_ A12

M_B_ A13

M_B_ A14

M_B_ A15

M_B_ BS0

M_B_ BS1

M_B_ BS2

M_B_ CAS#

M_B_ RAS#

M_B_ WE#

M_B_ CS#0

M_B_ CS#1

M_B_ CKE0

M_B_ CKE1

M_B_ ODT0_R

M_B_ ODT1

MEM_ CH1_VREFD Q

MEM_ CH1_VREFC A

DRAM_ RCOMP1

M_B_ CLKP0

M_B_ CLKN0

M_B_ DRAMRST#

BG9

DDR3L_CH1 _MA0_LPDDR3_C H1_CAB7

BG10

DDR3L_CH1 _MA1_LPDDR3_C H1_CAB9

BH9

DDR3L_CH1 _MA2_LPDDR3_C H1_CAB5

BD16

DDR3L_CH1 _MA3_LPDDR3_N C

BB16

DDR3L_CH1 _MA4_LPDDR3_N C

BG11

DDR3L_CH1 _MA5_LPDDR3_C H1_CAA2

BJ12

DDR3L_CH1 _MA6_LPDDR3_C H1_CAA0

BG14

DDR3L_CH1 _MA7_LPDDR3_C H1_CAA3

BG12

DDR3L_CH1 _MA8_LPDDR3_C H1_CAA1

BH11

DDR3L_CH1 _MA9_LPDDR3_C H1_CAA4

BG7

DDR3L_CH1 _MA10_LPDDR3_ CH1_CAB6

BH13

DDR3L_CH1 _MA11_LPDDR3_ CH1_CAA6

BG13

DDR3L_CH1 _MA12_LPDDR3_ CH1_CAA5

BH3

DDR3L_CH1 _MA13_LPDDR3_ CH1_CAB0

BG15

DDR3L_CH1 _MA14_LPDDR3_ CH1_CAA8

BG16

DDR3L_CH1 _MA15_LPDDR3_ CH1_CAA9

BH6

DDR3L_CH1 _BA0_LPDDR3_CH 1_CAB2

BG8

DDR3L_CH1 _BA1_LPDDR3_CH 1_CAB8

BH15

DDR3L_CH1 _BA2_LPDDR3_CH 1_CAA7

BH4

DDR3L_CH1 _CAS_N_LPDDR3_ CH1_CAB1

BJ6

DDR3L_CH1 _RAS_N_LPDDR3_ CH1_CAB3

BH7

DDR3L_CH1 _WE_N_LPDDR3_ CH1_CAB4

BD17

DDR3L_CH1 _CS0_N_LPDDR3_ CH1_CS0A_N

BB17

DDR3L_NC_ LPDDR3_CH1_CS1 A_N

AV17

DDR3L_NC_ LPDDR3_CH1_CS0 B_N

AW17

DDR3L_CH1 _CS1_N_LPDDR3_ CH1_CS1B_N

BG18

DDR3L_CH1 _CKE0_LPDDR3_C H1_CKE0A

BG17

DDR3L_CH1 _CKE1_LPDDR3_C H1_CKE1A

BH17

DDR3L_NC_ LPDDR3_CH1_CKE0 B

BJ16

DDR3L_NC_ LPDDR3_CH1_CKE1 B

AW16

DDR3L_CH1 _ODT0_LPDDR3_ CH1_ODTA

AV16

DDR3L_CH1 _ODT1_LPDDR3_ CH1_ODTB

AT30

MEM_CH1 _VREFDQ

AR29

MEM_CH1 _VREFCA

AV30

MEM_CH1 _RCOMP

BD19

DDR3L_CH1 _CLKP0_LPDDR3_ CH1_CLKP_B

BE19

DDR3L_CH1 _CLKN0_LPDDR3_ CH1_CLKN_B

BB21

DDR3L_CH1 _CLKP1_LPDDR3_ CH1_CLKP_A

BD21

DDR3L_CH1 _CLKN1_LPDDR3_ CH1_CLKN_A

AR30

DDR3L_CH1 _RESET_N_LPDDR3 _NC

Section 2 of 12

AR21

DDR3L_CH1 _CB0_LPDDR3_NC

AT21

DDR3L_CH1 _CB1_LPDDR3_NC

AW23

DDR3L_CH1 _CB2_LPDDR3_NC

AW21

DDR3L_CH1 _CB3_LPDDR3_NC

BA19

DDR3L_CH1 _CB4_LPDDR3_NC

AW19

DDR3L_CH1 _CB5_LPDDR3_NC

BA23

DDR3L_CH1 _CB6_LPDDR3_NC

BB23

DDR3L_CH1 _CB7_LPDDR3_NC

BD23

DDR3L_CH1 _DQSP8_LPDDR3 _NC

BE23

DDR3L_CH1 _DQSN8_LPDDR3 _NC

3

DDR3L_CH1 _DQ0_LPDDR3_C H1_DQA0

DDR3L_CH1 _DQ1_LPDDR3_C H1_DQA1

DDR3L_CH1 _DQ2_LPDDR3_C H1_DQA2

DDR3L_CH1 _DQ3_LPDDR3_C H1_DQA3

DDR3L_CH1 _DQ4_LPDDR3_C H1_DQA4

DDR3L_CH1 _DQ5_LPDDR3_C H1_DQA5

DDR3L_CH1 _DQ6_LPDDR3_C H1_DQA6

DDR3L_CH1 _DQ7_LPDDR3_C H1_DQA7

DDR3L_CH1 _DQ8_LPDDR3_C H1_DQA8

DDR3L_CH1 _DQ9_LPDDR3_C H1_DQA9

DDR3L_CH1 _DQ10_LPDDR3_ CH1_DQA10

DDR3L_CH1 _DQ11_LPDDR3_ CH1_DQA11

DDR3L_CH1 _DQ12_LPDDR3_ CH1_DQA12

DDR3L_CH1 _DQ13_LPDDR3_ CH1_DQA13

DDR3L_CH1 _DQ14_LPDDR3_ CH1_DQA14

DDR3L_CH1 _DQ15_LPDDR3_ CH1_DQA15

DDR3L_CH1 _DQ16_LPDDR3_ CH1_DQA16

DDR3L_CH1 _DQ17_LPDDR3_ CH1_DQA17

DDR3L_CH1 _DQ18_LPDDR3_ CH1_DQA18

DDR3L_CH1 _DQ19_LPDDR3_ CH1_DQA19

DDR3L_CH1 _DQ20_LPDDR3_ CH1_DQA20

DDR3L_CH1 _DQ21_LPDDR3_ CH1_DQA21

DDR3L_CH1 _DQ22_LPDDR3_ CH1_DQA22

DDR3L_CH1 _DQ23_LPDDR3_ CH1_DQA23

DDR3L_CH1 _DQ24_LPDDR3_ CH1_DQA24

DDR3L_CH1 _DQ25_LPDDR3_ CH1_DQA25

DDR3L_CH1 _DQ26_LPDDR3_ CH1_DQA26

DDR3L_CH1 _DQ27_LPDDR3_ CH1_DQA27

DDR3L_CH1 _DQ28_LPDDR3_ CH1_DQA28

DDR3L_CH1 _DQ29_LPDDR3_ CH1_DQA29

DDR3L_CH1 _DQ30_LPDDR3_ CH1_DQA30

DDR3L_CH1 _DQ31_LPDDR3_ CH1_DQA31

DDR3L_CH1 _DQ32_LPDDR3_ CH1_DQB0

DDR3L_CH1 _DQ33_LPDDR3_ CH1_DQB1

DDR3L_CH1 _DQ34_LPDDR3_ CH1_DQB2

DDR3L_CH1 _DQ35_LPDDR3_ CH1_DQB3

DDR3L_CH1 _DQ36_LPDDR3_ CH1_DQB4

DDR3L_CH1 _DQ37_LPDDR3_ CH1_DQB5

DDR3L_CH1 _DQ38_LPDDR3_ CH1_DQB6

DDR3L_CH1 _DQ39_LPDDR3_ CH1_DQB7

DDR3L_CH1 _DQ40_LPDDR3_ CH1_DQB8

DDR3L_CH1 _DQ41_LPDDR3_ CH1_DQB9

DDR3L_CH1 _DQ42_LPDDR3_ CH1_DQB10

DDR3L_CH1 _DQ43_LPDDR3_ CH1_DQB11

DDR3L_CH1 _DQ44_LPDDR3_ CH1_DQB12

DDR3L_CH1 _DQ45_LPDDR3_ CH1_DQB13

DDR3L_CH1 _DQ46_LPDDR3_ CH1_DQB14

DDR3L_CH1 _DQ47_LPDDR3_ CH1_DQB15

DDR3L_CH1 _DQ48_LPDDR3_ CH1_DQB16

DDR3L_CH1 _DQ49_LPDDR3_ CH1_DQB17

DDR3L_CH1 _DQ50_LPDDR3_ CH1_DQB18

DDR3L_CH1 _DQ51_LPDDR3_ CH1_DQB19

DDR3L_CH1 _DQ52_LPDDR3_ CH1_DQB20

DDR3L_CH1 _DQ53_LPDDR3_ CH1_DQB21

DDR3L_CH1 _DQ54_LPDDR3_ CH1_DQB22

DDR3L_CH1 _DQ55_LPDDR3_ CH1_DQB23

DDR3L_CH1 _DQ56_LPDDR3_ CH1_DQB24

DDR3L_CH1 _DQ57_LPDDR3_ CH1_DQB25

DDR3L_CH1 _DQ58_LPDDR3_ CH1_DQB26

DDR3L_CH1 _DQ59_LPDDR3_ CH1_DQB27

DDR3L_CH1 _DQ60_LPDDR3_ CH1_DQB28

DDR3L_CH1 _DQ61_LPDDR3_ CH1_DQB29

DDR3L_CH1 _DQ62_LPDDR3_ CH1_DQB30

DDR3L_CH1 _DQ63_LPDDR3_ CH1_DQB31

DDR3L_CH1 _DQSP0_LPDDR3 _CH1_DQSPA0

DDR3L_CH1 _DQSN0_LPDDR3 _CH1_DQSNA0

DDR3L_CH1 _DQSP1_LPDDR3 _CH1_DQSPA1

DDR3L_CH1 _DQSN1_LPDDR3 _CH1_DQSNA1

DDR3L_CH1 _DQSP2_LPDDR3 _CH1_DQSPA2

DDR3L_CH1 _DQSN2_LPDDR3 _CH1_DQSNA2

DDR3L_CH1 _DQSP3_LPDDR3 _CH1_DQSPA3

DDR3L_CH1 _DQSN3_LPDDR3 _CH1_DQSNA3

DDR3L_CH1 _DQSP4_LPDDR3 _CH1_DQSPB0

DDR3L_CH1 _DQSN4_LPDDR3 _CH1_DQSNB0

DDR3L_CH1 _DQSP5_LPDDR3 _CH1_DQSPB1

DDR3L_CH1 _DQSN5_LPDDR3 _CH1_DQSNB1

DDR3L_CH1 _DQSP6_LPDDR3 _CH1_DQSPB2

DDR3L_CH1 _DQSN6_LPDDR3 _CH1_DQSNB2

DDR3L_CH1 _DQSP7_LPDDR3 _CH1_DQSPB3

DDR3L_CH1 _DQSN7_LPDDR3 _CH1_DQSNB3

BXT_P_S OC_BGA129 6U22B

BJ26

BG30

BH31

BG31

BH27

BG27

BG26

BJ30

BA30

BB30

BE30

BD30

BE25

BB27

BD25

BD27

BG24

BJ20

BH23

BJ24

BG20

BG21

BH19

BG25

AT27

AW29

AR27

AT23

AV27

AR25

AR23

AW27

BF6

BD10

BE14

BB10

BA14

BB14

BD14

BE8

AV12

BD6

BD5

BB7

AV10

AY9

AY7

BF5

AU2

AT10

AT9

AU1

AY5

AV5

AV6

AV7

AY2

BD2

BD1

BE2

AW1

AW2

AY3

BG2

BG28

BH29

BD29

BB29

BJ22

BG22

AV25

AW25

BB12

BD12

BB5

BB6

AT5

AT6

BC2

BB1

M_B_ DQ0

M_B_ DQ1

M_B_ DQ2

M_B_ DQ3

M_B_ DQ4

M_B_ DQ5

M_B_ DQ6

M_B_ DQ7

M_B_ DQ8

M_B_ DQ9

M_B_ DQ10

M_B_ DQ11

M_B_ DQ12

M_B_ DQ13

M_B_ DQ14

M_B_ DQ15

M_B_ DQ16

M_B_ DQ17

M_B_ DQ18

M_B_ DQ19

M_B_ DQ20

M_B_ DQ21

M_B_ DQ22

M_B_ DQ23

M_B_ DQ24

M_B_ DQ25

M_B_ DQ26

M_B_ DQ27

M_B_ DQ28

M_B_ DQ29

M_B_ DQ30

M_B_ DQ31

M_B_ DQ32

M_B_ DQ33

M_B_ DQ34

M_B_ DQ35

M_B_ DQ36

M_B_ DQ37

M_B_ DQ38

M_B_ DQ39

M_B_ DQ40

M_B_ DQ41

M_B_ DQ42

M_B_ DQ43

M_B_ DQ44

M_B_ DQ45

M_B_ DQ46

M_B_ DQ47

M_B_ DQ48

M_B_ DQ49

M_B_ DQ50

M_B_ DQ51

M_B_ DQ52

M_B_ DQ53

M_B_ DQ54

M_B_ DQ55

M_B_ DQ56

M_B_ DQ57

M_B_ DQ58

M_B_ DQ59

M_B_ DQ60

M_B_ DQ61

M_B_ DQ62

M_B_ DQ63

M_B_ DQSP0

M_B_ DQSN0

M_B_ DQSP1

M_B_ DQSN1

M_B_ DQSP2

M_B_ DQSN2

M_B_ DQSP3

M_B_ DQSN3

M_B_ DQSP4

M_B_ DQSN4

M_B_ DQSP5

M_B_ DQSN5

M_B_ DQSP6

M_B_ DQSN6

M_B_ DQSP7

M_B_ DQSN7

2

1

03

M_B_ DQSP0 {12}

M_B_ DQSN0 {12}

M_B_ DQSP1 {12}

M_B_ DQSN1 {12}

M_B_ DQSP2 {12}

M_B_ DQSN2 {12}

M_B_ DQSP3 {12}

M_B_ DQSN3 {12}

M_B_ DQSP4 {12}

M_B_ DQSN4 {12}

M_B_ DQSP5 {12}

M_B_ DQSN5 {12}

M_B_ DQSP6 {12}

M_B_ DQSN6 {12}

M_B_ DQSP7 {12}

M_B_ DQSN7 {12}

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size D ocument N umber Rev

Size D ocument N umber Rev

Size D ocument N umber Rev

Thursda y, March 0 2, 2017

Date: Sheet of

Thursda y, March 0 2, 2017

Date: Sheet of

Thursda y, March 0 2, 2017

5

4

3

2

Date: Sheet

PROJECT :

Valley 2/9 (DDRB)

Valley 2/9 (DDRB)

Valley 2/9 (DDRB)

ZHV

ZHV

ZHV

3A

3A

3A

of

343

343

1

343

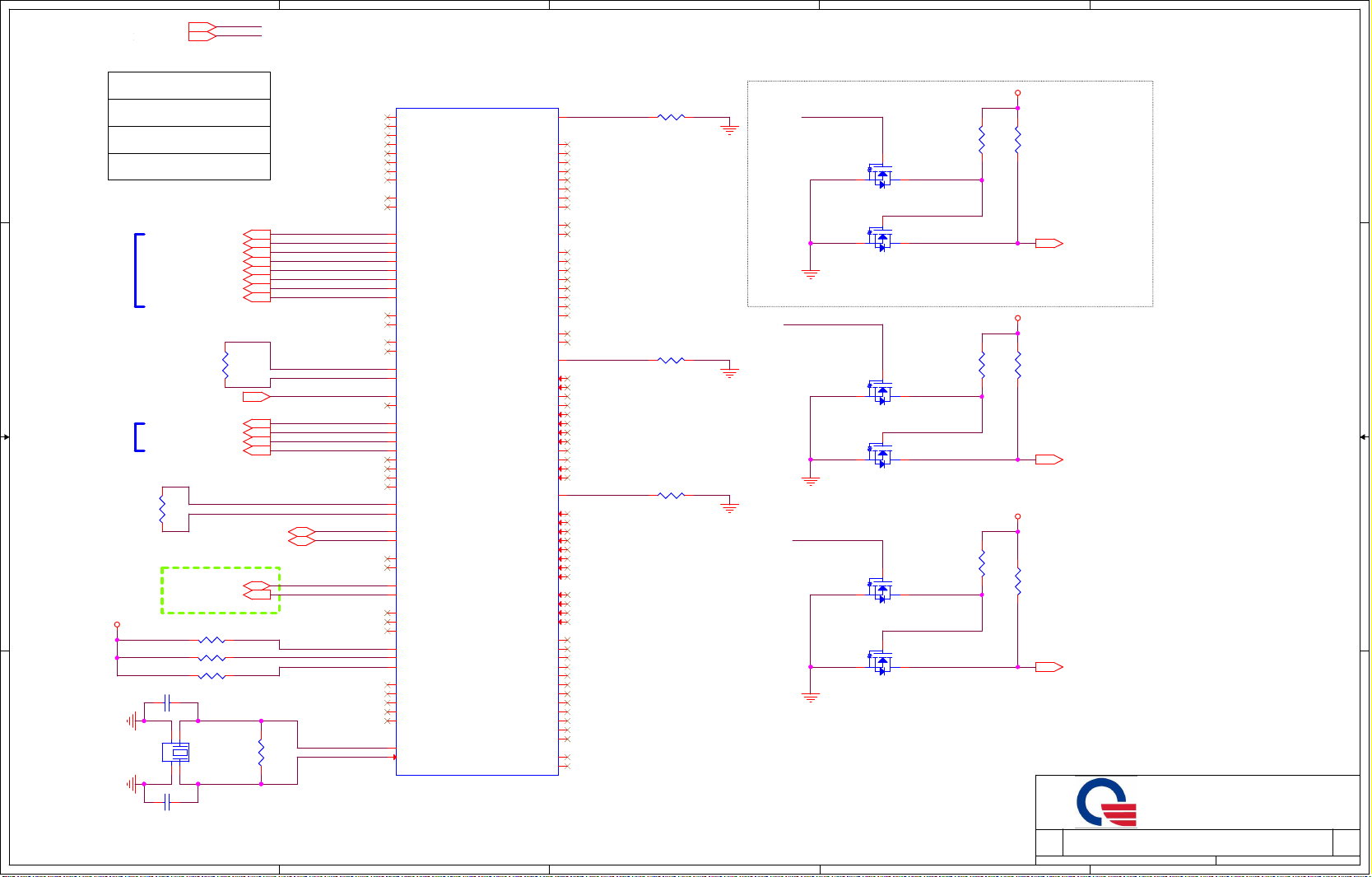

5

+1.8V_S5

+3V

4

3

2

1

ZHP CPU P/N A-stage

D D

AJ0QKG2VT00

defalut

AJ0QKG3VT00

AJ0QKG4VT00

IN_D2{14}

IN_D2#{14}

IN_D1{14}

IN_D1#{14}

402_1% _4

HDMI_HPD _CON{14}

INT_ED P_TXP0{14}

INT_ED P_TXN0{14}

INT_ED P_TXP1{14}

INT_ED P_TXN1{14}

C38315p/50V_4

1

2

4

3

C38415p/50V_4

IN_D0{14}

IN_D0#{14}

IN_CLK{14}

IN_CLK#{14}

R437

INT_eD P_AUXP{14}

INT_eD P_AUXN{14}

SDVO_D ATA{14}

SDVO_C LK{14}

1 2

1 2

1 2

200K_1 %_4

EDP_RC OMP_P

EDP_RC OMP_N

R241*100K_5%_ 4

R242*100K_5%_ 4

R240*100K_5%_ 4

follow C RB v1.0

R513

1 2

SOC_D DI0_RCOMP_P

SOC_D DI0_RCOMP_N

PCH_D ISP_ON_ C

PCH_ED P_BLON_C

PCH_D PST_PWM_C

XTAL19 _OUT

XTAL19 _IN

HDMI

C C

DDI0 HPD

eDP

R120

402_1% _4

B B

HDMI

+1.8V_S5

GND

A A

19.2MHZ /20ppm

Y3

GND

AF2

AF3

AD3

AD2

AC1

AC2

AB3

AB2

AK16

AK15

AK3

AK2

AM3

AM2

AH3

AH2

AL2

AL1

AM16

AM15

B51

C51

AG1

AG2

C50

A50

AG7

AG9

AG12

AG10

AC6

AC5

AC7

AC9

AG6

AG5

AH10

AH9

C54

A54

C49

B49

C52

B53

C53

C47

B47

C46

AG62

AF61

AG63

AE60

AF62

P29

R27

DDI1_T XP_0

DDI1_T XN_0

DDI1_T XP_1

DDI1_T XN_1

DDI1_T XP_2

DDI1_T XN_2

DDI1_T XP_3

DDI1_T XN_3

DDI1_AU XP

DDI1_AU XN

DDI0_T XP_0

DDI0_T XN_0

DDI0_T XP_1

DDI0_T XN_1

DDI0_T XP_2

DDI0_T XN_2

DDI0_T XP_3

DDI0_T XN_3

DDI0_AU XP

DDI0_AU XN

MIPI_I2C_SDA

MIPI_I2C_SCL

DDI0_R COMP_P

DDI0_R COMP_N

GPIO_200

GPIO_199

EDP_T XP_0

EDP_T XN_0

EDP_T XP_1

EDP_T XN_1

EDP_T XP_2

EDP_T XN_2

EDP_T XP_3

EDP_T XN_3

EDP_RC OMP_P

EDP_RC OMP_N

EDP_AU XP

EDP_AU XN

DDI1_D DC_SDA

DDI1_D DC_SCL

DDI0_D DC_SDA

DDI0_D DC_SCL

PNL1_V DDEN

PNL1_B KLTEN

PNL1_B KLTCTL

PNL0_V DDEN

PNL0_B KLTEN

PNL0_B KLTCTL

OSC_C LK_OUT_0

OSC_C LK_OUT_1

OSC_C LK_OUT_2

OSC_C LK_OUT_3

OSC_C LK_OUT_4

OSCOU T

OSCIN

BXT_P_ SOC_BGA1296U22D

MCSI_DPH Y1.2_RC OMP

MCSI_RX_ DATA0_ P

MCSI_RX_ DATA0_ N

MCSI_RX_ CLK0_P

MCSI_RX_ CLK0_N

MCSI_RX_ DATA1_ P

MCSI_RX_ DATA1_ N

MCSI_RX_ DATA2_ P

MCSI_RX_ DATA2_ N

MCSI_RX_ CLK1_P

MCSI_RX_ CLK1_N

MCSI_RX_ DATA3_ P

MCSI_RX_ DATA3_ N

MCSI_DPH Y1.1_RC OMP

GP_CAME RASB10

GP_CAME RASB11

Section 4 of 12

MDSI_RCO MP

MDSI_C_D P_0

MDSI_C_D N_0

MDSI_C_D P_1

MDSI_C_D N_1

MDSI_C_D P_2

MDSI_C_D N_2

MDSI_C_D P_3

MDSI_C_D N_3

MDSI_C_C LKP

MDSI_C_C LKN

MDSI_A_D P_0

MDSI_A_D N_0

MDSI_A_D P_1

MDSI_A_D N_1

MDSI_A_D P_2

MDSI_A_D N_2

MDSI_A_D P_3

MDSI_A_D N_3

MDSI_A_C LKP

MDSI_A_C LKN

MCSI_DP_ 0

MCSI_DN_ 0

MCSI_DP_ 1

MCSI_DN_ 1

MCSI_DP_ 2

MCSI_DN_ 2

MCSI_DP_ 3

MCSI_DN_ 3

MCSI_CLK P_0

MCSI_CLK N_0

MCSI_CLK P_2

MCSI_CLK N_2

GP_CAME RASB0

GP_CAME RASB1

GP_CAME RASB2

GP_CAME RASB3

GP_CAME RASB4

GP_CAME RASB5

GP_CAME RASB6

GP_CAME RASB7

GP_CAME RASB8

GP_CAME RASB9

MDSI_A_T E

MDSI_C_T E

MDSI_RCO MP

AP7

AK7

AK6

AM5

AM6

AM12

AM10

AK13

AM13

AM9

AM7

AP12

AP10

AR2

AR1

AP15

AP13

AP6

AP5

AP2

AP3

MNPH_R COMP

F27

M23

P23

L23

J23

J21

H21

M25

L25

F25

E25

H25

J25

MCSI_RCO MP

H27

P17

M17

P21

R21

L17

J17

F17

E17

M19

L19

H19

F19

L37

P34

J34

H30

M37

F30

R35

L34

M34

M35

R34

E30

M45

M43

R420

150_1% _4

R193

150_1% _4

R182

150_1% _4

12

GND

12

GND

12

GND

PCH_D ISP_ON_ C

Q17A

PJ4N3 KDW

Q17B

PJ4N3 KDW

GND

PCH_ED P_BLON_C

Q16A

PJ4N3 KDW

Q16B

PJ4N3 KDW

GND

PCH_D PST_PWM_C

Q15A

PJ4N3 KDW

Q15B

PJ4N3 KDW

GND

R277

5

2

5

2

5

2

10K_5% _4

34

61

R263

10K_5% _4

34

61

R267

10K_5% _4

34

61

2nd source :BG619200014 (TXC)

5

4

3

2

+3V

R270

10K_5% _4

1 2

1 2

PCH_D ISP_ON {14}

+3V

R272

10K_5% _4

PCH_ED P_BLON {14}

+3V

R274

1 2

10K_5% _4

PCH_D PST_PWM { 14}

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Docum ent Numb er Rev

Size Docum ent Numb er Rev

Size Docum ent Numb er Rev

Date: Sheet of

Thursd ay, March 02, 2017

Date: Sheet of

Thursd ay, March 02, 2017

Date: Sheet of

Thursd ay, March 02, 2017

PROJECT :

Valley 3/9 (Display)

Valley 3/9 (Display)

Valley 3/9 (Display)

1

ZHV

ZHV

ZHV

344

344

344

3A

3A

3A

04

5

+1.8V_S5{4,6,8,10,13, 15,17,21,22,23 ,24,28,30}

+3V_S5{6,8,13 ,15,21,22,23,2 5,30}

VSTBY_FSPI{13}

+1.8V{14,17,20,2 2,30,31}

+3V{4,13,14,16,1 7,18,19,20,21 ,22,23,25,26,27 ,28,30,31}

Direct Conne ct Interface ( DCI) then only USB Port

+1.8V_S5

R136

*10K_1%_4

10K_1%_4

*10K_1%_4

R135

+1.8V_S5

R140

D D

0 and Port 1 can be used MoW_WW42

USB3.0 Port

1 2

1 2

GND GND

+1.8V_S5

SOC_USB_OC 1{18}

1 2

Dualrole

USB3.0

USB 2.0 Port 1

Bluetoo th

Touch Screen

CCD

Card Re ader

SATA H DD(option)

SATA H DD

C C

B B

A A

need check up & Low Resit ance

3.3V

3.3V

3.3V

3.3V

CLK_24M_D EBUG{21}

CLK_TPM{21}

CLKRUN#{13,21}

LPC_LFRAM E#{13,21}

SOC_SERIRQ{2 1,23}

0 = No Override (Normal Operation)

1 = Override

ME_W R#{13}

2016/01/21

Intel reques t change to 6 80ohm

Can remove ( un-stuff) for QS sample

FST_SPI_D3_R FST_SPI_D3

FST_SPI_D2_R

LPC Signal

As same as B raswell

1.8V/3.3V

Modify LPC 10/27

LPC_LAD0{13,21}

LPC_LAD1{13,21}

LPC_LAD2{13,21}

LPC_LAD3{13,21}

CLK_PCI_EC{13}

R452 20_5%_4

R459 TPM@20_5%_4

R195

SOC_Override_NM

1 2

*short_0402

R113

ACZ_SYNC PCH_AZ_COD EC_SDIN0

1 2

*249_1%_4

5

When USB OTG feature is not required, USB2_OTG_ID needs to be connected to

GND, and USB2_VBUS_SNS n eeds to be pull up to V1p8A with external 8-10kohm

resistor PDG 0.9 10/27

10/22 change USB3.0 to p ort 1

USB30_TX1+{18}

USB30_TX1-{18}

USB30_RX 1+{18}

USB30_RX 1-{18}

USB2_CN2_ P{1 8}

USB2_CN2_ N{18}

USB_BT4_P{21}

USB_BT4_N{21}

USB_TS5_P{14}

USB_TS5_N{14}

USB_CCD6_ P{14}

USB_CCD6_ N{14}

USB_CAR7 _P{18}

USB_CAR7 _N{18}

SATA_TXP1{17}

SATA_TXN1{17}

SATA_RXP1{17}

SATA_RXN1{17}

SATA_TXP0{17}

SATA_TXN0{17}

SATA_RXP0{17}

SATA_RXN0{17}

R533 *s hort_0402

R507 *s hort_0402

+1.8V_S5

12

12

3

2

1

GND

12

GND

R109

*680_1%_4

R131 137_1%_ 4

R146 113_1%_ 4

R133 *0_5%_4

R208 10K_ 5%_4

R243 10K_ 5%_4

TP8

TP7

USBP1+{18}

USBP1-{18}

TP10

TP9

12

12

EMMC_DATA _0{17}

EMMC_DATA _1{17}

EMMC_DATA _2{17}

EMMC_DATA _3{17}

EMMC_DATA _4{17}

EMMC_DATA _5{17}

EMMC_DATA _6{17}

EMMC_DATA _7{17}

EMMC_RCL K{17}

EMMC_CMD{17}

EMMC_CLK{17}

GPIO_104{10}

GPIO_105{10}

GPIO_106{10}

GPIO_110{10}

GPIO_111{10}

GPIO_112{10}

GPIO_113{10}

GPIO_117{10}

GPIO_120{10}

GPIO_121{10}

GPIO_123{10}

R462 20_5%_4

R458 20_5%_4

R464 20_5%_4

R461 20_5%_4

R453 20_5%_4

R463 20_5%_4

R152 20_5%_4

R147 20_5%_4

GPIO_39{10}

GPIO_40{10}

GPIO_43{10}

GPIO_44{10}

GPIO_47{10}

GPIO_48{10}

R483

*short_0402

Q10

2N7002K

1 2

12

12

TP12

TP27

TP32

TP30

TP13

TP31

TP11

TP15

SOC_Override

12

12

12

FST_SPI_D0

FST_SPI_D1

FST_SPI_D2

SOC_SPI_CS#

SOC_SPI_CLK

12

R4822.2K_5%_4

12

12

12

12

12

12

12

12

USB_VBUS SNS

USB_SSIC_R COMP

USB_RCOMP

Dualrole

SOC_USB_OC 0

SOC_USB_OC 1

GPIO_104

GPIO_105

GPIO_106

GPIO_110

GPIO_111

GPIO_112

GPIO_113

GPIO_117

SOC_Override

GPIO_120

GPIO_121

GPIO_123

LPC_LAD0_ R

LPC_LAD1_ R

LPC_LAD2_ R

LPC_LAD3_ R

SOC_CLKOUT_0

SOC_CLKOUT_1

SOC_CLKRU N#

LPC_LFRAM E#_R

SOC_SERIRQ_R

GPIO_39

GPIO_40

GPIO_43

GPIO_44

GPIO_47

GPIO_48

SOC_EXT_SM I#

4

J1

USB3_P0_TXP

J2

USB3_P0_TXN

K9

USB3_P0_RXP

K10

USB3_P0_RXN

K3

USB3_P1_TXP

K2

USB3_P1_TXN

F2

USB3_P1_RXP

G2

USB3_P1_RXN

AC16

USB2_VBUS_SN S

AB15

USB_SSIC_R COMP

Y15

USB2_RCOM P

AC15

USB2_OTG_ID

AH13

USB_SSIC_0_ TX_P

AH12

USB_SSIC_0_ TX_N

AG16

USB_SSIC_0_ RX_P

AG15

USB_SSIC_0_ RX_N

B55

USB2_OC0_N

C55

USB2_OC1_N

V12

USB2_DP0

V10

USB2_DN0

V16

USB2_DP1

V15

USB2_DN1

Y13

USB2_DP2

V13

USB2_DN2

V9

USB2_DP3

V7

USB2_DN3

Y9

USB2_DP4

Y10

USB2_DN4

AB6

USB2_DP5

AB7

USB2_DN5

AC12

USB2_DP6

AC10

USB2_DN6

V5

USB2_DP7

V6

USB2_DN7

W1

SATA_P1_USB3 _P5_TXP

W2

SATA_P1_USB3 _P5_TXN

T5

SATA_P1_USB3 _P5_RXP

T6

SATA_P1_USB3 _P5_RXN

Y3

SATA_P0_TXP

Y2

SATA_P0_TXN

T9

SATA_P0_RXP

T7

SATA_P0_RXN

A58

FST_SPI_MO SI_IO0

B58

FST_SPI_MI SO_IO1

B61

FST_SPI_IO 3

B60

FST_SPI_IO 2

C57

FST_SPI_CS 1_N

B57

FST_SPI_CS 0_N

C56

FST_SPI_CL K

V58

EMMC_D0

T58

EMMC_D1

T59

EMMC_D2

V51

EMMC_D3

V52

EMMC_D4

Y49

EMMC_D5

V55

EMMC_D6

V57

EMMC_D7

V54

EMMC_RC LK

Y51

EMMC_CM D

Y58

EMMC_CLK

F54

SIO_SPI_0_CL K

F52

SIO_SPI_0_FS 0

H52

SIO_SPI_0_FS 1

H54

SIO_SPI_0_RX D

J52

SIO_SPI_0_TX D

F58

SIO_SPI_1_CL K

K55

SIO_SPI_1_FS 0

F61

SIO_SPI_1_FS 1

H57

SIO_SPI_1_RX D

H58

SIO_SPI_1_TX D

F62

SIO_SPI_2_CL K

D61

SIO_SPI_2_FS 0

E56

SIO_SPI_2_FS 1

D59

SIO_SPI_2_FS 2

C62

SIO_SPI_2_RX D

E62

SIO_SPI_2_TX D

Y61

LPC_AD0

Y62

LPC_AD1

W62

LPC_AD2

W63

LPC_AD3

AB61

LPC_CLKOUT 0

AA62

LPC_CLKOUT 1

V62

LPC_CLKRU N_N

V61

LPC_FRAME _N

AB62

LPC_SERIRQ

B45

LPSS_UART0 _TXD

C45

LPSS_UART0 _RXD

A46

LPSS_UART0 _RTS_N

C44

LPSS_UART0 _CTS_N

B43

LPSS_UART1 _TXD

C43

LPSS_UART1 _RXD

A42

LPSS_UART1 _RTS_N

C42

LPSS_UART1 _CTS_N

H41

LPSS_UART2 _TXD

J41

LPSS_UART2 _RXD

L41

LPSS_UART2 _RTS_N

M41

LPSS_UART2 _CTS_N

P51

SDIO_PWR_ DWN_N

T52

SDIO_D0

P57

SDIO_D1

T54

SDIO_D2

T55

SDIO_D3

T57

SDIO_CMD

P58

SDIO_CLK

AB55

SDCARD_LV L_WP

AC49

SDCARD_D 0

AC48

SDCARD_D 1

AC51

SDCARD_D 2

AB51

SDCARD_D 3

AC52

SDCARD_C MD

AB58

SDCARD_C LK

AB54

SDCARD_C D_N

4

PCIE2_USB3_ SATA3_RCOMP_ P

PCIE2_USB3_ SATA3_RCOMP_ N

PCIE_P3_USB 3_P4_TXP

PCIE_P3_USB 3_P4_TXN

PCIE_P3_USB 3_P4_RXP

PCIE_P3_USB 3_P4_RXN

PCIE_P4_USB 3_P3_TXP

PCIE_P4_USB 3_P3_TXN

PCIE_P4_USB 3_P3_RXP

PCIE_P4_USB 3_P3_RXN

PCIE_P5_USB 3_P2_TXP

PCIE_P5_USB 3_P2_TXN

PCIE_P5_USB 3_P2_RXP

PCIE_P5_USB 3_P2_RXN

Section 3 of 12

BXT_P_SOC_B GA1296U22E

GPIO_RCOM P

EMMC_RC OMP

ISH_GPIO_0

ISH_GPIO_1

Section 5 of 12

ISH_GPIO_2

ISH_GPIO_3

ISH_GPIO_4

ISH_GPIO_5

ISH_GPIO_6

ISH_GPIO_7

ISH_GPIO_8

ISH_GPIO_9

LPSS_I2C0_SD A

LPSS_I2C0_SC L

LPSS_I2C1_SD A

LPSS_I2C1_SC L

LPSS_I2C2_SD A

LPSS_I2C2_SC L

LPSS_I2C3_SD A

LPSS_I2C3_SC L

LPSS_I2C4_SD A

LPSS_I2C4_SC L

LPSS_I2C5_SD A

LPSS_I2C5_SC L

LPSS_I2C6_SD A

LPSS_I2C6_SC L

LPSS_I2C7_SD A

LPSS_I2C7_SC L

BXT_P_SOC_B GA1296U22C

PCIE_WAKE3 _N

PCIE_WAKE2 _N

PCIE_WAKE1 _N

PCIE_WAKE0 _N

PCIE_P0_TXP

PCIE_P0_TXN

PCIE_P0_RXP

PCIE_P0_RXN

PCIE_P1_TXP

PCIE_P1_TXN

PCIE_P1_RXP

PCIE_P1_RXN

PCIE_P2_TXP

PCIE_P2_TXN

PCIE_P2_RXP

PCIE_P2_RXN

PCIE_CLKRE Q0_N

PCIE_CLKRE Q1_N

PCIE_CLKRE Q2_N

PCIE_CLKRE Q3_N

PCIE_CLKOU T0P

PCIE_CLKOU T0N

PCIE_CLKOU T1P

PCIE_CLKOU T1N

PCIE_CLKOU T2P

PCIE_CLKOU T2N

PCIE_CLKOU T3P

PCIE_CLKOU T3N

RSVD_V49

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

GPIO_18

GPIO_19

GPIO_20

GPIO_21

GPIO_22

GPIO_23

GPIO_24

GPIO_25

GPIO_26

GPIO_27

GPIO_28

GPIO_29

GPIO_30

GPIO_31

GPIO_32

GPIO_33

PU@ page23

PCIE_WA KE3_N

N62

PCIE_WA KE2_N

P61

P62

R62

F6

SOC_PCIE_COM P

SOC_PCIE_COM N

F5

PCIE_TXP3_W LAN_C

P3

PCIE_TXN3_W LAN_C

P2

P12

P10

N2

M2

H5

H6

L2

L1

K7

M7

8/15: Change U32 to Open dr ain type IC ,s o R188 can rem ove it.

V3

V2

P7

P6

R1

R2

T10

T12

PCIE_TXP2_LA N_C

T2

PCIE_TXN2_LA N_C

T3

M5

M6

PCIE_CLKRE Q0#

AK62

PCIE_CLKRE Q1#

AH62

PCIE_CLKRE Q2_LAN#

AH61

PCIE_CLKRE Q3_WLAN #

AJ62

C11

B11

C10

A10

A7

B8

B7

B5

C1

RSVD_C1

F1

RSVD_F1

B4

RSVD_B4

A4

RSVD_A4

A18

RSVD_A18

C19

RSVD_C19

V49

SOC_GPIO_RCOM P

E34

EMMC_RCOM P

V59

BOARD_ID0

A38

BOARD_ID1

B33

BOARD_ID2

C39

BOARD_ID3

B39

BOARD_ID4

B35

BOARD_ID5

A34

B31

BOARD_ID6

H39

B29

BOARD_ID7

A30

L39

GPIO_11

C34

E39

C30

C38

F39

C36

C35

J39

C33

B27

C26

A26

B25

C25

C27

C31

C29

B37

H35

C37

H34

F35

F34

AM48

AK58

AK51

AM54

AM51

AM49

AM57

AM55

AM52

AK57

AR62

AR63

AN62

AM61

AP59

AP58

AM62

AL62

AP52

AP54

AP49

AP51

AL63

AK61

AP62

AP61

Gsensor_INT

TP_INT#

TP_INT_C

RAM_ID0

RAM_ID1

RAM_ID2

RAM_ID3

RAM_ID4

EMMC_ID0

EMMC_ID1

RAM_ID5

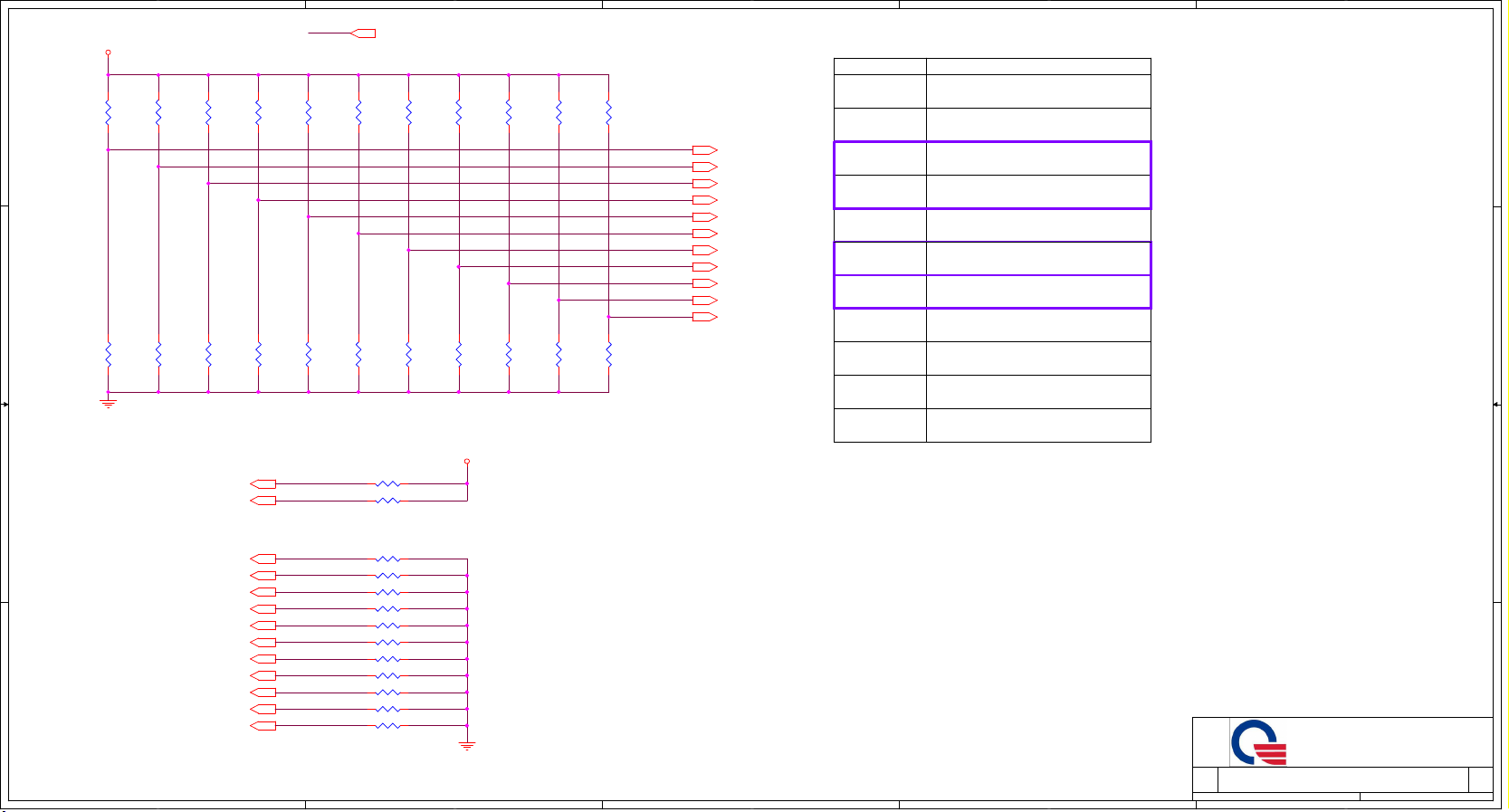

ACZ_BCLK

ACZ_SYNC

ACZ_SDOUT

UART2_RXD

UART2_TXD

UART2_RTS

UART2_CTS

I2C_0_SDA

I2C_0_SCL

I2C_1_SDA

I2C_1_SCL

I2C_2_SDA

I2C_2_SCL

I2C_3_SDA

I2C_3_SCL

I2C_4_SDA

I2C_4_SCL

I2C_5_SDA

I2C_5_SCL

I2C_6_SDA

I2C_6_SCL

I2C_NFC_SOC_S DA

I2C_NFC_SOC_S CL

R540 *short_04 02

the trace

need >1000 mil

11/02 modify

C364 0.1u/1 6V_4

C363 0.1u/1 6V_4

PCIE_CLKRE Q3_WLAN #

PCIE_CLKRE Q2_LAN#

PCIE_CLKRE Q1#

PCIE_CLKRE Q0#

C357 0.1u/16V _4

C359 0.1u/16V _4

12

R197 200_1%_4

12

R151 200_1%_4

TP14

12

12

R142 *0_5%_4

12

R139 *0_5%_4

TP5

TP4

SPKR {19}

1 2

R89 *short_0402

1 2

R90 *short_0402

T24

T25

3

PCIE_WA KE3_N {23}

PCIE_WA KE2_N {22}

12

PCIE_TXP3_W LAN {21}

PCIE_TXN3_W LAN {21 }

PCIE_RXP3_ WLAN {21}

PCIE_RXN3_W LAN {21}

R94 *10K_5%_4

R148 10K_5%_4

R425 10K_5%_4

R416 10K_5%_4

PCIE_CLKRE Q2_LAN# {22}

PCIE_CLKRE Q3_WLAN # {21}

CLK_PCIE_L ANP {22}

CLK_PCIE_L ANN {22}

CLK_PCIE_W LANP {21}

CLK_PCIE_W LANN {21}

GND

SENSOR_HU B_INT1# {20}

SOC_KBC_S CI {23 }

Gsensor_INT {23}

TP_INT# {15}

DEVSLP0 {17}

DEVSLP1 {17}

Follow APL PD G 0.9

33 ohm +-5%

1 2

R103 33_5%_4

1 2

R115 33_5%_4

1 2

R106 33_5%_4

I2C_1_SDA {20}

I2C_1_SCL {20}

I2C_2_SDA {20}

I2C_2_SCL {20}

I2C_4_SDA_R {15}

I2C_4_SCL_R {15}

3

WLAN

R175

402_1%_4

WLAN x1

+1.8V_S5

12

12

12

12

PCIE_TXP2_LA N {22}

PCIE_TXN2_LA N {22}

PCIE_RXP2_ LAN {22}

PCIE_RXN2_L AN {2 2}

LAN

WLAN

LSB:RAM_ID0, MSB:RAM_ID3

Touch pad

Touch panel

PCH_AZ_COD EC_BITCLK {19}

PCH_AZ_COD EC_SYNC {19}

PCH_AZ_COD EC_SDIN0 {19}

PCH_AZ_COD EC_SDOUT {19}

ISH_Mode1 {20}

ISH_Mode2 {20}

Reserve

Sensor HUB

Reseve for Gsensor

Touch panel

Touch pad

2

SPI ROM

VCC_SPI_BIOS

C387 0.1u/1 6V_4

VCC_SPI_BIOS

R538

1 2

3.3K_1%_4

GND

FST_SPI_D3_R

8

7

4

GND

VCC

IO3

VSS

GD25LB64CS IGR

SPI ROM

BOARD ID

1.8V

+1.8V_S5

GGD

B-Test U se

WND

1 2

R496 10K_5%_4

1 2

R492 *10K_5%_4

1 2

R497 *10K_5%_4

1 2

R527 10K_5%_4

1 2

R494 10K_5%_4

1 2

R493 *10K_5%_4

1 2

R236 10K_5%_4

1 2

R250 10K_5%_4

Board ID 0 0 = Non Touch Screen

Board ID 1

Board ID 2

Board ID 3

Board ID 4

Board ID 5 0 = With Connector

Board ID 6

Board ID 7

+1.8V_S5

1 2

RAM ID

RAM ID 0 0 = Single chanel (A)

RAM ID 1

RAM ID 2

RAM ID 3 Define vendor

RAM ID 4

RAM ID 5

EMM C ID

R225 10K_5%_4

1 2

R251 *10K_5%_4

1 2

R232 *10K_5%_4

1 2

R233 *10K_5%_4

1 2

R235 10K_5%_4

BIOS Strap DescriptionHardware ID

Chanel

1 = Dual chanel(A&B)

A Chanel

0 = 2GB

1 = 4GB

B Chanel

0 = 2GB

1 = 4GB

Define vendor

Reserve

Vender RAM_ID [1:0] Q PN EMMC

Samsung 00

Hynix 01

Kingston 10 Kingston 32/64

Reserve

I2C PU

I2C_0_SDA

I2C_0_SCL

I2C_1_SDA

I2C_1_SCL

I2C_2_SDA

I2C_2_SCL

I2C_3_SDA

I2C_3_SCL

I2C_4_SDA

I2C_4_SCL

I2C_5_SDA

I2C_5_SCL

I2C_6_SDA

I2C_6_SCL

I2C_NFC_SOC_S DA

I2C_NFC_SOC_S CL

2

1 2

R404 *1K_5%_4

1 2

R407 *1K_5%_4

1 2

R408 1K_5%_4

1 2

R415 1K_5%_4

1 2

R102 *1K_5%_4

1 2

R93 *1K_5%_4

1 2

R411 *1K_5%_4

1 2

R421 *1K_5%_4

1 2

R88 1K_5%_4

1 2

R91 1K_5%_4

1 2

R86 *1K_5%_4

1 2

R87 *1K_5%_4

1 2

R417 *1K_5%_4

1 2

R422 *1K_5%_4

1 2

R409 *1K_5%_4

1 2

R414 *1K_5%_4

VSTBY_FSPI VCC_SPI_BIOS

R545 *s hort_0402

12

U29

1

CE#

6

SCLK

5

SI

2

SO

3

IO2

8M QE =1

8M QE =1

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

BOARD_ID5

BOARD_ID6

BOARD_ID7

BIOS Strap DescriptionHardware ID

Touch Screen function

1 = Touch Screen

Borad id1 =0

Borad id1 =1

0 = Reserve

G-Senor function

0 = Non G-Senor

1 = G-Senor

DTPM function

0 = Non DTPM

1 = DTPM

Reserve for Sata0 (conne ctor)

1 = Without Connector

Reserve for Sata1 (SSD)

0 = With SSD

1 = Without SSD

Reserve

1 2

R228*10K_5%_4

1 2

R22910K_5%_4

1 2

R234*10K_5%_4

VCC_SPI_BIOS

SOC_SPI_CS# _R

R504 *short_0402

SOC_SPI_CLK _R SOC_SPI_CLK

R510 33_5%_4

SOC_SPI_MOS I_R FST_SPI_D0

R506 *short_0402

SOC_SPI_MISO_ R FST_SPI_D1

R505 *short_0402

FST_SPI_D2_R

SPI Socket P /N:DFHS08FS023

Quanta P/NSizeVender Vender P/N

AKE5EZ N0N01

1 2

R525 *10K_5%_4

1 2

R522 10K_5%_4

1 2

R526 10K_5%_4

1 2

R498 *10K_5%_4

1 2

R524 *10K_5%_4

1 2

R523 10K_5%_4

1 2

R256 *10K_5%_4

1 2

R223 *10K_5%_4

RAM_ID0

R252 *10K_5%_4

RAM_ID1

R224 10K_5%_4

RAM_ID2

R231 10K_5%_4

RAM_ID3

R253 10K_5%_4

RAM_ID4

R255 *10K_5%_4

RAM_ID5

EMMC_ID0

EMMC_ID1

Vendor

Samsung

Hynix

Micron

Reserve

SAMSUNG 32/64

AR0ZH TR1005

HYNIX 32/64

+1.8V_S5

TP_RST#_Q{6,2 3}

Size Do cument Nu mber Rev

Size Do cument Nu mber Rev

Size Do cument Nu mber Rev

Date: Sheet of

Thursday, March 02, 2017

Date: Sheet of

Thursday, March 02, 2017

Date: Sheet of

Thursday, March 02, 2017

1

R536 * 3.3K_1%_4

1 2

SOC_SPI_CS#

12

1 2

12

12

VCC_SPI_BIOS

R532

12

3.3K_1%_4

GD25LB64CS IGRAKE5EG- 0Q01

W25Q64 FWSSIQ

EMMC < default >

EMMC < HDD onl y>

1 2

1 2

1 2

1 2

1 2

1 2

R22710K_5%_4

1 2

R230*10K_5%_4

1 2

R25410K_5%_4

RAM_ID[4:3] Q PN

00

01

10

TP_INT#

TP_INT_C

TP_RST#_Q

Gsensor_INT

SOC_EXT_SM I#

Valley 4/ 9 (SD/PC IE/SATA)

Valley 4/ 9 (SD/PC IE/SATA)

Valley 4/ 9 (SD/PC IE/SATA)

1 2

R257 10K_5%_4

1 2

R491 10K_5%_4

1 2

R262 10K_5%_4

1 2

R495 10K_5%_4

1 2

R226 10K_5%_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ZHV

ZHV

ZHV

1

05

AKD59G STL12

+1.8V_S5

345

345

345

3A

3A

3A

5

4

3

2

1

+1.8V_S5 {4,5,8,1 0,13,15,17,21,22 ,23,24,28,30}

+3V_S5 {8,13,15,21,22,23, 25,30}

+1.05V {8,26,28}

+3V {4,13, 14,16,17,18,19, 20,21,22,23,25,2 6,27,28,30,31}

All P MU ca n set to 1 .8/3. 3V

ZHP s et to 3.3V

06

Modify 11/14

12/23 follo w Intel

PDG 1.0 cha nge R435

to 1K ohm.

1 2

+1.8V_S5

CORE_PWR OK

SOC_RSMR ST#

SUS_PWRD NACK

PCH_SUS_S TAT#

PMU_BATLO W#

AC_PRESEN T

SLP_S0IX#

SOC_REST_ BTN#

SOC_PLTRS T#

AC_PRESEN T

R515 *short_0402

R511 1K_5%_4

TP_RST#_Q{5,23}

R427

200_1%_4

+3V_S5

Touch panel

PMU_RCO MP

1 2

GND

10/21 c hange T P_RST to GPIO f ollow CR B

R170 1K_5%_4

1 2

R161 1K_5%_4

1 2

R469 1K_5%_4

D D

+1.8V_S5

+3V_S5

R124

R128

*short_0402

*0_5%_4

1 2

1 2

R110 20K_5%_4

R119 *20K_5%_4

R439 *10K_5%_4

R114 *10K_5%_4

R104 *20K_5%_4

R118 1K_5%_4

R96 10K_5%_4

R440 *10K_5%_4

R443 10K_5%_4

R111 *10K_5%_4

R92 *10K_5%_4

GND

C C

+1.8V_S5

R465

1 2

*10K_5%_4

H_PROCH OT#{13,24,28}

10/28 Modi fy PMU

Voltage to 3.3V

Modify 11/ 04

1 2

1 2

1 2

1 2

1 2

12

1 2

1 2

1 2

1 2

1 2

For Intel MoW04

PMIC_TH ERMTRIR_N

SOC_PMC_ WAKE

Pin AG55 is EMMC_PWR_EN_N (CRB 1.0)

SOC_RSMR ST#{23}

T27

SLP_S4#{23}

SLP_S3#{23}

SOC_PWRB TN#{23}

SOC_PLTRS T#{23}

CORE_PWR OK{23}

PMIC_TH ERMTRIR_N

DDI1_EDP _HPD_R{14}

GPIO_34{10}

GPIO_35{10}

GPIO_36{10}

+3V_RTC

R141

330K_5%_4

SOC_RTEST #

SOC_RSMR ST#

SOC_PROC HOT#

SOC_PMC_ WAKE

PMU_WIF I_SUSCLK

SLP_S4#

SLP_S3#

SLP_S0IX#

SOC_REST_ BTN#

PMU_RCO MP

SOC_PWRB TN#

SOC_PLTRS T#

PMU_BATLO W#

AC_PRESEN T

CORE_PWR OK

GPIO_34

GPIO_35

GPIO_36

12

R259 *0_5%_4

12

INTRUD ER#

SMB_SOC_D ATA

SMB_SOC_C LK

SMB_SOC_AL ERTB

AH49

RTC_TEST _N

AC57

RSM_RST_N

E47

PROCHOT_N

AG55

PMU_WAKE_N

AE62

PMU_SUSCLK

AK54

PMU_SLP_S4_N

AC62

PMU_SLP_S3_N

AD61

PMU_SLP_S0_N

AD62

PMU_RSTBTN_N

AG59

PMU_RCOMP

AK55

PMU_PWRBTN_N

AG57

PMU_PLTRST_N

AH51

PMU_BATLOW_N

AK49

PMU_AC_PRESENT

AG49

SOC_PWRO K

J47

PMIC_THERMTRIP_N

J45

PMIC_STDBY

M47

PMIC_SDWN_B_GPIO_213

F48

PMIC_RESET_N

H48

PMIC_PWRGOOD

F47

PMIC_I2C_SDA

H45

PMIC_I2C_SCL

L47

GPIO_214

P47

GPIO_215

H50

PMC_SPI_TXD

J50

PMC_SPI_RXD

M48

PMC_SPI_FS2

P48

PMC_SPI_FS1

L48

PMC_SPI_FS0

E52

PMC_SPI_CLK

B41

PWM0

C41

PWM1

F41

PWM2

E41

PWM3

B21

JTAGX

AC54

INTRUDER

T61

SMB_DATA

T62

SMB_CLK

R63

SMB_ALERT_N

H43

RSVD_H43

AG52

RSVD_AG52

J43

RSVD_J43

AG54

RSVD_AG54

PMU Block

Section 6 o f 12

BXT_P_SOC_ BGA1296U22F

RTC_RST_N

SUSPWRDNACK

SUS_STAT_N

AVS_I2S1_WS_SYNC

AVS_I2S1_SDO

AVS_I2S1_SDI

AVS_I2S1_MCLK

AVS_I2S1_BCLK

AVS_I2S2_SDO

AVS_I2S2_SDI

AVS_I2S2_MCLK

AVS_I2S2_BCLK

AVS_I2S2_WS_SYNC

AVS_I2S3_WS_SYNC

AVS_I2S3_SDO

AVS_I2S3_SDI

AVS_I2S3_BCLK

AVS_DMIC_DATA_2

AVS_DMIC_DATA_1

AVS_DMIC_CLK_B1

AVS_DMIC_CLK_AB2

AVS_DMIC_CLK_A1

VCC_RTC_EXTPAD

RTC_X2

RTC_X1

JTAG_PREQ_N

JTAG_PRDY_N

JTAG_PMODE

JTAG_TRST _N

JTAG_TMS

JTAG_TDO

JTAG_TDI

JTAG_TCK

GPIO_219

GPIO_218

GPIO_217

GPIO_216

PCIE_REF_CLK_RCOMP

SVID0_DATA

SVID0_CLK

SVID0_ALERT_N

AC55

AC63

AG58

J62

K62

K61

G62

H63

M58

K59

K58

H59

the tra ce

M57

need >1 000 mil

M61

L63

L62

M62

M52

M54

P52

M55

P54

BRTC_EXT PAD

AG51

AC58

AC59

XDP_H_PRE Q#

C20

XDP_H_PRD Y#

C21

B19

XDP_H_TR ST#

C24

XDP_H_TM S

C23

XDP_H_TD O

A22

XDP_H_TD I

C22

XDP_H_TC K

B23

L30

M30

M29

P30

PCIE_REF _CLK_RCOMP

E21

VR_SVID_D ATA

C18

VR_SVID_C LK

C17

B17

R509 220_1%_4

SRT_CRST #

SUS_PWRD NACK

PCH_SUS_S TAT#

GPIO_78

GPIO_88

ACZ_RST#

R179 33_5%_4

GPIO_92

GPIO_82

C111 0.1u/16V_4

RTC_X2

RTC_X1

R518 100_5%_4

R488 100_5%_4

R521 *51_1%_4

R520 51_1%_4

R489 100_5%_4

R519 51_1%_4

R490 51_1%_4

12

12

R444 *10K_5%_4

12

R449 *short_0402

GPIO_78 {10}

GPIO_88 {10}

12

Follow CR B

33 ohm +- 5%

GPIO_92 {10}

GPIO_82 {10}

GND

12

12

12

1 2

12

1 2

1 2

EMMC_RS T {17}

R194

12

60.4_1%_4

VR_SVID_AL ERT#

+1.8V_S5

GND

GND

GND

VR_SVID_D ATA {28}

VR_SVID_C LK {28}

VR_SVID_AL ERT# {28}

+1.8V_S5

PCH_SUSPW RDNACK {13}

PCH_AZ_C ODEC_RST# {19}

RTC Clock 32.768KHz

RTC_X2

10M_5%_4

RTC_X1

Add 10P to GND for layo ut length to o long 11/26

R132

GND

12

C372 *10p/50V_4

C374 *10p/50V_4

C373 *10p/50V_4

12

Y2

32.768KHZ/ 20ppm

C135 15p/50V_4

C128 15p/50V_4

GND

Change from +1.0V to +1 .05V

VR_SVID_D ATA

VR_SVID_AL ERT#

VR_SVID_C LK

SVID_CL K : U P:85 ohm Seri es:95 oh m

SVID_AL ERT : U P:68 ohm Seri es:220 o hm

SVID_DA TA : U P:170 oh m Seri es:20 oh m

12

R517 169_1%_4

1 2

R535 68_5%_4

12

R534 *86.6_1% _4

+1.05V

GND

C189

*0.1u/16V_4

+3V_S5

12

+1.8V_S5+3V_LDO_EC+1.8V_S5

B B

THERMT RIP#{13}

A A

R480

1 2

*10K_5%_4

5

U25

6

VCCA

VCCB

4

B

EO

*G2129TL1U

A

GND

12

R472*short_0402

5

THERM ALTRIP#

1

3

2

ACPRESENT{24}

AC Present: This input pin indicates w hen the

platform is plugged into AC power.

4

34

Q29A

5

*2N7002KDW

GND

R418 *short_0402

R405

*10K_5%_4

2

1 2

61

Q29B

*2N7002KDW

AC_PRESEN T

RTC Circuitry(RTC)

+5V_S5

R8

R4

68.1K_1%_4

R1

150K_1%_4

12

4.7K_5%_4

EC RSET RTC

12

12

3

R7

4.7K_5%_4

20 mils

+3V_RTC

R2

+3V_RTC_0

Q1

MMBT3904- 7-F

VCCRTC _2PMIC_TH ERMTRIR_N VCCRTC _3

12

20 mils

13

12

+ -

20MIL

CN1

AAA-BAT-046-K 03

34

2

+3VPCU

R3

1K_5%_4

20mils

12

VCCRTC _1

20MIL

2

1

update Sy mbol

SRT_CRST #

61

Q2B

2

2N7002KDW

CLR_CMO S{13}

CLR_CMO S SRT_CRST #

GND

SOC_RTEST #

34

Q2A

5

2N7002KDW

GND GND

2

1 2

D1

BAT54CW

20K_5%_4

30mils

3

R5

1 2

20K_5%_4

C7

1u/6.3V_4

C4

1u/6.3V_4

C11

1u/6.3V_4

20MIL

Change G1G2 footpr int from

"SOLDERJU MPER-2" to "RC0603-C" for

SMT reque st

For ESD

C419

0.1u/16V_4

R577

10_5%_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJEC T :

PROJEC T :

Size Document Nu mber Rev

Size Document Nu mber Rev

Size Document Nu mber Rev

Thursday, March 02, 2017

Thursday, March 02, 2017

Thursday, March 02, 2017

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJEC T :

Valle y 6/9 (U SB/LPC/ I2C)

Valle y 6/9 (U SB/LPC/ I2C)

Valle y 6/9 (U SB/LPC/ I2C)

1

SOC_RTEST #

12

G1

*SHORT_ PAD1

SRT_CRST #

12

G2

*SHORT_ PAD1

ZHV

ZHV

ZHV

20MIL

3A

3A

3A

346

346

346

5

4

3

2

1

R29

A12

A16

A20

A24

A28

A32

D D

C C

B B

A A

GND GND GND GND

A36

A40

A44

A48

A5

A52

A56

A62

A9

AA1

AA2

AA27

AA34

AA41

AA63

AB10

AB12

AB16

AB48

AB5

AB52

AB57

AB59

AB9

AC18

AC27

AC34

AC39

AE1

AE10

AE11

AE13

AE14

AE16

AE17

AE2

AE23

AE27

AE34

AE39

AE4

AE41

AE47

AE48

AE5

AE50

AE51

AE53

AE54

AE56

AE57

AE59

AE63

AE7

AE8

AG13

AG18

AG23

AG27

AG34

AG37

AG39

AG41

AG42

AG44

AG46

AH15

AH16

AH48

AH5

AH52

AH54

AH55

AH57

5

BXT_P_ SOC_BGA1296U22J

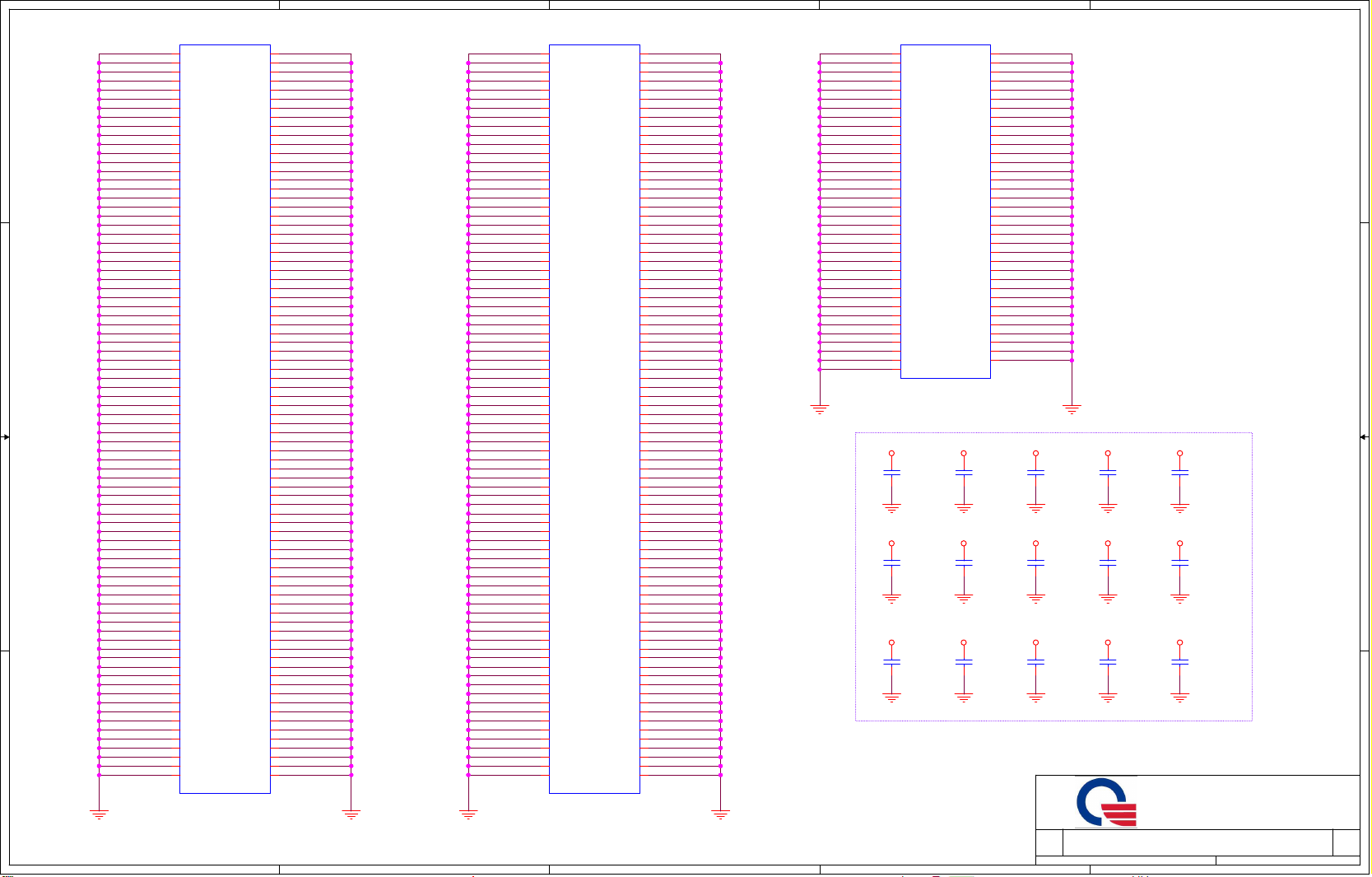

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

Section 10 of 12

AH58

AH59

AH6

AH7

AJ1

AJ18

AJ2

AJ23

AJ27

AJ34

AJ36

AJ63

AK10

AK12

AK18

AK23

AK27

AK36

AK48

AK5

AK52

AK59

AK9

AM18

AM22

AM27

AM34

AM36

AM39

AM46

AN1

AN10

AN11

AN13

AN14

AN16

AN17

AN2

AN25

AN27

AN28

AN30

AN34

AN36

AN37

AN39

AN47

AN48

AN5

AN50

AN51

AN53

AN54

AN56

AN57

AN59

AN63

AN7

AN8

AP55

AP9

AR19

AR32

AR45

AT12

AT16

AT19

AT2

AT25

AT29

AT3

AT35

AT39

AT45

AT48

AT52

AT57

AT61

AT62

AT7

AU32

AV19

AV2

AV21

AV23

AV29

AV3

AV32

AV35

AV41

AV43

AV45

AV55

AV61

AV62

AV9

AW14

AW30

AW34

AW50

AY10

AY32

AY54

AY58

AY6

B2

B3

B62

B63

B9

BA1

BA12

BA16

BA17

BA2

BA21

BA25

BA27

BA29

BA32

BA35

BA37

BA39

BA43

BA47

BA48

BA52

BA62

BA63

BB19

BB25

BB3

BB39

BB45

BB61

BC32

BD3

BD32

BD56

BD61

BD8

BE1

BE10

BE12

BE16

BE17

BE21

BE27

BE29

BE35

BE37

BE43

BE47

BE48

BE52

BE54

BE63

BF3

BF32

BF61

BG19

BG23

4

BXT_P_ SOC_BGA1296U22K

VSS_163

VSS_244

VSS_164

VSS_245

VSS_165

VSS_246

VSS_166

VSS_247

VSS_167

VSS_248

VSS_168

VSS_249

VSS_169

VSS_250

VSS_170

VSS_251

VSS_171

VSS_252

VSS_172

VSS_253

VSS_173

VSS_254

VSS_174

VSS_255

VSS_175

VSS_256

VSS_176

VSS_257

VSS_177

VSS_258

VSS_178

VSS_259

VSS_179

VSS_260

VSS_180

VSS_261

VSS_181

VSS_262

VSS_182

VSS_263

VSS_183

VSS_264

VSS_184

VSS_265

VSS_185

VSS_266

VSS_186

VSS_267

VSS_187

VSS_268

VSS_188

VSS_269

VSS_189

VSS_270

VSS_190

VSS_271

VSS_191

VSS_272

VSS_192

VSS_273

VSS_193

VSS_274

VSS_194

VSS_275

VSS_195

VSS_276

VSS_196

VSS_277

VSS_197

VSS_278

VSS_198

VSS_279

VSS_199

VSS_280

VSS_200

VSS_281

VSS_201

VSS_282

VSS_202

VSS_283

VSS_203

VSS_284

VSS_204

VSS_285

VSS_205

VSS_286

VSS_206

VSS_287

VSS_207

VSS_288

VSS_208

VSS_289

VSS_209

VSS_290

VSS_210

VSS_291

VSS_211

VSS_292

VSS_212

VSS_293

VSS_213

VSS_294

VSS_214

VSS_295

VSS_215

VSS_296

VSS_216

VSS_297

VSS_217

VSS_298

VSS_218

VSS_299

VSS_219

VSS_300

VSS_220

VSS_301

VSS_221

VSS_302

VSS_222

VSS_303

VSS_223

VSS_304

VSS_224

VSS_305

VSS_225

VSS_306

VSS_226

VSS_307

VSS_227

VSS_308

VSS_228

VSS_309

VSS_229

VSS_310

VSS_230

VSS_311

VSS_231

VSS_312

VSS_232

VSS_313

VSS_233

VSS_314

VSS_234

VSS_315

VSS_235

VSS_316

VSS_236

VSS_317

VSS_237

VSS_318

VSS_238

VSS_319

VSS_239

VSS_320

VSS_240

VSS_321

VSS_241

VSS_322

VSS_242

VSS_323

VSS_243

VSS_324

Section 11 of 12

BG29

BG32

BG35

BG41

BG45

BH1

BH2

BH21

BH25

BH39

BH43

BH62

BH63

BJ10

BJ14

BJ18

BJ28

BJ32

BJ36

BJ4

BJ46

BJ50

BJ54

BJ56

BJ60

BJ8

C12

C16

C28

C32

C40

C48

D32

D58

D6

E12

E14

E19

E27

E4

E54

F10

F21

F3

F32

F37

F43

F45

F50

F56

F59

F63

G1

G32

H17

H23

H29

H3

H37

H47

H61

H7

J12

J14

J19

J27

J30

J32

J35

J37

J48

J63

K32

K5

K54

K57

K6

L21

L27

L29

L35

L43

L45

L50

M14

M21

M27

M3

M32

M50

M59

M9

N1

N32

N63

P13

P19

P35

P37

P41

P43

P45

P5

P55

P59

P9

R23

R32

T49

U1

U10

U11

U13

U14

U16

U17

U18

GND GND

+VIN +VIN +VIN +VIN +VIN

GND G ND GND GND GN D

+VIN +VIN +VIN +VIN +VIN

GND G ND GND GND GN D

+VIN +VIN +VIN +VIN +VIN

GND G ND GND GND GN D

BXT_P_ SOC_BGA1296U22L

VSS_325

VSS_326

VSS_327

VSS_328

VSS_329

VSS_330

VSS_331

VSS_332

VSS_333

VSS_334

VSS_335

VSS_336

VSS_337

VSS_338

VSS_339

VSS_340

VSS_341

VSS_342

VSS_343

VSS_344

VSS_345

VSS_346

VSS_347

VSS_348

VSS_349

VSS_350

VSS_351

VSS_352

VSS_353

VSS_354

VSS_355

VSS_356

VSS_357

VSS_358

VSS_359

VSS_360

C225

0.01u/50 V_4

C23

0.01u/50 V_4

C24

0.01u/50 V_4

VSS_361

VSS_362

VSS_363

VSS_364

VSS_365

VSS_366

VSS_367

VSS_368

VSS_369

VSS_370

VSS_371

VSS_372

VSS_373

VSS_374

VSS_375

VSS_376

VSS_377

VSS_378

VSS_379

VSS_380

VSS_381

VSS_382

VSS_383

VSS_384

VSS_385

VSS_386

VSS_387

VSS_388

VSS_389

VSS_390

VSS_391

VSS_392

VSS_393

VSS_394

VSS_395

Sect 12/ 12

C239

0.01u/50 V_4

C5

0.01u/50 V_4

C10

0.01u/50 V_4

U2

U27

U34

U5

U50

U51

U53

U54

U56

U57

U59

U62

U63

U7

U8

V20

V27

V34

V42

Y12

Y16

Y22

Y27

Y34

Y42

Y46

Y48

Y5

Y52

Y54

Y55

Y57

Y59

Y6

Y7

C219

0.01u/50 V_4

C1

0.01u/50 V_4

C51

0.01u/50 V_4

C158

0.01u/50 V_4

C6

0.01u/50 V_4

C333

0.01u/50 V_4

C353

0.01u/50 V_4

C9

0.01u/50 V_4

C241

0.01u/50 V_4

07

Reserve

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Docum ent Numb er Rev

Size Docum ent Numb er Rev

Size Docum ent Numb er Rev

Date: Sheet of

Thursd ay, March 02, 2017

Date: Sheet of

Thursd ay, March 02, 2017

Date: Sheet of

3

2

Thursd ay, March 02, 2017

PROJECT :

Valley 7/9 (GND)

Valley 7/9 (GND)

Valley 7/9 (GND)

1

ZHV

ZHV

ZHV

3A

3A

3A

347

347

347

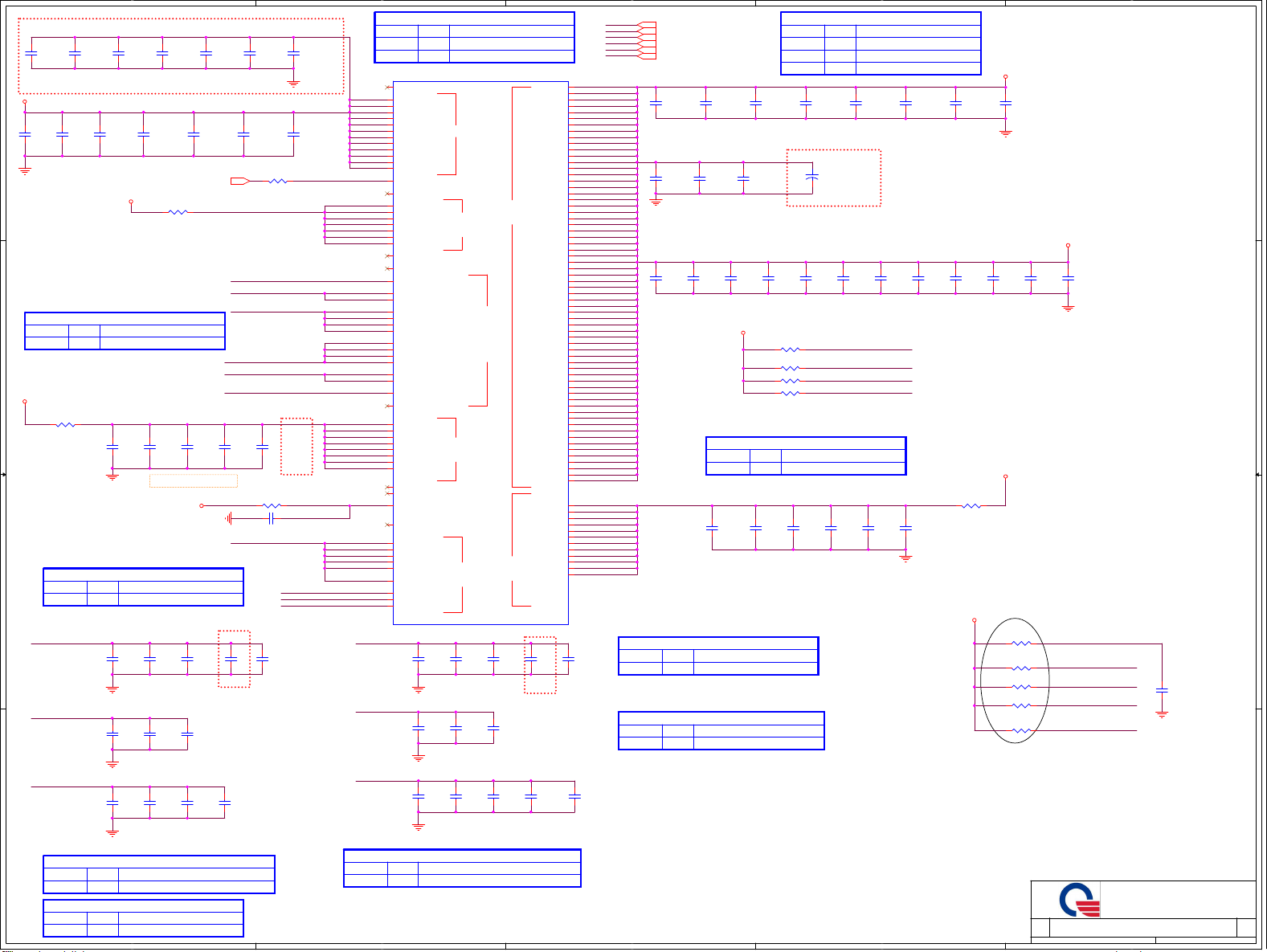

5

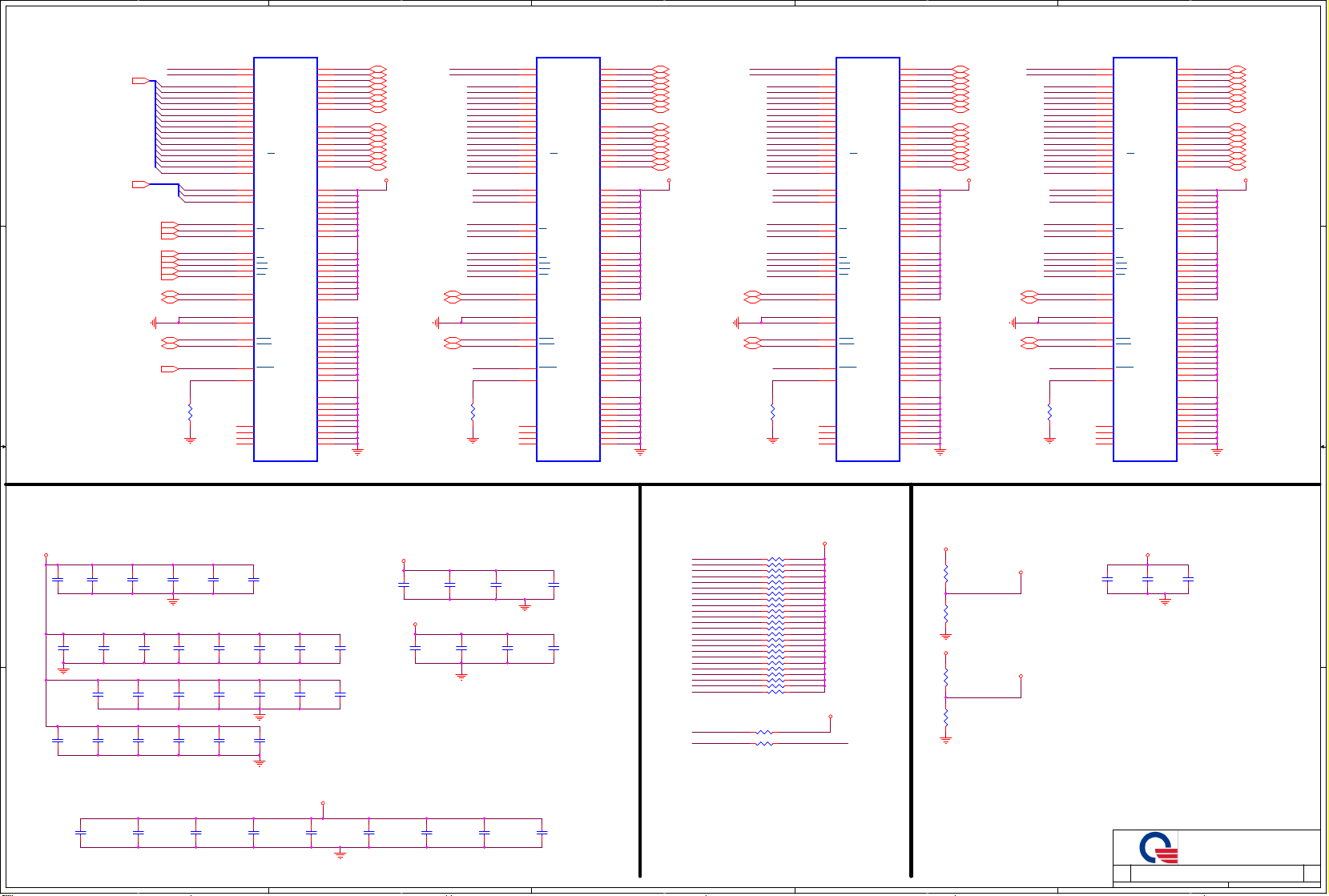

Add it 10/1 7

C376

C391

47u/6.3V_8

+VNN

D D

C125

C114

1u/6.3V_4

1u/6.3V_4

GND

+VDD1_1P8 Output Decoupling Recom mendations

0402

1uFx4

22uFx1

0603 TOP, inside sock et cavity

C C

+1.8V_S5

R122

1 2

*short_0805

VDD3_3P3_USB Output Decoupling Recom mendations

B B

1uFx3

22uFx1

VDD3_3P3_U SB

40mil

VDD2_1P24_A UD_ISH_PLL

40mil

VDD2_1P24_M PHY

A A

VDD2_1P24_AUD_ISH_PLL Output D ecoupling Recommendations

22uFx1

VDD2_1P24_MPHY Output Decoupling Recommendations

22uFx1

C390

47u/6.3V_8

47u/6.3V_8

C122

C123

1u/6.3V_4

22u/6.3V_6

+3V_S5

TOP*2 / BOT* 2, inside socket cavity

C124

22u/6.3V_6

GND

0402

GND

GND

GND

04021uFx2

04021uFx3

CAPS PLACE NEAR SOC PIN

TOP*2 / BOT* 2, inside socket cavity

TOP, inside socket c avity0603

C142

1u/6.3V_4

C335

1u/6.3V_4

C342

1u/6.3V_4

TOP*1 / BOT* 1, inside socket cavity

TOP, inside socket c avity0603

TOP*1 / BOT* 2, inside socket cavity

TOP, inside socket c avity0603

5

1 2

C121

1u/6.3V_4

C146

1u/6.3V_4

C336

1u/6.3V_4

C343

1u/6.3V_4

C378

47u/6.3V_8

R159

*short_0603

+3V_RTC

VNN_SENSE{28}

C203

22u/6.3V_6

+VDD1_1P8

C133

1u/6.3V_4

C139

1u/6.3V_4

C334

22u/6.3V_6

C129

1u/6.3V_4

C377

47u/6.3V_8

GND

Add it 10/2 7

C204

22u/6.3V_6

60mil

VDD3_3P3_U SB

40mil

VDD2_1P24_U SB2

VDD2_1P24_A UD_ISH_PLL

VDD2_1P24_M PHY

VDD2_1P24_G LML

VDD2_1P24_D SI_CSI

VDD2_1P24_A UD_ISH_PLL

C130

1u/6.3V_4

1 2

R153 *short_0603

C150 1u/6.3V_4

VCCRAM_ 1P05_IO_3PHASEIO

C120

1u/6.3V_4

C341

22u/6.3V_6

C392

47u/6.3V_8

GND

R130

1 2

Fixed Vnn S ense

*short_0402

Del it 10/1 7

C136

1u/6.3V_4

VCCRAM_ 1P05_FUSE

VCCRAM_ 1P05_FHV1

VCCRAM_ 1P05_FHV0

C160

22u/6.3V_6

C389

47u/6.3V_8

C110

22u/6.3V_6

VNN_REFI N_R

VRTC_3P3

100mil

4

+VNN Output Decoupling Recomm endations

1uFx3 0402

22uFx4

47uFx7

AJ44

RSVD_AJ44

AJ37

VNN_SVID_1

AJ39

VNN_SVID_2

AJ41

VNN_SVID_3

AJ42

VNN_SVID_4

AJ46

VNN_SVID_5

AK37

VNN_SVID_6

AK39

VNN_SVID_7

AK41

VNN_SVID_8

AK42

VNN_SVID_9

AK44

VNN_SVID_10

AK46

VNN_SVID_11

AM44

VNN_SVID_12

AG48

VNN_SENSE

BG63

RSVD_BG63

AC41

VCC_3P3V_A_1

AA42

VCC_3P3V_A_2

Y44

VCC_3P3V_A_3

V44

VCC_3P3V_A_4

V46

VCC_3P3V_A_5

AJ25

VCC_3P3V_A_USB_1

AK25

VCC_3P3V_A_USB_2

AC22

RSVD_AC22

AC20

RSVD_AC20

AG20

VCC_1P24V_1P35V_A_USB2

AJ20

VCC_1P24V_1P35V_A_PLL_1

AJ22

VCC_1P24V_1P35V_A_PLL_2

AE18

VCC_1P24V_1P35V_A_MPHY_1

AE20

VCC_1P24V_1P35V_A_MPHY_2

AE22

VCC_1P24V_1P35V_A_MPHY_3

AG22

VCC_1P24V_1P35V_A_MPHY_4

AM20

VCC_1P24V_1P35V_A_GLML2LDO_1

AM28

VCC_1P24V_1P35V_A_GLML2LDO_2

AM37

VCC_1P24V_1P35V_A_GLML2LDO_3

AK20

VCC_1P24V_1P35V_A_GLML2

AA18

VCC_1P24V_A_1

AA20

VCC_1P24V_A_2

AK22

VCC_1P24V_1P35V_A_AUD_ISH

V48

RSVD_V48

AA46

VCC_1P8V_A_1

AC46

VCC_1P8V_A_2

AE44

VCC_1P8V_A_3

AE42

VCC_1P8V_A_4

AC42

VCC_1P8V_A_5

AC44

VCC_1P8V_A_6

AE46

VCC_1P8V_A_7

AG25

VCC_1P8V_A_8

BJ3

RSVD_BJ3

BJ61

RSVD_BJ61

AA44

VCCRTC_3P3V

D1

RSVD_D1

AA22

VCC_1P05V_IO_1

AC23

VCC_1P05V_IO_2

V18

VCC_1P05V_IO_3

Y18

VCC_1P05V_IO_4

Y20

VCC_1P05V_IO_5

AA23

VCC_1P05V_3PHASEIO

P16

VCC_1P05V_FUSE

T15

VCC_1P05V_FHV1

T13

VCC_1P05V_FHV0

40mil

VDD2_1P24_G LML

40mil

VDD2_1P24_D SI_CSI

VCCRAM_ 1P05_IO_3PHASEIO

VCCRAM_1P05_IO_3PHASEIO Output Decoupling Recommendations

0402

1uFx4

22uFx1

0603 TOP, inside sock et cavity

4

BOT, inside socket c avity

TOP, inside socket c avity

0603

TOP, inside socket c avity

0805

4.8A

0.15A

TBD

0.4A

2.7A

Section 8 o f 12

C116

C107

1u/6.3V_4

1u/6.3V_4

GND

C348

C347

1u/6.3V_4

1u/6.3V_4

GND

C162

C147

1u/6.3V_4

1u/6.3V_4

GND

TOP*2 / BOT* 2, inside socket cavity

BXT_P_SOC_ BGA1296U22H

21A

C118

1u/6.3V_4

C346

22u/6.3V_6

C179

1u/6.3V_4

VCC_VCGI_1

VCC_VCGI_2

VCC_VCGI_3

VCC_VCGI_4

VCC_VCGI_5

VCC_VCGI_6

VCC_VCGI_7

VCC_VCGI_8

VCC_VCGI_9

VCC_VCGI_10

VCC_VCGI_11

VCC_VCGI_12

VCC_VCGI_13

VCC_VCGI_14

VCC_VCGI_15

VCC_VCGI_16

VCC_VCGI_17

VCC_VCGI_18

VCC_VCGI_19

VCC_VCGI_20

VCC_VCGI_21

VCC_VCGI_22

VCC_VCGI_23

VCC_VCGI_24

VCC_VCGI_25

VCC_VCGI_26

VCC_VCGI_27

VCC_VCGI_28

VCC_VCGI_29

VCC_VCGI_30

VCC_VCGI_31

VCC_VCGI_32

VCC_VCGI_33

VCC_VCGI_34

VCC_VCGI_35

VCC_VCGI_36

VCC_VCGI_37

VCC_VCGI_38

VCC_VCGI_39

VCC_VCGI_40

VCC_VCGI_41

VCC_VCGI_42

VCC_VCGI_43

VCC_VCGI_44

VCC_VCGI_45

VCC_VCGI_46

VCC_VCGI_47

VCC_VCGI_48

VCC_VCGI_49

VCC_VCGI_50

VCC_VCGI_51

VCC_VCGI_52

VCC_VCGI_53

VCC_VCGI_54

VCC_VCGI_55

VCC_VCGI_56

VCC_VCGI_57

VCC_VCGI_58

VCC_VCGI_59

VCC_VCGI_60

VCC_VCGI_61

VCC_VCGI_62

VCC_VCGI_63

VCC_VCGI_64

VCC_1P05V_1

VCC_1P05V_2

VCC_1P05V_3

VCC_1P05V_4

VCC_1P05V_5

VCC_1P05V_6

VCC_1P05V_7

VCC_1P05V_8

VCC_1P05V_9

VCC_1P05V_10

VCC_1P05V_11

VCC_1P05V_12

Add it 10/2 7

C117

1u/6.3V_4

C137

1u/6.3V_4

AA36

AA37

AA39

AC36

AC37

AE36

AE37

AG36

E43

E45

E48

E50

R45

R47

U36

U37

U39

U41

U42

U44

U46

U47

U48

V36

V37

V39

V41

Y36

Y37

Y39

Y41

AA28

AA30

AA32

AC28

AC30

AC32

AE28

AE30

AE32

AG28

AG30

AG32

AJ28

AJ30

AJ32

AK28

AK30

AK32

AK34

AM30

E29

E35

E37

F29

U28

U30

U32

V28

V30

V32

Y28

Y30

Y32

AA25

AC25

AE25

U22

U23

V22

V23

V25

Y23

Y25

U25

U20

C338

22u/6.3V_6

3

+VNN {9,28,29}

+3V_S5 {6,13,15,21,22,23, 25,30}

+1.05V {6,26,28}

+1.24V_S5 {30}

+VCC_VCC GI {28,29}

+3V_RTC {6,13}

+VCC_VCC GI

C172

22u/6.3V_6

C352

47u/6.3V_8

GND

C151

1u/6.3V_4

C171

22u/6.3V_6

+VCC_VCC GI

C355

47u/6.3V_8

C144

1u/6.3V_4

+VCC_VCC GI

+VCCRAM_1P05 Output Decoupling Recom mendations

22uFx2 TOP, inside socket cavity0603

100mil

+VCCRAM _1P05

C164

22u/6.3V_6

VDD2_1P24_GLML Output Decoupling Recommendations

22uFx1

VDD2_1P24_DSI_CSI Output De coupling Recommendations