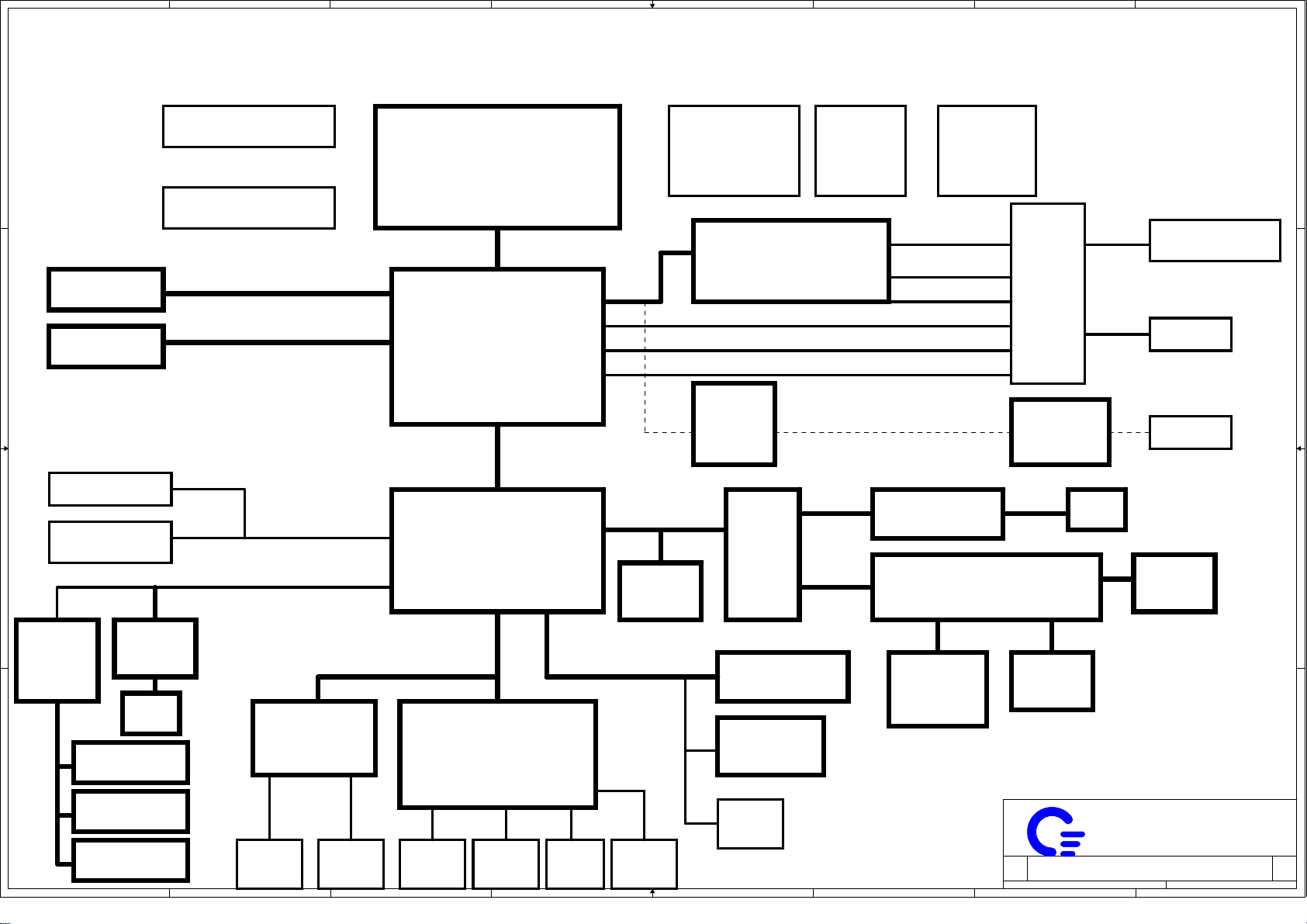

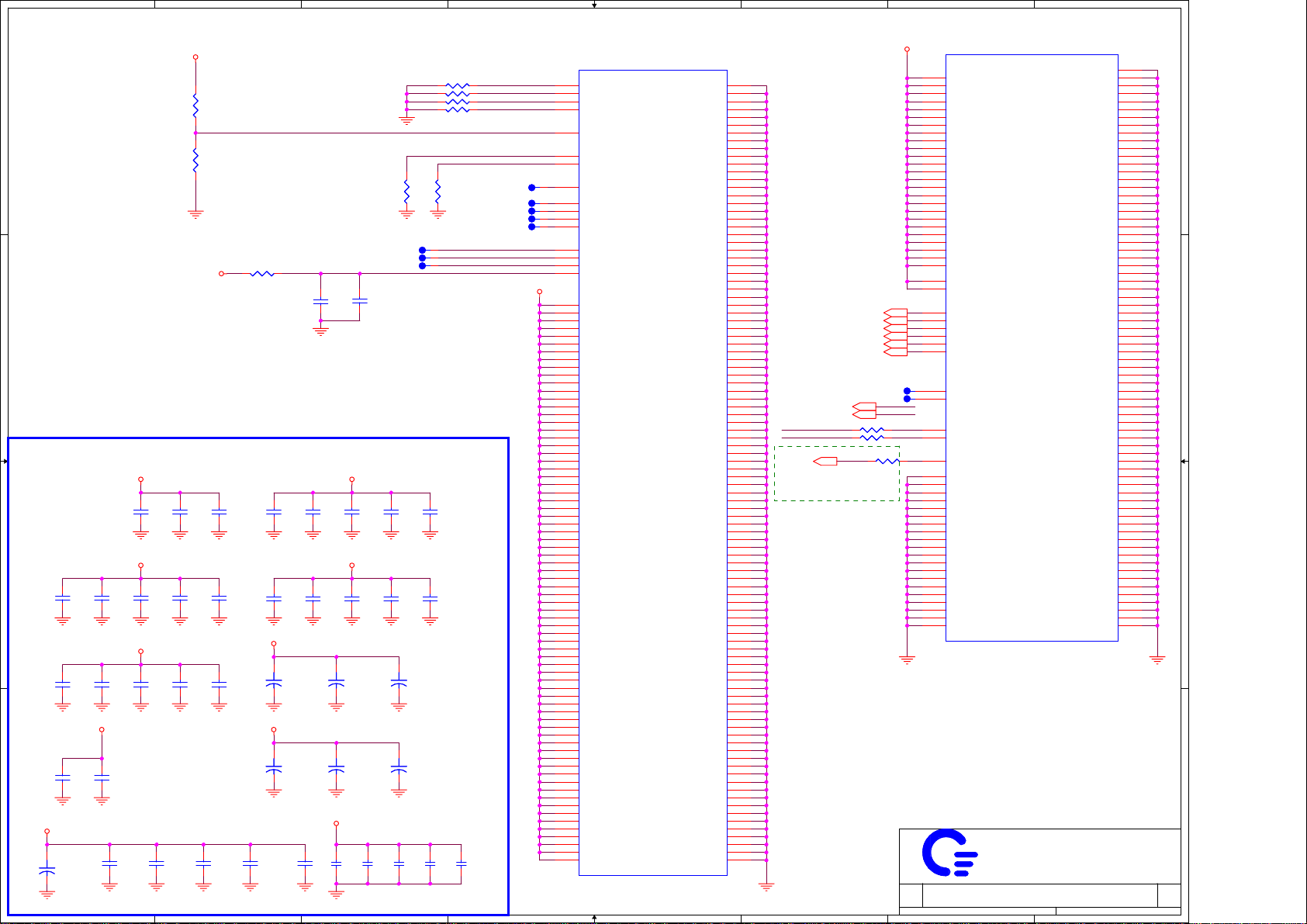

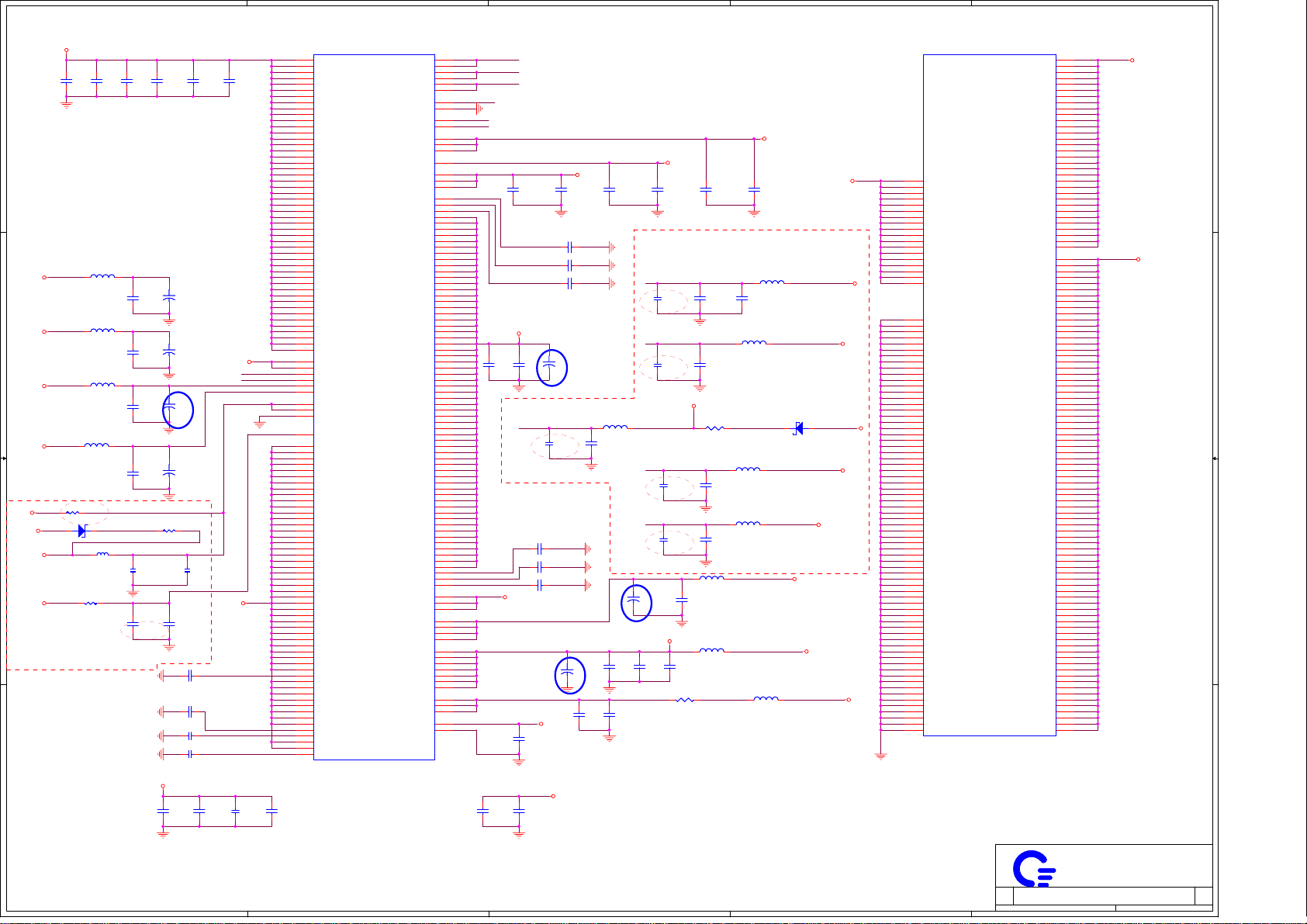

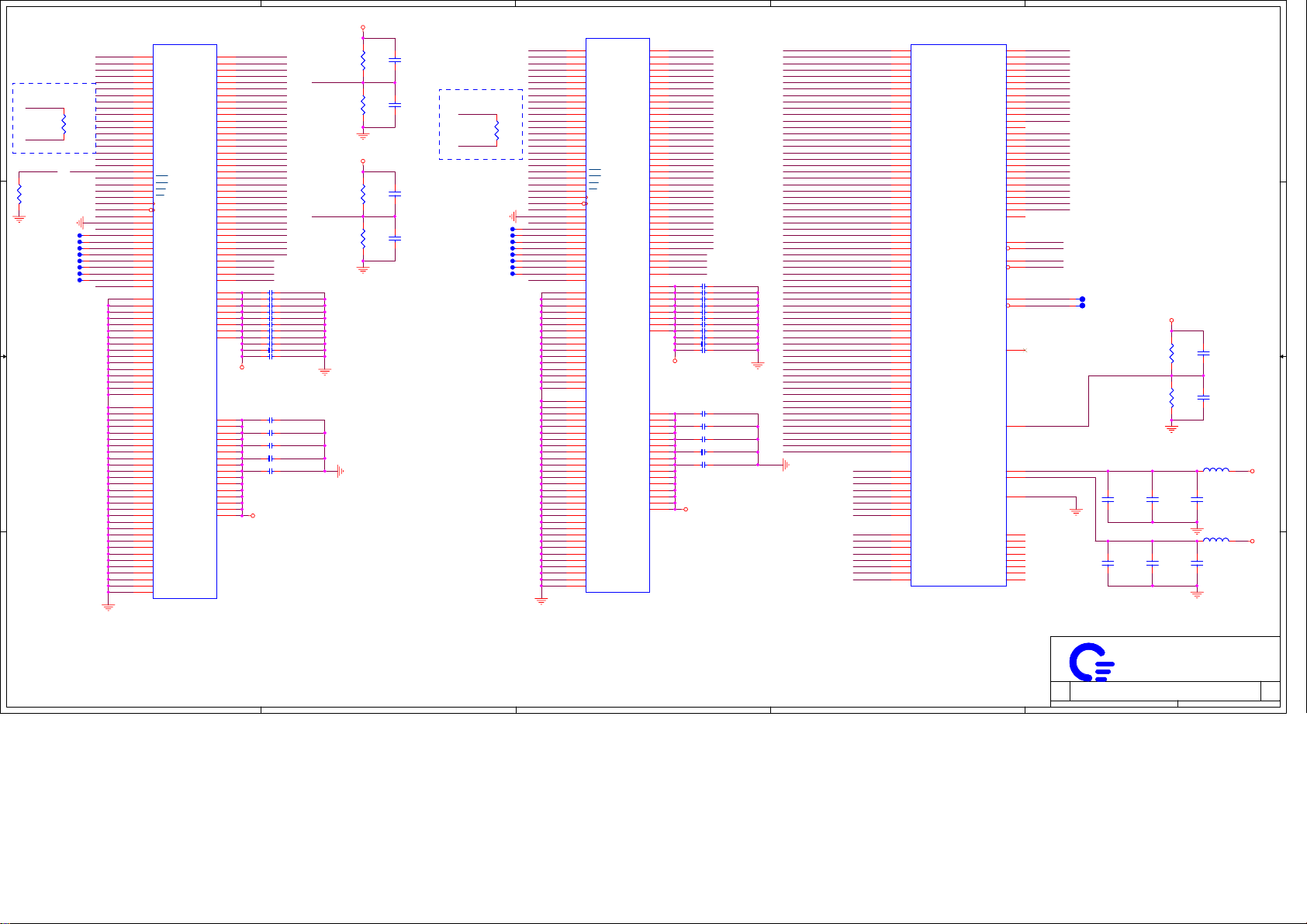

Acer TravelMate C200 Schematics

1

2

3

4

5

6

7

8

ZE1

REV:E2C

A A

CONNECTOR

Page 41

Dothan/Celeron-M

(478 Micro-FCPGA)

BATT

CHARGER

+0.9V

+1.8VSUS

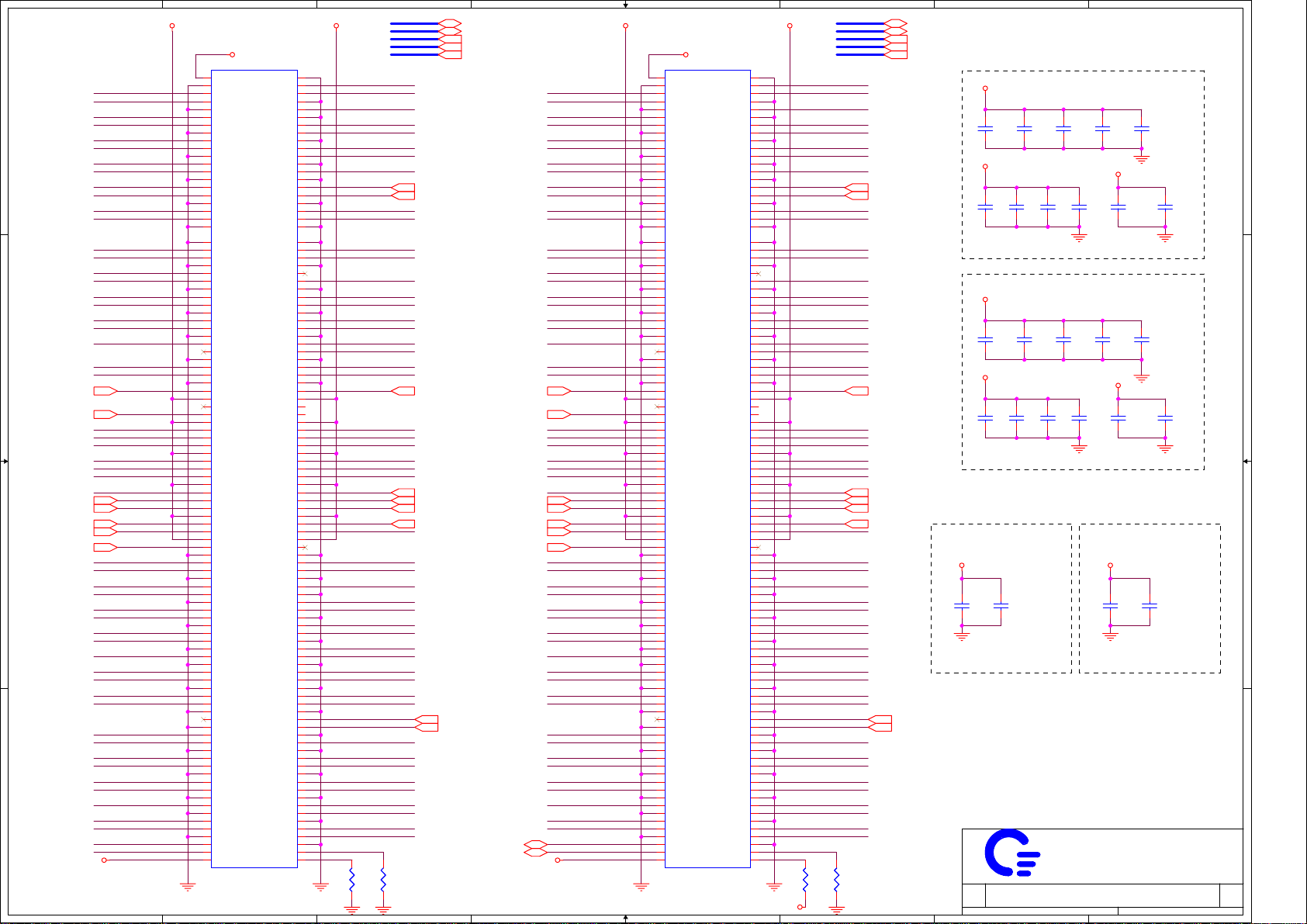

DDR-SODIMM1

Page 10,11

B B

DDR-SODIMM2

Page 10,11

533 MHZ DDR II

533 MHZ DDR II

Page 40

+1.5V

+1.8VSUS

Page 4,5

4X133MHZ

+1.05V

Alviso

1257 PCBGA

+2.5V

Page 6,7,8,9

DMI interface

Parallel-HDD

Page 32

Multi-Bay

C C

Page 32

IDE

IDE

Azalia

+1.5V +1.05V

+2.5V

+3V

+3VSUS

+1.5VSUS

ICH6-M

609 BGA

Page 18,19,20

33MHz PCI

MINI-PCI

Wireless LAN

Page 29

DC/DCAC/BATT

+1.2V/+2.5V

+1.05V/+1.5V

+1.8V/+0.9V

+3V/+5V

Page 37

EXT. VGA

n-VIDIA NV44MV

Page 12,13,14,15

INT_LVDS

INT_TVOUT

INT_VGA

DVI

CH7307

Page 16

PCI

BUFFER

Page 34

CPU VR

CLOCKS

Generator

Page 36 Page 3

EXT_LVDS

EXT_TVOUT

EXT_VGA

LAN (10M/100M/1G)

BCM5788M

Page 23

CARDBUS/1394/3-IN-1

TI 7411

Page 21,22

SWITCH

CIRCUIT

Page 17

DOCKING

Page 33

VGA

RJ45

Page 24

LCD Connector

Page 28

CRT

Page 17

EZ4 DVI

1394 PORT

Page 21

AL C260

(Codec)

&

Page 30

Head phone

D D

Internal-MIC

LINE-IN/MIC-IN

Page 31

Page 31

Page 31

1

MDC1.5

Page 30

RJ11

Page 24

SUPER I/O

PC87391

Page 26

COM A COM B

Digitizer

Page 26

2

FIR

Page 26

3V_591

EC NSC97551

176 Pins LQFP

Page 27

+5V +3VPCU

JOGDIAL

Page 28 Page 27 Page 27

3

+5V

Keyboard

FLASH

4

USB

+5V

FAN 1

Page 25

USB PORT X 3

Page 25

Mini-Bluetooth

(USB bus)

Page 25

Finger

Printer

Page 28

5

3 in 1

socket

MMC,SD,MS

Page 22

6

CARDBUS

CON.

Page 22

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Schematic Block Diagram

Schematic Block Diagram

Schematic Block Diagram

Date: Sheet

Date: Sheet

Date: Sheet

7

PROJECT : ZE1

PROJECT : ZE1

Quanta Computer Inc.

Quanta Computer Inc.

of

of

of

142Monday, August 22, 2005

142Monday, August 22, 2005

142Monday, August 22, 2005

8

E2C

E2C

E2C

1

B TEST CHANGE ITMES:

06/22 MODIFY LIST

1. Remove all no-use text meno, ie: Rev A2.

2. Page 12. Chage R157, R158, R162~R167 power source from +3V to IFPC_IOVDD.

3. Page 15. Add R615, R616, R614 Q44 and Q43. Follow nVIDIA's suggestion. TMDS Backdrive Prevention circuit.

4. Page 16. Change single R to RN. R62, R63 => RN16; R56, R57 => RN17; R58, R59 => RN18; R60, R61=> RN19. And all use 0 ohm.

5. Page 24. Swap net of CN10-12 and CN10-13. Wrong connection.

6. Page 25. Change USB power source from 5VPCU to +5VSUS. Wrong design.

7. Page 30. Reserve R617 (stuff), R618 (stuff), C859 (NA), C869 (NA), C861 (NA) and C862 (NA). For noise in EZ4's LINE-IN.

06/23 MODIFY LIST

8. Page 23. Delete R36 and R76. VESDchange PWR source from LAN_3V to 3V_LAN directly.

9. Page 23. Delete R40 from TCK.

10. Page 23. Delete R42 from Q9-B and Q9-C.

A A

11. Page 23. Add option resisters in 3VLAN. Add R56 and R57 for BCM4401.

12. Page 23. Add PI-filiter for AVDD and separate from VDDP. Add L72.

13. Page 23. Add PI-filiter for AVDDL. Add L73 and C863.

14. Page 23. BOM modification. Correct RDAC's resister from 1.18K to 1.24K (BCM5788).

15. Page 23. BOM modification. R70: stuff; R68: NA. FAE: Support CLKRUN#.

06/28 MODIFY LIST

16. Page 28. Delete R112 (pull hign/ 10K) and Add R624 (0 ohm) to GND. BOM.

17. Page 28. Add R625 and R626 to GND. ALPS setting. BOM.

18. Page 28. Add R619, R620, R621 and R623 for bypass 3D function. BOM.

19. Page 28. Reserve R624, R622, C864 and U62. Those are for 3D function.

06/28 MODIFY LIST

20. Page 13. Update and correct U27 and U28 footprint. Correct DQS and DQM.

21. Page 13. Re-route MDA[0..63], QSA[0..7] and -DQMA[0..7]

22. Page 9. C272 change from CH73301M8B9 to CH747LM8801(LOW profile). BOM

B2 TEST CHANGE ITMES:

07/19 MODIFY LIST

23. Page 25. Change U32, U58 and U33 to AL000547001 (GMT).

Change C489, C800 and C490 to CH71001M393 (100uF).

Del R289, R296, R562, R555, R292 and R294

24. Page 25. Add USB PWR control (SUSON) circuit. Add R554 (10K) and Q39(DTC144EUA )

25. Page 42. Add Semtcech solution in Track-point.

Add U63, U66, U65, U64, C866, C868, C867, C870, C872, C871, R637, R638, R643, R642, R645, R644, R647, R641, R646, R640, R639, R638.

26. Page 22. Chane CN13 from 4 in1 to 3 in 1. Re-routing it.

27. Page 28. BOM delete D4. Acer: no action in LID.

B B

07/26 MODIFY LIST

28. Page 32. Add HOLE45 for MDC.

29. Page 32. Add HOLE46 for VRAM. (NO SPACE!!!)

30. Page 32. Add clip's PAD. P5, P6 and P7.

07/29 MODIFY LIST

31. Page 27. Add PULL HIGH 10K/ R649 to 3V. (EC)

32. Page 40. BOM: Remove PR149 and Stuff PR147. (EC)

33. Page 40. Delete PQ41, PU10, PC97, PC98 and PC99. REFP => VIN; REF3V => 3V_591. (EC and PWR)

REFP in PD19-1 and PC130-1; REF3V in PU13-12, PR40-1, PR64-1 and PU14-5.

34. Page 40. Delete PR134 and PR139. Then SHORT them. (PWR)

35. Page 40. Change PQ52-3 from PU13-13(CC-SET) to PU13-8. And change PR87 from 0 ohm to 10K.(PWR)

36. Page 28. Upate CN7's footprint to 88264-06XX-6P-R

37. Page 28. Upate CN8's footprint to 88264-10XX-10P-R

38. Page 28. Upate CN3's footprint to 88264-04XX-4P-L

39. Page 39. Delete JP1. Change +1V5_S5 to +1.5V_S5.

40. Page 39. Delete JP2 and JP5. Change VCCP-OUT to +VCCP.

40. Page 31. Reserve and Stuff R650 and R651. For Fine-tune the value of headphone.

07/30 MODIFY LIST

41. Page 35. Disable NVVDD & +1.2V for INT VGA cost-down

42. Page 35. change R128 from 100K to 97.6Kohm, R127 from 34K to 100Kohm for power fine-tune VGA voltage

43. Page 42. Change trackpointer function from ALPS to SEMTECH

44. Page 12. Change EXT_BLON reistor R446 form 10K to 1K for boot white screen

45. Page 04. Disable R596 for Battery only can't boot

C TEST CHANGE ITMES:

08/9 MODIFY LIST

46. Page 26. Modify serial port function for EZ4 (MRXD1 & MTXD1)

C C

47. Page 25. Change USB_Power_on voltage from +5VSUS to 5VPCU

48. Page 25. Modify all USB power switch OC# pull-up 10k to +3VSUS

08/10 MODIFY LIST

49. Page 26. Add GND in C577 & C578 for FIR

50. Page 33. Remove LAN's reserve capacitors(C817/C513/C542/C546/C554/C555/C525/C523/C533/C530) by EMI engineer confirm

08/11 MODIFY LIST

51. Page 36. CPU CORE Power(PU11's pin25) add another CAP 0.022UF(C170) by power engineer request

52. Page 23. Add two new CAP 0.1UF(C873 & C874) for AVDD_LAN & +1.8V_1.2V_LAN by EMI request

08/12 MODIFY LIST

53. Page 23. Change R38 from 1.24k to 1.18k for LAN droop & template

54. Page 17. Change L59/L60/L61 from FBM-10-160808-470(47ohm) to BLM18BA220(22ohm) for EA measure fail

55. Page 28. Modify Bluetooth led can't light for FOXCONN Bluetooth module (Add R652 & R653)

56. Page 31. Modify Line-in noise change R650 &R651 from 0ohm to 1kohm

Page 30. Modify Line-in noise add C859 &C861 (0.1UF)

57. Page 31. Add AND gate(U67) & R654(0 ohm) for popo sound (delete D29 & D30 & R550)

58. Page 31. Add MOSFET (Q48&Q49) for headphone popo sound, and reserve Q46/Q47 for speaker popo sound issue

59. Page 33. Change L33/L34/L36 from 22ohm BEAD to short

08/13 MODIFY LIST

60. Page 26. Change R449 from 1k ohm to 4.7k ohm for SIO

08/18 MODIFY LIST

61. Page 17. Change R399/R400/R401/R387/R388/R390 size from 0402 to 0603 for EMI request

62. Page 31. Add Q50 & R656(10K) for Normal close type audio jack issue (Reserve)

63. Page 32. Change Q13 from Transistor to MOS and R110 (47k to 10k) & C139(0.22U to 0.1U) and add R657 (0R) from EC (154pin) for Lite_On ODD issue

64. Page 33. Add C875/C876/C877/C878 (12pf) for Docking DVI EMI issue(Reserve)

08/19 MODIFY LIST

D D

65. Page 21. Change 1394 connecotor(CN28) type form SMD to DIP for SMT request

66. Page 28. Update CN7's footprint to 88264-06XX-6P-R-ZE1 & CN8's footprint to 88264-10XX-10P-R-ZE1 for SMT request (Increase PAD length 0.2mm)

67. Page 25. Update CN5's footprint to SM08B-SURS-8P-R-ZE1 for SMT request (Increase PAD length 0.2mm)

68. Page 41. Add new CAP(PC171/PC172) in BAT-V plane for EMI request

69. Page 23. Add new CAP(C879/C880) in AVDD_LAN plane for EMI request

70. Page 23. Add new CAP(C881/C882) in +3V plane for EMI request

71. Page 33. Change C1/C2 from TOP to BOT side for Mechanical request

1

2

2

3

3

4

BCM5788M

BCM4401

NOTE

4

5

NA 1.24K

STUFF

R38 Q5, Q9 U7 U8R97, R87

1.27K

5

R51, R48 R56, R57

STUFF

NA

+3VRUN 3V_LAN RDAC

STUFF

NA NA

STUFF

6

NA

STUFF

NA

STUFF

AT93C46 24LC128

6

7

06/27 LAYOUT SWAP

Pin 'JDIM1.152' moved to net 'R_B_MD42'.

Pin 'JDIM2.153' moved to net 'R_A_MD46'.

Pin 'JDIM2.191' moved to net 'R_A_MD54'.

Pin 'JDIM2.181' moved to net 'R_A_MD48'.

Pin 'JDIM1.58' moved to net 'R_B_MD19'.

Pin 'JDIM2.6' moved to net 'R_A_MD0'.

Pin 'JDIM2.175' moved to net 'R_A_MD61'.

Pin 'JDIM2.16' moved to net 'R_A_MD6'.

Pin 'JDIM2.44' moved to net 'R_A_MD16'.

Pin 'JDIM2.43' moved to net 'R_A_MD21'.

Pin 'JDIM1.56' moved to net 'R_B_MD18'.

Pin 'JDIM2.154' moved to net 'R_A_MD42'.

Pin 'JDIM1.57' moved to net 'R_B_MD22'.

Pin 'JDIM2.192' moved to net 'R_A_MD51'.

Pin 'JDIM1.176' moved to net 'R_B_MD51'.

Pin 'JDIM2.179' moved to net 'R_A_MD49'.

Pin 'JDIM1.194' moved to net 'R_B_MD59'.

Pin 'JDIM1.192' moved to net 'R_B_MD58'.

Pin 'JDIM2.186' moved to net 'R_A_DQS#6'.

Pin 'JDIM1.5' moved to net 'R_B_MD4'.

Pin 'JDIM2.7' moved to net 'R_A_MD5'.

Pin 'JDIM2.167' moved to net 'R_A_DQS#7'.

Pin 'JDIM2.152' moved to net 'R_A_MD43'.

Pin 'JDIM1.7' moved to net 'R_B_MD5'.

Pin 'JDIM2.157' moved to net 'R_A_MD57'.

Pin 'JDIM2.20' moved to net 'R_A_MD13'.

Pin 'JDIM1.158' moved to net 'R_B_MD48'.

Pin 'JDIM2.159' moved to net 'R_A_MD60'.

Pin 'JDIM2.173' moved to net 'R_A_MD56'.

Pin 'JDIM1.191' moved to net 'R_B_MD62'.

Pin 'JDIM2.5' moved to net 'R_A_MD1'.

Pin 'JDIM1.61' moved to net 'R_B_MD29'.

Pin 'JDIM2.170' moved to net 'R_A_DM7'.

Pin 'JDIM2.57' moved to net 'R_A_MD22'.

Pin 'JDIM1.154' moved to net 'R_B_MD43'.

Pin 'JDIM2.188' moved to net 'R_A_DQS6'.

Pin 'JDIM1.62' moved to net 'R_B_MD24'.

Pin 'JDIM2.61' moved to net 'R_A_MD29'.

Pin 'JDIM1.182' moved to net 'R_B_MD57'.

Pin 'JDIM1.153' moved to net 'R_B_MD46'.

Pin 'JDIM1.151' moved to net 'R_B_MD47'.

Pin 'JDIM1.126' moved to net 'R_B_MD32'.

Pin 'JDIM1.157' moved to net 'R_B_MD52'.

Pin 'JDIM1.180' moved to net 'R_B_MD56'.

Pin 'JDIM1.175' moved to net 'R_B_MD55'.

Pin 'JDIM2.17' moved to net 'R_A_MD3'.

Pin 'JDIM1.4' moved to net 'R_B_MD0'.

Pin 'JDIM2.169' moved to net 'R_A_DQS7'.

Pin 'JDIM1.63' moved to net 'R_B_MD28'.

Pin 'JDIM1.36' moved to net 'R_B_MD15'.

Pin 'JDIM2.64' moved to net 'R_A_MD25'.

Pin 'JDIM1.38' moved to net 'R_B_MD10'.

Pin 'JDIM1.64' moved to net 'R_B_MD25'.

Pin 'RP4.4' moved to net 'R_B_MA4'.

Pin 'RP6.4' moved to net 'SM_CS2#'.

Pin 'RP7.2' moved to net 'M_ODT2'.

Pin 'RP20.2' moved to net 'R_A_MA13'.

Pin 'RP6.2' moved to net 'R_B_SRASA#'.

Pin 'RP28.4' moved to net 'R_A_BMWEA#'.

Pin 'RP24.2' moved to net 'R_A_MA12'.

Pin 'RP20.4' moved to net 'M_ODT0'.

Pin 'RP4.2' moved to net 'R_B_MA2'.

Pin 'RP7.4' moved to net 'R_B_MA13'.

Pin 'RP2.4' moved to net 'R_B_MA6'.

Pin 'RP2.2' moved to net 'CKE3'.

Pin 'RP24.4' moved to net 'R_A_MA9'.

Pin 'RP3.2' moved to net 'R_B_MA7'.

Pin 'RP14.2' moved to net 'R_B_MA12'.

Pin 'RP28.2' moved to net 'R_A_SCASA#'.

Pin 'RP14.4' moved to net 'R_B_MA9'.

Pin 'JDIM1.55' moved to net 'R_B_MD23'.

Pin 'JDIM1.45' moved to net 'R_B_MD20'.

Pin 'JDIM2.180' moved to net 'R_A_MD53'.

Pin 'JDIM2.58' moved to net 'R_A_MD19'.

Pin 'JDIM2.23' moved to net 'R_A_MD12'.

Pin 'JDIM2.185' moved to net 'R_A_DM6'.

Pin 'JDIM1.35' moved to net 'R_B_MD14'.

Pin 'JDIM1.174' moved to net 'R_B_MD50'.

Pin 'JDIM2.63' moved to net 'R_A_MD28'.

Pin 'JDIM2.45' moved to net 'R_A_MD20'.

Pin 'JDIM2.160' moved to net 'R_A_MD63'.

Pin 'JDIM1.179' moved to net 'R_B_MD61'.

Pin 'JDIM1.43' moved to net 'R_B_MD21'.

Pin 'JDIM2.182' moved to net 'R_A_MD52'.

Pin 'JDIM1.159' moved to net 'R_B_MD53'.

Pin 'JDIM2.151' moved to net 'R_A_MD47'.

Pin 'JDIM2.158' moved to net 'R_A_MD58'.

Pin 'JDIM1.189' moved to net 'R_B_MD63'.

Pin 'JDIM1.6' moved to net 'R_B_MD1'.

Pin 'JDIM2.14' moved to net 'R_A_MD2'.

Pin 'JDIM1.173' moved to net 'R_B_MD54'.

Pin 'JDIM2.62' moved to net 'R_A_MD24'.

Pin 'JDIM2.194' moved to net 'R_A_MD50'.

Pin 'JDIM1.160' moved to net 'R_B_MD49'.

Pin 'JDIM1.181' moved to net 'R_B_MD60'.

Pin 'JDIM2.46' moved to net 'R_A_MD17'.

Pin 'JDIM1.44' moved to net 'R_B_MD16'.

Pin 'JDIM2.189' moved to net 'R_A_MD55'.

Pin 'JDIM2.174' moved to net 'R_A_MD62'.

Pin 'JDIM1.46' moved to net 'R_B_MD17'.

Pin 'JDIM2.22' moved to net 'R_A_MD8'.

Pin 'JDIM2.19' moved to net 'R_A_MD7'.

Pin 'JDIM2.56' moved to net 'R_A_MD23'.

Pin 'JDIM2.176' moved to net 'R_A_MD59'.

Pin 'JDIM1.123' moved to net 'R_B_MD37'.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet

Date: Sheet

7

8

of

of

242Monday, August 22, 2005

242Monday, August 22, 2005

242Monday, August 22, 2005

8

PROJECT : ZE1

PROJECT : ZE1

Quanta Computer Inc.

Quanta Computer Inc.

E2C

E2C

E2C

1

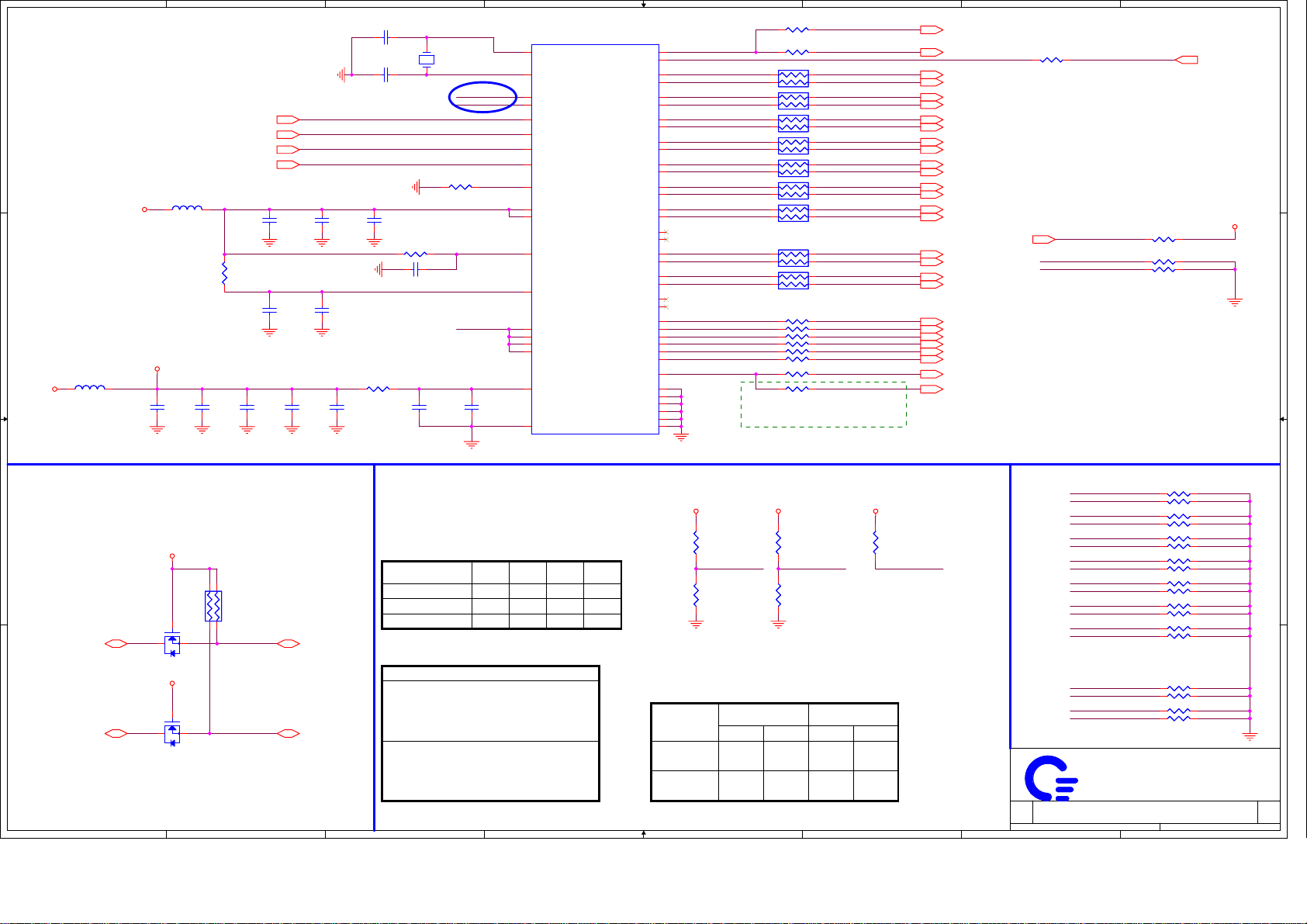

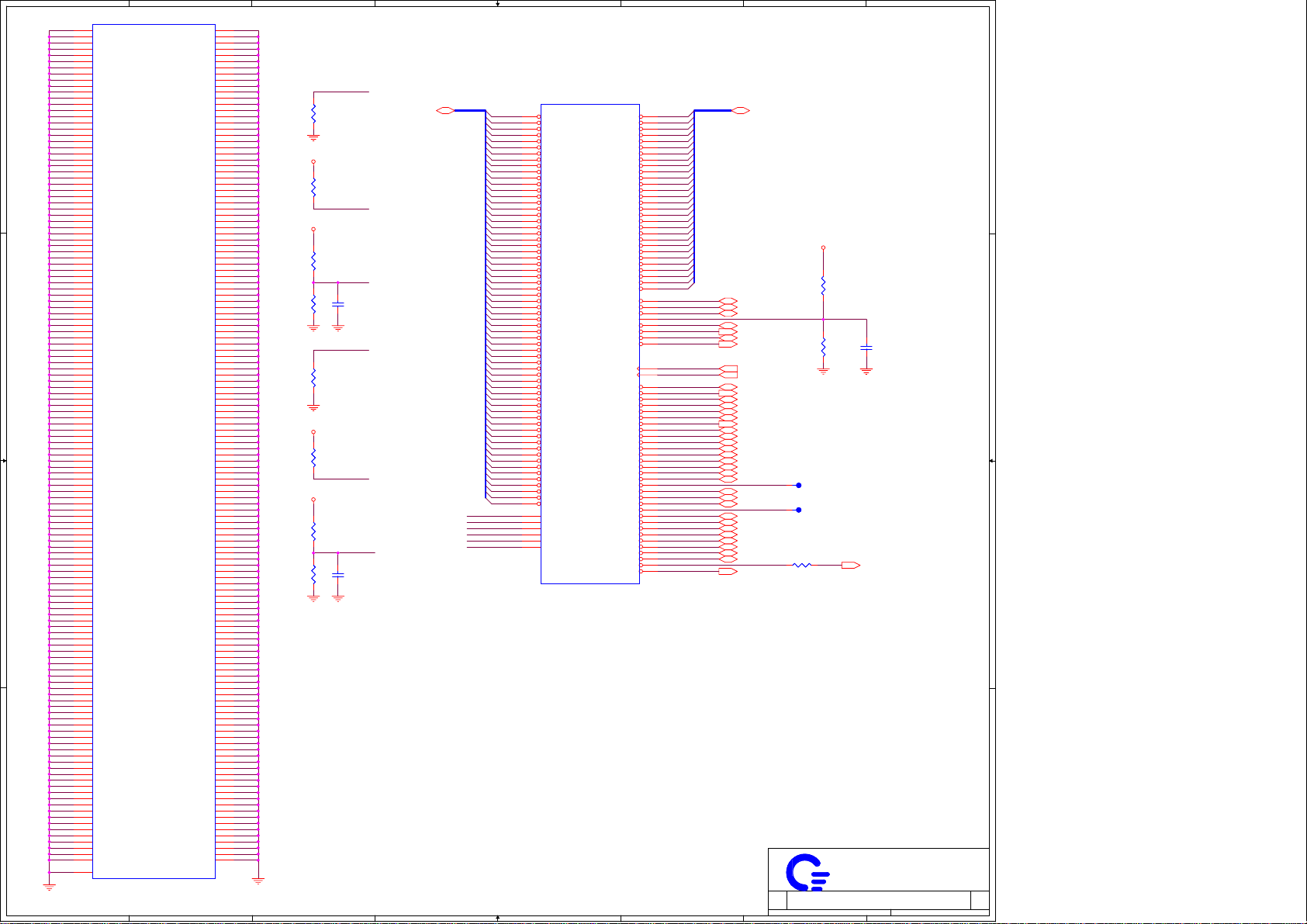

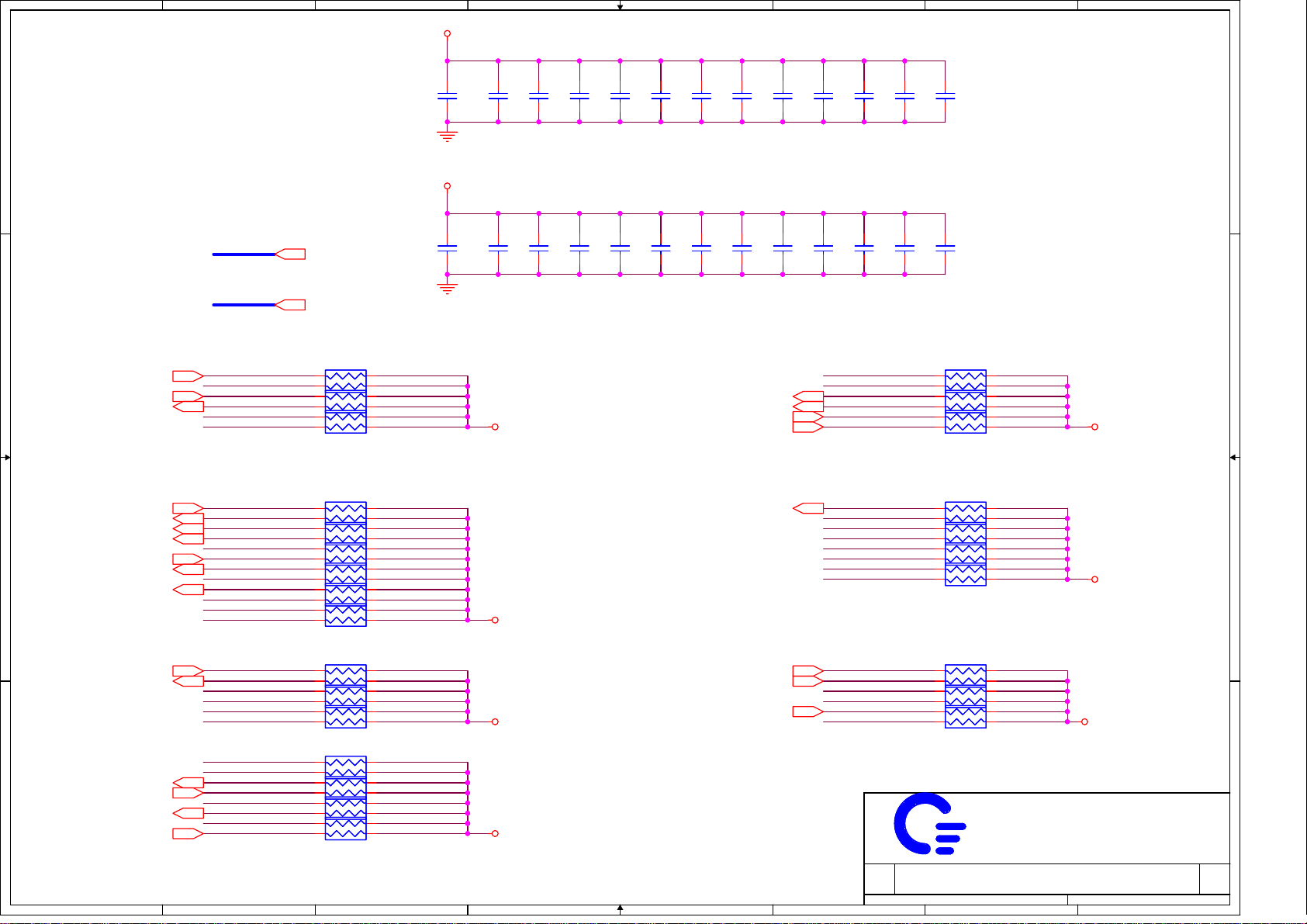

Clock gen

A A

L53 TI201209G121L53 TI201209G121

+3V

B B

VDD_CKG_CPU

L30 TI201209G121L30 TI201209G121

+3V

C466

C466

10U

10U

C451

C451

.047U

.047U

2

CLK_EN#(36)

STP_CPU#(19,36)

STP_PCI#(19)

SELPSB1_CLK(5,7)

CLKVDD

C705

R500

R500

2.2R

2.2R

C462

C462

.047U

.047U

C705

10U

10U

C706

C706

10U

10U

C464

C464

.047U

.047U

C708

C708

.047U

.047U

C707

C707

.047U

.047U

R277 2.2RR277 2.2R

C454

C454

.047U

.047U

C712 33PC712 33P

C711 33PC711 33P

C709

C709

.047U

.047U

R253 1/FR253 1/F

C449 .047UC449 .047U

3

Y8

Y8

14.318MHZ/20PF

14.318MHZ/20PF

R520 475/FR520 475/F

Iref=5mA, Ioh=4*Iref

C715

C715

.047U

.047U

CG_XIN

CG_XOUT

CGCLK_SMB

CGDAT_SMB

SELPSB1_CLK

IREF

VDD_CKGREF

VDD_CKG_48

VDD_CKG_CPU

VDDA_CKGVDD_CKG_CPU

C467

C467

10U

10U

250mA ( MAX. )

U48

U48

50

XIN

49

XOUT

46

SMCLK

47

SMDAT

10

VTT_PWRGD#/PD

54

CPU_STOP#

55

PCI/PCIE_STOP#

16

TEST_MODE/FSB

39

IREF

1

VDDPCI1

7

VDDPCI2

48

VDDREF

11

VDD48

21

VDDSRC1

28

VDDSRC2

34

VDDSRC3

42

VDDCPU

37

VDDA

38

GNDA

ICS954206

ICS954206

4

SEL_96M#/PCICLKF1

REF0

REF1/FSC

CPUCLK0

CPUCLK0#

CPUCLK1

CPUCLK1#

DOT_96

DOT_96#

96M_SS/SRC0

96M_SS#/SRC0#

SRC1

SRC1#

SRC2

SRC2#

SRC3

SRC3#

SRC4_SATA

SRC4#_SATA#

SRC5

SRC5#

SRC6

SRC6#

ITPCLK/SRC7

ITPCLK#/SRC7#

ITP_EN/PCICLKF0

PCICLK2

PCICLK3

PCICLK4

PCICLK5

USB_48/FSA

GND1

GND2

GND3

GND4

GND5

GND6

14M_REF

52

53

R_HCLK_CPU

44

R_HCLK_CPU#

43

R_HCLK_MCH

41

R_HCLK_MCH#

40

R_DOT96

14

R_DOT96#

15

R_DREFSSCLK

17

R_DREFSSCLK#

18

R_PCIE_VGA

19

R_PCIE_VGA#

20

R_PCIE_ICH

22

R_PCIE_ICH#

23

R_MCH_3GPLL

24

R_MCH_3GPLL#

25

26

27

R_PCIE_EZ1

31

R_PCIE_EZ1#

30

R_PCIE_EZ2

33

R_PCIE_EZ2#

32

36

35

R_PCLK_591

8

R_PCLK_ICH

9

R_PCLK_SIO

56

R_PCLK_MINI

3

R_PCLK_PCM

4

R_PCLK_LAN

5

SELPSB0_CLK

12

2

6

13

29

45

51

5

R509 12.1/FR509 12.1/F

R512 12.1/FR512 12.1/F

RP39

4

2

4

2

2

4

2

4

2

4

2

4

2

4

4

2

4

2

R510 33RR510 33R

R252 33RR252 33R

R503 33RR503 33R

R502 33RR502 33R

R505 33RR505 33R

R507 33RR507 33R

R514 22RR514 22R

R629 22RR629 22R

ECN C2A

48Mhz to Cardbus controller(7411) for cost down

RP39

3

33X2

33X2

1

RP41

RP41

3

33X2

33X2

1

RP40

RP40

1

33X2

33X2

3

RP42

RP42

1

33X2

33X2

3

RP43

RP43

1

33X2

33X2

3

RP45

RP45

1

33X2

33X2

3

RP47

RP47

1

33X2

33X2

3

RP46

RP46

3

33X2

33X2

1

RP44

RP44

3

33X2

33X2

1

6

14M_SIO (26)

14M_ICH (19)

HCLK_CPU (4)

HCLK_CPU# (4)

HCLK_MCH (6)

HCLK_MCH# (6)

DOT96 (7)

DOT96# (7)

DREFSSCLK (7)

DREFSSCLK# (7)

CLK_PCIE_VGA (12)

CLK_PCIE_VGA# (12)

CLK_PCIE_ICH (19)

CLK_PCIE_ICH# (19)

CLK_MCH_3GPLL (7)

CLK_MCH_3GPLL# (7)

CLK_PCIE_EZ1 (33)

CLK_PCIE_EZ1# (33)

CLK_PCIE_EZ2 (33)

CLK_PCIE_EZ2# (33)

PCLK_591 (27)

PCLK_ICH (18)

PCLK_SIO (26)

PCLK_MINI (29)

PCLK_PCM (21)

PCLK_LAN (23)

CLK48_USB (19)

TI-48M (21)

EZ_CLKREQ#(33)

7

R581 4.7KR581 4.7K

SELPSB2_CLKR_SELPSB2_CLK

CLKREQA# - SRC0, 2, SATA

CLKREQB# - SRC1, 3, 4

S/W programable for

effected clock pairs

EZ_CLKREQ#

R_PCLK_591

R_PCLK_ICH

ITP/SRC7 SELECT 0:SRC7 1:ITP

R298 1KR298 1K

R511 1KR511 1K

R513 1KR513 1K

8

SELPSB2_CLK (5,7)

+3V

SM Bus Speed setting

+VCCP +3V+VCCP

C C

+3V

2

4

RP38

RP38

Q37

Q37

10KX2

RHU002N06

RHU002N06

PDAT_SMB(19,33)

Q36

Q36

RHU002N06

D D

PCLK_SMB(19,33)

RHU002N06

10KX2

2

3 1

+3V

2

3 1

1

3

CGDAT_SMB

CGCLK_SMB

CGDAT_SMB (10)

CGCLK_SMB (10)

Resistor Stuff Table

RA RB RC RD

Dothan A 400 V X X V

Dothan A 533 X V X V

Dothan B X X X X

Clock Gen. Frequency Selection Table

FSC FSB FSA CPU SRC PCI

1 0 1 100 100 33

0 0 1 133 100 33

0 1 1 166 100 33

0 1 0 200 100 33

Default

Frequency

0 0 0 266 100 33

1 0 0 333 100 33

1 1 0 400 100 33

1 1 1 RSVD 100 33

1

2

3

4

R506

R506

*1K

*1K

RA

SELPSB2_CLK SELPSB0_CLKSELPSB1_CLK DOT96#

R508

R508

*1K

*1K

RB

DOTHAN BSEL Output Value

DOTHAN A-Step DOTHAN B-Step FSB

400 MHz

533 MHz 1

0

0

5

R258

R258

*1K

*1K

RC

R260

R260

*1K

*1K

RD

For Dothan B

BSEL0BSEL1 BSEL1 BSEL0

0

0

0

R515

R515

10K

10K

1

0

6

Clock terminator

HCLK_CPU

HCLK_CPU#

HCLK_MCH

HCLK_MCH#

CLK_PCIE_VGA

CLK_PCIE_VGA#

DOT96

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

CLK_PCIE_ICH

CLK_PCIE_ICH#

CLK_PCIE_EZ2

CLK_PCIE_EZ2#

CLK_PCIE_EZ1

CLK_PCIE_EZ1#

DREFSSCLK

DREFSSCLK#

R254

R254

R256

R256

R257 49.9/FR257 49.9/F

R259 49.9/FR259 49.9/F

R521 49.9/FR521 49.9/F

R522 49.9/FR522 49.9/F

R516 49.9/FR516 49.9/F

R517 49.9/FR517 49.9/F

R527 49.9/FR527 49.9/F

R528 49.9/FR528 49.9/F

R523 49.9/FR523 49.9/F

R526 49.9/FR526 49.9/F

R267 49.9/FR267 49.9/F

R269 49.9/FR269 49.9/F

R271 49.9/FR271 49.9/F

R274 49.9/FR274 49.9/F

R518 49.9/FR518 49.9/F

R519 49.9/FR519 49.9/F

49.9/F

49.9/F

49.9/F

49.9/F

Close to Clock Gen.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Clock Gen.

Clock Gen.

Clock Gen.

Date: Sheet

Date: Sheet

Date: Sheet

7

PROJECT : ZE1

PROJECT : ZE1

Quanta Computer Inc.

Quanta Computer Inc.

342Monday, August 22, 2005

342Monday, August 22, 2005

342Monday, August 22, 2005

of

of

of

8

B2A

B2A

B2A

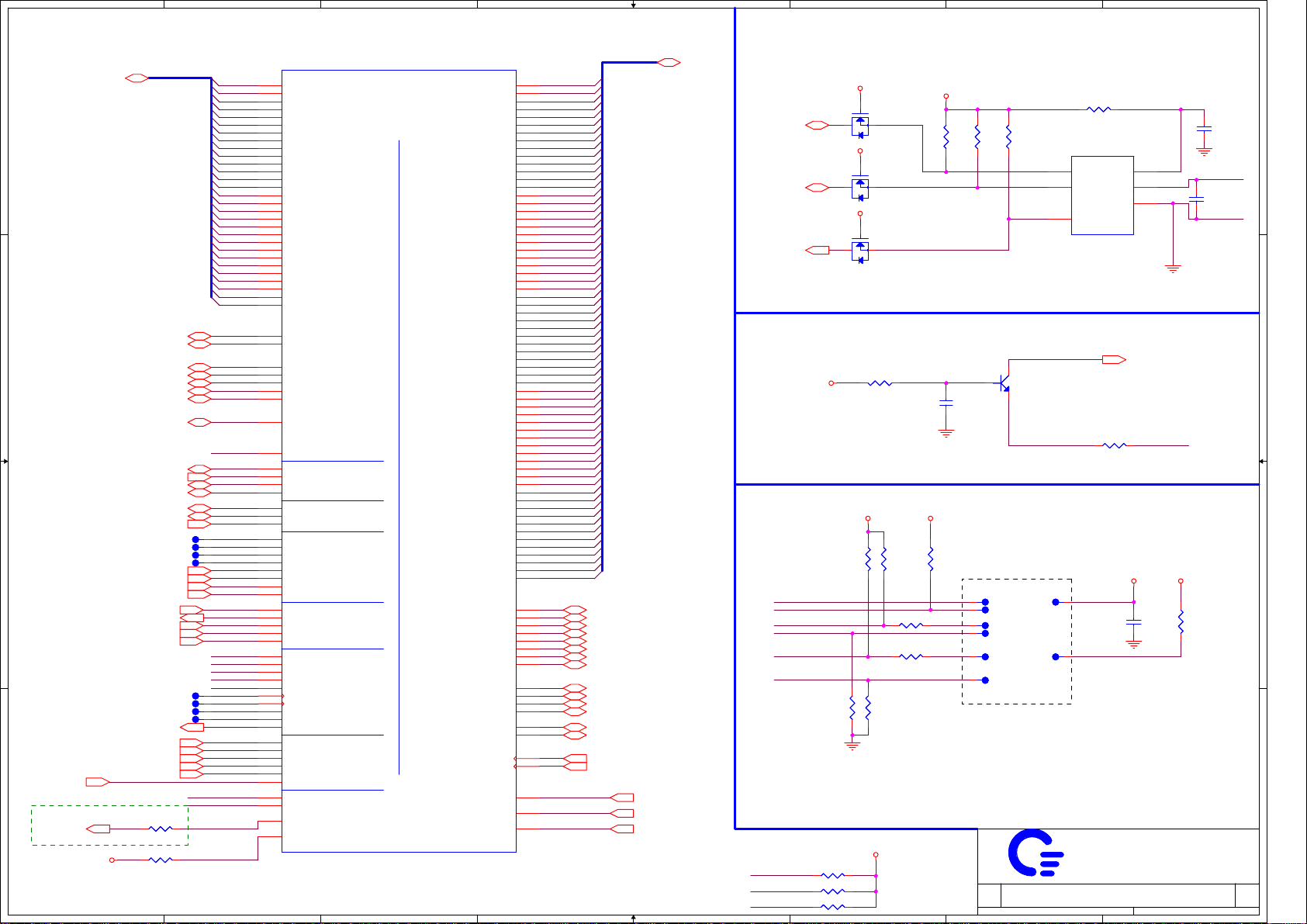

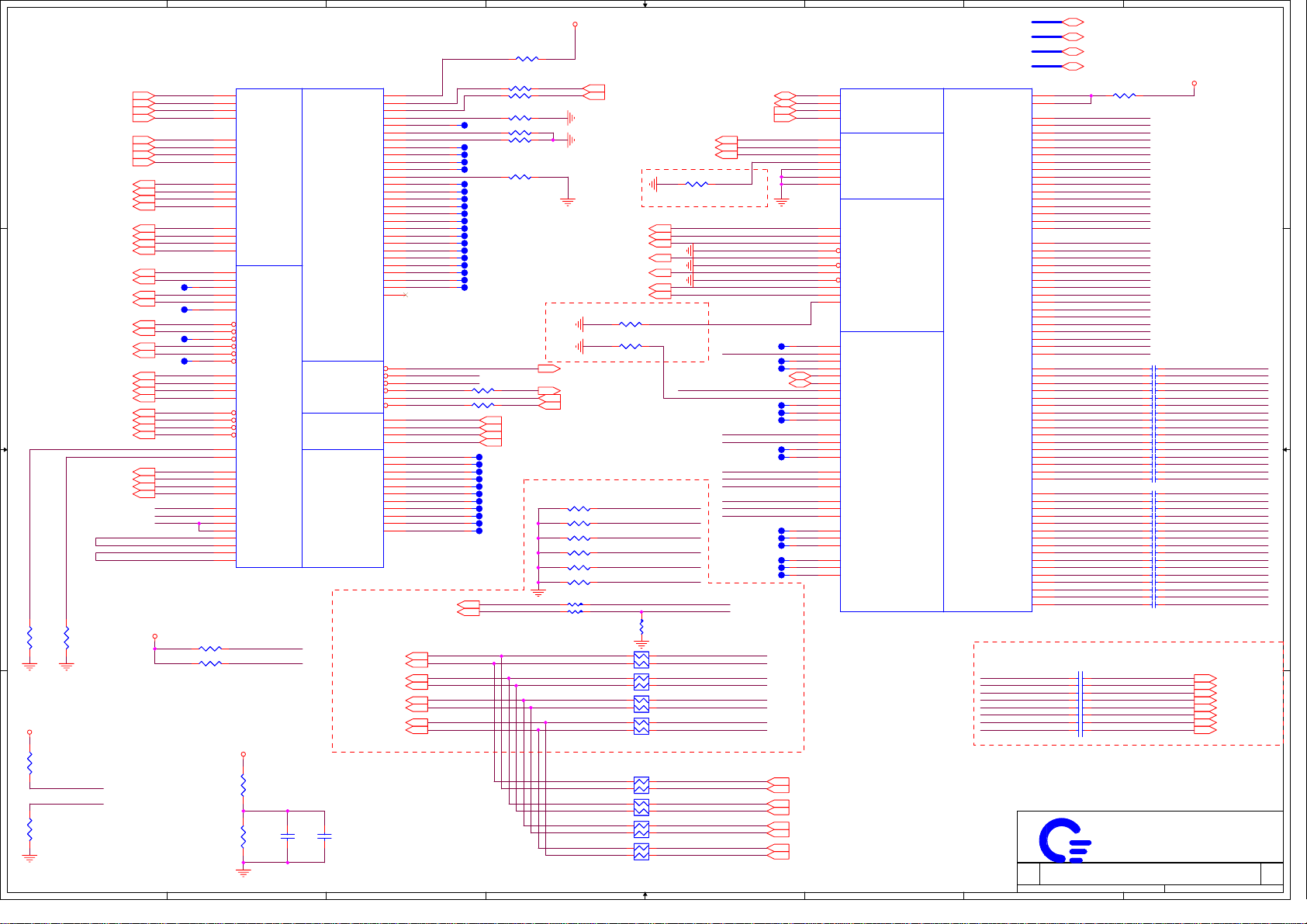

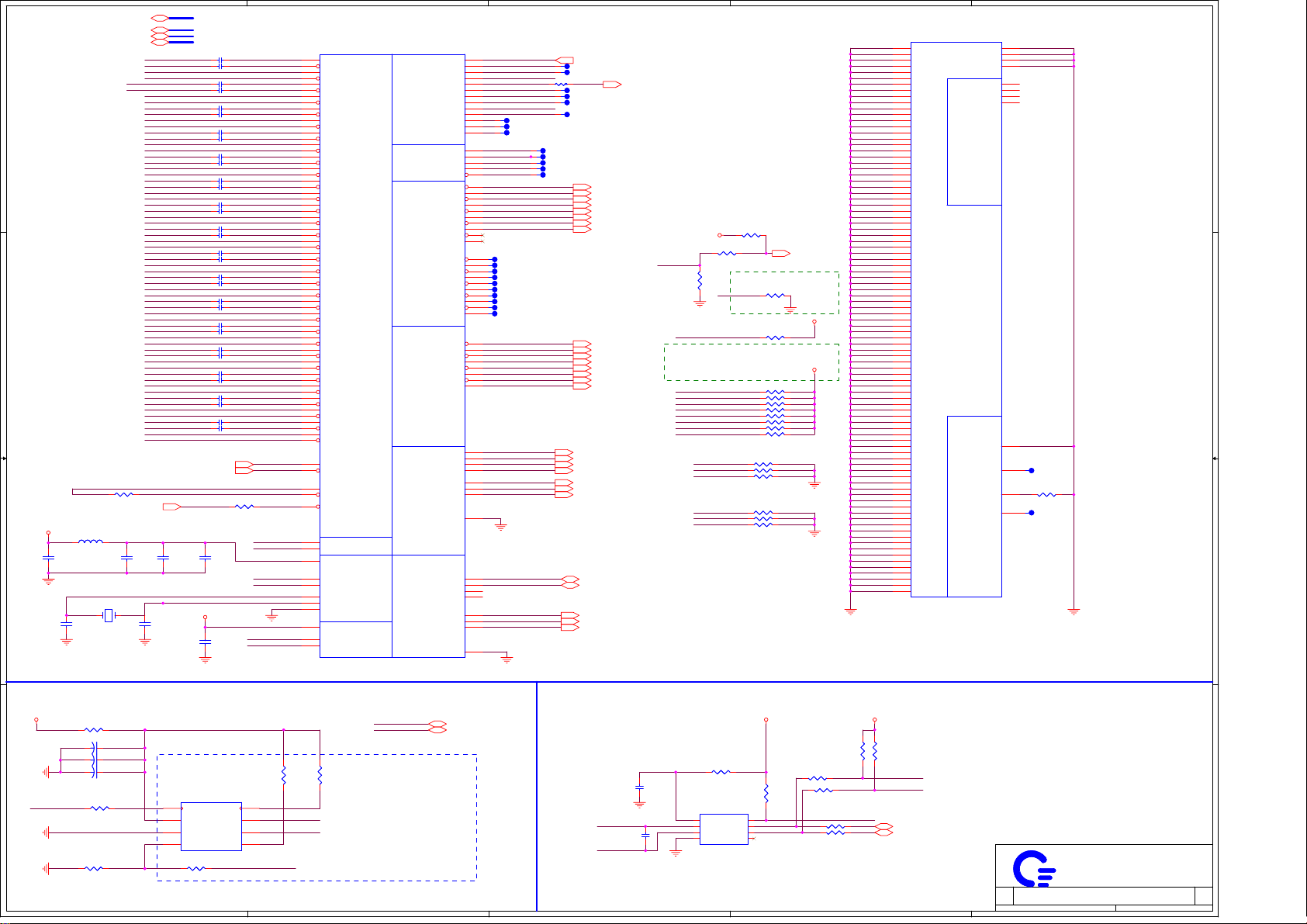

CPU

1

2

3

4

5

6

7

8

Thermal monitor

U51A

HA#[3..31](6)

A A

B B

C C

G1 Pin:NC for

Dothan and

DPRSTP# for

Yonah

DPRSTP#(18)

D D

ECN D2B For Battery only can't boot

THERMTRIP#(7,18)

+VCCP

1

HA#[3..31]

HADSTB0#(6)

HADSTB1#(6)

HREQ#0(6)

HREQ#1(6)

HREQ#2(6)

HREQ#3(6)

HREQ#4(6)

ADS#(6)

HBREQ0#(6)

BPRI#(6)

BNR#(6)

HLOCK#(6)

HIT#(6)

HITM#(6)

DEFER#(6)

T200T200

T197T197

T111T111

T113T113

HTRDY#(6)

RS#0(6)

RS#1(6)

RS#2(6)

A20M#(18)

FERR#(18)

IGNNE#(18)

CPUPWRGD(18)

SMI#(18)

T196T196

T198T198

T112T112

T199T199

DBR#(19)

INTR(18)

NMI(18)

STPCLK#(18)

CPUSLP#(6,18)

DPSLP#(18)

R596 *0RR596 *0R

EMI request

R499 56RR499 56R

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

A20M#

FERR#

IGNNE#

CPUPWRGD

SMI#

STPCLK#

CPUSLP#

DPSLP#

THERMDA

THERMDC

THERMTRIP#_RR

CPU_PROCHOT#

IERR#

BPM0#

BPM1#

BPM2#

BPM3#

TCK

TDO

TDI

TMS

TRST#

PREQ#

PRDY#

DBR#

U51A

P4

A3#

U4

A4#

V3

A5#

R3

A6#

V2

A7#

W1

A8#

T4

A9#

W2

A10#

Y4

A11#

Y1

A12#

U1

A13#

AA3

A14#

Y3

A15#

AA2

A16#

AF4

A17#

AC4

A18#

AC7

A19#

AC3

A20#

AD3

A21#

AE4

A22#

AD2

A23#

AB4

A24#

AC6

A25#

AD5

A26#

AE2

A27#

AD6

A28#

AF3

A29#

AE1

A30#

AF1

A31#

U3

ADSTB0#

AE5

ADSTB1#

R2

REQ0#

P3

REQ1#

T2

REQ2#

P1

REQ3#

T1

REQ4#

N2

ADS#

A4

IERR#

N4

BREQ0#

J3

BPRI#

L1

BNR#

J2

LOCK#

K3

HIT#

K4

HITM#

L4

DEFER#

C8

BPM0#

B8

BPM1#

A9

BPM2#

C9

BPM3#

M3

TRDY#

H1

RS0#

K1

RS1#

L2

RS2#

C2

A20M#

D3

FERR#

A3

IGNNE#

E4

PWRGOOD

B4

SMI#

A13

TCK

A12

TDO

C12

TDI

C11

TMS

B13

TRST#

A16

ITP_CLK0

A15

ITP_CLK1

B10

PREQ#

A10

PRDY#

A7

DBR#

D1

LINT0

D4

LINT1

C6

STPCLK#

A6

SLP#

B7

DPSLP#

G1

DPRSTP#

B18

THERMDA

A18

THERMDC

C17

THERMTRIP#

B17

PROCHOT#

Dothan Processor

Dothan Processor

2

Dothan

Dothan

REQUEST

REQUEST

PHASE

PHASE

SIGNALS

SIGNALS

ERROR

ERROR

SIGNALS

SIGNALS

ARBITRATION

ARBITRATION

PHASE

PHASE

SIGNALS

SIGNALS

SNOOP PHASE

SNOOP PHASE

SIGNALS

SIGNALS

RESPONSE

RESPONSE

PHASE

PHASE

SIGNALS

SIGNALS

PC

PC

COMPATIBILITY

COMPATIBILITY

SIGNALS

SIGNALS

DIAGNOSTIC

DIAGNOSTIC

& TEST

& TEST

SIGNALS

SIGNALS

EXECUTION

EXECUTION

CONTROL

CONTROL

SIGNALS

SIGNALS

THERMAL DIODE

THERMAL DIODE

1 OF 3

1 OF 3

3

DATA

DATA

PHASE

PHASE

SIGNALS

SIGNALS

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN0#

DSTBP0#

DSTBN1#

DSTBP1#

DSTBN2#

DSTBP2#

DSTBN3#

DSTBP3#

DINV0#

DINV1#

DINV2#

DINV3#

DBSY#

DRDY#

BCLK1

BCLK0

INIT#

RESET#

DPWR#

A19

A25

A22

B21

A24

B26

A21

B20

C20

B24

D24

E24

C26

B23

E23

C25

H23

G25

L23

M26

H24

F25

G24

J23

M23

J25

L26

N24

M25

H26

N25

K25

Y26

AA24

T25

U23

V23

R24

R26

R23

AA23

U26

V24

U25

V26

Y23

AA26

Y25

AB25

AC23

AB24

AC20

AC22

AC25

AD23

AE22

AF23

AD24

AF20

AE21

AD21

AF25

AF22

AF26

C23

C22

K24

L24

W25

W24

AE24

AE25

D25

J26

T24

AD20

M2

H2

B14

B15

B5

B11

C19

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

CPUINIT#

CPURST#

4

HD#[0..63]

HDSTBN0# (6)

HDSTBP0# (6)

HDSTBN1# (6)

HDSTBP1# (6)

HDSTBN2# (6)

HDSTBP2# (6)

HDSTBN3# (6)

HDSTBP3# (6)

HDBI0# (6)

HDBI1# (6)

HDBI2# (6)

HDBI3# (6)

DBSY# (6)

DRDY# (6)

HCLK_CPU# (3)

HCLK_CPU (3)

CPUINIT# (18)

CPURST# (6)

DPWR# (6)

HD#[0..63] (6)

5

MBCLK(12,27,41)

MBDATA(12,27)

THERM_ALERT#(19)

Power reset circuit

+VCCP

ITP debug

TDI

TMS

TDO

TRST#

CPURST#

TCK

Close to CPU

TDI

R492 150/FR492 150/F

IERR#

R486 56RR486 56R

CPUPWRGD

R276 200/FR276 200/F

+3V

Q38

Q38

RHU002N06

RHU002N06

2

3 1

+3V

Q40

Q40

RHU002N06

RHU002N06

2

3 1

+3V

2

3 1

R263 332/FR263 332/F

+VCCP +VCCP

R489

R489

54.9/F

54.9/F

R495

+VCCP

6

R495

27.4/F

27.4/F

R496

R496

680R

680R

+3V

THCLK_SMB

R549

R549

10K

10K

THDAT_SMB

Q41

Q41

*RHU002N06

*RHU002N06

THERM_ALERT#_RR

C453

C453

.1U

.1U

Default ITP Function Disabled

R491

R494

R494

*54.9/F

*54.9/F

R493 *22.6/FR493 *22.6/F JT4JT4

R490 *22.6/FR490 *22.6/F

R491

39.2/F

39.2/F

TCK NO STUB

JITP Connector

Place these Components

as close as possible.

VCC

DXP

GND

280VCC

1

3

2

C799

C799

.1U

.1U

THERMDA

C775

C775

2200P

2200P

THERMDC

R553

R553

10K

10K

R575

R575

10K

10K

R566 100RR566 100R

U57

U57

4

SCLK

5

SDA

6

ALERT#

MAX6642ATT98-T

MAX6642ATT98-T

Address 1001 101

1999_SHT#

Q25

Q25

2

MMBT3904

MMBT3904

1 3

R610 330RR610 330R

JT7JT7

JT8JT8

JT2JT2

JT3JT3

JT1JT1

JT5JT5

JT6JT6

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

DOTHAN (HOST)

DOTHAN (HOST)

DOTHAN (HOST)

Date: Sheet

Date: Sheet

Date: Sheet

7

Quanta Computer Inc.

Quanta Computer Inc.

1999_SHT# (37)

THERMTRIP#

+VCCP +3V_S5

C733

C733

*.1U

*.1U

DBR#

PROJECT : ZE1

PROJECT : ZE1

R488

R488

150/F

150/F

442Monday, August 22, 2005

442Monday, August 22, 2005

442Monday, August 22, 2005

8

of

of

of

B2A

B2A

B2A

1

2

3

4

5

6

7

8

CPU

Place pulldown

C727

C727

T116T116

T115T115

T203T203

C461

C461

10U

10U

C717

C717

10U

10U

+

+

+

+

C468

C468

.1U

.1U

3

resistors within

0.5" of COMP pins

R278 27.4/FR278 27.4/F

R280 54.9/FR280 54.9/F

R282 27.4/FR282 27.4/F

R279 54.9/FR279 54.9/F

R487

R487

R262

R262

*1K

*1K

*1K

*1K

C480

C480

10U

10U

C456

C456

10U

10U

C785

C785

150U/4V

150U/4V

C642

C642

150U/4V

150U/4V

C472

C472

C471

C471

.1U

.1U

.1U

.1U

T201T201

T202T202

T207T207

T117T117

T114T114

COMP0

COMP1

COMP2

COMP3

GTLREF0

TEST1

TEST2

VCC_CORE

4

P25

P26

AB2

AB1

AD26

AF7

AC1

E26

AC26

D18

D20

D22

E17

E19

E21

G21

H22

K22

V22

W21

Y22

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AB6

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC9

AC11

AC13

AC15

AC17

AC19

AD8

AD10

AD12

AD14

AD16

AD18

AE9

AE11

AE13

AE15

AE17

AE19

AF8

AF10

AF12

AF14

AF16

AF18

C5

F23

B2

C3

N1

B1

F26

D6

D8

E5

E7

E9

F6

F8

F18

F20

F22

G5

H6

J5

J21

U5

V6

W5

Y6

U51B

U51B

COMP0

COMP1

COMP2

COMP3

GTLREF0

TEST1

TEST2

NC1

RSVD2

RSVD3

RSVD4

RSVD5

VCCA3

VCCA2

VCCA1

VCCA0

VCC00

VCC01

VCC02

VCC03

VCC04

VCC05

VCC06

VCC07

VCC08

VCC09

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

Dothan Processor

Dothan Processor

Dothan

Dothan

2 OF 3

2 OF 3

POWER,

POWER,

GROUND,

GROUND,

RESERVED

RESERVED

SIGNALS

SIGNALS

A2

VSS00

A5

VSS01

A8

VSS02

A11

VSS03

A14

VSS04

A17

VSS05

A20

VSS06

A23

VSS07

A26

VSS08

B3

VSS09

B6

VSS10

B9

VSS11

B12

VSS12

B16

VSS13

B19

VSS14

B22

VSS15

B25

VSS16

C1

VSS17

C4

VSS18

C7

VSS19

C10

VSS20

C13

VSS21

C15

VSS22

C18

VSS23

C21

VSS24

C24

VSS25

D2

VSS26

D5

VSS27

D7

VSS28

D9

VSS29

D11

VSS30

D13

VSS31

D15

VSS32

D17

VSS33

D19

VSS34

D21

VSS35

D23

VSS36

D26

VSS37

E3

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

5

DOTHAN-A NC

E6

DOTHAN-B POP

E8

E10

E12

E14

E16

E18

E20

E22

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

L22

L25

M1

M4

M5

M21

M24

N3

N6

N22

N23

N26

P2

P5

P21

P24

R1

R4

SELPSB2_CLK(3,7)

SELPSB1_CLK(3,7)

SELPSB2_CLK

SELPSB1_CLK

PSI#(36)

ECN C2A

Reserve for Power saving

R498 0RR498 0R

R497 0RR497 0R

6

CPU_VID0(36)

CPU_VID1(36)

CPU_VID2(36)

CPU_VID3(36)

CPU_VID4(36)

CPU_VID5(36)

R628 *0RR628 *0R

+VCCP

R281

R281

1K/F

1K/F

A A

B B

Place voltage divider within

0.5" of GTLREF pin

R283

R283

2K/F

2K/F

R275 0RR275 0R

+1.5V

C463

C463

.01U

.01U

CPU_VCCA

C473

C473

10U

10U

CAP

VCC_CORE

C742

C742

C743

C743

10U

10U

C C

D D

+VCCP

C436

C436

+

+

150U/4V

150U/4V

C477

C477

10U

10U

10U

10U

C744

C744

10U

10U

C720

C720

VCC_CORE

1

C476

C476

10U

10U

10U

10U

C745

C745

10U

10U

VCC_CORE

C719

C719

C474

C474

.1U

.1U

C741

C741

10U

10U

10U

10U

C459

C459

C465

C465

.1U

.1U

10U

10U

C721

C721

10U

10U

10U

10U

C460

C460

C735

C735

.1U

.1U

C740

C740

10U

10U

C722

C722

10U

10U

10U

10U

C458

C458

2

10U

10U

10U

10U

VCC_CORE

VCC_CORE

C731

C731

.1U

.1U

C475

C475

+

+

+

+

C479

C479

C658

C658

150U/4V

150U/4V

C815

C815

150U/4V

150U/4V

C728

C728

.1U

.1U

C718

C718

10U

10U

10U

10U

VCC_CORE

VCC_COREVCC_CORE

C478

C478

+VCCP

+

+

+

+

C737

C737

.1U

.1U

C457

C457

10U

10U

C723

C723

10U

10U

C801

C801

150U/4V

150U/4V

C470

C470

150U/4V

150U/4V

.1U

.1U

+VCCP

T206T206

T205T205

BSEL0

BSEL1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

U51C

U51C

D10

VCCP0

D12

VCCP1

D14

VCCP2

D16

VCCP3

E11

VCCP4

E13

VCCP5

E15

VCCP6

F10

VCCP7

F12

VCCP8

F14

VCCP9

F16

VCCP10

K6

VCCP11

L5

VCCP12

L21

VCCP13

M6

VCCP14

M22

VCCP15

N5

VCCP16

N21

VCCP17

P6

VCCP18

P22

VCCP19

R5

VCCP20

R21

VCCP21

T6

VCCP22

T22

VCCP23

U21

VCCP24

P23

VCCQ0

W4

VCCQ1

E2

VID0

F2

VID1

F3

VID2

G3

VID3

G4

VID4

H4

VID5

AE7

VCCSENSE

AF6

VSSSENSE

C16

BSEL0

C14

BSEL1

E1

PSI

R6

VSS100

R22

VSS101

R25

VSS102

T3

VSS103

T5

VSS104

T21

VSS105

T23

VSS106

T26

VSS107

U2

VSS108

U6

VSS109

U22

VSS110

U24

VSS111

V1

VSS112

V4

VSS113

V5

VSS114

V21

VSS115

V25

VSS116

W3

VSS117

W6

VSS118

W22

VSS119

Dothan Processor

Dothan Processor

DOTHAN (POWER & NC)

DOTHAN (POWER & NC)

DOTHAN (POWER & NC)

Dothan

Dothan

3 OF 3

3 OF 3

POWER, GROUND AND NC

POWER, GROUND AND NC

VID

VID

PROJECT : ZE1

PROJECT : ZE1

Quanta Computer Inc.

Quanta Computer Inc.

7

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

542Monday, August 22, 2005

542Monday, August 22, 2005

542Monday, August 22, 2005

W23

W26

Y2

Y5

Y21

Y24

AA1

AA4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB3

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD22

AD25

AE3

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF2

AF5

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF24

of

of

of

8

B2A

B2A

B2A

1

U46E

U46E

AF23

VSS136

H23

VSS137

AL22

VSS138

AH22

VSS139

J22

VSS140

E22

VSS141

D22

VSS142

A22

VSS143

AN21

VSS144

AF21

VSS145

F21

VSS146

C21

VSS147

AK20

VSS148

V20

VSS149

G20

VSS150

A A

B B

C C

D D

F20

VSS151

E20

VSS152

D20

VSS153

A20

VSS154

AN19

VSS155

AG19

VSS156

W19

VSS157

T19

VSS158

J19

VSS159

H19

VSS160

C19

VSS161

AL18

VSS162

U18

VSS163

B18

VSS164

A18

VSS165

AN17

VSS166

AJ17

VSS167

AF17

VSS168

G17

VSS169

C17

VSS170

AL16

VSS171

K16

VSS172

H16

VSS173

D16

VSS174

A16

VSS175

K15

VSS176

C15

VSS177

AN14

VSS178

AL14

VSS179

AJ14

VSS180

AG14

VSS181

K14

VSS182

J14

VSS183

F14

VSS184

B14

VSS185

A14

VSS186

J12

VSS187

D12

VSS188

B12

VSS189

AN11

VSS190

AL11

VSS191

AJ11

VSS192

AG11

VSS193

AF11

VSS194

AA11

VSS195

Y11

VSS196

H11

VSS197

F11

VSS198

AA10

VSS199

Y10

VSS200

L10

VSS201

D10

VSS202

AN9

VSS203

AH9

VSS204

AE9

VSS205

AC9

VSS206

AA9

VSS207

V9

VSS208

T9

VSS209

K9

VSS210

H9

VSS211

A9

VSS212

AL8

VSS213

Y8

VSS214

P8

VSS215

L8

VSS216

E8

VSS217

C8

VSS218

AN7

VSS219

AK7

VSS220

AG7

VSS221

AA7

VSS222

V7

VSS223

G7

VSS224

AJ6

VSS225

AE6

VSS226

AC6

VSS227

AA6

VSS228

T6

VSS229

P6

VSS230

L6

VSS231

J6

VSS232

B6

VSS233

AP5

VSS234

AL5

VSS235

W5

VSS236

E5

VSS237

AN4

VSS238

AF4

VSS239

Y4

VSS240

U4

VSS241

P4

VSS242

L4

VSS243

H4

VSS244

C4

VSS245

AJ3

VSS246

AC3

VSS247

AB3

VSS248

AA3

VSS249

C3

VSS250

A3

VSS251

AN2

VSS252

AL2

VSS253

AH2

VSS254

AE2

VSS255

AD2

VSS256

V2

VSS257

T2

VSS258

P2

VSS259

L2

VSS260

B27

VSS261

J26

VSS262

G26

VSS263

E26

VSS264

A26

VSS265

AN24

VSS266

AL24

VSS267

J2

VSS268

G2

VSS269

D2

VSS270

Y1

VSS271

B36

VSSALVDS

1

VSS

VSS

2

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

ALVISO

ALVISO

2

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

AG37

Y37

V37

T37

P37

M37

K37

H37

E37

AN36

AL36

AJ36

AF36

AE36

AD36

AC36

AB36

AA36

C36

AE35

Y35

W35

V35

U35

T35

R35

P35

N35

M35

L35

K35

J35

H35

G35

F35

E35

D35

B35

AN34

AH34

AD34

AC34

AB34

AA34

C34

AL33

AF33

AD33

W33

V33

U33

T33

R33

P33

N33

M33

L33

K33

J33

H33

G33

F33

E33

D33

AN32

AJ32

AD32

AC32

AB32

AA32

Y32

C32

A32

AL31

AG31

AD31

W31

V31

U31

T31

R31

P31

N31

M31

L31

K31

J31

H31

G31

F31

E31

D31

AP30

AE30

AC30

AB30

AA30

Y30

C30

AM29

AJ29

AG29

AD29

AA29

W29

V29

U29

P29

L29

H29

G29

F29

E29

D29

A29

AC28

AB28

AA28

W28

E28

AN27

AL27

AJ27

AG27

AF27

AB27

AA27

W27

G27

E27

AJ24

AG24

J24

F24

D24

B24

+VCCP

+VCCP

+VCCP

+VCCP

3

3

HXRCOMP

R478

R478

24.9/F

24.9/F

R225

R225

54.9/F

54.9/F

HXSCOMP

R474

R474

221/F

221/F

R475

R475

100/F

100/F

HYRCOMP

R226

R226

24.9/F

24.9/F

R227

R227

54.9/F

54.9/F

HYSCOMP

R220

R220

221/F

221/F

R223

R223

100/F

100/F

HXSWING

C664

C664

.1U

.1U

HYSWING

C403

C403

.1U

.1U

4

HD#[0..63](4)

HD#[0..63]

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

4

5

U46A

U46A

E4

HD0#

E1

HD1#

F4

HD2#

H7

HD3#

E2

HD4#

F1

HD5#

E3

HD6#

D3

HD7#

K7

HD8#

F2

HD9#

J7

HD10#

J8

HD11#

H6

HD12#

F3

HD13#

K8

HD14#

H5

HD15#

H1

HD16#

H2

HD17#

K5

HD18#

K6

HD19#

J4

HD20#

G3

HD21#

H3

HD22#

J1

HD23#

L5

HD24#

K4

HD25#

J5

HD26#

P7

HD27#

L7

HD28#

J3

HD29#

P5

HD30#

L3

HD31#

U7

HD32#

V6

HD33#

R6

HD34#

R5

HD35#

P3

HD36#

T8

HD37#

R7

HD38#

R8

HD39#

U8

HD40#

R4

HD41#

T4

HD42#

T5

HD43#

R1

HD44#

T3

HD45#

V8

HD46#

U6

HD47#

W6

HD48#

U3

HD49#

V5

HD50#

W8

HD51#

W7

HD52#

U2

HD53#

U1

HD54#

Y5

HD55#

Y2

HD56#

V4

HD57#

Y7

HD58#

W1

HD59#

W3

HD60#

Y3

HD61#

Y6

HD62#

W2

HD63#

C1

HXRCOMP

C2

HXSCOMP

D1

HXSWING

T1

HYRCOMP

L1

HYSCOMP

P1

HYSWING

ALVISO

ALVISO

5

HOST

HOST

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADS#

HADSTB0#

HADSTB1#

HVREF

HBNR#

HBPRI#

BREQ0#

HCPURST#

HCLKINN

HCLKINP

HDBSY#

HDEFER#

HDINV#0

HDINV#1

HDINV#2

HDINV#3

HDPWR#

HDRDY#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

HEDRDY#

HHIT#

HHITM#

HLOCK#

HPCREQ#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HRS0#

HRS1#

HRS2#

HCPUSLP#

HTRDY#

G9

C9

E9

B7

A10

F9

D8

B10

E10

G10

D9

E11

F10

G11

G13

C10

C11

D11

C12

B13

A12

F12

G12

E12

C13

B11

D13

A13

F13

F8

B9

E13

J11

A5

D5

E7

H10

AB1

AB2

C6

E6

H8

K3

T7

U5

G6

F7

G4

K1

R3

V3

G5

K2

R2

W4

F6

D4

D6

B3

A11

A7

D7

B8

C7

A8

A4

C5

B4

G8

B5

6

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HCPUSLP#_GMCH

HA#[3..31]

HA#[3..31] (4)

ADS# (4)

HADSTB0# (4)

HADSTB1# (4)

BNR# (4)

BPRI# (4)

HBREQ0# (4)

CPURST# (4)

HCLK_MCH# (3)

HCLK_MCH (3)

DBSY# (4)

DEFER# (4)

HDBI0# (4)

HDBI1# (4)

HDBI2# (4)

HDBI3# (4)

DPWR# (4)

DRDY# (4)

HDSTBN0# (4)

HDSTBN1# (4)

HDSTBN2# (4)

HDSTBN3# (4)

HDSTBP0# (4)

HDSTBP1# (4)

HDSTBP2# (4)

HDSTBP3# (4)

HIT# (4)

HITM# (4)

HLOCK# (4)

HREQ#0 (4)

HREQ#1 (4)

HREQ#2 (4)

HREQ#3 (4)

HREQ#4 (4)

RS#0 (4)

RS#1 (4)

RS#2 (4)

HTRDY# (4)

7

HVREF

T82T82

T104T104

R244 0RR244 0R

+VCCP

R224

R224

100/F

100/F

R228

R228

200/F

200/F

C398

C398

.1U

.1U

CPUSLP# (4,18)

DO NOT INSTALL FOR DOTHAN-A AND INSTALL FOR DOTHAN-B(R244)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

ALVISO_A (HOST)

ALVISO_A (HOST)

ALVISO_A (HOST)

Date: Sheet

Date: Sheet

6

Date: Sheet

PROJECT : ZE1

PROJECT : ZE1

Quanta Computer Inc.

Quanta Computer Inc.

7

8

B2A

B2A

642Monday, August 22, 2005

642Monday, August 22, 2005

642Monday, August 22, 2005

8

B2A

of

of

of

1

DMI_TXN0(19)

DMI_TXN1(19)

DMI_TXN2(19)

A A

B B

C C

R207

R207

*40.2/F

*40.2/F

Route as short

as possible.

+1.8VSUS

R196

R196

80.6/F

80.6/F

D D

R203

R203

80.6/F

80.6/F

DMI_TXN3(19)

DMI_TXP0(19)

DMI_TXP1(19)

DMI_TXP2(19)

DMI_TXP3(19)

DMI_RXN0(19)

DMI_RXN1(19)

DMI_RXN2(19)

DMI_RXN3(19)

DMI_RXP0(19)

DMI_RXP1(19)

DMI_RXP2(19)

DMI_RXP3(19)

CLK_SDRAM0(10)

CLK_SDRAM1(10)

CLK_SDRAM3(10)

CLK_SDRAM4(10)

CLK_SDRAM0#(10)

CLK_SDRAM1#(10)

CLK_SDRAM3#(10)

CLK_SDRAM4#(10)

CKE0(10,11)

CKE1(10,11)

CKE2(10,11)

CKE3(10,11)

SM_CS0#(10,11)

SM_CS1#(10,11)

SM_CS2#(10,11)

SM_CS3#(10,11)

M_ODT0(10,11)

M_ODT1(10,11)

M_ODT2(10,11)

M_ODT3(10,11)

SMXSLEW

SMYSLEW

It's point to point,

55ohm trace, keep as

short as possible.

R206

R206

*40.2/F

*40.2/F

M_RCOMPN

M_RCOMPP

T58T58

T65T65

T59T59

T64T64

CKE0

CKE1

CKE2

CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

M_OCDCOMP0

M_OCDCOMP1

M_RCOMPN

M_RCOMPP

SMVREF_MCH

+2.5V

R241 10KR241 10K

R240 10KR240 10K

Place Close to MCH

1

2

CFG[0:2]=100 FOR FSB 533

CFG[0:2]=101 FOR FSB 400

U46C

U46C

AA31

DMIRXN0

AB35

DMIRXN1

AC31

DMIRXN2

AD35

DMIRXN3

Y31

DMIRXP0

AA35

DMIRXP1

AB31

DMIRXP2

AC35

DMIRXP3

AA33

DMITXN0

AB37

DMITXN1

AC33

DMITXN2

AD37

AA37

AB33

AC37

AM33

AE11

AJ34

AC10

AN33

AE10

AJ33

AD10

AP21

AM21

AH21

AK21

AN16

AM14

AH15

AG16

AF22

AF16

AP14

AL15

AM11

AN10

AK10

AK11

AF37

AD1

AE27

AE28

AF10

Y33

AL1

AF6

AK1

AF5

AF9

DMITXN3

DMITXP0

DMITXP1

DMITXP2

DMITXP3

SM_CK0

SM_CK1

SM_CK2

SM_CK3

SM_CK4

SM_CK5

SM_CK0#

SM_CK1#

SM_CK2#

SM_CK3#

SM_CK4#

SM_CK5#

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

SM_OCDCOMP0

SM_OCDCOMP1

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

SMRCOMPN

SMRCOMPP

SMVREF0

SMVREF1

SMXSLEWIN

SMXSLEWOUT

SMYSLEWIN

SMYSLEWOUT

ALVISO

ALVISO

+1.8VSUS

2

PM_EXTTS#0

PM_EXTTS#1

R180

R180

10K/F

10K/F

SMVREF_MCH

R205

R205

10K/F

10K/F

DMIDDR MUXING

DMIDDR MUXING

C336

C336

.1U

.1U

CFG/RSVDPMLCKNC

CFG/RSVDPMLCKNC

THRMTRIP#

DREF_CLKN

DREF_CLKP

DREF_SSCLKN

DREF_SSCLKP

C325

C325

2.2U

2.2U

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

BM_BUSY#

EXT_TS0#

EXT_TS1#

PWROK

RSTIN#

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

TXLCLKOUT+(28)

TXLCLKOUT-(28)

TXLOUT0+(28)

TXLOUT0-(28)

TXLOUT1-(28)

TXLOUT1+(28)

TXLOUT2+(28)

TXLOUT2-(28)

G16

H13

G14

F16

F15

G15

E16

D17

J16

D15

E15

D14

E14

H12

C14

H15

J15

H14

G22

G23

D23

G25

G24

J17

A31

A30

D26

D25

J23

J21

H22

F5

AD30

AE29

A24

A23

C37

D37

AP37

AN37

AP36

AP2

AP1

AN1

B1

A2

B37

A36

A37

3

CFG0

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

PM_EXTTS#0

PM_EXTTS#1

DOT96#

DOT96

DREFSSCLK#

DREFSSCLK

TP_NC1

TP_NC2

TP_NC3

TP_NC4

TP_NC5

TP_NC6

TP_NC7

TP_NC8

TP_NC9

TP_NC10

TP_NC11

DISP_ON(12,15,28)

BLON(12,28)

3

T85T85

T93T93

T70T70

T98T98

T89T89

T97T97

T81T81

T103T103

T71T71

T74T74

T72T72

T86T86

T76T76

T87T87

T73T73

T80T80

T75T75

T101T101

T105T105

T78T78

R255 0RR255 0R

R183 100RR183 100R

T144T144

T143T143

T137T137

T147T147

T141T141

T139T139

T184T184

T187T187

T185T185

T190T190

T188T188

BLON

TXLCLKOUT+

TXLCLKOUT-

TXLOUT0+

TXLOUT0-

TXLOUT1TXLOUT1+

TXLOUT2+

TXLOUT2-

R231 4.7KR231 4.7K

R245 0RR245 0R

R246 0RR246 0R

R234 *1KR234 *1K

R230 *1KR230 *1K

R237 1KR237 1K

R239 1KR239 1K

DOT96# (3)

DOT96 (3)

DREFSSCLK# (3)

DREFSSCLK (3)

4

+VCCP

FOR DDR533

Low=DMIx2

High=DMIx4

FOR CPU533

SELPSB1_CLK (3,5)

SELPSB2_CLK (3,5)

INT_TV_COMP(17)

INT_TV_Y/G(17)

INT_TV_C/R(17)

R232 *INT@4.99K/FR232 *INT@4.99K/F

5

SDVO_CTRLDATA(16)

SDVO_CTRLCLK(16)

CLK_MCH_3GPLL#(3)

CLK_MCH_3GPLL(3)

INT_TV_COMP

INT_TV_Y/G

INT_TV_C/R

TV_REFSET

INT VGA Staff

INT_DDCCLK(17)

INT_DDCDAT(17)

INT_VGA_BLU(17)

INT_VGA_GRN(17)

INT_VGA_RED(17)

INT_VSYNC(17)

INT_HSYNC(17)

INT_DDCCLK

INT_DDCDAT

INT_VGA_BLU

INT_VGA_GRN

INT_VGA_RED

INT_VSYNC

INT_HSYNC

INT VGA Staff

INT_DISP_ON

INT_TXLCLKOUT+

INT_TXLCLKOUT-

INT_TXLOUT0+

INT_TXLOUT0-

INT_TXLOUT1INT_TXLOUT1+

INT_TXLOUT2+

INT_TXLOUT2-

REFSET

INT_BLON

I_EDIDCLK(28)

I_EDIDDATA(28)

INT_TXLCLKOUTINT_TXLCLKOUT+

INT_TXLOUT0INT_TXLOUT1INT_TXLOUT2-

INT_TXLOUT0+

INT_TXLOUT1+

INT_TXLOUT2+

R229 *INT@255/FR229 *INT@255/F

R242 *INT@1.5K/FR242 *INT@1.5K/F

PM_BMBUSY# (19)

THERMTRIP# (4,18)

IMVP_PWRGD_NB (19)

PLTRST# (12,16,18,19,26,27,32,33)

INT VGA Staff

R483 *INT@150/FR483 *INT@150/F

R480 *INT@150/FR480 *INT@150/F

R481 *INT@150/FR481 *INT@150/F

R484 *INT@150/FR484 *INT@150/F

R485 *INT@150/FR485 *INT@150/F

R482 *INT@150/FR482 *INT@150/F

R233 *INT@0RR233 *INT@0R

R235 *INT@0RR235 *INT@0R

RN13 *INT@0X2RN13 *INT@0X2

RN14 *INT@0X2RN14 *INT@0X2

RN15 *INT@0X2RN15 *INT@0X2

RN12 *INT@0X2RN12 *INT@0X2

INT_TV_C/R

INT_TV_COMP

INT_TV_Y/G

INT_VGA_RED

INT_VGA_GRN

INT_VGA_BLU

241

241

241

241

INT_DISP_ONDISP_ON

INT_BLON

R236

R236

*INT@100K

*INT@100K

3

3

3

3

EXT VGA Staff(Place back RN12/RN13/RN14/RN15)

RN3 EXT@0X2RN3 EXT@0X2

3

1

RN2 EXT@0X2RN2 EXT@0X2

3

1

RN1 EXT@0X2RN1 EXT@0X2

1

3

RN4 EXT@0X2RN4 EXT@0X2

3

1

4

4

2

4

2

2

4

4

2

EXT_TXLCLKOUTEXT_TXLCLKOUT+

EXT_TXLOUT0+

EXT_TXLOUT0-

EXT_TXLOUT1EXT_TXLOUT1+

EXT_TXLOUT2EXT_TXLOUT2+

5

T91T91

T92T92

T95T95

T100T100

T83T83

T84T84

T96T96

T99T99

T79T79

T88T88

T94T94

T106T106

T77T77

T90T90

U46F

U46F

H24

SDVOCTRL_DATA

H25

SDVOCTRL_CLK

AB29

GCLKN

AC29

GCLKP

A15

TVDAC_A

C16

TVDAC_B

A17

TVDAC_C

J18

TV_REFSET

B15

TV_IRTNA

B16

TV_IRTNB

B17

TV_IRTNC

E24

DDCCLK

E23

DDCDATA

E21

BLUE

D21

BLUE#

C20

GREEN

B20

GREEN#

A19

RED

B19

RED#

H21

VSYNC

G21

HSYNC

J20

REFSET

E25

LBKLT_CTRL

F25

LBKLT_EN

C23

LCTLA_CLK

C22

LCTLB_DATA

F23

LDDC_CLK

F22

LDDC_DATA

F26

LVDD_EN

C33

LIBG

C31

LVBG

F28

LVREFH

F27

LVREFL

B30

LACLKN

B29

LACLKP

C25

LBCLKN

C24

LBCLKP

B34

LADATAN0

B33

LADATAN1

B32

LADATAN2

A34

LADATAP0

A33

LADATAP1

B31

LADATAP2

C29

LBDATAN0

D28

LBDATAN1

C27

LBDATAN2

C28

LBDATAP0

D27

LBDATAP1

C26

LBDATAP2

EXT_TXLCLKOUT- (12)

EXT_TXLCLKOUT+ (12)

EXT_TXLOUT0+ (12)

EXT_TXLOUT0- (12)

EXT_TXLOUT1- (12)

EXT_TXLOUT1+ (12)

EXT_TXLOUT2- (12)

EXT_TXLOUT2+ (12)

ALVISO

ALVISO

6

MISC

MISC

TV VGA LVDS

TV VGA LVDS

6

EXP_COMPI

EXP_ICOMPO

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

EXP_TXN7

EXP_TXN8

EXP_TXN9

PCI-EXPRESS GRAPHICS

PCI-EXPRESS GRAPHICS

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

INT VGA Staff(Place back

C681/C667/C673/C659/C683/C671/C675/C662)

CGMCHEXP_TXP0

CGMCHEXP_TXN0 SDVOB_RCGMCHEXP_TXP1

CGMCHEXP_TXN1

CGMCHEXP_TXP2

CGMCHEXP_TXN2

CGMCHEXP_TXP3

CGMCHEXP_TXN3

7

GMCHEXP_TXP[15..0] (12)

GMCHEXP_TXN[15..0] (12)

GMCHEXP_RXP[15..0] (12,16)

GMCHEXP_RXN[15..0] (12,16)

D36

D34

E30

F34

G30

H34

J30

K34

L30

M34

N30

P34

R30

T34

U30

V34

W30

Y34

D30

E34

F30

G34

H30

J34

K30

L34

M30

N34

P30

R34

T30

U34

V30

W34

E32

F36

G32

H36

J32

K36

L32

M36

N32

P36

R32

T36

U32

V36

W32

Y36

D32

E36

F32

G36

H32

J36

K32

L36

M32

N36

P32

R36

T32

U36

V32

W36

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

7

R219 24.9/FR219 24.9/F

GMCHEXP_RXN0

GMCHEXP_RXN1

GMCHEXP_RXN2

GMCHEXP_RXN3

GMCHEXP_RXN4

GMCHEXP_RXN5

GMCHEXP_RXN6

GMCHEXP_RXN7

GMCHEXP_RXN8

GMCHEXP_RXN9

GMCHEXP_RXN10

GMCHEXP_RXN11

GMCHEXP_RXN12

GMCHEXP_RXN13

GMCHEXP_RXN14

GMCHEXP_RXN15

GMCHEXP_RXP0

GMCHEXP_RXP1

GMCHEXP_RXP2

GMCHEXP_RXP3

GMCHEXP_RXP4

GMCHEXP_RXP5

GMCHEXP_RXP6

GMCHEXP_RXP7

GMCHEXP_RXP8

GMCHEXP_RXP9

GMCHEXP_RXP10

GMCHEXP_RXP11

GMCHEXP_RXP12

GMCHEXP_RXP13

GMCHEXP_RXP14

GMCHEXP_RXP15

CGMCHEXP_TXN0

CGMCHEXP_TXN1 GMCHEXP_TXN1

CGMCHEXP_TXN2

CGMCHEXP_TXN3

CGMCHEXP_TXN4

CGMCHEXP_TXN5

CGMCHEXP_TXN6

CGMCHEXP_TXN7

CGMCHEXP_TXN9

CGMCHEXP_TXN10

CGMCHEXP_TXN11

CGMCHEXP_TXN12

CGMCHEXP_TXN13

CGMCHEXP_TXN15

CGMCHEXP_TXP0

CGMCHEXP_TXP1

CGMCHEXP_TXP2

CGMCHEXP_TXP3

CGMCHEXP_TXP4

CGMCHEXP_TXP5

CGMCHEXP_TXP6

CGMCHEXP_TXP7

CGMCHEXP_TXP8

CGMCHEXP_TXP9

CGMCHEXP_TXP10

CGMCHEXP_TXP11

CGMCHEXP_TXP12

CGMCHEXP_TXP13

CGMCHEXP_TXP15

C420 *INT@.1UC420 *INT@.1U

C418 *INT@.1UC418 *INT@.1U

C409 *INT@.1UC409 *INT@.1U

C406 *INT@.1UC406 *INT@.1U

C414 *INT@.1UC414 *INT@.1U

C412 *INT@.1UC412 *INT@.1U

C404 *INT@.1UC404 *INT@.1U

C399 *INT@.1UC399 *INT@.1U

ALVISO_B (DMI & PCIE)

ALVISO_B (DMI & PCIE)

ALVISO_B (DMI & PCIE)

C681 EXT@.1UC681 EXT@.1U

C667 EXT@.1UC667 EXT@.1U

C673 EXT@.1UC673 EXT@.1U

C659 EXT@.1UC659 EXT@.1U

C417 EXT@.1UC417 EXT@.1U

C653 EXT@.1UC653 EXT@.1U

C411 EXT@.1UC411 EXT@.1U

C643 EXT@.1UC643 EXT@.1U

C405 EXT@.1UC405 EXT@.1U

C625 EXT@.1UC625 EXT@.1U

C602 EXT@.1UC602 EXT@.1U

C613 EXT@.1UC613 EXT@.1U

C632 EXT@.1UC632 EXT@.1U

C606 EXT@.1UC606 EXT@.1U

C608 EXT@.1UC608 EXT@.1U

C604 EXT@.1UC604 EXT@.1U

C683 EXT@.1UC683 EXT@.1U

C671 EXT@.1UC671 EXT@.1U

C675 EXT@.1UC675 EXT@.1U

C662 EXT@.1UC662 EXT@.1U

C422 EXT@.1UC422 EXT@.1U

C657 EXT@.1UC657 EXT@.1U

C413 EXT@.1UC413 EXT@.1U

C641 EXT@.1UC641 EXT@.1U

C408 EXT@.1UC408 EXT@.1U

C626 EXT@.1UC626 EXT@.1U

C601 EXT@.1UC601 EXT@.1U

C612 EXT@.1UC612 EXT@.1U

C631 EXT@.1UC631 EXT@.1U

C605 EXT@.1UC605 EXT@.1U

C607 EXT@.1UC607 EXT@.1U

C603 EXT@.1UC603 EXT@.1U

SDVOB_R+

SDVOB_G+

SDVOB_GSDVOB_B+

SDVOB_B-

SDVOB_CLK+

SDVOB_CLK-

PROJECT : ZE1

PROJECT : ZE1

Quanta Computer Inc.

Quanta Computer Inc.

8

VCC3G_PCIE

EXT VGA Staff

GMCHEXP_TXN0

GMCHEXP_TXN2

GMCHEXP_TXN3

GMCHEXP_TXN4

GMCHEXP_TXN5

GMCHEXP_TXN6

GMCHEXP_TXN7

GMCHEXP_TXN8CGMCHEXP_TXN8

GMCHEXP_TXN9

GMCHEXP_TXN10

GMCHEXP_TXN11

GMCHEXP_TXN12

GMCHEXP_TXN13

GMCHEXP_TXN14CGMCHEXP_TXN14

GMCHEXP_TXN15

GMCHEXP_TXP0

GMCHEXP_TXP1

GMCHEXP_TXP2

GMCHEXP_TXP3

GMCHEXP_TXP4

GMCHEXP_TXP5

GMCHEXP_TXP6

GMCHEXP_TXP7

GMCHEXP_TXP8

GMCHEXP_TXP9

GMCHEXP_TXP10

GMCHEXP_TXP11

GMCHEXP_TXP12

GMCHEXP_TXP13

GMCHEXP_TXP14CGMCHEXP_TXP14

GMCHEXP_TXP15

SDVOB_R+ (16)

SDVOB_R- (16)

SDVOB_G+ (16)

SDVOB_G- (16)

SDVOB_B+ (16)

SDVOB_B- (16)

SDVOB_CLK+ (16)

SDVOB_CLK- (16)

of

of

of

742Monday, August 22, 2005

742Monday, August 22, 2005

742Monday, August 22, 2005

8

B2A

B2A

B2A

1

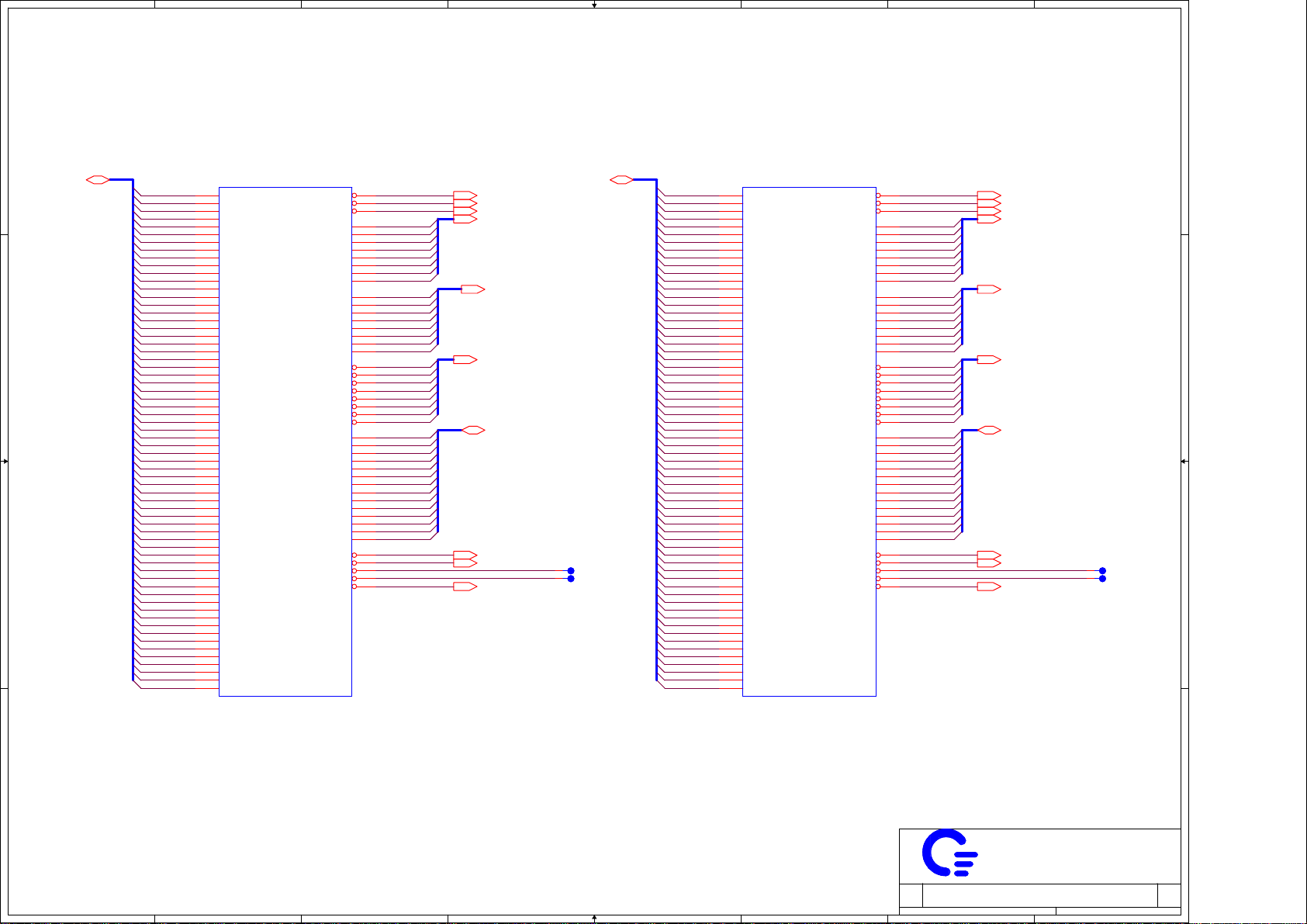

A A

2

3

4

5

6

7

8

R_A_MD[0..63](10)

B B

C C

R_A_MD0

R_A_MD1

R_A_MD2

R_A_MD3

R_A_MD4

R_A_MD5

R_A_MD6

R_A_MD7

R_A_MD8

R_A_MD9

R_A_MD10

R_A_MD11

R_A_MD12

R_A_MD13

R_A_MD14

R_A_MD15

R_A_MD16

R_A_MD17

R_A_MD18

R_A_MD19

R_A_MD20

R_A_MD21

R_A_MD22

R_A_MD23

R_A_MD24

R_A_MD25

R_A_MD26

R_A_MD27

R_A_MD28

R_A_MD29

R_A_MD30

R_A_MD31

R_A_MD32

R_A_MD33

R_A_MD34

R_A_MD35

R_A_MD37

R_A_MD38

R_A_MD39

R_A_MD40

R_A_MD41

R_A_MD42

R_A_MD43

R_A_MD44

R_A_MD45

R_A_MD46

R_A_MD47

R_A_MD48

R_A_MD49

R_A_MD50

R_A_MD51

R_A_MD52

R_A_MD53

R_A_MD54

R_A_MD55

R_A_MD56

R_A_MD57

R_A_MD58

R_A_MD59

R_A_MD60

R_A_MD61

R_A_MD62

R_A_MD63

AG35

AH35

AL35

AL37

AH36

AJ35

AK37

AL34

AM36

AN35

AP32

AM31

AM34

AM35

AL32

AM32

AN31

AP31

AN28

AP28

AL30

AM30

AM28

AL28

AP27

AM27

AM23

AM22

AL23

AM24

AN22

AP22

AM9

AL9

AL6

AP7

AP11

AP10

AL7

AM7

AN5

AN6

AN3

AP3

AP6

AM6

AL4

AM3

AK2

AK3

AG2

AG1

AL3

AM2

AH3

AG3

AF3

AE3

AD6

AC4

AF2

AF1

AD4

AD5

U46B

U46B

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQ32

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SADQ38

SADQ39

SADQ40

SADQ41

SADQ42

SADQ43

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SADQ55

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

SA_BS0#

SA_BS1#

SA_BS2#

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_CAS#

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

SA_WE#

ALVISO

ALVISO