Page 1

A

B

C

D

E

DC/DC IMVP4

Switching Power

1D2V_S0

1D05V_S0

32

CLOCK

Generator

33

ICS950813CG

DDR

Max1907AETL

INPUTS

4 4

DCBATOUT VCC_CORE

OUTPUT

1.2/1.05V DC/DC

TPS5110

INPUTS OUTPUTS

DCBATOUT

DRAM

Socket

DC/DC&CHARGER

Max1645

3 3

INPUTS OUTPUTS

AD+

36

BT+

* 2

3V/5V/2D5V/1D8V

DC/DC

TPS5130

OUTPUTSINPUTS

DCBATOUT

2 2

CM8500/APL1805

OUTPUTSINPUTS

2D5V_S3

3D3V_S5 1D5V_DC_S0

1D25V_DC_S0

3D3V_S5

5V_S5

2D5V_S3

1D8D_S0

35

SIO

NS87392

34

FIR

TFDU6102

DIGITIZER

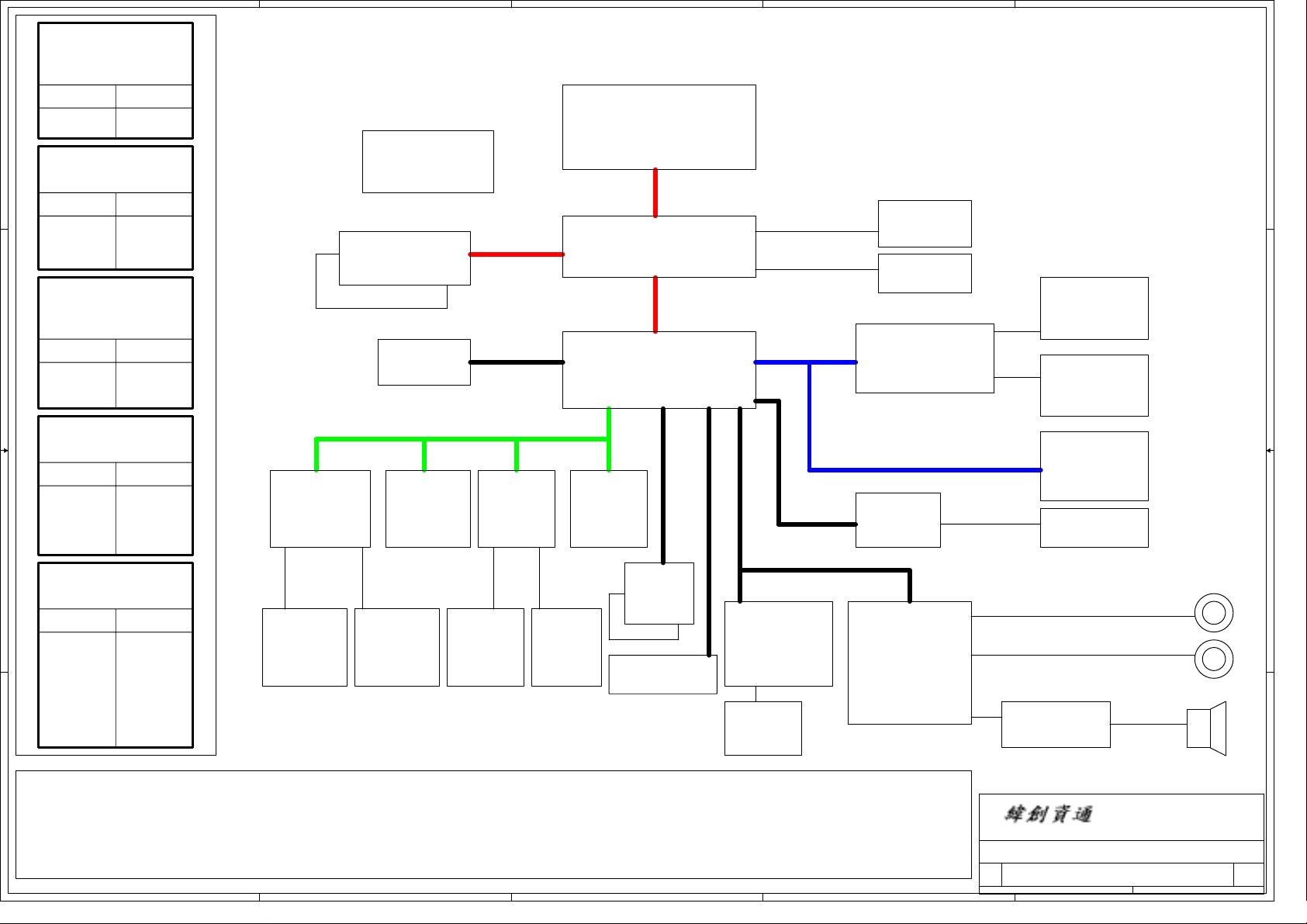

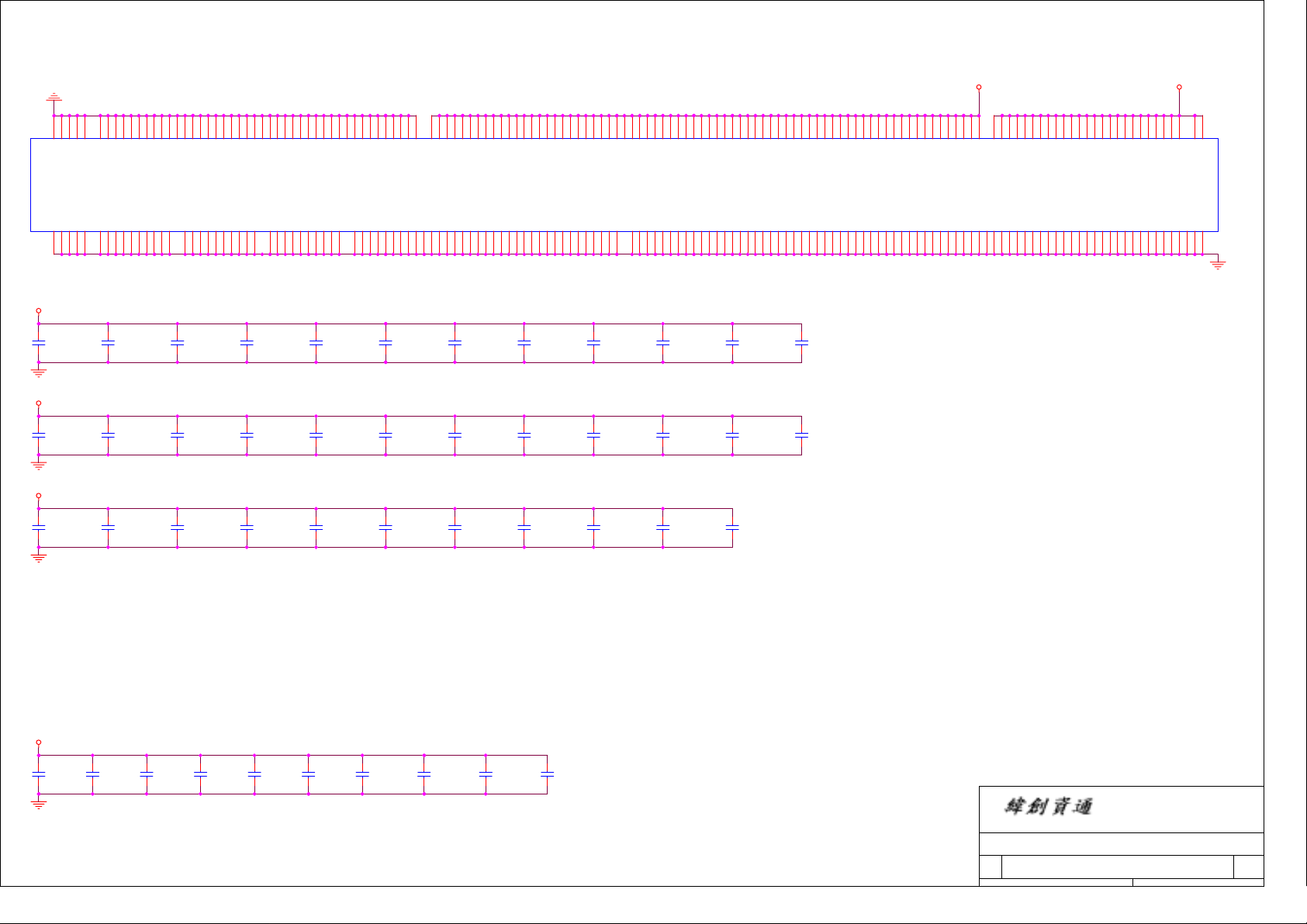

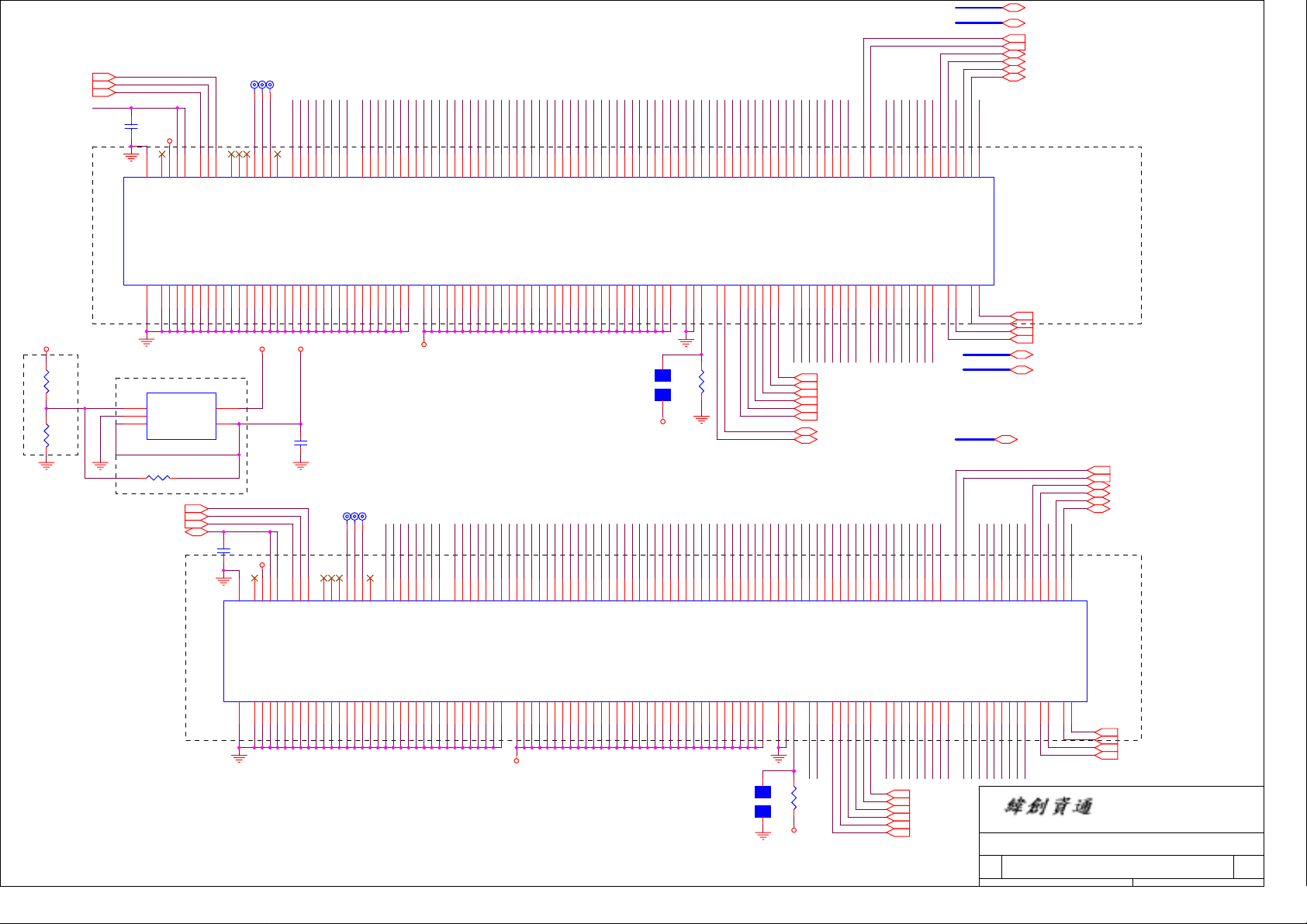

A1+ Block Diagram

CPU

PIV Banias

ULV/LV

900MHz/1GHz

uFCBGA

3

HOST BUS

400MHz

DDR 266

9,10,11

Montara-GM

Hub I/F

IDE BUS

HDD

28

Ultra

DMA-100

ICH4-M

LPC BUS

USB2.0

BIOS

ROM

49LF004A-33-4C 82562ET

KBC

M38857

TOUCH

PAD

DEBUG

PORT

27

282829

USB 2.0

PORT

0,1

23

INT

KB

BLUETOOTH

27271323

4,5

6,7,8

14,15,16

USB1.1

MODEM

DAUGHTER

CARD

21

PCI BUS

AC-LINK

RJ-11

22

CRT

LCD

R5C551

CARDBUS

& 1394

LAN PHYMII

AC 97

Codec

21

CS4299-XQ

24

12

13

18,19

CARDBUS

SLOT * 1

IEEE 1394

CONNECTOR

MINIPCI

802.11b

802.11a

RJ-45

Amplifier

APA2020A

20

20

21

2222

Line-out

Line-in/Mic

25

1 1

AC

IN

Port Replicator (100 PIN)

SEARIAL

RJ11 PRINTER

RJ45

A

PORT

CRT PS2USB*2

B

LINE

MIC

C

IN

LINE

OUT

D

Title

BLOCK DIAGRAM

Size Document Number Rev

A3

Date: Sheet

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

A1+

139Monday, March 03, 2003

E

-1

of

Page 2

A

B

C

D

E

A1+ PCI Routing Table ver. 0.1

DEVICE IDSEL IRQ DREQ/DGNT

R5C551

Mini PCI

4 4

AD17

AD21

A/D

B/C

REQ0#/GNT#0

REQ3#/GNT#3

Pin Name Strap Description Configuration I/F Type Buffe r Type

GST(1) Clock Config:Bit_1

GST(0) Clock Config:Bit_0

Low=Banias processor (default)LCLKCTLB CPU Strap

Key:PSB/Sys Mem Core/GFX

Core/(CL/CH(Core Clock)):

00(def)=Config#0

(400/266/200/(133/200))

01=Config#1

(400/200/200/(100/200))

10=Config#2

(400/200/133/(100/133))

GPIO

DVO

WOL & WOR

N/B H/W TRAP

3 3

2 2

WOL

AC Adaptor Battery Only

S1 Can Can

S3 Can No

S4 Can No

S5 Can No

ICH-4

SMBC_ICH

SMBD_ICH

3D3V_S5 3D3V_S0

3D3V_S0

3D3V_S0

INV_SMB_CTL

CK-408_SCL

CK-408_SDA

DIMM

CLK. Gen.

INV_SCL

INV_SDA

1 1

A

B

inverter

EEPROM

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

REVISION HISTORY

Size Document Number Rev

A3

C

D

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

A1+

E

239Thursday, December 26, 2002

SA

of

Page 3

A

B

C

D

E

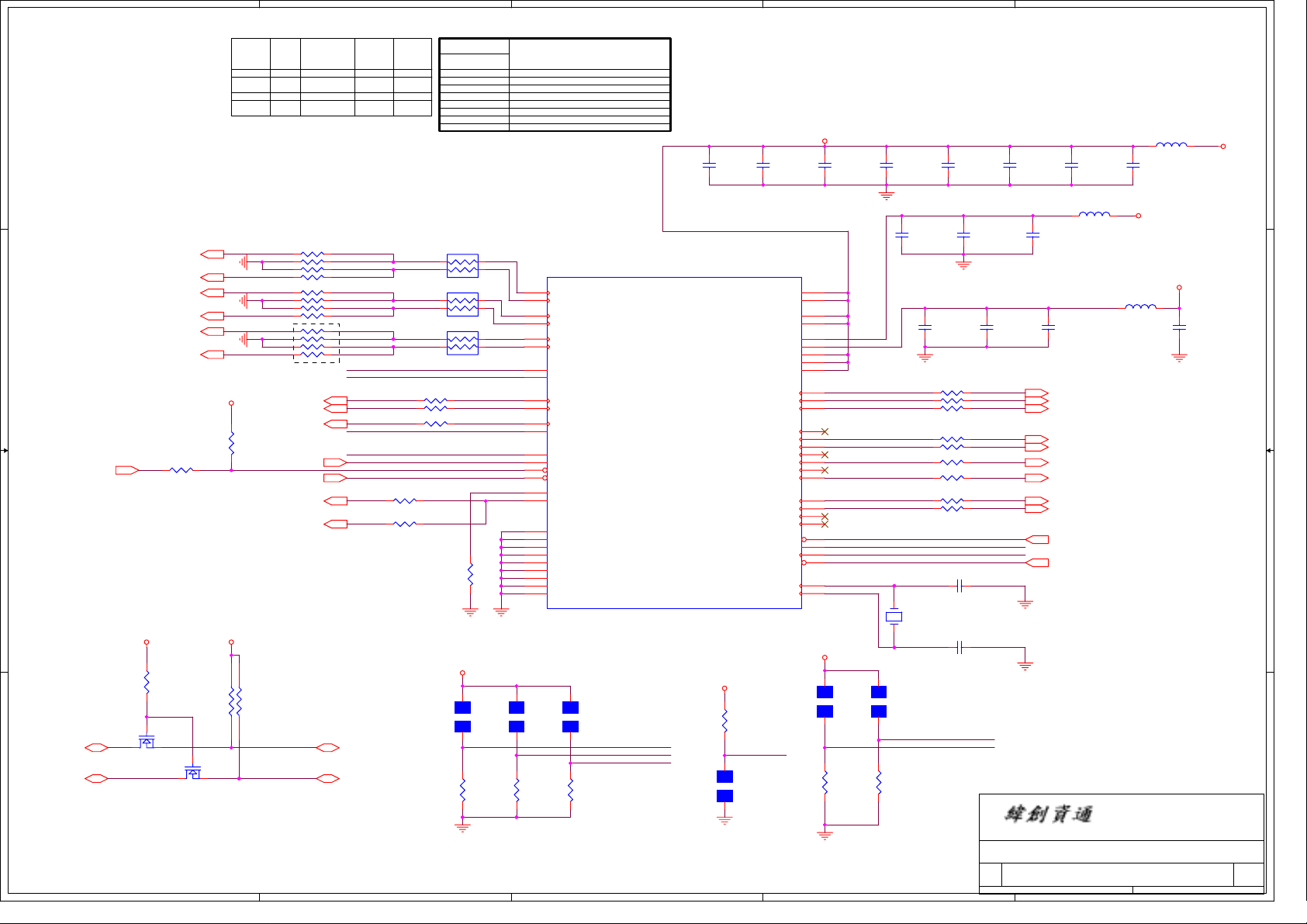

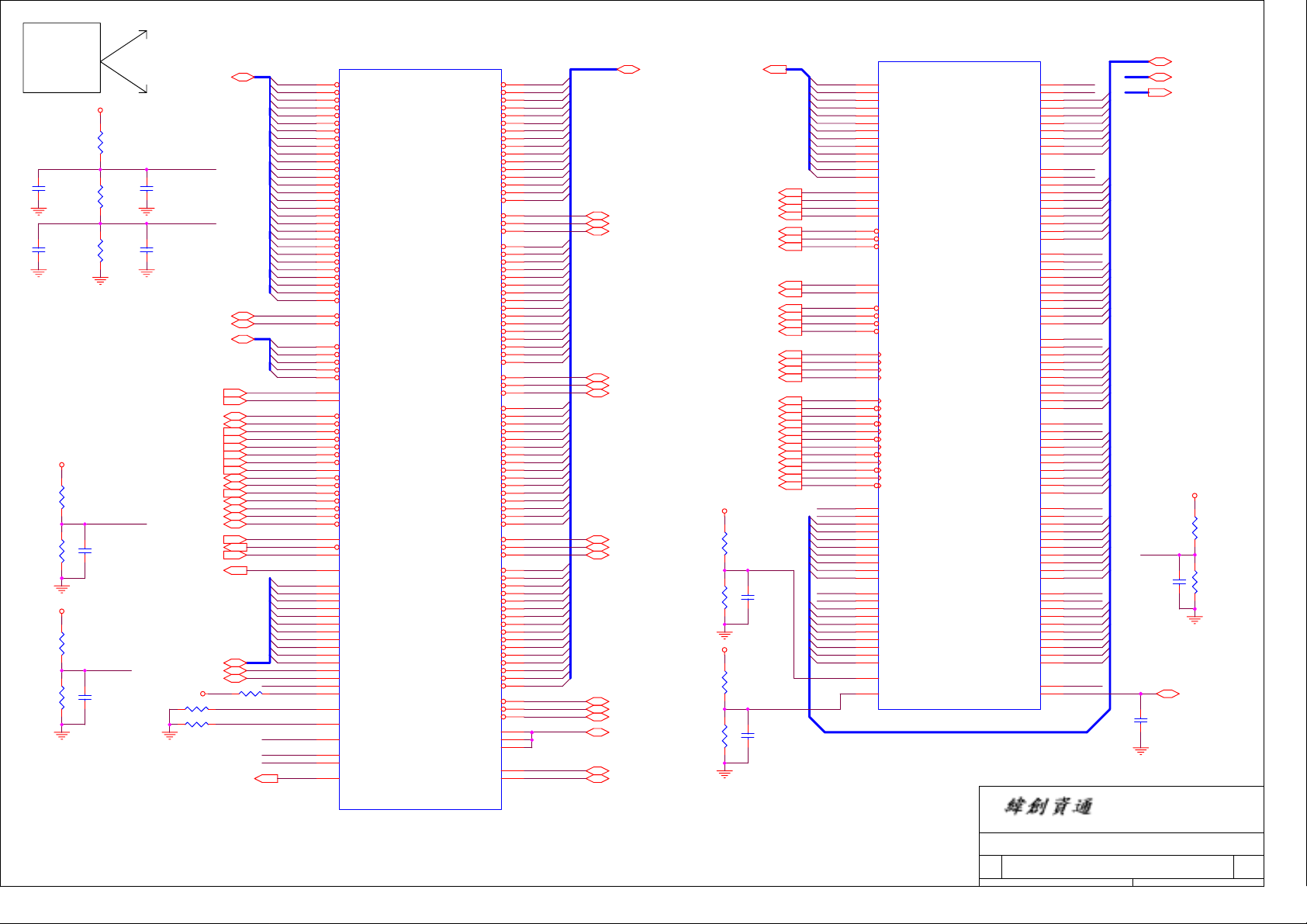

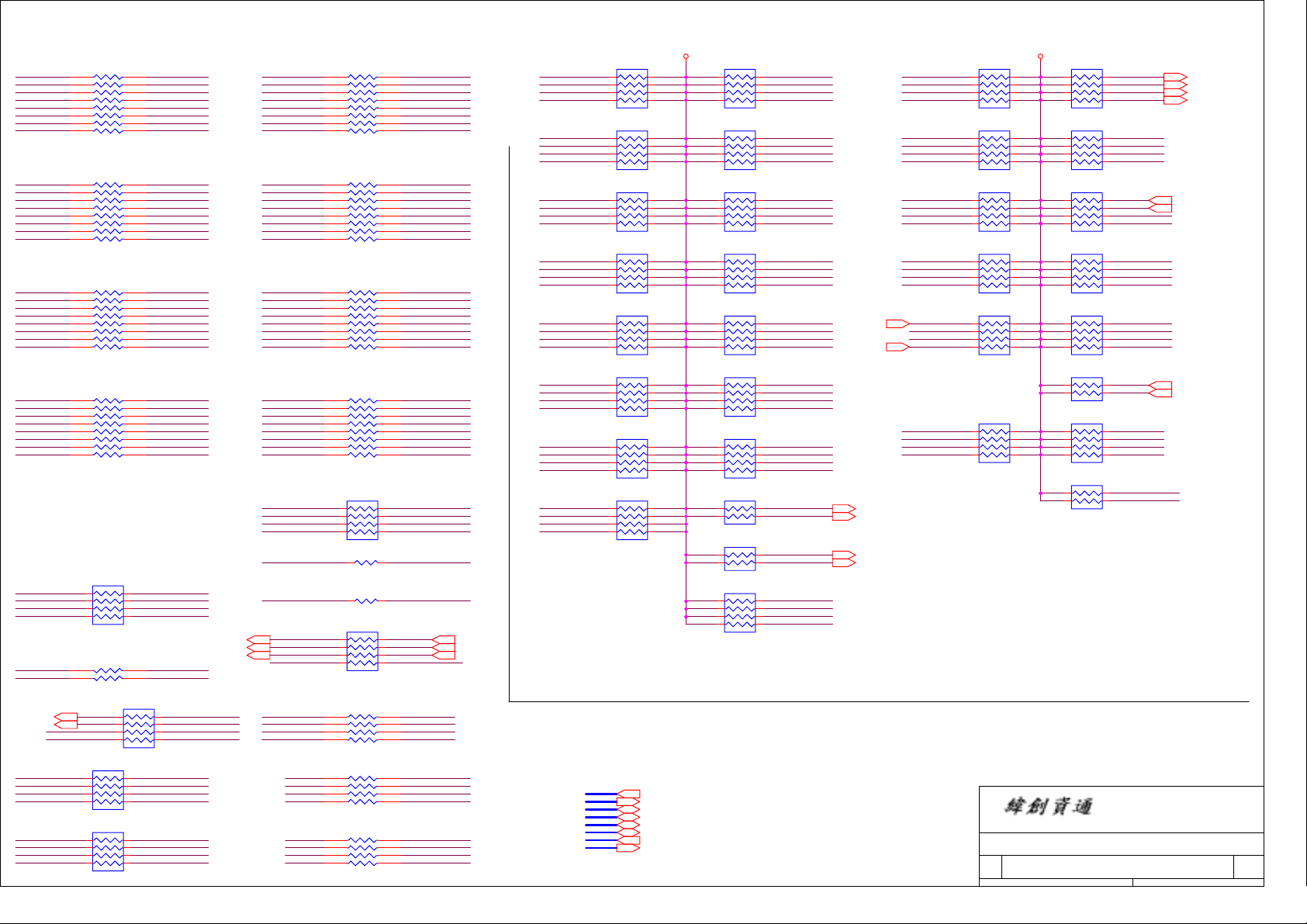

Freq. Setting

1 2

1 2

33R2

1 2

Freqency Select

RN39

2 3

1

SRN33-2-U2

RN38

2 3

1

SRN33-2-U2

RN37

2 3

1

SRN33-2-U2

33R2

CK-408_PWRSAVE#

R278

475R3F

FS4 FS3 FS2

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

CLK_ITP_CK408

4

CLK_ITP#_CK408

CLK_MCH_CK408

4

CLK_MCH#_CK408

CLK_CPU_CK408CLK_CPU_R

4

CLK_CPU#_CK408

CLK48_ICH_CK408

CLK48_DREF_CK408

33R2

DREFSSCLK_CK408

FS4

CK-408_MULT0

CK-408_IREF

CLK14_CK408

12

3D3V_S0

12

R42

DUMMY-R2

12

R269

10KR2

CPU,3V66,PCI

Standard Clocking

Standard Clocking

Standard Clocking

Standard Clocking

Pwr Save Clocking

3% Overclocking

5% Overclocking

10% Overclocking

U46

52

CPUCLKT0

51

CPUCLKC0

49

CPUCLKT1

48

CPUCLKC1

45

CPUCLKT2

44

CPUCLKC2

55

FS1

54

FS0

39

48MHZ_USB/FS2

38

48MHZ_DOT

35

3V66_1/VCH_CLK/FS3

33

3V66_0/FS4

43

MULTSEL

53

CPU_STOP#

40

PWRSAVE#

34

PCI_STOP#

42

IREF

56

REF

4

GND

9

GND

15

GND

20

GND

27

GND

47

GND

41

GND

36

GND

31

GND

ICS950813YGT

12

R274

DUMMY-R2

12

R273

10KR2

0.3% Center Spread

0 to -0.5%, Down Spread

0.3% Center Spread

0 to - 0.75%, Down Spread

Spread Off

0.3% Center Spread

0.3% Center Spread

0.3% Center Spread

12

R60

DUMMY-R2

CLK48_ICH

DREFSSCLK

FS4

12

R59

10KR2

CLKGEN_+3VRUN

C65

SC10U10V5ZY

PCICLK_F0

PCICLK_F1

ASEL/PCICLK_F2

E_PCICLK1/PCICLK1

E_PCICLK3/PCICLK3

VTT_PWRGD#

12

R43

10KR2

CK-408_MULT0

12

R44

DUMMY-R2

12

C450

SCD1U10V2MX-1

VDDPCI

VDDPCI

VDDCPU

VDDCPU

VDD48

VDD3V66

VDD3V66

VDDREF

PCICLK0

PCICLK2

PCICLK4

PCICLK5

PCICLK6

3V66_2

3V66_3

3V66_4

3V66_5

SDATA

12

3D3V_S0

C

VDDA

PD#

SCLK

X1

X2

12

C70

SCD1U10V2MX-1

8

14

50

46

26

37

32

19

1

PCLK_DEBUG_CK408

5

6

PCLK_FWH_CK408

CLKPCIF_ICH_CK408

7

10

11

PCLK_PCM_CK408

12

PCLK_MINI_CK408

13

16

PCLK_KBC_CK408

17

18

PCLK_SIO_CK408

21

CLK66_ICH_CK408

CLK66_GMCH_CK408

22

23

24

25

29

30

28

CK-408_X1

2

3

CK-408_X2

3D3V_S0

12

R271

DUMMY-R2

12

R275

10KR2

12

12

R284

DUMMY-R2

12

D

PLACE NEAR EACH PIN

12

C451

SCD1U10V2MX-1

12

R321 33R2

R320 33R2

R311 33R2

R315 33R2

R314 33R2

R313 33R2

R312 33R2

R319 33R2

R318 33R2

CK-408_SDA

CK-408_SCL

1 2

R281

10KR2

C51

SCD1U10V2MX-1

CLKGEN_APWR

C463

SCD1U10V2MX-1

Filtering CKT for

48MHz power plane

12

C380

SC10U10V5ZY

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

C424

1 2

SC10P50V2JN-1

X3

X-14D318MHZ-1-U

C414

1 2

SC10P50V2JN-1

CK-408_FS1

CK-408_FS0

C69

SCD01U16V2KX

Title

Size Document Number Rev

Date: Sheet

12

C48

SCD1U10V2MX-1

12

CLKGEN_48MPWR

C36

SCD01U50V3KX

CLOCK GEN.

A3

12

C50

SCD1U10V2MX-1

L9

1 2

MLB-201209-18

C466

SC10U10V5ZY

12

C49

SCD1U10V2MX-1

PCLK_DEBUGBD 28

PCLK_FWH 28

CLKPCIF_ICH 15

PCLK_PCM 18

PCLK_MINI 21

PCLK_KBC 27

PCLK_SIO 29

CLK66_ICH 14

CLK66_GMCH 7

PM_SLP_S1# 15

CLK_PWRGD# 32

A1+

L11

1 2

MLB-201209-19

12

C452

SCD1U10V2MX-1

3D3V_S0

3D3V_S0

L6

1 2

MLB-201209-18

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

12

339Thursday, June 19, 2003

E

C30

SCD1U16V

of

3D3V_S0

-1

FS1 FS0 CPU AGP PCI

0 0 100.00 66.66 33.33

0 1 133.33 66.66 33.33

1 0 200.00 66.66 33.33

4 4

CLK_ITP_CPU4

CLK_ITP_CPU#4

CLK_MCH6

CLK_MCH#6

3D3V_S0

12

1

2N7002

D

A

CLK_CPU4

CLK_CPU#4

R61

1 2

DUMMY-0R2-0

R371

10KR2

SMB_CLK_EN

G

23

S

Q38

2N7002

D

1

3 3

CK_PWRSAVE#29

2 2

SMBC_ICH13,15

SMBD_ICH13,15

1 1

Q35

1 1 166.66 66.66 33.33

R268 0R2-0

1 2

R243 42D2R3F

1 2

R242 42D2R3F

1 2

R267 0R2-0

1 2

R266 0R2-0

1 2

R241 42D2R3F

1 2

R240 42D2R3F

1 2

R265 0R2-0

1 2

R264 10R2

1 2

R239 42D2R3F

1 2

R238 42D2R3F

1 2

R263 10R2

1 2

SC-3-1

3D3V_S0

12

3D3V_S0

3

2

G

23

S

1 4

R62

10KR2

RN5

SRN10KJ

CLK48_ICH14

CLK48_DREF7

DREFSSCLK7

PM_STPCPU#15

PM_STPPCI#15

CLK14_ICH15

CLK14_SIO29

CK-408_SCL

CK-408_SDA

CLK_ITP_R

CLK_ITP#_R

CLK_MCH_R

CLK_MCH#_R

CLK_CPU#_R

CK-408_FS1

CK-408_FS0

R280

R279

R282

R289 33R2

1 2

R65 33R2

1 2

CK-408_SCL 9

CK-408_SDA 9

B

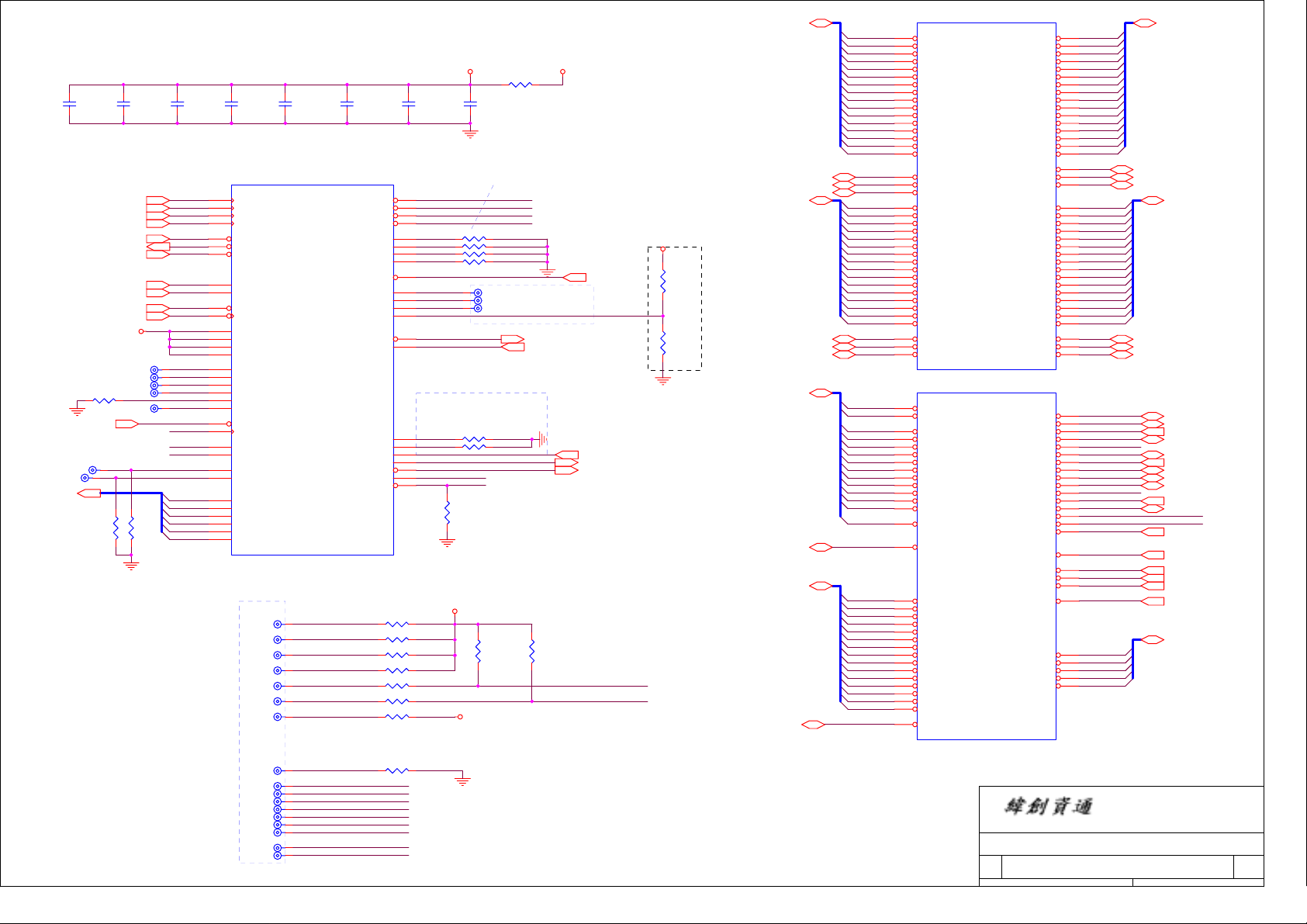

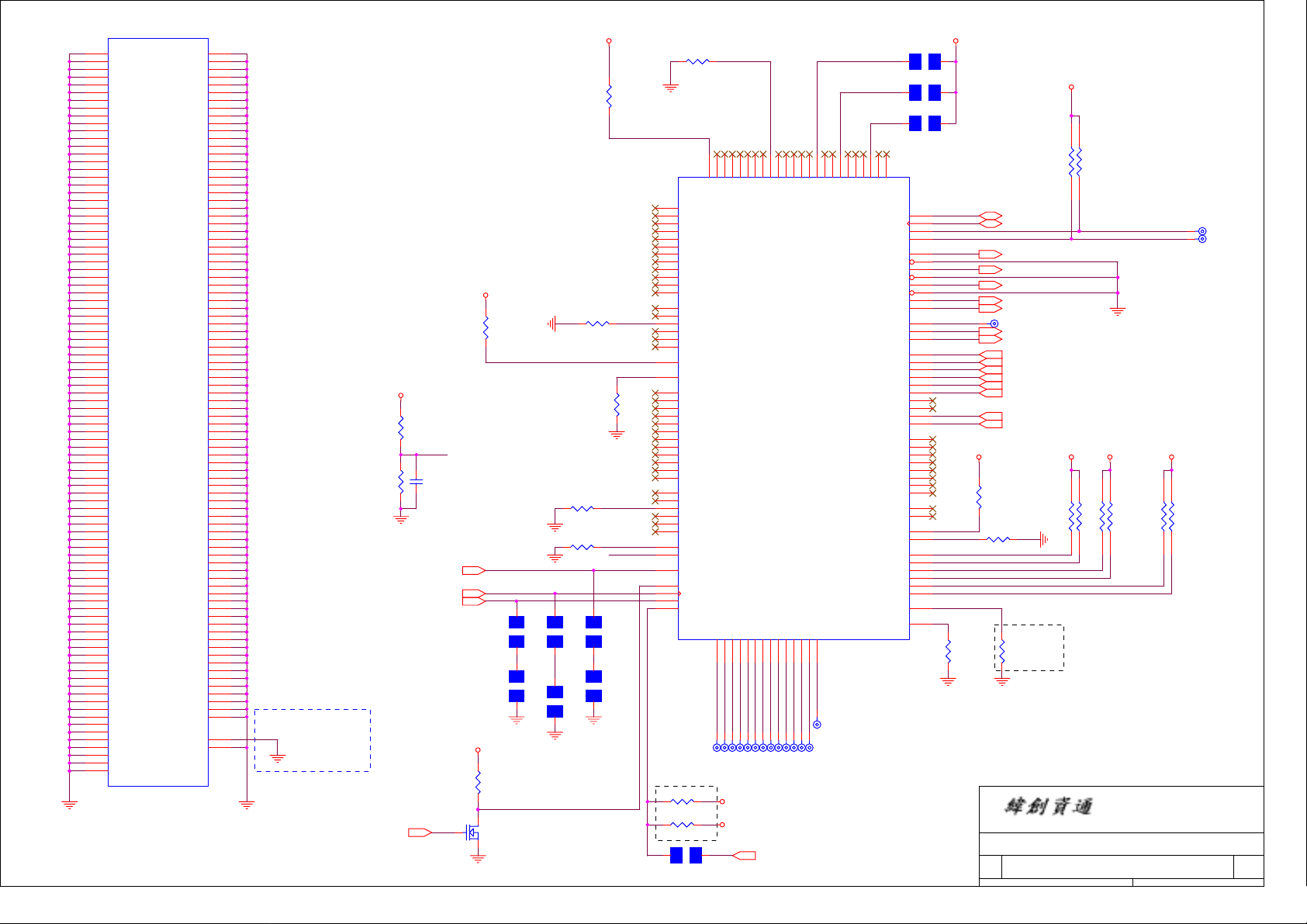

Page 4

12

C441

SC10U6D3V5MX

CLK_ITP_CPU#3

R223

1KR2

1 2

CC_CPUSLP#15

TP71

TP74

H_VID[5:0]32

R56

54D9R3F

Place these two

resistors near pin

AE7,AF6

CLK_CPU3

CLK_CPU#3

CLK_ITP_CPU3

CC_A20M#15

CC_FERR#15

CC_IGNNE#15

CC_INTR15

CC_NMI15

CC_SMI#15

CC_STPCLK#15

CPU_VCCA

12

12

C442

SC10U6D3V5MX

TP78

TP72

TP58

TP77

TP79

12

R50

54D9R3F

12

C292

SC10U6D3V5MX

CC_RSVD1

CC_RSVD2

CC_RSVD3

CC_RSVD4

TEST3

CC_RSVD5

H_TCK

H_TDI

H_TDO

VCCSENSE

VSSSENSE

H_VID5

H_VID4

H_VID3

H_VID2

H_VID1

H_VID0

For CPU VCCA[0:3] PLL

place one 0.01u & 10u for

each VCCA pin

AC26

B15

B14

A16

A15

F26

AF7

C14

C16

A13

C12

A12

AE7

AF6

C2

D3

A3

D1

D4

B4

C6

N1

B1

B2

C3

E1

A6

H4

G4

G3

F3

F2

E2

12

C289

SC10U6D3V5MX

CPU1D

BCLK0

BCLK1

ITP_CLK0

ITP_CLK1

A20M#

FERR#

IGNNE#

LINT0

LINT1

SMI#

STPCLK#

VCCA3

VCCA2

VCCA1

VCCA0

RSVD

RSVD

RSVD

RSVD

TEST3

PSI#

SLP#

TCK

TDI

TDO

VCCSENSE

VSSSENSE

VID5

VID4

VID3

VID2

VID1

VID0

BANIAS-900MHZ

C435

SCD01U16V2KX

THERMTRIP#

PLACE NEAR

TP75

GTL_IERR#

TP76

CC_CPUPWRGD

TP61

H_TDI

TP62

H_TMS

TP63

H_TDOITP

TP70 R277 22D6R3F

ITP_CPURST# GTL_CPURST#

TP73

ITP_DBRESET#

C436

SCD01U16V2KX

BPM3#

BPM2#

BPM1#

BPM0#

COMP3

COMP2

COMP1

COMP0

DPSLP#

RSVD

RSVD

RSVD

GTLREF

PROCHOT#

PWRGOOD

TEST1

TEST2

THERMDA

THERMDC

TMS

TRST#

R290 56R2J

1 2

R291 330R2

1 2

R254 150R2

1 2

R262 39D2R3F

1 2

R258 22D6R3F

1 2

1 2

R286 240R3

1 2

C464

SCD01U16V2KX

Layout note:

COMP0 and COMP2 need to be Zo=27.4ohm traces.

COMP1 and COMP3 should be routed asx Zo=55ohm,

traces shorter than 0.5".

H_BPM3_ITP#

C9

A9

H_BPM2_ITP#

B8

H_BPM1_ITP#

C8

H_BPM0_ITP#

COMP3

AB1

AB2

COMP2

P26

COMP1

P25

COMP0

B7

AC1

H_GTLREF3

G1

H_GTLREF2

H_GTLREF1

E26

AD26

B17

CC_PROCHOT#

CC_CPUPWRGD

E4

A1 stepping:No stuff

A0 stepping:stuff

C5

TEST1

F23

TEST2

B18

A18

C17

C11

B13

VCC_IO_S0

R307

1 2

0R3-U

C433

SCD01U16V2KX

R328 54D9R3F

1 2

R329 27D4R3F

1 2

R203 54D9R3F

1 2

R204 27D4R3F

1 2

TP81

PLACE NEAR H_GTLREF0

TP80

TP55

CC_PROCHOT# 17

CC_CPUPWRGD 15

R296

1 2

1 2

R208

12

DUMMY-1KR2

DUMMY-1KR2

H_TMS

H_TRST#

R235

680R2

Place within 2" to CPU

R237

54D9R3F

12

R245

54D9R3F

12

3D3V_S0

1D8V_S0CPU_VCCA

H_TDO

CC_DPSLP# 6,15,32

H_GTLREF0

THERMDP 17

THERMDN 17

PM_THERMTRIP# 15

VCC_IO_S0

12

R201

49D9R3F

Voltage divider placed

within 0.5" of CPU pin

via a Zo=55ohm trace.

12

R202

100R3F

SC-4-1

CPU1C

GTL_D#15

C25

E23

B23

C26

E24

D24

B24

C20

B20

A21

B26

A24

B21

A22

A25

A19

D25

C23

C22

K25

N25

H26

M25

N24

M23

G24

F25

H24

M26

G25

H23

K24

AA2

AA3

AF1

AE1

AF3

AD6

AE2

AD5

AC6

AB4

AD2

AE4

AD3

AC3

AC7

AC4

AF4

AE5

L26

J25

J23

L23

J26

L24

Y3

U1

Y1

Y4

W2

T4

W1

V2

R3

V3

U4

P4

U3

D15#

D14#

D13#

D12#

D11#

D10#

D9#

D8#

D7#

D6#

D5#

D4#

D3#

D2#

D1#

D0#

DINV0#

DSTBN0#

DSTBP0#

D31#

D30#

D29#

D28#

D27#

D26#

D25#

D24#

D23#

D22#

D21#

D20#

D19#

D18#

D17#

D16#

DINV1#

DSTBN1#

DSTBP1#

BANIAS-900MHZ

CPU1B

A16#

A15#

A14#

A13#

A12#

A11#

A10#

A9#

A8#

A7#

A6#

A5#

A4#

A3#

ADSTB0#

A31#

A30#

A29#

A28#

A27#

A26#

A25#

A24#

A23#

A22#

A21#

A20#

A19#

A18#

A17#

ADSTB1#

DINV2#

DSTBN2#

DSTBP2#

DINV3#

DSTBN3#

DSTBP3#

DBSY#

DEFER#

DRDY#

IERR#

LOCK#

PRDY#

PREQ#

RESET#

TRDY#

DPWR#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

GTL_D#14

GTL_D#13

GTL_D#12

GTL_D#11

GTL_D#10

GTL_D#9

GTL_D#8

GTL_D#7

GTL_D#6

GTL_D#5

GTL_D#4

GTL_D#3

GTL_D#2

GTL_D#1

GTL_D#0

GTL_DINV#06

GTL_DSTBN#06

GTL_DSTBP#06

GTL_D#[31..16]6 GTL_D#[63..48] 6

GTL_DINV#16

GTL_DSTBN#16

GTL_DSTBP#16

GTL_A#[16..3]6

GTL_ADSTB#06

GTL_A#[31..17]6

GTL_ADSTB#16

GTL_D#31

GTL_D#30

GTL_D#29

GTL_D#28

GTL_D#27

GTL_D#26

GTL_D#25

GTL_D#24

GTL_D#23

GTL_D#22

GTL_D#21

GTL_D#20

GTL_D#19

GTL_D#18

GTL_D#17

GTL_D#16

GTL_A#16

GTL_A#15

GTL_A#14

GTL_A#13

GTL_A#12

GTL_A#11

GTL_A#10

GTL_A#9

GTL_A#8

GTL_A#7

GTL_A#6

GTL_A#5

GTL_A#4

GTL_A#3

GTL_A#31

GTL_A#30

GTL_A#29

GTL_A#28

GTL_A#27

GTL_A#26

GTL_A#25

GTL_A#24

GTL_A#23

GTL_A#22

GTL_A#21

GTL_A#20

GTL_A#19

GTL_A#18

GTL_A#17

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

D39#

D38#

D37#

D36#

D35#

D34#

D33#

D32#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

D52#

D51#

D50#

D49#

D48#

ADS#

BNR#

BPRI#

BR0#

DBR#

HIT#

HITM#

INIT#

RS2#

RS1#

RS0#

Y25

AA26

Y23

V26

U25

V24

U26

AA23

R23

R26

R24

V23

U23

T25

AA24

Y26

T24

W25

W24

AF26

AF22

AF25

AD21

AE21

AF20

AD24

AF23

AE22

AD23

AC25

AC22

AC20

AB24

AC23

AB25

AD20

AE24

AE25

N2

L1

J3

N4

A7

M2

L4

H2

K3

K4

A4

B5

J2

A10

B10

B11

M3

L2

K1

H1

C19

T1

P1

T2

P3

R2

GTL_D#47

GTL_D#46

GTL_D#45

GTL_D#44

GTL_D#43

GTL_D#42

GTL_D#41

GTL_D#40

GTL_D#39

GTL_D#38

GTL_D#37

GTL_D#36

GTL_D#35

GTL_D#34

GTL_D#33

GTL_D#32

GTL_D#63

GTL_D#62

GTL_D#61

GTL_D#60

GTL_D#59

GTL_D#58

GTL_D#57

GTL_D#56

GTL_D#55

GTL_D#54

GTL_D#53

GTL_D#52

GTL_D#51

GTL_D#50

GTL_D#49

GTL_D#48

ITP_DBRESET#

GTL_IERR#

H_BPM4_PRDY#

H_BPM5_PREQ#

GTL_CPURST#

GTL_REQ#4

GTL_REQ#3

GTL_REQ#2

GTL_REQ#1

GTL_REQ#0

GTL_D#[47..32] 6GTL_D#[15..0]6

GTL_DINV#2 6

GTL_DSTBN#2 6

GTL_DSTBP#2 6

GTL_DINV#3 6

GTL_DSTBN#3 6

GTL_DSTBP#3 6

GTL_ADS# 6

GTL_BNR# 6

GTL_BPRI# 6

GTL_BR0# 6

GTL_DBSY# 6

GTL_DEFER# 6

GTL_DRDY# 6

GTL_HIT# 6

GTL_HITM# 6

CC_INIT# 15,28

GTL_LOCK# 6

GTL_CPURST# 6

GTL_TRDY# 6

GTL_RS#2 6

GTL_RS#1 6

GTL_RS#0 6

GTL_DPWR# 6

GTL_REQ#[0..4] 6

TP59

TP60

TP65

TP67

TP68

TP69

TP66

TP64

TP56

TP57

H_TCK

R249 27D4R3F

1 2

H_TRST#

H_BPM3_ITP#

H_BPM2_ITP#

H_BPM1_ITP#

H_BPM0_ITP#

H_BPM4_PRDY#

H_BPM5_PREQ#

CLK_ITP_CPU

CLK_ITP_CPU#

BANIAS-900MHZ

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

Banias CPU (1/2)

Size Document Number Rev

A3

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

A1+

439Thursday, June 19, 2003

-1

Page 5

CPU1A

C21

VSS

VSS

C24

BANIAS-900MHZ

C10

C13

C15

C18

VSS

VSS

VSS

VSSD2VSSD5VSSD7VSSD9VSS

Ref 10598 EMTS

P69 need place

Decoupling

near between

VCCQ ???

VCC_CORE VCC_IO_S0

D18

D20

D22

E17

E19

E21

F18

F20

F22

G21

H22

J21

K22

V22

W21

Y22

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AB6

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC9

AC11

AC13

AC15

AC17

AC19

AD8

AD10

AD12

AD14

AD16

AD18

AE9

AE11

AE13

AE15

AE17

AE19

AF8

AF10

AF12

AF14

AF16

AF18

D10

D12

D14

D16

E11

E13

E15

F10

F12

F14

F16

L21

M22

N21

P22

R21

T22

U21

P23

AD9

VSS

AD11

VCCPT6VCCP

VSS

VSS

AD13

AD15

VCCP

VSS

AD17

VSS

AD19

W4

VCCQ0

VCCQ1

VSS

VSS

AD22

B25

VSS

VSS

VSS

VSSB3VSSB6VSSB9VSS

VSS

VSS

VSS

VSS

VSSC1VSSC4VSSC7VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSE3VSSE6VSSE8VSS

VSS

E10

D11

D13

D15

D17

D19

D21

D23

E12

D26

E14

VSS

VSS

VSS

VSS

E16

E18

VSS

VSS

E20

AD25

AE3

VSSA2VSSA5VSSA8VSS

VSS

VSS

VSS

VSS

VSSF1VSSF4VSSF5VSSF7VSSF9VSS

E22

E25

AE6

VSS

AE8

VSS

AE10

VSS

AE12

VSS

AE14

VSS

F11

AE16

VSS

VSS

F13

AE18

VSS

VSS

F15

AE20

VSS

VSS

F17

AE23

VSS

VSS

F19

AE26

VSS

VSS

F21

AF2

VSS

AF5

F24

VSS

VSS

AF9

VSS

AF11

AF13

VSS

VSS

VSSG6VSSG2VSS

G22

AF15

VSS

VSS

G23

AF17

VSS

VSS

G26

AF19

VSS

AF21

VSS

VSSH5VSSH3VSS

AF24

VSS

H21

VCCD6VCCD8VCC

VSS

VSSJ1VSSJ4VSSJ6VSS

H25

VCC

J22

VCC

VCCE5VCCE7VCCE9VCC

VSS

VSSK2VSSK5VSS

J24

K21

K23

VSS

VCC

VSS

K26

VCC

VCCF6VCCF8VCC

VSSL3VSSL6VSS

L22

VCC

VSS

VSSM1VSSM4VSSM5VSS

L25

VCC

VCCG5VCC

M21

VCCH6VCC

VSS

M24

VCCJ5VCC

VSSN3VSSN6VSS

N22

VCC

VSS

N23

VCCU5VCCV6VCC

VSS

VSSP2VSSP5VSS

N26

VCCW5VCC

P21

VCCY6VCC

VSS

VSSR1VSSR4VSSR6VSS

P24

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCPK6VCCPL5VCCP

VCCPM6VCCP

VCCPN5VCCP

VCCPP6VCCP

VCCPR5VCCP

VSS

VSST3VSST5VSS

VSS

VSS

VSSU2VSSU6VSS

VSS

VSSV1VSSV4VSSV5VSS

VSS

VSSW3VSSW6VSS

VSS

VSS

VSSY2VSSY5VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

T21

T23

T26

R22

R25

V21

V25

U22

U24

W22

W23

W26

Y21

Y24

AA1

AA4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB3

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

A11

A14

A17

A20

A23

A26

B12

B16

B19

B22

VCC_CORE

12

VCC_CORE

12

VCC_CORE

12

VCC_IO_S0

12

C310

SC10U6D3V5MX

C316

SC10U6D3V5MX

C25

SC10U6D3V5MX

C373

SCD1U10V2MX-1

10uF_6.3V *35 ,0805,X5R

12

C323

SC10U6D3V5MX

12

C313

SC10U6D3V5MX

12

C26

SC10U6D3V5MX

12

C318

SC10U6D3V5MX

12

C332

SC10U6D3V5MX

12

C35

SC10U6D3V5MX

0.1uF_10V * 10

12

12

C363

SCD1U10V2MX-1

12

C350

SCD1U10V2MX-1

C338

SCD1U10V2MX-1

Place near CPU

12

C320

SC10U6D3V5MX

12

C331

SC10U6D3V5MX

12

C381

SC10U6D3V5MX

12

C406

SCD1U10V2MX-1

12

C311

SC10U6D3V5MX

12

C322

SC10U6D3V5MX

12

C330

SC10U6D3V5MX

12

C401

SCD1U10V2MX-1

12

12

12

12

C400

SCD1U10V2MX-1

C382

SC10U6D3V5MX

C337

SC10U6D3V5MX

C329

SC10U6D3V5MX

12

12

C394

SC10U6D3V5MX

12

C376

SC10U6D3V5MX

12

C328

SC10U6D3V5MX

C315

SCD1U10V2MX-1

12

C312

SCD1U10V2MX-1

12

C410

SC10U6D3V5MX

12

C391

SC10U6D3V5MX

12

C333

SC10U6D3V5MX

12

12

C383

SC10U6D3V5MX

12

C378

SC10U6D3V5MX

12

C385

SC10U6D3V5MX

C308

SCD1U10V2MX-1

12

C396

SC10U6D3V5MX

12

C367

SC10U6D3V5MX

12

C386

SC10U6D3V5MX

12

C402

SC10U6D3V5MX

12

C353

SC10U6D3V5MX

12

C387

SC10U6D3V5MX

12

C388

SC10U6D3V5MX

12

C403

SC10U6D3V5MX

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

Banias CPU (2/2)

Size Document Number Rev

A3

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

A1+

539Wednesday, July 09, 2003

-1

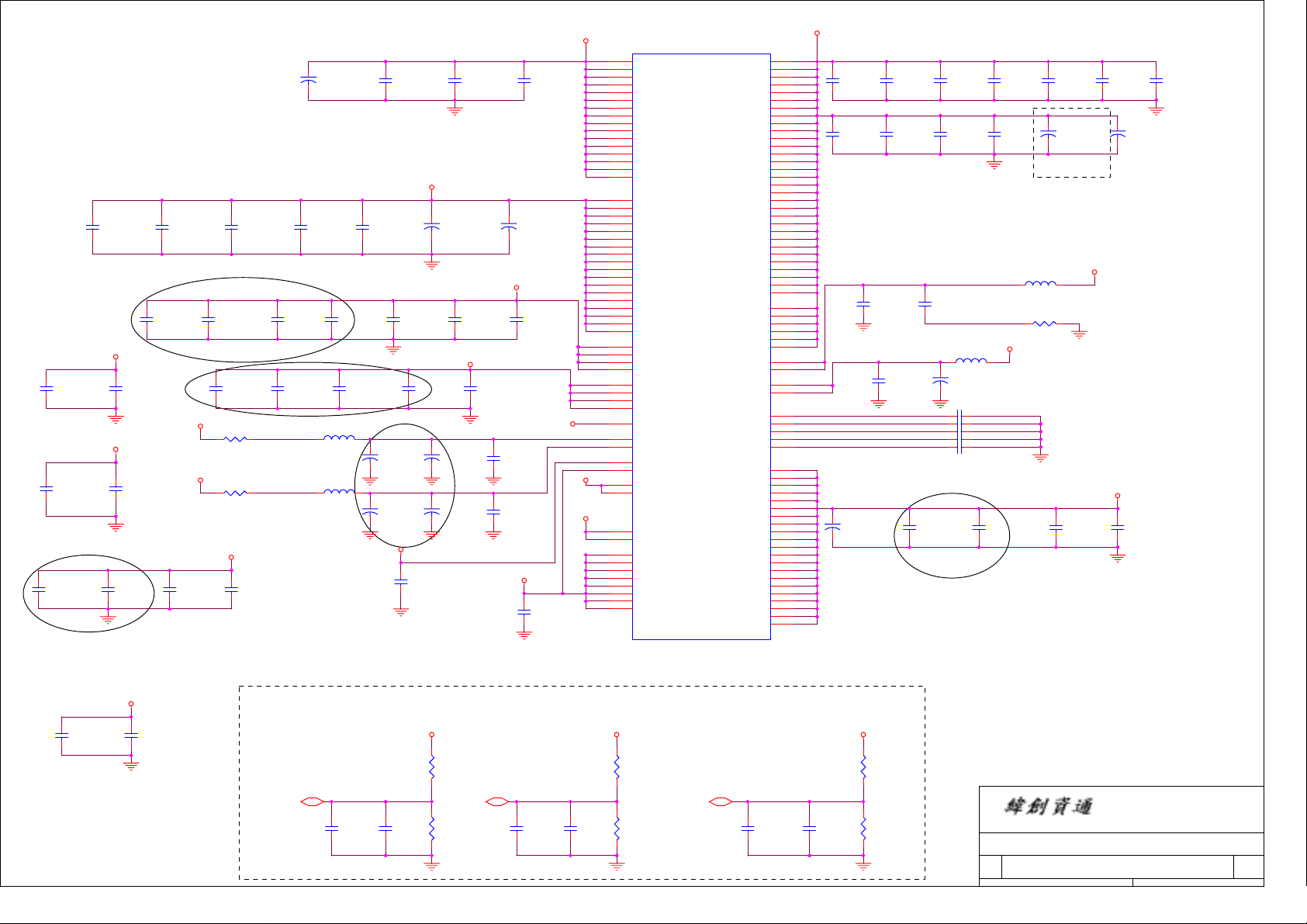

Page 6

GMCH

CPURST#

(GTL_CPURST#)

1D5V_S0

12

C582

SCD1U10V2MX-1

12

C583

SCD1U10V2MX-1

VCC_IO_S0

12

R107

301R3F

12

R103

150R3F

VCC_IO_S0

12

R359

301R3F

12

R363

150R3F

CPU

ITP

12

R406

226R3F

12

R407

147R3F

Close to pin

12

R408

113R3F

Close to pin

HYSWING

12

C85

SCD1U10V2MX-1

HXSWING

12

C514

SCD1U10V2MX-1

HXRCOMP,HYRCOMP as 18mil

wide trace

GTL_A#[31:3]4

PSWING

800 mV +/-8%

C581

SCD01U16V2KX

HLVREF

350 mV +/-8%

C584

SCD01U16V2KX

GTL_ADSTB#04

GTL_ADSTB#14

GTL_REQ#[4:0]4

CLK_MCH3

CLK_MCH#3

GTL_ADS#4

GTL_DRDY#4

GTL_DEFER#4

GTL_TRDY#4

GTL_RS#04

GTL_RS#14

GTL_RS#24

PCIRST1#13,16,18

GTL_BR0#4

GTL_BNR#4

GTL_BPRI#4

GTL_DBSY#4

GTL_HITM#4

GTL_HIT#4

GTL_LOCK#4

CC_DPSLP#4,15,32

GTL_CPURST#4

PWROK15,17

GTL_DPWR#4

HL_[10:0]14

HL_STB14

HL_STB#14

1D2V_S0

R106 27D4R3F

1 2

R356 27D4R3F

1 2

R116

1 2

GTL_A#4

GTL_A#5

GTL_A#6

GTL_A#7

GTL_A#8

GTL_A#9

GTL_A#10

GTL_A#11

GTL_A#12

GTL_A#13

GTL_A#14

GTL_A#15

GTL_A#16

GTL_A#17

GTL_A#18

GTL_A#19

GTL_A#20

GTL_A#21

GTL_A#22

GTL_A#23

GTL_A#24

GTL_A#25

GTL_A#26

GTL_A#27

GTL_A#28

GTL_A#29

GTL_A#30

GTL_A#31

GTL_REQ#0

GTL_REQ#1

GTL_REQ#2

GTL_REQ#3

GTL_REQ#4

HL_0

HL_1

HL_2

HL_3

HL_4

HL_5

HL_6

HL_7

HL_8

HL_9

HL_10

HLVREF

HLZCOMP

27D4R3F

HYRCOMP

HXRCOMP

PSWING

HYSWING

HXSWING

P23

R27

U23

U24

R24

U28

V28

U27

V27

U25

V26

V25

V23

W25

AA27

W24

W23

W27

AA28

W28

AB27

AB28

AA26

R28

P25

R23

R25

AE29

AD29

N24

M28

M25

N23

P26

M27

AD28

M23

N25

P28

M26

N28

N27

P27

AA22

H28

B20

K28

B18

T25

T28

T27

Y24

Y25

Y27

Y26

T26

T23

L28

Y23

F15

J11

U7

U4

U3

V3

W2

W6

V6

W7

T3

V5

V4

W3

V2

W1

T2

U2

F7

HA[3]#

HA[4]#

HA[5]#

HA[6]#

HA[7]#

HA[8]#

HA[9]#

HA[10]#

HA[11]#

HA[12]#

HA[13]#

HA[14]#

HA[15]#

HA[16]#

HA[17]#

HA[18]#

HA[19]#

HA[20]#

HA[21]#

HA[22]#

HA[23]#

HA[24]#

HA[25]#

HA[26]#

HA[27]#

HA[28]#

HA[29]#

HA[30]#

HA[31]#

HADSTB[0]#

HADSTB[1]#

HREQ[0]#

HREQ[1]#

HREQ[2]#

HREQ[3]#

HREQ[4]#

BCLK

BCLK#

ADS#

DRDY#

DEFER#

HTRDY#

RS[0]#

RS[1]#

RS[2]#

RSTIN#

BREQ0#

BNR#

BPRI#

DBSY#

HITM#

HIT#

HLOCK#

DPSLP#

CPURST#

PWROK

DPWR#

HL[0]

HL[1]

HL[2]

HL[3]

HL[4]

HL[5]

HL[6]

HL[7]

HL[8]

HL[9]

HL[10]

HLSTB

HLSTB#

HLVREF

HLZCOMP

HYRCOMP

HXRCOMP

PSWING

HYSWING

HXSWING

AGPBUSY#

U11C

HOST

HUB LINK

MONTARA-GM

HD[0]#

HD[1]#

HD[2]#

HD[3]#

HD[4]#

HD[5]#

HD[6]#

HD[7]#

HD[8]#

HD[9]#

HD[10]#

HD[11]#

HD[12]#

HD[13]#

HD[14]#

HD[15]#

HDSTBP[0]#

HDSTBN[0]#

DINV[0]#

HD[16]#

HD[17]#

HD[18]#

HD[19]#

HD[20]#

HD[21]#

HD[22]#

HD[23]#

HD[24]#

HD[25]#

HD[26]#

HD[27]#

HD[28]#

HD[29]#

HD[30]#

HD[31]#

HDSTBP[1]#

HDSTBN[1]#

DINV[1]#

HD[32]#

HD[33]#

HD[34]#

HD[35]#

HD[36]#

HD[37]#

HD[38]#

HD[39]#

HD[40]#

HD[41]#

HD[42]#

HD[43]#

HD[44]#

HD[45]#

HD[46]#

HD[47]#

HDSTBP[2]#

HDSTBN[2]#

DINV[2]#

HD[48]#

HD[49]#

HD[50]#

HD[51]#

HD[52]#

HD[53]#

HD[54]#

HD[55]#

HD[56]#

HD[57]#

HD[58]#

HD[59]#

HD[60]#

HD[61]#

HD[62]#

HD[63]#

HDSTBP[3]#

HDSTBN[3]#

DINV[3]#

HDVREF[0]

HDVREF[1]

HDVREF[2]

HAVREF

HCCVREF

K22

H27

K25

L24

J27

G28

L27

L23

L25

J24

H25

K23

G27

K26

J23

H26

K27

J28

J25

F25

F26

B27

H23

E27

G25

F28

D27

G24

C28

B26

G22

C26

E26

G23

B28

D26

C27

E25

B21

G21

C24

C23

D22

C25

E24

D24

G20

E23

B22

B23

F23

F21

C20

C21

E21

E22

B25

G18

E19

E20

G17

D20

F19

C19

C17

F17

B19

G16

E16

C16

E17

D16

C18

E18

D18

G19

K21

J21

J17

Y22

Y28

GTL_D#0GTL_A#3

GTL_D#1

GTL_D#2

GTL_D#3

GTL_D#4

GTL_D#5

GTL_D#6

GTL_D#7

GTL_D#8

GTL_D#9

GTL_D#10

GTL_D#11

GTL_D#12

GTL_D#13

GTL_D#14

GTL_D#15

GTL_D#16

GTL_D#17

GTL_D#18

GTL_D#19

GTL_D#20

GTL_D#21

GTL_D#22

GTL_D#23

GTL_D#24

GTL_D#25

GTL_D#26

GTL_D#27

GTL_D#28

GTL_D#29

GTL_D#30

GTL_D#31

GTL_D#32

GTL_D#33

GTL_D#34

GTL_D#35

GTL_D#36

GTL_D#37

GTL_D#38

GTL_D#39

GTL_D#40

GTL_D#41

GTL_D#42

GTL_D#43

GTL_D#44

GTL_D#45

GTL_D#46

GTL_D#47

GTL_D#48

GTL_D#49

GTL_D#50

GTL_D#51

GTL_D#52

GTL_D#53

GTL_D#54

GTL_D#55

GTL_D#56

GTL_D#57

GTL_D#58

GTL_D#59

GTL_D#60

GTL_D#61

GTL_D#62

GTL_D#63

HDVREF

HAVREF

HCCVREF

GTL_D#[63..0] 4

GTL_DSTBP#0 4

GTL_DSTBN#0 4

GTL_DINV#0 4

GTL_DSTBP#1 4

GTL_DSTBN#1 4

GTL_DINV#1 4

GTL_DSTBP#2 4

GTL_DSTBN#2 4

GTL_DINV#2 4

GTL_DSTBP#3 4

GTL_DSTBN#3 4

GTL_DINV#3 4

HDVREF 8

HAVREF 8

HCCVREF 8AGPBUSY#15

R109

604R3F

R108

150R3F

R111

150R3F

R110

604R3F

M_A[12..0]9,10

2D5V_S3

12

12

2D5V_S3

12

12

M_AB19,10

M_AB29,10

M_AB49,10

M_AB59,10

M_WE#9,10

M_CAS#9,10

M_RAS#9,10

M_BS0#9,10

M_BS1#9,10

M_CS0_R#9,10

M_CS1_R#9,10

M_CS2_R#9,10

M_CS3_R#9,10

M_CKE0_R#9,10

M_CKE1_R#9,10

M_CKE2_R#9,10

M_CKE3_R#9,10

CLK_DDR09

CLK_DDR0#9

CLK_DDR19

CLK_DDR1#9

CLK_DDR29

CLK_DDR2#9

CLK_DDR39

CLK_DDR3#9

CLK_DDR49

CLK_DDR4#9

CLK_DDR59

CLK_DDR5#9

SMVSWINGL

12

C100

SCD1U10V2MX-1

12

C103

SCD1U10V2MX-1

SMVSWINGH

M_A0

M_A1

M_A2

M_A3

M_A4

M_A5

M_A6

M_A7

M_A8

M_A9

M_A10

M_A11

M_A12

M_DQS7

M_DM7

M_DATA56

M_DATA57

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

M_DQS8

M_DM8

M_DATA64

M_DATA65

M_DATA66

M_DATA67

M_DATA68

M_DATA69

M_DATA70

M_DATA71

AC18

AD14

AD13

AD17

AD11

AC13

AD8

AD7

AC6

AC5

AC19

AD5

AB5

AD16

AC12

AF11

AD10

AD25

AC24

AC21

AD22

AD20

AD23

AD26

AC22

AC25

AC7

AB7

AC9

AC10

AB2

AA2

AC26

AB25

AC3

AD4

AC2

AD2

AB23

AB24

AA3

AB4

AH27

AH28

AH26

AE26

AG28

AF28

AG26

AF26

AE27

AD27

AD15

AH15

AG14

AE14

AE17

AG16

AH14

AE15

AF16

AF17

AJ22

AJ19

U11A

SMA[0]

SMA[1]

SMA[2]

SMA[3]

SMA[4]

SMA[5]

SMA[6]

SMA[7]

SMA[8]

SMA[9]

SMA[10]

SMA[11]

SMA[12]

SMAB[1]

SMAB[2]

SMAB[4]

SMAB[5]

SWE#

SCAS#

SRAS#

SBA[0]

SBA[1]

SCS[0]#

SCS[1]#

SCS[2]#

SCS[3]#

SCKE[0]

SCKE[1]

SCKE[2]

SCKE[3]

SCK[0]

SCK[0]#

SCK[1]

SCK[1]#

SCK[2]

SCK[2]#

SCK[3]

SCK[3]#

SCK[4]

SCK[4]#

SCK[5]

SCK[5]#

SDQS[7]

SDM[7]

SDQ[56]

SDQ[57]

SDQ[58]

SDQ[59]

SDQ[60]

SDQ[61]

SDQ[62]

SDQ[63]

SDQS[8]

SDM[8]

SDQ[64]

SDQ[65]

SDQ[66]

SDQ[67]

SDQ[68]

SDQ[69]

SDQ[70]

SDQ[71]

SMVSWINGL

SMVSWINGH

MONTARA-GM

DDR

MEMORY

Title

Size Document Number Rev

Date: Sheet of

AG2

AE5

AF2

AE3

AF4

AH2

AD3

AE2

AG4

AH3

AH5

AE6

AD6

AG5

AG7

AE8

AF5

AH4

AF7

AH6

AH8

AE9

AF8

AG8

AH9

AG10

AH7

AD9

AF10

AE11

AE12

AH12

AH10

AH11

AG13

AF14

AG11

AD12

AF13

AH13

AH17

AD19

AH16

AG17

AF19

AE20

AD18

AE18

AH18

AG19

AE21

AD21

AH20

AG20

AF22

AH22

AF20

AH19

AH21

AG22

AH24

AD24

AE23

AH23

AE24

AH25

AG23

AF23

AF25

AG25

AB1

AJ24

M_DQS0

M_DM0

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA5

M_DATA6

M_DATA7

M_DQS1

M_DM1

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DQS2

M_DM2

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DQS3

M_DM3

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_DQS4

M_DM4

M_DATA32

M_DATA33

M_DATA34

M_DATA35

M_DATA36

M_DATA37

M_DATA38

M_DATA39

M_DQS5

M_DM5

M_DATA40

M_DATA41

M_DATA42

M_DATA43

M_DATA44

M_DATA45

M_DATA46

M_DATA47

M_DQS6

M_DM6

M_DATA48

M_DATA49

M_DATA50

M_DATA51

M_DATA52

M_DATA53

M_DATA54

M_DATA55

SMRCOMP

SDQS[0]

SDM[0]

SDQ[0]

SDQ[1]

SDQ[2]

SDQ[3]

SDQ[4]

SDQ[5]

SDQ[6]

SDQ[7]

SDQS[1]

SDM[1]

SDQ[8]

SDQ[9]

SDQ[10]

SDQ[11]

SDQ[12]

SDQ[13]

SDQ[14]

SDQ[15]

SDQS[2]

SDM[2]

SDQ[16]

SDQ[17]

SDQ[18]

SDQ[19]

SDQ[20]

SDQ[21]

SDQ[22]

SDQ[23]

SDQS[3]

SDM[3]

SDQ[24]

SDQ[25]

SDQ[26]

SDQ[27]

SDQ[28]

SDQ[29]

SDQ[30]

SDQ[31]

SDQS[4]

SDM[4]

SDQ[32]

SDQ[33]

SDQ[34]

SDQ[35]

SDQ[36]

SDQ[37]

SDQ[38]

SDQ[39]

SDQS[5]

SDM[5]

SDQ[40]

SDQ[41]

SDQ[42]

SDQ[43]

SDQ[44]

SDQ[45]

SDQ[46]

SDQ[47]

SDQS[6]

SDM[6]

SDQ[48]

SDQ[49]

SDQ[50]

SDQ[51]

SDQ[52]

SDQ[53]

SDQ[54]

SDQ[55]

SMRCOMP

SMVREF_0

op buffer build-in

to SC1486.

Montara (1/3)

A3

M_DATA[71..0] 10

M_DQS[8..0] 10

M_DM[8..0] 10

2D5V_S3

SMRCOMP

12

C135

SCD1U10V2MX-1

DDRVREF 9

12

C98

SCD1U10V2MX-1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

A1+

639Wednesday, July 09, 2003

12

12

R119

60D4R3F

R117

60D4R3F

-1

Page 7

AA29

W29

U29

N29

G29

E29

C29

AE28

AC28

E28

D28

AJ27

AG27

AC27

F27

A27

AJ26

AB26

W26

U26

R26

N26

G26

AE25

AA25

D25

A25

AG24

AA24

V24

T24

P24

M24

K24

H24

F24

B24

AJ23

AC23

AA23

D23

A23

AE22

W22

U22

R22

N22

F22

C22

AG21

AB21

AA21

Y21

V21

T21

P21

M21

H21

D21

A21

AJ20

AC20

AA20

F20

AE19

AB19

H19

D19

A19

AJ18

AG18

AA18

F18

AC17

AB17

U17

R17

N17

H17

D17

A17

AE16

AA16

T16

P16

L29

J29

L26

J26

L22

J22

J20

J18

J16

U11E

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

MONTARA-GM

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSADAC

VSSALVDS

AE13

AB13

U13

R13

N13

H13

F13

D13

A13

AJ12

AG12

AA12

J12

AJ11

AC11

AB11

H11

F11

D11

AJ10

AE10

AA10

J10

C10

AG9

AB9

W9

U9

T9

R9

N9

L9

E9

AC8

Y8

V8

T8

P8

K8

H8

AJ7

AE7

AA7

R7

M7

J7

G7

E7

C7

AG6

Y6

L6

Y5

U5

B5

AE4

AC4

AA4

W4

T4

N4

K4

G4

D4

AJ3

AG3

R2

AJ1

AE1

AA1

U1

L1

G1

C1

F16

AG15

AB15

U15

R15

N15

H15

D15

AC14

AA14

T14

P14

J14

B8

B11

Need connect to cap

first then to GND

1D5V_S0

12

R376

1KR2

GMCH_RSVD0

1D5V_S0

12

R118

100KR2

1D5V_S0

12

R404

1KR3F

GVREF

12

12

R115

C579

1KR3F

SCD1U10V2MX-1

CLK66_GMCH3

CLK48_DREF3

DREFSSCLK3

DUMMY-R2

1D5V_S0

PM_SUS_CLK15

1

G

R361

C511

DUMMY-C2

12

R374

1KR2

D

Q40

2N7002

S

2 3

12

DREFSSCLK_T

12

C562

1 2

R380

1 2

100KR2

R114

1 2

40D2R3F

12

R377DUMMY-R2

CLK48_DREF_T

12

DUMMY-C2

CLK48_DPMS

R389

100KR2

DVOBCINTR#

DVOBCCLKINT

12

DVOCFLDSTL

DVORCOMP

GVREF

12

R387

DUMMY-R2

CLK66_GMCH_T

12

C568

DUMMY-C2

DVOBFLDSTL

R390

100KR2

R3

R5

R6

R4

P6

P5

N5

P2

N2

N3

M1

M5

P3

P4

M2

T6

T5

L2

G2

M3

K5

K1

K3

K2

J6

J5

H2

H1

H3

H4

H6

G3

J3

J2

H5

K6

L5

L3

D1

F1

Y3

D5

B7

B17

D6

MONTARA-GM

EXTTS_0

R391

1 2

10KR2

R379

1 2

DUMMY-10KR2

R388

1 2

DUMMY-R2

R381

1KR2

1 2

U11B

RSVDL7RSVDE5RSVDF5RSVDE3RSVDE2RSVDG5RSVDF4RSVDG6RSVDF6RSVD

DVOBD[0]

DVOBD[1]

DVOBD[2]

DVOBD[3]

DVOBD[4]

DVOBD[5]

DVOBD[6]

DVOBD[7]

DVOBD[8]

DVOBD[9]

DVOBD[10]

DVOBD[11]

DVOBCLK

DVOBCLK#

DVOBFLDSTL

DVOBHSYNC

DVOBVSYNC

DVOBBLANK#

DVOBCINTR#

DVOBCCLKINT

DVOCD[0]

DVOCD[1]

DVOCD[2]

DVOCD[3]

DVOCD[4]

DVOCD[5]

DVOCD[6]

DVOCD[7]

DVOCD[8]

DVOCD[9]

DVOCD[10]

DVOCD[11]

DVOCCLK

DVOCCLK#

DVOCFLDSTL

DVOCHSYNC

DVOCVSYNC

DVOCBLANK#

DVORCOMP

GVREF

GCLKIN

DPMS

DREFCLK

DREFSSCLK

EXTTS_0

ADDID7 GST[0]

F12

D12

B12

AA5

RSVD

RSVD

RSVD

RSVDL4RSVDC4RSVDF3RSVDD3RSVDC3RSVDB3RSVDF2RSVDD2RSVDC2RSVDB2RSVD

DVOB CRT

VIDEO

LVDS

DVOC

NC

NC

NC

NC

NC

NC

NC

NCA2NC

NCB1NC

AJ4NCAJ2

B29NCA29

A28

AA9

AJ28

GMCH_NC8

GMCH_NC7

GMCH_NC6

GMCH_NC5

GMCH_NC4

TP6

TP2

TP86

TP16

TP17

PM_THRM# 15,17

AH1

AC16NCAC15

DDR Feedback(inside the package)

M_RCVI#

M_RCVO#

Route transitioned to buttom

side with vias near ball

GMCH_NC11

GMCH_NC10

GMCH_NC9

TP83

TP91

TP18

TP92

TP82

AJ29

GMCH_NC0

AH29

GMCH_NC1

TP5

GMCH_NC3

GMCH_NC2

TP1

TP4

TP3

3D3V_S0

2D5V_S3

SB-7-1

GST[1]

GST[2]

D7

DDCA_DATA

DDCA_CLK

DDCPDATA

DDCPCLK

RED

RED#

GREEN

GREEN#

BLUE

BLUE#

HSYNC

VSYNC

PANELBKLTCTL

PANELBKLTEN

PANELVDDEN

IYAP[0]

IYAM[0]

IYAP[1]

IYAM[1]

IYAP[2]

IYAM[2]

IYAP[3]

IYAM[3]

ICLKAP

ICLKAM

IYBP[0]

IYBM[0]

IYBP[1]

IYBM[1]

IYBP[2]

IYBM[2]

IYBP[3]

IYBM[3]

ICLKBM

ICLKBP

LCLKCTLA

LCLKCTLB

MDDCCLK

MDDCDATA

MDVICLK

MDVIDATA

MI2CCLK

MI2CDATA

REFSET

LIBG

1D5V_S0

R385 DUMMY-R2

1 2

R375

124R3F

RN62

SRN10KJ

RN67

SRN10KJ

3D3V_S0

3

2

1 4

1D5V_S0 1D5V_S0

1D5V_S0

3

2

1 4

DAT_DDC_EDID

CLK_DDC_EDID

3

RN66

SRN2D7KJ

2

1 4

R386 DUMMY-R2

1 2

R392 DUMMY-R2

1 2

S.B.

G9

B6

C5

B4

A7

A8

C8

D8

C9

D9

H10

J9

G8

BL_PWM

F8

A5

TXOUT0+

F14

G14

TXOUT0-

E14

TXOUT1+

E15

TXOUT1-

TXOUT2+

C14

TXOUT2-

C15

B13

C13

E13

TXCLK+

TXCLK-

D14

G12

H12

E11

E12

C11

C12

G10

G11

E10

F10

H9

DVODETECT

LCLKCTLB

C6

P7

MDDCCLK

T7

MDDCDATA

N7

MDVI_CLK

MDVI_DAT

M6

MI2CCLK

K7

N6

MI2CDATA

E8

LIBG

A10

3D3V_S0

12

1 2

R382 1KR2

REFSET

12

R368

1K5R3F

DAT_DDC1 12

CLK_DDC1 12

DAC_RED 12,39

DAC_GREEN 12,39

DAC_BLUE 12,39

DAC_HSYNC 12,39

DAC_VSYNC 12,39

TP87

BL_ON 13

LCDVDD_ON 13

TXOUT0+ 13

TXOUT0- 13

TXOUT1+ 13

TXOUT1- 13

TXOUT2+ 13

TXOUT2- 13

TXCLK+ 13

TXCLK- 13

R372

1KR2

12

SC-7-1

H/W STRAPPING

LCLKCTLB Hi > P4-m CPU , Lo > Banias CPU

Hi > non DVO , Lo > DVODVODETECT

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

Montara (2/3)

Size Document Number Rev

A3

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

A1+

TP89 TPAD30

TP90 TPAD30

3

RN65

SRN10KJ

2

1 4

739Wednesday, July 09, 2003

-1

Page 8

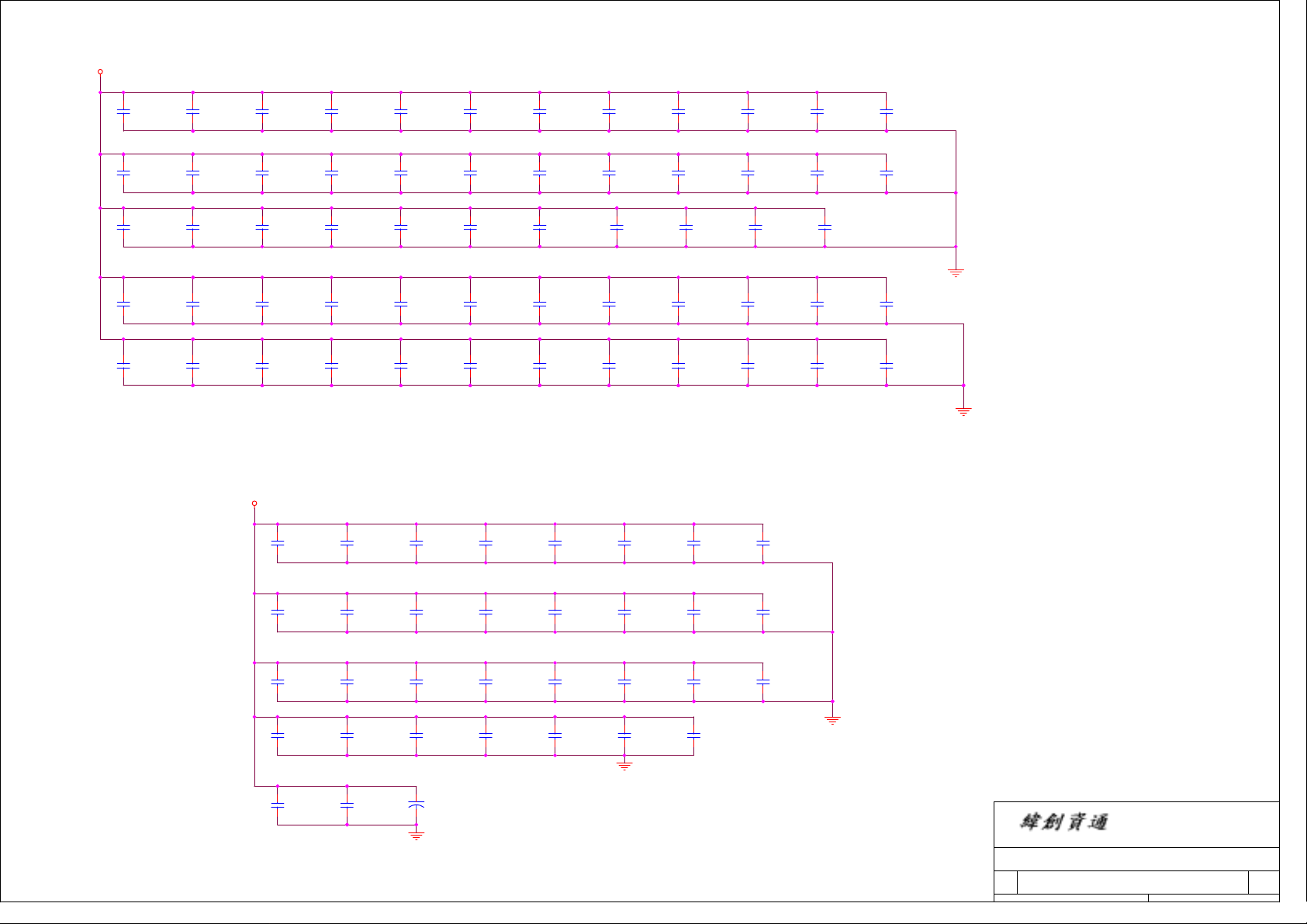

USE 4*4D7U TO REPLACE 2*10U

Caps for VCCALVDS

12

C544

SCD1U10V2MX-1

Caps for VCCGPIO

12

C585

SCD1U10V2MX-1

C522

SC4D7U10V-U

12

C538

SCD1U10V2MX-1

1D5V_S0

C539

SCD01U16V2KX

3D3V_S0

12

C133

SC10U6D3V5MX

Caps for VCCHL

C518

SC4D7U10V-U

12

C529

SCD1U10V2MX-1

C528

SC4D7U10V-U

1D2V_S0

1D2V_S0

12

C575

SCD1U10V2MX-1

12

C510

SCD1U10V2MX-1

C576

SC4D7U10V-U

C521

SC4D7U10V-U

R378

1R3

1 2

R366

1 2

1R3

1D2V_S0

12

C565

SCD1U10V2MX-1

C484

SC4D7U10V-U

C555

SC4D7U10V-U

VCCADPLLA

VCCADPLLB

The origional

total capacity is

2 * 220uF

12

TC5

ST47U4VBM

12

C512

SCD1U10V2MX-1

L26

1 2

IND-D1UH

L24

1 2

IND-D1UH

12

C139

SC10U6D3V5MX

12

C141

SC10U6D3V5MX

Caps for VCCTXLVDS

12

C537

SC4D7U10V-U

SCD1U10V2MX-1

Caps for VCCDLVDS

C547

SC4D7U10V-U

12

TC20

ST47U4VBM

12

TC18

ST47U4VBM

1D2V_S0

1D2V_S0

12

C545

C536

SC4D7U10V-U

12

12

12

C573

SCD1U10V2MX-1

Cap for

VCCAGPLL

12

C542

SCD1U10V2MX-1

TC22

ST47U6D3V-U1

12

C535

SCD1U10V2MX-1

1D5V_S0

TC21

ST47U4VBM

TC19

ST47U4VBM

12

2D5V_S3

12

C541

SCD1U10V2MX-1

12

C560

SCD1U10V2MX-1

12

C524

SCD1U10V2MX-1

1D2V_S0

12

C557

SCD1U10V2MX-1

TC6

ST150U6D3V-1-U

12

C548

SCD1U10V2MX-1

1D5V_S0

VCC_ADPLLA

VCC_ADPLLB

12

C558

SCD1U10V2MX-1

Cap for

VCCAHPLL

1D5V_S0

1D5V_S0

3D3V_S0

W21

AA19

AA17

U16

R16

N16

AA15

U14

R14

N14

H14

D10

G13

D29

T17

P17

T15

P15

T13

P13

A12

B10

B15

B14

A11

B16

P9

M9

K9

R8

N8

M8

L8

J8

H7

E6

M4

J4

E4

N1

J1

E1

J15

F9

J13

A6

Y2

B9

A9

A3

A4

V9

W8

U8

V7

U6

W5

Y1

V1

U11D

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCC

VCC

VCC

VCC

VCC

POWER

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCTXLVDS

VCCTXLVDS

VCCTXLVDS

VCCTXLVDS

VCCDLVDS

VCCDLVDS

VCCDLVDS

VCCDLVDS

VCCALVDS

VCCADPLLA

VCCADPLLB

VCCAGPLL

VCCAHPLL

VCCADAC

VCCADAC

VCCGPIO

VCCGPIO

VCCHL

VCCHL

VCCHL

VCCHL

VCCHL

VCCHL

VCCHL

VCCHL

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCQSM

VCCQSM

VCCASM

VCCASM

VTTHF

VTTHF

VTTHF

VTTHF

VTTHF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

MONTARA-GM

AG29

AF29

AC29

AF27

AJ25

AF24

AB22

AJ21

AF21

AB20

AF18

AB18

AJ17

AB16

AF15

AB14

AJ13

AA13

AF12

AB12

AA11

AB10

AJ9

AF9

Y9

AB8

AA8

Y7

AF6

AB6

AA6

AJ5

Y4

AF3

AB3

AG1

AC1

AJ8

AJ6

AF1

AD1

V29

M29

H29

A24

A22

AB29

Y29

K29

F29

A26

V22

T22

P22

M22

H22

U21

R21

N21

L21

H20

A20

J19

H18

A18

H16

G15

2D5V_S3

VTTHF_V29

VTTHF_M29

VTTHF_H29

VTTHF_A24

VTTHF_A22

12

C509

SCD1U10V2MX-1

12

C123

SCD1U10V2MX-1

VCC_QSM

12

12

TC2

ST150U6D3V-1-U

12

C551

SCD1U10V2MX-1

12

C129

SCD1U10V2MX-1

C126

SCD1U10V2MX-1

12

VCC_ASM

12

C138

SCD1U10V2MX-1

C483 SCD1U10V2MX-1

C86 SCD1U10V2MX-1

C84 SCD1U10V2MX-1

C494 SCD1U10V2MX-1

C501 SCD1U10V2MX-1

C505

SC4D7U10V-U

ESR<15mohm

12

C564

SCD1U10V2MX-1

12

C116

SCD1U10V2MX-1

C543

SC4D7U10V6KX

VSS_QSM

L14

1 2

IND-1UH-5

12

TC8

ST100U6D3V-U

1 2

1 2

1 2

1 2

1 2

12

C107

SCD1U10V2MX-1

12

C540

SCD1U10V2MX-1

L25

IND-D68UH-2

1 2

R373

1 2

1R3

1D2V_S0

C506

SC4D7U10V-U

12

C97

SCD1U10V2MX-1

12

TC17

ST150U6D3VM-U

SC-8-1

12

C525

SCD1U10V2MX-1

2D5V_S3

12

C488

SCD1U10V2MX-1

12

TC4

ST150U6D3V-1-U

VCC_IO_S0

12

C83

SCD1U10V2MX-1

12

C136

SCD1U10V2MX-1

C554

SCD1U10V2MX-1

1D5V_S0

C553

SCD01U16V2KX

Caps for VCCADAC

12

This two cap chould connect to

VSSADAC first then to GND

C480

SCD1U10V2MX-1

12

SC1U10V3KX

Reference Voltage: 2/3 Vcc_IO

VCC_IO_S0VCC_IO_S0VCC_IO_S0

12

C500

SCD1U10V2MX-1

12

12

R357

49D9R3F

R355

100R3F

HDVREF6HAVREF6HCCVREF6

HDVREFHAVREFHCCVREF

12

C515

SCD1U10V2MX-1

12

12

R339

49D9R3F

12

12

C482

R345

100R3F

12

C502

SC1U10V3KX

C504

SC1U10V3KX

12

12

R360

49D9R3F

R358

100R3F

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

Montara (3/3)

Size Document Number Rev

A3

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

A1+

839Wednesday, July 09, 2003

-1

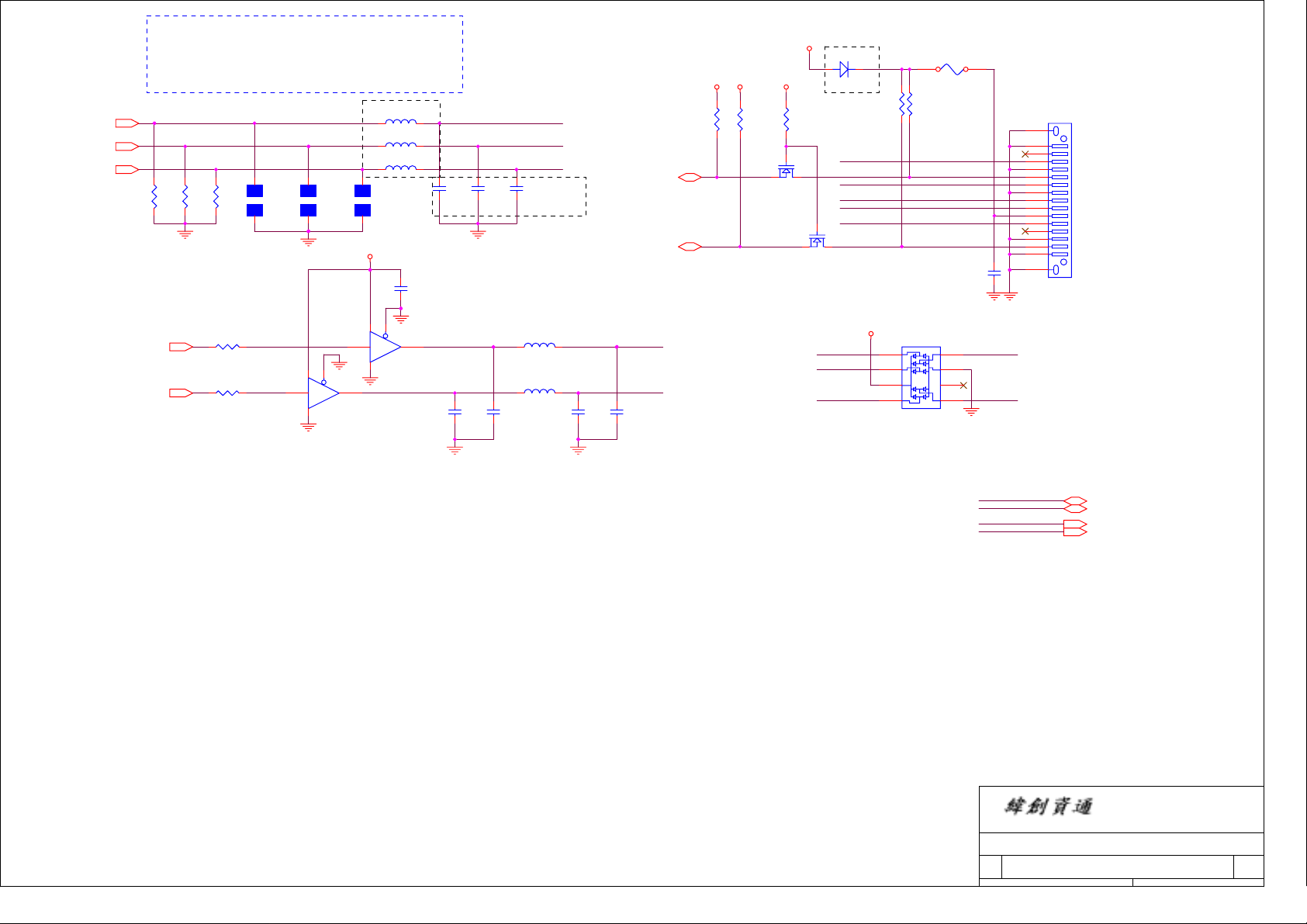

Page 9

M_RAS#6,10

M_CAS#6,10

M_WE#6,10

DDRVREF

SCD1U16V

C598

M_DATA_R_[71..0] 10

M_A_FR_[12..0] 10

M_BS1# 6,10

M_BS0# 6,10

M_A5 6,10

M_A0

DM1

A0

DDR-SODIMM-N-U1

M_A4 6,10

M_A2 6,10

M_A1 6,10

-1-9-1

TP8

TP9

TP7

DM0_RESET#

DM0_A13

DM0_BA2

M_DATA_R_71

12

3D3V_S0

197

120

1

2

VREF

VREF

VDDSPD

118

119

/WE

/CAS

/RAS

201

199

GND

VDDID

86

124NC123

200

85

97

98

84

NC

NC

NC/A13

NC/BA2

NC/(RESET#)

NC

CB7

M_DATA_R_65

M_DATA_R_68

M_DATA_R_66

M_DATA_R_69

M_DATA_R_70

M_DATA_R_67

73

79

83

74

80

CB2

CB3

CB472CB5

CB6

M_DATA_R_60

M_DATA_R_59

M_DATA_R_63

M_DATA_R_64

M_DATA_R_62

M_DATA_R_58

M_DATA_R_57

M_DATA_R_61

177

181

187

189

178

182

188

190

CB071CB1

DQ63

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

M_DATA_R_50

M_DATA_R_54

M_DATA_R_52

M_DATA_R_51

M_DATA_R_56

M_DATA_R_55

M_DATA_R_53

164

166

172

176

DQ56

DQ53

DQ54

DQ55

M_DATA_R_46

M_DATA_R_49

M_DATA_R_47

M_DATA_R_48

163

165

171

175

146

152

154

DQ48

DQ49

DQ50

DQ51

DQ46

DQ47

DQ52

M_DATA_R_39

M_DATA_R_43

M_DATA_R_45

M_DATA_R_40

M_DATA_R_41

M_DATA_R_44

153

142

DQ44

DQ45

M_DATA_R_37

M_DATA_R_42

M_DATA_R_38

141

145

151

130

136

140

DQ40

DQ41

DQ42

DQ43

DQ38

DQ39

M_DATA_R_31

M_DATA_R_28

M_DATA_R_34

M_DATA_R_29

M_DATA_R_33

M_DATA_R_30

M_DATA_R_35

M_DATA_R_32

M_DATA_R_36

67

127

129

135

139

60

66

68

128

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ2856DQ29

DQ30

DQ31

M_DATA_R_21

M_DATA_R_23

M_DATA_R_26

M_DATA_R_25

M_DATA_R_24

M_DATA_R_22

M_DATA_R_27

55

59

44

50

54

DQ24

DQ25

DQ2665DQ27

DQ22

DQ23

M_DATA_R_15

M_DATA_R_16

M_DATA_R_17

M_DATA_R_20

M_DATA_R_18

M_DATA_R_19

43

49

53

32

42

DQ1641DQ17

DQ18

DQ19

DQ20

DQ21

M_DATA_R_8

M_DATA_R_11

M_DATA_R_9

M_DATA_R_14

M_DATA_R_12

M_DATA_R_13

M_DATA_R_10

31

24

23

18

DQ819DQ9

DQ1029DQ11

DQ1220DQ13

DQ1430DQ15

M_DATA_R_1

M_DATA_R_6

M_DATA_R_2

M_DATA_R_7

M_DATA_R_4

M_DATA_R_5

M_DATA_R_3

M_DATA_R_0

5

7

13

17

8

DQ0

DQ1

DQ2

DQ3

DQ46DQ5

DQ614DQ7

M_A10

M_A6

M_A8

M_A11

M_A12

115

101

116

117

99

100

A12

A11

BA1

BA0

A10 / AP

M_A3

M_A9

M_A7

105

107

108

110

111

102

A9

A7

A8

112

106

109

A5

A4

A2

A1

A6

A3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

137

138

149

150

159

161

162

173

174

185

186

202

2D5V_S3 DDRVREF5V_S3

12

R423

SC-9-1

470R3F

1D25V_DDR_S3

12

R422

470R3F

U15

1

IN+

2

VSS

3

IN-

DUMMY-G1211X-U1

1 2

R421 0R3-U

M_RAS_FR#10

M_CAS_FR#10

M_WE_FR#10

DDRVREF6

SCD1U16V

VDD

OUT

C599

5

4

12

202

201

VSS

VSS

VSS

VSS

104

126

125

SC1U10V3ZY

SB-9-1

3D3V_S0

197

199

GND

VDDID

VDDSPD

VSS

VSS

GND

185

186

103

C160

2

VREF

VSS

174

1

173

VSS90VSS

88

VREF

VSS

162

VSS

VSS

VSS

52

124NC123

NC

VSS

137

VSS

NC

VSS

VSS

51

TP84

VSS

126

VSS

39

40

TP85

TP88

DM1_BA2

97

98

NC/BA2

VSS

104

125

VSS

DM1_A13

NC/A13

VSS

VSS

VSS

27

38

28

16

DM1_RESET#

M_DATA_R_71

86

85

84

NC

CB7

NC/(RESET#)

VSS

VSS

VSS90VSS

88

87

103

15

M_DATA_R_70

80

76

VSS

4

M_DATA_R_69

74

CB6

VSS

75

VSS

VSS

3

2D5V_S3

M_DATA_R_67

M_DATA_R_68

83

CB472CB5

VSS

VSS

64

63

CB3

VSS

VDD

VDD

VDD

180

179

191

192

M_DATA_R_65

M_DATA_R_66

M_DATA_R_64

73

79

CB071CB1

CB2

VSS

VSS

VSS

39

52

40

51

VSS

VSS

VSS

VSS

64

75

76

63

87

120

118

200

119

/WE

/CAS

/RAS

VSS

VSS

VSS

VSS

138

149

150

159

161

VSS

VSS

VDD

VSS

VDD

VDD

VDD

VDD

VDD

VDD

VDD

144

168

155

132

143

156

157

167

M_DATA_R_57

M_DATA_R_60

M_DATA_R_61

M_DATA_R_56

M_DATA_R_58

M_DATA_R_62

M_DATA_R_63

M_DATA_R_59

177

181

187

189

178

182

188

190

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

4

3

27

38

28

16

15

2D5V_S3

VDD

DQ56

VDD

VDD

VDD

VDD

VDD

VDD

VDD

92

94

81

82

93

113

114

131

M_DATA_R_54

M_DATA_R_53

M_DATA_R_51

M_DATA_R_52

M_DATA_R_55

M_DATA_R_50

M_DATA_R_49

M_DATA_R_48

163

165

171

175

164

166

172

176

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

VDD

VDD

VDD

VDD

VDD

VDD

VDD

168

180

179

191

192

156

157

167

VDD

DQ48

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

57

69

58

70

M_DATA_R_44

M_DATA_R_45

M_DATA_R_46

M_DATA_R_47

142

146

152

154

DQ45

DQ46

DQ47

VDD

VDD

VDD

144

155

132

143

45

46

R101

DUMMY-R2

M_DATA_R_43

M_DATA_R_42

151

153

DQ42

DQ43

DQ44

VDD

VDD

114

131

VDD

VDD

VDD

VDD

VDD

VDD

VDD

9

36

22

33

10

21

34

12

R102

0R2-0

3D3V_S0

M_DATA_R_35

M_DATA_R_41

M_DATA_R_36

M_DATA_R_34

M_DATA_R_39

M_DATA_R_40

M_DATA_R_38

M_DATA_R_37

135

139

141

145

128

130

136

140

DQ35

DQ40

DQ41

DQ36

DQ37

DQ38

DQ39

VDD

VDD

VDD

VDD

113

VDD

VDD

VDD

92

69

94

81

70

82

93

DQ34

VDD

SCL

SDA

SA0

SA1

SA2

195

193

194

196

198

DM1_SA0

12

M_DATA_R_33

M_DATA_R_30

M_DATA_R_31

M_DATA_R_28

M_DATA_R_27

M_DATA_R_32

M_DATA_R_29

67

127

129

60

66

68

DQ32

DQ33

DQ2856DQ29

DQ30

DQ31

VDD

VDD

VDD

VDD

VDD

VDD

VDD

45

36

46

57

33

58

34

R105

DUMMY-R2

CK0

CK2

CK1

/CK0

/CK2

/CK1

DM8

DM5

DM6

DM7

35

89

37

91

M_DATA_R_26

DQ2665DQ27

VDD

22

78

160

158

M_DATA_R_23

M_DATA_R_22

M_DATA_R_24

M_DATA_R_25

55

59

50

54

DQ24

DQ25

DQ22

DQ23

VDD

VDD

VDD

9

10

21

12

M_DM_R_8

M_DATA_R_20

M_DATA_R_19

M_DATA_R_21

53

42

44

DQ20

DQ21

SA1

SA2

194

196

198

DM2_SA0

12

3D3V_S0

DQ19

SA0

170

184

M_DM_R_7

M_DM_R_6

M_DATA_R_17

M_DATA_R_18

43

49

DQ18

SDA

193

CK-408_SDA

R104

0R2-0

134

148

M_DM_R_5

M_DM_R_4

CLK_DDR0 6

CLK_DDR0# 6

CLK_DDR1 6

CLK_DDR1# 6

CLK_DDR2 6

CLK_DDR2# 6

CK-408_SCL 3

CK-408_SDA 3

M_DATA_R_16

M_DATA_R_15

32

DQ1641DQ17

SCL

195

CK-408_SCL

DM4

DQS8

DQS4

DQS5

DQS6

DQS7

DM0

DM1

DM2

DM3

61

77

12

26

48

62

M_DM_R_3

M_DM_R_1

M_DM_R_2

M_DATA_R_13

M_DATA_R_12

M_DATA_R_14

24

DQ1220DQ13

DQ1430DQ15

CK2

/CK2

/CK1

91

89

158

133

147

169

183

M_DQS_R8

M_DQS_R5

M_DQS_R7

M_DQS_R6

DQ1029DQ11

/CK0

M_DQS_R3

M_DQS_R4

M_DATA_R_6

M_DATA_R_9

M_DATA_R_7

M_DATA_R_5

M_DATA_R_4

M_DATA_R_8

23

8

18

DQ819DQ9

DQ46DQ5

DQ614DQ7

CK0

DM8

DM6

DM7

78

35

148

170

184

M_DM_R_6

M_DM_R_7

M_DM_R_8

M_DM_R_5

CLK_DDR3 6

CLK_DDR3# 6

CLK_DDR4 6

CLK_DDR4# 6

CLK_DDR5 6

CLK_DDR5# 6

M_DM_R_0

M_DATA_R_11

M_DATA_R_10

31

CK1

37

160

DQS3

47

M_DQS_R2

M_DATA_R_3

17

DQ3

DM5

134

M_DM_R_4

DQS2

25

M_DQS_R1

M_DATA_R_2

13

DQ2

DM4

62

M_DM_R_3

DQS1

11

M_DQS_R0

M_DATA_R_1

7

DQ1

DM3

48

M_DM_R_2

CKE0

CKE1

DQS0

/CS0

/CS1

96

95

121

122

M_CS0_R# 6,10

M_CS1_R# 6,10

M_CKE0_R# 6,10

M_CKE1_R# 6,10

M_DQS_R[8..0] 10

M_DM_R_[8..0] 10

M_A[12..0] 6,10

M_A_FR_3

M_A_FR_8

M_A_FR_9

M_A_FR_6

M_A_FR_7

M_A_FR_11

M_A_FR_10

M_A_FR_12

115

101

105

107

108

110

25

M_DQS_R1

106

A7

DQS1

11

M_DQS_R0

A6

DQS0

111

109

A5

A4

A2

A1

A3

CKE0

CKE1

/CS1

96

95

122

102

99

100

A9

A8

A12

A11

A10 / AP

DQS2

DQS3

DQS4

DQS5

DQS6

47

61

133

147

169

M_DQS_R2

M_DQS_R3

M_DQS_R4

M_DQS_R5

M_DQS_R6

Title

DDR Socket

Size Document Number Rev

A3

Date: Sheet of

DM2

M_DATA_R_0

5

116

117

BA1

BA0

DQ0

DQS8

DQS7

DM0

DM1

77

12

26

183

M_DQS_R7

M_DQS_R8

M_DM_R_1

M_DM_R_0

Change to 62.10017.441

-1

M_BS1_FR# 10

M_BS0_FR# 10

M_AB5 6,10

M_AB4 6,10

M_AB2 6,10

M_AB1 6,10

M_A_FR_0

112

DM2

A0

DDR-SODIMM-R-U1

/CS0

121

M_CS2_R# 6,10

M_CS3_R# 6,10

M_CKE2_R# 6,10

M_CKE3_R# 6,10

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

A1+

SC-9-2

-1-9-1

939Thursday, June 19, 2003

-1

Page 10

RN30

1

M_DATA9

M_DQS1 M_DQS_R1

M_DATA8

M_DATA3

M_DQS0

M_DATA2

M_DATA0

M_DATA1

M_DM5

M_DATA44

M_DATA45

M_DATA39

M_DATA38

M_DM4

M_DATA36

M_DATA37

M_DATA49 M_DATA_R_49

M_DATA48

M_DATA43

M_DATA42 M_DATA_R_42

M_DQS5

M_DATA41

M_DATA40

M_DATA35

M_DM1

M_DATA13

M_DATA12

M_DATA7

M_DM0

M_DATA6

M_DATA4

M_DATA5

M_DATA19

M_DQS2

M_DATA17

M_DATA16

M_DATA11

M_DATA10

M_WE_FR#9

M_BS0_FR#9

M_A_FR_10 M_A10

M_A_FR_3

M_A_FR_9

M_A_FR_12

M_A_FR_8

M_A_FR_11

M_DATA71 M_DATA_R_71

M_DATA70

M_DM8

M_DATA69

2

3

4

5

6

7

8 9

SRN10J-3

RN11

1

2

3

4

5

6

7

8 9

SRN10J-3

RN10

1

2

3

4

5

6

7

8 9

SRN10J-3

RN29

1

2

3

4

5

6

7

8 9

SRN10J-3

RN26

1

2

3

4 5

SRN10J-1

RN27

1 4

2

SRN10J

1

2

3

4 5

RN56

1

2

3

4 5

SRN10J-1

RN22

1

2

3

4 5

SRN10J-1

16

15

14

13

12

11

10

16

15

14

13

12

11

10

16

15

14

13

12

11

10

16

15

14

13

12

11

10

8

7

6

3

RN52

SRN10J-1

8

7

6

8

7

6

M_DATA_R_9

M_DATA_R_8

M_DATA_R_3

M_DQS_R0

M_DATA_R_2

M_DATA_R_0

M_DATA_R_1

M_DM_R_5

M_DATA_R_44

M_DATA_R_45

M_DATA_R_39

M_DATA_R_38

M_DM_R_4

M_DATA_R_36

M_DATA_R_37

M_DATA_R_48

M_DATA_R_43

M_DQS_R5

M_DATA_R_41

M_DATA_R_40

M_DATA_R_35

M_DM_R_1

M_DATA_R_13

M_DATA_R_12

M_DATA_R_7

M_DM_R_0

M_DATA_R_6

M_DATA_R_4

M_DATA_R_5

M_DATA_R_19

M_DQS_R2

M_DATA_R_17

M_DATA_R_16

M_DATA_R_11

M_DATA_R_10

8

7

6

M_A9

M_A12

M_A8

M_A11

M_DATA_R_70

M_DM_R_8

M_DATA_R_69

SERIES DAMPING PARALLEL TERMINATION

PLACE RNs CLOSE TO DM0, < 0.75"

STRICT EQUAL LENGTH

LIMITATION WITH DQS, CB PINS

M_DATA59

M_DATA58

M_DQS7

M_DATA57

M_DATA56

M_DATA51

M_DQS6

M_DATA50

M_DATA68

M_DATA31

M_DATA30

M_DM3

M_DATA29

M_DATA28

M_DATA23

M_DATA65

M_DATA64

M_DATA27

M_DATA26

M_DQS3

M_DATA24

M_DATA25

M_DATA18

M_DATA63

M_DATA62

M_DM7

M_DATA61

M_DATA60

M_DATA55

M_DM6

M_DATA54

M_DQS4

M_DATA34

M_DATA32

M_DQS8

M_CAS_FR#9

M_RAS_FR#9

M_BS1_FR#9 M_BS1# 6,9

M_WE#

M_BS0#

M_A3

M_A_FR_0 M_A0

M_DATA66 M_DATA_R_66

M_DATA67

M_A_FR_7

M_A_FR_6

M_DATA15

M_DATA14

M_DATA21

M_DM2

M_DATA46

M_DATA47

M_DATA52

M_DATA53

RN7

1

16

2

15

3

14

4

13

5

12

6

11

7

10

8 9

SRN10J-3

RN23

1

16

2

15

3

14

4

13

5

12

6

11

7

10

8 9

SRN10J-3

RN24

1

16

2

15

3

14

4

13

5

12

6

11

7

10

8 9

SRN10J-3

RN6

1

16

2

15

3

14

4

13

5

12

6

11

7

10

8 9

SRN10J-3

RN12

1

8

2

7

3

6

4 5

SRN10J-1

R113

1 2

10R2

R112

1 2

10R2

RN51

1

8

2

7

3

6

4 5

SRN10J-1

RN21 SRN10J

2

3

1 4

2

3

1 4

RN55 SRN10J

RN28 SRN10J

2

3

1 4

2

3

1 4

RN25 SRN10J

RN9 SRN10J

2

3

1 4

2

3

1 4

RN8 SRN10J

M_DATA_R_59

M_DATA_R_58

M_DQS_R7

M_DATA_R_57

M_DATA_R_56

M_DATA_R_51

M_DQS_R6

M_DATA_R_50

M_DATA_R_68

M_DATA_R_31

M_DATA_R_30

M_DM_R_3

M_DATA_R_29

M_DATA_R_28

M_DATA_R_23

M_DATA_R_22M_DATA22

M_DATA_R_65

M_DATA_R_64

M_DATA_R_27