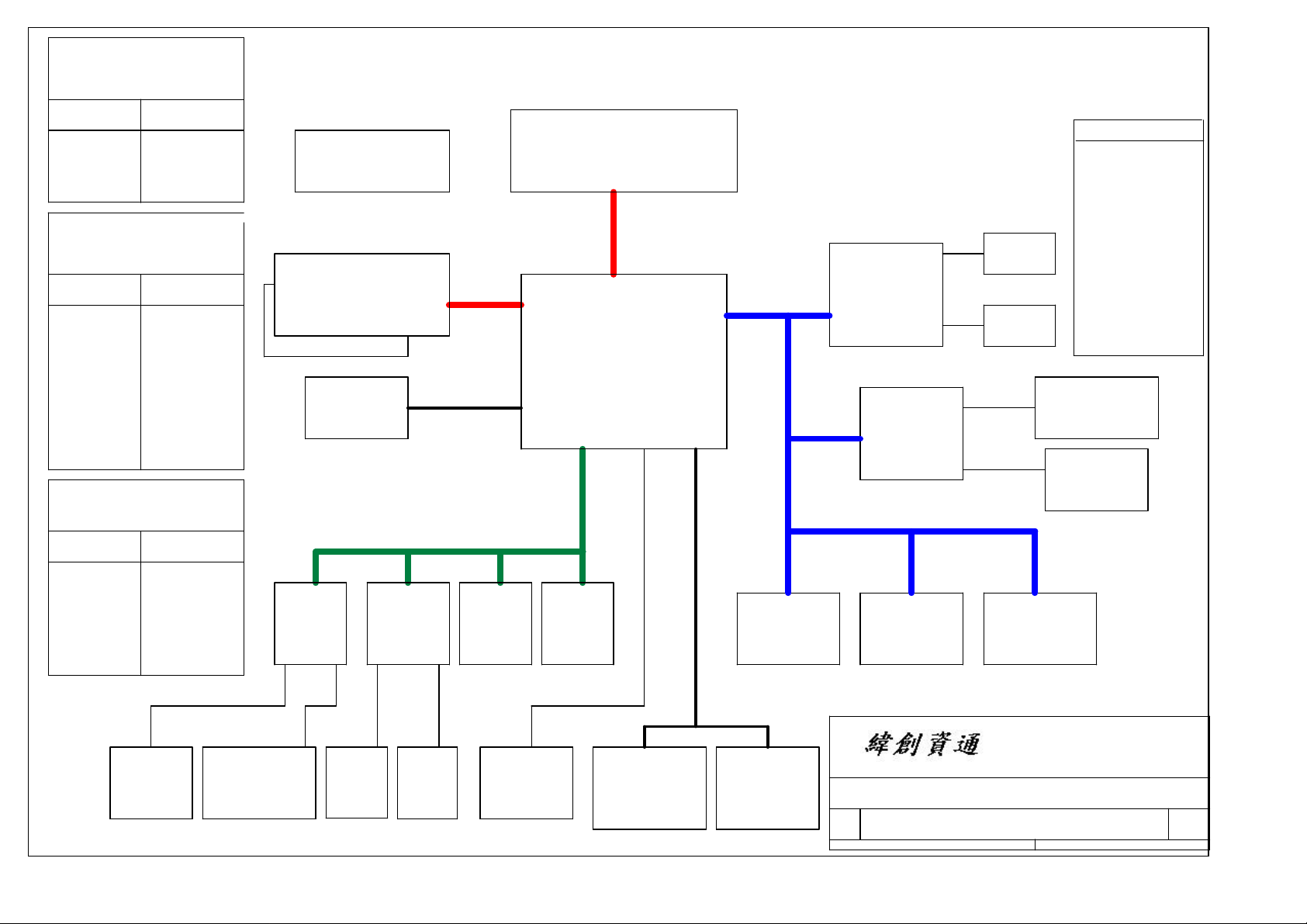

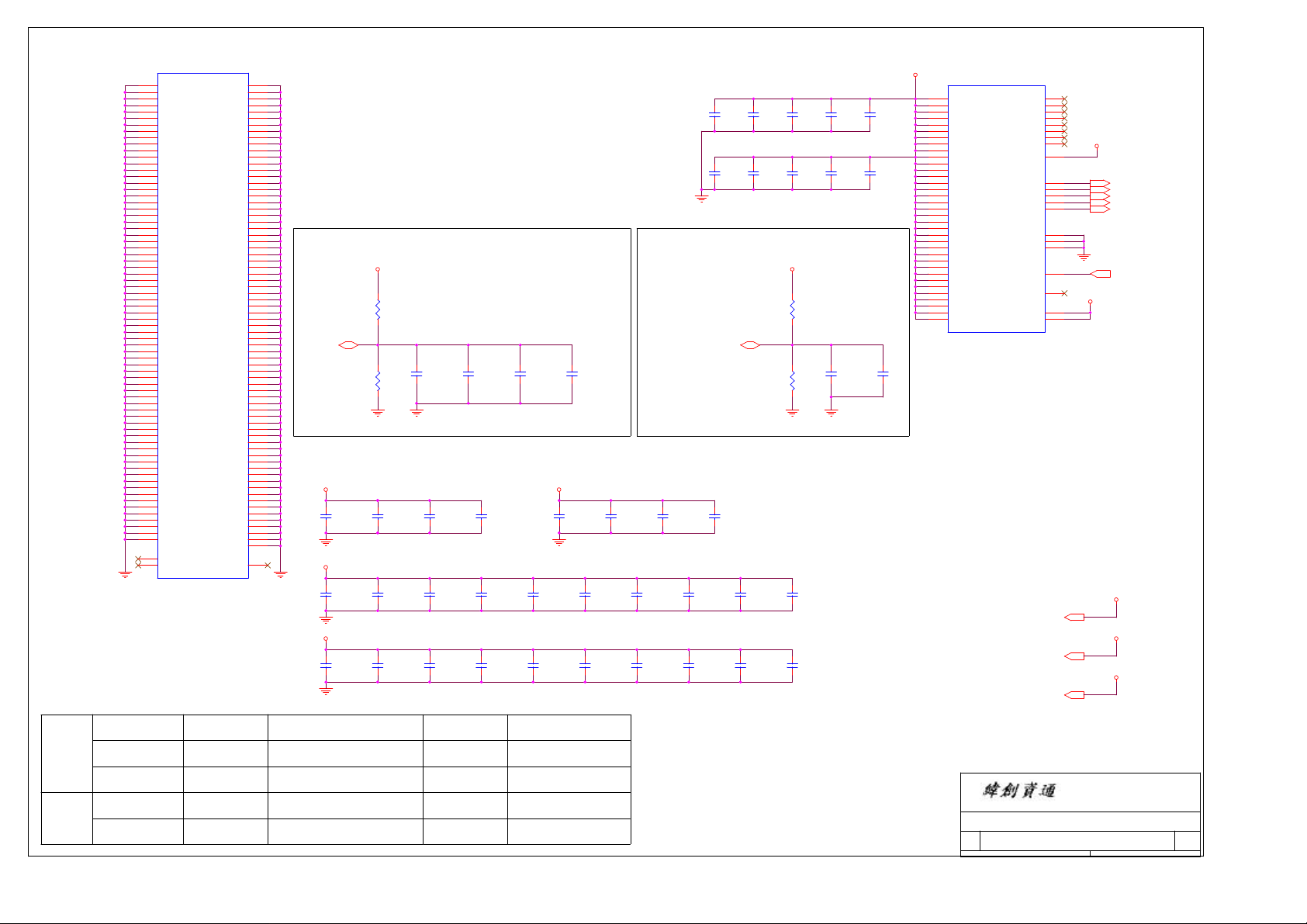

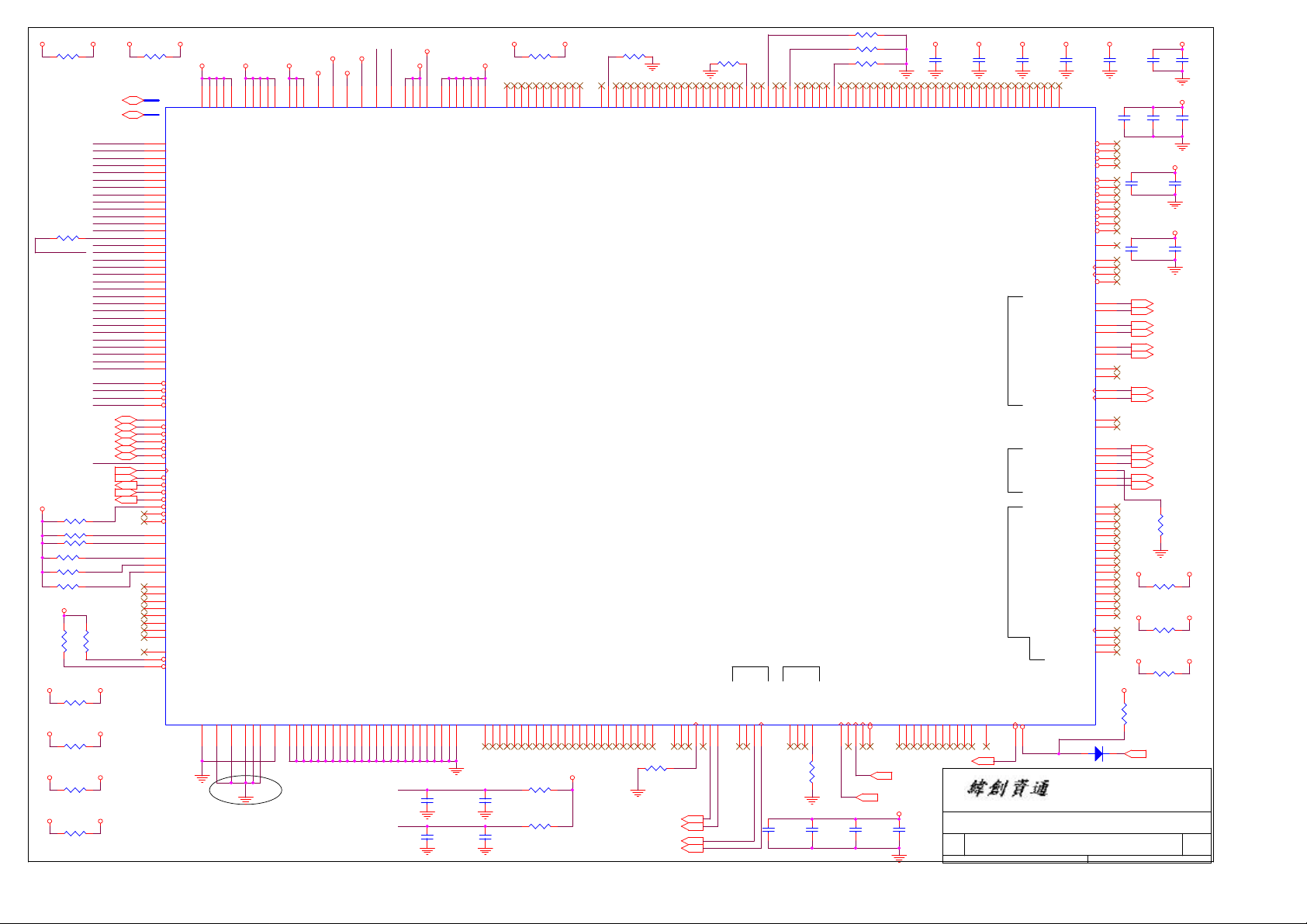

Acer TravelMate C100, TravelMate TM100 Schematics

CPU DC/DC

Switching Power

MAX1718/MAX1714

INPUTS

OUTPUTS

VCC_CORE_S0DCBATOUT

VCCT_S0

PAGE:27,28

DC/DC&CHARGER

Switching Power

MAX1632/OZT05J02

INPUTS

DCBATOUT

AD+

OUTPUTS

3D3V_S5AC

3D3V1_S5AC

3D3V_S3

3D3V_S0

5V_S0

12V_S0

BT+

PAGE:29,30,31

/32,33

OTHER DC/DC

MAX1792/G913

INPUTS

OUTPUTS

CLOCK

3D3V_S0/2D5V_S0

Genertor

ICS9248-61

SDRAM

SDRAM*2

5V_S0

HDD

Page:13

TM100

PIII TUALATIN

ULV 700MHz~

Page:3 Page:3,4

3D3V_S3

FCBGA

+3.3V/M+3V/+2.5V/M+2.5V/+5V

100MHz

Page:8

CORE LOGIC

Intel 82443MX

IDE BUS

Ultra 33

XD BUS

CPU

HOST BUS

100MHz

Page:7

33MHz

Project Code :

2D5V_S3/3D3V_S3

/2D5VRD_S3

VGA

SMI SM722

+3.3V/+5V/+12V

CARDBUS

O2 OZ711

TARZEN

PCI BUS

91.48R01.001

PCB P/N :

01201-1

PCB : 48.48R01.001

5V_S0

CRT

Page:10

3D3V_S0

Page:9

Page:14

LCD

Page:11

SMART Card

SLOT *1

CARDBUS

SLOT *1

PCB LAYER

L1:COMPONENT

L2:GND

L3:SIGNAL

L4:SIGNAL

L5:GND

L6:VCC

L7:SIGNAL

L8:SIGNAL

L9:GND

L10:COMPONENT

Page:15

Page:15

3D3V_S0

2D5V_S0

3D3V_S3 2D5V_S3

FIR

2D5V_S0

1D5V_S0

1D8V_S0

PAGE:28

DIGITIZER

IRMS6452

Page:26

5V_S0

5V_S3

KBC

M38869

Page:23

5V_S3

INTKB

Page:23Page:23

5V_S0

BIOS

ROM

Page:24

5V_S0 5VA_S03D3V_S0/5V_S05V_S03D3V_S0

PORT

0,1

5V_S0

SIO

NS 97338

Page:25 Page:27

Touch

Pad

Page:11

DEBUG

PORT

Page:26

5V_S0

MODEM AC 97USB

Daughter

Card

Page:19

LAN_3D3V_S5AC/

LAN_2D5V_S5AC/

LAN

RTL8100BL

AC-LINK

Codec

CS4299-XQ

Page:20,21,22

3D3V_S0

IEEE 1394

TI TSB43AB21

Page:16

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Page:17,18

3D3V_S5AC

MINIPCI

802.11

Page:19

Title

System Block Diagram

Size Document Number Rev

A4

Date: Sheet of

TM100

1 35Thursday, April 04, 2002

-1

1. Support S3 State (Suspend To RAM):

No

Wake Up Event Chip Controller

Description

PME#_RSM(WOL) LAN Controller RTL8100L Magic Packet/ Wake Up Frame1

2 BanisterPWRBTN#_5RSM Wake Event from User

3 LID KBC

4 Ring IN

5 KBC

Any Key

MDC

6 BL2# KBC

2. Change notice :

* Before SMT of SA::

1>0R3-0-U ( 63.R0004.151) DEL: R260, R211, R214 ADD: R261, R209, R216, R263

2>Charger firmware U48 from P/N:71.12509.00A(PIC) to P/N:71.00012.00A(ATMEL)

* SA - > SB:

1>Swap smart card connecter and use this one. P/N: 20.K0090.012

2>Dummy the 5 resisters of VGA: R46, R238, R240, R241, R242 - P/N:63.47234.151

3>Modify the U4-4 from 2D5V_S0 to 2D5V_S3

4>Change the Q6 from 2N7002 - P/N:84.27002.031 to TP0610 -P/N: 84.00610.031 , then swap D and S

5>Change R6 from 10K - 63.10334.151 to 1K - 63.10234.151

6>Connect R49 and R52 LVDSVDD to 2D5V_S3

7>Modify core voltage setting: (1)R313:100K->Dummy (2)R311:Dummy->1K (3)R325,R326:1K->Dummy (4)R328,R329:Dummy->100K

8>Modify GPIO of KBC: (1)P20:HOTKEY->CHG_FLASH (2)P66:PCB_VER_SET2->EN_FLASH

9>R403:33R(63.33034.1D1)->0R(63.R0034.1D1)

10>Add U86 to modify the driving voltage from 3.3V to 5V

11>VGAU34: 71.00722.00U->71.00722.A0U

* SB - > SC:

Page 3:

1> Reserve test pads for 48MSEL100/66# and DIV4#

2> Change R418 to 0R and BC351 to dummy to tune 48M signal quality

Page 7:

3> Change

GPIO2 to MP_COMMAND, GPIO3 to MP_ACK, GPIO6 to OBLAN-80211#, GPIO20 to AD_OFF, GPIO29 to PCI_REQ#3, GPIO30 to PCI_GNT#3

Page 11:

4> Modify the logic of STD_LED and PWR_LED

5> Add R521 to pull 3D3V_S0 for SUSB#

Page 12:

6> Change R269 pull H plane from 5V_S0 to 3D3V_S0

Page 13:

7> Change HDD connecter for ME request

8> Add pull H for PCI_REQ#3, PCI_GNT#3. and PCI_PERR#

Page 14:

9> Change PCI_REQ# from 1 to 3 , PCI_GNT# from 1 to 3

10> Add R546 between BAN_PME# and CARDBUS_PME#

Page 15:

11> Change the cardbus socket SKT3 for ME request

Page 16:

12> Change PLLVDD(Pin 1) to 3D3V_S0

13> Dummy Pin121~125 for 43AB21, but reserve resisters for 43AB22

Page 17/18:

14> Mount the components for RTL8100BL

15> Add R524 and Q32 for preventing leakage current

16> Modify JK2(RJ11-45) for ME request

17> Add circuit for BIOS setting between LAN and 802.11

Page 19:

18> Add BC486 and BC488 for EMI request

Page 20/21/22:

19> Add BEEP from uP to control BEEP sound

20> Codec Pin 27: NC

21> Add BC487 between AUD_GND and DIG_GND for EMI

22> Change U75 and U80 to GMT 1211

23> Change U77 to APA2020

24> Performance tuing:

(1) BC308 to 0.01UF (2)BC466, BC467, and BC469 to 3.3V (3)R491 to 470R (4)DUMMY:BC424, BC448, BC451, R506, R381,

R383, BC475, BC476, BC434, BC432 (5)Change R513, R516, R497, R495 to 12K(6)Change R514, R496 to 15K (7)R498, R515 to

27K (8)R382, R380 to 0R3

Page 23:

25> Modify KBC P27 to NC, P40 to EMAIL_LED#, P65 to BACKLIGHT_OFF#

Page 24:

26> Change button_interrupt from IRQ7 to PCI_INTB#

Page 28:

27> Reserve R532 for EMI request

28> Add R531to pull L(Reduce_on)

Page 29:

29> Change U3 and U36 to FDS6982S, then dummy D3 and D17

30> Change D13 and D14 to 83.1R003.A8F

Page 32:

U9 -pin 13: NC

Page 33:

31> Modify the U48 circuit for preventing U48(5V) drive 82440MX(3V)

32> Use U48 to replace U9(uP) to contorl charge_LED

Page 34:

33> Reserve test pads for clock-down circuit

* SC -> SD

Page 6:

1.Change Q26 from BSS138 to MMBT3904

Page 7 :

2.GPIO9 : Replace 802.11LED# with OBLAN-80211#

3.Add smith trigger and debounce RC to solve 100uS drop of SUSB#

Page 10:

4.Change VGA connecter for ME request

Page 11:

5.Change U88-1 control pin from U50-2 to BL2#

6.Replace digitizer reset signal from SUSB# to PCIRST2#

7.Add R564 to limit the current

Page 12:

8.U51-1control signal changed from 3D3V_S0 to PRE_SUSC#

Page 13:

9.Add D34 to prevent park voltage of HDD under -0.3V

Page 14:

10.Add DTC124EKA and dummy R546 to be the gate of PME# of OZ711.

Page 16:

11.Change 1394 connecter for ME request

Page 17:

12.Use U90 as the gate to control PCIRST2# to OBLAN and PL 10K to PCIRST2#_LAN

13.Replace the L15 to R563(0R3) for vendor request.

14.Add 100K to PL the U70-74 to solve the wake on LAN.

Page 18:

15.Dummy BC38, R526, R527, R528 for vendor request.

Page 19:

16.Modify the 802.11L_ACT from CN18 pin12 to pin11.

17.Use U91 as the gate to control PCIRST2# to 802.11 and PL 10K to PCIRST2#_80211

18.Add 10K to pull up BAN_PME# to 3D3V_S5

Page 20:

19.Add 3 open-gapes for EMI request.

Page 21:

20.Add DC bias PH 4.7K to internal MIC

Page 22:

21.Update Audio Jack for ME request

Page 23:

22.Modify the email-led control method because there is no GND on KB for KB matrix to PL.

23.Use 7474 to keep the reset of KBC while in S3.

24.Use the DTC124EKA and RB731U to prevent the leakage between KBC and Banister while in S3.

Page 24:

25.Add helf smith-trigger to 5 button.

Page 26:

26.Delet F2 and change it to 0.75A

27.Add Beads between USB conn. and bypass C for EMI request

Page 27:

28.Use CC_CPUSTP to drive CC_DPSLP#

29.Change R93 from 0R to 4.7R for EMI request

Page 28:

30.Change R532 from 0R to 4.7R

Page 29:

31.Parallel 47KR to BC55

32.For SKIP mode , modify the BC5 and BC140 to 47PF and add 100PF to replace R24 and R37.

33.Change R26,R27,R13 and R36 from 0R to 4.7R for EMI request.

Page 30:

34.Add smith trigger and debounce RC to solve 100uS drop of SUSC#

Page 31:

35.Add bypass 0.1uF between AC Jack and bead for EMI request .

36.Change R3 from 10K to 2.2K

Page 32:

37.Change R97 from 15mR to 18mR for current limit of adaptor.

38.Change R258 and R96 from 0R to 4.7R for EMI request

Page 33:

39.Add 10KR to Pull BL2# to 3D3V_S3

40.Change R261 from 10K to 2.2K

41.Change U44 from MAX1615 to LP2951 for cost down

Page 35:

42.DEL: K8, K9, K10, and K11

43.Add: K15

SD -> SE

Page 10:

1 Add F2 for safety request.

Page 13:

2.Remove R335 for the driving high is not enough.

Page 27:

3. Del R567

Page 32:

4.Change R97 from 64.R0185.A71 to 64.R0185781 because it might generate shortage due to the pad of compoment is too large

SE => -1

Page 7:

1. Change VCC of 82440MX from 3D3V_S0 to 3D3V_S3.

2. Change power plane of R139 from 5V_S0 to 5V_S3

3. Change power plane of D9 from 3D3V_S0 to 3D3V_S3

Page 20:

4. Reserve R569 and R570 to use different Codec.

Page 22:

5. Tune R380, R381, R383, and R383 for audio performance.

Page 30:

6. Add U21D between U35 and U60C.

Title

Size Document Number Rev

C

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

TM100 Rev_History

TM100

2 35Thursday, April 04, 2002

-1

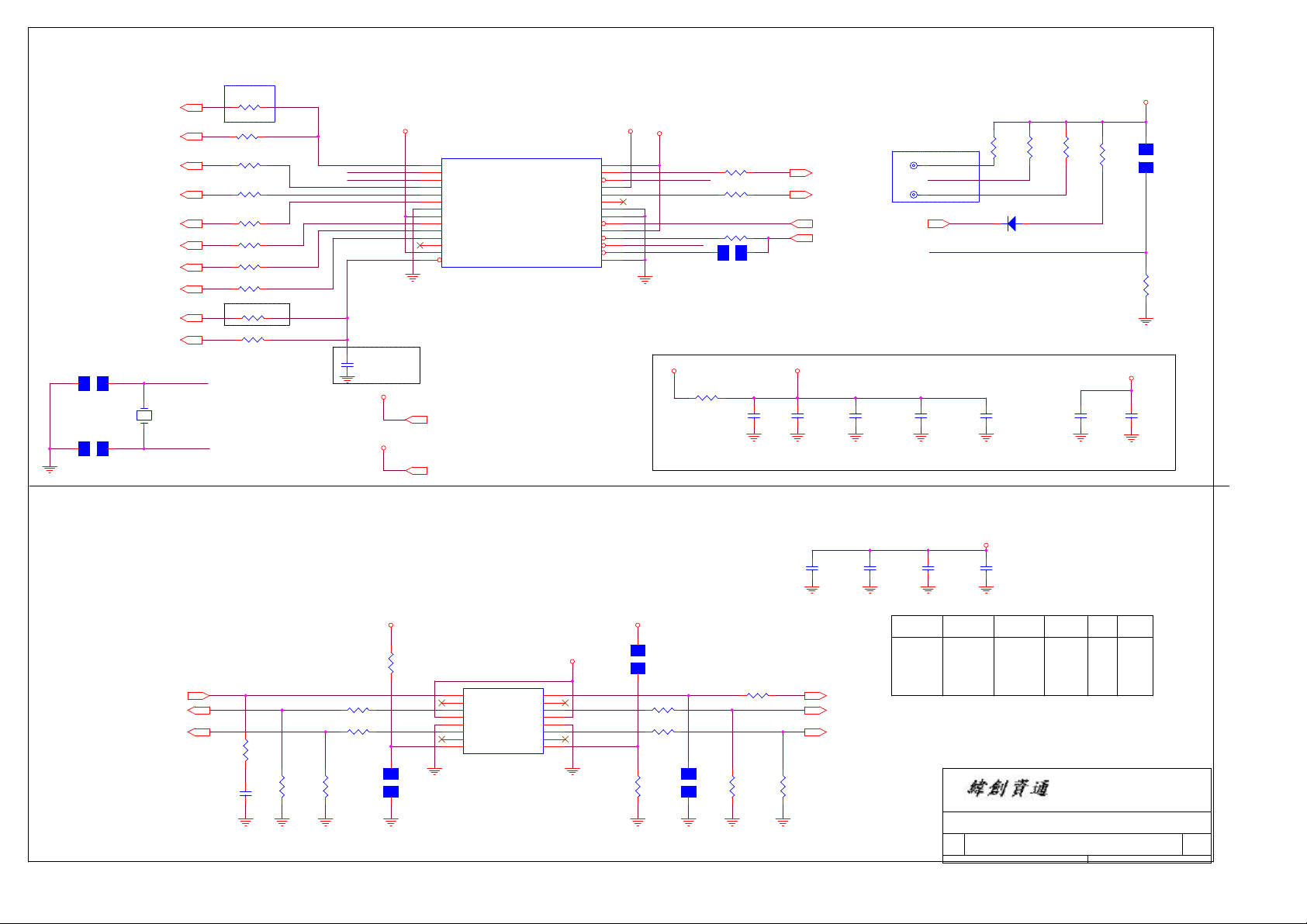

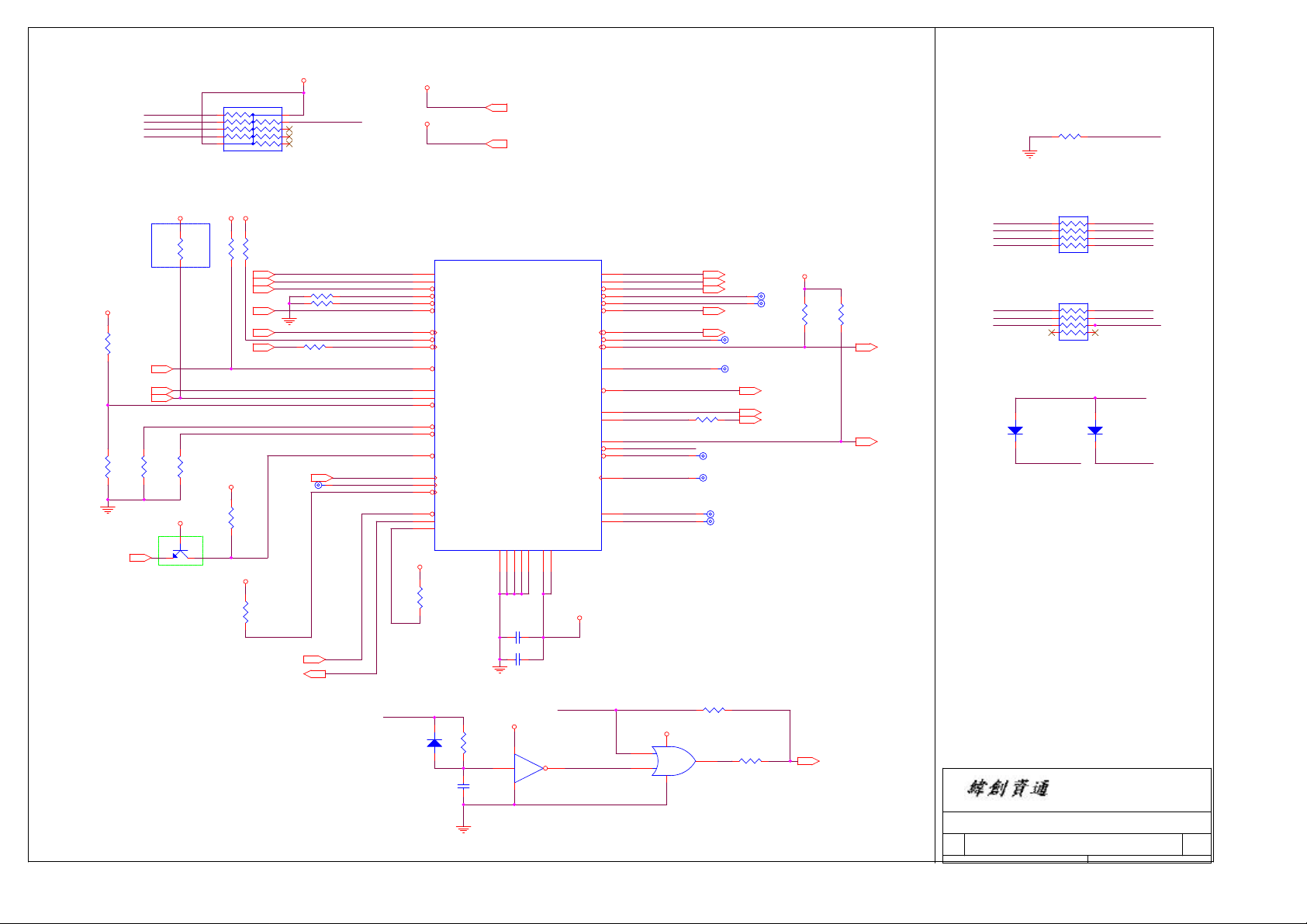

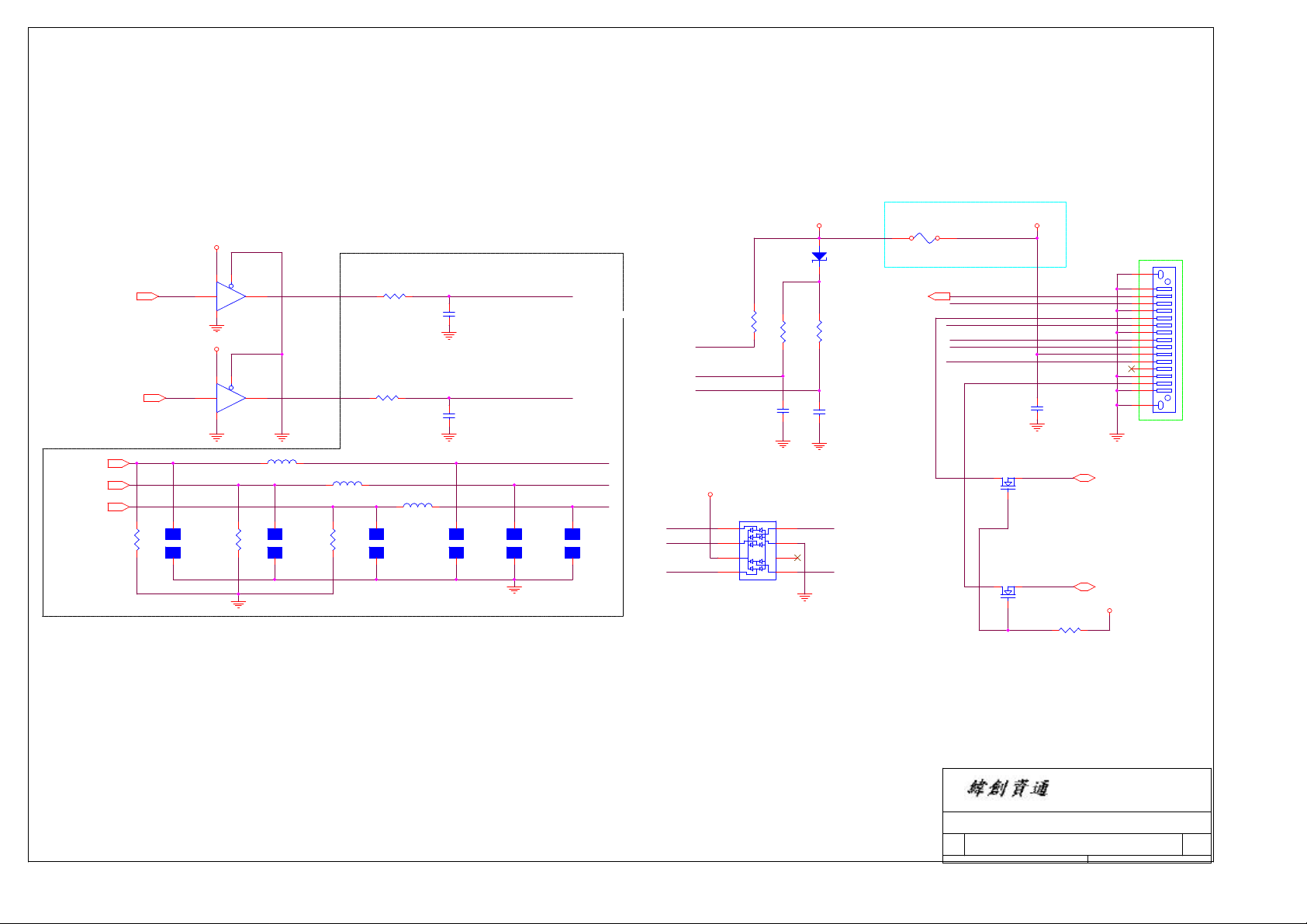

BC333

1 2

DUMMY-C3

BC332

1 2

DUMMY-C3

SA->SB

R403 0R2-0

14MGCL_D36

14M_P47

PCLK_MX7

PCLK_VGA9

14M_IN

X3

X-14.318MHZ-1

14M_OUT

PCLK_PCM14

PCLK_LAN17

PCLK_MINI19

PCLK_139416

48M_P47

SIO_48M25

12

63.R0034.1D1

R405 33R2

63.33034.1D1

R404

33R2

1 2

63.33034.1D1

R421

1 2

63.33034.1D1

R420

1 2

63.33034.1D1

R424 33R2

1 2

63.33034.1D1

R423 33R2

1 2

63.33034.1D1

R422 33R2

1 2

63.33034.1D1

R418

1 2

63.R0034.1D1

R444

1 2

63.10034.1D1

33R2

33R2

12

12

0R2-0

10R2

SB->SC

SB->SC

14MP4

14M_IN

14M_OUT

PCLKMX

PCLKVGA

PCLKPCM

PCLKLAN

PCLKMINI

PCLK1394

48MSEL100/66#

BC351

DUMMY-SC10P

ZZ.10034.1B1

3D3V_S0

2D5V_S0

CLK_3D3V_S0

10

11

12

13

14

3D3V_S0 6,7,8,11,12,13,14,15,16,17,19,20,23,24,25,26,27,28,30,35

2D5V_S0 4,28

Clock Generator

U65

1

REF0

2

XTAL_IN

3

XTAL_OUT

4

PCICLK_F

5

PCICLK1

6

PCICLK2

7

VSSPCI

8

VDDPCI

9

PCICLK3

PCICLK4

PCICLK5

EPCICLK

VDD

USBCLK/SEL100/66#

ICS9248-61

VSSCORE

PCI_STOP#

VDDCORE

CPU_STOP#

PWRDWN#

VDDREF

REF1

SPREAD#

VDDCPU

CPUCLK0

CPUCLK1

VSSCPU

DIV4#

VSS48

2D5V_S0

28

27

26

25

24

23

22

21

20

19

18

17

16

15

CPU CLOCK = 440BX CLOCK + 877 MILS

440BX CLOCK = 1.25 ~ 1.35 inches

CLK_3D3V_S0

R400 33R2

1 2

R414 DUMMY-R2

R442

0R3-0-U

1 2

SC4D7U10V5ZY

78.47593.411

1 2

63.33034.1D1

R413 22R2

1 2

63.22034.1D1

63.R0034.1D1

R415

1 2

0R2-0

ZZ.DUMMY.X02

BC330

(PIN 13)

14MVGA

SPREAD#

CLKCPUCLK0

CPU_STOP#1

CLK_PWRDN#

DIV4#

3D3V_S0

14M_VGA 9

CLK_CPUCLK0 4,7

CLK_PCI_STOP# 7

CC_CPUSTP# 6,27

CLK_3D3V_S0

BC350

SCD1U

78.10492.4B1

3D3V_S0

12

12

CLK_PWRDN#

ZZ.04148.011

(PIN 25)

12

R411

10KR2

63.10334.1D1

R417

10KR2

63.10334.1D1

1 2

2D5V_S0

BC329

SCD1U

78.10492.4B1

12

R402

DUMMY-R2

12

R401

10KR2

63.10334.1D1

BC338

SC4D7U10V5ZY

78.47593.411

12

R412

SB->SC

TP32

TP33

SUSA#7

BC339

SCD1U

78.10492.4B1

(PIN 19)(PIN 8)

(PIN 28)

R419

10KR2

63.10334.1D1

48MSEL100/66#

DIV4#

SUSA#

SPREAD#

BC340

SCD1U

78.10492.4B1

10KR2

63.10334.1D1

CPU_STOP#1

D31 DUMMY-S1N4148

*Layout*

20 mil

BC331

SCD1U

78.10492.4B1

near Chip Pin

*Layout*

DCLKIN longer than other

CLK (2.4inch)

CLKDBUF7

CLK_SDRAM18

CLK_SDRAM08

R125

56R3

63.56034.151

BC84

SC15P

78.15034.1B1

12

12

R123

100KR2

63.10434.1D1

R121 10R2

1 2

63.10034.1D1

R122 10R2

1 2

63.10034.1D1

12

R124

100KR2

63.10434.1D1

SDRAM Clock Buffer

3D3V_S0

12

R119

1KR2

63.10234.1D1

SDRAMCK1

SDRAMCK0 SDRAMCK2

12

R120

DUMMY-R2

ZZ.DUMMY.X02

U13

1

REF

2

CLKA1

3

CLKA2

4

VDD

5

GND

6

CLKB1

7

CLKB2

8

FS2

ICS9112BM-17

CLKOUT

CLKA4

CLKA3

CLKB4

CLKB3

VDD

GND

3D3V_S0

16

DCLKIN_R

15

14

SDRAMCK3

13

12

11

10

9

FS1

3D3V_S0

12

12

R107

1KR2

63.10234.1D1

R108

DUMMY-R2

ZZ.DUMMY.X02

R116 10R2

1 2

63.10034.1D1

R115 10R2

1 2

63.10034.1D1

BC82

DUMMY-C3

3D3V_S0

BC80

SCD1U

78.10492.4B1

R114 22R2

12

63.22034.1D1

12

12

R118

100KR2

63.10434.1D1

12

R117

100KR2

63.10434.1D1

DCLKIN 7

CLK_SDRAM3 8

CLK_SDRAM2 8

BC83

SCD1U

78.10492.4B1

FS2

0

0

*1

1

BC85

SCD1U

78.10492.4B1

FS1

TRISTATE

0

1

0

1

Title

Size Document Number Rev

A3

Date: Sheet of

BC81

SC4D7U10V5ZY

78.47593.411

PLL

CLKB[1..4]CLKA[1..4]

DRIVEN PLL N

DRIVEN

TRISTATE

TRISTATE

DRIVEN DRIVEN

DRIVENDRIVEN

OUTPUT

CLKOUT

DRIVEN

DRIVEN

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

SOURCE

PLL

PLLDRIVEN

SHUTDOWN

N

YREF

N

Clock Generator & SDRAM Clock Buffer

TM100

3 35Thursday, April 04, 2002

-1

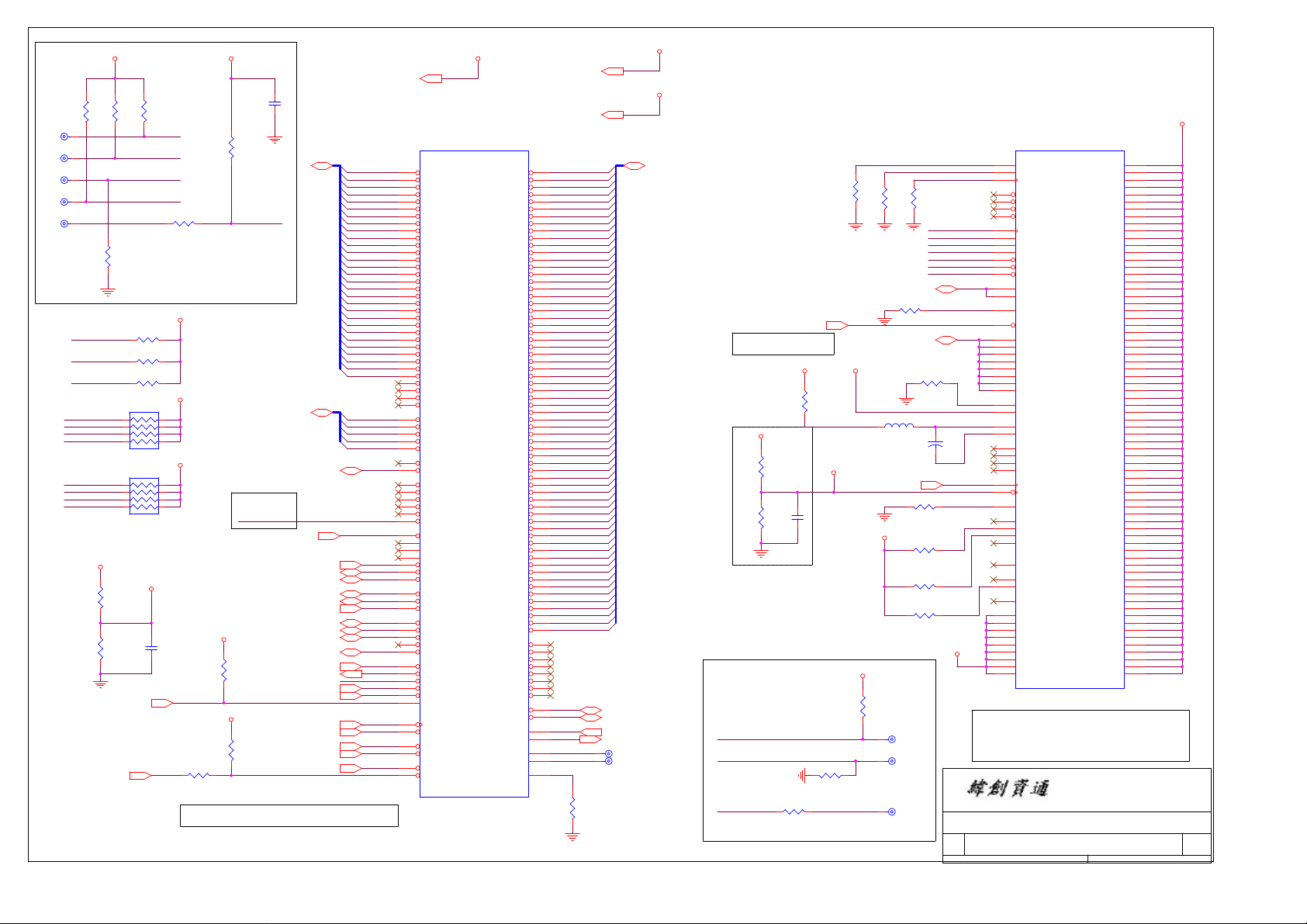

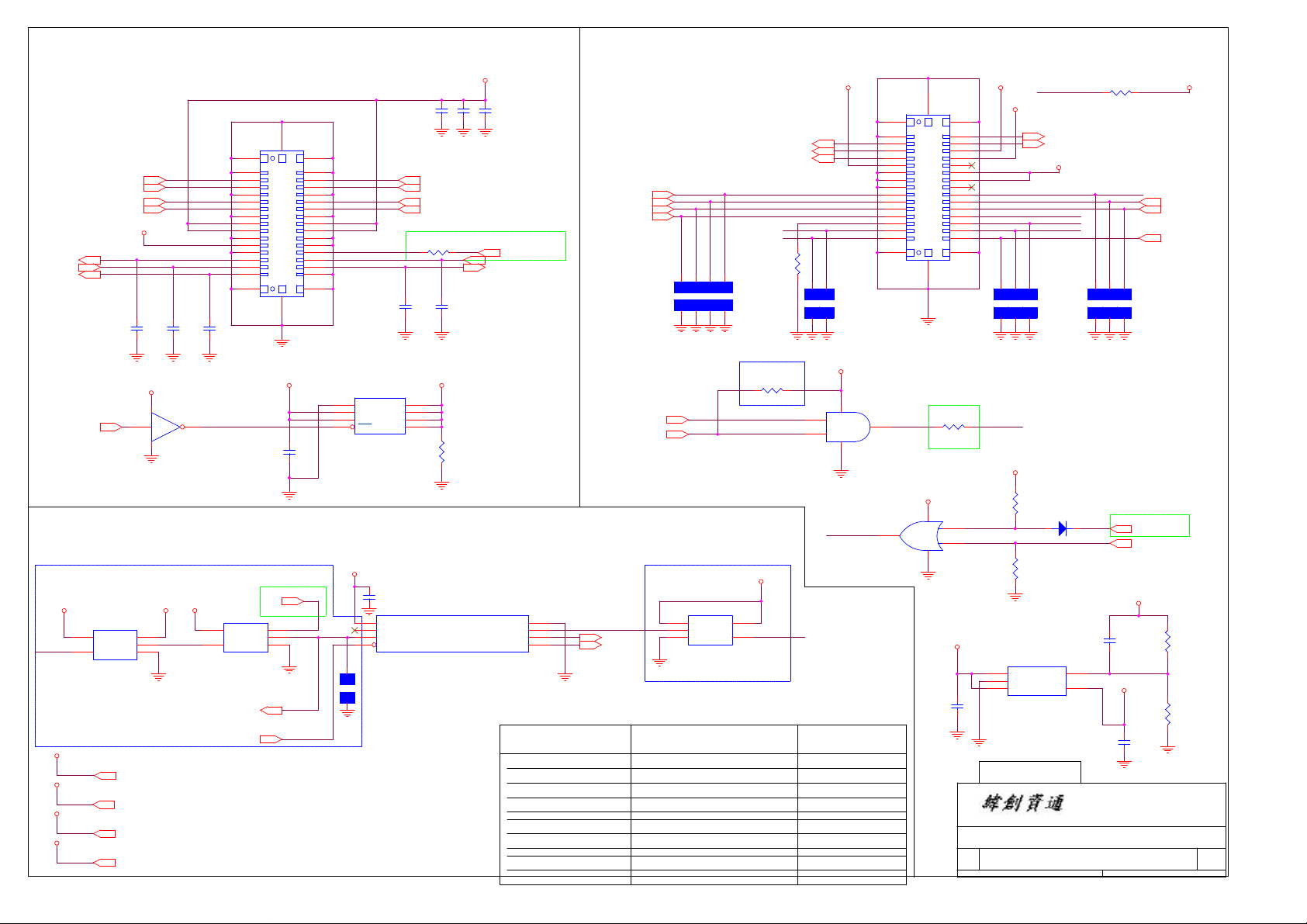

TP28

TPAD30

ZZ.PAD30.XXX

TP21

TPAD30

TP15

TPAD30

TP14

TPAD30

TP13

TPAD30

12

R191

200R3

CC_FLUSH#

CC_INIT#

CC_STPCLK#

CC_INTR

CC_NMI

CC_DPSLP#

CC_SMI#

CC_A20M#

CC_FERR#

CC_IERR#

CC_IGNNE#

2D5V_S0

CC_CPUPWRGD6

GTL_CPURST#6,7

12

12

12

12

R251

150R3

ITP_PREQ#

R192

510R3

R249 3KR3

1 2

R187 1KR3

1 2

63.10234.151

R246 680R3

1 2

63.68134.151

RN6

1

2

3

4 5

SRN1K5-1

66.15236.08A

RN3

1

2

3

4 5

SRN1K5-1

66.15236.08A

R295

1KR3F

64.10015.651

R292

2K49R3F

64.24915.651

12

R297

200R3

ITP_TDI

ITP_TDO

ITP_TRST#

1 2

63.30234.151

8

7

6

8

7

6

1D8V_S0

BC257

SCD1U

78.10492.4B1

R173

240R3

1D5V_S0

1D5V_S0

1D5V_S0

R243

1 2

0R3-0-U

63.R0004.151

12

R174

56D2R3F

64.56R25.651

GTL_HA#[31..3]7

ITP_PRDY#ITP_PRDY#_TP

GTL_REQ#[0..4]7

FOR NOISE

REDUCTION

GTL_BREQ#07

1D8V_S0

12

R294

1K5R3

63.15234.151

CC_CPUPWRGD

VCCT_S0

12

R245

56D2R3F

64.56R25.651

GTL_CPURST1#

Layout note:

Place CPU_RST# Resistor < 0.1" from CPU

BC145

SCD1U

78.10492.4B1

GTL_ADS#7

GTL_BPRI#7

GTL_BNR#7

GTL_LOCK#7

GTL_HIT#7

GTL_HITM#7

GTL_DEFER#7

GTL_RS#07

GTL_RS#17

GTL_RS#27

GTL_TRDY#7

CC_A20M#7

CC_FERR#7

CC_IGNNE#7

CC_SMI#6

CC_STPCLK#6

CC_DPSLP#27

CC_INTR6

CC_NMI6

CC_INIT#6

GTL_HD#[63..0] 7

TP3

TP2

TPAD30

TPAD30

ZZ.PAD30.XXX

ZZ.PAD30.XXX

VCC_CORE_S0

VCCT_S0

GHI#:internal pull

up to VCCT

2D5V_S0

12

R293

1KR3F

64.10015.651

12

R291

1KR3F

64.10015.651

Place near CPU

ITP_TMS

ITP_TCK

CC_PERF#6

VCCT_S0

R244

1 2

240R3

63.10234.151

12

R290

0R3-0-U

63.R0004.151

CPUCLKREF

BC258

SC1U10V3ZY

78.10593.4B1

1D5V_S0VCCT_S0VCCT_S0

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

VCC_CORE_S05,27

VCCT_S05,6,7,28

A16

GTL_HD#0

D0#

B17

GTL_HD#1

D1#

A17

GTL_HD#2

D2#

D23

GTL_HD#3

D3#

B19

GTL_HD#4

D4#

C20

GTL_HD#5

D5#

C16

GTL_HD#6

D6#

A20

GTL_HD#7

D7#

A22

GTL_HD#8

D8#

A19

GTL_HD#9

D9#

A23

GTL_HD#10

A24

GTL_HD#11

C18

GTL_HD#12

D24

GTL_HD#13

B24

GTL_HD#14

A18

GTL_HD#15

E23

GTL_HD#16

B21

GTL_HD#17

B23

GTL_HD#18

GTL_HD#19

E26

C24

GTL_HD#20

GTL_HD#21

F24

D25

GTL_HD#22

GTL_HD#23

E24

GTL_HD#24

B25

G24

GTL_HD#25

GTL_HD#26

H24

GTL_HD#27

F26

GTL_HD#28

L24

GTL_HD#29

H25

GTL_HD#30

C26

K24

GTL_HD#31

G26

GTL_HD#32

GTL_HD#33

K25

GTL_HD#34

J24

GTL_HD#35

K26

GTL_HD#36

F25

GTL_HD#37

N26

GTL_HD#38

J26

GTL_HD#39

M24

GTL_HD#40

U26

GTL_HD#41

P25

GTL_HD#42

L26

GTL_HD#43

R24

GTL_HD#44

R26

GTL_HD#45

M25

GTL_HD#46

V25

T24

GTL_HD#47

GTL_HD#48

M26

P24

GTL_HD#49

GTL_HD#50

AA26

GTL_HD#51

T26

GTL_HD#52

U24

Y25

GTL_HD#53

GTL_HD#54

W26

GTL_HD#55

V26

GTL_HD#56

AB25

GTL_HD#57

T25

GTL_HD#58

Y24

GTL_HD#59

W24

GTL_HD#60

Y26

GTL_HD#61

AB24

GTL_HD#62

AA24

GTL_HD#63

V24

AE24

AD25

AE25

AC24

AF24

AD26

AC26

AD24

W3

Y1

AF13

AF14

AE12

H_BSEL0_3D3

AF10

H_BSEL1_3D3

AF16

CPU_EDGCTRLP

12

R190

110R3F

GTL_DBSY# 7

GTL_DRDY# 7

THERMDP1 12

THERMDN 12

1D5V_S05,28

U5A

CC_FERR#

CC_FLUSH#

AF23

AD23

AC3

AF6

AF5

AD9

AD3

AB4

AE4

AF8

AD15

AE14

AE6

K1

J1

G2

K3

J2

H3

G1

A3

J3

H1

D3

F3

G3

C2

B5

B11

C6

B9

B7

C8

A8

A10

B3

A13

A9

C3

C12

C10

A6

A15

A14

B13

A12

R1

L3

T1

U1

L1

T4

AA3

W2

AB3

P3

C14

AF4

A7

C4

C22

R2

L2

V3

AA2

U2

T3

Y3

V1

U3

M5

W1

B15

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

REQ0#

REQ1#

REQ2#

CPU

REQ3#

REQ4#

RP#

ADS#

AERR#

AP0#

AP1#

BERR#

BINIT#

IERR#

BREQ0#

NC

NC

NC

BPRI#

BNR#

LOCK#

HIT#

HITM#

DEFER#

RS0#

RS1#

RS2#

RSP#

TRDY#

A20M#

FERR#

FLUSH#

IGNNE#

SMI#

PWRGOOD

STPCLK#

DPSLP#

INTR/LINT0

NMI/LINT1

INIT#

RESET#

TUAL700

71.TULAT.G0U

1/4

DEP0#

DEP1#

DEP2#

DEP3#

DEP4#

DEP5#

DEP6#

DEP7#

DBSY#

DRDY#

THERMDA

THERMDC

SELFSB0

SELFSB1

EDGECTRLP

GTL_HA#3

GTL_HA#4

GTL_HA#5

GTL_HA#6

GTL_HA#7

GTL_HA#8

GTL_HA#9

GTL_HA#10

GTL_HA#11

GTL_HA#12

GTL_HA#13

GTL_HA#14

GTL_HA#15

GTL_HA#16

GTL_HA#17

GTL_HA#18

GTL_HA#19

GTL_HA#20

GTL_HA#21

GTL_HA#22

GTL_HA#23

GTL_HA#24

GTL_HA#25

GTL_HA#26

GTL_HA#27

GTL_HA#28

GTL_HA#29

GTL_HA#30

GTL_HA#31

GTL_REQ#0

GTL_REQ#1 CPU_PLL

GTL_REQ#2

GTL_REQ#3

GTL_REQ#4

CC_IERR#

R253

39R3

CG_CPURST#_TPGTL_CPURST#

12

R185

1KR3

63.10234.151

VCC_CORE_S0

VCCT_S0

12

R186

1KR3

CPU_CMOSREF5

1 2

IND-4D7UH

CLK_CPUCLK03,7

VCCT_S0

12

R250

39R3

12

R175

1KR3

63.10234.151

R188

1 2

56D2R3F

64.56R25.651

AGTLREF5,7

L11

1 2

1 2

1 2

TP22

TPAD30

TP23

TPAD30

TP20

TPAD30

U5B

CPU_TESTLO_1

CPU_PLL1

CPU_PLL2

TC7

SE33U8V-U

79.3361U.9P1

CPU_TESTLO

CPU_NCHCTRLP

CPU_TESTHI_1

CPU_TESTHI

AD19

AD17

AF20

AF22

AE20

AD22

AD21

AD10

AD7

AD11

AF7

AF15

AF19

AE22

AF12

AD5

AE16

AF21

AB26

H26

AF9

AA1

AC1

AD1

AF18

AD16

AF11

AE8

N24

AE10

AB6

AA5

AC5

L5

A21

A4

N1

Y4

R5

N3

N2

P1

P5

E1

F1

M1

E2

P4

M6

P6

W5

Y6

U5

V6

PICD0

PICD1

PICCLK

BP2#

BP3#

BPM0#

BPM1#

TCK

TDI

TDO

TMS

TRST#

PREQ#

PRDY#

CMOSREF_1

CMOSREF_0

RTTIMPEDP

GHI#

VREF_1

VREF_2

VREF_3

VREF_4

VREF_5

VREF_6

VREF_7

VREF_8

TESTLO

VCC

PLL1

PLL2

CPU

NC

NC

NC

2/4

NC

CLK0

BLK0#/CLKREF

TESTLO

NC

NCHCTRLP

TESTHI

NC

NC

NC

TESTHI

NC

VCC_76

VCC_77

VCC_78

VCC_79

VCC_80

VCC_75

VCC_74

VCC_73

VCC_72

TUAL700

71.TULAT.G0U

VCC_0

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6

VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56

VCC_57

VCC_58

VCC_59

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

CPU_PICD0

CPU_PICD1

CPU_PICCLK

12

CPU_RTTIMPEDP

R127

1 2

1KR3

12

R126

1KR3

R189

14R3F

R252

1KR3

R286

1KR3

VCC_CORE_S0

ITP_TCK

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_PREQ#

ITP_PRDY#

12

71.TULAT.G0U(700MHz)

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

Size Document Number Rev

A3

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

CPU 1/2

TM100

4 35Thursday, April 04, 2002

D22

F22

E21

H22

G21

K22

J21

M22

L21

P22

N21

T22

R21

V22

U21

Y22

W21

AB22

AA21

AC21

D20

F20

E19

AB20

AA19

AC19

D18

F18

E17

AB18

AA17

AC17

D16

F16

E15

AB16

AA15

AC15

D14

F14

E13

AB14

AA13

AC13

D12

F12

E11

AB12

AA11

AC11

D10

F10

E9

AB10

AA9

AC9

D8

F8

E7

AB8

AA7

AC7

D6

F6

E5

H6

G5

K6

J5

N5

T6

VCC_CORE_S0

-1

U5C

E16

VSS_0

R4

VSS_1

E25

VSS_2

G25

VSS_3

J25

VSS_4

L25

VSS_5

N25

VSS_6

R25

VSS_7

U25

VSS_8

W25

VSS_9

AA25

VSS_10

AC25

VSS_11

AF25

VSS_12

AE26

VSS_13

C23

VSS_14

F23

VSS_15

H23

VSS_16

K23

VSS_17

M23

VSS_18

P23

VSS_19

T23

VSS_20

V23

VSS_21

Y23

VSS_22

AB23

VSS_23

AE23

VSS_24

B22

VSS_25

D21

VSS_26

F21

VSS_27

E22

VSS_28

H21

VSS_29

G22

VSS_30

K21

VSS_31

J22

VSS_32

M21

VSS_33

L22

VSS_34

P21

VSS_35

N22

VSS_36

T21

CPU

VSS_37

R22

VSS_38

V21

VSS_39

U22

VSS_40

Y21

VSS_41

W22

VSS_42

AB21

VSS_43

AA22

VSS_44

AC22

VSS_45

AE21

VSS_46

B20

VSS_47

D19

VSS_48

AB19

VSS_49

AA20

VSS_50

AC20

VSS_51

AE19

VSS_52

B18

VSS_53

D17

VSS_54

F17

VSS_55

E18

VSS_56

AB17

VSS_57

AA18

VSS_58

AC18

VSS_59

AE17

VSS_60

B16

VSS_61

D15

VSS_62

F15

VSS_63

AB15

VSS_64

AA16

VSS_65

AC16

VSS_66

AE15

VSS_67

B14

VSS_68

D13

VSS_69

F13

VSS_70

C1

NC

AF17

NC

Decouping Recommendation

Underneath balls

VCCT

on solder side

On the peripheral

near balls

Bulk Caps

Place close to

processor for

all

Bulk Caps

VCC_CORE

VSS_142

VSS_141

VSS_140

VSS_139

VSS_138

VSS_137

VSS_136

VSS_135

VSS_134

VSS_133

VSS_132

VSS_131

VSS_130

VSS_129

VSS_128

VSS_127

VSS_126

VSS_125

VSS_124

VSS_123

VSS_122

VSS_121

VSS_120

VSS_119

VSS_118

VSS_117

VSS_116

VSS_115

VSS_114

VSS_113

VSS_112

VSS_111

VSS_110

VSS_109

VSS_108

VSS_107

VSS_106

VSS_105

VSS_104

VSS_103

3/4

VSS_102

VSS_101

VSS_100

VSS_99

VSS_98

VSS_97

VSS_96

VSS_95

VSS_94

VSS_93

VSS_92

VSS_91

VSS_90

VSS_89

VSS_88

VSS_87

VSS_86

VSS_85

VSS_84

VSS_83

VSS_82

VSS_81

VSS_80

VSS_79

VSS_78

VSS_77

VSS_76

VSS_75

VSS_74

VSS_73

VSS_72

VSS_71

TUAL700

71.TULAT.G0U

0.47uF * 24

10uF / 6.3V * 10

1uF * 10

F19

E20

C25

A25

AE1

AD2

AB2

Y2

V2

T2

P2

M2

K2

H2

F2

D2

B2

W4

U4

M3

K4

H4

F4

D4

B4

AE5

AC6

AA6

AB5

W6

Y5

U6

V5

R6

T5

L6

N6

J6

K5

G6

H5

F5

B6

AE7

AC8

AA8

AB7

E8

F7

D7

B8

AE9

AC10

AA10

AB9

E10

F9

D9

B10

AE11

AC12

AA12

AB11

E12

F11

D11

B12

AE13

AC14

AA14

AB13

E14

N4

NC

AGTLREF4,7

VCC_CORE_S0

BC174

SC10U10V-U

78.10613.2A1

VCC_CORE_S0

BC208

SCD1U16V3KX

VCC_CORE_S0

BC182

SCD1U16V3KX

Use 2-3 vias per pad for reduced

inductance during layout

Placement should be near

processor for all

Use 2 vias per pad for reduced

inductance during layout

Almador-M Checklist Ver. 0.5 8/28

BC215

BC147

BC168

SC1U10V3ZY

BC184

SC1U10V3ZY

SC1U10V3ZY

78.10593.4B1

SC1U10V3ZY

GTLREF( 2/3 +VCCT)

VCCT_S0 1D5V_S0

12

R289

1KR3F

12

R288

2KR3F

BC255

SCD1U16V3KX

Place resistors

between GMCH

and CPU

BC167

SCD1U16V3KX

BC149

SCD1U16V3KX

BC221

SCD1U16V3KX

CMOSREF ( 2/3 1.5V )

CPU_CMOSREF4

Place caps near CPU

VCC_CORE_S0

BC212

SC10U10V-U

78.10613.2A1

BC175

SCD1U16V3KX

BC169

SCD1U16V3KX

BC210

SC10U10V-U

78.10613.2A1

BC218

SCD1U16V3KX

BC146

SCD1U16V3KX

TM100

0.1uF * 24

10uF / 10V * 10

220uF / 2.5V * 8

1uF * 10

220uF / 2.5V * 2

BC176

SC10U10V-U

78.10613.2A1

BC206

SCD1U16V3KX

BC216

SCD1U16V3KX

BC173

SCD1U16V3KX

BC207

SCD1U16V3KX

Ver. 0.1

10uF / 6.3V * 12

10uF / 6.3V * 10 + 6 * NS

150uF / 4V * 12 + 2 * NS

1uF * 10 + 2 * NS

150uF / 4V * 5 + 1 * NS

BC180

SCD1U16V3KX

BC217

SCD1U16V3KX

BC150

SCD1U16V3KX

BC177

SCD1U16V3KX

BC179

SCD1U16V3KX

BC170

SCD1U16V3KX

BC213

SCD1U16V3KX

BC214

SCD1U16V3KX

BC178

SCD1U16V3KX

BC209

SCD1U16V3KX

BC172

SCD1U16V3KX

BC181

SCD1U16V3KX

BC261

BC205

SC1U10V3ZY

SC1U10V3ZY

BC259

R247

1KR3F

R248

2KR3F

BC256

SC1U10V3ZY

BC220

SCD1U16V3KX

SC1U10V3ZY

12

12

Place caps near CPU

BC171

SCD1U16V3KX

BC211

SCD1U16V3KX

BC148

SC1U10V3ZY

BC183

SC1U10V3ZY

VCCT_S0

BC219

SCD1U16V3KX

U5D

A26

VCCT_1

G23

VCCT_2

J23

VCCT_3

L23

VCCT_4

N23

VCCT_5

R23

VCCT_6

U23

VCCT_7

W23

VCCT_8

AA23

VCCT_9

C21

VCCT_10

C19

VCCT_11

AD20

VCCT_12

C17

VCCT_13

AD18

VCCT_14

C15

VCCT_15

AD14

AD12

AC23

C13

C11

AD8

AD6

AA4

AC4

AE3

AF2

AF1

CPU

VCCT_16

VCCT_17

VCCT_18

VCCT_19

C9

C7

C5

E4

G4

J4

L4

V4

4/4

VCCT_20

VCCT_21

VCCT_22

VCCT_23

VCCT_24

VCCT_25

VCCT_26

VCCT_27

VCCT_28

VCCT_29

VCCT_30

VCCT_31

VCCT_32

VCCT_33

VCCT_34

VCCT_35

VTTPWRGOOD

TUAL700

71.TULAT.G0U

Title

Size Document Number Rev

Custom

Date: Sheet of

AD4

NC_1

A5

NC_2

D1

NC_3

AD13

NC_4

B1

NC_5

P26

NC_6

A11

NC_7

VCCT_36

VCCT_37

VCCT_38

VCC_CORE_S04,27

VCCT_S04,6,7,28

1D5V_S04,28

VID0

VID1

VID2

VID3

VID4

VSS

VSS

VSS

NC

NC

VCCT_S0

A2

AE18

AB1

AC2

AE2

AF3

R3

B26

M4

AF26

E3

D26

VCCT_S0

D5

E6

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

CPU 2/2 CONFIGURATION

TM100

CPU_VID0 27

CPU_VID1 27

CPU_VID2 27

CPU_VID3 27

CPU_VID4 27

VTTPWRGOOD_1D2 28

VCC_CORE_S0

VCCT_S0

1D5V_S0

5 35Thursday, April 04, 2002

-1

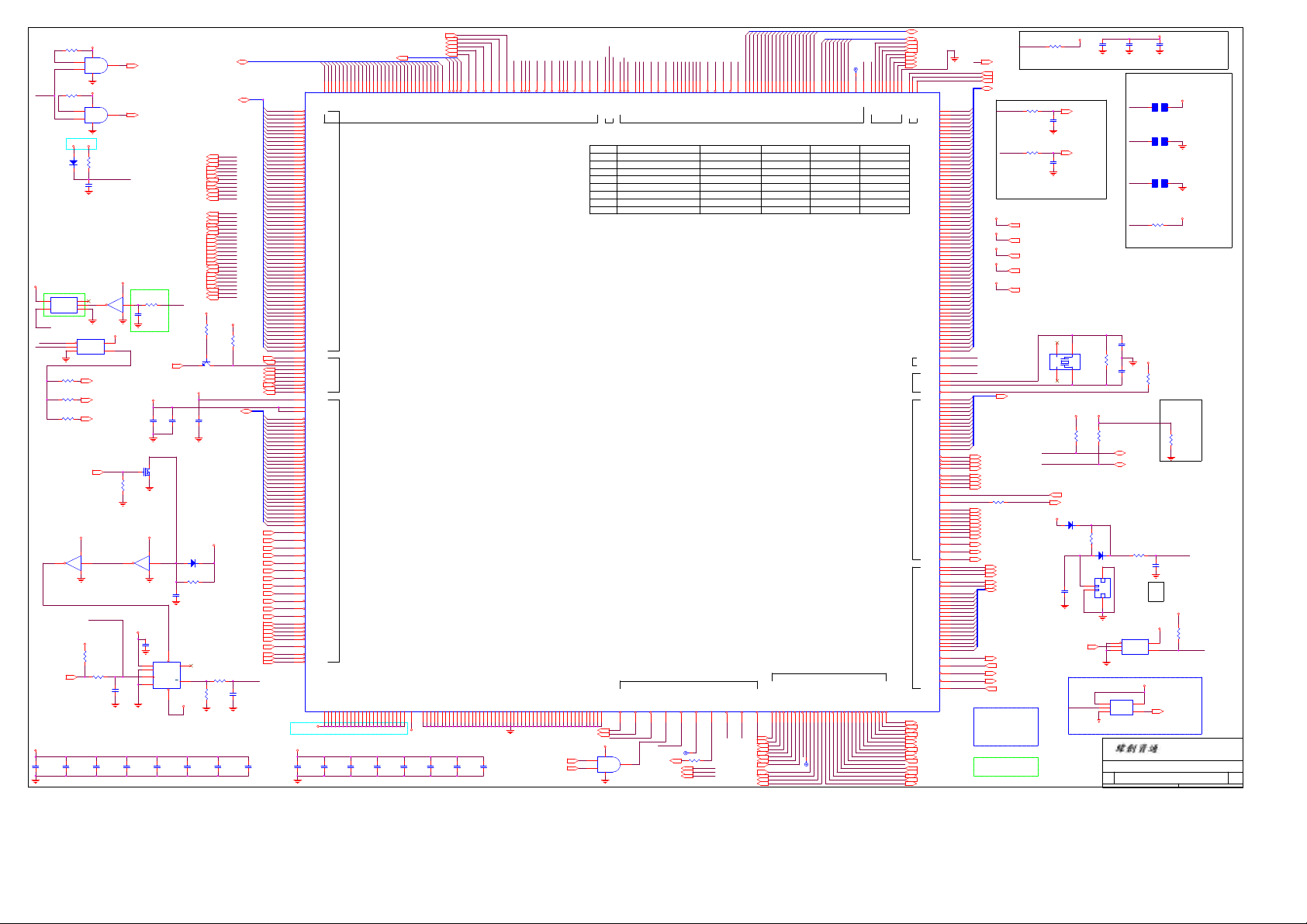

BAN_G_LO/HI#7

R101

10KR3

63.10334.151

GTL_CPURST#4,7

3D3V_S0

12

VCORE_OK27

1 2

BAN_INIT#

BAN_INTR

BAN_NMI

BAN_SMI#

SB->SC

R88

Dummy-10KR3

ZZ.10334.151

VCCT_OK27,28

R277

DUMMY-0R3-0-U

1 2

SC->SD

RP1

1

2

3

4

5 6

SRP10K

66.10336.100

3D3V_S0 3D3V_S0

3D3V_S0

12

R276

Dummy-10KR3

ZZ.10334.151

BAN_NMI7

BAN_INTR7

BAN_INIT#7

BAN_SMI#7

BAN_STPCLK#7

BAN_CPUSTP#7

DUMMY-0R3-0-U

1 2

VCCT_S0

1

2

Q26

MMBT3904-U

84.T3904.011

R85

3

12

R230

10KR3

63.10334.151

ISSCL_IGN_VGATE#

ISSCL_VR100-50#

ISSCL_PLL30-60#

3D3V_S0

12

R87

10KR3

63.10334.151

12

R102

4K7R3

63.47234.151

3D3V_S0

12

10

9

8

7

R89

10KR3

63.10334.151

14MGCL_D33

3D3V_S0

BAN_STPCLK#

R91 0R3-0-U

63.R0004.151

1 2

1 2

R90 0R3-0-U

63.R0004.151

1 2

R231

0R3-0-U

63.R0004.151

TP4

TPAD30

ISSCL_A20M#

ISSCL_IGNNE#

ISSCL_SUSSTAT#

ISSCL_CPU_STP#

ISSCL_CLK_OUT

ISSCL_CLKEN#

R273

10KR3

63.10334.151

3D3V_S0

VCCT_S0

20

16

22

24

21

17

23

19

13

14

15

29

43

28

44

41

26

25

45

37

36

38

3D3V_S0

12

U42

ISSCL+-U

71.ISSCL.00G

NMI

INTR

INIT#

A20M#

IGNNE#

SMI#

STP_CLK#

SUSSTAT1#

CPU_STP#

G_LO_HI#

VR_ON

VGATE

IGN_VGATE#

VR100/50#

PLL30/60#

CRESET#

CLK_IN

CLK_OUT

CLKEN#

DPRSLPIN#

DPRSLPVR

RSVD2

3D3V_S0 3,7,8,11,12,13,14,15,16,17,19,20,23,24,25,26,27,28,30,35

VCCT_S0 4,5,7,28

1

G_NMI

4

G_INTR

8

G_INIT#

48

ISSCL_CPU_A20M#

2

ISSCL_CPU_IGNNE#

5

3

11

ISSCL_CPU_SUSSTAT1#

47

46

ISSCL_RSVD1

10

9

32

ISSCL_PWRGD

12

33

ISSCL_VR_HI-LO#

34

ISSCL_LP_TRANS#

35

ISSCL_TCLKOUT

39

ISSCL_TMODE2

40

ISSCL_TMODE1

G_STPCLK#

G_SUSSTAT1#

STP_CPU_STP#

CPUPWRGD

LP_TRANS#

GND_16VCC3_1

GND_2

GND_4

GND_331VCC3_2

GND_5

7

18

42

30

27

BC199

SCD1U

78.10492.4B1

G_A20M#

G_IGNNE#

G_SMI#

RSVD1

LO/HI#

VRPWRGD

VRCHGNG#

VR_HI/LO#

TCLKOUT

TMODE2

TMODE1

3D3V_S0

1 2

R275

0R3-0-U

63.R0004.151

TP27

TPAD30

TP26

TPAD30

CC_NMI 4

CC_INTR 4

CC_INIT# 4

CC_SMI# 4

CC_STPCLK# 4

TP19

TPAD30

TP17

TPAD30

TP24 TPAD30

TP25 TPAD30

3D3V_S0

TP16

TPAD30

12

TP18

R86

TPAD30

10KR3

63.10334.151

CC_PERF# 4

CC_CPUPWRGD 4

ISSCL_VR_PWRGD 7

12

R226

10KR3

63.10334.151

CC_CPUSTP# 3,27

VR_CHGNG#_3 7

Non-Speedstep Option

R274

BAN_INTR

BAN_SMI#

BAN_INIT#

BAN_NMI

BAN_CPUSTP#

BAN_STPCLK#

VCORE_OK

12

ISSCL_VR_PWRGD

1 2

1

2

3

4 5

1

2

3

4 5

D24

DUMMY-BAT54

ZZ.00054.081

Dummy-10KR3

ZZ.10334.151

RN1

Dummy-SRN0-1

ZZ.R0035.08A

RN2

Dummy-SRN0-1

ZZ.R0035.08A

CC_CPUPWRGD

ISSCL_VR_HI-LO#

CC_INTR

8

CC_SMI#

7

CC_INIT#

6

CC_NMI

CC_CPUSTP#

8

7

CC_STPCLK#

6

ISSCL_VR_PWRGD

12

D25

DUMMY-BAT54

ZZ.00054.081

VCORE_OK

PM_DPRSLPIN#7

PM_DPRSLPVR27

VCCT_OK

D20

S1N4148

83.04148.011

SC10U10V6ZY-U

78.10693.4I1

12

1 2

BC201

R227

270KR3

64.27035.651

BC244

SCD1U

78.10492.4B1

3D3V_S0

147

3 4

ISSCL_VR_HI-LO#

U58B

TSLCX14

73.07414.X2B

R300

0R3-0-U

1 2

63.R0004.151

3D3V_S0

U56A

147

1

2

3

TSLCX32

73.07432.X2B

R301

Dummy-0R3-0-U

1 2

ZZ.R0004.151

CORE_ZMODE 27

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

Size Document Number Rev

A3

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

ISSCL+

TM100

6 35Thursday, April 04, 2002

-1

3D3V_S0

R340 10KR3

1 2

63.10334.151

4

5

3D3V_S0

R317 10KR3

1 2

PCIRST#

63.10334.151

9

10

3D3V_S3 5V_S3

12

12

D9

BAT54

12

BC110

SC1U10V3ZY

ref. for 5V tolerance,

need check sequence

with VCC(3V)

3D3V_S5

SC->SD

U98

1

5

NC

VCC

2

A

4

GND3Y

NC7SZ14

73.7SZ14.0AH

SUSB#

U62

1

SUSB

OE#

BAN_SUSCLK_1

2

A

GND3Y

NC7SZ125

73.7S125.0AH

R371

10R3

1 2

R373

10R3

1 2

R372

10R3

1 2

HW_THRM_SDN12

SUSPEND/RESUME BUTTON

U60A

147

TSLCX14

73.07414.X2B

12

(PX4 HAS 16MS DEBUNCE)

3D3V_S5

12

1 2

PWRBTN#12

3D3V_S0

BC284

BC286

SCD01U50V3KX

SCD01U50V3KX

U57B

147

6

PCIRST1# 9,13,14,15,24

TSLCX08

73.07408.X2B

U57C

147

8

PCIRST2# 11,16,17,19,23

TSLCX08

73.07408.X2B

SE->-1

R139

1KR3

MX_VREF

3D3V_S5

U60D

SC->SD

TSLCX14

73.07414.X2B

147

98

SUSB PRE_SUSB#

3D3V_S5

5

VCC

32K suspend

4

32KHZ

clock

output

G768_32K 12

OZ711_32K 14

OZSW_32K 15

1

G

12

R341

10KR3

63.10334.151

BAN_PWRBTN#

3D3V_S5

R338

10KR3

R339

1KR3

BC278

SCD1U

PCI_PLOCK#13,14

R565

10KR3

1 2

63.10334.151

BC495

SCD1U

CC_FERR#4

take care Layout

VCCT_S0

BC282

BC280

SCD1U

SCD1U

D

Q27

2N7002

S

84.27002.031

2 3

3D3V_S53D3V_S5

U60B

147

TSLCX14

73.07414.X2B

1 2

34

1 2

BC293

SCD1U

BC277

SCD1U

U59A

4

5

14

Q

VCC

2

PR

D

3

CLK

6

Q

7

GND

CL

TSLCX74

1

73.07474.X2B

3D3V_S5

PCI_TRDY#9,13,14,16,17,19

PCI_STOP#9,13,14,16,17,19

PCI_SERR#13,14,16,17,19

PCI_REQ#213,16

PCI_REQ#19,13

PCI_REQ#013,17,19

PCI_INTB#13,17,24

PCI_INTA#9,13,14

PCI_GNT#213,16

PCI_GNT#19,13

PCI_GNT#013,17,19

RSTDRV_324,25

BIOSCS#_324

IOCHRDY_524,25

decouping CAP place at corner of MX

BC294

SCD01U50V3KX

BC299

SCD01U50V3KX

SCD01U50V3KX

BC279

SCD01U50V3KX

MEMW#_324,25

MEMR#_324,25

IRQ14_513,25

DACK#2_325

DACK#1_325

DACK#0_325

AGTLREF

D8

S1N4148

R351

100KR3

N1

M4

J1

L4

K2

OC0L1OC1

CLK48

USBP0-

USBP0+

VCCUSB

SMB

CRT/TEST

DRAM

IDE

GPIO27/DRQ3P5GPIO28/DACK3#P4GPIO29/REQ3#

GPIO26/KBCCS#

GPIO30/GNT3#

A4

B5

USBP1+

L2

K1

USBP1-

VSSUSB

AC'97USB

SA[0..18] 23,24,25

SD[0..7] 23,24,25

48M_P4 3

USB_OC0# 26

USB_OC1# 26

USBP0+ 26

USBP0- 26

USBP1+ 26

USBP1- 26

U18

C1

E1

MD0

AC_BIT_CLK

MD1

AC_DATA_IN0D2AC_DATA_IN1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

SMBDATA

SMBCLK

VCCRTC

RTCX1

RTCX2

TEST#

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

CKE0#

CKE1#

CKE2#

CKE3#

CS0#

CS1#

CS2#

CS3#

DCLK

DCLKO

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

SCAS#

SRAS#

WE#

PDA0

PDA1

PDA2

PDCS1#

PDCS3#

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

PDDACK#

PDDRQ

PDIOR#

PDIOW#

PIORDY

PCI_GNT#3 13,14

PCI_REQ#3 13,14

DACK#3_3 25

DRQ3_5 25

KBCCS# 23

ECCS# 23

VGA_PDOWN# 9

PCI_INTD# 13,14,16,17,19

PCI_INTC# 13,16,17,19,24

REMOTE_CTRL_EN# 25

AD_OFF 31

BL2# 11,23,33

BOOTBLOCK 23

BTN_CLK# 24

DIMM_SEL 8

MX_SPKR 20

AE9

AF9

AF10

AE10

AD9

AC10

AE11

AF11

AF12

AF13

AE12

AD15

AE13

AF14

AF15

AE14

AB20

AC21

AB22

AB21

Y21

AA22

AC23

AC22

AB23

AA23

Y22

W22

W21

W23

Y23

W24

AC9

AB10

AC11

AB11

AC12

AD11

AB12

AD13

AB14

AC13

AD12

AC14

AB15

AB16

AC15

AD17

AE23

AE24

AF23

AF24

AE25

AD23

AE26

AF25

AB26

AA26

AA25

AB24

Y24

Y25

Y26

V22

J2

J3

N2

M1

M3

K5

AE18

AC17

AC19

AE19

AC18

AB18

AD20

AE20

AF20

AE21

AE22

AD21

AF21

AF22

AA18

AB17

AB19

AC20

AF19

AE17

AD19

AC16

AB25

AC24

AD16

AF16

AD25

AC25

AE15

AF17

AD26

AC26

AF18

AE16

AA19

AF8

AA6

AD7

AB6

AC5

AA7

AE6

AD5

AD8

AE5

AC7

AB8

AA8

AB9

AA10

AC8

AE7

AA9

AF7

AE8

AC6

AB5

AF5

AF6

AB7

AA5

82440MX-100

M_MD0

M_MD1

M_MD2

M_MD3

M_MD4

M_MD5

M_MD6

M_MD7

M_MD8

M_MD9

M_MD10

M_MD11

M_MD12

M_MD13

M_MD14

M_MD15

M_MD16

M_MD17

M_MD18

M_MD19

M_MD20

M_MD21

M_MD22

M_MD23

M_MD24

M_MD25

M_MD26

M_MD27

M_MD28

M_MD29

M_MD30

M_MD31

M_MD32

M_MD33

M_MD34

M_MD35

M_MD36

M_MD37

M_MD38

M_MD39

M_MD40

M_MD41

M_MD42

M_MD43

M_MD44

M_MD45

M_MD46

M_MD47

M_MD48

M_MD49

M_MD50

M_MD51

M_MD52

M_MD53

M_MD54

M_MD55

M_MD56

M_MD57

M_MD58

M_MD59

M_MD60

M_MD61

M_MD62

M_MD63

MX_SMB_DATA

MX_SMB_CLK

M_MA0

M_MA1

M_MA2

M_MA3

M_MA4

M_MA5

M_MA6

M_MA7

M_MA8

M_MA9

M_MA10

M_MA11

M_MA12

M_MA13

CLK_DBUF

M_DQM0

M_DQM1

M_DQM2

M_DQM3

M_DQM4

M_DQM5

M_DQM6

M_DQM7

M_SCAS#

M_SRAS#

M_BMWE#

PIDE_A0_3

PIDE_A1_3

PIDE_A2_3

PIDE_CS1#_3

PIDE_CS3#_3

PIDE_D0

PIDE_D1

PIDE_D2

PIDE_D3

PIDE_D4

PIDE_D5

PIDE_D6

PIDE_D7

PIDE_D8

PIDE_D9

PIDE_D10

PIDE_D11

PIDE_D12

PIDE_D13

PIDE_D14

PIDE_D15

PIDE_DACK#_3

PIDE_DRQ_5

PIDE_IOR#_3

PIDE_IOW#_3

PIDE_IORDY_3

BAN_AC_RST# 19,20PCI_AD[0..31]9,14,16,17,19

BAN_AC_BITCLK 20

BAN_AC_DIN0 20

BAN_AC_DIN1 19

M_MD[0:63] 8

3D3V_S0

5V_S0

3D3V_S5

AGTLREF

VCCT_S0

VCCRTC

M_CKE0 8

M_CKE1 8

M_CKE2 8

M_CKE3 8

M_CS#0 8

M_CS#1 8

M_CS#2 8

M_CS#3 8

1 2

M_DQM0 8

M_DQM1 8

M_DQM2 8

M_DQM3 8

M_DQM4 8

M_DQM5 8

M_DQM7 8

M_SCAS# 8

M_SRAS# 8

M_BMWE# 8

SB->SC

Change

GPIO2 to MP_COMMAND

GPIO3 to MP_ACK

GPIO6 to OBLAN-80211#

GPIO20 to AD_OFF

GPIO29 to PCI_REQ#3

GPIO30 to PCI_GNT#3

SC->SD

Change

GPIO9 : Use

OBLAN-80211# to

replace 802.11LED#

R355 0R3-0-U

1 2

USBPWR

63.R0004.151

R353

BAN_AC_DOUT1

1 2

10R3

BC295

SC22P

R365

BAN_AC_SYNC1

1 2

22R3

BC311

SC22P

For AC-link

waveform

3D3V_S0 3,6,8,11,12,13,14,15,16,17,19,20,23,24,25,26,27,28,30,35

5V_S0 10,11,12,13,15,19,20,22,23,24,25,26,27,28,29,30,33,35

3D3V_S5 17,19,23,29,30,31,34,35

AGTLREF 4,5

VCCT_S0 4,5,6,28

*Layout*

(10,10)

mil

2 3

MX_RTCX1

MX_RTCX2

MX_SMB_CLK

MX_SMB_DATA

3D3V_S5

BC126

SCD1U

PX4_TEST#

DCLKIN 3

CLKDBUF 3

1 2

THERM_ALERT#12

D11

BAT54

M_MA[0:13] 8

R32022R2

63.22034.1D1

PIDE_A0_3 13

PIDE_A1_3 13

PIDE_A2_3 13

PIDE_CS1#_3 13

PIDE_CS3#_3 13

PIDE_D[0..15] 13

PIDE_DACK#_3 13

PIDE_DRQ_5 13

PIDE_IOR#_3 13

PIDE_IOW#_3 13

PIDE_IORDY_3 13

3D3V_S5

SC1000P50V3KX

Place near USBVCC (pin L5)

BAN_AC_DOUT 19,20

BAN_AC_SYNC 19,20

R138

41

1MR3

X1

1 2

X4P-32.768KHZ-2

82.30001.121

3D3V_S03D3V_S0

12

12

R375

R376

4K7R3

4K7R3

12

R155

2KR3

63.20234.151

D10

1 2

BAT54

34

1

2

SA->SB

1

SOUNDTHEAD#

2

AUD_AGND

Title

Size Document Number Rev

D

Date: Sheet of

PCLK_MX3

PCI_PAR9,14,16,17,19

PCI_IRDY#9,13,14,16,17,19

PCI_FRAME#9,13,14,16,17,19

PCI_DEVSEL#9,13,14,16,17,19

PCI_AD11

D10

PCI_AD12

AD12E9AD13

PCI_AD13

A11

PCI_AD14

A10

AD14

PCI_AD15

PCI_AD16

B11

AD15

PCI_AD17

D11

AD16C9AD17

PCI_AD18

E10

AD18

PCI_AD19

C10

AD19

PCI_AD20

PCI_AD21

B14

C12

AD20

AD21

PCI_AD22

E13

AD22

PM_CLKRUN#13,14,16,19

PCI_AD23

D12

AD23

PCI_AD24

C11

AD24

PCI_AD25

A16

AD25

PCI_AD26

B15

AD26

PCI_AD28

PCI_AD27

C13

A17

AD27

PCI_AD29

B16

AD28

AD29

PCI_AD30

B13

AD30

PCI_AD31

C15

AD31

PCI_C/BE#0

PCI_C/BE#1

B10

C/BE0#B6C/BE1#

PCI_C/BE#3

PCI_C/BE#2

A13

D13

C/BE2#

C/BE3#

PCIRST#

PCI_INTB#

PCI_INTA#

PCI_GNT#2

PCI_GNT#1

PCI_GNT#0

B17

E8

A12

D9

B12

A15

E12

E15

C16

D14

E5

PAR

IRDY#

PCICLK

PIRQA#D5PIRQB#

PGNT0#

PGNT1#

PCIRST#

PGNT2#

CLKRUN#

DEVSEL#

FRAME#

PCI BUS I/F X BUS I/F

*Layout*

GTL+ :

(5,5)

mil

MX_VREF

PCI_PLOCK#

PCI_REQ#2

PCI_REQ#0

PCI_REQ#1

BAN_AC_RST#

BAN_AC_SYNC1

PCI_TRDY#

PCI_SERR#

PCI_STOP#

BAN_AC_DOUT1

D15

A14

E14

D8

F9

F10

F7

F2

G5

D1

VREF

STOP#

SERR#

TRDY#

PLOCK#F8PREQ0#

PREQ1#

PREQ2#

AC_RST#

AC_SYNC

AC_SDATA_OUT

AC'97

MA12#

MA11#

MA8#

MA9# pull-down

MA1#

IOW#_3

DRQ0_5

DRQ1_5

DACK#2_3

IRQ1_5

DRQ2_5

IRQ4_5

IRQ7_5

IRQ6_5

IRQ5_5

IOR#_3

DACK#0_3

IOCHRDY_5

DACK#1_3

AA4

AB1

AE4

U4

R1

Y4

DREQ0

DREQ1V1DREQ2

DACK0#

DACK1#Y5DACK2#

IOCHRDY

System frequence select

In-Order Queue Depth Enable pull-up

Quick Start Select pull-up

High Frequency VCO(Host PLL)

CPU clock ratio : sets NMIMA13#

CPU clock ratio : sets INTR

CPU clock ratio : sets IGNNE#

CPU clock ratio : sets A20M#

MEMR#_3

IRQ3_5

IRQ14_5

IRQ12_5

U3

AD2

AF3

AE3

AF2

F5

IOR#

IRQ1

IRQ3Y3IRQ4

IRQ5W6IRQ6Y2IRQ7

IOW#

IRQ12

IRQ14

82443MX-100MHZ

(BANISTER)

PM

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSSA1VSSF3VSS

VSSN3VSSW3VSS

VSSC7VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCCSUS

K6

L13

L14

L16

T13

T14

T16

P16

N16

G21

AA21

AD24

3D3V_S5

BC287

BC289

SCD1U

SCD1U

L12

AF1

R11

AD6

M11

BC310

SCD1U

L15

T12

P12

N12

BC288

SCD1U

T15

P13

P14

P15

N13

R13

N14

R14

N15

M13

M14

BC94

SCD1U

E24

R16

C19

R12

C22

R15

M16

M12

M15

AD10

AD18

ISSCL_VR_PWRGD6

PWRGOOD_312

VSS

F21

P24

A26

K24

H24

C14

U24

AF26

AA20

AA24

AD14

AD22

BAN_CPUSTP#6

CLK_PCI_STOP#3

3D3V_S0

147

12

13

CPUSTP#D3PCISTP#

BAN_PWRBTN#

U57D

11

TSLCX08

73.07408.X2B

PWRBTN#H2PWROK

RSMRST#M5SUS_STAT#

RSMRST#

PRE_SUSC#12,23,30

L3

M2

TP29TPAD30

R367 10R3

1 2

SUSA#

SUSA#3

SUSB#

SUSB#30,31

PRE_SUSC#

E4

BAN_SUSCLK9

U1

MEMR#

1 ( no pipelining )

Stop Clock ModeMA10#

slow speed

NMI low

INTR low

IGNNE# lowMA7#

A20M# low

PCI_C/BE#[0..3]9,14,16,17,19

PCI_AD10

PCI_AD5

PCI_AD3

PCI_AD0

PCI_AD2

PCI_AD4

PCI_AD1

PCI_AD8

PCI_AD9

PCI_AD7

PCI_AD6

B9

M24

M23

M22

M25

M26

W25

W26

3D3V_S0

AD0D7AD1A5AD2B8AD3E7AD4B7AD5A9AD6A6AD7A7AD8A8AD9

G24

HD0#

G26

HD1#

E26

HD2#

D24

HD3#

H26

HD4#

F25

HD5#

J25

HD6#

E25

HD7#

H21

HD8#

J22

HD9#

G25

HD10#

F23

HD11#

G23

HD12#

C25

HD13#

F26

HD14#

H25

HD15#

B25

HD16#

F24

HD17#

D25

HD18#

D26

HD19#

D23

HD20#

C24

HD21#

G22

HD22#

H22

HD23#

B24

HD24#

E22

HD25#

C26

HD26#

C23

HD27#

A23

HD28#

A25

HD29#

E23

HD30#

B26

HD31#

E21

HD32#

B23

HD33#

C21

HD34#

A24

HD35#

B22

HD36#

D21

HD37#

F19

HD38#

D22

HD39#

C17

HD40#

B20

HD41#

A21

HD42#

B21

HD43#

D20

HD44#

D19

HD45#

E20

HD46#

F18

HD47#

E19

HD48#

C20

HD49#

E16

HD50#

A22

HD51#

C18

HD52#

A20

HD53#

E17

HD54#

D18

HD55#

D17

HD56#

B19

HD57#

A19

HD58#

E18

HD59#

B18

HD60#

F17

HD61#

A18

HD62#

D16

HD63#

C4

A20GATE

B4

A20M#

B1

FERR#

A2

IGNNE#

B2

INIT#

B3

INTR

A3

NMI

D4

RCIN#

C2

SMI#

E3

STPCLK#

F22

GTLREF

K21

VTTA

F20

VTTB

P25

HA3#

R23

HA4#

N22

HA5#

R25

HA6#

P22

HA7#

N24

HA8#

T25

HA9#

P23

HA10#

HA11#

HA12#

HA13#

P26

HA14#

N26

HA15#

L22

HA16#

L26

HA17#

J21

HA18#

N25

HA19#

K23

HA20#

L23

HA21#

HA22#

K22

HA23#

L25

HA24#

HA25#

J23

HA26#

H23

HA27#

N23

HA28#

L24

HA29#

K26

HA30#

K25

HA31#

V26

ADS#

R26

BNR#

R24

BPRI#

BREQ0#

J26

CPURST#

U21

DBSY#

R22

DEFER#

U22

DRDY#

J24

HCLKIN

V23

HIT#

U26

HITM#

U23

HLOCK#

T26

HREQ0#

T23

HREQ1#

T22

HREQ2#

V25

HREQ3#

U25

HREQ4#

T24

HTRDY#

RS0#

V24

RS1#

V21

RS2#

3D3V_S3

BC300

SCD1U

AD10C8AD11

HOST BUS

CPU SIDEBAND

HOST BUS

PWR GND

VCCC3VCC

VCCG6VCCY6VCC

VCC

VCC

VCC

VCC

VCC

L11

T11

E11

P11

N11

AD3

AB13

AA17

BC312

BC298

SCD1U

SCD1U

GTL_HD#[0..63]4

TC_325

14M_P43

IRQ12_523,25

IRQ7_525

IRQ6_525

IRQ5_525

IRQ4_525

IRQ3_525

IRQ1_523,25

IOW#_323,24,25

IOR#_323,24,25

DRQ2_525

DRQ1_525

DRQ0_525

VCCT_S0

12

R342

1KR3

63.10234.151

FERR_B

2

31

Q28

S2N3904-U1

84.03904.011

GTL_HA#[3..31]4

BC281

SCD1U

78.10492.4B1

3D3V_S5

R349

1 2

12

10KR3

R350

1MR3

GTL_HD#0

GTL_HD#1

GTL_HD#2

GTL_HD#3

GTL_HD#4

GTL_HD#5

GTL_HD#6

GTL_HD#7

GTL_HD#8

GTL_HD#9

GTL_HD#10

GTL_HD#11

GTL_HD#12

GTL_HD#13

GTL_HD#14

GTL_HD#15

GTL_HD#16

GTL_HD#17GTL_HD#17

GTL_HD#18GTL_HD#18

GTL_HD#19GTL_HD#19

GTL_HD#20GTL_HD#20

GTL_HD#21GTL_HD#21

GTL_HD#22GTL_HD#22

GTL_HD#23GTL_HD#23

GTL_HD#24GTL_HD#24

GTL_HD#25GTL_HD#25

GTL_HD#26GTL_HD#26

GTL_HD#27GTL_HD#27

GTL_HD#28GTL_HD#28

GTL_HD#29GTL_HD#29

GTL_HD#30GTL_HD#30

GTL_HD#31GTL_HD#31

GTL_HD#32GTL_HD#32

GTL_HD#33GTL_HD#33

GTL_HD#34GTL_HD#34

GTL_HD#35GTL_HD#35

GTL_HD#36GTL_HD#36

GTL_HD#37GTL_HD#37

GTL_HD#38GTL_HD#38

GTL_HD#39GTL_HD#39

GTL_HD#40GTL_HD#40

GTL_HD#41GTL_HD#41

GTL_HD#42GTL_HD#42

GTL_HD#43GTL_HD#43

GTL_HD#44GTL_HD#44

GTL_HD#45GTL_HD#45

GTL_HD#46GTL_HD#46

GTL_HD#47GTL_HD#47

GTL_HD#48GTL_HD#48

GTL_HD#49GTL_HD#49

GTL_HD#50GTL_HD#50

GTL_HD#51GTL_HD#51

GTL_HD#52GTL_HD#52

GTL_HD#53GTL_HD#53

GTL_HD#54GTL_HD#54

GTL_HD#55GTL_HD#55

GTL_HD#56GTL_HD#56

3D3V_S0

GTL_HD#57GTL_HD#57

GTL_HD#58GTL_HD#58

12

GTL_HD#59GTL_HD#59

R343

GTL_HD#60GTL_HD#60

10KR3

GTL_HD#61GTL_HD#61

GTL_HD#62GTL_HD#62

63.10334.151

GTL_HD#63GTL_HD#63

A20GATE23

CC_A20M#4

BANFERR#

CC_IGNNE#4

BAN_INIT#6

BAN_INTR6

BAN_NMI6

KBDCPURST23

BAN_SMI#6

BAN_STPCLK#6

GTL_HA#3

GTL_HA#4

GTL_HA#5

GTL_HA#6

GTL_HA#7

GTL_HA#8

GTL_HA#9

GTL_HA#10

GTL_HA#11

GTL_HA#12

GTL_HA#13

GTL_HA#14

GTL_HA#15

GTL_HA#16

GTL_HA#17

GTL_HA#18

GTL_HA#19

GTL_HA#20

GTL_HA#21

GTL_HA#22

GTL_HA#23

GTL_HA#24

GTL_HA#25

GTL_HA#26

GTL_HA#27

GTL_HA#28

GTL_HA#29

GTL_HA#30

GTL_HA#31

GTL_ADS#4 M_DQM6 8

GTL_BNR#4

GTL_BPRI#4

GTL_BREQ#04

GTL_CPURST#4,6

GTL_DBSY#4

GTL_DEFER#4

GTL_DRDY#4

CLK_CPUCLK03,4

GTL_HIT#4

GTL_HITM#4

GTL_LOCK#4

GTL_REQ#04

GTL_REQ#14

GTL_REQ#24

GTL_REQ#34

GTL_REQ#44

GTL_TRDY#4

GTL_RS#04

GTL_RS#14

GTL_RS#24

RSMRST#

BC292

SCD1U

SE->-1

BC301

SCD01U50V3KX

BC283

SCD01U50V3KX

BC285

MEMW#_3

14M_P4

U2

AB4

MEMW#

LowPIN NAME

SUSCLK

H1

BAN_SUSCLK_1

FLASH_GPIO133

FLASH_GPIO233

BIOSCS#_3

OSC

BIOSCS#R4RSTDRV

SUSA#G3SUSB#

SUSA#

MP_COMMAND11

VR_CHGNG#_36

PM_DPRSLPIN#6

OBLAN-80211#11,17

BAN_G_LO/HI#6

RSTDRV_3

T4

G2

PRE_SUSB#

BAN_PME#14,17,19,34

EC_SCI#23

MP_ACK11

SERIRQ#13,14,19

SW_WAKE#23

SA0

SA2

SA1

AC1

AE1

AD1

SA0

SA1

SA3

AE2

SA2

SA3

SUSC#G1GPIO0/PME#

PRE_SUSC#

SA10

SA4

SA5

SA6

SA7

SA8

SA9

AA2

AB2

AA3

AC4

AB3

W1

AA1

SA4

SA5

SA6

SA7

SA8

SA9

High

100MHz

Quick Start Mode

fast speed

NMI low

INTR low

IGNNE# low

A20M# low

GPIO1/GPI1F4GPIO2/REQA#

F1

D6

C5

SA13

SA11

SA12

AC2

AC3

SA10

SA11

SA12W5SA13

GPIO4J5GPIO5

GPIO3/GNTA#

H5

AF4

GPIO6/IRQ8#

SA16

SA17

SA14

SA15

SA14W2SA15Y1SA16U6SA17W4SA18

Internal ResistorFunction

GPIO9

GPIO7/SERIRQ

GPIO10/LIDH4GPIO11/BATLOW#H3GPIO12/RI#J4GPIO13R3GPIO14/SPKRP1GPIO15N5GPIO16/PCS1#P3GPIO17K4GPIO18G4GPIO19/PCS0#N4GPIO20

GPIO8/THERM#

J6

F6

H6

THRM#

GPIO9

TP41

TPAD30

ZZ.PAD30.XXX

SA18

SD0

U5

SD0V5SD1V2SD2T2SD3R2SD4V6SD5V4SD6T3SD7

pull-down66 MHz

pull-down

pull-down

pull-down

pull-down

GPIO

TP5TPAD30

SD4

SD6

SD2

SD7

SD3

SD1

SD5

TC_3

USBPWR

T1

V3TCAD4

L5

SYSCLK

Status Register

NBXCFG[13]

NBXCFG[3]4 (max )

PMCR[3]

GPIO21/ZEROWS#

GPIO22/PIRQC#C6GPIO23/PIRQD#

GPIO25/MCCS#

GPIO24/EXTSMI#

T5

K3

P2

E6

E2

R5

SOUNDTHEAD#

3D3V_S5

BC297

BC296

SCD1U

strapping resistor placed

less than 0.5 inch from

MA line routing

HOST_HFV

R131

M_MA8

1 2

DUMMY-R3

HIGH:FAST

NC: SLOW

QUICK START

SELECT

R130

M_MA10

1 2

DUMMY-R3

NC:QUICK START MODE

LOW:STOP CLOCK MODE

IN-ORDER QUEUE

DEPTH ENABLE

R132

M_MA11

1 2

DUMMY-R3

NC:IOQD=MAX(4)

LOW:IOQD=1

SYSTEM

FREQUENCE

R133

M_MA12

1 2

10KR3

HIGH:100MHZ

NC:66MHZ

BC114

SC30P

3D3V_S5

12

BC113

SC30P

R354

10KR3

Prevent

Resume Well

Leakage

MX_SMB_CLK 8,11,12

MX_SMB_DATA 8,11,12

RTC BATTERY 65mAH

P/N 23.20004.111

working voltage

2.0- 3.3V

R156

RTBATDRTBAT

1 2

1KR3

CN8

MLXCON2

21.D0010.102

+

-

3D3V_S0

U61

1

5

OE#

VCC

2

A

4

GND3Y

NC7SZ125

73.7S125.0AH

OP5VA_S0

U86

5

A

VCC

B

4

GND3Y

NC7SZ08

73.7SZ08.0AH

82440MX (BANISTER)

TM100

BC117

SC10U10V6ZY-U

78.10693.4I1

*Layout*

3D3V_S0

???WHAT

MX STRAPPING

OPTIONS

3D3V_S0

12

R377

100KR3

VCCRTC

BC130

SCD1U

1

3D3V_S0

12

R352

10KR3

THRM#

SOUNDTHEAD#_1 22

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

7 35Thursday, April 04, 2002

-1

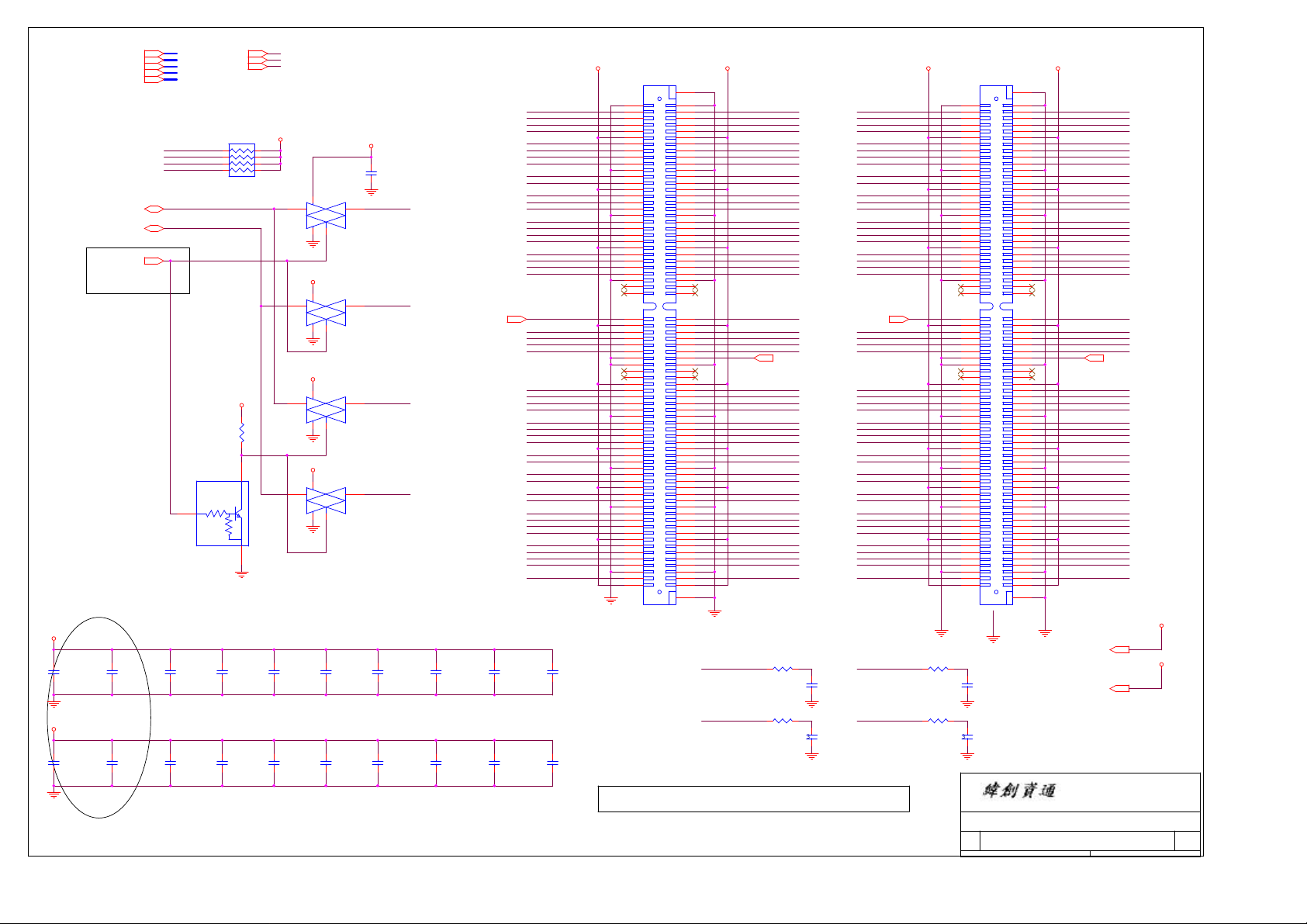

Cap. Height is

too high

3D3V_S3

BC89

SC4D7U16V6ZY-U

78.47591.421

3D3V_S3

BC275

SC4D7U16V6ZY-U

78.47591.421

M_MA[0..13]7

M_CS#[0..3]7

M_DQM[0..7]7

M_CKE[0..3]7

MX_SMB_DATA7,11,12

MX_SMB_CLK7,11,12

DIMM_SEL7

BC270

SC4D7U16V6ZY-U

78.47591.421

BC290

SC4D7U16V6ZY-U

78.47591.421

SDATA_DIMMA

SCLK_DIMMA

SDATA_DIMMB

SCLK_DIMMB

Q3

DTC124EUA-U

2

BC96

SCD1U

78.10492.4B1

BC87

SCD1U

78.10492.4B1

M_SCAS#7

M_SRAS#7M_MD[0..63]7

M_BMWE#7

2222K

R163

10KR3

6

7

8

K

RN5

SRN100K

66.10436.080

3D3V_S0

12

3D3V6_S0

31

BC95

SCD1U

78.10492.4B1

BC88

SCD1U

78.10492.4B1

45

3

2

1

3D3V_S3

147

1 2

3D3V_S3

147

11 10

3D3V_S3

147

4 3

3D3V_S3

147

8 9

BC86

SCD1U

78.10492.4B1

BC106

SCD1U

78.10492.4B1

13

12

5

6

BC99

SCD1U

78.10492.4B1

BC120

SCD1U

78.10492.4B1

3D3V_S3

U22A

SDATA_DIMMA

TSHC4066

73.04066.0AB

U22B

SCLK_DIMMA

TSHC4066

73.04066.0AB

U22C

SDATA_DIMMB

TSHC4066

73.04066.0AB

U22D

SCLK_DIMMB

TSHC4066

73.04066.0AB

BC131

SCD1U

78.10492.4B1

BC101

SC1000P50V3KX

BC108

SC1000P50V3KX

CLK_SDRAM03

BC107

SC1000P50V3KX

BC121

SC1000P50V3KX

SDATA_DIMMB

BC97

SC1000P50V3KX

BC109

SC1000P50V3KX

M_MD0

M_MD1

M_MD2

M_MD3

M_MD4

M_MD5

M_MD6

M_MD7

M_DQM0

M_DQM1

M_MA0

M_MA1

M_MA2

M_MD8

M_MD9

M_MD10

M_MD11

M_MD12

M_MD13

M_MD14

M_MD15

M_SRAS#

M_BMWE#

M_CS#0

M_CS#1

M_MD16

M_MD17

M_MD18

M_MD19

M_MD20

M_MD21

M_MD22

M_MD23

M_MA6

M_MA8

M_MA9

M_MA10

M_DQM2

M_DQM3

M_MD24

M_MD25

M_MD26

M_MD27

M_MD28

M_MD29

M_MD30

M_MD31

3D3V_S3 3D3V_S3

DM1

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

SDIMM144-U

62.10017.144

BC100

SC1000P50V3KX

BC129

SC1000P50V3KX

NOTE: NETWORK RESISTOR NEAR GMCH < 1.5 inch.

(Reverse Type)(Normal Type)

3D3V_S3 3D3V_S3

145

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144143

146

CLK_SDRAM0

CLK_SDRAM1

M_MD32

M_MD33

M_MD34

M_MD35

M_MD36

M_MD37

M_MD38

M_MD39

M_DQM4

M_DQM5

M_MA3

M_MA4

M_MA5

M_MD40

M_MD41

M_MD42

M_MD43

M_MD44

M_MD45

M_MD46

M_MD47

M_CKE0

M_SCAS#

M_CKE1

M_MA12

M_MA13

CLK_SDRAM1 3

M_MD48

M_MD49

M_MD50

M_MD51

M_MD52

M_MD53

M_MD54

M_MD55

M_MA7

M_MA11

M_MA12

M_MA13

M_DQM6

M_DQM7

M_MD56

M_MD57

M_MD58

M_MD59

M_MD60

M_MD61

M_MD62

M_MD63

SCLK_DIMMB

AMP 3-390113-1

H=5.2mm

R136

1 2

DUMMY-56R3

ZZ.56034.151

R137

1 2

DUMMY-56R3

ZZ.56034.151

CLK_SDRAM0_1

BC104

DUMMY-SC10P

ZZ.10034.1B1

BC105

DUMMY-SC10P

ZZ.10034.1B1

CLK_SDRAM23

M_MD0

M_MD1

M_MD2

M_MD3

M_MD4

M_MD5

M_MD6

M_MD7

M_DQM0

M_DQM1

M_MA0

M_MA1

M_MA2

M_MD8

M_MD9

M_MD10

M_MD11

M_MD12

M_MD13

M_MD14

M_MD15

M_BMWE#

M_CS#2

M_CS#3

M_MD16

M_MD17

M_MD18

M_MD19

M_MD20

M_MD21

M_MD22

M_MD23

M_MA6

M_MA8

M_MA9

M_MA10

M_DQM2

M_DQM3

M_MD24

M_MD25

M_MD26

M_MD27

M_MD28

M_MD29

M_MD30

M_MD31

CLK_SDRAM2

CLK_SDRAM3

R356

1 2

DUMMY-56R3

ZZ.56034.151

R357

1 2

DUMMY-56R3

ZZ.56034.151

DM2

145

1

2

3

4

5

6

7

8

9

SDIMM144-1U

62.10017.051

BC302

DUMMY-SC10P

ZZ.10034.1B1

BC303

DUMMY-SC10P

ZZ.10034.1B1

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144143

146

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

CLK_SDRAM2_1

CLK_SDRAM3_1CLK_SDRAM1_1

Title

Size Document Number Rev

Custom

Date: Sheet of

M_MD32

M_MD33

M_MD34

M_MD35

M_MD36

M_MD37

M_MD38

M_MD39

M_DQM4

M_DQM5

M_MA3

M_MA4

M_MA5

M_MD40

M_MD41

M_MD42

M_MD43

M_MD44

M_MD45

M_MD46

M_MD47

M_CKE2

M_SCAS#M_SRAS#

M_CKE3

M_MA12

M_MA13

CLK_SDRAM3 3

M_MD48

M_MD49

M_MD50

M_MD51

M_MD52

M_MD53

M_MD54

M_MD55

M_MA7

M_MA11

M_MA12

M_MA13

M_DQM6

M_DQM7

M_MD56

M_MD57

M_MD58

M_MD59

M_MD60

M_MD61

M_MD62

M_MD63

SCLK_DIMMASDATA_DIMMA

AMP 1123528-1

H=5.2mm

3D3V_S03,6,7,11,12,13,14,15,16,17,19,20,23,24,25,26,27,28,30,35

3D3V_S39,11,12,23,28,30,31,33

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

SO-DIMM

TM100

8 35Thursday, April 04, 2002

3D3V_S0

3D3V_S3

-1

1 2

0R3-0-U

63.R0004.151

R75 10R2

1 2

VGA_IDSEL

HVDD

R64 4K7R2

1 2

R55 4K7R2

1 2

1 2

R54 4K7R2

1 2

R67 10KR2

1 2

R68 10KR2

1 2

R69 10KR2

3D3V_S3

R66

20KR2

63.20334.1D1

1 2

AVDD3

1 2

HVDD

1 2

FPVDD

1 2

R57

PCI_AD[0..31]7,14,16,17,19

PCI_C/BE#[0..3]

63.10034.1D1

PCI_PAR7,14,16,17,19

PCI_FRAME#

PCI_TRDY#

PCI_IRDY#

PCI_STOP#

PCI_DEVSEL#

PCLK_VGA3

PCIRST1#7,13,14,15,24

PCI_REQ#17,13

PCI_GNT#17,13

PCI_INTA#7,13,14

63.10334.1D1

12

12

R65

2K7R2

63.27234.1D1

3D3V_S3AVDD

R56

0R3-0-U

63.R0004.151

3D3V_S3

R70

0R2-0

63.R0034.1D1

3D3V_S3

R73

0R2-0

63.R0034.1D1

3D3V_S3

R47

0R2-0

63.R0034.1D1

PCI_AD0

PCI_AD1

PCI_AD2

PCI_AD3

PCI_AD4

PCI_AD5

PCI_AD6

PCI_AD7

PCI_AD8

PCI_AD9

PCI_AD10

PCI_AD11

PCI_AD12

PCI_AD13

PCI_AD14

PCI_AD15

PCI_AD16

PCI_AD17

PCI_AD18

PCI_AD19

PCI_AD20

PCI_AD21

PCI_AD22

PCI_AD23

PCI_AD24