5

D D

4

3

2

1

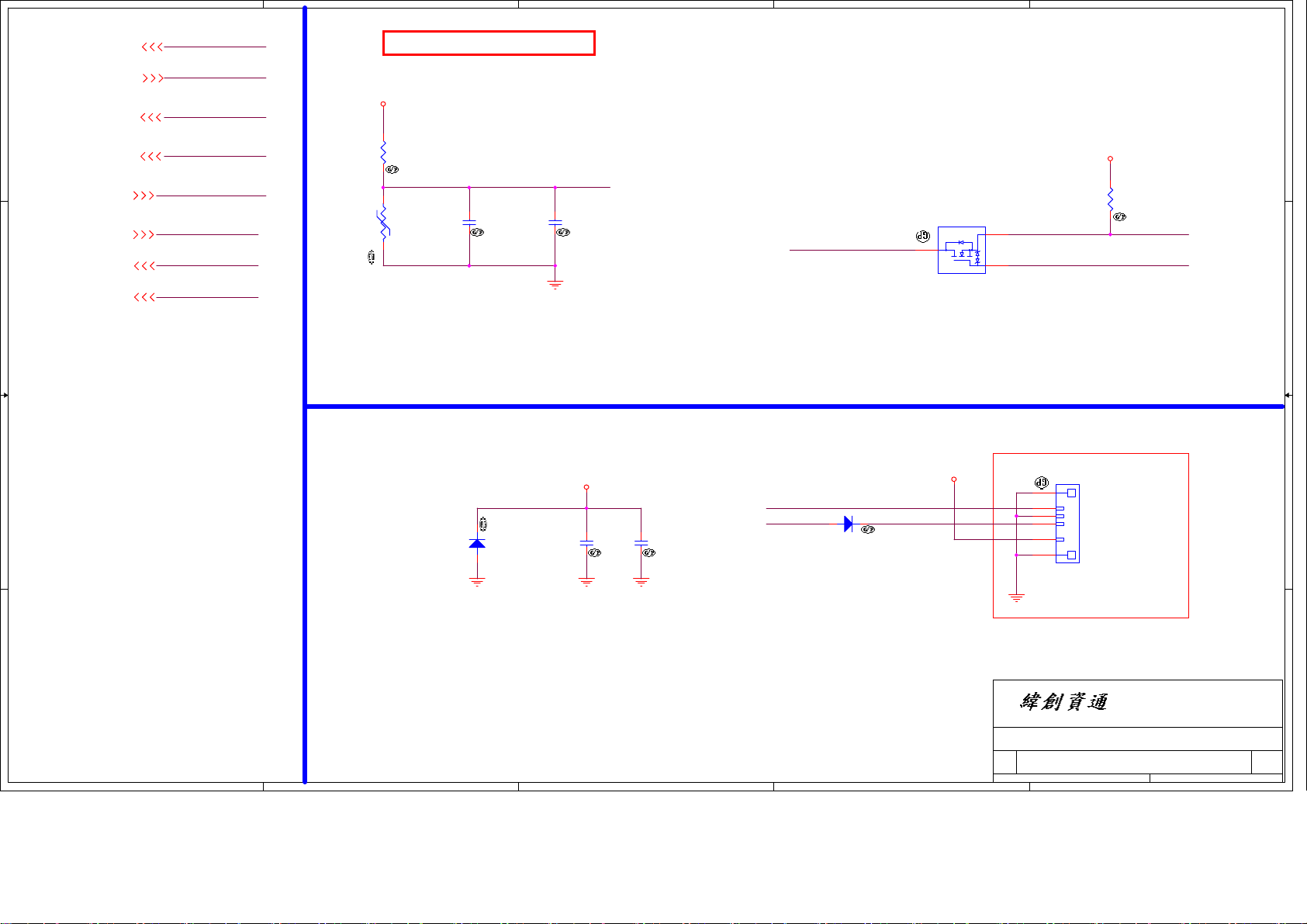

17809 -1m Carlsberg_KL

Schematics Document

C C

B B

A A

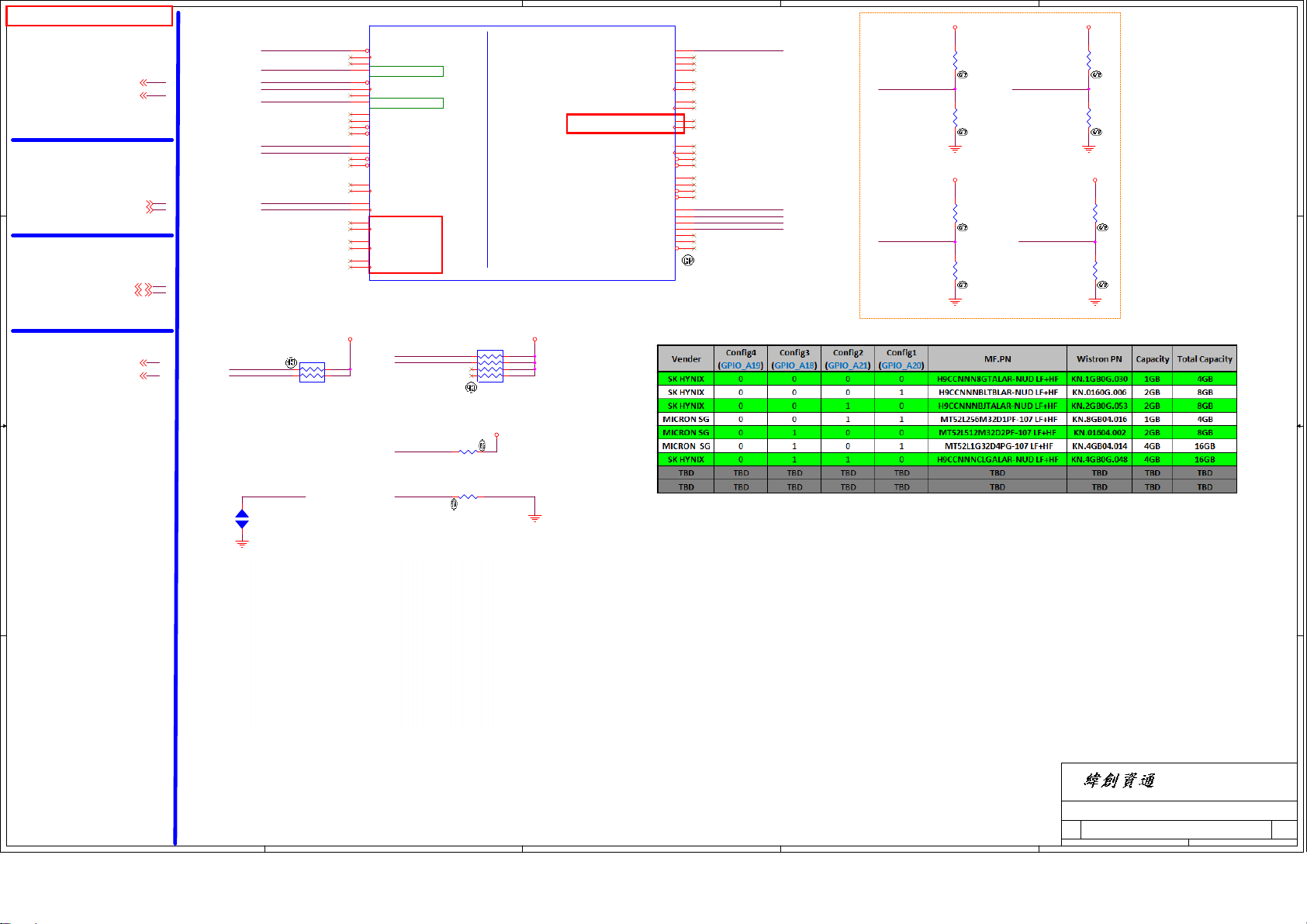

DY : None Installed

UMA: UMA only installed

DIS: DISCRTE OPTIMUS installed

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Date: Sheet of

Date: Sheet of

Date: Sheet of

Cover Page

Cover Page

Cover Page

Carlsberg_KL

Carlsberg_KL

Carlsberg_KL

1

1 106

1 106

1 106

-1M

-1M

-1M

5

4

Project Code: 4PD0D7010001

PCB No : 17809

Re

vision : -1m

3

2

1

D D

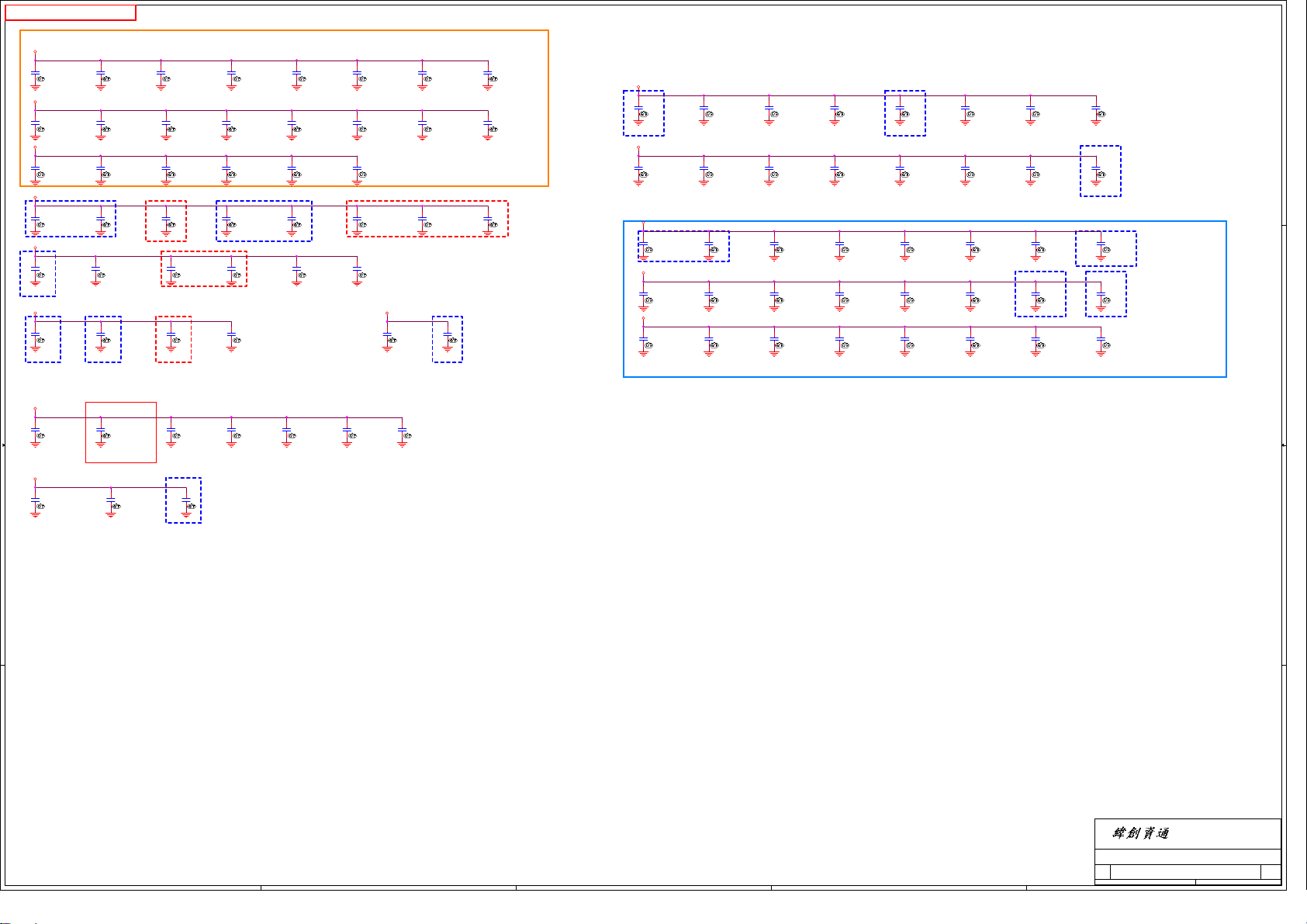

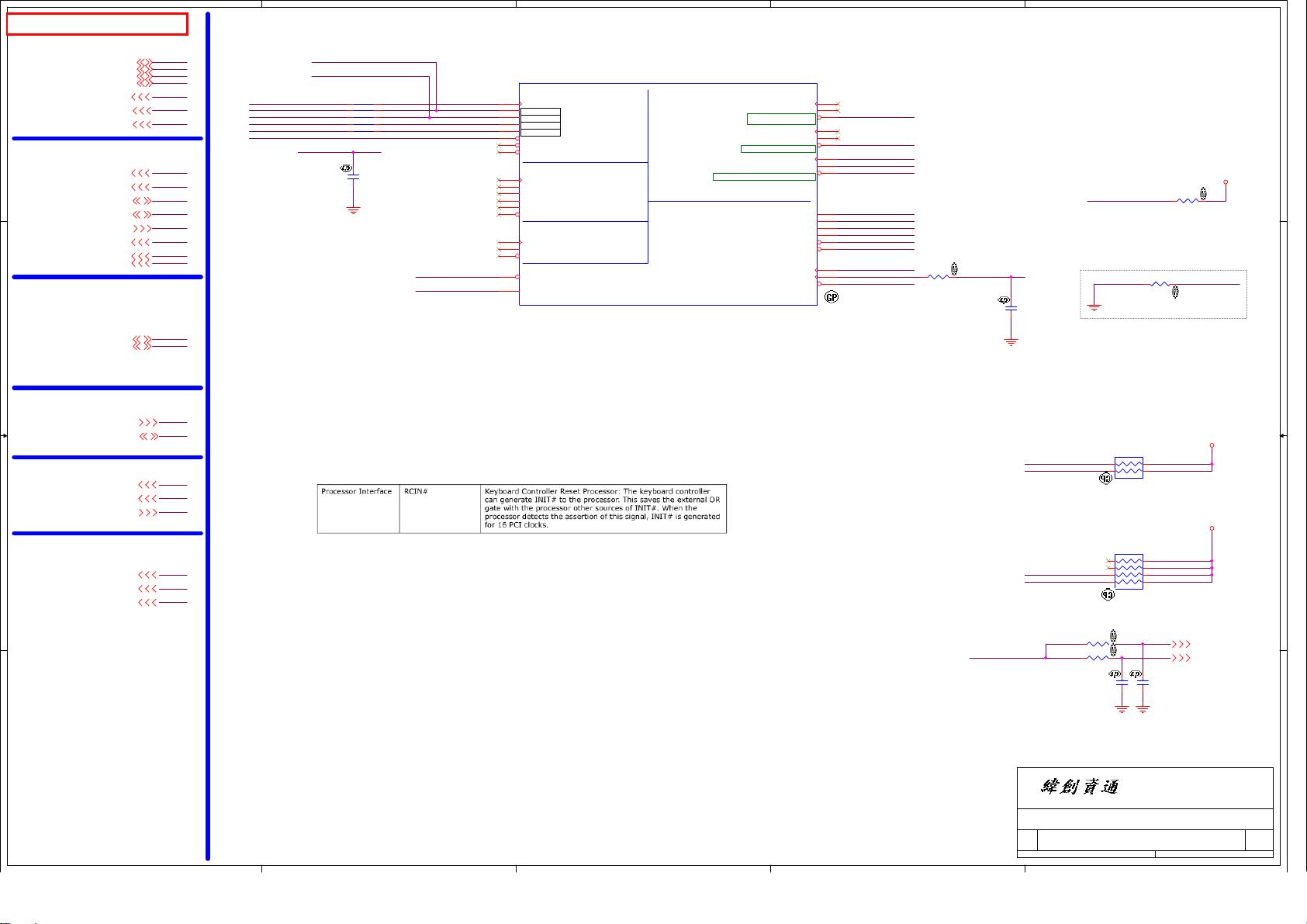

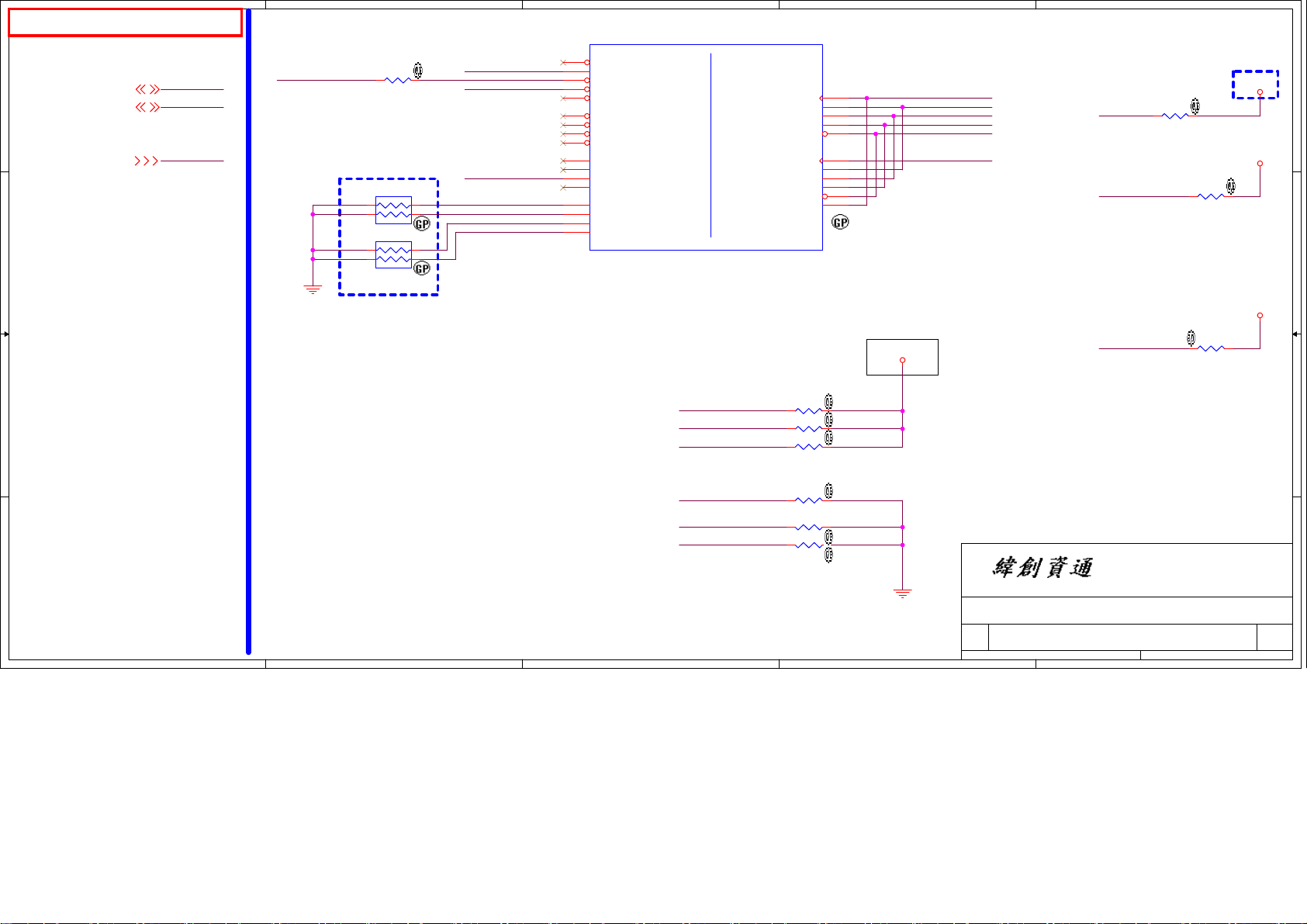

CCD/DMIC

55

LCD FHD:1920*1080

WXGA:1366*768

Touch Panel

55

DMIC

USB2.0x1

eDPx2

I2C x1

USB2.0x1

LCD CONN.

USB2.0x1

I2C x1 DY

USB2.0x1

DMIC

eDPx2

DY

LPDDR3 Channel A

LPDDR3 Channel B

24MHz

U22:X1601

U42:X2301

LPDDR3 MD x2 pcs

LPDDR3 MD x2 pcs

16

23

12

13

Intel CPU

X1

602

RTS5450

Charger

BQ24780S

16

TYPEC

73

57

Mini-Card

WLAN & BT

comb module

2

M2

SSD

74

M2

SSD

61

62

63

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Nu mber Rev

Size Document Nu mber Rev

Size Document Nu mber Rev

Custom

Custom

Custom

Wednesday, N ovember 01, 20 17

Wednesday, N ovember 01, 20 17

Wednesday, N ovember 01, 20 17

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

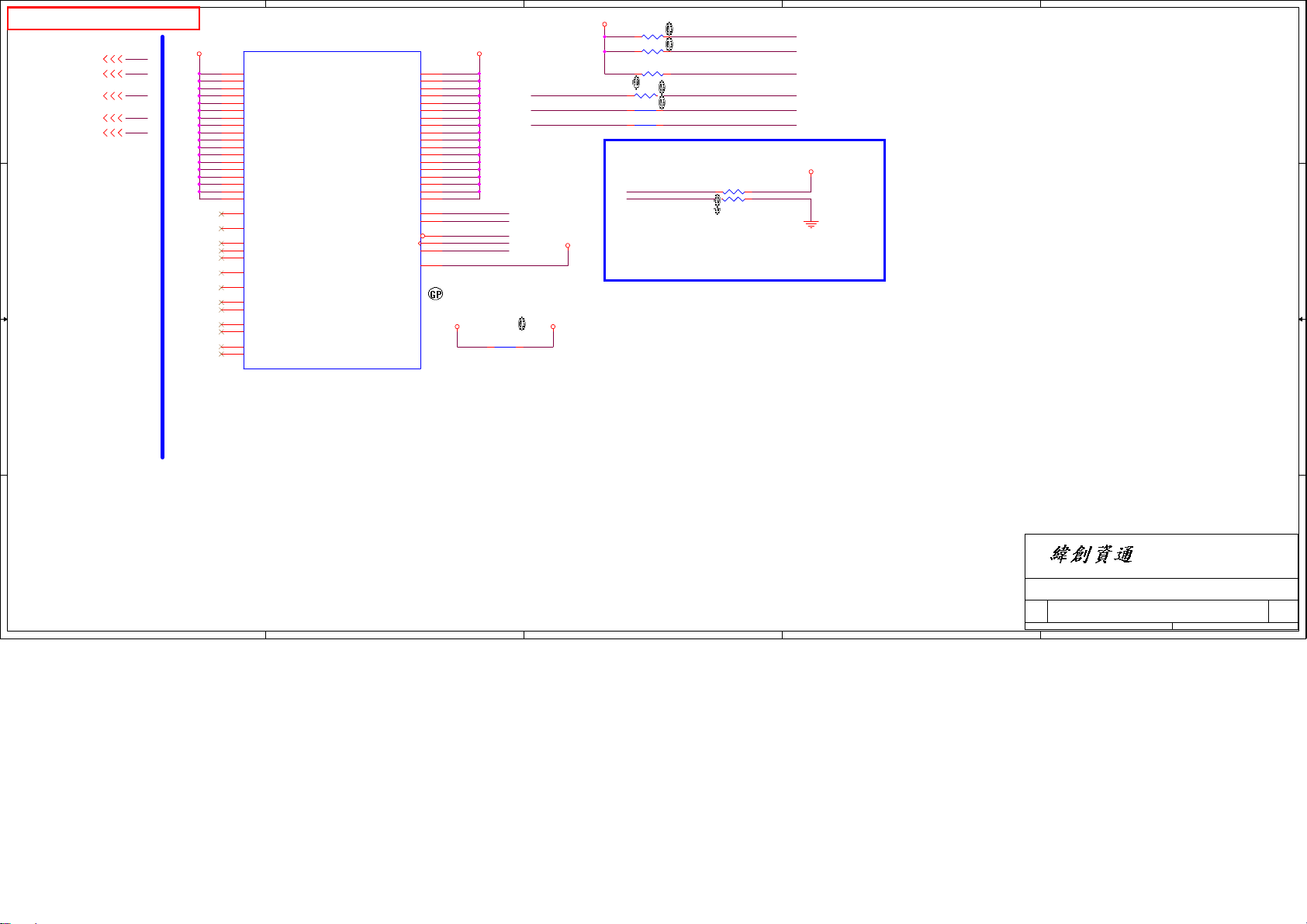

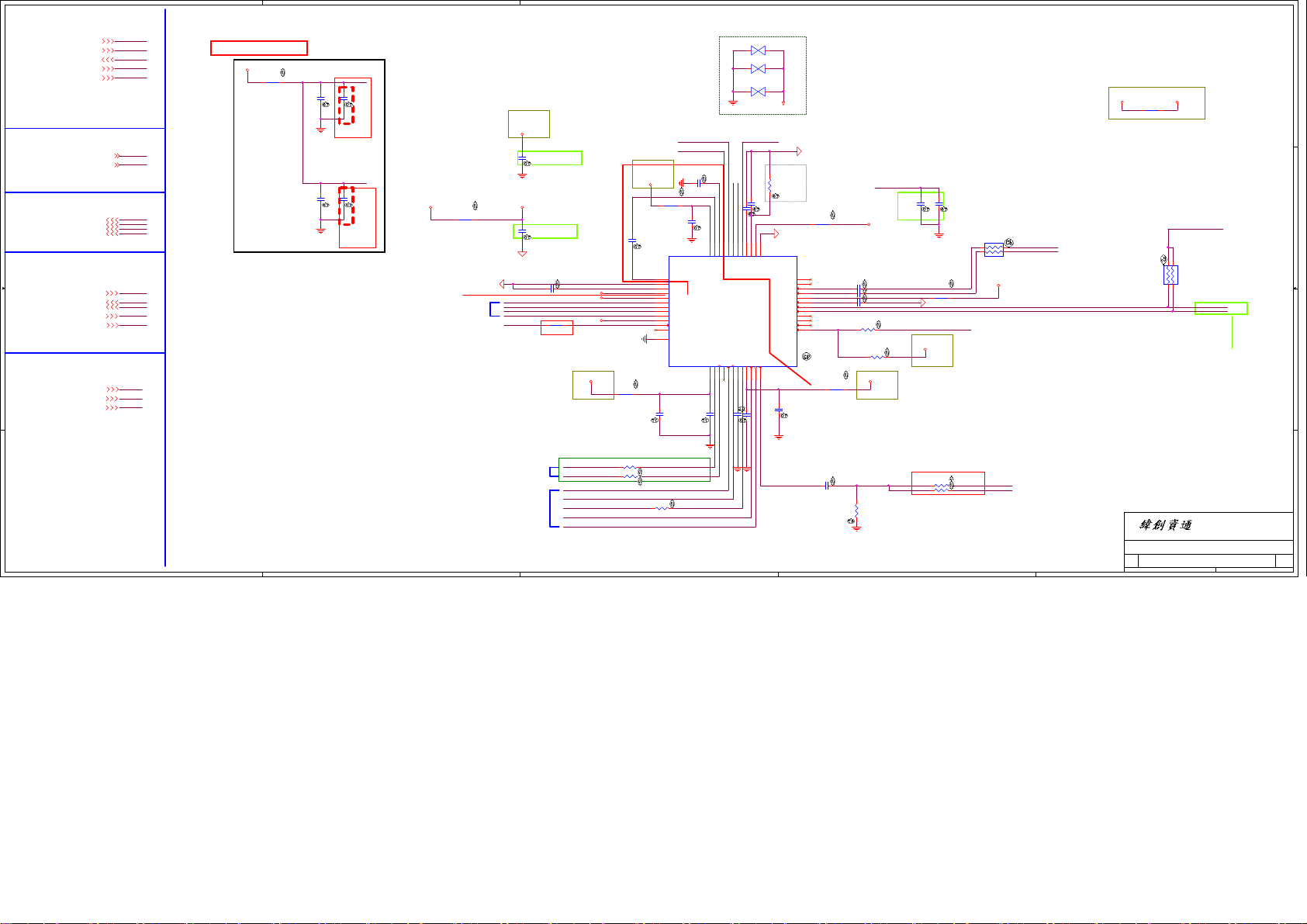

Block Diagram

Block Diagram

Block Diagram

Carlsberg_KL

Carlsberg_KL

Carlsberg_KL

1

2 106

2 106

2 106

-1M

-1M

-1M

73

92

57

25

HDMI 1.4b

44

55

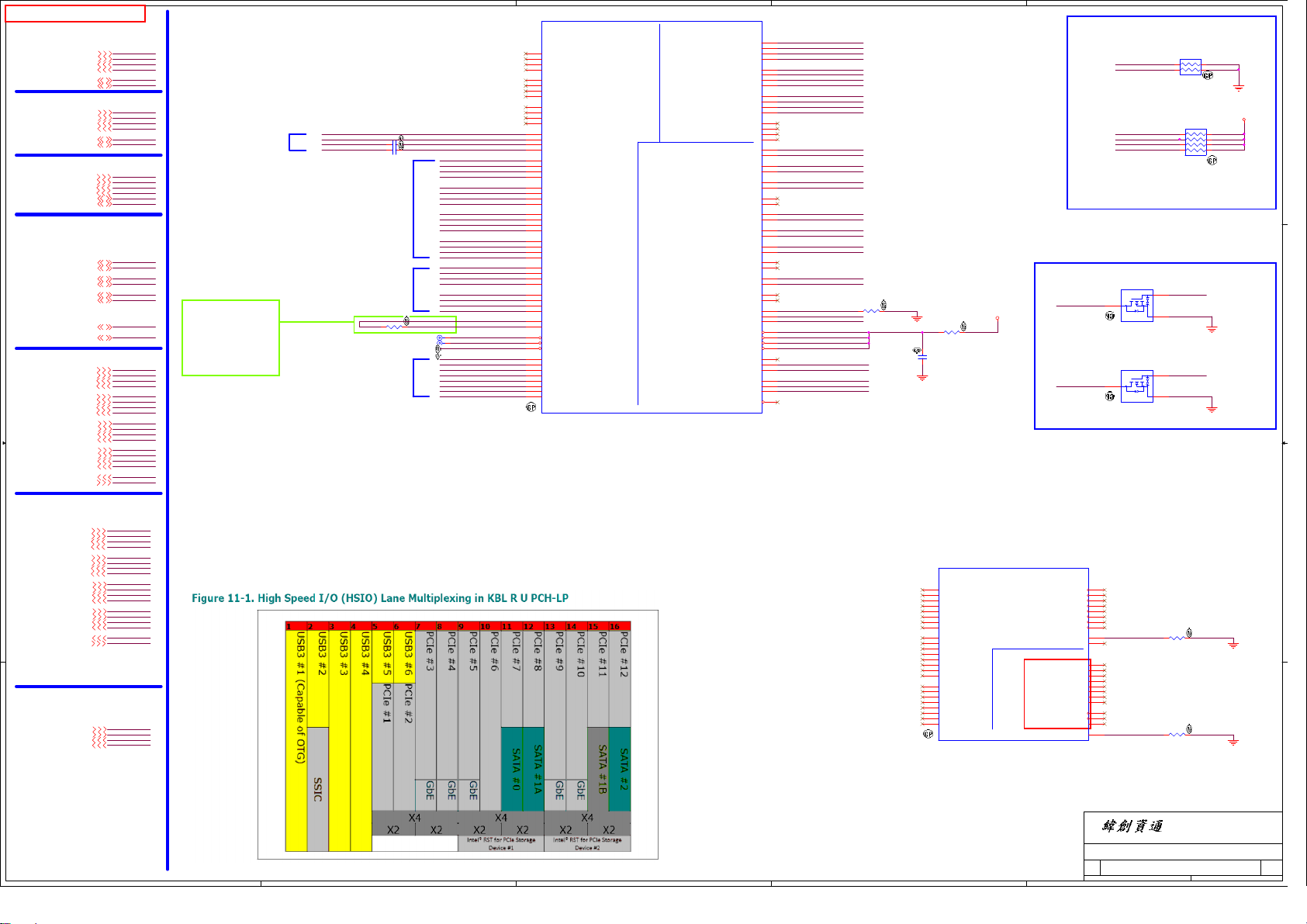

Kabylake R U

32.768KHz

15W

USB3.0 *1

USB2.0 x1

USB3.0 x 1

C C

35

USB Charger

USB3.0 *1

I2C for Precision Touchpad

Small Board :17A38-SA

Combo Jack

B B

A A

DMIC

SPK 2W 8 ohm

Hall sensor

5

27

0R

SPK-OUT_R_+/SPK-OUT_L_+/-

29

66

66

Connector

HD Audio Codec

ALC255

I2C for Precision Touchpad

Thermal

VD_IN1

FAN

4

USB2.0 x1

36

10 USB 2.0/1.1 ports

USB2.0 x1

USB3.0 x1

35

HD Audio

27

6 USB 3.0 ports

High Definition Audio

3 SATA ports

6 PCIE ports

LPC I/F

ACPI 5.0

ITPM

DDIx 1

USB3.0 x 1

USB2.0 x 1

USB2.0

DDI1

PCIe x 1

USB2.0 x 1

PCIe x 4(SATA*1)

PCIe x 4(SATA*1)

SPI

Finger print

Redriver

PS8201

SPI Flash

MX25U6473FM2I

-10G-GP

8MB

5,7,8,9,10,

11,12,15,16,18,19,21

TPM

VID

26

PWM

26

LPC BUS

91NPCT650

KB9028QA

PS2

Touch PAD

KBC

LPC debug port

24

Int.

KB

6565

3

68

SMBus

5

4

3

2

1

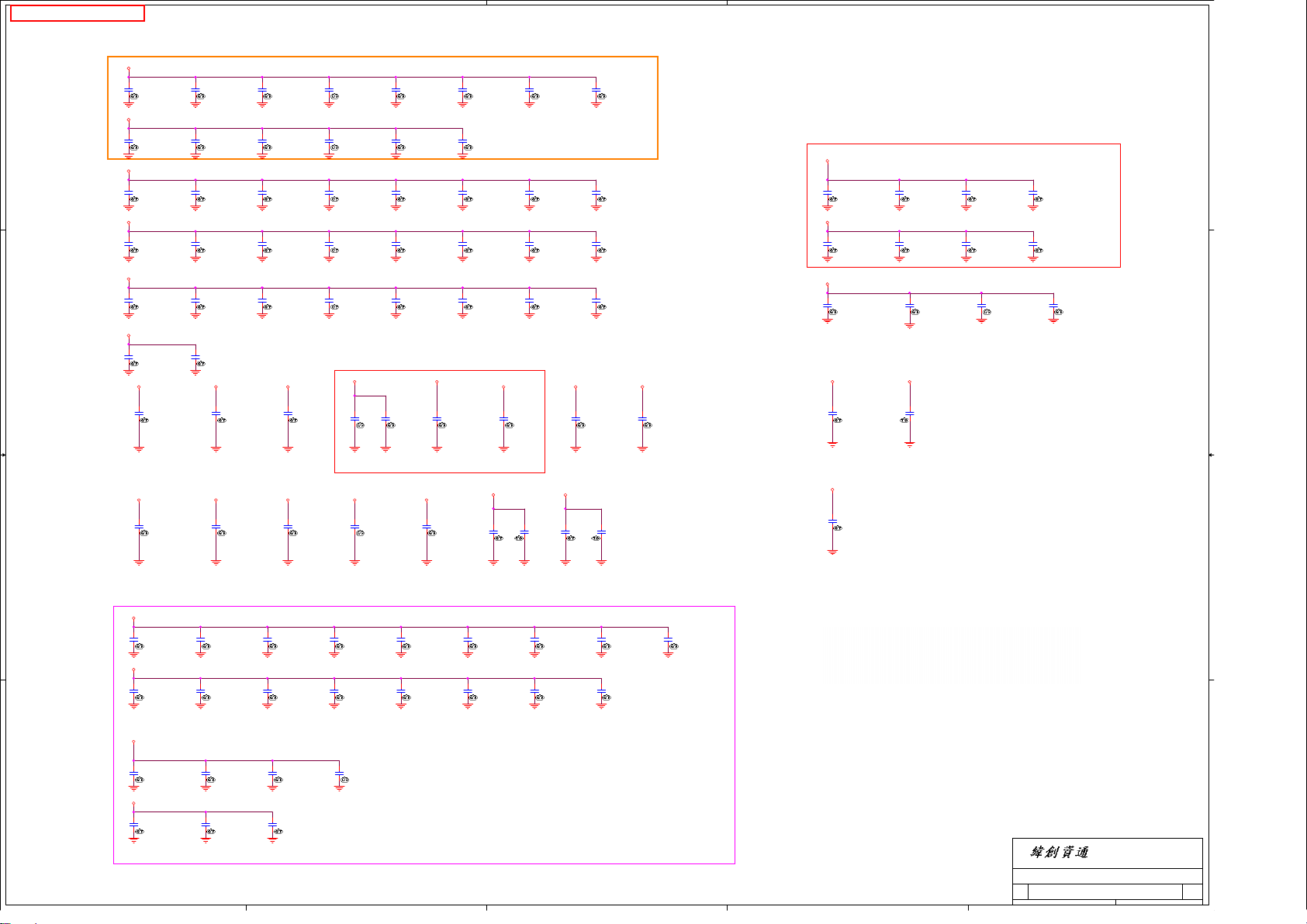

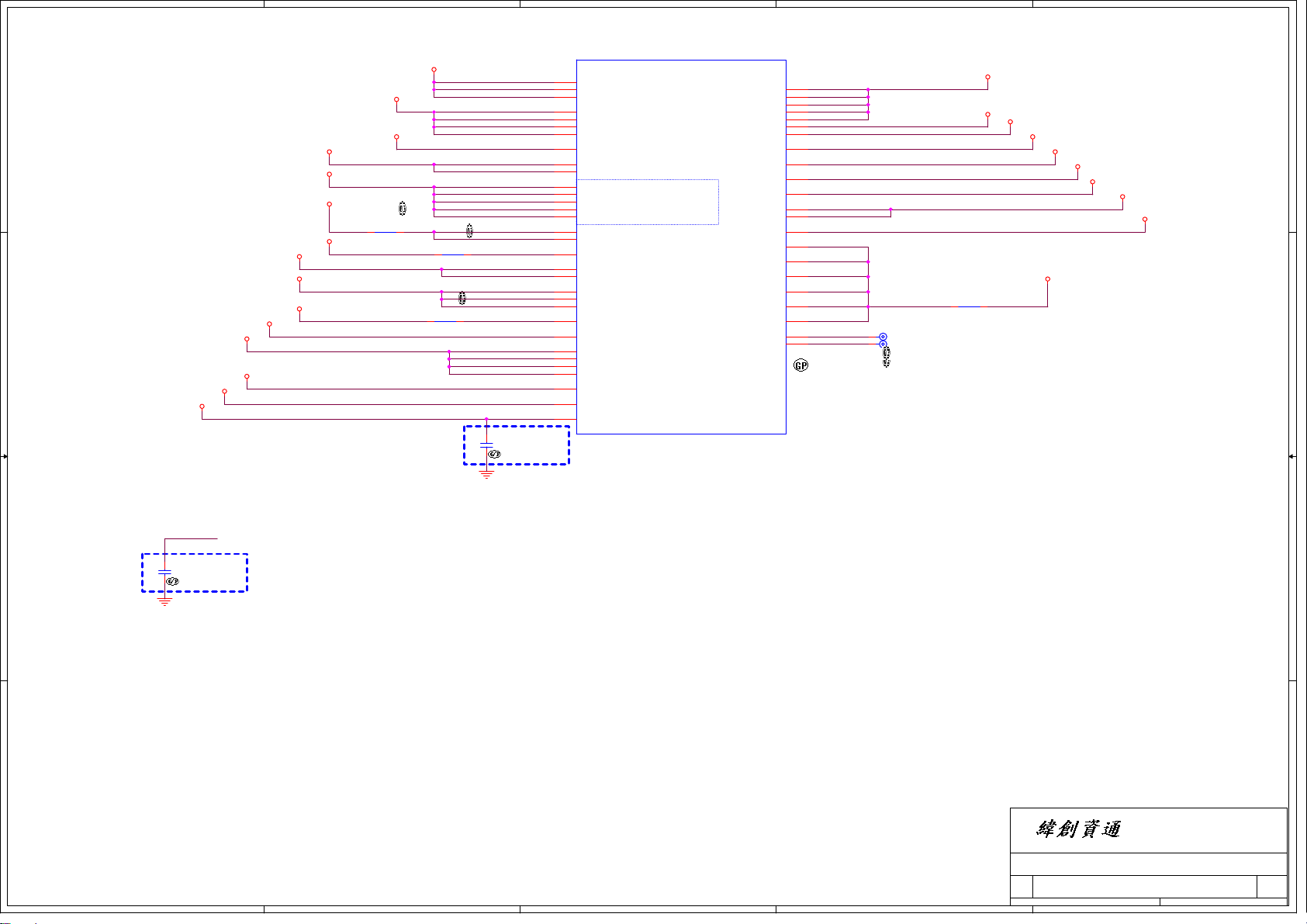

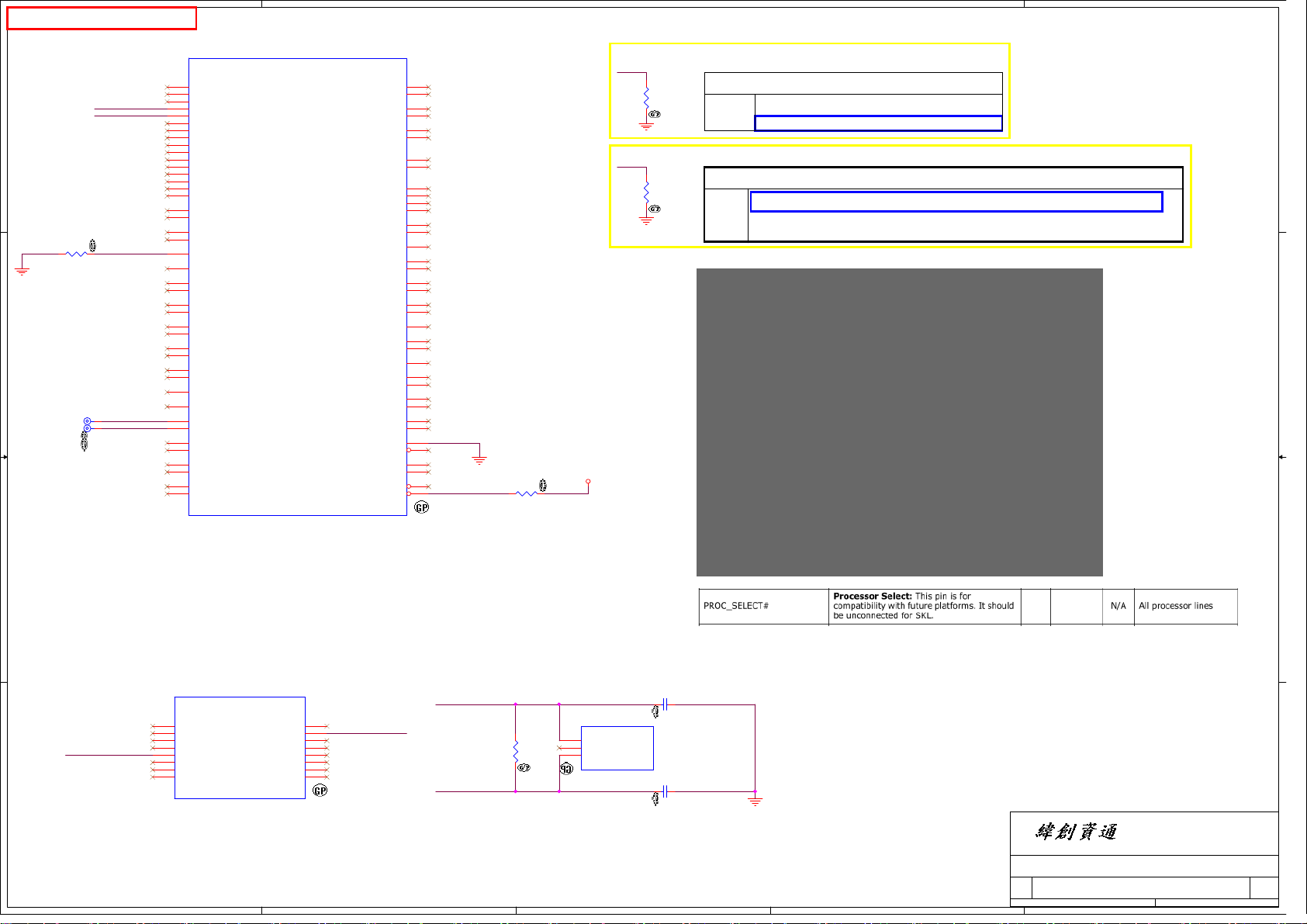

Main Func = CPU

CPU1A

SKYLAKE_ULT

DDI

DISPLAY SIDEBANDS

Strap

Strap

Strap

3D3V_S0

EDP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

1 2

HDMI_DATA_CPU_N2

HDMI_DATA_CPU_P2

HDMI_DATA_CPU_N1

HDMI_DATA_CPU_P1

HDMI_DATA_CPU_N0

HDMI_DATA_CPU_P0

HDMI_DATA_CPU_N3

HDMI_DATA_CPU_P3

DP_DDI_TX_N0

DP_DDI_TX_P0

DP_DDI_TX_N1

DP_DDI_TX_P1

DP_DDI_TX_N2

DP_DDI_TX_P2

DP_DDI_TX_N3

DP_DDI_TX_P3

HDMI_CLK_CPU

HDMI_DATA_CPU

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPD_CDA

EDP_RCOMP

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22

N12

GPP_E23

E52

EDP_RCOMP

SKYLAKE-U-GP

CPU

eDP_TX_CPU_N055

eDP_TX_CPU_P055

D D

eDP_TX_CPU_N155

eDP_TX_CPU_P155

eDP_AUX_CPU_N55

eDP_AUX_CPU_P55

eDP_HPD_CPU55

eDP_BLEN_CPU24

eDP_BLCTRL_CPU55

eDP_VDDEN_CPU55

HDMI

TYPEC

HDMI

eDP

HDMI_DATA_CPU_N257

HDMI_DATA_CPU_P257

C C

HDMI_DATA_CPU_N157

HDMI_DATA_CPU_P157

HDMI_DATA_CPU_N057

HDMI_DATA_CPU_P057

HDMI_DATA_CPU_N357

HDMI_DATA_CPU_P357

HDMI_CLK_CPU14,57

HDMI_DATA_CPU14,57

HDMI_DET_CPU57

1V_VCCIO

HDMI

R301 24D9R2F-L-GP

1 OF 20

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

RSVD#G46

RSVD#F46

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

eDP_TX_CPU_N0

eDP_TX_CPU_P0

eDP_TX_CPU_N1

eDP_TX_CPU_P1

eDP_AUX_CPU_N

eDP_AUX_CPU_P

DP_AUX_CPU_N

DP_AUX_CPU_P

HDMI_DET_CPU

DP_HPD_CON

EC_SCI#

eDP_HPD_CPU

eDP_BLEN_CPU

eDP_BLCTRL_CPU

eDP_VDDEN_CPU

eDP

eDP

DP_DDI_TX_N073

B B

A A

DP_DDI_TX_P073

DP_DDI_TX_N173

DP_DDI_TX_P173

DP_DDI_TX_N273

DP_DDI_TX_P273

DP_DDI_TX_N373

DP_DDI_TX_P373

DP_AUX_CPU_N73

DP_AUX_CPU_P73

DDPC_CTRLDATA14

DP_HPD_CON73

DDPD_CDA14

EC_SCI#24

5

TYPEC

OTHER

3D3V_S0

EC_SCI#

R307

12

2K2R2J-L1-GP

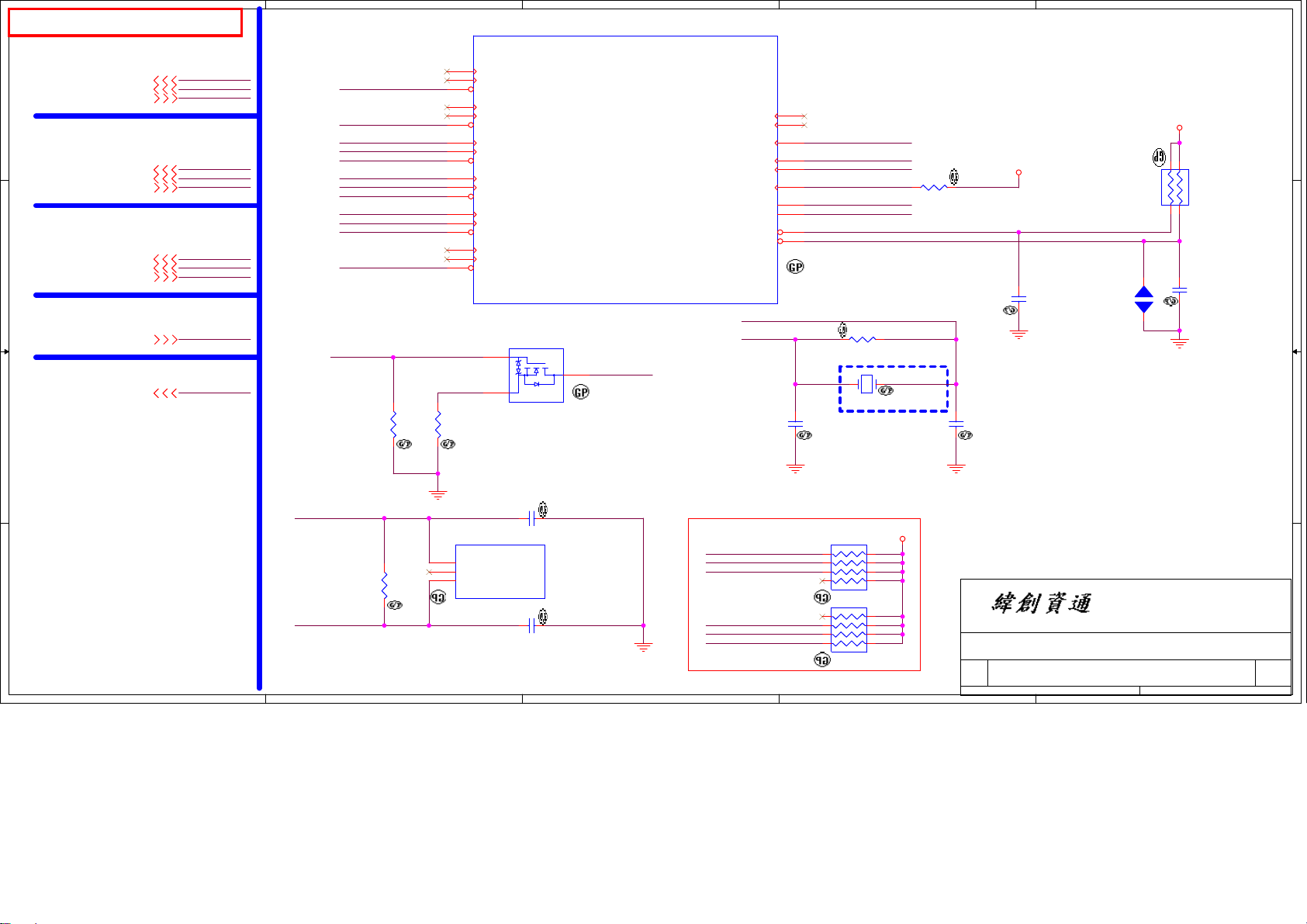

(#543016) eDP_RCOMP Guideline

Signal Trace

eDP_RCOMP 20 mils 25 mils 24.9 Ω ±1%

sign Guideline:

De

Skylake processor signal eDP_RCOMP should be connected to the VCCIO rail via a single 24.9 ±1% Ω resistor.

Width

4

eDP_BLEN_CPU

DP_HPD_CON

20170302 Change

Isolation

Spacing

R304

1 2

100KR2F-L3-GP

R320

1 2

100KR2F-L3-GP

Resistor

Value

Max = 100 mils

Length

3

12

R310

2K2R2J-2-GP

DY

DDPC_CTRLCLK

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

CPU_(DISPLAY)

CPU_(DISPLAY)

CPU_(DISPLAY)

Carlsberg_KL

Carlsberg_KL

Carlsberg_KL

1

3 106

3 106

3 106

-1M

-1M

-1M

5

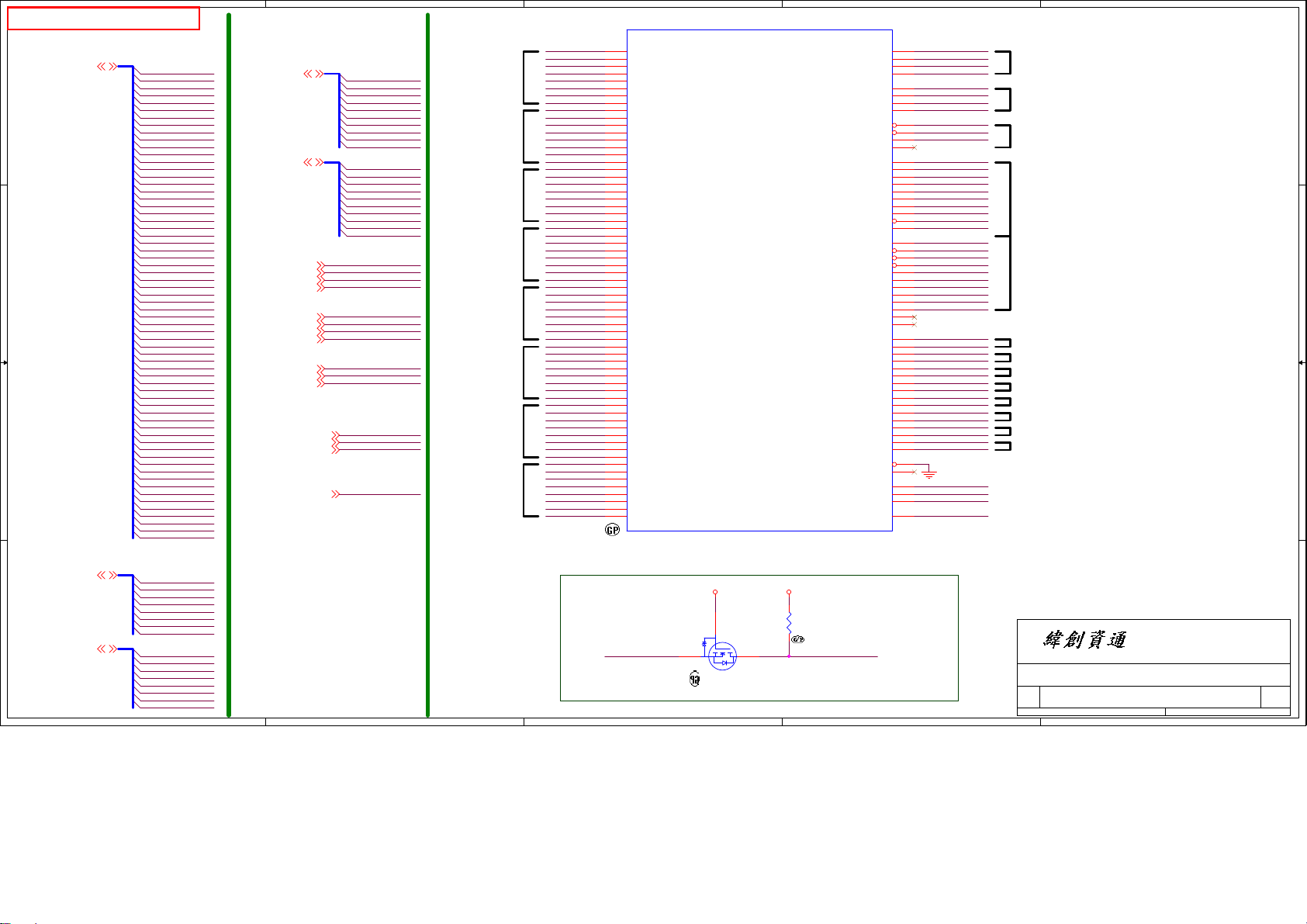

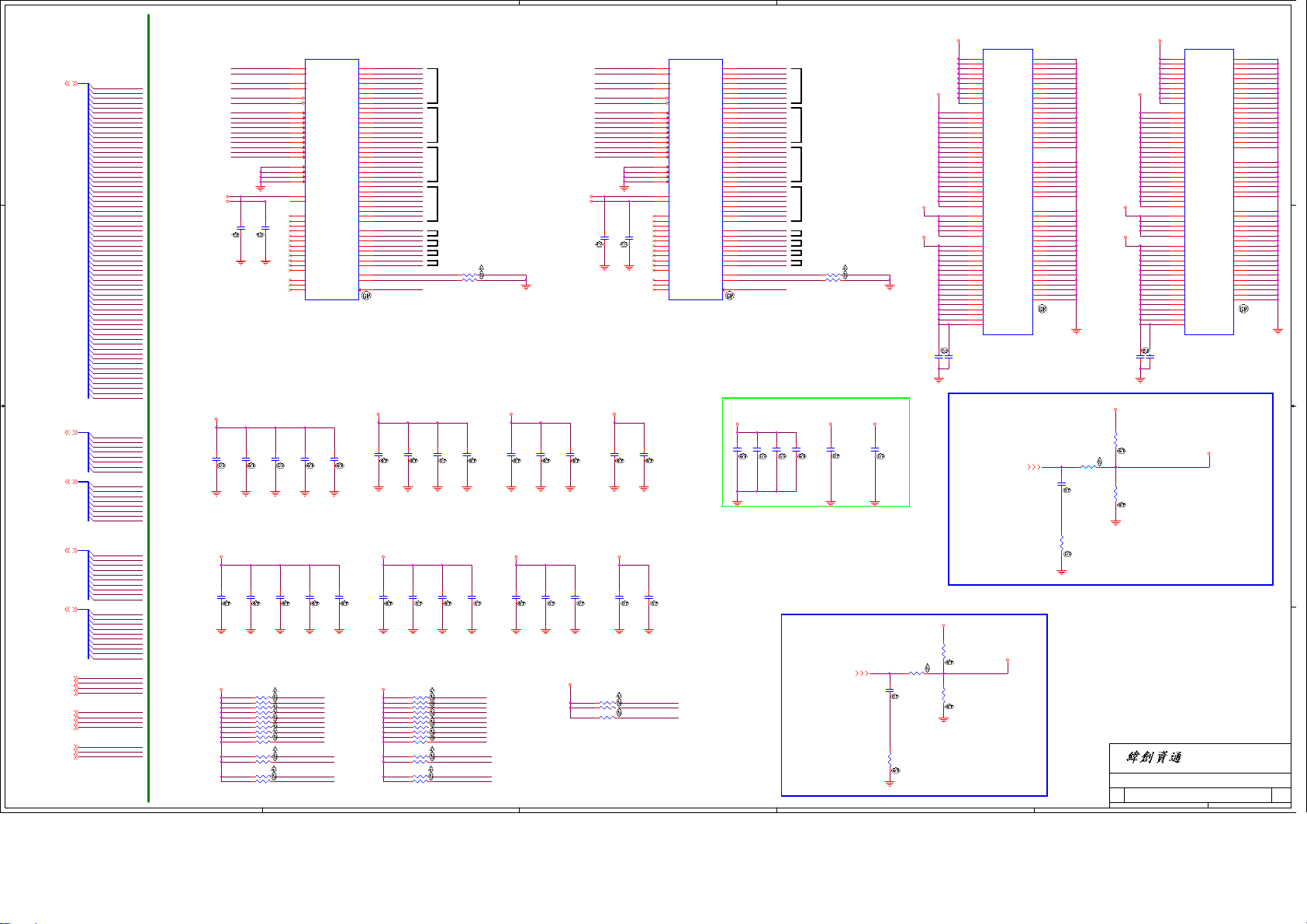

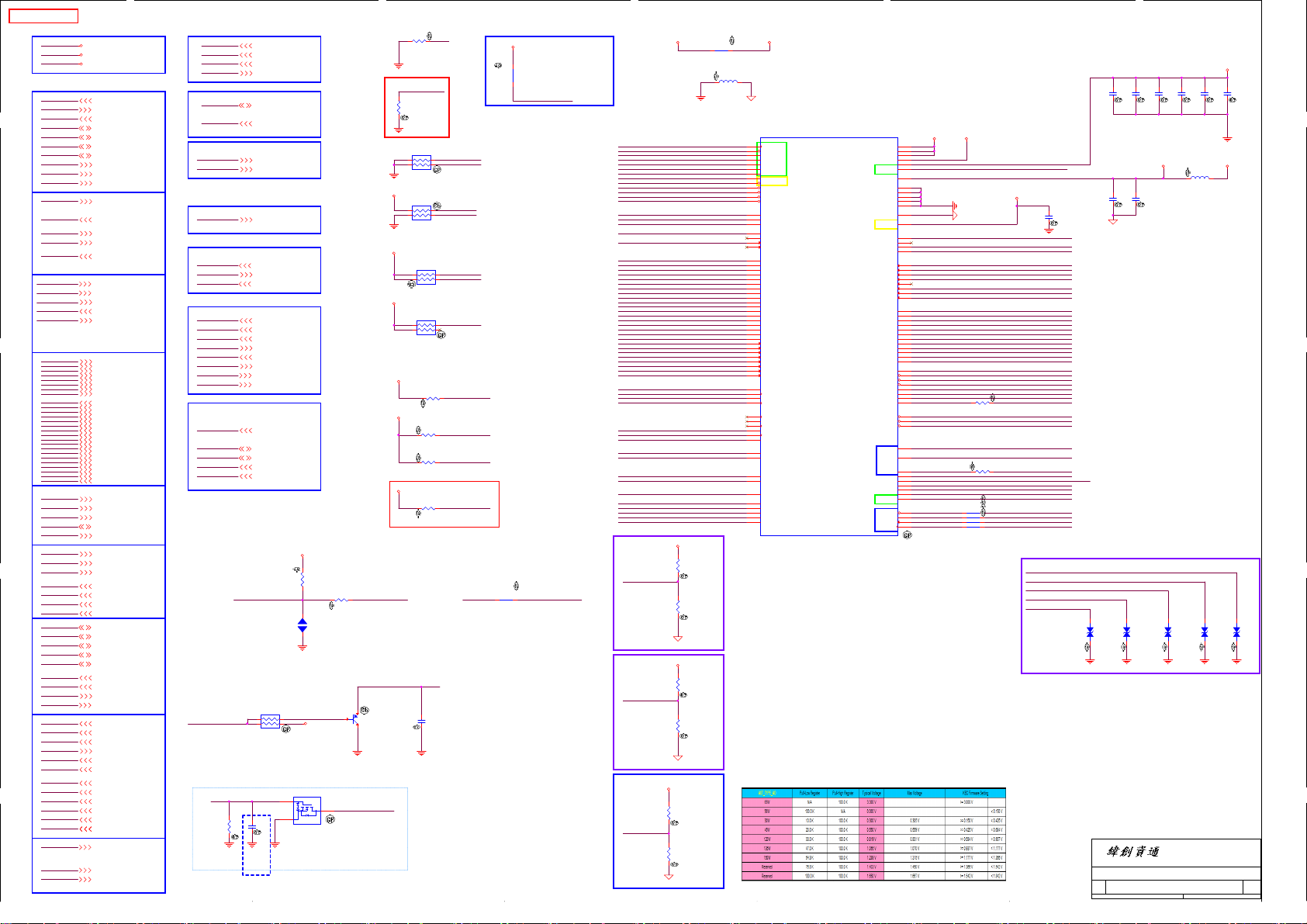

Main Func = CPU

DATA

M_A_DQ[63:0]12

D D

C C

B B

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_CA_A[9:0]12

M_A_CA_B[9:0]12

M_A_CLK012

M_A_CLK#012

M_A_CLK112

M_A_CLK#112

M_A_CKE012

M_A_CKE112

M_A_CKE212

M_A_CKE312

M_A_CS#012

M_A_CS#112

M_A_ODT012

V_DDR_CA_VREF12

DDR_VREFDQ01_CHA12

DDR_VREFDQ02_CHB13

DDR_VTT_CTRL_Q51

CMD

CLK

CKE

CTRL

VREF

VT

4

M_A_CA_A0

M_A_CA_A1

M_A_CA_A2

M_A_CA_A3

M_A_CA_A4

M_A_CA_A5

M_A_CA_A6

M_A_CA_A7

M_A_CA_A8

M_A_CA_A9

M_A_CA_B0

M_A_CA_B1

M_A_CA_B2

M_A_CA_B3

M_A_CA_B4

M_A_CA_B5

M_A_CA_B6

M_A_CA_B7

M_A_CA_B8

M_A_CA_B9

T CTRL

M_A_DQ[0:7]

M_A_DQ[8:15]

M_A_DQ[16:23]

M_A_DQ[24:31]

M_A_DQ[32:39]

M_A_DQ[40:47]

M_A_DQ[48:55]

M_A_DQ[56:63]

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

CPU1B

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

SKYLAKE-U-GP

3

SKYLAKE_ULT

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

CPU

071.SKYLA.000U

DDR CH - A

2 OF 20

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

2

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

AH66

AH65

AG69

AG70

BA64

AY64

AY60

BA60

AR66

AR65

AR61

AR60

AW50

AT52

V_DDR_CA_VREF

AY67

DDR_VREFDQ01_CHA

AY68

DDR_VREFDQ02_CHB

BA67

AW67

M_A_CLK#0

M_A_CLK0

M_A_CLK#1

M_A_CLK1

M_A_CKE0

M_A_CKE1

M_A_CKE2

M_A_CKE3

M_A_CS#0

M_A_CS#1

M_A_ODT0

M_A_CA_A0

M_A_CA_A1

M_A_CA_A2

M_A_CA_A3

M_A_CA_A4

M_A_CA_A5

M_A_CA_A6

M_A_CA_A7

M_A_CA_A8

M_A_CA_A9

M_A_CA_B0

M_A_CA_B1

M_A_CA_B2

M_A_CA_B3

M_A_CA_B4

M_A_CA_B5

M_A_CA_B6

M_A_CA_B7

M_A_CA_B8

M_A_CA_B9

M_A_DQS_DN0

M_A_DQS_DP0

M_A_DQS_DN1

M_A_DQS_DP1

M_A_DQS_DN2

M_A_DQS_DP2

M_A_DQS_DN3

M_A_DQS_DP3

M_A_DQS_DN4

M_A_DQS_DP4

M_A_DQS_DN5

M_A_DQS_DP5

M_A_DQS_DN6

M_A_DQS_DP6

M_A_DQS_DN7

M_A_DQS_DP7

DDR_VTT_CTRL

1

A-CLK

A-CKE

A-CTRL

A

A-CMD

B

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS_DP[7:0]12

A A

M_A_DQS_DN[7:0]12

DQS

5

M_A_DQS_DP0

M_A_DQS_DP1

M_A_DQS_DP2

M_A_DQS_DP3

M_A_DQS_DP4

M_A_DQS_DP5

M_A_DQS_DP6

M_A_DQS_DP7

M_A_DQS_DN0

M_A_DQS_DN1

M_A_DQS_DN2

M_A_DQS_DN3

M_A_DQS_DN4

M_A_DQS_DN5

M_A_DQS_DN6

M_A_DQS_DN7

3D3V_S01D2V_S3

12

R401

G

DDR_VTT_CTRL DDR_VTT_CTRL_Q

2nd = 084.00138.0A31

4

3

DS

Q401

DMN5L06K-7-GP

84.05067.031

220KR2F-GP

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

CPU_(DDR)

CPU_(DDR)

CPU_(DDR)

Carlsberg_KL

Carlsberg_KL

Carlsberg_KL

4 106

4 106

4 106

1

-1M

-1M

-1M

5

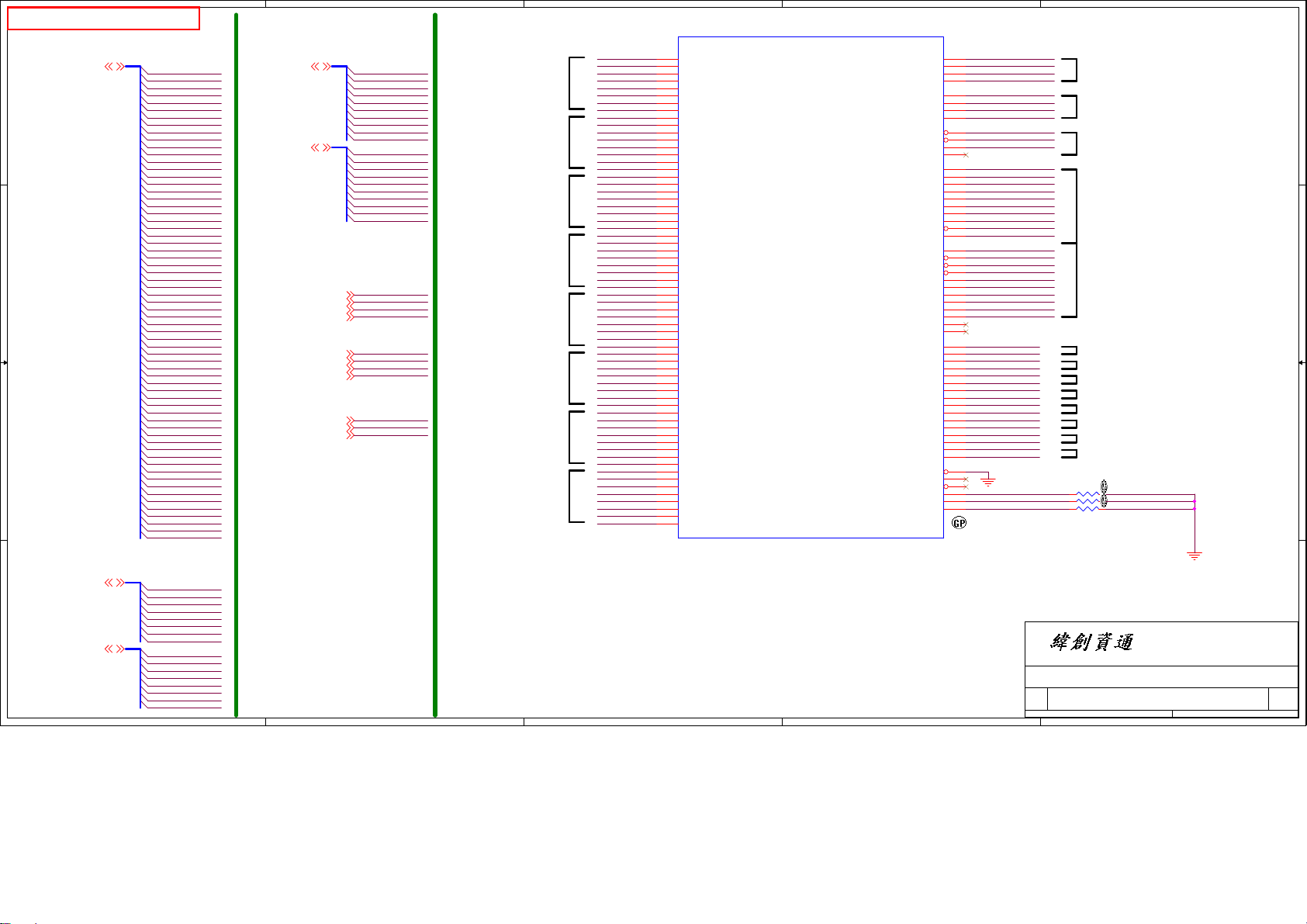

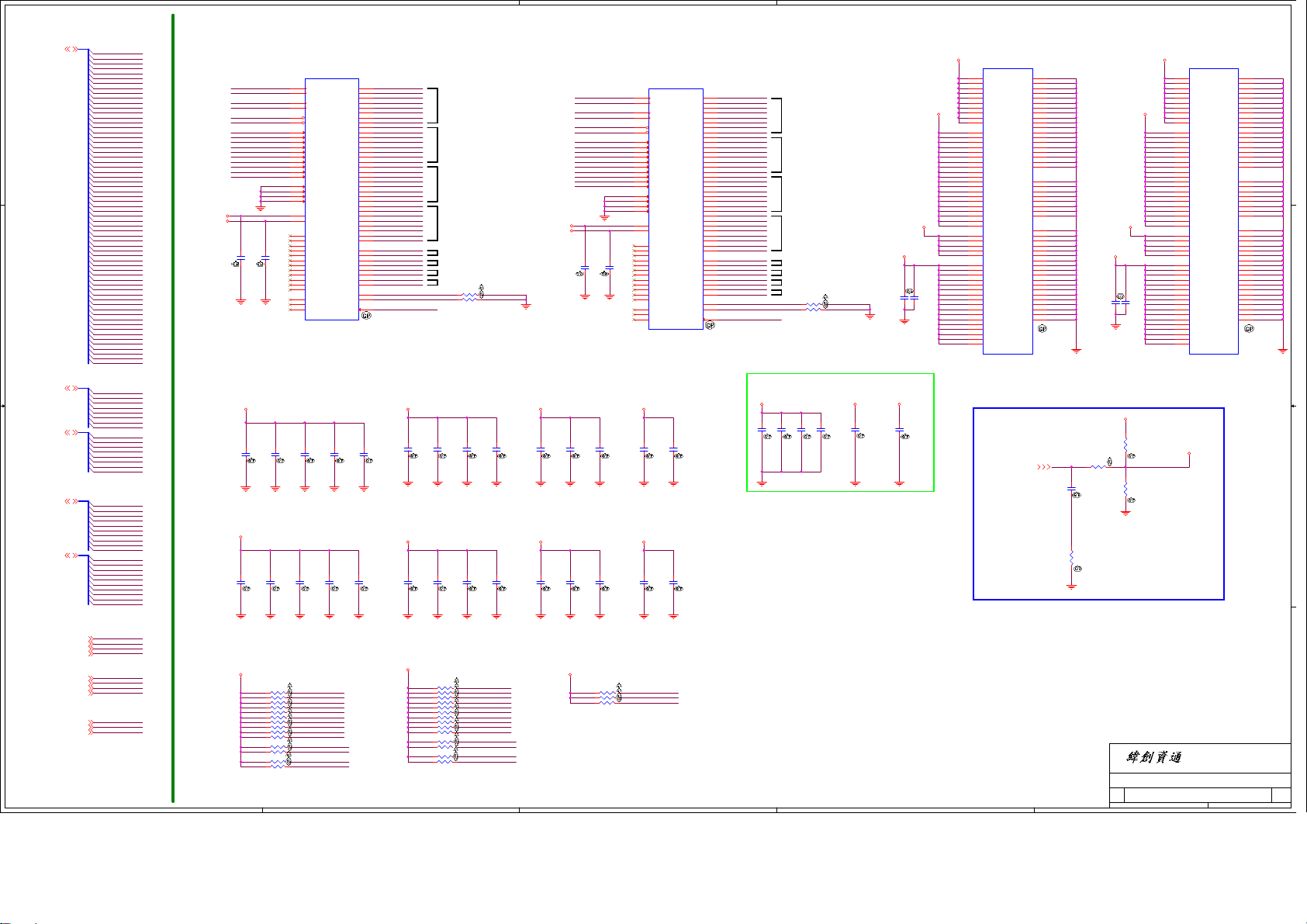

Main Func = CPU

DATA

M_B_DQ[63:0]13

D D

C C

B B

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_CA_A[9:0]13

M_B_CA_B[9:0]13

M_B_CLK013

M_B_CLK#013

M_B_CLK113

M_B_CLK#113

M_B_CKE013

M_B_CKE113

M_B_CKE213

M_B_CKE313

M_B_CS#013

M_B_CS#113

M_B_ODT013

CMD

M_B_CA_A0

M_B_CA_A1

M_B_CA_A2

M_B_CA_A3

M_B_CA_A4

M_B_CA_A5

M_B_CA_A6

M_B_CA_A7

M_B_CA_A8

M_B_CA_A9

M_B_CA_B0

M_B_CA_B1

M_B_CA_B2

M_B_CA_B3

M_B_CA_B4

M_B_CA_B5

M_B_CA_B6

M_B_CA_B7

M_B_CA_B8

M_B_CA_B9

CLK

CKE

CTRL

4

M_B_DQ[0:7]

M_B_DQ[8:15]

M_B_DQ[16:23]

M_B_DQ[24:31]

M_B_DQ[32:39]

M_B_DQ[40:47]

M_B_DQ[48:55]

M_B_DQ[56:63]

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

3

CPU1C

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKYLAKE-U-GP

SKYLAKE_ULT

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

CPU

071.SKYLA.000U

DDR CH - B

2

3 OF 20

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

BA38

AY38

AY34

BA34

AT38

AR38

AT32

AR32

BA30

AY30

AY26

BA26

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

M_B_CLK#0

M_B_CLK#1

M_B_CLK0M_B_DQ0

M_B_CLK1

M_B_CKE0

M_B_CKE1

M_B_CKE2

M_B_CKE3

M_B_CS#0

M_B_CS#1

M_B_ODT0

M_B_CA_A0

M_B_CA_A1

M_B_CA_A2

M_B_CA_A3

M_B_CA_A4

M_B_CA_A5

M_B_CA_A6

M_B_CA_A7

M_B_CA_A8

M_B_CA_A9

M_B_CA_B0

M_B_CA_B1

M_B_CA_B2

M_B_CA_B3

M_B_CA_B4

M_B_CA_B5

M_B_CA_B6

M_B_CA_B7

M_B_CA_B8

M_B_CA_B9

M_B_DQS_DN0

M_B_DQS_DP0

M_B_DQS_DN1

M_B_DQS_DP1

M_B_DQS_DN2

M_B_DQS_DP2

M_B_DQS_DN3

M_B_DQS_DP3

M_B_DQS_DN4

M_B_DQS_DP4

M_B_DQS_DN5

M_B_DQS_DP5

M_B_DQS_DN6

M_B_DQS_DP6

M_B_DQS_DN7

M_B_DQS_DP7

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

B-CLK

B-CKE

B-CTRL

A

B-CMD

B

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

1 2

R501 200R2F-L-GP

1 2

R502 80D6R2F-L-GP

1 2

R503 162R2F-GP

1

5

DQS

M_B_DQS_DP0

M_B_DQS_DP1

M_B_DQS_DP2

M_B_DQS_DP3

M_B_DQS_DP4

M_B_DQS_DP5

M_B_DQS_DP6

M_B_DQS_DP7

M_B_DQS_DN0

M_B_DQS_DN1

M_B_DQS_DN2

M_B_DQS_DN3

M_B_DQS_DN4

M_B_DQS_DN5

M_B_DQS_DN6

M_B_DQS_DN7

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

CPU_(DDR)

CPU_(DDR)

CPU_(DDR)

Carlsberg_KL

Carlsberg_KL

Carlsberg_KL

1

-1M

-1M

-1M

106

106

5

5

5

106

M_B_DQS_DP[7:0]13

A A

M_B_DQS_DN[7:0]13

5

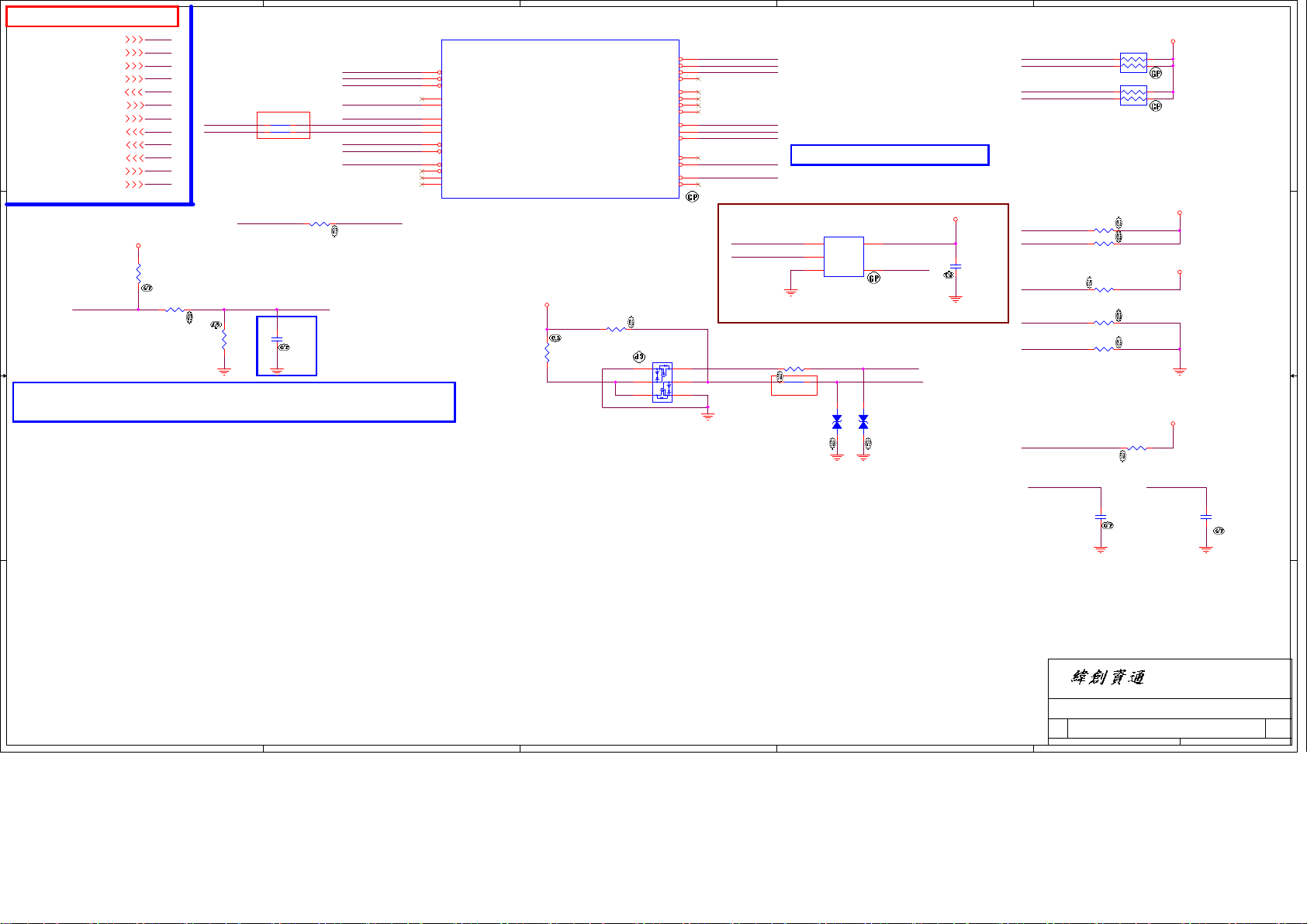

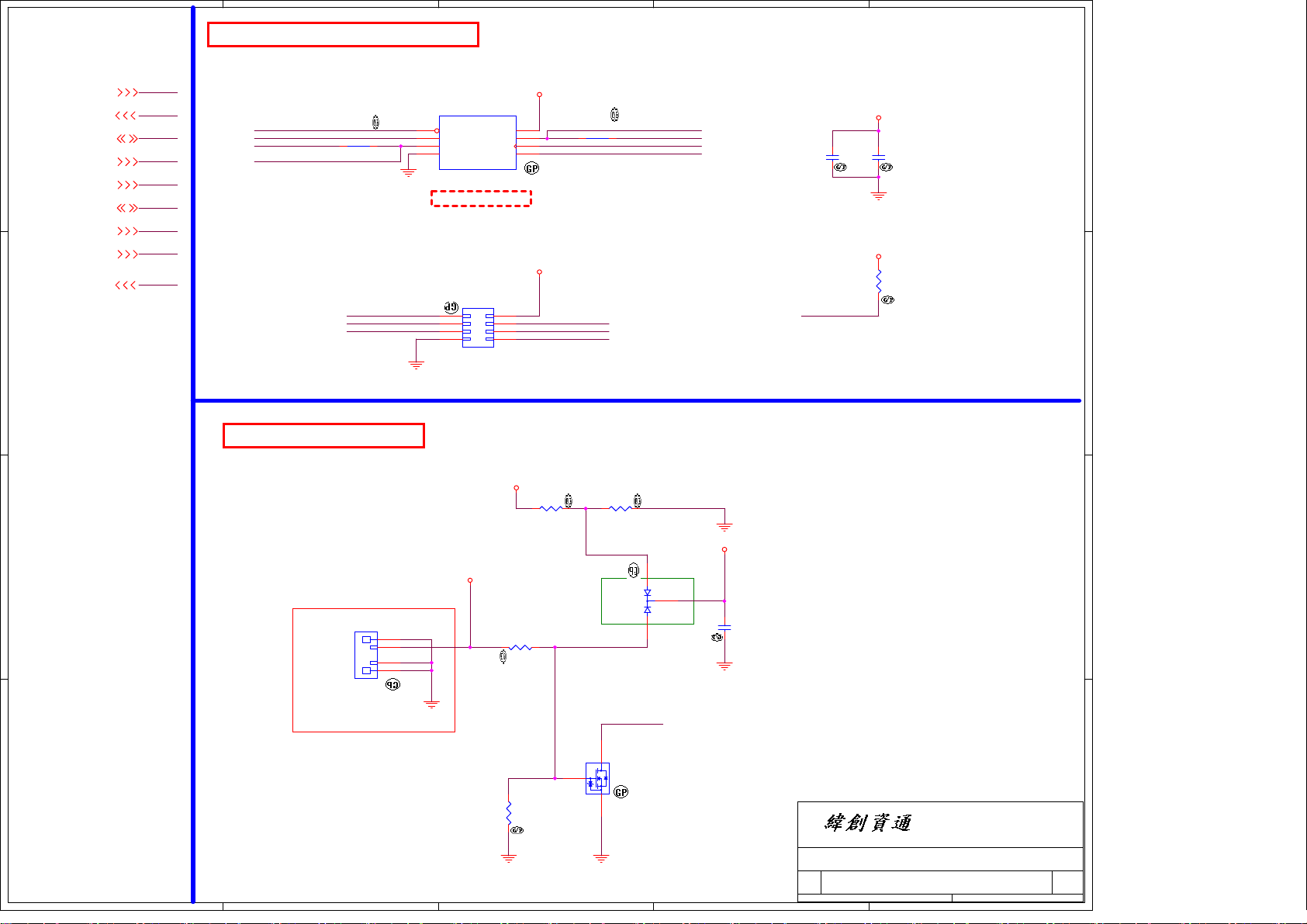

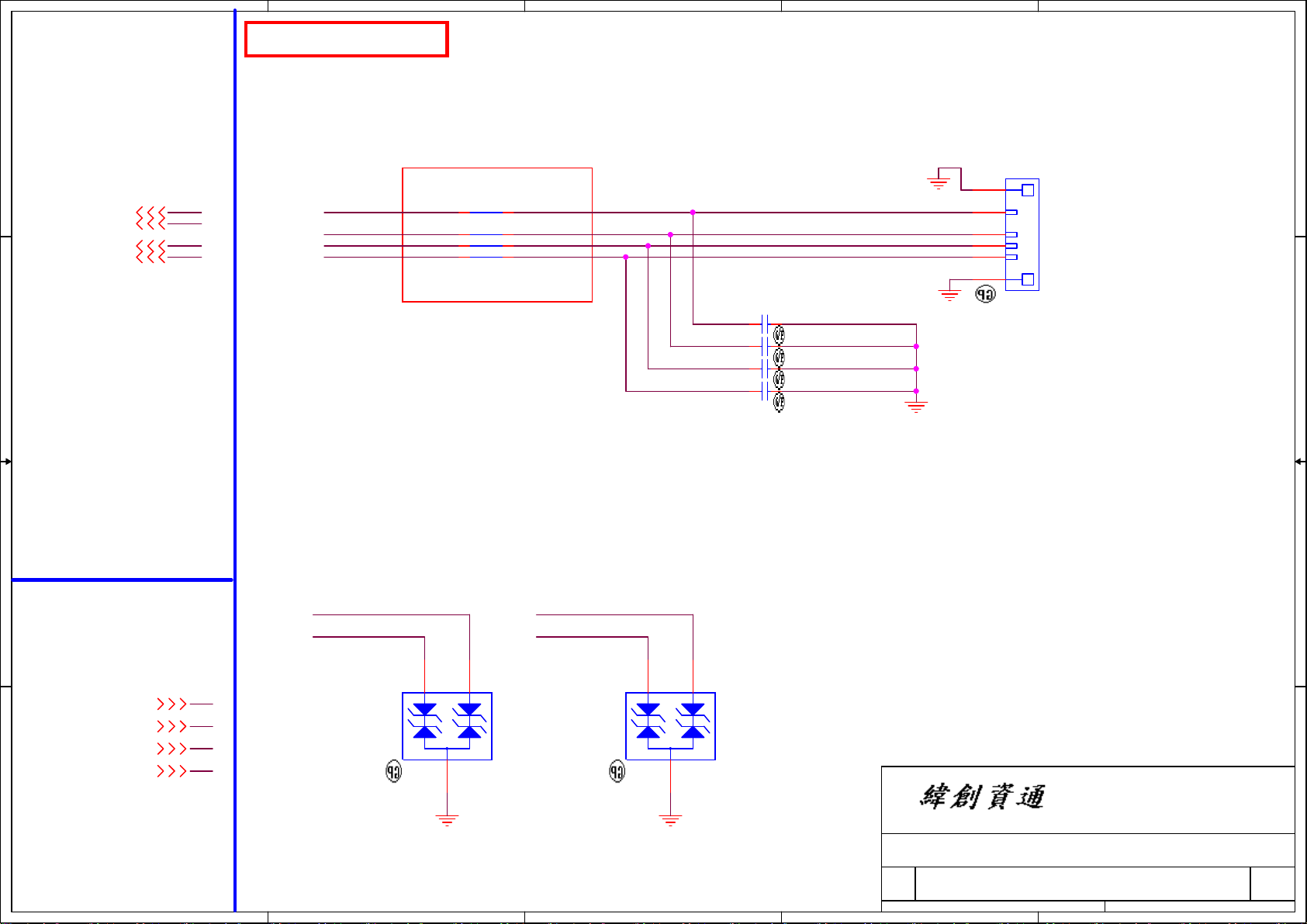

Main Func = PCH

DETECT&RESET

TOUCH_DET#55

RTC_DET#25

D D

DEBUG PORT

Touch Panel

LPSS_UART2_RXD68

LPSS_UART2_T XD68

Touch Pad

I2C

PM_TP_DATA65

PM_TP_CLK65

TOUCH_DET#

GPP_B18/GSPI0_MOSI

RTC_DET#

PSW_CLR#

GPP_B22/GSPI1_MOSI

LPSS_UART2_RXD

LPSS_UART2_T XD

-1m

PM_TP_DATA

PM_TP_CLK

CPU1F

AN8

GPP_B15/GSPI0_CS#

AP7

GPP_B16/GSPI0_CLK

AP8

GPP_B17/GSPI0_MISO

AR7

GPP_B18/GSPI0_MOSI

AM5

GPP_B19/GSPI1_CS#

AN7

GPP_B20/GSPI1_CLK

AP5

GPP_B21/GSPI1_MISO

AN5

GPP_B22/GSPI1_MOSI

AB1

GPP_C8/UART0_RXD

AB2

GPP_C9/UART0_TXD

W4

GPP_C10/UART0_RTS#

AB3

GPP_C11/UART0_CTS#

AD1

GPP_C20/UART2_RXD

AD2

GPP_C21/UART2_TXD

AD3

GPP_C22/UART2_RTS#

AD4

GPP_C23/UART2_CTS#

U7

GPP_C16/I2C0_SDA

U6

GPP_C17/I2C0_SCL

U8

GPP_C18/I2C1_SDA

U9

GPP_C19/I2C1_SCL

AH9

GPP_F4/I2C2_SDA

AH10

GPP_F5/I2C2_SCL

AH11

GPP_F6/I2C3_SDA

AH12

GPP_F7/I2C3_SCL

AF11

GPP_F8/I2C4_SDA

AF12

GPP_F9/I2C4_SCL

SKYLAKE-U-GP

CPU

4

LPSS ISH

SKYLAKE_ULT

Strap

Strap

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SDA

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

1.8V Only

SX_EXIT_HOLDOFF#/GPP_A12/BM_BUSY#/ISH_GP6

3

6 OF 20

GPP_D9

GPP_D10

GPP_D11

GPP_D12

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D15/ISH_UART0_RTS#

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

P2

P3

P4

P1

M4

N3

N1

N2

AD11

AD12

U1

U2

U3

U4

AC1

AC2

AC3

AB4

AY8

BA8

BB7

BA7

AY7

AW7

AP13

TPM_ID

-1m

1.8V Only

MEM_CHA_EN

MEM_CHB_EN

MEM_CONFIG1

MEM_CONFIG2

2

12

R604

10KR2J-3-GP

10KR2J-3-GP

10KR2J-3-GP

MEM_CONFIG1 MEM_CONFIG2

10KR2J-3-GP

DY

12

R605

DY

3D3V_S5 3D3V_S5

12

R608

DY

12

R609

DY

10KR2J-3-GP

MEM_CHB_ENMEM_CHA_EN

10KR2J-3-GP

R606

R607

R610

10KR2J-3-GP

R611

10KR2J-3-GP

1

3D3V_S53D3V_S5

12

DY

12

DY

12

DY

12

DY

[#545659 Rev0.7]

C C

OTHER

GPP_B18/GSPI0_MOSI14

GPP_B22/GSPI1_MOSI14

PSW_CLR#

TOUCH_DET#

4

3D3V_S0 3D3V_S0

RN611

SRN2K2J-5-GP

23

1

PM_TP_CLK

PM_TP_DATA

RTC_DET#

8

7

6

R603

1 2

10KR2J-3-GP

RN609

SRN2K2J-4-GP

3D3V_S5

1

2

3

45

PSW_CLR#

21

Pass Word Clear

G601

B B

A A

5

GAP-OPEN

TPM_ID

4

R602

12

TPM

10KR2F-L1-GP

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

e Document Number Rev

Size Document Number Rev

Size Document Number Rev

Siz

Custom

Custom

Custom

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

CPU_(LPSS/ISH)

CPU_(LPSS/ISH)

CPU_(LPSS/ISH)

Carlsberg_KL

Carlsberg_KL

Carlsberg_KL

1

6 106

6 106

6 106

-1M

-1M

-1M

5

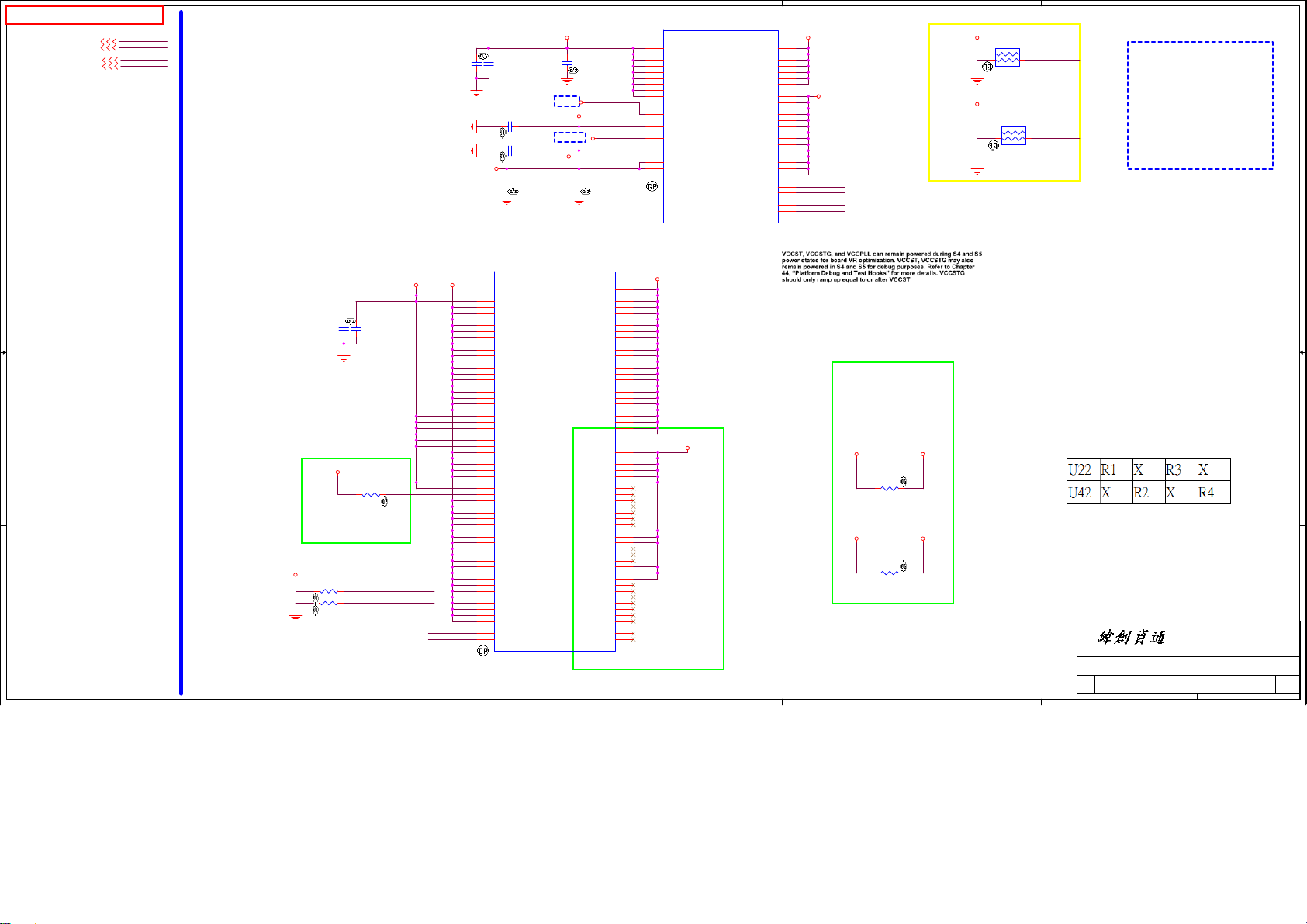

Main Func = CPU

SVID

SVID_ALERT#_CPU46

SVID_CLK_CPU46

D D

SVID_DATA_CPU46

VCCCORE_SENSE46

VSSCORE_SENSE46

C C

B B

1V_CPU_CORE

A30

A34

A39

A44

AK33

AK35

AK37

AK38

AK40

AL33

AL37

AL40

AM32

AM33

AM35

AM37

AM38

G30

K32

AK32

AB62

P62

V62

H63

G61

AC63

AE63

AE62

AG62

AL63

AJ62

CPU1L

SKYLAKE-U-GP

CPU POWER 1 OF 4

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVD#K32

RSVD#AK32

VCCOPC3

VCCOPC2

VCCOPC1

VCC_OPC_1P82

VCC_OPC_1P81

VCCOPC_SENSE

VSSOPC_SENSE

VCCEOPIO2

VCCEOPIO1

VCCEOPIO_SENSE

VSSEOPIO_SENSE

SKYLAKE_ULT

CPU

4

12 OF 20

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC_SENSE

VSS_SENSE

VIDALERT#

VIDSCK

VIDSOUT

VCCSTG

1V_CPU_CORE

G32

G33

G35

G37

G38

G40

G42

J30

J33

J37

J40

K33

K35

K37

K38

K40

K42

K43

VCCCORE_SENSE

E32

VSSCORE_SENSE

E33

VIDALERT#_CPU

B63

VIDSCK_CPU

A63

VIDSOUT_CPU

D64

G20

VCCSTG(ICCMAX.=0.04A)

1V_VCCST

VIDSCK_CPU

VIDSOUT_CPU

1V_VCCSTG

1V_VCCSTG1V_VCCIO

R709

1 2

0R0402-PAD-1-GP

Layout Note:

1. Place close to CPU

2. VCC_SENSE/ VSS_SENSE

impedance=50 ohm

3. Length match<25mil

3

R727

1 2

56R2J-4-GP

54D9R2F-L1-GP

1 2

R731

DY

12

R726 100R2F-L3-GP

1 2

R728 220R2J-L2-GP

1 2

R729 0R0402-PAD-1-GP

1 2

R730 0R0402-PAD-1-GP

CLOSE CPU

VCCCORE_SENSE

VSSCORE_SENSE

1. Place close to CPU

VCC_SENSE/ VSS_SENSE impedance=50 ohm

2.

3. Length match<25mil

SVID_ALERT#_CPU

SVID_CLK_CPU

SVID_DATA_CPU

SVID_ALERT#_CPUVIDALERT#_CPU

SVID_CLK_CPU

SVID_DATA_CPU

1V_CPU_CORE

12

R732 100R2F-L3-GP

12

R733 100R2F-L3-GP

2

1

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

A A

Title

Title

Title

ze Document Number Rev

Size Document Number Rev

Size Document Number Rev

Si

Custom

Custom

Custom

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CPU_POWER1

CPU_POWER1

CPU_POWER1

Carlsberg_KL

Carlsberg_KL

Carlsberg_KL

1

7 106

7 106

7 106

-1M

-1M

-1M

Main Func = CPU

5

VSSSA_SENSE46

VCCSA_SENSE46

VCCGT_SENSE46

VSSGT_SENSE46

D D

4

DY

FC800

SCD1U25V2KX-L-GP

DY

FC801

SCD1U25V2KX-L-GP

1 2

1 2

20170221 Change 1D2V_S3

12

C802 SC1U10V2KX-1GP

12

C803 SCD1U25V2KX-L-GP

1V_VCCST

C804

12

SCD1U25V2KX-L-GP

1D2V_S3

1D2V_S3

12

1D2V_S3

1V_VCCST

1V_VCCSTG

VDDQ 2A

C801

SC1U10V2KX-1GP

VD

DQC 0D2A

VccST 0D06A

0D02A 10mils

VCCPLL_OC 0D12A

VccPLL 0D12A

C805

12

SCD1U25V2KX-L-GP

DY

AU23

AU28

AU35

AU42

BB23

BB32

BB41

BB47

BB51

AM40

AL23

A18

A22

K20

K21

3

CPU1N

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQC

VCCST

VCCSTG

VCCPLL_OC

VCCPLL

VCCPLL

SKYLAKE-U-GP

CPU

CPU POWER 3 OF 4

SKYLAKE_ULT

14 OF 20

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCIO_SENSE

VSSIO_SENSE

VSSSA_SENSE

VCCSA_SENSE

AK28

AK30

AL30

AL42

AM28

AM30

AM42

AK23

AK25

G23

G25

G27

G28

J22

J23

J27

K23

K25

K27

K28

K30

AM23

AM22

H21

H20

1V_VCCIO

1V_VCCSA

VCCIO_SENSE

VSSIO_SENSE

VSSSA_SENSE

VCCSA_SENSE

VccIO 1D0V 3D1A

VccSA 0-1.15V 5A

2

1V_VCCSA

RN805

VCCSA_SENSE

1

4

1V_VCCIO

SRN100J-3-GP

RN806

4

SRN100J-3-GP

23

1

23

VSSSA_SENSE

VCCIO_SENSE

VSSIO_SENSE

1

20170223 Delete

C C

DY

FC803

SCD1U25V2KX-L-GP

B B

1V_VCCGT

A A

5

1 2

1V_VCCGT

U42:DY

U22:Stuff

R814

12

R815

12

DY

FC802

SCD1U25V2KX-L-GP

1 2

R813

1 2

0R2J-2-GP

U22

100R2F-L3-GP

100R2F-L3-GP

1V_VCCGT_C

VCCGT_SENSE

VSSGT_SENSE

4

1V_VCCGT

CPU_POWER_K52

VCCGT_SENSE

VSSGT_SENSE

CPU1M

CPU POWER 2 OF 4

A48

VCCGT

SKYLAKE_ULT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT_SENSE

VSSGT_SENSE

SKYLAKE-U-GP

42 and U22 power co-lay

AA63

AA64

AA66

AA67

AA69

AA70

AA71

AC64

AC65

AC66

AC67

AC68

AC69

AC70

AC71

A53

A58

A62

A66

J43

J45

J46

J48

J50

J52

J53

J55

J56

J58

J60

K48

K50

K52

K53

K55

K56

K58

K60

L62

L63

L64

L65

L66

L67

L68

L69

L70

L71

M62

N63

N64

N66

N67

N69

J70

J69

U

13 OF 20

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGTX1

VCCGTX2

VCCGTX3

VCCGTX4

VCCGTX5

VCCGTX6

VCCGTX7

VCCGTX8

VCCGTX9

VCCGTX10

VCCGTX11

VCCGTX12

VCCGTX13

VCCGTX14

VCCGTX15

VCCGTX16

VCCGTX17

VCCGTX18

VCCGTX19

VCCGTX20

VCCGTX21

VCCGTX22

VCCGTX23

VCCGTX24

VCCGTX25

VCCGTX26

VCCGTX27

VCCGTX28

VCCGTX29

VCCGTX_SENSE

VSSGTX_SENSE

N70

N71

R63

R64

R65

R66

R67

R68

R69

R70

R71

T62

U65

U68

U71

W63

W64

W65

W66

W67

W68

W69

W70

W71

Y62

AK42

AK43

AK45

AK46

AK48

AK50

AK52

AK53

AK55

AK56

AK58

AK60

AK70

AL43

AL46

AL50

AL53

AL56

AL60

AM48

AM50

AM52

AM53

AM56

AM58

AU58

AU63

BB57

BB66

AK62

AL61

1V_VCCGT

CPU

3

1V_CPU_CORE

If no plan to use U

e in the same

2+3

platform. These balls

can be connected to

VccCore. No shunting

resistor needed.

20170208 ENG R811 Change to 063.R0007.0161

1V_VCCGT_C 1V_VCCGT

R3

R811

1 2

D0002R5J-GP-U

063.R0007.0161

U22

1V_VCCGT_C 1V_CPU_CORE

R4

R812

1 2

D0002R5J-GP-U

063.R0007.0161

U42

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

e Document Number Rev

Size Document Number Rev

Size Document Number Rev

Siz

Custom

Custom

Custom

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

CPU_POWER1

CPU_POWER1

CPU_POWER1

Carlsberg_KL

Carlsberg_KL

Carlsberg_KL

1

8 106

8 106

8 106

-1M

-1M

-1M

5

D D

C C

4

3

2

1

Blanking

B B

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

A A

Title

Title

Title

Reserved

Reserved

Reserved

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Date: Sheet of

Date: Sheet of

Date: Sheet of

5

4

3

2

Carlsberg_KL

Carlsberg_KL

Carlsberg_KL

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

9 106

9 106

9 106

1

-1M

-1M

-1M

12

PC1002

SC22U6D3V3MX-L1-GP

12

PC1034

SC22U6D3V3MX-L1-GP

PC10A2

12

SC22U6D3V3MX-L1-GP

PC1039

12

SC10U6D3V2MX-GP-U

DY

PC1017

12

SC10U6D3V2MX-GP-U

PC1033

12

SC10U6D3V2MX-GP-U

DY

20170118 DY

5

12

PC1018

DY

SC22U6D3V3MX-L1-GP

12

PC1035

SC22U6D3V3MX-L1-GP

PC10A3

12

SC22U6D3V3MX-L1-GP

DY

PC1040

12

SC10U6D3V2MX-GP-U

DY

20170308 DY

PC1031

12

SC10U6D3V2MX-GP-U

DY

PC1036

12

SC10U6D3V2MX-GP-U

DY

20170308 DY

20170308 DY

12

PC1019

SC22U6D3V3MX-L1-GP

12

PC1041

SC22U6D3V3MX-L1-GP

PC10A4

12

SC22U6D3V3MX-L1-GP

DY

PC1003

12

SC10U6D3V2MX-GP-U

DY

20170118 DY

PC10A5

12

SC10U6D3V2MX-GP-U

DY

PC1037

12

SC10U6D3V2MX-GP-U

12

PC1021

SC22U6D3V3MX-L1-GP

12

PC1042

SC22U6D3V3MX-L1-GP

PC10A9

12

SC22U6D3V3MX-L1-GP

DY

PC1004

12

SC10U6D3V2MX-GP-U

DY

PC10A6

12

SC10U6D3V2MX-GP-U

Main Func = CPU

1V_CPU_CORE

12

PC1001

SC22U6D3V3MX-L1-GP

1V_CPU_CORE

12

D D

PC1030

SC22U6D3V3MX-L1-GP

1V_CPU_CORE

PC10A1

12

SC22U6D3V3MX-L1-GP

DY

1V_CPU_CORE

PC1038

12

SC10U6D3V2MX-GP-U

DY

20170124 DY

1V_CPU_CORE

PC1008

12

SC10U6D3V2MX-GP-U

DY

20170118 DY

1V_CPU_CORE

PC1032

12

SC10U6D3V2MX-GP-U

DY

C C

20170124 DY

12

PC1022

SC22U6D3V3MX-L1-GP

12

PC1043

SC22U6D3V3MX-L1-GP

PC10B1

12

SC22U6D3V3MX-L1-GP

DY

PC1005

12

SC10U6D3V2MX-GP-U

DY

PC1020

12

SC10U6D3V2MX-GP-U

1V_CPU_CORE

4

PC1047

12

SC1U10V2KX-L1-GP

12

PC1023

SC22U6D3V3MX-L1-GP

12

PC1044

SC22U6D3V3MX-L1-GP

PC1006

12

SC10U6D3V2MX-GP-U

DY

20170308 DY

12

20170118 DY

0603 22u

PC1046

SC18P50V2JN-1-GP

DY

12

PC1024

SC22U6D3V3MX-L1-GP

12

PC1045

SC22U6D3V3MX-L1-GP

PC1007

12

SC10U6D3V2MX-GP-U

DY

3

1V_CPU_CORE

U22 0603 22uF *22 , 0402 10uF*11 , 1uF*1

U42 0603 22uF *4 , 0402 10uF*15

1D2V_S3

PC1009

12

SC10U6D3V2MX-GP-U

DY

20170118 DY

1D2V_S3

PC1025

12

SC10U6D3V2MX-GP-U

1V_CPU_CORE

12

1V_CPU_CORE

12

U42

1V_CPU_CORE

12

DY

PC10C1

SC10U6D3V2MX-GP-U

DY

20170124 DY

PC10D2

SC10U6D3V2MX-GP-U

PC10E4

SC22U6D3V3MX-L1-GP

PC1010

12

SC10U6D3V2MX-GP-U

PC1026

12

SC10U6D3V2MX-GP-U

12

12

U42

12

DY

PC10C2

SC10U6D3V2MX-GP-U

DY

PC10D3

SC10U6D3V2MX-GP-U

PC10E5

SC22U6D3V3MX-L1-GP

12

12

12

U42

12

U42

12

U42

PC1011

SC10U6D3V2MX-GP-U

PC1027

SC10U6D3V2MX-GP-U

PC10C3

SC10U6D3V2MX-GP-U

PC10D4

SC10U6D3V2MX-GP-U

PC10E6

SC22U6D3V3MX-L1-GP

PC1012

12

SC10U6D3V2MX-GP-U

PC1028

12

SC10U6D3V2MX-GP-U

For U42 power

PC10C4

12

SC10U6D3V2MX-GP-U

U42

PC10D5

12

SC10U6D3V2MX-GP-U

U42

PC10E7

12

SC22U6D3V3MX-L1-GP

U42

2

12

DY

20170118 DY

12

U42

U42

U42

PC1013

SC10U6D3V2MX-GP-U

PC1029

SC10U6D3V2MX-GP-U

PC10C5

12

SC10U6D3V2MX-GP-U

PC10D6

12

SC10U6D3V2MX-GP-U

PC10E8

12

SC10U6D3V2MX-GP-U

PC1014

12

SC10U6D3V2MX-GP-U

PC10E1

12

SC10U6D3V2MX-GP-U

12

U42

12

U42

12

U42

PC10C6

SC10U6D3V2MX-GP-U

PC10D7

SC10U6D3V2MX-GP-U

PC10E9

SC10U6D3V2MX-GP-U

PC1015

12

SC10U6D3V2MX-GP-U

PC10E2

12

SC10U6D3V2MX-GP-U

12

U42

20170118

12

DY

12

U42

PC10C7

SC10U6D3V2MX-GP-U

PC10D8

SC10U6D3V2MX-GP-U

PC10F1

SC10U6D3V2MX-GP-U

1D2V_S3

0402 10uF*13

PC1016

12

SC10U6D3V2MX-GP-U

PC10E3

12

SC10U6D3V2MX-GP-U

DY

20170118 DY

PC10D1

12

SC10U6D3V2MX-GP-U

DY

20170124 DY

PC10D9

12

SC10U6D3V2MX-GP-U

DY

20170124 DY

PC10F2

12

SC10U6D3V2MX-GP-U

U42

1

0603 22u

1V_VCCIO

10uF * 2 1uF *4

1V_VCCIO

PC1048

12

SC10U6D3V2MX-GP-U

2017/07/06 -1

PC1049

12

SC10U6D3V2MX-GP-U

PC1050

12

SC10U6D3V2MX-GP-U

PC1051

12

SC1U10V2KX-L1-GP

PC1052

12

SC1U10V2KX-L1-GP

PC1055

12

SC1U10V2KX-L1-GP

PC1056

12

SC1U10V2KX-L1-GP

20170118 DY

1V_VCCGT_C

PC10A7

12

SC10U6D3V2MX-GP-U

B B

A A

PC10A8

12

SC10U6D3V2MX-GP-U

5

PC10B2

12

SC22U6D3V3MX-L1-GP

20170118

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

CPU_(Power CAP1)

CPU_(Power CAP1)

CPU_(Power CAP1)

Carlsberg_KL

Carlsberg_KL

Carlsberg_KL

1

10 106

10 106

10 106

-1M

-1M

-1M

of

Main Func = CPU

5

4

3

2

1

LICED GT

S

1V_VCCGT

12

D D

C C

1V_VCCGT

12

1V_VCCGT

12

1V_VCCGT

12

DY

1V_VCCGT

12

DY

1V_VCCGT

12

CLOSE CPU AB19 CLOSE CPU AF20CLOSE CPU K17

SC1U10V2KX-L1-GP

U-line 23e 28W

IccMax current-10ms max[A] = 67 A

PC1101

SC22U6D3V3MX-L1-GP

PC1167

SC22U6D3V3MX-L1-GP

PC1121

SC10U6D3V2MX-GP-U

PC1133

SC10U6D3V2MX-GP-U

PC1109

SC10U6D3V2MX-GP-U

PC1165

SC10U6D3V2MX-GP-U

1D0V_S5 1D0V_S5 1D0V_S5

12

PC1142

SC1U10V2KX-L1-GP

12

PC1102

SC22U6D3V3MX-L1-GP

12

PC10B3

SC22U6D3V3MX-L1-GP

12

PC1122

SC10U6D3V2MX-GP-U

12

PC1107

SC10U6D3V2MX-GP-U

12

PC1110

SC10U6D3V2MX-GP-U

DY

12

PC1166

SC10U6D3V2MX-GP-U

DY

SC1U10V2KX-L1-GP

12

PC1112

SC22U6D3V3MX-L1-GP

12

PC10B4

SC22U6D3V3MX-L1-GP

12

PC1123

SC10U6D3V2MX-GP-U

12

PC1108

SC10U6D3V2MX-GP-U

12

PC1111

SC10U6D3V2MX-GP-U

DY

12

PC1143

DY

SC1U10V2KX-L1-GP

CLOSE CPU AF18 CLOSE CPU N18

3D3V_S5

12

PC1153

SC1U10V2KX-L1-GP

3D3V_S5

3D3V_S5 3D3V_S5 3D3V_S5

12

PC1154

DY

SC1U10V2KX-L1-GP

0603 22u

12

PC1116

SC22U6D3V3MX-L1-GP

12

PC10B5

SC22U6D3V3MX-L1-GP

12

PC1124

SC10U6D3V2MX-GP-U

12

PC1136

SC10U6D3V2MX-GP-U

DY

12

PC1141

SC10U6D3V2MX-GP-U

DY

2017/07/06 -1

1D0V_S5 1D0V_S5

12

PC1144

SC1U10V2KX-L1-GP

CLOSE CPU N15

12

PC1155

SC1U10V2KX-L1-GP

DY

12

PC1134

SC22U6D3V3MX-L1-GP

12

PC10B6

SC22U6D3V3MX-L1-GP

12

PC1125

SC10U6D3V2MX-GP-U

12

PC1103

SC10U6D3V2MX-GP-U

12

PC1113

SC10U6D3V2MX-GP-U

12

12

SC22U6D3V5MX-L3-GP

PC1145

PC1146

12

PC1135

SC22U6D3V3MX-L1-GP

12

PC10B7

SC22U6D3V3MX-L1-GP

12

PC1126

SC10U6D3V2MX-GP-U

12

PC1104

SC10U6D3V2MX-GP-U

12

PC1114

SC10U6D3V2MX-GP-U

SC1U10V2KX-L1-GP

12

PC1147

CLOSE CPU K15

12

PC1156

DY

12

PC1157

SC1U10V2KX-L1-GP

DY

12

PC1137

SC22U6D3V3MX-L1-GP

12

PC1127

SC10U6D3V2MX-GP-U

DY

12

PC1105

SC10U6D3V2MX-GP-U

12

PC1115

SC10U6D3V2MX-GP-U

1D0V_S5

12

SC1U10V2KX-L1-GP

PC1148

3D3V_S5 3D3V_RTC_AUX

12

12

PC1159

PC1158

SCD1U25V2KX-L-GP

SC1U10V2KX-L1-GP

12

PC1138

SC22U6D3V3MX-L1-GP

12

PC1128

SC10U6D3V2MX-GP-U

DY

12

PC1168

SC10U6D3V2MX-GP-U

DY

12

PC1171

SC10U6D3V2MX-GP-U

1D0V_S5

SC1U10V2KX-L1-GP

12

PC1149

1D0V_S5

SC1U10V2KX-L1-GP

12

PC1150

DY

CLOSE CPU A10

12

12

PC1160

SC1U10V2KX-L1-GP

PC1161

SCD1U25V2KX-L-GP

1V_VCCGT

0603 22uF *14 , 0402 10uF*28

1V_VCCSA

2017/05/16 - SB

2017/05/19 - SB

1V_VCCSA

12

PC1172

SC10U6D3V2MX-GP-U

1V_VCCSA

12

1V_VCCSA

12

PC1139

SC10U6D3V2MX-GP-U

1D0V_VCCDSW

12

SC1U10V2KX-L1-GP

PC1129

SC22U6D3V3MX-L1-GP

PC1163

12

PC1173

SC10U6D3V2MX-GP-U

12

PC1130

SC22U6D3V3MX-L1-GP

12

VCCRTCEXT

12

SCD1U25V2KX-L-GP

CLOSE CPU AL1 CLOSE CPU BB10

1D8V_S5

12

PC1162

SC1U10V2KX-L1-GP

PC1170

SC10U6D3V2MX-GP-U

PC1164

12

12

PC1119

SC22U6D3V3MX-L1-GP

PC1131

SC22U6D3V3MX-L1-GP

12

PC1152

SC10U6D3V2MX-GP-U

0402 10uF*4

0603 22uF*6

12

PC1120

SC22U6D3V3MX-L1-GP

12

PC1132

SC22U6D3V3MX-L1-GP

20170118

12

PC1140

SC10U6D3V2MX-GP-U

B B

CLOSE CPU V19

CLOSE CPU AG15CLOSE CPU AJ19

CLOSE CPU Y16

CLOSE CPU AK17CLOSE CPU T16

CLOSE CPU AK19

CLOSE CPU AA1

2017/06/30 -1

1V_VCCGT

12

PC1183

SC10U6D3V2MX-GP-U

1V_VCCGT

12

PC1187

SC10U6D3V2MX-GP-U

1V_VCCSA

12

PC1198

SC10U6D3V2MX-GP-U

A A

1V_VCCSA

12

PC1117

SC10U6D3V2MX-GP-U

5

12

PC1174

SC10U6D3V2MX-GP-U

12

PC1177

SC10U6D3V2MX-GP-U

12

PC1197

SC10U6D3V2MX-GP-U

12

PC1118

SC10U6D3V2MX-GP-U

12

PC1182

SC10U6D3V2MX-GP-U

12

PC1180

SC10U6D3V2MX-GP-U

12

PC1199

SC10U6D3V2MX-GP-U

12

PC1151

SC10U6D3V2MX-GP-U

12

PC1179

SC10U6D3V2MX-GP-U

12

PC1188

SC10U6D3V2MX-GP-U

12

PC1106

SC10U6D3V2MX-GP-U

Modify by power Jason

2017/0630

4

12

PC1184

SC10U6D3V2MX-GP-U

12

PC1181

SC10U6D3V2MX-GP-U

12

PC1185

SC10U6D3V2MX-GP-U

12

PC1186

SC10U6D3V2MX-GP-U

12

PC1189

SC10U6D3V2MX-GP-U

12

PC1178

SC10U6D3V2MX-GP-U

12

PC1175

SC10U6D3V2MX-GP-U

12

PC1176

SC10U6D3V2MX-GP-U

Modify by power Jason

2017/0630

3

12

PC1190

SC10U6D3V2MX-GP-U

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Wednesday, November 01, 2017

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

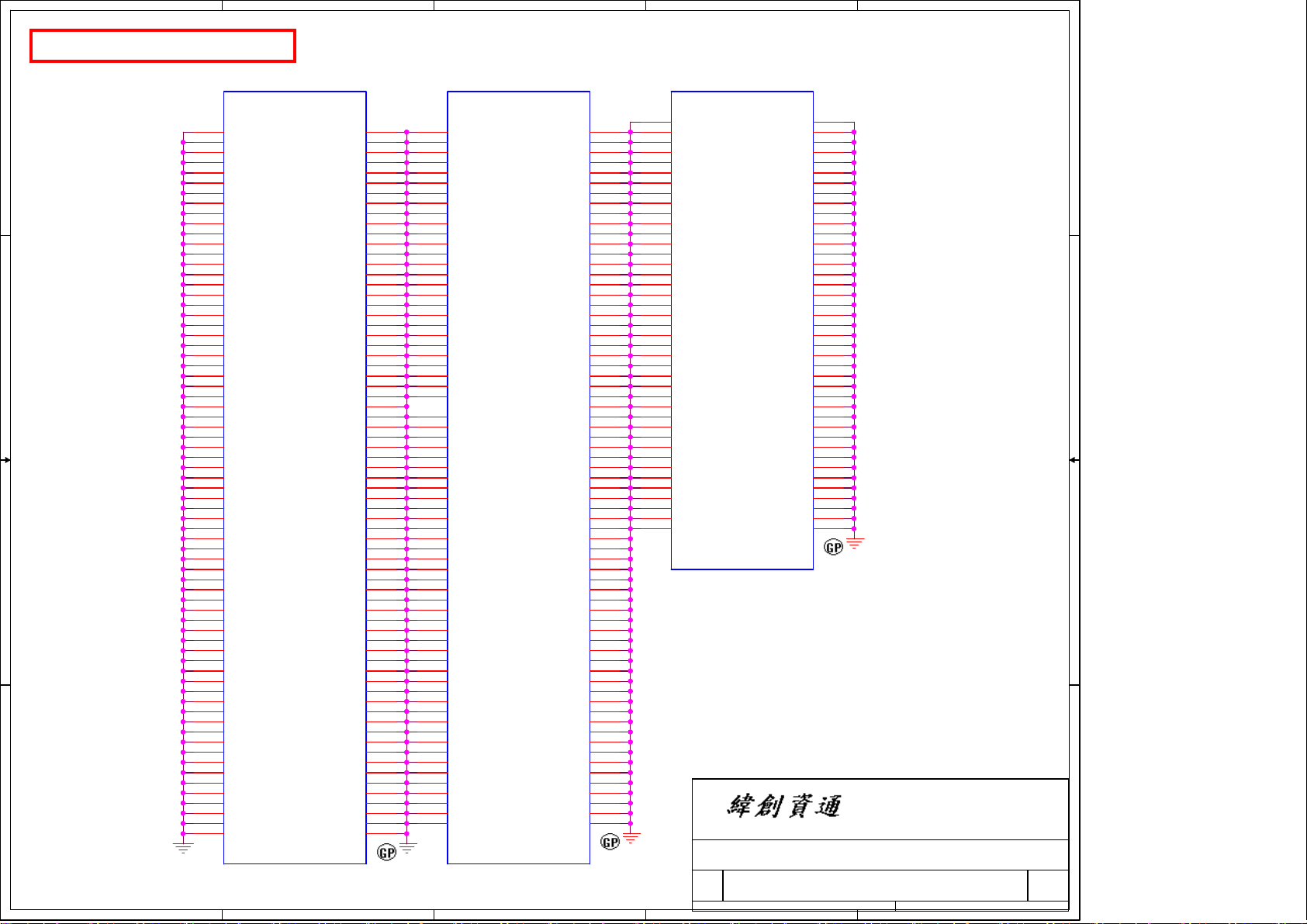

CPU_(Power CAP2)

CPU_(Power CAP2)

CPU_(Power CAP2)

Carlsberg_KL

Carlsberg_KL

Carlsberg_KL

1

11 106

11 106

11 106

-1M

-1M

-1M

5

4

3

2

1

1D2V_S3

1D2V_S3

DY

FC1200

1 2

1D8V_DDR

1 2

DY

FC1201

SCD1U25V2KX-L-GP

U1201A

A3

VDD1

U3

VDD1

A4

VDD1

U4

VDD1

A5

VDD1

U5

VDD1

A6

VDD1

U6

VDD1

A10

VDD1

U10

VDD1

D4

VDD2

P4

VDD2

D5

VDD2

G5

VDD2

H5

VDD2

J5

VDD2

K5

VDD2

L5

VDD2

P5

VDD2

D6

VDD2

H6

VDD2

J6

VDD2

K6

VDD2

P6

VDD2

A8

VDD2

U8

VDD2

A9

VDD2

U9

VDD2

H12

VDD2

K12

VDD2

F2

VDDCA

G2

VDDCA

L2

VDDCA

M2

VDDCA

H3

VDDCA

E8

VDDQ

H8

VDDQ

K8

VDDQ

N8

VDDQ

H9

VDDQ

J9

VDDQ

J10

VDDQ

A11

VDDQ

H11

VDDQ

K11

VDDQ

U11

VDDQ

C12

VDDQ

E12

VDDQ

G12

VDDQ

L12

VDDQ

N12

VDDQ

R12

VDDQ

K4E6E304EE-EGCF-GP

1 OF 2

VSSCA

VSSCA

VSSCA

VSSCA

VSSCA

VSSCA

VSSCA

VSSCA

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Layout Note:Place Close U1201 between U1301

CHA/CHB_LPDDR3_VREFCA

V_DDR_CA_VREF4

1D2V_S3

12

R1210

1 2

R1212

10R2F-L-GP

2

8K2R2F-1-GP

12

R1211

8K2R2F-1-GP

M_VREF_DQ_SA

B2

H2

K2

T2

T3

E4

N4

R4

T4

B5

C5

E5

F5

M5

N5

R5

T5

L6

J12

C3

D3

G3

P3

F4

G4

J4

M4

B6

C6

E6

F6

G6

M6

N6

R6

T6

G9

L9

H10

K10

B12

D12

F12

M12

P12

T12

SCD1U25V2KX-L-GP

R1206

1 2

5D11R2F-GP

12

C1239

+V_VREF_RC3

SCD022U25V2KX-GP

12

R1207

24D9R2F-L-GP

Channel A

2 OF 2

M_A_CLK0

M_A_DQ[63:0]4

D D

C C

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_VREF_CA_DIMMA

M_VREF_DQ_SA

DQS

DATA

M_A_DQS_DP[7:0]4

M_A_DQS_DN[7:0]4

B B

M_A_DQS_DP0

M_A_DQS_DP1

M_A_DQS_DP2

M_A_DQS_DP3

M_A_DQS_DP4

M_A_DQS_DP5

M_A_DQS_DP6

M_A_DQS_DP7

M_A_DQS_DN0

M_A_DQS_DN1

M_A_DQS_DN2

M_A_DQS_DN3

M_A_DQS_DN4

M_A_DQS_DN5

M_A_DQS_DN6

M_A_DQS_DN7

CMD

M_A_CA_A[9:0]4

M_A_CA_B[9:0]4

M_A_CLK04

M_A_CLK#04

M_A_CLK14

M_A_CLK#14

A A

M_A_CKE04

M_A_CKE14

M_A_CKE24

M_A_CKE34

M_A_CS#04

M_A_CS#14

M_A_ODT04

CLK

CKE

CTRL

M_A_CA_A0

M_A_CA_A1

M_A_CA_A2

M_A_CA_A3

M_A_CA_A4

M_A_CA_A5

M_A_CA_A6

M_A_CA_A7

M_A_CA_A8

M_A_CA_A9

M_A_CA_B0

M_A_CA_B1

M_A_CA_B2

M_A_CA_B3

M_A_CA_B4

M_A_CA_B5

M_A_CA_B6

M_A_CA_B7

M_A_CA_B8

M_A_CA_B9

5

M_A_CLK#0

M_A_CKE0

M_A_CKE1

M_A_CS#0

M_A_CS#1

M_A_CA_A0

M_A_CA_A1

M_A_CA_A2

M_A_CA_A3

M_A_CA_A4

M_A_CA_A5

M_A_CA_A6

M_A_CA_A7

M_A_CA_A8

M_A_CA_A9

C1237

12

C1238

SCD047U16V2KX-1-GP

LPDDR3 DECAPS follow SkyLake U/Y PDG Table 4-58

Layout Note: Place these Caps near U1201

1D2V_S3

Q DECAPS VDD1 DECAPS VDD2 DECAPS

12

12

C1202

C1203

SC10U6D3V2MX-GP-U

SC10U6D3V2MX-GP-U

Layout Note: Place these Caps near U1202

VDDQ DECAPS

12

12

C1208

C1209

SC10U6D3V2MX-GP-U

SC10U6D3V2MX-GP-U

CHA TERMINATIONS

0D6V_VTT 0D6V_VTT

1 2

R1214 68R1J -GP

R1215 68R1J -GP

1 2

1 2

R1216 68R1J -GP

R1217 68R1J -GP

1 2

1 2

R1218 68R1J -GP

1 2

R1219 68R1J -GP

R1220 68R1J -GP

1 2

1 2

R1221 68R1J -GP

R1222 68R1J -GP

1 2

1 2

R1223 68R1J -GP

1 2

R1236 80D6R 1F-GP

R1237 80D6R 1F-GP

1 2

R1242 37D4R 2F-GP

1 2

1 2

R1243 37D4R 2F-GP

U1201B

J3

CK_T

J2

CK_C

K3

CKE0

K4

CKE1

L3

CS0#

L4

CS1#

R2

CA0

P2

CA1

N2

CA2

N3

CA3

M3

CA4

F3

CA5

E3

CA6

E2

CA7

D2

CA8

C2

CA9

L8

DM0

G8

DM1

P8

DM2

D8

DM3

H4

VREF_CA

J11

VREF_DQ

A1

DNU#A1

A2

12

DNU#A2

A12

DNU#A12

A13

DNU#A13

B1

DNU#B1

B13

DNU#B13

T1

DNU#T1

T13

DNU#T13

U1

SCD047U16V2KX-1-GP

DNU#U1

U2

DNU#U2

U12

DNU#U12

U13

DNU#U13

C4

NC#C4

K9

NC#K9

R3

NC#R3

K4E6E304EE-EGCF-GP

12

SCD1U10V1KX-GP

SCD1U10V1KX-GP

M_A_CA_A0

M_A_CA_A1

M_A_CA_A2

M_A_CA_A3

M_A_CA_A4

M_A_CA_A5

M_A_CA_A6

M_A_CA_A7

M_A_CA_A8

M_A_CA_A9

C1214

12

C1215

M_A_CKE0

M_A_CKE1

M_A_CLK0

M_A_CLK#0

12

SCD1U10V1KX-GP

SCD1U10V1KX-GP

12

C1223

SC1U10V2KX-L1-GP

12

C1224

SC1U10V2KX-L1-GP

M_A_DQ3

P9

DQ0

M_A_DQ7

N9

DQ1

M_A_DQ0

N10

DQ2

M_A_DQ5

N11

DQ3

M_A_DQ2

M8

DQ4

M_A_DQ6

M9

DQ5

M_A_DQ4

M10

DQ6

M_A_DQ1

M11

DQ7

M_A_DQ15

F11

DQ8

M_A_DQ10

F10

DQ9

M_A_DQ12

F9

DQ10

M_A_DQ9

F8

DQ11

M_A_DQ13

E11

DQ12

M_A_DQ14

E10

DQ13

M_A_DQ8

E9

DQ14

M_A_DQ11

D9

DQ15

M_A_DQ30

T8

DQ16

M_A_DQ26

T9

DQ17

M_A_DQ24

T10

DQ18

M_A_DQ28

T11

DQ19

M_A_DQ31

R8

DQ20

M_A_DQ27

R9

DQ21

M_A_DQ25

R10

DQ22

M_A_DQ29

R11

DQ23

M_A_DQ17

C11

DQ24

M_A_DQ16

C10

DQ25

M_A_DQ22

C9

DQ26

M_A_DQ18

C8

DQ27

M_A_DQ20

B11

DQ28

M_A_DQ21

B10

DQ29

M_A_DQ23

B9

DQ30

M_A_DQ19

B8

DQ31

M_A_DQS_DP0

L10

DQS0_T

M_A_DQS_DN0

L11

DQS0_C

M_A_DQS_DP1

G10

DQS1_T

M_A_DQS_DN1

G11

DQS1_C

M_A_DQS_DP3

P10

DQS2_T

M_A_DQS_DN3

P11

DQS2_C

M_A_DQS_DP2

D10

DQS3_T

M_A_DQS_DN2

D11

DQS3_C

CH_A_DRAM0_ZQ0

B3

ZQ0

CH_A_DRAM0_ZQ1

B4

ZQ1

M_A_ODT0

J8

ODT

1D8V_DDR 1D2V_S3

12

C1226

C1216

SC10U6D3V2MX-GP-U

1D8V_DDR 1D2V_S31D2V_S3

12

12

C1217

C1230

SC10U6D3V2MX-GP-U

R1224 68R1J -GP

R1225 68R1J -GP

R1227 68R1J -GP

R1226 68R1J -GP

R1229 68R1J -GP

R1228 68R1J -GP

R1231 68R1J -GP

R1230 68R1J -GP

R1233 68R1J -GP

R1232 68R1J -GP

R1238 80D6R 1F-GP

R1240 80D6R 1F-GP

R1244 37D4R 2F-GP

R1245 37D4R 2F-GP

4

DQ0

M_A_DQ[0:7]

DQ1

M_

DQ3

M_A_DQ[24:31]

DQ2

M_A_DQ[16:23]

M_A_DQS0

M_A_DQS1

M_A

M_A_DQS2

12

12

C1204

C1225

SC10U6D3V2MX-GP-U

SC10U6D3V2MX-GP-U

VDD1 DECAPS VDD2 DECAPS

12

12

C1210

C1231

SC10U6D3V2MX-GP-U

SC10U6D3V2MX-GP-U

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

A_DQ[8:15]

_DQS3

1 2

1 2

12

C1205

SC10U6D3V2MX-GP-U

12

SC10U6D3V2MX-GP-U

M_A_CA_B0

M_A_CA_B1

M_A_CA_B2

M_A_CA_B3

M_A_CA_B4

M_A_CA_B5

M_A_CA_B6

M_A_CA_B7

M_A_CA_B8

M_A_CA_B9

M_A_CKE2

M_A_CKE3

M_A_CLK1

M_A_CLK#1

C1211

M_VREF_CA_DIMMA

M_VREF_DQ_SA

R1202243R2F-2-GP

R1203243R2F-2-GP

12

12

C1227

C1228

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

12

12

C1233

C1234

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

M_A_CLK1

M_A_CLK#1

M_A_CKE2

M_A_CKE3

M_A_CS#0

M_A_CS#1

M_A_CA_B0

M_A_CA_B1

M_A_CA_B2

M_A_CA_B3

M_A_CA_B4

M_A_CA_B5

M_A_CA_B6

M_A_CA_B7

M_A_CA_B8

M_A_CA_B9

12

C1236

SCD047U16V2KX-1-GP

1D2V_S3

12

12

C1229

SC10U6D3V2MX-GP-U

SC1U10V2KX-L1-GP

1D2V_S3

12

12

C1232

SC10U6D3V2MX-GP-U

SC1U10V2KX-L1-GP

0D6V_VTT

R1234 80D6R 1F-GP

1 2

1 2

R1235 80D6R 1F-GP

1 2

R1241 80D6R 1F-GP

C1235

12

SCD047U16V2KX-1-GP

VDDCA DECAPSVDD

12

C1206

SC10U6D3V2MX-GP-U

VDDCA DECAPS

12

C1212

SC10U6D3V2MX-GP-U

3

C1207

C1213

M_A_CS#0

M_A_CS#1

M_A_ODT0

J3

J2

K3

K4

L3

L4

R2

P2

N2

N3

M3

F3

E3

E2

D2

C2

L8

G8

P8

D8

H4

J11

A1

A2

A12

A13

B1

B13

T1

T13

U1

U2

U12

U13

C4

K9

R3

U1202B

CK_T

CK_C

CKE0

CKE1

CS0#

CS1#

CA0

CA1

CA2

CA3

CA4

CA5

CA6

CA7

CA8

CA9

DM0

DM1

DM2

DM3

VREF_CA

VREF_DQ

DNU#A1

DNU#A2

DNU#A12

DNU#A13

DQS0_T

DNU#B1

DQS0_C

DNU#B13

DQS1_T

DNU#T1

DQS1_C

DNU#T13

DQS2_T

DQS2_C

DNU#U1

DQS3_T

DNU#U2

DQS3_C

DNU#U12

DNU#U13

NC#C4

NC#K9

NC#R3

K4E6E304EE-EGCF-GP

2 OF 2

M_A_DQ34

P9

DQ0

M_A_DQ38

N9

DQ1

M_A_DQ36

N10

DQ2

M_A_DQ33

N11

DQ3

M_A_DQ35

M8

DQ4

M_A_DQ39

M9

DQ5

M_A_DQ32

M10

DQ6

M_A_DQ37

M11

DQ7

M_A_DQ46

F11

DQ8

M_A_DQ43

F10

DQ9

M_A_DQ44

F9

DQ10

M_A_DQ41

F8

DQ11

M_A_DQ47

E11

DQ12

M_A_DQ42

E10

DQ13

M_A_DQ45

E9

DQ14

M_A_DQ40

D9

DQ15

M_A_DQ52

T8

DQ16

M_A_DQ48

T9

DQ17

M_A_DQ55

T10

DQ18

M_A_DQ54

T11

DQ19

M_A_DQ53

R8

DQ20

M_A_DQ49

R9

DQ21

M_A_DQ51

R10

DQ22

M_A_DQ50

R11

DQ23

M_A_DQ60

C11

DQ24

M_A_DQ57

C10

DQ25

M_A_DQ63

C9

DQ26

M_A_DQ58

C8

DQ27

M_A_DQ61

B11

DQ28

M_A_DQ56

B10

DQ29

M_A_DQ62

B9

DQ30

M_A_DQ59

B8

DQ31

M_A_DQS_DP4

L10

M_A_DQS_DN4

L11

M_A_DQS_DP5

G10

M_A_DQS_DN5

G11

M_A_DQS_DP6

P10

M_A_DQS_DN6

P11

M_A_DQS_DP7

D10

M_A_DQS_DN7

D11

CH_A_DRAM1_ZQ0

B3

ZQ0

CH_A_DRAM1_ZQ1

B4

ZQ1

M_A_ODT0

J8

ODT

Layout Note: Place these Caps

nea

r CHA Terminations

0D6V_VTT 0D6V_VTT 0D6V_VTT

12

12

C1243

C1242

C1241

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

VTT

SC1U6D3V2KX-GP

DECAPS

12

C1244

DQ4

M_A_DQ[32:39]

DQ5

M_A_DQ[40:47]

DQ6

M_A_DQ[48:55]

DQ7

M_A_DQ[56:63]

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

12

SC1U6D3V2KX-GP

C1246

1 2

1 2

SC22U6D3V3MX-1-GP

Layout Note:Place Close U1201

CHA_LPDDR3_VREFDQ

DDR_VREFDQ01_C HA4

R1204243R2F-2-GP

R1205243R2F-2-GP

SCD1U25V2KX-L-GP

12

12

C1245

SC1U6D3V2KX-GP

12

C1240

+V_VREF_RC1

SCD022U25V2KX-GP

12

R1213

24D9R2F-L-GP

1D8V_DDR

1D2V_S3

1D2V_S3

1D2V_S31D2V_S3

DY

DY

FC1202

FC1203

SCD1U25V2KX-L-GP

1 2

1 2

1D2V_S3

12

R1209

8K2R2F-1-GP

12

R1208

8K2R2F-1-GP

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

LPDDR3_CHA

LPDDR3_CHA

LPDDR3_CHA

Carlsberg_KL

Carlsberg_KL

Carlsberg_KL

1

1 OF 2

U1202A

A3

VDD1

VSS

U3

VDD1

VSS

A4

VDD1

VSS

U4

VDD1

VSS

A5

VDD1

VSS

U5

VDD1

VSS

A6

VDD1

VSS

U6

VDD1

A10

U10

H12

K12

J10

A11

H11

K11

U11

C12

E12

G12

L12

N12

R12

VSS

VDD1

VSS

VDD1

VSS

VSS

D4

VDD2

VSS

P4

VDD2

VSS

D5

VDD2

VSS

G5

VDD2

VSS

H5

VDD2

VSS

J5

VDD2

VSS

K5

VDD2

VSS

L5

VDD2

VSS

P5

VDD2

D6

VDD2

H6

VDD2

VSSCA

J6

VDD2

VSSCA

K6

VDD2

VSSCA

P6

VDD2

VSSCA

A8

VDD2

VSSCA

U8

VDD2

VSSCA

A9

VDD2

VSSCA

U9

VDD2

VSSCA

VDD2

VDD2

VSSQ

F2

VDDCA

VSSQ

G2

VDDCA

VSSQ

L2

VDDCA

VSSQ

M2

VDDCA

VSSQ

H3

VDDCA

VSSQ

VSSQ

E8

VDDQ

VSSQ

H8

VDDQ

VSSQ

K8

VDDQ

VSSQ

N8

VDDQ

VSSQ

H9

VDDQ

VSSQ

J9

VDDQ

VSSQ

VDDQ

VSSQ

VDDQ

VSSQ

VDDQ

VSSQ

VDDQ

VSSQ

VDDQ

VSSQ

VDDQ

VSSQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

K4E6E304EE-EGCF-GP

M_VREF_CA_DIMMA

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

12 106Wednesday, November 01, 2017

12 106Wednesday, November 01, 2017

12 106Wednesday, November 01, 2017

B2

H2

K2

T2

T3

E4

N4

R4

T4

B5

C5

E5

F5

M5

N5

R5

T5

L6

J12

C3

D3

G3

P3

F4

G4

J4

M4

B6

C6

E6

F6

G6

M6

N6

R6

T6

G9

L9

H10

K10

B12

D12

F12

M12

P12

T12

-1M

-1M

-1M

5

4

3