5

D D

4

3

2

1

HuaQin Confidential

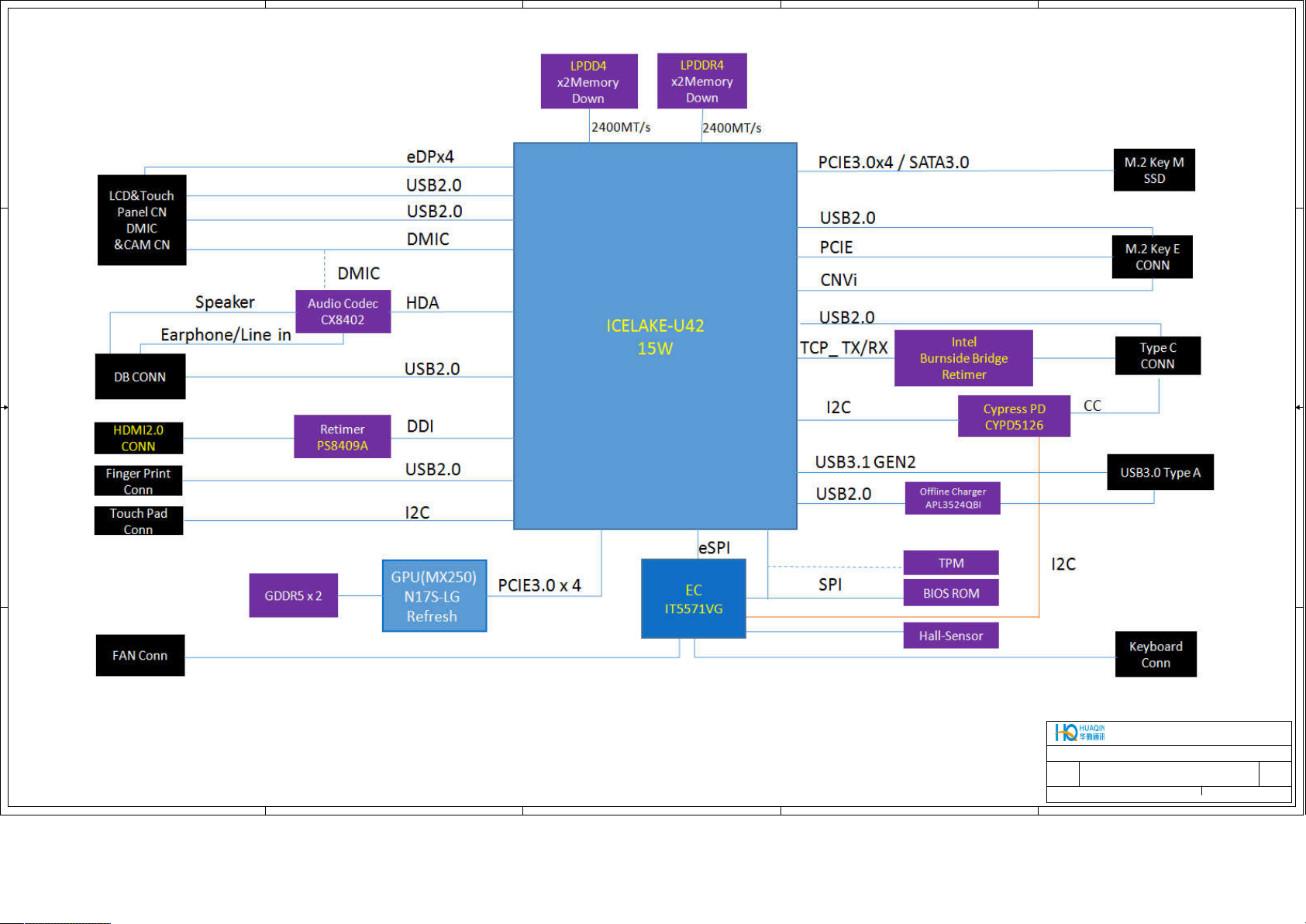

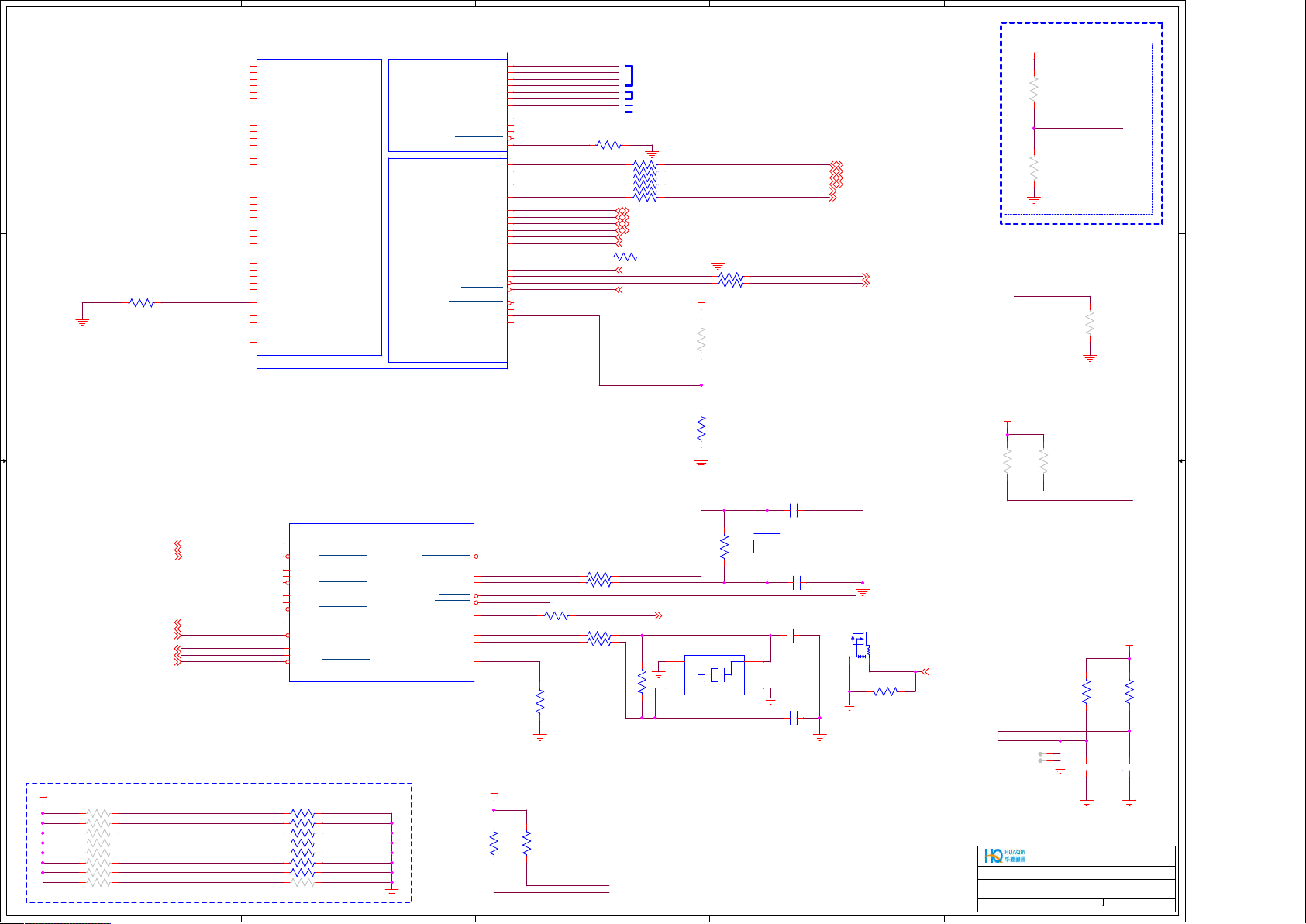

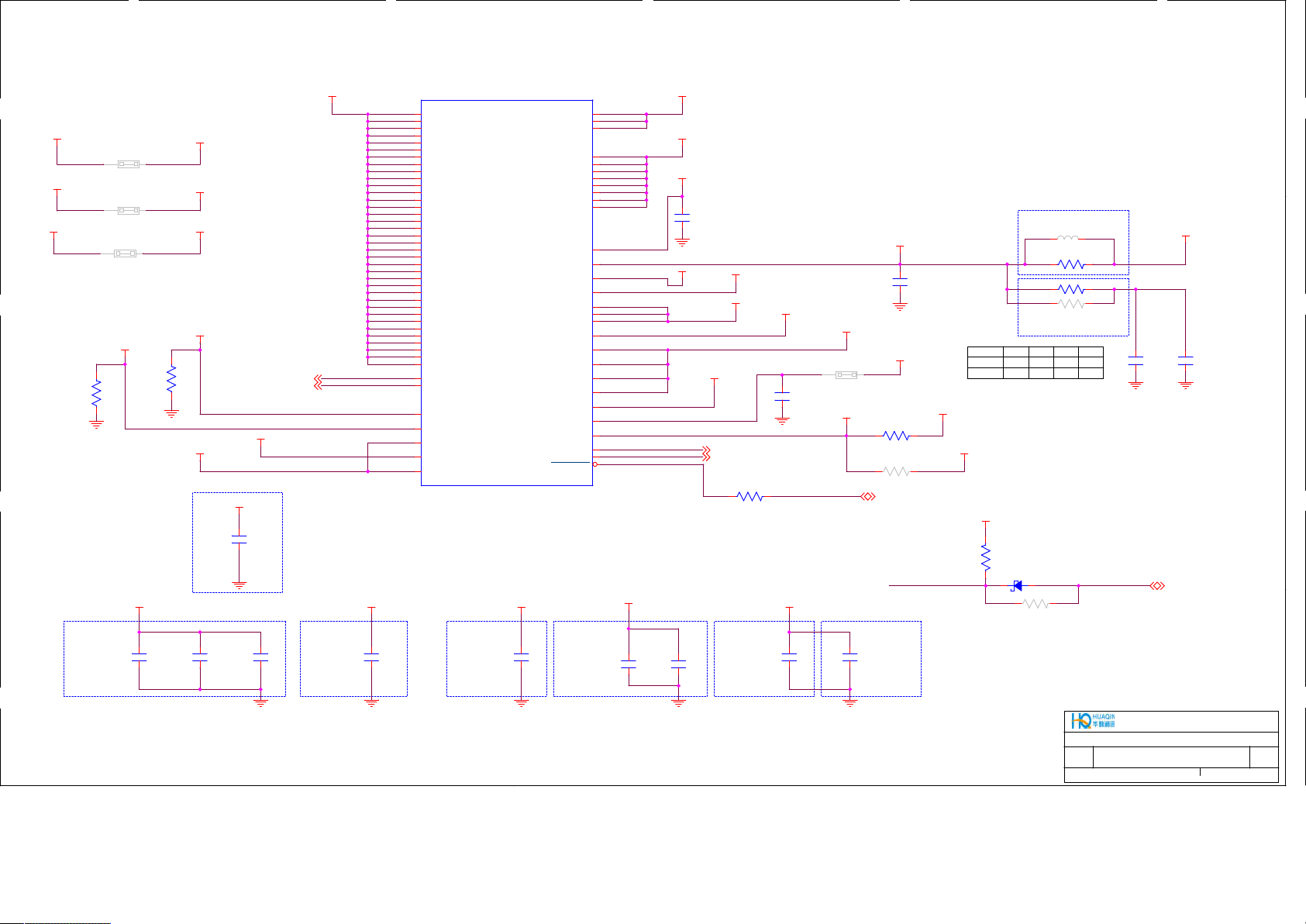

NB8511/12_M/B Schematics Document

C C

Intel ICL Lake U-Processor with LPDDR4

REV1.0

2019-02-01

B B

A A

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Author

Reviewer

Approver

5

4

3

Leo.Liu & Payne.Zhang

Nelosn.Hai & Nemo.Jiang

Lobo_Fan

2

Page name:

Page name:

Page name:

Size:

Project

Size:

Project

Size:

Project

Name:

A4

Name:

A4

Name:

A4

Date: Sheet: of

Date: Sheet: of

Date: Sheet: of

Monday, July 15, 2019 1 72

Monday, July 15, 2019 1 72

Monday, July 15, 2019 1 72

Huaqin Telecom Technology Com.,Ltd.

Cover page

Cover page

Cover page

NB8511

NB8511

NB8511

1

REV:

REV:

REV:

V1.0

V1.0

V1.0

5

D D

C C

4

3

2

1

B B

A A

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Page name:

Page name:

Page name:

Size:

Size:

Size:

A4

A4

A4

Date: Sheet: of

Date: Sheet: of

Date: Sheet: of

5

4

3

2

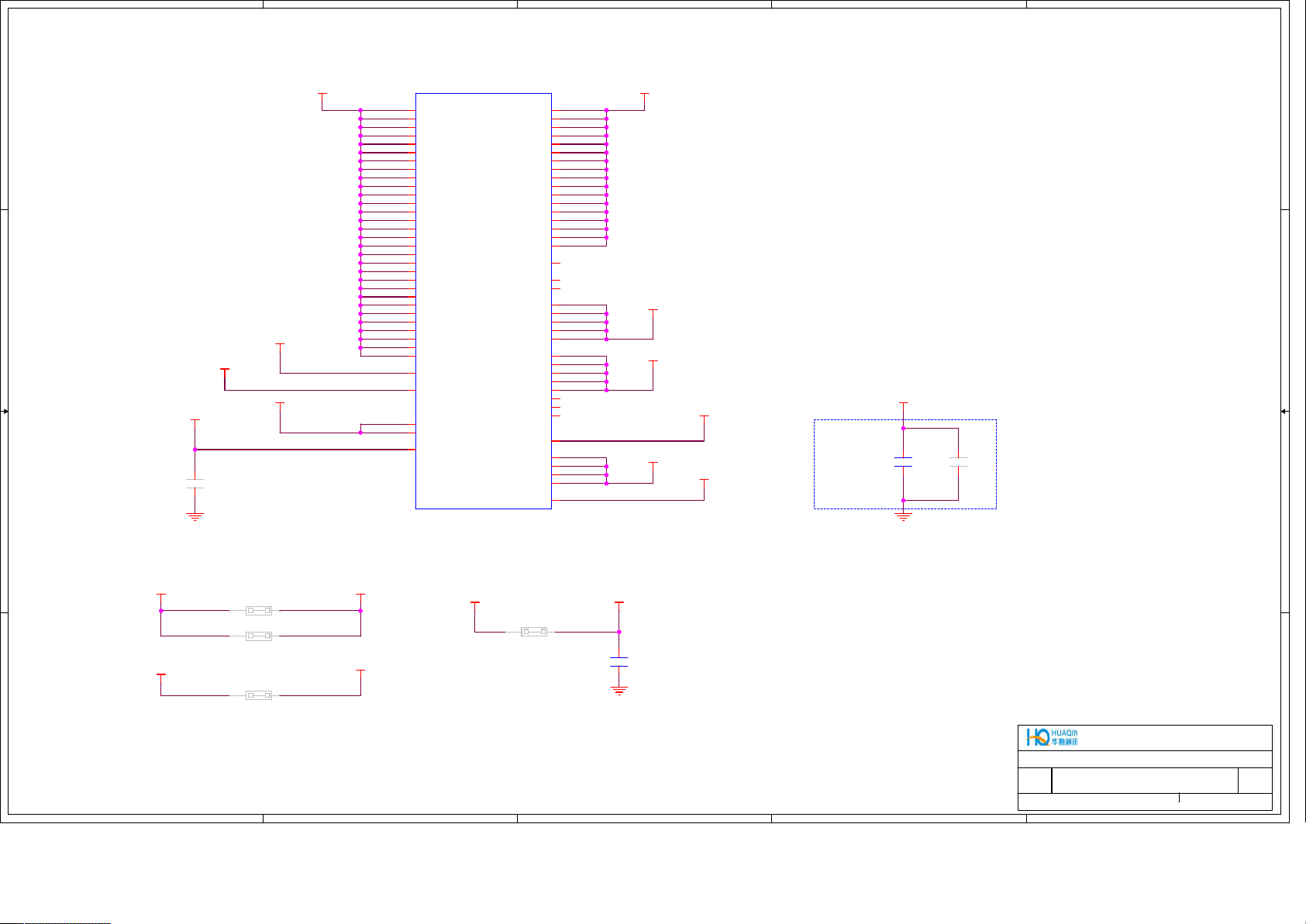

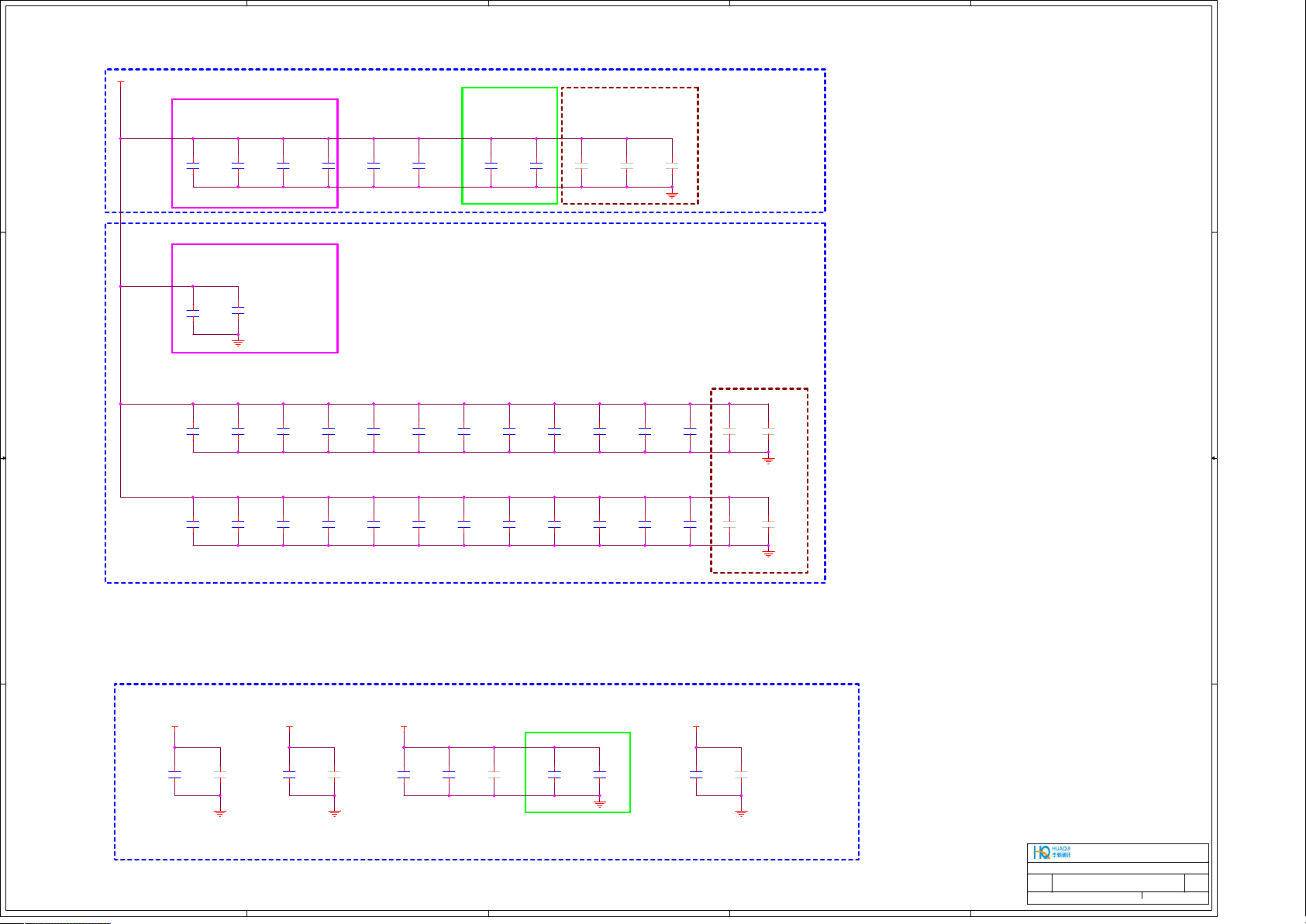

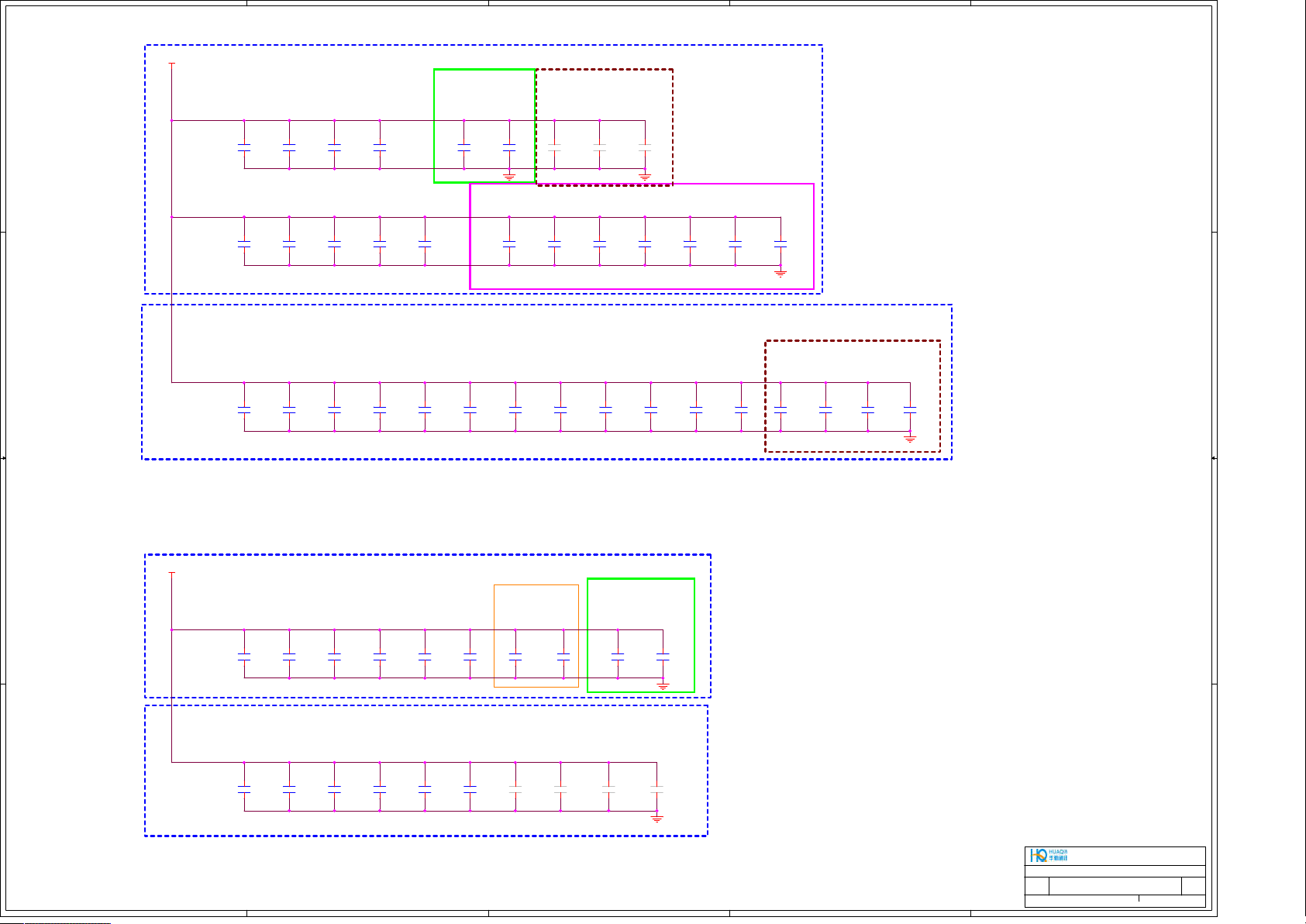

Block Diagram

Block Diagram

Block Diagram

Project

Project

Project

Name:

Name:

Name:

NB8511

NB8511

NB8511

Monday, July 15, 2019 2 72

Monday, July 15, 2019 2 72

Monday, July 15, 2019 2 72

1

REV:

REV:

REV:

V1.0

V1.0

V1.0

D D

5

MEM ID

4

3

2

1

C C

B B

HW_ID3 HW_ID2 HW_ID1

0

0 0 0

0

0 0

0

0 0

1

0

0 1 0 0

1

0 0 0

GPU ID

HW_ID5 HW_ID4

00

1

0

11

KB BL ID

HW_ID6

0 No keyboard Backlignt

1 Keyboard Backlignt

Description

HW_ID0

SAMSUNG LPDDR4 3733 1GB K4F8E304HB-MGCJ LF+HF D20

HYNIX LPDDR4 3733 1GB H9HCNNN8KUMLHR-NME LF+HF DDP

1

MICRON LPDDR4 4266 2GB MT53E512M32D2NP-046 WT:E LF+HF Z11N

HYNIX LPDDR4 3733 2GB H9HCNNNBPUMLHR-NME LF+HF DE

001

HYNIX LPDDR4X 4266 4GB H9HCNNNCPMALHR-NEE LF+HF QDP

4x 16Gb(reserve)

Description

N17-LG-Refresh

NC NC

Mount

N17-LG

Mount

TotalDescription

4GB

4GB

8GB

8GB

16GB

A A

Reserve ID

HW_ID7

0

1

Reserve

Reserve

5

Description

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Page name:

Page name:

Page name:

Size:

Size:

Size:

A4

A4

A4

Date: Sheet: of

Date: Sheet: of

Date: Sheet: of

4

3

2

I2C Table

I2C Table

I2C Table

Project

Project

Project

Name:

Name:

Name:

NB8511

NB8511

NB8511

Monday, July 15, 2019 3 72

Monday, July 15, 2019 3 72

Monday, July 15, 2019 3 72

REV:

REV:

REV:

1

V1.0

V1.0

V1.0

5

D D

C C

4

3

2

1

B B

A A

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Page name:

Page name:

Page name:

Size:

Size:

Size:

A4

A4

A4

Date: Sheet: of

Date: Sheet: of

5

4

3

2

Date: Sheet: of

Huaqin Telecom Technology Com.,Ltd.

Blank

Blank

Blank

Project

Project

Project

Name:

Name:

Name:

NB8511

NB8511

NB8511

Monday, July 15, 2019 4 72

Monday, July 15, 2019 4 72

Monday, July 15, 2019 4 72

1

REV:

REV:

REV:

V1.0

V1.0

V1.0

5

4

3

2

1

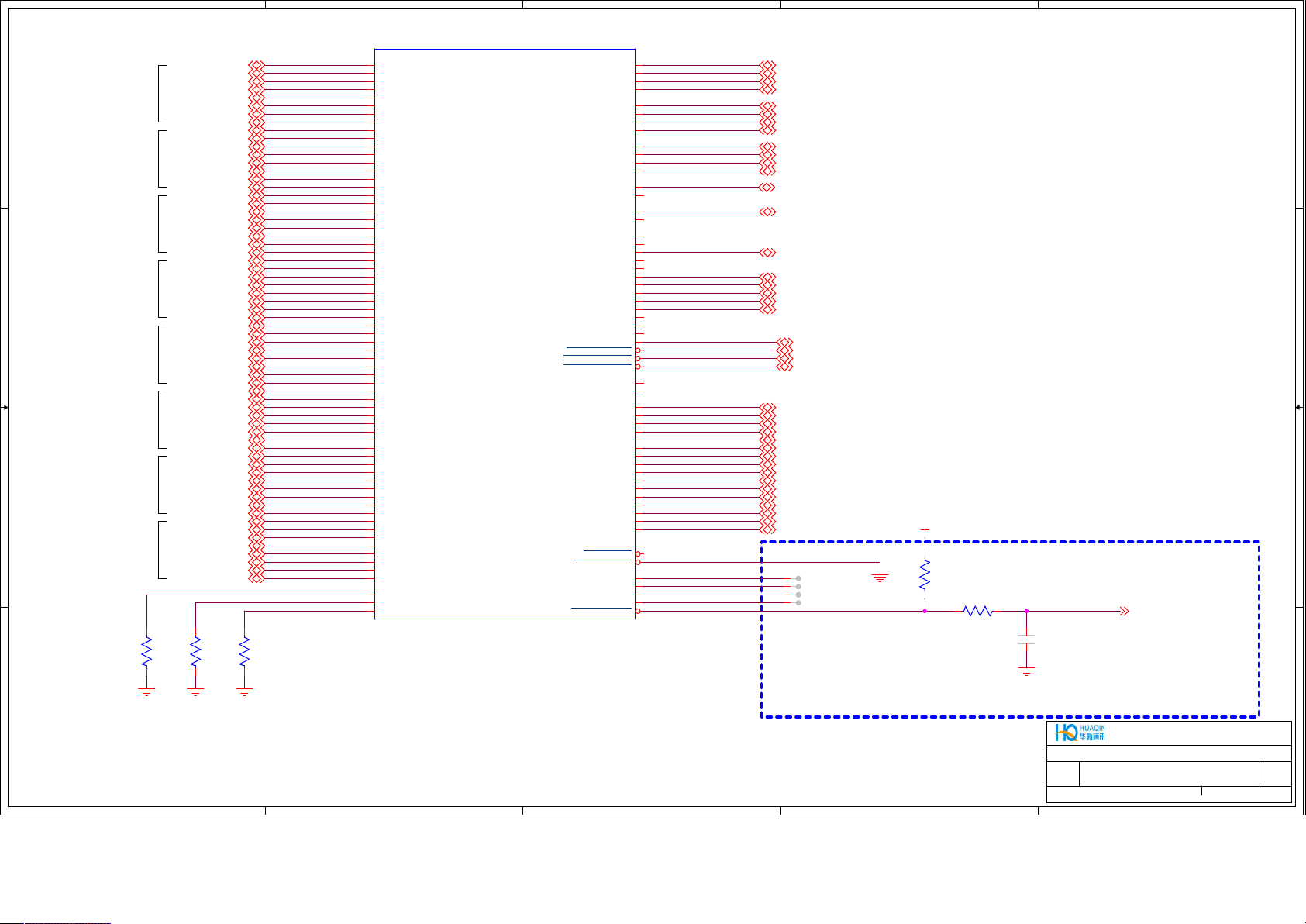

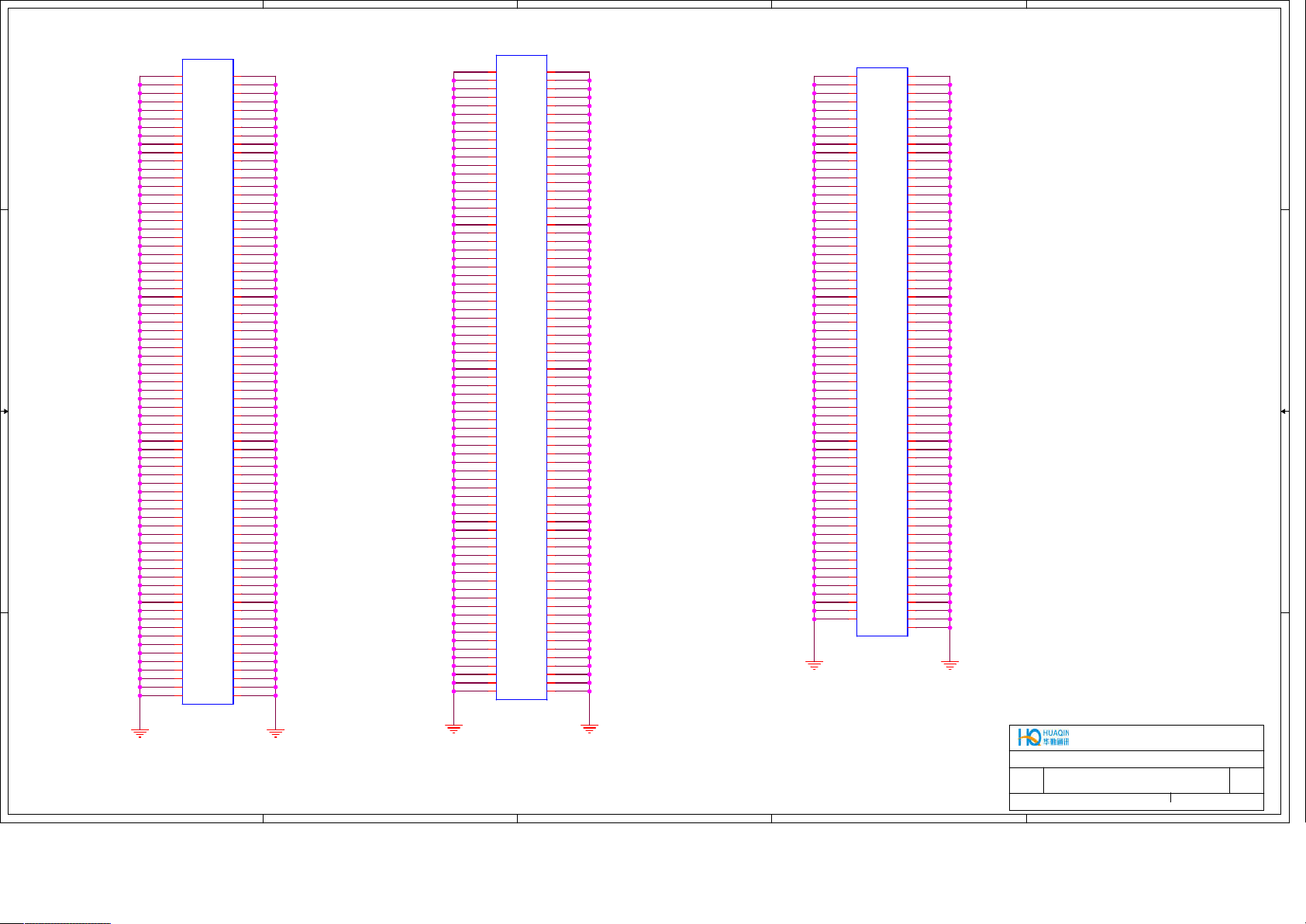

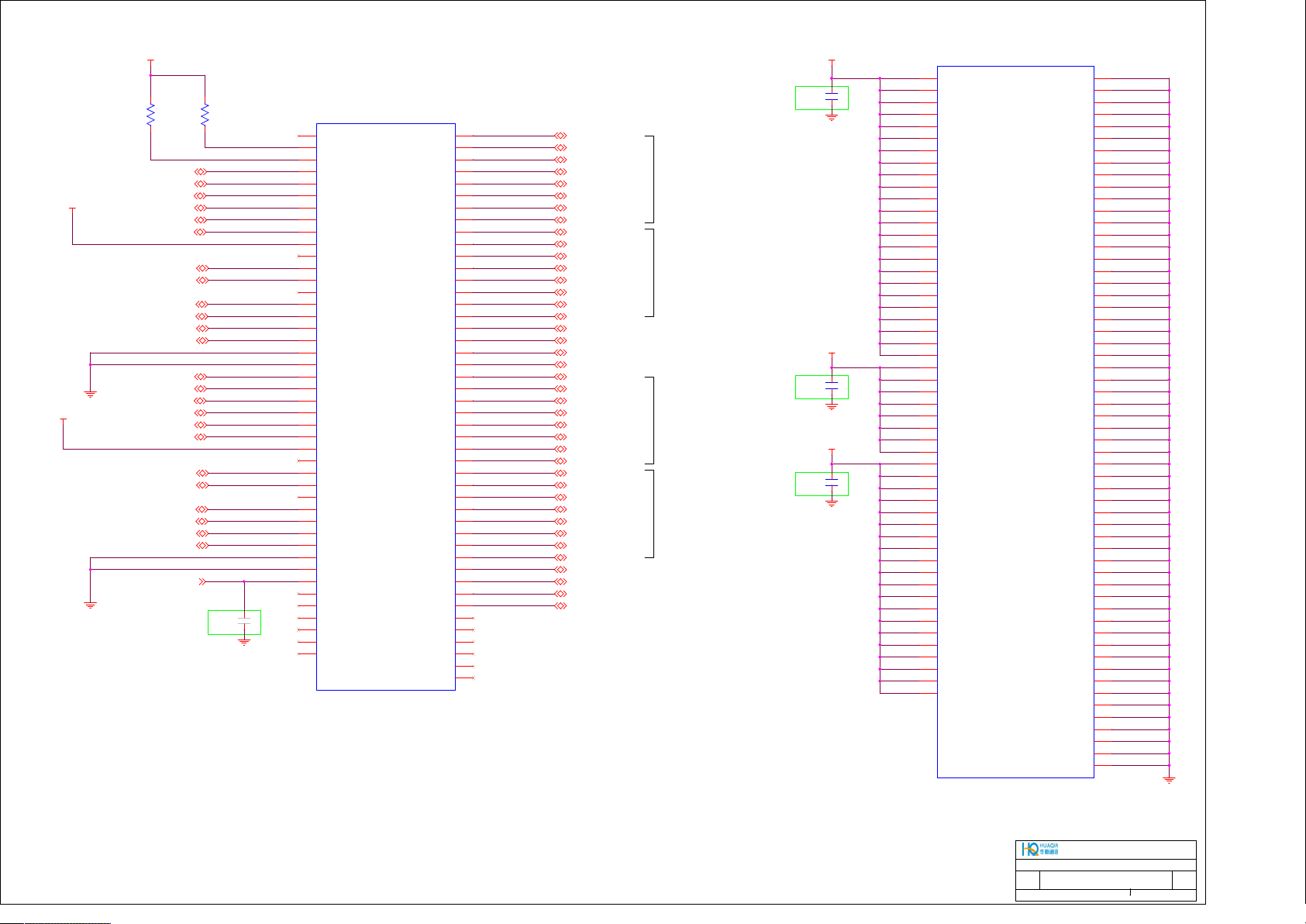

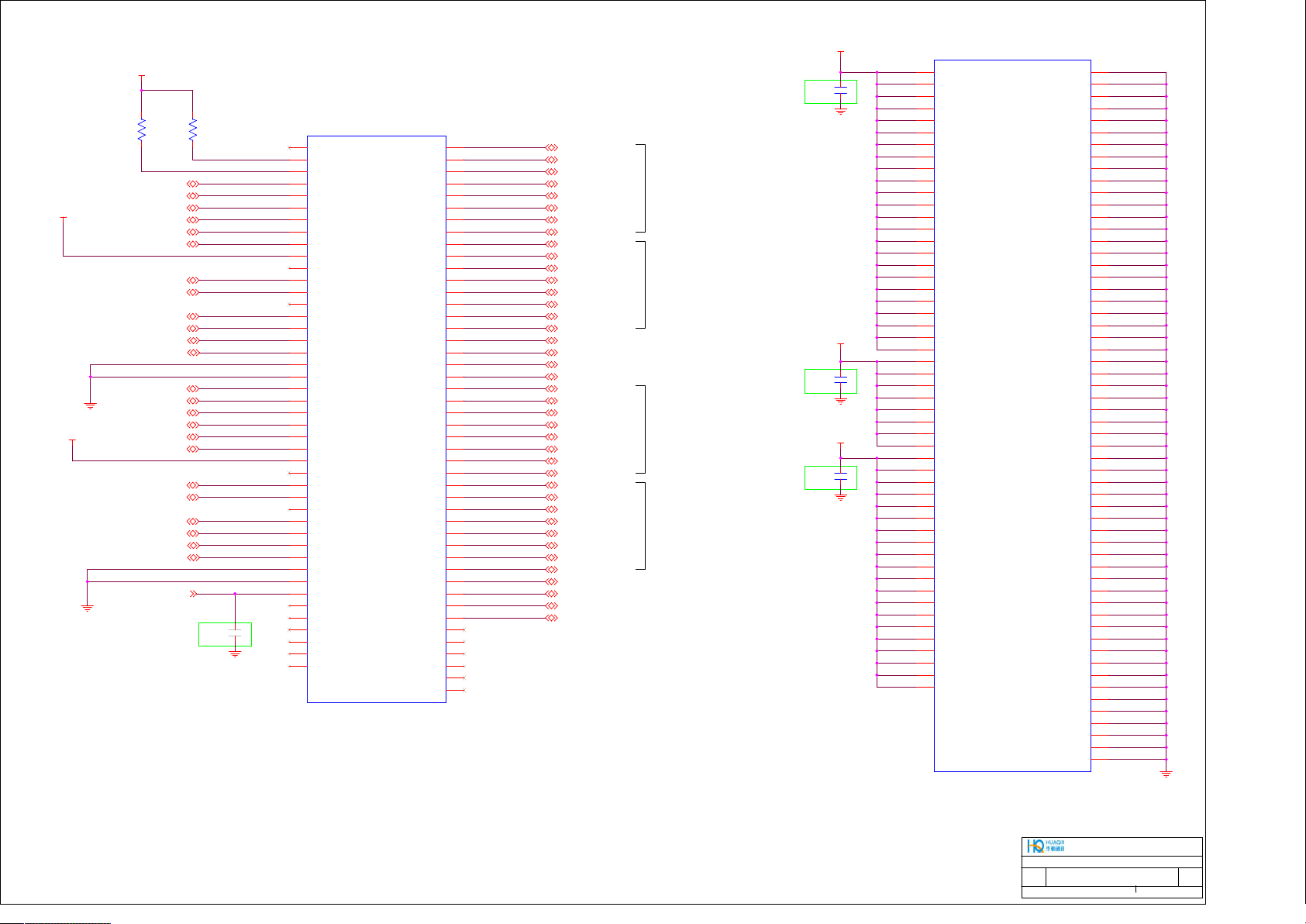

CHA

RU3

M_A_DQ_0[0]

M_A_DQ_0[1]

M_A_DQ_0[2]

M_A_DQ_0[3]

M_A_DQ_0[4]

M_A_DQ_0[5]

M_A_DQ_0[6]

M_A_DQ_0[7]

M_A_DQ_1[0]

M_A_DQ_1[1]

M_A_DQ_1[2]

M_A_DQ_1[3]

M_A_DQ_1[4]

M_A_DQ_1[5]

M_A_DQ_1[6]

M_A_DQ_1[7]

M_A_DQ_2[0]

M_A_DQ_2[1]

M_A_DQ_2[2]

M_A_DQ_2[3]

M_A_DQ_2[4]

M_A_DQ_2[5]

M_A_DQ_2[6]

M_A_DQ_2[7]

M_A_DQ_3[0]

M_A_DQ_3[1]

M_A_DQ_3[2]

M_A_DQ_3[3]

M_A_DQ_3[4]

M_A_DQ_3[5]

M_A_DQ_3[6]

M_A_DQ_3[7]

M_A_DQ_4[0]

M_A_DQ_4[1]

M_A_DQ_4[2]

M_A_DQ_4[3]

M_A_DQ_4[4]

M_A_DQ_4[5]

M_A_DQ_4[6]

M_A_DQ_4[7]

M_A_DQ_5[0]

M_A_DQ_5[1]

M_A_DQ_5[2]

M_A_DQ_5[3]

M_A_DQ_5[4]

M_A_DQ_5[5]

M_A_DQ_5[6]

M_A_DQ_5[7]

M_A_DQ_6[0]

M_A_DQ_6[1]

M_A_DQ_6[2]

M_A_DQ_6[3]

M_A_DQ_6[4]

M_A_DQ_6[5]

M_A_DQ_6[6]

M_A_DQ_6[7]

M_A_DQ_7[0]

M_A_DQ_7[1]

M_A_DQ_7[2]

M_A_DQ_7[3]

M_A_DQ_7[4]

M_A_DQ_7[5]

M_A_DQ_7[6]

M_A_DQ_7[7]

DDR_RCOMP_0

DDR_RCOMP_1

DDR_RCOMP_2

M_A_DQ_0[0]21

M_A_DQ_0[1]21

M_A_DQ_0[2]21

D D

BYTE1

BYTE2

BYTE3

BYTE0

C C

BYTE4

BYTE5

BYTE6

B B

BYTE7

电阻

_100R_0201_1/20W_F

RU1

M_A_DQ_0[3]21

M_A_DQ_0[4]21

M_A_DQ_0[5]21

M_A_DQ_0[6]21

M_A_DQ_0[7]21

M_A_DQ_1[0]21

M_A_DQ_1[1]21

M_A_DQ_1[2]21

M_A_DQ_1[3]21

M_A_DQ_1[4]21

M_A_DQ_1[5]21

M_A_DQ_1[6]21

M_A_DQ_1[7]21

M_A_DQ_2[0]21

M_A_DQ_2[1]21

M_A_DQ_2[2]21

M_A_DQ_2[3]21

M_A_DQ_2[4]21

M_A_DQ_2[5]21

M_A_DQ_2[6]21

M_A_DQ_2[7]21

M_A_DQ_3[0]21

M_A_DQ_3[1]21

M_A_DQ_3[2]21

M_A_DQ_3[3]21

M_A_DQ_3[4]21

M_A_DQ_3[5]21

M_A_DQ_3[6]21

M_A_DQ_3[7]21

M_A_DQ_4[0]22

M_A_DQ_4[1]22

M_A_DQ_4[2]22

M_A_DQ_4[3]22

M_A_DQ_4[4]22

M_A_DQ_4[5]22

M_A_DQ_4[6]22

M_A_DQ_4[7]22

M_A_DQ_5[0]22

M_A_DQ_5[1]22

M_A_DQ_5[2]22

M_A_DQ_5[3]22

M_A_DQ_5[4]22

M_A_DQ_5[5]22

M_A_DQ_5[6]22

M_A_DQ_5[7]22

M_A_DQ_6[0]22

M_A_DQ_6[1]22

M_A_DQ_6[2]22

M_A_DQ_6[3]22

M_A_DQ_6[4]22

M_A_DQ_6[5]22

M_A_DQ_6[6]22

M_A_DQ_6[7]22

M_A_DQ_7[0]22

M_A_DQ_7[1]22

M_A_DQ_7[2]22

M_A_DQ_7[3]22

M_A_DQ_7[4]22

M_A_DQ_7[5]22

M_A_DQ_7[6]22

M_A_DQ_7[7]22

RU2

电阻

_100R_0201_1/20W_F

电阻

_100R_0201_1/20W_F

CA48

DDRA_DQ0_0/DDR0_DQ0_0

CA47

DDRA_DQ0_1/DDR0_DQ0_1

CA49

DDRA_DQ0_2/DDR0_DQ0_2

BV49

DDRA_DQ0_3/DDR0_DQ0_3

CA45

DDRA_DQ0_4/DDR0_DQ0_4

BV47

DDRA_DQ0_5/DDR0_DQ0_5

BV45

DDRA_DQ0_6/DDR0_DQ0_6

BV48

DDRA_DQ0_7/DDR0_DQ0_7

CC42

DDRA_DQ1_0/DDR0_DQ1_0

CC39

DDRA_DQ1_1/DDR0_DQ1_1

CC43

DDRA_DQ1_2/DDR0_DQ1_2

CE38

DDRA_DQ1_3/DDR0_DQ1_3

CC38

DDRA_DQ1_4/DDR0_DQ1_4

CE39

DDRA_DQ1_5/DDR0_DQ1_5

CE42

DDRA_DQ1_6/DDR0_DQ1_6

CE43

DDRA_DQ1_7/DDR0_DQ1_7

BT48

DDRA_DQ2_0/DDR0_DQ2_0

BT47

DDRA_DQ2_1/DDR0_DQ2_1

BT49

DDRA_DQ2_2/DDR0_DQ2_2

BN49

DDRA_DQ2_3/DDR0_DQ2_3

BT45

DDRA_DQ2_4/DDR0_DQ2_4

BN47

DDRA_DQ2_5/DDR0_DQ2_5

BN45

DDRA_DQ2_6/DDR0_DQ2_6

BN48

DDRA_DQ2_7/DDR0_DQ2_7

BV42

DDRA_DQ3_0/DDR0_DQ3_0

BV39

DDRA_DQ3_1/DDR0_DQ3_1

BV43

DDRA_DQ3_2/DDR0_DQ3_2

BW38

DDRA_DQ3_3/DDR0_DQ3_3

BV38

DDRA_DQ3_4/DDR0_DQ3_4

BW39

DDRA_DQ3_5/DDR0_DQ3_5

BW42

DDRA_DQ3_6/DDR0_DQ3_6

BW43

DDRA_DQ3_7/DDR0_DQ3_7

AY48

DDRB_DQ0_0/DDR0_DQ4_0

AY47

DDRB_DQ0_1/DDR0_DQ4_1

AY49

DDRB_DQ0_2/DDR0_DQ4_2

AU45

DDRB_DQ0_3/DDR0_DQ4_3

AY45

DDRB_DQ0_4/DDR0_DQ4_4

AU47

DDRB_DQ0_5/DDR0_DQ4_5

AU48

DDRB_DQ0_6/DDR0_DQ4_6

AU49

DDRB_DQ0_7/DDR0_DQ4_7

AY42

DDRB_DQ1_0/DDR0_DQ5_0

AY38

DDRB_DQ1_1/DDR0_DQ5_1

AY43

DDRB_DQ1_2/DDR0_DQ5_2

BB39

DDRB_DQ1_3/DDR0_DQ5_3

AY39

DDRB_DQ1_4/DDR0_DQ5_4

BB38

DDRB_DQ1_5/DDR0_DQ5_5

BB42

DDRB_DQ1_6/DDR0_DQ5_6

BB43

DDRB_DQ1_7/DDR0_DQ5_7

AR48

DDRB_DQ2_0/DDR0_DQ6_0

AR47

DDRB_DQ2_1/DDR0_DQ6_1

AR49

DDRB_DQ2_2/DDR0_DQ6_2

AM45

DDRB_DQ2_3/DDR0_DQ6_3

AR45

DDRB_DQ2_4/DDR0_DQ6_4

AM47

DDRB_DQ2_5/DDR0_DQ6_5

AM48

DDRB_DQ2_6/DDR0_DQ6_6

AM49

DDRB_DQ2_7/DDR0_DQ6_7

AT42

DDRB_DQ3_0/DDR0_DQ7_0

AT39

DDRB_DQ3_1/DDR0_DQ7_1

AR43

DDRB_DQ3_2/DDR0_DQ7_2

AT38

DDRB_DQ3_3/DDR0_DQ7_3

AR38

DDRB_DQ3_4/DDR0_DQ7_4

AR39

DDRB_DQ3_5/DDR0_DQ7_5

AR42

DDRB_DQ3_6/DDR0_DQ7_6

AT43

DDRB_DQ3_7/DDR0_DQ7_7

D47

DDR_RCOMP_0

E46

DDR_RCOMP_1

C47

DDR_RCOMP_2

ICL_U_IP_EXT_WW20

DDRA_CLK_N/DDR0_CLK_N_0

DDRA_CLK_P/DDR0_CLK_P_0

DDRB_CLK_N/DDR0_CLK_N_1

DDRB_CLK_P/DDR0_CLK_P_1

DDRA_CKE0/DDR0_CKE0

DDRB_CKE1/DDR0_CKE1

DDRA_CS_0/DDR0_CS_N_0

DDRB_CS_1/DDR0_CS_N_1

DDRB_CA2/DDR0_MA14WE_N

DDRB_CA1/DDR0_MA15CAS_N

DDRB_CA3/DDR0_MA16RAS_N

DDRA_DQSN_0/DDR0_DQSN_0

DDRA_DQSP_0/DDR0_DQSP_0

DDRA_DQSN_1/DDR0_DQSN_1

DDRA_DQSP_1/DDR0_DQSP_1

DDRA_DQSN_2/DDR0_DQSN_2

DDRA_DQSP_2/DDR0_DQSP_2

DDRA_DQSN_3/DDR0_DQSN_3

DDRA_DQSP_3/DDR0_DQSP_3

DDRB_DQSN_0/DDR0_DQSN_4

DDRB_DQSP_0/DDR0_DQSP_4

DDRB_DQSN_1/DDR0_DQSN_5

DDRB_DQSP_1/DDR0_DQSP_5

DDRB_DQSN_2/DDR0_DQSN_6

DDRB_DQSP_2/DDR0_DQSP_6

DDRB_DQSN_3/DDR0_DQSN_7

DDRB_DQSP_3/DDR0_DQSP_7

2 of 19

DDRA_CKE1/NC

DDRB_CKE0/NC

DDRA_CS_1/NC

DDRB_CS_0/NC

DDRB_CA4/DDR0_BA0

DDRA_CA5/DDR0_BG0

NC/DDR0_BG1

NC/DDR0_MA0

NC/DDR0_MA1

DDRB_CA5/DDR0_MA2

NC/DDR0_MA3

NC/DDR0_MA4

DDRA_CA0/DDR0_MA5

DDRA_CA2/DDR0_MA6

DDRA_CA4/DDR0_MA7

DDRA_CA3/DDR0_MA8

DDRA_CA1/DDR0_MA9

NC/DDR0_MA10

NC/DDR0_MA11

NC/DDR0_MA12

DDRB_CA0/DDR0_MA13

NC/DDR0_ODT_0

NC/DDR0_ODT_1

NC/DDR0_PAR

NC/DDR0_ACT_N

NC/DDR0_ALERT_N

DDR0_VREF_CA

DDR1_VREF_CA

DDR_VTT_CTL

DRAM_RESET_N

NC/DDR0_BA1

RSVD_73

????UU1B

BL48

BL47

BF42

BF43

BG49

BJ47

BF38

BF41

BM38

BM42

BP42

BG42

BM43

BG39

BB49

BD47

BB48

BL49

BG38

BL45

BJ46

BG48

BE45

BG45

BG47

BE47

BJ38

BB47

BE48

BM39

BG43

BJ42

BM41

BJ39

BB45

BY47

BY46

CC41

CE41

BR47

BR46

BV41

BW41

AV46

AV47

AY41

BB41

AN46

AN47

AR41

AT41

BF39

BE49

BD46

M38

C44

B45

M39

DK47

M_A_CK_DDR0_DN

M_A_CK_DDR0_DP

M_A_CK_DDR1_DN

M_A_CK_DDR1_DP

M_A_LP4_CKE_A0

M_A_LP4_CKE_A1

M_A_LP4_CKE_B0

M_A_LP4_CKE_B1

M_A_LP4_CS_A_R0_N

M_A_LP4_CS_A_R1_N

M_A_LP4_CS_B_R0_N

M_A_LP4_CS_B_R1_N

M_A_LP4_CAB4

M_A_LP4_CAA5

M_A_LP4_CAB5

M_A_LP4_CAA0

M_A_LP4_CAA2

M_A_LP4_CAA4

M_A_LP4_CAA3

M_A_LP4_CAA1

M_A_LP4_CAB0

M_A_LP4_CAB2

M_A_LP4_CAB1

M_A_LP4_CAB3

M_A_DQS_0_DN

M_A_DQS_0_DP

M_A_DQS_1_DN

M_A_DQS_1_DP

M_A_DQS_2_DN

M_A_DQS_2_DP

M_A_DQS_3_DN

M_A_DQS_3_DP

M_A_DQS_4_DN

M_A_DQS_4_DP

M_A_DQS_5_DN

M_A_DQS_5_DP

M_A_DQS_6_DN

M_A_DQS_6_DP

M_A_DQS_7_DN

M_A_DQS_7_DP

TP_+V_D4CH1_CA_VREF

TP_+V_D4CH0_CA_VREF

TP_+V_LPCH0_DQ_VREF

TP_DDR_VTT_CTRL

M_A_CK_DDR0_DN 21

M_A_CK_DDR0_DP 21

M_A_CK_DDR1_DN 22

M_A_CK_DDR1_DP 22

M_A_LP4_CKE_A0 21

M_A_LP4_CKE_A1 21

M_A_LP4_CKE_B0 22

M_A_LP4_CKE_B1 22

M_A_LP4_CS_A_R0_N 21

M_A_LP4_CS_A_R1_N 21

M_A_LP4_CS_B_R0_N 22

M_A_LP4_CS_B_R1_N 22

M_A_LP4_CAB4 22

M_A_LP4_CAA5 21

M_A_LP4_CAB5 22

M_A_LP4_CAA0 21

M_A_LP4_CAA2 21

M_A_LP4_CAA4 21

M_A_LP4_CAA3 21

M_A_LP4_CAA1 21

M_A_LP4_CAB0 22

M_A_LP4_CAB2 22

M_A_LP4_CAB1 22

M_A_LP4_CAB3 22

M_A_DQS_0_DN 21

M_A_DQS_0_DP 21

M_A_DQS_1_DN 21

M_A_DQS_1_DP 21

M_A_DQS_2_DN 21

M_A_DQS_2_DP 21

M_A_DQS_3_DN 21

M_A_DQS_3_DP 21

M_A_DQS_4_DN 22

M_A_DQS_4_DP 22

M_A_DQS_5_DN 22

M_A_DQS_5_DP 22

M_A_DQS_6_DN 22

M_A_DQS_6_DP 22

M_A_DQS_7_DN 22

M_A_DQS_7_DP 22

1

TPU1 20MIL

ns

1

TPU2 20MIL

ns

1

TPU3 20MIL

ns

1

TPU4 20MIL

ns

+VDDQ_CPU

RD1

电阻

_470R_0201_1/20W_J

RD2

电阻

DRAM_RESET_N_RDRAM_RESET_N

_0R_0201_1/20W_J

CD1

ns

电容

_100nF_0201_X5R_6.3 V_M(±20%)

DRAM_RESET_N_R 21,22,23,24

A A

PLACE RESET COMPONENTS CLOSE TO CPU

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Page name:

Page name:

Page name:

Size:

Size:

Size:

A4

A4

A4

Date: Sheet: of

Date: Sheet: of

Date: Sheet: of

5

4

3

2

ICL-U42(CHA)

ICL-U42(CHA)

ICL-U42(CHA)

Project

Project

Project

Name:

Name:

Name:

NB8511

NB8511

NB8511

Monday, July 15, 2019 5 72

Monday, July 15, 2019 5 72

Monday, July 15, 2019 5 72

1

REV:

REV:

REV:

V1.0

V1.0

V1.0

5

4

3

2

1

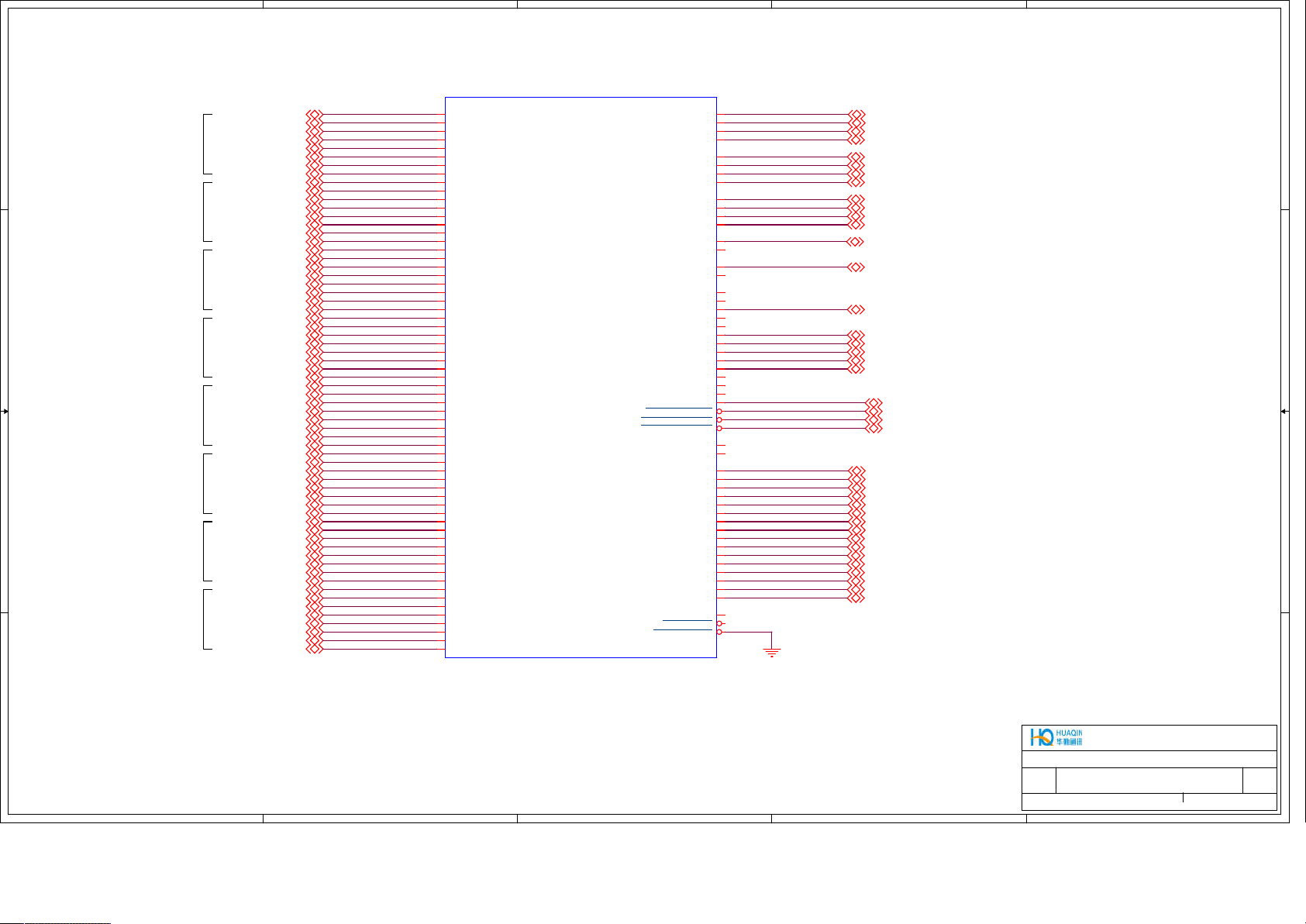

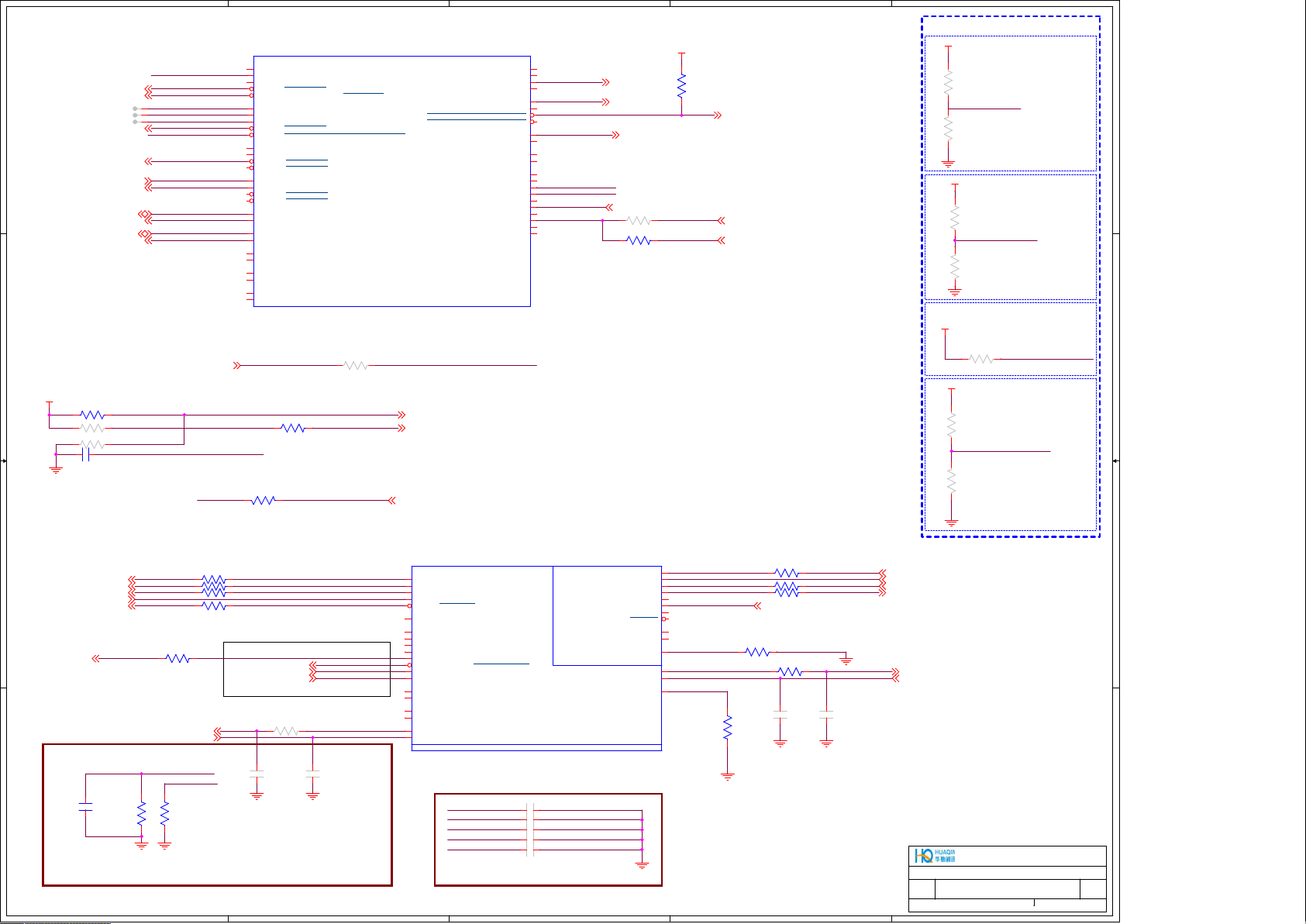

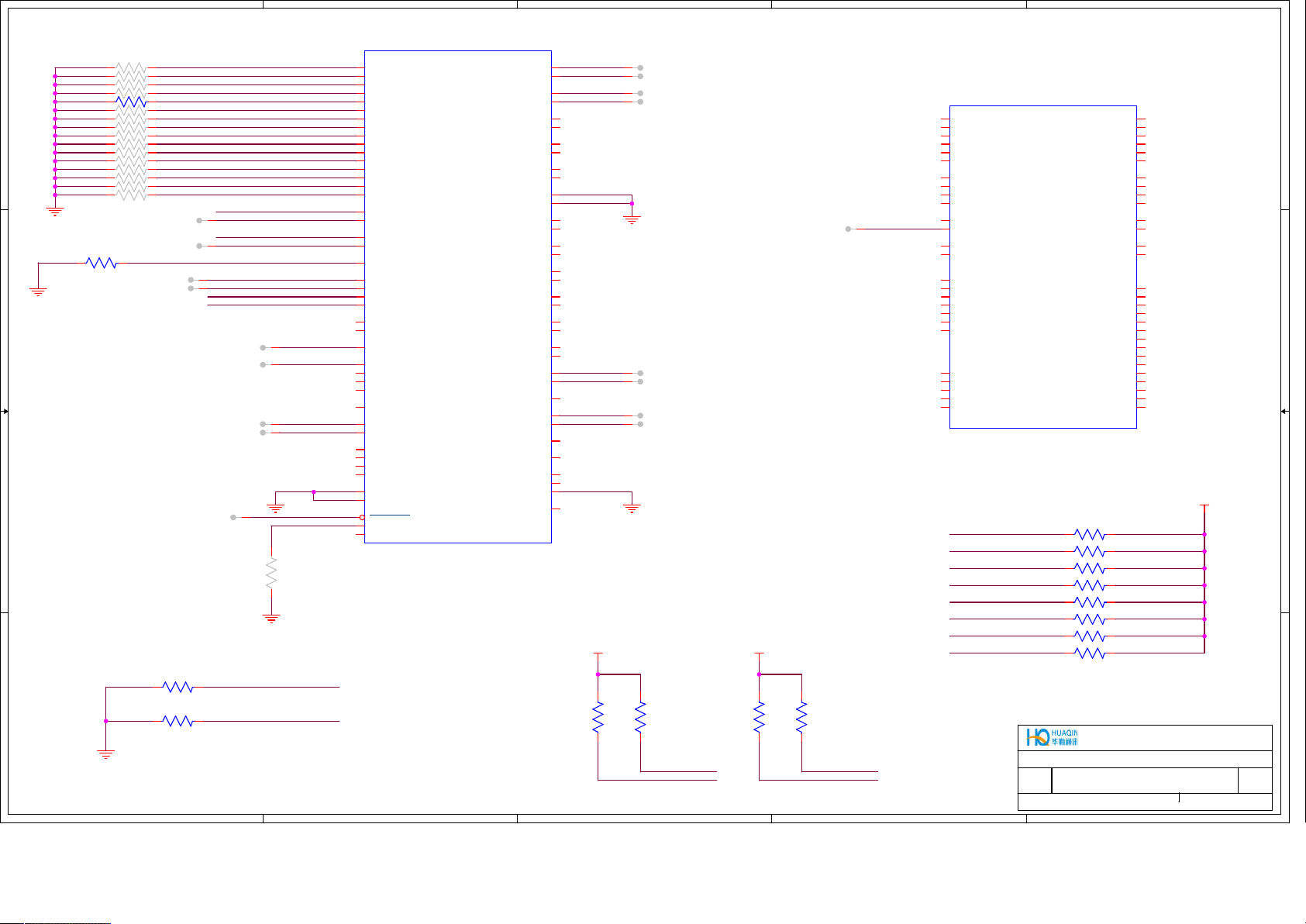

CHB

????UU1C

D D

BYTE0

BYTE1

BYTE2

C C

BYTE3

BYTE4

BYTE5

B B

BYTE6

BYTE7

M_B_DQ_0[1]23

M_B_DQ_0[2]23

M_B_DQ_0[3]23

M_B_DQ_0[4]23

M_B_DQ_0[5]23

M_B_DQ_0[6]23

M_B_DQ_0[7]23

M_B_DQ_1[0]23

M_B_DQ_1[1]23

M_B_DQ_1[2]23

M_B_DQ_1[3]23

M_B_DQ_1[4]23

M_B_DQ_1[5]23

M_B_DQ_1[6]23

M_B_DQ_1[7]23

M_B_DQ_2[0]23

M_B_DQ_2[1]23

M_B_DQ_2[2]23

M_B_DQ_2[3]23

M_B_DQ_2[4]23

M_B_DQ_2[5]23

M_B_DQ_2[6]23

M_B_DQ_2[7]23

M_B_DQ_3[0]23

M_B_DQ_3[1]23

M_B_DQ_3[2]23

M_B_DQ_3[3]23

M_B_DQ_3[4]23

M_B_DQ_3[5]23

M_B_DQ_3[6]23

M_B_DQ_3[7]23

M_B_DQ_4[0]24

M_B_DQ_4[1]24

M_B_DQ_4[2]24

M_B_DQ_4[3]24

M_B_DQ_4[4]24

M_B_DQ_4[5]24

M_B_DQ_4[6]24

M_B_DQ_4[7]24

M_B_DQ_5[0]24

M_B_DQ_5[1]24

M_B_DQ_5[2]24

M_B_DQ_5[3]24

M_B_DQ_5[4]24

M_B_DQ_5[5]24

M_B_DQ_5[6]24

M_B_DQ_5[7]24

M_B_DQ_6[0]24

M_B_DQ_6[1]24

M_B_DQ_6[2]24

M_B_DQ_6[3]24

M_B_DQ_6[4]24

M_B_DQ_6[5]24

M_B_DQ_6[6]24

M_B_DQ_6[7]24

M_B_DQ_7[0]24

M_B_DQ_7[1]24

M_B_DQ_7[2]24

M_B_DQ_7[3]24

M_B_DQ_7[4]24

M_B_DQ_7[5]24

M_B_DQ_7[6]24

M_B_DQ_7[7]24

M_B_DQ_0[0]

M_B_DQ_0[1]

M_B_DQ_0[2]

M_B_DQ_0[3]

M_B_DQ_0[4]

M_B_DQ_0[5]

M_B_DQ_0[6]

M_B_DQ_0[7]

M_B_DQ_1[0]

M_B_DQ_1[1]

M_B_DQ_1[2]

M_B_DQ_1[3]

M_B_DQ_1[4]

M_B_DQ_1[5]

M_B_DQ_1[6]

M_B_DQ_1[7]

M_B_DQ_2[0]

M_B_DQ_2[1]

M_B_DQ_2[2]

M_B_DQ_2[3]

M_B_DQ_2[4]

M_B_DQ_2[5]

M_B_DQ_2[6]

M_B_DQ_2[7]

M_B_DQ_3[0]

M_B_DQ_3[1]

M_B_DQ_3[2]

M_B_DQ_3[3]

M_B_DQ_3[4]

M_B_DQ_3[5]

M_B_DQ_3[6]

M_B_DQ_3[7]

M_B_DQ_4[0]

M_B_DQ_4[1]

M_B_DQ_4[2]

M_B_DQ_4[3]

M_B_DQ_4[4]

M_B_DQ_4[5]

M_B_DQ_4[6]

M_B_DQ_4[7]

M_B_DQ_5[0]

M_B_DQ_5[1]

M_B_DQ_5[2]

M_B_DQ_5[3]

M_B_DQ_5[4]

M_B_DQ_5[5]

M_B_DQ_5[6]

M_B_DQ_5[7]

M_B_DQ_6[0]

M_B_DQ_6[1]

M_B_DQ_6[2]

M_B_DQ_6[3]

M_B_DQ_6[4]

M_B_DQ_6[5]

M_B_DQ_6[6]

M_B_DQ_6[7]

M_B_DQ_7[0]

M_B_DQ_7[1]

M_B_DQ_7[2]

M_B_DQ_7[3]

M_B_DQ_7[4]

M_B_DQ_7[5]

M_B_DQ_7[6]

M_B_DQ_7[7]

AK48

DDRC_DQ0_0/DDR1_DQ0_0

AK45

DDRC_DQ0_1/DDR1_DQ0_1

AK49

DDRC_DQ0_2/DDR1_DQ0_2

AG47

DDRC_DQ0_3/DDR1_DQ0_3

AK47

DDRC_DQ0_4/DDR1_DQ0_4

AG45

DDRC_DQ0_5/DDR1_DQ0_5

AG48

DDRC_DQ0_6/DDR1_DQ0_6

AG49

DDRC_DQ0_7/DDR1_DQ0_7

AJ38

DDRC_DQ1_0/DDR1_DQ1_0

AL39

DDRC_DQ1_1/DDR1_DQ1_1

AJ39

DDRC_DQ1_2/DDR1_DQ1_2

AL43

DDRC_DQ1_3/DDR1_DQ1_3

AL38

DDRC_DQ1_4/DDR1_DQ1_4

AJ42

DDRC_DQ1_5/DDR1_DQ1_5

AL42

DDRC_DQ1_6/DDR1_DQ1_6

AJ43

DDRC_DQ1_7/DDR1_DQ1_7

AB49

DDRC_DQ2_0/DDR1_DQ2_0

AB48

DDRC_DQ2_1/DDR1_DQ2_1

AE49

DDRC_DQ2_2/DDR1_DQ2_2

AE47

DDRC_DQ2_3/DDR1_DQ2_3

AE48

DDRC_DQ2_4/DDR1_DQ2_4

AB47

DDRC_DQ2_5/DDR1_DQ2_5

AB45

DDRC_DQ2_6/DDR1_DQ2_6

AE45

DDRC_DQ2_7/DDR1_DQ2_7

AD38

DDRC_DQ3_0/DDR1_DQ3_0

AD39

DDRC_DQ3_1/DDR1_DQ3_1

AE39

DDRC_DQ3_2/DDR1_DQ3_2

AE43

DDRC_DQ3_3/DDR1_DQ3_3

AE38

DDRC_DQ3_4/DDR1_DQ3_4

AD43

DDRC_DQ3_5/DDR1_DQ3_5

AD42

DDRC_DQ3_6/DDR1_DQ3_6

AE42

DDRC_DQ3_7/DDR1_DQ3_7

J48

DDRD_DQ0_0/DDR1_DQ4_0

J45

DDRD_DQ0_1/DDR1_DQ4_1

J49

DDRD_DQ0_2/DDR1_DQ4_2

G47

DDRD_DQ0_3/DDR1_DQ4_3

J47

DDRD_DQ0_4/DDR1_DQ4_4

G45

DDRD_DQ0_5/DDR1_DQ4_5

G48

DDRD_DQ0_6/DDR1_DQ4_6

E48

DDRD_DQ0_7/DDR1_DQ4_7

J38

DDRD_DQ1_0/DDR1_DQ5_0

G39

DDRD_DQ1_1/DDR1_DQ5_1

G38

DDRD_DQ1_2/DDR1_DQ5_2

G42

DDRD_DQ1_3/DDR1_DQ5_3

J39

DDRD_DQ1_4/DDR1_DQ5_4

J42

DDRD_DQ1_5/DDR1_DQ5_5

G43

DDRD_DQ1_6/DDR1_DQ5_6

J43

DDRD_DQ1_7/DDR1_DQ5_7

B43

DDRD_DQ2_0/DDR1_DQ6_0

D43

DDRD_DQ2_1/DDR1_DQ6_1

A43

DDRD_DQ2_2/DDR1_DQ6_2

C40

DDRD_DQ2_3/DDR1_DQ6_3

C43

DDRD_DQ2_4/DDR1_DQ6_4

D40

DDRD_DQ2_5/DDR1_DQ6_5

B40

DDRD_DQ2_6/DDR1_DQ6_6

A40

DDRD_DQ2_7/DDR1_DQ6_7

B35

DDRD_DQ3_0/DDR1_DQ7_0

D35

DDRD_DQ3_1/DDR1_DQ7_1

A35

DDRD_DQ3_2/DDR1_DQ7_2

D38

DDRD_DQ3_3/DDR1_DQ7_3

C35

DDRD_DQ3_4/DDR1_DQ7_4

C38

DDRD_DQ3_5/DDR1_DQ7_5

B38

DDRD_DQ3_6/DDR1_DQ7_6

A38

DDRD_DQ3_7/DDR1_DQ7_7

ICL_U_IP_EXT_WW20

DDRC_CLK_N/DDR1_CLK_N_0

DDRC_CLK_P/DDR1_CLK_P_0

DDRD_CLK_N/DDR1_CLK_N_1

DDRD_CLK_P/DDR1_CLK_P_1

DDRD_CA2/DDR1_MA14WE_N

DDRD_CA1/DDR1_MA15CAS_N

DDRD_CA3/DDR1_MA16RAS_N

DDRC_DQSN_0/DDR1_DQSN_0

DDRC_DQSP_0/DDR1_DQSP_0

DDRC_DQSN_1/DDR1_DQSN_1

DDRC_DQSP_1/DDR1_DQSP_1

DDRC_DQSN_2/DDR1_DQSN_2

DDRC_DQSP_2/DDR1_DQSP_2

DDRC_DQSN_3/DDR1_DQSN_3

DDRC_DQSP_3/DDR1_DQSP_3

DDRD_DQSN_0/DDR1_DQSN_4

DDRD_DQSP_0/DDR1_DQSP_4

DDRD_DQSN_1/DDR1_DQSN_5

DDRD_DQSP_1/DDR1_DQSP_5

DDRD_DQSN_2/DDR1_DQSN_6

DDRD_DQSP_2/DDR1_DQSP_6

DDRD_DQSN_3/DDR1_DQSN_7

DDRD_DQSP_3/DDR1_DQSP_7

3 of 19

DDRC_CKE0/DDR1_CKE0

DDRC_CKE1/NC

DDRD_CKE0/NC

DDRD_CKE1/DDR1_CKE1

DDRC_CS_0/DDR1_CS_N_0

DDRC_CS_1/NC

DDRD_CS_0/NC

DDRD_CS_1/DDR1_CS_N_1

DDRD_CA4/DDR1_BA0

NC/DDR1_BA1

DDRC_CA5/DDR1_BG0

NC/DDR1_BG1

NC/DDR1_MA0

NC/DDR1_MA1

DDRD_CA5/DDR1_MA2

NC/DDR1_MA3

NC/DDR1_MA4

DDRC_CA0/DDR1_MA5

DDRC_CA2/DDR1_MA6

DDRC_CA4/DDR1_MA7

DDRC_CA3/DDR1_MA8

DDRC_CA1/DDR1_MA9

NC/DDR1_MA10

NC/DDR1_MA11

NC/DDR1_MA12

DDRD_CA0/DDR1_MA13

NC/DDR1_ODT_0

NC/DDR1_ODT_1

NC/DDR1_PAR

NC/DDR1_ACT_N

NC/DDR1_ALERT_N

M_B_CK_DDR0_DN

Y48

M_B_CK_DDR0_DP

Y47

M_B_CK_DDR1_DN

M43

M_B_CK_DDR1_DP

M42

M_B_LP4_CKE_A0

U45

M_B_LP4_CKE_A1

V46

M_B_LP4_CKE_B0

M41

M_B_LP4_CKE_B1

P43

M_B_LP4_CS_A_R0_N

V42

M_B_LP4_CS_A_R1_N

V39

M_B_LP4_CS_B_R0_N

Y39

M_B_LP4_CS_B_R1_N

T39

M_B_LP4_CAB4

T38

T42

M_B_LP4_CAA5

R45

N47

P42

Y49

M_B_LP4_CAB5

U48

Y45

U47

M_B_LP4_CAA0

R49

M_B_LP4_CAA2

U49

M_B_LP4_CAA4

M47

M_B_LP4_CAA3

M45

M_B_LP4_CAA1

R47

P39

N46

R48

M_B_LP4_CAB0

Y41

M_B_LP4_CAB2

V41

M_B_LP4_CAB1

Y42

M_B_LP4_CAB3

V47

V43

V38

M_B_DQS_0_DN

AH46

M_B_DQS_0_DP

AH47

M_B_DQS_1_DN

AJ41

M_B_DQS_1_DP

AL41

M_B_DQS_2_DN

AC47

M_B_DQS_2_DP

AC46

M_B_DQS_3_DN

AE41

M_B_DQS_3_DP

AD41

M_B_DQS_4_DN

H47

M_B_DQS_4_DP

H46

M_B_DQS_5_DN

G41

M_B_DQS_5_DP

J41

M_B_DQS_6_DN

C42

M_B_DQS_6_DP

D42

M_B_DQS_7_DN

D36

M_B_DQS_7_DP

C36

P38

M48

M49

M_B_CK_DDR0_DN 23M_B_DQ_0[0]23

M_B_CK_DDR0_DP 23

M_B_CK_DDR1_DN 24

M_B_CK_DDR1_DP 24

M_B_LP4_CKE_A0 23

M_B_LP4_CKE_A1 23

M_B_LP4_CKE_B0 24

M_B_LP4_CKE_B1 24

M_B_LP4_CS_A_R0_N 23

M_B_LP4_CS_A_R1_N 23

M_B_LP4_CS_B_R0_N 24

M_B_LP4_CS_B_R1_N 24

M_B_LP4_CAB4 24

M_B_LP4_CAA5 23

M_B_LP4_CAB5 24

M_B_LP4_CAA0 23

M_B_LP4_CAA2 23

M_B_LP4_CAA4 23

M_B_LP4_CAA3 23

M_B_LP4_CAA1 23

M_B_LP4_CAB0 24

M_B_LP4_CAB2 24

M_B_LP4_CAB1 24

M_B_LP4_CAB3 24

M_B_DQS_0_DN 23

M_B_DQS_0_DP 23

M_B_DQS_1_DN 23

M_B_DQS_1_DP 23

M_B_DQS_2_DN 23

M_B_DQS_2_DP 23

M_B_DQS_3_DN 23

M_B_DQS_3_DP 23

M_B_DQS_4_DN 24

M_B_DQS_4_DP 24

M_B_DQS_5_DN 24

M_B_DQS_5_DP 24

M_B_DQS_6_DN 24

M_B_DQS_6_DP 24

M_B_DQS_7_DN 24

M_B_DQS_7_DP 24

A A

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Page name:

Page name:

Page name:

Size:

Size:

Size:

A4

A4

A4

Date: Sheet: of

Date: Sheet: of

Date: Sheet: of

5

4

3

2

ICL-U42(CHB)

ICL-U42(CHB)

ICL-U42(CHB)

Project

Project

Project

Name:

Name:

Name:

NB8511

NB8511

NB8511

Monday, July 15, 2019 6 72

Monday, July 15, 2019 6 72

Monday, July 15, 2019 6 72

1

REV:

REV:

REV:

V1.0

V1.0

V1.0

5

4

3

2

1

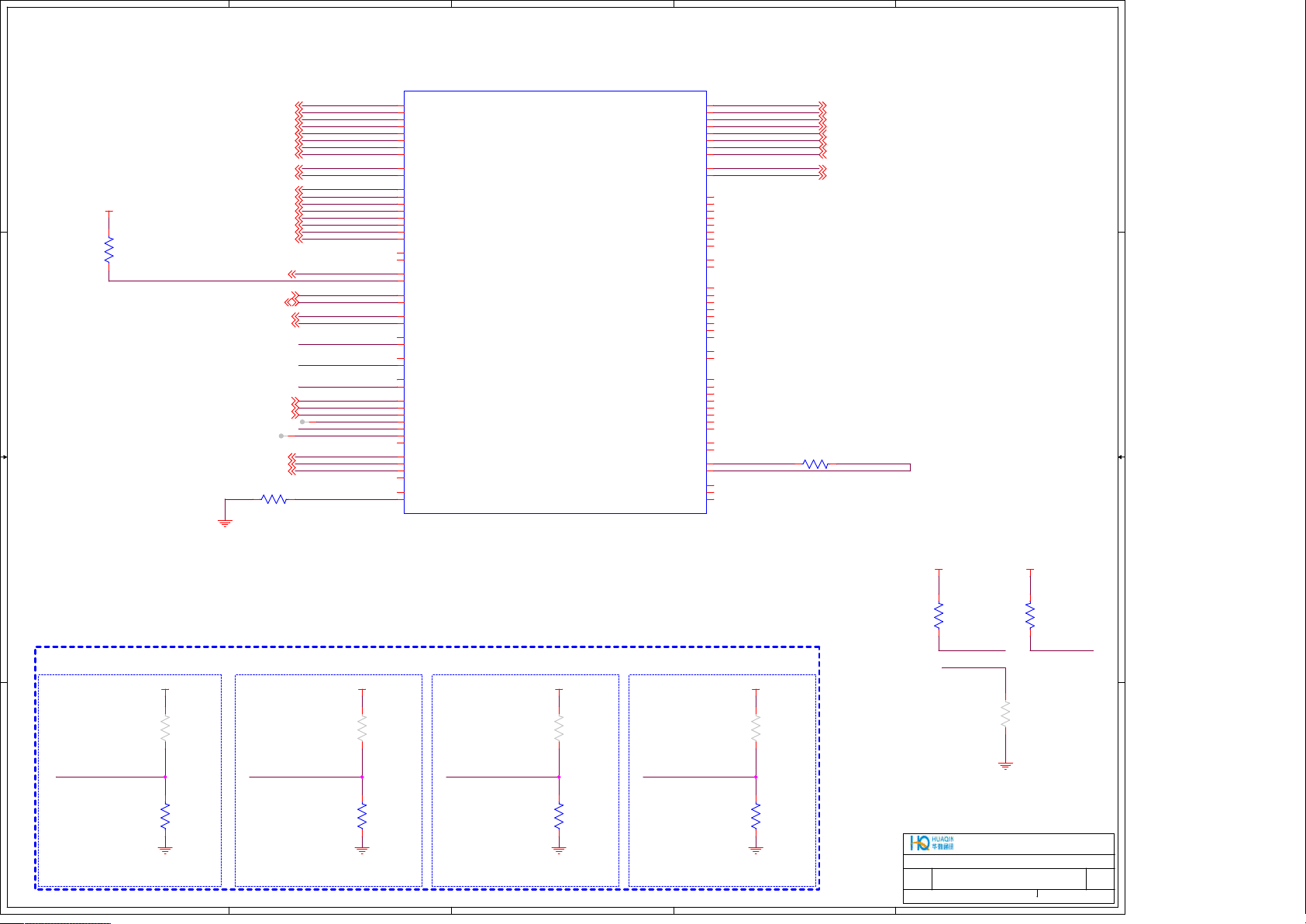

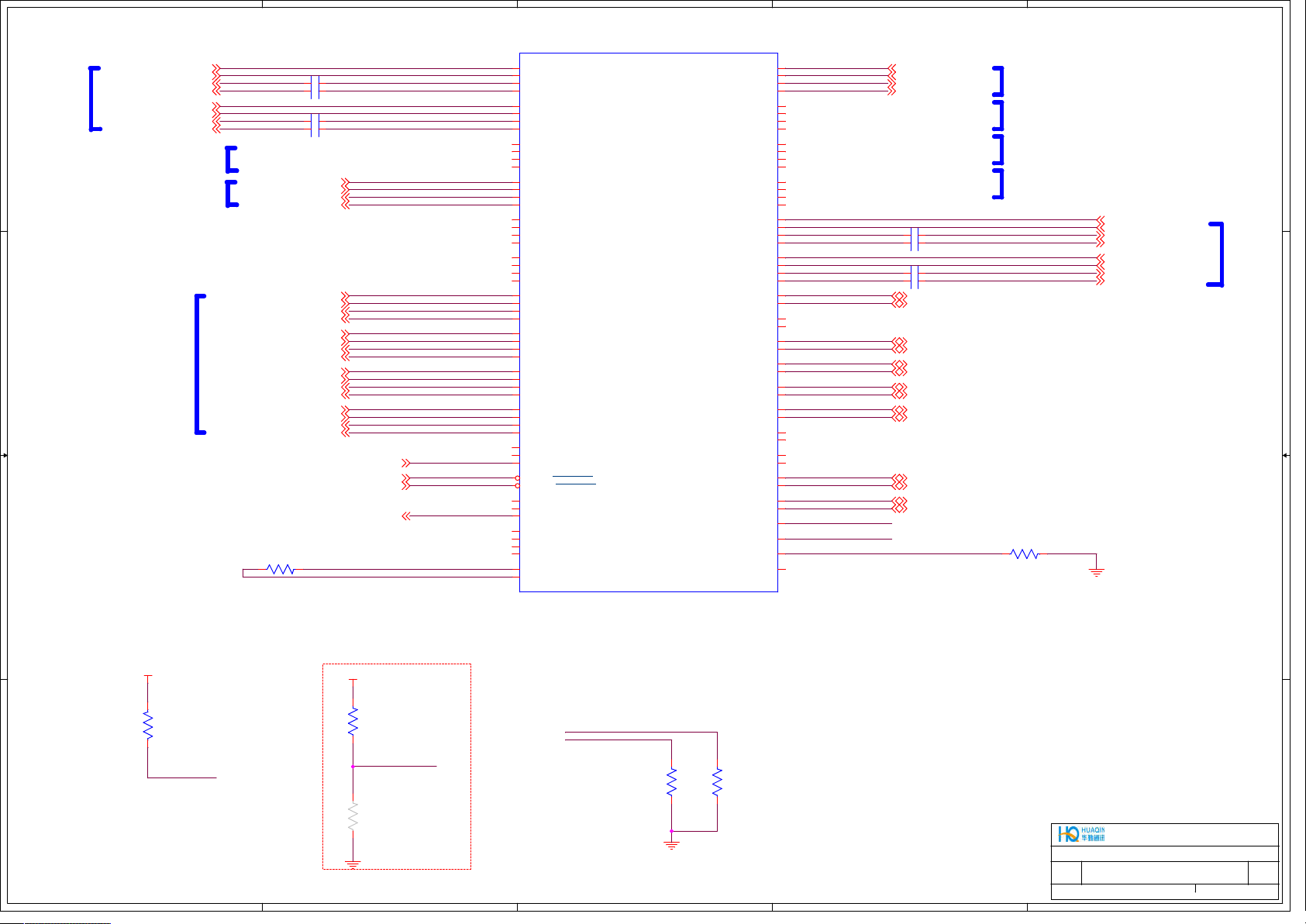

TCP0_TX_N0

TCP0_TX_P0

TCP0_TX_N1

TCP0_TX_P1

TCP0_AUX_N

TCP0_AUX_P

TCP1_TX_N0

TCP1_TX_P0

TCP1_TX_N1

TCP1_TX_P1

TCP1_AUX_N

TCP1_AUX_P

TCP2_TX_N0

TCP2_TX_P0

TCP2_TX_N1

TCP2_TX_P1

TCP2_AUX_N

TCP2_AUX_P

TCP3_TX_N0

TCP3_TX_P0

TCP3_TX_N1

TCP3_TX_P1

TCP3_AUX_N

TCP3_AUX_P

TC_RCOMP_N

TC_RCOMP_P

GPP_A21

GPP_A22

????UU1A

BB5

BB6

AV6

AV5

BH2

BH1

BF1

BF2

AY5

AY6

AR5

AR6

AL5

AL3

BD2

BD1

BB1

BB2

AN3

AN5

BF6

BF5

BJ5

BJ6

BL1

BL2

BM2

BM1

BG6

BG5

BP6

BP5

BV5

BV6

BR1

BR2

BT2

BT1

BT6

BT5

AY1

AY2

CT38

CV43

CV41

TCP0_TX0_DN

TCP0_TX0_DP

TCP0_TX1_DN

TCP0_TX1_DP

TCP0_TXRX0_DN

TCP0_TXRX0_DP

TCP0_TXRX1_DN

TCP0_TXRX1_DP

TCP0_AUX_DN

TCP0_AUX_DP

TCRCOMP_DN

TCRCOMP_DP

TCP0_TX0_DN 45

TCP0_TX0_DP 45

TCP0_TX1_DN 45

TCP0_TX1_DP 45

TCP0_TXRX0_DN 45

TCP0_TXRX0_DP 45

TCP0_TXRX1_DN 45

TCP0_TXRX1_DP 45

TCP0_AUX_DN 45

TCP0_AUX_DP 45

RU5

电阻_150R_0201_1/20W_F

TPU620MIL

ns

EDP_TX0_SOC_DN

EDP_TX0_SOC_DP

EDP_TX1_SOC_DN

EDP_TX1_SOC_DP

EDP_TX2_SOC_DN

EDP_TX2_SOC_DP

EDP_TX3_SOC_DN

EDP_TX3_SOC_DP

EDP_AUX_SOC_DN

EDP_AUX_SOC_DP

DDI1_TX0_DN

DDI1_TX0_DP

DDI1_TX1_DN

DDI1_TX1_DP

DDI1_TX2_DN

DDI1_TX2_DP

DDI1_TX3_DN

DDI1_TX3_DP

BT_RF_KILL_N

DDI1_DDC_SCL

DDI1_DDC_SDA

TBT_LSX0_TXD

TBT_LSX0_RXD

GPP_E21

GPP_D10

GPP_D12

EDP_HPD

DDI1_HPD

HPD_P1

1

ns

USB_OC1_N

USB_OC2

1

EDP_VDD_EN

EDP_BKLT_EN

EDP_BKLT_PWM

DISP_RCOMP

EDP_TX0_SOC_DN39

EDP_TX0_SOC_DP39

HDMI

EDP_TX1_SOC_DN39

EDP_TX1_SOC_DP39

EDP_TX2_SOC_DN39

EDP_TX2_SOC_DP39

EDP_TX3_SOC_DN39

EDP_TX3_SOC_DP39

EDP_AUX_SOC_DN39

EDP_AUX_SOC_DP39

DDI1_TX0_DN40

DDI1_TX0_DP40

DDI1_TX1_DN40

DDI1_TX1_DP40

DDI1_TX2_DN40

DDI1_TX2_DP40

DDI1_TX3_DN40

DDI1_TX3_DP40

BT_RF_KILL_N43

DDI1_DDC_SCL40

DDI1_DDC_SDA40

TBT_LSX0_TXD45

TBT_LSX0_RXD45

EDP_HPD39

DDI1_HPD40

HPD_P144

TPU720MIL

EDP_VDD_EN39

EDP_BKLT_EN38,39

EDP_BKLT_PWM39

RU6

电阻_150R_0201_1/20W_F

D D

+V3P3A_PCH

RU4

电阻_2.2K_0201_1/20 W_J(±5%)

C C

eDP

Y5

DDIA_TXN_0

Y3

DDIA_TXP_0

Y1

DDIA_TXN_1

Y2

DDIA_TXP_1

V2

DDIA_TXN_2

V1

DDIA_TXP_2

V3

DDIA_TXN_3

V5

DDIA_TXP_3

W4

DDIA_AUX_N

W3

DDIA_AUX_P

AE3

DDIB_TXN_0

AE5

DDIB_TXP_0

AE2

DDIB_TXN_1

AE1

DDIB_TXP_1

AC5

DDIB_TXN_2

AC3

DDIB_TXP_2

AC1

DDIB_TXN_3

AC2

DDIB_TXP_3

AD3

DDIB_AUX_N

AD4

DDIB_AUX_P

DP15

GPP_E22/DDPA_CTRLCLK/PCIE_LNK_DOWN

DJ17

GPP_E23/DDPA_CTRLDATA/BK4/SBK4

DL40

GPP_H16/DDPB_CTRLCLK

DP42

GPP_H17/DDPB_CTRLDATA

DL17

GPP_E18/DDP1_CTRLCLK/TBT_LSX0_TXD

DK17

GPP_E19/DDP1_CTRLDATA/TBT_LSX0_RXD

DN17

GPP_E20/DDP2_CTRLCLK/TBT_LSX1_TXD

DP17

GPP_E21/DDP2_CTRLDATA/TBT_LSX1_RXD

DK34

GPP_D9/ISH_SPI_CS_N/DDP3_CTRLCLK/GSPI2_CS0_N/TBT_LSX2_TXD

DL34

GPP_D10/ISH_SPI_CLK/DDP3_CTRLDATA/GSPI2_CLK/TBT_LSX2_RXD

DN33

GPP_D11/ISH_SPI_MISO/DDP4_CTRLCLK/GSPI2_MISO/TBT_LSX3_TXD

DL33

GPP_D12/ISH_SPI_MOSI/DDP4_CTRLDATA/GSPI2_MOSI/TBT_LSX3_RXD

DW11

GPP_E14/DPPE_HPDA/DISP_MISCA

CV42

GPP_A18/DDSP_HPDB/DISP_MISCB

CV39

GPP_A19/DDSP_HPD1/DISP_MISC1

CY43

GPP_A20/DDSP_HPD2/DISP_MISC2

CR41

GPP_A14/USB_OC1_N/DDSP_HPD3/DISP_MISC3

CT41

GPP_A15/USB_OC2_N/DDSP_HPD4/DISP_MISC4

DV14

GPP_E17

DN21

EDP_VDDEN

DL19

EDP_BKLTEN

DU19

EDP_BKLTCTL

J3

RSVD_1

D2

DISP_UTILS

R2

DISP_RCOMP

ICL_U_IP_EXT_WW20

1 0f 19

TCP0_TXRX_N0

TCP0_TXRX_P0

TCP0_TXRX_N1

TCP0_TXRX_P1

TCP1_TXRX_N0

TCP1_TXRX_P0

TCP1_TXRX_N1

TCP1_TXRX_P1

TCP2_TXRX_N0

TCP2_TXRX_P0

TCP2_TXRX_N1

TCP2_TXRX_P1

TCP3_TXRX_N0

TCP3_TXRX_P0

TCP3_TXRX_N1

TCP3_TXRX_P1

GPP_A17/DISP_MISCC

B B

PCH STRAP---VCCIO CONFIGURATION

+V3P3A_PCH +V3P3A_PCH +V3P3A_PCH +V3P3A_PCH

电阻_4.7K_0201_1/20W_J

RU8

ns

TBT_LSX0_RXD GPP_E21

A A

TBT_LSX0_RXD

0: DDP1 I2C / TBT LSx #0 / BSSB_LS #0 pins at 1.8V

1: DDP1 I2C / TBT LSx #0 / BSSB_LS #0 pins at 3.3V

电阻_20K_0201_1/20W_J

RU13

GPP_E21

0 = DDP1 I2C / TBT LSx #0 / BSSB_LS #0 pins at 1.8V

1 = DDP1 I2C / TBT LSx #0 / BSSB_LS #0 pins at 3.3V

Internal 20K PD

5

电阻_4.7K_0201_1/20W_J

RU9

ns

电阻_20K_0201_1/20W_J

RU14

4

GPP_D12 GPP_D10

GPP_D12

0: DDP4 I2C/TBT LSX #3/BSSB_LS #3 pins at 1.8V

电阻_4.7K_0201_1/20W_J

电阻_20K_0201_1/20W_J

RU10

ns

RU15

GPP_D10

0: DDP3 I2C/TBT LSX #2/BSSB_LS #2 pins at 1.8V

3

电阻_4.7K_0201_1/20W_J

电阻_20K_0201_1/20W_J

RU11

ns

RU16

2

+V3P3A_PCH

电阻_10K_0201_1/20W_J

RU7

HPD_P1

Page name:

Page name:

Page name:

Size:

Project

Size:

Project

Size:

Project

Name:

A4

Name:

A4

Name:

A4

Date: Sheet: of

Date: Sheet: of

Date: Sheet: of

Monday, July 15, 2019 7 72

Monday, July 15, 2019 7 72

Monday, July 15, 2019 7 72

+V3P3A_PCH

电阻_10K_0201_1/20W_J

RU143

USB_OC1_N

电阻_100K_0201_1/20W_J

ns

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

ICL-U42(DISPLAY)

ICL-U42(DISPLAY)

ICL-U42(DISPLAY)

NB8511

NB8511

NB8511

1

USB_OC2

RU12

REV:

REV:

REV:

V1.0

V1.0

V1.0

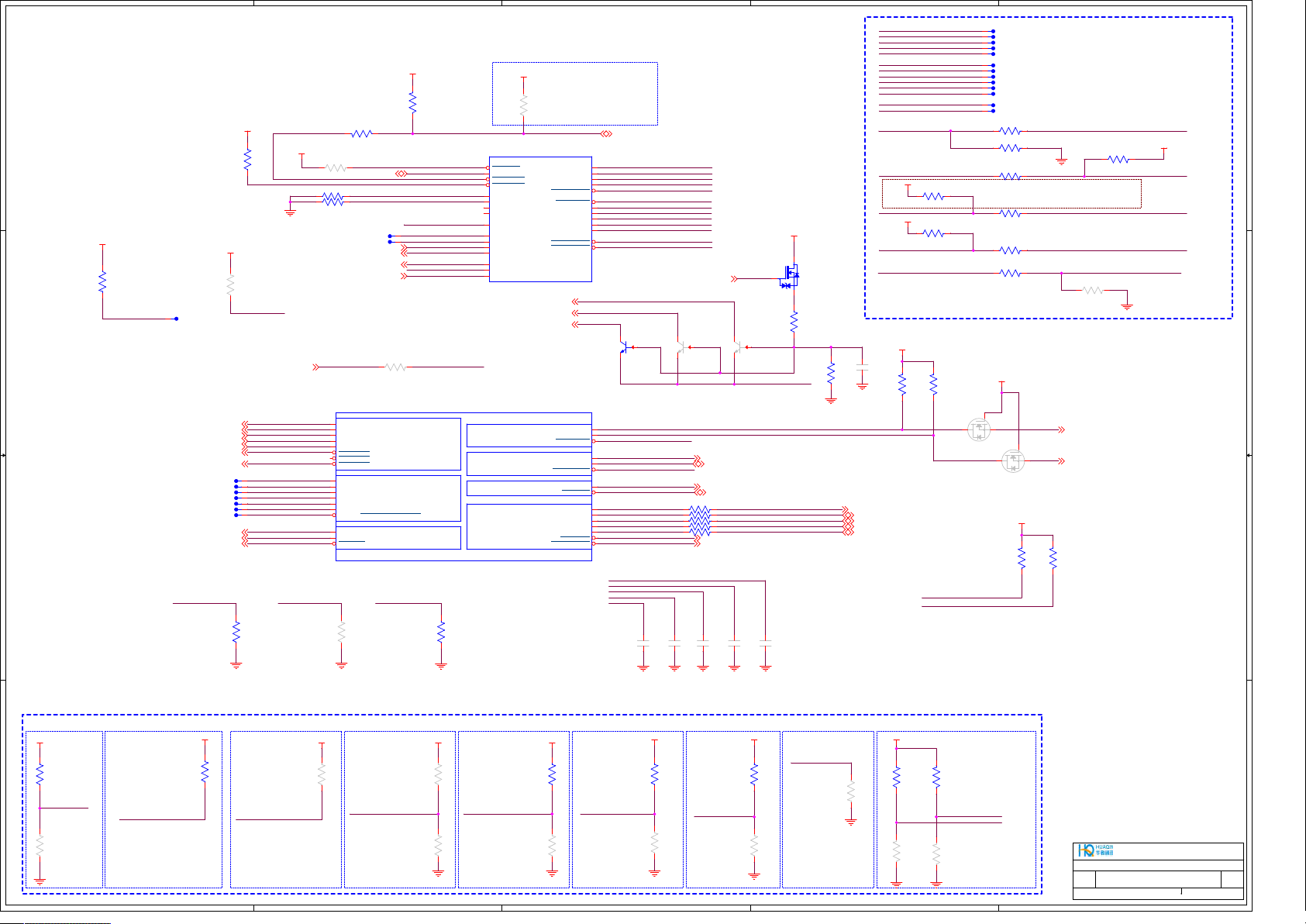

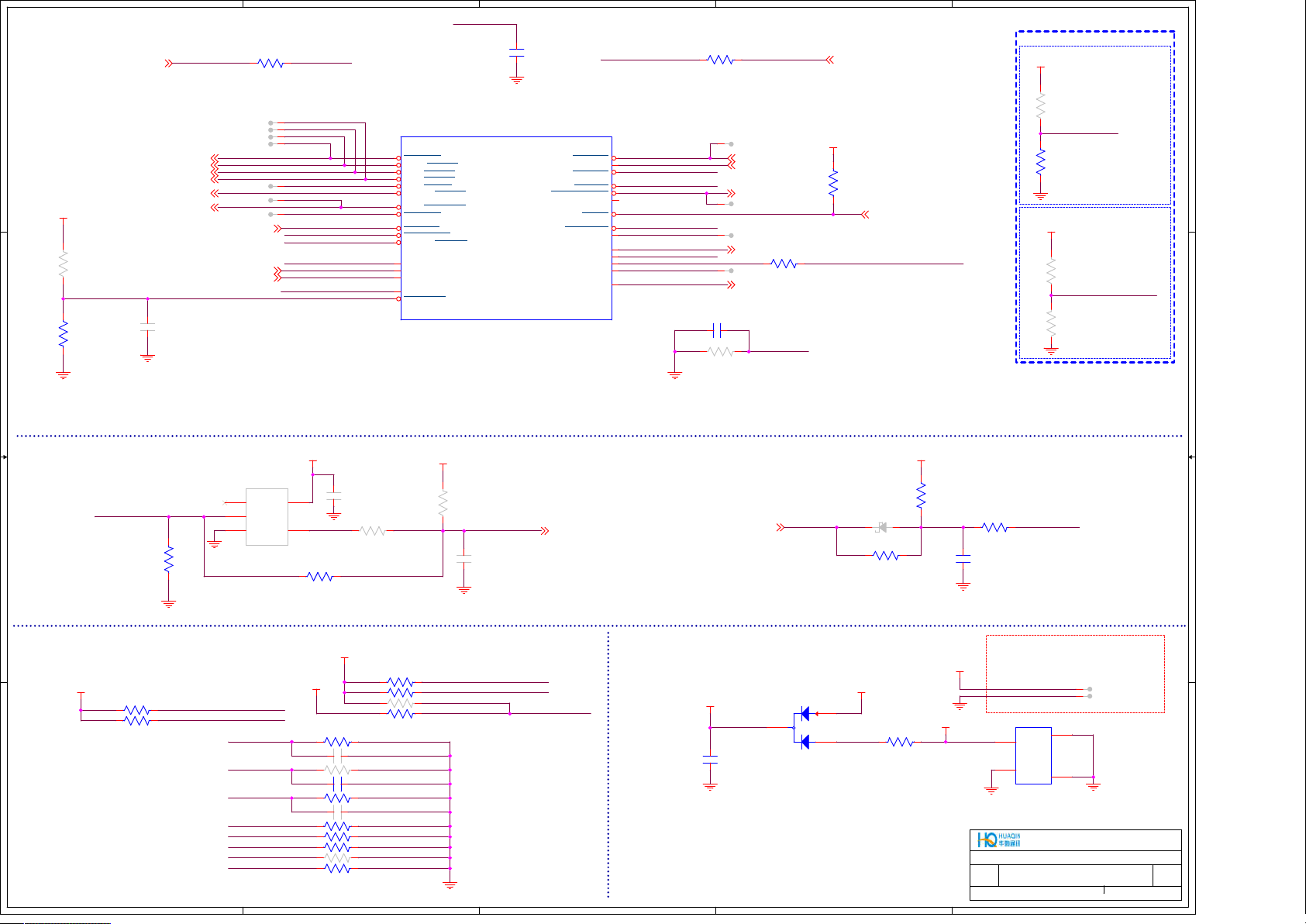

5

D D

+VCC1P05_OUT_FET

电阻_1K_0201_1/20W_J

RU222

DBG_PMODE

1

ns

C C

+V1P0S_VCCST

RU21

电阻_1K_0201_1/20W_J

+V3P3SX

ns

TP177 20MIL

RU32

电阻_10K_0201_1/20W_J

SOC_SCI_N

WAKE_PCIE_N_SOC10,43

+V1P0S_VCCST

RU24 电阻_49.9R_0201_1/20W_F

ns

RU26 电阻_49.9R_0201_1/20W_F

RU28 电阻_49.9R_0201_1/20W_F

WAKE_PCIE_N_SOC

4

RU19

电阻_499Ω_0201_1/20W_F

PECI_SOC38

TP18520MIL

TP18620MIL

SOC_SCI_N38

RETIMER_FORCE_PWR44,45

EC_SLP_S0_CS_N38,40

UART_BT_WAKE_N_SOC43

电阻_0R_0201_1/20W_J

+VCCSTG_TERM

1

1

ns

ns

RU229

ns

RU17

电阻_1K_0201_1/20W_J

CATERR_SOC_N

PECI_SOC

PROCHOT_SOC_N

THERMTRIP_SOC_N

CPU_POPI_RCOMP

PCH_POPI_RCOMP

DBG_PMODE

GPP_E3

GPP_E7

SOC_SCI_N

RETIMER_FORCE_PWR

EC_SLP_S0_CS_N

WAKE_PCIE_N_SOC_H2

UART_BT_WAKE_N_SOC

WAKE_PCIE_N_SOC_H2

+VCCSTG_TERM

J4

CATERR_N

CD5

PECI

C3

PROCHOT_N

E3

THRMTRIP_N

CJ41

PROC_POPIRCOMP

DU3

PCH_OPIRCOMP

A14

RSVD_25

B14

RSVD_26

DL15

DBG_PMODE

DV11

GPP_E3/CPU_GP0

DT11

GPP_E7/CPU_GP1

CR38

GPP_B3/CPU_GP2

CR39

GPP_B4/CPU_GP3

DT12

GPP_E6

DJ38

GPP_H2/CNV_BT_I2S_SDO

DL38

GPP_H19/TIME_SYNC0

ICL_U_IP_EXT_WW20

PLACE NEAR THE FAR DEVICE

RU18

ns

电阻_10K_0201_1/20W_J

CPU_PROCHOT_N

PROC_TRST_N

PCH_TRST_N

PROC_PRDY_N

PROC_PREQ_N

4 of 19

5P0VA_EN38,62

3P3VA_EN29,38,57,61

RSMRST_N_EC12,38,57

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PCH_TCK

PCH_TDI

PCH_TDO

PCH_TMS

PCH_JTAGX

? ???UU1D

MIPI60_CPU_JTAG_TCLK

P3

MIPI60_CPU_JTAG_TDI

K5

MIPI60_CPU_JTAG_TDO

K3

MIPI60_CPU_JTAG_TMS

P4

MIPI60_CPU_JTAG_TRST_N

N1

MIPI60_PCH_JTAG_TRST_N

N5

MIPI60_PCH_JTAG_TCLK

R5

MIPI60_PCH_JTAG_TDI

K1

MIPI60_PCH_JTAG_TDO

K2

MIPI60_PCH_JTAG_TMS

N3

MIPI60_PCH_JTAGX

N2

MIPI60_PRDY_N

P6

MIPI60_PREQ_N

M6

5P0VA_EN

3P3VA_EN

RSMRST_N_EC

3

CPU_PROCHOT_N 14,38,66

QU6

1

2 3

LMBT3904LT1G

EC_IMVP_PWRGD38,66

QU4

1

ns

2 3

LMBT3904LT1G

QU5

ns

2 3

LMBT3904LT1G

+V1P0S_VCCST

1

1

THERMTRIP_SOC_N

32

D

G

QU7

S

WNM2046-3/TR

RU224

电阻_1K_0201_1/20W_J

2

MIPI60_CPU_JTAG_TCLK

MIPI60_CPU_JTAG_TDI

MIPI60_CPU_JTAG_TDO

MIPI60_CPU_JTAG_TMS

MIPI60_CPU_JTAG_TRST_N

MIPI60_PCH_JTAG_TRST_N

MIPI60_PCH_JTAG_TCLK

MIPI60_PCH_JTAG_TDI

MIPI60_PCH_JTAG_TDO

MIPI60_PCH_JTAG_TMS

MIPI60_PCH_JTAGX

MIPI60_PRDY_N

MIPI60_PREQ_N

MIPI60_CPU_JTAG_TDI

+VCCSTG_TERM

RU27

电阻_51R_0201_1/20W_J

MIPI60_CPU_JTAG_TDO MIPI60_PCH_JTAG_TDO

+VCCSTG_TERM

RU30

电阻_51R_0201_1/20W_J

MIPI60_CPU_JTAG_TMS

MIPI60_CPU_JTAG_TRST_N

ns

CU168

电容_100nF_0201_X5R_6.3 V_M(±20%)

+V3P3A_PCH

电阻_2.2K_0201_1/20 W_J(±5%)

电阻_2.2K_0201_1/20 W_J(±5%)

RU35

电阻_100K_0201_1/20W_J

RU232

1

1

1

ns

1

ns

1

ns

ns

1

ns

1

1

ns

1

ns

1

ns

1

ns

ns

1

ns

1

ns

ns

RU20

RU22 电阻_51R_0201_1/20W_J

RU25 电阻_0R_0201_1/20W_J

change RU27 to 51Ω - 02/26

RU29

RU31

RU33

RU36

TP1 20MIL

TP2 20MIL

TP3 20MIL

TP4 20MIL

TP5 20MIL

TP6 20MIL

TP7 20MIL

TP8 20MIL

TP9 20MIL

TP10 20MIL

TP11 20MIL

TP12 20MIL

TP13 20MIL

+V3P3SX

电阻_0R_0201_1/20W_J

电阻_0R_0201_1/20W_J

电阻_0R_0201_1/20W_J

电阻_0R_0201_1/20W_J

电阻_51R_0201_1/20W_J

1

MIPI_60

MIPI60_PCH_JTAGXMIPI60_CPU_JTAG_TCLK

RU23

电阻_51R_0201_1/20W_J

MIPI60_PCH_JTAG_TDI

MIPI60_PCH_JTAG_TMS

MIPI60_PCH_JTAG_TRST_N

RU34

ns

+VCCSTG_TERM

FLASH_SPI_CLK36,37

FLASH_SPI_MOSI36,37

FLASH_SPI_MISO36,37

FLASH_SPI_IO237

FLASH_SPI_IO337

FLASH_SPI_CS0_N37

FLASH_SPI_CS2_N36

CLNK_CLK_SOC43

CLNK_DATA_SOC43

CLNK_RESET_SOC43

B B

FLASH_SPI_CLK ESPI_CS_N ESPI_RESET

电阻_100K_0201_1/20W_J

PCH STRAP

电阻_20K_0201_1/20W_J

BOOT HALT ESPI OR EC LESSTLS CONFIDENTIALITY

RU47

A A

FLASH_SPI_MOSI

电阻_4.7K_0201_1/20W_J

ns

RU57

FLASH_SPI_MOSI

1: DISABLED

0: ENABLED

WEAK INTERNAL PU

GPPC_C2_SMBALERT_N GPPC_C5_SML0ALERT_N

GPPC_C2_SMBALERT_N

0: Disable TLS CONFIDENTIALITY DISABLE(Default)

1: Enable TLS CONFIDENTIALITY DISABLE

Internal 20K PD

5

+V3P3A_PCH +V3P3A_SPI_FLASH +V3P3A_SPI_FLASH

RU48

FLASH_SPI_CLK

FLASH_SPI_MOSI

FLASH_SPI_MISO

FLASH_SPI_IO2

FLASH_SPI_IO3

FLASH_SPI_CS0_N

FLASH_SPI_CS2_N

SPI1_CLK

1

TP18320MIL

GPP_E13

1

TP18220MIL

GPP_E12

1

ns

TP18120MIL

GPP_E1

1

ns

TP17920MIL

GPP_E2

1

ns

TP17820MIL

SPI1_CS0_N

1

ns

TP18420MIL

GPP_E8

1

ns

TP18020MIL

ns

ns

CLNK_CLK_SOC

CLNK_DATA_SOC

CLNK_RESET_SOC

RU44

电阻_4.7K_0201_1/20W_J

GPPC_C5_SML0ALERT_N

0: Enable eSPI. (Default)

1: Disable

Internal 20K PD

电阻_75K_0201_1/20 W_F(±1%)

RU49

DB42

DD43

DF43

DF42

DD41

DB43

DF41

DB41

DV16

DT16

DU18

DT18

DW18

DW16

DU16

DV19

DW19

DT19

RU45

+V3P3A_PCH+V3P3A_PCH

电阻_4.7K_0201_1/20W_J

ns

SPI0_CLK

SPI0_MOSI

SPI0_MISO

SPI0_IO2

SPI0_IO3

SPI0_CS0_N

SPI0_CS1_N

SPI0_CS2_N

GPP_E11/SPI1_CLK/BK1/SBK1

GPP_E13/SPI1_MOSI/BK3/SBK3

GPP_E12/SPI1_MISO/BK2/SBK2

GPP_E1/SPI1_IO2

GPP_E2/SPI1_IO3

GPP_E10/SPI1_CS_N/BK0/SBK0

GPP_E8/SATALED_N/SPI1_CS1_N

CL_CLK

CL_DATA

CL_RST_N

ICL_U_IP_EXT_WW20

ns

电阻_75K_0201_1/20 W_F(±1%)

MAF/SAF STRAP

WAKE_PCIE_N_SOC_H2

GPPC_H2(WAKE_PCIE_N_SOC)

0: Enable MAFS

1: Enable SAFS

WEAK INTERNAL PD 20K

4

RU46

+V3P3A_PCH

RU50

RU58

SPI 0 SPI 1 MLINK

SMBUSSML 0SML1eSPI

GPP_C6/SML1CLK/SUSWARN_N/SUSPWRDNACK

5 of 19

JTAG ODT DISABLE

电阻_4.7K_0201_1/20W_J

ns

EC_SLP_S0_CS_N

电阻_20K_0201_1/20W_J

ns

EC_SLP_S0_CS_N

0: JTAG ODT DISABLED

1: JTAG ODT ENABLED

NO INTERNAL PU/PD

GPP_C1/SMBDATA

GPP_C2/SMBALERT_N

GPP_C4/SML0DATA

GPP_C5/SML0ALERT_N

GPP_C7/SML1DATA/SUSACK_N

GPP_A4/ESPI_CS_N

GPP_A6/ESPI_RESET_N

+V3P3A_PCH

RU51

RU59

GPP_C0/SMBCLK

GPP_C3/SML0CLK

GPP_A5/ESPI_CLK

GPP_A0/ESPI_IO0

GPP_A1/ESPI_IO1

GPP_A2/ESPI_IO2

GPP_A3/ESPI_IO3

电阻_100K_0201_1/20W_J

JTAG ODT DISABLE

电阻_4.7K_0201_1/20W_J

ns

????UU1E

DK27

DP24

DL24

DK24

DJ24

DP22

DN22

DL22

CR47

CN45

CN48

CN49

CN47

CT45

CR46

ESPI_CLK_EC

ESPI_IO0_EC

ESPI_IO1_EC

ESPI_IO2_EC

ESPI_IO3_EC

FLASH_SPI_IO3

FLASH_SPI_IO3

0: ENABLED

1: DISABLED

NO INTERNAL PU/PD

PCH_SMB1_CLK

PCH_SMB1_DATA

GPPC_C2_SMBALERT_N

SMBUS_CLK0

SMBUS_DAT0

GPPC_C5_SML0ALERT_N

TYPEC_PD_SOC_CLK

TYPEC_PD_SOC_DAT

ESPI_CLK

RU37 电阻_49.9R_0201_1/20W_F

ESPI_IO0

RU38 电阻_10R_0201_1/20W_J

ESPI_IO1

RU39 电阻_10R_0201_1/20W_J

ESPI_IO2

RU40 电阻_10R_0201_1/20W_J

ESPI_IO3

RU43 电阻_10R_0201_1/20W_J

ESPI_CS_N

ESPI_RESET

电容_22pF_0201_C0G_25 V_J(±5%)

电容_22pF_0201_C0G_25 V_J(±5%)

CU1

ns

电阻_100K_0201_1/20W_J

RU52

电阻_100K_0201_1/20W_J

RU60

ns

3

电容_22pF_0201_C0G_25 V_J(±5%)

CU2

ns

CONSENT STRAP

FLASH_SPI_IO2

0: ENABLED

1: DISABLED

NO INTERNAL PU/PD

SMBUS_CLK0 45

SMBUS_DAT0 45

TYPEC_PD_SOC_CLK 44

TYPEC_PD_SOC_DAT 44

ESPI_CS_N 38

ESPI_RESET 38

电容_22pF_0201_C0G_25 V_J(±5%)

CU4

CU3

ns

ns

电阻_100K_0201_1/20W_J

FLASH_SPI_IO2

电阻_4.7K_0201_1/20W_J

ESPI_CLK_EC

ESPI_IO0_EC

ESPI_IO1_EC

ESPI_IO2_EC

ESPI_IO3_EC

电容_22pF_0201_C0G_25 V_J(±5%)

CU5

ns

DFXTESTMODE

DBG_PMODE

RU53

RU61

ns

DBG_PMODE

0: DFXTESTMODE ENABLED

1: DFXTESTMODE DISABLED(DEFAULT)

WEAK INTERNAL PU 20K

RU54

ESPI_CLK_EC 38

ESPI_IO0_EC 38

ESPI_IO1_EC 38

ESPI_IO2_EC 38

ESPI_IO3_EC 38

电阻_1K_0201_1/20W_J

ns

2

+V3P3A_PCH

电阻_10K_0201_1/20W_J

电阻_20K_0201_1/20W_J

RU62

ns

RU55

SMBUS_CLK0

SMBUS_DAT0

电阻_10K_0201_1/20W_J

电阻_20K_0201_1/20W_J

ns

5

G

3 4

ns

S

D

QU1A

LBSS139DW1T1G

6 1

XTAL INPUT FREQUENCY

1.SPI1_CS0_N

XTAL INPUT FREQUENCY [0]

2.SPI1_CLK

XTAL INPUT FREQUENCY [1]

RU56

SPI1_CS0_N

SPI1_CLK

RU63

00: DIVIDER BYPASS

01: DIVIDE BY 2 (HVM: 38.4MHZ INPUT)

10: DIVIDE BY 10 (HVM: 250MHZ INPUT)

11: DIVIDE BY 4 (BI: 100MHZ INPUT)

( QUALIFIED BY DFXTESTMODE)

NO INTERNAL PU/PD

2

G

ns

S

D

QU1B

LBSS139DW1T1G

+V3P3A_PCH

电阻_2.2K_0201_1/20 W_J(±5%)

RU41

SMB_EC_SCLK 29,38,56

SMB_EC_SDATA 29,38,56

电阻_2.2K_0201_1/20 W_J(±5%)

RU42

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Page name:

Page name:

Page name:

Size:

Size:

Size:

A4

A4

A4

Date: Sheet: of

Date: Sheet: of

Date: Sheet: of

Huaqin Telecom Technology Com.,Ltd.

ICL-U42(SPI/ESPI/MIPI60)

ICL-U42(SPI/ESPI/MIPI60)

ICL-U42(SPI/ESPI/MIPI60)

Project

Project

Project

Name:

Name:

Name:

NB8511

NB8511

NB8511

Monday, July 15, 2019 8 72

Monday, July 15, 2019 8 72

Monday, July 15, 2019 8 72

1

REV:

REV:

REV:

V1.0

V1.0

V1.0

5

4

3

2

1

PCH STRAP

+V1P8A

电阻_4.7K_0201_1/20W_J

RU64

ns

CNV_BRI_DT_SOC

电阻_20K_0201_1/20W_J

RU67

CNV_BRI_DT_SOC

0: 38.4/19.2MHZ (DEFAULT)

ns

1: 24MHZ (25 MHZ WHEN XTAL

FREQ DIVIDER NON ZERO)

WEAK INTERNAL PD 20K

CNV_RGI_DT_SOC

XTAL SEL

RU223

ns

电阻_4.7K_0201_1/20W_J

EMMC_RCOMP

CNV_WT_D0N

CNV_WT_D0P

CNV_WT_D1N

CNV_WT_D1P

CNV_WT_CLKN

CNV_WT_CLKP

CNV_WR_D0N

CNV_WR_D0P

CNV_WR_D1N

CNV_WR_D1P

CNV_WR_CLKN

CNV_WR_CLKP

????UU1I

DP27

DU30

DT30

DT29

DV30

DU29

DW30

DW29

DV28

DW28

DN27

DT28

DU28

DV45

DU45

DU44

DT44

DL42

DK42

DP44

DN44

DG42

DG44

DK44

DJ44

DT45

DL29

DP31

DL31

DN29

DJ29

DP29

DL27

DK29

EMMC_RCOMP

CNV_WT_LANE0_DN_R

CNV_WT_LANE0_DP_R

CNV_WT_LANE1_DN_R

CNV_WT_LANE1_DP_R

CNV_WT_CLK_DN_R

CNV_WT_CLK_DP_R

CNV_WR_LANE0_DN

CNV_WR_LANE0_DP

CNV_WR_LANE1_DN

CNV_WR_LANE1_DP

CNV_WR_CLK_DN

CNV_WR_CLK_DP

CNV_WT_RCOMP

CNV_BRI_RSP_SOC

CNV_RGI_DT_SOC

CNV_BRI_DT_SOC

CNV_RGI_RSP_SOC

D12

CSI_E_CLK_N

C12

CSI_E_CLK_P

B12

CSI_E_DN_0

A12

CSI_E_DP_0

G13

CSI_E_DN_1

F13

CSI_E_DP_1

K10

CSI_F_CLK_N

L10

CSI_F_CLK_P

D D

RU76

电阻_100R_0201_1/20W_F

C C

CSI_COMP

L8

CSI_F_DN_0

M8

CSI_F_DP_0

M11

CSI_F_DN_1

L11

CSI_F_DP_1

D9

CSI_D_CLK_N

C9

CSI_D_CLK_P

A7

CSI_D_DN_0

B7

CSI_D_DP_0

B9

CSI_D_DN_1

A9

CSI_D_DP_1

D7

CSI_D_DN_2/CSI_C_DN_0

C7

CSI_D_DP_2/CSI_C_DP_0

D8

CSI_D_DN_3/CSI_C_CLK_N

C8

CSI_D_DP_3/CSI_C_CLK_P

G11

CSI_H_CLK_N

J11

CSI_H_CLK_P

F6

CSI_H_DN_0

G6

CSI_H_DP_0

G10

CSI_H_DN_1

F10

CSI_H_DP_1

G8

CSI_H_DN_2/CSI_G_DN_0

J8

CSI_H_DP_2/CSI_G_DP_0

K6

CSI_H_DN_3/CSI_G_CLK_N

L6

CSI_H_DP_3/CSI_G_CLK_P

B4

CSI_RCOMP

DT34

GPP_D4/IMGCLKOUT0

DP38

GPP_H20/IMGCLKOUT1

DK36

GPP_H21/IMGCLKOUT2

DL36

GPP_H22/IMGCLKOUT3

DN38

GPP_H23/IMGCLKOUT4

ICL_U_IP_EXT_WW20

CSI2

9 of 19

GPP_F8/EMMC_DATA0

GPP_F9/EMMC_DATA1

GPP_F10/EMMC_DATA2

GPP_F11/EMMC_DATA3

GPP_F12/EMMC_DATA4

GPP_F13/EMMC_DATA5

GPP_F14/EMMC_DATA6

eMMCCNVi

GPP_F15/EMMC_DATA7

GPP_F7/EMMC_CMD

GPP_F16/EMMC_RCLK

GPP_F17/EMMC_CLK

GPP_F18/EMMC_RESET_N

GPP_F1/CNV_BRI_RSP/UART0_RXD

GPP_F2/CNV_RGI_DT/UART0_TXD

GPP_F0/CNV_BRI_DT/UART0_RTS_N

GPP_F3/CNV_RGI_RSP/UART0_CTS_N

CNV_WT_RCOMP

GPP_F4/CNV_RF_RESET_N

GPP_F6/CNV_PA_BLANKING

GPP_F19/A4WP_PRESENT

GPP_F5/MODEM_CLKREQ

电阻_200R_0201_1/20W_F

A4WP_PRESENT

HW_ID0

HW_ID1

HW_ID2

HW_ID3

HW_ID4

HW_ID5

HW_ID6

HW_ID7

Memory ID

GPU ID

LCD ID

Project ID

RU65

RU66 电阻_0R_0201_1/20W_J

RU68 电阻_0R_0201_1/20W_J

RU69 电阻_0R_0201_1/20W_J

RU70 电阻_0R_0201_1/20W_J

RU71 电阻_0R_0201_1/20W_J

RU72 电阻_0R_0201_1/20W_J

CNV_WR_LANE0_DN 43

CNV_WR_LANE0_DP 43

CNV_WR_LANE1_DN 43

CNV_WR_LANE1_DP 43

CNV_WR_CLK_DN 43

CNV_WR_CLK_DP 43

RU73 电阻_150R_0201_1/20W_F

CNV_BRI_RSP_SOC 43

CNV_RGI_RSP_SOC 43

CNV_WT_LANE0_DN

CNV_WT_LANE0_DP

CNV_WT_LANE1_DN

CNV_WT_LANE1_DP

CNV_WT_CLK_DN

CNV_WT_CLK_DP

RU74 电阻_33R_0201_1/20W_F

RU75 电阻_33R_0201_1/20W_F

+V1P8A

电阻_100K_0201_1/20W_J

RU77

ns

电阻_100K_0201_1/20W_J

CNV_WT_LANE0_DN 43

CNV_WT_LANE0_DP 43

CNV_WT_LANE1_DN 43

CNV_WT_LANE1_DP 43

CNV_WT_CLK_DN 43

CNV_WT_CLK_DP 43

CNV_RGI_DT

CNV_BRI_DT

CNV_RGI_DT 43

CNV_BRI_DT 43

RU78

????UU1J

PCIE_REFCLK_GFX_DN29

PCIE_REFCLK_GFX_DP29

PCIE_CLKREQ_VGA_N29

B B

PCIE_REFCLK_WLAN_DN43

PCIE_REFCLK_WLAN_DP43

PCIE_WLAN_CLK_REQ_N43

PCIE_REFCLK_SSD_DN41

PCIE_REFCLK_SSD_DP41

PCIE_SSD_CLKREQ141

+V1P8A

A A

RU92 电阻_4.7K_0201_1/20W_J

ns_LP4/X_ID@

RU94 电阻_4.7K_0201_1/20W_J

ns_LP4/X_ID@

RU96 电阻_4.7K_0201_1/20W_J

ns_LP4/X_ID@

RU98 电阻_4.7K_0201_1/20W_J

ns_LP4X_ID@

RU102 电阻_4.7K_0201_1/20W_J

DLG_R_ID@

RU105 电阻_4.7K_0201_1/20W_J

DGPU_ID@

RU107 电阻_4.7K_0201_1/20W_J

LCD4X@

RU109 电阻_4.7K_0201_1/20W_J

NB8512@

5

PCIE_REFCLK_GFX_DN

PCIE_REFCLK_GFX_DP

PCIE_CLKREQ_VGA_N

PCIE_REFCLK_WLAN_DN

PCIE_REFCLK_WLAN_DP

PCIE_WLAN_CLK_REQ_N

PCIE_REFCLK_SSD_DN

PCIE_REFCLK_SSD_DP

PCIE_SSD_CLKREQ1

HW_ID0

HW_ID1

HW_ID2

HW_ID3

HW_ID4

HW_ID5

HW_ID6

HW_ID7

CJ3

CLKOUT_PCIE_N0

CJ5

CLKOUT_PCIE_P0

DK33

GPP_D5/SRCCLKREQ0_N

CL2

CLKOUT_PCIE_N1

CL1

CLKOUT_PCIE_P1

DN34

GPP_D6/SRCCLKREQ1_N

CL3

CLKOUT_PCIE_N2

CL5

CLKOUT_PCIE_P2

DP34

GPP_D7/SRCCLKREQ2_N

CK3

CLKOUT_PCIE_N3

CK4

CLKOUT_PCIE_P3

DP36

GPP_D8/SRCCLKREQ3_N

CJ2

CLKOUT_PCIE_N4

CJ1

CLKOUT_PCIE_P4

DN40

GPP_H10/SRCCLKREQ4_N

ICL_U_IP_EXT_WW20

10 of 19

HW ID

RU93 电阻_4.7K_0201_1/20W_J

LP_4/X_ID@

RU95 电阻_4.7K_0201_1/20W_J

LP_4I/X_ID@

RU97 电阻_4.7K_0201_1/20W_J

LP_4/X_ID@

RU99 电阻_4.7K_0201_1/20W_J

LP4_ID@

RU100 电阻_4.7K_0201_1/20W_J

DLG_ID@

RU106 电阻_4.7K_0201_1/20W_J

UMA_ID@

RU108 电阻_4.7K_0201_1/20W_J

LCD2X@

RU110 电阻_4.7K_0201_1/20W_J

NB8511@

4

CLKOUT_PCIE_N5

CLKOUT_PCIE_P5

GPP_H11/SRCCLKREQ5_N

RTCX1

RTCX2

RTCRST_N

SRTCRST_N

GPD8/SUSCLK

XTAL_IN

XTAL_OUT

XCLK_BIASREF

电阻_60.4R_0201_1/20_F(±1%)

CF5

CF3

DP40

XTAL_32K_SOC_IN

DL48

XTAL_32K_SOC_OUT

DL49

RTC_RST_N

DT47

SRTC_RST_N

DK46

SUS_CLK

DF49

XTAL_38P4M_SOC_IN

DW8

XTAL_38P4M_SOC_OUT

DU8

XCLK_BIASREF

DU6

RU88

+V3P3SX

电阻_10K_0201_1/20W_J

电阻_10K_0201_1/20W_J

RU103

RU82 电阻_0R_0201_1/20W_J

RU83 电阻_0R_0201_1/20W_J

电阻_33R_0201_1/20W_F

RU84

电阻_0R_0201_1/20W_J

RU85

RU86

电阻_0R_0201_1/20W_J

RU101

PCIE_WLAN_CLK_REQ_N

PCIE_CLKREQ_VGA_N

SUS_CLK_WLAN 43

电阻_200K_0201_1/20 W_F(±1%)

RU87

3

电阻_10M_0201_1/20 W_J(±5%)

MAIN 38.4MHZ CRYSTAL

YU2

38.4MHZ

2

GND1

1

1

GND2

X3S038400BA1H-HS

CU6 电容_6.8pF_0201_C0G_50 V_C(±0.25pF)

RU81

电容_8.2pF_0201_C0G_50 V_C(±0.25pf)

电容_8.2pF_0201_C0G_50 V_C(±0.25pf)

YU1

Q13FC1350000200

1 2

RTC CRYSTAL

CU7 电容_6.8pF_0201_C0G_50 V_C(±0.25pF)

CU8

3

3

4

CU9

2

3

D

QU2

LMN2500N3T5G

S

G

1

2

RU90

电阻_10K_0201_1/20W_J

EC_RTCRST 38

+V1P8A

RU79

电阻_10K_0201_1/20W_J

电阻_20K_0201_1/20W_J

RU80

ns

ns

CNV_RGI_RSP_SOC

CNV_BRI_RSP_SOC

close to SOC - 07/10

+VCCRTC

电阻_27K_0201_1/20W_F

电阻_27K_0201_1/20W_F

RU91

SRTC_RST_N

RTC_RST_N

TPU820MIL

TPU920MIL

Page name:

Page name:

Page name:

ICL-U42(CNV1/CSI/CLK)

ICL-U42(CNV1/CSI/CLK)

ICL-U42(CNV1/CSI/CLK)

Size:

Project

Size:

Project

Size:

Project

Name:

Name:

Name:

A4

A4

A4

Date: Sheet: of

Date: Sheet: of

Date: Sheet: of

Monday, July 15, 2019 9 72

Monday, July 15, 2019 9 72

Monday, July 15, 2019 9 72

电容_1uF_0201_X5R_6.3V_M

1

ns

1

ns

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

NB8511

NB8511

NB8511

1

电容_1uF_0201_X5R_6.3V_M

CU10

RU89

CU11

REV:

REV:

REV:

V1.0

V1.0

V1.0

5

4

3

2

1

PCH STRAP

????UU1F

CH48

GPPC_B18_GSPI0_MOSI

PCH_WLAN_OFF_N43

GPPC_B_14_SPKR50

TPU1020MIL

TPU1120MIL

D D

C C

+V3P3SX

RU119 电阻_10K_0201_1/20W_J

RU120 电阻_10K_0201_1/20W_J

RU122 电阻_10K_0201_1/20W_J

CU13 电容_10nF_0201_X7R_16V_K

TPU1220MIL

TCH_EN_SOC39

WLAN_RST_N43

UART2_RXD55

UART2_TXD55

RT_TCP0_I2C0_SDA45

RT_TCP0_I2C0_SCL45

TOUCHPAD_I2C_SDA52

TOUCHPAD_I2C_CLK52

GPU

ns

ns

GPU

PCH_WLAN_OFF_N

GPPC_B_14_SPKR

GPSI1_CLK

1

ns

GPSI1_MOSI

1

ns

GPSI1_MISO

1

ns

TCH_EN_SOC

GPPC_B23_SML1_ALERT_N

WLAN_RST_N

UART2_RXD

UART2_TXD

RT_TCP0_I2C0_SDA

RT_TCP0_I2C0_SCL

TOUCHPAD_I2C_SDA

TOUCHPAD_I2C_CLK

I2C_PD_SOC_INT_N12,44

GPU_PWREN

PCH_GPU_RST_N_R

PCH_GPU_RST_N

GPP_B16/GSPI0_CLK

CF48

GPP_B18/GSPI0_MOSI

CF47

GPP_B17/GSPI0_MISO

CH49

GPP_B15/GSPI0_CS0_N

CH47

GPP_B14/SPKR/TIME_SYNC1/GSPI0_CS1_N

CL47

GPP_B20/GSPI1_CLK

CK47

GPP_B22/GSPI1_MOSI

CK46

GPP_B21/GSPI1_MISO

CH45

GPP_B19/GSPI1_CS0_N

CL48

GPP_B23/SML1ALERT_N/PCHHOT_N/GSPI1_CS1_N

DP21

GPP_C8/UART0_RXD

DK21

GPP_C9/UART0_TXD

DL21

GPP_C10/UART0_RTS_N

DJ22

GPP_C11/UART0_CTS_N

DT22

GPP_C20/UART2_RXD

DW22

GPP_C21/UART2_TXD

DV22

GPP_C22/UART2_RTS_N

DU22

GPP_C23/UART2_CTS_N

DT24

GPP_C16/I2C0_SDA

DT23

GPP_C17/I2C0_SCL

DW23

GPP_C18/I2C1_SDA

DU23

GPP_C19/I2C1_SCL

DU41

GPP_H4/I2C2_SDA

DV41

GPP_H5/I2C2_SCL

DW41

GPP_H6/I2C3_SDA

DT41

GPP_H7/I2C3_SCL

DT40

GPP_H8/I2C4_SDA/CNV_MFUART2_RXD

DW40

GPP_H9/I2C4_SCL/CNV_MFUART2_TXD

ICL_U_IP_EXT_WW20

RU218 电阻_0R_0201_1/20W_J

RU121

GPU

电阻_0R_0201_1/20W_J

GPP_D15/ISH_UART0_RTS_N/GSPI2_CS1_N/IMGCLKOUT5

GPP_C14/UART1_RTS_N/ISH_UART1_RTS_N

GPP_C15/UART1_CTS_N/ISH_UART1_CTS_N

6 of 19

ns

GPP_D13/ISH_UART0_RXD

GPP_D14/ISH_UART0_TXD

GPP_D16/ISH_UART0_CTS_N/CNV_WCEN

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_B5/ISH_I2C0_SDA

GPP_B6/ISH_I2C0_SCL

GPP_B7/ISH_I2C1_SDA

GPP_B8/ISH_I2C1_SCL

GPP_B9/I2C5_SDA/ISH_I2C2_SDA

GPP_B10/I2C5_SCL/ISH_I2C2_SCL

GPU_PWREN 29

PCH_GPU_RST_N 29

GPPC_B23_SML1_ALERT_NI2C_PD_SOC_INT_N

GPP_D0/ISH_GP0

GPP_D1/ISH_GP1

GPP_D2/ISH_GP2

GPP_D3/ISH_GP3

GPP_D17/ISH_GP4

GPP_D18/ISH_GP5

GPP_E15/ISH_GP6

GPP_E16/ISH_GP7

DV33

DW33

CNVI_EN_N

DT33

DU33

SSD_RST_N

DK22

DW24

GPU_EVENT_N

DV24

DU24

BT_WAKE_N_SOC

CN43

CN42

CN41

CL43

CL41

CJ39

GPU_PWREN

DU36

PCH_GPU_RST_N_R

DV36

DW36

FB_GC6_EN_R

DT36

DU34

GPU_PWROK_R GPU_PWROK

DW34

DT14

DU14

CNVI_EN_N 43

SSD_RST_N 41

FB_GC6_EN_R 29

RU115 电阻_0R_0201_1/20W_J

RU116

+V3P3SX

GPU

BT_WAKE_N_SOC 43

ns

GPU

电阻_0R_0201_1/20W_J

RU111

电阻_10K_0201_1/20W_J

GPU_PG_Q

GPU_EVENT_N 29

GPU_PWROK 29,69

GPU_PG_Q 29

+V3P3SX

RU112

ns

电阻_4.7K_0201_1/20W_J

RU113

ns

+V3P3SX

RU117

ns

FLASH DESCRIPTOR SECURITY OVERRIDE

+V3P3A_PCH

RU118

+V3P3A_PCH

ns

ns

HDA_SDO_R EC_ME_UNLOCK

RU125

电阻_4.7K_0201_1/20W_J

EC_ME_UNLOCK 38

TOP SWAP OVERRIDE

GPPC_B_14_SPKR

0: Disable Top Swap mode. (Default)

1: Enable

Internal 20K PD

GPPC_B_14_SPKR

电阻_20K_0201_1/20W_J

GPPC_B18_GSPI0_MOSI

0: Disable No Reboot mode. (Default)

1: Enable

RU114

Internal 20K PD

ns

电阻_4.7K_0201_1/20W_J

GPPC_B18_GSPI0_MOSI

电阻_20K_0201_1/20W_J

HDA_SDO_R

0: SECURITY MEASURES NOT OVERRIDEN

1: OVERRIDEN

WEAK INTERNAL PD 20K

ns

电阻_4.7K_0201_1/20W_J

CPUNSSC CLOCK FREQ

RU123

电阻_4.7K_0201_1/20W_J

GPPC_B23_SML1_ALERT_N

RU124

电阻_20K_0201_1/20W_J

GPPC_B23_SML1_ALERT_N

0: 38.4MHZ CLOCK FROM DIRECT

CRYSTAL (DEFAULT)

1: 19.2MHZ CLOCK FROM DIVIDER

(DERIVED FROM 38.4MHZ CRYSTAL)

WEAK INTERNAL PD 20K

NO REBOOT

HDA_SDO_R

????UU1G

SSD1_DET_R

SD3_RCOMP

CE46

RIPQ_N_SOC

CC48

WAKE_PCIE_N_SOC_R

CC49

CAM_PWR_ON_SOC_R

CC47

CF45

TOUCHPAD_INT_N

CC45

CF49

CE47

DK38

DG38

SD3_RCOMP

CJ43

DG36

DG34

SNDW_RCOMP

CV38

GPP_G6/SD_CLK

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G0/SD_CMD

SD3.0

GPP_G7/SD_WP

GPP_G5/SD_CD_N

GPP_H0/CNV_BT_I2S_SDO

SNDW_RCOMP

ns

HDA_BCLK_RHDA_ BCLK

HDA_SYNC_RHDA_SYNC

HDA_SDO_RHDA_SDO

HDA_SDI

CNV_RF_RESET_N

CNV_MFUART2_RXD

CNV_MODEM_CLKREQ

电容_27pF_0201_C0G_25V_J

CU17

ns

B B

M.2_BT_PCMCLK43

A A

HDA_BCLK50

HDA_SYNC50

HDA_SDO50

HDA_SDI50

HDA_RST_N50

M.2_BT_PCMCLK SOC_BT_PCMCLK

电容_100nF_0201_X5R_6.3 V_M(±20%)

电阻_71.5K_0201_1/20_F(±1%)

CU169

RU127 电阻_33R_0201_1/20W_F

RU129 电阻_33R_0201_1/20W_F

RU131 电阻_33R_0201_1/20W_F RU132 电阻_0R_0201_1/20W_J

HDA_RST_N HDA_RST_N_R

RU133 电阻_33R_0201_1/20W_F

RU135

电阻_33R_0201_1/20W_F

PCH_DMIC2_CLK139

PCH_DMIC2_DATA139

CNV_MODEM_CLKREQ

CNV_RF_RESET_N

RU140

电阻_75K_0201_1/20 W_F(±1%)

RU139

CNV_RF_RESET_N43

CNV_MFUART2_RXD43

CNV_MODEM_CLKREQ43

Config to 1.8V level

RU138 电阻_33R_0201_1/20W_F

电容_27pF_0201_C0G_25V_J

CU16

ns

Close to CPU

5

4

CY46

GPP_R0/HDA_BCLK/I2S0_SCLK

CV49

GPP_R1/HDA_SYNC/I2S0_SFRM

CY47

GPP_R2/HDA_SDO/I2S0_TXD

CV45

GPP_R3/HDA_SDI0/I2S0_RXD

DA47

GPP_R4/HDA_RST_N

DP33

GPP_D19/I2S_MCLK

DC45

GPP_A23/I2S1_SCLK

DA49

GPP_R5/HDA_SDI1/I2S1_SFRM

DA45

GPP_R6/I2S1_TXD

DA48

GPP_R7/I2S1_RXD

CT49

GPP_A7/I2S2_SCLK

CT48

GPP_A8/I2S2_SFRM/CNV_RF_RESET_N

CV47

GPP_A10/I2S2_RXD

CT47

GPP_A9/I2S2_TXD/MODEM_CLKREQ

CY39

GPP_S0/SNDW1_CLK

CY38

GPP_S1/SNDW1_DATA

DB39

GPP_S2/SNDW2_CLK

DD38

GPP_S3/SNDW2_DATA

DF38

GPP_S4/SNDW3_CLK/DMIC_CLK1

DD39

GPP_S5/SNDW3_DATA/DMIC_DATA1

ICL_U_IP_EXT_WW20

HDA_SYNC_R

HDA_BCLK_R

HDA_SDO_R

HDA_RST_N_R

HDA_SDI

Close to CPU

GPP_H1/SD_PWR_EN_N/CNV_BT_I2S_SDO

GPP_S6/SNDW4_CLK/DMIC_CLK0

GPP_S7/SNDW4_DATA/DMIC_DATA0

AUDIO

7 of 19

CU18 电容_2pF_0201_C0G_25V_±0.25pF

ns

CU19 电容_2pF_0201_C0G_25V_±0.25pF

ns

CU20 电容_2pF_0201_C0G_25V_±0.25pF

ns

CU21 电容_2pF_0201_C0G_25V_±0.25pF

ns

CU22 电容_2pF_0201_C0G_25V_±0.25pF

ns

3

RU126 电阻_0R_0201_1/20W_J

RU130 电阻_0R_0201_1/20W_J

TOUCHPAD_INT_N 52

RU134 电阻_200R_0201_1/20W_F

RU136 电阻_33R_0201_1/20W_F

RU137

电容_27pF_0201_C0G_25V_J

CU14

ns

2

电阻_200R_0201_1/20W_F

SSD1_DET 11,41

RIPQ_N_SOC 36

WAKE_PCIE_N_SOC 8,43

CAM_PWR_ON_SOC 39

PCH_DMIC1_CLK0 39

电容_27pF_0201_C0G_25V_J

CU15

ns

PCH_DMIC1_DATA0 39

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Page name:

Page name:

Page name:

Size:

Size:

Size:

A4

A4

A4

Date: Sheet: of

Date: Sheet: of

Date: Sheet: of

Huaqin Telecom Technology Com.,Ltd.

ICL-U42(HDA/SD/ISH/GSPI)

ICL-U42(HDA/SD/ISH/GSPI)

ICL-U42(HDA/SD/ISH/GSPI)

Project

Project

Project

Name:

Name:

Name:

NB8511

NB8511

NB8511

Monday, July 15, 2019 10 72

Monday, July 15, 2019 10 72

Monday, July 15, 2019 10 72

1

REV:

REV:

REV:

V1.0

V1.0

V1.0

5

4

3

2

1

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB_ID

USB2_COMP

RSVD_BSCAN

????UU1H

USB3_P1_RX_DN

DJ8

USB3_P1_RX_DP

DJ6

USB3_P1_TX_DN

DJ2

USB3_P1_TX_DP

DJ1

DG9

DG7

DJ3

DJ5

DE7

DE9

DF3

DF5

DC7

DC9

DF2

DF1

PCIE_CRX_GTX_N0

DA6

PCIE_CRX_GTX_P0

DA7

PCIE_CTX_GRX_N0_C PCIE_CTX_GRX_N0

DE4

PCIE_CTX_GRX_P0_C

DE3

PCIE_CRX_GTX_N1

CY7

PCIE_CRX_GTX_P1

CY6

PCIE_CTX_GRX_N1_C PCIE_CTX_GRX_N1

DD1

PCIE_CTX_GRX_P1_C

DD2

USB2_P1_DN

DN8

USB2_P1_DP

DP8

DK11

DJ11

USB2_P3_TYPEC_DN

DP13

USB2_P3_TYPEC_DP

DN13

USB2_P4_DN

DK10

USB2_P4_DP

DJ10

USB2_P5_FP_DN

DL5

USB2_P5_FP_DP

DL3

USB_P7_CAM_N

DP11

USB_P7_CAM_P

DN11

DK13

DJ13

DN6

DP6

USB2_P9_TS_DN

DL2

USB2_P9_TS_DP

DL1

USB2_P10_BT_DN

DP10

USB2_P10_BT_DP

DN10

USB2_OTG_ID

DL6

USB2_VBUSSENSE

DL11

USB2_COMP

DN5

CD3

USB3_P1_RX_DN 49

USB3_P1_RX_DP 49

USB3_P1_TX_DN 49

USB3_P1_TX_DP 49

CU27 电容_220nF_0201_X5R_6.3V_M

CU28 电容_220nF_0201_X5R_6.3V_M

GPU

GPU

CU29 电容_220nF_0201_X5R_6.3V_M

CU30 电容_220nF_0201_X5R_6.3V_M

GPU

GPU

USB2_P1_DN 49

USB2_P1_DP 49

USB2_P3_TYPEC_DN 48

USB2_P3_TYPEC_DP 48

USB2_P4_DN 54

USB2_P4_DP 54

USB2_P5_FP_DN 52

USB2_P5_FP_DP 52

USB_P7_CAM_N 39

USB_P7_CAM_P 39

USB2_P9_TS_DN 39

USB2_P9_TS_DP 39

USB2_P10_BT_DN 43

USB2_P10_BT_DP 43

RU141

电阻_113R_0201_1/20 W_F(±1%)

USB3.0 TypeA 1 AUO

NA

NA

NA

PCIE_CTX_GRX_P0

PCIE_CTX_GRX_P1

USB3.0 Type-A 1 AUO

NA

Type-C

DB USB2.0 Type-A

Finger Print

Camera

NA

NA

Touch Panel

BT

USB2_COMP2 RESISTOR SHOULD

BE PLACED NEAR TO THE PIN

LENGHT <450 MILS

PCIE_CRX_GTX_N0 29

PCIE_CRX_GTX_P0 29

PCIE_CTX_GRX_N0 29

PCIE_CTX_GRX_P0 29

PCIE_CRX_GTX_N1 29

PCIE_CRX_GTX_P1 29

PCIE_CTX_GRX_N1 29

PCIE_CTX_GRX_P1 29

GPU

PCIE_CRX_GTX_N229

PCIE_CRX_GTX_P229

PCIE_CTX_GRX_N229

GPU

D D

PCIE_CTX_GRX_P229

PCIE_CRX_GTX_N329

PCIE_CRX_GTX_P329

PCIE_CTX_GRX_N329

PCIE_CTX_GRX_P329

PCIE_CRX_GTX_N2

PCIE_CRX_GTX_P2

PCIE_CTX_GRX_N2

PCIE_CTX_GRX_P2

PCIE_CRX_GTX_N3

PCIE_CRX_GTX_P3

PCIE_CTX_GRX_N3

PCIE_CTX_GRX_P3

CU23 电容_220nF_0201_X5R_6.3V_M

CU24 电容_220nF_0201_X5R_6.3V_M

GPU

GPU

CU25 电容_220nF_0201_X5R_6.3V_M

CU26 电容_220nF_0201_X5R_6.3V_M

GPU

GPU

PCIE_CTX_GRX_N2_C

PCIE_CTX_GRX_P2_C

PCIE_CTX_GRX_N3_C

PCIE_CTX_GRX_P3_C

NA

PCIE_WLAN_RX_DN43

WLAN

C C

SSD1

B B

PCIE_WLAN_RX_DP43

PCIE_WLAN_TX_DN43

PCIE_WLAN_TX_DP43

PCIE13_CRX_DTX_N41

PCIE13_CRX_DTX_P41

PCIE13_CTX_DRX_N41

PCIE13_CTX_DRX_P41

PCIE14_CRX_DTX_N41

PCIE14_CRX_DTX_P41

PCIE14_CTX_DRX_N41

PCIE14_CTX_DRX_P41

PCIE15_CRX_DTX_N41

PCIE15_CRX_DTX_P41

PCIE15_CTX_DRX_N41

PCIE15_CTX_DRX_P41

PCIE16_SATA_CRX_DTX_N41

PCIE16_SATA_CRX_DTX_P41

PCIE16_SATA_CTX_DRX_N41

PCIE16_SATA_CTX_DRX_P41

RU142

电阻_100R_0201_1/20W_F

PCIE_WLAN_RX_DN

PCIE_WLAN_RX_DP

PCIE_WLAN_TX_DN

PCIE_WLAN_TX_DP

PCIE13_CRX_DTX_N

PCIE13_CRX_DTX_P

PCIE13_CTX_DRX_N

PCIE13_CTX_DRX_P

PCIE14_CRX_DTX_N

PCIE14_CRX_DTX_P

PCIE14_CTX_DRX_N

PCIE14_CTX_DRX_P

PCIE15_CRX_DTX_N

PCIE15_CRX_DTX_P

PCIE15_CTX_DRX_N

PCIE15_CTX_DRX_P

PCIE16_SATA_CRX_DTX_N

PCIE16_SATA_CRX_DTX_P

PCIE16_SATA_CTX_DRX_N

PCIE16_SATA_CTX_DRX_P

SSD1_DET10,41

USB_OC049

USB_OC354

SATA1_DEVSLP41

PCIE_RCOMP_N

PCIE_RCOMP_P

SSD1_DET

USB_OC0

USB_OC3

SATA1_DEVSLP

CV7

PCIE7_RXN

CV6

PCIE7_RXP

DD3

PCIE7_TXN

DD5

PCIE7_TXP

CT6

PCIE8_RXN

CT7

PCIE8_RXP

DA3

PCIE8_TXN

DA5

PCIE8_TXP

CP7

PCIE9_RXN

CP6

PCIE9_RXP

DA2

PCIE9_TXN

DA1

PCIE9_TXP

CM7

PCIE10_RXN

CM6

PCIE10_RXP

CY3

PCIE10_TXN

CY4

PCIE10_TXP

CK7

PCIE11_RXN/SATA0_RXN

CK6

PCIE11_RXP/SATA0_RXP

CW2

PCIE11_TXN/SATA0_TXN

CW1

PCIE11_TXP/SATA0_TXP

CJ6

PCIE12_RXN/SATA1A_RXN

CJ7

PCIE12_RXP/SATA1A_RXP

CW5

PCIE12_TXN/SATA1A_TXN

CW3

PCIE12_TXP/SATA1A_TXP

CG7

PCIE13_RXN

CG6

PCIE13_RXP

CT3

PCIE13_TXN

CT5

PCIE13_TXP

CE6

PCIE14_RXN

CE7

PCIE14_RXP

CT2

PCIE14_TXN

CT1

PCIE14_TXP

CC5

PCIE15_RXN/SATA1B_RXN

CC6

PCIE15_RXP/SATA1B_RXP

CR3

PCIE15_TXN/SATA1B_TXN

CR4

PCIE15_TXP/SATA1B_TXP

CA6

PCIE16_RXN/SATA2_RXN

CA5

PCIE16_RXP/SATA2_RXP

CP1

PCIE16_TXN/SATA2_TXN

CP2

PCIE16_TXP/SATA2_TXP

DW12

GPP_E0/SATAXPCIE0/SATAGP0

CR42

GPP_A12/SATAXPCIE1/SATAGP1

CR43

GPP_A13/SATAXPCIE2/SATAGP2

DW14

GPP_E9/USB_OC0_N

CT43

GPP_A16/USB_OC3_N

DU12

GPP_E4/DEVSLP0

DU11

GPP_E5/DEVSLP1

CV48

GPP_A11/DEVSLP2

DT38

GPP_H12/M2_SKT2_CFG0

DW38

GPP_H13/M2_SKT2_CFG1

DV38

GPP_H14/M2_SKT2_CFG2

DU38

GPP_H15/M2_SKT2_CFG3

DN1

PCIE_RCOMPN

DN3

PCIE_RCOMPP

ICL_U_IP_EXT_WW20

8 of 19

PCIE1_RXN/USB31_1_RXN

PCIE1_RXP/USB31_1_RXP

PCIE1_TXN/USB31_1_TXN

PCIE1_TXP/USB31_1_TXP

PCIE2_RXN/USB31_2_RXN

PCIE2_RXP/USB31_2_RXP

PCIE2_TXN/USB31_2_TXN

PCIE2_TXP/USB31_2_TXP

PCIE3_RXN/USB31_3_RXN

PCIE3_RXP/USB31_3_RXP

PCIE3_TXN/USB31_3_TXN

PCIE3_TXP/USB31_3_TXP

PCIE4_RXN/USB31_4_RXN

PCIE4_RXP/USB31_4_RXP

PCIE4_TXN/USB31_4_TXN

PCIE4_TXP/USB31_4_TXP

PCIE5_RXN/USB31_5_RXN

PCIE5_RXP/USB31_5_RXP

PCIE5_TXN/USB31_5_TXN

PCIE5_TXP/USB31_5_TXP

PCIE6_RXN/USB31_6_RXN

PCIE6_RXP/USB31_6_RXP

PCIE6_TXN/USB31_6_TXN

PCIE6_TXP/USB31_6_TXP

USB_VBUSSENSE

PCH STRAP

+V3P3A_PCH

电阻_10K_0201_1/20W_J

RU144

USB_OC3

A A

5

RING OSCILLATOR BYPASS

+V3P3A_PCH

电阻_20K_0201_1/20W_J

RU145

USB_OC0

电阻_4.7K_0201_1/20W_J

RU150

ns

USB_OC0

0: RING OSCILLATOR

1: BYPASS MODE ENABLED

(QUALIFIED BY DFXTESTMODE)

NO INTERNAL PU/PD

4

USB2_OTG_ID

USB2_VBUSSENSE

电阻

电阻

_10K_0201_1/20W_J

_10K_0201_1/20W_J

RU146

RU147

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Page name:

Page name:

Page name:

Size:

Size:

Size:

A4

A4

A4

Date: Sheet: of

Date: Sheet: of

Date: Sheet: of

3

2

Huaqin Telecom Technology Com.,Ltd.

ICL-U42(USB/PCIE)

ICL-U42(USB/PCIE)

ICL-U42(USB/PCIE)

Project

Project

Project

Name:

Name:

Name:

NB8511

NB8511

NB8511

Monday, July 15, 2019 11 72

Monday, July 15, 2019 11 72

Monday, July 15, 2019 11 72

1

REV:

REV:

REV:

V1.0

V1.0

V1.0

5

RU152

DSW_PWROK_EC38,57

D D

SLP_SUS_N63

SLP_S5_N45

SLP_S4_N38,64

SLP_S3_N38,68

SLP_S0_N38,68

+VCCRTC

RU156

ns

电阻_1M_0201_1/20W_J

电阻_10K_0201_1/20W_J

RU225

C C

SLP_WLAN_N43

CU31

ns

电容_100nF_0201_16 V_M(±20%)

电阻_0R_0201_1/20W_J

TPU1320MIL

TPU1420MIL

TPU1520MIL

TPU1820MIL

TPU1720MIL

TPU2020MIL

TPU2220MIL

RSMRST_N_EC8,38,57

PCH_PWROK38,57

SYS_PWROK38

DSW_PWROKDSW_PWROK_EC

1

ns

1

ns

1

ns

1

ns

SLP_SUS_N

SLP_S5_N

SLP_S4_N

SLP_S3_N

SLP_A_N

1

ns

SLP_S0_N

1

ns

SLP_WLAN_N

SLP_LAN_N

1

ns

RSMRST_N_EC

PM_SYSRST_N

PLT_RST_SOC_N

DSW_PWROK

PCH_PWROK

SYS_PWROK

INPUT3VSEL

SM_INTRUDER_N

BY DEFAULT 3.3V FLASH SUPPORT.

FOR 1.8V FLASH OPERATION UNSTUFF CH23

4

DM49

SLP_SUS_N

DF45

GPD10/SLP_S5_N

DC48

GPD5/SLP_S4_N

DF47

GPD4/SLP_S3_N

DH47

GPD6/SLP_A_N

CL45

GPP_B12/SLP_S0_N

DE49

GPD9/SLP_WLAN_N

DN48

SLP_LAN_N

DG49

RSMRST_N

DK19

SYS_RESET_N

CM49

GPP_B13/PLTRST_N

DR48

DSW_PWROK

DN47

PCH_PWROK

DP19

SYS_PWROK

DN49

INPUT3VSEL

DR47

INTRUDER_N

ICL_U_IP_EXT_WW20

<Option>

DSW_PWROK

电容_4.7nF_0201_X7R_10v_K

GPP_H3/SX_EXIT_HOLDOFF_N/CNV_BT_I2S_SDO

CU170

GPP_H18/CPU_C10_GATE_N

GPD11/LANPHYPC/DSWLDO_MON

VCCSTPWRGOOD_TCSS

11 of 19

GPD3/PWRBTN_N

GPD1/ACPRESENT

GPD0/BATLOW_N

GPP_B11/PMCALERT

WAKE_N

GPD_2/LAN_WAKE_N

VCCST_OVERRIDE

VCCST_PWRGD

PROCPWRGD

GPD7

3

I2C_PD_SOC_INT_N_R I2C_PD_SOC_INT_N

????UU1K

PM_PWRBTN_R_N

CY42

PM_AC_PRESENT

DE46

PM_BATLOW_N

DH48

I2C_PD_SOC_INT_N_R

CL39

CPU_C10_GATE_N

DU40

DG40

WAKE_PCH_N

DL45

LAN_WAKE_N

DE47

DF48

GPD11

VCCST_OVERRIDE

CE4

H_VCCST_PWRGD

CF2

VCCSTPWRGOOD_TCSS VCCST_OVERRIDE

CE3

CF1

PROCPWRGD

TCP_RETIMER_PERST_N

DC47

RU151

电阻_0R_0201_1/20W_J

1

ns

TPU16 20MIL

PM_PWRBTN_R_N 38

PM_AC_PRESENT 38

CPU_C10_GATE_N 38,68

1

ns

TPU21 20MIL

1

ns

TPU23 20MIL

VCCST_OVERRIDE 68

RU157 电阻_0R_0201_1/20W_J

1

ns

TPU24 20MIL

TCP_RETIMER_PERST_N 45

CU32 电容_4.7nF_0201_X7R_10v_K

RU160

PROCPWRGD

ns

电阻_100K_0201_1/20W_J

2

I2C_PD_SOC_INT_N 10,44

+V3P3A

电阻_4.7K_0201_1/20W_J

RU155

WAKE_PCH_N 43

1

PCH STRAP

3V SELECT STRAP

+V3P3A_PCH

+V3P3A_PCH

LOW-> 3.3V +/-5%

HIGH->3.0V +/-5%

RU154

ns

电阻_4.7K_0201_1/20W_J

INPUT3VSEL

RU153

电阻_100K_0201_1/20W_J

XTAL INPUT MODE

GPD7(TCP_RETIMER_PERST_N)

0: XTAL IS ATTACHED

1: XTAL INPUT IS SINGLE ENDED

Internal 20K PD

RU158

ns

电阻_4.7K_0201_1/20W_J

TCP_RETIMER_PERST_N

RU159

电阻_20K_0201_1/20W_J

ns

+V3P3A

UU2

ns

1

NC

PLT_RST_SOC_N

B B

电阻_100K_0201_1/20W_J

RU165

2

A

GND3Y

74AUP1G07GW

VCC

CU33

5

4

电阻_0R_0201_1/20W_J

ns

电容_100nF_0201_X5R_6.3 V_M(±20%)

RU163

ns

电阻_0R_0201_1/20W_J

RU167

+V3P3A

RU161

电阻_2.2K_0201_1/20 W_J(±5%)

ns

CU34

ns

电容_100pF_0201_C0G_50V_J

PLT_RST_N

PLT_RST_N 29,36,41,43,45

EC_VCCST_PWRGD38

EC_VCCST_PWRGD

RU166

DU1

ns

LRB500V-40T1G

电阻_0R_0201_1/20W_J

+V1P0S_VCCST

RU162

电阻_1K_0201_1/20W_J

RU164

电阻_60.4R_0201_1/20_F(±1%)

CU35

电容_100pF_0201_C0G_50V_J

H_VCCST_PWRGD

BUFFER TO REDUCE LOADING ON PLT_RST_N

+V3P3A_PCH

+V3P3A_PCH

RU171 电阻_10K_0201_1/20W_J

RU172 电阻_1K_0201_1/20W_J

A A

5

PM_SYSRST_N

LAN_WAKE_N

SYS_PWROK

PCH_PWROK

RSMRST_N_EC

SLP_WLAN_N

SLP_S3_N

SLP_S4_N

SLP_S5_N

VCCST_OVERRIDE

+V3P3SX

RU173 电阻_100K_0201_1/20W_J

CU36 电容_100pF_0201_C0G_50V_J

RU175 电阻_100K_0201_1/20W_J

CU38 电容_2.2nF_0201_X5R_25V_K

RU176 电阻_100K_0201_1/20W_J

CU39 电容_100pF_0201_C0G_50V_J

RU177 电阻_100K_0201_1/20W_J

RU178 电阻_100K_0201_1/20W_J

RU179 电阻_100K_0201_1/20W_J

RU180 电阻_100K_0201_1/20W_J

RU181 电阻_100K_0201_1/20W_J

RU169 电阻_100K_0201_1/20W_J

RU170 电阻_100K_0201_1/20W_J

RU226 电阻_100K_0201_1/20W_J

ns

RU227 电阻_100K_0201_1/20W_J

ns

ns

ns

ns

4

SLP_S0_N

PM_BATLOW_N

CPU_C10_GATE_N

RTC

RTC_VCC

+VCCRTC

(Max=3.3 V)

CU37

电容_1uF_0201_X5R_6.3V_M

3

DU2

3

+VCC3P3_LDO_OUT

2

LRC LBAT54CWT1

1

2

RU174

电阻_1K_0201_1/20W_J

RTC_VCC

FOR product line

1

ns

TP188 40 MIL

1

ns

TP190 40 MIL

JRTCU1

3

MTG1

1

1

2

2

4

MTG2

50278-00201-001

Huaqin Telecom Technology Com.,Ltd.

Huaqin Telecom Technology Com.,Ltd.

Page name:

Page name:

Page name:

Size:

Size:

Size:

A4

A4

A4

Date: Sheet: of

Date: Sheet: of

Date: Sheet: of

Huaqin Telecom Technology Com.,Ltd.

ICL-U42(PMU)

ICL-U42(PMU)

ICL-U42(PMU)

Project

Project

Project

Name:

Name:

Name:

NB8511

NB8511

NB8511

Monday, July 15, 2019 12 72

Monday, July 15, 2019 12 72

Monday, July 15, 2019 12 72

1

REV:

REV:

REV:

V1.0

V1.0

V1.0

5

+VCCIN +VCCIN

A19

VCCIN_1

AC12

VCCIN_2

V13

VCCIN_3

W12

VCCIN_4

Y13

VCCIN_5

K29

VCCIN_6

D D

C C

B B

VCCIN_VIDALERT_N_R

VCCIN_VIDSCK_R

VCCIN_VIDSOUT_R

K31

VCCIN_7

B19

VCCIN_8

B23

VCCIN_9

B27

VCCIN_10

B29

VCCIN_11

BN10

VCCIN_12

BP11

VCCIN_13

BP9

VCCIN_14

BR10

VCCIN_15

BT11

VCCIN_16

A21

VCCIN_17

BT9

VCCIN_18

BU10

VCCIN_19

BV36

VCCIN_20

BV9

VCCIN_21

BW10

VCCIN_22

BW36

VCCIN_23

BW9

VCCIN_24

BY10

VCCIN_25

C19

VCCIN_26

C23

VCCIN_27

A23

VCCIN_28

C27

VCCIN_29

C29

VCCIN_30

CA36

VCCIN_31

CA9

VCCIN_32

CB10

VCCIN_33

CC11

VCCIN_34

CC36

VCCIN_35

CC9

VCCIN_36

CD10

VCCIN_37

CE11

VCCIN_38

A24

VCCIN_39

CE34

VCCIN_40

CE35

VCCIN_41

CF10

VCCIN_42

CF33

VCCIN_43

CG11

VCCIN_44

CG34

VCCIN_45

CG35

VCCIN_46

CH10

VCCIN_47

J30

VCCIN_48

CJ11

VCCIN_49

A27

VCCIN_50

CJ34

VCCIN_51

H1

VIDALERT

H2

VIDSCK

H3

VIDSOUT

ICL_U_IP_EXT_WW20

12 of 19

4

VCCIN_52

VCCIN_53

VCCIN_54

VCCIN_55

VCCIN_56

VCCIN_57

VCCIN_58

VCCIN_59

VCCIN_60

VCCIN_61

VCCIN_62

VCCIN_63

VCCIN_64

VCCIN_65

VCCIN_66

VCCIN_67

VCCIN_68

VCCIN_69

VCCIN_70

VCCIN_71

VCCIN_72

VCCIN_73

VCCIN_74

VCCIN_75

VCCIN_76

VCCIN_77

VCCIN_78

VCCIN_79

VCCIN_80

VCCIN_81

VCCIN_82

VCCIN_83

VCCIN_84

VCCIN_85

VCCIN_86

VCCIN_87

VCCIN_88

VCCIN_89

VCCIN_90

VCCIN_91

VCCIN_92

VCCIN_93

VCCIN_94

VCCIN_95

VCCIN_96

VCCIN_97

VCCIN_98

VCCIN_99

VCCIN_100

VCCIN_101

VCCIN_102

VCCIN_103

VCCIN_104

VCCIN_SENSE

VSSIN_SENSE

3

????UU1L

CJ35

CK10

J32

CL34