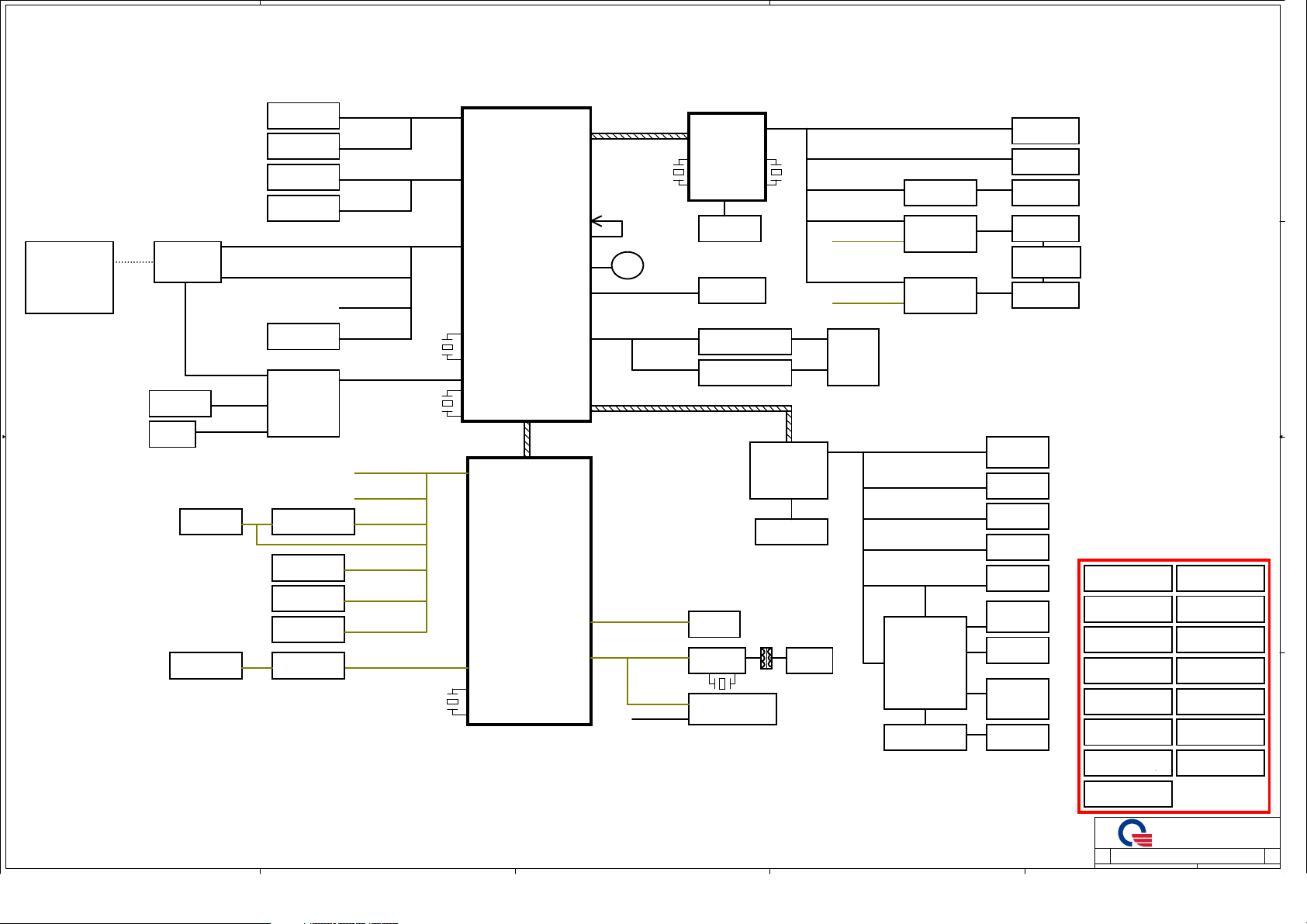

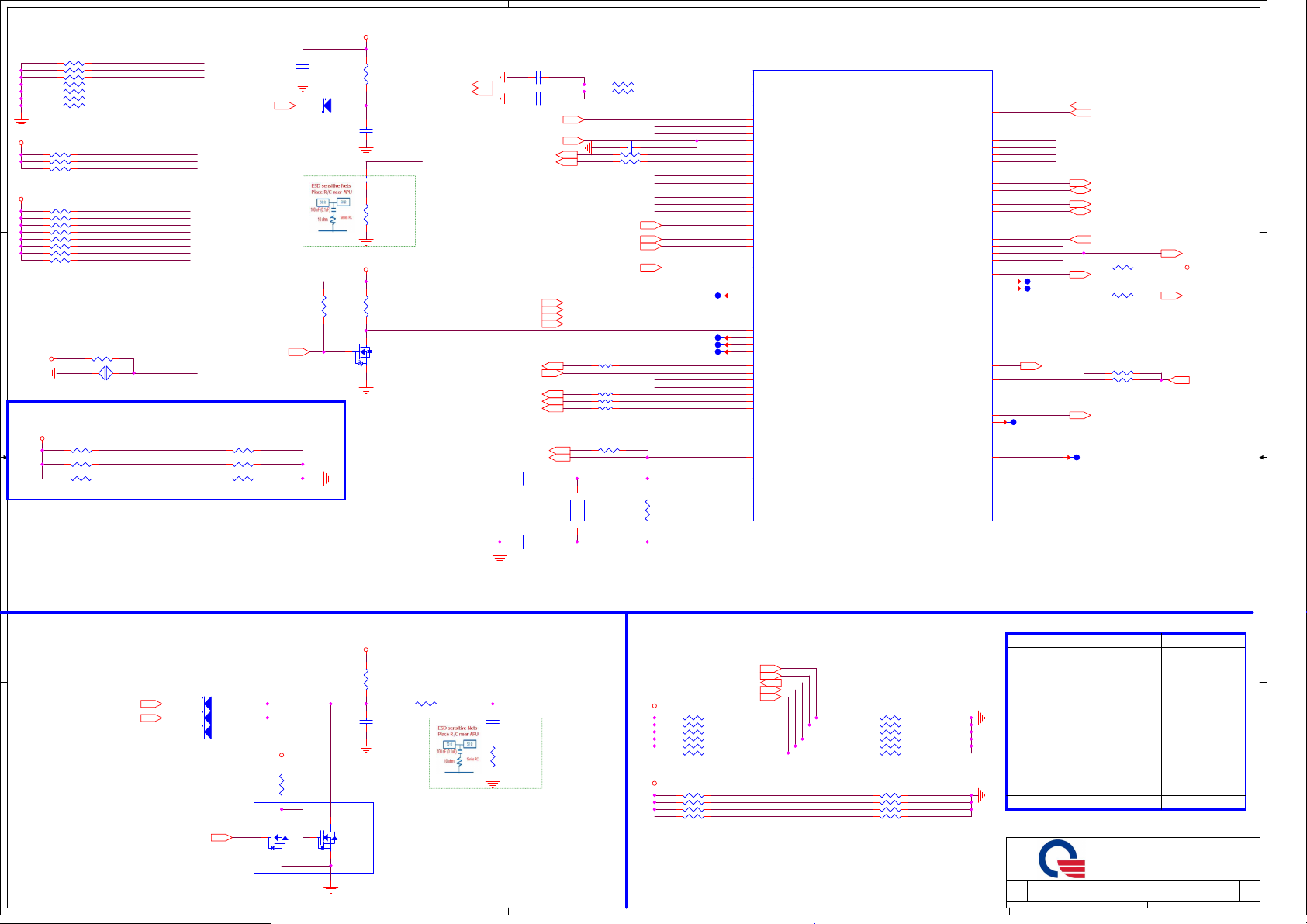

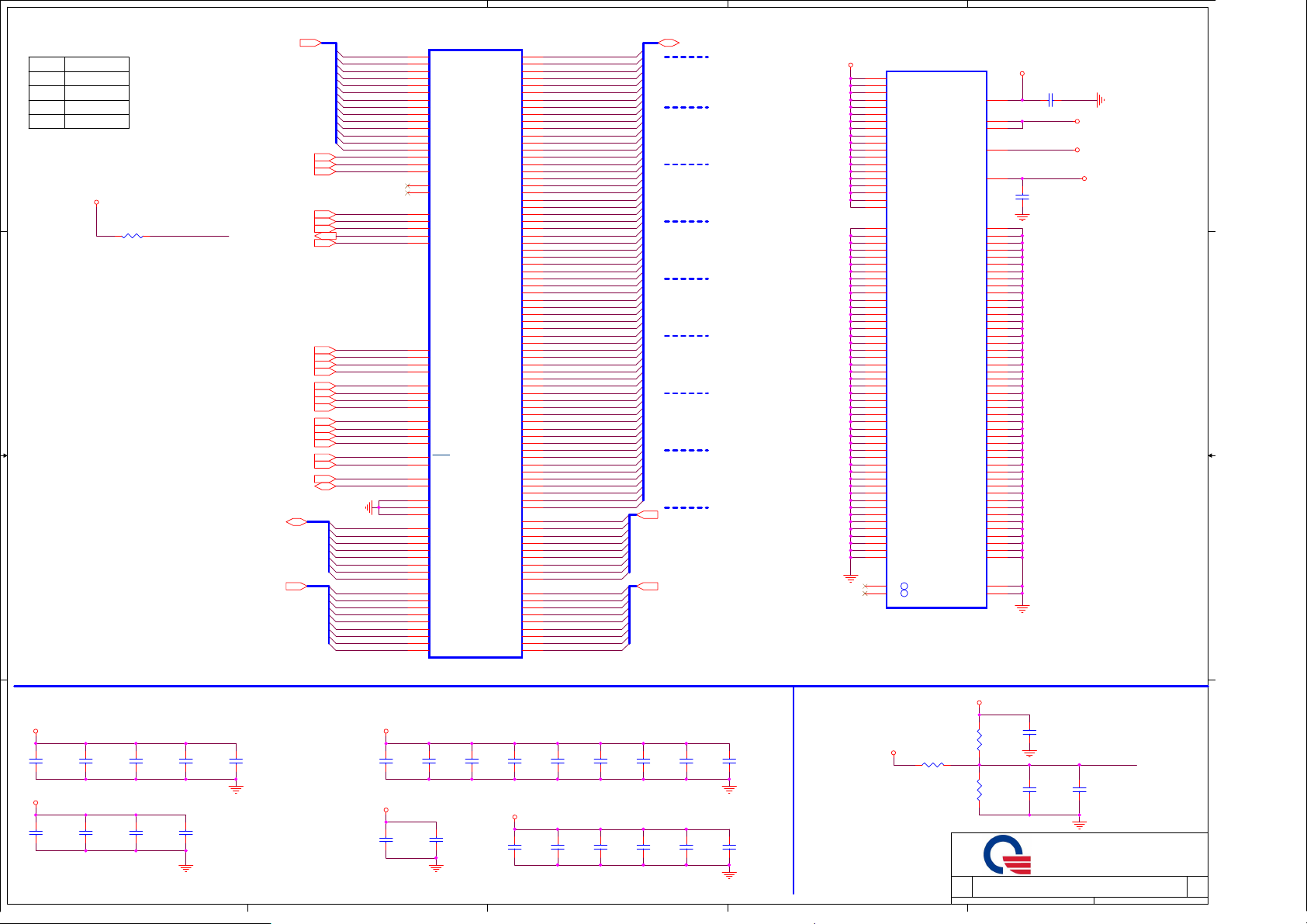

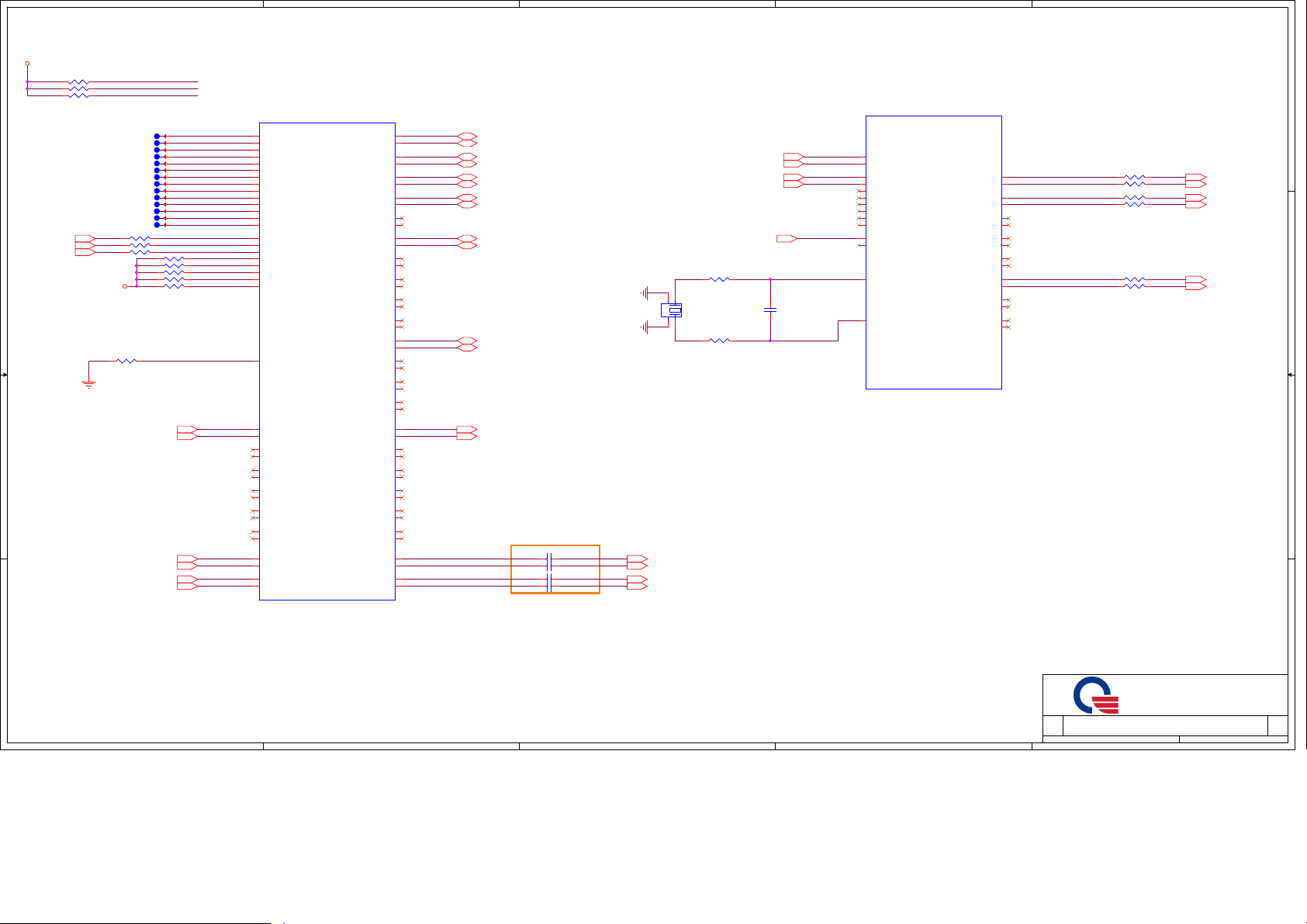

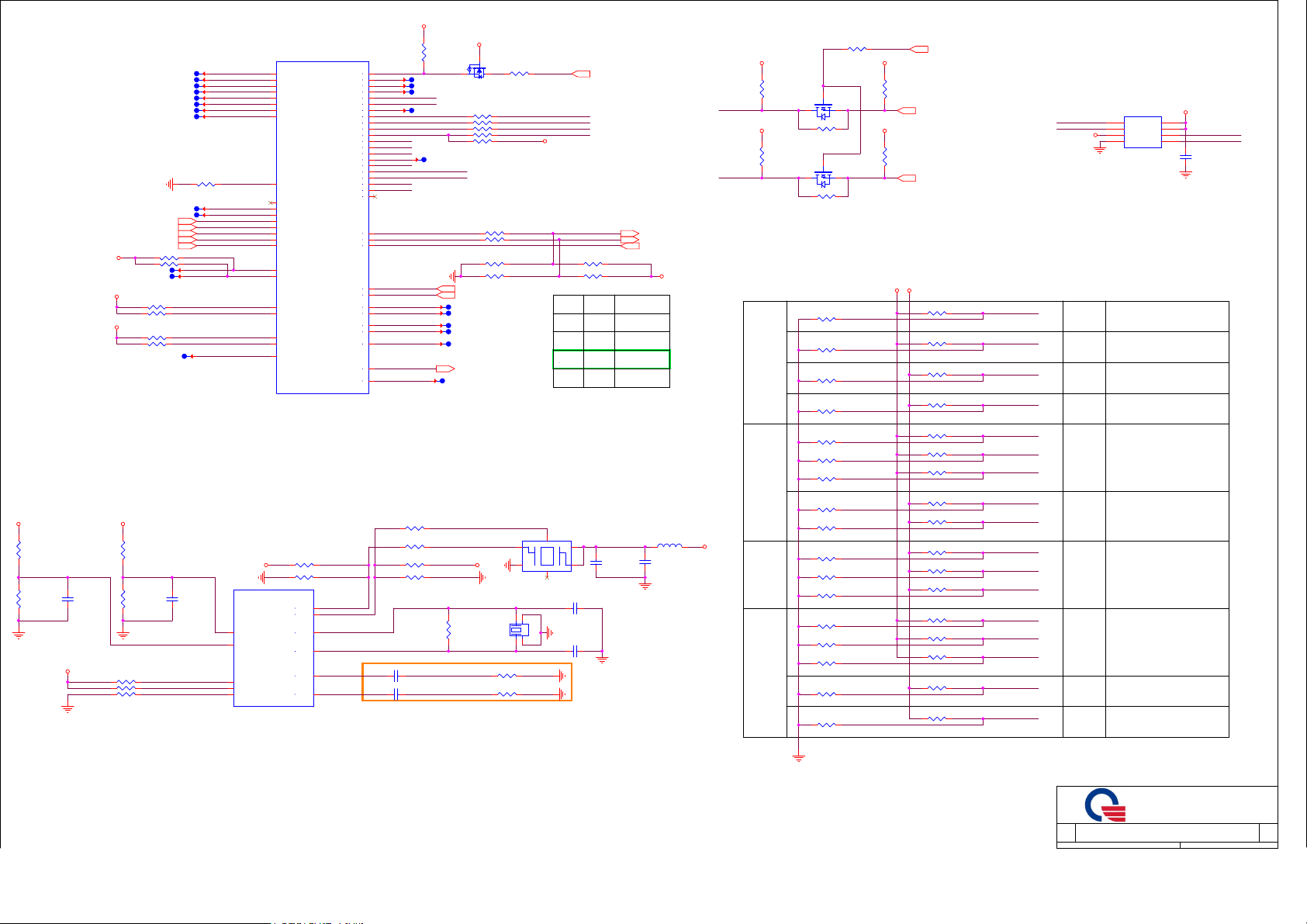

Acer Predator PH517-61 Schematic

5

4

3

2

1

ZGX System Block Diagram

1 of 2/CH (xR-0) : SR(2667), DR(2400-2667) MT/s

2 of 2/CH (1R-1R) : 2133-2400 MT/s

2 of 2/CH (2R-xR) : 1866-2133 MT/s

X'TAL

48MHz

X'TAL

32.768 kHz

CHA

Memory

CHB

USB

Azalia

HDA

USB

AMD Promontory

SATA

X'TAL

25MHz

AMD APU

Raven Ridge

17H(10h-1Fh)

Summit Ridge

17H(00h-0Fh)

Pinnacle Ridge

P2,3,4,5,6,7,8

PCIe (GPP)

/SATA

AM4 Socketu

BGA-1331

PCIe(HUB)

PCIe x4 (GEN3)

PROM 2/4

(400 series)

SATA Express

P13,14,15

uBGA-583

PEG *16 (Summit)

PEG *8 (Raven)

PEG

CLK

RTC

SPI

LPC

SPI

SATA Express(GEN3) 0~1

PCIe

BATT

P7

GPP(GEN3) 0~3

SATA(GEN3) 1

PCIe (GEN2) -0

CIe (GEN2) -1

P

USB2 - 2

AMD GPU

X'TAL

100 MHz

M.2

SSD-2

LAN

Killer E2500

X'TAL

25 MHz

M.2

WLAN+BT w/ Debug

Vega 10

Vega 11

P16,17,18,19,20

SPI ROM 512K

P18

3.3 V

SPI ROM 16MB

P6

1.8 V

PCIE Re-driver *2

PS8559BQFN40GTR

PCIE CLK Re-driver

PI6CEQ20200LIEX

SPI ROM 128 KB

3.3 V P41

P29

P33

P30

DP

X'TAL

27 MHz

P28

P28

EC

IT8987E/BX

RJ45 Con.

DPA

DPB

DPC

DPD

USB2 - 5

USB3.1 (GEN2) - 0

DPE

USB2 - 0

USB3.1 (GEN2) - 1

M.2

SSD-1

P41

P33

P28

eDP Re-driver

TUSB546

Type-C MUX

+Re-driver

TUSB1046

Type-C MUX

+Re-driver

TUSB1046

MCU

ENE 6K5130

PWM IC for LED

P2501NHC0

P37

P37

P23

P27

P27

PS/2

I2C-0

HDMI 2.0 Con.

DP Con.

eDP Con.

Type-C Con.

With PD+DP

USB TYPE-C PD

CYPRESS CCG4

CYPD4225-40LQXIT

Type-C Con.

With PD+DP

Daughter Board

Power LED

Battery LED

HDD LED

Thermal Seneor

CPU/GPU FAN

(PWM)

Plastic KB

Touch Pad

Con.

Daughter Board

Macro Key

(LED)

BASE B/L

Daughter Board

Power Button

(LED)

HALL Seneor

KBL

SUB@ SubWoofer

*Tobii@ Tobii

P21

P22

P24

P26,27

P25

P26,27

P40

P36

P36

P38

P39

P37

P37

P40

P37

P-KB@ Plastic Keyboard

*M-KB@ Metal Keyboard

Macro@ Macro Key

*XBOX@ XBOX

*LVPECL@ LVPECL XTAL

SP@ Special part

SR@ Summit

EV@ GPU

TYPE-C@ Type C solution

*ID2@ BASE KBL

*P_BAT@ Battery onnector

*HDT@ AMD Debug

*DBG@ Debug CARD

*PCIE@ PCIE SSD

*SATA@ SATA SSD

*UHD@ Battery Vin boost

N-UHD@ nun-Battery Vin boost

*CLKR@ CLK redriver

N-CLKR@ non-CLK redriver

DS@ HDD Device Sleep

*NDS@ non-HDD Device Sleep

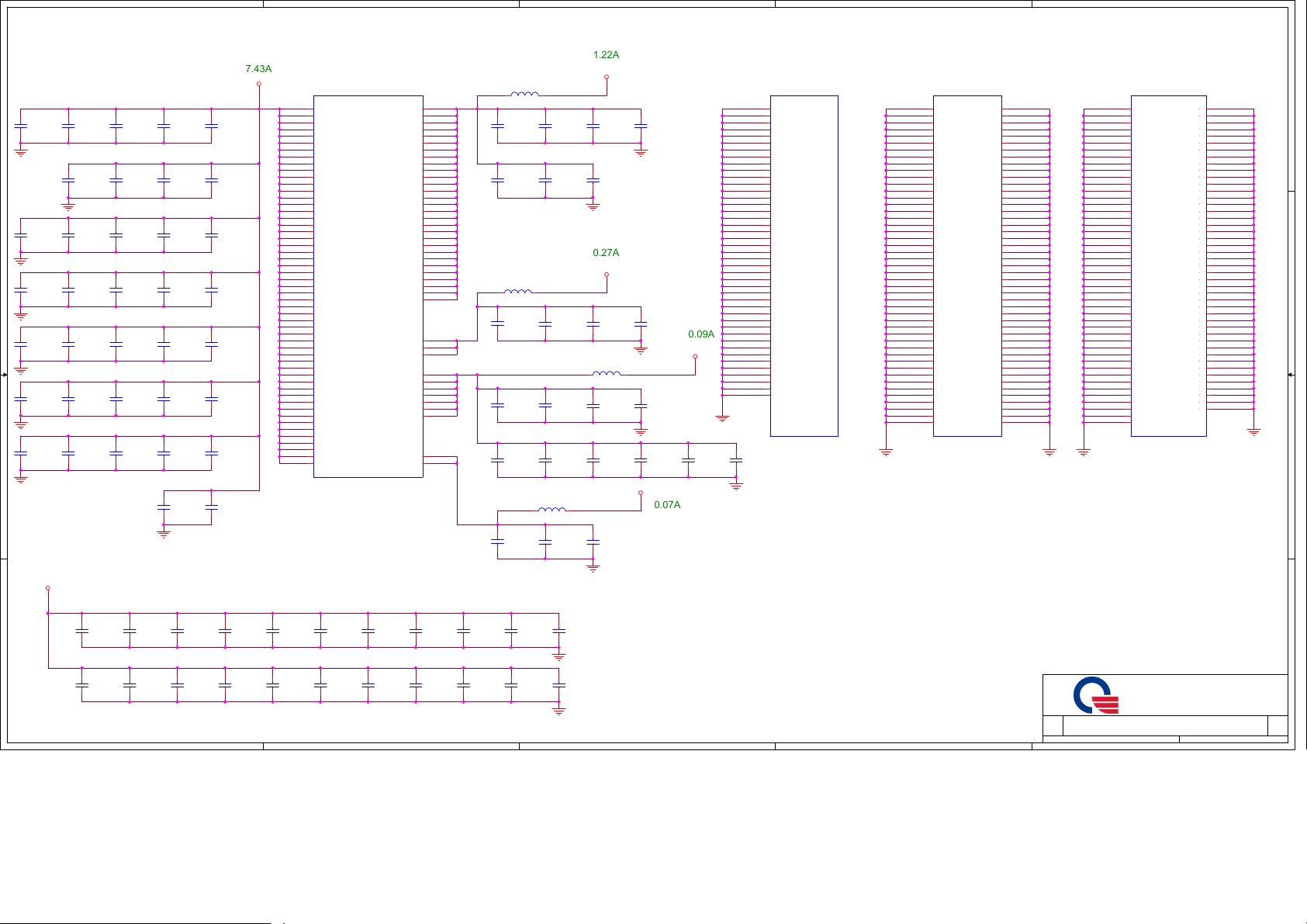

Power source

BQ24780S

Batery Charger

TPS51225R

3V/5V/+3V_GFX

G5335QT2U

+1.05V_PCH_S5

AOZ2263QI-18

+VDDP_S5

RT8231B

DDR4_+1.2VSUS

MP2853GU (6+2)

VCORE

G5335QT2U

+1.8V_S5

TPS61087

+12V_FAN

P42

P43

P44

P45

P46

P47,48

P49

P50

TPS61087

+12V_PANEL

NCP81022

+VGPU_CORE

NCP302045

+VDD_GFX

G5335QT2U

+VDDCI_GFX

G5335QT2U

+0.8V_GFX

AOZ1331DI

+1.8V_GFX & Thermal

M5671RE1U

+VPP_GFX & PCC

D D

DDR4 SO-DIMM

RVS

DDR4 SO-DIMM

STD

DDR4 SO-DIMM

RVS

DDR4 SO-DIMM

RVS

Daughter Board

USB3.0 redriver

Headphone AMP

USB3 Con. *2

HP Con. *1

MIC Con. *1

PTN36002

SV3H715+SV3S700A

C C

FFC

I/O Board Con.

P40

XBOX

Channel A0

P9

Channel A1

P10

Channel B0

P11

Channel B1

P12

USB2 - 0

USB3.0 (GEN1) - 0

USB2 - 1

USB3.0 (GEN1) - 1

USB2 - 2

(BT)

USB2 - 3

P36

AUDIO CODEC

SubWoofer

P32

ALC1006

DMIC

P24

USB3 Con.

B B

HDD (cable tpye)

A A

ALC299

P35

P34

P31

(Type-C)

(Type-C)

USB Charger

TPS2544RTER

Metal Keyboard

CCD

Tobii

PS8527B

P35

P38

P24

P36

P34

USB2 - 5

USB3.1 (GEN2) - 0

USB2 - 0

USB3.1 (GEN2) - 1

USB2 - 10

USB3.0 (GEN1) - 0

USB2 - 1

USB2 - 2

USB2 - 3

SATA (GEN3) - 0SATA Re-driver

01

P51

P52,53,54

P55

P56

P57

P58

P59

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

ZGX

PROJECT :

ZGX

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Block Diagram

Block Diagram

Block Diagram

Date: Sheet of

Tuesday, June 26, 2018

Date: Sheet of

Tuesday, June 26, 2018

Date: Sheet of

5

4

3

2

Tuesday, June 26, 2018

1

ZGX

1 59

1 59

1 59

1A

1A

1A

5

4

3

2

1

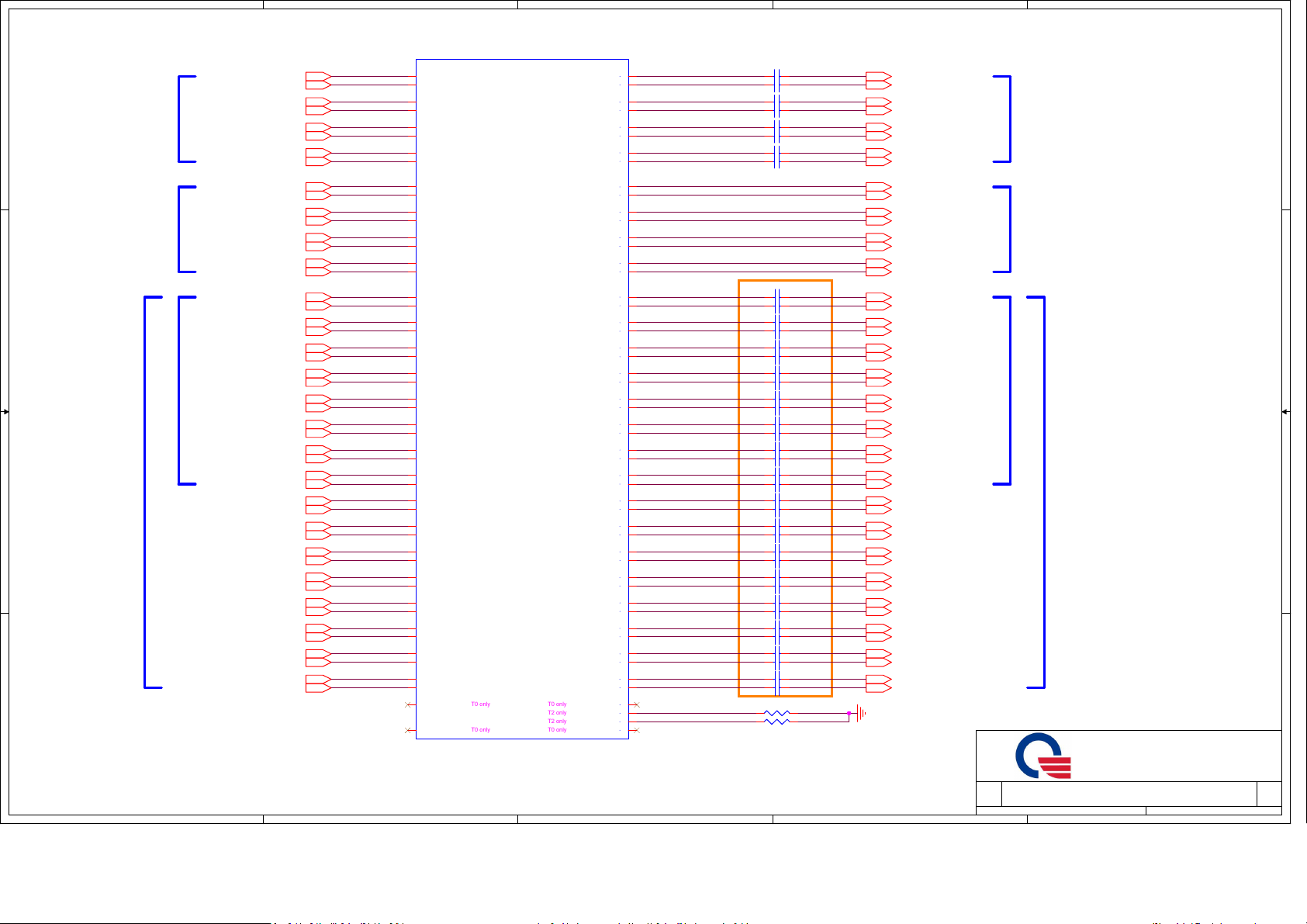

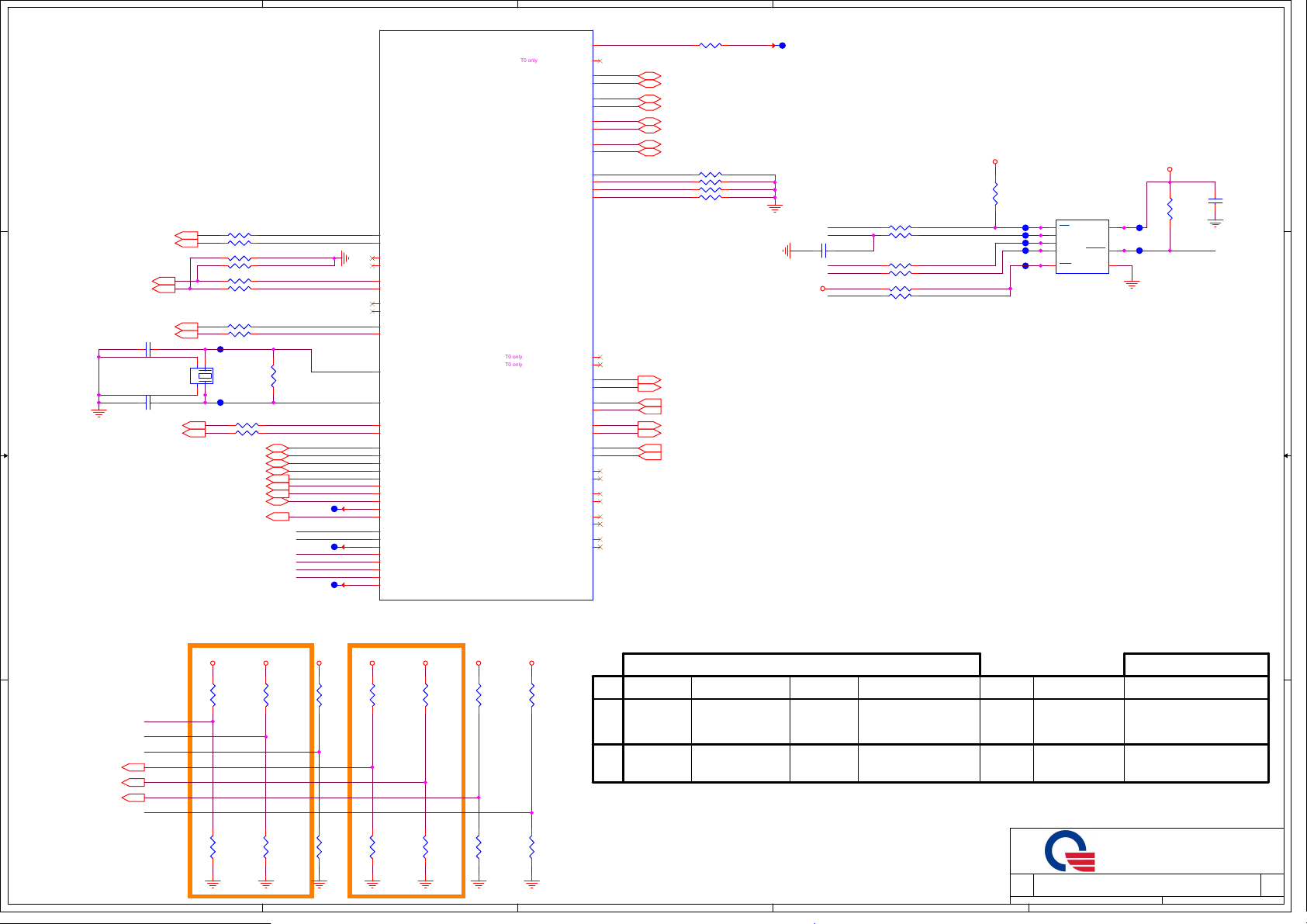

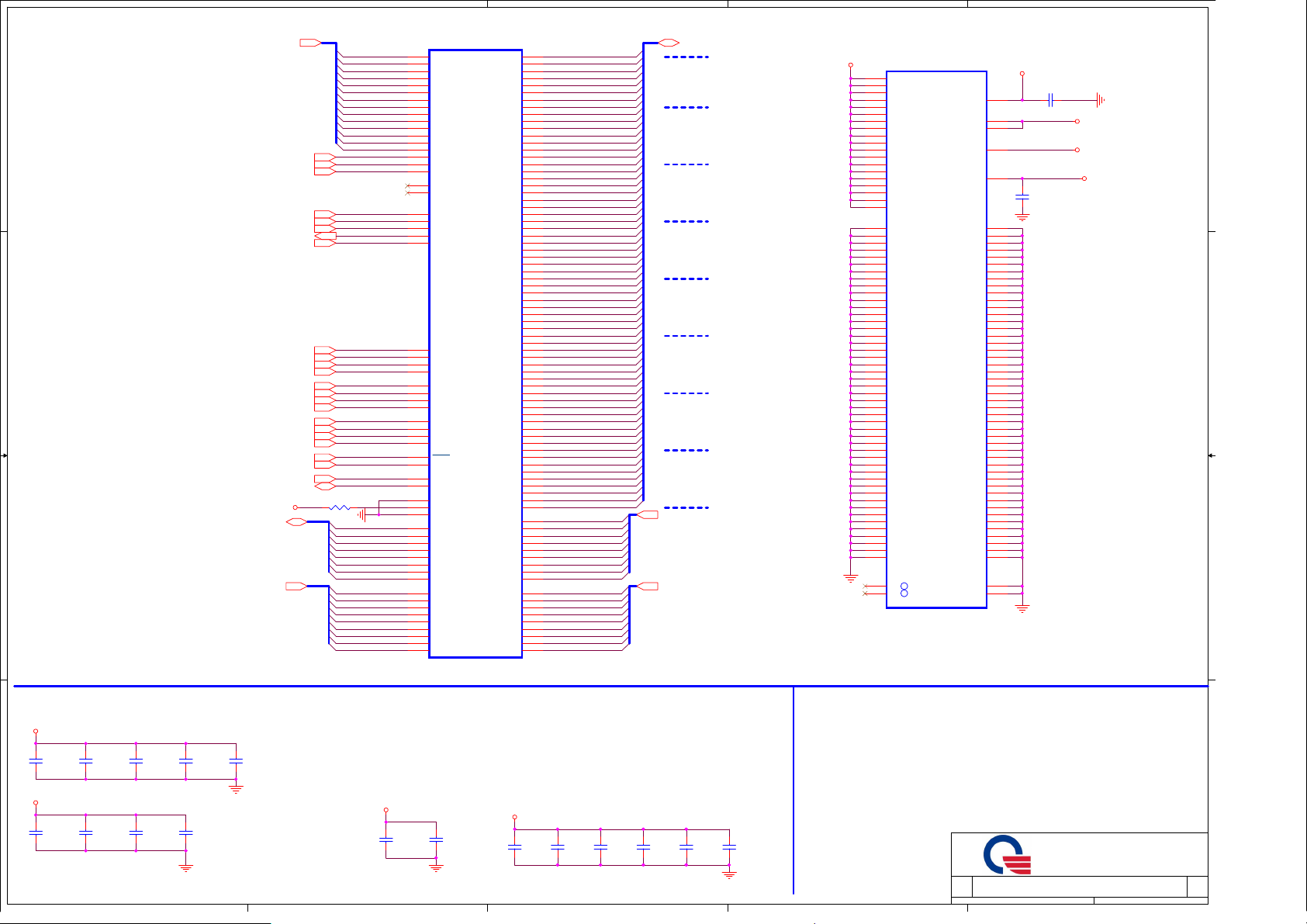

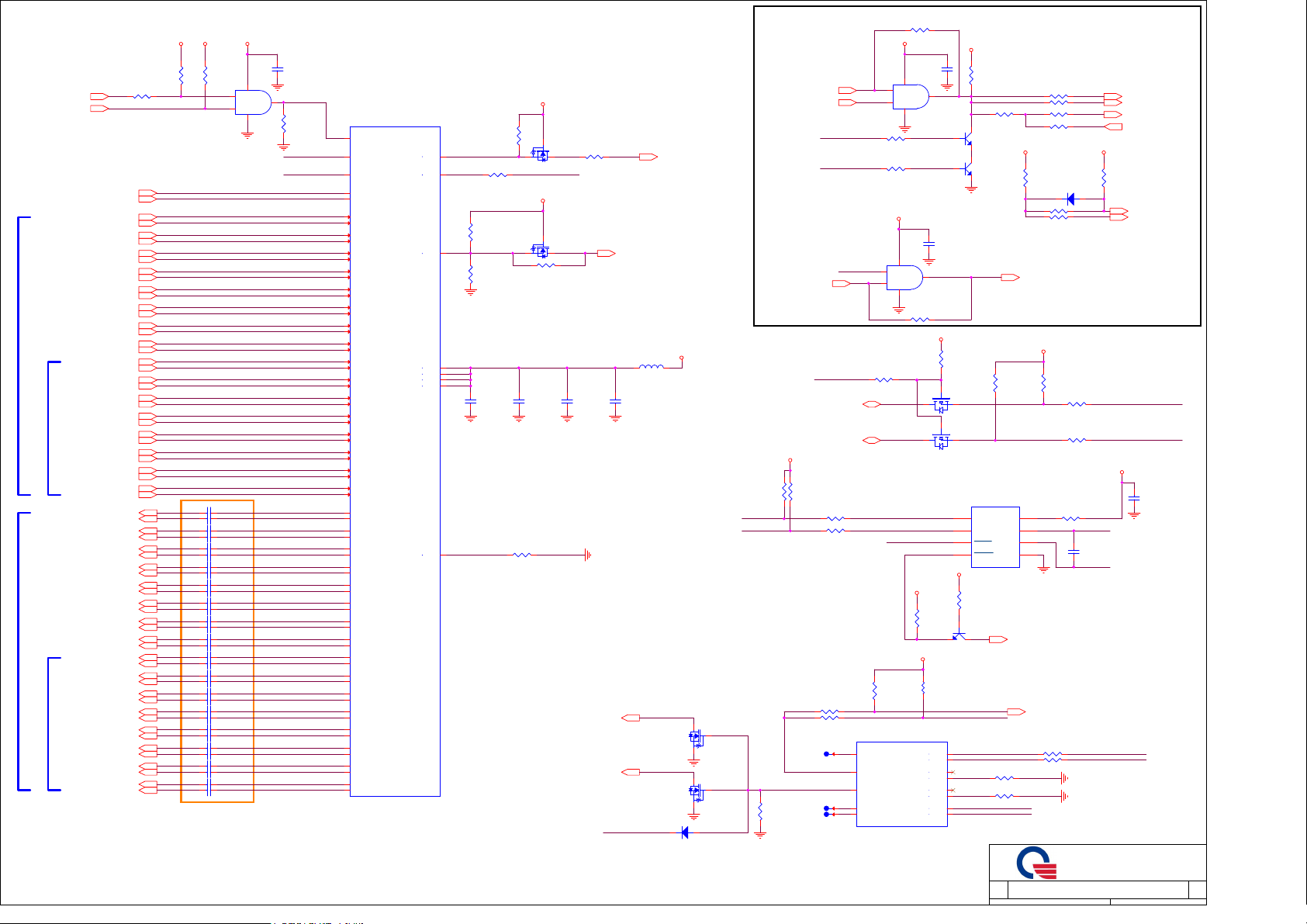

(CPU)

P_HUB_RXP0[13]

P_HUB_RXN0[13]

P_HUB_RXP1[13]

D D

FCH

M.2 SSD1

C C

GFX (RR)

GFX (SR)

B B

A A

5

P_HUB_RXN1[13]

P_HUB_RXP2[13]

P_HUB_RXN2[13]

P_HUB_RXP3[13]

P_HUB_RXN3[13]

PCIE_SSD_RXP0[28]

PCIE_SSD_RXN0[28]

PCIE_SSD_RXP1[28]

PCIE_SSD_RXN1[28]

PCIE_SSD_RXP2[28]

PCIE_SSD_RXN2[28]

PCIE_SSD_RXP3[28]

PCIE_SSD_RXN3[28]

GFX_PEG_RXP0[16]

GFX_PEG_RXN0[16]

GFX_PEG_RXP1[16]

GFX_PEG_RXN1[16]

GFX_PEG_RXP2[16]

GFX_PEG_RXN2[16]

GFX_PEG_RXP3[16]

GFX_PEG_RXN3[16]

GFX_PEG_RXP4[16]

GFX_PEG_RXN4[16]

GFX_PEG_RXP5[16]

GFX_PEG_RXN5[16]

GFX_PEG_RXP6[16]

GFX_PEG_RXN6[16]

GFX_PEG_RXP7[16]

GFX_PEG_RXN7[16]

GFX_PEG_RXP8[16]

GFX_PEG_RXN8[16]

GFX_PEG_RXP9[16]

GFX_PEG_RXN9[16]

GFX_PEG_RXP10[16]

GFX_PEG_RXN10[16]

GFX_PEG_RXP11[16]

GFX_PEG_RXN11[16]

GFX_PEG_RXP12[16]

GFX_PEG_RXN12[16]

GFX_PEG_RXP13[16]

GFX_PEG_RXN13[16]

GFX_PEG_RXP14[16]

GFX_PEG_RXN14[16]

GFX_PEG_RXP15[16]

GFX_PEG_RXN15[16]

U28B

AE8

P_HUB_RXP0

AD8

P_HUB_RXN0

AB8

P_HUB_RXP1

AA8

P_HUB_RXN1

Y6

P_HUB_RXP2

Y7

P_HUB_RXN2

W4

P_HUB_RXP3

W5

P_HUB_RXN3

AR9

P_GPP_RXP0

AT9

P_GPP_RXN0

AM9

P_GPP_RXP1

AM10

P_GPP_RXN1

AR10

P_GPP_RXP2/SATA_RX0P

AP10

P_GPP_RXN2/SATA_RX0N

AP11

P_GPP_RXP3/SATA_RX1P

AN11

P_GPP_RXN3/SATA_RX1N

F6

P_GFX_RXP0

F5

P_GFX_RXN0

G5

P_GFX_RXP1

G4

P_GFX_RXN1

H7

P_GFX_RXP2

H6

P_GFX_RXN2

J6

P_GFX_RXP3

J5

P_GFX_RXN3

K8

P_GFX_RXP4

K7

P_GFX_RXN4

K5

P_GFX_RXP5

K4

P_GFX_RXN5

L7

P_GFX_RXP6

L6

P_GFX_RXN6

M6

P_GFX_RXP7

M5

P_GFX_RXN7

N8

P_GFX_RXP8

N7

P_GFX_RXN8

N5

P_GFX_RXP9

N4

P_GFX_RXN9

P7

P_GFX_RXP10

P6

P_GFX_RXN10

R6

P_GFX_RXP11

R5

P_GFX_RXN11

T8

P_GFX_RXP12

T7

P_GFX_RXN12

T4

P_GFX_RXP13

T5

P_GFX_RXN13

U7

P_GFX_RXP14

U6

P_GFX_RXN14

V6

P_GFX_RXP15

V5

P_GFX_RXN15

W8

P_ZVDDP

AV7

SATA_ZVDDP

APU_AM4_SOCKET_1331P

4

T0 only

T0 only

PCIE

P_GPP_TXP2/SATA_TX0P

P_GPP_TXN2/SATA_TX0N

P_GPP_TXP3/SATA_TX1P

P_GPP_TXN3/SATA_TX1N

T0 only

T2 only

T2 only

AM4 REV 0.95

PART 2 OF 12

T0 only

P_HUB_TXP0

P_HUB_TXN0

P_HUB_TXP1

P_HUB_TXN1

P_HUB_TXP2

P_HUB_TXN2

P_HUB_TXP3

P_HUB_TXN3

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

P_GFX_TXP4

P_GFX_TXN4

P_GFX_TXP5

P_GFX_TXN5

P_GFX_TXP6

P_GFX_TXN6

P_GFX_TXP7

P_GFX_TXN7

P_GFX_TXP8

P_GFX_TXN8

P_GFX_TXP9

P_GFX_TXN9

P_GFX_TXP10

P_GFX_TXN10

P_GFX_TXP11

P_GFX_TXN11

P_GFX_TXP12

P_GFX_TXN12

P_GFX_TXP13

P_GFX_TXN13

P_GFX_TXP14

P_GFX_TXN14

P_GFX_TXP15

P_GFX_TXN15

P_ZVSS

P0A_ZVSS

P0B_ZVSS

SATA_ZVSS

P_HUB_TXP0_C

AE4

P_HUB_TXN0_C

AE5

P_HUB_TXP1_C

AA5

P_HUB_TXN1_C

AB5

P_HUB_TXP2_C

AC6

P_HUB_TXN2_C

AC7

P_HUB_TXP3_C

AD5

P_HUB_TXN3_C

AD6

AT12

AR12

AP13

AR13

AL13

AM13

AN14

AP14

GFX_PEG_TXP0_C

D1

GFX_PEG_TXN0_C

E1

GFX_PEG_TXP1_C

E3

GFX_PEG_TXN1_C

F3

GFX_PEG_TXP2_C

F2

GFX_PEG_TXN2_C

G2

GFX_PEG_TXP3_C

G1

GFX_PEG_TXN3_C

H1

GFX_PEG_TXP4_C

H3

GFX_PEG_TXN4_C

J3

GFX_PEG_TXP5_C

J2

GFX_PEG_TXN5_C

K2

GFX_PEG_TXP6_C

K1

GFX_PEG_TXN6_C

L1

GFX_PEG_TXP7_C

L3

GFX_PEG_TXN7_C

M3

GFX_PEG_TXP8_C

M2

GFX_PEG_TXN8_C

N2

GFX_PEG_TXP9_C

N1

GFX_PEG_TXN9_C

P1

GFX_PEG_TXP10_C

P3

GFX_PEG_TXN10_C

R3

GFX_PEG_TXP11_C

R2

GFX_PEG_TXN11_C

T2

GFX_PEG_TXP12_C

T1

GFX_PEG_TXN12_C

U1

GFX_PEG_TXP13_C

U3

GFX_PEG_TXN13_C

V3

GFX_PEG_TXP14_C

V2

GFX_PEG_TXN14_C

W2

GFX_PEG_TXP15_C

W1

GFX_PEG_TXN15_C

Y1

W7

P0A_ZVSS

V8

P0B_ZVSS

AT8

AV6

3

C112 0.22U/10V_4

C113 0.22U/10V_4

C106 0.22U/10V_4

C107 0.22U/10V_4

C109 0.22U/10V_4

C108 0.22U/10V_4

C111 0.22U/10V_4

C110 0.22U/10V_4

C865 EV@0.22u/10V_4

C866 EV@0.22u/10V_4

C855 EV@0.22u/10V_4

C863 EV@0.22u/10V_4

C871 EV@0.22u/10V_4

C877 EV@0.22u/10V_4

C851 EV@0.22u/10V_4

C859 EV@0.22u/10V_4

C868 EV@0.22u/10V_4

C873 EV@0.22u/10V_4

C862 EV@0.22u/10V_4

C867 EV@0.22u/10V_4

C838 EV@0.22u/10V_4

C842 EV@0.22u/10V_4

C852 EV@0.22u/10V_4

C860 EV@0.22u/10V_4

C833 EV@0.22u/10V_4

C836 EV@0.22u/10V_4

C832 EV@0.22u/10V_4

C835 EV@0.22u/10V_4

C834 EV@0.22u/10V_4

C840 EV@0.22u/10V_4

C837 EV@0.22u/10V_4

C841 EV@0.22u/10V_4

C856 EV@0.22u/10V_4

C849 EV@0.22u/10V_4

C850 EV@0.22u/10V_4

C857 EV@0.22u/10V_4

C853 EV@0.22u/10V_4

C861 EV@0.22u/10V_4

C847 EV@0.22u/10V_4

C854 EV@0.22u/10V_4

R61 *200_1%_4

R106 *20 0_1%_4

P_HUB_TXP0 [13]

P_HUB_TXN0 [13]

P_HUB_TXP1 [13]

P_HUB_TXN1 [13]

P_HUB_TXP2 [13]

P_HUB_TXN2 [13]

P_HUB_TXP3 [13]

P_HUB_TXN3 [13]

PCIE_SSD_TXP0 [28]

PCIE_SSD_TXN0 [28]

PCIE_SSD_TXP1 [28]

PCIE_SSD_TXN1 [28]

PCIE_SSD_TXP2 [28]

PCIE_SSD_TXN2 [28]

PCIE_SSD_TXP3 [28]

PCIE_SSD_TXN3 [28]

GFX_PEG_TXP0 [16]

GFX_PEG_TXN0 [16]

GFX_PEG_TXP1 [16]

GFX_PEG_TXN1 [16]

GFX_PEG_TXP2 [16]

GFX_PEG_TXN2 [16]

GFX_PEG_TXP3 [16]

GFX_PEG_TXN3 [16]

GFX_PEG_TXP4 [16]

GFX_PEG_TXN4 [16]

GFX_PEG_TXP5 [16]

GFX_PEG_TXN5 [16]

GFX_PEG_TXP6 [16]

GFX_PEG_TXN6 [16]

GFX_PEG_TXP7 [16]

GFX_PEG_TXN7 [16]

GFX_PEG_TXP8 [16]

GFX_PEG_TXN8 [16]

GFX_PEG_TXP9 [16]

GFX_PEG_TXN9 [16]

GFX_PEG_TXP10 [16]

GFX_PEG_TXN10 [16]

GFX_PEG_TXP11 [16]

GFX_PEG_TXN11 [16]

GFX_PEG_TXP12 [16]

GFX_PEG_TXN12 [16]

GFX_PEG_TXP13 [16]

GFX_PEG_TXN13 [16]

GFX_PEG_TXP14 [16]

GFX_PEG_TXN14 [16]

GFX_PEG_TXP15 [16]

GFX_PEG_TXN15 [16]

gnd voids undermeath

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

FCH

M.2 SSD1

GFX (RR)

GFX (SR)

Tuesday, June 26, 2018

Tuesday, June 26, 2018

Tuesday, June 26, 2018

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

AM4 PCIE

AM4 PCIE

AM4 PCIE

1

ZGX

ZGX

ZGX

02

2 59

2 59

2 59

1A

1A

1A

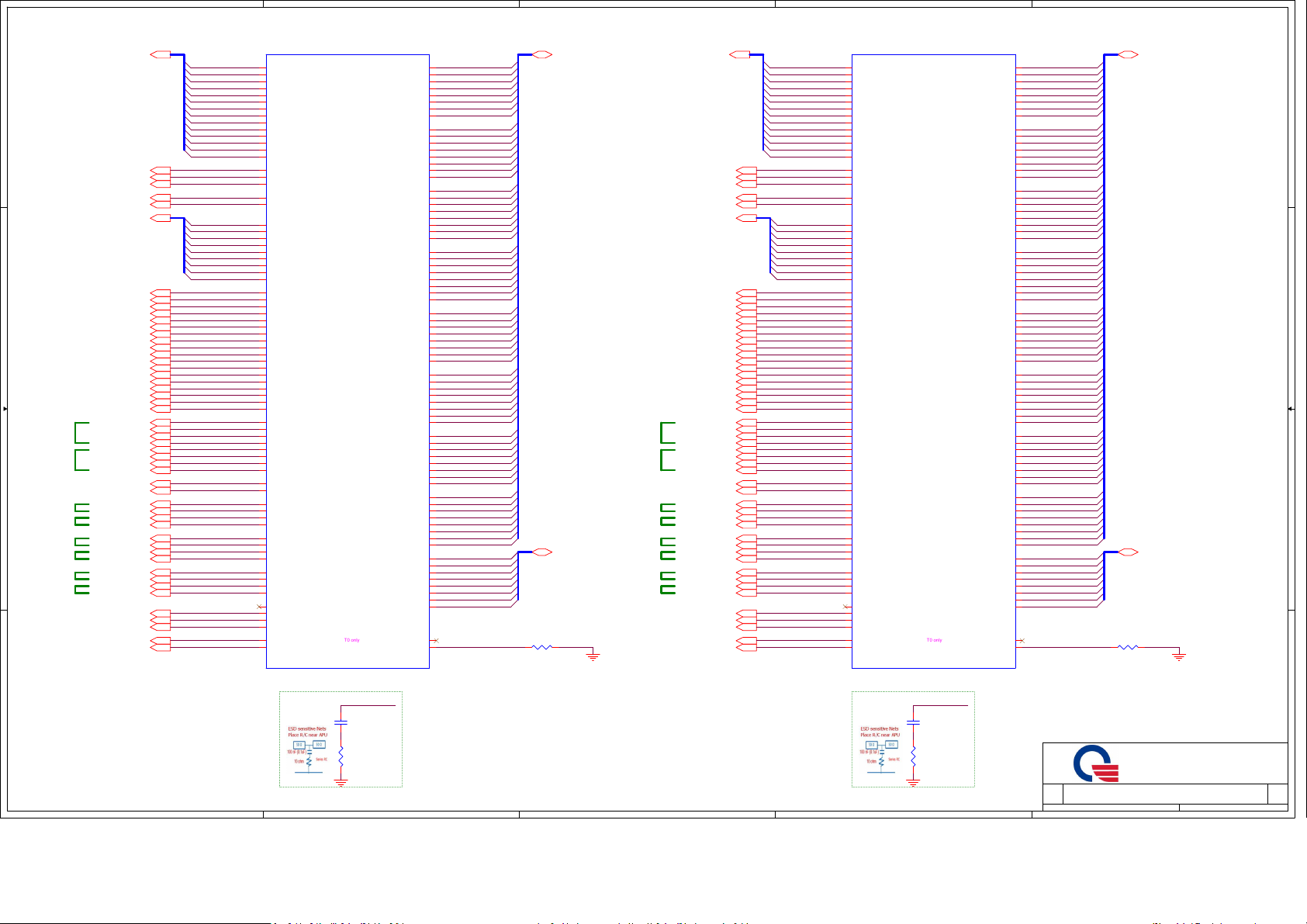

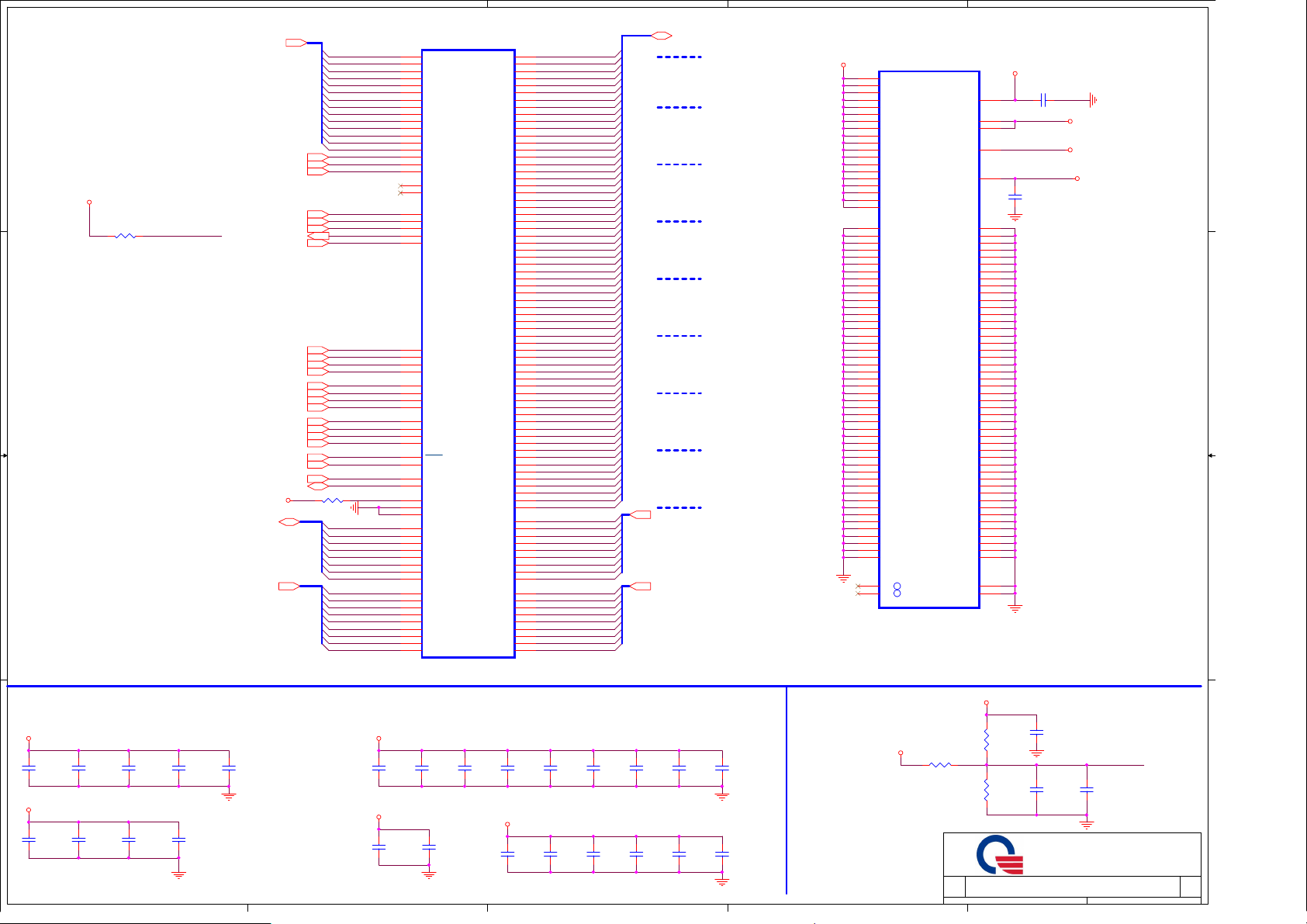

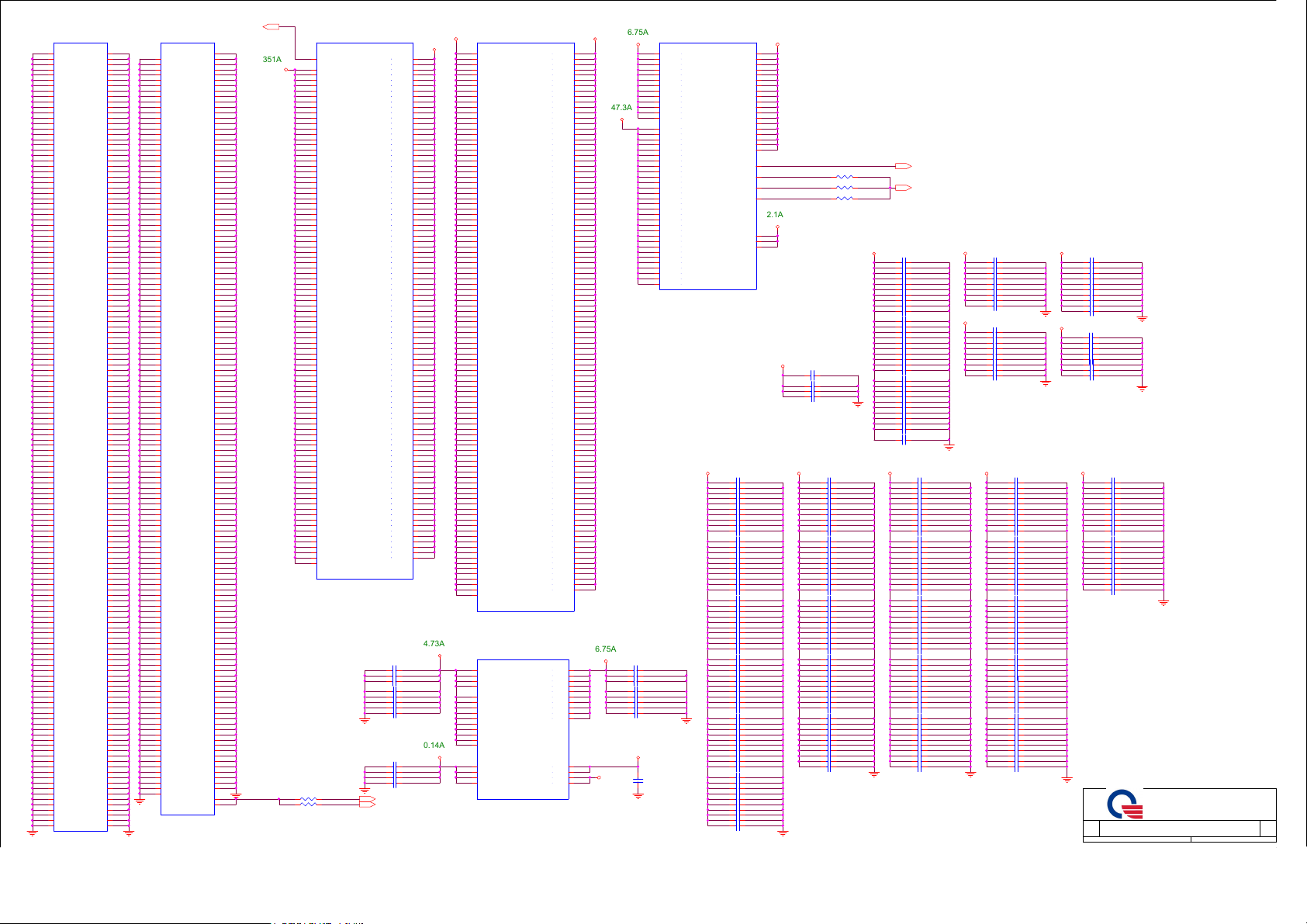

5

4

3

2

1

(CPU)

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

D D

M_A_ACT#[9,10]

M_A_BG0[9,10]

M_A_BG1[9,10]

M_A_BANK0[9,10]

M_A_BANK1[9,10]

M_A_DM[8:0][9,10] M_B_DM[ 8:0][11, 12]

M_A_DQS0[9,10]

M_A_DQS#0[9,10]

C C

CH A0

CH A1

CH A0

B B

CH A1

CH A0

CH A1

CH A0

CH A1

M_A_DQS1[9,10]

M_A_DQS#1[9,10]

M_A_DQS2[9,10]

M_A_DQS#2[9,10]

M_A_DQS3[9,10]

M_A_DQS#3[9,10]

M_A_DQS4[9,10]

M_A_DQS#4[9,10]

M_A_DQS5[9,10]

M_A_DQS#5[9,10]

M_A_DQS6[9,10]

M_A_DQS#6[9,10]

M_A_DQS7[9,10]

M_A_DQS#7[9,10]

M_A_DQS8[9,10]

M_A_DQS#8[9,10]

M_A0_CLK0[9]

M_A0_CLK0#[9]

M_A0_CLK1[9]

M_A0_CLK1#[9]

M_A1_CLK0[10]

M_A1_CLK0#[10]

M_A1_CLK1[10]

M_A1_CLK1#[10]

M_A_RST#[9,10]

M_A_EVENT#[9,10] M_B_EVENT#[11,12]

M_A0_CKE0[9]

M_A0_CKE1[9]

M_A1_CKE0[10]

M_A1_CKE1[10]

M_A0_ODT0[9]

M_A0_ODT1[9]

M_A1_ODT0[10]

M_A1_ODT1[10]

M_A0_CS#0[9]

M_A0_CS#1[9]

M_A1_CS#0[1 0]

M_A1_CS#1[1 0]

M_A_RAS#[9,10]

M_A_CAS#[9,10]

M_A_WE#[9,1 0]

M_A_ALERT#[9,10]

M_A_PARITY[9 ,10]

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DM8 M_B_DM8

U28A

AA32

MA_ADD0

T32

MA_ADD1

T35

MA_ADD2

T31

MA_ADD3

R30

MA_ADD4

R33

MA_ADD5

R32

MA_ADD6

P34

MA_ADD7

P30

MA_ADD8

P31

MA_ADD9

AA36

MA_ADD10

P33

MA_ADD11

N35

MA_ADD12

AE32

MA_ADD13

M35

MA_ACT_L

N31

MA_BG0

N32

MA_BG1

AA35

MA_BANK0

AA33

MA_BANK1

K19

MA_DM0

J23

MA_DM1

G26

MA_DM2

H30

MA_DM3

AJ31

MA_DM4

AM31

MA_DM5

AL29

MA_DM6

AL26

MA_DM7

G34

MA_DM8

H19

MA_DQS_H0

G19

MA_DQS_L0

F23

MA_DQS_H1

G23

MA_DQS_L1

F27

MA_DQS_H2

F26

MA_DQS_L2

F30

MA_DQS_H3

E30

MA_DQS_L3

AJ33

MA_DQS_H4

AJ34

MA_DQS_L4

AN32

MA_DQS_H5

AN33

MA_DQS_L5

AP29

MA_DQS_H6

AN29

MA_DQS_L6

AP26

MA_DQS_H7

AN26

MA_DQS_L7

H34

MA_DQS_H8

H33

MA_DQS_L8

T34

MA_CLK_H0

U34

MA_CLK_L0

U33

MA_CLK_H1

V33

MA_CLK_L1

V35

MA_CLK_H2

V36

MA_CLK_L2

V32

MA_CLK_H3

W32

MA_CLK_L3

L33

MA_RESET_L

W35

MA_EVENT_L

M32

MA0_CKE0

M30

MA0_CKE1

M33

MA1_CKE0

L34

MA1_CKE1

AD35

MA0_ODT0

AF31

MA0_ODT1

AD33

MA1_ODT0

AF34

MA1_ODT1

AC33

MA0_CS_L0

AE35

MA0_CS_L1

AC34

MA1_CS_L0

AE34

MA1_CS_L1

AF33

MA_ADD_17

AB34

MA_RAS_L_ADD16

AD32

MA_CAS_L_ADD15

AB35

MA_WE_L_ADD14

N34

MA_ALERT_L

Y33

MA_PAROUT

APU_AM4_SOCKET_1331P

MEMORY A

AM4 REV 0.95

PART 1 OF 12

T0 only

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_CHECK0

MA_CHECK1

MA_CHECK2

MA_CHECK3

MA_CHECK4

MA_CHECK5

MA_CHECK6

MA_CHECK7

MA_ZVDDIO_MEM_S3

MA_ZVSS

M_A_DQ0

E18

M_A_DQ1

J18

M_A_DQ2

J20

M_A_DQ3

H21

M_A_DQ4

H18

M_A_DQ5

F18

M_A_DQ6

G20

M_A_DQ7

F20

M_A_DQ8

H22

M_A_DQ9

G22

M_A_DQ10

E24

M_A_DQ11

J24

M_A_DQ12

F21

M_A_DQ13

J21

M_A_DQ14

H24

M_A_DQ15

F24

M_A_DQ16

J26

M_A_DQ17

J27

M_A_DQ18

G28

M_A_DQ19

H28

M_A_DQ20

H25

M_A_DQ21

G25

M_A_DQ22

E28

M_A_DQ23

H27

M_A_DQ24

F29

M_A_DQ25

J30

M_A_DQ26

H31

M_A_DQ27

F32

M_A_DQ28

J29

M_A_DQ29

G29

M_A_DQ30

E31

M_A_DQ31

G31

M_A_DQ32

AH34

M_A_DQ33

AJ30

M_A_DQ34

AK30

M_A_DQ35

AL34

M_A_DQ36

AH31

M_A_DQ37

AH32

M_A_DQ38

AK33

M_A_DQ39

AK32

M_A_DQ40

AM34

M_A_DQ41

AM33

M_A_DQ42

AP31

M_A_DQ43

AR33

M_A_DQ44

AL32

M_A_DQ45

AL31

M_A_DQ46

AP34

M_A_DQ47

AP32

M_A_DQ48

AR31

M_A_DQ49

AK29

M_A_DQ50

AM28

M_A_DQ51

AL28

M_A_DQ52

AM30

M_A_DQ53

AN30

M_A_DQ54

AP28

M_A_DQ55

AR28

M_A_DQ56

AK27

M_A_DQ57

AK26

M_A_DQ58

AP25

M_A_DQ59

AR25

M_A_DQ60

AN27

M_A_DQ61

AM27

M_A_DQ62

AL25

M_A_DQ63

AM25

MA_CHECK0

F33

MA_CHECK1

G32

MA_CHECK2

K31

MA_CHECK3

K32

MA_CHECK4

E33

MA_CHECK5

E34

MA_CHECK6

J32

MA_CHECK7

J33

Y34

MA_ZVSS_40 MB_ZVSS_40

AJ37

M_A_DQ[63:0] [9,10]M_A_A[13:0][9,10]

DDR_CHECK:

connected signals within

their respective byte grouping

CH B0

CH B1

CH B0

CH B1

CH B0

CH B1

CH B0

CH B1

M_B_A[13:0][11,12]

M_B_ACT#[11,12]

M_B_BG0[11,12]

M_B_BG1[11,12]

M_B_BANK0[11,12]

M_B_BANK1[11,12]

M_B_DQS0[11,12]

M_B_DQS#0[11,12]

M_B_DQS1[11,12]

M_B_DQS#1[11,12]

M_B_DQS2[11,12]

M_B_DQS#2[11,12]

M_B_DQS3[11,12]

M_B_DQS#3[11,12]

M_B_DQS4[11,12]

M_B_DQS#4[11,12]

M_B_DQS5[11,12]

M_B_DQS#5[11,12]

M_B_DQS6[11,12]

M_B_DQS#6[11,12]

M_B_DQS7[11,12]

M_B_DQS#7[11,12]

M_B_DQS8[11,12]

M_B_DQS#8[11,12]

M_B0_CLK0[11]

M_B0_CLK0#[11]

M_B0_CLK1[11]

M_B0_CLK1#[11]

M_B1_CLK0[12]

M_B1_CLK0#[12]

M_B1_CLK1[12]

M_B1_CLK1#[12]

M_B_RST#[11,12]

M_B0_CKE0[11]

M_B0_CKE1[11]

M_B1_CKE0[12]

M_B1_CKE1[12]

M_B0_ODT0[11]

M_B0_ODT1[11]

M_B1_ODT0[12]

M_B1_ODT1[12]

M_B0_CS#0[11]

M_B0_CS#1[11]

M_B1_CS#0[12]

M_B1_CS#1[12]

M_B_RAS#[11,12]

M_B_CAS#[11,12]

M_B_WE#[11,12]

M_B_ALERT#[11,12]

M_B_PARITY[1 1,12]

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

U28I

AC36

MB_ADD0

U36

MB_ADD1

U37

MB_ADD2

T38

MB_ADD3

T37

MB_ADD4

R39

MB_ADD5

R36

MB_ADD6

P39

MB_ADD7

R38

MB_ADD8

P36

MB_ADD9

AC39

MB_ADD10

P37

MB_ADD11

N38

MB_ADD12

AG38

MB_ADD13

M38

MB_ACT_L

M36

MB_BG0

M39

MB_BG1

AD38

MB_BANK0

AC37

MB_BANK1

C21

MB_DM0

D26

MB_DM1

A32

MB_DM2

D37

MB_DM3

AL38

MB_DM4

AR39

MB_DM5

AT35

MB_DM6

AW29

MB_DM7

F39

MB_DM8

B22

MB_DQS_H0

A22

MB_DQS_L0

C27

MB_DQS_H1

B27

MB_DQS_L1

C33

MB_DQS_H2

C32

MB_DQS_L2

B37

MB_DQS_H3

A37

MB_DQS_L3

AM37

MB_DQS_H4

AM36

MB_DQS_L4

AT38

MB_DQS_H5

AT39

MB_DQS_L5

AU34

MB_DQS_H6

AV34

MB_DQS_L6

AU28

MB_DQS_H7

AU29

MB_DQS_L7

G38

MB_DQS_H8

G37

MB_DQS_L8

U39

MB_CLK_H0

V39

MB_CLK_L0

V38

MB_CLK_H1

W38

MB_CLK_L1

W37

MB_CLK_H2

Y37

MB_CLK_L2

Y39

MB_CLK_H3

AA39

MB_CLK_L3

K35

MB_RESET_L

AA38

MB_EVENT_L

L37

MB0_CKE0

K37

MB0_CKE1

L39

MB1_CKE0

L36

MB1_CKE1

AF39

MB0_ODT0

AH36

MB0_ODT1

AF37

MB1_ODT0

AH38

MB1_ODT1

AE37

MB0_CS_L0

AG39

MB0_CS_L1

AE38

MB1_CS_L0

AG36

MB1_CS_L1

AH37

MB_ADD_17

AD36

MB_RAS_L_ADD16

AF36

MB_CAS_L_ADD15

AD39

MB_WE_L_ADD14

N37

MB_ALERT_L

AB38

MB_PAROUT

APU_AM4_SOCKET_1331P

MEMORY B

T0 only

AM4 REV 0.95

PART 9 OF 12

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB_CHECK0

MB_CHECK1

MB_CHECK2

MB_CHECK3

MB_CHECK4

MB_CHECK5

MB_CHECK6

MB_CHECK7

MB_ZVDDIO_MEM_S3

MB_ZVSS

D20

B21

B24

C24

A20

C20

A23

C23

A26

C26

A29

C29

A25

B25

A28

B28

A31

B31

B34

C35

B30

C30

B33

A34

B36

E36

C39

D38

A35

C36

B38

C38

AK39

AL37

AN36

AN39

AK38

AK36

AM39

AN38

AR36

AR37

AU37

AV37

AP37

AP38

AT36

AU38

AW35

AU35

AW32

AU32

AV36

AW36

AW33

AV33

AW30

AV30

AW27

AW26

AV31

AU31

AV28

AV27

F38

F36

H39

J39

E37

E39

H36

H37

Y36

AJ39

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

MB_CHECK0

MB_CHECK1

MB_CHECK2

MB_CHECK3

MB_CHECK4

MB_CHECK5

MB_CHECK6

MB_CHECK7

M_B_DQ[63:0] [1 1,12]

MB_CHECK[7:0] [11,12]MA_CHECK[7:0] [9,10]

DDR_CHECK:

connected signals within

their respective byte grouping

R675 *40.2_1%_4R6 77 *40.2_1%_4

03

A A

5

M_A_RST# M_B_RST#

C963

*0.1u/16V_4

R711

*10_5%_6

4

3

2

C962

*0.1u/16V_4

R710

*10_5%_6

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, June 26, 2018

Date: Sheet of

Tuesday, June 26, 2018

Date: Sheet of

Tuesday, June 26, 2018

PROJECT :

AM4 MEMORY

AM4 MEMORY

AM4 MEMORY

ZGX

ZGX

ZGX

3 59

3 59

1

3 59

1A

1A

1A

5

4

3

2

1

(CPU)

+1.8V

R151 1K_1%_4

R150 1K_1%_4

R144 300_5%_4

R135 300_5%_4

+3V

R644 1K_1%_4

D D

R112 1K_1%_4

R649 1K_1%_4

C469

*27p/50V_4

APU_PWRGD_SVID_RE G

C474

*27p/50V_4

FOR DEBUG, PLACE THESE CAPS CLOSE TO APU

C C

APU_PWRGD_SVID_RE G[47]

Serial VID

B B

+1.8V

R639

*1K_1%_4

R647

*220_1%_4

APU_PWRGD

APU_RST#

C451

*27p/50V_4

APU_SVT

C939

*27p/50V_4

R643

*1K_1%_4

R629

*220_1%_4

APU_SIC

APU_SID

APU_PWRGD

APU_RST#

APU_ALERT#_C

APU_PROCHOT#_C

THERMTRIP#

+1.8V

R641

*1K_1%_4

R143

*2.2K_5%_4

R142

*220_1%_4

APU_SVT

APU_SVC

APU_SVD

SVT need 0R in power side

R648 10_1%_4

R651 10_1%_4

R139 HD T@0_5%_4

R141 *Short_4

APU_RST#

R137 *Short_4

R628 *Short_4

R107 *Short_4

VID Override table (VDD)

FAN:3VS0

APU_ALERT#[41]

APU_PROCHOT#[41,42,59]

APU_SVC[47]

APU_SVD[47]

APU_SVT[47]

APU_PWRGD_D

3V_S0

VFIX MODE

SVC SVD

0

0

001

1

1 1 0.8V

for normal operation open all switches

Boot Voltage

1.1V

1.0V

0.9V

APU_SVD_R

APU_PWRGD

APU_RST#_C

APU_SIC

APU_SID

APU_ALERT#_C

APU_PROCHOT#_C

THERMTRIP#

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

U28C

B6

DP2_TXP0

B7

DP2_TXN0

A7

DP2_TXP1

A8

DP2_TXN1

C8

DP2_TXP2

C9

DP2_TXN2

B9

DP2_TXP3

B10

DP2_TXN3

D4

DP1_TXP0

D5

DP1_TXN0

D7

DP1_TXP1

D8

DP1_TXN1

F8

DP1_TXP2

G8

DP1_TXN2

E9

DP1_TXP3

F9

DP1_TXN3

D2

DP0_TXP0

C2

DP0_TXN0

C3

DP0_TXP1

B3

DP0_TXN1

B4

DP0_TXP2

A4

DP0_TXN2

C5

DP0_TXP3

C6

DP0_TXN3

D17

SVC

C17

18_S0

SVD

A17

SVT

E16

PWROK

B16

B18

C18

D16

H15

A19

A14

C14

C15

B15

B13

E13

D14

18_S0

RESET_L

SIC

18/33_S0

SID

ALERT_L

PROCHOT_L

THERMTRIP_L

TDI

TDO

18_S5

TCK

TMS

TRST_L

18_S5

DBRDY

18_S0

DBREQ_L

18_S5

APU_AM4_SOCKET_1331P

DISPLAY/SVI2/JTAG/TEST

T0 only

T0 only

18_S0

18_S0

18_S0

18_S0

18_S0

18_S0

18_S0

DP_STEREOSYNC

33_S0

VDDCR_CPU_SENSE

VDDCR_SOC_SENSE

VDDIO_MEM_S3_SENSE

AM4 REV 0.95

PART 3 OF 12

CORETYPE0

TYPE2-L

TYPE3-H

DP_ZVSS

DP_AUX_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

DP2_AUXP

DP2_AUXN

DP2_HPD

DP1_AUXP

DP1_AUXN

DP1_HPD

DP0_AUXP

DP0_AUXN

DP0_HPD

TEST4

TEST5

TEST6

TEST47

TEST10

TEST14

TEST15

TEST16

TEST17

TEST11

TEST19

TEST18

TEST28_H

TEST28_L

TEST31

TEST40

AM4R1

CORETYPE0

CORETYPE1

TEST41

VSS_SENSE_A

VDDP_SENSE

VSS_SENSE_B

+1.8V_S5

R146

*1K_1%_4

A1

F12

E12

G13

H13

H12

A10

A11

E10

F11

G11

D10

G10

H10

H9

L23

M22

D13

P28

AB4

C12

B12

C11

D11

A13

H16

G16

E6

E7

AA30

W30

K14

AL8

AM24

AN9

A16

F14

E15

G14

F15

AL22

AM23

+1.8V_S5

A

+3V_S5 3V_LDO

R611

*10K_5%_4

AM4R1

R613 *0_5%_4

TEST4_HERMDA

TEST5_THERMDC

APU_TEST6

APU_TEST47

APU_TEST10

APU_TEST14

APU_TEST15

APU_TEST16

APU_TEST17

APU_TEST11

APU_TEST19

APU_TEST18APU_SVC_R

APU_TEST28_H

APU_TEST28_L

APU_TEST31

APU_TEST40

DP_STEREOSYNC

AM4R1

CORETYPE0

CORETYPE1

APU_TEST41

APU_VSS_SENSE_A

VDDP_SENSE

VSS_SENSE_B

GND

U8

*SN74LVC1G07YZVR

A2

VCC

Y

B2

B1

R122 1K_1%_4

+5V_S5

+3V_S5

2

3

1

Q13

*2N7002K

TP25

TP24

TP95

TP26

TP86

R621 *1K_1%_4

TP94

R614 *1K_1%_4

R619 *1K_1%_4

R625 *1K_1%_4

R552 1K_1%_4

R557 1K_1%_4

TP8

TP5

TP29

TP28

R126 *1K_1%_4

R121 1K_1%_4

TP96

VDDIO_MEM_S3_SENSE [46]

R114 *Short_4

R115 *Short_4

R155

R154

*1K_1%_4

*10K_1%_4

R132

*10K_1%_4

SYS_SHDN# [4,16,36,41,43,58]

+3V_S5

VDDCR_CPU_SENSE [47]

VDDCR_SOC_SENSE [47]

VSS_VDDCR_CPU_SEN SE [47]

VSS_VDDCR_SOC_SENSE [47]

VDDP_SENSE [45]

VSS_SENSE_B [45]

Q18

*AO3402

C549

*180p/50V_4

+1.8V

2

+1.8V_S5

3

1

04

+3V

R128

*10K_1%_4

VDDCR_CPU_PG[41,47]

THERMTRIP#

SMBUS(Internal Thermal sensor)

3ND_MBCLK[37,40,41]

(PU in EC side )

3ND_MBDATA[37,40,41]

+1.8V

1

2

3

Q16

*PJA3413

C560

10u/6.3V_4

R152

0_5%_4

+1.8_S0S5

TYPE2-18_S0

TYPE3-18_S5

R167

*100_1%_4

R130 *100K_1%_4

2

1 3

Q14

METR3904-G

R131

1K_1%_4

SYS_SHDN# [4,16,36,41,43,58]

+1.8V

2

6 1

Q15B PJT138K

Q15A PJT138K

3 4

5

+1.8V

APU_SIC

18/33_S03V_S0

APU_SID

R149 *0_5%_4

CN30

20 21

19

22

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

*HDT@HDT CONN

88511-2001-20p-l

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, June 26, 2018

Date: Sheet of

Tuesday, June 26, 2018

Date: Sheet of

Tuesday, June 26, 2018

PROJECT :

AM4 DISPLAY/MISC

AM4 DISPLAY/MISC

AM4 DISPLAY/MISC

ZGX

ZGX

ZGX

4 59

4 59

1

4 59

1A

1A

1A

C416

HDT@0.1u/16V_4

+1.8V_S5

TP150

APU_TEST18

APU_TEST19

APU_RST_L_BUF

CPU_LDT_RST_HTPA#

HDT_DBREQ#

APU_DBRDY

APU_TCK

APU_TMS

HDT_APU_TDI

HDT_TRST#

APU_TDO

APU_PWROK_BUF

2

HDT(Hardware Debug Tool ) Connector

+1.8V_S5 +1.8V_S5

CN7

4

8

10

12

16

18

20

*HDT@HDT CONN

APU_TCK

APU_TMS

HDT_APU_TDI

APU_TDO

APU_PWROK_BUF

APU_RST_L_BUF

APU_DBRDY

HDT_DBREQ#

APU_TEST19

APU_TEST18

R622 HDT@0_5 %_4

R567 HDT@33_ 1%_4

4

APU_TDI

APU_DBREQ#

C926

*HDT@0.01u/50V_4

R634 HDT@1K_1%_4

R635 HDT@1K_1%_4

R626 HDT@1K_1%_4

R569 HDT@1K_1%_4

R568 HDT@1K_1%_4

R129 HDT@1K_1%_4

C397

HDT@0.01u/50V_4

R554

A A

HDT@1K_1%_4

APU_TRST#

C869

HDT@0.01u/50V_4

R570 HD T@33_1%_4

R560 HD T@10K_1%_4

R563 HD T@10K_1%_4

R575 HD T@10K_1%_4

HDT_TRST#

DBRDY3

DBRDY2

DBRDY1

1 2

3

5 6

7

9

11

13 14

15

17

19

PLACE HDT CONNECTOR ON BOT

5

+1.8V_S5

U7

APU_RST#

APU_PWRGD_D APU_PWROK_BUF

3

1

2

GND

3

A24Y2

HDT@SN74LVC2G07DCKR

+1.8V_S5

A1

Y1

VCC

6

5

APU_RST_L_BUF

5

(CPU)

SCL0

SDA0

PCIE_REQ_GPU#

I2C_SCL

I2C_SDA

APU_I2C_INT#

DNBSWON#

PCIE_WAKE#

PCIE_RST#

S0A3

ACPRESENT

1 2

PU in STRAPS PINS side

ACZ_SDIN0

ACZ_SDIN1

ACZ_SDIN2

ACZ_BCLK_R

ACZ_RST#_R

ACZ_SYNC_R

ACZ_SDOUT_R

SYS_RST#

APU_TEST0

APU_TEST1

APU_TEST2

RSMRST_GATE# from EC

RSMRST#[41]

USB_OC_APU0#[40]

R80 15K_1%_4

R576 15K_1%_4

C364

10u/6.3V_4

D7

1

RB500V-40

R609

10K_1%_4

R591 *10K_1%_4

R604 10K_1%_4

R600 10K_1%_4

R598 1K_1%_4

R587 1K_1%_4

R590 1K_1%_4

R595 1K_1%_4

D D

+3V

R654 2.2K_5%_4

R657 2.2K_5%_4

R653 *10K_1%_4

+3V_S5

R603 2.2K_5%_4

R602 2.2K_5%_4

R92 10K_1%_4

R81 10K_1%_4

R74 10K_1%_4

R70 10K_1%_4

R577 *2.2K_5%_4

R125 *8.2K_5%_4

C C

+3V_S5

R564 *10K_1%_4

J1

*SHORT_PAD

Test mode setting (Follow AMD's suggestion)

+3V_S5

NC,no install by default

R77 *2.2K_5%_4

R79 *1K_1%_4

R580 *2.2K_5%_4

B B

2

2

+1.8V_S5

RSMRST#_R

+3V_S5

3

1

4

R84

22K_1%_4

AMD : 10ms RC-delay

C189

1u/6.3V_4

C188

*0.1u/16V_4

R88

*10_5%_6

R601

10K_1%_4

Q56

2N7002K

3

2

1

05

U28D

AU22

LPC_RST_L

AL7

PCIE_RST_L/EGPIO26

AP5

RSMRST_L

AN5

PWR_BTN_L/AGPIO0

AM3

PWR_GOOD

AM4

SYS_RESET_L/AGPIO1

AL5

WAKE_L/AGPIO2

AT2

SLP_S3_L

AP2

SLP_S5_L

AR3

S0A3_GPIO/AGPIO10/SGPIO0_CLK

AP4

S5_MUX_CTRL/EGPIO42

AM6

TEST0

AM7

TEST1/TMS

AT3

TEST2

AN24

ESPI_RESET_L/KBRST_L

AL2

LPC_PME_L/AGPIO22

AW17

AGPIO86

AN3

AGPIO23/SGPIO0_LOAD

AT23

CLK_REQ0_L/SATA_IS0_L/SATA_ZP0_L/AGPIO92

AV24

CLK_REQ1_L/AGPIO115

AT24

CLK_REQ2_L/AGPIO116

AL23

CLK_REQ3_L/SATA_IS1_L/SATA_ZP1_L/EGPIO131

AR22

CLK_REQG_L/OSCIN/EGPIO132

AL1

USB_OC0_L/AGPIO16

AM1

USB_OC1_L/TDI/AGPIO17

AR1

USB_OC2_L/TCK/AGPIO18

AP1

USB_OC3_L/TDO/AGPIO24

AW3

AZ_BITCLK

AV3

AZ_SDIN0

AU5

AZ_SDIN1

AV4

AZ_SDIN2

AU1

AZ_RST_L

AU2

AZ_SYNC

AU4

AZ_SDOUT

AP8

RTCCLK

AW5

X32K_X1

AW6

X32K_X2

APU_AM4_SOCKET_1331P

ACPI/SD/AZ/GPIO/RTC/I2C/MISC

33_S5

18_S5

33_S5

33_S5

TMS-33_S5

33_S5

S0

33_S5

USB _ OC

Type 0 active low

Type 2 active high

Type 1/3 programmable

18_S5

33_S0

T0 only (GENINT1)

33_S0

33_S5

33_S5

33_S5

33_S5

AM4 REV 0.95

PART 4 OF 12

33_S5

33_S0

33_S5

S5

33_S0

33_S5

33_S0

33_S0

EGPIO95

S0

EGPIO96

EGPIO97

EGPIO98

S0

EGPIO99

EGPIO100

SCL0/I2C2_SCL/EGPIO113

SDA0/I2C2_SDA/EGPIO114

SCL1/I2C3_SCL/AGPIO19

SDA1/I2C3_SDA/AGPIO20

S5

AGPIO3

S5

AGPIO4

AGPIO5/DEVSLP0

33_S5

S5

AGPIO6

S5

AGPIO9/SGPIO0_DATAOUT

S0

SATA_ACT_L/AGPIO130

AGPIO40/SGPIO0_DATAIN

33_S0

33_S5

AGPIO8

GENINT1_L/AGPIO89

GENINT2_L/AGPIO90

SPKR/AGPIO91

BLINK/AGPIO11

FANIN0/AGPIO84

FANOUT0/AGPIO85

TEST4613

AW11

AV12

AW12

AU13

AV13

AT14

AU25

AV25

AK3

AK2

AT6

AR6

AP22

AN8

AP7

AN2

AV22

AU23

AM22

AR4

AW23

AT5

AN23

AP23

AL4

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID8

BOARD_ID9

BOARD_ID10

TP98

TP97

SSD1_LED#_CPU

SPKR [31]

TP30

APU_TEST46

SSD1 Det

SSD SATA I/F --> L

S

SD PCIE I/F --> H

NGFF_DET1 [28]

NGFF_DET2_CPU [29]

SCL0 [9,10,11,12]

SDA0 [9,10,11,12]

I2C_SCL [39]

I2C_SDA [39]

AGPIO3 [6]

R145 NDS@10 K_1%_4

DEVSLP_GATE# [28,29,34]

R124 *Short_4

R1014 *0_5%_4

R1015 0_5%_4

SSD1_RST# [28]

TP11

DEVSLP_SSD1 [28]

+3V

SSD1_LED# [28,40]

APU_I2C_INT# [39]

PCIE_WAKE#[13,16,30,33]

PCIE_REQ_GPU#[16]

ACZ_BCLK[31]

ACZ_SDIN0[31]

ACZ_RST#[31]

ACZ_SYNC[31]

ACZ_SDOUT[31]

C938 150p/50V_4

C120 150p/50V_4

DNBSWON#[41]

SUSB#[41]

SUSC#[41]

SUS_CLK[30]

RTC_CLK[6]

C892

15p/50V_4

C896

15p/50V_4

PLTRST#[30,41]

PCIERST#[13,16,28,29,30,33,36]

PCIE_CLKREQ_SSD1#[28]

DGPU_RST_L[16]

APU_CLKREQN[13]

R650 33_1%_4

R66 33_1%_4

C153 *100p/50V_4

R581 *Short_4

R574 *Short_4

SIO_RCIN#[41]

SIO_EXT_SCI#[41]

PM_SMI#_C[13]

ACPRESENT[41]

R597 22_1%_4

R585 22_1%_4

R588 22_1%_4

R594 22_1%_4

R104 *0_5%_4R76 15K_1%_4

12

Y4

32.768KHZ/20ppm

AMD CL maximum ESR of the XTAL is 65 kΩ

TXC:BG332768111 20PPM (ESR 70kΩ)Metal shell

NDK:BG332768108 20PPM (ESR 70kΩ)Metal shell

SEIKO:BG632768006 20PPM (ESR 70kΩ)Metal shell

**SEG:BG332768453 20PPM (ESR 70kΩ)Glass shell

LPC_RST#_R

PCIE_RST#

RSMRST#_R

SYS_PWRGD

SYS_RST#

SUSB#_C

SUSC#_C

S0A3

BOARD_ID4

APU_TEST0

APU_TEST1

APU_TEST2

TP27

USB_OC_APU0#_C

TP87

TP90

TP89

ACZ_BCLK_R

ACZ_SDIN1

ACZ_SDIN2

ACZ_RST#_R

ACZ_SYNC_R

ACZ_SDOUT_R

32K_X1

32K_X2

R607

20M_5%_4

SYS PWRGD

5

SYS_PWRGD_R

+3V_S5

R558

100K_1%_4

34

Q53A

2N7002KDW

EC_PWROK[41]

SYS_RST#[6,13]

A A

D57 RB500V-40

D58 *RB500V-40

SUSB#

D6 *RB500V-40

5

21

21

21

HWPG[41]

+3V_S5

R555

8.2K_5%_4

R551 *Short_4

C858

0.1u/25V_4

61

2

Q53B

2N7002KDW

4

SYS_PWRGD

C848

*0.1u/16V_4

R547

*10_5%_6

BOARD ID

+3V

R123 10K_1%_4

R116 10K_1%_4

R118 *10K_1%_4

R610 10K_1%_4

R615 *10K_1%_4

R120 *10K_1%_4

+3V_S5

R589 *10K_1%_4

R99 *10K_1%_4

R109 *10K_1%_4

R97 *10K_1%_4

3

BOARD_ID0[24]

BOARD_ID1[24]

BOARD_ID3[24]

BOARD_ID5[6]

BOARD_ID6[6]

BOARD_ID0

R119 *10K_1%_4

BOARD_ID1

R113 *10K_1%_4

BOARD_ID2

R117 10K_1%_4

BOARD_ID3

R608 *10K_1%_4

BOARD_ID5

R616 10K_1%_4

BOARD_ID6

R612 10K_1%_4

BOARD_ID4

R582 10K_1%_4

BOARD_ID8

R91 10K_1%_4

BOARD_ID9

R108 10K_1%_4

BOARD_ID10

R98 10K_1%_4

2

GPIO

BOARD_ID0

BOARD_ID1

BOARD_ID2

BOARD_ID3

BOARD_ID4

BOARD_ID5

Normal,DD,Freesync

Reserve Reserve

nun-OD Panel OD Panel

Reserve Reserve

Reserve Reserve (Default)

BOARD_ID6

NA

BOARD_ID8

BOARD_ID9

BOARD_ID10

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Reserve Reserve

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

AM4 ACPI/AZ/SD/I2C/GPIO/FC

AM4 ACPI/AZ/SD/I2C/GPIO/FC

AM4 ACPI/AZ/SD/I2C/GPIO/FC

Tuesday, June 26, 2018

Tuesday, June 26, 2018

Tuesday, June 26, 2018

1

LowHigh

Reserve,DDNVSR,Normal,Freesync

Reserve,NVSR

(Default)

(Default)

ReserveReserve (Default)

NANA

ReserveReserve (Default)

ReserveReserve (Default)

(Default)

ZGX

ZGX

ZGX

5 59

5 59

5 59

1A

1A

1A

AMD read EDID data to get its device ID and manufacture code via AUX channel.(NO NVSR)

5

(CPU)

D D

GFX_PEG_CLKP[16]

GFX_PEG_CLKN[16]

CLK_PCIE_SSDP[28]

CLK_PCIE_SSDN[28]

CLK_PCIE_HUBP[14]

CLK_PCIE_HUBN[14]

C C

B B

C872 2.2p/50V_4

TXC:BG648000021 15PPM

HHE:BG648000026 15PPM

C864 2.2p/50V_4 TP84

CLK_PCI_EC[41]

CLK_LPC_DEBUG[30]

R57 *Short_4

R49 *CLKR@49.9_1%_4

R54 *CLKR@49.9_1%_4

R62 *Short_4

R53 *Short_4

R60 *Short_4

R59 *Short_4

TP85

1

2

Y2

48MHZ/15ppm

4

3

all XTAL need add TP2650 for ICT test

test pad must place in Bottom side

R638 22_1%_4

R627 22_1%_4

LPC_LAD0[30,41]

LPC_LAD1[30,41]

LPC_LAD2[30,41]

LPC_LAD3[30,41]

LPC_LFRAME#[30,41]

BOARD_ID6[5]

SERIRQ[41]

CLKRUN#[41]

BOARD_ID5[5]

GFX_PEG_CLKP_C

GFX_PEG_CLKN_C

CLK_PCIE_SSDP_C

CLK_PCIE_SSDN_C

CLK_PCIE_HUBP_C

CLK_PCIE_HUBN_C

48M_X1

R559

1M_1%_4

48M_X2

LPCCLK0

LPCCLK1

TP93

SPI_CLK

SPI_CS#

TP91

SPI_SO

SPI_SI

SPI_WP

SPI_HOLD#

TP92

4

U28E

AF6

GFX_CLK P

AF7

GFX_CLK N

AG5

GPP_CLK 0P

AG6

GPP_CLK 0N

AH4

GPP_CLK 1P

AH5

GPP_CLK 1N

AH7

GPP_CLK 2P

AH8

GPP_CLK 2N

AJ6

GPP_CLK 3P

AJ7

GPP_CLK 3N

AJ1

X48M_X1

AH1

X48M_X2

AU20

LPCCLK0 /EGPIO74

AU19

LPCCLK1 /EGPIO75

AW2 0

LAD0/EGP IO104

AV21

LAD1/EGP IO105

AT21

LAD2/EGP IO106

AT20

LAD3/EGP IO107

AW1 8

LFRAME_ L/EGPIO109

AT15

ESPI_ALER T_L/LDRQ0_L/EGP IO108

AW2 1

SERIRQ/AGPIO8 7

AV19

LPC_CLK RUN_L/AGPIO88

AV18

LPC_PD_ L/AGPIO21

AT18

EGPIO70

AW1 4

AT17

AW1 5

AU14

AU16

AV16

AV15

AU17

S0

SPI_CLK/ES PI_CLK

SPI_CS1_L /EGPIO118

SPI_CS2_L /ESPI_CS_L/EGPIO119

SPI_DI/ESPI_DAT 1

SPI_DO/ESP I_DAT0

SPI_WP _L/ESPI_DAT2/EGP IO122

SPI_HOLD_ L/ESPI_DAT3/EGPIO13 3

SPI_TPM_C S_L/AGPIO76

APU_AM4_SOCKET_1331P

33_S0

33_S0

CLK/USB/SPI/LPC

33_S0

33_S0

33_S0

TYPE2-18_S0

TYPE3-18_S5

AM4 REV 0.95

PART 5 OF 12

18_S5

T0 only

USB_HSD 0P

USB_HSD 0N

USB_HSD 1P

USB_HSD 1N

33_S5

USB_HSD 2P

USB_HSD 2N

USB_HSD 3P

USB_HSD 3N

USB0_ZV SS

USB1_ZV SS

USB2_ZV SS

USB3_ZV SS

T0 only

USB_SS_ ZVSS

T0 only

USB_SS_ ZVDDP

USB_SS_ 0TXP

USB_SS_ 0TXN

USB_SS_ 0RXP

USB_SS_ 0RXN

USB_SS_ 1TXP

USB_SS_ 1TXN

S5

USB_SS_ 1RXP

USB_SS_ 1RXN

USB_SS_ 2TXP

USB_SS_ 2TXN

EGPIO108-18/33_S0

USB_SS_ 2RXP

USB_SS_ 2RXN

USB_SS_ 3TXP

USB_SS_ 3TXN

USB_SS_ 3RXP

USB_SS_ 3RXN

48M_OSC

USB_ZVS S

AR7

AT11

AU7

AU8

AW8

AW9

AU10

AU11

AV9

AV10

AJ3

AN6

AK6

AK5

AJ4

AK8

AF3

AF4

Y3

Y4

AB1

AC1

AA2

AA3

AC3

AC4

AD2

AE2

AG2

AG3

AE1

AF1

3

48M_OSC

R103 *22_1%_4

TP16

2

AM4 USB"3.1" RX need through an 0.33uF AC-coupling capacitor.

USB0_ZVSS

USB1_ZVSS

USB2_ZVSS

USB3_ZVSS

USB2_APU_0P [40]

USB2_APU_0N [40]

USB2_APU_1P [40]

USB2_APU_1N [40]

USB2_APU_2P [30]

USB2_APU_2N [30]

USB2_APU_3P [36]

USB2_APU_3N [36]

R48 *200_1%_4

R87 *200_1%_4

R55 *200_1%_4

R65 *200_1%_4

USB3.0 Port 1 (DB)

USB3.0 Port 2 (DB)

Blue tooth

XBOX

C953 *22p/50V_4

+1.8_S0S5

R695 *Short_4

SPI_CLK

R670 10_5%_4

SPI EMI

SPI_SI

R673 *Short_4

SPI_SO

R671 *Short_4

R692 *10K_1%_4

SPI_WP

R688 *Short_4

SPI_CS_ASPI_CS#

SPI_SCK_A

SPI_SDI_A

SPI_SDO_A

SPI_WP_R

SP@ socket P/N: DG008000011 only for A-TEST

(FP:50960-0084n-001-8p-socket)

B-STAGE need change FP to soic8-7_9-1_27-2_16h

USB3_APU_TXP0 [40]

USB3_APU_TXN0 [40]

USB3_APU_RXP0 [40]

USB3_APU_RXN0 [40]

USB3_APU_TXP1 [40]

USB3_APU_TXN1 [40]

USB3_APU_RXP1 [40]

USB3_APU_RXN1 [40]

USB3.0 Port 1 (DB)

USB3.0 Port 2 (DB)

BIOS ROM(16MB)

+1.8_S0S5

R694

10K_1%_4

U29

1

TP106

TP99R58 *Short_4

TP102

TP101

TP105

CS

6

CLK

5

DI

2

DO

3

WP

SP@MX25U12835FM2I-10G

BIOS every pin need add TP2675(First)/TP2650 for ICT test

test pad must place in TOP side

VCC

HOLD

GND

8

7

4

1

+1.8_S0S5

TP31

TP100

R674

*10K_1%_4

SPI_HOLD#

06

C954

0.1u/16V_4

Type0 only Type0 only

R105

*10K_1%_4

R102

*2K_1%_4

4

+3V_S5 +3V_S5+3V +3V +3V

R95

*10K_1%_4

R100

*2K_1%_4

STRAPS PINS

R637

*10K_1%_4

LPCCLK0

LPCCLK1

LPC_LFRAME#

RTC_CLK[5]

A A

AGPIO3[5]

SYS_RST#[5,13]

5

SPI_SCK_A

R631

*2K_1%_4

R623

*10K_1%_4

R624

*2K_1%_4

R618

SR@10K_1%_4

R620

*SR@2K_1%_4

R566

10K_1%_4

R565

*2K_1%_4

+1.8_S0S5+3V_S5

R669

10K_1%_4

R672

*2K_1%_4

LPC_CLK0 LFRAME#

BOOT Fail Timer

ENABLE

PU

OOT Fail Timer

B

DISABLE

PD

DEFAULT

3

CZ/ST ONLY ZP ONLY

LPC_CLK1

Use 48Mhz crystal clock

and generate both internal

and external clocks

DEFAULT

Use 100Mhz PCIE clock as

reference clock and generate

internal clocks only

RTC_CLK AGPIO3

Coin battery

is on board.

Coin battery

isn't on board.

Enhanced Reset logic

(for quicker S5 resume) normal reset mode

Default to

traditional reset logic

2

SYS_RST#

SPI ROM

DEFAULTDEFAULT DEFAULT DEFAULT DEFAULT

LPC ROM

short reset mode

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Tuesday, June 26, 2018

Date: Sheet of

Tuesday, June 26, 2018

Date: Sheet of

Tuesday, June 26, 2018

PROJECT :

AM4 CLK/LPC/SPI/USB

AM4 CLK/LPC/SPI/USB

AM4 CLK/LPC/SPI/USB

SPI CLK(ZP)

Use 48Mhz crystal clock and

generate both internal and

external clocks

Use 100Mhz PCIE clock as

reference clock and generate

internal clocks only

ZGX

ZGX

ZGX

6 59

6 59

6 59

1

1A

1A

1A

5

(CPU)

TOP : Under the CPU

BOT : BOT CAVITY

C919

C914

22u/6.3V_6

22u/6.3V_6

D D

C489

22u/6.3V_6

TOP

C374

C311

22u/6.3V_6

22u/6.3V_6

C470

22u/6.3V_6

BOT

C279

C292

4.7u/6.3V_4

4.7u/6.3V_4

C C

B B

A A

TOP

C240

4.7u/6.3V_4

C276

0.22u/10V_4

C242

4.7u/6.3V_4

C299

0.22u/10V_4

C920

22u/6.3V_6

C476

22u/6.3V_6

C341

22u/6.3V_6

C373

22u/6.3V_6

C291

4.7u/6.3V_4

C238

4.7u/6.3V_4

C435

0.22u/10V_4

C908

22u/6.3V_6

C931

22u/6.3V_6

C409

22u/6.3V_6

C313

22u/6.3V_6

C414

4.7u/6.3V_4

C241

4.7u/6.3V_4

C319

0.22u/10V_4

C922

22u/6.3V_6

C930

22u/6.3V_6

C454

22u/6.3V_6

C312

22u/6.3V_6

C463

4.7u/6.3V_4

C243

4.7u/6.3V_4

C429

4.7u/6.3V_4

C385

0.22u/10V_4

C269

0.22u/10V_4

C915

22u/6.3V_6

C934

22u/6.3V_6

C434

22u/6.3V_6

C342

22u/6.3V_6

C237

4.7u/6.3V_4

C234

4.7u/6.3V_4

C274

4.7u/6.3V_4

C294

0.22u/10V_4

C239

0.22u/10V_4

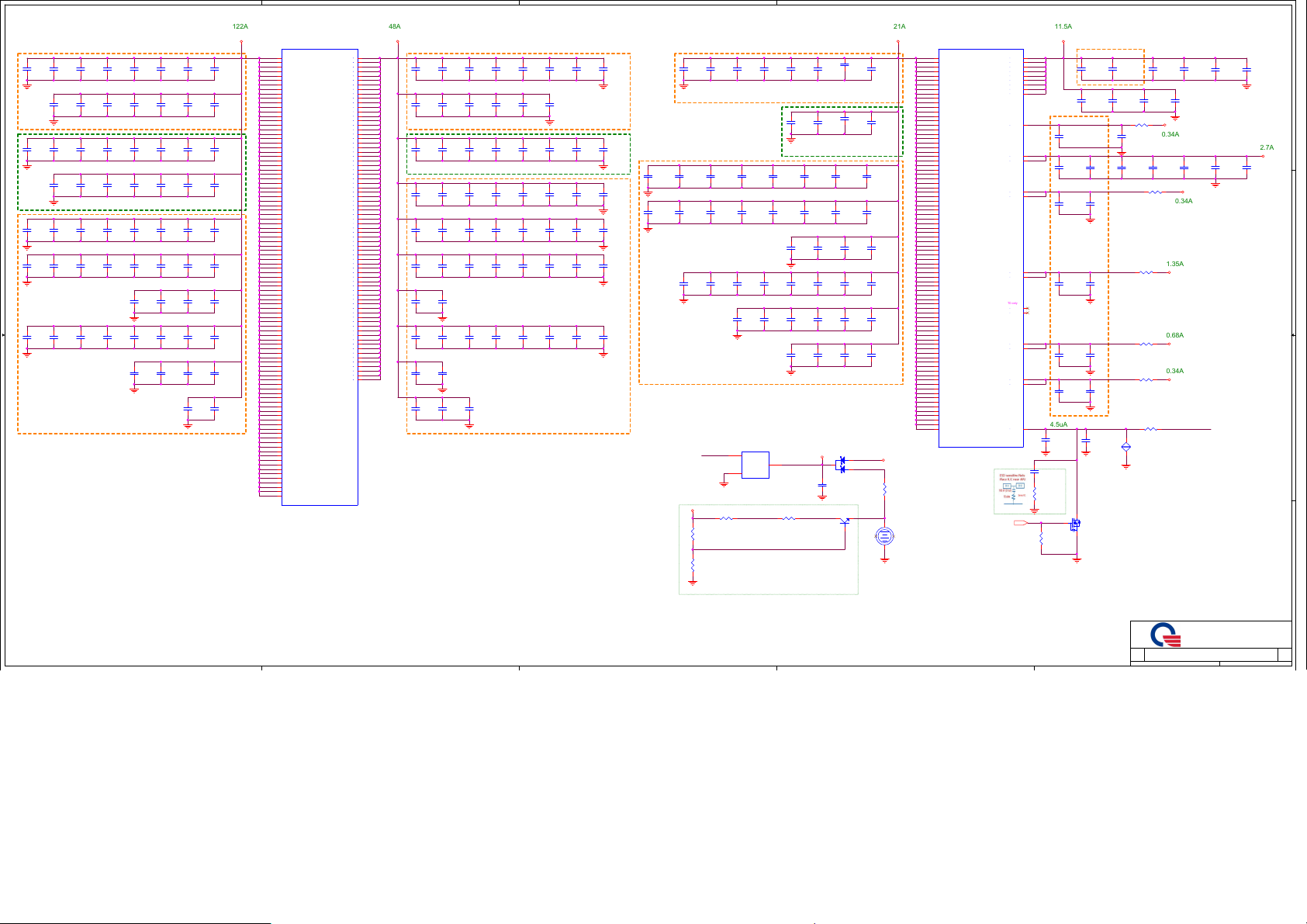

122

A

VDDCR_CPU VDDCR_NB +1.2VSUS VDDP

C447

C925

22u/6.3V_6

22u/6.3V_6

C911

C907

22u/6.3V_6

22u/6.3V_6

C347

C410

22u/6.3V_6

22u/6.3V_6

C444

C448

22u/6.3V_6

22u/6.3V_6

C446

C244

4.7u/6.3V_4

4.7u/6.3V_4

C248

C254

4.7u/6.3V_4

4.7u/6.3V_4

C456

C280

4.7u/6.3V_4

4.7u/6.3V_4

C267

C281

0.22u/10V_4

0.22u/10V_4

C293

C257

0.22u/10V_4

0.22u/10V_4

C282

C270

180p/50V_4

180p/50V_4

U28L

M7

VDDCR_CPU_1

N3

VDDCR_CPU_2

N6

VDDCR_CPU_3

P2

VDDCR_CPU_4

R7

VDDCR_CPU_5

T3

VDDCR_CPU_6

T6

VDDCR_CPU_7

T9

VDDCR_CPU_8

U2

VDDCR_CPU_9

U10

VDDCR_CPU_10

V9

VDDCR_CPU_11

V11

VDDCR_CPU_12

W3

VDDCR_CPU_13

W6

VDDCR_CPU_14

W10

VDDCR_CPU_15

W12

VDDCR_CPU_16

Y2

VDDCR_CPU_17

Y9

VDDCR_CPU_18

Y11

VDDCR_CPU_19

Y13

VDDCR_CPU_20

AA7

VDDCR_CPU_21

AA10

VDDCR_CPU_22

AA12

VDDCR_CPU_23

AB3

VDDCR_CPU_24

AB6

VDDCR_CPU_25

AB9

VDDCR_CPU_26

AB11

VDDCR_CPU_27

AB13

VDDCR_CPU_28

AC2

VDDCR_CPU_29

AC10

VDDCR_CPU_30

AC12

VDDCR_CPU_31

AD7

VDDCR_CPU_32

AD9

VDDCR_CPU_33

AD11

VDDCR_CPU_34

AD13

VDDCR_CPU_35

AE3

VDDCR_CPU_36

AE6

VDDCR_CPU_37

AE10

VDDCR_CPU_38

AE12

VDDCR_CPU_39

AF2

VDDCR_CPU_40

AF9

VDDCR_CPU_41

AF11

VDDCR_CPU_42

AF13

VDDCR_CPU_43

AG7

VDDCR_CPU_44

AG10

VDDCR_CPU_45

AG12

VDDCR_CPU_46

AG14

VDDCR_CPU_47

AG16

VDDCR_CPU_48

AG18

VDDCR_CPU_49

AG20

VDDCR_CPU_50

AG22

VDDCR_CPU_51

AG24

VDDCR_CPU_52

AG26

VDDCR_CPU_53

AH3

VDDCR_CPU_54

AH6

VDDCR_CPU_55

AH9

VDDCR_CPU_56

AH11

VDDCR_CPU_57

AH13

VDDCR_CPU_58

AH15

VDDCR_CPU_59

AH17

VDDCR_CPU_60

AH19

VDDCR_CPU_61

AH21

VDDCR_CPU_62

AH23

VDDCR_CPU_63

AH25

VDDCR_CPU_64

AH27

VDDCR_CPU_65

AJ2

VDDCR_CPU_66

AJ10

VDDCR_CPU_67

AJ12

VDDCR_CPU_68

AJ14

VDDCR_CPU_69

AJ22

VDDCR_CPU_70

AJ24

VDDCR_CPU_71

AK7

VDDCR_CPU_72

AK9

VDDCR_CPU_73

AK11

VDDCR_CPU_74

AK13

VDDCR_CPU_75

AL3

VDDCR_CPU_76

AL6

VDDCR_CPU_77

AL10

VDDCR_CPU_78

AL12

VDDCR_CPU_79

AL14

VDDCR_CPU_80

AM2

VDDCR_CPU_81

AM8

VDDCR_CPU_82

AN7

VDDCR_CPU_83

AN10

VDDCR_CPU_84

AN13

VDDCR_CPU_85

AP3

VDDCR_CPU_86

AP9

VDDCR_CPU_87

AP12

VDDCR_CPU_88

AR2

VDDCR_CPU_89

AT4

VDDCR_CPU_90

AU3

VDDCR_CPU_91

AU6

VDDCR_CPU_92

AU9

VDDCR_CPU_93

AU12

VDDCR_CPU_94

AU15

VDDCR_CPU_95

AV5

VDDCR_CPU_96

AV8

VDDCR_CPU_97

AV11

VDDCR_CPU_98

AV14

VDDCR_CPU_99

APU_AM4_SOCKET_1331P

AM4 REV 0.95

PART 12 OF 12

POWER

VDDCR_SOC_1

VDDCR_SOC_2

VDDCR_SOC_3

VDDCR_SOC_4

VDDCR_SOC_5

VDDCR_SOC_6

VDDCR_SOC_7

VDDCR_SOC_8

VDDCR_SOC_9

VDDCR_SOC_10

VDDCR_SOC_11

VDDCR_SOC_12

VDDCR_SOC_13

VDDCR_SOC_14

VDDCR_SOC_15

VDDCR_SOC_16

VDDCR_SOC_17

VDDCR_SOC_18

VDDCR_SOC_19

VDDCR_SOC_20

VDDCR_SOC_21

VDDCR_SOC_22

VDDCR_SOC_23

VDDCR_SOC_24

VDDCR_SOC_25

VDDCR_SOC_26

VDDCR_SOC_27

VDDCR_SOC_28

VDDCR_SOC_29

VDDCR_SOC_30

VDDCR_SOC_31

VDDCR_SOC_32

VDDCR_SOC_33

VDDCR_SOC_34

VDDCR_SOC_35

VDDCR_SOC_36

VDDCR_SOC_37

VDDCR_SOC_38

VDDCR_SOC_39

VDDCR_SOC_40

VDDCR_SOC_41

VDDCR_SOC_42

VDDCR_SOC_43

VDDCR_SOC_44

VDDCR_SOC_45

VDDCR_SOC_46

VDDCR_SOC_47

VDDCR_SOC_48

VDDCR_SOC_49

VDDCR_SOC_50

VDDCR_SOC_51

VDDCR_SOC_52

VDDCR_SOC_53

VDDCR_SOC_54

VDDCR_SOC_55

VDDCR_SOC_56

VDDCR_SOC_57

VDDCR_SOC_58

VDDCR_SOC_59

VDDCR_SOC_60

VDDCR_SOC_61

VDDCR_SOC_62

VDDCR_SOC_63

VDDCR_SOC_64

VDDCR_SOC_65

VDDCR_SOC_66

VDDCR_SOC_67

VDDCR_SOC_68

VDDCR_SOC_69

VDDCR_SOC_70

VDDCR_SOC_71

VDDCR_SOC_72

VDDCR_SOC_73

4

48A

B5

B8

B11

B14

B17

B20

C4

C7

C10

C13

C16

C19

D3

E2

F7

F10

F13

F16

G3

G6

G9

G12

G15

G18

H2

J7

J10

J12

J14

J16

K3

K6

K9

K11

K13

K15

L2

L10

L12

L14

L16

L18

L20

L22

L24

L26

M9

M11

M13

M15

M17

M19

M21

M23

M25

N10

N12

N14

N16

N18

N20

N22

N24

N26

P9

P11

P13

R10

R12

T11

T13

U12

V13

C929

22u/6.3V_6

C439

22u/6.3V_6

C372

22u/6.3V_6

C390

4.7u/6.3V_4

C449

4.7u/6.3V_4

C324

4.7u/6.3V_4

C250

4.7u/6.3V_4

C305

0.22u/10V_4

C490

0.22u/10V_4

C488

180p/50V_4

C913

22u/6.3V_6

C247

22u/6.3V_6

C437

22u/6.3V_6

C403

4.7u/6.3V_4

C289

4.7u/6.3V_4

C360

4.7u/6.3V_4

C478

4.7u/6.3V_4

C349

0.22u/10V_4

C475

0.22u/10V_4

C462

180p/50V_4

C927

22u/6.3V_6

C466

22u/6.3V_6

C452

22u/6.3V_6

C283

4.7u/6.3V_4

C338

4.7u/6.3V_4

C450

4.7u/6.3V_4

C458

0.22u/10V_4

C477

180p/50V_4

C918

22u/6.3V_6

C932

22u/6.3V_6

C438

22u/6.3V_6

C334

4.7u/6.3V_4

C396

4.7u/6.3V_4

C278

4.7u/6.3V_4

C442

0.22u/10V_4

C393

22u/6.3V_6

C906

22u/6.3V_6

C320

22u/6.3V_6

C370

4.7u/6.3V_4

C275

4.7u/6.3V_4

C371

4.7u/6.3V_4

C441

0.22u/10V_4

C924

22u/6.3V_6

C310

22u/6.3V_6

C345

22u/6.3V_6

C430

4.7u/6.3V_4

C272

4.7u/6.3V_4

C433

4.7u/6.3V_4

C492

0.22u/10V_4

C344

22u/6.3V_6

C465

22u/6.3V_6

C431

4.7u/6.3V_4

C251

4.7u/6.3V_4

C246

4.7u/6.3V_4

C471

0.22u/10V_4

C928

22u/6.3V_6

OP

T

C408

22u/6.3V_6

BOT

C245

4.7u/6.3V_4

C277

4.7u/6.3V_4

C309

4.7u/6.3V_4

C300

0.22u/10V_4

TOP

3

C935

22u/6.3V_6

C933

22u/6.3V_6

C936

22u/6.3V_6

C464

22u/6.3V_6

C937

22u/6.3V_6

C468

22u/6.3V_6

C500

22u/6.3V_6

TOP

C486

22u/6.3V_6

22u/6.3V_6

22u/6.3V_6

C481

C482

BOT

C521

C504

4.7u/6.3V_4

C506

4.7u/6.3V_4

4.7u/6.3V_4

C525

4.7u/6.3V_4

C512

0.22u/10V_4

C509

4.7u/6.3V_4

C502

4.7u/6.3V_4

C507

0.22u/10V_4

C493

4.7u/6.3V_4

C518

4.7u/6.3V_4

C473

0.22u/10V_4

C529

0.22u/10V_4

C513

4.7u/6.3V_4

C503

4.7u/6.3V_4

C508

0.22u/10V_4

C479

0.22u/10V_4

C515

4.7u/6.3V_4

C472

0.22u/10V_4

C491

0.22u/10V_4

C496

180p/50V_4

C511

4.7u/6.3V_4

C494

4.7u/6.3V_4

C497

4.7u/6.3V_4

C524

0.22u/10V_4

C517

0.22u/10V_4

C514

180p/50V_4

C510

4.7u/6.3V_4

C495

4.7u/6.3V_4

C519

4.7u/6.3V_4

C499

0.22u/10V_4

C520

0.22u/10V_4

C505

180p/50V_4

TOP

Q38

+5V_S5

20MIL

R297

68.1K_1%_ 4

R298

150K_1%_4

+1.5V_RTC

1

VOUT

2

GND

AP2138N-1.5TRG1

R304 4.7K_5%_4

20MIL

3

VIN

+VCCRTC_4 +VCCRTC_3

R293 4.7K_5%_4

+VCCRTC_5

20MIL20MIL

20MIL

+3VRTC

3

C743

1u/6.3V_4

D24

BAT54CW

2

1

13

Q43METR3 904-G

2

Charge function

+VCCRTC_2

C467

22u/6.3V_6

C480

22u/6.3V_6

C522

4.7u/6.3V_4

C501

4.7u/6.3V_4

C526

4.7u/6.3V_4

C498

0.22u/10V_4

C516

0.22u/10V_4

C487

180p/50V_4

+3VPCU

+BAT

12

+ -

20MIL

20MIL

2

21A

R294

1K_1%_4

CN19

AAA-BAT-046-K03

34

U28F

K36

VDDIO_MEM_S3_1

K39

VDDIO_MEM_S3_2

L32

VDDIO_MEM_S3_3

L35

VDDIO_MEM_S3_4

L38

VDDIO_MEM_S3_5

M29

VDDIO_MEM_S3_6

M31

VDDIO_MEM_S3_7

M34

VDDIO_MEM_S3_8

M37

VDDIO_MEM_S3_9

N28

VDDIO_MEM_S3_10

N30

VDDIO_MEM_S3_11

N33

VDDIO_MEM_S3_12

N36

VDDIO_MEM_S3_13

N39

VDDIO_MEM_S3_14

P27

VDDIO_MEM_S3_15

P29

VDDIO_MEM_S3_16

P32

VDDIO_MEM_S3_17

P35

VDDIO_MEM_S3_18

P38

VDDIO_MEM_S3_19

R28

VDDIO_MEM_S3_20

R31

VDDIO_MEM_S3_21

R34

VDDIO_MEM_S3_22

R37

VDDIO_MEM_S3_23

T27

VDDIO_MEM_S3_24

T29

VDDIO_MEM_S3_25

T33

VDDIO_MEM_S3_26

T36

VDDIO_MEM_S3_27

T39

VDDIO_MEM_S3_28

U28

VDDIO_MEM_S3_29

U30

VDDIO_MEM_S3_30

U32

VDDIO_MEM_S3_31

U35

VDDIO_MEM_S3_32

U38

VDDIO_MEM_S3_33

V27

VDDIO_MEM_S3_34

V29

VDDIO_MEM_S3_35

V31

VDDIO_MEM_S3_36

V34

VDDIO_MEM_S3_37

V37

VDDIO_MEM_S3_38

W28

VDDIO_MEM_S3_39

W33

VDDIO_MEM_S3_40

W34

VDDIO_MEM_S3_41

W36

VDDIO_MEM_S3_42

W39

VDDIO_MEM_S3_43

Y27

VDDIO_MEM_S3_44

Y29

VDDIO_MEM_S3_45

Y31

VDDIO_MEM_S3_46

Y32

VDDIO_MEM_S3_47

Y35

VDDIO_MEM_S3_48

Y38

VDDIO_MEM_S3_49

AA28

VDDIO_MEM_S3_50

AA34

VDDIO_MEM_S3_51

AA37

VDDIO_MEM_S3_52

AB27

VDDIO_MEM_S3_53

AB29

VDDIO_MEM_S3_54

AB31

VDDIO_MEM_S3_55

AB32

VDDIO_MEM_S3_56

AB33

VDDIO_MEM_S3_57

AB36

VDDIO_MEM_S3_58

AB39

VDDIO_MEM_S3_59

AC28

VDDIO_MEM_S3_60

AC30

VDDIO_MEM_S3_61

AC32

VDDIO_MEM_S3_62

AC35

VDDIO_MEM_S3_63

AC38

VDDIO_MEM_S3_64

AD27

VDDIO_MEM_S3_65

AD29

VDDIO_MEM_S3_66

AD31

VDDIO_MEM_S3_67

AD34

VDDIO_MEM_S3_68

AD37

VDDIO_MEM_S3_69

AE28

VDDIO_MEM_S3_70

AE30

VDDIO_MEM_S3_71

AE33

VDDIO_MEM_S3_72

AE36

VDDIO_MEM_S3_73

AE39

VDDIO_MEM_S3_74

AF27

VDDIO_MEM_S3_75

AF29

VDDIO_MEM_S3_76

AF32

VDDIO_MEM_S3_77

AF35

VDDIO_MEM_S3_78

AF38

VDDIO_MEM_S3_79

AG33

VDDIO_MEM_S3_80

AG34

VDDIO_MEM_S3_81

AG35

VDDIO_MEM_S3_82

AG37

VDDIO_MEM_S3_83

AH39

VDDIO_MEM_S3_84

APU_AM4_SOCKET_1331P

POWER

VDDCR_SOC_S5_1

VDDCR_SOC_S5_2

AM4 REV 0.95

PART 6 OF 12

RTC(RTC)

VDDP_1

VDDP_2

VDDP_3

VDDP_4

VDDP_5

VDDP_6

VDDP_7

VDDP_8

VDDP_9

VDDIO_AUDIO

VDD_18_1

VDD_18_2

VDD_33_1

VDD_33_2

VDDP_S5_1

VDDP_S5_2

T0 only

VDD_18_S5_1

VDD_18_S5_2

VDD_33_S5_1

VDD_33_S5_2

VDDBT_RTC_G

CLR_CMOS[41]

For EC reset RTC

1

11.5A

07

C1182

*0.1u/16V_4

R934

*10_5%_6

R987

100K_1%_4

VDDIO_AUDIO

VDD_33

TOP

VDDP_S5_C

VDD_18_S5

VDD_33_S5

4.5uA

C317

0.22u/10V_4

2

C318

0.22u/10V_4

C455

22u/6.3V_6

C453

0.22u/10V_4

C348

0.22u/10V_4

C343

0.22u/10V_4

C436

0.22u/10V_4

+1.5V_RTC_RST#

3

1

TOP

Q71

2N7002K

C386

*22u/6.3V_6

C483

*0.22u/10V_4

C440

0.22u/10V_4

C457

10u/6.3V_4

C353

10u/6.3V_4

C346

10u/6.3V_4

C387

10u/6.3V_4

20MIL

C322

1u/6.3V_4

C415

*22u/6.3V_6

C461

*180p/50V_4

R133 *Short_4

C407

10u/6.3V_4

C388

0.22u/10V_4

R138 *Short_4

R136 *Short_8

R127 *Short_4

R140 *Short_4

R950 1K_1%_4

12

G1

*SHORT_PAD

C459

*22u/6.3V_6

C432

*180p/50V_4

C384

0.1u/16V_4

C484

*10u/6.3V_4

C411

22u/6.3V_6

C485

*10u/6.3V_4

C445

22u/6.3V_6

2.7

A

+1.8V

C460

*22u/6.3V_6

C391

*180p/50V_4

+1.8V

0.34A

C443

0.22u/10V_4

+3V

0.34A

1.35A

VDDP_S5

0.68A

+1.8V_S5

0.34A

+3V_S5

+1.5V_RTC

AM18

AM19

AM20

AN18

AN19

AN20

AP18

AP19

AP20

AM15

AJ20

AK20

AJ21

AK21

AJ16

AJ17

AJ18

AK18

AJ15

AK15

AJ19

AK19

AL15

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

ZGX

PROJECT :

ZGX

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

AM4 POWER

AM4 POWER

AM4 POWER

Date: Sheet of

Tuesday, June 26, 2018

Date: Sheet of

Tuesday, June 26, 2018

Date: Sheet of

5

4

3

2

Tuesday, June 26, 2018

1

ZGX

7 59

7 59

7 59

1A

1A

1A

5

(CPU)

D D

C C

B B

U28G

J15

L29

AJ11

A12

A15

A18

A21

A24

A27

A30

A33

A36

B19

B23

B26

B29

B32

B35

C22

C25

C28

C31

C34

C37

D12

D15

D18

D19

D21

D22

D23

D24

D25

D27

D29

D30

D31

D32

D33

D34

D35

D36

D39

E11

E14

E17

E20

E21

E23

E26

E27

E29

E32

A3

A6

A9

C1

D6

D9

E4

E5

E8

GND

VSS_397

VSS_398

VSS_399

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

AM4 REV 0.95

PART 7 OF 12

APU_AM4_SOCKET_1331P

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

E35

E38

F1

F4

F17

F19

F22

F25

F28

F31

F34

F35

F37

G7

G21

G24

G27

G30

G33

G35

G36

G39

H4

H5

H8

H11

H14

H17

H20

H23

H26

H29

H32

H35

H38

J1

J4

J8

J9

J11

J13

J17

J19

J22

J25

J28

J31

J34

J35

J37

K10

K12

K18

K20

K21

K22

K23

K26

K27

K28

K29

K30

4

U28H

K33

L11

L13

L15

L17

L19

L21

L25

L27

L28

L30

L31

M10

M12

M14

M16

M18

M20

M24

M26

M27

M28

N11

N13

N15

N17

N19

N21

N23

N25

N27

N29

P10

P12

R11

R13

R27

R29

T10

T12

T28

T30

U11

L4

L5

L8

L9

M1

M4

M8

N9

P4

P5

P8

R1

R4

R8

R9

U4

U5

U8

U9

GND

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

VSS_182

VSS_183

AM4 REV 0.95

PART 8 OF 12

APU_AM4_SOCKET_1331P

VSS_184

VSS_185

VSS_186

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_215

VSS_214

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

VSS_243

VSS_244

VSS_245

U13

U27

U29

U31

V1

V4

V7

V10

V12

V28

V30

W9

W11

W13

W27

W29

W31

Y5

Y8

Y10

Y12

Y28

Y30

AA1

AA4

AA6

AA9

AA11

AA13

AA27

AA31

AA29

AB7

AB10

AB12

AB28

AB30

AC5

AC8

AC9

AC11

AC13

AC27

AC29

AC31

AD1

AD4

AD10

AD12

AD28

AD30

AE7

AE9

AE11

AE13

AE27

AE29

AE31

AF5

AF8

AF10

AF12

U28J

AF28

VSS_246

AF30

VSS_247

AG1

VSS_248

AG4

VSS_249

AG8

VSS_250

AG9

VSS_251

AG11

VSS_252

AG13

VSS_253

AG15

VSS_254

AG17

VSS_255

AG19

VSS_256

AG21

VSS_257

AG23

VSS_258

AG25

VSS_259

AG27

VSS_260

AG28

VSS_261

AG29

VSS_262

AG30

VSS_263

AG31

VSS_264

AG32

VSS_265

AH10

VSS_266

AH12

VSS_267

AH14

VSS_268

AH16

VSS_269

AH18

VSS_270

AH20

VSS_271

AH22

VSS_272

AH24

VSS_273

AH26

VSS_274

AH28

VSS_275

AH29

VSS_276

AH30

VSS_277

AH33

VSS_278

AJ5

VSS_279

AJ8

VSS_280

AJ9

VSS_281

AJ13

VSS_282

AJ23

VSS_283

AJ25

VSS_284

AJ26

VSS_285

AJ27

VSS_286

AJ28

VSS_287

AJ29

VSS_288

AJ32

VSS_289

AJ35

VSS_290

AJ36

VSS_291

AJ38

VSS_292

AK1

VSS_293

AK4

VSS_294

AK10

VSS_295

AK12

VSS_296

AK14

VSS_297

AK22

VSS_298

AK25

VSS_299

AK28

VSS_300

AK31

VSS_301