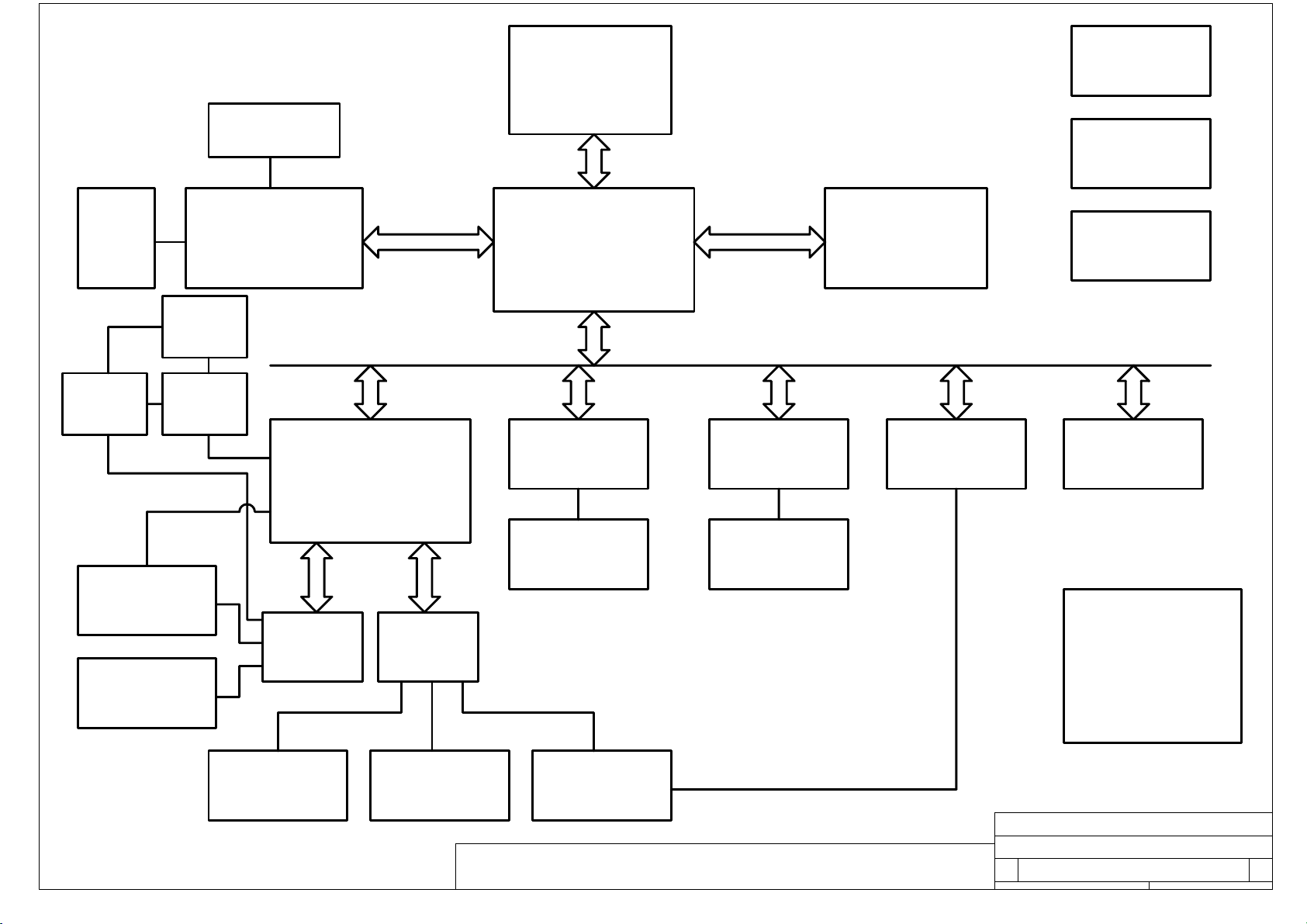

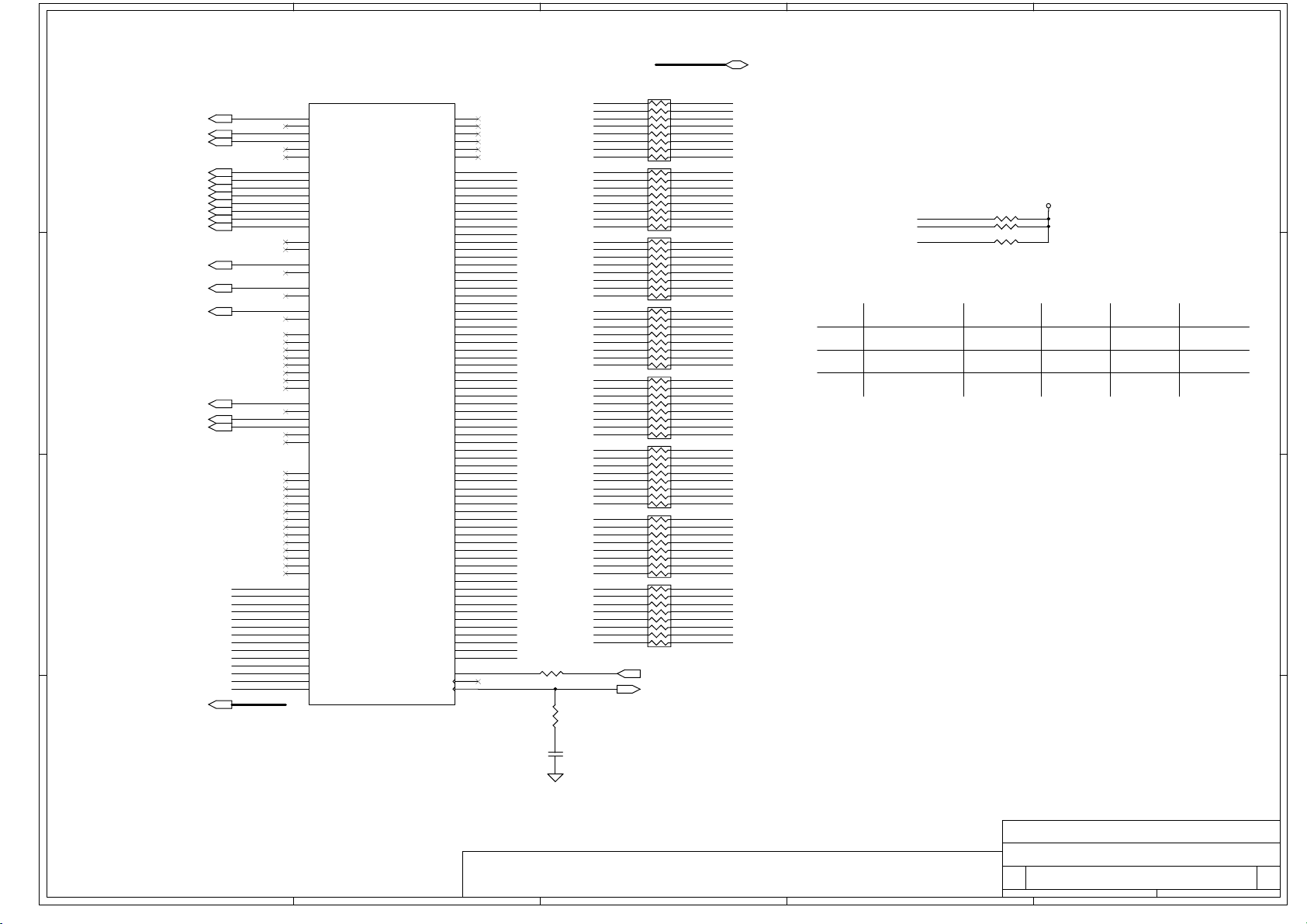

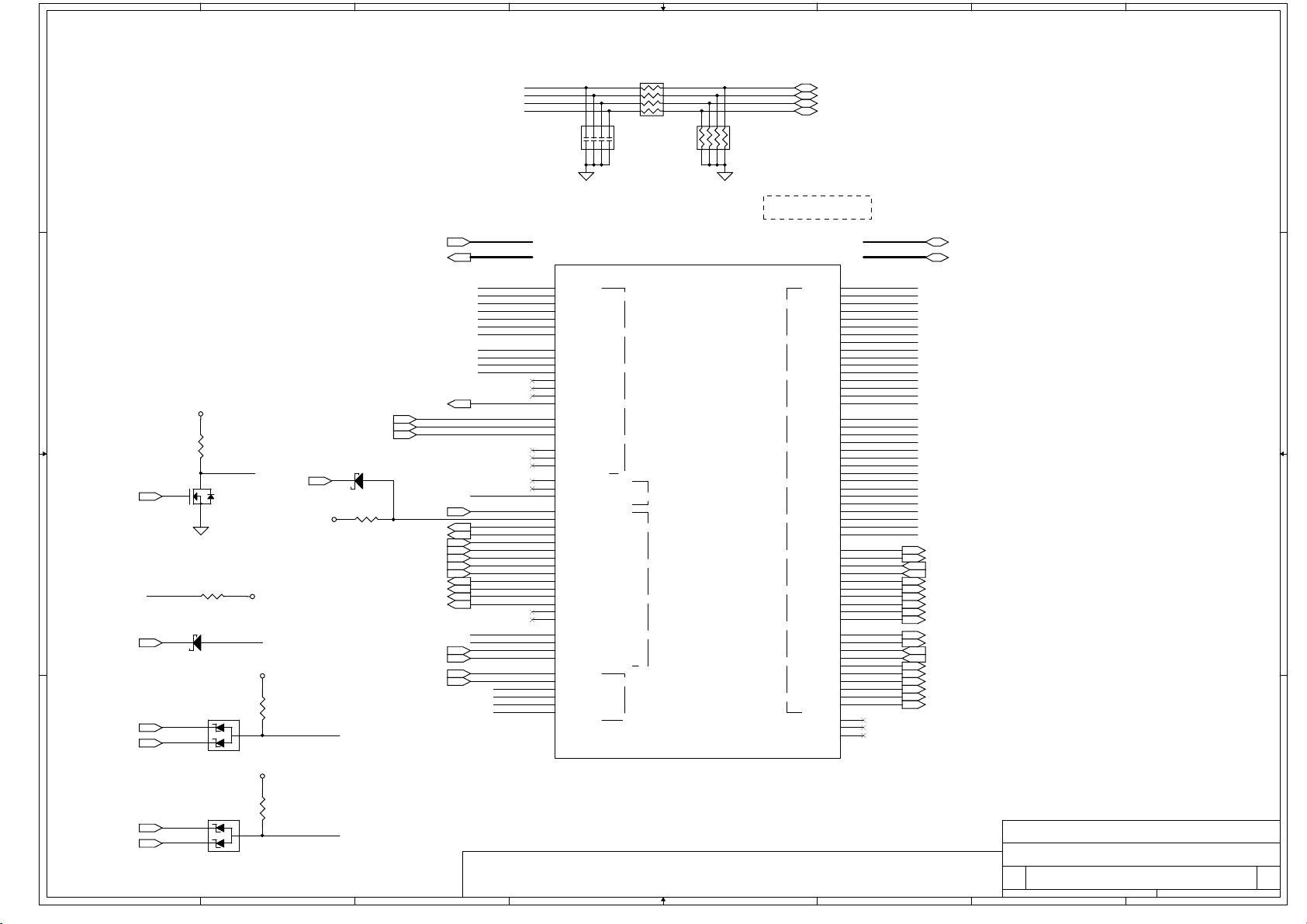

Acer LA-854 Schematics

COMPAL CONFIDENTIAL

MODEL NAME : 888F2 LA854

REV:0.1

LCD & CRT

PAGE 17

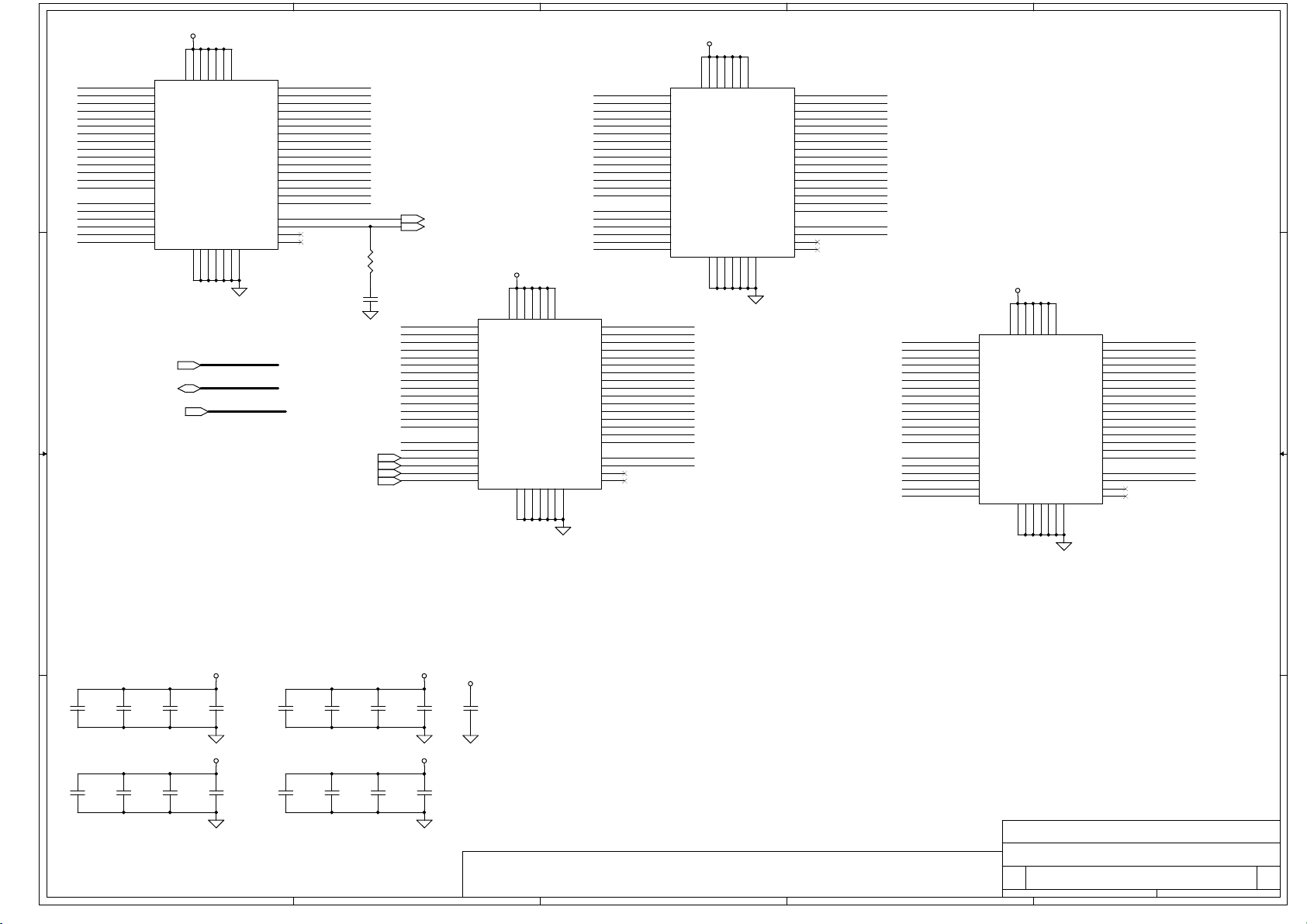

Celeron

uBGA2/uPGA2

CPU

PAGE 2,3

PSB

CLOCK

ICS9248-92

PAGE 12

PCI / ISA

PULL UP/DOWN

RESISTERS

PAGE 13

SGRAM

INTERNAL IDE

IDE/FDD

PAGE 22

FIR/USB

LPT PORT

PAGE 16

PIRQA#

Direct CD

Play

PAGE 21

IDE

Damping

PAGE 20

PAGE 32

PAGE 31

VGA

ATI Mobility P

PAGE 14,15

BUS#0,DEV#7

FUNC 0: PCI-TO-ISA BRIDGE

FUNC 1: IDE INTERFACE

FUNC 2: USB INTERFACE

FUNC 3: POWER MANAGEMENT

ISA

SIO

FDC37N869

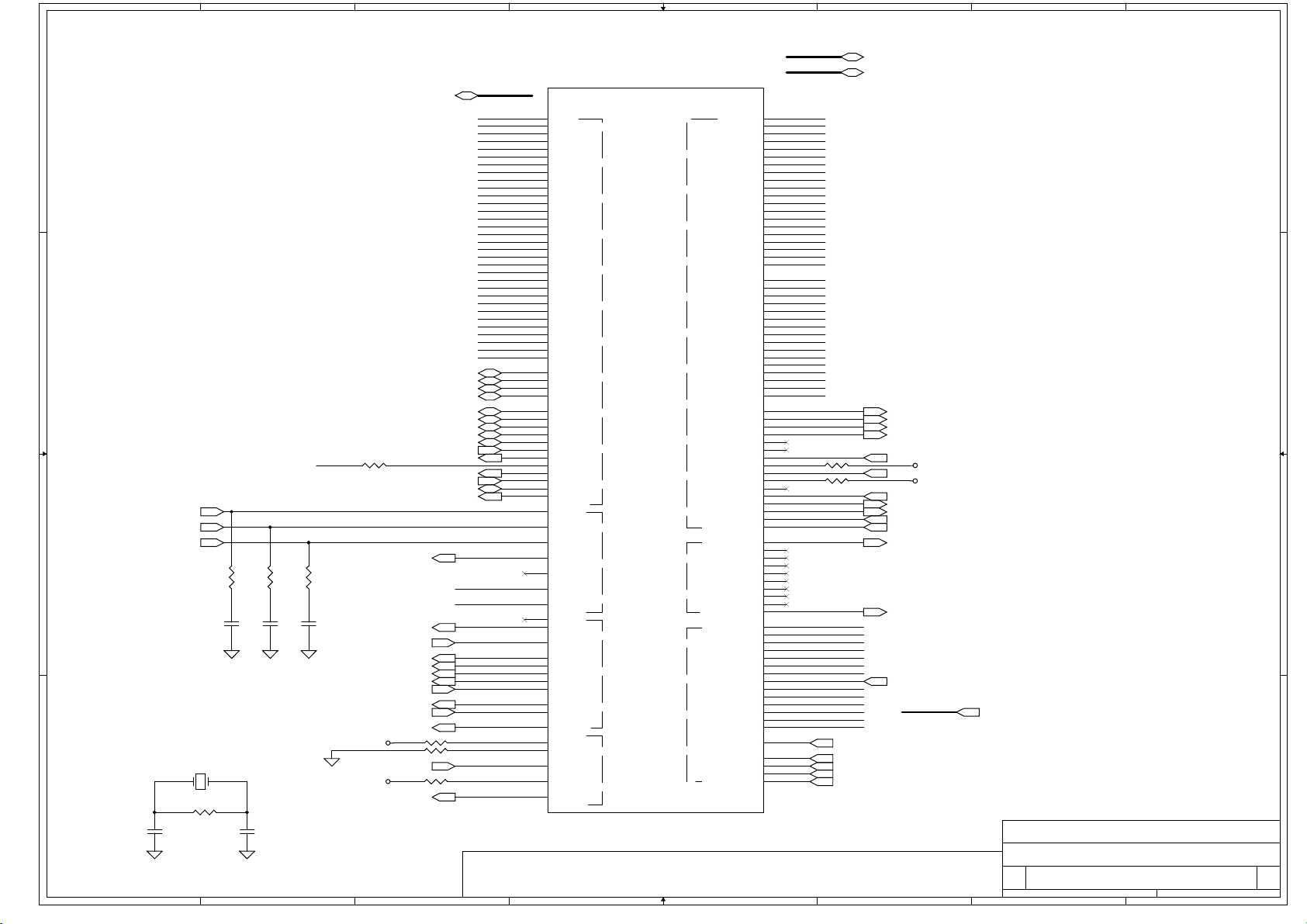

PIIX4M

PAGE 30

PCI BUS

IDSEL: AD1 8

PIRQD#

PAGE 9,10,11

ISA

EC/KBC

PC87570

PAGE 23

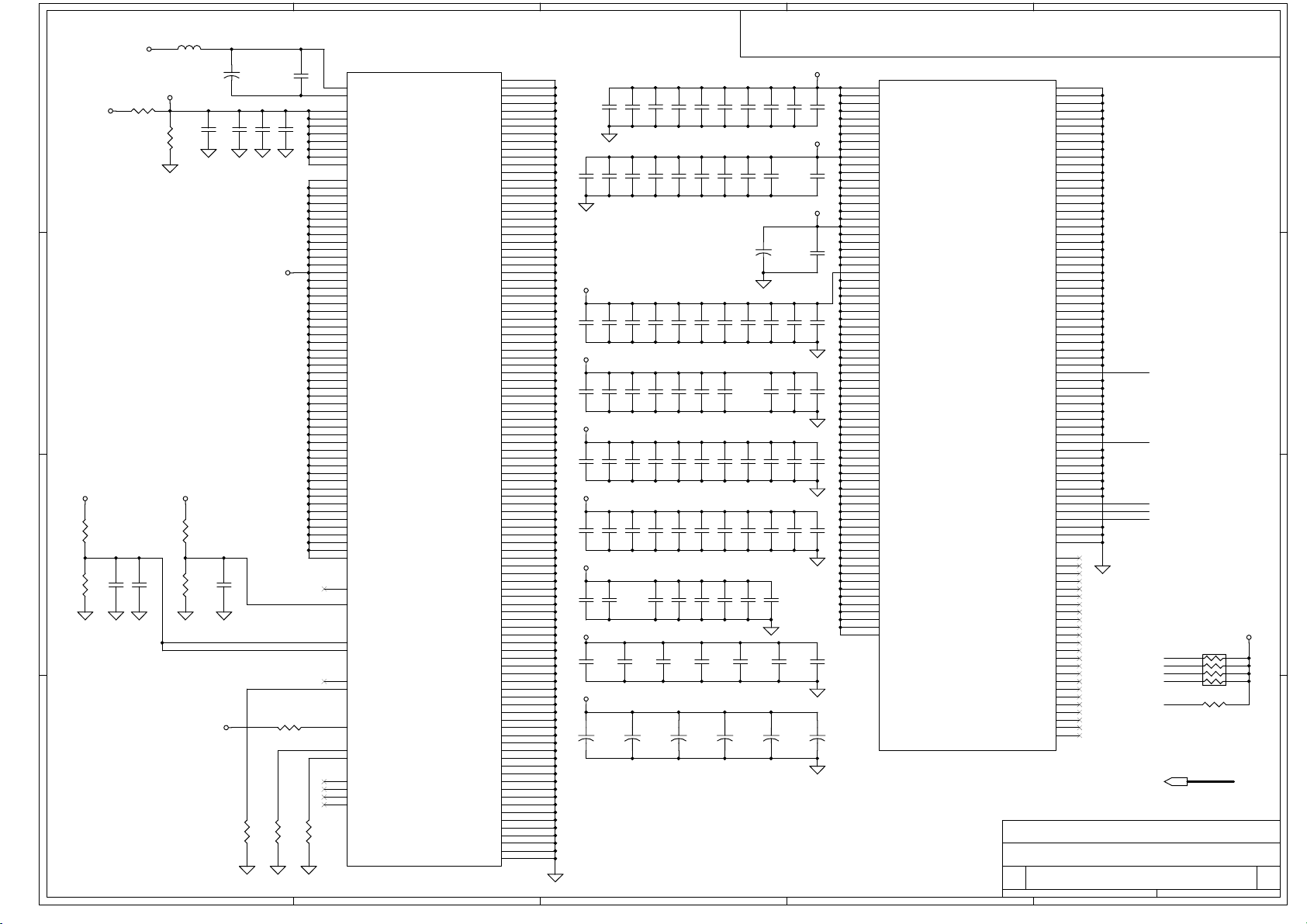

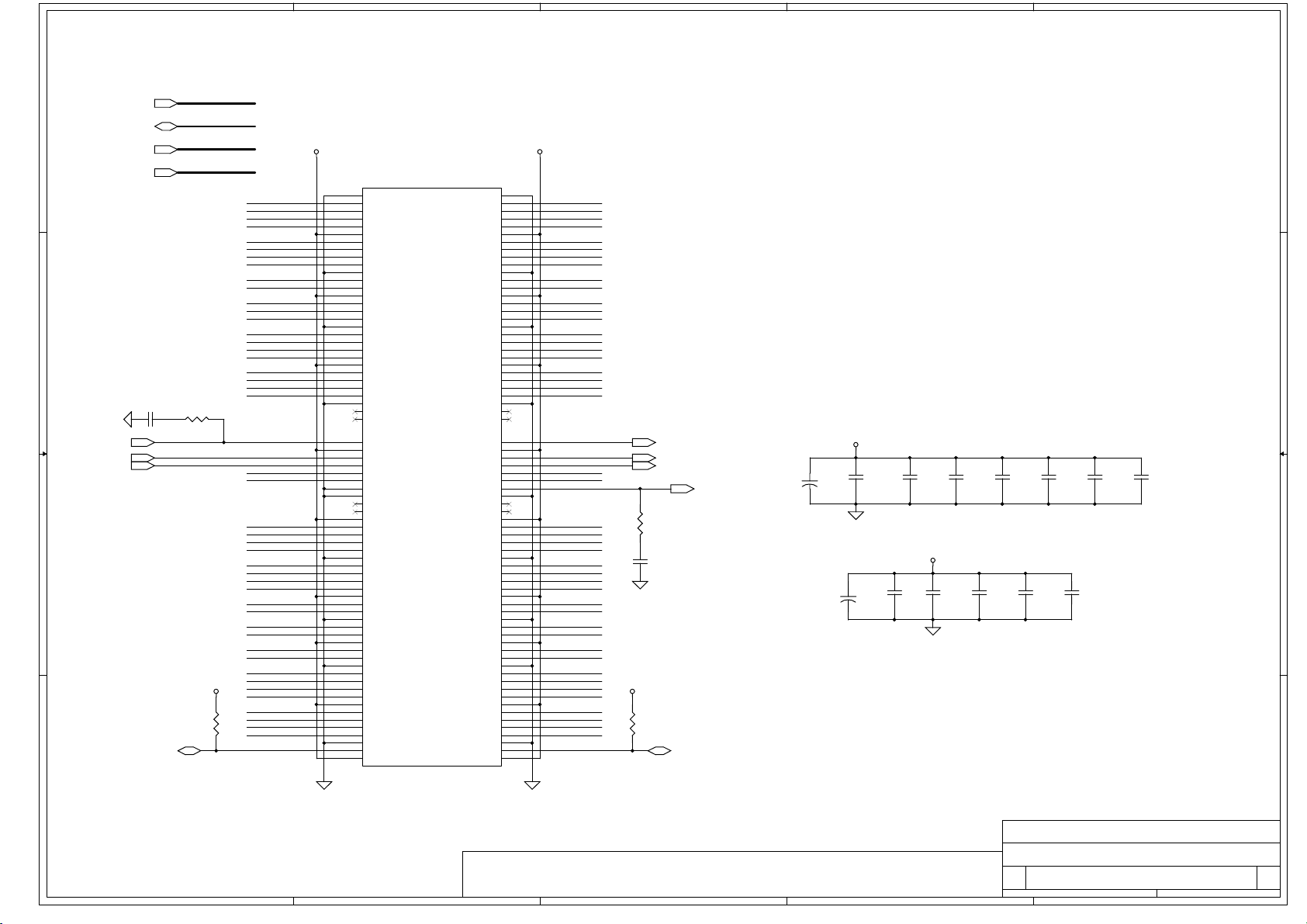

443ZX-100M

BUS#0,DEV#0

IDSEL: AD1 1

HOST-TO-PCI BRIDGE

BUS#0,DEV#1

IDSEL: AD1 2

PCI-TO-PCI BRIDGE

PAGE 4,5,6

IDSEL: AD2 4

MASTER 2

PIRQB#

1394 OHCI

TSB12LV26

PAGE 26

1394 PHY

TSB41LV01

PAGE 27

MEMORY BUSAGP BUS

CARDBUS

PCI1420

PCMCIA

SOCKET

SODIMM

-BANK 2,3

ON BOARD 32/64MB

-BANK 0

PAGE 7,8

IDSEL: AD1 5

MASTER 3

PIRQA#, PIRQB#

SIRQ

IDSEL: AD1 9

MASTER 4

PIRQC#

AUDIO

CS4281-CQ

PAGE 18 PAGE 28

AC LINK

PAGE 19

POWER

INTERFACE

PAGE 25,35

IDSEL: AD27, A D28

MASTER 0, 1

PIRQD#

Mini PCI

Connector

PAGE 29

DC/DC POWER

+2.5V POWER

CPU_IO POWER

+3VALW POWER

+5VALW POWER

+12VALW POWER

CPU_CORE POWER

PAGE 36,37,38,39

TRACK POINT

PS2/KB

INTERFACE

BIOS

EC BUFFER

PAGE 24PAGE 33 PAGE 34

PROPRIETARY NOTE

Switchs &

Connectors

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Compal Electronics, Inc.

Title

SCHEMATIC, M/B LA-854

Size Document Number Rev

B

401172

Date: Sheet

140Saturday, December 23, 2000

of

0C

A

B

C

D

E

D10

D11

C7

C8

B9

A9

C10

B11

C12

B13

A14

B12

E12

B16

A13

D13

D15

D12

B14

E14

C13

A19

B17

A18

C17

D17

C18

B19

D18

B20

A20

B21

D19

C21

E18

C20

F19

D20

D21

H18

F18

J18

F21

E20

H19

E21

J20

H21

L18

G20

P18

G21

K18

K21

M18

L21

R19

K19

T20

J21

L20

M19

U18

R18

V20

T21

U21

R21

V18

P21

P20

U19

AA3

T1

AA18

Y20

AB21

AA10

AC9

A6

M3

AA16

R318

110_1%

HD#[0..63]

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

R312 1K

CPUINIT#

FLUSH#

CPURST#

C

1 2

12

C118

10PF

R66

10

HD#[0..63] 4

DBSY# 4

DRDY# 4

CPUINIT# 9

CPURST# 4

HCLK_CPU 4,12

2200PF

+5VS

12

16

15

14

13

12

11

10

R132

1K

D9

RB751V

R133

200

12

+5VS

12

R134

1K

NMI

INTR

IGNNE#

A20M#

SLP#

CPUINIT#

STPCLK#

FLUSH#

IERR#

SMI#

PREQ#

CPURST#

PWRGD_CPU

21

from 87570

SMC 21,23,24

SMD 21,23,24

ATF#

RP26

1 8

2 7

3 6

4 5

8P4R-1.5K

1 2

R100 1.5K

1 2

R102 1K

1 2

R101 680

1 2

R320 1.5K

1 2

R321 1.5K

1 2

R104 270

1 2

R313 1.5K

1 2

R24 56.2_1%

1 2

R112 1.5K

ATF# 24

CPU_IO

+2.5V_CLK

12

C199

.1UF

12

C453

THERMDA

THERMDC

1617VCC

U11

1

NC

2

VCC

3

DXP

4

DXN

5

NC

6

ADD1

7

GND

8 9

GND NC

MAX1617

VR_POK35,39

STBY

SMBCLK

SMBDATA

ALERT

ADD0

NC

NC

Compal Electronics, Inc.

Title

SCHEMATIC, M/B LA-854

Size Document Number Rev

B

401172

D

Date: Sheet

240Saturday, December 23, 2000

E

0C

of

IERR#

A20M#

FERR#1.5

IGNNE#

PWRGD_CPU

SMI#

PREQ#

12

12

12

12

INTR

NMI

STPCLK#

SLP#

THERMDA

THERMDC

HA#[3..31]

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

AB2

AA1

AB1

AD9

AA21

W21

W19

AA2

AD10

AC12

AC13

AB10

AC15

AD13

AD14

AA14

AA11

AB20

W20

AA12

AB15

AB18

AC19

AC11

AB12

AA15

AB16

V21

Y21

L3

K3

J2

L4

L1

K5

K1

J1

J3

K4

G1

H1

E4

F1

F4

F2

E1

C4

D3

D1

E2

D5

D4

C3

C1

B3

A3

B2

C2

A4

A5

B4

C5

T2

V4

V2

W3

W5

W2

Y2

E6

C6

U4

T4

R1

V1

Y4

U3

U2

U1

W1

Y1

V5

U44A

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

RP#

ADS#

AERR#

AP0#

AP1#

BERR#

BINIT#

IERR#

BREQ0#

BPRI#

BNR#

LOCK#

HIT#

HITM#

DEFER#

BP2#

BP3#

BPM0#

BPM1#

TRDY#

RS0#

RS1#

RS2#

RSP#

A20M#

FERR#

IGNNE#

PWRGOOD

SMI#

TDO

TDI

TMS

TRST#

TCK

PREQ#

PRDY#

SELPSB0

SELPSB1

INTR/LINT0

NMI/LINT1

STPCLK#

SLP#

THERMDA

THERMDC

MICRO-PGA

REQUEST

PHASE

SIGNALS

ERROR

SIGNALS

ARBITRATION

PHASE

SIGNALS

SNOOP PHASE

SIGNALS

RESPONSE

PHASE

SIGNALS

PC

COMPATIBILITY

SIGNALS

DIAGNOSTIC

& TEST

SIGNALS

EXECUTION

CONTROL

SIGNALS

THERMAL DIODE

B

COPPERMINE

DATA

PHASE

SIGNALS

PROPRIETARY NOTE

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DEP0#

DEP1#

DEP2#

DEP3#

DEP4#

DEP5#

DEP6#

DEP7#

DBSY#

DRDY#

PICCLK

PICD1

PICD0

INIT#

FLUSH#

RESET#

BCLK

EDGCTRLN

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

HA#[3..31]4

R326

1K

R120

10K

1 2

2

Q18

FDV301N

CPU_IO

A

+3VSCPU_IOCPU_IO

13

66MHZ

100MHZ

RESERVED

133MHZ

1 2

HREQ#04

HREQ#14

HREQ#24

HREQ#34

HREQ#44

BREQ0#4

HLOCK#4

DEFER#4

HTRDY#4

IGNNE#9

R80 @56

R322 10K

R323 @10K

R324 1K

STPCLK#9

FERR# 9

ADS#4

BPRI#4

BNR#4

HIT#4

HITM#4

RS#04

RS#14

RS#24

A20M#9

SMI#9

RP64 8P4R-1K

1 8

2 7

3 6

4 5

INTR9

NMI9

4 4

R103

1.5K

1 2

FERR#1.5

3 3

2 2

1 1

SELPSB[1:0] STSEM BUS FREQUENCY

00

01

10

11

A

R307

1 2

1K_1%

12

C150

.1UF

1 2

L9 4.7Uh

VCCTREF

12

+2.5V_CLK+2.5V_CLK

A

R308

2K_1%

1 2

1 2

R60

2K_1%

R53

2K_1%

CPU_IO

CPU_IO

CPU_IO

4 4

3 3

R109

1.5K_1%

1 2

2 2

1 1

R110

1K_1%

1 2

12

C448

.1UF

12

C149

.1UF

+

C415

33U_6.3X2.5

12

C67

.1UF

12

C110

.1UF

VCCT_VCCA

VCCT_VSSA

VCCTREF

12

C69

.1UF

4.7U_0805

CPU_CORE

CLKREF

CMOSREF

R325 1.5K

R316

56.2_1%

1 2

12

U44B

C99

.1UF

L2

VCCA

M2

VSSA

E5

VREF0

E16

12

C51

R111

1K

1 2

VREF1

E17

VREF2

F5

VREF3

F17

VREF4

U5

VREF5

Y17

VREF6

Y18

VREF7

H8

VCC0

H10

VCC1

H12

VCC2

H14

VCC3

H16

VCC4

J7

VCC5

J9

VCC6

J11

VCC7

J13

VCC8

J15

VCC9

K8

VCC10

K10

VCC11

K12

VCC12

K14

VCC13

K16

VCC14

L7

VCC15

L9

VCC16

L11

VCC17

L13

VCC18

L15

VCC19

M8

VCC20

M10

VCC21

M12

VCC22

M14

VCC23

M16

VCC24

N7

VCC25

N9

VCC26

N11

VCC27

N13

VCC28

N15

VCC29

P8

VCC30

P10

VCC31

P12

VCC32

P14

VCC33

P16

VCC34

R7

VCC35

R9

VCC36

R11

VCC37

R13

VCC38

R15

VCC39

T8

VCC40

T10

VCC41

T12

VCC42

T14

VCC43

T16

VCC44

U7

VCC45

U9

VCC46

U11

VCC47

U13

VCC48

U15

VCC49

AB19

RSVD

P2

CLKREF

AA9

CMOSREF1

AD18

CMOSREF2

R2

GHI#

AD19

RTTIMPEDP

AD17

12

TESTHI

Y5

TESTLO1

N5

TESTLO2

AD20

TESTP1

H4

TESTP2

AA17

TESTP3

G4

TESTP4

R70

1K

1 2

MICRO-PGA

B

PLL ANALOG VOLTAGE

COPPERMINE

POWER,

GROUND,

RESERVED

SIGNALS

B

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

A2

A7

A8

A12

A21

B1

B5

B6

B7

B8

B10

B15

B18

C9

C11

C15

C16

C19

D2

D6

D7

D9

E3

E7

E8

E9

E10

E11

E13

E19

F3

F6

F7

F8

F9

F10

F11

F12

F13

F14

F15

F16

F20

G3

G19

H2

H7

H9

H11

H13

H15

H20

J4

J8

J10

J12

J14

J16

J19

K2

K7

K9

K11

K13

K15

K20

L5

L8

L10

L12

L14

L16

L19

M7

M9

M11

M13

M15

M20

N2

N3

N4

N8

N10

N12

N14

N16

N18

N19

N20

P5

P7

P9

P11

P13

P15

P19

R3

R4

R5

R8

R10

12

C141

.1UF

CPU_CORE

12

C88

.1U

CPU_CORE

12

C121

.1U

CPU_CORE

12

C168

.1U

CPU_CORE

12

C68

.1U

CPU_CORE

12

C34

.1U

CPU_CORE

12

C91

2.2U_0805

CPU_CORE

+

C409

220U_E

6.3V

12

C125

.1UF

12

C147

.1UF

12

12

12

C48

.1U

12

C62

.1U

12

C33

.1U

C89

.1U

C122

.1U

12

C109

.1UF

12

C146

.1UF

12

C108

.1U

12

C123

.1U

12

C195

.1U

12

C59

.1U

12

C80

2.2U_0805

+

C410

220U_E

6.3V

C

12

C90

.1UF

12

C145

.1UF

12

C107

.1U

12

C124

.1U

12

C194

.1U

12

C57

.1U

12

C36

.1U

12

C92

2.2U_0805

C

12

C76

.1UF

12

C85

.1UF

12

12

12

C193

.1U

12

C53

.1U

12

C46

.1U

+

C87

.1U

C50

.1U

C405

220U_E

6.3V

12

C75

.1UF

12

C103

.1UF

12

C86

.1U

12

C49

.1U

12

C169

.1U

12

C38

.1U

12

C173

.1U

12

C416

2.2U_0805

PROPRIETARY NOTE

12

12

C74

C73

.1UF

.1UF

12

12

C144

C119

.1UF

.1UF

12

12

C84

.1U

12

C52

.1U

12

12

C164

C160

.1U

.1U

12

12

C40

C39

.1U

.1U

12

12

C179

C174

.1U

.1U

12

C427

2.2U_0805

+

C411

220U_E

6.3V

C106

.1U

12

C72

.1UF

12

C447

.1UF

+

C451

220U_E

12

C105

.1U

12

C151

.1U

12

C152

.1U

12

C41

.1U

12

C79

2.2U_0805

12

C419

2.2U_0805

+

C452

220U_E

6.3V

G6

G7

G8

G9

H6

J6

K6

L6

M6

N6

P1

P6

R6

T6

U6

V6

V7

V8

V9

Y6

Y7

Y8

U44C

VCCT0

VCCT1

VCCT2

VCCT3

VCCT4

VCCT5

VCCT6

VCCT7

VCCT8

VCCT9

VCCT10

VCCT11

VCCT12

VCCT13

VCCT14

VCCT15

VCCT16

VCCT17

VCCT18

VCCT19

VCCT20

VCCT21

VCCT22

VCCT23

VCCT24

VCCT25

VCCT26

VCCT27

VCCT28

VCCT29

VCCT30

VCCT31

VCCT32

VCCT33

VCCT34

VCCT35

VCCT36

VCCT37

VCCT38

VCCT39

VCCT40

VCCT41

VCCT42

VCCT43

VCCT44

VCCT45

VCCT46

VCCT47

VCCT48

VCCT49

VCCT50

VCCT51

VCCT52

VCCT53

VCCT54

VCCT55

VCCT56

VCCT57

VCCT58

VCCT59

VCCT60

VCCT61

VCCT62

VCCT63

VCCT64

VCCT65

VCCT66

VCCT67

VCCT68

VCCT69

VCCT70

VCCT71

MICRO-PGA

D

COPPERMINE

POWER, GROUND AND NC

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VID4

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VID3

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VID0

VID1

VID2

VSS159

VSS160

VSS161

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

R12

R14

R16

R20

T3

T5

T7

T9

T11

T13

T15

T18

T19

U8

U10

U12

U14

U16

U20

V3

V19

W4

W18

Y3

Y9

Y10

Y11

Y12

Y13

Y14

Y15

Y16

Y19

AA4

AA13

AA20

AB3

AB4

AB5

AB9

AB11

AB13

AB14

AB17

AC1

AC2

AC4

AC5

AC10

AC14

AC16

AC18

AC21

AD1

AD2

AD3

AD4

AD5

AD16

AD21

A15

A16

A17

C14

D8

D14

D16

E15

G2

G5

G18

H3

H5

J5

M4

M5

P3

P4

AA5

AA19

AC3

AC17

AC20

AD15

VID[0..4]39

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

CPU_IO

12

12

C71

C148

.1UF

.1UF

G10

G11

12

C131

.1UF

12

C450

.1UF

12

C120

.1U

12

C163

.1U

12

C132

.1U

12

C35

.1U

12

C413

2.2U_0805

+

C406

220U_E

6.3V

G12

G13

G14

G15

G16

G17

H17

K17

M17

N17

P17

R17

U17

V10

V11

V12

V13

V14

V15

V16

V17

W10

W11

W12

W13

W14

W15

W16

W17

AA6

AA7

AA8

AB6

AB7

AB8

AC6

AC7

AC8

AD6

AD7

AD8

J17

L17

T17

W6

W7

W8

W9

12

12

C159

.1U

12

C142

.1U

12

C42

.1U

CPU_IO

CPU_IO

C104

.1U

VID4

VID3

VID0

VID1

VID2

E

VID0

VID1

VID2

VID3

VID4

R319 1K

RP65

1 8

2 7

3 6

4 5

8P4R-1K

1 2

VID[0..4]

Compal Electronics, Inc.

Title

SCHEMATIC, M/B LA-854

Size Document Number Rev

B

401172

D

Date: Sheet

340Saturday, December 23, 2000

E

+5V

0C

of

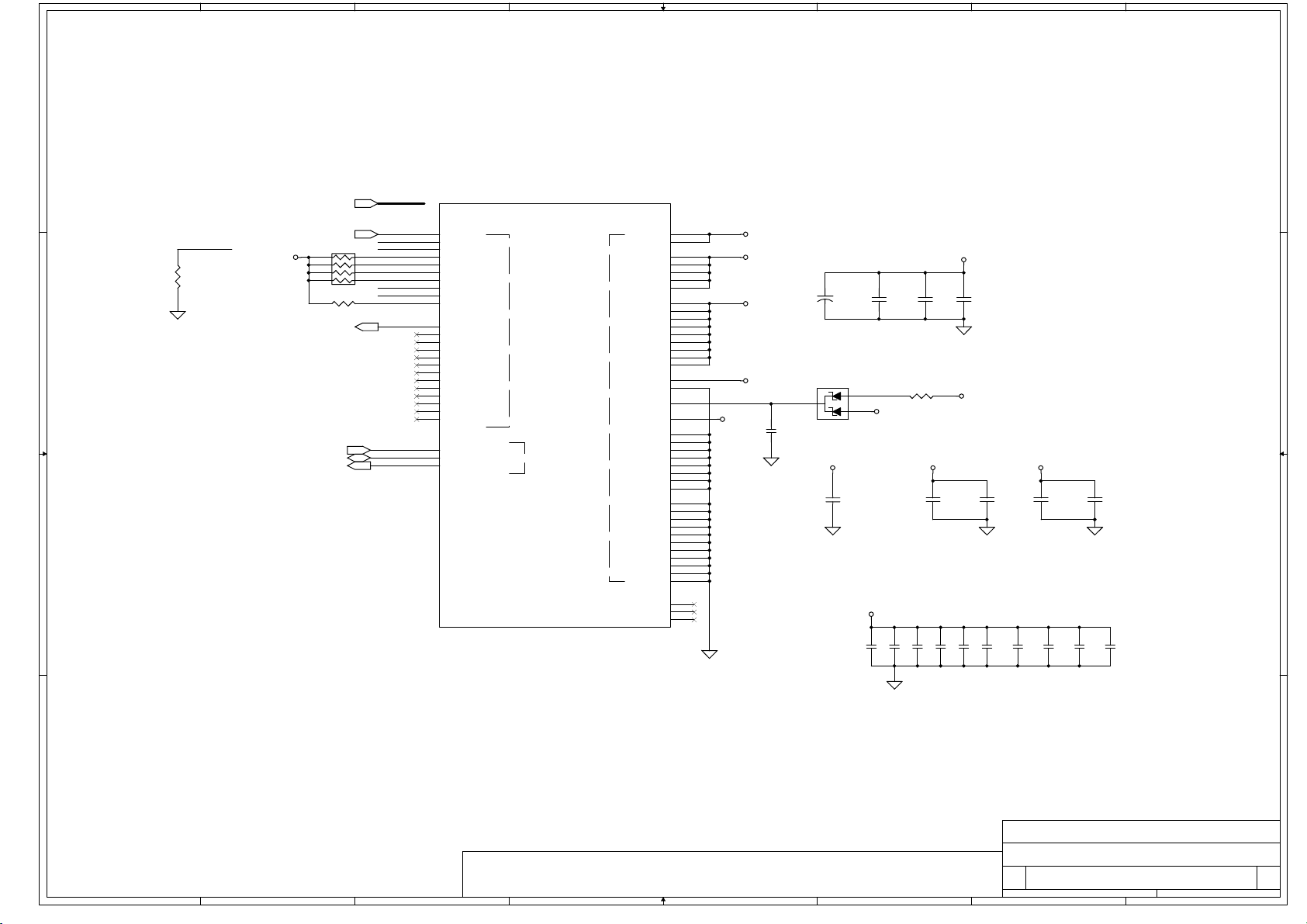

1 1

A

2 2

3 3

4 4

HD#[0..63]2

A

2.32K_1%

1 2

.01UF

.1UF

.1UF

B

PROPRIETARY NOTE

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

R84

12

C435

12

C425

12

C426

1UF_0805

12

RB751V

C418

3.48K_1%

R69

1 2

VCCTREF

+3V

2 1

R35 1K

D3

HD#61

HD#60

C10

HD60#

HD#58

HD#59

C11

D9

HD58#

HD59#

CRESET#

M26

HD#57

HD#56

E11

A9

A7

HD55#

HD56#

HD57#

CPURST#

RS#2

L25

B23

CPURST# 2

RS#2 2

HD#55

HD#54

A10

HD54#

RS#1

L26

RS#1 2

HD#53

B10

HD52#

HD53#

HTRDY#

RS#0

K26

HTRDY# 2

RS#0 2

HD#52

C8

HD51#

H25

HD#51

C12

B7

HD50#

DRDY#

K23

DRDY# 2

HD#50

HD#49

A11

HD49#

DBSY#

L23

DBSY# 2

HD#48

B11

HD47#

HD48#

DEFER#

DEFER# 2

HD#47

A12

HD46#

HITM#

J26

HITM# 2

D11

L22

HD#63

+3V AGPREF

1 2

12

C112

5PF

+5V

1 2

REFVCC5

HD#62

B8A8B9

HD61#

HD62#

HD63#

443ZX-100M

HCLKIN

N23

R68

10

HCLK_CPU 2,12

HD#40

HD#37

HD#36

C14

B13

HD36#

HD37#

HREQ#3

HREQ#4

K25

J25

HREQ#3 2

HREQ#4 2

HD#34

HD#35

D14

D15

HD34#

HD35#

HREQ#1

HREQ#2

J23

K24

HREQ#1 2

HREQ#2 2

HD#32

HD#33

B15

A15

HD31#

HD32#

HD33#

HREQ#0

ADS#

J22

ADS# 2

HREQ#0 2

HD#31

D16

A16

HD30#

K21

HD#29

HD#30

B16

HD29#

HA31#

D23

HA#31

HD#28

C15

HD27#

HD28#

HA29#

HA30#

E22

HA#30

HD#27

C16

A17

HD26#

HA28#

C24

A23

HA#29

HD#25

HD#26

B17

HD25#

HA27#

B24

HA#27

HA#28

HD#24

D17

HD23#

HD24#

HA25#

HA26#

C23

HA#26

HD#23

E17

HD22#

HA24#

D24

HA#25

HD#22

C17

HD21#

HA23#

A24

HA#24

HD#21

B18

HD20#

HA22#

C25

HA#23

HD#20

A19

HD19#

HA21#

A25

HA#22

HD#42

HD#45

HD#46

E13

HD45#

HIT#

L24

HIT# 2

C13

HD44#

HD#38

HD#39

HD#43

HD#44

HD#41

D13

D12

E14

A13

B12

B14

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HOST BUS INTERFACE (Processor System

Bus)

HLOCK#

BREQ0#

BPRI#

BNR#

B26

H26

H24

K22

BNR# 2

BPRI# 2

HLOCK# 2

BREQ0# 2

HD#19

A18

HD18#

HA20#

C26

HA#21

HD#18

C19

B19

HD17#

HA19#

D26

B25

HA#20

HD#16

HD#17

D18

HD16#

HA18#

D25

HA#18

HA#19

D19

HD15#

HA17#

E25

HD#14

HD#15

D20

HD14#

HA16#

E26

HA#16

HA#17

HD#13

E18

HD12#

HD13#

HA14#

HA15#

E23

HA#15

HD#12

E19

B20

HD11#

HA13#

F24

F25

HA#14

HD#11

HD#10

A20

HD9#

HD10#

HA11#

HA12#

F23

HA#12

HA#13

4.7U_0805

HD#9

B21

E20

HD8#

HA10#

G22

F22

HA#11

220U_E

C431

HD#7

HD#8

C20

HD7#

HA9#

G26

HA#9

HA#10

+

C414

12

HD#6

A21

HD6#

HA8#

F26

HA#8

HD#5

C21

HD5#

HA7#

G24

HA#7

D21

HD4#

HA6#

H23

HD#4

HD3#

HA5#

HA#6

HD#3

A22

G23

HA#5

+3V

HD#2

E21

HD2#

HA4#

H22

HA#4

HD#1

D22

HD1#

HA3#

G25

HA#3

HD#0

B22

HD0#

HD#[0..63]

U8A

B

HA#[3..31]

HA#[3..31] 2

C

VSS64

AF13

VSS63

AF1

AD22

VSS61

VSS62

AD18

VSS60

AD9

SUS_STAT#10,14

AD4

SUSTAT#

VSS58

VSS59

AB25

AD5

+3V

R72 1K

1 2

M25

TESTIN#

VSS57

AB15

AB24

VSS55

VSS56

AB12

AB3

.1UF

.1UF

AE23

NC1

NC2

VSS53

VSS54

AA21

AE22

NC0

VSS52

AA19

C420

C434

P22

AA8

AGPREF

12

12

AGPREF

VSS50

VSS51

AA6

N4

VSS49

REFVCC5

F17

C2

VTTB

REFVCC5

VSS46

VSS47

VSS48

T15V3V24W6W21

CPU_IO

M24

VTTA

VSS44

VSS45

R22

T12

VCCTREF

M23

E16

VCC40

GTL_REFA

GTL_REFB

VSS40

VSS41

VSS42

VSS43

R13

R14

R16

AF14

VCC39

VSS39

AF2

AE26

VCC37

VCC38

VSS37

VSS38

P26R5R11

AE1

VCC36

VSS36

P15

AA20

VCC35

VSS35

P14

AA18

P13

AA9

VCC33

VCC34

VSS33

VSS34

P12

12

.1UF

C433

12

.1UF

C439

12

.1UF

C429

12

.1UF

C436

12

.1UF

C432

12

.1UF

C438

12

.01UF

C430

12

.01UF

C437

AA7

VCC32

VCC30

VCC31

V21Y6Y21

T16

V6

VCC28

VCC29

T13

T14

VCC26

VCC27

T11

VCC24

VCC25

R15

VCC23

POWER and GROUND

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

M13

M14

M16

M22N1N12

N13

N14

N15

N24

R12

P11

P16

VCC21

VCC22

VSS21

VSS22

L15M5M11

.1UF

.1UF

.01UF

P1

VCC20

VSS20

L12

12

C443

12

C441

12

C442

N26

VCC18

VCC19

VSS18

VSS19

N22

N11

N16

VCC16

VCC17

VSS16

VSS17

M12

M15

VCC14

VCC15

VSS14

VSS15

F19

F21H6H21J3J24

L16

VCC12

VCC13

VSS12

VSS13

L14

L11

L13

VCC10

VCC11

VSS10

VSS11

E15

E24F6F8

.1UF

.1UF

.1UF

.1UF

.01UF

.01UF

.01UF

.01UF

J21

VCC9

VSS9

C446

C440

C444

C445

C422

C421

C424

C423

J6

VCC8

VSS8

12

12

12

12

12

12

12

12

G21

VCC7

VSS7

C22E3E12

G6

VCC6

VSS6

C18

F20

VCC5

VSS5

F18

VCC4

VSS4

F9

VCC3

VSS3

A26C5C9

F7

VCC2

VSS2

A14

B1

VCC1

VSS1

A1

U8D

D

+3V

RSMRST#10,35

R135 0

1 2

D

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet

B

BXPWROKRSMRST#

443ZX-100M

4011720CSCHEMATIC, M/B LA-854

VSS65

VSS66BXPWROK

AF26AF3

E

440Saturday, December 23, 2000

of

E

A

GFRAME#

GIRDY#

GTRDY#

GDEVSEL#

GSTOP#

SBA[0..7]

GREQ#

GGNT#

RBF#

PIPE#

AD_STBA

AD_STBB

SBSTB

ST0

ST1

ST2

1 2

R87

GAD[0..31]

R99 0

18

GAD[0..31]14 AD[0..31] 9,18,26,28,29

GTRDY#

1 2

GIRDY#

1 2

GDEVSEL#

4 4

3 3

GPAR14

2 2

GSTOP#

AD_STBA

AD_STBB

GFRAME#

GREQ#

GGNT#

SBSTB

RBF#

PIPE#

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

8.2K

R315

R310 8.2K

8.2K

R314

R97 8.2K

8.2K

R105

R309 8.2K

R91 8.2K

R57 8.2K

R61 8.2K

R78 8.2K

8.2K

R86

8.2K

R83

R93

100K

1 2

GCLKO14

+3V

GC/BE#014

GC/BE#114

GC/BE#214

GC/BE#314

GFRAME#14

GIRDY#14

GTRDY#14

GDEVSEL#14

GSTOP#14

SBA[0..7]14

GREQ#14

GGNT#14

PIPE#14

AD_STBA14

AD_STBB14

SBSTB14

R92 18

RBF#14

ST014

ST114

ST214

1 2

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

1 2

1 2

R311 0

AGPCLKI

AGPCLKO

B

1 2

12

C428

15PF

R306

47

AB5

AE2

AD3

AD2

AD1

AC3

AC1

AB4

AB1

AA5

AA3

AA4

AA2

AA1

AB2

AC2

W1

W2

U5

U4

U3

U1

U6

R3

R4

R2

U2

W3

W4

W5

M2

M1

N2

R1

M4

M3

N3

N5

Y5

Y3

V2

V1

T3

T4

T2

T1

Y4

V4

V5

Y2

Y1

K1

P2

P4

P3

L5

L3

T5

L4

L2

L1

P5

U8C

G_AD0

G_AD1

G_AD2

G_AD3

G_AD4

G_AD5

G_AD6

G_AD7

G_AD8

G_AD9

G_AD10

G_AD11

G_AD12

G_AD13

G_AD14

G_AD15

G_AD16

G_AD17

G_AD18

G_AD19

G_AD20

G_AD21

G_AD22

G_AD23

G_AD24

G_AD25

G_AD26

G_AD27

G_AD28

G_AD29

G_AD30

G_AD31

G_CBE0#

G_CBE1#

G_CBE2#

G_CBE3#

G_FRAME#

G_IRDY#

G_TRDY#

G_DEVSEL#

G_PAR

G_STOP

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

G_REQ#

G_GNT#

RBF#

PIPE#

AD_STBA

AD_STBB

SB_STB

ST0

ST1

ST2

GCLKIN

GCLKO

443ZX-100M

AGP INTERFACE

PCI INTERFACE

FRAME#

TRDY#

DEVSEL#

STOP#

SERR#

PLOCK#

PHOLD#

PHLDA#

PREQ0#

PREQ1#

PREQ2#

PREQ3#

PREQ4#

PGNT0#

PGNT1#

PGNT2#

PGNT3#

PGNT4#

PCIRST

CLKRUN#

PCLKIN

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

CBE0#

CBE1#

CBE2#

CBE3#

IRDY#

PAR

WSC#

K6

K2

K4

K3

K5

J1

J2

H2

H1

J5

H3

H5

H4

G1

G2

G4

D1

D3

D2

C1

A2

C3

B3

D4

E5

A4

D5

B4

B5

A5

E6

C6

J4

G3

E4

C4

E2

E1

F5

F3

G5

F4

F1

F2

B6

D6

AE3

A6

C7

F10

D8

D10

E7

D7

E10

E8

E9

A3

AC4

B2

AD[0..31]

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

FRAME#

IRDY#

TRDY#

DEVSEL#

STOP#

SERR#

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

GNT#0

GNT#1

GNT#2

GNT#3

GNT#4

C

CLKRUN#

R305

1 2

12

C417

15PF

D

REQ#0

GNT#0

REQ#1

GNT#1

C/BE#0 9,18,26,28,29

C/BE#1 9,18,26,28,29

C/BE#2 9,18,26,28,29

C/BE#3 9,18,26,28,29

FRAME# 9,13,18,26,28,29

IRDY# 9,13,18,26,28,29

TRDY# 9,13,18,26,28,29

DEVSEL# 9,13,18,26,28,29

PAR 9,13,18,26,28,29

STOP# 9,13,18,26,28,29

SERR# 9,13,18,26,29

PLOCK# 13

PHLD# 9,13

PHLDA# 9,13

REQ#0 10,29

REQ#1 10,29

REQ#2 10,26

REQ#3 10,18

REQ#4 10,28

GNT#0 29

GNT#1 29

GNT#2 26

GNT#3 18

GNT#4 28

PCIRST# 9,18,19,26,28,29

CLKRUN# 9,13,18,26,28,29,30

PCLK_BX 12

47

+3VS

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

RP63

6

7

8

9

10

10P8R-10K

REQ#4

1 2

R303 10K

GNT#4

1 2

R302 10K

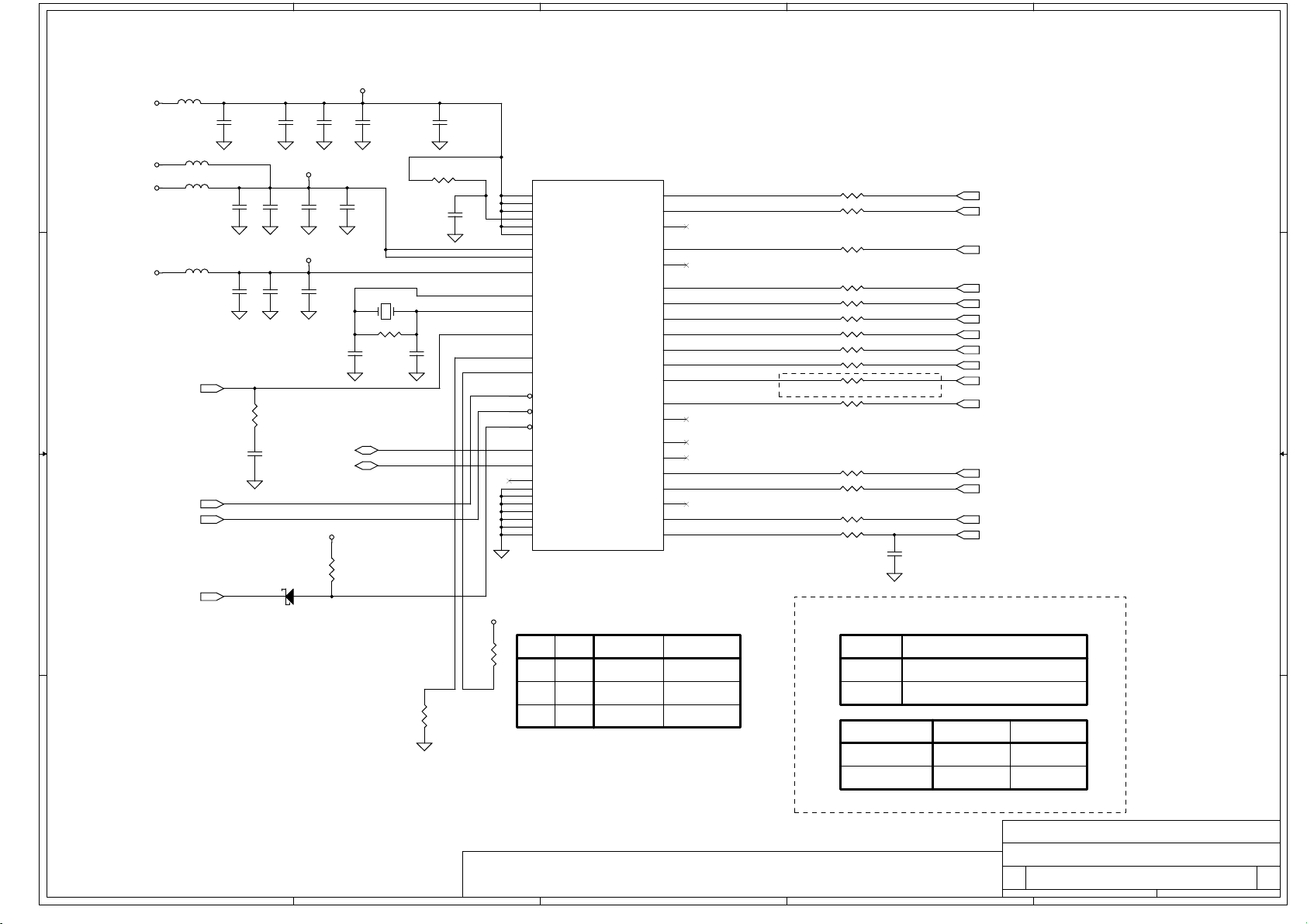

PCI REQ ASSIGME NT

LAN

MODEM

1394

PCMCIA CONTROLLER

PCI AUDIO

5

REQ#2

4

GNT#2

3

REQ#3

2

GNT#3

1

+3VS

E

+3VS

1 1

Compal Electronics, Inc.

Title

PROPRIETARY NOTE

A

B

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

SCHEMATIC, M/B LA-854

Size Document Number Rev

B

401172

Date: Sheet

540Saturday, December 23, 2000

E

of

0C

A

B

C

D

E

MD[0..63]

U8B

MMA0

MMA1

MMA2

MMA3

MMA4

MMA5

MMA6

MMA7

MMA8

MMA9

MMA10

MMA11

MMA12

MMA13

MMA[0..13]

AB14

AF15

AE15

AC15

AD15

AE16

AD13

AC13

AC25

AB26

AE14

AC14

AA22

AA24

AE13

AD14

AE12

AC12

AF16

AA17

AF12

AB13

AE11

AA10

AA23

AA26

AF11

AD12

AA25

AC22

AF23

AE24

AD23

AC23

AF24

AF17

AB16

AE17

AC17

AF18

AE19

AF19

AC18

AC19

AE20

AD20

AF21

AC21

AF25

AD16

AC16

AD17

AB17

AE18

AD19

AB18

AB19

AF20

AC20

AB20

AE21

AD21

AF22

Y22

CSA0#/RASA0#

CSA#1/RASA1#

CSA2#/RASA2#

CSA3#/RASA3#

NC30

NC31

DQMA0/CASA0#

DQMA1/CASA1#

DQMA2/CASA2#

DQMA3/CASA3#

DQMA4/CASA4#

DQMA5/CASA5#

DQMA6/CASA6#

DQMA7/CASA7#

NC3

NC4

WEA#

NC5

SRASA#

SRASB#

SCASA#

SCASB#

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

CKE0

CKE1

CKE2

CKE3

NC14

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

NC25

NC26

NC27

NC28

NC29

MAB0#

MAB1#

MAB2#

MAB3#

MAB4#

MAB5#

MAB6#

MAB7#

MAB8#

MAB9#

MAB10#

MAB11#

MAB12#

MAB13#

443ZX-100M

DRAM INTERFACE

4 4

3 3

2 2

RRAS#07

RRAS#28

RRAS#38

RCAS#07,8

RCAS#17,8

RCAS#27,8

RCAS#37,8

RCAS#47,8

RCAS#57,8

RCAS#67,8

RCAS#77,8

RMWEA#7,8

SRASA#7,8

SCASA#7,8

CKE07

CKE28

CKE38

MMA[0..13]7,8

NC32

NC33

NC34

NC35

NC36

NC37

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DCLKO

DCLKRD

DCLKWR

AE25

AD24

AD26

AC24

AC26

AB23

AF4

AE4

AF5

AD6

AE6

AB7

AC7

AF7

AB8

AB9

AC9

AE9

AB10

AC10

AF10

AD11

Y24

Y25

W23

W24

W26

W25

V26

U24

U23

T22

T23

T26

R24

R25

P23

N25

AC5

AE5

AB6

AC6

AF6

AD7

AE7

AC8

AD8

AF8

AE8

AF9

AD10

AE10

AB11

AC11

Y23

Y26

W22

V22

V23

V25

U22

U25

U26

T24

T25

U21

R23

R26

P24

P25

AB21

AB22

AD25

MDD0

MDD1

MDD2

MDD3

MDD4

MDD5

MDD6

MDD7

MDD8

MDD9

MDD10

MDD11

MDD12

MDD13

MDD14

MDD15

MDD16

MDD17

MDD18

MDD19

MDD20

MDD21

MDD22

MDD23

MDD24

MDD25

MDD26

MDD27

MDD28

MDD29

MDD30

MDD31

MDD32

MDD33

MDD34

MDD35

MDD36

MDD37

MDD38

MDD39

MDD40

MDD41

MDD42

MDD43

MDD44

MDD45

MDD46

MDD47

MDD48

MDD49

MDD50

MDD51

MDD52

MDD53

MDD54

MDD55

MDD56

MDD57

MDD58

MDD59

MDD60

MDD61

MDD62

MDD63

DCLKO1

1 2

R138 33

1 2

12

MDD3

MDD35

MDD34

MDD2

MDD33

MDD32

MDD0

MDD1

RP32 16P8R-10

MDD46

MDD47

MDD15

MDD12

MDD13

MDD44

MDD45

MDD14

RP35 16P8R-10

MDD24 MD24

MDD54

MDD59 MD59

MDD22

MDD53

MDD52

MDD51

MDD20

RP27 16P8R-10

MDD27

MDD58

MDD57

MDD26

MDD25

MDD56

MDD55

MDD23

RP22 16P8R-10

MDD8

MDD7

MDD38

MDD37

MDD6

MDD5

MDD36

MDD4

RP33 16P8R-10

MDD9

MDD10

MDD11

MDD43

MDD39

MDD40

MDD42

MDD41

RP34 16P8R-10

MDD21

MDD19

MDD18

MDD50

MDD49 MD49

MDD17

MDD16

MDD48

RP31 16P8R-10

MDD31

MDD63

MDD62

MDD30

MDD61

MDD29

MDD28

MDD60

RP20 16P8R-10

R131

@47

C204

@15PF

1

2

3

4

5

6

7

8 9

1

2

3

4

5

6

7

8 9

1

2

3

4

5

6

7

8 9

1

2

3

4

5

6

7

8 9

1

2

3

4

5

6

7

8 9

1

2

3

4

5

6

7

8 9

1

2

3

4

5

6

7

8 9

1

2

3

4

5

6

7

8 9

DCLKO 12

DCLKWR 12

MD3

16

MD35

15

MD34

14

MD2

13

MD33

12

MD32

11

MD0

10

MD1

MD46

16

MD47

15

MD15

14

MD12

13

MD13

12

MD44

11

MD45

10

MD14

16

MD54

15

14

MD22

13

MD53

12

MD52

11

MD51

10

MD20

MD27

16

MD58

15

MD57

14

MD26

13

MD25

12

MD56

11

MD55

10

MD23

MD8

16

MD7

15

MD38

14

MD37

13

MD6

12

MD5

11

MD36

10

MD4

MD9

16

MD10

15

MD11

14

MD43

13

MD39

12

MD40

11

MD42

10

MD41

MD21

16

MD19

15

MD18

14

MD50

13

12

MD17

11

MD16

10

MD48

MD31

16

MD63

15

MD62

14

MD30

13

MD61

12

MD29

11

MD28

10

MD60

MD[0..63] 7,8

MMA12

R146 10K

MMA10

MMA6

Pin Name Function Low High Interal Resistor

MAB12#

Host Frequency Select

MAB10#

Quick Start Select

MAB6#

Host Bus Buffer Mode Select

1 2

R137 10K

1 2

R317 10K

1 2

66MHz

Stop Clock Mode

Desktop GTL+

+3V

100MHz

Quick Start Mode

Mobile Low Power

GTL+

Pull-down

Pull-down

Pull-down none

Status Register

NBXCFG[13]

PMCR[3]

1 1

Compal Electronics, Inc.

Title

PROPRIETARY NOTE

A

B

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

SCHEMATIC, M/B LA-854

Size Document Number Rev

B

401172

Date: Sheet

640Saturday, December 23, 2000

E

of

0C

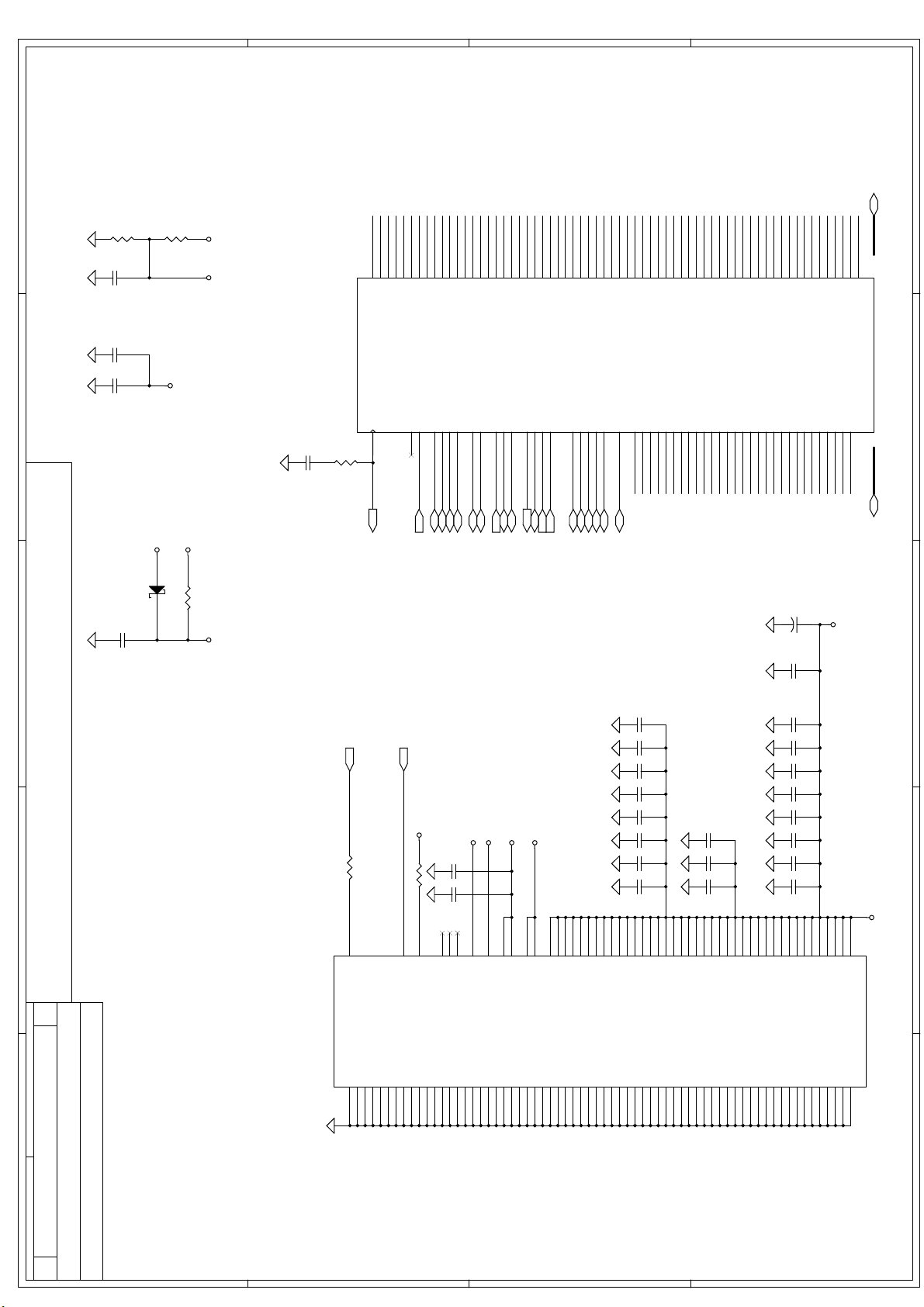

A

+3V

VSSQ

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15DQML

CKE

CLK

RVD

RVD

U48

4

5

7

8

10

11

13

42

44

45

47

48

50

51

5315

37

38

36

40

4MX16S

MD11 MMA1 0 MD42

MD13 MMA1 2 MD44

MD14

RMWEA#6,8

SCASA#6,8

SRASA#6,8

RRAS#06

MMA0 MD0

MMA1 MD1 MMA0 MD32

MMA2 MD2 MMA1 MD33

MMA3 MD3 MMA2 MD34

MMA4 MD4 MMA3 MD35

MMA5 MD5 MMA4 MD36

1 1

MMA6 MD6 MMA5 MD37

MMA7 MD7 MMA6 MD38

MMA8 MD8 MMA7 MD39

MMA9 MD9 MMA8 MD40

MMA10 MD10 MMA9 MD41

MMA13

MMA12 MD12

MMA11

RCAS#0 MD15 MD46

RCAS#1 RCAS#4 MD47

RMWEA# CKE0 RCAS#5

SCASA# CLK_SDRAM0 RMWEA# CKE0

SRASA# SCASA# CLK_SDRAM0

RRAS#0 SRASA#

2 2

11427394349

23 2

A0 DQ0

24

A1

VCC

VCC

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BA1

A13/BA0

DQMH

WE#

CAS#

RAS#

CS#

VCC

VCCQ

VCCQ

VCCQ

VSS

VSS

VSS

VSSQ

VSSQ

2841546124652

MMA[0..13]

MD[0..63]

RCAS#[0..7]

VCCQ

VSSQ

25

26

29

30

31

32

33

34

22

35

21

20

39

16

17

18

19

MMA[0..13]6,8

MD[0..63]6,8

RCAS#[0..7]6,8

B

C

+3V

D

32/64MB

VSSQ

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15DQML

CKE

CLK

RVD

RVD

U47

4

5

7

8

10

11

13

42

44

45

47

48

50

51

5315

37

38

36

40

4MX16S

MD43

MD45

MMA13

MMA11

SRASA#

RRAS#0

SDRAM

+3V

11427394349

23 2

A0 DQ0

24

A1

VCC

VCC

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BA1

A13/BA0

DQMH

WE#

CAS#

RAS#

CS#

VCC

VCCQ

VCCQ

VCCQ

VSS

VSS

VSS

VSSQ

VSSQ

2841546124652

VCCQ

VSSQ

25

26

29

30

31

32

33

34

22

35

21

20

39

16

17

18

19

VSSQ

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15DQML

CKE

CLK

RVD

RVD

U45

4

5

7

8

10

11

13

42

44

45

47

48

50

51

5315

37

38

36

40

4MX16S

BANK0

MMA13

MMA11

CKE0 6

CLK_SDRAM0 12

VCCQ

VSSQ

VSSQ

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15DQML

CKE

CLK

RVD

RVD

RRAS#0

U46

4

5

7

8

10

11

13

42

44

45

47

48

50

51

5315

37

38

36

40

4MX16S

R213

@10

C289

@15PF

MMA0 MD16

MMA1 MD17

MMA2 MD18 MMA0 MD48

MMA3 MD19 MMA1 MD49

MMA4 MD20 MMA2 MD50

MMA5 MD21 MMA3 MD51

MMA6 MD22 MMA4 MD52

MMA7 MD23 MMA5 MD53

MMA8 MD24 MMA6 MD54

MMA9 MD25 MMA7 MD55

MMA10 MD26 MMA8 MD56

MMA13

MMA12 MD28 MMA10 MD58

MMA11

RCAS#2 MD31

RCAS#3 MD62

RMWEA# CKE0 RCAS#6 MD63

SCASA# CLK_SDRAM0 RCAS#7

SRASA# RMWEA# CKE0

RRAS#0 SCASA# CLK_SDRAM0

+3V

11427394349

23 2

A0 DQ0

24

A1

VCC

VCC

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BA1

A13/BA0

DQMH

WE#

CAS#

RAS#

CS#

VCC

VCCQ

VCCQ

VCCQ

VSS

VSS

VSS

VSSQ

VSSQ

2841546124652

25

26

29

30

31

32

33

34

22

35

21

20

39

16

17

18

19

11427394349

23 2

A0 DQ0

24

A1

VCC

VCC

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BA1

A13/BA0

DQMH

WE#

CAS#

RAS#

CS#

VCC

VCCQ

VCCQ

VCCQ

VSS

VSS

VSS

VSSQ

VSSQ

2841546124652

VCCQ

VSSQ

25

26

29

30

31

32

33

34

22

35

21

20

39

16

17

18

19

MD27 MMA9 MD57

MD29

MD30 MMA12 MD60

E

MD59

MD61

3 3

C305

.1UF

C296

1000PF

+3V

+3V

C331

.1UF

C350

1000PF

+3V

12

C332

.1UF

+3V

C293

C216

.1UF

4 4

C381

1000PF

C217

.1UF

C510

1000PF

C253

.1UF

C511

1000PF

C254

.1UF

+3V

C351

1000PF

.1UF

C263

1000PF

C294

.1UF

C264

1000PF

Compal Electronics, Inc.

Title

PROPRIETARY NOTE

A

B

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

SCHEMATIC, M/B LA-854

Size Document Number Rev

B

401172

Date: Sheet

740Saturday, December 23, 2000

E

of

0C

A

SO-DIM 144 PINS

B

C

D

E

RAM MODULE CONN.

C483

22PF

MMA[0..13]

MD[0..63]

RCAS#[0..7]

RRAS#[0..3]

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

RCAS#0

RCAS#4

MMA0 MMA3

MMA1 MMA4

MMA2 MMA5

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

R348

33

RMWEA# CKE3

RRAS#2 MMA12

RRAS#3 MMA13

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MMA6 MMA7

MMA8

MMA9 MMA12

MMA10

RCAS#2

RCAS#6

MD48

MD49

MD50

+3V +3V

MD51

MD52

R148

10K

MD53

MD54

MD55

MMA[0..13]6,7

1 1

2 2

3 3

4 4

MD[0..63]6,7

RCAS#[0..7]6,7

RRAS#[0..3]6,7

CLK_SDRAM212

SRASA#6,7

RMWEA#6,7

BANK2/3

+3V +3V

JP19

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

VSS

DQ0

DQ1

DQ2

DQ3

VCC

DQ4

DQ5

DQ6

DQ7

VSS

CE0#

CE1#

VCC

A0

A1

A2

VSS

DQ8

DQ9

DQ10

DQ11

VCC

DQ12

DQ13

DQ14

DQ15

VSS

RESVD/DQ64

RESVD/DQ65

RFU/CLK0

VCC

RFU

WE#

RE0#

RE1#

OE#/RESVD

VSS

RESVD/DQ66

RESVD/DQ67

VCC

DQ16

DQ17

DQ18

DQ19

VSS

DQ20

DQ21

DQ22

DQ23

VCC

A6

A8

VSS

A9

A10

VCC

CE2#/RESVD

CE3#/RESVD

VSS

DQ24

DQ25

DQ26

DQ27

VCC

DQ28

DQ29

DQ30

DQ31

VSS

SDA

VCC

SO-DIMM144

RESVD/DQ68

RESVD/DQ69

RESVD/DQ70

RESVD/DQ71

CE6#/RESVD

CE7#/RESVD

VSS

DQ32

DQ33

DQ34

DQ35

VCC

DQ36

DQ37

DQ38

DQ39

VSS

CE4#

CE5#

VCC

VSS

DQ40

DQ41

DQ42

DQ43

VCC

DQ44

DQ45

DQ46

DQ47

VSS

RFU/CKE0

VCC

RFU

RFU/CKE1

RFU

RFU

RFU/CLK1

VSS

VCC

DQ48

DQ49

DQ50

DQ51

VSS

DQ52

DQ53

DQ54

DQ55

VCC

A11/BA0

VSS

A12/BA1

A13/A11

VCC

VSS

DQ56

DQ57

DQ58

DQ59

VCC

DQ60

DQ61

DQ62

DQ63

VSS

SCL

VCC

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

A3

32

A4

34

A5

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

A7

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

RCAS#1

RCAS#5

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

CKE2

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MMA11

MMA13

RCAS#3

RCAS#7

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

SCKP4SDAP4

CKE2 6

SCASA# 6,7

CKE3 6

R341

33

C472

22PF

R130

10K

CLK_SDRAM3 12

SCKP4 11,12SDAP411,12

+

C212

10UF_1206

6.3V

+3V

+

C509

10UF_1206

6.3V

C454

.1UF

C495

.01UF

C460

.1UF

+3V

1000PF

C505

C465

.1UF

C508

1000PF

C470

.1UF

1000PF

C208

C479

.01UF

1000PF

C219

C361

.01UF

C497

.01UF

DIMM1

Compal Electronics, Inc.

Title

PROPRIETARY NOTE

A

B

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

SCHEMATIC, M/B LA-854

Size Document Number Rev

B

401172

Date: Sheet

840Saturday, December 23, 2000

E

of

0C

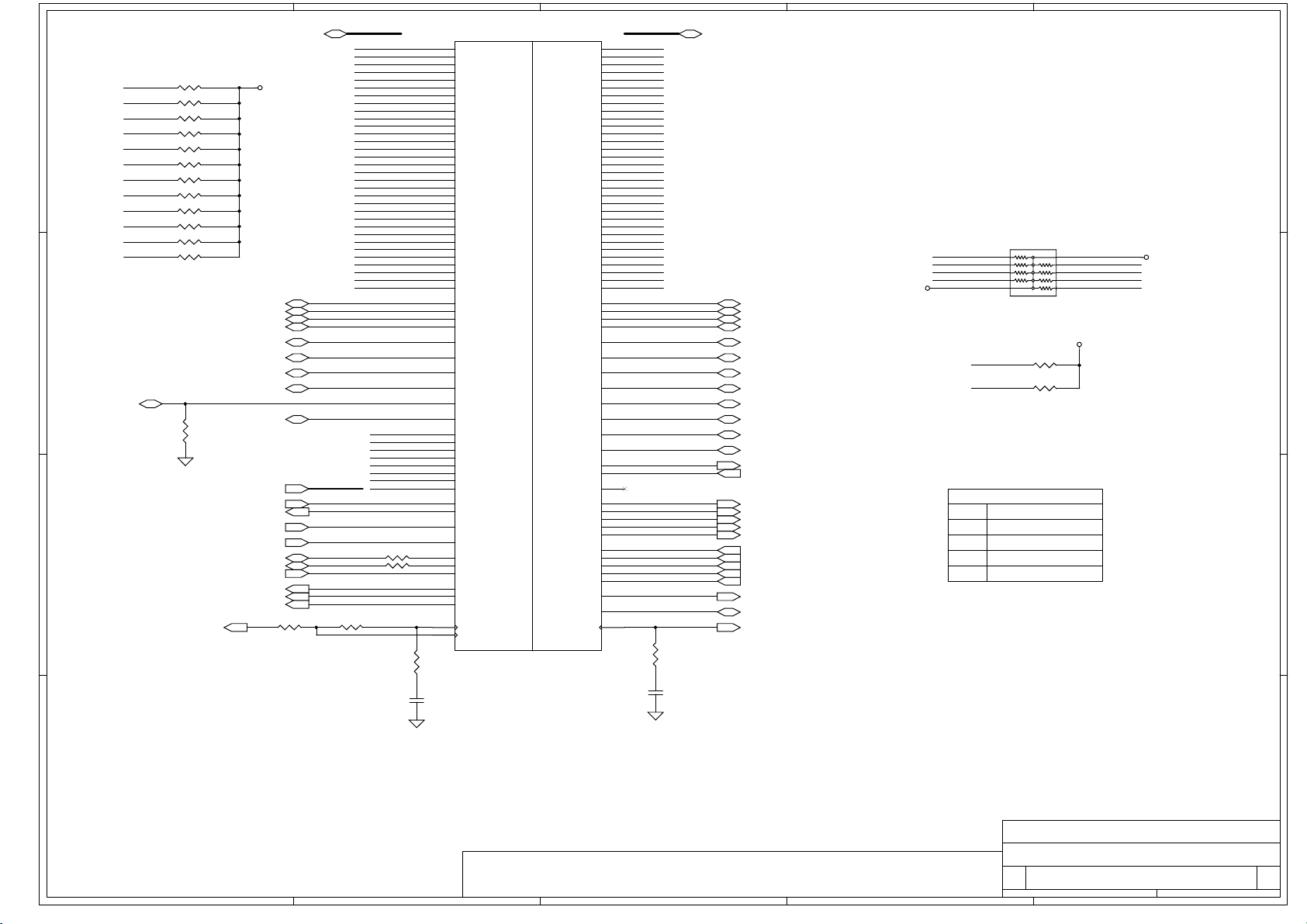

1

2

3

4

5

6

7

8

SA[0..19]

U11

T11

W11

Y11

T10

W10

U9

V9

Y9

T8

W8

U7

V7

Y7

V6

Y6

T5

W5

U4

V4

V3

W3

U2

T2

W2

Y2

T1

V1

W16

T16

Y17

V17

Y18

W18

Y19

W19

Y5

T4

V15

U15

W4

U3

V12

Y12

T3

Y1

U10

W12

Y4

W7

Y3

W1

M2

K1

N4

L4

N5

L1

K2

M4

M3

P1

H20

J20

T9

W9

U8

V8

Y8

Y20

U1

U12

W13

T13

V14

Y14

J19

R3

R4

P5

G1

SD[0..15]

SA0

SA1

SA2

SA3

SA4

SA5

SA6

SA7

SA8

SA9

SA10

SA11

SA12

SA13

SA14

SA15

SA16

SA17

SA18

SA19

SD0

SD1

SD2

SD3

SD4

SD5

SD6

SD7

SD8

SD9

SD10

SD11

SD12

SD13

SD14

SD15

R121 1K

FQS0

R73 10K

IRQ0

IRQ1

IRQ3

IRQ4

IRQ5

IRQ6

IRQ7

IRQ8#

IRQ9

IRQ10

IRQ11

IRQ12

IRQ14

IRQ15

1 2

1 2

U12A

PCI

CLOCK

CPU

MISC

PIIX4

1of3

324 mBGA

ISA

X-BUS

IRQs

SA10

SA11

SA12

SA13

SA14

SA15

SA16

SA17

SA18

SA19

SD10

SD11

SD12

SD13

SD14

SD15

IOR#

IOW#

MEMR#

MEMW#

SMEMR#

SMEMW#

IOCS16#

MEMCS16#

IOCHRDY

IOCHK#/GPI_0

BALE

SBHE#

AEN

REFRESH#

ZEROWS#

RSTDRV

BIOSCS#

KBCCS#/GPO_26

MCCS#

PCS0#

PCS1#

RTCALE/GPO_25

RTCCS#/GPO_24

XOE#/GPO_23

XDIR#/GPO_22

A20GATE

IRQ0/GPO_14

IRQ1

IRQ3

IRQ4

IRQ5

IRQ6

IRQ7

IRQ8#/GPI_6

IRQ9

IRQ10

IRQ11

IRQ12

IRQ14

IRQ15

SERIRQ/GPI_7

PIRQA#

PIRQB#

PIRQC#

PIRQD#

5

SA0

SA1

SA2

SA3

SA4

SA5

SA6

SA7

SA8

SA9

SD0

SD1

SD2

SD3

SD4

SD5

SD6

SD7

SD8

SD9

B10

AD0

A10

AD1

D9

AD2

C9

AD3

B9

AD4

A9

AD5

D8

AD6

E8

AD7

B8

AD8

A8

AD9

D7

AD10

C7

AD11

B7

AD12

A7

AD13

D6

AD14

E6

AD15

E4

AD16

C4

AD17

B4

AD18

A4

AD19

D3

AD20

E3

AD21

C3

AD22

B3

AD23

E2

AD24

C2

AD25

B2

AD26

A2

AD27

D1

AD28

E1

AD29

C1

AD30

B1

AD31

C8

C/BE0#

C6

C/BE1#

D4

C/BE2#

D2

C/BE3#

A5

FRAME#

B5

IRDY#

C5

TRDY#

D5

STOP#

E5

DEVSEL#

A6

SERR#

B6

PAR

A3

IDSEL

B12

PHOLD#

A12

PHLDA#

C10

CLKRUN#

A1

PCIRST#

D11

PCICLK

L3

CLK48

V11

OSC

P17

SUSCLK

T7

SYSCLK

N19

RTCX1#

R20

RTCX2#

M19

CPURST

L18

INIT

N20

RCIN#

L19

INTR

L20

NMI

P20

SMI#

J18

STPCLK#

K20

SLP#

L17

IGNNE#

K19

FERR#

M20

A20M#

R17

CONFIG1

R18

CONFIG2

M18

PWROK

V18

TEST#

K17

SPKR

PIIX4M

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

C/BE#05,18,26,28,29

C/BE#15,18,26,28,29

C/BE#25,18,26,28,29

C/BE#35,18,26,28,29

FRAME#5,13,18,26,28,29

IRDY#5,13,18,26,28,29

TRDY#5,13,18,26,28,29

STOP#5,13,18,26,28,29

DEVSEL#5,13,18,26,28,29

SERR#5,13,18,26,29

PAR5,13,18,26,28,29

PHLD#5,13

PHLDA#5,13

CLKRUN#5,13,18,26,28,29,30

PCIRST#5,18,19,26,28,29

RTCX1

RTCX2

100KR171

AD[0..31]

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

PROPRIETARY NOTE

AD[0..31]5,18,26,28,29

A A

B B

AD18

1 2

R76

100

PCLK_PIIX412

48M12

14MOSC12

C C

D D

RTCX2 RTCX1

12

1

1 2

R179 @1M

C246

22PF

X3

R115

33

1 2

C188

22P

1 2

32.768KHZ

12

R75

C135

22

10P

C247

22PF

R116

33

1 2

1 2

C189

22P

1 2

1 2

2

RTCCLK18,19

CPUINIT#2

RC#23

INTR2

NMI2

SMI#2

STPCLK#2

PX4_SLP#13

IGNNE#2

FERR#2

A20M#2

1 2

+3V

1 2

R147 100K

SPWROFF#23,35

1 2

+3V

R142 10K

SPKR34

3

SA[0..19] 13,23,30

SD[0..15] 13,23,30

IOR# 13,23,30

IOW# 13,23,30

MEMR# 13,23

MEMW# 13,23

IOCS16# 13

IOCHRDY 13,23,30

SBHE# 13

AEN 23,30

REFRESH# 13

ZWS# 13

RSTDRV 22,30

BIOSCS# 23

GATEA20 23

IRQ8# 13

SIRQ 13,18,30

PIRQA# 13,14,18

PIRQB# 13,18,26,29

PIRQC# 13,28

PIRQD# 13,29

6

+3VS

+3VS

IRQ[0..15]

IRQ[0..15] 13,20,21,23

Compal Electronics, Inc.

Title

SCHEMATIC, M/B LA-854

Size Document Number Rev

B

401172

Date: Sheet

7

940Saturday, December 23, 2000

8

0C

of

1

2

3

4

5

6

7

8

3 6

4 5

CP8

8P4C-33PF

RP12

4 5

3 6

2 7

1 8

8P4R-33

DMA

APIC

Power Mgmt

USB

182736

PIIX4

2of3

324 mBGA

USB1_D+

USB1_D-

45

RP13

8P4R-15K

IDE Bus

5

USB1_D+ 32

USB1_D- 32

USB0_D+ 32

USB0_D- 32

USB TRACE ROUTING 6 MILUSB Host Termination should be close to PIIX4

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

SDDO

SDD1

SDD2

SDD3

SDD4

SDD5

SDD6

SDD7

SDD8

SDD9

SDD10

SDD11

SDD12

SDD13

SDD14

SDD15

PDIOR#

PDIOW#

PIORDY

PDDREQ

PDDACK#

PDCS1#

PDCS3#

PDA0

PDA1

PDA2

SDIOR#

SDIOW#

SIORDY

SDDREQ

SDDACK#

SDCS1#

SDCS3#

SDA0

SDA1

SDA2

NC1

NC2

NC3

F20

E18

E20

D18

D20

C20

B20

A20

A19

B19

C19

D19

D17

E19

E17

F19

E15

B15

D14

C14

A14

C13

A13

C12

D12

B13

D13

B14

E14

A15

C15

D15

F17

F16

G20

F18

G19

H17

H16

G16

G18

G17

C16

B16

D16

A16

A17

B18

C18

C17

B17

A18

J4

N18

N3

PDD[0..15]

SDD[0..15]

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

SDD0

SDD1

SDD2

SDD3

SDD4

SDD5

SDD6

SDD7

SDD8

SDD9

SDD10

SDD11

SDD12

SDD13

SDD14

SDD15

PDD[0..15] 20

SDD[0..15] 20

PDIOR# 20

PDIOW# 20

PDIORDY 20

PDDREQ 20

PDDACK# 20

PDCS1# 20

PDCS3# 20

PDA0 20

PDA1 20

PDA2 20

SDIOR# 20

SDIOW# 20

SDIORDY 21

SDDREQ 21

SDDACK# 20

SDCS1# 20

SDCS3# 20

SDA0 20

SDA1 20

SDA2 20

Compal Electronics, Inc.

Title

SCHEMATIC, M/B LA-854

Size Document Number Rev

B

401172

6

Date: Sheet

7

10 40Saturday, December 23, 2000

8

0C

of

USBP1+

USBP1USBP0+ USB0_D+

USBP0- USB0_D-

A A

1 8

2 7

REQA#

REQB#

REQC#

PROPRIETARY NOTE

DRQ[0..7]

DACK#[0..3]

DRQ0

DRQ1

DRQ2

DRQ3

DRQ5

DRQ6

DRQ7

DACK#0

DACK#1

DACK#2

DACK#3

ACIN_SYS#

PX4_RI#

PBTN#

PX4_REQ#1

PX4_REQ#2

OVCUR#0

OVCUR#1

USBP1+

USBP1USBP0+

USBP0-

U12B

W15

DREQ0#

U6

DREQ1#

V2

DREQ2#

U5

DREQ3#

Y16

DREQ5#

U16

DREQ6#

U17

DREQ7#

U14

DACK0#

W6

DACK1#

Y10

DACK2#

V5

DACK3#

T15

DACK5#

V16

DACK6#

W17

DACK7#

V10

TC

M1

REQA#/GPI_2

N2

REQB#/GPI_3

P3

REQC#/GPI_4

N1

GNTA#/GPO_9

P2

GNTB#/GPO_10

P4

GNTC#/GPO_11

J17

APICACK#/GPO_12

H18

APICCS#/GPO_13

K18

APICREQ#/GPI_5

V20

EXTSMI#

U19

BATLOW#/GPI_9

R1

CPU_STP#/GPO_17

R2

PCI_STP#/GPO_18

H19

THRM#/GPI_8

P16

LID/GPI_10

P18

RIA_B/GPI_12

M17

RSMRST#

U20

PWRBTN#

W20

SUSA#

V19

SUSB#/GPO_15

U18

SUSC#/GPO_16

T17

SUS_ST1#/GPO_20

T18

SUS_ST2#/GPO_21

K16

ZZ/GPO_19

E10

PCIREQA#

A11

PCIREQB#

B11

PCIREQC#

C11

PCIREQD#

J1

OC0#

J2

OC1#

F1

USBP1+

H2

USBP1-

G2

USBP0+

H3

USBP0-

PIIX4M

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE

USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

DRQ[0..7]13,30

DACK#[0..3]30

B B

+3VS

12

R165

4.7K

ACIN_SYS#

13

1 2

R154 10K

D11

21

RB751V

D5

1

2

D8

1

2

Q22

2N7002

PBTN#

RB717F

RB717F

ACIN23,34,36

C C

ON/OFF23,34

REQ#15,29

REQ#35,18

D D

REQ#05,29

REQ#45,28

1

2

PX4_RI#

LLBATT#24

+3V

+3V

+3VS

R108

10K

+3VS

R122

10K

2

PX4_REQ#1

PX4_REQ#2

3

3

REQA#13

REQB#13

REQC#13

D12

RB751V

R161 10K

21

TC30

EXTSMI#23

CPU_STP#12

PCI_STP#12

ATF_INT#23

LID#13,24

PX4_RI#24

RSMRST#4,35

PBTN#13

SUSA#12,23

SUSB#23

SUSC#23

SUS_STAT#4,14

GGREQ#14

REQ#25,26

OVCUR#032

OVCUR#132

3

1

A A

2

3

4

5

6

7

8

PID[0..3]17

32#/64M

12

R65

0

B B

C C

+3VS

SCI#23

RP17

1 8

2 7

3 6

4 5

8P4R-10K

1 2

R351 10K

FLASH#24

SMBALT#13

SDAP48,12

SCKP48,12

PID[0..3]

PID0

PID1

32#/64M

MID1

MID2

MID3

PID2

PID3

U12C

P19

GPI_1

L2

GPI_13

J3

GPI_14

L5

GPI_15

K3

GPI_16

K4

GPI_17

H1

GPI_18

H4

GPI_19

H5

GPI_20

G3

GPI_21

G4

GPO_0

Y15

GPO_1/LA17

T14

GPO_2/LA18

W14

GPO_3/LA19

U13

GPO_4/LA20

V13

GPO_5/LA21

Y13

GPO_6/LA22

T12

GPO_7/LA23

T19

GPO_8

G5

GPO_27

F2

GPO_28

F3

GPO_29

F4

GPO_30

N17

SMBALERT/GPI_11

T20

SMBDATA

R19

SMBCLK

PIIX4M

GPIO

SMB

PIIX4

3of3

324 mBGA

POWER

VCCSUS1

VCCSUS2

VCC1

VCC2

VCC3

VCC4

VCC5

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCUSB

VSSUSB

VREF

VBAT

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

R16

N16

R15

R6

F15

E11

F6

T6

P15

R7

G6

F14

F5

E16

E12

E9

K5

J5

J16

L16

J9

J10

J11

J12

K9

K10

K11

K12

L9

L10

L11

L12

M9

M10

M11

M12

D10

E7

E13

M5

NC

R5

NC

M16

NC

PIIX4_VREF

+RTCVCC

+3V

+3VS

+3VS

+3VS

3

D10 RB425D

C238

1U_25V_0805

12

C176

+

10U_25V_1210

+RTCVCC

12

C235

1U

+3VS

C196

C200

C183

.1U

.1U

+3VS

C237

R173

1K

C236

.1U

.1U

2

1

+3VS

C232

.01U

.1U

12

+5VS

+3V+3V

C136

1000P

C234

.01U

C137

1000P

C233

.01U

C231

.1U

C230

.01U

C134

C133

1000P

.1U

C170

1000P

C229

.01U

1000P

C165

D D

Compal Electronics, Inc.

Title

PROPRIETARY NOTE

1

2

3

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL AND

TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERRED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY BE