Page 1

A

ZZZ

1 1

PCB

Part Number = DAZ0K400100

B

C

D

E

Compal Confidential

2 2

K73TA Schematics Document

AMD Sabine

APU Llano / Hudson M3 / Whistler

DIS only

3 3

2011-03-08

LA-7553P REV: 0.2

4 4

http://hobi-elektronika.net

A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2010/08/04 2010/08/04

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

B

D

Date: Sheet

Compal Electronics, Inc.

Cover Page

QBL70 LA-7553P

E

151Friday, April 29, 2011

0.22

of

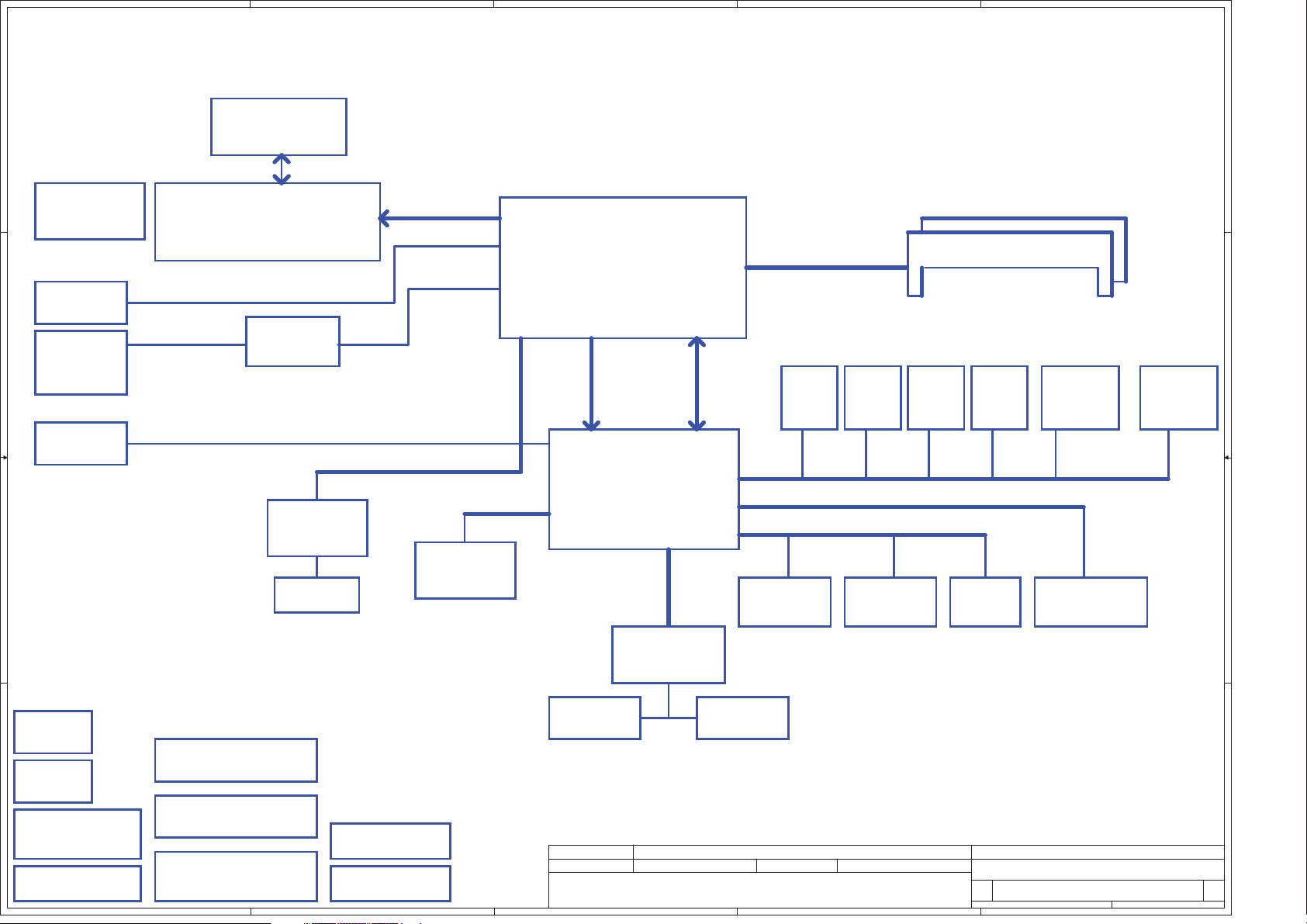

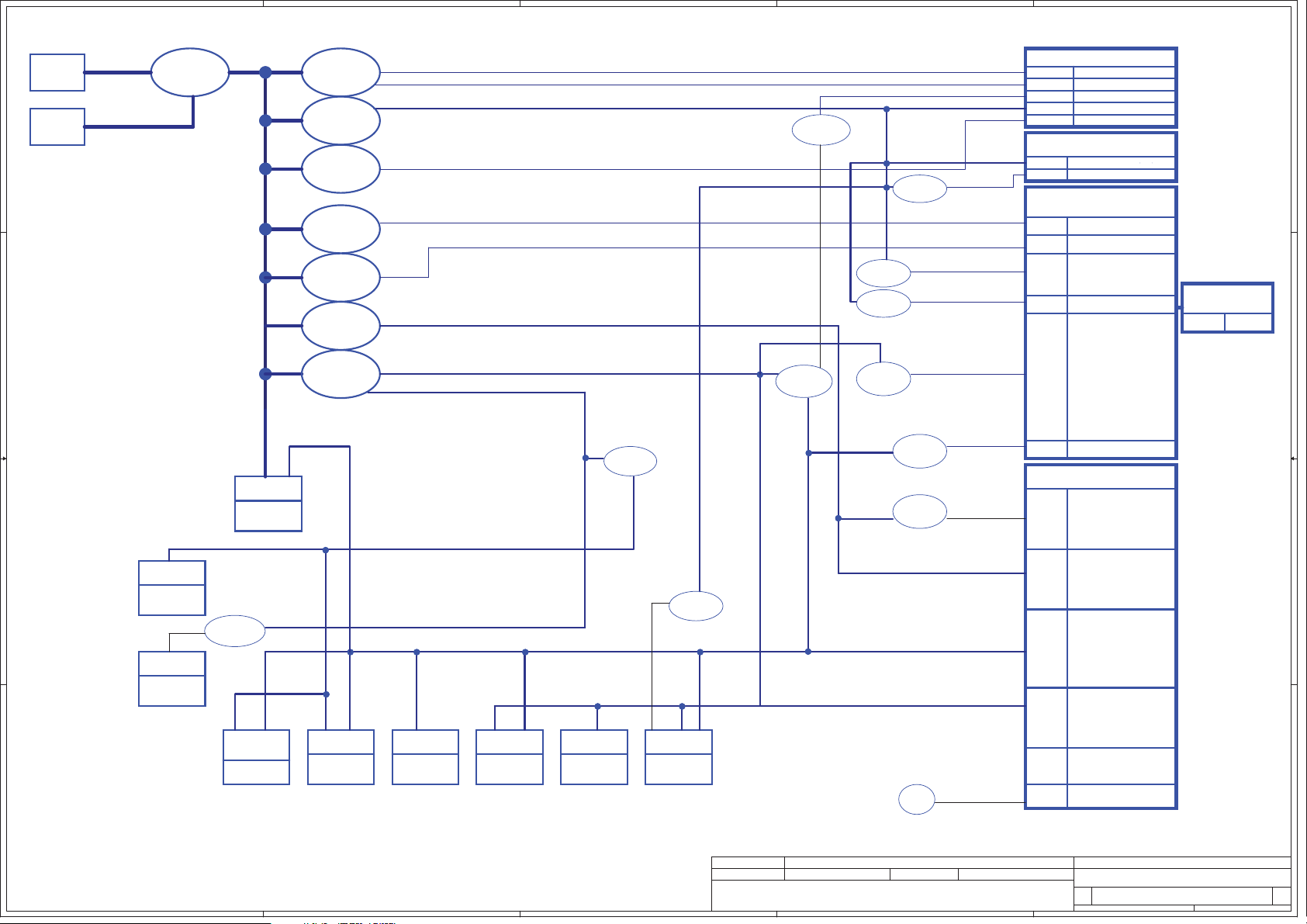

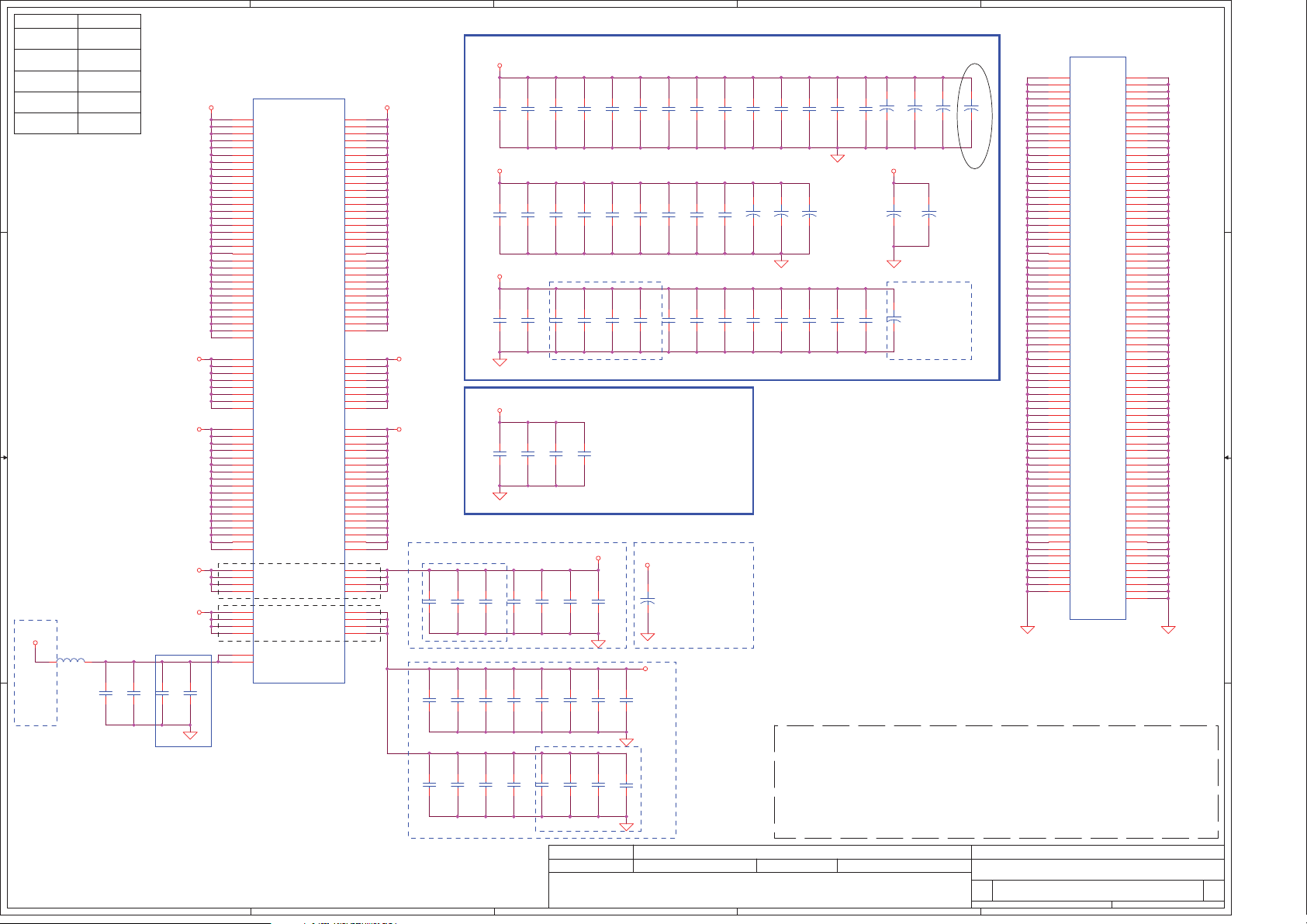

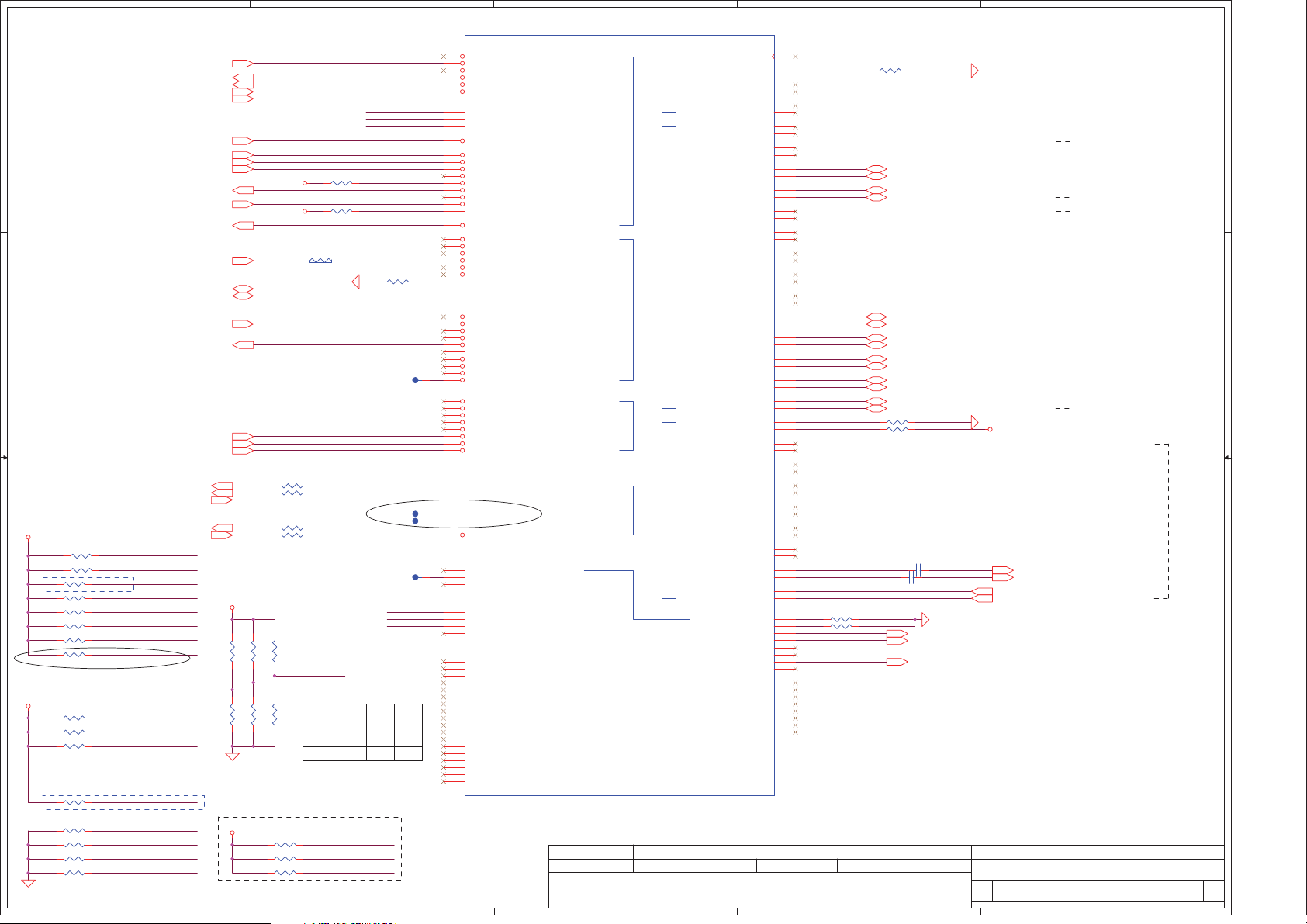

Page 2

A

Compal Confidential

Model Name : QBL70

B

C

D

E

1 1

VRAM 512M/1G/2G

64M16/128M16 x 8

page 23, 24

Sabine

DDR3

Thermal Sensor

ADM1032

page 19

Vancuver Whistler

ATI

uFCBGA-962

Page 18~22

GFX x 4

APU HDMI

(UMA / Muxless)

DP x1 (DP0 TXP/N0)

Gen2GFX x 8

AMD FS1 APU

Llano

uPGA-722 Package

Memory BUS(DDR3)

Dual Channel

1.5V DDRIII 800~1333MHz

204pin DDRIII-SO-DIMM X2

BANK 0, 1, 2, 3

Page 11,12

HDMI Conn.

page 28

2 2

LVDS Conn.

LVDS

Reserve eDP

page 27

CRT Conn.

page 27

3 3

Travis LVDS

Translator

page 26

LAN(GbE)

RTL8111E

RJ45

GPP0

page 31

page 31

FCH CRT (VGA DAC)

GPP0

MINI Card 1

WLAN

page 35

P_GPP x 2

GEN1

DP x 4

(DP1 TXP/ N 0~4)

Hudson-M2/M3

uFCBGA-656

Page 6~10

FCH

Page 13~17

UMI

LPC BUS

USB2

page 30

USB

3.3V 48MHz

HD Audio

S-ATA

Gen2

port 0

SATA HDD1

Conn.

page 29

USB2

page 30 page 27

Port 0 Port 5

3.3V 24.576MHz/48M hz

USB2 x 2

(LS-7323P)

page 33

Port 1

port 2

SATA HDD2

page 29

CMOS

Camera

ODD

Conn.

page 29

Mini Card

(with BT)

Port2 Port 3

port 1

HDA Codec

ALC269

page 35

Card Reader

RTS5137

page 34

Port 4

page 33

ENE KB930

page 32

Touch Pad Int.KBD

LED

page 35

RTC CKT.

4 4

page 13

DC/DC

Interface CKT.

page 38

External board

LS-7324P

HDD/B

LS-7325P

Power/B

page 36

page 36

BIOS ROM

SYS BIOS (2M)

page 15

LS-7323P

Power Circuit

http://hobi-elektronika.net

page 39~48

Audio BD

A

page 33 page 32

EC BIOS (128K)

B

page 37

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2010/08/04 2010/08/04

page 37

Compal Secret Data

Deciphered Date

D

Date: Sheet

Title

Size Document Number Rev

B

Compal Electronics, Inc.

Block Diagrams

QBL70 LA-7553P

251Friday, April 29, 2011

E

of

0.22

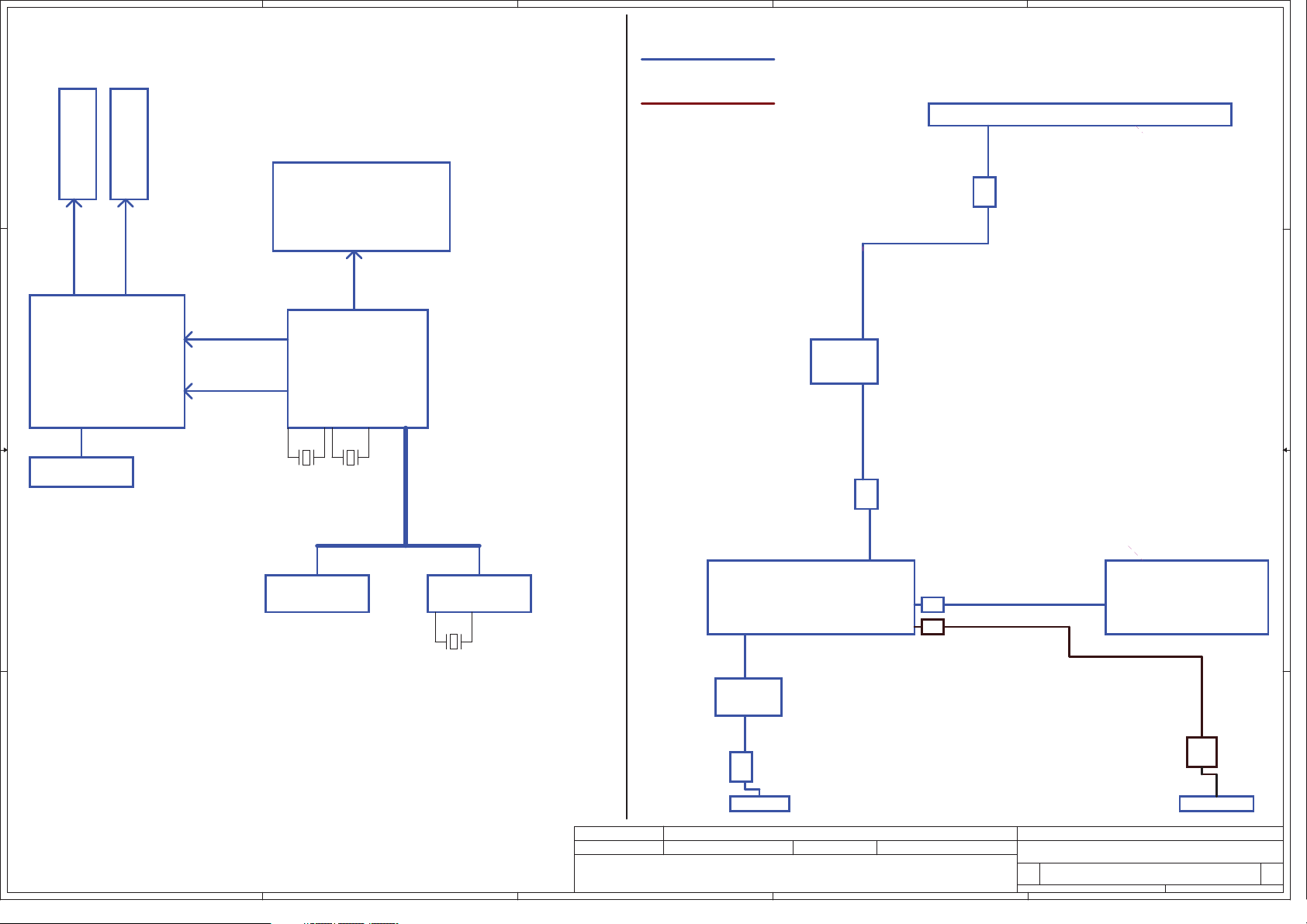

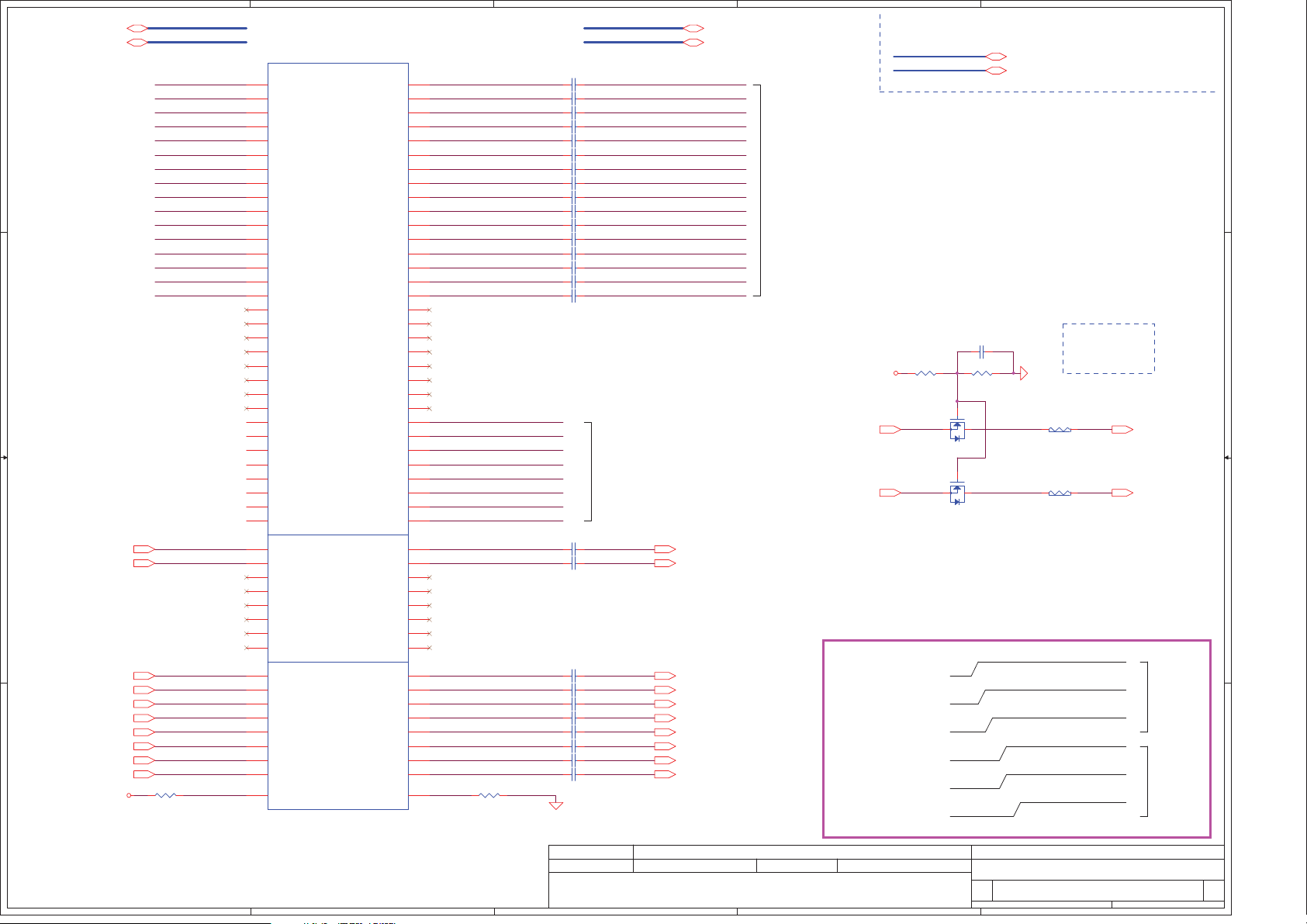

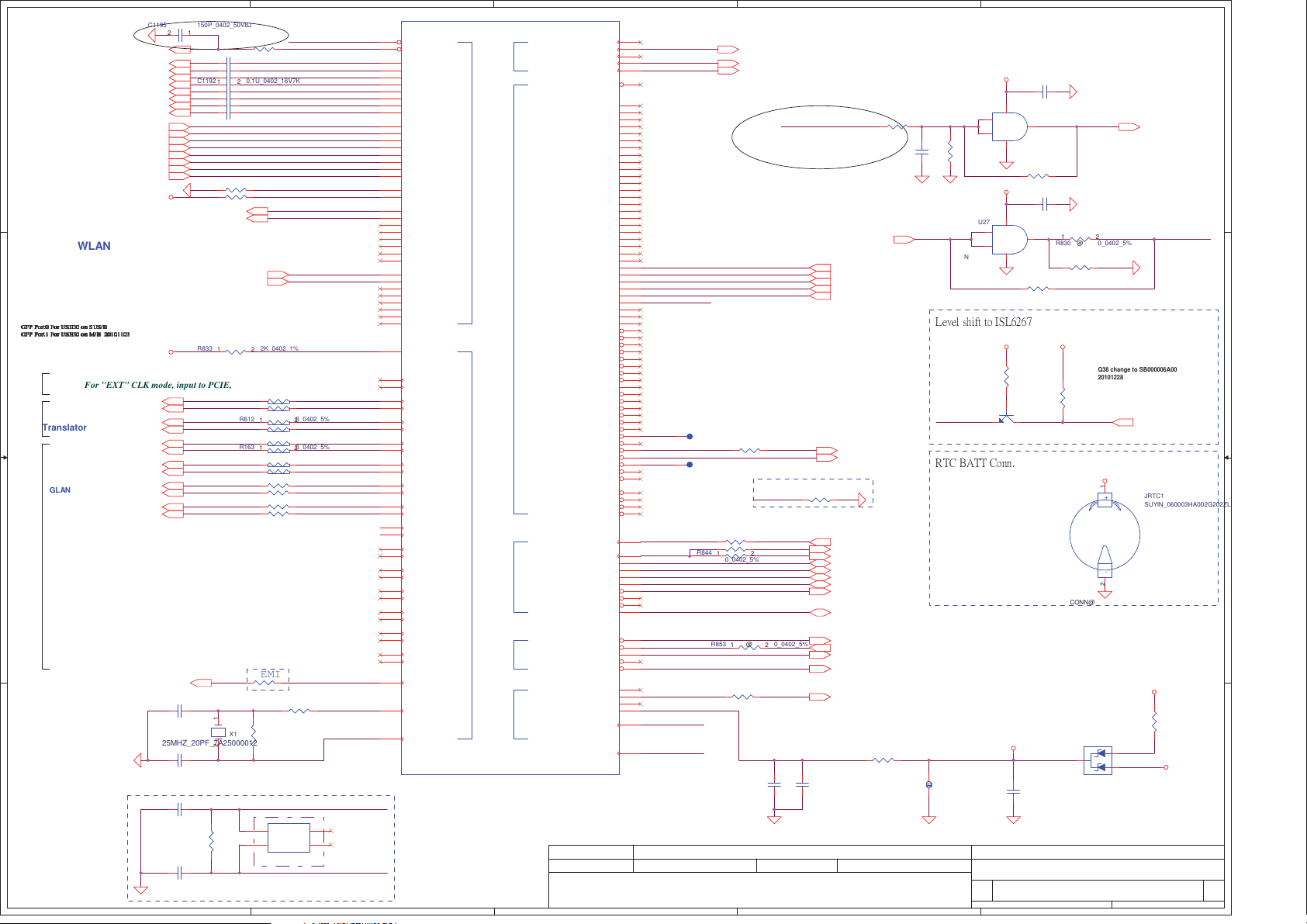

Page 3

5

4

3

2

1

CLOCK DISTRIBUTION

DISPLAY DISTRIBUTION

: LVDS PATH

D D

B_SODIMM

A_SODIMM

AMD

MEM_MA_CLK7_P/N

MEM_MB_CLK1_P/N

MEM_MB_CLK7_P/N

1066~1600MHz

C C

AMD

CPU FS1 SOCKET

DP0_AUX

MEM_MA_CLK1_P/N

1066~1600MHz

APU_DISP_CLKP/N

100MHz

APU_CLKP/N

100MHz

LVDS Transtator

ATI VG A

Whistler

CLK_PEG_VGAP/N

100MHz

AMD

FCH

Hudson-M2/M3

Internal CLK GEN

GPP_CLK

100MHz

32.768KHz 25MHz

: APU HDMI PATH

APU_TXOUT[0:2]+/APU_TXOUT_CLK+/APU_TZOUT[0:2]+/APU_TZOUT_CLK+/APU_LVDS_CLK/DATA

LVDS_OUT

RTD2132

DP_IN

C

TXOUT[0:2]+/TXCLK+/TZOUT[0:2]+/TZCLK+/I2CC_SCL/DA

LVDS CONN

R

DP0_TXP/N[0:1]

DP0_AUXP/N

B B

WLAN

Mini PCI Socket

GPP1

GbE LAN

25MHz

GPP0

APU

DP1

DP0

PCIE_GFX[0:7]

PCIE_GFX[12:15]

C

C

PCIE_GFX[0:7]

VGA

FCH

R

A A

http://hobi-elektronika.net

5

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2010/08/04 2010/08/04

Compal Secret Data

Deciphered Date

Title

CLOCK / DISPLAY DISTRIBUTION

Size Document Number Rev

Custom

QBL70 LA-7553P

2

Date: Sheet

LS

HDMI CONNCRT CONN

1

351Friday, April 29, 2011

0.22

of

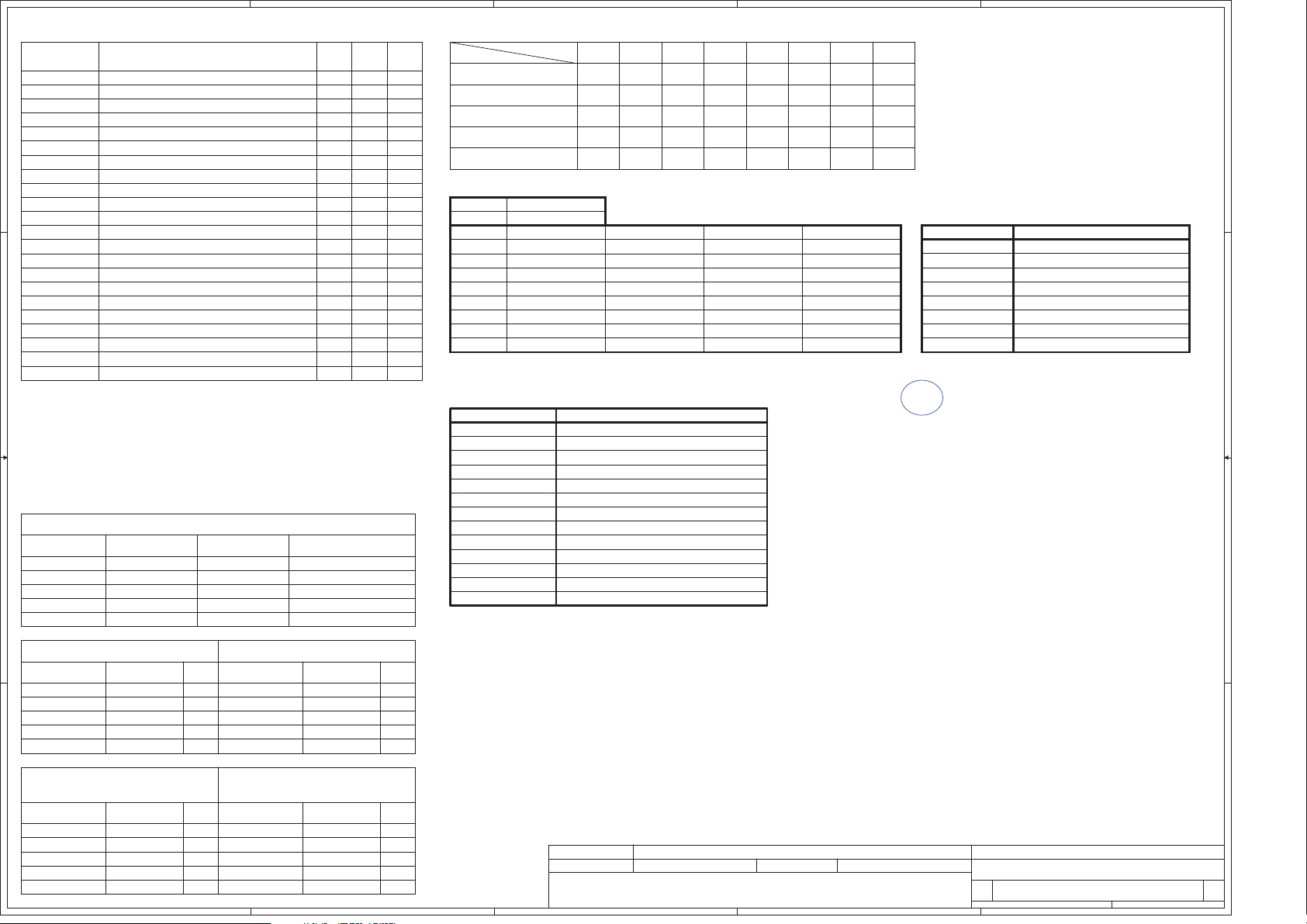

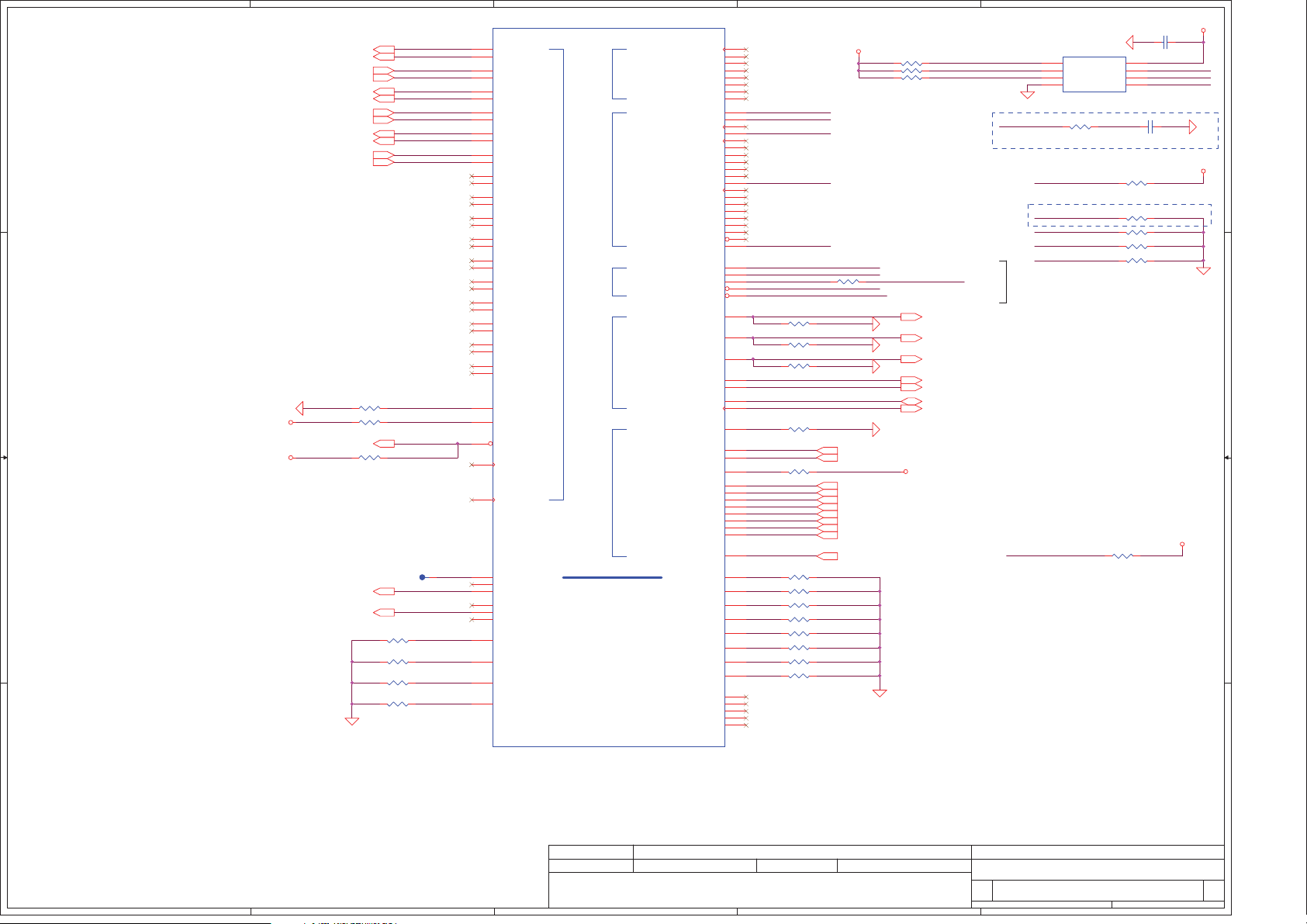

Page 4

A

B

C

D

E

Voltage Rails

SIGNAL

Power Plane Description

VIN

B+

+CPU_CORE

+CPU_CORE_1 ON OFF OFF

1 1

+CPU_CORE_NB ON OFF OFFVoltage for On-die VGA of APU

+VGA_CORE OFFOFFON0.95-1.2V switched power rail

+0.75VS ONON OFF0.75V swi tched power rai l for DDR termina tor

+1.0VSG ON OFF OFF1.0V switched power rail for VGA

+1.1ALW 1.1V switched power rail for FCH ON ON*ON

+1.1VS

+1.2VS ON OFF OFF

+1.5V ON

+1.5VS

+1.8VSG OFFON OFF1.8V switched power rail

+2.5VS

+3VALW

+3V_LAN ONONON

+3VS

+5VALW

+5VS

2 2

+VSB ON ON*

+RTCVCC

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

Adapter power supply ( 19V)

AC or battery power rail for power circuit.

Core voltage for CPU

Core voltage for CPU (0.7-1.2V)

1.2V switched power rail for APU

1.5V power r ail for CPU VDDIO a nd DDR

1.5V switched power rail

2.5V for CP U_VDDA

3.3V always on power rail

3.3V power rail for LAN

3.3V switched power rail

5V always on power rail

5V switched power rail

VSB always on power rail

RTC power

S1 S3 S5

N/A N/A N/A

ON OFF

ON OFF OFF1.1V switched power rail for FCH

ON OFF

ON

ON

ON

ON

ON

ON

N/AN/AN/A

OFF

OFF

ON

OFF

OFF

OFF

ON ON*

OFF

OFF

ON

ON*

OFF

OFFON

ONON

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF) LOW

Board ID / SKU ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7 NC

100K +/- 5%Ra/Rc/Re

Rb / Rd / Rf V min

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

SLP_S1# SLP_S3#

HIGH HIGH HIGH HIGH

LOW

LOW

LOW

LOW

LOW LOW

LOW

AD_BID

0

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

SLP_S4# SLP_S5# +VALW +V +VS Clock

ON

ON

ON

OFF

OFF

V

AD_BID

0.538 V

0.875 V

ON ON

ON

OFF

OFF

OFF

max

0 V

HIGH

LOW

HIGHHIGHHIGH

HIGH

HIGH

LOW

V typ

AD_BID

0.503 V

0.819 V

ON

ON

ON

ON

ON

0 V 0 V

1.185 V 1.264 V

2.200 V

3.300 V

2.341 V

3.300 V

LOW

OFF

OFF

OFF

BOARD ID Table

Board ID

M3@

U25

0

1

2

3

4

5

6

7

NA

P5WS5

P5WH5

P7YE5

P7YS5

NA

NA

NA

PCB Revision

BTO Option Table

BTO ItemBOM Structure

VGA@ Use VGA (Mux)

128@ Use VRAM channel A&B

M2@ Use Hudson-M2

x = 1 is read cmd, x= 0 is writee cmd.

External PCI Devices

Device IDSEL# REQ#/GNT# Interrupts

3 3

M3@ Use Hudson-M3

USB30@ USB30 on M/B

USB20@ USB20 on M/B

TranslatorTL@

VRAM ID TableX76@

FCH M3

Part Number = SA000043ID0

BOM Config

EC SM Bus1 address EC SM Bus2 address

Device Address HEX

Smart Battery

0001 011X b

FCH

SM Bus 0 address

4 4

Device Address Device Address

DDR DIMM1

DDR DIMM2

http://hobi-elektronika.net

1101 000X b

1101 001X b

A

Device Address HEX

16H

ADI ADM1032 (VGA)

1001 101X b

FCH

SM Bus 1 address

HEX

D0

D2

9AH

HEX

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2010/08/04 2010/08/04

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

B

D

Date: Sheet

Compal Electronics, Inc.

Notes List

QBL70 LA-7553P

E

451Friday, April 29, 2011

0.22

of

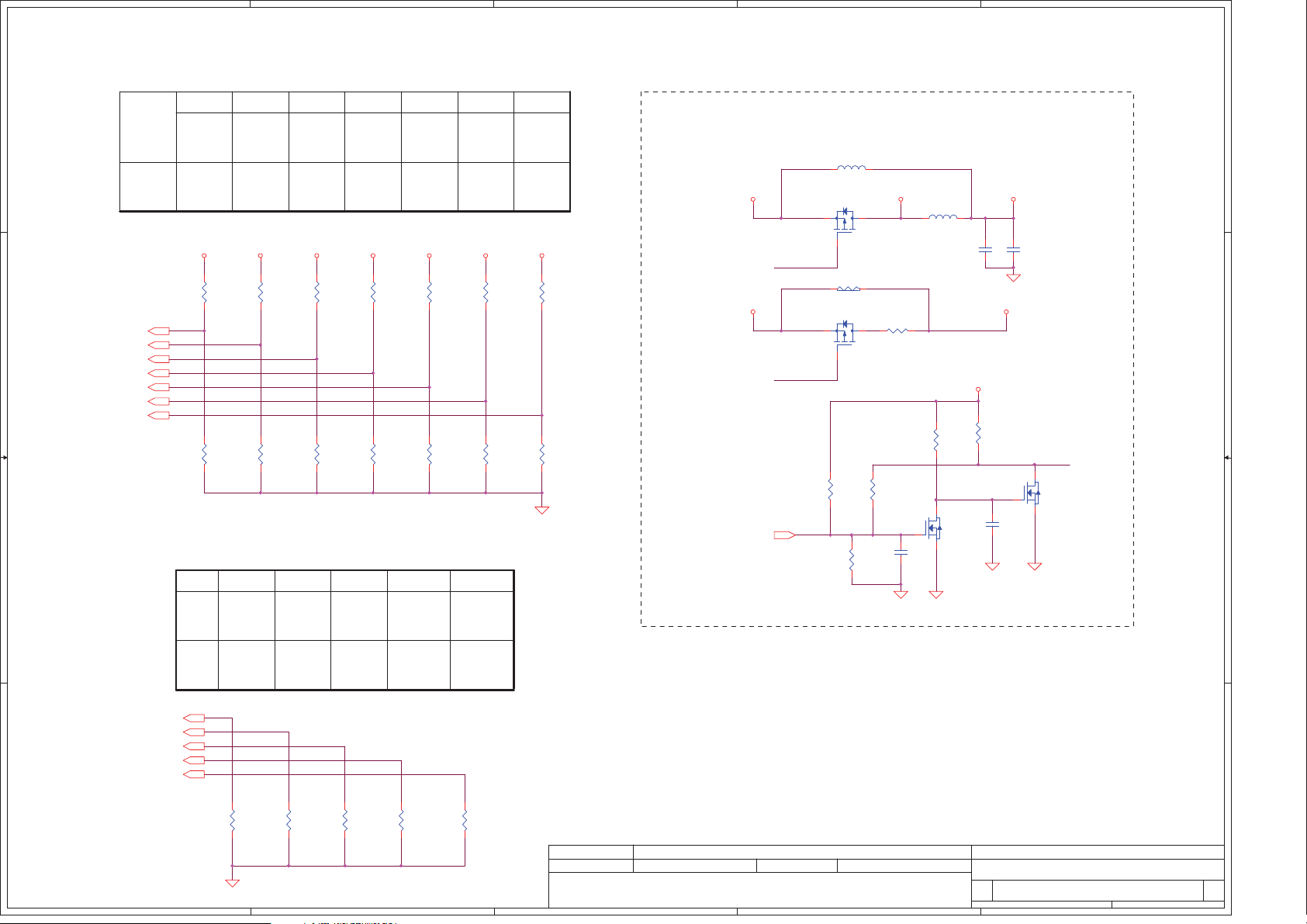

Page 5

5

4

3

2

1

BATTERY

12.6V

AC ADAPTOR

D D

19V 90W

BATT+

VIN

PU3

CHARGER

ISL6251AHAZ-T

B+

C C

+INVPWR_B+

LCD panel

15.6"

B+ 300mA

+3.3 350mA

B B

FAN Control

APL5607

+5VS 500mA

U22/U23

TPA2301DRG4

+USB_VCCA

+USB_VCCB

PU13

ISL6267HRZ-T

PU6

G5603RU1U

PU10

G5603RU1U

PU11

TPS51218DSCR

PU12

G5603RU1U

PU5

G5603RU1U

PU4

RT8205EGQW

+3VS

+5VS

+CPU_CORE

+CPU_CORE_NB

+1.5V

+1.2VS

+VGA_CORE

+VDDCI

+1.1VALW

+3VALW

+5VALW

+5VALW

+3VS

U33

SI4800

Q57

SI2301

U33

SI4800

+2.5VS

PU9

APL5508

PU8

G9731G11U

U34

AO4430L

PU7

SY8033BDBC

PU2

UP7711U8

+1.0VSG

+1.5VSG

+1.8VSG

Q61

SI2301

U34

AO4430L

+0.75VS

+3VSG

+1.1VS

+CPU_CORE

+CPU_CORE_NB

+2.5VS

+1.5V

+1.2VS

+0.75VS

+VGA_CORE

+VDDCI

+1.0VSG

+1.5VSG

+1.8VSG

+3VSG

+1.1VS

+1.1VALW

+3VS

USB X3

+5V

Dual+1

2.5A

SATA

HDD*2

ODD*1

+5V 3A

+3.3V

A A

Audio Codec

ALC271X

+5V 45mA

+3.3VS 25mA

Realtek

RTS5138

EC

ENE KB930

+3.3VALW 30mA

+3.3VS 3mA

+3VALW

LAN

Atheros AR8151

+3.3VALW 201mA

+1.5VS

Mini Card*2

+1.5VS 500mA

+3.3VS 1A+3.3VS 300mA

+3.3VALW 330mA

RTC

Bettary

+3VALW

AMD APU FS1

0.7~1.475V

0.7~1.475V

+2.5VS

+1.5V

+1.2VS

VDD CORE 54A

VDDNB 27.5A

VDDA 500mA

VDDIO 4.6A

VDDR 6.7A

RAM DDR III SODIMMX2

+1.5V

+0.75VS

0.85~1.1V

0.9~1.0V

+1.0VSG

+1.5VSG

+1.8VSG

+3VSG

VDD_MEM 4A

VTT_MEM 0.5A

VGA AT I

Whistler/Seymour/Granville

VDDC 47A

VDDCI 4.6A

DPLL_VDDC: 125 mA

SPV10: 120 mA

PCIE_VDDC: 2000 mA

DP[A:E]_VDD10: 680 mA

VDDR1: 3400 mA

PLL_PVDD: 75 mA

TSVDD: 20 mA

AVDD: 70 mA

VDD1DI: 100 mA

VDD2DI: 50 mA

A2VDDQ: 1.5 mA

VDD_CT: 110 mA

VDDR4: 170 mA

PCIE_PVDD: 40 mA

MPV18: 150 mA

SPV18: 75 mA

PCIE_VDDR: 400 mA

DP[A:F]_VDD18: 920 mA

DP[A:F]_PVDD: 120 mA

A2VDD: 130 mA

VDDR3: 60 mA

FCH AMD Hudson M2/M3

VDDPL_11_DAC: 7 mA

VDDAN_11_ML: 226 mA

VDDCR_11: 1007 mA

+1.1VS

VDDAN_11_CLK: 340 mA

VDDAN_11_PCIE: 1088 mA

VDDAN_11_SATA: 1337 mA

VDDAN_11_USB_S: 140 mA

VDDCR_11_USB_S: 197 mA

VDDAN_11_SSUSB_S: 282 mA

+1.1VALW

VDDCR_11_SSUSB_S: 424 mA

VDDCR_11_S: 187 mA

VDDPL_11_SYS: 70 mA

VDDIO_33_PCIGP: 131 mA

VDDPL_33_SYS: 47 mA

VDDPL_33_DAC: 20 mA

VDDPL_33_ML: 20 mA

VDDAN_33_DAC: 200 mA

+3VS

VDDPL_33_PCIE: 43 mA

VDDPL_33_SATA: 93 mA

VDDIO_AZ_S: 26 mA

VDDPL_33_SSUSB_S: 20 mA

VDDPL_33_USB_S: 17 mA

VDDAN_33_USB_S: 658 mA

+3VALW

VDDIO_33_S: 59 mA

VDDXL_33_S: 5 mA

VDDAN_33_HWM_S: 12 mA

VDDIO_33_GBE_S

VDDCR_11_GBE_S

GND

VDDIO_GBE_S

VDDBT_RTC_GRTC BAT

VRAM 512/1GB/2GB

64M / 128Mx16 * 4 / 8

+1.5VSG 2.4 A

http://hobi-elektronika.net

5

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

4

3

MAY BE USED BY OR DISCLOSED TO ANY TH IRD PARTY WITHOUT PRIOR WR ITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2010/08/04 2010/08/04

Compal Secret Dat a

Deciphered Date

2

Title

POWER DELIVE RY CHART

Size Document Number Rev

Custom

QBL70 LA-7553P

Date: Sheet

1

551Friday, April 29, 2011

of

0.22

Page 6

A

PCIE_GTX_C_FRX_P[0..7]18

JCPU1A

PCIE_GTX_C_FRX_P0

PCIE_GTX_C_FRX_N0

1 1

2 2

PCIE_DTX_C_FRX_P031

3 3

4 4

PCIE_DTX_C_FRX_N031

UMI_MTX_C_FRX_P013

UMI_MTX_C_FRX_N013

UMI_MTX_C_FRX_P113

UMI_MTX_C_FRX_N113

UMI_MTX_C_FRX_P213

UMI_MTX_C_FRX_N213

UMI_MTX_C_FRX_P313

UMI_MTX_C_FRX_N313

+1.2VS

PCIE_GTX_C_FRX_P1

PCIE_GTX_C_FRX_N1

PCIE_GTX_C_FRX_P2

PCIE_GTX_C_FRX_N2

PCIE_GTX_C_FRX_P3

PCIE_GTX_C_FRX_N3

PCIE_GTX_C_FRX_P4

PCIE_GTX_C_FRX_N4

PCIE_GTX_C_FRX_P5

PCIE_GTX_C_FRX_N5

PCIE_GTX_C_FRX_P6

PCIE_GTX_C_FRX_N6

PCIE_GTX_C_FRX_P7

PCIE_GTX_C_FRX_N7

1 2

R1802 196_0402_1%

P_ZVDDP

AA8

AA9

Y7

Y8

W5

W6

W8

W9

V7

V8

U5

U6

U8

U9

T7

T8

R5

R6

R8

R9

P7

P8

N5

N6

N8

N9

M7

M8

L5

L6

L8

L9

AC5

AC6

AC8

AC9

AB7

AB8

AA5

AA6

AF8

AF7

AE6

AE5

AE9

AE8

AD8

AD7

K5

AMD_TOPEDO_FS-1

P_GFX_RXP0

P_GFX_RXN0

P_GFX_RXP1

P_GFX_RXN1

P_GFX_RXP2

P_GFX_RXN2

P_GFX_RXP3

P_GFX_RXN3

P_GFX_RXP4

P_GFX_RXN4

P_GFX_RXP5

P_GFX_RXN5

P_GFX_RXP6

P_GFX_RXN6

P_GFX_RXP7

P_GFX_RXN7

P_GFX_RXP8

P_GFX_RXN8

P_GFX_RXP9

P_GFX_RXN9

P_GFX_RXP10

P_GFX_RXN10

P_GFX_RXP11

P_GFX_RXN11

P_GFX_RXP12

P_GFX_RXN12

P_GFX_RXP13

P_GFX_RXN13

P_GFX_RXP14

P_GFX_RXN14

P_GFX_RXP15

P_GFX_RXN15

P_GPP_RXP0

P_GPP_RXN0

P_GPP_RXP1

P_GPP_RXN1

P_GPP_RXP2

P_GPP_RXN2

P_GPP_RXP3

P_GPP_RXN3

P_UMI_RXP0

P_UMI_RXN0

P_UMI_RXP1

P_UMI_RXN1

P_UMI_RXP2

P_UMI_RXN2

P_UMI_RXP3

P_UMI_RXN3

P_ZVDDP

PCI EXPRESS

GPPUMI-LINK GRAPHICS

B

CONN@

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

P_GFX_TXP4

P_GFX_TXN4

P_GFX_TXP5

P_GFX_TXN5

P_GFX_TXP6

P_GFX_TXN6

P_GFX_TXP7

P_GFX_TXN7

P_GFX_TXP8

P_GFX_TXN8

P_GFX_TXP9

P_GFX_TXN9

P_GFX_TXP10

P_GFX_TXN10

P_GFX_TXP11

P_GFX_TXN11

P_GFX_TXP12

P_GFX_TXN12

P_GFX_TXP13

P_GFX_TXN13

P_GFX_TXP14

P_GFX_TXN14

P_GFX_TXP15

P_GFX_TXN15

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_UMI_TXP0

P_UMI_TXN0

P_UMI_TXP1

P_UMI_TXN1

P_UMI_TXP2

P_UMI_TXN2

P_UMI_TXP3

P_UMI_TXN3

P_ZVSS

PCIE_FTX_GRX_P0

AA2

PCIE_FTX_GRX_N0

AA3

PCIE_FTX_GRX_P1

Y2

PCIE_FTX_GRX_N1

Y1

PCIE_FTX_GRX_P2

Y4

PCIE_FTX_GRX_N2

Y5

PCIE_FTX_GRX_P3

W2

PCIE_FTX_GRX_N3

W3

PCIE_FTX_GRX_P4

V2

PCIE_FTX_GRX_N4

V1

PCIE_FTX_GRX_P5

V4

PCIE_FTX_GRX_N5

V5

PCIE_FTX_GRX_P6

U2

PCIE_FTX_GRX_N6

U3

PCIE_FTX_GRX_P7

T2

PCIE_FTX_GRX_N7

T1

T4

T5

R2

R3

P2

P1

P4

P5

PCIE_FTX_GRX_P12

N2

PCIE_FTX_GRX_N12

N3

PCIE_FTX_GRX_P13

M2

PCIE_FTX_GRX_N13

M1

PCIE_FTX_GRX_P14

M4

PCIE_FTX_GRX_N14

M5

PCIE_FTX_GRX_P15

L2

PCIE_FTX_GRX_N15

L3

PCIE_FTX_DRX_P0

AD4

PCIE_FTX_DRX_N0

AD5

AC2

AC3

AB2

AB1

AB4

AB5

UMI_FTX_MRX_P0

AF1

UMI_FTX_MRX_N0

AF2

UMI_FTX_MRX_P1

AF5

UMI_FTX_MRX_N1

AF4

UMI_FTX_MRX_P2

AE3

UMI_FTX_MRX_N2

AE2

UMI_FTX_MRX_P3

AD1

UMI_FTX_MRX_N3

AD2

P_ZVSS

K4

C917 0.1U_0402_16V7K

C918 0.1U_0402_16V7K

C919 0.1U_0402_16V7K

C920 0.1U_0402_16V7K

C921 0.1U_0402_16V7K

C922 0.1U_0402_16V7K

C923 0.1U_0402_16V7K

C924 0.1U_0402_16V7K

C925 0.1U_0402_16V7K

C926 0.1U_0402_16V7K

C927 0.1U_0402_16V7K

C928 0.1U_0402_16V7K

C929 0.1U_0402_16V7K

C930 0.1U_0402_16V7K

C931 0.1U_0402_16V7K

C932 0.1U_0402_16V7K

1 2

R1803 196_0402_1%

C

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

2

1

To HDMI

0

CK

C950 0.1U_0402_16V7K

1 2

C951 0.1U_0402_16V7K

1 2

C956 0.1U_0402_16V7K

1 2

C957 0.1U_0402_16V7K

1 2

C958 0.1U_0402_16V7K

1 2

C959 0.1U_0402_16V7K

1 2

C960 0.1U_0402_16V7K

1 2

C961 0.1U_0402_16V7K

1 2

C962 0.1U_0402_16V7K

1 2

C963 0.1U_0402_16V7K

1 2

PCIE_FTX_C_GRX_P[0..7] 18

PCIE_FTX_C_GRX_N[0..7] 18PCIE_GTX_C_FRX_N[0..7]18

PCIE_FTX_C_GRX_P0

PCIE_FTX_C_GRX_N0

PCIE_FTX_C_GRX_P1

PCIE_FTX_C_GRX_N1

PCIE_FTX_C_GRX_P2

PCIE_FTX_C_GRX_N2

PCIE_FTX_C_GRX_P3

PCIE_FTX_C_GRX_N3

PCIE_FTX_C_GRX_P4

PCIE_FTX_C_GRX_N4

PCIE_FTX_C_GRX_P5

PCIE_FTX_C_GRX_N5

PCIE_FTX_C_GRX_P6

PCIE_FTX_C_GRX_N6

PCIE_FTX_C_GRX_P7

PCIE_FTX_C_GRX_N7

PCIE_FTX_C_DRX_P0 31

PCIE_FTX_C_DRX_N0 31

UMI_FTX_C_MRX_P0 13

UMI_FTX_C_MRX_N0 13

UMI_FTX_C_MRX_P1 13

UMI_FTX_C_MRX_N1 13

UMI_FTX_C_MRX_P2 13

UMI_FTX_C_MRX_N2 13

UMI_FTX_C_MRX_P3 13

UMI_FTX_C_MRX_N3 13

For UMA Mux.

GLAN

D

APU To HDMI

CPU TSI interface level shift

C935 0.1U_0402_16V4Z

1 2

R1798

1 2

+3VS

31.6K_0402_1%

APU_SID8,14

APU_SIC8,14

APU_SID

BSH111 1N_SOT23-3

APU_SIC

BSH111 1N_SOT23-3

G

S

G

S

1 2

30K_0402_1%

2

Q9

13

D

2

Q10

13

D

Power Sequence of APU

+1.5V

+2.5VS

+1.5VS

+CPU_CORE

+CPU_CORE_NB

+1.2VS

R1799

EC_SMB_DA

EC_SMB_CK

PCIE_FTX_GRX_P[12..15] 28

PCIE_FTX_GRX_N[12..15] 28

BSH111, the Vgs is:

min = 0.4V

Max = 1.3V

1 2

R1800 0_0402_5%

1 2

R1801 0_0402_5%

E

EC_SMB_DA2 19,32

To EC

EC_SMB_CK2 19,32

Group A

Group B

http://hobi-elektronika.net

A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2010/08/04 2010/08/04

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

D

Date: Sheet

Compal Electronics, Inc.

AMD FS1 PCIE / UMI / TSI

QBL70 LA-7553P

E

651Friday, April 29, 2011

0.22

of

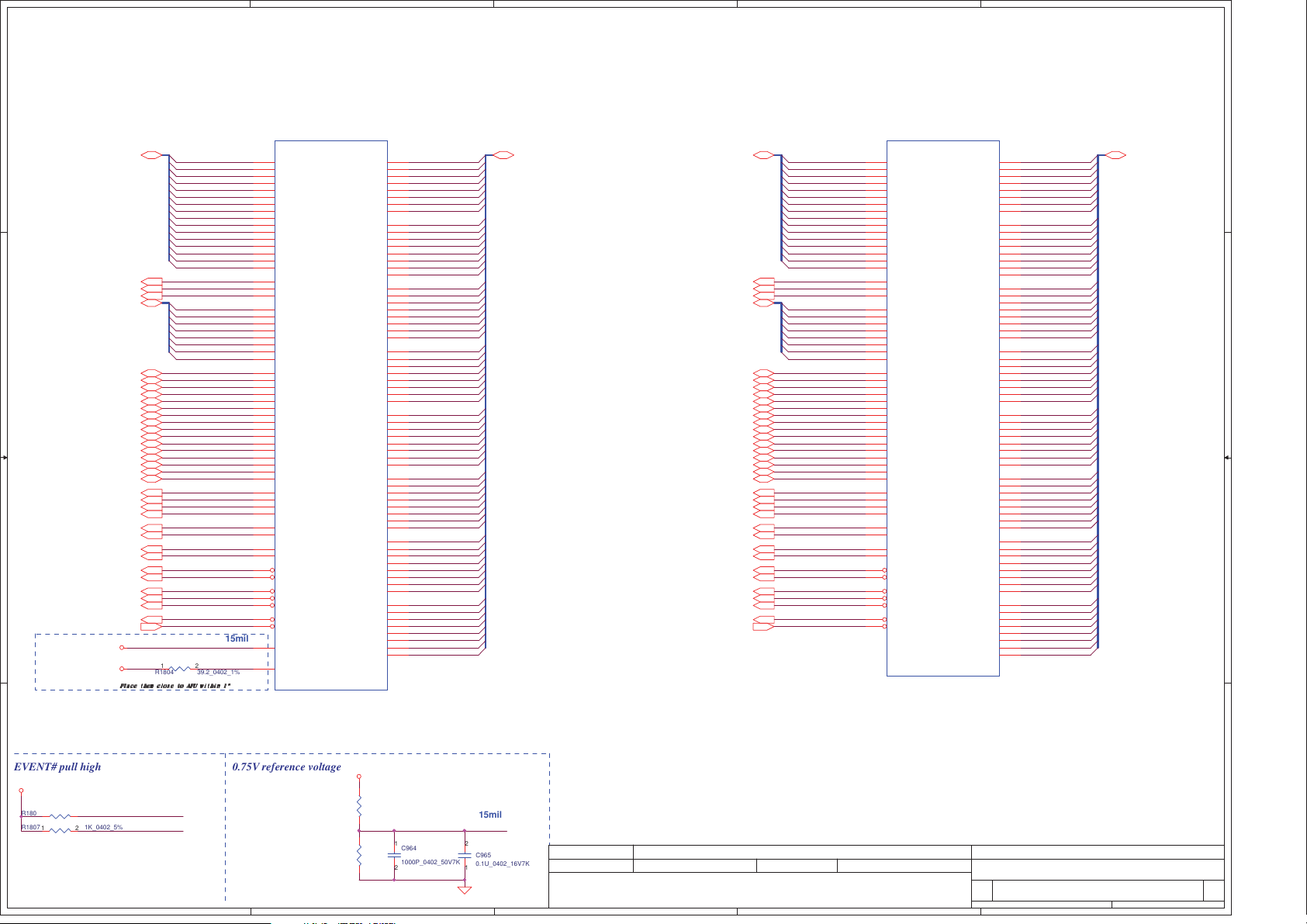

Page 7

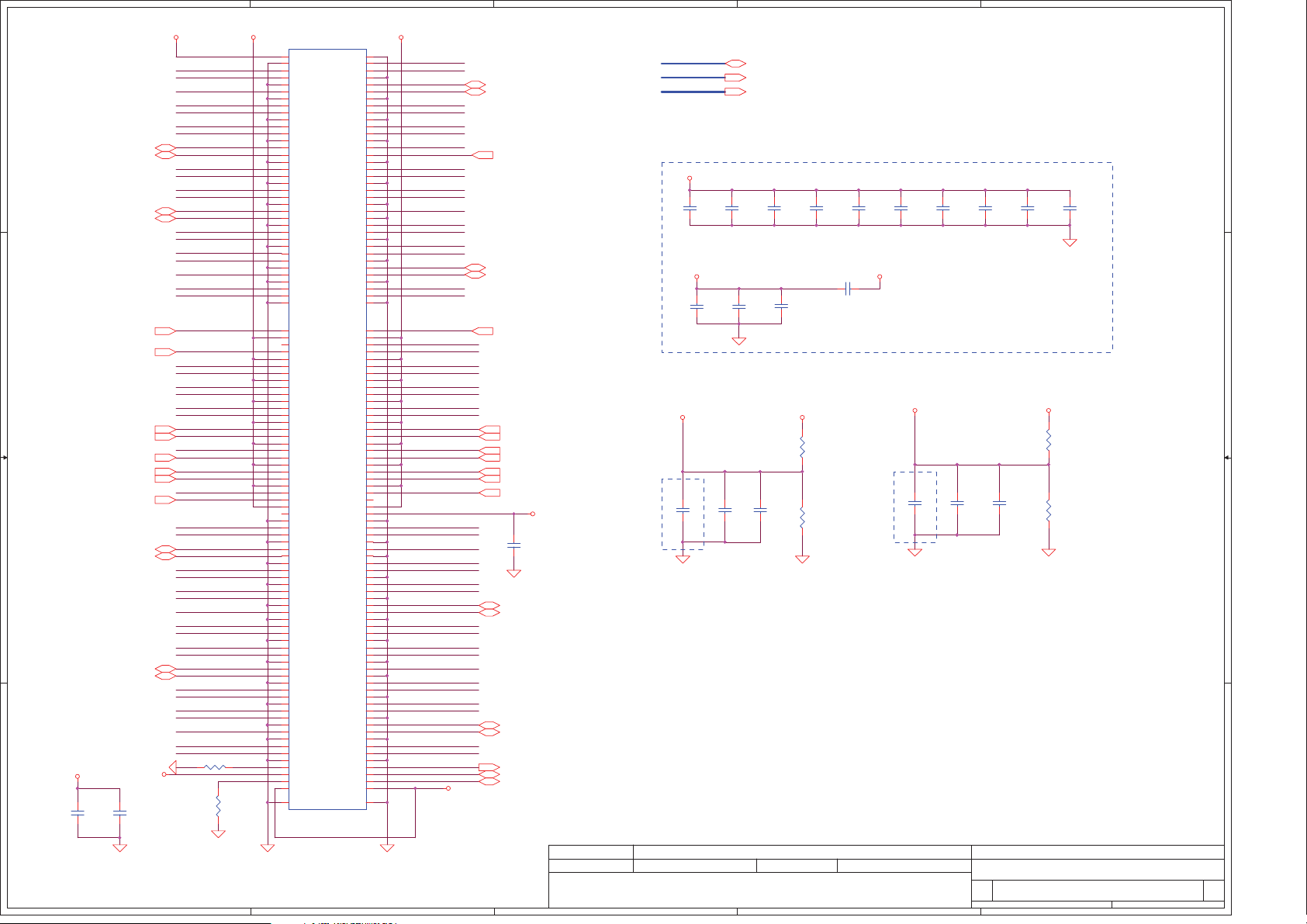

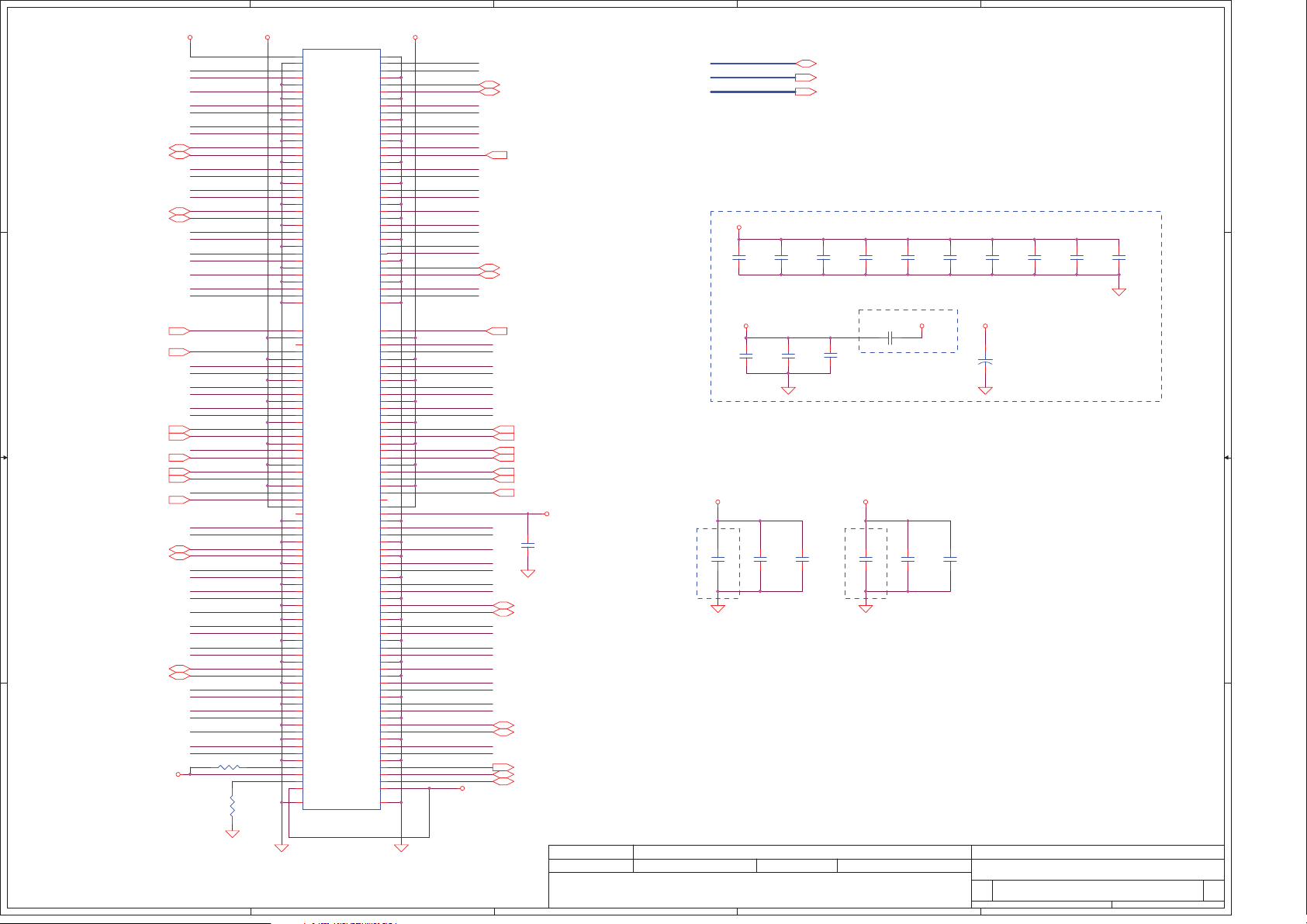

A

1 1

JCPU1B

DDRA_SMA[15..0]11

DDRA_SBS0#11

DDRA_SBS1#11

DDRA_SBS2#11

DDRA_SDM[7..0]11

2 2

DDRA_SDQS011

DDRA_SDQS0#11

DDRA_SDQS111

DDRA_SDQS1#11

DDRA_SDQS211

DDRA_SDQS2#11

DDRA_SDQS311

DDRA_SDQS3#11

DDRA_SDQS411

DDRA_SDQS4#11

DDRA_SDQS511

DDRA_SDQS5#11

DDRA_SDQS611

DDRA_SDQS6#11

DDRA_SDQS711

DDRA_SDQS7#11

DDRA_CLK011

DDRA_CLK0#11

DDRA_CLK111

DDRA_CLK1#11

DDRA_CKE011

DDRA_CKE111

DDRA_ODT011

DDRA_ODT111

3 3

DDRA_SCS0#11

DDRA_SCS1#11

DDRA_SRAS#11

DDRA_SCAS#11

DDRA_SWE#11

MEM_MA_RST#11

MEM_MA_EVENT#11

+MEM_VREF

+1.5V

Qmbdf!uifn!dmptf!up!BQV!xjuijo!2#

Qmbdf!uifn!dmptf!up!BQV!xjuijo!2#

Qmbdf!uifn!dmptf!up!BQV!xjuijo!2#Qmbdf!uifn!dmptf!up!BQV!xjuijo!2#

DDRA_SMA0

DDRA_SMA1

DDRA_SMA2

DDRA_SMA3

DDRA_SMA4

DDRA_SMA5

DDRA_SMA6

DDRA_SMA7

DDRA_SMA8

DDRA_SMA9

DDRA_SMA10

DDRA_SMA11

DDRA_SMA12

DDRA_SMA13

DDRA_SMA14

DDRA_SMA15

DDRA_SBS0#

DDRA_SBS1#

DDRA_SBS2#

DDRA_SDM0

DDRA_SDM1

DDRA_SDM2

DDRA_SDM3

DDRA_SDM4

DDRA_SDM5

DDRA_SDM6

DDRA_SDM7

DDRA_SDQS0

DDRA_SDQS0#

DDRA_SDQS1

DDRA_SDQS1#

DDRA_SDQS2

DDRA_SDQS2#

DDRA_SDQS3

DDRA_SDQS3#

DDRA_SDQS4

DDRA_SDQS4#

DDRA_SDQS5

DDRA_SDQS5#

DDRA_SDQS6

DDRA_SDQS6#

DDRA_SDQS7

DDRA_SDQS7#

DDRA_CLK0

DDRA_CLK0#

DDRA_CLK1

DDRA_CLK1#

DDRA_CKE0

DDRA_CKE1

DDRA_ODT0

DDRA_ODT1

DDRA_SCS0#

DDRA_SCS1#

DDRA_SRAS#

DDRA_SCAS#

DDRA_SWE#

MEM_MA_RST#

MEM_MA_EVENT#

15mil

1 2

R1804 39.2_0402_1%

M_ZVDDIO

U20

MA_ADD0

R20

MA_ADD1

R21

MA_ADD2

P22

MA_ADD3

P21

MA_ADD4

N24

MA_ADD5

N23

MA_ADD6

N20

MA_ADD7

N21

MA_ADD8

M21

MA_ADD9

U23

MA_ADD10

M22

MA_ADD11

L24

MA_ADD12

AA25

MA_ADD13

L21

MA_ADD14

L20

MA_ADD15

U24

MA_BANK0

U21

MA_BANK1

L23

MA_BANK2

E14

MA_DM0

J17

MA_DM1

E21

MA_DM2

F25

MA_DM3

AD27

MA_DM4

AC23

MA_DM5

AD19

MA_DM6

AC15

MA_DM7

G14

MA_DQS_H0

H14

MA_DQS_L0

G18

MA_DQS_H1

H18

MA_DQS_L1

J21

MA_DQS_H2

H21

MA_DQS_L2

E27

MA_DQS_H3

E26

MA_DQS_L3

AE26

MA_DQS_H4

AD26

MA_DQS_L4

AB22

MA_DQS_H5

AA22

MA_DQS_L5

AB18

MA_DQS_H6

AA18

MA_DQS_L6

AA14

MA_DQS_H7

AA15

MA_DQS_L7

T21

MA_CLK_H0

T22

MA_CLK_L0

R23

MA_CLK_H1

R24

MA_CLK_L1

H28

MA_CKE0

H27

MA_CKE1

Y25

MA_ODT0

AA27

MA_ODT1

V22

MA_CS_L0

AA26

MA_CS_L1

V21

MA_RAS_L

W24

MA_CAS_L

W23

MA_WE_L

H25

MA_RESET_L

T24

MA_EVENT_L

W20

M_VREF

W21

M_ZVDDIO

AMD_TOPEDO_FS-1

MEMORY CHANNEL A

CONN@

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

B

E13

J13

H15

J15

H13

F13

F15

E15

H17

F17

E19

J19

G16

H16

H19

F19

H20

F21

J23

H23

G20

E20

G22

H22

G24

E25

G27

G26

F23

H24

E28

F27

AB28

AC27

AD25

AA24

AE28

AD28

AB26

AC25

Y23

AA23

Y21

AA20

AB24

AD24

AA21

AC21

AA19

AC19

AC17

AA17

AB20

Y19

AD18

AD17

AA16

Y15

AA13

AC13

Y17

AB16

AB14

Y13

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDQ2

DDRA_SDQ3

DDRA_SDQ4

DDRA_SDQ5

DDRA_SDQ6

DDRA_SDQ7

DDRA_SDQ8

DDRA_SDQ9

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ12

DDRA_SDQ13

DDRA_SDQ14

DDRA_SDQ15

DDRA_SDQ16

DDRA_SDQ17

DDRA_SDQ18

DDRA_SDQ19

DDRA_SDQ20

DDRA_SDQ21

DDRA_SDQ22

DDRA_SDQ23

DDRA_SDQ24

DDRA_SDQ25

DDRA_SDQ26

DDRA_SDQ27

DDRA_SDQ28

DDRA_SDQ29

DDRA_SDQ30

DDRA_SDQ31

DDRA_SDQ32

DDRA_SDQ33

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ36

DDRA_SDQ37

DDRA_SDQ38

DDRA_SDQ39

DDRA_SDQ40

DDRA_SDQ41

DDRA_SDQ42

DDRA_SDQ43

DDRA_SDQ44

DDRA_SDQ45

DDRA_SDQ46

DDRA_SDQ47

DDRA_SDQ48

DDRA_SDQ49

DDRA_SDQ50

DDRA_SDQ51

DDRA_SDQ52

DDRA_SDQ53

DDRA_SDQ54

DDRA_SDQ55

DDRA_SDQ56

DDRA_SDQ57

DDRA_SDQ58

DDRA_SDQ59

DDRA_SDQ60

DDRA_SDQ61

DDRA_SDQ62

DDRA_SDQ63

DDRA_SDQ[63..0] 11

C

DDRB_SMA[15..0]12

DDRB_SBS0#12

DDRB_SBS1#12

DDRB_SBS2#12

DDRB_SDM[7..0]12

DDRB_SDQS012

DDRB_SDQS0#12

DDRB_SDQS112

DDRB_SDQS1#12

DDRB_SDQS212

DDRB_SDQS2#12

DDRB_SDQS312

DDRB_SDQS3#12

DDRB_SDQS412

DDRB_SDQS4#12

DDRB_SDQS512

DDRB_SDQS5#12

DDRB_SDQS612

DDRB_SDQS6#12

DDRB_SDQS712

DDRB_SDQS7#12

DDRB_CLK012

DDRB_CLK0#12

DDRB_CLK112

DDRB_CLK1#12

DDRB_CKE012

DDRB_CKE112

DDRB_ODT012

DDRB_ODT112

DDRB_SCS0#12

DDRB_SCS1#12

DDRB_SRAS#12

DDRB_SCAS#12

DDRB_SWE#12

MEM_MB_RST#12

MEM_MB_EVENT#12

DDRB_SMA0

DDRB_SMA1

DDRB_SMA2

DDRB_SMA3

DDRB_SMA4

DDRB_SMA5

DDRB_SMA6

DDRB_SMA7

DDRB_SMA8

DDRB_SMA9

DDRB_SMA10

DDRB_SMA11

DDRB_SMA12

DDRB_SMA13

DDRB_SMA14

DDRB_SMA15

DDRB_SBS0#

DDRB_SBS1#

DDRB_SBS2#

DDRB_SDM0

DDRB_SDM1

DDRB_SDM2

DDRB_SDM3

DDRB_SDM4

DDRB_SDM5

DDRB_SDM6

DDRB_SDM7

DDRB_SDQS0

DDRB_SDQS0#

DDRB_SDQS1

DDRB_SDQS1#

DDRB_SDQS2

DDRB_SDQS2#

DDRB_SDQS3

DDRB_SDQS3#

DDRB_SDQS4

DDRB_SDQS4#

DDRB_SDQS5

DDRB_SDQS5#

DDRB_SDQS6

DDRB_SDQS6#

DDRB_SDQS7

DDRB_SDQS7#

DDRB_CLK0

DDRB_CLK0#

DDRB_CLK1

DDRB_CLK1#

DDRB_CKE0

DDRB_CKE1

DDRB_ODT0

DDRB_ODT1

DDRB_SCS0#

DDRB_SCS1#

DDRB_SRAS#

DDRB_SCAS#

DDRB_SWE#

MEM_MB_RST#

MEM_MB_EVENT#

D

T27

P24

P25

N27

N26

M28

M27

M24

M25

L26

U26

L27

K27

W26

K25

K24

U27

T28

K28

D14

A18

A22

C25

AF25

AG22

AH18

AD14

C15

B15

E18

D18

E22

D22

B26

A26

AG24

AG25

AG21

AF21

AG17

AG18

AH14

AG14

R26

R27

P27

P28

J26

J27

W27

Y28

V25

Y27

V24

V27

V28

J25

T25

JCPU1C

MEMORY CHANNEL B

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

MB_CLK_H0

MB_CLK_L0

MB_CLK_H1

MB_CLK_L1

MB_CKE0

MB_CKE1

MB_ODT0

MB_ODT1

MB_CS_L0

MB_CS_L1

MB_RAS_L

MB_CAS_L

MB_WE_L

MB_RESET_L

MB_EVENT_L

AMD_TOPEDO_FS-1

CONN@

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

A14

B14

D16

E16

B13

C13

B16

A16

C17

B18

B20

A20

E17

B17

B19

C19

C21

B22

C23

A24

D20

B21

E23

B23

E24

B25

B27

D28

B24

D24

D26

C27

AG26

AH26

AF23

AG23

AG27

AF27

AH24

AE24

AE22

AH22

AE20

AH20

AD23

AD22

AD21

AD20

AF19

AE18

AE16

AH16

AG20

AG19

AF17

AD16

AG15

AD15

AG13

AD13

AG16

AF15

AE14

AF13

DDRB_SDQ0

DDRB_SDQ1

DDRB_SDQ2

DDRB_SDQ3

DDRB_SDQ4

DDRB_SDQ5

DDRB_SDQ6

DDRB_SDQ7

DDRB_SDQ8

DDRB_SDQ9

DDRB_SDQ10

DDRB_SDQ11

DDRB_SDQ12

DDRB_SDQ13

DDRB_SDQ14

DDRB_SDQ15

DDRB_SDQ16

DDRB_SDQ17

DDRB_SDQ18

DDRB_SDQ19

DDRB_SDQ20

DDRB_SDQ21

DDRB_SDQ22

DDRB_SDQ23

DDRB_SDQ24

DDRB_SDQ25

DDRB_SDQ26

DDRB_SDQ27

DDRB_SDQ28

DDRB_SDQ29

DDRB_SDQ30

DDRB_SDQ31

DDRB_SDQ32

DDRB_SDQ33

DDRB_SDQ34

DDRB_SDQ35

DDRB_SDQ36

DDRB_SDQ37

DDRB_SDQ38

DDRB_SDQ39

DDRB_SDQ40

DDRB_SDQ41

DDRB_SDQ42

DDRB_SDQ43

DDRB_SDQ44

DDRB_SDQ45

DDRB_SDQ46

DDRB_SDQ47

DDRB_SDQ48

DDRB_SDQ49

DDRB_SDQ50

DDRB_SDQ51

DDRB_SDQ52

DDRB_SDQ53

DDRB_SDQ54

DDRB_SDQ55

DDRB_SDQ56

DDRB_SDQ57

DDRB_SDQ58

DDRB_SDQ59

DDRB_SDQ60

DDRB_SDQ61

DDRB_SDQ62

DDRB_SDQ63

E

DDRB_SDQ[63..0] 12

EVENT# pull high 0.75V reference voltage

+1.5V

4 4

R1806 1K_0402_5%

1 2

R1807 1K_0402_5%

1 2

http://hobi-elektronika.net

MEM_MA_EVENT#

MEM_MB_EVENT# +MEM_VREF

A

R1805

1K_0402_1%

R1808

1K_0402_1%

+1.5V

1 2

1 2

B

1

C964

1000P_0402_50V7K

2

15mil

2

C965

0.1U_0402_16V7K

1

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2010/08/04 2010/08/04

Compal Secret Data

Deciphered Date

Custom

D

Date: Sheet

Title

Size Document Number Rev

Compal Electronics, Inc.

AMD FS1 DDRIII I/F

QBL70 LA-7553P

751Friday, April 29, 2011

E

of

0.22

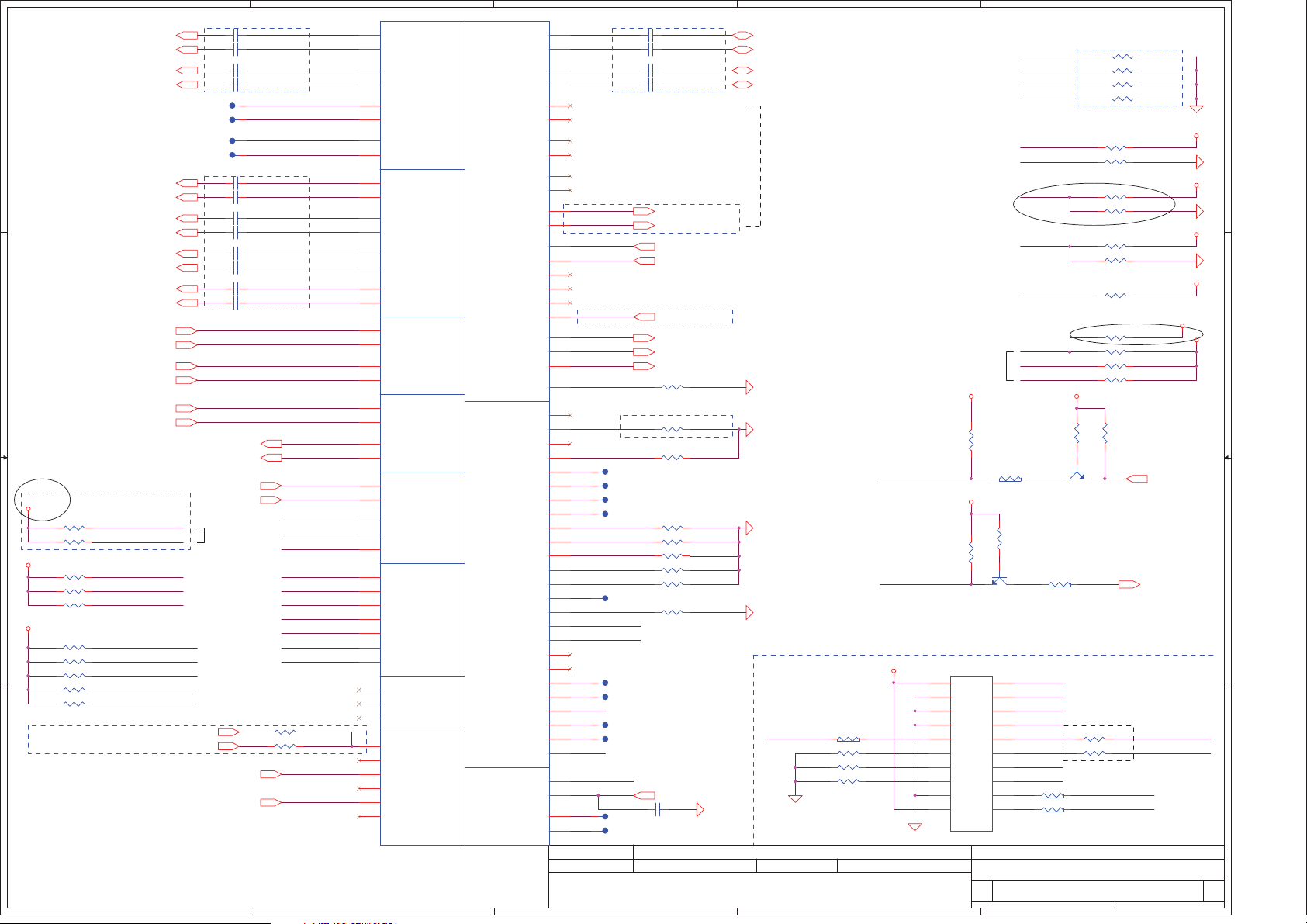

Page 8

A

Place near APU

C971 0.1U_0402_16V7K

DP0_TXP0_C26

To LVDS

Translator

1 1

To FCH VGA ML

100MHz

2 2

100MHz_NSS

+1.5V

R575 1K_0402_5%

1 2

R576 1K_0402_5%

1 2

+1.5V

3 3

R579 1K_0402_5%

1 2

R581 1K_0402_5%

1 2

R791 1K_0402_5%

1 2

+1.5V

Close to Header

R592 1K_0402_5%

1 2

R593 1K_0402_5%

1 2

R594 1K_0402_5%

1 2

R595 1K_0402_5%

1 2

R596 300_0402_5%

1 2

Route as differen tial

with VSS_SENSE

4 4

http://hobi-elektronika.net

DP0_TXN0_C26

DP0_TXP1_C26

DP0_TXN1_C26

ML_VGA_TXP015

ML_VGA_TXN015

ML_VGA_TXP115

ML_VGA_TXN115

ML_VGA_TXP215

ML_VGA_TXN215

ML_VGA_TXP315

ML_VGA_TXN315

APU_CLKP13

APU_CLKN13

APU_DISP_CLKP13

APU_DISP_CLKN13

APU_SVC47

APU_SVD47

Chang to PU +1.5VS (D G ref.)

20101111

APU_SVC

APU_SVD

APU_SIC

APU_SID

ALERT_L

APU_TDI

APU_TCK

APU_TMS

APU_TRST#

APU_DBREQ#

APU_VDDNB_RUN_FB_L47

APU_VDD_RUN_FB_L47

A

1 2

C973 0.1U_0402_16V7K

1 2

C1016 0.1U_0402_16V7K

1 2

C1017 0.1U_0402_16V7K

1 2

T35

T20

T21

T22

Place near APU

C977 0.1U_0402_16V7K

1 2

C968 0.1U_0402_16V7K

1 2

C969 0.1U_0402_16V7K

1 2

C970 0.1U_0402_16V7K

1 2

C978 0.1U_0402_16V7K

1 2

C979 0.1U_0402_16V7K

1 2

C980 0.1U_0402_16V7K

1 2

C981 0.1U_0402_16V7K

1 2

APU_CLKP

APU_CLKN

APU_DISP_CLKP

APU_DISP_CLKN

APU_SVC

APU_SVD

APU_SIC6,14

TSI

APU_SID6,14

APU_RST#13

APU_PWRGD13

Serial VID

R597 0_0402_5%

R600 0_0402_5%

APU_VDDNB_SEN47

APU_VDD_SEN47

APU_SIC

APU_SID

APU_RST#

APU_PWRGD

APU_PROCHOT#

APU_THERMTRIP#

ALERT_L

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBRDY

APU_DBREQ#

1 2

1 2

APU_VDDNB_SEN

APU_VDD_SEN

DP0_TXP0

DP0_TXN0

DP0_TXP1

DP0_TXN1

DP0_TXP2

DP0_TXN2

DP0_TXP3

DP0_TXN3

DP1_TXP0

DP1_TXN0

DP1_TXP1

DP1_TXN1

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

B

JCPU1D

F2

DP0_TXP0

F1

DP0_TXN0

E3

DP0_TXP1

E2

DP0_TXN1

D2

DP0_TXP2

D1

DP0_TXN2

C2

DP0_TXP3

C3

DP0_TXN3

K2

DP1_TXP0

K1

DP1_TXN0

J3

DP1_TXP1

J2

DP1_TXN1

H2

DP1_TXP2

H1

DP1_TXN2

G2

DP1_TXP3

G3

DP1_TXN3

AH7

CLKIN_H

AH6

CLKIN_L

AH4

DISP_CLKIN_H

AH3

DISP_CLKIN_L

B8

SVC

A8

SVD

AH11

SIC

AG11

SID

AF10

RESET_L

AE10

PWROK

AD10

PROCHOT_L

AG12

THERMTRIP_L

AH12

ALERT_L

C12

TDI

A12

TDO

A11

TCK

D12

TMS

B12

TRST_L

B11

DBRDY

C11

DBREQ_L

E8

RSVD_1

K21

RSVD_2

AC11

RSVD_3

B9

VSS_SENSE

C8

VDDP_SENSE

A9

VDDNB_SENSE

B10

VDDIO_SENSE

C9

VDD_SENSE

A10

VDDR_SENSE

AMD_TOPEDO_FS-1

B

DISPLAY PORT 0DISPLAY PORT 1CLKSER.CTRLJTAG RSVDSENSE

System DP

CONN@

DP0_AUXP

DP0_AUXN

DP1_AUXP

DP1_AUXN

DP2_AUXP

DP2_AUXN

DP3_AUXP

DP3_AUXN

DP4_AUXP

DP4_AUXN

DP5_AUXP

DP5_AUXN

DP0_HPD

DP1_HPD

DP2_HPD

DP3_HPD

DP4_HPD

DP5_HPD

DP_BLON

DP_DIGON

DP_VARY_BL

DP_AUX_ZVSS

TEST6

TEST9

TEST10

TEST12

TEST14

TEST15

TEST16

TEST17

TEST18

TEST19

TEST20

TEST21

TEST DISPLAY PORT MISC.

TEST22

TEST23

TEST24

TEST25_H

TEST25_L

TEST28_H

TEST28_L

TEST30_H

TEST30_L

TEST31

TEST32_H

TEST32_L

TEST35

FS1R1

DMAACTIVE_L

THERMDA

THERMDC

C

Place near APU

DP0_AUXP

D4

DP0_AUXN

D5

ML_VGA_AUXP

E5

ML_VGA_AUXN

E6

J5

J6

H4

H5

G5

G6

APU_HDMI_CLK

F4

APU_HDMI_DATA

F5

D7

E7

J7

H7

G7

F7

C6

C5

C7

D8

AA10

G10

H10

H12

D9

E9

G9

H9

H11

G11

F12

E11

D11

F10

G12

AH10

AH9

K7

K8

AA12

AB12

K22

AB11

AA11

D10

Y11

AB10

AE12

AD12

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C972 0.1U_0402_16V7K

1 2

C974 0.1U_0402_16V7K

1 2

C975 0.1U_0402_16V7K

1 2

C976 0.1U_0402_16V7K

1 2

APU_HDMI_CLK 28

APU_HDMI_DATA 28

DP0_HPD

DP1_HPD

DP5_HPD

DP_ENBKL

DP_ENVDD

DP_INT_PWM

DP_AUX_ZVSS

T6

T7

T8

T9

APU_TEST18

APU_TEST19

APU_TEST20

APU_TEST21

APU_TEST22

T10

APU_TEST24

TEST25_H

TEST25_L

T11

T12

M_TEST

T13

T14

TEST35

FS1R1

ALLOW_STOP

T15

T16

Llano do not support this thermal die

DP0_HPD 10

DP1_HPD 10

DP5_HPD 10

DP_ENBKL 10

DP_ENVDD 10

DP_INT_PWM 10

R569 150_0402_1%

1 2

Chang to unpop (DG ref.)

20101111

R573 0_0402_5%@

1 2

R574 1K_0402_5%

1 2

R582 1K_0402_5%

1 2

R583 1K_0402_5%

1 2

R584 1K_0402_5%

1 2

R585 1K_0402_5%

1 2

R589 1K_0402_5%

1 2

R590 1K_0402_5%

1 2

ALLOW_STOP 13

C639 0.1U_0402_16V4Z

1 2

@

2010/08/04 2010/08/04

C

DP0_AUXP_C 26

DP0_AUXN_C 26

ML_VGA_AUXP_C 15

ML_VGA_AUXN_C 15

LVDS

CRT

HDMI

HDT Debug conn

Compal Secret Data

AUX 2~5 are for GFX interface

use, they could be selected to I2C

or AUX logic

VDDIO level

Need Level shift

VDDIO level

Need Level shift

VDDIO level

Need Level shift

APU_TRST#

R598 0_0402_5%

R601 10K_0402_5%

R603 10K_0402_5%

R605 10K_0402_5%

Deciphered Date

D

To LVDS

Translator

To FCH

Asserted as an input to force the

processor into the HTC-active state

APU_PROCHOT#

THERMTRIP shutdown

temperature: 125 degree

APU_THERMTRIP#

+1.5V

1 2

1 2

1 2

1 2

D

MISC

1 2

+1.5V

R610

1K_0402_5%

1 2

MMBT3904_NL_SOT23-3

JHDT1

1

1

3

3

5

5

7

7

9

9

11

11

13

13

15

15

17

17

19

19

SAMTE_ASP-136446-07-B

CONN@

Custom

Date: Sheet

E

If not used, pins are left unconnected (DG ref.)

20101111

DP0_AUXP

DP0_AUXN

ML_VGA_AUXP

ML_VGA_AUXN

TEST25_L

TEST25_H

TEST35

TEST35 PD 300ohm (DG ref. )

20101111

M_TEST

FS1R1

FS1R1 : Control S5 Dual PWR plane

In laptop, seems no use

ALLOW_STOP

APU_RST#

APU_PWRGD

R586

1K_0402_5%

1 2

R591 0_0402_5%

Indicates to the FCH that a thermal trip

12

has occurred. Its assertion will cause th e FCH to

transition the system to S5 immediately

R609

10K_0402_5%

B

2

Q12

E

3 1

C

R611 0_0402_5%

APU_TCK

2

2

APU_TMS

4

4

APU_TDI

6

6

APU_TDO

8

8

10

10

12

12

APU_DBRDY

14

14

APU_DBREQ#

16

16

R606 0_0402_5%

18

18

R608 0_0402_5%

20

20

Title

AMD FS1 Display / MISC / HDT

Size Document Number Rev

QBL70 LA-7553P

R554 1.8K_0402_5%

R555 1.8K_0402_5%

R1809 1.8K_0402_5%

R556 1.8K_0402_5%

R548 510_0402_1%

R557 510_0402_1%

R558 300_0402_5%

R559 300_0402_5%

R564 39.2_0402_1%@

R567 39.2_0402_1%

R571 10K_0402_5%

R1812 1K_0402_5%

R577 1K_0402_5%

R578 300_0402_5%

R580 300_0402_5%

+3VS+1.5V

12

R587

10K_0402_5%

2

B

Q11

E

31

C

MMBT3904_NL_SOT23-3

1 2

1 2

1 2

1 2

1 2

@

1 2

1 2

1 2

1 2

1 2

@

1 2

1 2

12

R588

10K_0402_5%

12

12

12

12

EC_THERM# 13,32,47

H_THERMTRIP# 14

Cut on CPU side, Debug mount

R599 0_0402_5%@

1 2

R602 0_0402_5%@

1 2

1 2

1 2

APU_TEST19

APU_TEST18

Compal Electronics, Inc.

851Friday, April 29, 2011

E

+1.2VS

+1.5V

+1.5V

+3VALW

+1.5V

+1.5VS

APU_PWRGD

APU_RST#

of

0.22

Page 9

A

Power Name

VDD

+CPU_CORE

VDDNB

+CPU_CORE_N B

VDDIO

+1.5V

VDDP / VDDR

+1.2VS

VDDA

1 1

+2.5VS

CORE_NB

330uF X 2

22uF X 4

2 2

3 3

+2.5VS

Del C1039

201012061900

4 4

http://hobi-elektronika.net

Consumption

50A

22.5A

4A

3A / 3.5A

0.75A

CPU_CORE

330uF X 4

22uF X 11

+CPU_CORE_NB

L1

FBMA-L11-201209-221LMA30T_0805

12

C1041

0.22U_0603_16V4Z

C1040

3300P_0402_50V7K

1

12

2

A

+CPU_CORE

+1.5V

+1.2VS

+1.2VS

40mil

VDDA

C1043

C18

180P_0402_50V8J

4.7U_0805_10V4Z

1

1

@

2

2

JCPU1E

C1

VDD

D3

VDD

D6

VDD

E1

VDD

F3

VDD

F6

VDD

F8

VDD

G1

VDD

H3

VDD

H6

VDD

H8

VDD

J1

VDD

K3

VDD

K6

VDD

L1

VDD

L11

VDD

L19

VDD

M3

VDD

M6

VDD

M10

VDD

M18

VDD

N1

VDD

N11

VDD

N19

VDD

P3

VDD

P6

VDD

P10

VDD

P18

VDD

R1

VDD

R11

VDD

R19

VDD

T3

VDD

J9

VDDNB

J10

VDDNB

J11

VDDNB

J12

VDDNB

J14

VDDNB

J16

VDDNB

K9

VDDNB

K10

VDDNB

G28

VDDIO

H26

VDDIO

J28

VDDIO

K20

VDDIO

K23

VDDIO

K26

VDDIO

L22

VDDIO

L25

VDDIO

L28

VDDIO

M20

VDDIO

M23

VDDIO

M26

VDDIO

N22

VDDIO

N25

VDDIO

N28

VDDIO

P20

VDDIO

P23

VDDIO

P26

VDDIO

AG2

VDDP_A_1

AG3

VDDP_A_2

AG4

VDDP_A_3

AG5

VDDP_A_4

AG6

VDDR

AG7

VDDR

AG8

VDDR

AG9

VDDR

AE11

VDDA

AF11

VDDA

AMD_TOPEDO_FS-1

Keep trace from resistor to APU

within 0.6"

Keep trace from Caps to APU

within 1.2"

CONN@

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDP_B_1

VDDP_B_2

VDDP_B_3

VDDP_B_4

VDDR

VDDR

VDDR

VDDR

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

2000mil2000mil

T6

T10

T18

U1

U11

U19

V3

V6

V10

V18

W1

W11

W13

W15

W17

W19

Y3

Y6

Y10

Y12

Y14

Y16

Y18

Y20

AA1

AB3

AB6

AC1

AD3

AD6

AE1

K11

K12

K13

K14

K16

K17

K18

L18

R22

R25

R28

T20

T23

T26

U22

U25

U28

V20

V23

V26

W22

W25

W28

Y24

Y26

AA28

A3

A4

B3

B4

A5

A6

B5

B6

B

+CPU_CORE

900mil900mil

160mil160mil

120mil120mil

160mil160mil

B

+CPU_CORE_NB

+1.5V

VDDP decoupling

10U_0603_6.3V6M

C8

C7

1

1

2

2

VDDR decoupling

180P_0402_50V8J

C1044

C1045

1

1

2

2

C1052

0.22U_0603_16V4Z

C1053

1

1

2

2

C

CPU BOTTOM SIDE DECOUPLING

+CPU_CORE

C982

1

2

+CPU_CORE_NB

C1000

1

2

+1.5V

C1012

1

2

+1.5V

C1027

1

2

10U_0603_6.3V6M

10U_0603_6.3V6M

C6

1

2

180P_0402_50V8J

180P_0402_50V8J

C1046

1

2

0.22U_0603_16V4Z

C1054

0.22U_0603_16V4Z

1

2

22U_0805_6.3V6M

C983

C996

22U_0805_6.3V6M

1

1

2

2

C1001

22U_0805_6.3V6M

22U_0805_6.3V6M

C1002

1

1

2

2

22U_0805_6.3V6M

C1013

22U_0805_6.3V6M

C14

1

1

2

2

0.22U_0603_16V4Z

C1029

C1028

0.22U_0603_16V4Z

1

1

2

2

180P_0402_50V8J

180P_0402_50V8J

C1035

C1034

1

1

2

2

1000P_0402_50V7K

180P_0402_50V8J

C1048

C1047

1

1

2

2

4.7U_0603_6.3V6K

C1055

0.22U_0603_16V4Z

C10

1

1

2

2

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C997

22U_0805_6.3V6M

22U_0805_6.3V6M

4.7U_0603_6.3V6K

180P_0402_50V8J

C1036

1

2

C1049

1

2

C11

1

2

Issued Date

22U_0805_6.3V6M

C984

22U_0805_6.3V6M

1

1

2

2

C1004

C1003

22U_0805_6.3V6M

1

1

2

2

4.7U_0603_6.3V6K

C15

C16

1

1

2

2

C1030

180P_0402_50V8J

1

2

Decoupling between CPU and DIMMs

across VDDIO and VSS split

+1.2VS

0.22U_0603_16V4Z

0.22U_0603_16V4Z

C1037

1

2

1000P_0402_50V7K

1000P_0402_50V7K

C1050

1

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

C12

1

2

0.22U_0603_16V4Z

4.7U_0603_6.3V6K

C1051

C13

C985

22U_0805_6.3V6M

1

2

C1005

0.22U_0603_16V4Z

1

2

4.7U_0603_6.3V6K

C17

1

2

+1.2VS

1

+

2

1000P_0402_50V7K

+1.2VS

1

2

4.7U_0603_6.3V6K

2

1

C986

1

2

C1006

1

2

C1018

1

2

C1038

220U_6.3V_M

C1038 change to SF000002Y00

20101228

2010/08/04 2010/08/04

C

22U_0805_6.3V6M

C987

0.22U_0603_16V4Z

1

2

C1007

180P_0402_50V8J

180P_0402_50V8J

1

2

C1019

0.22U_0603_16V4Z

0.22U_0603_16V4Z

1

2

C988

0.22U_0603_16V4Z

C989

0.01U_0402_16V7K

1

1

2

2

C1008

180P_0402_50V8J

C1010

C1009

390U_2.5V_10M

1

1

+

2

2

C1021

0.22U_0603_16V4Z

C1020

0.22U_0603_16V4Z

1

1

2

2

Compal Secret Data

Deciphered Date

D

C998

0.01U_0402_16V7K

C991

180P_0402_50V8J

C990

0.01U_0402_16V7K

1

2

390U_2.5V_10M

1

+

2

C1022

0.22U_0603_16V4Z

1

2

Demo Board Capacitor (include PWM side)

CPU_CORE

470uF x 6

22uF x 9

0.22uF x 2

180pF x 2

10nF x 3

C1011

C1023

1

1

2

2

390U_2.5V_10M

1

+

2

0.22U_0603_16V4Z

C1024

180P_0402_50V8J

1

1

2

2

CORE_NB

470uF x 4

22uF x 6

0.22uF x 2

180uF x 3

C992

1

2

+CPU_CORE

C1025

1

2

D

C993

180P_0402_50V8J

1

+

2

C1014

180P_0402_50V8J

C5

C994

390U_2.5V_10M

390U_2.5V_10M

1

+

2

C1015

390U_2.5V_10M

1

1

+

2

2

330U_D2_2V_Y

1

+

2

VDDIO_SUS

(CPU side)

680uF x 1

330uF x 1

22uF x 3

4.7uF x 4

0.22uF x 6

180pF x 4

C999

390U_2.5V_10M

C995

330U_D2_2V_Y

1

1

+

+

@

2

2

390U_2.5V_10M

+

VDDIO_SUS

(DIMM x2)

100uF x 4

0.1uF

Title

Size Document Number Rev

Custom

Date: Sheet

JCPU1F

A7

VSS

A13

VSS

A15

VSS

A17

VSS

A19

VSS

A21

VSS

A23

VSS

A25

VSS

B7

VSS

C4

VSS

C10

VSS

C14

VSS

C16

VSS

C18

VSS

C20

VSS

C22

VSS

C24

VSS

C26

VSS

C28

VSS

D13

VSS

D15

VSS

D17

VSS

D19

VSS

D21

VSS

D23

VSS

D25

VSS

D27

VSS

E4

VSS

E10

VSS

E12

VSS

F9

VSS

F11

VSS

F14

VSS

F16

VSS

F18

VSS

F20

VSS

F22

VSS

F24

VSS

F26

VSS

F28

VSS

G4

VSS

G8

VSS

G13

VSS

G15

VSS

G17

VSS

G19

VSS

G21

VSS

G23

VSS

G25

VSS

J4

VSS

J8

VSS

J18

VSS

J20

VSS

J22

VSS

J24

VSS

K19

VSS

L4

VSS

L7

VSS

L10

VSS

M9

VSS

M11

VSS

M19

VSS

N4

VSS

N7

VSS

N10

VSS

N18

VSS

P9

VSS

P11

VSS

P19

VSS

R4

VSS

R7

VSS

R10

VSS

R18

VSS

T9

VSS

AMD_TOPEDO_FS-1

VDDP/R_PWM

470uF x 2

10uF x 1

VDDP

10uF x 3

0.22uF x 2

180pF x 2

Compal Electronics, Inc.

AMD FS1 PWR / GND

QBL70 LA-7553P

E

CONN@

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E

T11

T19

U4

U7

U10

U18

V9

V11

V19

W4

W7

W10

W12

W14

W16

W18

Y9

Y22

AA4

AA7

AB9

AB13

AB15

AB17

AB19

AB21

AB23

AB25

AB27

AC4

AC7

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AC24

AC26

AC28

AD9

AD11

AE4

AE7

AE13

AE15

AE17

AE19

AE21

AE23

AE25

AE27

AF3

AF6

AF9

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AH5

AH8

AH13

AH15

AH17

AH19

AH21

AH23

AH25

VDDR

4.7uF x 4

0.22uF x 4

1nF x 4

180pF x 4

951Friday, April 29, 2011

of

0.22

Page 10

5

4

3

2

1

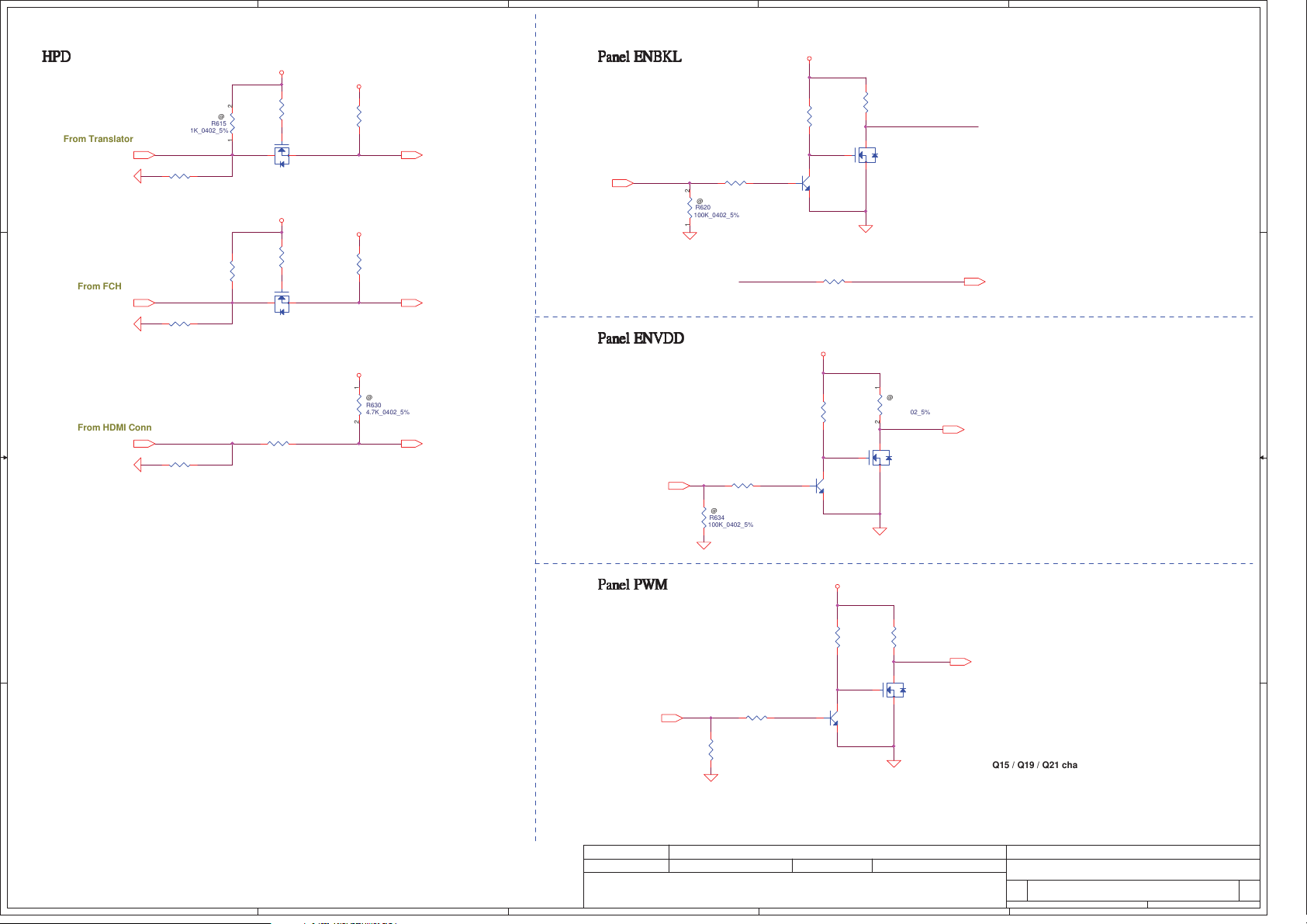

ʼnőŅ

ʼnőŅ őŢůŦŭġņŏŃŌō

ʼnőŅʼnőŅ

@

@

@

R615

1K_0402_5%

12

R622

1K_0402_5%

12

12

@

@

D D

Translator HPD

From Translator

LVDS_HPD26 DP0_HPD 8

LVDS_HPD

R618 100K_0402_5%

CRT HPD

From FCH

FCH_CRT_HPD15 DP1_HPD 8

C C

FCH_CRT_HPD

R627 100K_0402_5%

HDMI HPD

From HDMI Conn

APU_HDMI_HPD28 DP5_HPD 8

APU_HDMI_HPD

R659 100K_0402_5%

+3VS

12

R613

10K_0402_5%

2

1 3

D

Q13

2N7002_SOT23

+3VS

12

2

1 3

D

Q16

2N7002_SOT23

1 2

G

S

R621

10K_0402_5%

G

S

1 2

1 2

R677 0_0402_5%

R616

1K_0402_5%

+1.5VS

1 2

+1.5VS

12

1K_0402_5%

R623

+1.5VS

12

@

R630

4.7K_0402_5%

őŢůŦŭġņŏŃŌō

őŢůŦŭġņŏŃŌōőŢůŦŭġņŏŃŌō

DP_ENBKL8

őŢůŦŭġņŏŗŅŅ

őŢůŦŭġņŏŗŅŅ

őŢůŦŭġņŏŗŅŅőŢůŦŭġņŏŗŅŅ

DP_ENBKL

DP_ENVDD8

@

1 2

R619 2.2K_0402_5%

@

R620

100K_0402_5%

1 2

1 2

R633 2.2K_0402_5%

@

R634

100K_0402_5%

1 2

DP_ENBKL ENBKL

@

+3VS

@

R617

100K_0402_5%

1 2

2

C

E

3 1

2

B

MMBT3904_NL_SOT23-3

1 2

+3VS

@

R1810

100K_0402_5%

1 2

C

E

3 1

MMBT3904_NL_SOT23-3

G

@

Q15

2

B

R624 0_0402_5%

@

Q19

12

@

R614

4.7K_0402_5%

13

D

S

2

G

@

Q14

2N7002_SOT23

12

@

R632

4.7K_0402_5%

13

D

Q18

@

2N7002_SOT23

S

ENBKL

ENBKL 32

APU_ENVDD 27

B B

A A

http://hobi-elektronika.net

5

4

őŢůŦŭġőŘŎ

őŢůŦŭġőŘŎ

őŢůŦŭġőŘŎőŢůŦŭġőŘŎ

DP_INT_PWM8

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

1 2

R637 2.2K_0402_5%

12

R638

4.7K_0402_5%

2010/08/04 2010/08/04

Compal Secret Data

+3VS

12

R635

47K_0402_5%

C

Q21

2

B

E

3 1

Deciphered Date

12

R636

4.7K_0402_5%

13

D

2

G

Q20

2N7002_SOT23

S

MMBT3904_NL_SOT23-3

2

APU_INVT_PWM 26,27

Q15 / Q19 / Q21 change to SB000006A00

20101228

Title

AMD FS1 Singal Level Shifter

Size Document Number Rev

Custom

QBL70 LA-7553P

Date: Sheet

1

10 51Friday, April 29, 2011

0.22

of

Page 11

A

+1.5V +1.5V+VREF_DQ

JDIMM2

15mil

VREF_DQ1VSS1

3

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDM0

DDRA_SDQ2

1 1

DDRA_SDQS1#7

DDRA_SDQS17

DDRA_SDQS2#7

DDRA_SDQS27

DDRA_CKE07

2 2

3 3

4 4

C1080

2.2U_0603_6.3V4Z

DDRA_SBS2#7

DDRA_CLK07

DDRA_CLK0#7

DDRA_SBS0#7

DDRA_SWE#7

DDRA_SCAS#7 DDRA_ODT0 7

DDRA_SCS1#7

DDRA_SDQS4#7

DDRA_SDQS47

DDRA_SDQS6#7

DDRA_SDQS67

+3VS

1

1

C1081

0.1U_0402_16V4Z

2

2

DDRA_SDQ3

DDRA_SDQ8

DDRA_SDQ9

DDRA_SDQS1#

DDRA_SDQS1

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ16

DDRA_SDQ17

DDRA_SDQS2#

DDRA_SDQS2

DDRA_SDQ18

DDRA_SDQ19

DDRA_SDQ24

DDRA_SDQ25

DDRA_SDM3

DDRA_SDQ26

DDRA_SDQ27

DDRA_CKE0

DDRA_SBS2#

DDRA_SMA12

DDRA_SMA9

DDRA_SMA8

DDRA_SMA5

DDRA_SMA3

DDRA_SMA1

DDRA_CLK0

DDRA_CLK0#

DDRA_SMA10

DDRA_SBS0#

DDRA_SWE#

DDRA_SCAS# DDRA_ODT0

DDRA_SMA13

DDRA_SCS1#

DDRA_SDQ32

DDRA_SDQ33

DDRA_SDQS4#

DDRA_SDQS4

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ40

DDRA_SDQ41

DDRA_SDM5

DDRA_SDQ42

DDRA_SDQ43

DDRA_SDQ48

DDRA_SDQ49

DDRA_SDQS6#

DDRA_SDQS6

DDRA_SDQ50

DDRA_SDQ51

DDRA_SDQ56

DDRA_SDQ57

DDRA_SDM7

DDRA_SDQ58

DDRA_SDQ59

R643 10K_0402_5%

+3VS

1 2

12

R645

10K_0402_5%

VSS2

5

DQ0

7

DQ1

9

VSS4

11

DM0

13

VSS5

15

DQ2

17

DQ3

19

VSS7

21

DQ8

23

DQ9

25

VSS9

27

DQS#1

DQS129RESET#

VSS1131VSS12

33

DQ10

35

DQ11

VSS1337VSS14

39

DQ16

41

DQ17

VSS1543VSS16

45

DQS#2

47

DQS2

49

VSS18

51

DQ18

53

DQ19

55

VSS20

57

DQ24

59

DQ25

VSS2261DQS#3

63

DM3

VSS2365VSS24

67

DQ26

69

DQ27

VSS2571VSS26

73

CKE0

75

VDD1

77

NC1

79

BA2

81

VDD3

83

A12/BC#

85

A9

87

VDD5

89

A8

91

A5

93

VDD7

95

A3

97

A1

99

VDD9

101

CK0

103

CK0#

105

VDD11

107

A10/AP

109

BA0

111

VDD13

113

WE#

115

CAS#

117

VDD15

119

A13

121

S1#

123

VDD17

125

NCTEST

127

VSS27

129

DQ32

131

DQ33

133

VSS29

135

DQS#4

137

DQS4

139

VSS32

141

DQ34

143

DQ35

145

VSS34

147

DQ40

149

DQ41

151

VSS36

153

DM5

155

VSS37

157

DQ42

159

DQ43

161

VSS39

163

DQ48

165

DQ49

167

VSS41

169

DQS#6

171

DQS6

173

VSS44

175

DQ50

177

DQ51

179

VSS46

181

DQ56

183

DQ57

185

VSS48

187

DM7

189

VSS49

191

DQ58

193

DQ59

195

VSS51

197

SA0

199

VDDSPD

201

SA1

203

VTT1

205

G1

TYCO_2-2013310-1

CONN@

VSS3

DQS#0

DQS0

VSS6

VSS8

DQ12

DQ13

VSS10

DQ14

DQ15

DQ20

DQ21

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS3

DQ30

DQ31

CKE1

VDD2

VDD4

VDD6

VDD8

VDD10

CK1#

VDD12

RAS#

VDD14

ODT0

VDD16

ODT1

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

VTT2

DQ4

DQ5

DQ6

DQ7

DM1

DM2

A15

A14

A11

CK1

BA1

S0#

NC2

DM4

DM6

SDA

SCL

B

2

DDRA_SDQ4

4

DDRA_SDQ5

6

8

DDRA_SDQS0#

10

DDRA_SDQS0

12

14

DDRA_SDQ6

16

DDRA_SDQ7

18

20

DDRA_SDQ12

22

DDRA_SDQ13

24

26

DDRA_SDM1

28

MEM_MA_RST#

30

32

DDRA_SDQ14

34

DDRA_SDQ15

36

38

DDRA_SDQ20

40

DDRA_SDQ21

42

44

DDRA_SDM2

46

48

DDRA_SDQ22

50

DDRA_SDQ23

52

54

DDRA_SDQ28

56

DDRA_SDQ29

58

60

DDRA_SDQS3#

62

DDRA_SDQS3

64

66

DDRA_SDQ30

68

DDRA_SDQ31

70

72

DDRA_CKE1

74

76

DDRA_SMA15

78

DDRA_SMA14

80

82

DDRA_SMA11

84

DDRA_SMA7

86

A7

88

DDRA_SMA6

90

A6

A4

A2

A0

G2

DDRA_SMA4

92

94

DDRA_SMA2

96

DDRA_SMA0

98

100

DDRA_CLK1

102

DDRA_CLK1#

104

106

DDRA_SBS1#

108

DDRA_SRAS#

110

112

DDRA_SCS0#

114

116

118

DDRA_ODT1

120

122

124

15mil

126

128

DDRA_SDQ36

130

DDRA_SDQ37

132

134

DDRA_SDM4

136

138

DDRA_SDQ38

140

DDRA_SDQ39

142

144

DDRA_SDQ44

146

DDRA_SDQ45

148

150

DDRA_SDQS5#

152

DDRA_SDQS5

154

156

DDRA_SDQ46

158

DDRA_SDQ47

160

162

DDRA_SDQ52

164

DDRA_SDQ53

166

168

DDRA_SDM6

170

172

DDRA_SDQ54

174

DDRA_SDQ55

176

178

DDRA_SDQ60

180

DDRA_SDQ61

182

184

DDRA_SDQS7#

186

DDRA_SDQS7

188

190

DDRA_SDQ62

192

DDRA_SDQ63

194

196

MEM_MA_EVENT#

198

200

202

204

206

+0.75VS

DDRA_SDQS0# 7

DDRA_SDQS0 7

MEM_MA_RST# 7

DDRA_SDQS3# 7

DDRA_SDQS3 7

DDRA_CKE1 7

DDRA_CLK1 7

DDRA_CLK1# 7

DDRA_SBS1# 7

DDRA_SRAS# 7

DDRA_SCS0# 7

DDRA_ODT1 7

1

C1066

1000P_0402_50V7K

2

DDRA_SDQS5# 7

DDRA_SDQS5 7

DDRA_SDQS7# 7

DDRA_SDQS7 7

MEM_MA_EVENT# 7

FCH_SDATA0 12,14,35

FCH_SCLK0 12,14,35

+VREF_CA

C

DDRA_SDQ[0..63]

DDRA_SDM[0..7]

DDRA_SMA[0..15]

Place near DIMM1

+1.5V

0.1U_0402_16V4Z

2

C1067

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C1077

1

0.1U_0402_16V4Z

15mil

4.7U_0603_6.3V6K

+VREF_DQ

1

1

@

C1060

2

2

0.1U_0402_16V4Z

DDRA_SDQ[0..63] 7

DDRA_SDM[0..7] 7

DDRA_SMA[0..15] 7

2

C1068

1

0.1U_0402_16V4Z

2

C1078

1

4.7U_0603_6.3V6K

1

C1061

2

1000P_0402_50V7K

2

1

C1062

0.1U_0402_16V4Z

2

C1070

C1069

1

C1106 0.1U_0402_16V4Z

1

C1079

2

+1.5V+VREF_DQ

R639

1K_0402_1%

1 2

R641

1K_0402_1%

1 2

D

2

C1071

1

0.1U_0402_16V4Z

+1.5V+0.75VS

@

1 2

Add C1106

20101101

0.1U_0402_16V4Z

2

C1072

1

4.7U_0603_6.3V6K

1

2

2

C1073

1

0.1U_0402_16V4Z

15mil

+VREF_CA

1

@

C1063

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C1074

1

1

C1064

2

1000P_0402_50V7K

2

C1075

1

0.1U_0402_16V4Z

+1.5V+VREF_CA

C1065

0.1U_0402_16V4Z

2

C1076

1

R640

1K_0402_1%

1 2

R642

1K_0402_1%

1 2

E

http://hobi-elektronika.net

A

DIMM_A STD H:9.2mm

<Address: 00>

B

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2010/08/04 2010/08/04

Compal Secret Data

Deciphered Date

Custom

D

Date: Sheet

Title

Size Document Number Rev

Compal Electronics, Inc.

DDRIII SO-DIMM 2

QBL70 LA-7553P

E

11 51Friday, April 29, 2011

of

0.22

Page 12

A

B

C

D

E

DQ4

DQ5

DQ6

DQ7

DM1

DM2

NC2

DM4

DM6

SDA

A15

A14

A11

CK1

BA1

S0#

SCL

+1.5V+1.5V

2

DDRB_SDQ4

4

DDRB_SDQ5

6

8

DDRB_SDQS0#

10

DDRB_SDQS0

12

14

DDRB_SDQ6

16

DDRB_SDQ7

18

20

DDRB_SDQ12

22

DDRB_SDQ13

24

26

DDRB_SDM1

28

MEM_MB_RST#

30

32

DDRB_SDQ14

34

DDRB_SDQ15

36

38

DDRB_SDQ20

40

DDRB_SDQ21

42

44

DDRB_SDM2

46

48

DDRB_SDQ22

50

DDRB_SDQ23

52

54

DDRB_SDQ28

56

DDRB_SDQ29

58

60

DDRB_SDQS3#

62

DDRB_SDQS3

64

66

DDRB_SDQ30

68

DDRB_SDQ31

70

72

DDRB_CKE1

74

76

DDRB_SMA15

78

DDRB_SMA14

80

82

DDRB_SMA11

84

DDRB_SMA7

86

A7

88

DDRB_SMA6

90

A6

A4

A2

A0

G2

DDRB_SMA4

92

94

DDRB_SMA2

96

DDRB_SMA0

98

100

DDRB_CLK1

102

DDRB_CLK1#

104

106

DDRB_SBS1#

108

DDRB_SRAS#

110

112

DDRB_SCS0#

114

DDRB_ODT0DDRB_SCAS#

116

118

DDRB_ODT1

120

122

124

15mil

126

128

DDRB_SDQ36

130

DDRB_SDQ37

132

134

DDRB_SDM4

136

138

DDRB_SDQ38

140

DDRB_SDQ39

142

144

DDRB_SDQ44

146

DDRB_SDQ45

148

150

DDRB_SDQS5#

152

DDRB_SDQS5

154

156

DDRB_SDQ46

158

DDRB_SDQ47

160

162

DDRB_SDQ52

164

DDRB_SDQ53

166

168

DDRB_SDM6

170

172

DDRB_SDQ54

174

DDRB_SDQ55

176

178

DDRB_SDQ60

180

DDRB_SDQ61

182

184

DDRB_SDQS7#

186

DDRB_SDQS7

188

190

DDRB_SDQ62

192

DDRB_SDQ63

194

196

MEM_MB_EVENT#

198

200

202

204

206

+0.75VS

DDRB_SDQS0# 7

DDRB_SDQS0 7

MEM_MB_RST# 7

DDRB_SDQS3# 7

DDRB_SDQS3 7

DDRB_CKE1 7

DDRB_CLK1 7

DDRB_CLK1# 7

DDRB_SBS1# 7

DDRB_SRAS# 7

DDRB_SCS0# 7

DDRB_ODT0 7

DDRB_ODT1 7

1

C1088

1000P_0402_50V7K

2

DDRB_SDQS5# 7

DDRB_SDQS5 7

DDRB_SDQS7# 7

DDRB_SDQS7 7

MEM_MB_EVENT# 7

FCH_SDATA0 11,14,35

FCH_SCLK0 11,14,35

+VREF_CA

DDRB_SDQ[0..63]

DDRB_SDM[0..7]

DDRB_SMA[0..15]

DDRB_SDQ[0..63] 7

DDRB_SDM[0..7] 7

DDRB_SMA[0..15] 7

Place near DIMM2

+1.5V

0.1U_0402_16V4Z

2

2

C1089

1

0.1U_0402_16V4Z

+0.75VS

0.1U_0402_16V4Z

+VREF_DQ +VREF_CA

15mil 15mil

4.7U_0603_6.3V6K

1

@

C1082

2

C1090

1

0.1U_0402_16V4Z

2

2

C1099

1

1

+VREF_DQ +VREF_CA

0.1U_0402_16V4Z

1

C1083

2

1000P_0402_50V7K

2

C1091

1

0.1U_0402_16V4Z

1

C1101

C1100

2

4.7U_0603_6.3V6K

1

C1084

2

0.1U_0402_16V4Z

2

1