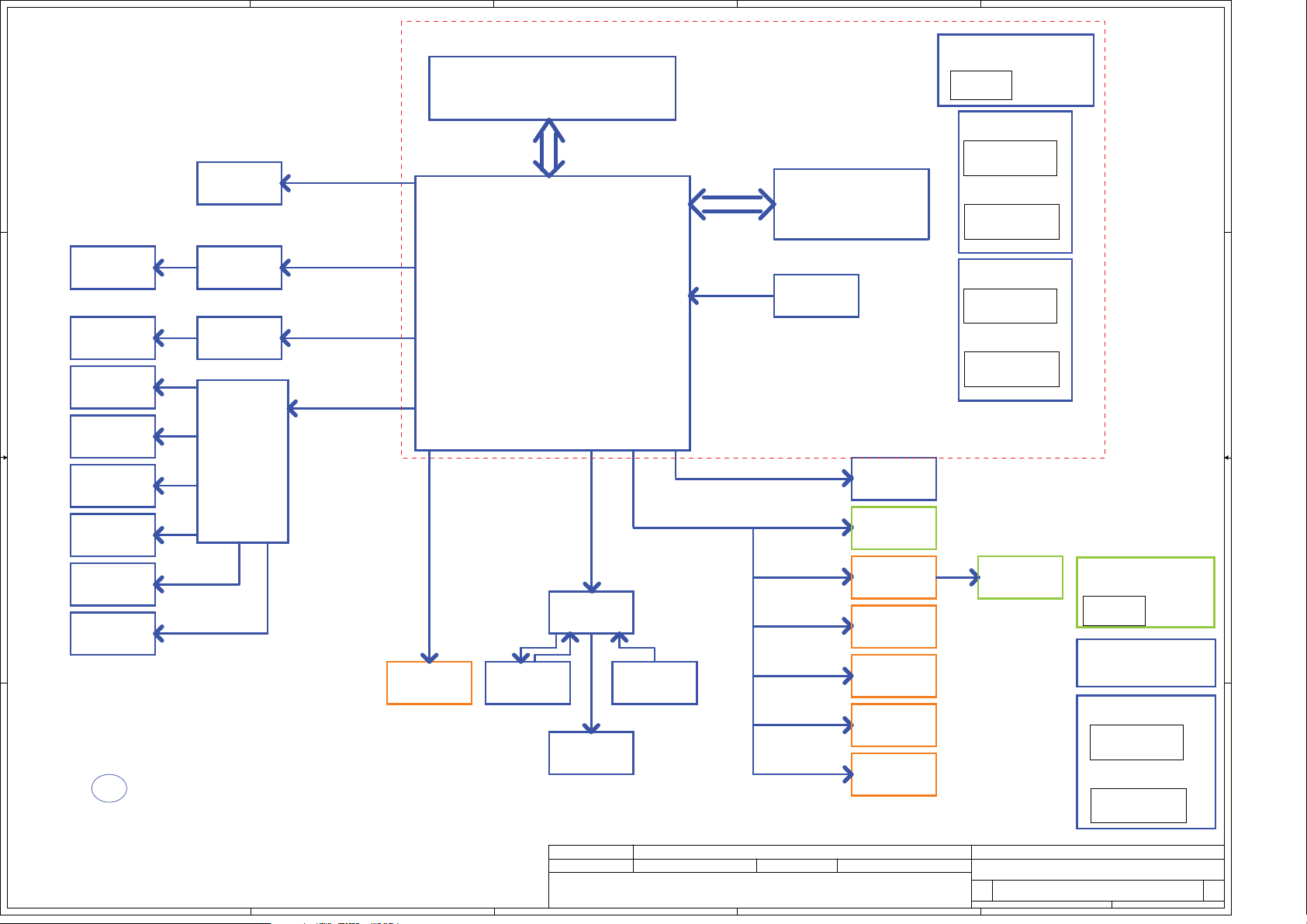

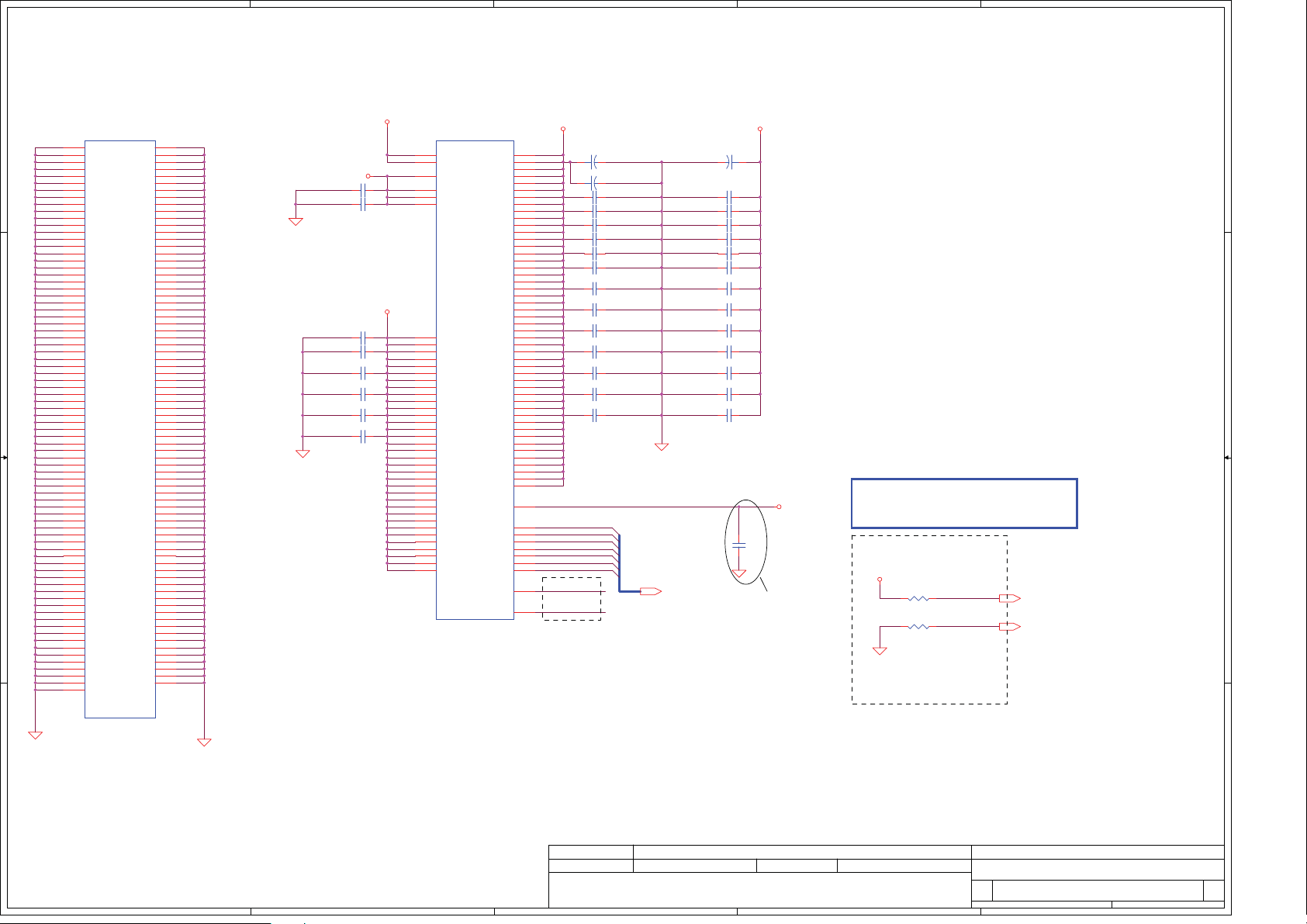

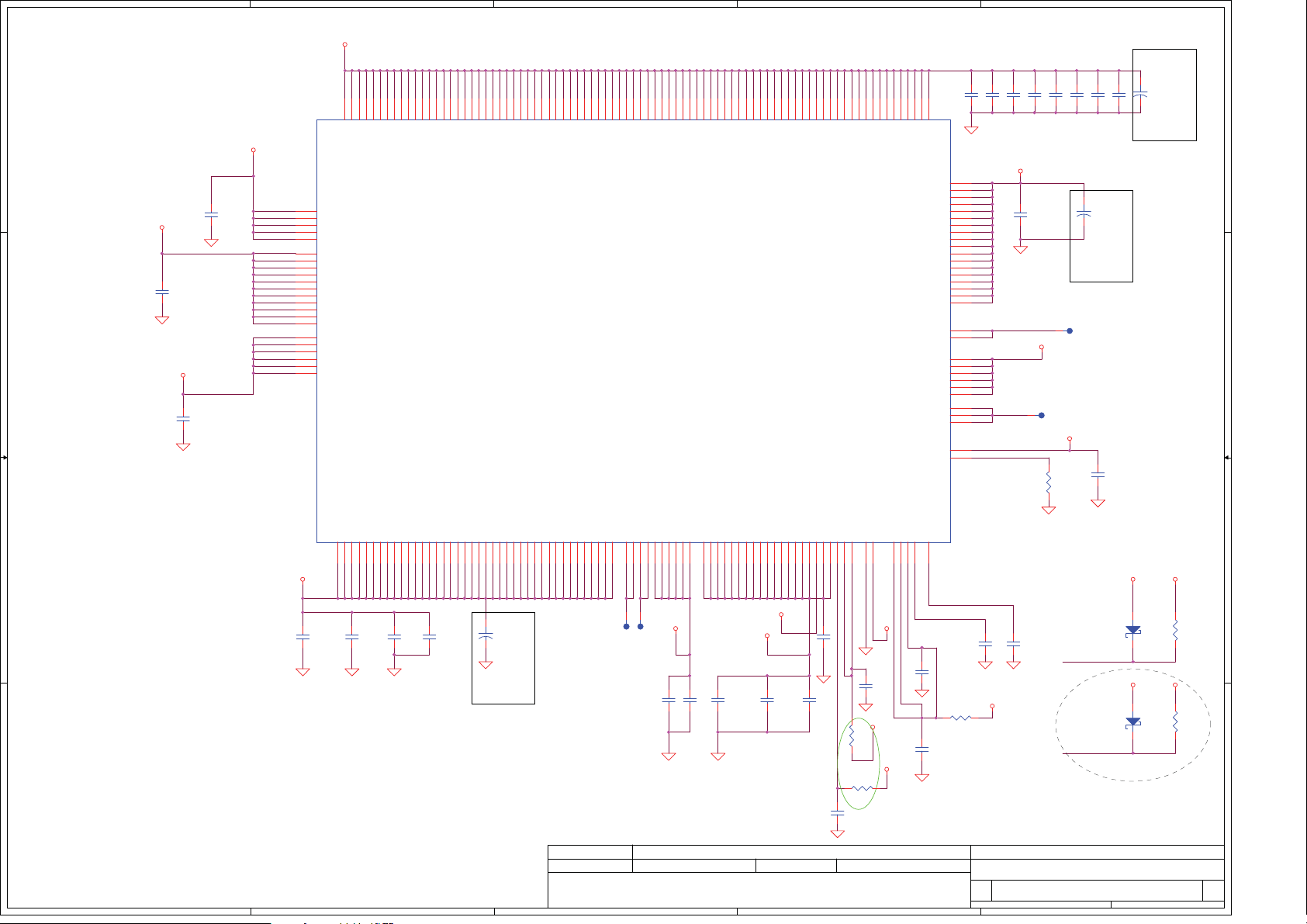

Acer LA-5301P Schematics

A

1 1

B

C

D

E

Compal Confidential

2 2

NYU00 LA-5301P R02

Schematics Document

Menlow-Silverthorne with Poulsbo

3 3

Monday, April 06, 2009

4 4

http://hobi-elektronika.net

A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDEN TIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMA TION IT C ONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPA L ELEC TRONICS, INC.

C

2008/05/30 2011/05/30

Compal Secret Data

Deciphered Date

Title

Size Docu ment Number Re v

Custom

D

Date: Sheet

Compal Electronics, Inc.

Cover Sheet

NYU00 LA-5301P

E

128

0.2

of

A

Compal Confidential

Model Name :

B

C

D

E

CPU Regulator

LA-5301P

CPU-Board

1 1

10.1" LCD

Connector

Page 15

HDMI

Connector

SATA

Conn.

2 2

40,60,80G1.8"

Page 19

HDD

BIOS

SST25LF080A

Page 20

TouchPad

Conn.

Page 19

KeyBoard

Conn.

Page 18

TMDS

SATA

SPI

Flash

PS/2

Matrix

SDVO->HDMI

SiI1392

Page 17

PATA->SATA

GL831

EC

ENE KB926

Page 18

LED

3 3

G-Sensor

SMBUS

MMA7455

Light Sensor

SMBUS

TSL2561FN

LVDS I/F

SDVO I/F

PATA

LPC BUS

PCIE

WLAN

Arcadyan

Atheros XB63

CPU-Silverthrone

1.33G/1.6G

H_A#( 3..35)

H_D#(0..63)

FSB

533MHz

SCH- Poulsbo

Page 6~10

HDA I/F

Audio Codec

ALC 269

Page 16

HP/MIC Jack

Page 4,5

USB2.0

DMIC-IN

DDR2-533

SingleChannel

DDR2 64MX16X8pcs

HY5PS1G1631CFP-S6

Page 11,12

Clock Gen.

9UMS9610

Page 13

SDIO

USB2.0

SD Card Socket

Ext.USB 2.0

X3

USB2.0

USB2.0

USB2.0

USB2.0

3G-Module

BlueTooth

Camera(1.3M)

Lite-On

(Reserve)

Page 15

Page 22

Page 22

+1.8V

+1.05VS

+0.9VS

+1.5VS

SIM

Connector

DCIN/CHARGER

BATT Conn/OTP

+3VALW

Speaker X2

ZZZ

LA-5301P

4 4

PCB

DA80000EN00

USB2.0

NFC

PN533

(Reserve)

+5VALW

http://hobi-elektronika.net

A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDEN TIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMA TION IT C ONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPA L ELEC TRONICS, INC.

C

2008/11/10 2011/11/10

Compal Secret Data

Deciphered Date

Title

Size Docu ment Number Re v

Custom

D

Date: Sheet

Compal Electronics, Inc.

Block Diagram

NYU00 LA-5301P

E

228Monday, Apr il 06, 2009

0.2

of

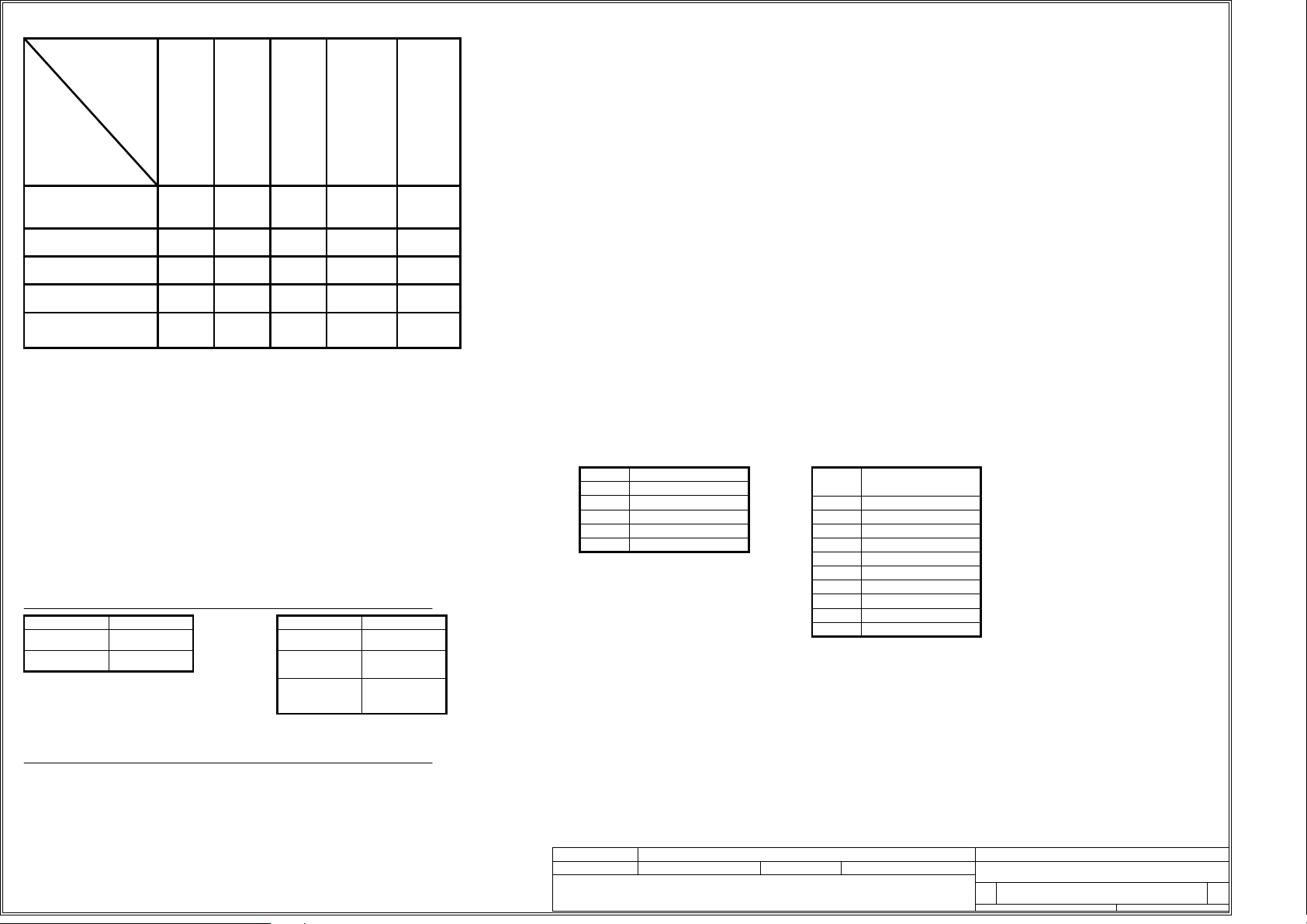

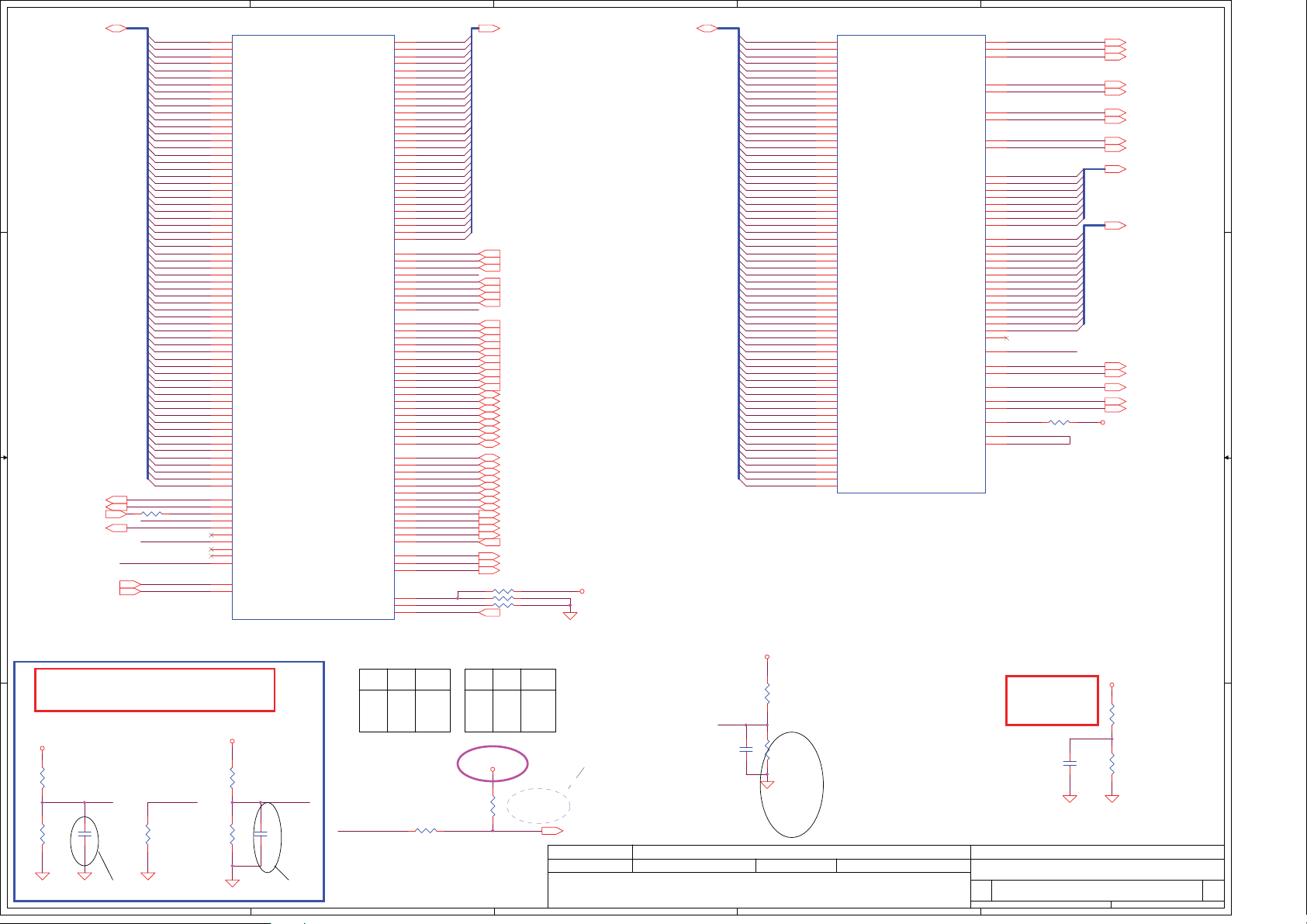

Voltage Rails

A

O MEANS ON X MEANS OFF

power

plane

State

S0

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

O MEANS ON

X MEANS OFF

+VBAT

O

O

O

O

X

S3 : STR

S4 : STD

+5VALW

+3VALW

+1.8V

+0.9V

O

O

O

X

XXX

+5VS

+3VS

+1.8VS

+1.5VS

+CPU_CORE

+VCCP

OO

O

X

XX

X

X

CLOCK

O

X

X

X

X

S5 : SOFT OFF

1 1

EC SM Bus1 address

AddressDevice

G SENSOR

MMA745 5

0001_1101

EC SM Bus2 address

Device

THERMAL SENSOR 1

EMC1402-1-ACZL-TR

THERMAL SENSOR 2

EMC1402-2-ACZL-TR

LIGHT SENSOR

TSL2561FN

Address

100_1100

100_1101

ADDRSEL

GND

0101001

BOM Structure USB PORT LIST

MARK FUNCTION

Address

NC FOR ALL@

PORT DEVICE

HOST LEFT1

0

HOST LEFT2

1

2

HOST RIGHT1

3

3G

4

BT

CAM

5

(RESERVE)

6

(RESERVE)

7

Poulsbo SM Bus address

Device

Clock Generator

(ICS9UMS9610BKLF-T)

1101 001Xb

Address

http://hobi-elektronika.net

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDEN TIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMA TION IT C ONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPA L ELEC TRONICS, INC.

A

2008/05/30 2011/05/30

Compal Secret Data

Deciphered Date

Title

Size Docu ment Number Re v

Custom

Date: Sheet

Compal Electronics, Inc.

Notes List

NYU00 LA-5301P

of

328Monday, April 06, 2009

0.2

5

4

3

2

1

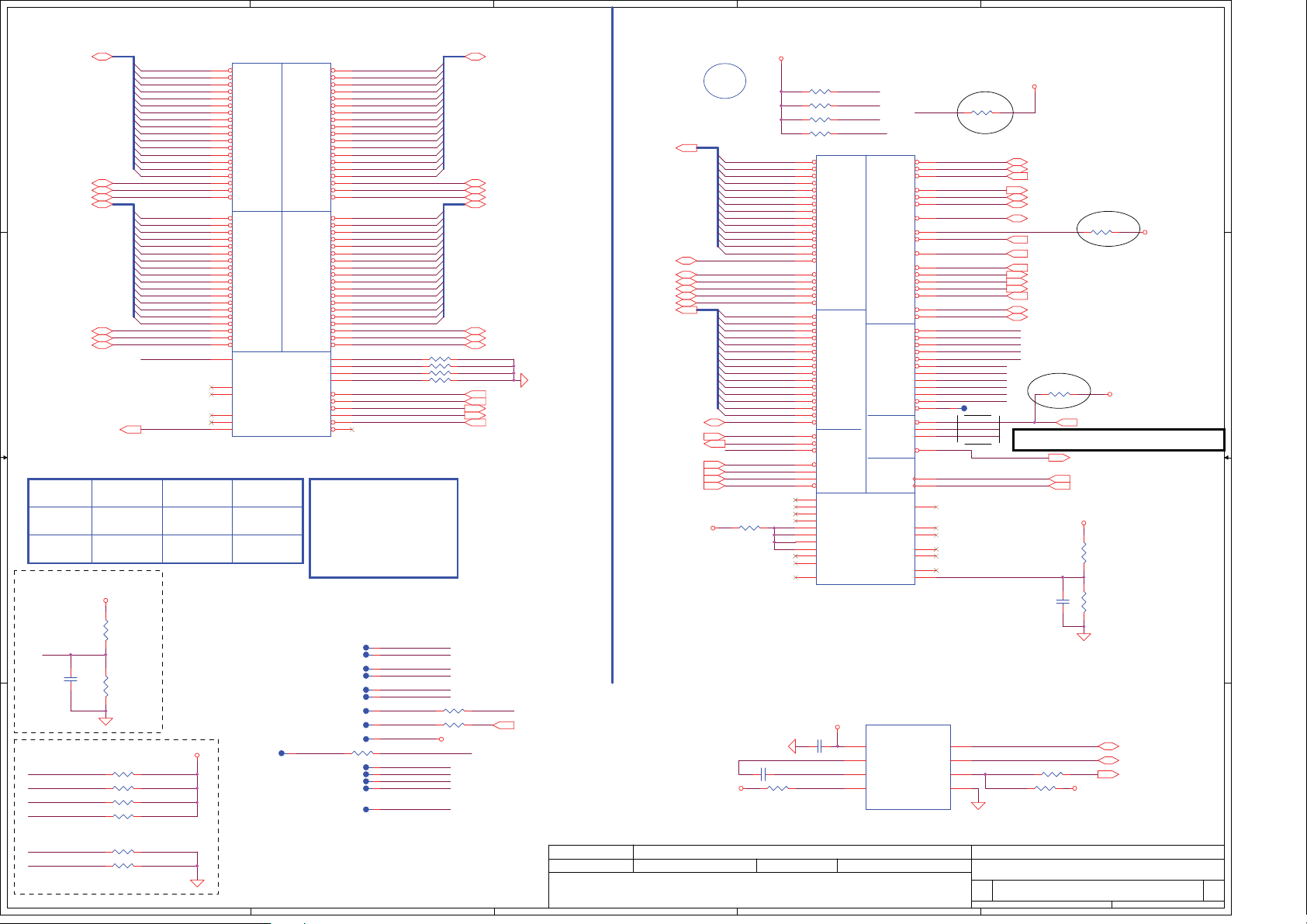

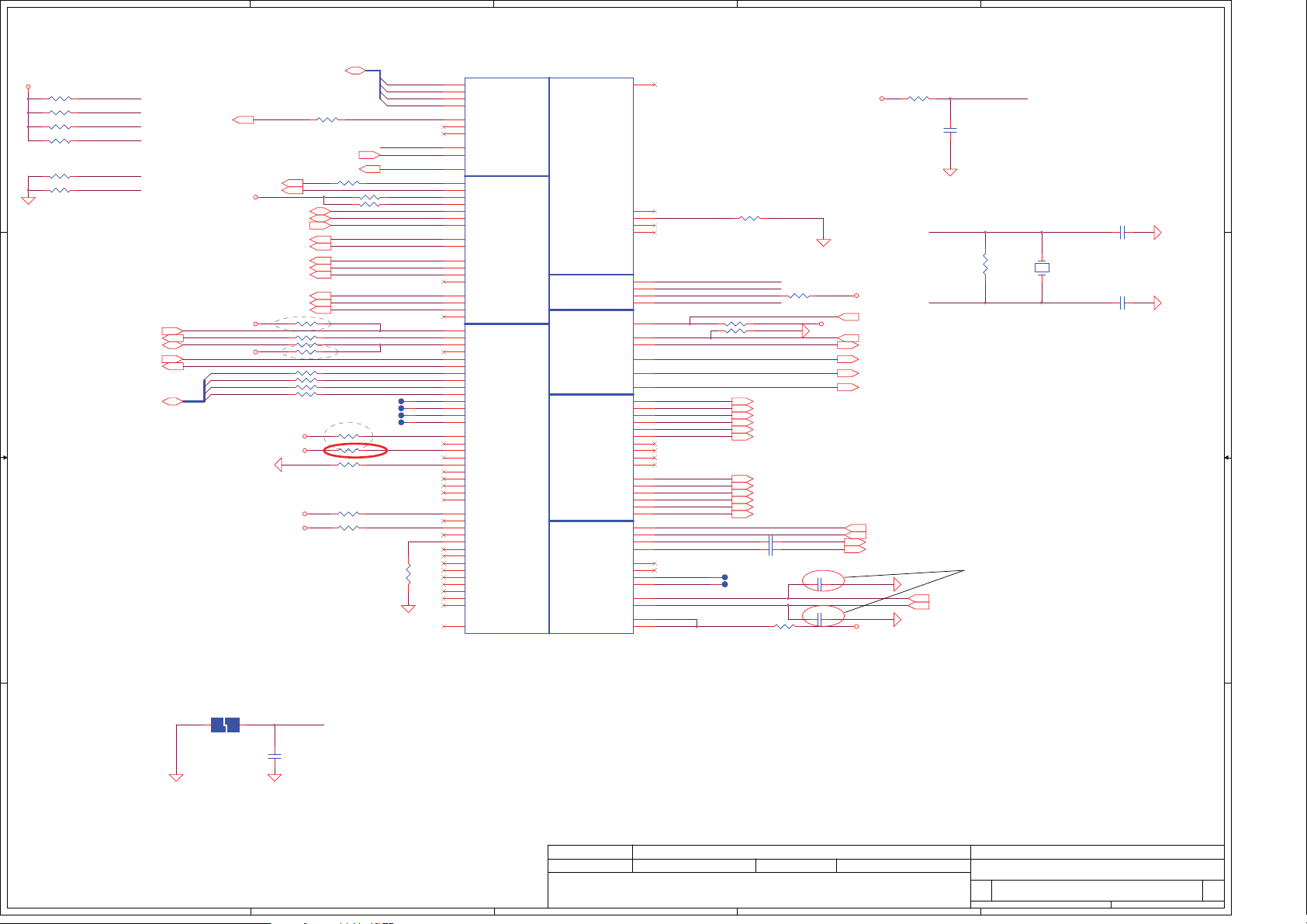

Silverthrone Host Data Interface Silverthrone Host Data Interface

H_D#[0..1 5]<6>

D D

H_DSTBN#0<6>

H_DSTBP#0<6>

H_DINV#0<6>

H_D#[16..31]<6>

H_DSTBN#1<6>

H_DSTBP#1<6>

C C

H_DINV#1<6>

CPU_BSEL2<6,13>

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DSTBN#0

H_DSTBP#0

H_DINV#0

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DSTBN#1

H_DSTBP#1

H_DINV#1

+CPU_GTLREF

CPU_BSEL2

U2B

Y27

D[0]#

AH27

D[1]#

Y31

D[2]#

AC30

D[3]#

AE30

D[4]#

AF29

D[5]#

AA26

D[6]#

AB31

D[7]#

W30

D[8]#

AC28

D[9]#

AD31

D[10]#

AF27

D[11]#

AD27

D[12]#

AG28

D[13]#

AB25

D[14]#

AC26

D[15]#

AA28

DSTBN[0]#

AA30

DSTBP[0]#

AE28

DINV[0]#

AE24

D[16]#

AC24

D[17]#

AJ20

D[18]#

AE20

D[19]#

AJ22

D[20]#

AF25

D[21]#

AH25

D[22]#

AH23

D[23]#

AH19

D[24]#

AF23

D[25]#

AE18

D[26]#

AH17

D[27]#

AD19

D[28]#

AJ24

D[29]#

AJ18

D[30]#

AF19

D[31]#

AF21

DSTBN[1]#

AH21

DSTBP[1]#

AE22

DINV[1]#

AJ26

GTLREF

MISC

P31

TEST1

T31

TEST2

R30

BSEL[0]

M31

BSEL[1]

U28

BSEL[2]

SILVERTHORNE_FCBGA8-441

DATA GRP 0 DATA GRP 1

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

DATA GRP 2

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

DATA GRP 3

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

RSVD12

AE8

AD7

AH15

AF9

AH9

AE10

AJ16

AF13

AF7

AF15

AH13

AJ14

AJ12

AH7

AJ8

AJ10

AH11

AF11

AE12

AH5

AB5

AJ6

Y1

AF5

AG4

AF3

AC6

AE6

AE4

W4

AC2

AE2

AD1

AA2

AC4

AB1

AA4

Y5

AE14

AD13

E16

F15

G2

G6

V31

G4

J2

K27

<NO_STUFF>

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DSTBN#2

H_DSTBP#2

H_DINV#2

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#3

H_DSTBP#3

H_DINV#3

COMP0

R11 27.4_0402_1%

COMP1

R15 54.9_0402_1%

COMP2

R13 27.4_0402_1%

COMP3

R14 54.9_0402_1%

H_DPRSTP#

H_DPSLP#

H_DPWR#

H_PW RGOOD

H_CPUSLP#

1 2

1 2

1 2

1 2

layout note: Route TEST3 & TEST5 traces on ground referenced layer to the TPs

CPU_BSEL CPU_BSEL2 CPU_BSEL1

100

133

B B

Close to CPU pin AD26

within 500mils.

+CPU_GTLREF

1

C4

0.1U_0402_16V7K

2

XDP Reserve

XDP_TDI

XDP_TMS

A A

XDP_TDO

XDP_BPM#5

10

0

+1.05VS_C6

12

R20

1K_0402_1%

12

R27

2K_0402_1%

R19 56_0402_5%

1 2

R21 56_0402_5%

1 2

R23 56_0402_5%@

1 2

R25 56_0402_5%@

1 2

0

+1.05VS

CPU_BSEL0

1

1

T34

TPC24

Resistor placed within

0.5" of CPU pin.Trace

should be at least 25

mils away from any other

toggling signal.

COMP[0,2] trace width is

18 mils. COMP[1,3] trace

width is 4 mils.

XDP_BPM#5

T25

T26

T27

T28

T29

T30

T31

T32

T33

T35

T36

T37

T38

T39

XDP_BPM#4

XDP_BPM#3

XDP_BPM#2

XDP_BPM#1

XDP_BPM#0

H_PW RGOOD_0

SLPIOVR#_0

R122

1K_0402_1%

12

XDP_TDO

XDP_TRST#

XDP_TDI

XDP_TMS

XDP_TCK

H_RESET#H_RESET#_0

TPC24

TPC24

TPC24

TPC24

TPC24

TPC24

TPC24

TPC24

TPC24

TPC24

TPC24

TPC24

TPC24

TPC24

H_D#[32..47] <6>

H_DSTBN#2 <6>

H_DSTBP#2 <6>

H_DINV#2 <6>

H_D#[48..63] <6>

H_DSTBN#3 <6>

H_DSTBP#3 <6>

H_DINV#3 <6>

H_DPRSTP# <6,25>

H_DPSLP# <6>

H_DPWR# <6>

H_PWRGOOD <6>

H_CPUSLP# <6>

R587 1K_0402_5%

H_PW RGOOD

12

R96 1K_0402_5%

12

+1.05VS

SLPIOV R# <8,22>

U2

1.33G@

SA00002BA20

H_A#[3..16]<6>

H_ADSTB#0<6>

H_REQ#0<6>

H_REQ#1<6>

H_REQ#2<6>

H_REQ#3<6>

H_REQ#4<6>

H_A#[17..31]<6>

H_ADSTB#1<6>

H_A20M#<18>

H_PBE#<6>

H_STPCLK#<6>

H_INTR<6>

H_NMI<6>

H_SMI#<6>

+1.05VS_C6

+1.05VS_C6

H_THERMTRIP#

C1

0.1U_0402_16V7K

+1.05VS_C6

H_ADS# <6>

H_BNR# <6>

H_BPRI# <6>

H_DEFER# <6>

H_DRDY# <6>

H_DBSY# <6>

H_BR0# <6>

H_INIT # <6,18>

H_LOCK# <6>

H_RESET# <6>

H_RS#0 <6>

H_RS#1 <6>

H_RS#2 <6>

H_TRDY# <6>

H_HIT# <6>

H_HITM# <6>

R12

56_0402_5%

H_THERMDA, H_THERMDC routing together,

Trace width / Spacing = 10 / 10 mil

CLK_CPU_BCLK <13>

CLK_CPU_BCLK# <13>

+1.05VS_C6

1

2

H_ADSTB#0

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

1 2

R16

10K_0402_5%

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_ADSTB#1

H_A20M#

H_PBE#

H_IGNNE#

H_STPCLK#

H_INTR

H_NMI

H_SMI#

1 2

R1 120_0402_5%

1 2

R2 1K_0402_1%

1 2

R4 1K_0402_5%

1 2

R593 56_0402_5%

U2A

E22

A[3]#

A22

A[4]#

D21

A[5]#

E24

A[6]#

B17

A[7]#

A18

A[8]#

B23

A[9]#

A16

A[10]#

E18

A[11]#

D15

A[12]#

B19

A[13]#

A20

A[14]#

D17

A[15]#

B15

A[16]#

D19

ADSTB[0]#

B25

REQ[0]#

D23

REQ[1]#

E20

REQ[2]#

A24

REQ[3]#

B21

REQ[4]#

B5

A[17]#

A12

A[18]#

D5

A[19]#

E12

A[20]#

B9

A[21]#

A6

A[22]#

B13

A[23]#

E14

A[24]#

A10

A[25]#

B7

A[26]#

D13

A[27]#

A8

A[28]#

C4

A[29]#

A14

A[30]#

B11

A[31]#

D11

ADSTB[1]#

G30

A20M#

J28

FERR#

H27

IGNNE#

K1

STPCLK#

H31

LINT0

L28

LINT1

J26

SMI#

AE16

RSVD7

AF17

RSVD8

AD15

RSVD9

AD17

RSVD10

D9

RSVD0

D7

RSVD1

E8

RSVD2

E10

RSVD3

L30

RSVD4

J30

RSVD5

K29

RSVD13

SILVERTHORNE_FCBGA8-441

H_PBE#

H_A20M#

H_IGNNE#

XDP_BPM#5

ADDR GROUP

0

ADDR GROUP 1

NC

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

RSVD14

XDP/ITP SIGNALSH CLK

PROCHOT#

THRMDA

THRMDC

THERM

THERMTRIP#

BCLK[0]

BCLK[1]

VSS0

RSVD11

RSVD6

RSVD15

TEST4

TEST3

CMREF[1]

Intel CRB1_5

H_INIT#

1 2

R3

1K_0402_1%

H_ADS#

C26

H_BNR#

H25

H_BPRI#

G24

H_DEFER#

B27

H_DRDY#

W28

H_DBSY#

D29

H_BR0#

C28

H_IERR#

H1

H_INIT#

F31

H_LOCK#

D25

H_RESET#

M5

H_RS#0

D27

H_RS#1

E28

H_RS#2

E26

H_TRDY#

F25

H_HIT#

E30

H_HITM#

F29

XDP_BPM#0

F1

XDP_BPM#1

E2

XDP_BPM#2

F5

XDP_BPM#3

D3

XDP_BPM#4

E4

XDP_BPM#5

F7

XDP_TCK

L2

XDP_TDI

N2

TDI

XDP_TDO

M1

XDP_TMS

P1

XDP_TRST#

J4

G26

H5

T5

U4

T1

P29

R28

K31

A26

E6

G28

U30

V27

AE26

.

H_THERMDA

H_THERMDC

+CMREF

T1 TPC1 2

Thermal Sensor

+3VS

C2

0.1U_0402_16V4Z

C3

2200P_0402_50V7K

1 2

1 2

+3VS +3VS

R26 10K_0402_5%

1 2

H_THERMDC

THERM#

U3

1

VDD

2

DP

3

DN

4

THERM#

EMC1402-1-ACZL-TR_MSOP8

Address:100_1100

SMCLK

SMDATA

ALERT#

GND

EC_SMB_CK2

8

EC_SMB_DA2H_THERMDA

7

THERM_SCI#

6

5

R24 0_0402_5%@

1 2

R22

10K_0402_5%

12

R5

56_0402_5%

12

12

+1.05VS

PROCHOT# <8,25>

H_THERMTRIP# <6>

12

R17

1K_0402_1%

12

R18

1K_0402_1%

EC_THERM# <7,8,18>

Check : to sb

+1.05VS

EC_SMB_CK2 <14,18,20>

EC_SMB_DA2 <14,18,20>

XDP_TRST#

XDP_TCK

http://hobi-elektronika.net

R28 56_0402_5%

1 2

R29 56_0402_5%

1 2

5

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDEN TIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMA TION IT C ONTAINS

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPA L ELEC TRONICS, INC.

3

2008/05/30 2011/05/30

Compal Secret Data

Deciphered Date

Title

Size Docu ment Number Re v

Custom

2

Date: Sheet

Compal Electronics, Inc.

Silverthorne(1/2)-AGTL+/XDP

NYU00 LA-5301P

1

428Monday, Apr il 06, 2009

0.2

of

5

4

3

2

1

+1.05VS

12

C60.1U_0402_16V4Z

12

C70.1U_0402_16V4Z

+1.05VS_C6

12

C6620.1U_0402_16V4Z

12

C160.1U_0402_16V4Z

12

C181U_0402_6.3V6K

12

C201U_0402_6.3V6K

12

C221U_0402_6.3V6K

12

C241U_0402_6.3V6K

+1.05VS_C6

U2C

AA14

VCCP35

J16

VCCP36

M27

VCCP0

H7

VCCPC61

H9

VCCPC62

J8

VCCPC63

AA8

VCCP1

AA10

VCCP2

AA12

VCCP3

AA16

VCCP4

AA18

VCCP5

AA20

VCCP6

AA22

VCCP7

AB7

VCCP8

AB9

VCCP9

AB11

VCCP10

AB13

VCCP11

AB15

VCCP12

AB17

VCCP13

AB19

VCCP14

AB21

VCCP15

AB23

VCCP16

H11

VCCP17

H13

VCCP18

H15

VCCP19

H17

VCCP20

H19

VCCP21

H21

VCCP22

H23

VCCP23

J10

VCCP24

J12

VCCP25

J14

VCCP26

J18

VCCP27

J20

VCCP28

J22

VCCP29

L26

VCCP30

N26

VCCP31

R26

VCCP32

U26

VCCP33

W26

VCCP34

VCCSENSE

VSSSENSE

SILVER THORNE_FCBGA8-441

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

D D

U2D

A4

VSS1

A28

VSS2

AA6

VSS4

AA24

VSS5

AB3

VSS6

AB27

VSS7

AB29

VSS8

AC8

VSS9

AC10

VSS10

AC12

VSS11

AC14

VSS12

AC16

VSS13

AC18

VSS14

AC20

VSS15

AC22

VSS16

AD3

VSS17

AD5

VSS18

AD9

VSS19

AD11

VSS20

AD21

VSS21

AD23

VSS22

AD25

VSS23

AD29

VSS24

AF1

VSS25

AF31

VSS26

AG2

VSS27

AG6

VSS28

AG8

VSS29

AG10

C C

B B

AG12

AG14

AG16

AG18

AG20

AG22

AG24

AG26

AG30

AH3

AH29

AJ28

C10

C12

C14

C16

C18

C20

C22

C24

C30

D31

G10

G12

G14

G16

G18

G20

G22

H29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS41

VSS42

AJ4

VSS45

VSS46

B3

VSS48

B29

VSS49

C2

VSS51

C6

VSS52

C8

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

D1

VSS63

VSS64

F3

VSS65

F9

VSS66

F11

VSS67

F13

VSS68

F17

VSS69

F19

VSS70

F21

VSS71

F23

VSS72

F27

VSS73

G8

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

H3

VSS82

VSS83

J6

VSS84

VSS162

VSS161

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS149

VSS148

VSS147

VSS146

VSS145

VSS144

VSS143

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

VSS135

VSS134

VSS133

VSS132

VSS131

VSS130

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS122

VSS121

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

VSS104

VSS103

VSS102

VSS101

VSS100

VSS99

VSS98

VSS97

VSS96

VSS95

VSS94

VSS93

VSS92

VSS91

VSS90

VSS89

VSS88

VSS87

VSS86

VSS85

Y29

Y25

Y23

Y21

Y19

Y17

Y15

Y13

Y11

Y9

Y7

Y3

W6

V29

V25

V23

V21

V19

V17

V15

V13

V11

V9

V7

V5

V3

T29

T27

T25

T23

T21

T19

T17

T15

T13

T11

T9

T7

T3

P27

P25

P23

P21

P19

P17

P15

P13

P11

P9

P7

P3

N28

M29

M25

M23

M21

M19

M17

M15

M13

M11

M9

M7

M3

L6

K25

K23

K21

K19

K17

K15

K13

K11

K9

K7

K3

J24

L8

L10

L12

L14

L16

L18

L20

L22

L24

N6

N8

N10

N12

N14

N16

N18

N20

N22

N24

R6

R8

R10

R12

R14

R16

R18

R20

R22

R24

U6

U8

U10

U12

U14

U16

U18

U20

U22

U24

W8

W10

W12

W14

W16

W18

W20

W22

W24

N30

P5

R4

N4

K5

L4

R2

U2

W2

V1

+CPU_CORE

C5 220U_B2_2.5VM_R15M

C550 220U_B2_2.5VM_R15M

1 2

1 2

C136 10U_0603_6.3V6M

C9 10U_0603_6.3V6M

C10 10U_0603_6.3V6M

C656 10U_0603_6.3V6M

C658 10U_0603_6.3V6M

C660 10U_0603_6.3V6M

C14 1U_0402_6.3V6K

C15 1U_0402_6.3V6K

C17 1U_0402_6.3V6K

C19 1U_0402_6.3V6K

C21 1U_0402_6.3V6K

C23 1U_0402_6.3V6K

C25 1U_0402_6.3V6K

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPU_VID5

CPU_VID6

VCCSENSE

VSSSENSE

+

+

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

C8

220U_B2_2.5VM_R15M

CPU_VID[0..6] <25>

+CPU_CORE

+

12

12

C12310U_0603_6.3V6M

12

C12110U_0603_6.3V6M

12

C12210U_0603_6.3V6M

12

C65710U_0603_6.3V6M

12

C65910U_0603_6.3V6M

12

C66110U_0603_6.3V6M

12

C111U_0402_6.3V6K

12

C121U_0402_6.3V6K

12

C131U_0402_6.3V6K

12

C1401U_0402_6.3V6K

12

C1391U_0402_6.3V6K

12

C1381U_0402_6.3V6K

12

C1371U_0402_6.3V6K

1

C26

0.1U_0402_16V4Z

2

Near pin N30

+1.5VS

Length match within 25 mils.

The trace width/space/other is

20/7/25.

+CPU_CORE

R30

100_0402_1%

1 2

R31

100_0402_1%

1 2

VCCSENSE

VSSSENSE

VCCSENSE <25>

VSSSENSE <25>

Close to CPU pin

within 500mils.

SILVERTHORNE_FCBGA8-441

A A

http://hobi-elektronika.net

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDEN TIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMA TION IT C ONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPA L ELEC TRONICS, INC.

3

2008/05/30 2011/05/30

Compal Secret Data

Deciphered Date

Title

Size Docu ment Number Re v

Custom

2

Date: Sheet

Compal Electronics, Inc.

Silverthorne(2/2)-PWR/GND

NYU00 LA-5301P

1

528Monday, Apr il 06, 2009

0.2

of

5

H_D#[0..6 3]<4> H_A#[3..31] <4>

D D

C C

H_NMI<4>

H_SMI#<4>

H_PBE#<4>

H_STPCLK#<4>

B B

H_INIT#<4,18>

H_INTR<4>

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

R33 24_0402_5%

1 2

+H_SWNG

+H_RCOMP

H_THERMTRIP_R#

U4A

V8

H_D0#

AF4

H_D1#

V2

H_D2#

AA1

H_D3#

AC1

H_D4#

AD2

H_D5#

V4

H_D6#

Y2

H_D7#

U1

H_D8#

Y8

H_D9#

AB2

H_D10#

AF2

H_D11#

AB4

H_D12#

AF8

H_D13#

AE1

H_D14#

AB8

H_D15#

AJ1

H_D16#

AH2

H_D17#

AM8

H_D18#

AN1

H_D19#

AK4

H_D20#

AG1

H_D21#

AH8

H_D22#

AK8

H_D23#

AP8

H_D24#

AK2

H_D25#

AR1

H_D26#

AT8

H_D27#

AT2

H_D28#

AH4

H_D29#

AP4

H_D30#

AP2

H_D31#

AV4

H_D32#

BB6

H_D33#

AV6

H_D34#

AY8

H_D35#

BA1

H_D36#

AU1

H_D37#

AT6

H_D38#

AV8

H_D39#

BB4

H_D40#

AT4

H_D41#

AY6

H_D42#

AV10

H_D43#

AV2

H_D44#

BC1

H_D45#

BB2

H_D46#

AY2

H_D47#

BD2

H_D48#

BH4

H_D49#

BD10

H_D50#

BK10

H_D51#

BD6

H_D52#

BD4

H_D53#

BF2

H_D54#

BE1

H_D55#

BD8

H_D56#

BF4

H_D57#

BH10

H_D58#

BK6

H_D59#

BB8

H_D60#

BF6

H_D61#

BF10

H_D62#

BH6

H_D63#

AB10

H_NMI

AB6

H_SMI#

AH6

H_PBE#

V6

H_SWING

AD10

H_STPCLK#

AK6

H_TESTIN#

T10

H_RCOMPO

AT10

RESERVED5

AP10

RESERVED4

AM6

H_THRMTRIP#

AF10

H_INIT#

AF6

H_INTR

POULSBO_FCBGA1249

HOST

layout note:

Route H_SCOMP and H_SCOMP# with trace width, spacing and impedance (55 ohm) same as FSB data traces

Layout Note:

H_RCOMP / H_VREF / H_SWNG

trace width and spacing is 10/20

R47

100_0402_1%

+1.05VS

12

12

R42

221_0603_1%

1

2

+H_SWNG+H_VREF

C30

0.1U_0402_16V7K

+1.05VS

12

R41

1K_0402_1%

A A

R45

12

2K_0402_1%

C29

1

0.1U_0402_16V7K

2

<BOM Structure>

+H_RCOMP

12

R46

24.9_0402_1%

Near B3 pinwithin 100 mils from NB

http://hobi-elektronika.net

5

4

H_A#3

M2

H_A3#

H_A4#

H_A5#

H_A6#

H_A7#

H_A8#

H_A9#

H_A10#

H_A11#

H_A12#

H_A13#

H_A14#

H_A15#

H_A16#

H_A17#

H_A18#

H_A19#

H_A20#

H_A21#

H_A22#

H_A23#

H_A24#

H_A25#

H_A26#

H_A27#

H_A28#

H_A29#

H_A30#

H_A31#

H_ADS#

H_ADSTB0#

H_ADSTB1#

H_GVREF

H_BNR#

H_BPRI#

H_BREQ0#

H_CPURST#

H_CGVREF

H_CLKINN

H_CLKINP

H_DBSY#

H_DEFER#

H_DINV0#

H_DINV1#

H_DINV2#

H_DINV3#

H_DPWR#

H_DRDY#

H_DSTBN0#

H_DSTBN1#

H_DSTBN2#

H_DSTBN3#

H_DSTBP0#

H_DSTBP1#

H_DSTBP2#

H_DSTBP3#

H_HIT#

H_HITM#

H_LOCK#

H_REQ0#

H_REQ1#

H_REQ2#

H_REQ3#

H_REQ4#

H_RS0#

H_RS1#

H_RS2#

H_CPUSLP#

H_TRDY#

H_CPUPWRGD

H_DPSLP#

H_DPRSTP#

CFG0

CFG1

BSEL2

FSB BSEL2

100

13310

CFG1 10K pull-down is required.

H_THERMTRIP_R#

4

M8

K4

P2

F4

G1

M4

F6

H6

D2

H2

J1

F2

D4

D12

H12

G11

A7

A9

A11

B6

H8

F10

B10

D6

D10

B12

B4

D8

K6

H4

B8

Y10

R1

P10

L1

M6

AD4

K10

M10

H10

AD6

AD8

AM2

AY10

BK8

P6

J9

Y4

AL1

AW1

BH8

W1

AM4

AY4

BF8

V10

T6

Y6

P4

N1

K8

P8

K2

T4

T2

T8

AH10

F12

AP6

F8

AK10

J27

B34

F28

1 2

R48

24_0402_5%

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_ADS#

H_ADSTB#0

H_ADSTB#1

+H_VREF

H_BNR#

H_BPRI#

H_BR0#

H_RESET#

CLK_MCH_BCLK#

CLK_MCH_BCLK

H_DBSY#

H_DEFER#

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DPWR#

H_DRDY#

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_HIT#

H_HITM#

H_LOCK#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

H_CPUSLP#

H_TRDY#

CFG0

100

133

H_ADS# <4>

H_ADSTB#0 <4>

H_ADSTB#1 <4>

H_BNR# <4>

H_BPRI# <4>

H_BR0# <4>

H_RESET# <4>

CLK_MCH_BCLK# <13>

CLK_MCH_BCLK <13>

H_DBSY# <4>

H_DEFER# <4>

H_DINV#0 <4>

H_DINV#1 <4>

H_DINV#2 <4>

H_DINV#3 <4>

H_DPWR# <4>

H_DRDY# <4>

H_DSTBN#0 <4>

H_DSTBN#1 <4>

H_DSTBN#2 <4>

H_DSTBN#3 <4>

H_DSTBP#0 <4>

H_DSTBP#1 <4>

H_DSTBP#2 <4>

H_DSTBP#3 <4>

H_HIT# <4>

H_HITM# <4>

H_LOCK# <4>

H_REQ#0 <4>

H_REQ#1 <4>

H_REQ#2 <4>

H_REQ#3 <4>

H_REQ#4 <4>

H_RS#0 <4>

H_RS#1 <4>

H_RS#2 <4>

H_CPUSLP# <4>

H_TRDY# <4>

H_PW RGOOD <4>

H_DPSLP# <4>

H_DPRSTP# <4,25>

R35 10K_0402_5%

1 2

R36 10K_0402_5%@

1 2

R37 10K_0402_5%

1 2

CPU_BSEL2 <4,13>

CFG0DDRFSB

DDRFSBFSB

100

13310 100

+1.05VS

12

133

within 2" from R48

R44

120_0402_5%

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDEN TIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMA TION IT C ONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPA L ELEC TRONICS, INC.

3

+1.05VS

H_THERMTRIP# <4>

Issued Date

3

DDR_A_D[0..63]<11,12>

+H_CGVREF

C27

0.1U_0402_16V7K

In pre-ES R571=2k H_CGVREF=2/3VCCP

In ES R571 choose 1k

2008/05/30 2011/05/30

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

+1.05VS

12

R38

1K_0402_1%

12

1

R40

1K_0402_1%

2

Compal Secret Data

Deciphered Date

U4D

BG49

BG47

BE45

BC43

BE47

BC47

BC45

BK44

BK42

BG41

BK40

BC41

BG43

BJ43

BJ39

BG39

BC39

BK38

BG37

BK36

BJ37

BG35

BJ35

BC35

BK34

BG31

BG33

BK30

BC33

BJ33

BJ31

BC31

BJ29

BG29

BK28

BC29

BE27

BK26

BG25

BJ25

BC25

BG23

BK22

BJ21

BK24

BJ23

BG21

BC21

BK20

BJ19

BG17

BJ17

BG19

BC19

BC17

BK16

BG15

BC15

BJ13

BK12

BK14

BJ15

BC13

BC11

POULSBO_FCBGA1249

SM_DQ0

SM_DQ1

SM_DQ2

SM_DQ3

SM_DQ4

SM_DQ5

SM_DQ6

SM_DQ7

SM_DQ8

SM_DQ9

SM_DQ10

SM_DQ11

SM_DQ12

SM_DQ13

SM_DQ14

SM_DQ15

SM_DQ16

SM_DQ17

SM_DQ18

SM_DQ19

SM_DQ20

SM_DQ21

SM_DQ22

SM_DQ23

SM_DQ24

SM_DQ25

SM_DQ26

SM_DQ27

SM_DQ28

SM_DQ29

SM_DQ30

SM_DQ31

SM_DQ32

SM_DQ33

SM_DQ34

SM_DQ35

SM_DQ36

SM_DQ37

SM_DQ38

SM_DQ39

SM_DQ40

SM_DQ41

SM_DQ42

SM_DQ43

SM_DQ44

SM_DQ45

SM_DQ46

SM_DQ47

SM_DQ48

SM_DQ49

SM_DQ50

SM_DQ51

SM_DQ52

SM_DQ53

SM_DQ54

SM_DQ55

SM_DQ56

SM_DQ57

SM_DQ58

SM_DQ59

SM_DQ60

SM_DQ61

SM_DQ62

SM_DQ63

2

DDR_A_BS#0

BC27

SM_BS0

SM_BS1

SM_BS2

SM_CK0

SM_CK1

SM_CK0#

SM_CK1#

SM_CKE0

SM_CKE1

SM_DQS0

SM_DQS1

SM_DQS2

SM_DQS3

SM_DQS4

SM_DQS5

SM_DQS6

SM_DQS7

SM_MA0

SM_MA1

SM_MA2

SM_MA3

SM_MA4

SM_MA5

SM_MA6

SM_MA7

SM_MA8

SM_MA9

SM_MA10

SM_MA11

SM_MA12

SM_MA13

SM_MA14

SM_VREF

SM_RAS#

SM_CAS#

SM_WE#

SM_CS0#

SM_CS1#

DDR SYSTEM MEMORY

SM_RCOMPO

SM_RCVENIN

SM_RCVENOUT

Title

Size Docu ment Number Re v

Custom

2

Date: Sheet

DDR_A_BS#1

BE25

DDR_A_BS#2

BA35

BG45

BE11

BJ45

BG11

BE39

BE37

DDR_A_DQS0

BJ47

DDR_A_DQS1

BJ41

DDR_A_DQS2

BC37

DDR_A_DQS3

BK32

DDR_A_DQS4

BG27

DDR_A_DQS5

BE23

DDR_A_DQS6

BK18

DDR_A_DQS7

BG13

DDR_A_MA0

BJ27

DDR_A_MA1

BA19

DDR_A_MA2

BA27

DDR_A_MA3

BA25

DDR_A_MA4

BE29

DDR_A_MA5

BC23

DDR_A_MA6

BE31

DDR_A_MA7

BA31

DDR_A_MA8

BA33

DDR_A_MA9

BA29

DDR_A_MA10+H_CGVREF

BE17

DDR_A_MA11

BE35

DDR_A_MA12

BE33

DDR_A_MA13

BE19

BA37

+SM_VREF

BE43

DDR_A_RAS#

BE21

DDR_A_CAS#

BA13

DDR_A_WE#

BA17

BA23

BA15

BE13

BA39

BE41

1 2

R32 30.1_0402_1%

Layout Note:

V_DDR_MCH_REF

trace width and

spacing is 20/20.

C28

0.1U_0402_16V7K

Compal Electronics, Inc.

Poulsbo(1/5)-HOST/DDR

NYU00 LA-5301P

+SM_VREF

1

2

1

DDR_A_BS#0 <11,12>

DDR_A_BS#1 <11,12>

DDR_A_BS#2 <11,12>

M_CLK_DDR0 <11,12>

M_CLK_DDR1 <11,12>

M_CLK_DDR#0 <11,12>

M_CLK_DDR#1 <11,12>

M_CKE0 <11>

M_CKE1 <12>

DDR_A_DQS[0..7] <11,12>

DDR_A_MA[0..13] <11,12>

DDR_A_RAS# <11,12>

DDR_A_CAS# <11,12>

DDR_A_WE# <11,12>

M_CS#0 <11>

M_CS#1 <12>

+0.9VS

+1.8V

R39

10K_0402_1%

1 2

R43

10K_0402_1%

1 2

628Monday, April 06, 2009

1

0.2

of

5

4

3

2

1

+3VS

1 2

R49 10K_0402_5%

1 2

R50 8.2K_0402_5%

D D

1 2

R51 10K_0402_5%

1 2

R52 10K_0402_5%

1 2

R56 100K_0402_5%

1 2

R115 100K_0402_5%

C C

B B

LPC_CLKRUN#

SIRQ

EDID_CLK_LCD

EDID_DAT_LCD

ENBKL

GMCH_LVDD EN

MINSD_CD#<14>

MINSD_CLK<14>

MINSD_CMD<14>

MINSD_WP<14>

MINSD_PWR#<14>

MINSD_DATA[0..3]<14>

CLK_PCI_LPC<18>

+3VS

+3VS

+3VS

MINSD_DATA0

MINSD_DATA1

MINSD_DATA2

MINSD_DATA3

INVT_PW M<15>

LPC_AD[0 ..3]<18>

R55 22_0402_5%

1 2

LPC_FRAME#<18>

R588

ENBKL<18>

EDID_CLK_LCD<15>

EDID_DAT_LCD<15>

GMCH_LVDD EN<15>

LVDSAC+<15>

LVDSAC-<15>

LVDSA0-<15>

LVDSA1-<15>

LVDSA2-<15>

LVDSA0+<15>

LVDSA1+<15>

LVDSA2+<15>

R118 10K_0402_5%

R175 47_0402_5%

R179 47_0402_5%

R117 22K_0402_5%

R174 47_0402_5%

R176 47_0402_5%

R177 47_0402_5%

R178 47_0402_5%

1 2

R53 10K_0402_5%

R57 10K_0402_5%

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

+3VS

R116 10K_0402_5%

1 2

+3VS

R478 39K_0402_5%

1 2

R62 10K_0402_5%

1 2

+3VS

R63 10K_0402_5%

1 2

+3VS

R64 39K_0402_5%

SIRQ<18>

0_0402_5%

1 2

1 2

EDID_CLK_LCD

EDID_DAT_LCD

GMCH_LVDD EN

LVDSAC+

LVDSAC-

LVDSA0LVDSA1LVDSA2-

LVDSA0+

LVDSA1+

LVDSA2+

R65

0_0402_5%

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_CLKOUT0

LPC_CLKRUN#

SIRQ

INVT_PWM_SCH

MINSD_CD#

MINSD_CLK_R

MINSD_CMD_R

MINSD_DATA0_R

MINSD_DATA1_R

MINSD_DATA2_R

MINSD_DATA3_R

T16TPC12

T17TPC12

T18TPC12

T19TPC12

SD1_CMD_R

SD2_CMD_R

12

U4B

K38

LPC_AD0

J39

LPC_AD1

A35

LPC_AD2

L39

LPC_AD3

F38

LPC_CLKOUT0

B36

LPC_CLKOUT1

D38

LPC_CLKOUT2

D36

LPC_CLKRUN#

B38

LPC_SERIRQ

K40

LPC_FRAME#

A33

L_BKLTCTL

A31

L_BKLTEN

D28

L_CTLA_CLK

K26

L_CTLB_DATA

A27

L_DDCCLK

H28

L_DDCDATA

D30

L_VDDEN

AF48

LA_CLKP

AF50

LA_CLKN

AJ43

LA_DATAN0

AK48

LA_DATAN1

AH48

LA_DATAN2

AG45

LA_DATAN3

AJ45

LA_DATAP0

AK50

LA_DATAP1

AH50

LA_DATAP2

AG43

LA_DATAP3

B18

SD0_CD#

D18

SD0_CLK

J15

SD0_CMD

H18

SD0_LED

F18

SD0_WP

H20

SD0_PWR#

H16

SD0_DATA0

A17

SD0_DATA1

K18

SD0_DATA2

F16

SD0_DATA3

K16

SD0_DATA4

B16

SD0_DATA5

D16

SD0_DATA6

K20

SD0_DATA7

B22

SD1_CD#

H22

SD1_CLK

F20

SD1_CMD

A21

SD1_LED

B20

SD1_WP

D20

SD1_PWR#

F22

SD1_DATA0

J19

SD1_DATA1

K22

SD1_DATA2

D22

SD1_DATA3

K24

SD2_CD#

D26

SD2_CLK

B24

SD2_CMD

D24

SD2_LED

B26

SD2_WP

A19

SD2_PWR#

J23

SD2_DATA0

A25

SD2_DATA1

F26

SD2_DATA2

A23

SD2_DATA3

F24

SD2_DATA4

H24

SD2_DATA5

H26

SD2_DATA6

E25

SD2_DATA7

G21

RESERVED18

POULSBO_FCBGA1249

LPC BUS

LVDS

SDIO / MMC

RESERVED8

RESERVED0

RESERVED1

MISC SIGNALSSYSTEM MGMTSDVOPCIE

RESERVED2

RESERVED3

INTVRMEN

RTC

DPRSLPVR

SDVO_CTRLCLK

SDVO_CTRLDATA

SDVOB_CLK

SDVOB_CLK#

SDVOB_INT

SDVOB_INT#

SDVOB_STALL

SDVOB_STALL#

SDVOB_TVCLKIN

SDVOB_TVCLKIN#

SDVOB_RED

SDVOB_RED#

SDVOB_GREEN

SDVOB_GREEN#

SDVOB_BLUE

SDVOB_BLUE#

PCIE_PERn1

PCIE_PERp1

PCIE_PETn1

PCIE_PETp1

PCIE_PERn2

PCIE_PERp2

PCIE_PETn2

PCIE_PETp2

PCIE_CLKINN

PCIE_CLKINP

PCIE_ICOMP I

PCIE_ICOMP O

RTC_X1

RTC_X2

RTCRST#

EXTTS

PWROK

SLPRDY#

SLPMODE

RSMRST#

BK50

E49

B32

BE15

BA21

F48

F50

F46

H48

D32

ICH_POK

C49

J49

D34

L45

L43

SDVO_CTRLCLK

F30

SDVO_CTRLDATA

A29

SDVO_CLK

AV48

SDVO_CLK#

AV50

AU47

AU49

AN45

AN43

AP48

AP50

SDVO_RED

AM50

SDVO_RED#

AM48

SDVO_GREEN

AT50

SDVO_GREEN#

AT48

SDVO_BLUE

AR45

SDVO_BLUE#

AR43

PCIE_WLANTX_IRX_C_N2

AW45

PCIE_WLANTX_IRX_C_P2

AW43

PCIE_ITX_WLANRX_N2

BB48

PCIE_ITX_WLANRX_P2

BB50

BA43

BA45

BE49

BD50

CLK_PCIE_ICH#

AY48

CLK_PCIE_ICH

AY50

BA47

BA49

R58

10K_0402_5%

1 2

ICH_RTCX1

ICH_RTCX2

ICH_RTCRST#

R60 10K_0402_5%

1 2

R61 10K_0402_5%

1 2

+PCIE _ICOMP

1 2

SDVO_CTRLCLK <17>

SDVO_CTRLDATA <17>

SDVO_CLK <17>

SDVO_CLK# <17>

SDVO_INT <17>

SDVO_INT# <17>

SDVO_RED <17>

SDVO_RED# <17>

SDVO_GREEN <17>

SDVO_GREEN# <17>

SDVO_BLUE <17>

SDVO_BLUE# <17>

C34 0.1U_0402_16V7K

1 2

C35 0.1U_0402_16V7K

1 2

T66 TPC24

T67 TPC24

R66 24.9_0402_1%

C669 22P_0402_50V8J

C670 22P_0402_50V8J

1 2

R59 10K_0402_5%

+3VS

1 2

1 2

+RTCVCC

1 2

R54

20K_0402_1%

+RTCVCC

EC_THERM# <4,8,18>

ICH_POK <18>

PM_SLPRDY# <18>

DPRSLPVR <25>

PM_SLPMODE <18>

EC_RSMRST# <18>

PCIE_WLANTX_IRX_C_N2 <14>

PCIE_WLANTX_IRX_C_P2 <14>

PCIE_ITX_C_WLANRX_N2 <14>

PCIE_ITX_C_WLANRX_P2 <14>

+1.5VS

ICH_RTCRST#

1

C31

1U_0402_6.3V6K

2

ICH_RTCX1

R67

10M_0402_5%

ICH_RTCX2

12

12

X1

32.768KHZ_12.5P_1TJE125DP1A000M

!!Input from CPU thermal sensor

WLAN

RF Solution

CLK_PCIE_ICH# <13>

CLK_PCIE_ICH <13>

C3610P_0402_50V8J

C3710P_0402_50V8J

RTC Reset SW

(Place under door)

JRTC1

112

JUMP_43X39

A A

http://hobi-elektronika.net

5

2

ICH_RTCRST#

1

C274

0.01U_0402_16V7K

2

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDEN TIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMA TION IT C ONTAINS

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPA L ELEC TRONICS, INC.

3

2008/05/30 2011/05/30

Compal Secret Data

Deciphered Date

Title

Size Docu ment Number Re v

Custom

2

Date: Sheet

Compal Electronics, Inc.

Poulsbo(2/5)-LVDS/SDVO/SDIO/PCIE

NYU00 LA-5301P

728Monday, April 06, 2009

1

of

0.2

5

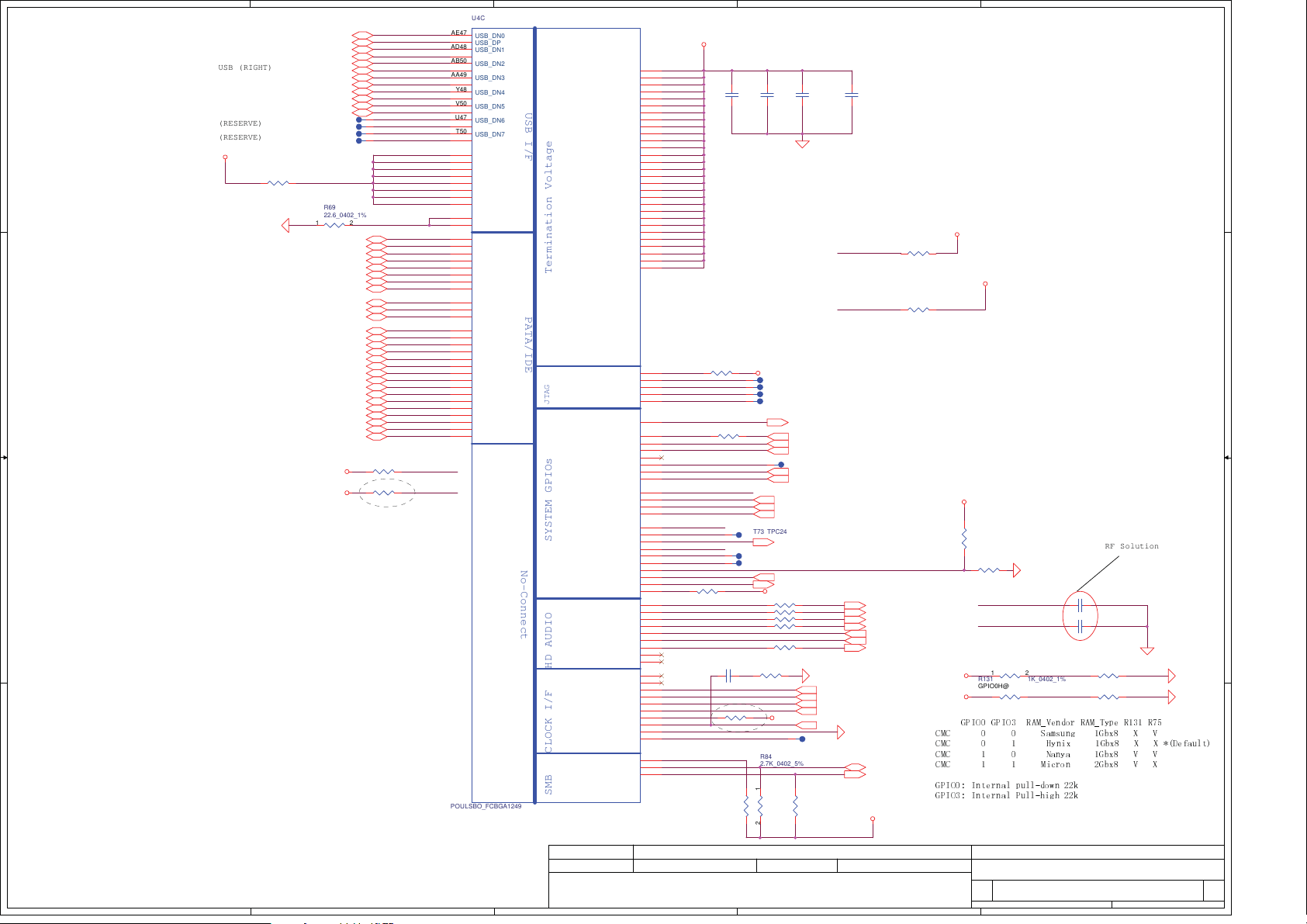

USB (LEFT)

USB (LEFT)

USB (RIGHT)

3G

BT

D D

CAM

(RESERVE)

USB20_N0<15>

USB20_P0<15>

USB20_N1<15>

USB20_P1<15>

USB20_N2<14>

USB20_P2<14>

USB20_N3<14>

USB20_P3<14>

USB20_N4<20>

USB20_P4<20>

USB20_N5<20>

USB20_P5<20>

(RESERVE)

+3VALW

R68 10K_0402_5%

1 2

R69

22.6_0402_1%

1 2

C C

B B

A A

PD_DREQ<19>

PD_IORDY<19>

PD_IRQ<19>

PD_DACK#<19>

PD_IOW#<19>

PD_IOR#<19>

PD_CS#3<19>

PD_CS#1<19>

PD_A2<19>

PD_A1<19>

PD_A0<19>

PD_D15<19>

PD_D14<19>

PD_D13<19>

PD_D12<19>

PD_D11<19>

PD_D10<19>

PD_D9<19>

PD_D8<19>

PD_D7<19>

PD_D6<19>

PD_D5<19>

PD_D4<19>

PD_D3<19>

PD_D2<19>

PD_D1<19>

PD_D0<19>

+3VS

+3VS

4

USB20_N0

USB20_P0

USB20_N1

USB20_P1

USB20_N2

USB20_P2

USB20_N3

USB20_P3

USB20_N4

USB20_P4

USB20_N5

USB20_P5

T81TPC24

T82TPC24

T87TPC24

T88TPC24

USB20_N6

USB20_P6

USB20_N7

USB20_P7

+USB_RBIAS

R70

4.7K_0402_5%

R123

10K_0402_5%

PD_DREQ

PD_IORDY

PD_IRQ

PD_DACK#

PD_IOW#

PD_IOR#

PD_CS#3

PD_CS#1

PD_A2

PD_A1

PD_A0

PD_D15

PD_D14

PD_D13

PD_D12

PD_D11

PD_D10

PD_D9

PD_D8

PD_D7

PD_D6

PD_D5

PD_D4

PD_D3

PD_D2

PD_D1

PD_D0

PD_IORDY

12

PD_IRQ

12

AE47

AE49

AD48

AD50

AB50

AB48

AA49

AA47

W45

AA45

AA43

W43

AC45

AC43

Y48

Y50

V50

V48

U47

U49

T50

T48

R43

R45

U43

U45

J43

D46

G45

B46

A37

F44

C47

E47

K42

J45

H40

B40

E43

H42

D42

F40

A43

A41

J41

A39

B42

F42

D44

L41

B44

G43

D40

U4C

USB_DN0

USB_DP0

USB_DN1

USB_DP1

USB_DN2

USB_DP2

USB_DN3

USB_DP3

USB_DN4

USB_DP4

USB_DN5

USB_DP5

USB_DN6

USB_DP6

USB_DN7

USB_DP7

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

USB_OC4#

USB_OC5#

USB_OC6#

USB_OC7#

USB_RBIASN

USB_RBIASP

PATA_DDREQ

PATA_IORDY

PATA_IDEIRQ

PATA_DDACK#

PATA_DIOW#

PATA_DIOR#

PATA_DCS3#

PATA_DCS1#

PATA_DA2

PATA_DA1

PATA_DA0

PATA_DD15

PATA_DD14

PATA_DD13

PATA_DD12

PATA_DD11

PATA_DD10

PATA_DD9

PATA_DD8

PATA_DD7

PATA_DD6

PATA_DD5

PATA_DD4

PATA_DD3

PATA_DD2

PATA_DD1

PATA_DD0

USB I/F PATA/IDE

JTAG

SYSTEM GPIOsHD AUDIOCLOCK I/F

No-Connect

SMB Termination Voltage

POULSBO_FCBGA1249

3

VTT_1

VTT_2

VTT_3

VTT_4

VTT_5

VTT_6

VTT_7

VTT_8

VTT_9

VTT_10

VTT_11

VTT_12

VTT_13

VTT_14

VTT_15

VTT_17

VTT_18

VTT_19

VTT_20

VTT_21

VTT_22

VTT_23

VTT_24

VTT_25

VTT_26

VTT_27

VTT_28

VTT_29

VTT_16

TRST#

STPCPU#

RSTRDY#

RESET#

RSTWARN

GPIOSUS0

GPIOSUS1

GPIOSUS2

GPIOSUS3

WAKE#

SMI#

THRM#

GPE#

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

SPKR

HDA_CLK

HDA_SYNC

HDA_RST#

HDA_SDI0

HDA_SDI1

HDA_SDO

HDA_DOCKEN#

HDA_DOCKRST#

RESERVED6

RESERVED7

DA_REFCLKINN

DA_REFCLKINP

DB_REFCLKINNSSC

DB_REFCLKINPSSC

CLKREQ#

CLK14

USB_CLK48

SUSCLK

SMB_ALERT#

SMB_DATA

SMB_CLK

TMS

TDO

TCK

AW13

AV12

AU13

AT12

AR13

AP12

AN13

AM12

AL13

AK12

AJ13

AH12

AG13

AF12

AE13

AC13

AB12

AA13

Y12

W13

V12

U13

T12

R13

P12

N13

M14

M12

AD12

N49

M50

K48

TDI

M48

N47

H30

H50

BA41

K50

U41

N43

N45

R41

N41

B30

F32

P50

G29

K30

F34

G33

K36

H36

F36

J31

H34

K28

J35

K14

E13

A13

F14

B14

D14

E15

H14

AU43

AU45

AL45

AL43

AE45

AE43

B28

H32

W41

J47

K32

G37

H38

+1.05VS

C38

1U_0402_6.3V6K

1

2

R125

10K_0402_5%

100_0402_1%

R73

1 2

PLT_RST#

SB_INT_FLASH_SEL

SCH_PCIE_W AKE#

EC_SMI#

EC_THERM#

GPIO0

EC_EAPD_R#_SCH

GPIO3

1 2

R76 10K_0402_5%

SPKR_SCH

HDA_BITCLK_AUDIO_SCH

HDA_SYNC_AUDIO_SCH

HDA_RST_AUDIO#_SCH

HDA_SDOUT_AUDIO_SCH

C45

@

10P_0402_50V8J

1 2

R124

10K_0402_5%

R83

10K_0402_5%

C40

1U_0402_6.3V6K

1

1

2

2

C39

1U_0402_6.3V6K

12

+1.05VS

T12 TPC12

T13 TPC12

T14 TPC12

T15 TPC12

H_STP_CPU# <13>

PM_RSTRDY# <18>

PLT_RST# < 14,17,18,19>

PM_RSTWARN_R <18>

TPC24

T55

PBTN_OUT# <18>

EC_LID_OUT# <18>

EC_SMI# <18>

EC_THERM# <4,7,18>

EC_SCI# <18>

T73 TPC24

BT_APM <20>

TPC24

T57

TPC24

T58

SLPIOV R# <4,22>

PROCHOT# <4,25>

+3VS

R180 39_0402_5%

1 2

R78 39_0402_5%

1 2

R79 39_0402_5%

1 2

R80 39_0402_5%

1 2

1 2

R81 39_0402_5%

R82 10_0402_5%@

1 2

12

+3VS

R84

2.7K_0402_5%

12

12

T5 PAD

12

R85

2.7K_0402_5%

2

1

C41

10U_0603_6.3V6M

2

SCH_PCIE_W AKE#

R71 1K_0402_5%

EC_THERM#

R72 8.2K_0402_5%@

SPKR <16>

HDA_BITCLK_AUDIO <16,17>

HDA_SYNC_AUDIO <16,17>

HDA_R ST_AUDIO# <16,17>

HDA_SDIN0 <16>

HDA_SDIN1 <17>

HDA_SDOUT_AUDIO <16,17>

CLK_MC H_DREFCLK# <13>

CLK_MCH_DREFCLK <13>

MCH_SS CDREFCLK# <13>

MCH_SS CDREFCLK <13>

CLK_14M_SCH <13>

SMB_DAT <13>

SMB_CLK <13>

+3VS

1

+3VALW

1 2

+3VS

1 2

+3VS

12

@

R74

10K_0402_5%

1 2

R77

10K_0402_5%

HDA_BITCLK_AUDIO

HDA_SDOUT_AUDIO

1 2

+3VS

R131 1K_0402_1%

GPIO0H@

1 2

+3VS

R126 1K_0402_1%@

*3,2*3,25$0B9HQGRU5$0B7\SH55

&0&6DPVXQJ*E[;9

&0&+\QL[*E[;;'HIDXOW

&0&1DQ\D*E[99

&0&0LFURQ*E[9;

*3,2,QWHUQDOSXOOGRZQN

*3,2,QWHUQDO3XOOKLJKN

C671 22P_0402_50V8J

C672 22P_0402_50V8J

GPIO0

GPIO3

RF Solution

1 2

1 2

1 2

R127 1K_0402_1%

@

1 2

R75 1K_0402_1%

GPIO3L@

http://hobi-elektronika.net

5

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDEN TIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMA TION IT C ONTAINS

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPA L ELEC TRONICS, INC.

3

2008/05/30 2011/05/30

Compal Secret Data

Deciphered Date

Title

Size Docu ment Number Re v

Custom

2

Date: Sheet

Compal Electronics, Inc.

Poulsbo(3/5)-HDA/PATA/USB

NYU00 LA-5301P

828Monday, Apr il 06, 2009

1

0.2

of

5

4

3

2

1

+1.05VS

T32

T30

T28

T26

T24

T22

T20

T18

T16

AK22

AK20

AK18

AK16

AH34

AH32

AH30

AH28

AH26

AH24

AH22

AH20

AH18

AH16

AF34

AF32

AF30

AF28

AF26

AF24

AF22

AF20

AF18

AF16

AD30

AD28

AD26

AD24

AD22

AD20

AD18

AB18

AB16

Y30

Y28

Y26

Y24

V22

V20

V18

AG37

AF38

AF36

AE37

AD36

AT34

AT32

AR37

AP38

AP36

AN37

AU37

AT38

AT36

AM36

AV38

AK36

AJ37

AH38

AH36

AK38

AL37

U4E

VCCLVDS_101

VCCLVDS_100

VCCLVDS_1

VCCLVDS_2

VCCLVDS_3

VCCPCIE_4

VCCPCIE_5

VCCPCIE_6

VCCPCIE_7

VCCPCIE_8

VCCPCIE_9

VCCPCIE_1

VCCPCIE_2

VCCPCIE_3

VCCPCIE_100

VCCPCIE_101

VCCSDVO_110

VCCSDVO_100

VCCSDVO_101

VCCSDVO_103

VCCSDVO_106

VCCSDVO_105

VCC_79

VCC_80

D D

+1.5VS

C53

1U_0402_6.3V6K

+1.5VS

1

2

C C

+1.5VS

1

2

C56

1U_0402_6.3V6K

1

C57

1U_0402_6.3V6K

2

Y22

T34

VCC_9

VCC_8

VCC_7

VCC_6

VCC_5

VCC_4

VCC_3

VCC_2

VCC_1

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_81

VCC_69

VCC_10

VCC_34

VCC

AD16

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

AM34

AM32

AM30

AM28

AM26

AM24

AM22

AM20

AM18

AM16

AK34

AK32

AK30

AB30

AB28

AB26

AB24

AB22

AB20

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_54

VCC_48

AK28

VCC_55

VCC_56

VCC_57

VCC_58

VCC_59

VCC_60

VCC_61

C46

0.1U_0402_16V7K

Y18

Y16

V34

V32

V30

V28

V16

AK26

AK24

VCC_62

VCC_71

VCC_72

VCC_73

VCC_74

VCC_75

VCC_82

VCC_120

VCC_121

RESERVED10

RESERVED9

VCC15USB_1

VCC15USB_2

VCC15USB_3

VCC15USB_4

VCC15USB_5

VCC15USB_6

RESERVED12

RESERVED11

RESERVED13

VCCAPCIEBG

VSSAPCIEBG

V26

V24

VCC_76

VCC_77

VCC_78

VCC15_1

VCC15_2

VCC15_3

VCC15_4

VCC15_5

VCC15_6

VCC15_7

VCC15_8

VCC15_9

VCC15_10

VCC15_11

VCC15_12

VCC15_13

VCC15_14

VCC15_15

VCC15_16

VCC15_17

VCC15_18

Y20

VCC_70

C47

0.1U_0402_16V7K

1

2

R33

R31

R29

R27

R25

R23

R21

R19

R17

R15

P34

P32

N33

N31

M38

M36

M34

M32

P38

P36

AD34

AD32

AB34

AB32

Y34

Y32

AB38

AA37

W37

AW41

AY42

C49

1U_0402_6.3V6K

1

1

2

2

C48

0.1U_0402_16V7K

+1.5VS

1

C54

1U_0402_6.3V6K

2

Place under Poulsbo

+1.5VS

1

2

C50

4.7U_0603_6.3V6K

Place under Poulsbo

1

2

T7 PAD

+3VS

R86

0_0402_5%

1 2

C663

10U_0603_6.3V6M

C51

10U_0603_6.3V6M

1

1

1

2

2

2

C664

10U_0603_6.3V6M

1

+

C55

150U_B2_6.3VM_R35M

2

T6 PAD

1

C58

0.1U_0402_16V7K

2

1

+

C52

150U_B2_6.3VM_R35M

2

VCCSM_103

VCCSM_104

VCCSM_105

VCCSM_106

AW29

AW27

AW25

AW23

C61

1U_0402_6.3V6K

VCCSM_10

VCCSM_107

VCCSM_108

AW37

AW21

AW19

1

2

VCCSM_1

VCCSM_2

VCCSM_3

VCCSM_4

VCCSM_5

VCCSM_6

AV36

AV34

AV32

AV30

AV28

AV26

AW17

1

2

C62

10U_0603_6.3V6M

VCCSM_7

VCCSM_21

VCCSM_22

AV24

AV22

VCCSM_23

VCCSM_24

VCCSM_25

VCCSM_26

VCCSM_27

AT30

AT28

AT26

AV20

AV18

AV16

1

+

C63

150U_B2_6.3VM_R35M

2

VCCSM_28

VCCSM_29

VCCSM_30

VCCSM_31

VCCSM_32

VCCSM_33

VCCSM_34

VCCSM_35

VCCSM_36

VCCSM_37

VCCSM_38

VCCSM_39

VCCSM_40

VCCSM_41

AT24

AT22

AT20

AT18

AT16

AP34

AP32

AP30

AP28

AP26

AP24

AP22

AP20

C67

0.1U_0402_16V7K

VCCSM_100

VCCSM_101

VCCSM_102

VCCSM_43

AP16

AW35

AW33

B B

C59

1U_0402_6.3V6K

+1.8V

1

2

AW31

1

2

C60

1U_0402_6.3V6K

VCCP33USBSUS_2

RESERVED16

RESERVED17

VCCSM_42

RESERVED14

RESERVED15

Y38

N37

N35

AB36

AP18

AC37

T8

T9

PAD

PAD

Place under Poulsbo

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND C ONTAINS CONFIDEN TIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMA TION IT C ONTAINS

http://hobi-elektronika.net

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPA L ELEC TRONICS, INC.

3

VCC33_15

VCC33SUS_1

VCC33SUS_2

VCC33SUS_3

VCCP33USBSUS_1

VCCP33USBSUS_3

T38

R39

U37

M18

W39

AA39

1

1

2

2

C69

0.1U_0402_16V7K

2008/05/30 2011/05/30

VCC33_9

VCC33_10

VCC33_11

VCC33_12

VCC33_13

VCC33_14

M30

M28

M26

M24

M22

M20

C70

1U_0402_6.3V6K

1

2

C71

1U_0402_6.3V6K

Compal Secret Data

VCC33_6

N19

VCC33_3

VCC33_4

VCC33_5

VCC33_7

VCC33_8

N25

N23

N21

N17

N15

+RTCVCC

+3VS

1

2

C72

1U_0402_6.3V6K

0.1U_0402_16V7K

Deciphered Date

VCC33_1

VCC33_2

VCC33RTC

VCCHDA_1

VCCHDA_2

VCCAUSBPLL

VCCDHPLL

VCCAHPLL

VCCAUSBBGSUS

VCCADPLLA

VCCAPCIEPLL

VCCADPLLB

VCC5REF_1

K34

AE39

AN49

AG39

+VCCADPLL

VCC5REFSUS

POULSBO_FCBGA1249

AA41

+V5_5REFSUS_SCH

+V5_5REF_SCH

0.1U_0402_16V7K

1

C68

0.1U_0402_16V7K

2

1 2

R88

0_0402_5%

1

C74

0.1U_0402_16V7K

2

+5VALW+3VALW

12

D1

CH751H-40PT_SOD323-2

1

2

+1.5VS

Title

NYU00 LA-5301P

1

2

C66

0.1U_0402_16V7K

+V5_5REFSUS_SCH

D2

CH751H-40PT_SOD323-2

+V5_5REF_SCH

Compal Electronics, Inc.

Poulsbo(4/5)-PWR

C65

Size Docu ment Number Re v

Custom

Date: Sheet

21

21

1

R87

10_0402_5%

+5VS+3VS

12

R132

10_0402_5%

928Monday, April 06, 2009

of

0.2

VCC33_16

A45

N29

N27

M16

1

2

J11

K12

1

C64

2

1U_0402_6.3V6K

+VCCAUSBPLL

C75

BB10

BA11

AC39

+VCCAHPLL

C73

0.1U_0402_16V7K

R89

0_0402_5%

1 2

1 2

R90

1

0_0402_5%

2

2

VSSAUSBBGSUS

AE41

AC41

1

2

+1.5VS

+3VALW+3VALW

+1.5VS

Loading...

Loading...