Page 1

A

B

C

D

E

LA-2251

1 1

2 2

Compal confidential

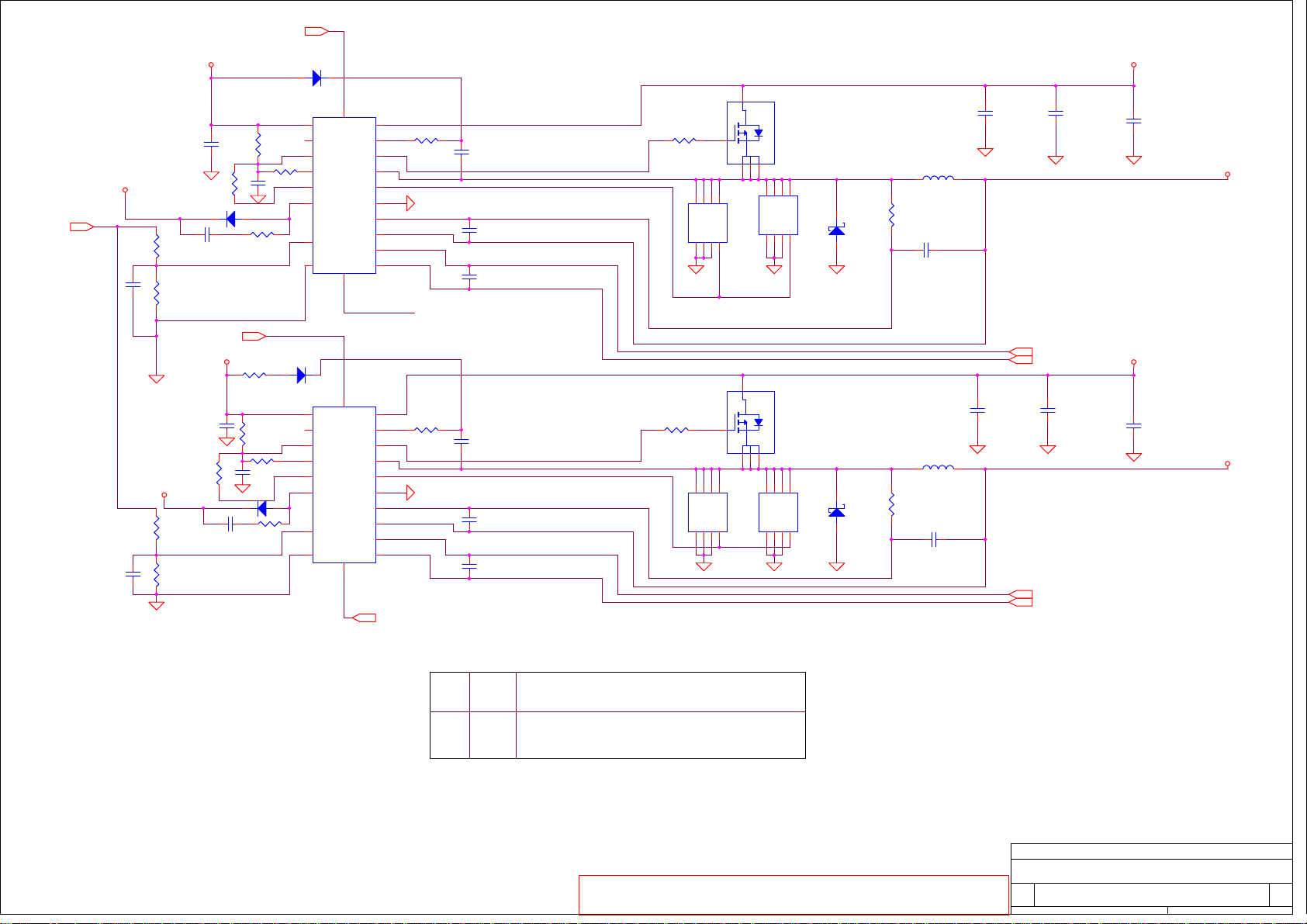

Schematics Document

DT TRANSPORT or Prescott uFCPGA

with Sis661FX+Sis963L core logic

3 3

4 4

A

B

2004-05-17

REV:1.0

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Title

Size Document Number Rev

D

Date: Sheet

Compal Electronics, Inc.

Cover Sheet

LA-2251

E

1.0

of

147Monday, May 17, 2004

Page 2

A

B

C

D

E

Compal confidential

File Name :LA-2251

1 1

CRT Conn.

page 17

W/O EXT VGA CHIP

LVDS Encoder

LCD Conn

page 17

SiS 302ELV

Fan Control

page 16

DVL

page 7

1.8V

Intel Northwood/Prescott Processor

uFCBGA-479/uFCPGA-478 CPU

page 4,5,6

H_A#(3..31)

FSB

533/800MHz

H_D#(0..63)

SiS 661FX

BGA 839 pin

page 8,9,10,11

Thermal Sensor

ADM1032AR

page 7

Memory BUS(DDR)

2.5V 200MHz DDR-266/333/400

USB1.1

MIAN CLOCK

GENERATOR

ICS952013CF

DDR-SO-DIMM X2

BANK 0, 1, 2, 3

BT/USB KEY

page 14,15

page 29

page 12

DDR CLOCK

BUFFER

ICS93722

page 13

USB2.0

3.3V 48MHz

2 2

RJ45 CONN

page 25

Mini PCI

socket

page 26

IDSEL:AD17/AD21

(PIRQB#,GNT#1/4,REQ#1/4)

3 3

TRANSFOMOR

H0013

3.3V 33 MHz

IEEE 1394

VIA-VT6301S

page 24

IDSEL:AD16

(PIRQA#,GNT#0,REQ#0)

PCI BUS

LAN`S PHY

RTL8201CL

page 25page 25

CardBus Controller

ENE CB1410

Slot 0

page 23

IDSEL:AD20

(PIRQA#,GNT#2,REQ#2)

page 23

RTC CKT.

page 18

Power OK CKT.

page 35

Power On/Off CKT.

page 32

Touch Pad

EC I/O Buffer

4 4

DC/DC Interface CKT.

page 36

ENE KB910

LPC K/B CTRL

page 32

page 34

page 33

Int.KBD

BIOS

page 32

page 34

MuTIOL

1.8V 133MHz 4x

SiS 963L

BGA 371 pin

page 18,19,20,21

LPC BUS

3.3V 33MHz

3.3V 24.576MHz

AC-LINK

3.3V

Primary IDE

ATA-133

Secondary IDE

ATA-133

PARALLEL

USB conn x3

Audio Codec

ALC250

MDC & BT Conn.

Mini-PCI solt

HDD

Connector

CDROM

Connector

VIA VT1211

Super I/O

page 31

page 29

page 27

page 29

page 26

page 22

page 22

page 30

AMP & Audio Jack

page 28

RJ11 CONN

page 29

FDD

page 31

Power Circuit DC/DC

page 37,38,39,40,41,42,43,44,45

A

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Block Diagram

LA-2251

E

1.0

of

247Monday, May 17, 2004

Page 3

Voltage Rails

A

Power Plane

VIN

B+

+CPU_CORE Core voltage for CPU

+1.2V

+1.25VS

+1.8VALW 1.8V always on power rail ON*ON*ON

+1.8VS 1.8V switched power rail for SIS M661FX NB. OFF

+3VS OFF

+5VS

+12VALW

RTCVCC

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

Description

Adapter power supply (19V)

AC or battery power rail for power circuit.

The voltage(1.2V) for Processor VID select

1.25V switched power rail for DDR Vtt

2.5V system power rail for DDR ON+2.5V ON OFF

3.3V switched power rail

5V switched power rail OFF

12V always on power rail

RTC power

S3

S0-S1

N/AONN/A

N/A

N/A

N/A

ON

OFF

OFF

ON

OFF

OFF

ON

ON+3VALW ON3.3V always on power rail

ON OFF

ON

ON

OFF

ON

ON

ON

ON

ON

S5

N/A

OFF

OFF

OFF

OFFON OFF2.5V switched power rail for DDR Clock Buffer+2.5VS

ON*

ON*+5VALW 5V always on power rail

ON*

ON

Symbol Note :

: means Digital Ground

: means Analog Ground

@ : means just reserve , no build

FIR@ : means just build when FIR Module build in .

External PCI Devices

1 1

NB Internal VGA

AGP BUS

SOUTHBRIDGE

USB

AC97

ATA 100

ETHERNET

1394

LAN

CARD BUS

Wireless LAN(MINI PCI)

Note: PLACE CLOSE TO M661FX,

L

USE 10/10 WIDTH/SPACE

IDSEL # PIRQREQ/GNT #DEVICE

N/A

AGP_DEVSEL

AD13 (INT.)

AD14 (INT.)

AD13 (INT.)

AD13 (INT.)

AD15 (INT.)

AD16

AD19

AD20

AD17/AD21

N/A

N/A

N/A

N/A

N/A

N/A

N/A

0

3

2

1/4

A

A

N/A

E/F/H

C

A

D

A

D

A

B

Board ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7 NC

100K +/- 5%Ra

Rb V min

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

AD_BID

0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

V typ

AD_BID

V

AD_BID

0 V 0 V

0.503 V

0.819 V

0.538 V

0.875 V

1.185 V 1.264 V

2.200 V

3.300 V

2.341 V

3.300 V

max

Board ID

0

1

2

3

4

PCB Revision

0.1

0.2

0.3

0.4

1.0

5

6

7

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Notes List

LA-2251

of

347Monday, May 17, 2004

1.0

Page 4

5

4

+CPU_CORE

3

2

1

D D

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

C C

H_REQ#[0..4]8

H_ADS#8

R48

62_0402_5%@

+CPU_CORE

+CPU_CORE

B B

R49

1 2

1 2

H_BR0#8

H_BPRI#8

H_BNR#8

H_LOCK#8

CK_BCLK12

CK_BCLK#12

H_HIT#8

H_HITM#8

H_DEFER#8

51_0402_5%

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_IERR#

CK_BCLK

CK_BCLK#

AF22

AF23

A10

A12

A14

A16

A18

A20

AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19

C10

C12

C14

C16

C18

C20

D11

D13

D15

D17

D19

D9

VCC_65C8VCC_66

VCC_84

VCC_85

F9

F11

VCC_67

VCC_68

VCC_69

VCC_70

VCC_77

VCC_78

VCC_79E8VCC_80

E18

E20

+CPU_CORE

1 2

E10

VCC_71D7VCC_72

VCC_73

VCC_74

VCC_75

VCC_76

AMP_3-1565030-1_Prescott

E12

E14

E16

D#10

D#11

D#12

D#13

D#14

D#15

D#16

D#17

D#18

D#19

D#20

D#21

D#22

D#23

D#24

D#25

D#26

D#27

D#28

D#29

D#30

D#31

D#32

D#33

D#34

D#35

D#36

D#37

D#38

D#39

D#40

D#41

D#42

D#43

D#44

D#45

D#46

D#47

D#48

D#49

D#50

D#51

D#52

D#53

D#54

D#55

D#56

D#57

D#58

D#59

D#60

D#61

D#62

D#63

12

R50

47K_0402_5%

3 1

H_D#[0..63] 8H_A#[3..31]8

2

B

+5VS+5VS

12

R51

47K_0402_5%

1

C

Q9

2SC2411K_SC59

E

3

H_BOOTSELECT 43

CHECK WITH Power Team

H_D#0

B21

D#0

H_D#1

B22

D#1

H_D#2

A23

D#2

H_D#3

A25

D#3

H_D#4

C21

D#4

H_D#5

D22

D#5

H_D#6

B24

D#6

H_D#7

C23

D#7

H_D#8

C24

D#8

H_D#9

B25

D#9

H_D#10

G22

H_D#11

H21

H_D#12

C26

H_D#13

D23

H_D#14

J21

H_D#15

D25

H_D#16

H22

H_D#17

E24

H_D#18

G23

H_D#19

F23

H_D#20

F24

H_D#21

E25

H_D#22

F26

H_D#23

D26

H_D#24

L21

H_D#25

G26

H_D#26

H24

H_D#27

M21

H_D#28

L22

H_D#29

J24

H_D#30

K23

H_D#31

H25

H_D#32

M23

H_D#33

N22

H_D#34

P21

H_D#35

M24

H_D#36

N23

H_D#37

M26

H_D#38

N26

H_D#39

N25

H_D#40

R21

H_D#41

P24

H_D#42

R25

H_D#43

R24

H_D#44

T26

H_D#45

T25

H_D#46

T22

H_D#47

T23

H_D#48

U26

H_D#49

U24

H_D#50

U23

H_D#51

V25

H_D#52

U21

H_D#53

V22

H_D#54

V24

H_D#55

W26

H_D#56

Y26

H_D#57

W25

H_D#58

Y23

H_D#59

Y24

H_D#60

Y21

H_D#61

AA25

H_D#62

AA22

H_D#63

AA24

2

Q10

MMBT3904_SOT23

JP25A

VCC_0

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6A8VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56B7VCC_57B9VCC_58

VCC_59

VCC_61

VCC_62

VCC_63

AD4

VSS_54

AD8

VSS_55

AD1

12

BOOTSELECT

VCC_81

F13

R53

100K_0402_5%

VCC_64

VCC_82

VCC_83

F15

F17

F19

R52 22K_0402_5%

K2

A#3

K4

A#4

L6

A#5

K1

A#6

L3

A#7

M6

A#8

L2

A#9

M3

A#10

M4

A#11

N1

A#12

M1

A#13

N2

A#14

N4

A#15

N5

A#16

T1

A#17

R2

A#18

P3

A#19

P4

A#20

R3

A#21

T2

A#22

U1

A#23

P6

A#24

U3

A#25

T4

A#26

V2

A#27

R6

A#28

W1

A#29

T5

A#30

U4

A#31

V3

A#32

W2

A#33

Y1

A#34

AB1

A#35

J1

REQ#0

K5

REQ#1

J4

REQ#2

J3

REQ#3

H3

REQ#4

G1

ADS#

AC1

AP#0

V5

AP#1

AA3

BINIT#

AC3

IERR#

H6

BR0#

D2

BPRI#

G2

BNR#

G4

LOCK#

BCLK0

BCLK1

F3

HIT#

E3

HITM#

E2

DEFER#

VSS_0H1VSS_1H4VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12A3VSS_13A9VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

A11

A13

A15

A17

A19

A21

A24

H23

H26

A26

AA1

AA4

AA11

AA13

AA15

AA17

AA19

AA23

AA26

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

AA7

AA9

AB10

AB12

AB14

AB16

Prescott

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

AB3

AB6

AB8

AB18

AB20

AB21

AB24

AC11

AC13

AC15

AC17

AC19

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

AC2

AC5

AC7

AC9

AC22

AC25

AD10

AD12

AD14

AD16

AD18

AD21

AD23

A A

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Prescott Processor in uFCPGA478

LA-2251

1

447Monday, May 17, 2004

1.0

of

Page 5

5

+CPU_CORE

56_0402_5%

R18

R20

R21

D D

R22

R23

C C

B B

+CPU_CORE

+CPU_CORE

A A

H_FERR#

1 2

56_0402_5%

H_THERMTRIP#

1 2

62_0402_5%

H_PROCHOT#

1 2

51_0402_5%

H_PWRGOOD

1 2

56_0402_5%

H_RESET#

1 2

+CPU_CORE

L1 LQG21F4R7N00_0805

1 2

1 2

L2 LQG21F4R7N00_0805

PLL Layout note :

1.Place cap within 600 mils of

the VCCA and VSSA pins.

2.H_VCCIOPLL,HVCCA,HVSSA trace wide

12 mils(min)

R36

54.9_0603_1%

ITP_TDO

1 2

If CPU is P4 , Change the resistor

R546 value to 75_0603_1%

R38

54.9_0603_1%

ITP_DBRESET#

1 2

Close to the ITP

R39

47_0402_5%

If CPU is P4 , Change the resistor

R550 value to 39_0402_5%

1 2

150_0402_5%

If CPU is P4 , Change the resistor

R556 value to 27.4_0402_5%

R45 47_0402_5%

ITP_TMS

12

R43

ITP_TDI

ITP_TCK

12

Place near SB200 (U6)

Place near CPU

R22-->62ohm for Prescott C-step Processor

+CPU_CORE

Note: Please change to 10uH, DC current

of 100mA parts and close to cap

33U_D2_8M_R35

C71

H_RS#[0..2]8

H_TRDY#8

H_A20M#18

H_FERR#18

H_IGNNE#18

H_PWRGOOD8

H_STPCLK#18

H_INIT#18

H_RESET#8

H_DBSY#8

H_DRDY#8

BSEL012

BSEL112

H_THERMDA7

H_THERMDC7

H_THERMTRIP#7,18

R29 56_0402_5%

1 2

R30 56_0402_5%

1 2

1 8

2 7

3 6

4 5

RP2 56_0804_8P4R_5%

1

1

C72

+

+

2

2

33U_D2_8M_R35

H_SMI#18

H_INTR18

H_NMI18

H_VCCA

VCCSENSE43

VSSSENSE43

+1.2V

H_VSSA

R31

CK_ITP12

CK_ITP#12

R32

51.1_0402_1%

If CPU is P4 , Change the

resistor R32,R33 value to

51.1_0603_1%,or prescott

61.9_0603_1%

Close to the CPU

R47

1 2

680_0603_5%

Between the CPU and ITP

ITP_TRST#

5

H_RS#0

H_RS#1

H_RS#2

H_FERR#

H_PWRGOOD

H_RESET#

H_THERMDA

H_THERMDC

H_THERMTRIP#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_TCK

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

1 2

0_0402_5%

12

12

CPUCLK_STP#12,18,43

4

CK_ITP

CK_ITP#

COMP0

COMP1

R33

51.1_0402_1%

4

AB23

AB25

AD20

AE23

AD22

AC26

AD26

AB2

AD6

AD5

AC6

AB5

AC4

AA5

AB4

AF3

F1

G5

F4

J6

C6

B6

B2

B5

Y4

D1

E5

W5

H5

H2

B3

C4

A2

Y6

D4

C1

D5

F7

E6

A5

A4

L24

P1

JP25B

RS#0

RS#1

RS#2

RSP#

TRDY#

A20M#

FERR#

IGNNE#

SMI#

PWRGOOD

STPCLK#

LINT0

LINT1

INIT#

RESET#

DBSY#

DRDY#

BSEL0

BSEL1

THERMDA

THERMDC

THERMTRIP#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

TCK

TDI

TDO

TMS

TRST#

VCCIOPLL

VCCA

VCCSENSE

VSSSENSE

VCCVIDLB

VSSA

ITP_CLK0

ITP_CLK1

COMP0

COMP1

R539

1 2

12K_0402_5%

AE11

AE13

AE15

AE17

VSS_57

VSS_58

VSS_59

VSS_129F8VSS_130

VSS_131

G21

G24

R40

4.7K_0402_5%

2

AE19

AE22

AE24

VSS_60

VSS_61

VSS_62

VSS_132G3VSS_133G6VSS_134J2VSS_135

J22

+3VS

12

3 1

AE7

AE9

AF1

AF10

AF12

VSS_63

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_136

VSS_137J5VSS_138

VSS_139

VSS_140K3VSS_141K6VSS_142L1VSS_143

J25

K21

K24

VID_PWRGD42,43

Q45

MMBT3904_SOT23

AF14

AF16

VSS_70

VSS_71

2

AF18

AF20

AF6

AF8

B10

VSS_72

VSS_73

VSS_75

VSS_76

VSS_144

VSS_145L4VSS_146M2VSS_147

L23

L26

M22

R37

4.7K_0402_5%

Q8

MMBT3904_SOT23

3 1

B12

B14

VSS_77

VSS_78

VSS_79

VSS_148

VSS_149M5VSS_150

M25

+3VS

CPU_STP#

B16

N21

12

B18

VSS_80

N24

B20

B23

VSS_81

VSS_82

VSS_151

VSS_152N3VSS_153N6VSS_154P2VSS_155

VSS_83

B26

VSS_84

P22

+3VS

2

3

C11

VSS_85B4VSS_86B8VSS_87

VSS_156

P25

12

R35

4.7K_0402_5%

1

O

3

C13

C15

C17

C19

C22

C25

D10

D12

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92C2VSS_93

VSS_94

VSS_95C5VSS_96C7VSS_97C9VSS_98

Prescott

VSS_157P5VSS_158R1VSS_159

VSS_160

VSS_161R4VSS_162

VSS_163

VSS_164T3VSS_165T6VSS_166U2VSS_167

VSS_168

T21

T24

R23

R26

U22

U25

H_VID_PWRGD

13

D

2

G

Q6

Q7

G3I

DTC124EK_SC59

S

2N7002 1N_SOT23

+CPU_CORE

R_A

R_B

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

D14

D16

D18

D20

D21

D24

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106D3VSS_107D6VSS_108D8VSS_109E1VSS_110

VSS_169U5VSS_170V1VSS_171

VSS_172

VSS_173V4VSS_174

VSS_175

VSS_176W3VSS_177W6VSS_178Y2VSS_179

V23

V26

W21

W24

GTL Reference Voltage

Layout note :

12

R44

49.9_0402_1%

12

R46

100_0402_1%

E11

E13

E15

E17

E19

E23

E26

F10

F12

F14

F16

F18

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117E4VSS_118E7VSS_119E9VSS_120

VSS_121

VSS_122

VSS_123

VID0

VID1

VID2

VID3

VSS_180

VSS_181

Y5

Y22

Y25

2

C74

0.1U_0402_10V6K

1

VID4

VIDPWRGD

VID5

AE5

AE4

AE3

AE2

AE1

AD2

AD3

VID0

VID1

VID2

VID3

VID4

VID5

1. +CPU_GTLREF Trace wide

12mils(min),Space 15mils

2. Place R_A and R_B near CPU.

3. Place decoupling cap 220PF near CPU.

+CPU_GTLREF

1

C75

220P_0402_25V8K

2

2

F22

F25

F5

VSS_124

VSS_125F2VSS_126

VSS_127

OPTIMIZED/COMPAT#

AF4

1

2

2

R19 0_0402_5%@

1 2

AF26

VSS_128

SKTOCC#

DP#0

DP#1

DP#2

DP#3

GTLREF0

GTLREF1

GTLREF2

GTLREF3

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

TESTHI8

TESTHI9

TESTHI10

TESTHI11

TESTHI12

DSTBN#0

DSTBN#1

DSTBN#2

DSTBN#3

DSTBP#0

DSTBP#1

DSTBP#2

DSTBP#3

ADSTB#0

ADSTB#1

DBI#0

DBI#1

DBI#2

DBI#3

DBR#

PROCHOT#

MCERR#

SLP#

NC1

NC2

NC3

NC4

NC5

VCCVID

AMP_3-1565030-1_Prescott

+1.2V

C73

0.1U_0402_10V6K

R34 2.43K_0603_1%

1 2

H_VID_PWRGD

J26

K25

+CPU_GTLREF

K26

L25

AA21

AA6

F20

F6

R24 0_0402_5%

AE26

AD24

H_TESTHI0_1

AA2

AC21

AC20

H_TESTHI2_7

AC24

AC23

AA20

AB22

H_TESTHI8

U6

H_TESTHI9

W4

H_TESTHI10

Y3

H_TESTHI11

A6

H_DPSLP#

AD25

H_TESTHI12

E22

K22

R22

W22

F21

J23

P23

W23

L5

R5

E21

G25

P26

V21

ITP_DBRESET#

AE25

H_PROCHOT#

C3

V6

AB26

A22

A7

AF25

AF24

AE21

1

1 2

R25 56_0402_5%

1 2

R573 56_0402_5%

1 2

RP1 56_0804_8P4R_5%

1 8

2 7

3 6

4 5

R27 56_0402_5%

1 2

R28 56_0402_5%

1 2

H_DSTBN#0 8

H_DSTBN#1 8

H_DSTBN#2 8

H_DSTBN#3 8

H_DSTBP#0 8

H_DSTBP#1 8

H_DSTBP#2 8

H_DSTBP#3 8

H_ADSTB#0 8

H_ADSTB#1 8

H_DINV#0 8

H_DINV#1 8

H_DINV#2 8

H_DINV#3 8

H_PROCHOT# 18

H_CPUSLP# 18

+1.2V

VID543

VID443

VID343

VID243

VID143

VID043

Title

Size Document Number Rev

Date: Sheet

+CPU_CORE

CPU_STP#

VID5

R41 1K_0402_5%

1 2

VID4

R42 1K_0402_5%

1 2

VID3

VID2

VID1

VID0

18

27

36

45

RP3 1K_1206_8P4R_5%

Compal Electronics, Inc.

Prescott Processor in uFCPGA478

LA-2251

1

547Monday, May 17, 2004

CPU_GHI# 18

+3VS

of

1.0

Page 6

5

4

3

2

1

+CPU_CORE

1

C23

22U_1206_16V4Z

2

D D

+CPU_CORE

1

C34

22U_1206_16V4Z

2

+CPU_CORE

1

C44

22U_1206_16V4Z

2

C C

+CPU_CORE

1

C46

22U_1206_16V4Z

2

1

C24

22U_1206_16V4Z

2

1

C35

22U_1206_16V4Z

2

1

C45

22U_1206_16V4Z

2

1

C47

22U_1206_16V4Z

2

1

C25

22U_1206_16V4Z

2

1

C36

22U_1206_16V4Z

2

1

C48

22U_1206_16V4Z

2

Place 11 North of Socket(Stuff 6)

1

C26

22U_1206_16V4Z

2

1

C27

22U_1206_16V4Z

2

1

2

Place 12 Inside Socket(Stuff all)

1

C37

22U_1206_16V4Z

2

1

C38

22U_1206_16V4Z

2

1

2

Place 9 South of Socket(Unstuff all)

1

C49

22U_1206_16V4Z

2

1

C50

22U_1206_16V4Z

2

1

2

C28

22U_1206_16V4Z

C39

22U_1206_16V4Z

C51

22U_1206_16V4Z

1

C29

22U_1206_16V4Z

2

1

C40

22U_1206_16V4Z

2

1

C52

22U_1206_16V4Z

2

1

C30

22U_1206_16V4Z

2

1

C41

22U_1206_16V4Z

2

1

C53

22U_1206_16V4Z

2

1

C31

22U_1206_16V4Z

2

1

C42

22U_1206_16V4Z

2

1

C54

22U_1206_16V4Z

2

1

C32

22U_1206_16V4Z

2

1

C43

22U_1206_16V4Z

2

1

C33

22U_1206_16V4Z

2

B B

+CPU_CORE

1

C55

+

470U_D2_2.5VM

2

+CPU_CORE

1

C66

+

470U_D2_2.5VM

2

A A

1

C56

+

470U_D2_2.5VM

2

1

C67

+

470U_D2_2.5VM

2

5

1

C57

+

470U_D2_2.5VM

2

1

C68

+

330U_D2E_2.5VM@

2

1

C58

+

330U_D2E_2.5VM@

2

1

C69

+

470U_D2_2.5VM

2

1

C59

+

470U_D2_2.5VM

2

1

C70

+

470U_D2_2.5VM

2

4

3

Place Inside Socket around the edge

+CPU_CORE

1

C60

0.22U_0603_10V7K

2

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

C61

0.22U_0603_10V7K

2

1

C62

0.22U_0603_10V7K

2

1

C63

0.22U_0603_10V7K

2

2

1

C64

0.22U_0603_10V7K

2

1

C65

0.22U_0603_10V7K

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

CPU Decoupling

LA-2251

1

1.0

of

647Monday, May 17, 2004

Page 7

5

4

3

2

1

Thermal Sensor ADM1032AR

+3VALW

W=15mil

12

R535

0_0402_5%

D D

12

R9

10K_0402_5%@

1

C11

2200P_0402_25V7K

C C

2

+CPU_CORE

2

C10

1

0.1U_0402_16V4Z

W=15mil

1

H_THERMDA

2

H_THERMDC

3

THERM#

R10 300_0402_5%

1 2

H_THERMTRIP#

Note: PLACE C10 CLOSE TO U1.1

L

U1

VDD

D+

ALERT#

DTHERM#4GND

ADM1032AR_SOP8

Address:1001_100X

SCLK

SDATA

H_THERMDA

H_THERMDC

8

7

6

5

C12 1U_0603_10V4Z@

Q3

CBE

2SC2411K_SC59

123

1 2

H_THERMDA 5

H_THERMDC 5

EC_SMC_2 33

EC_SMD_2 33

MAINPWON 37,38,40H_THERMTRIP#5,18

FAN CONN.1FAN CONN. 2

Fan Control circuit Fan Control circuit

+5VS+12VALW

2

C13

0.1U_0402_16V4Z

EN_FAN233

B B

R16

13K_0603_1%

1 2

1

5

U2

1

P

+

3

-

G

LM321MF_SOT23-5

2

C17

1 2

2200P_0603_16V7K@

1 2

R14 7.32K_0603_1%

D3

RB751V_SOD323

6

2

1

D

Q4

G

FAN2_ON FAN1_ON

3

4

O

2 1

S

SI3456DV-T1_TSOP6

4 5

0.001U_0402_50V7M@

FAN2_VOUT

FANSPEED233

1

C19

10U_0805_10V4Z

2

1

C15

2

C21

0.001U_0402_50V7M

+3VS

12

1

2

R12

10K_0402_5%

JP27

1

2

3

MOLEX_53398-0390

EN_FAN133

13K_0603_1%

0.1U_0402_16V4Z

R17

C14

1 2

2

1

5

U3

1

P

+

O

3

-

G

LM321MF_SOT23-5

2

C18

1 2

2200P_0603_16V7K@

1 2

R15 7.32K_0603_1%

D4

RB751V_SOD323

4

2 1

3

1

G

+5VS+12VALW

6

2

D

S

4 5

FAN1_VOUT

1

C20

10U_0805_10V4Z

2

Q5

SI3456DV-T1_TSOP6

0.001U_0402_50V7M@

FANSPEED133

0.001U_0402_50V7M

+3VS

1

12

C16

R13

10K_0402_5%

2

C22

1

2

JP28

1

2

3

MOLEX_53398-0390

A A

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

CPU Thermal Sensor&FAN CTRL

LA-2251

1

747Monday, May 17, 2004

1.0

of

Page 8

5

4

3

2

1

ZCLK0

10_0402_5%@

ZDREQ

ZUREQ

ZSTB#0

ZSTB0

ZSTB#1

ZSTB1

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZAD16

ZVREF

ZCMP_P

ZCMP_N

Z4XAVDD

Z4XAVSS

ZAD[0..16]

R498

12

U18D

AL6

ZCLK

AK5

ZDREQ

AL4

ZUREQ

AJ3

ZSTB0#

AJ2

ZSTB0

AF2

ZSTB1#

AE3

ZSTB1

AH5

ZAD0

AK2

ZAD1

AJ4

ZAD2

AJ6

ZAD3

AH2

ZAD4

AH4

ZAD5

AG3

ZAD6

AG6

ZAD7

AF4

ZAD8

AG2

ZAD9

AF5

ZAD10

AG4

ZAD11

AD2

ZAD12

AE6

ZAD13

AE2

ZAD14

AE4

ZAD15

AL3

ZAD16

AK4

ZVREF

AD4

ZCOMP_P

AD5

ZCOMP_N

AN1

Z1XAVDD

AM2

Z1XAVSS

AL2

Z4XAVDD

AL1

Z4XAVSS

D4

NC_0

D5

NC_1

AM5

NC_2

E11

NC_3

F11

NC_4

F13

NC_5

AL33

NC_6

AM34

NC_7

A9

NC_8

SISM661FX_BGA839

M661FX

MuTIOL

POWER

AUX_IVDD

AUX3.3

IVDD_0

IVDD_1

IVDD_2

IVDD_3

IVDD_4

IVDD_5

IVDD_6

IVDD_7

IVDD_8

IVDD_9

IVDD_10

IVDD_11

IVDD_12

IVDD_13

IVDD_14

IVDD_15

IVDD_16

IVDD_17

IVDD_18

IVDD_19

IVDD_20

IVDD_21

IVDD_22

IVDD_23

IVDD_24

IVDD_25

IVDD_26

IVDD_27

IVDD_28

IVDD_29

IVDD_30

IVDD_31

PVDD_0

PVDD_1

PVDD_2

PVDD_3

PVDD_4

PVDD_5

PVDD_6

PVDD_7

PVDD_8

VDDZ_0

VDDZ_1

VDDZ_2

VDDZ_3

VDDZ_4

VDDZ_5

VDDZ_6

VDDZ_7

VDDZ_8

VDDZ_9

VDDZ_10

VDDZ_11

VDDZ_12

VDD3.3_0

VDD3.3_1

VDD3.3_2

AB12

AC12

N13

N14

N16

N18

N19

N21

N23

N24

P13

P24

T24

V24

W13

Y24

AA24

AB13

AC24

AD13

AD15

AD17

AD19

AD21

AD23

AD24

R13

U13

AA13

B16

C16

D16

E16

F15

N22

N20

R24

T13

U24

V13

W24

Y13

N15

AH3

AJ1

AK3

AM3

W11

W12

Y11

Y12

AA12

AD3

AE1

AF3

AG1

L17

M17

N17

+1.8VALW

+3VALW

+1.8VS

+1.8VS

+1.8VS

+3VS

+3VS

661 solder side

+1.8VS

+1.8VS

661 solder side

VDD3.3

C338 0.1U_0402_16V7K

1 2

C339 0.1U_0402_16V7K

1 2

C340 0.1U_0402_16V7K@

1 2

C341 0.1U_0402_16V7K@

1 2

IVDD

C342 0.1U_0402_16V7K

1 2

C343 0.1U_0402_16V7K

1 2

C344 0.1U_0402_16V7K

1 2

C628 10U_0805_10V4Z

1 2

C346 0.1U_0402_16V7K

1 2

C347 0.1U_0402_16V7K

1 2

C348 0.1U_0402_16V7K

1 2

C349 0.1U_0402_16V7K

1 2

C351 0.1U_0402_16V7K

1 2

PVDD/VDDZ

C352 0.1U_0402_16V7K

1 2

C629 10U_0805_10V4Z

1 2

C630 1U_0603_10V4Z

1 2

C353 0.1U_0402_16V7K

1 2

C354 0.1U_0402_16V7K

1 2

C355 0.1U_0402_16V7K

1 2

U18A

AA34

HA3#

Y32

HA4#

AA31

HA5#

AA35

HA6#

AB33

HA7#

AB32

HA8#

AB35

HA9#

AC34

HA10#

AC31

HA11#

AD35

HA12#

AC35

HA13#

AD33

HA14#

AD32

HA15#

AC33

HA16#

AG34

HA17#

AF33

HA18#

AE34

HA19#

AE33

HA20#

AE35

HA21#

AF35

HA22#

AH35

HA23#

AE31

HA24#

AG35

HA25#

AH32

HA26#

AJ34

HA27#

AF32

HA28#

AJ35

HA29#

AG33

HA30#

AH33

HA31#

Y35

HREQ0#

W33

HREQ1#

W31

HREQ2#

Y33

HREQ3#

W35

HREQ4#

AG31

HASTB1#

AA33

HASTB0#

AJ31

CPUCLK

AJ33

CPUCLK#

V35

ADS#

V33

BNR#

U31

BREQ0#

R34

BPRI#

F22

CPUPWRGD

U33

DBSY#

T35

DEFER#

R36

DPWR#

W34

DRDY#

U34

HIT#

R35

HITM#

T33

HLOCK#

V32

HTRDY#

U35

RS#0

T32

RS#1

R33

RS#2

AA26

HVREF0

W26

HVREF1

U26

HVREF2

R26

HVREF3

L20

HVREF4

B22

HCOMPVREF_N

D22

HCOMP_P

C22

HCOMP_N

B23

CPURST#

SISM661FX_BGA839

M661FX

HOST

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

DBI0#

DBI1#

DBI2#

DBI3#

P35

N35

N34

L34

P33

P32

M33

M35

L35

K35

L33

L31

K33

N33

K32

J35

H33

G35

J31

J33

F35

H35

G34

J34

F32

E35

D34

E33

F33

C35

G31

D35

D33

D31

E31

B34

D32

B35

B33

C33

D29

C32

B31

B30

C30

B29

F28

E29

B28

C28

D28

B27

E27

D26

D27

B26

B25

C26

F24

D25

D23

B24

E23

C24

M32

H32

D30

E25

N31

G33

F30

D24

R31

E34

B32

F26

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

+1.8VS

H_DSTBP#0 5

H_DSTBP#1 5

H_DSTBP#2 5

H_DSTBP#3 5

H_DSTBN#0 5

H_DSTBN#1 5

H_DSTBN#2 5

H_DSTBN#3 5

1 2

14_0402_1%

1 2

100_0402_1%

H_DINV#[0..3]

H_D#[0..63]

H_A#[3..31]

H_REQ#[0..4]

HNCOMP

Rds-on(n) = 10 ohm

HNCVERF = 1/3 VCCP

HPCOMP

Rds-on(p) = 56 ohm

HPCVERF = 2/3 VCCP

H_ADSTB#15

H_ADSTB#05

CLK_NB_BCLK12

CLK_NB_BCLK#12

H_ADS#4

H_BNR#4

H_BR0#4

H_BPRI#4

H_DBSY#5

H_DEFER#4

H_DRDY#5

H_HIT#4

H_HITM#4

H_LOCK#4

H_TRDY#5

H_RS#05

H_RS#15

H_RS#25

H_RESET#5

H_DINV#[0..3]5

H_D#[0..63]4

D D

C C

B B

H_A#[3..31]4

H_REQ#[0..4]4

+CPU_CORE

R199

R200

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#1

H_ADSTB#0

CLK_NB_BCLK

CLK_NB_BCLK#

H_ADS#

H_BNR#

H_BR0#

H_BPRI#

H_PWRGOOD_NB

H_DBSY#

H_DEFER#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_RS#0

H_RS#1

H_RS#2

HVREF

HNCVREF

HPCOMP

HNCOMP

H_RESET#

12

R201

150_0402_1%

12

R203

51_0402_5%

C677

12

15P_0402_50V8J@

ZAD[0..16]18

ZCLK012

ZDREQ18

ZUREQ18

ZSTB#018

ZSTB018

ZSTB#118

ZSTB118

1

C345

0.1U_0402_16V7K

2

1

C350

0.1U_0402_16V7K

2

+CPU_CORE +CPU_CORE+3VALW

12

R532

470_0402_5%@

H_PWRGOOD_SB18

A A

H_PWRGOOD5

5

12

R533

1K_0402_5%@

Reserve for Prescott C-step Processor

2

G

1 3

Q44

D

S

2N7002_SOT23@

R534 0_0402_5%

1 2

H_PWRGOOD_NB

4

12

R205

75_0402_1%

12

R208

150_0402_1%

1

C356

0.01U_0402_16V7K

2

1

C361

2

0.01U_0402_16V7K

place this capacitor

under 660FX solder side

HVREF

1

C362

0.1U_0402_16V7K

2

12

R206

150_0402_1%

12

R209

75_0402_1%

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

1

C357

0.01U_0402_16V7K

2

1

C363

0.01U_0402_16V7K

2

HNCVREF

+1.8VS

1

2

+3VS

1

2

L23

1 2

0_0603_5%

C358

10U_0805_10V4Z

L24

1 2

0_0603_5%

C364

4.7U_0805_10V4Z

1

C359

2

0.1U_0402_16V7K

1

C365

2

0.1U_0402_16V7K

2

R204 56_0402_5%

1 2

1

C360

0.01U_0402_16V7K

2

R207 56_0402_5%

1 2

Z4XAVDD

1

C366

0.01U_0402_16V7K

2

Z4XAVSS

Title

Size Document Number Rev

Date: Sheet

ZCMP_N

ZCMP_P

Compal Electronics, Inc.

M661FX-1 (HOST/HyperZip/Powers)

LA-2251

1

1.0

of

847Monday, May 17, 2004

Page 9

5

4

3

2

1

RSYNC

C369

C372

L28

1 2

0_0603_5%

LSYNC

CSYNC VB

RSYNC

LSYNC

CSYNC

ENTEST

PM_PWRGD

EC_RSMRST#

VVBWN

VCOMP

DACAVDD

DACAVSS

+3VS

1

C383

4.7U_0805_10V4Z

2

D D

VAD[0..11]16

VBD[0..11]16

VBCTL[0..1]16

VAD[0..11]

VBD[0..11]

VBCTL[0..1]

C30~C34 is noise issue(Optional Use)

VAD10

VAD11

12

R528

1

C697

2

VAVSYNC

VAHSYNC

VBD11

VBD10

VBCTL0

VBCTL1

VBHSYNC

VBVSYNC

12

AGCLK

BGCLK

BCAD

BHCLK

CLK_AGP_66M

10_0402_5%@

15P_0402_50V8J@

VADE

VBDE

VADE16

VAVSYNC16

VAHSYNC16

VBDE16

VBHSYNC16

VBVSYNC16

C C

B B

A A

C718

15P_0402_50V8J

VAGCLK16

VBGCLK16

VBHCLK16

CLK_AGP_66M12

VBCLK16

R566

12

12_0402_5%

R216

1 2

10_0402_5%

R217

1 2

10_0402_5%

R218

R221

1 2

0_0402_5%

1 2

0_0402_5%

VBCAD16

VBD7

VBD6

VBD5

VBD4

VBD3

VBD2

VBD1

VBD0

VAD6

VAD5

VAD4

VAD7

VAD8

VAD9

VBD8

VBD9

VAD1

VAD0

VAD2

VAD3

U18C

Y5

AAD0/VBD7

W4

AAD1/VBD6

V2

AAD2/VBD5

W6

AAD3/VBD4

V4

AAD4/VBD3

U2

AAD5/VBD2

V5

AAD6/VBD1

U4

AAD7/VBD0

R2

AAD8/VAD6

T4

AAD9/VAD5

R3

AAD10/VAD4

T5

AAD11/VAD7

P2

AAD12/VAD8

R4

AAD13/VAD9

N2

AAD14/VAD10

R6

AAD15/VAD11

L3

AAD16/VADE

L4

AAD17/VAVSYNC

K2

AAD18/VAHSYNC

L6

AAD19/VBD11

J2

AAD20/VBD10

J3

AAD21/VBD8

K4

AAD22/VBD9

J4

AAD23/VAD1

J6

AAD24/VAD0

H4

AAD25/VAD2

G3

AAD26/VAD3

H5

AAD27/VBDE

F2

AAD28/VBCTL0

G4

AAD29/VBCTL1

E2

AAD30/VBHSYNC

G6

AAD31/VBVSYNC

B3

SBA0/VBCLK

E6

SBA1

B2

SBA2

E4

SBA3

F5

SBA4

D2

SBA5

F4

SBA6

E3

SBA7

C2

SB_STB

D3

SB_STB#

T2

AD_STB0/VAGCLK

U3

AD_STB0#/VAGCLKN

G2

AD_STB1/VBGCLK

H2

AD_STB1#/VBGCLKN

U6

AC/BE0#

P4

AC/BE1#

M5

AC/BE2#

K5

AC/BE3#

C6

AREQ#/VBCAD

E8

AGNT#

N6

AFRAME#

M4

AIRDY#

N4

ATRDY#

L2

ADEVSEL#

P5

ASERR#

M2

ASTOP#

N3

APAR

D7

RBF#/VBHCLK

B4

WBF#/AGPIO2

C7

GC_DET#

B6

ST0

F7

ST1

B5

ST2

C4

ADBIHI/PIPE#

D6

ADBILO

D8

AGPCLK

SISM661FX_BGA839

M661FX

VGAMISC

LVDS/AGP

AGP3.0 = 50 ohm

50_1%

43.75_1%

R224

1 2

49.9_0402_1%

R225

1 2

43.2_0402_1%

AGPRCOMN

AGPRCOMP

VOSCI

ROUT

GOUT

BOUT

HSYNC

VSYNC

VGPIO0

VGPIO1

INTA#

CSYNC

RSYNC

LSYNC

VCOMP

VRSET

VVBWN

DACAVDD1

DACAVSS1

DACAVDD2

DACAVSS2

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

PCIRST#

PWROK

AUXOK

TRAP1

TRAP0

TESTMODE2

TESTMODE1

TESTMODE0

DLLEN#

ENTEST

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

C1XAVDD

C1XAVSS

C4XAVDD

C4XAVSS

AGPCOMP_N

AGPCOMP_P

AGPVREF

AGPVSSREF

+1.8VS

A15

B12

B13

A13

A11

B11

E13

C11

C10

D12

E12

D11

E15

D15

E14

D13

C12

D14

C13

B15

C15

B14

C14

AN2

AM4

AN3

F9

D10

C9

B9

B10

E10

D9

B8

C8

A7

B7

AK34

AL36

AK35

AJ36

Y2

W2

W3

Y4

R499

10_0402_5%@

CSYNC

RSYNC

LSYNC

VCOMP

VRSET

VVBWN

DACAVDD

DACAVSS

DACAVDD

DACAVSS

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

NB_RST#

PM_PWRGD

EC_RSMRST#

ENTEST

A4XAVDD

A4XAVSS

C4XAVDD

C4XAVSS

AGPRCOMN

AGPRCOMP

AVREFGC

1 2

C678

1 2

15P_0402_50V8J@

REFCLK0 12,16

CRT_R 17

CRT_G 17

CRT_B 17

CRT_HSYNC 17

CRT_VSYNC 17

3VDDCCL 17

3VDDCDA 17

PCI_PIRQA# 16,20,23,24

NB_RST# 16,20

PM_PWRGD 18,35

EC_RSMRST# 18,25,33

AVREFGC

C387

0.1U_0402_16V7K

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

300_0402_1%

1

300_0402_1%

2

1

C367

2

0.01U_0402_16V7K

1

C370

2

0.01U_0402_16V7K

+1.8VS

12

R222

12

R223

0.1U_0402_16V7K

L25

1 2

0_0603_5%

1

C368

0.1U_0402_16V7K

2

L26

1 2

0_0603_5%

1

C371

0.1U_0402_16V7K

2

C381

A4XAVSS

+3VS

1

2

4.7U_0805_10V4Z

+3VS

1

2

4.7U_0805_10V4Z

1

1

C382

2

2

0.01U_0402_16V7K

panel link

C375

1 2

0.1U_0402_16V7K

C376

1 2

0.1U_0402_16V7K

0.1U_0402_16V7K

VGA

1

1

1

R210 4.7K_0402_5%

1 2

R211 4.7K_0402_5%@

1 2

R212 4.7K_0402_5%@

1 2

R213 4.7K_0402_5%

1 2

C373 0.1U_0402_16V4Z@

1 2

C374 0.1U_0402_16V4Z

1 2

VRSET

L27

1 2

0_0603_5%

1

1

C378

C377

1U_0603_10V4Z

2

2

C4XAVDDA4XAVDD

1

1

C385

2

2

0.01U_0402_16V7K

C4XAVSS

0.1U_0402_16V7K

C384

+1.8VS

1

C379

10U_0805_10V4Z

2

L29

1 2

0_0603_5%

0

0

0

+3VS

+3VS

1

2

12

R214

130_0402_5%

130 1%

C386

4.7U_0805_10V4Z

Enable Disable

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

M661FX-1 (LVDS/AGP/VGA/MISC)

LA-2251

947Monday, May 17, 2004

1

1.0

of

Page 10

5

4

3

2

1

Note: PLACE CLOSE TO DIMM0,and between NB chip and DIMM0

L

RP48

DDRA_DQ3

1 4

DDRA_DQ4

2 3

DDRA_DQ1

D D

C C

?

B B

A A

DDRA_DQ0

DDRA_DQ6

DDRA_DQ7

DDRA_DQ5

DDRA_DQ2

R241 10_0402_5%

DDRA_DM0

R243 10_0402_5%

DDRA_DQ8

DDRA_DQ13

DDRA_DQ9

DDRA_DQ12

DDRA_DQ10

DDRA_DQ15

DDRA_DQ14

DDRA_DQ11

DDRA_DQS1

R227 10_0402_5%

DDRA_DM1

R228 10_0402_5%

DDRA_DQ20

DDRA_DQ17

DDRA_DQ18

DDRA_DQ21

DDRA_DQ16

DDRA_DQ22

DDRA_DQ19

DDRA_DQ23

DDRA_DM2

R249 10_0402_5%

DDRA_DQS2

R253 10_0402_5%

DDRA_DQ30

DDRA_DQ28

DDRA_DQ31

DDRA_DQ25

DDRA_DQ29

DDRA_DQ24

DDRA_DQ27

DDRA_DQ26

R257 10_0402_5%

R260 10_0402_5%

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

DDRA_SDQ3

DDRA_SDQ4

10_0404_4P2R_5%

RP51

DDRA_SDQ1

DDRA_SDQ0

10_0404_4P2R_5%

RP53

10_0404_4P2R_5%

RP55

DDRA_SDQ5

DDRA_SDQ2

10_0404_4P2R_5%

DDRA_SDQS0DDRA_DQS0

12

DDRA_SDM0

12

RP36

DDRA_SDQ8

DDRA_SDQ13

10_0404_4P2R_5%

RP39

DDRA_SDQ9

DDRA_SDQ12

10_0404_4P2R_5%

RP42

DDRA_SDQ10

DDRA_SDQ15

10_0404_4P2R_5%

RP45

DDRA_SDQ14

DDRA_SDQ11

10_0404_4P2R_5%

DDRA_SDQS1

12

DDRA_SDM1

12

RP57

DDRA_SDQ20

DDRA_SDQ17

10_0404_4P2R_5%

RP59

DDRA_SDQ18

DDRA_SDQ21

10_0404_4P2R_5%

RP61

DDRA_SDQ16

DDRA_SDQ22

10_0404_4P2R_5%

RP63

DDRA_SDQ19

DDRA_SDQ23

10_0404_4P2R_5%

DDRA_SDM2

12

DDRA_SDQS2

12

RP65

DDRA_SDQ30

DDRA_SDQ28

10_0404_4P2R_5%

RP67

DDRA_SDQ31

DDRA_SDQ25

10_0404_4P2R_5%

RP69

DDRA_SDQ29

DDRA_SDQ24

10_0404_4P2R_5%

RP71

DDRA_SDQ27

DDRA_SDQ26

10_0404_4P2R_5%

DDRA_SDQS3DDRA_DQS3

12

DDRA_SDM3DDRA_DM3

12

DDRA_SDQ6

DDRA_SDQ7

DDRA_DQ32

DDRA_DQ36

DDRA_DQ33

DDRA_DQ37

DDRA_DQ34

DDRA_DQ35

DDRA_DQ39

DDRA_DQS4

DDRA_DM4

DDRA_DQ45

DDRA_DQ40

DDRA_DQ42

DDRA_DQ41

DDRA_DQ43

DDRA_DQ44

DDRA_DQ46

DDRA_DQS5

DDRA_DM5

DDRA_DQ54 DDRA_SDQ54

DDRA_DQ49 DDRA_SDQ49

DDRA_DQ50 DDRA_SDQ50

DDRA_DQ55

DDRA_DQ51

DDRA_DQ52

DDRA_DQS6

DDRA_DM6 DDRA_SDM6

DDRA_DQ56 DDRA_SDQ56

DDRA_DQ62

DDRA_DQ61 DDRA_SDQ61

DDRA_DQ63

DDRA_DQ60 DDRA_SDQ60

DDRA_DQ59

DDRA_DQ57

DDRA_DQS7

DDRA_DM7

RP35

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

R226 10_0402_5%

R229 10_0402_5%

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

R242 10_0402_5%

R244 10_0402_5%

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

R258 10_0402_5%

R261 10_0402_5%

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

R250 10_0402_5%

R254 10_0402_5%

DDRA_SDQ32

DDRA_SDQ36

10_0404_4P2R_5%

RP38

DDRA_SDQ33

DDRA_SDQ37

10_0404_4P2R_5%

RP41

DDRA_SDQ38DDRA_DQ38

DDRA_SDQ34

10_0404_4P2R_5%

RP44

DDRA_SDQ35

DDRA_SDQ39

10_0404_4P2R_5%

DDRA_SDQS4

12

DDRA_SDM4

12

RP49

DDRA_SDQ45

DDRA_SDQ40

10_0404_4P2R_5%

RP52

DDRA_SDQ42

DDRA_SDQ41

10_0404_4P2R_5%

RP54

DDRA_SDQ43

DDRA_SDQ44

10_0404_4P2R_5%

RP56

DDRA_SDQ47DDRA_DQ47

DDRA_SDQ46

10_0404_4P2R_5%

DDRA_SDQS5

12

DDRA_SDM5

12

RP66

DDRA_SDQ48DDRA_DQ48

10_0404_4P2R_5%

RP68

DDRA_SDQ53DDRA_DQ53

10_0404_4P2R_5%

RP70

DDRA_SDQ55

10_0404_4P2R_5%

RP72

DDRA_SDQ51

DDRA_SDQ52

10_0404_4P2R_5%

DDRA_SDQS6

12

12

RP58

DDRA_SDQ58DDRA_DQ58

10_0404_4P2R_5%

RP60

DDRA_SDQ62

10_0404_4P2R_5%

RP62

DDRA_SDQ63

10_0404_4P2R_5%

RP64

DDRA_SDQ59

DDRA_SDQ57

10_0404_4P2R_5%

DDRA_SDQS7

12

DDRA_SDM7

12

DDRA_SDM[0..7]

DDRA_SDQ[0..63]

DDRA_SDQS[0..7]

DDRA_SMA[0..15]

DDRA_DQ0

DDRA_DQ1

DDRA_DQ2

DDRA_DQ3

DDRA_DQ4

DDRA_DQ5

DDRA_DQ6

DDRA_DQ7

DDRA_DQ8

DDRA_DQ9

DDRA_DQ10

DDRA_DQ11

DDRA_DQ12

DDRA_DQ13

DDRA_DQ14

DDRA_DQ15

DDRA_DQ16

DDRA_DQ17

DDRA_DQ18

DDRA_DQ19

DDRA_DQ20

DDRA_DQ21

DDRA_DQ22

DDRA_DQ23

DDRA_DQ24

DDRA_DQ25

DDRA_DQ26

DDRA_DQ27

DDRA_DQ28

DDRA_DQ29

DDRA_DQ30

DDRA_DQ31

DDRA_DQ32

DDRA_DQ33

DDRA_DQ34

DDRA_DQ35

DDRA_DQ36

DDRA_DQ37

DDRA_DQ38

DDRA_DQ39

DDRA_DQ40

DDRA_DQ41

DDRA_DQ42

DDRA_DQ43

DDRA_DQ44

DDRA_DQ45

DDRA_DQ46

DDRA_DQ47

DDRA_DQ48

DDRA_DQ49

DDRA_DQ50

DDRA_DQ51

DDRA_DQ52

DDRA_DQ53

DDRA_DQ54

DDRA_DQ55

DDRA_DQ56

DDRA_DQ57

DDRA_DQ58

DDRA_DQ59

DDRA_DQ60

DDRA_DQ61

DDRA_DQ62

DDRA_DQ63

DDRA_DM0

DDRA_DM1

DDRA_DM2

DDRA_DM3

DDRA_DM4

DDRA_DM5

DDRA_DM6

DDRA_DM7

DDRA_SDM[0..7] 14,15

DDRA_SDQ[0..63] 14,15

DDRA_SDQS[0..7] 14,15

DDRA_SMA[0..15] 14,15

U18B

AN35

MD0

AP36

MD1

AK33

MD2

AM33

MD3

AN34

MD4

AK32

MD5

AR34

MD6

AN33

MD7

AM32

MD8

AL31

MD9

AR31

MD10

AL30

MD11

AN32

MD12

AR33

MD13

AN31

MD14

AM31

MD15

AP30

MD16

AR30

MD17

AM29

MD18

AL27

MD19

AN30

MD20

AN29

MD21

AL28

MD22

AN28

MD23

AP26

MD24

AN25

MD25

AR24

MD26

AL24

MD27

AL25

MD28

AR26

MD29

AM25

MD30

AN24

MD31

AN21

MD32

AP20

MD33

AN20

MD34

AL18

MD35

AM21

MD36

AR21

MD37

AL19

MD38

AM19

MD39

AL15

MD40

AL14

MD41

AN15

MD42

AR15

MD43

AN16

MD44

AM15

MD45

AN14

MD46

AL13

MD47

AM13

MD48

AL12

MD49

AL11

MD50

AR12

MD51

AP14

MD52

AR14

MD53

AN13

MD54

AP12

MD55

AL10

MD56

AR11

MD57

AM9

MD58

AR9

MD59

AM11

MD60

AN11

MD61

AP10

MD62

AN9

MD63

AR35

DQM0

AR32

DQM1

AL29

DQM2

AP24

DQM3

AL20

DQM4

AP16

DQM5

AN12

DQM6

AN10

DQM7

SISM661FX_BGA839

40 ohms

DDRCOMN

40 ohms

DDRCOMP

M661FX

MEMORY

R259

1 2

40.2_0402_1%

R264

1 2

40.2_0402_1%

DQS0/CSB0#

DQS1/CSB1#

DQS2/CSB2#

DQS3/CSB3#

DQS4/CSB4#

DQS5/CSB5#

DQS6/CSB6#

DQS7/CSB7#

FWDSDCLKO

DDRCOMP_P

DDRCOMP_N

+2.5V

MA10

MA11

MA12

MA13

MA14

TEST1

SRAS#

SCAS#

SWE#

CS0#

CS1#

CS2#

CS3#

CS4#

CS5#

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

S3AUXSW#

DRAMTEST

DLLAVDD

DLLAVSS

DDRAVDD

DDRAVSS

TRAP2

DDRVREFA

DDRVREFB

DDRVREFB

AR23

MA0

AN23

MA1

AN22

MA2

AM23

MA3

AL23

MA4

AL26

MA5

AN26

MA6

AN27

MA7

AR27

MA8

AR28

MA9

AP22

AN18

AR22

AP28

AM27

AT14

AP34

AP32

AR29

AR25

AR20

AR16

AR13

AR10

AL17

AR19

AN19

AM17

AL16

AN17

AR17

AP18

AR18

AP4

AT3

AR3

AP3

AR2

AN4

AP2

AL21

AL22

AL35

AL34

AM35

AN36

AP1

AF16

AF23

AR8

AP8

0.01U_0402_16V7K

0.01U_0402_16V7K

1

C391

2

1

C396

2

Note: PLACE CLOSE TO DIMM0,and between NB chip and DIMM0

L

DDRA_ADD0

DDRA_ADD1

DDRA_ADD2

DDRA_ADD3

DDRA_ADD4

DDRA_ADD5

DDRA_ADD6

DDRA_ADD7

DDRA_ADD8

DDRA_ADD9

DDRA_ADD10

DDRA_ADD13

DDRA_ADD14

DDRA_ADD11

DDRA_ADD12

DDRA_ADD15

DDRA_DQS0

DDRA_DQS1

DDRA_DQS2

DDRA_DQS3

DDRA_DQS4

DDRA_DQS5

DDRA_DQS6

DDRA_DQS7

DDRA_RAS#

DDRA_CAS#

DDRA_WE#

DDRA_CS#0

DDRA_CS#1

DDRA_CS#2

DDRA_CS#3

DDRA_CKE0

DDRA_CKE1

DDRA_CKE2

DDRA_CKE3

R245 4.7K_0402_5%

S3AUXSW#

ADCLKO

DLLAVDD

DLLAVSS

DDRAVDD

DDRAVSS

DDRVREFA

DDRVREFB

DDRCOMP

DDRCOMN

1 2

R246

1 2

22_0402_5%

+2.5V +2.5V

12

R255

150_0402_1%

12

R262

150_0402_1%

DDRA_RAS# DDR_RAS#

DDRA_WE#

DDRA_CS#0 DDR_CS#0

DDRA_CS#1

DDRA_CS#2

DDRA_CS#3 DDR_CS#3

S3AUXSW# 33

FWDSDCLKO

1

C398

2

0.01U_0402_16V7K

DDRVREFA

0.01U_0402_16V7K

RP34

0_0404_4P2R_5%

RP37

0_0404_4P2R_5%

RP40

0_0404_4P2R_5%

RP43

0_0404_4P2R_5%

RP46

0_0404_4P2R_5%

RP47

0_0404_4P2R_5%

RP50

0_0404_4P2R_5%

RP102

0_0404_4P2R_5%

12

R256

150_0402_1%

12

R263

150_0402_1%

DDRA_SMA13

DDRA_SMA10

DDRA_SMA1

DDRA_SMA3

DDRA_SMA0

DDRA_SMA2

DDRA_SMA5

DDRA_SMA7

DDRA_SMA4

DDRA_SMA6

DDRA_SMA8

DDRA_SMA11

DDRA_SMA9

DDRA_SMA12

DDRA_SMA15DDRA_ADD15

DLLAVDD

0.1U_0402_16V7K

DLLAVSS

DDRAVDD

0.1U_0402_16V7K

DDRAVSS

DDRA_ADD13

DDRA_ADD10

DDRA_ADD1

DDRA_ADD3

DDRA_ADD0

DDRA_ADD2

DDRA_ADD5

DDRA_ADD7

DDRA_ADD4

DDRA_ADD6

DDRA_ADD8

DDRA_ADD11

DDRA_ADD9

DDRA_ADD12

DDRA_ADD14 DDRA_SMA14

10P_0402_50V8J@

1

2

1

2

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

1 4

2 3

R230 0_0402_5%

1 2

R231 0_0402_5%

1 2

R232 0_0402_5%

1 2

R233 0_0402_5%

1 2

R234 0_0402_5%

1 2

R235 0_0402_5%

1 2

R236 0_0402_5%

1 2

R237 0_0402_5%

1 2

R238 0_0402_5%

1 2

R239 0_0402_5%

1 2

R240 0_0402_5%

1 2

+3VALW

FWDSDCLKO 13

C392

C397

DDR_CAS#DDRA_CAS#

DDR_WE#

DDR_CKE0DDRA_CKE0

DDR_CKE1DDRA_CKE1

DDR_CKE2DDRA_CKE2

DDR_CKE3DDRA_CKE3

DDR_CS#1

DDR_CS#2

C388

C393

1

2

0.01U_0402_16V7K

1

2

0.01U_0402_16V7K

DDR_RAS# 14,15

DDR_CAS# 14,15

DDR_WE# 14,15

DDR_CKE0 14,15

DDR_CKE1 14,15

DDR_CKE2 14,15

DDR_CKE3 14,15

DDR_CS#0 14,15

DDR_CS#1 14,15

DDR_CS#2 14,15

DDR_CS#3 14,15

L30

1 2

0_0603_5%

1

C389

2

L31

1 2

0_0603_5%

1

C394

2

+3VS

1

C390

10U_0805_10V4Z

2

+3VS

1

C395

10U_0805_10V4Z

2

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

M661FX-2 (MEMORY for DDR)

LA-2251

10 47Monday, May 17, 2004

1

1.0

of

Page 11

5

+2.5V

D D

C C

+CPU_CORE

B B

U18E

AL7

VDDM_0

AL8

VDDM_1

AL9

VDDM_2

AM6

VDDM_3

AM7

VDDM_4

AM8

VDDM_5

AN5

VDDM_6

AN6

VDDM_7

AN7

VDDM_8

AN8

VDDM_9

AP5

VDDM_10

AP6

VDDM_11

AP7

VDDM_12

AR4

VDDM_13

AR5

VDDM_14

AR6

VDDM_15

AR7

VDDM_16

AT4

VDDM_17

AT5

VDDM_18

AT6

VDDM_19

AT7

VDDM_20

AB25

VDDM_21

AC25

VDDM_22

AD12

VDDM_23

AD25

VDDM_24

AE11

VDDM_25

AE12

VDDM_26

AE13

VDDM_27

AE14

VDDM_28

AE15

VDDM_29

AE16

VDDM_30

AE17

VDDM_31

AE18

VDDM_32

AE19

VDDM_33

AE20

VDDM_34

AE21

VDDM_35

AE22

VDDM_36

AE23

VDDM_37

AE24

VDDM_38

AE25

VDDM_39

AE26

VDDM_40

AF11

VDDM_41

AF12

VDDM_42

AF25

VDDM_43

AF26

VDDM_44

AD22

PVDDM_0

AD20

PVDDM_1

AD18

PVDDM_2

AD16

PVDDM_3

AD14

PVDDM_4

AC13

PVDDM_5

AB24

PVDDM_6

A17

VTT_0

A18

VTT_1

A19

VTT_2

A20

VTT_3

A21

VTT_4

B17

VTT_5

B18

VTT_6

B19

VTT_7

B20

VTT_8

B21

VTT_9

C17

VTT_10

C18

VTT_11

C19

VTT_12

C20

VTT_13

C21

VTT_14

SISM661FX_BGA839

M661FX

POWER

VDDQ_0

VDDQ_1

VDDQ_2

VDDQ_3

VDDQ_4

VDDQ_5

VDDQ_6

VDDQ_7

VDDQ_8

VDDQ_9

VDDQ_10

VDDQ_11

VDDQ_12

VDDQ_13

VDDQ_14

VDDQ_15

VDDQ_16

VDDQ_17

VDDQ_18

VDDQ_19

VDDQ_20

VDDQ_21

VDDQ_22

VDDQ_23

VDDQ_24

VDDQ_25

VDDQ_26

VDDQ_27

VDDQ_28

VDDQ_29

VDDQ_30

VDDQ_31

VDDQ_32

VDDQ_33

VTT_15

VTT_16

VTT_17

VTT_18

VTT_19

VTT_20

VTT_21

VTT_22

VTT_23

VTT_24

VTT_25

VTT_26

VTT_27

VTT_28

VTT_29

VTT_30

VTT_31

VTT_32

VTT_33

VTT_34

VTT_35

VTT_36

VTT_37

VTT_38

VTT_39

VTT_40

VTT_41

VTT_42

VTT_43

VTT_44

VTT_45

VTT_46

VTT_47

VTT_48

VTT_49

AA1

AA2

AA3

AA4

AA5

AA6

AB1

AB2

AB3

AB4

AB5

AB6

AC1

AC2

AC3

AC4

AC5

AC6

L11

L12

L13

M11

M12

M13

M14

M15

M16

N11

N12

P12

R12

T12

U12

V12

D17

D18

D19

D20

D21

E17

E18

E19

E20

E21

F17

F18

F19

F20

F21

L25

L26

M18

M19

M20

M21

M22

M23

M24

M25

M26

N25

P25

R25

T25

U25

V25

W25

Y25

AA25

+1.8VS

+CPU_CORE

4

change to

DPWR# for 660

U18F

A3

VSS_0

A5

VSS_1

C1

VSS_2

C3

VSS_3

C5

VSS_4

E1

VSS_5

E5

VSS_6

E7

VSS_7

E9

VSS_8

F3

VSS_9

G1

VSS_10

G5

VSS_11

H3

VSS_12

J1

VSS_13

J5

VSS_14

K3

VSS_15

L1

VSS_16

L5

VSS_17

M3

VSS_18

N1

VSS_19

N5

VSS_20

P3

VSS_21

R1

VSS_22

R5

VSS_23

T3

VSS_24

U1

VSS_25

U5

VSS_26

V3

VSS_27

W1

VSS_28

W5

VSS_29

Y3

VSS_30

AE5

VSS_31

AG5

VSS_32

AJ5

VSS_33

AL5

VSS_34

A22

VSS_35

A24

VSS_36

A26

VSS_37

A28

VSS_38

A30

VSS_39

A32

VSS_40

A34

VSS_41

C23

VSS_42

C25

VSS_43

C27

VSS_44

C29

VSS_45

C31

VSS_46

C34

VSS_47

C36

VSS_48

E22

VSS_49

E24

VSS_50

E26

VSS_51

E28

VSS_52

E30

VSS_53

E32

VSS_54

E36

VSS_55

F34

VSS_56

G32

VSS_57

G36

VSS_58

H34

VSS_59

J32

VSS_60

J36

VSS_61

K34

VSS_62

L32

VSS_63

L36

VSS_64

M34

VSS_65

N32

VSS_66

N36

VSS_67

P34

VSS_68

R32

VSS_69

T34

VSS_70

U32

VSS_71

U36

VSS_72

V34

VSS_73

SISM661FX_BGA839

3

M661FX

GROUND

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

P14

P15

P16

P17

P18

P19

P20

P21

P22

P23

R14

R15

R16

R17

R18

R19

R20

R21

R22

R23

T14

T15

T16

T17

T18

T19

T20

T21

T22

T23

U14

U15

U16

U17

U18

U19

U20

U21

U22

U23

V14

V15

V16

V17

V18

V19

V20

V21

V22

V23

W14

W15

W16

W17

W18

W19

W20

W21

W22

W23

W32

W36

Y14

Y15

Y16

Y17

Y18

Y19

Y20

Y21

Y22

Y23

Y34

2

U18G

AA14

AA15

AA16

AA17

AA18

AA19

AA20

AA21

AA22

AA23

AA32

AA36

AB34

AB14

AB15

AB16

AB17

AB18

AB19

AB20

AB21

AB22

AB23

AC14

AC15

AC16

AC17

AC18

AC19

AC20

AC21

AC22

AC23

AC32

AC36

AD34

AE32

AE36

AF34

AG32

AG36

+1.8VS

C603 0.1U_0402_16V7K

1 2

C605 0.1U_0402_16V7K

1 2

C607 0.1U_0402_16V7K

1 2

C609 0.1U_0402_16V7K

1 2

Note: Place these capacitors under M661FX solder side

L

M661FX

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_187

SISM661FX_BGA839

VDDQ

GROUND

C602 0.1U_0402_16V7K

1 2

C604 0.1U_0402_16V7K

1 2

C606 0.1U_0402_16V7K

1 2

C608 0.1U_0402_16V7K

1 2

C610 0.1U_0402_16V7K

1 2

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

1

AH34

AJ32

AM10

AM12

AM14

AM16

AM18

AM20

AM22

AM24

AM26

AM28

AM30

AP9

AP11

AP13

AP15

AP17

AP19

AP21

AP23

AP25

AP27

AP29

AP31

AP33

AP35

AT8

AT10

AT12

AT16

AT18

AT20

AT22

AT24

AT26

AT28

AT30

AT32

AT34

AL32

change to

MA15 for

660

+3VALW

C631

10U_0805_10V4Z

C637

1U_0603_10V4Z

C618

0.1U_0402_16V7K

A A

5

1 2

1 2

1 2

AUX3.3

+3VALW

661 solder side

C615

1 2

0.1U_0402_16V7K

C619

1 2

0.1U_0402_16V7K

+CPU_CORE

C635

1 2

10U_0805_10V4Z

C641

1 2

10U_0805_10V4Z

+2.5V +3VALW

C660

1 2

0.1U_0402_16V7K

C659

1 2

0.1U_0402_16V7K

Note: Place these capacitors

L

between the +2.5V and +3VALW

Power Plane .

4

C613

1 2

0.1U_0402_16V7K

C642

1 2

1U_0603_10V4Z

C622

1 2

0.1U_0402_16V7K

C658

1 2

0.1U_0402_16V7K

C657

1 2

0.1U_0402_16V7K

+1.8VALW

C636

1 2

10U_0805_10V4Z

C617

1 2

0.1U_0402_16V7K