Acer Iconia One B1-750 Schematics

5

www.schematic-x.blogspot.com

4

3

2

1

D D

C C

B B

A A

Title

Title

Title

<Title>

<Title>

<Title>

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

<Doc> <RevCode>

A2

<Doc> <RevCode>

A2

<Doc> <RevCode>

A2

5

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

1

1 40Thursday, Augus t 28, 2014

1 40Thursday, Augus t 28, 2014

1 40Thursday, Augus t 28, 2014

5

<RevCode>

<RevCode>

<RevCode>

4

3

2

1

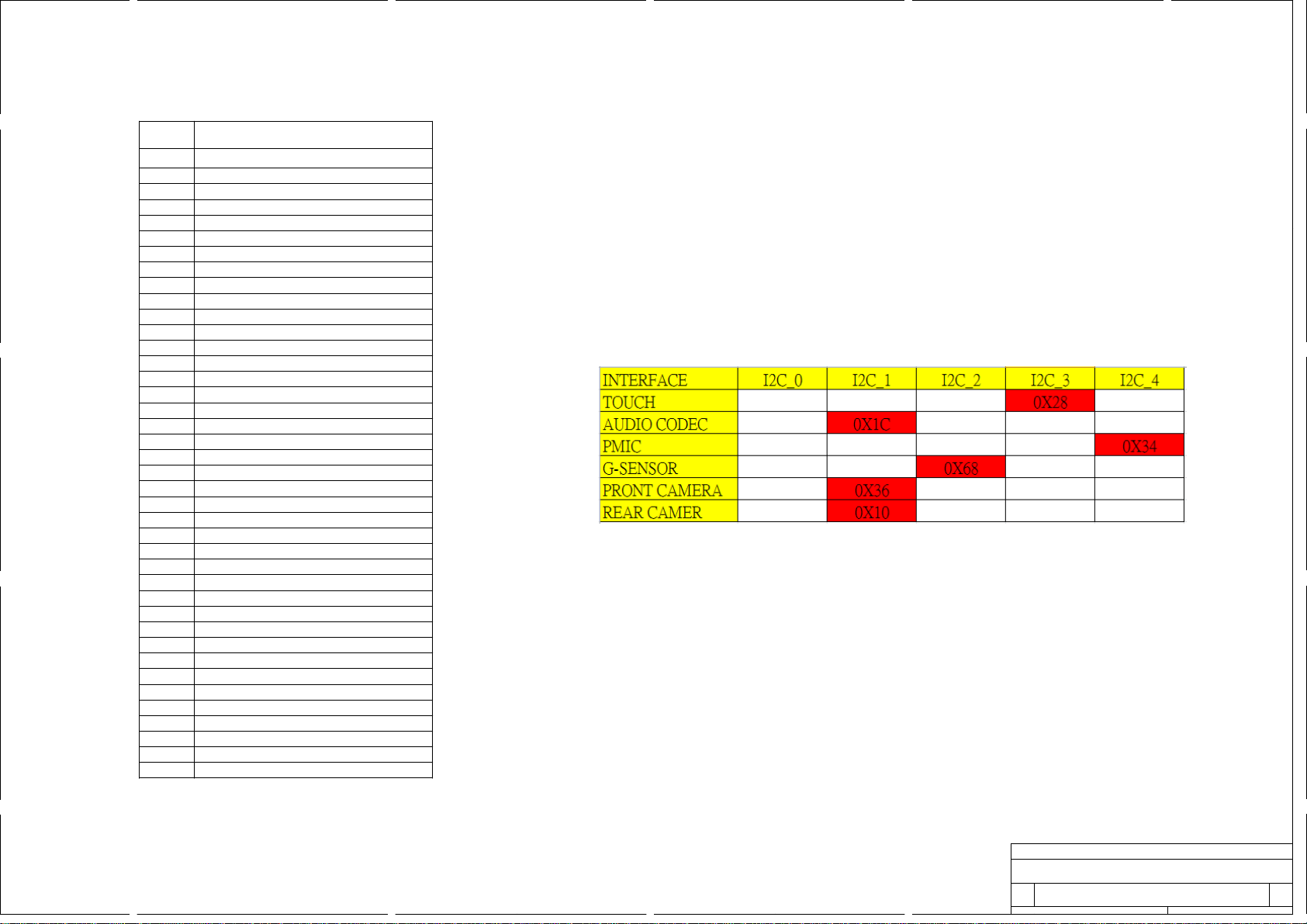

TABLE OF CONTENT & NOTES

TABLE OF CONTENTS

D D

1

2

3

4

5

6

7

8

9

10

11

12

C C

B B

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34 WiFi/BT BCM4330

35 WiFi/BT BCM4330 Power/IO

36

37

38

39

40

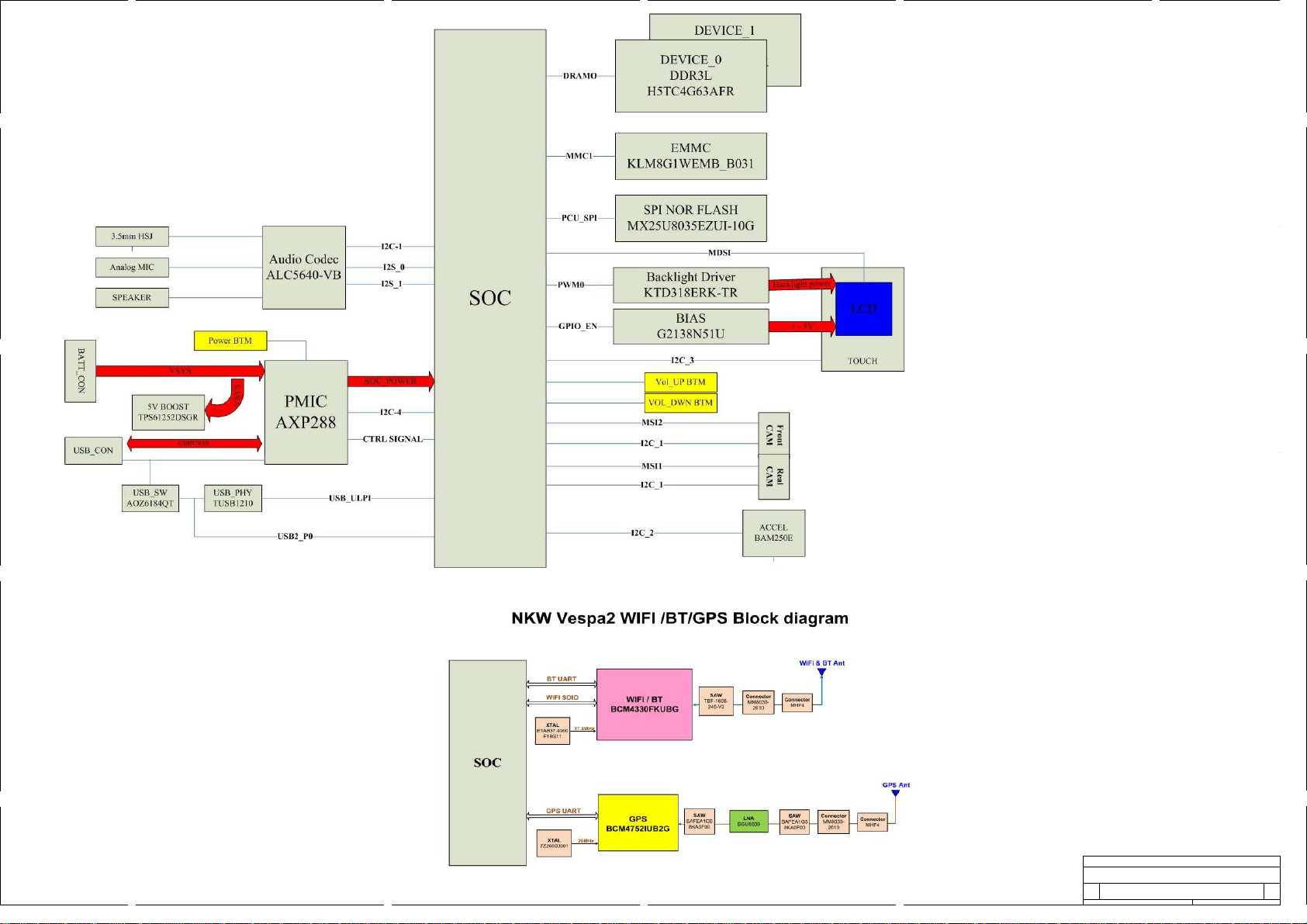

BLOCK DIAGRAM

TABLE OF CONTENT & NOTES

SOC: MEMORY

SOC: DISPLAY & CAMERA

SOC: STORAGE & I2S

SOC: USB & I2C

SOC: PMU/DFX/CLK/UART/SUS

SOC: POWER 1

SOC: POWER 2

SOC: GND

SOC: DECOUPLING

PMIC: SWITCHING REGULATORS

PMIC: LDOS

PMIC: HOST & MISC INTERFACES

PMIC: EXTERNAL REGULATORS

MEMORY DEVICE 0 & 1

USB PHY & MUX

SPI NOR FLASH

EMMC

DISPLAY: BACKLIGHT CONTROLLER & BIAS voltage regulator

DISPLAY & TOUCH CONNECTORS

CAMERAS - FRONT & REAR

SENSORS

AUDIO CODEC

SPEAKERS

HEADSET JACK AND BUTTONS

USB CONNECTOR

MICRO-SD CONNECTOR

BATTERY & DEBUG CONNECTOR

GPS

SAR PROXIMITY SENSOR

MFG TEST POINTS, SHIELDS & MOUNTING HOLES

SHEET NAMESHEET NO.

A A

Title

Title

Title

<Title>

<Title>

<Title>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

<Doc>

A3

<Doc>

A3

<Doc>

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

2 40Thursday, August 28, 2014

2 40Thursday, August 28, 2014

2 40Thursday, August 28, 2014

5

<RevCode>

<RevCode>

<RevCode>

4

3

2

1

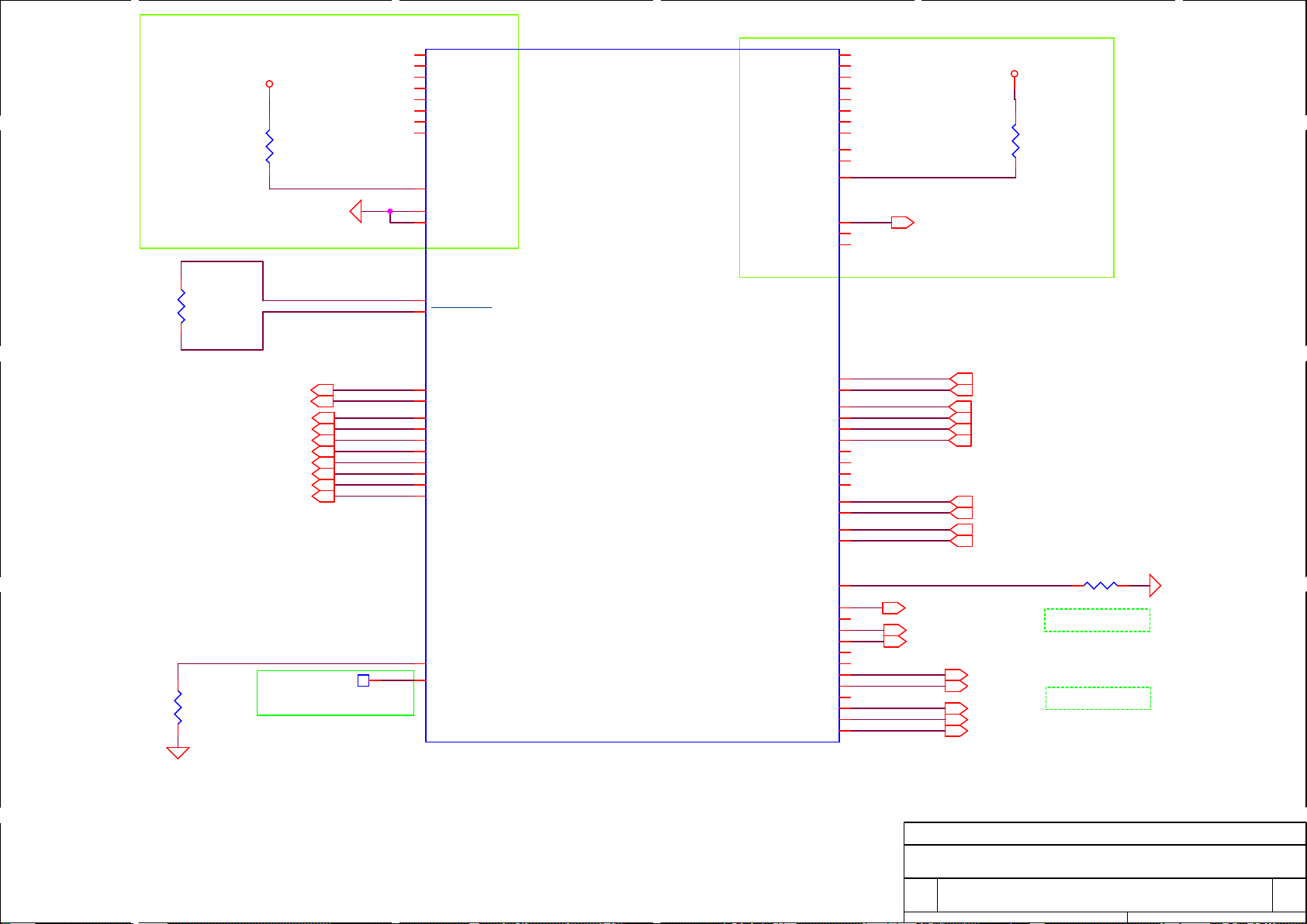

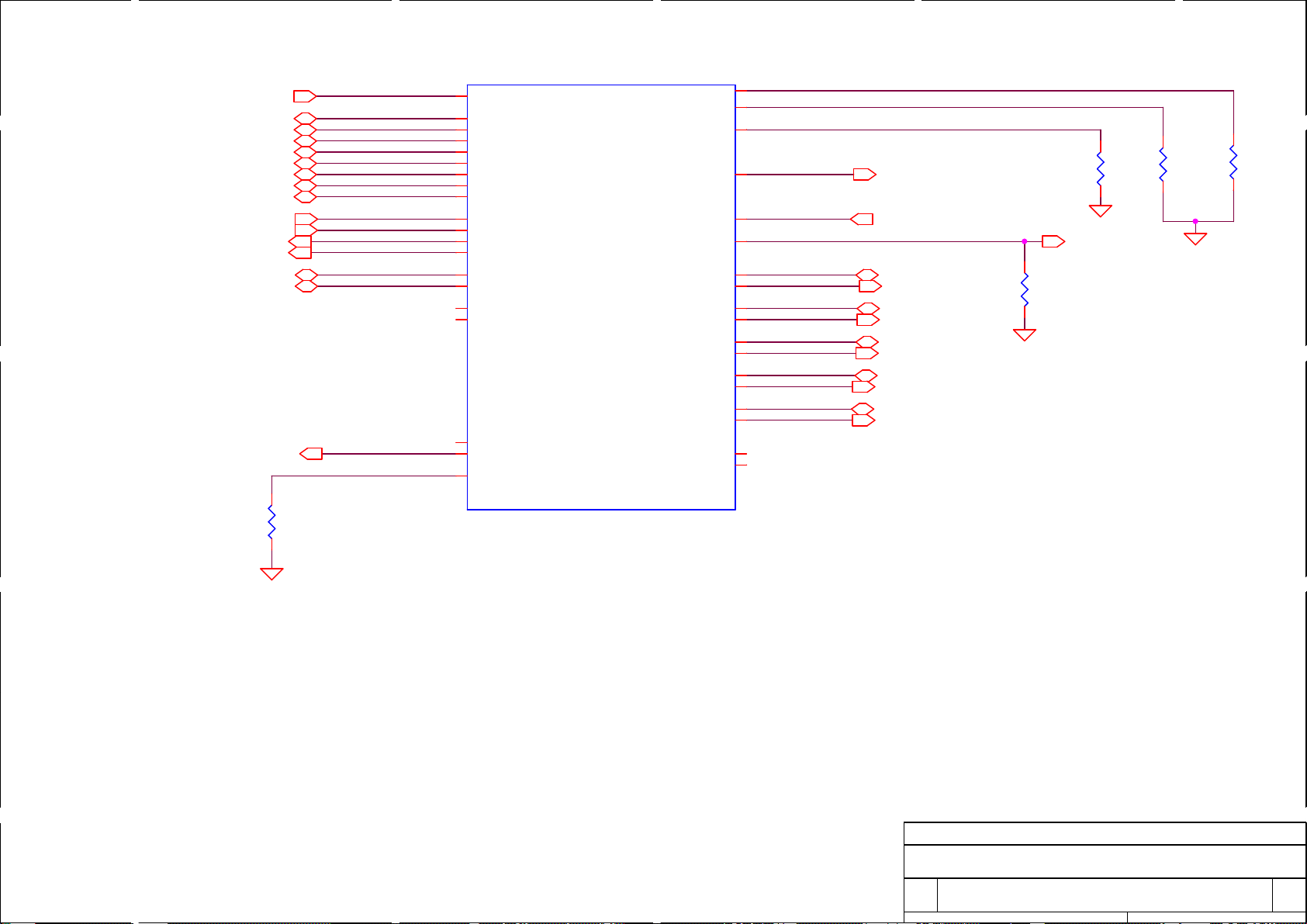

SOC:MEMORY

?

U1000A

O

M0_MA0[16]

O

M0_MA1[16]

O

M0_MA2[16]

O

M0_DRAMRSTB[16]

12

R1012

29.4/F_4

RC0402_S

M0_MA3[16]

O

M0_MA4[16]

O

M0_MA5[16]

O

M0_MA6[16]

O

M0_MA7[16]

O

M0_MA8[16]

O

M0_MA9[16]

O

M0_MA10[16]

O

M0_MA11[16]

O

M0_MA12[16]

O

M0_MA13[16]

O

M0_MA14[16]

O

M0_DM0[16]

O

M0_DM1[16]

O

M0_DM2[16]

O

M0_DM3[16]

O

M0_RASB[16]

O

M0_CASB[16]

O

M0_WEB[16]

O

M0_BS0[16]

O

M0_BS1[16]

O

M0_BS2[16]

O

M0_CS0_B[16]

O

M0_CKE0[16]

O

M0_ODT0[16]

12

R1013

23.2/F_4

RC0402_S

O

O

O

TP1041

TP1042

pad-nku-tp2050np-g

pad-nku-tp2050np-g

I

I

DDR3_SOC_ODTPU

DDR3_SOC_DQPU

DDR3_SOC_CMDPU

1

1

M0_CLK0_DP[16]

M0_CLK0_DN[16]

DRAM_PW ROK[14]

VCCA_PW ROK[14]

D D

C C

+VREF_DDR[13,16]

B B

12

C1011

0.1U/16V/X7R_4

CC0402_S

12

R1011

162/F_4

RC0402_S

M24

DRAM0_MA[00]

L23

DRAM0_MA[01]

N23

DRAM0_MA[02]

M20

DRAM0_MA[03]

M22

DRAM0_MA[04]

L22

DRAM0_MA[05]

K24

DRAM0_MA[06]

N25

DRAM0_MA[07]

J25

DRAM0_MA[08]

H24

DRAM0_MA[09]

N20

DRAM0_MA[10]

K25

DRAM0_MA[11]

M25

DRAM0_MA[12]

M23

DRAM0_MA[13]

H25

DRAM0_MA[14]

K23

DRAM0_MA[15]

A20

DRAM0_DM[0]

D21

DRAM0_DM[1]

D25

DRAM0_DM[2]

F19

DRAM0_DM[3]

AC24

DRAM0_DM[4]

V24

DRAM0_DM[5]

Y22

DRAM0_DM[6]

T23

DRAM0_DM[7]

N22

DRAM0_RAS#

P20

DRAM0_CAS#

P21

DRAM0_WE#

M21

DRAM0_BS[0]

N19

DRAM0_BS[1]

K22

DRAM0_BS[2]

P22

DRAM0_CS[0]#

P23

DRAM0_CS[2]#

G22

DRAM0_CKE[0]

G23

DRAM0_CKE[1]

F23

DRAM0_CKE[2]

F22

DRAM0_CKE[3]

P24

DRAM0_ODT[0]

P25

DRAM0_ODT[2]

J23

DRAM0_CKP[0]

J22

DRAM0_CKN[0]

K20

DRAM0_CKP[2]

K21

DRAM0_CKN[2]

U19

DRAM0_DRAMRST#

AD20

DRAM_VREF

AC20

DRAM_VDD_S4_PWROK

AB20

DRAM_CORE_PWROK

AE22

DRAM_RCOMP[2]

AE20

DRAM_RCOMP[1]

AE21

DRAM_RCOMP[0]

SOC_VLV2_CR_BGA

REV = 2.0

BGA592-INTEL-BAY-TRAIL-T-TEST

1 OF 9

AJSR1UDVT01

DRAM0_DQ[00]

DRAM0_DQ[01]

DRAM0_DQ[02]

DRAM0_DQ[03]

DRAM0_DQ[04]

DRAM0_DQ[05]

DRAM0_DQ[06]

DRAM0_DQ[07]

DRAM0_DQ[08]

DRAM0_DQ[09]

DRAM0_DQ[10]

DRAM0_DQ[11]

DRAM0_DQ[12]

DRAM0_DQ[13]

DRAM0_DQ[14]

DRAM0_DQ[15]

DRAM0_DQ[16]

DRAM0_DQ[17]

DRAM0_DQ[18]

DRAM0_DQ[19]

DRAM0_DQ[20]

DRAM0_DQ[21]

DRAM0_DQ[22]

DRAM0_DQ[23]

DRAM0_DQ[24]

DRAM0_DQ[25]

DRAM0_DQ[26]

DRAM0_DQ[27]

DRAM0_DQ[28]

DRAM0_DQ[29]

DRAM0_DQ[30]

DRAM0_DQ[31]

DRAM0_DQ[32]

DRAM0_DQ[33]

DRAM0_DQ[34]

DRAM0_DQ[35]

DRAM0_DQ[36]

DRAM0_DQ[37]

DRAM0_DQ[38]

DRAM0_DQ[39]

DRAM0_DQ[40]

DRAM0_DQ[41]

DRAM0_DQ[42]

DRAM0_DQ[43]

DRAM0_DQ[44]

DRAM0_DQ[45]

DRAM0_DQ[46]

DRAM0_DQ[47]

DRAM0_DQ[48]

DRAM0_DQ[49]

DRAM0_DQ[50]

DRAM0_DQ[51]

DRAM0_DQ[52]

DRAM0_DQ[53]

DRAM0_DQ[54]

DRAM0_DQ[55]

DRAM0_DQ[56]

DRAM0_DQ[57]

DRAM0_DQ[58]

DRAM0_DQ[59]

DRAM0_DQ[60]

DRAM0_DQ[61]

DRAM0_DQ[62]

DRAM0_DQ[63]

DRAM0_DQSP[0]

DRAM0_DQSN[0]

DRAM0_DQSP[1]

DRAM0_DQSN[1]

DRAM0_DQSP[2]

DRAM0_DQSN[2]

DRAM0_DQSP[3]

DRAM0_DQSN[3]

DRAM0_DQSP[4]

DRAM0_DQSN[4]

DRAM0_DQSP[5]

DRAM0_DQSN[5]

DRAM0_DQSP[6]

DRAM0_DQSN[6]

DRAM0_DQSP[7]

DRAM0_DQSN[7]

D18

B18

A21

C18

A22

B20

A18

B22

C20

D23

E19

E23

D22

E22

E20

D20

E25

A23

C23

F25

B24

D24

B23

F24

F20

F21

G20

H23

G21

J21

J20

H22

AD24

AB25

Y24

AE23

AA25

AC23

AD23

Y25

V23

T24

W22

W23

R23

R22

V22

T25

AB22

AC22

Y19

AD22

AA22

Y23

Y20

Y21

T22

T20

W20

V20

U21

W21

U20

T21

D19

C19

C22

C21

C24

C25

H20

H19

AC25

AB24

V25

U25

AB23

AA23

U22

U23

B

M0_DATA0[16]

B

M0_DATA1[16]

B

M0_DATA2[16]

B

M0_DATA3[16]

B

M0_DATA4[16]

B

M0_DATA5[16]

B

M0_DATA6[16]

B

M0_DATA7[16]

B

M0_DATA8[16]

B

M0_DATA9[16]

B

M0_DATA10[16]

B

M0_DATA11[16]

B

M0_DATA12[16]

B

M0_DATA13[16]

B

M0_DATA14[16]

B

M0_DATA15[16]

B

M0_DATA16[16]

B

M0_DATA17[16]

B

M0_DATA18[16]

B

M0_DATA19[16]

B

M0_DATA20[16]

B

M0_DATA21[16]

B

M0_DATA22[16]

B

M0_DATA23[16]

B

M0_DATA24[16]

B

M0_DATA25[16]

B

M0_DATA26[16]

B

M0_DATA27[16]

B

M0_DATA28[16]

B

M0_DATA29[16]

B

M0_DATA30[16]

B

M0_DATA31[16]

B

M0_DQS0_DP [16]

B

M0_DQS0_DN [16]

B

M0_DQS1_DP [16]

B

M0_DQS1_DN [16]

B

M0_DQS2_DP [16]

B

M0_DQS2_DN [16]

B

M0_DQS3_DP [16]

B

M0_DQS3_DN [16]

A A

Title

Title

Title

<Title>

<Title>

<Title>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

<Doc>

A3

<Doc>

A3

<Doc>

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

3 40Thursday, August 28, 2014

3 40Thursday, August 28, 2014

3 40Thursday, August 28, 2014

5

D

C

B

A

<RevCode>

<RevCode>

<RevCode>

+V1P8A_SOC[4,7,9,11]

D

12

R1018

402/F_4

RC0402_S

12

R9110

10K/F_4

RC0201_S

DDI0_PLLOBS_DP

DDI0_PLLOBS_DN

4

AB4

AB3

AB2

AA1

Y2

Y1

Y4

Y3

E14

D13

C13

AA3

AA4

3

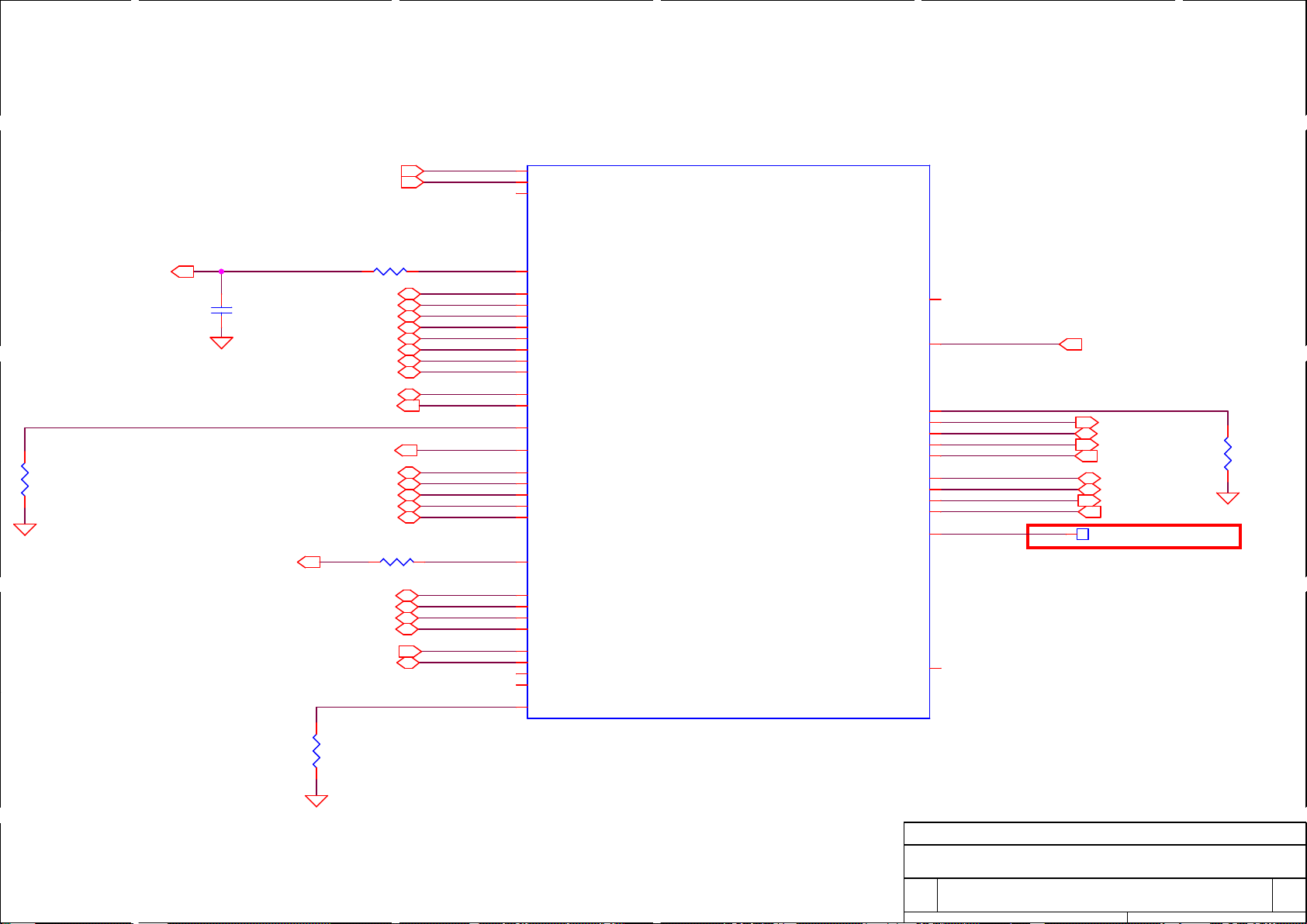

SOC: DISPLAY & CAMERA

?

U1000B

DDI0_TXP[0]

DDI0_TXN[0]

DDI0_TXP[1]

DDI0_TXN[1]

DDI0_TXP[2]

DDI0_TXN[2]

DDI0_TXP[3]

DDI0_TXN[3]

DDI0_HPD

DDI0_DDCDATA

DDI0_DDCCLK

DDI_RCOMP_P

DDI_RCOMP

2 OF 9

DDI1_TXP[0]

DDI1_TXN[0]

DDI1_TXP[1]

DDI1_TXN[1]

DDI1_TXP[2]

DDI1_TXN[2]

DDI1_TXP[3]

DDI1_TXN[3]

DDI1_AUXP

DDI1_AUXN

DDI1_HPD

DDI1_VDDEN

DDI1_BKLTEN

DDI1_BKLTCTL

U7

U6

V5

V4

T1

U1

U4

U5

Y5

W6

B12

B14

A14

A13

2

O

DISP_RSTN [24]

1

+V1P8A_SOC[4,7,9,11]

12

R9109

10K/F_4

RC0201_S

C

MDSI_A_CLK_DN[24]

MDSI_A_CLK_DP[24]

MDSI_A_DATA0_DN[24]

MDSI_A_DATA0_DP[24]

MDSI_A_DATA1_DN[24]

MDSI_A_DATA1_DP[24]

MDSI_A_DATA2_DN[24]

MDSI_A_DATA2_DP[24]

MDSI_A_DATA3_DN[24]

MDSI_A_DATA3_DP[24]

O

O

O

O

O

O

O

O

O

O

P5

MDSI_A_CLKN

P4

MDSI_A_CLKP

T4

MDSI_A_DN[0]

T3

MDSI_A_DP[0]

R4

MDSI_A_DN[1]

R3

MDSI_A_DP[1]

T6

MDSI_A_DN[2]

T5

MDSI_A_DP[2]

P6

MDSI_A_DN[3]

N6

MDSI_A_DP[3]

B

P1

MDSI_RCOMP

F17

1

MDSI_A_TE

SOC_VLV2_CR_BGA

REV = 2.0

BGA592-INTEL-BAY-TRAIL-T-TEST

12

R1016

150/F_4

RC0402_S

MDSI_COMP

TP1036

pad-nku-tp2050np-g

MCSI1_CLKN

MCSI1_CLKP

MCSI1_DN[0]

MCSI1_DP[0]

MCSI1_DN[1]

MCSI1_DP[1]

MCSI1_DN[2]

MCSI1_DP[2]

MCSI1_DN[3]

MCSI1_DP[3]

MCSI2_CLKN

MCSI2_CLKP

MCSI2_DN[0]

MCSI2_DP[0]

MCSI_RCOMP

GPIO_S0_NC[15]

GPIO_S0_NC[16]

GPIO_S0_NC[17]

GPIO_S0_NC[18]

GPIO_S0_NC[19]

GPIO_S0_NC[20]

GPIO_S0_NC[21]

GPIO_S0_NC[22]

GPIO_S0_NC[23]

GPIO_S0_NC[24]

GPIO_S0_NC[25]

GPIO_S0_NC[26]

M5

M6

P3

P2

M1

N1

M4

M3

L3

L4

K4

K5

K6

J6

K1

D17

B16

C15

C14

C17

C16

D16

D15

D14

F18

E17

E16

O

PMIC_USB_EN [15]

O

CAM1_RESET_N[25]

O

CAM2_ID[25]

I

MCSI_1_CLK_DN [25]

I

MCSI_1_CLK_DP [25]

I

MCSI_1_DATA0_DN[25]

I

MCSI_1_DATA0_DP[25]

I

MCSI_1_DATA1_DN[25]

I

MCSI_1_DATA1_DP[25]

I

MCSI_2_CLK_DN [25]

I

MCSI_2_CLK_DP [25]

I

MCSI_2_DATA_DN [25]

I

MCSI_2_DATA_DP[25]

MCSI_COMP

O

CAMERA_1_PD[25]

O

CAMERA_2_PD[25]

O

BT_DEV_WAKE[35]

O

BT_DEV_EN[35]

O

TOUCH_RESET_N [24]

R1017

RC0402_S

1 2

150/F_4

A

Title

Title

Title

<Title>

<Title>

<Title>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

<Doc>

A4

<Doc>

A4

<Doc>

A4

Date: Sheet of

Date: Sheet of

Date: Sheet of

4 40Thursday, August 28, 2014

4 40Thursday, August 28, 2014

4 40Thursday, August 28, 2014

5

D

C

B

A

<RevCode>

<RevCode>

<RevCode>

4

3

2

1

D

C

B

12

R1021

49.9/F_4

RC0201_S

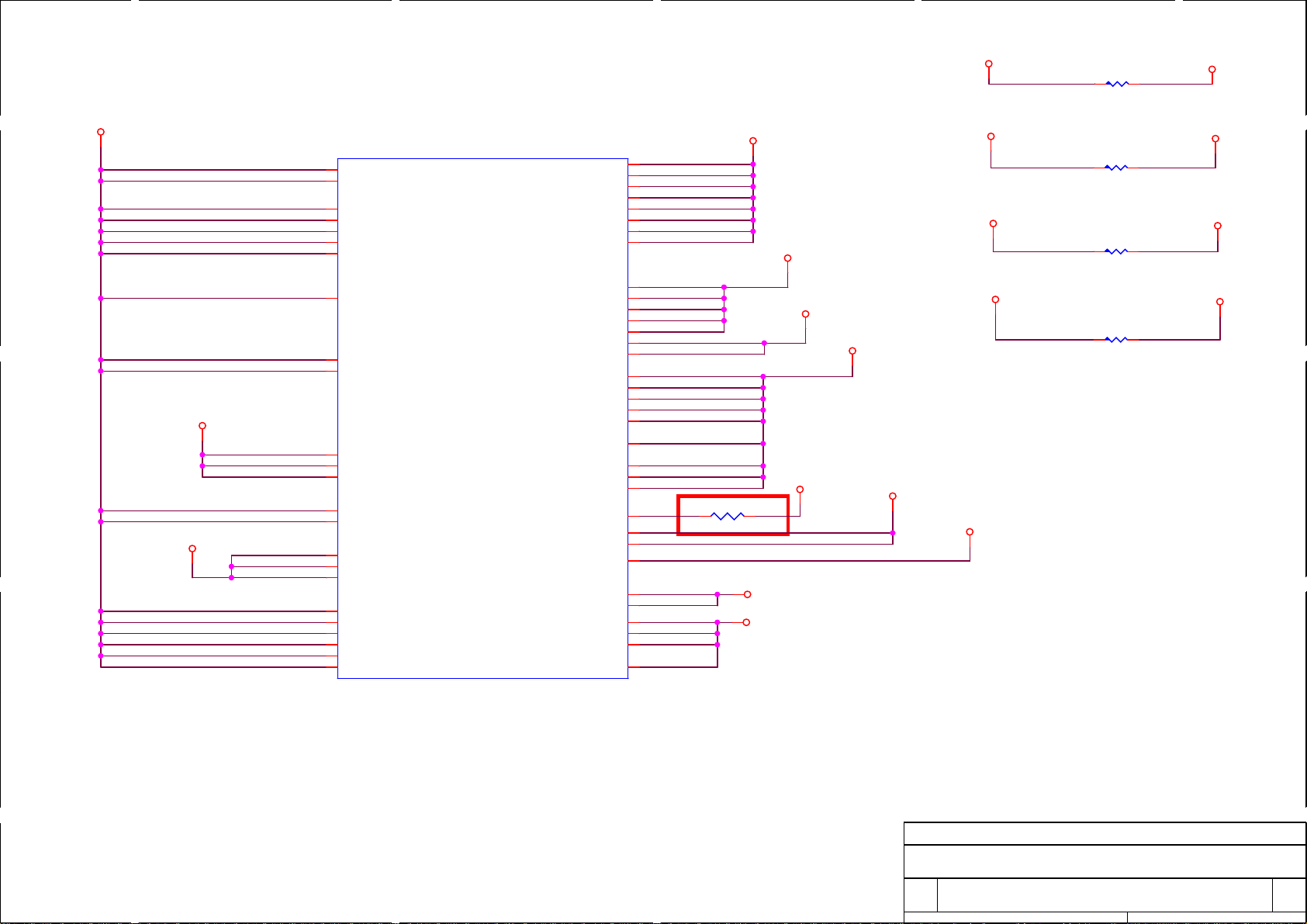

SOC: STORAGE/ I2S

?

U1000C

GPI_VOLUMEDOWN[29]

GPI_VOLUMEUP[29]

EMMC_CLK[20]

O

C9403

0.1U/10V/DNI

CC0201_S

EMMC_RESET_N[20]

SDMMC3_CLK[33]

O

12

EMMC_DATA_0[20]

EMMC_DATA_1[20]

EMMC_DATA_2[20]

EMMC_DATA_3[20]

EMMC_DATA_4[20]

EMMC_DATA_5[20]

EMMC_DATA_6[20]

EMMC_DATA_7[20]

EMMC_CMD[20]

SDIO2_CLK[35]

SDIO2_DATA_0[35]

SDIO2_DATA_1[35]

SDIO2_DATA_2[35]

SDIO2_DATA_3[35]

SDIO2_CMD[35]

SDMMC3_D0[33]

SDMMC3_D1[33]

SDMMC3_D2[33]

SDMMC3_D3[33]

SDMMC3_CD_N[5,33]

SDMMC3_CMD[33]

R1020

49.9/F_4

RC0201_S

0R

I

I

R9116

0R

SDMMC3_RCOMP

RC0201_S

R9115

O

O

RC0201_S

B

B

B

B

I

B

CPU_MMC1_CLK

B

B

B

B

B

B

B

B

B

B

B

B

B

B

CPU_SD3_CLK

AB6

GPIO_S0_SC[00]

AA6

GPIO_S0_SC[01]

Y6

GPIO_S0_SC[02]

AE8

MMC1_CLK

AB7

MMC1_D[0]

AC7

MMC1_D[1]

AC8

MMC1_D[2]

AB9

MMC1_D[3]

AA9

MMC1_D[4]

AA8

MMC1_D[5]

Y8

MMC1_D[6]

Y7

MMC1_D[7]

AB8

MMC1_CMD

AD8

MMC1_RST#

AE6

MMC1_RCOMP

AE9

SD2_CLK

AB11

SD2_D[0]

AB10

SD2_D[1]

AC10

SD2_D[2]

AD10

SD2_D[3]_CD#

AC9

SD2_CMD

AC12

SD3_CLK

AC11

SD3_D[0]

AB13

SD3_D[1]

AA12

SD3_D[2]

AA13

SD3_D[3]

Y12

SD3_CD#

AB12

SD3_CMD

Y9

SD3_1P8EN

AA10

SD3_PWREN#

AE10

SD3_RCOMP

SOC_VLV2_CR_BGA

REV = 2.0

BGA592-INTEL-BAY-TRAIL-T-TEST

3 OF 9

GPIO_S0_SC[03]

GPIO_S0_SC[07]

AUDIO_RCOMP

I2S0_CLK

I2S0_L_R

I2S0_DATAOUT

I2S0_DATAIN

I2S1_CLK

I2S1_L_R

I2S1_DATAOUT

I2S1_DATAIN

GPIO_S0_SC[65]

PROCHOT#

AC5

AA5

AE14

Y16

Y14

AA14

Y13

AC13

AC14

AB14

Y10

U17

F16

I

SDMMC3_CD_N [5,33]

AUDIO_RCOMP

O

I2S_0_CLK[27]

B

I2S_0_FS[27]

O

I2S_0_TXD[27]

I

I2S_0_RXD[27]

B

I2S_1_CLK[27,35]

B

I2S_1_FS[27,35]

O

I2S_1_TXD[27,35]

I2S_1_RXD[27,35]

I

1

TP9030pad-nku-tp4050np

12

R1022

49.9/F_4

RC0201_S

A

Title

Title

Title

<Title>

<Title>

<Title>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

<Doc>

A4

<Doc>

A4

<Doc>

A4

Date: Sheet of

Date: Sheet of

Date: Sheet of

5 40Thursday, August 28, 2014

5 40Thursday, August 28, 2014

5 40Thursday, August 28, 2014

5

D

C

B

A

<RevCode>

<RevCode>

<RevCode>

4

3

2

1

SOC: USB/I2C

?

U1000D

USB_ULPI_0_CLK[18]

D

USB_ULPI_0_DATA0[18]

USB_ULPI_0_DATA1[18]

USB_ULPI_0_DATA2[18]

USB_ULPI_0_DATA3[18]

USB_ULPI_0_DATA4[18]

USB_ULPI_0_DATA5[18]

USB_ULPI_0_DATA6[18]

USB_ULPI_0_DATA7[18]

USB_ULPI_0_DIR[18]

USB_ULPI_0_NXT[18]

USB_ULPI_0_STP[18]

USB_ULPI_0_REFCLK[18]

USB2_P0_DP[18]

USB2_P0_DN[18]

I

B

B

B

B

B

B

B

B

I

I

O

O

B

B

C

COMBO_WLAN_EN[35]

O

USB_RCOMP

12

R1027

45.3/F_4

RC0402_S

N3

USB_ULPI_CLK

J5

USB_ULPI_DATA[0]

H5

USB_ULPI_DATA[1]

J4

USB_ULPI_DATA[2]

H1

USB_ULPI_DATA[3]

H2

USB_ULPI_DATA[4]

J3

USB_ULPI_DATA[5]

J1

USB_ULPI_DATA[6]

K2

USB_ULPI_DATA[7]

K3

USB_ULPI_DIR

N4

USB_ULPI_NXT

M2

USB_ULPI_STP

F10

USB_ULPI_REFCLK

G4

USB_DP[0]

G3

USB_DN[0]

H4

USB_DP[1]

H3

USB_DN[1]

4 OF 9

AJSR1UDVT01

F13

USB_OC[0]#

F14

USB_OC[1]#

F1

USB_RCOMPO

SOC_VLV2_CR_BGA

REV = 2.0

BGA592-INTEL-BAY-TRAIL-T-TEST

USB_REXT[1]

USB_REXT[0]

GPIO_RCOMP

GPIO_S0_SC[57]

GPIO_S0_SC[61]

GPIO_S0_SC[54]

SIO_I2C0_DATA

SIO_I2C0_CLK

SIO_I2C1_DATA

SIO_I2C1_CLK

SIO_I2C2_DATA

SIO_I2C2_CLK

SIO_I2C3_DATA

SIO_I2C3_CLK

SIO_I2C4_DATA

SIO_I2C4_CLK

D1_I2C_DATA

D1_I2C_CLK

A8

C1

A4

AC6

AD6

AE5

AE12

AD12

AE13

AD14

AB15

AC15

AB16

AC16

AD16

AE16

AA17

AB17

USB3_REXT_P1

USB3_REXT_P0

GPIO_RCOMP

O

UART_3_TXD[29,36]

I

UART_3_RXD[29,36]

B

I2C_0_SDA [18]

O

I2C_0_SCL [18]

B

I2C_1_SDA [25,27,36]

O

I2C_1_SCL [25,27,36]

B

I2C_2_SDA [26]

O

I2C_2_SCL [26]

B

I2C_3_SDA [24]

O

I2C_3_SCL [24]

B

I2C_4_SDA [14]

O

I2C_4_SCL [14]

O

12

R1029

10K/F_4

RC0201_S

12

R1028

49.9/F_4

RC0402_S

USB_ULPI_0_CS [18]

12

R1045

1.24K/F_4

RC0201_S

12

R1044

1.24K/F_4

RC0201_S

B

A

Note: RCOMP: Place as close as possible to SOC. Preferably trace resistance < 0.5 ohm

Title

Title

Title

<Title>

<Title>

<Title>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

<Doc>

A4

<Doc>

A4

<Doc>

A4

Date: Sheet of

Date: Sheet of

Date: Sheet of

6 40Thursday, August 28, 2014

6 40Thursday, August 28, 2014

6 40Thursday, August 28, 2014

5

<RevCode>

<RevCode>

<RevCode>

4

3

2

1

SOC:PMU/DFX/CLOCK/UART/SUS

?

U1000E

XTAL25_IN

XTAL25_OUT

ICLK_ICOMP

12

R1030

4.02K/J_4

RC0402_S

PLT_CLK0_CAM1[25]

PLT_CLK0_CAM2[25]

CODEC_MCLK[27]

XDP_H_TCK[36]

XDP_H_TRST_N[36]

XDP_H_TMS[36]

XDP_H_TDI[36]

XDP_H_TDO[36]

XDP_H_PRDY_N[36]

XDP_H_PREQ_N[36]

SPI_NOR_CS0_N[19,36]

SPI_NOR_MISO[19,36]

SPI_NOR_MOSI[19,36]

SPI_NOR_CLK[19,36]

PMIC_INT[14]

WIFI_32K_CLK[34]

GPS_32K_CLK[37]

LCM_ID[24]

VCM1_PW DM[25]

O

O

O

I

I

I

I

O

O

I

O

I

O

O

I

GPIO_SUS1

GPIO_SUS3

GPIO_SUS4

O

O

I

O

+V1P8A_SOC[4,7,9,11]

12

C1003

12P/50V/NPO_4

CC0402_S

XDP_H_TRST_N

12

R1005

51/F_4

RC0201_S

xtl-3_2x2_5-2_2x1_7

Y1000

2 4

1

3

E3FB25.0000F10E33

R1031

12

RC0402_S

1M/J_4

+V1P8A_SOC[4,7,9,11]

R1002

12

XDP_H_TCK

51/F_4

RC0201_S

12

C1004

12P/50V/NPO_4

CC0402_S

12

R1048

DNI

RC0201_S

XDP_H_TDO

D D

C C

B B

+V1P8A_SOC[4,7,9,11]

V3

ICLK_OSCIN

V2

ICLK_OSCOUT

V1

ICLK_ICOMP

AB5

PMC_PLT_CLK[0]

AE4

PMC_PLT_CLK[1]

AD4

PMC_PLT_CLK[3]

AD2

PMC_PLT_CLK[4]

E5

TAP_TCK

G6

TAP_TRST#

H6

TAP_TMS

F4

TAP_TDI

F6

TAP_TDO

F7

TAP_PRDY#

F5

TAP_PREQ#

C12

PCU_SPI_CS[0]#

D12

PCU_SPI_CS[1]#

E13

PCU_SPI_MISO

E12

PCU_SPI_MOSI

F12

PCU_SPI_CLK

E9

GPIO_S5[00]

D7

GPIO_S5[01]

F9

GPIO_S5[02]

E8

GPIO_S5[03]

F8

GPIO_S5[04]

D6

GPIO_S5[05]

D4

GPIO_S5[06]

D5

GPIO_S5[07]

D3

GPIO_S5[08]

E6

GPIO_S5[09]

C5

GPIO_S5[10]

SOC_VLV2_CR_BGA

REV = 2.0

BGA592-INTEL-BAY-TRAIL-T-TEST

5 OF 9

AJSR1UDVT01

SIO_UART1_RXD

SIO_UART1_TXD

SIO_UART1_RTS#

SIO_UART1_CTS#

SIO_UART2_RXD

SIO_UART2_TXD

SIO_UART2_RTS#

SIO_UART2_CTS#

PMC_SUSPWRDNACK

PMC_SUSCLK_0

PMC_SLP_S0IX#

PMC_SLP_S4#

PMC_SLP_S3#

USB_ULPI_RST#

PMC_ACPRESENT

GPIO_S5[15]

PMC_BATLOW#

PMC_PWRBTN#

PMC_PLTRST#

GPIO_S5[17]

PMC_SUS_STAT#

ILB_RTC_TEST#

PMC_RSMRST#

PMC_CORE_PWROK

ILB_RTC_RST#

ILB_RTC_X1

ILB_RTC_X2

ILB_RTC_EXTPAD

SVID_ALERT#

SVID_DATA

SIO_PWM[0]

SIO_PWM[1]

GPIO_S5[22]

GPIO_S5[23]

GPIO_S5[24]

GPIO_S5[25]

GPIO_S5[26]

GPIO_S5[27]

GPIO_S5[28]

GPIO_S5[29]

GPIO_S5[30]

SVID_CLK

AB19

AC19

AC18

AB18

AD18

AE18

AC17

AE17

D10

A9

C7

D8

C8

C6

B8

B10

C9

A10

B6

D9

E10

E3

F3

F2

E4

D1

E1

D2

C10

C11

D11

AA16

Y17

A6

B4

A3

B3

B2

C2

C3

C4

A5

1

PMU_SLP_S4_N

PMU_SLP_S3_N

TP1026

1

pad-nku-tp2050np-g

RTEST_N

SRTCRST_N

RTC_X1

RTC_X2

BVCCRTC_EXPAD

O

BKLT_PW M[23]

O

I

I

I

B

JACK_DET_N [27,29]

1

UART_1_BT_RXD [35]

I

UART_1_BT_TXD[35]

O

UART_1_BT_RTS [35]

O

UART_1_BT_CTS [35]

I

UART_GPS_RXD [37]

I

UART_GPS_TXD [37]

O

UART_GPS_RTS [37]

O

UART_GPS_CTS [37]

I

SUSPWRDNACK [14]

O

O

PMU_SLP_S0IX_N [14]

O

USB_ULPI_RESET_N [18]

I

COMBO_W LAN_IRQ [35]

pad-nku-tp2050np-g

TP1040

O

I

I

GPS_WAKEUP [37]

BATT_ID [36]

O

GYRO_INT1 [26]

GYRO_INT2 [26]

TP1034pad-nku-tp2050np-g

PLTRST_N[14,36]

BT_HOST_WAKE[35]

RSMRST_N [14,36]

UART_3_DEBUG_SW [29]

DDR configuration

+V1P8A_SOC[4,7,9,11]

pad-nku-tp2050np-g

TP1030

1

1

1

PMC_SUS_STAT# USB_ID_CONN

1

TP1043

I

PMC_CORE_PWROK [14,36]

12

C1002

0.1U/16V/X7R_4

CC0402_S

DDRID1

DDRID2

pad-nku-tp2050np-g

TP1027

pad-nku-tp2050np-g

TP1028

RC0402_S

R1049

1 2

0R/F_4

pad-nku-tp2050np-g

12

CC0402_S

xtl-3_2x1_5-2_5-smt

Y1001

Micro Crystal

R1033

1 2

10M/J_4

RC0402_S

C1005

18P/50V/C0G_4

12

12

C1006

18P/50V/C0G_4

CC0402_S

USB_ID_CONN [18,30]

I

+VRTC[7,9,13,36]

12

R1046

20K/F_4

RC0402_S

12

C1052

1U/6.3V/X5R_4

CC0201_S

SRTCRST_N

+VRTC[7,9,13,36]

12

12

R1047

20K/F_4

RC0402_S

C1053

1U/6.3V/X5R_4

CC0201_S

12

R1003

51/F_4

RC0201_S

12

R1004

51/F_4

RC0201_S

XDP_H_TDI

XDP_H_TMS

A A

RC0201_S

R1036

DNI

12

DDRID1

R1042

1 2

0R/F_4

R1043

1 2

0R/F_4

R1038

1 2

0R/F_4

RC0201_S

RC0201_S

RC0201_S

I

TOUCH_INT_N [24]

I

AUDIO_INT [27]

I

USBMUX_SEL[18]

12

R1035

DNI

RC0201_S

GPIO_SUS3

GPIO_SUS4

GPIO_SUS1

12

1K/F_4/DNI

RC0201_S

12

RC0201_S

R1050

R1051

10K/F_4/DNI

12

R1052

1K/F_4/DNI

RC0201_S

DDRID2

12

R1053

10K/F_4/DNI

RC0201_S

Title

Title

Title

<Title>

<Title>

<Title>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

<Doc>

A3

<Doc>

A3

<Doc>

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

A

B

C

MP

ID1 ID2

0 0

0

1

0

1

1 1

7 40Thursday, August 28, 2014

7 40Thursday, August 28, 2014

7 40Thursday, August 28, 2014

5

D

C

B

A

<RevCode>

<RevCode>

<RevCode>

4

3

2

1

SOC: POWER1

D

C

+VDDQ_DDR[8,11,12,16]

+VDDQ_DDR[8,11,12,16]

+V1P2SX_SOC[8,9,11]

B

+V_VCC[11,12]

?

U1000F

A12

CORE_VCC_S0IX_1

G15

CORE_VCC_S0IX_3

H14

CORE_VCC_S0IX_4

H15

CORE_VCC_S0IX_5

H16

CORE_VCC_S0IX_6

K13

CORE_VCC_S0IX_8

K14

CORE_VCC_S0IX_9

K15

CORE_VCC_S0IX_10

K16

CORE_VCC_S0IX_11

L14

CORE_VCC_S0IX_12

L15

CORE_VCC_S0IX_13

L16

CORE_VCC_S0IX_14

M14

CORE_VCC_S0IX_15

F15

CORE_VCC_S0IX_2

M15

CORE_VCC_S0IX_16

N14

CORE_VCC_S0IX_17

N15

CORE_VCC_S0IX_18

P13

CORE_VCC_S0IX_19

P14

CORE_VCC_S0IX_20

P15

CORE_VCC_S0IX_21

P16

CORE_VCC_S0IX_22

J17

CORE_VCC_S0IX_7

W19

DRAM_VDD_S4_7

L18

DRAM_VDD_S4_2

L19

DRAM_VDD_S4_3

M19

DRAM_VDD_S4_5

L20

DRAM_VDD_S4_4

K18

DRAM_VDD_S4_1

T19

DRAM_VDD_S4_6

P19

DRAM_V1P24_S0IX_F1

SOC_VLV2_CR_BGA

REV = 2.0

BGA592-INTEL-BAY-TRAIL-T-TEST

UNCORE_VNN_S4_26

UNCORE_VNN_S4_2

UNCORE_VNN_S4_3

UNCORE_VNN_S4_4

UNCORE_VNN_S4_5

UNCORE_VNN_S4_8

UNCORE_VNN_S4_9

UNCORE_VNN_S4_11

UNCORE_VNN_S4_12

UNCORE_VNN_S4_13

UNCORE_VNN_S4_14

UNCORE_VNN_S4_7

UNCORE_VNN_S4_15

UNCORE_VNN_S4_6

UNCORE_VNN_S4_17

UNCORE_VNN_S4_18

UNCORE_VNN_S4_19

UNCORE_VNN_S4_20

UNCORE_VNN_S4_21

UNCORE_VNN_S4_22

UNCORE_VNN_S4_23

UNCORE_VNN_S4_24

UNCORE_VNN_S4_25

UNCORE_VNN_S4_27

UNCORE_VNN_S4_28

UNCORE_VNN_S4_29

UNCORE_VNN_S4_30

UNCORE_VNN_S4_31

UNCORE_VNN_S4_32

UNCORE_VNN_S4_33

UNCORE_VNN_S4_34

UNCORE_VNN_S4_16

UNCORE_VNN_S4_35

UNCORE_VNN_S4_36

UNCORE_VNN_S4_1

UNCORE_VNN_S4_10

AJSR1UDVT016 OF 9

U12

K12

L11

L12

L13

M11

M12

M9

N10

N11

N12

M10

R13

L9

T11

T12

T13

T14

T15

T16

T17

U10

U11

U13

U14

U15

U16

V10

V11

V13

V17

R8

V18

W18

AB1

M8

+V_VNN[11,12]

+V1P2SX[13]

SH1000

short0402_S

+V1P2SX_SOC[8,9,11]

0R/F_4

A

Title

Title

Title

<Title>

<Title>

<Title>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

<Doc>

A4

<Doc>

A4

<Doc>

A4

Date: Sheet of

Date: Sheet of

Date: Sheet of

8 40Thursday, August 28, 2014

8 40Thursday, August 28, 2014

8 40Thursday, August 28, 2014

5

D

C

B

A

<RevCode>

<RevCode>

<RevCode>

4

3

2

1

SOC: POWER2

D

C

B

+V1P0A_SOC[9,11]

?

U1000G

J16

CORE_V1P05_S4_5

M16

CORE_V1P05_S4_8

J7

UNCORE_V1P0_G3_1

K8

UNCORE_V1P0_G3_4

L7

UNCORE_V1P0_G3_6

K7

UNCORE_V1P0_G3_3

W10

GPIO_V1P0_S4

G8

USB_V1P0_S4_1

H7

USB_V1P0_S4_2

H8

UNCORE_V1P0_S4

+V1P0SX[9,11,12]

V15

UNCORE_V1P0_S0IX_6

W15

UNCORE_V1P0_S0IX_8

V16

UNCORE_V1P0_S0IX_7

K9

UNCORE_V1P0_G3_5

J9

+V1P0SX[9,11,12]

UNCORE_V1P0_G3_2

T7

DDI_V1P0_S0IX_1

U8

DDI_V1P0_S0IX_3

T8

DDI_V1P0_S0IX_2

AE24

DRAM_V1P0_S4_1

H18

DRAM_V1P0_S4_3

G19

DRAM_V1P0_S4_2

U18

DRAM_V1P0_S4_6

N18

DRAM_V1P0_S4_5

M18

DRAM_V1P0_S4_4

SOC_VLV2_CR_BGA

REV = 2.0

BGA592-INTEL-BAY-TRAIL-T-TEST

AJSR1UDVT01

7 OF 9

CORE_V1P05_S4_7

CORE_V1P05_S4_6

CORE_V1P05_S4_4

CORE_V1P05_S4_10

CORE_V1P05_S4_9

CORE_V1P05_S4_2

CORE_V1P05_S4_3

CORE_V1P05_S4_1

UNCORE_V1P0_S0IX_4

UNCORE_V1P0_S0IX_3

UNCORE_V1P0_S0IX_5

UNCORE_V1P0_S0IX_1

UNCORE_V1P0_S0IX_2

MIPI_V1P24_S4_1

MIPI_V1P24_S4_2

UNCORE_V1P8_S4_3

UNCORE_V1P8_S4_1

UNCORE_V1P8_S4_4

UNCORE_V1P8_S4_2

MIPI_V1P8_S4

UNCORE_V1P8_G3

PMC_V1P8_G3_2

PMC_V1P8_G3_1

PMC_V1P8_G3_3

RTC_VCC

USB_V3P3_S0IX

PCU_V3P3_G3

SD3_V1P8V3P3_S4

ICLK_V1P24_S4_F1

ICLK_V1P24_S4_F2

UNCORE_V1P24_S0IX_F5

UNCORE_V1P24_S0IX_F4_2

UNCORE_V1P24_S0IX_F4_1

UNCORE_V1P24_S0IX_F1

L17

K17

G18

R18

R17

A17

G17

A16

R11

R10

T10

H11

H12

N7

P7

W16

W12

Y15

W13

J15

G11

J10

H10

K10

F11

H9

G12

W14

M7

N8

P12

H13

G13

P9

SH9015

+V1P0A_SOC[9,11]

1 2

0R

RC0201_S

+V1P0SX[9,11,12]

+V1P2A_SOC[9,11]

+V1P8A_SOC[4,7,9,11]

+VRTC[7,13,36]

+V1P2A_SOC[9,11]

+V1P2SX_SOC[8,11]

+V3P3A_SOC[9,11]

+V1P0A[12]

+V1P2A[13]

+V1P8A[12,13,18,19,20,24,25,26,27,29,35,36,37]

+V3P3_ALDO3[13,29]

+V3P3A_SDIO_SOC[11,13]

SH1001

SH1002

SH1003

SH1004

0R/F_4

short0603_S

0R/F_4

short0402_S

0R/F_4

RC0402_S

0R/F_4

short0402_S

+V1P0A_SOC[9,11]

+V1P2A_SOC[9,11]

+V1P8A_SOC[4,7,9,11]

+V3P3A_SOC[9,11]

A

Title

Title

Title

<Title>

<Title>

<Title>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

<Doc>

A4

<Doc>

A4

<Doc>

A4

Date: Sheet of

Date: Sheet of

Date: Sheet of

9 40Thursday, August 28, 2014

9 40Thursday, August 28, 2014

9 40Thursday, August 28, 2014

5

D

C

B

A

<RevCode>

<RevCode>

<RevCode>

4

3

2

1

SOC: GND

D

?

U1000H

V8

VSS86

V7

VSS85

E7

VSS28

E24

VSS27

E21

VSS26

E2

VSS25

E18

VSS24

E15

VSS23

E11

VSS22

B9

VSS21

B5

VSS20

B21

VSS19

B17

VSS18

B13

VSS17

B1

C

B

AE2

AD9

AD5

AD21

AD17

AD13

AA7

AA24

AA21

AA2

AA18

AA15

AA11

W17

W11

J11

G9

N9

R7

A24

V19

K11

K19

J19

AD25

R19

P17

G14

J12

VSS16

VSS15

VSS14

VSS13

VSS11

VSS10

VSS9

VSS8

VSS7

VSS6

VSS5

VSS4

VSS3

VSS2

VSS89

L8

VSS51

VSS88

P8

VSS63

VSS36

J8

VSS44

VSS33

V9

VSS87

VSS60

VSS73

VSS1

VSS82

VSS45

VSS46

VSS41

VSS12

VSS68

VSS61

VSS30

VSS37

8 OF 9

VLV2_CR

USB_VSSA

VSS92

VSS91

VSS93

VSS80

VSS94

VSS90

VSS84

VSS83

VSS81

VSS79

VSS78

VSS77

VSS76

VSS75

VSS74

VSS72

VSS71

VSS70

VSS69

VSS67

VSS65

VSS64

VSS62

VSS59

VSS58

VSS57

VSS56

VSS55

VSS54

VSS53

VSS52

VSS50

VSS49

VSS48

VSS47

VSS43

VSS42

VSS40

VSS39

VSS38

VSS35

VSS34

VSS32

VSS31

VSS29

VSS66

W8

W7

W9

V12

Y11

W5

V6

V21

V14

U9

U24

U2

T9

T18

R9

R6

R5

R21

R20

R16

R14

R12

P18

N24

N21

N2

N17

N16

N13

M17

M13

L6

L5

L21

L10

J24

J2

J18

J14

J13

H21

H17

G5

G16

G10

R15

G7

?

U1000I

AC4

RESERVED9

AC3

RESERVED8

AE3

RESERVED13

AD3

RESERVED11

AC2

RESERVED6

AC1

RESERVED5

T2

RESERVED17

N5

RESERVED14

A2

RESERVED1

U3

RESERVED18

Y18

RESERVED21

P10

RESERVED15

P11

RESERVED16

AD1

RESERVED10

AE1

RESERVED12

W4

RESERVED20

W3

RESERVED19

AA19

RESERVED2

AA20

RESERVED3

AC21

RESERVED7

AB21

RESERVED4

SOC_VLV2_CR_BGA

REV = 2.0

BGA592-INTEL-BAY-TRAIL-T-TEST

9 OF 9

VLV2_CR

PWR_RSVD_OBS1

PWR_RSVD_OBS3

PWR_RSVD_OBS2

A25

B25

AE25

A

SOC_VLV2_CR_BGA

REV = 2.0

BGA592-INTEL-BAY-TRAIL-T-TEST

Title

Title

Title

<Title>

<Title>

<Title>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

<Doc>

A4

<Doc>

A4

<Doc>

A4

Date: Sheet of

Date: Sheet of

Date: Sheet of

10 40Thursday, August 28, 2014

10 40Thursday, August 28, 2014

10 40Thursday, August 28, 2014

5

D

C

B

A

<RevCode>

<RevCode>

<RevCode>

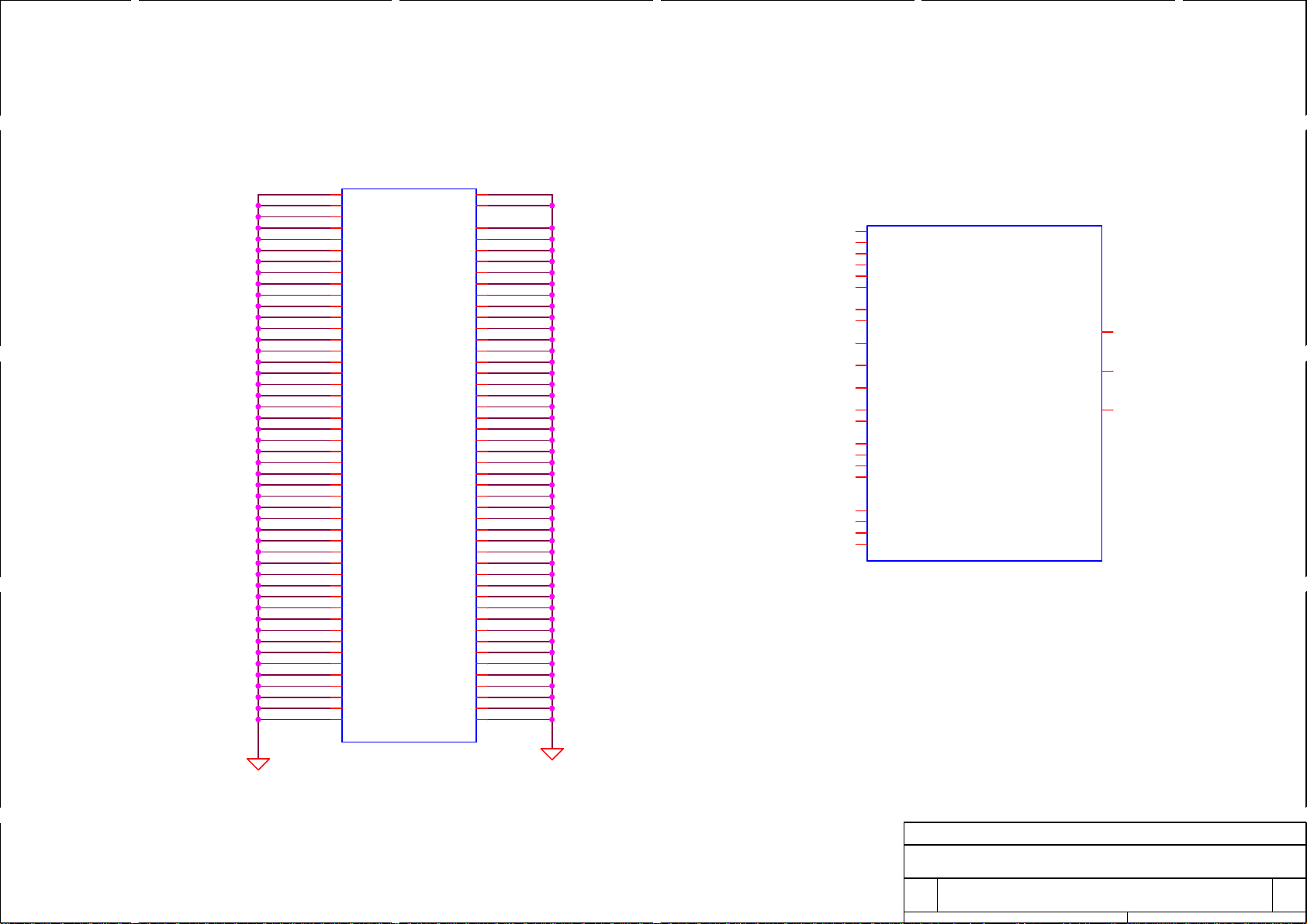

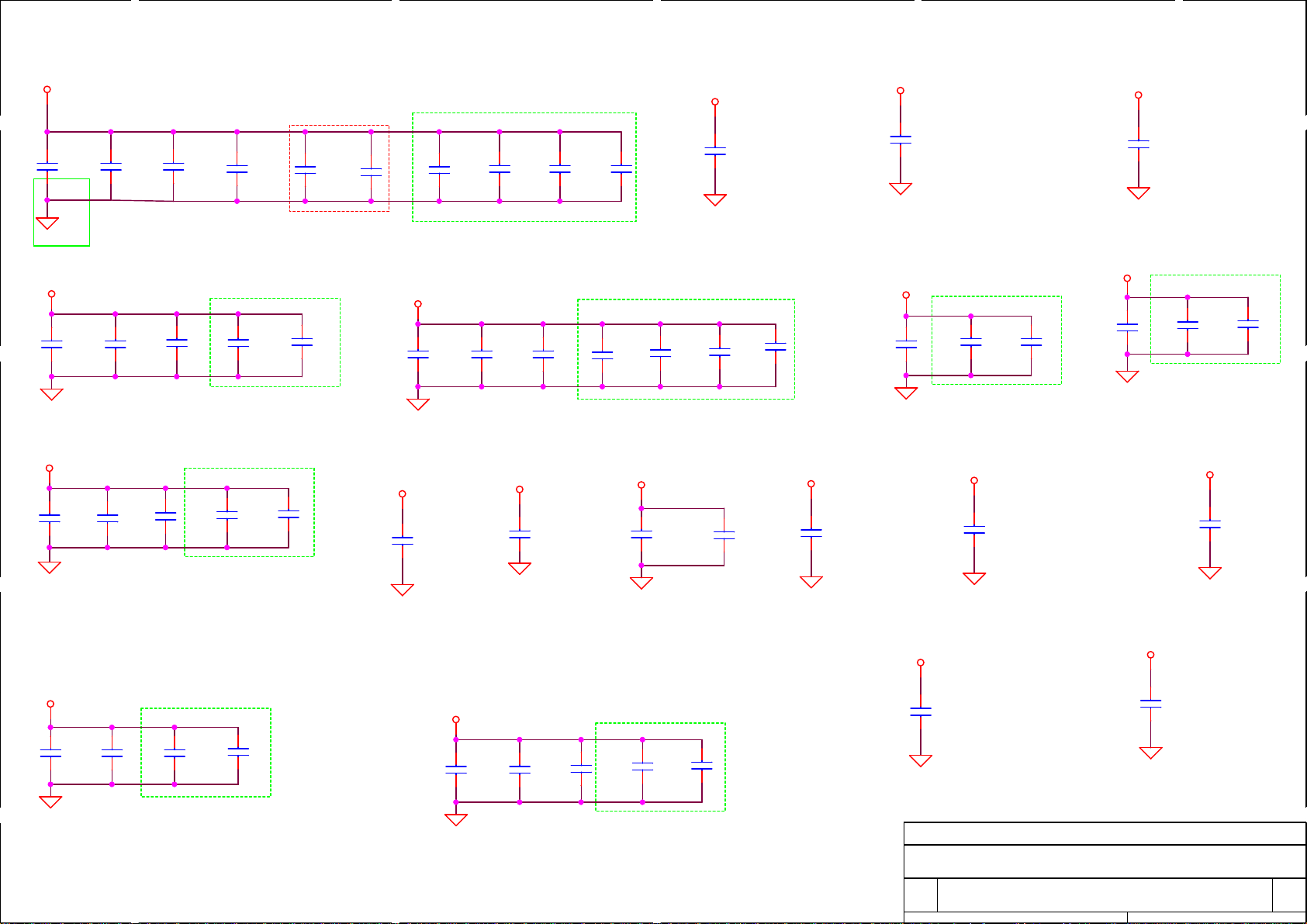

SOC: DECOUPLING

4

3

2

1

D

C

+V_VCC

12

C1007

CC0201_S

+V_VNN[8,12]

12

C1010

CC0201_S

+VDDQ_DDR

12

C1037

DNI

DNI

DNI

12

C1008

CC0201_S

12

C1051

CC0201_S

12

C1039

DNI

1U/6.3V/X5R_4

12

C1049

CC0201_S

12

C1056

CC0201_S

12

C1041

1U/6.3V/X5R_4

*1U/6.3V/X5R_4

12

C1050

CC0201_S

12

C1062

CC0201_S

12

C1016

1U/6.3V/X5R_4

*1U/6.3V/X5R_4

12

CC0201_S

12

CC0201_S

12

C1017

C1054

1U/6.3V/X5R_4

C1015

*1U/6.3V/X5R_4

12

C1055

CC0201_S

+V1P0A_SOC[9,11]

+VDDQ_DDR[8,11,12,16]

1U/6.3V/X5R_4

12

CC0201_S

12

C1036

12

C1021

CC0201_S

C1009

DNI

12

1U/6.3V/X5R_4

CC0201_S

12

C1012

CC0201_S

+V1P2SX_SOC[8,9]

C1022

*1U/6.3V/X5R_4

12

12

1U/6.3V/X5R_4

CC0201_S

12

CC0201_S

C1038

C1023

C1042

DNI

12

1U/6.3V/X5R_4

CC0201_S

12

C1064

CC0201_S

+V1P0A_SOC[9,11]

C1024

1U/6.3V/X5R_4

12

1U/6.3V/X5R_4

12

C1059

CC0201_S

C1048

+V1P0SX[9,11,12]

CC0201_S

1U/6.3V/X5R_4

12

C1031

1U/6.3V/X5R_4

12

C1060

CC0201_S

12

C1013

1U/6.3V/X5R_4

CC0201_S

+V1P0A_SOC[9,11]

12

C1029

1U/6.3V/X5R_4

CC0201_S

+V1P0A_SOC[9,11]

12

C1061

12

12

C1028

12

C1025

C1026

+V1P2A_SOC[9,11]

12

C1033

1U/6.3V/X5R_4

CC0201_S

+V1P2A_SOC[9,11]

C1027

12

C1032

12

12

C1047

DNI

DNI

1U/6.3V/X5R_4

1U/6.3V/X5R_4

+V1P0A_SOC[9,11]

12

C1014

CC0201_S

+V3P3A_SDIO_SOC[9,13]

1U/6.3V/X5R_4

CC0201_S

12

C1040

1U/6.3V/X5R_4

CC0201_S

CC0201_S

CC0201_S

+V1P8A_SOC[4,7,9,11]

12

1U/6.3V/X5R_4

CC0201_S

C1057

B

CC0201_S

+V1P0SX

A

CC0201_S

CC0201_S

1U/6.3V/X5R_4

CC0201_S

1U/6.3V/X5R_4

+V1P0A_SOC[9,11]

CC0201_S

1U/6.3V/X5R_4

CC0201_S

C1043

12

C1044

12

12

C1020

CC0201_S

12

C1046

1U/6.3V/X5R_4

12

1U/6.3V/X5R_4

CC0201_S

C1063

DNI

1U/6.3V/X5R_4

CC0201_S

CC0201_S

1U/6.3V/X5R_4

CC0201_S

1U/6.3V/X5R_4

1U/6.3V/X5R_4

CC0201_S

CC0201_S

1U/6.3V/X5R_4

+V1P8A_SOC[4,7,9,11]

12

C1035

1U/6.3V/X5R_4

CC0201_S

Title

Title

Title

<Title>

<Title>

<Title>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

<Doc>

A4

<Doc>

A4

<Doc>

A4

Date: Sheet of

Date: Sheet of

Date: Sheet of

CC0201_S

1U/6.3V/X5R_4

+V3P3A_SOC[9]

12

C1058

1U/6.3V/X5R_4

CC0201_S

11 40Thursday, August 28, 2014

11 40Thursday, August 28, 2014

11 40Thursday, August 28, 2014

1U/6.3V/X5R_4

CC0201_S

1U/6.3V/X5R_4

CC0201_S

C1045

12

C1030

12

1U/6.3V/X5R_4

CC0201_S

12

C1018

1U/6.3V/X5R_4

CC0201_S

12

C1019

DNI

1U/6.3V/X5R_4

CC0201_S

CC0201_S

1U/6.3V/X5R_4

1U/6.3V/X5R_4

CC0201_S

C2062

22U/6.3V

CC0603_S

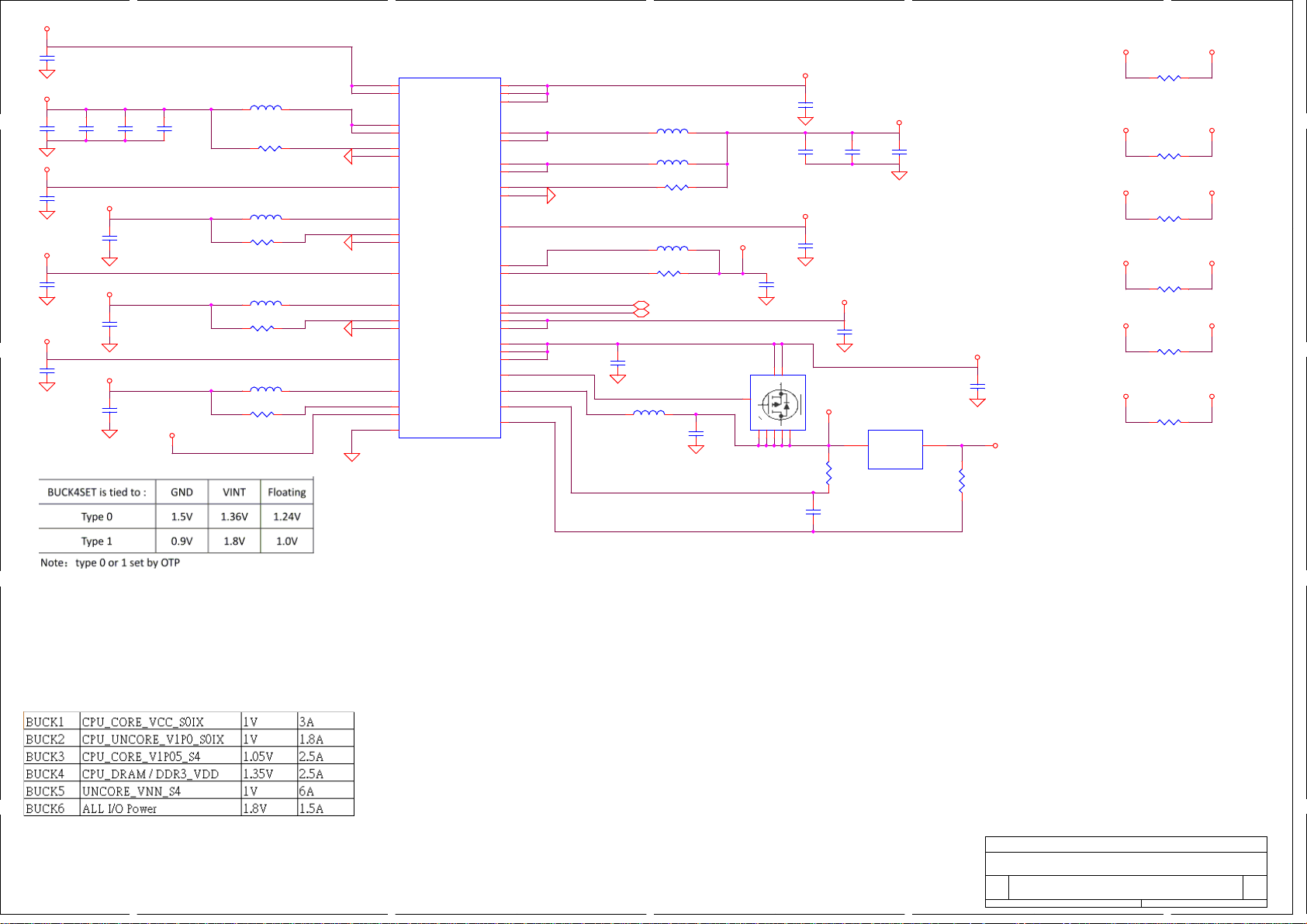

+V_BUCK2[12]

+V1P0A[9]

+VDDQ[12,13]

5

C2063

22U/6.3V

CC0603_S

C2015

22U/6.3V

CC0603_S

C2018

22U/6.3V

CC0603_S

C2005

22U/6.3V

CC0603_S

short0201_S

short0201_S

short0201_S

short0201_S

BUCK_LX1

BUCK_FB1

BUCK_LX2

BUCK_FB2

BUCK_LX3

BUCK_FB3

BUCK_LX4

BUCK_FB4

L2001 1UH/3A

C2008

22U/6.3V

CC0603_S

+VINT_PMIC[13]

L2_5X2-1_2

SH2005

0R/5%

L2004 1UH/3A

L2_5X2-1_2

SH2008

0R/5%

L2003 1UH/3A

L2_5X2-1_2

SH2007

0R/5%

L2005 1UH/3A

L2_5X2-1_2

SH2006

0R/5%

+V_IPSOUT_R

C2021

10U/16V

CC0603_S

+V_BUCK1[12]

D D

C C

C2061

22U/6.3V

CC0603_S

+V_IPSOUT_R

C2019

10U/16V

CC0603_S

+V_IPSOUT_R

C2011

10U/16V

CC0603_S

+V_IPSOUT_R

C2007

10U/16V

CC0603_S

BUCK4SET PIN CONNECTED TO VINT TO SET VDDQ AT 1.35V FOR DDR3L

4

U2003A

25

VIN_1

26

VIN_2

27

LX1_1

28

LX1_2

29

BUCK1

16

GND

72

VIN2

71

LX2

73

BUCK2

30

GND

15

VIN3

14

LX3

13

BUCK3

49

GND

8

VIN4

9

LX4

10

BUCK4

66

BUCK4SET

77

EPAD/GND

AXP288_1P04

QFN76-9X9-4-77P-AXP288

VIN5_1

VIN5_2

VIN5_3

LX5A_1

LX5A_2

LX5B_1

LX5B_2

BUCK5

GND

VIN6

LX6

BUCK6

VBUS_1

VBUS_2

IPSOUT_1

IPSOUT_2

VIN_CHG

N_BATDRV

LX_CHG

LOADSENSE

BATSENSE

3

3

G

D11D22D35D46D5

+V_IPSOUT_R[12,13]

+V_IPSOUT_R[12,13]

C2043

22U/6.3V

CC0603_S

8

S14S2

7

C2017

10U/16V

CC0603_S

C2020

22U/6.3V

CC0603_S

C2010

10U/16V

CC0603_S

+VUSB_CONN_FUSE[15,18,30]

WPM1481-6/TR

+VSYS[12,15,18,23,27,35,37]

SH9024

0R/1%

short0201_S

C2026

1UF/10V

CC0201_S

C2004

4.7U/16V

CC0603_S

43

44

45

41

42

47

48

46

74

22

23

24

31

DP

32

DM

55

61

59

60

70

57

69

67

68

BUCK_LX5_A

BUCK_LX5_B

BUCK_FB5

BUCK_LX6

BUCK_FB6

N_BATDRV

LX_CHG

SNS_LOADSENSE

SNS_BATSENSE

L2000 1UH/3A

L2_5X2-1_2

L2006 1UH/3A

L2_5X2-1_2

SH2004

0R/5%

L2002 1UH/3A

L2_5X2-1_2

SH2003

short0201_S

0R/5%

B

USB2_MUX_PMIC_DP [18]

B

USB2_MUX_PMIC_DN [18]

C2052

PLACE CLOSE TO VIN_CHG PIN

10U/16V

CC0603_S

L2007 1UH/3A

L2_5X2-1_2

short0201_S

C2003

10U/10V

CC0603_S

+V1P8A[9,13,18,19,20,24,25,26,27,29,35,36,37]

Q2000

+V_BUCK5[12]

C2022

22U/6.3V

CC0603_S

1

CSP

RC0805_S

2

C2064

22U/6.3V

CC0603_S

R20090.01R/1%

CSN

1

+VSYS[12,15,18,23,27,35,37] +VSYS_PMIC[13]

SH2000

0R/1% short0603_S

+V_IPSOUT[12] +V_IPSOUT_R[12,13]

SH2011

0R/1% short0603_S

+VDDQ[12,13] +VDDQ_DDR[8,11,16]

SH2012

0R/1% short0603_S

+V_BUCK5[12] +V_VNN[8,11]

SH2014

0R/1% short0603_S

+V_BUCK1[12] +V_VCC[8,11]

+V_IPSOUT[12]

C2006

10U/10V

CC0603_S

2

SH9025

0R/1%

short0201_S

+VBATTERY [36]

+V_BUCK2[12] +V1P0SX[9,11]

SH2017

0R/1% short0603_S

SH2018

0R/1% short0603_S

B B

A A

Title

Title

Title

<Title>

<Title>

<Title>

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

<Doc> <RevCode>

A3

<Doc> <RevCode>

A3

<Doc> <RevCode>

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

12 40Thursday, August 28, 2014

12 40Thursday, August 28, 2014

12 40Thursday, August 28, 2014

Loading...

Loading...