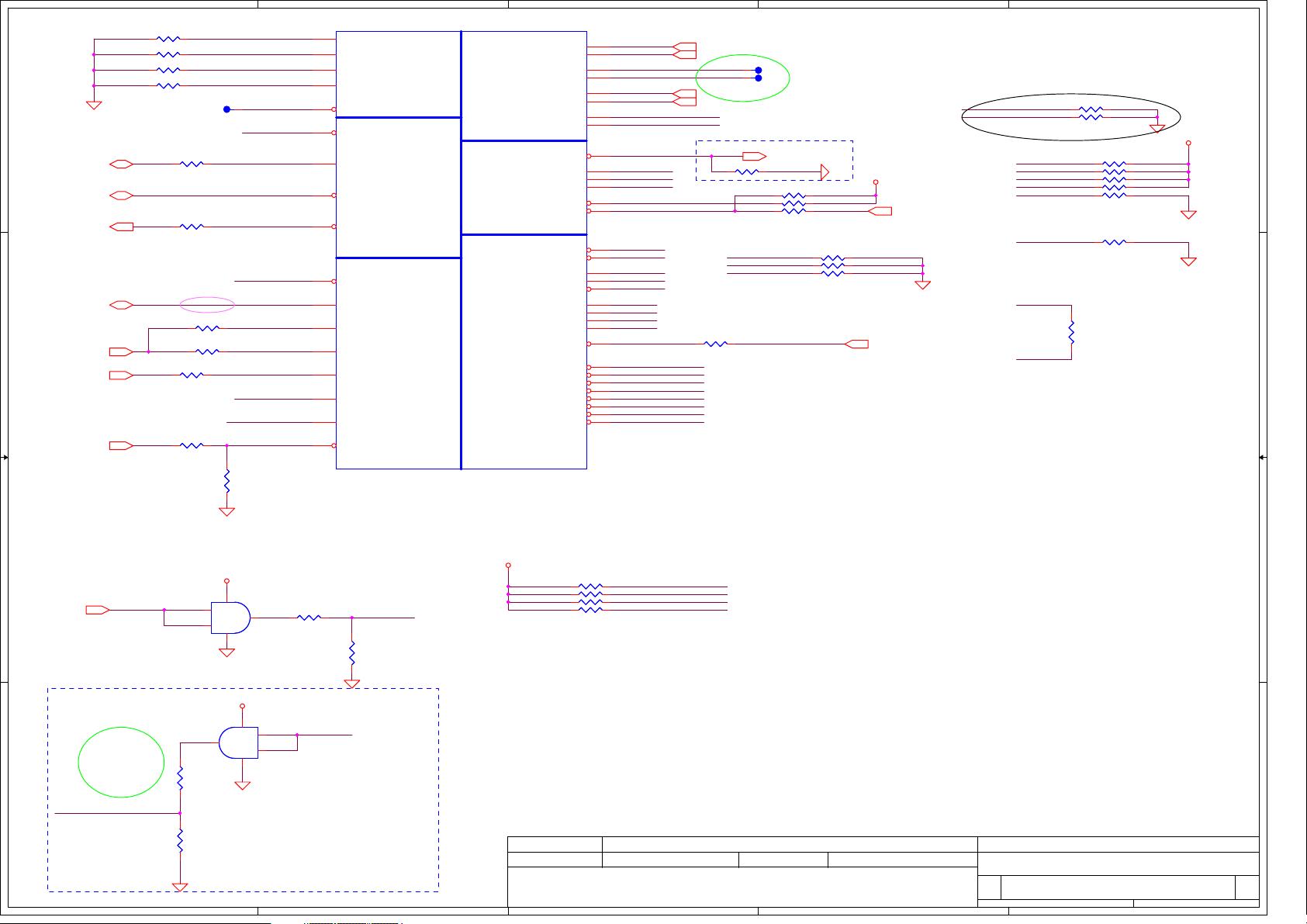

Acer LA-6392P PAU30, Iconia 6120 Schematic

A

1 1

B

C

D

E

Compal Confidential

2 2

ZZZ

PAU30 M/B Schematics Document

ZZZ

DAZ@

DAZ@

DAZ0F900100

DAZ0F900100

PCB PAU30 LA-6392P LS-6391P/6392P/6393P/6394 P

PCB PAU30 LA-6392P LS-6391P/6392P/6393P/6394 P

ZZZ1

ZZZ1

DA1@

DA1@

DA80000KE10

DA80000KE10

PCB 0F9 LA-6392P REV1 M/B

PCB 0F9 LA-6392P REV1 M/B

ZZZ2

ZZZ2

DA2@

DA2@

DA20000KT10

ZZZ3

ZZZ3

ZZZ4

ZZZ4

ZZZ5

ZZZ5

DA20000KT10

DA2@

DA2@

DA20000KU10

DA20000KU10

DA2@

DA2@

DA20000KV10

DA20000KV10

DA2@

DA2@

DA20000LE10

DA20000LE10

A

3 3

PCB 0F9 LS-6391P REV1 POWER_BTN/B

PCB 0F9 LS-6391P REV1 POWER_BTN/B

PCB 0F9 LS-6392P REV1 SWITCH/B

PCB 0F9 LS-6392P REV1 SWITCH/B

PCB 0F9 LS-6393P REV1 LED/B

PCB 0F9 LS-6393P REV1 LED/B

4 4

PCB 0F9 LS-6394P REV1 LID SWITCH/B

PCB 0F9 LS-6394P REV1 LID SWITCH/B

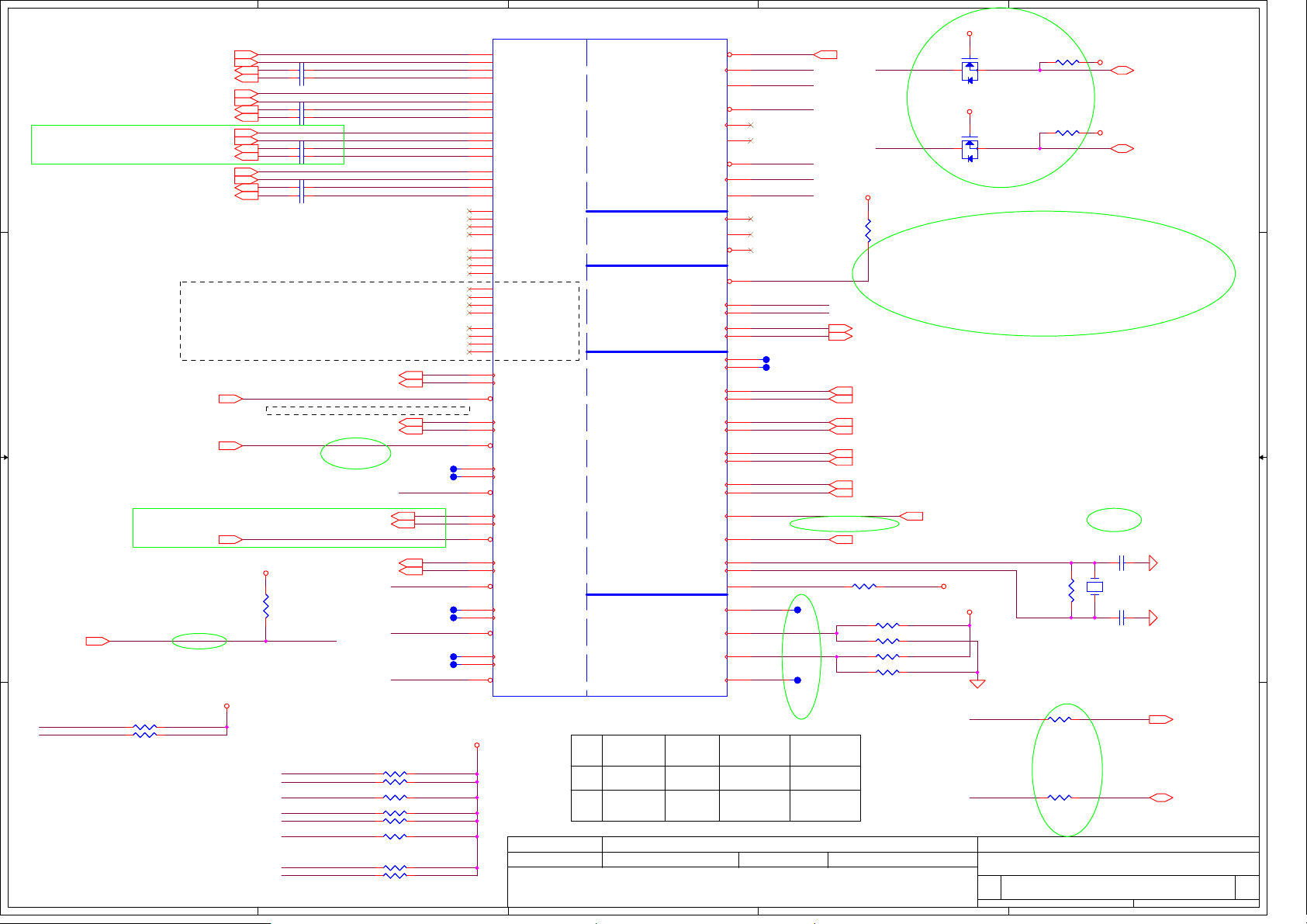

Intel Arrandale Processo SV with DDRIII + Ibex Peak-M

2010-11-22

REV:1.0

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTRO NICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTRO NICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTRO NICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2009/11/23 2010/11/23

2009/11/23 2010/11/23

2009/11/23 2010/11/23

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

PAU30 M/B LA-6392P Schematic

PAU30 M/B LA-6392P Schematic

PAU30 M/B LA-6392P Schematic

1 51Monday, November 22, 2010

1 51Monday, November 22, 2010

1 51Monday, November 22, 2010

E

0.1

0.1

0.1

A

B

C

D

E

Compal Confidential

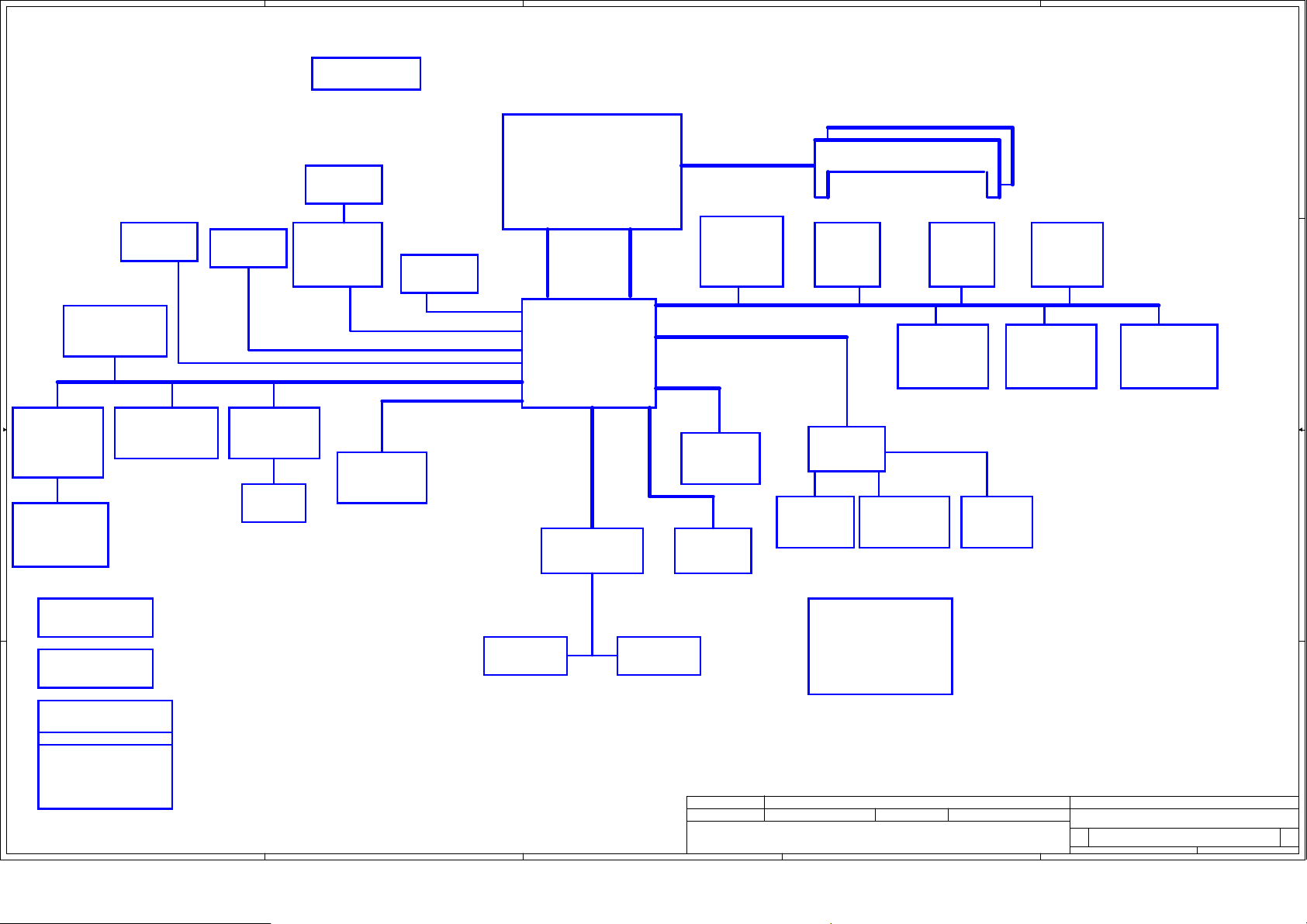

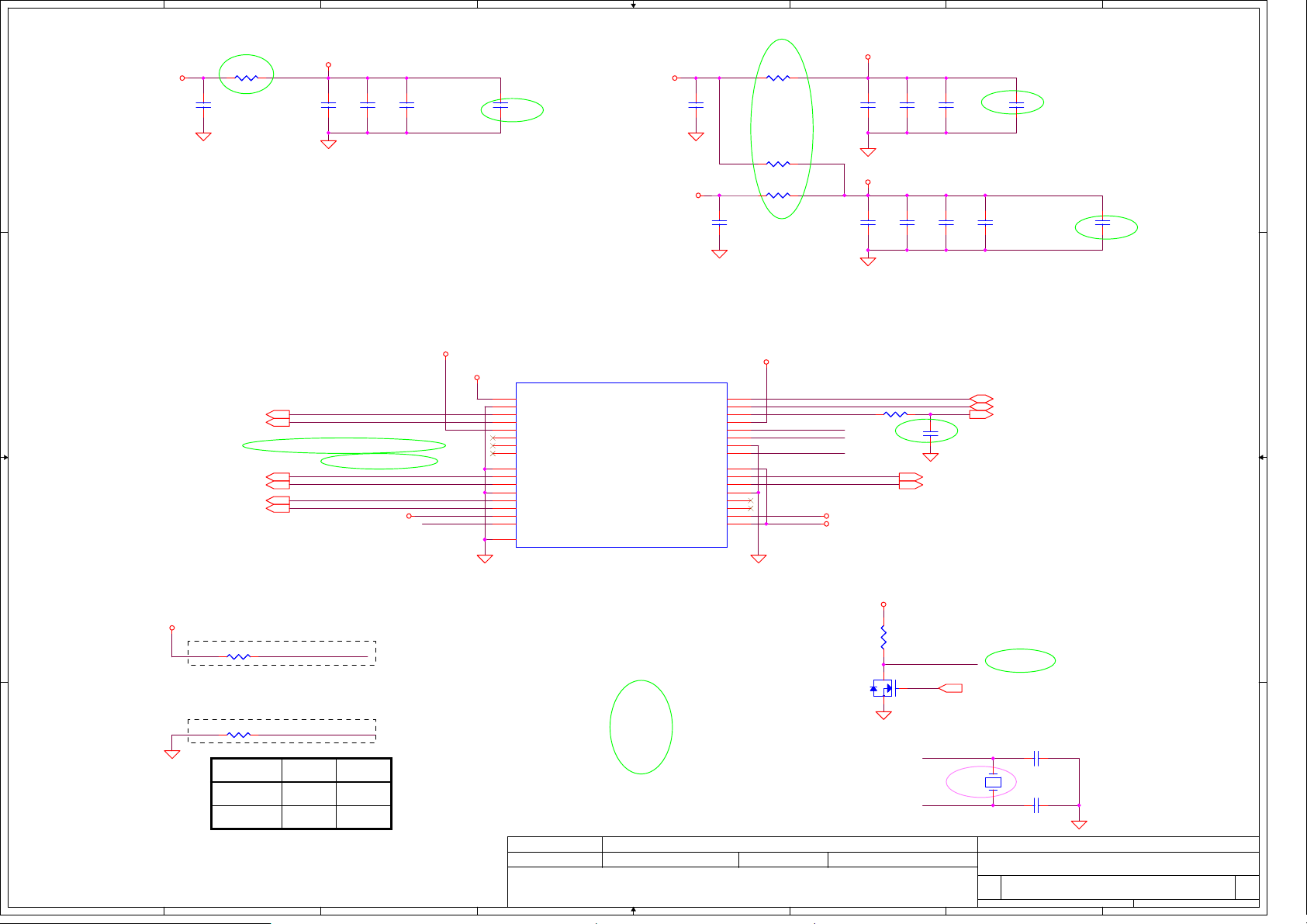

Model Name : PAU30

File Name : LA-6392P

1 1

HDMI Conn.

page 34

2 2

MINI Card x1

3G/GPS

page 36

port 4

port 3

port 2 port 1

CRT Conn.

page 33

HDMI(DDPC)

PCI-Express x 8 (ABD PCIE1 2.5GT/S CKD PCIE1/2 2.5/5GT/S)

Fan Control

page 46

LVDS Conn.

page 32

SDVO to

LVDS

Converter

page 31,32

LVDS Conn.

page 30

LVDS(UMA)

SDVO(DDPB)

Analog RGB(UMA)

SATA x 6 (GEN1 1.5GT/S ,GEN2 3GT/S)

Intel

Arrandale (UMA only)

Processor

rPGA988A

FDI x8

(UMA)

100MHz

2.7GT/s

Intel

Ibex Peak-M

100MHz

100MHz

PCH

page 15,16,17,18

19,20,21,22,23

page 4,5,6,7,8,9

DMI x4

100MHz

1GB/s x4

Memory BUS(DDRIII)

Dual Channel

1.5V DDRIII 800/1066

USB conn x2

USB port 0

USB port 1

page 40 page 40 page 30

USBx14

HD Audio

3.3V 48MHz

3.3V 24MHz

SPI

204pin DDRIII-SO-DIMM X2

BANK 0, 1, 2, 3

Bluetooth

Conn

USB port 13

page 10,11

Camera

USB port 8

SIMM Card

USB port 5

Touch

Screen x2

USB port 2, 3

page 40

3G Minicard

USB port 9

WLAN Minicard

USB port 4

page 36page 36page 36

PCI-E to

USB3.0

µPD720200

page 39

MINI Card x1

WLAN

page 36 page 37

USB Conn.

(USB 3.0 x 1

3 3

USB 2.0 x 1

page 39

RTC CKT.

page 15

Power On/Off CKT.

page 43

LAN(GbE)

AR8151

RJ45

page 38

port 0

SATA HDD

Conn.

page 35

EC I/O Buffer

SM BUS

LPC BUS

33MHz

ENE KB926

page 41

BIOS ROM

page 42page 42

SPI ROM x1

page 15

G-Sensor

page 46

HDA Codec

ALC271X

page 44

Int. Speaker Phone Jack x 2

page 45 page 45

Clock Generator

IDT: 9LVS3199AKLFT

SILEGO: SLG8LV597VTR

Realtek: RTM890N-631-GRT

133/120/100/96/14.318MHZ to PCH

page 14

Int.MIC

page 45

DC/DC Interface CKT.

4 4

page 47,48

Power Circuit DC/DC

page 47,48

A

B

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPA L ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPA L ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPA L ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2009/11/23 2010/11/23

2009/11/23 2010/11/23

2009/11/23 2010/11/23

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

PAU30 M/B LA-6392P Schematic

PAU30 M/B LA-6392P Schematic

PAU30 M/B LA-6392P Schematic

E

2 51Tuesday, September 07, 2010

2 51Tuesday, September 07, 2010

2 51Tuesday, September 07, 2010

0.1

0.1

0.1

A

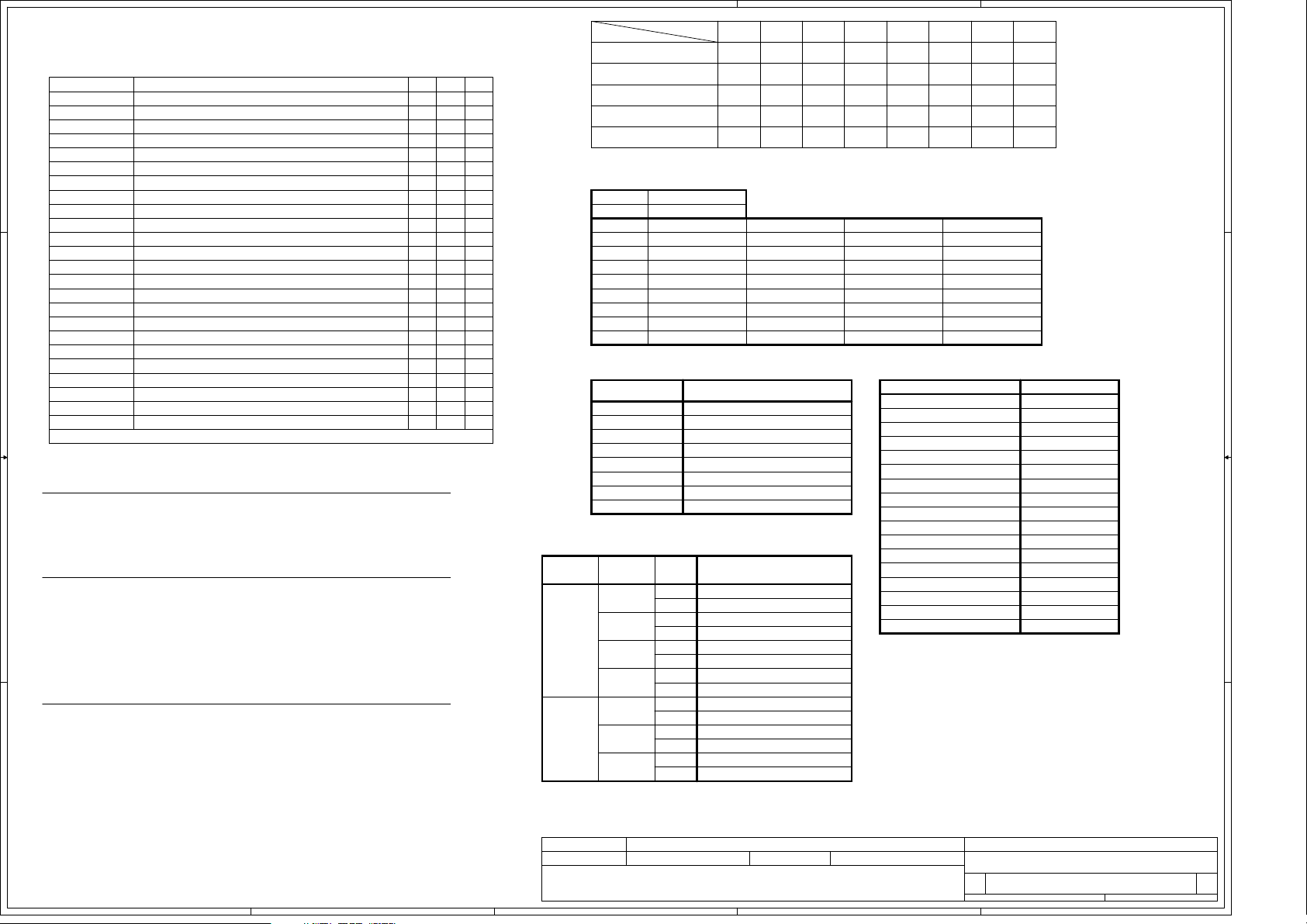

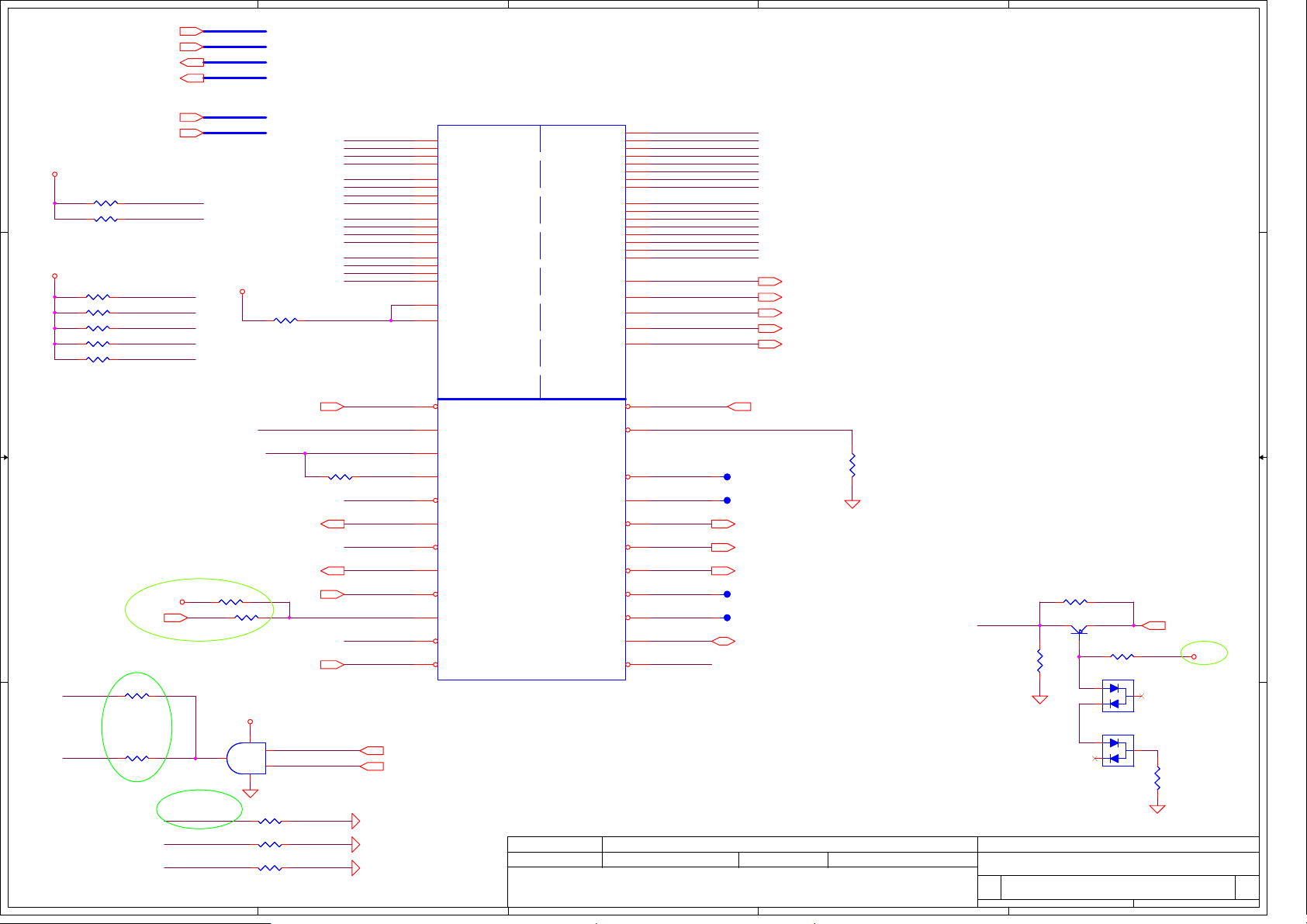

Voltage Rails

Power Plane Description

VIN

1 1

2 2

BATT+ Battery power supply (12.6V) N/A N/A N/A

B+

+CPU_CORE

+VGA_CORE

+VGFX_CORE Core voltage for Arrandale GPU (only for arrandaleCPU)

+0.75VS +0.75VP to +0.75VS switched power rail for DDR terminator

+1.0VSDGPU

+1.05VS_VTT

+1.05VS_PCH +1.05VS_VTT to +1.05VS_PCH power for PCH

+1.5V

+1.5VS

+1.5VSDGPU +1.5VS to +1.5VSDGPU switched power rail for GPU ON OFF OFF

+1.8VS (+5VALW or +3VALW) to 1.8V switched power rail to PCH & GPU

+3VALW +3VALW always on power rail

+3VALW_EC +3VALW always to KBC ON ON ON*

+3V_LAN +3VALW to +3V_LAN power rail for LAN ON ON

+3VS

+5VALW

+5VS +5VALW to +5VS switched power rail OFFON OFF

+VSB +VSBP to +VSB always on power rail for sequence control ON ON*

+RTCVCC RTC power

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

EC SM Bus1 address

Device

Smart Battery

PCH SM Bus address

3 3

Device

Clock Generator (9LVS3199AKLFT,

RTM890N-631-GRT)

DDR DIMM0

DDR DIMM2

43level BOM Config

431954BOL01

4 4

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

Core voltage for GPU

+1.0VSPDGPU to +1.0VSDGPU switched power rail for GPU

+1.05VS_VTTP to +1.05VS_VTT switched power rail for ARD CPU

+1.5VP to +1.5V power rail for DDRIII ON ON OFF

+1.5V to +1.5VS switched power rail

+3VALW to +3VS power rail

+5VALWP to +5VALW power rail

EC SM Bus2 address

Address Address

0001 011X b

Address

1101 0010b

1001 000Xb

1001 010Xb

SMT MB A6392 PAU30 W/3G

Device

BOM ConfigP/N Des.

DAZ@

B

S1 S3 S5

N/A N/A N/A

ON

ON OFF

ON OFF OFF

ON OFF OFF

ON OFF OFF

ON OFF OFF

ON OFF OFF

ON OFF OFF

ON

ON

ON

ON

ON

ON

N/AN/AN/A

OFF

OFF

OFF

OFF

OFF

ON ON*

ON*

OFF

OFF

ON ON*

ONON

C

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

Board ID / SKU ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

Rb / Rd / Rf V min

0

1

2

3

4

5

6

7 NC

BOARD ID Table

Board ID

0

1

2

3

4

5

6

7

USB Port Table

USB 2.0 USB 1.1 Port

UHCI0

EHCI1

EHCI2

UHCI1

UHCI2

UHCI3

UHCI4

UHCI5

UHCI6

SIGNAL

SLP_S1# SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

100K +/- 5%Ra/Rc/Re

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

PCB Revision

0

1

2

3

4

5

6

7

8

9

10

11

12

13

D

HIGH HIGH HIGH HIGH

LOW

LOW

LOW

LOW LOW LOW LOW

AD_BID

HIGH

LOWLOWLOW

HIGHHIGHHIGH

HIGH

HIGH

0 V

ON

ON

ON

ON

ON

V typ

AD_BID

0 V 0 V

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

0.503 V

0.819 V

1.185 V 1.264 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

2.200 V

3.300 V

BTO Option Table

BTO Item BOM Structure

0.1

0.2

0.3

1.0

VRAM

VRAM

Connector CONN@

Blue Tooth BT@

3 External

USB Port

USB Port (Left Side)

USB Port (Left Side)

USB/Touch Screen2

USB/Touch Screen1

Mini Card(WLAN)

SIMM CARD

Camera

Mini Card(3G)

Blue Tooth

Unpop

ON

ON

ON

OFF

OFF

V

AD_BID

0.538 V

0.875 V

2.341 V

3.300 V

ON ON

ON

OFF

OFF

OFF

max

E

LOW

OFF

OFF

OFF

X76@

VENTURA@Ventura

@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTRO NICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTRO NICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTRO NICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

C

2009/11/23 2010/11/23

2009/11/23 2010/11/23

2009/11/23 2010/11/23

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Notes List

Notes List

Notes List

PAU30 M/B LA-6392P Schematic

PAU30 M/B LA-6392P Schematic

PAU30 M/B LA-6392P Schematic

3 51Tuesday, September 07, 2010

3 51Tuesday, September 07, 2010

3 51Tuesday, September 07, 2010

E

0.1

0.1

0.1

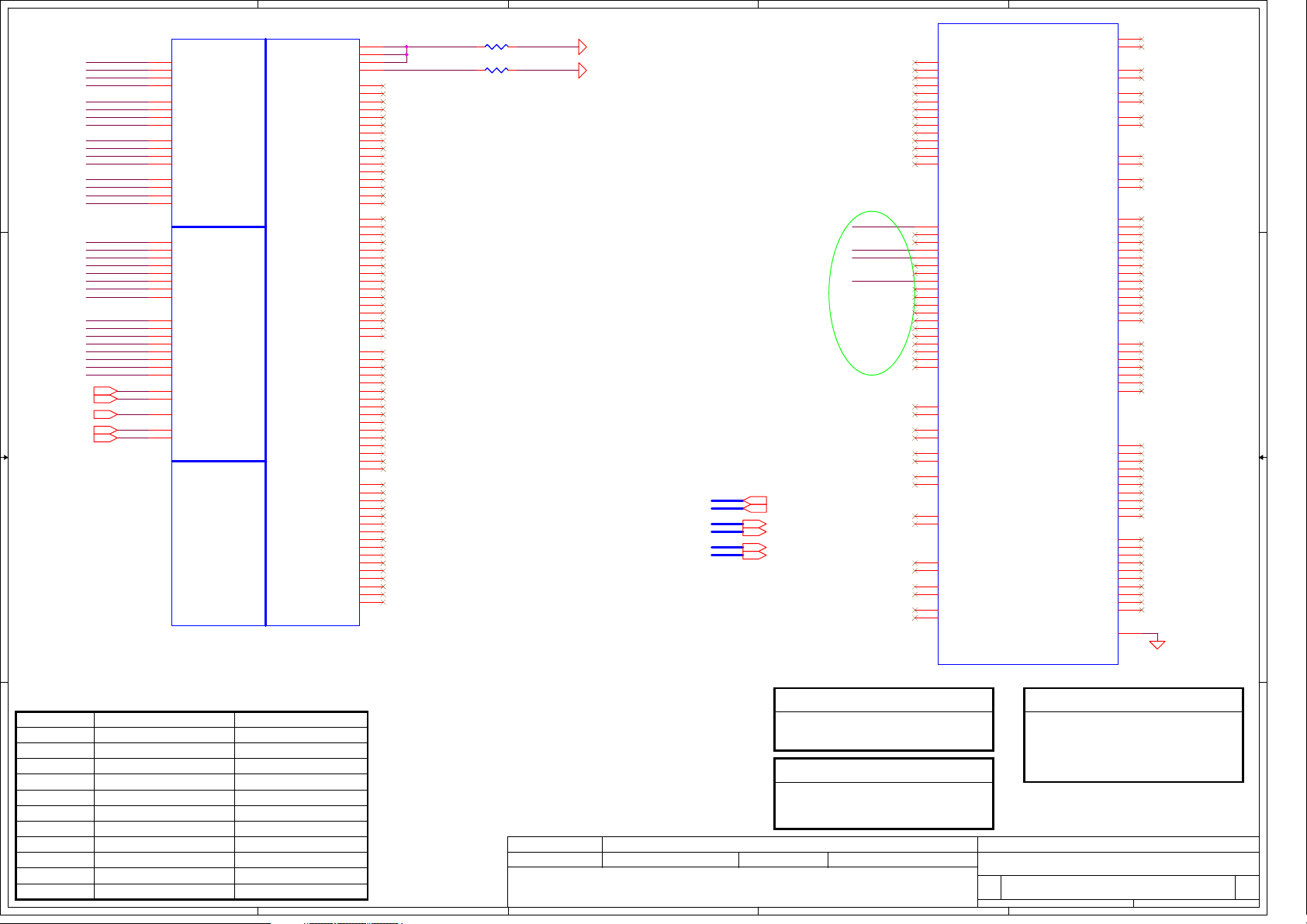

5

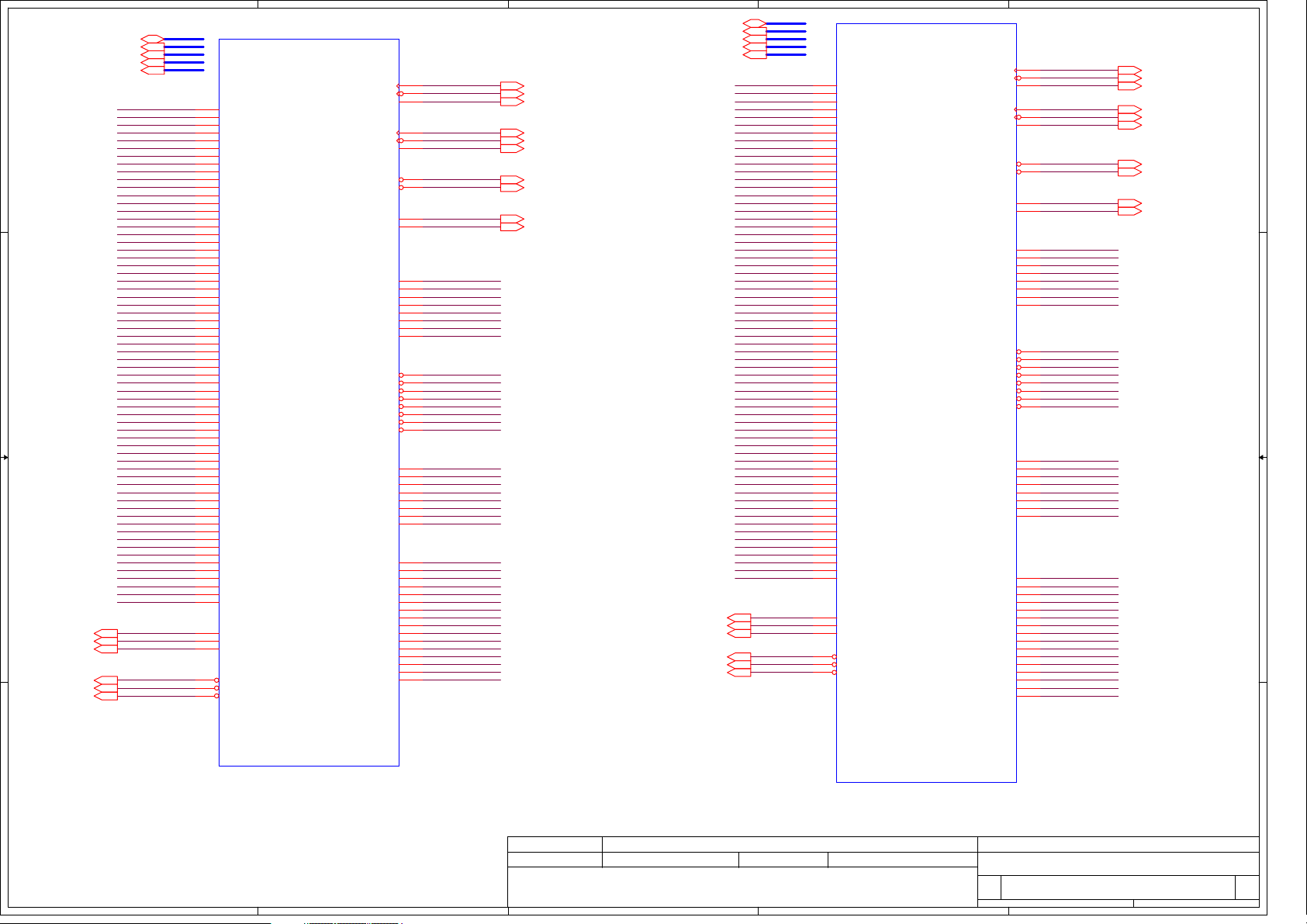

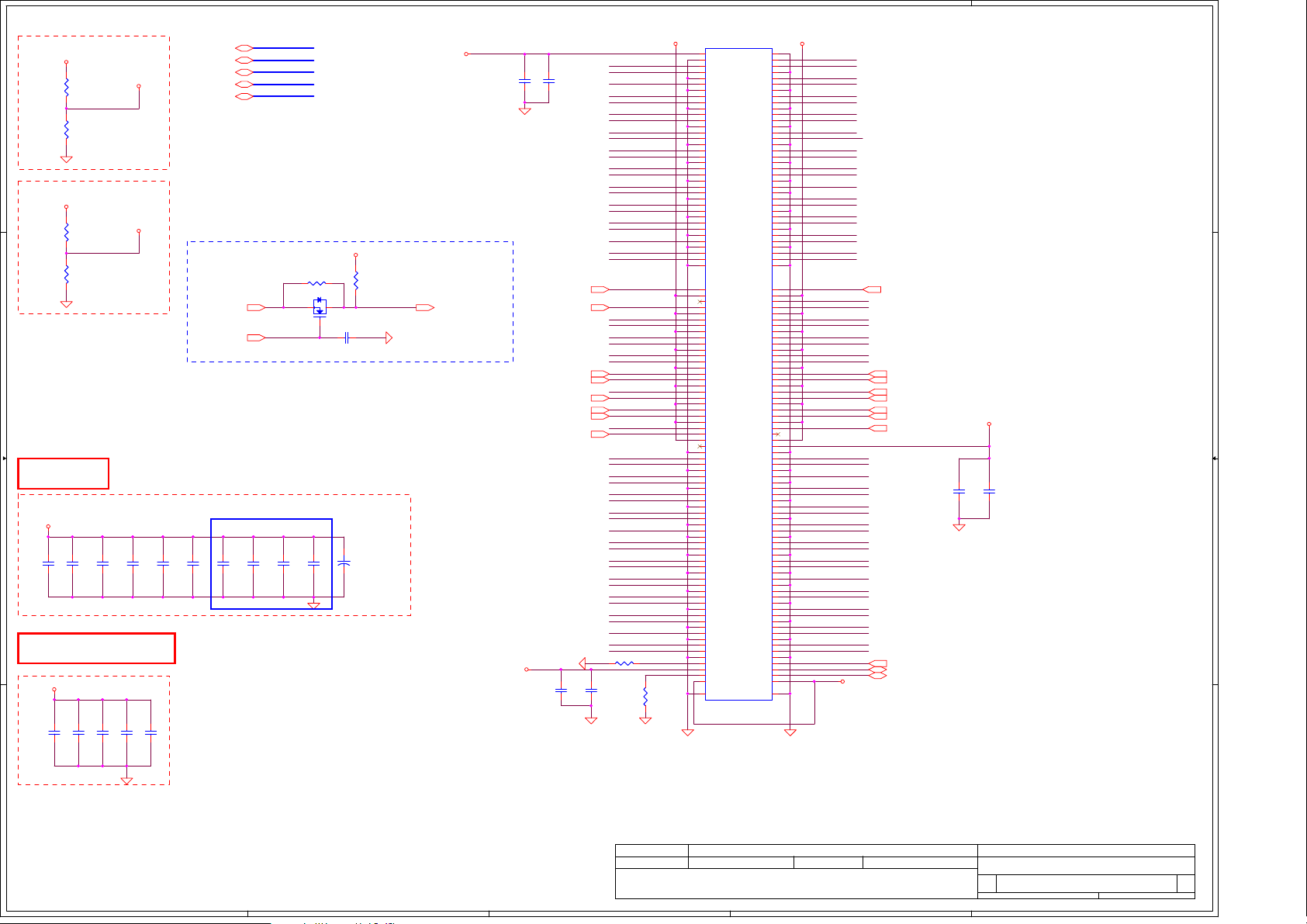

JCPU1A

JCPU1A

DMI_PTX_H RX_N0

DMI_PTX_H RX_N1

DMI_PTX_H RX_N2

DMI_PTX_H RX_N3

DMI_PTX_H RX_P0

DMI_PTX_H RX_P1

DMI_PTX_H RX_P2

H_FDI_INT(15)

DMI_PTX_H RX_P3

DMI_HTX_P RX_N0

DMI_HTX_P RX_N1

DMI_HTX_P RX_N2

DMI_HTX_P RX_N3

DMI_HTX_P RX_P0

DMI_HTX_P RX_P1

DMI_HTX_P RX_P2

DMI_HTX_P RX_P3

H_FDI_TXN 0

H_FDI_TXN 1

H_FDI_TXN 2

H_FDI_TXN 3

H_FDI_TXN 4

H_FDI_TXN 5

H_FDI_TXN 6

H_FDI_TXN 7

H_FDI_TXP 0

H_FDI_TXP 1

H_FDI_TXP 2

H_FDI_TXP 3

H_FDI_TXP 4

H_FDI_TXP 5

H_FDI_TXP 6

H_FDI_TXP 7

D D

C C

H_FDI_FSYNC0(15)

H_FDI_FSYNC1(15)

H_FDI_LSYNC0(15)

H_FDI_LSYNC1(15)

B B

A24

DMI_RX#[0]

C23

DMI_RX#[1]

B22

DMI_RX#[2]

A21

DMI_RX#[3]

B24

DMI_RX[0]

D23

DMI_RX[1]

B23

DMI_RX[2]

A22

DMI_RX[3]

D24

DMI_TX#[0]

G24

DMI_TX#[1]

F23

DMI_TX#[2]

H23

DMI_TX#[3]

D25

DMI_TX[0]

F24

DMI_TX[1]

E23

DMI_TX[2]

G23

DMI_TX[3]

E22

FDI_TX#[0]

D21

FDI_TX#[1]

D19

FDI_TX#[2]

D18

FDI_TX#[3]

G21

FDI_TX#[4]

E19

FDI_TX#[5]

F21

FDI_TX#[6]

G18

FDI_TX#[7]

D22

FDI_TX[0]

C21

FDI_TX[1]

D20

FDI_TX[2]

C18

FDI_TX[3]

G22

FDI_TX[4]

E20

FDI_TX[5]

F20

FDI_TX[6]

G19

FDI_TX[7]

F17

FDI_FSYNC[0]

E17

FDI_FSYNC[1]

C17

FDI_INT

F18

FDI_LSYNC[0]

D17

FDI_LSYNC[1]

IC,AUB_CFD _rPGA,R1P0

IC,AUB_CFD _rPGA,R1P0

CONN@

CONN@

DMI Intel(R) FDI

DMI Intel(R) FDI

PEG_ICOMPI

10mil

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

15mil

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

B26

A26

B27

A25

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

4

PEG_IRCOM P

EXP_RBIAS

R1419

R1419

1 2

R1420

R1420

1 2

3

49.9_040 2_1%

49.9_040 2_1%

750_040 2_1%

750_040 2_1%

6/22 remove unused pin net

DMI_PTX_H RX_N[0..3] (15)

DMI_PTX_H RX_P[0..3] (15)

DMI_HTX_P RX_N[0..3] (15)

DMI_HTX_P RX_P[0..3] (15)

H_FDI_TXN [0..7] (15)

H_FDI_TXP [0..7] (15)

CFG0

CFG3

CFG4

CFG7

2

JCPU1E

JCPU1E

AP25

RSVD1

AL25

RSVD2

AL24

RSVD3

AL22

RSVD4

AJ33

RSVD5

AG9

M27

H17

G25

G17

E31

E30

AM30

AM28

AP31

AL32

AL30

AM31

AN29

AM32

AK32

AK31

AK28

AJ28

AN30

AN32

AJ32

AJ29

AJ30

AK30

H16

B19

A19

A20

B20

AC9

AB9

A34

A33

C35

B35

L28

J17

U9

T9

C1

A3

J29

J28

RSVD6

RSVD7

RSVD8

SA_DIMM_VREF

SB_DIMM_VREF

RSVD11

RSVD12

RSVD13

RSVD14

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

RSVD_TP_86

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD_NCTF_23

RSVD_NCTF_24

RSVD26

RSVD27

RSVD_NCTF_28

RSVD_NCTF_29

RSVD_NCTF_30

RSVD_NCTF_31

(CFD Only)

(CFD Only)

RSVD_NCTF_37

RSVD_NCTF_40

RSVD_NCTF_41

RSVD_NCTF_42

RSVD_NCTF_43

RSVD_NCTF_54

RSVD_NCTF_55

RSVD_NCTF_56

RSVD_NCTF_57

RSVD_TP_59

RSVD_TP_60

RESERVED

RESERVED

RSVD_TP_66

RSVD_TP_67

RSVD_TP_68

RSVD_TP_69

RSVD_TP_70

RSVD_TP_71

RSVD_TP_72

RSVD_TP_73

RSVD_TP_74

RSVD_TP_75

RSVD_TP_76

RSVD_TP_77

RSVD_TP_78

RSVD_TP_79

RSVD_TP_80

RSVD_TP_81

RSVD_TP_82

RSVD_TP_83

RSVD_TP_84

RSVD_TP_85

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD38

RSVD39

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

RSVD53

RSVD58

KEY

RSVD62

RSVD63

RSVD64

RSVD65

VSS

AJ13

AJ12

AH25

AK26

AL26

AR2

AJ26

AJ27

AP1

AT2

AT3

AR1

AL28

AL29

AP30

AP32

AL27

AT31

AT32

AP33

AR33

AT33

AT34

AP35

AR35

AR32

E15

F15

A2

D15

C15

AJ15

AH15

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

AP34

1

IC,AUB_CFD _rPGA,R1P0

IC,AUB_CFD _rPGA,R1P0

CONN@

CONN@

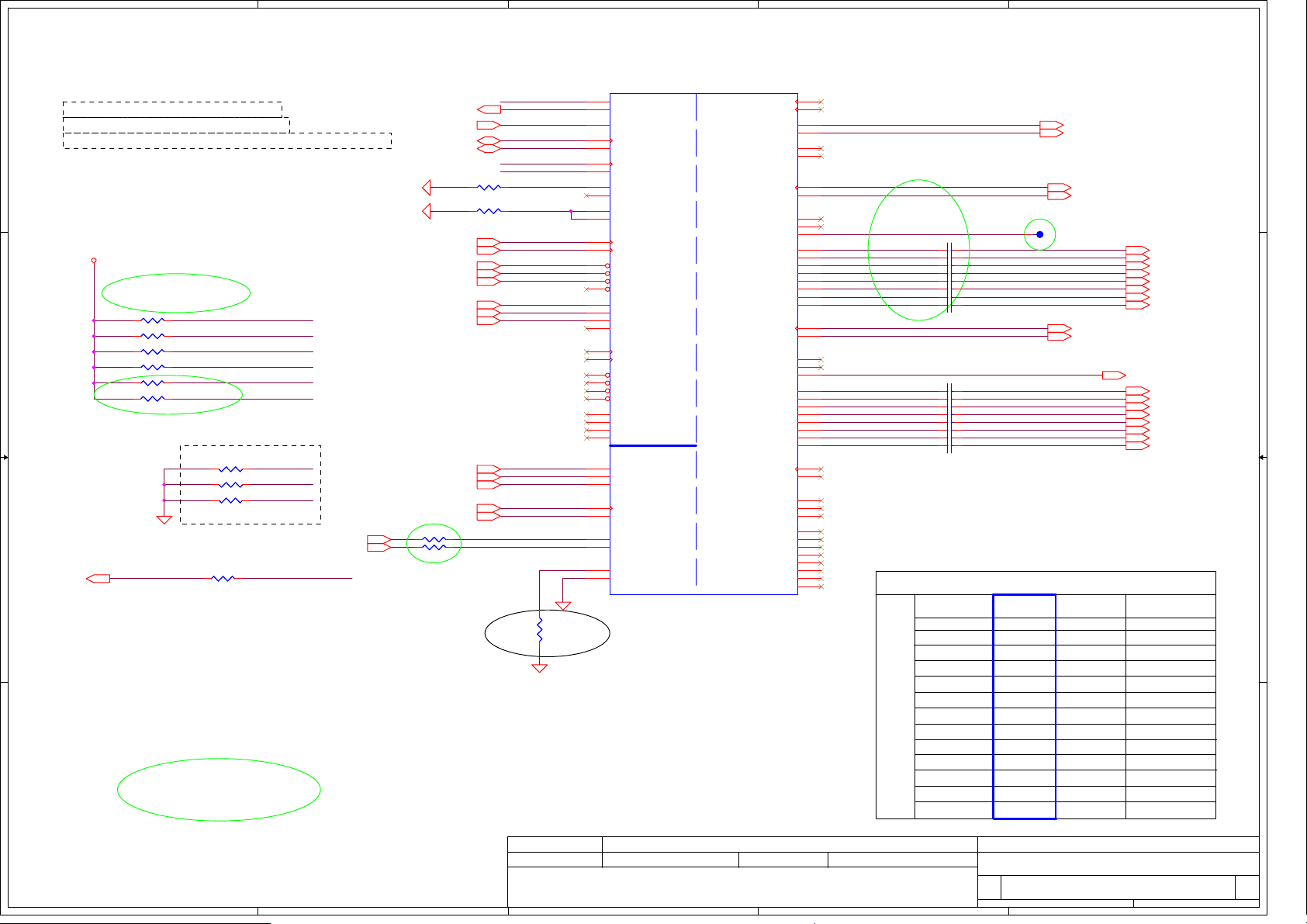

eDP Signals Mapping

eDP Singal

eDP_TX0

PEG Singals

PEG_HTX_C_GRX_P15

eDP_TX#0 PEG_HTX_C_GRX_N15

eDP_TX1 PEG_HTX_C_GRX_P14

eDP_TX#1

A A

eDP_TX2

eDP_TX#2

eDP_TX3

eDP_TX#3

eDP_AUX

eDP_AUX#

eDP_HPD#

PEG_HTX_C_GRX_N14

PEG_HTX_C_GRX_P13

PEG_HTX_C_GRX_N13

PEG_HTX_C_GRX_P12

PEG_HTX_C_GRX_N12

PEG_GTX_C_HRX_P13

PEG_GTX_C_HRX_N13

PEG_GTX_C_HRX_P12

5

Lane Reversal

PEG_HTX_C_GRX_P0

PEG_HTX_C_GRX_N0

PEG_HTX_C_GRX_P1

PEG_HTX_C_GRX_N1

PEG_HTX_C_GRX_P2

PEG_HTX_C_GRX_N2

PEG_HTX_C_GRX_P3

PEG_HTX_C_GRX_N3

PEG_GTX_C_HRX_P2

PEG_GTX_C_HRX_N2

PEG_GTX_C_HRX_P3

Security Class ification

Security Class ification

Security Class ification

2009/11/ 23 2010/11/ 23

2009/11/ 23 2010/11/ 23

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2009/11/ 23 2010/11/ 23

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

CFG0 - PCI-Express Configuration Select

*1:Single PEG

0:Bifurcation enabled

CFG3 - PCI-Express Static Lane Reversal

*1 :Normal Operation

0 :Lane Numbers Reversed

15 -> 0, 14 -> 1, ...

Deciphered Date

Deciphered Date

Deciphered Date

Title

Title

Title

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

CFG4 - Display Port Presence

*1:Disabled; No Physical Display Port

attached to Embedd ed Display Port

0:Enabled; An externa l Display Port

device is connected to the Emb edded

Display Port

*:Default

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

PROCESSOR (1/6) DMI,FDI,PEG

PROCESSOR (1/6) DMI,FDI,PEG

PROCESSOR (1/6) DMI,FDI,PEG

B

B

B

PAU30 M/B LA-6392P Schematic

PAU30 M/B LA-6392P Schematic

PAU30 M/B LA-6392P Schematic

1

1.0

1.0

1.0

4 51Monday, November 22, 2 010

4 51Monday, November 22, 2 010

4 51Monday, November 22, 2 010

5

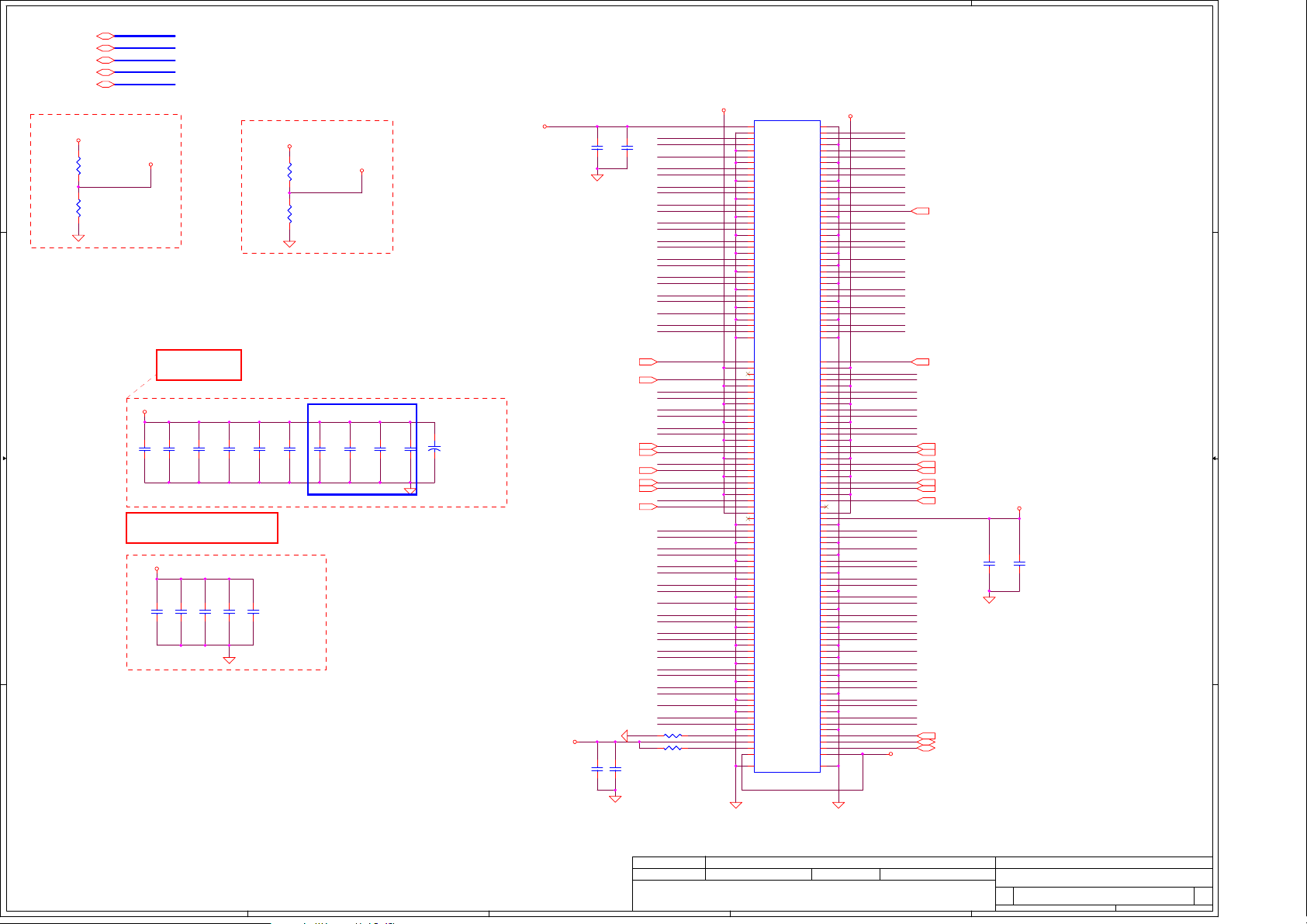

JCPU1B

R1421 20_0402 _1% R142 1 20_0402 _1%

R1422 20_0402 _1% R142 2 20_0402 _1%

R1423 49.9_040 2_1% R142 3 49.9_040 2_1%

R1424 49.9_040 2_1% R142 4 49.9_040 2_1%

D D

H_PECI(18)

H_PROCH OT#(47)

H_THERM TRIP#(18)

R1427

1 2

0_0402_ 5%

0_0402_ 5%

R1437

R1437

1 2

0_0402_ 5%

0_0402_ 5%

12

12

12

12

PAD

PAD

T48

T48

R142 7

del R1442 07/22

H_PM_SYNC(15)

R1443

R144 3

1 2

0_0402_ 5%

C C

H_CPUPW RGD(18)

PM_DRAM _PWRGD(15)

PLT_RST #(17)

2009/2/4

#414044 DG

Update Rev1.11

0_0402_ 5%

R1446

0_0402_ 5%

0_0402_ 5%

R1447

1 2

0_0402_ 5%

0_0402_ 5%

R1449

1 2

1.5K_040 2_1%

1.5K_040 2_1%

R144 6

1 2

R144 7

R14 49

H_COMP3

H_COMP2

H_COMP1

H_COMP0

SKTOCC# _R

@

@

H_CATER R#

H_PECI_R

H_PROCH OT#

H_THERM TRIP#_R

H_CPURS T#

H_CPUPW RGD_1

H_CPUPW RGD_0

PM_DRAM _PWRGD_R

H_VTTPW RGD_R

H_PW RGD_XDP_R

PLT_RST #_R

12

R1450

R1450

750_040 2_1%

750_040 2_1%

JCPU1B

AT23

AT24

G16

AT26

AH24

AK14

AT15

AN26

AK15

AP26

AL15

AN14

AN27

AK13

AM15

AM26

AL14

IC,AUB_CFD _rPGA,R1P0

IC,AUB_CFD _rPGA,R1P0

CONN@

CONN@

4

COMP3

COMP2

COMP1

COMP0

SKTOCC#

CATERR#

PECI

PROCHOT#

THERMTRIP#

RESET_OBS#

PM_SYNC

VCCPWRGOOD_1

VCCPWRGOOD_0

SM_DRAMPWROK

VTTPWRGOOD

TAPPWRGOOD

RSTIN#

MISC THERMAL

MISC THERMAL

DPLL_REF_SSCLK#

CLOCKS

CLOCKS

DDR3

MISC

DDR3

MISC

PWR MANAGEMENT

PWR MANAGEMENT

JTAG & BPM

JTAG & BPM

BCLK

BCLK#

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

DPLL_REF_SSCLK

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PM_EXT_TS#[0]

PM_EXT_TS#[1]

PRDY#

PREQ#

TCK

TMS

TRST#

TDO

TDI_M

TDO_M

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

TDI

A16

B16

AR30

AT30

E16

D16

A18

A17

F6

AL1

AM1

AN1

AN15

AP15

AT28

AP27

AN28

AP28

AT27

AT29

AR27

AR29

AP29

AN25

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

3

CLK_CPU _DP_R

CLK_CPU _DP#_R

SM_RCOM P_0

SM_RCOM P_1

SM_RCOM P_2

PM_EXTT S#0

PM_EXTT S#1_R

XDP_PRD Y#

XDP_PRE Q#

XDP_TCL K

XDP_TMS

XDP_TRS T#

XDP_TDI_R

XDP_TDO _R

XDP_TDI_M

XDP_TDO _M

XDP_DBR #_R

CLK_CPU _BCLK (18)

CLK_CPU _BCLK# (18)

CLK_CPU _XDP

CLK_CPU _XDP#

CLK_CPU _DMI (14)

CLK_CPU _DMI# (14)

R1445 0_0402_ 5% R1445 0_0402_ 5%

1 2

XDP_OBS 0

XDP_OBS 1

XDP_OBS 2

XDP_OBS 3

XDP_OBS 4

XDP_OBS 5

XDP_OBS 6

XDP_OBS 7

T55 PAD @T55 P AD@

T56 PAD @T56 P AD@

SM_DRAM RST# (10)

1 2

R1429 10 0K_0402_5%

R1429 10 0K_0402_5%

R1433 10K_040 2_5% R143 3 10K_040 2_5%

1 2

R1435 10K_040 2_5% R143 5 10K_040 2_5%

1 2

R1436 0_0402_ 5% R1436 0_0402_ 5%

1 2

SM_RCOM P_0

SM_RCOM P_1

SM_RCOM P_2

R1439 100_040 2_1% R1439 100_040 2_1%

R1440 24.9_040 2_1% R144 0 24.9_040 2_1%

R1441 130_040 2_1% R1441 130_040 2_1%

XDP_DBR ESET#

2

5/26 add test point

2009/08/14 #4253 02

CP_S3PowerReduction

WhitePaper_Rev1 .0

+1.05VS_ VTT_CPU

PM_EXTT S#0_1 (10,11)

1 2

1 2

1 2

XDP_DBR ESET# (15)

2009/08/14

remove DP REF SSCLK

CLK_CPU _DP_R

CLK_CPU _DP#_R

XDP_PRD Y#

XDP_TMS

XDP_TDI_R

XDP_PRE Q#

XDP_TCL K

XDP_TRS T#

XDP_TDO _M

XDP_TDI_M

R1425 0_0402_ 5% R1425 0_0402_ 5%

R1426 0_0402_ 5% R1426 0_0402_ 5%

1 2

1 2

R1428 51_0402 _5%@R1428 51_0402 _5%@

1 2

R1430 51_0402 _5%@R1430 51_0402 _5%@

1 2

R1431 51_0402 _5%@R1431 51_0402 _5%@

1 2

R1432 51_0402 _5%@R1432 51_0402 _5%@

1 2

R1434 51_0402 _5%@R1434 51_0402 _5%@

1 2

R1438 51_0402 _5% R1438 51_04 02_5%

1 2

12

R1444

R1444

0_0402_ 5%

0_0402_ 5%

1

+1.05VS_ VTT_CPU

B B

H_VTTPW RGD(31,45)

#425302

CP_S3PowerReduction

WhitePaper_Rev0.7

H_VTTPW RGD

MC74VHC 1G08DFT2G_SC 70-5

MC74VHC 1G08DFT2G_SC 70-5

6/2 remove R1456

A A

PM_DRAM _PWRGD_R

5

U103

U103

2

1

12

R1457

R1457

1.5K_040 2_1%

1.5K_040 2_1%

12

R1459

R1459

750_040 2_1%

750_040 2_1%

+3VALW

5

P

B

Y

A

G

3

+3VALW

5

P

B

4

Y

A

G

MC74VHC 1G08DFT2G_SC 70-5

MC74VHC 1G08DFT2G_SC 70-5

3

2009/04/23

Intel CRB 1.55 Update

Change R393 to 1.1K_1%, R394 to 3.01K_1%

4

1 2

R1454 2K_0402 _1%

R1454 2K_0402 _1%

U104

U104

H_VTTPW RGD

2

1

H_VTTPW RGD_R

12

R1455

R1455

1K_0402 _1%

1K_0402 _1%

4

+1.05VS_ VTT_CPU

R1451 49.9_ 0402_1% R1451 49.9_ 0402_1%

R1452 68_0 402_5% R1452 68_0 402_5%

R1453 68_0 402_5%@R145 3 6 8_0402_5%@

R1492 51_0 402_5%R1492 51_0 402_5%

Security Class ification

Security Class ification

Security Class ification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1 2

12

12

12

H_CATER R#

H_PROCH OT#

H_CPURS T#

XDP_TDO _R

Compal Secret Data

Compal Secret Data

2009/11/ 23 2010/11/ 23

2009/11/ 23 2010/11/ 23

2009/11/ 23 2010/11/ 23

3

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

PROCESSOR (2/6) CLK,JTAG

PROCESSOR (2/6) CLK,JTAG

PROCESSOR (2/6) CLK,JTAG

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

B

B

B

PAU30 M/B LA-6392P Schematic

PAU30 M/B LA-6392P Schematic

PAU30 M/B LA-6392P Schematic

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

5 51Monday, November 22, 2 010

5 51Monday, November 22, 2 010

5 51Monday, November 22, 2 010

1

1.0

1.0

1.0

5

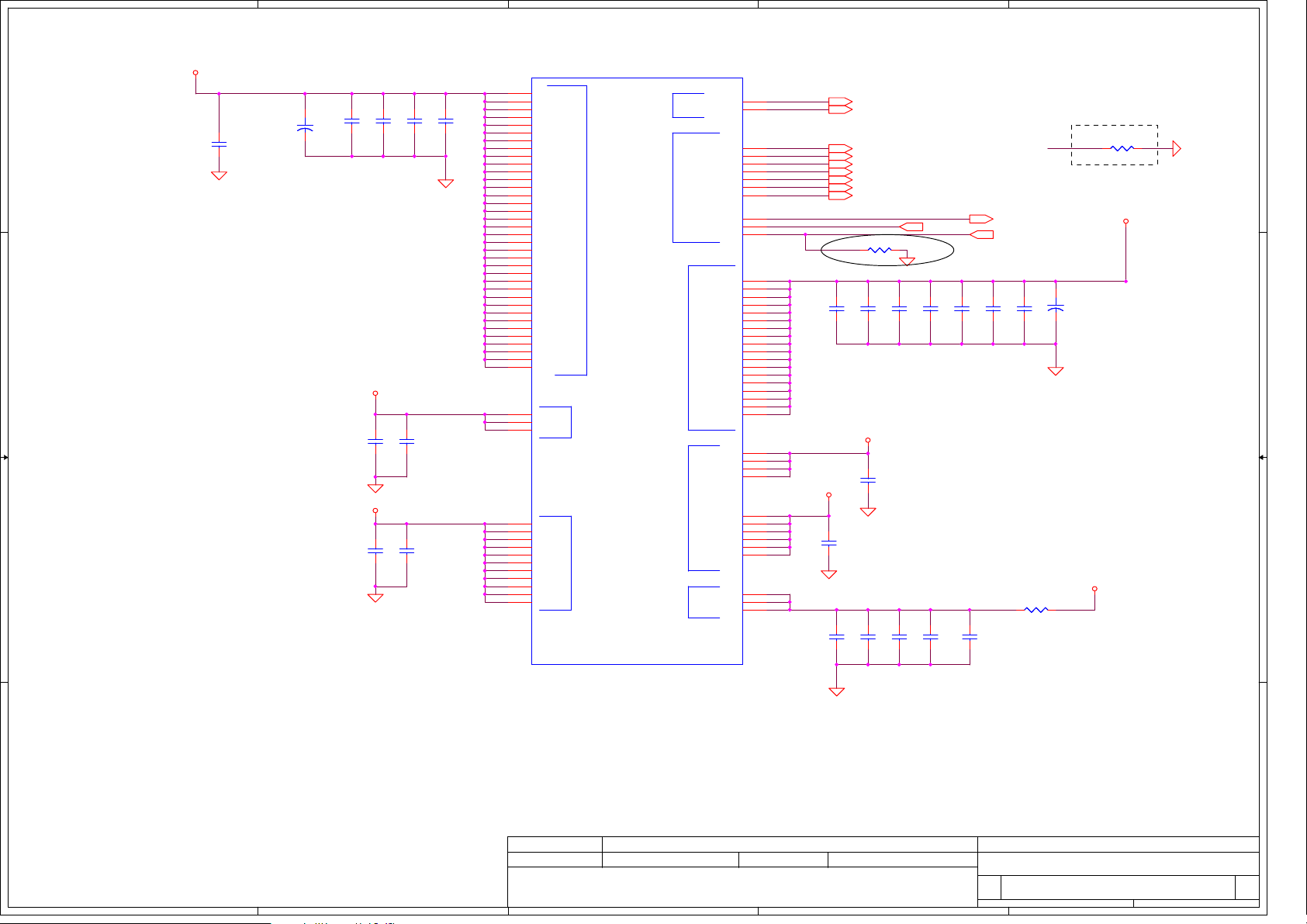

JCPU1C

C10

D10

H10

G10

AH5

AF5

AK6

AK7

AF6

AG5

AJ10

AL10

AK12

AK8

AK11

AN8

AM10

AR11

AL11

AM9

AN9

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

AC3

AB2

AE1

AB3

AE9

A10

B10

E10

F10

J10

AJ7

AJ6

AJ9

AL7

AL8

G8

G7

M6

M8

C7

A7

A8

D8

E6

F7

E9

B7

E7

C6

K7

J8

J7

L7

L9

L6

K8

N8

P9

U7

JCPU1C

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

DDR_A_D [0..63](10)

DDR_A_D M[0..7](10)

DDR_A_D QS#[0..7](10)

DDR_A_D QS[0..7](10)

DDR_A_M A[0..15](10)

DDR_A_D 0

DDR_A_D 1

D D

C C

B B

DDR_A_B S0(10)

DDR_A_B S1(10)

DDR_A_B S2(10)

DDR_A_C AS#(10)

DDR_A_R AS#(10)

DDR_A_W E#(10)

DDR_A_D 2

DDR_A_D 3

DDR_A_D 4

DDR_A_D 5

DDR_A_D 6

DDR_A_D 7

DDR_A_D 8

DDR_A_D 9

DDR_A_D 10

DDR_A_D 11

DDR_A_D 12

DDR_A_D 13

DDR_A_D 14

DDR_A_D 15

DDR_A_D 16

DDR_A_D 17

DDR_A_D 18

DDR_A_D 19

DDR_A_D 20

DDR_A_D 21

DDR_A_D 22

DDR_A_D 23

DDR_A_D 24

DDR_A_D 25

DDR_A_D 26

DDR_A_D 27

DDR_A_D 28

DDR_A_D 29

DDR_A_D 30

DDR_A_D 31

DDR_A_D 32

DDR_A_D 33

DDR_A_D 34

DDR_A_D 35

DDR_A_D 36

DDR_A_D 37

DDR_A_D 38

DDR_A_D 39

DDR_A_D 40

DDR_A_D 41

DDR_A_D 42

DDR_A_D 43

DDR_A_D 44

DDR_A_D 45

DDR_A_D 46

DDR_A_D 47

DDR_A_D 48

DDR_A_D 49

DDR_A_D 50

DDR_A_D 51

DDR_A_D 52

DDR_A_D 53

DDR_A_D 54

DDR_A_D 55

DDR_A_D 56

DDR_A_D 57

DDR_A_D 58

DDR_A_D 59

DDR_A_D 60

DDR_A_D 61

DDR_A_D 62

DDR_A_D 63

DDR_A_B S0

DDR_A_B S1

DDR_A_B S2

DDR_A_C AS#

DDR_A_R AS#

DDR_A_W E#

SA_CK[0]

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

4

AA6

AA7

P7

Y6

Y5

P6

AE2

AE8

AD8

AF9

B9

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

DDR_A_D M0

DDR_A_D M1

DDR_A_D M2

DDR_A_D M3

DDR_A_D M4

DDR_A_D M5

DDR_A_D M6

DDR_A_D M7

DDR_A_D QS#0

DDR_A_D QS#1

DDR_A_D QS#2

DDR_A_D QS#3

DDR_A_D QS#4

DDR_A_D QS#5

DDR_A_D QS#6

DDR_A_D QS#7

DDR_A_D QS0

DDR_A_D QS1

DDR_A_D QS2

DDR_A_D QS3

DDR_A_D QS4

DDR_A_D QS5

DDR_A_D QS6

DDR_A_D QS7

DDR_A_M A0

DDR_A_M A1

DDR_A_M A2

DDR_A_M A3

DDR_A_M A4

DDR_A_M A5

DDR_A_M A6

DDR_A_M A7

DDR_A_M A8

DDR_A_M A9

DDR_A_M A10

DDR_A_M A11

DDR_A_M A12

DDR_A_M A13

DDR_A_M A14

DDR_A_M A15

DDR_A_C LK0 (10)

DDR_A_C LK0# (10)

DDR_A_C KE0 (10)

DDR_A_C LK1 (10)

DDR_A_C LK1# (10)

DDR_A_C KE1 (10)

DDR_A_C S0# (10)

DDR_A_C S1# (10)

DDR_A_O DT0 (10 )

DDR_A_O DT1 (10 )

3

JCPU1D

AF3

AG1

AK1

AG4

AG3

AH4

AK3

AK4

AM6

AN2

AK5

AK2

AM4

AM3

AP3

AN5

AT4

AN6

AN4

AN3

AT5

AT6

AN7

AP6

AP8

AT9

AT7

AP9

AR10

AT10

AB1

AC5

AC6

JCPU1D

B5

A5

C3

B3

E4

A6

A4

C4

D1

D2

F2

F1

C2

F5

F3

G4

H6

G2

J6

J3

G1

G5

J2

J1

J5

K2

L3

M1

K5

K4

M4

N5

AJ3

AJ4

W5

R7

Y7

DDR_B_D [0..63](11)

DDR_B_D M[0..7](11)

DDR_B_D QS#[0..7](11)

DDR_B_D QS[0..7](11)

DDR_B_M A[0..15](11)

DDR_B_D 0

DDR_B_D 1

DDR_B_D 2

DDR_B_D 3

DDR_B_D 4

DDR_B_D 5

DDR_B_D 6

DDR_B_D 7

DDR_B_D 8

DDR_B_D 9

DDR_B_D 10

DDR_B_D 11

DDR_B_D 12

DDR_B_D 13

DDR_B_D 14

DDR_B_D 15

DDR_B_D 16

DDR_B_D 17

DDR_B_D 18

DDR_B_D 19

DDR_B_D 20

DDR_B_D 21

DDR_B_D 22

DDR_B_D 23

DDR_B_D 24

DDR_B_D 25

DDR_B_D 26

DDR_B_D 27

DDR_B_D 28

DDR_B_D 29

DDR_B_D 30

DDR_B_D 31

DDR_B_D 32

DDR_B_D 33

DDR_B_D 34

DDR_B_D 35

DDR_B_D 36

DDR_B_D 37

DDR_B_D 38

DDR_B_D 39

DDR_B_D 40

DDR_B_D 41

DDR_B_D 42

DDR_B_D 43

DDR_B_D 44

DDR_B_D 45

DDR_B_D 46

DDR_B_D 47

DDR_B_D 48

DDR_B_D 49

DDR_B_D 50

DDR_B_D 51

DDR_B_D 52

DDR_B_D 53

DDR_B_D 54

DDR_B_D 55

DDR_B_D 56

DDR_B_D 57

DDR_B_D 58

DDR_B_D 59

DDR_B_D 60

DDR_B_D 61

DDR_B_D 62

DDR_B_D 63

DDR_B_B S0(11)

DDR_B_B S1(11)

DDR_B_B S2(11)

DDR_B_C AS#(11)

DDR_B_R AS#(11)

DDR_B_W E#(11)

DDR_B_BS0

DDR_B_B S1

DDR_B_B S2

DDR_B_C AS#

DDR_B_R AS#

DDR_B_W E#

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

2

SB_CK[0]

SB_CK#[0]

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

DDR SYSTEM MEMORY - B

DDR SYSTEM MEMORY - B

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

W8

W9

M3

V7

V6

M2

AB8

AD6

AC7

AD1

D4

E1

H3

K1

AH1

AL2

AR4

AT8

D5

F4

J4

L4

AH2

AL4

AR5

AR8

C5

E3

H4

M5

AG2

AL5

AP5

AR7

U5

V2

T5

V3

R1

T8

R2

R6

R4

R5

AB5

P3

R3

AF7

P5

N1

DDR_B_D M0

DDR_B_D M1

DDR_B_D M2

DDR_B_D M3

DDR_B_D M4

DDR_B_D M5

DDR_B_D M6

DDR_B_D M7

DDR_B_D QS#0

DDR_B_D QS#1

DDR_B_D QS#2

DDR_B_D QS#3

DDR_B_D QS#4

DDR_B_D QS#5

DDR_B_D QS#6

DDR_B_D QS#7

DDR_B_D QS0

DDR_B_D QS1

DDR_B_D QS2

DDR_B_D QS3

DDR_B_D QS4

DDR_B_D QS5

DDR_B_D QS6

DDR_B_D QS7

DDR_B_M A0

DDR_B_M A1

DDR_B_M A2

DDR_B_M A3

DDR_B_M A4

DDR_B_M A5

DDR_B_M A6

DDR_B_M A7

DDR_B_M A8

DDR_B_M A9

DDR_B_M A10

DDR_B_M A11

DDR_B_M A12

DDR_B_M A13

DDR_B_M A14

DDR_B_M A15

1

DDR_B_C LK0 (11)

DDR_B_C LK0# (11)

DDR_B_C KE0 (11)

DDR_B_C LK1 (11)

DDR_B_C LK1# (11)

DDR_B_C KE1 (11)

DDR_B_C S0# (11)

DDR_B_C S1# (11)

DDR_B_O DT0 (11 )

DDR_B_O DT1 (11 )

IC,AUB_CFD _rPGA,R1P0

IC,AUB_CFD _rPGA,R1P0

CONN@

CONN@

A A

Security Class ification

Security Class ification

Security Class ification

2009/11/ 23 2010/11/ 23

2009/11/ 23 2010/11/ 23

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2009/11/ 23 2010/11/ 23

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

IC,AUB_CFD _rPGA,R1P0

IC,AUB_CFD _rPGA,R1P0

CONN@

CONN@

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

PROCESSOR (3/6) DDRIII

PROCESSOR (3/6) DDRIII

PROCESSOR (3/6) DDRIII

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

B

B

B

Date: Sheet

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

PAU30 M/B LA-6392P Schematic

PAU30 M/B LA-6392P Schematic

PAU30 M/B LA-6392P Schematic

1

of

6 51Monday, November 22, 2 010

6 51Monday, November 22, 2 010

6 51Monday, November 22, 2 010

1.0

1.0

1.0

5

JCPU1F

JCPU1F

W15 MOW

+CPU_CORE

W

48A Continuous 18A

AG35

VCC1

AG34

VCC2

AG33

VCC3

AG32

D D

C C

B B

A A

5

VCC4

AG31

VCC5

AG30

VCC6

AG29

VCC7

AG28

VCC8

AG27

VCC9

AG26

VCC10

AF35

VCC11

AF34

VCC12

AF33

VCC13

AF32

VCC14

AF31

VCC15

AF30

VCC16

AF29

VCC17

AF28

VCC18

AF27

VCC19

AF26

VCC20

AD35

VCC21

AD34

VCC22

AD33

VCC23

AD32

VCC24

AD31

VCC25

AD30

VCC26

AD29

VCC27

AD28

VCC28

AD27

VCC29

AD26

VCC30

AC35

VCC31

AC34

VCC32

AC33

VCC33

AC32

VCC34

AC31

VCC35

AC30

VCC36

AC29

VCC37

AC28

VCC38

AC27

VCC39

AC26

VCC40

AA35

VCC41

AA34

VCC42

AA33

VCC43

AA32

VCC44

AA31

VCC45

AA30

VCC46

AA29

VCC47

AA28

VCC48

AA27

VCC49

AA26

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

IC,AUB_CFD_rPGA,R1P0

IC,AUB_CFD_rPGA,R1P0

CONN@

CONN@

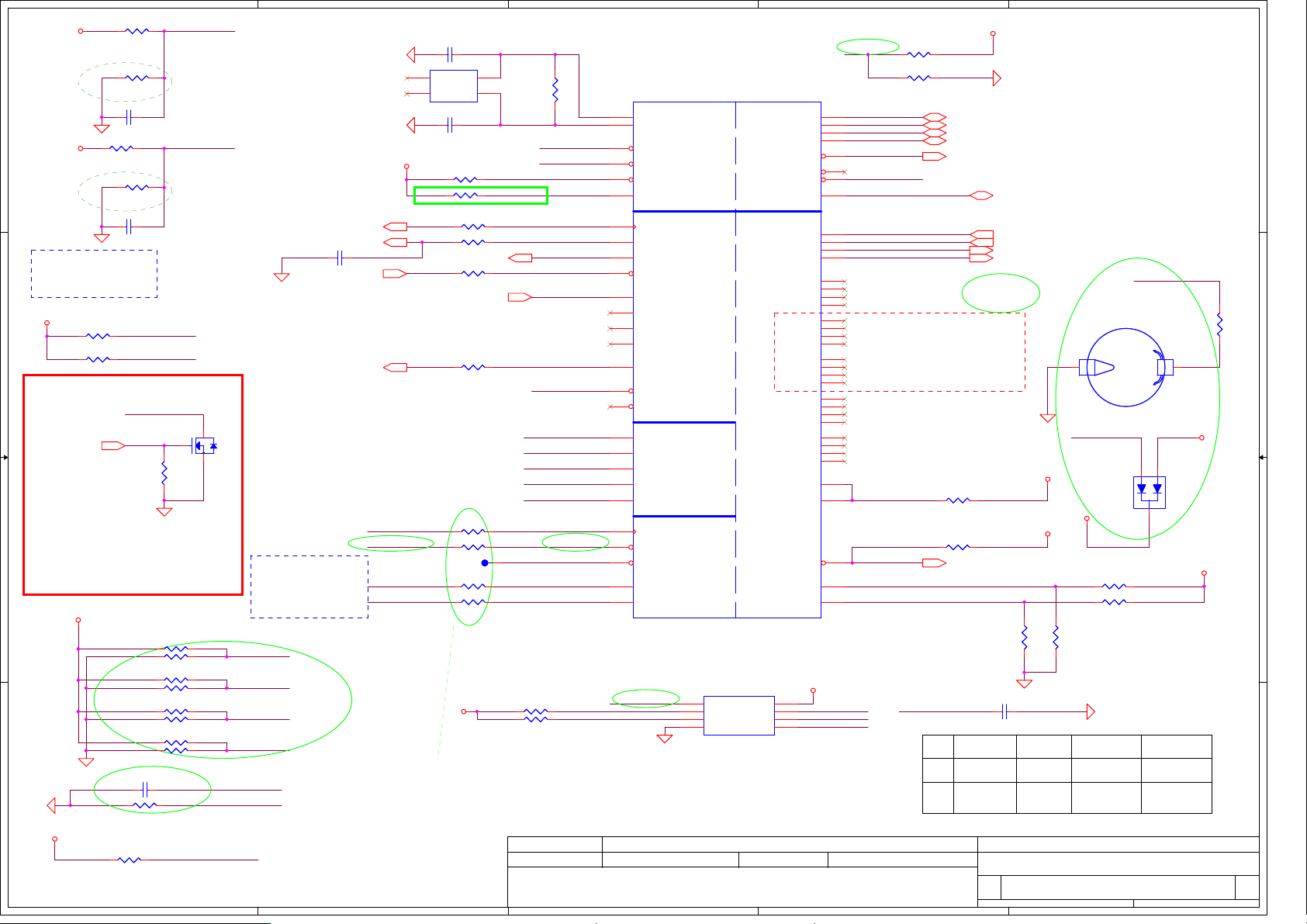

1.1V RAIL POWER

1.1V RAIL POWER

CPU CORE SUPPLY

CPU CORE SUPPLY

POWER

POWER

CPU VIDS

CPU VIDS

SENSE LINES

SENSE LINES

Peak 21A

VTT0_1

VTT0_2

VTT0_3

VTT0_4

VTT0_5

VTT0_6

VTT0_7

VTT0_8

VTT0_9

VTT0_10

VTT0_11

VTT0_12

VTT0_13

VTT0_14

VTT0_15

VTT0_16

VTT0_17

VTT0_18

VTT0_19

VTT0_20

VTT0_21

VTT0_22

VTT0_23

VTT0_24

VTT0_25

VTT0_26

VTT0_27

VTT0_28

VTT0_29

VTT0_30

VTT0_31

VTT0_32

VTT0_33

VTT0_34

VTT0_35

VTT0_36

VTT0_37

VTT0_38

VTT0_39

VTT0_40

VTT0_41

VTT0_42

VTT0_43

VTT0_44

PSI#

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

PROC_DPRSLPVR

VTT_SELECT

ISENSE

VCC_SENSE

VSS_SENSE

VTT_SENSE

VSS_SENSE_VTT

4

AH14

AH12

AH11

AH10

J14

J13

H14

H12

G14

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

AN33

AK35

AK33

AK34

AL35

AL33

AM33

AM35

AM34

H_VTTVID1

G15

H_VTTVID1 = low, 1.1V

H_VTTVID1 = high, 1.05V

AN35

VCCSENSE_R

AJ34

VSSSENSE_R

AJ35

B15

VSS_SENSE_VTT

A15

4

10U_0805_6.3V6M

1

C1344

C1344

2

10U_0805_6.3V6M

10U_0805_6.3V6M

+1.05VS_VTT_CPU

+

+

1

2

1 2

10U_0805_6.3V6M

1

C1345

C1345

2

1

+

+

C1360

C1360

330U_D2_2V_Y

330U_D2_2V_Y

2

+1.05VS_VTT_CPU

VTT_SENSE (45)

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C1343

C1343

2

10U_0805_6.3V6M

10U_0805_6.3V6M

C1359,C1360 change to ESR9 6/29

330U_D2_2V_Y

330U_D2_2V_Y

1

C1359

C1359

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C1375

C1375

C1374

C1374

2

22U_0805_6.3V6M

22U_0805_6.3V6M

T49

@ T49

@

PAD

PAD

IMVP_IMON (47)

R1479 0_0402_5% R1479 0_0402_5%

1 2

R1480 0_0402_5% R1480 0_0402_5%

1 2

R1482 0_0402_5%R1482 0_0402_5%

10U_0805_6.3V6M

10U_0805_6.3V6M

1

1

C1346

C1346

C1347

C1347

<BOM Structure>

<BOM Structure>

2

2

10U_0805_6.3V6M

10U_0805_6.3V6M

H_PSI# (47)

CPU_VID0 (47)

CPU_VID1 (47)

CPU_VID2 (47)

CPU_VID3 (47)

CPU_VID4 (47)

CPU_VID5 (47)

CPU_VID6 (47)

H_DPRSLPVR (47)

R1478 100_0402_1%

R1478 100_0402_1%

VCCSENSE

VSSSENSE

R1481 100_0402_1%

R1481 100_0402_1%

VTT Rail

Auburndale +1.1VS_VTT=1.05V

Clarksfield +1.1VS_VTT=1.1V

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTOD Y OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTRO NICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTRO NICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

DEPARTMENT EXCE PT AS AUTHORIZED BY COMPAL ELECTRO NICS, INC. NEITHER THIS SHEET NOR T HE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

+1.05VS_VTT_CPU

1

1

C1348

C1348

C1349

C1349

2

2

10U_0805_6.3V6M

10U_0805_6.3V6M

CSC (Current Sense Configuration)

8/25

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPU_VID5

CPU_VID6

H_DPRSLPVR

H_PSI#

1 2

1 2

3

R1460 1K_0402 _1% R1460 1K_0402 _1%

1 2

R1461 1K_0402 _1%@R1461 1K_0402_1%@

1 2

R1462 1K_0402 _1% R1462 1K_0402 _1%

1 2

R1463 1K_0402 _1%@R1463 1K_0402_1%@

1 2

R1464 1K_0402 _1% R1464 1K_0402 _1%

1 2

R1465 1K_0402 _1%@R1465 1K_0402_1%@

1 2

R1466 1K_0402 _1%@R1466 1K_0402_1%@

1 2

R1467 1K_0402 _1% R1467 1K_0402 _1%

1 2

R1468 1K_0402 _1%@R1468 1K_0402_1%@

1 2

R1469 1K_0402 _1% R1469 1K_0402 _1%

1 2

R1470 1K_0402 _1% R1470 1K_0402 _1%

1 2

R1471 1K_0402 _1%@R1471 1K_0402_1%@

1 2

R1472 1K_0402 _1%@R1472 1K_0402_1%@

1 2

R1473 1K_0402 _1% R1473 1K_0402 _1%

1 2

R1474 1K_0402 _1% R1474 1K_0402 _1%

1 2

R1475 1K_0402 _1%@R1475 1K_0402_1%@

1 2

R1476 1K_0402 _1%@R1476 1K_0402_1%@

1 2

R1477 1K_0402 _1% R1477 1K_0402 _1%

1 2

+CPU_CORE

VCCSENSE (47)

VSSSENSE (47)

Compal Secret Data

Compal Secret Data

2009/11/23 2010/11/23

2009/11/23 2010/11/23

2009/11/23 2010/11/23

Compal Secret Data

+CPU_CORE

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C1350

C1350

2

+1.05VS_VTT_CPU

Deciphered Date

Deciphered Date

Deciphered Date

1

C1351

C1351

2

10U_0805_6.3V6M

10U_0805_6.3V6M

330U_D2_2V_Y

330U_D2_2V_Y

2

+CPU-CORE

Decoupling

SPCAP,Polymer

MLCC 0805 X5R

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C1352

C1352

2

(Place these capacitors between inductor and socket on Bottom)

+CPU_CORE

1

C1361

C1361

2

10U_0805_6.3V6M

10U_0805_6.3V6M

+CPU_CORE

1

C1368

C1368

2

22U_0805_6.3V6M

22U_0805_6.3V6M

+CPU_CORE

1

C1376

C1376

2

22U_0805_6.3V6M

22U_0805_6.3V6M

+CPU_CORE

1

+

+

C1382

C1382

@

@

2

2

C,uF

4X470uF 4m ohm/4

16X22uF

ESR, mohm

3m ohm/12

Stuffing Option

2X470uF

16X10uF 3m ohm/16

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C1353

2

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C1362

2

(Place these capacitors under CPU socket, top layer)

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C1369

C1369

2

(Place these capacitors on CPU cavity, Bottom Layer)

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C1377

C1377

2

(Place these capacitors on CPU cavity, Bottom Layer)

C1353

C1354

C1362

C1363

10U_0805_6.3V6M

10U_0805_6.3V6M

C1370

C1370

22U_0805_6.3V6M

22U_0805_6.3V6M

C1378

C1378

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C1354

2

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C1363

2

1

C1371

2

1

2

10U_0805_6.3V6M

1

C1355

C1355

2

1

C1364

C1364

2

10U_0805_6.3V6M

10U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C1371

2

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C1379

C1379

2

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C1356

2

1

C1365

2

1

C1372

C1372

2

1

C1380

C1380

2

4 x 470uF(4.5mohm@100kHz; 4.0mohm@SRF)

1

+

+

C1383

C1383

2

330U_D2_2V_Y

330U_D2_2V_Y

TOP side (under inductor)

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

+

+

C1384

C1384

2

330U_D2_2V_Y

330U_D2_2V_Y

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

PROCESSOR (4/6) PWR,Bypass

PROCESSOR (4/6) PWR,Bypass

PROCESSOR (4/6) PWR,Bypass

PAU30 M/B LA-6392P Schematic

PAU30 M/B LA-6392P Schematic

PAU30 M/B LA-6392P Schematic

330U_D2_2V_Y

330U_D2_2V_Y

1

C1356

C1357

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

10U_0805_6.3V6M

C1365

C1366

22U_0805_6.3V6M

22U_0805_6.3V6M

C1373

C1373

22U_0805_6.3V6M

22U_0805_6.3V6M

C1381

C1381

1

+

+

C1385

C1385

2

1

1

C1357

2

1

C1366

2

1

2

1

2

330U_D2_2V_Y

330U_D2_2V_Y

7 51Monday, November 22, 2010

7 51Monday, November 22, 2010

7 51Monday, November 22, 2010

10U_0805_6.3V6M

10U_0805_6.3V6M

1

C1358

C1358

2

1

C1367

C1367

2

10U_0805_6.3V6M

10U_0805_6.3V6M

1

+

+

C1386

C1386

2

1.0

1.0

1.0

5

4

3

2

1

+VGFX_C ORE

10U_080 5_6.3V6M

22U_080 5_6.3V6M

22U_080 5_6.3V6M

10U_080 5_6.3V6M

10U_080 5_6.3V6M

D D

C C

B B

C1470

C1470

1

2

C1388

C1388

330U_D2 _2V_Y

330U_D2 _2V_Y

1

1

C1389

C1389

+

+

2

2

22U_080 5_6.3V6M

22U_080 5_6.3V6M

C1400

C1400

22U_080 5_6.3V6M

22U_080 5_6.3V6M

C1404

C1404

22U_080 5_6.3V6M

22U_080 5_6.3V6M

C1390

C1390

+1.05VS_ VTT_CPU

1

2

+1.05VS_ VTT_CPU

1

2

10U_080 5_6.3V6M

1

1

C1391

C1391

C1387

C1387

2

2

10U_080 5_6.3V6M

10U_080 5_6.3V6M

1

C1401

C1401

22U_080 5_6.3V6M

22U_080 5_6.3V6M

2

1

C1405

C1405

22U_080 5_6.3V6M

22U_080 5_6.3V6M

2

1

2

JCPU1G

JCPU1G

AT21

VAXG1

AT19

VAXG2

AT18

VAXG3

AT16

VAXG4

AR21

VAXG5

AR19

VAXG6

AR18

VAXG7

AR16

VAXG8

AP21

VAXG9

AP19

VAXG10

AP18

VAXG11

AP16

VAXG12

AN21

VAXG13

AN19

VAXG14

AN18

VAXG15

AN16

VAXG16

AM21

VAXG17

AM19

VAXG18

AM18

VAXG19

AM16

VAXG20

AL21

VAXG21

AL19

VAXG22

AL18

VAXG23

AL16

VAXG24

AK21

VAXG25

AK19

VAXG26

AK18

VAXG27

AK16

VAXG28

AJ21

VAXG29

AJ19

VAXG30

AJ18

VAXG31

AJ16

VAXG32

AH21

VAXG33

AH19

VAXG34

AH18

VAXG35

AH16

VAXG36

J24

VTT1_45

J23

VTT1_46

H25

VTT1_47

K26

VTT1_48

J27

VTT1_49

J26

VTT1_50

J25

VTT1_51

H27

VTT1_52

G28

VTT1_53

G27

VTT1_54

G26

VTT1_55

F26

VTT1_56

E26

VTT1_57

E25

VTT1_58

IC,AUB_CFD _rPGA,R1P0

IC,AUB_CFD _rPGA,R1P0

CONN@

CONN@

15A

GRAPHICS

GRAPHICS

FDI PEG & DMI

FDI PEG & DMI

VAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

SENSE

LINES

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_VR_EN

GFX_DPRSLPVR

GFX_IMON

GRAPHICS VIDs

GRAPHICS VIDs

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

VTT0_59

VTT0_60

VTT0_61

VTT0_62

VTT1_63

VTT1_64

VTT1_65

1.1V1.8V

1.1V1.8V

VTT1_66

VTT1_67

VTT1_68

VCCPLL1

VCCPLL2

VCCPLL3

POWER

POWER

3A

0.6A

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

AN24

AR25

AT25

AM24

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

L10

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

GFXVR_E N

GFXVR_D PRSLPVR

C1392

C1392

1U_0402 _6.3V4Z

1U_0402 _6.3V4Z

+1.05VS_ VTT_CPU

C140 3

+1.8VS_V CCSFR

C1406

C1406

1U_0402 _6.3V4Z

1U_0402 _6.3V4Z

VCC_AXG _SENSE (46)

VSS_AXG _SENSE (46)

GFXVR_V ID_0 (46)

GFXVR_V ID_1 (46)

GFXVR_V ID_2 (46)

GFXVR_V ID_3 (46)

GFXVR_V ID_4 (46)

GFXVR_V ID_5 (46)

GFXVR_V ID_6 (46)

R1484 1K_0402 _5%@R1484 1K_0402 _5%@

1 2

1U_0402 _6.3V4Z

1U_0402 _6.3V4Z

1

1

C1393

C1393

2

2

+1.05VS_ VTT_CPU

1

2

1

C1403

22U_080 5_6.3V6M

22U_080 5_6.3V6M

2

1

1

C1407

C1407

2

2

1U_0402 _6.3V4Z

1U_0402 _6.3V4Z

GFXVR_D PRSLPVR (46)

1U_0402 _6.3V4Z

1U_0402 _6.3V4Z

1

C1395

C1395

C1394

C1394

2

1U_0402 _6.3V4Z

1U_0402 _6.3V4Z

C1402

C1402

10U_080 5_6.3V6M

10U_080 5_6.3V6M

2.2U_060 3_6.3V4Z

2.2U_060 3_6.3V4Z

1

C1408

C1408

2

4.7U_080 5_10V4Z

4.7U_080 5_10V4Z

1

1

C1396

C1396

2

2

1U_0402 _6.3V4Z

1U_0402 _6.3V4Z

40mil

1

C1409

C1409

2

GFXVR_E N (4 6)

GFXVR_IMO N (46)

22U_080 5_6.3V6M

22U_080 5_6.3V6M

1

C1398

C1398

C1397

C1397

2

22U_080 5_6.3V6M

22U_080 5_6.3V6M

1 2

1

C1410

C1410

2

22U_080 5_6.3V6M

22U_080 5_6.3V6M

GFXVR_E N

1

2

R1485

R1485

0_0805_ 5%

0_0805_ 5%

1 2

R1483 470_040 2_5% R14 83 470_ 0402_5%

Reserved for +1.5V to +1.5V_1

+1.5VS

1

+

+

C1399

C1399

330U_D2 _2V_Y

330U_D2 _2V_Y

2

+1.8VS

A A

Security Class ification

Security Class ification

Security Class ification

2009/11/ 23 2010/11/ 23

2009/11/ 23 2010/11/ 23

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2009/11/ 23 2010/11/ 23

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

PROCESSOR (5/6) PWR

PROCESSOR (5/6) PWR

PROCESSOR (5/6) PWR

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

Custom

Custom

Custom

PAU30 M/B LA-6392P Schematic

PAU30 M/B LA-6392P Schematic

PAU30 M/B LA-6392P Schematic

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

8 51Monday, November 22, 2 010

8 51Monday, November 22, 2 010

8 51Monday, November 22, 2 010

1

1.0

1.0

1.0

5

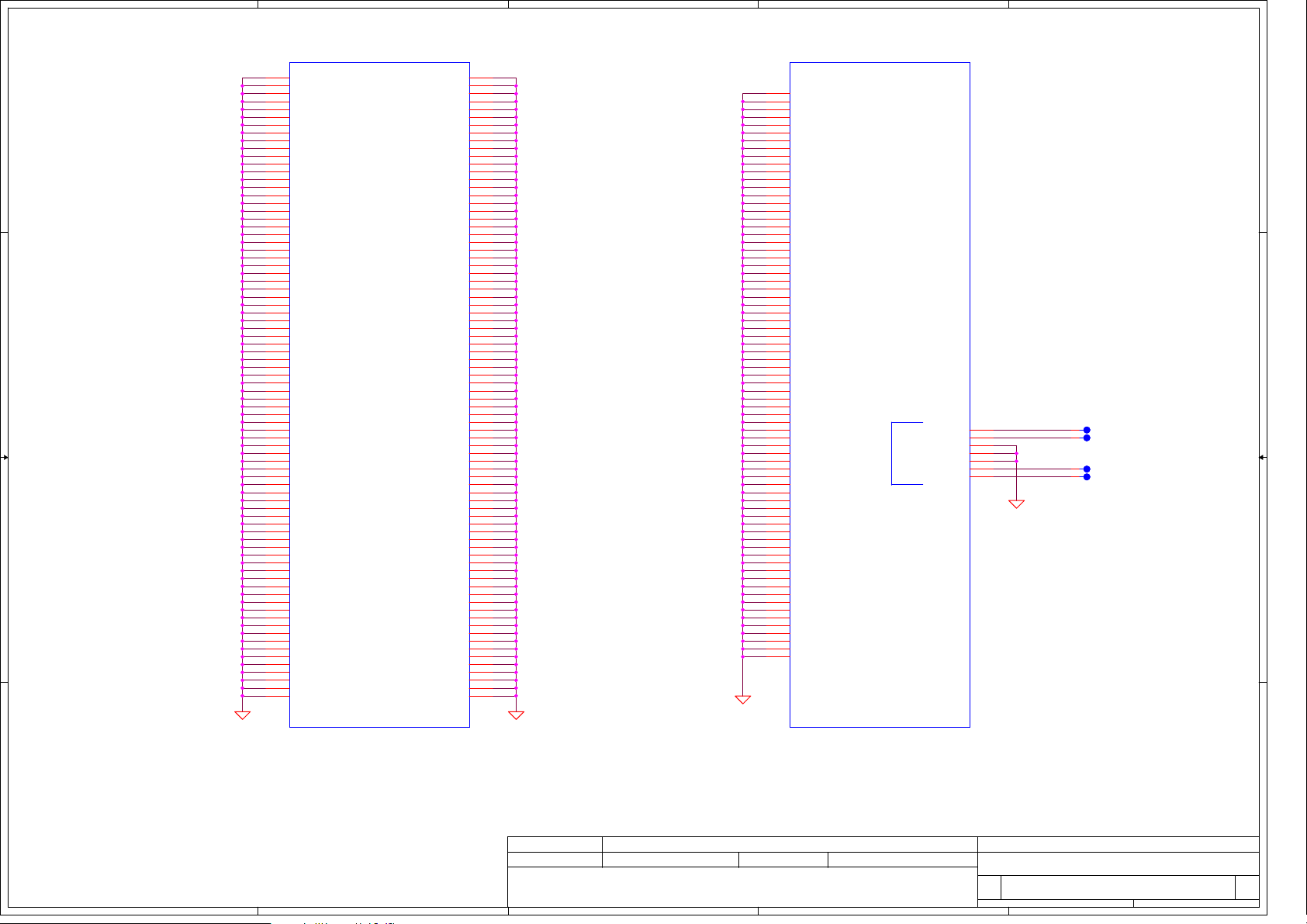

JCPU1H

JCPU1H

AT20

VSS1

AT17

VSS2

AR31

VSS3

AR28

VSS4

AR26

VSS5

AR24

VSS6

D D

C C

B B

AR23

AR20

AR17

AR15

AR12

AR9

AR6

AR3

AP20

AP17

AP13

AP10

AP7

AP4

AP2

AN34

AN31

AN23

AN20

AN17

AM29

AM27

AM25

AM20

AM17

AM14

AM11

AM8

AM5

AM2

AL34

AL31

AL23

AL20

AL17

AL12

AL9

AL6

AL3

AK29

AK27

AK25

AK20

AK17

AJ31

AJ23

AJ20

AJ17

AJ14

AJ11

AJ8

AJ5

AJ2

AH35

AH34

AH33

AH32

AH31

AH30

AH29

AH28

AH27

AH26

AH20

AH17

AH13

AH9

AH6

AH3

AG10

AF8

AF4

AF2

AE35

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

4

VSS

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

3

JCPU1I

JCPU1I

K27

VSS161

K9

VSS162

K6

VSS163

K3

VSS164

J32

VSS165

J30

VSS166

J21

VSS167

J19

VSS168

H35

VSS169

H32

VSS170

H28

VSS171

H26

VSS172

H24

VSS173

H22

VSS174

H18

VSS175

H15

VSS176

H13

VSS177

H11

VSS178

H8

VSS179

H5

VSS180

H2

VSS181

G34

VSS182

G31

VSS183

G20

VSS184

G9

VSS185

G6

VSS186

G3

VSS187

F30

VSS188

F27

VSS189

F25

VSS190

F22

VSS191

F19

VSS192

F16

VSS193

E35

VSS194

E32

VSS195

E29

VSS196

E24

VSS197

E21

VSS198

E18

VSS199

E13

VSS200

E11

VSS201

E8

VSS202

E5

VSS203

E2

VSS204

D33

VSS205

D30

VSS206

D26

VSS207

D9

VSS208

D6

VSS209

D3

VSS210

C34

VSS211

C32

VSS212

C29

VSS213

C28

VSS214

C24

VSS215

C22

VSS216

C20

VSS217

C19

VSS218

C16

VSS219

B31

VSS220

B25

VSS221

B21

VSS222

B18

VSS223

B17

VSS224

B13

VSS225

B11

VSS226

B8

VSS227

B6

VSS228

B4

VSS229

A29

VSS230

A27

VSS231

A23

VSS232

A9

VSS233

2

VSS

VSS

NCTF

NCTF

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

AT35

AT1

AR34

B34

B2

B1

A35

H_NCTF1

H_NCTF2

H_NCTF6

H_NCTF7

1

@

@

PAD

PAD

T51

T51

@

@

PAD

PAD

T52

T52

@

@

PAD

PAD

T53

T53

@

@

PAD

PAD

T54

T54

IC,AUB_CFD _rPGA,R1P0

IC,AUB_CFD _rPGA,R1P0

CONN@

CONN@

A A

Security Class ification

Security Class ification

Security Class ification

2009/11/ 23 2010/11/ 23

2009/11/ 23 2010/11/ 23

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS