Acer Helios 700, Helios 717 boardview

1

2

3

4

5

6

7

8

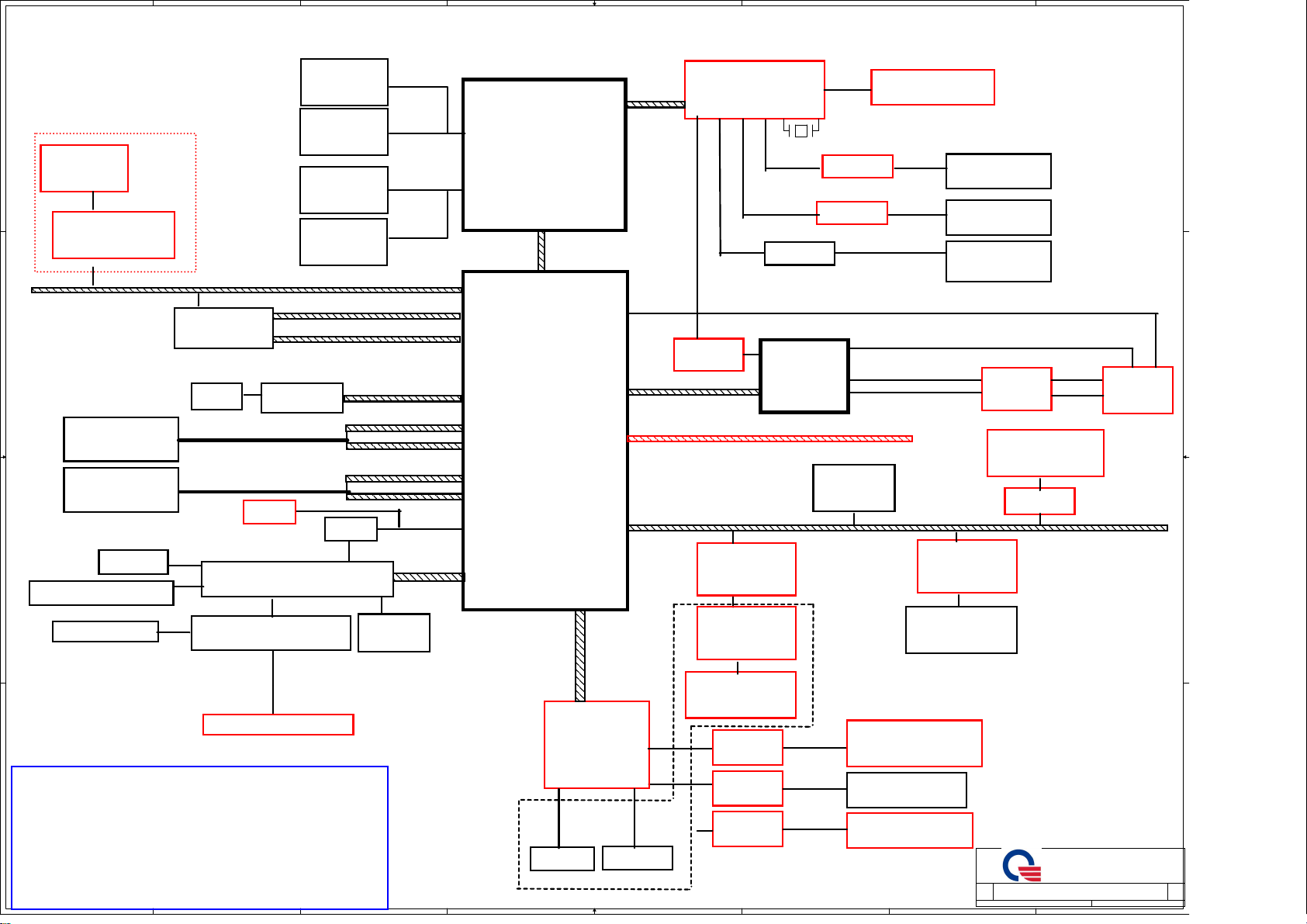

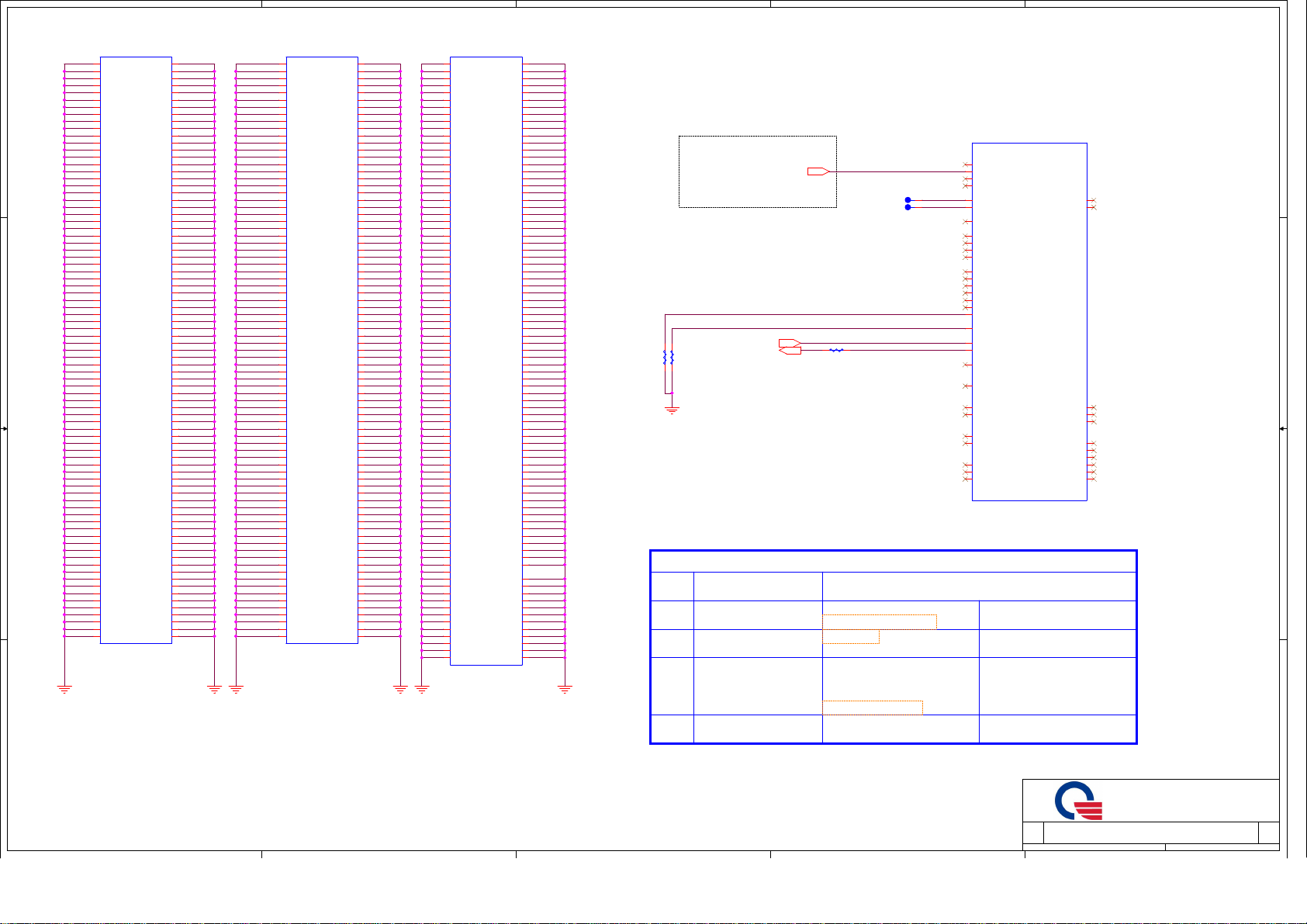

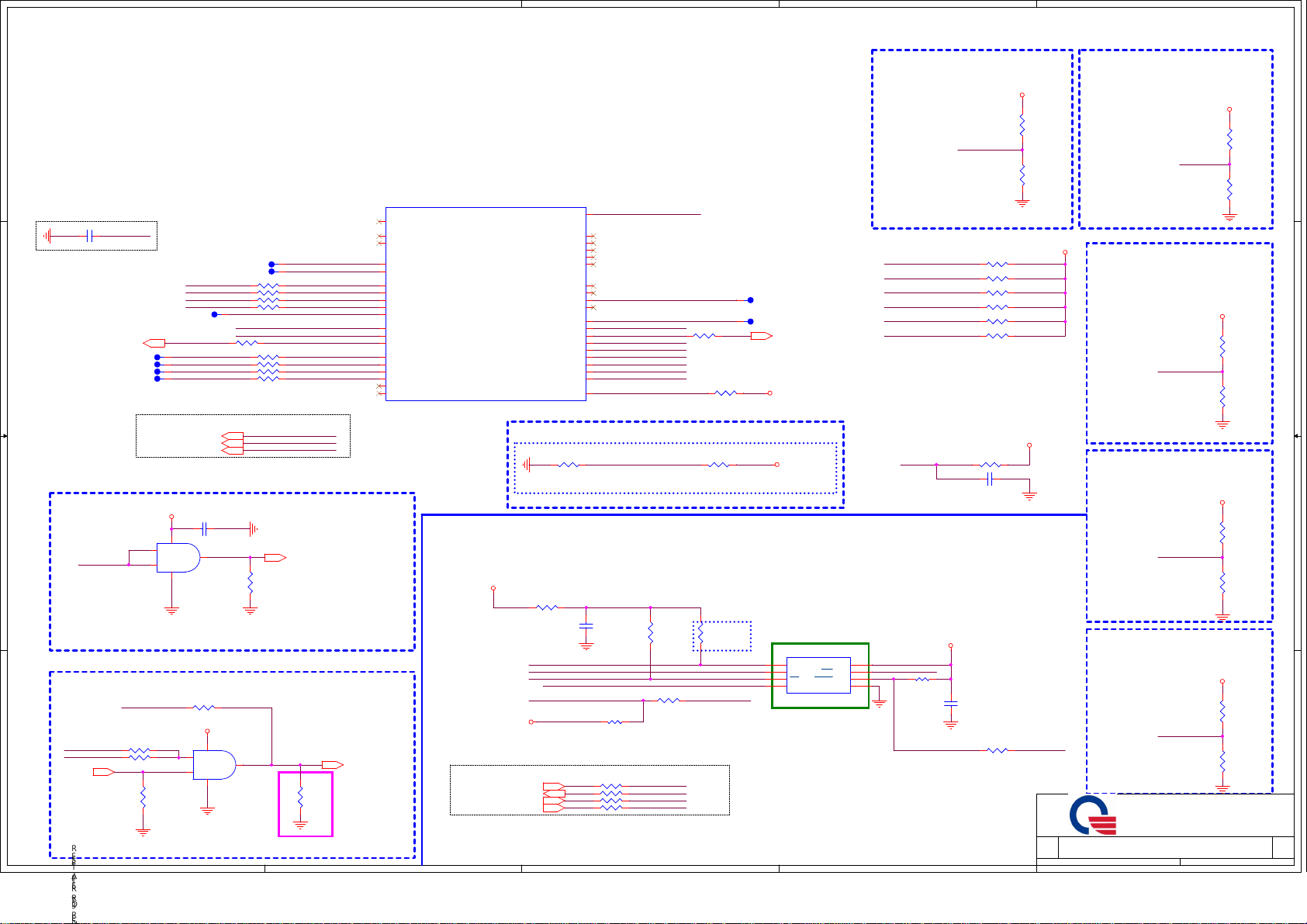

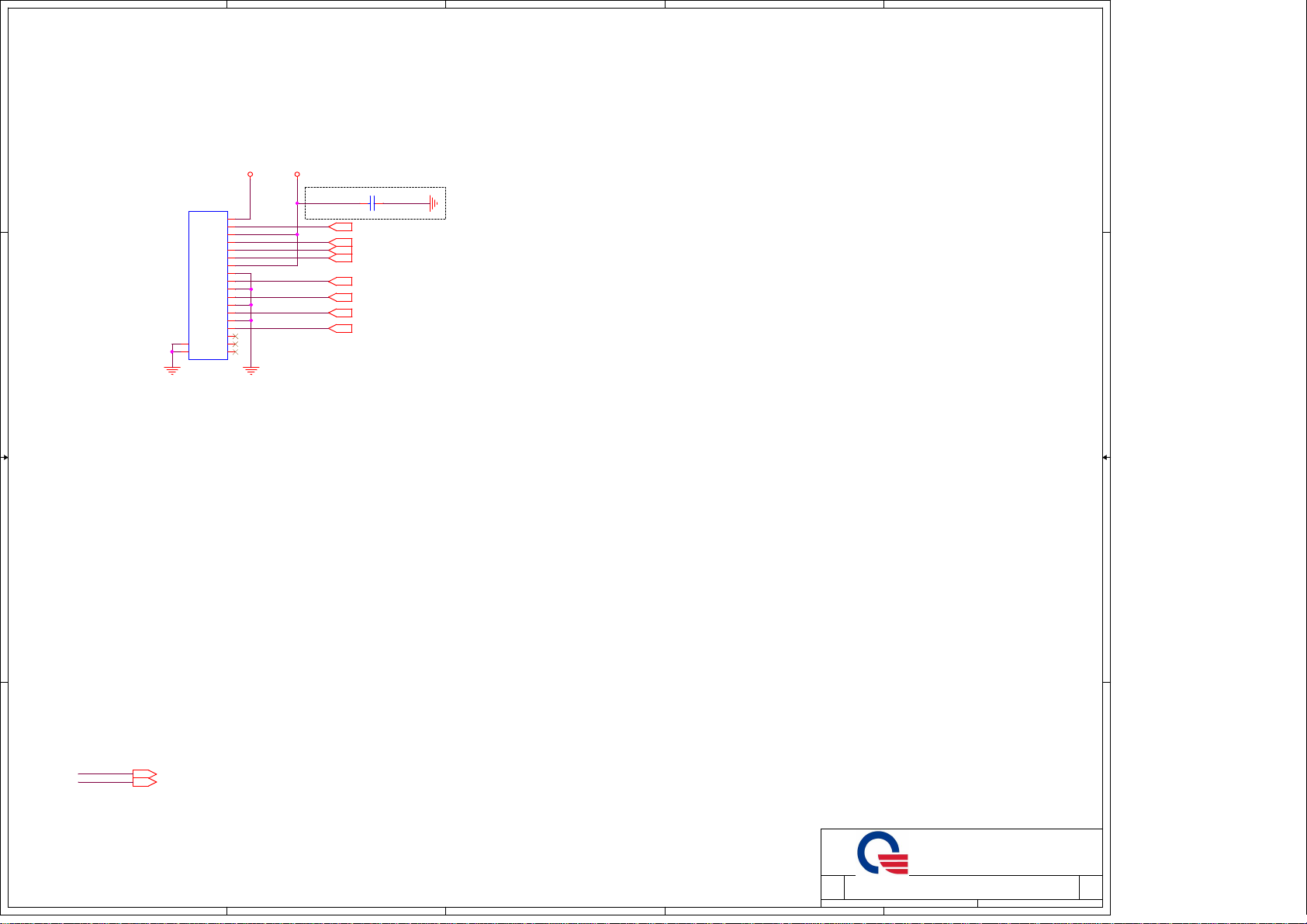

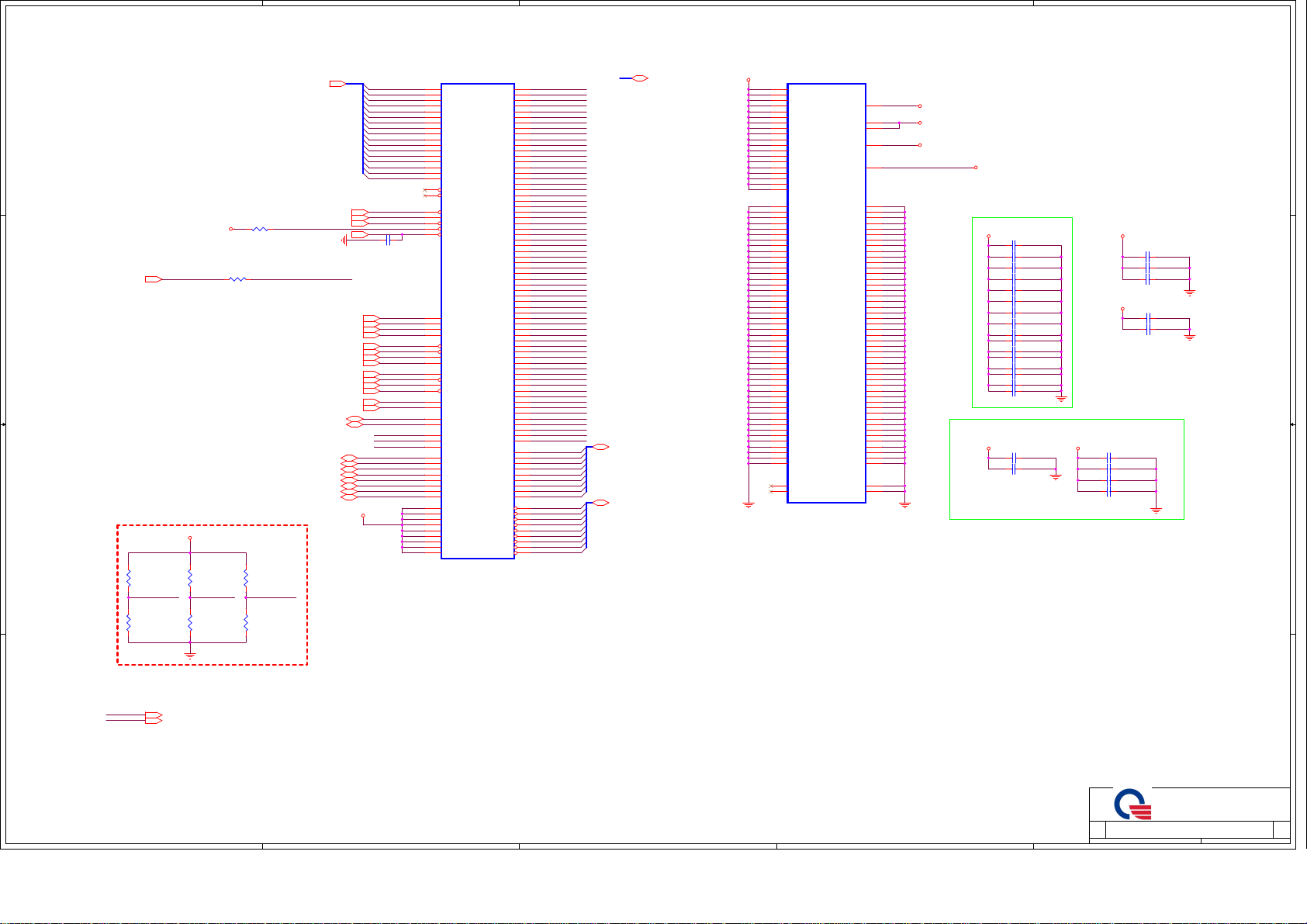

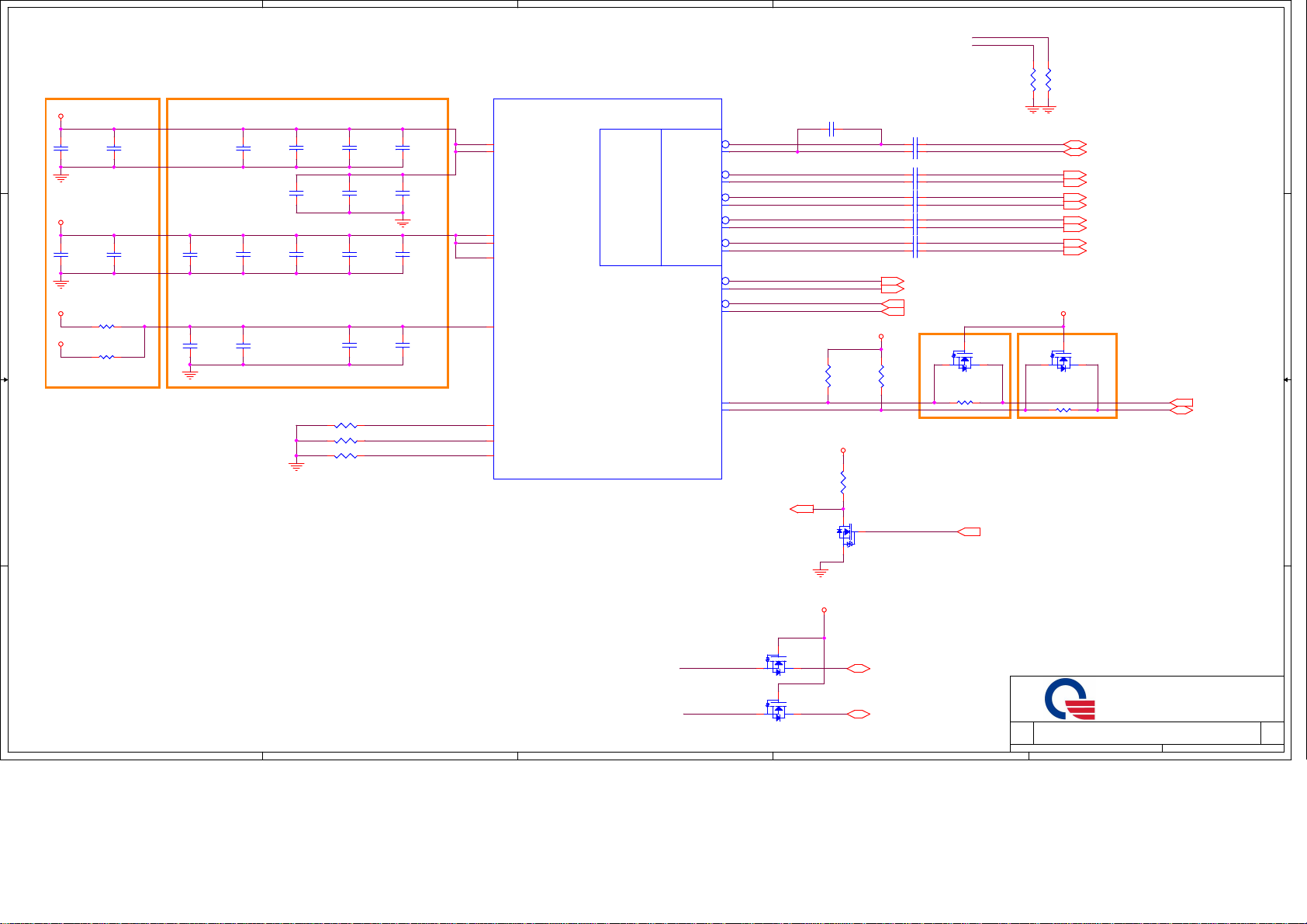

Levante_CFS CFL-H/K +1170/1180 MAX-P SYSTEM DIAGRAM

SODIMM0

Max. 16GB

RVS H9.2

A A

Port14

LAN

Killer E3000

10x10x0.9mm

PCIe Redriver

SN75LVPE802RTJR

4x4x0.8mm

Daughter board

SODIMM1

Max. 16GB

RVS H5.2

SODIMM0

Max. 16GB

RVS H4.0 or 5.2

SODIMM1

Max. 16GB

STD H4.0 or 5.2

2400MT/s

DDR4

Channel A

2400MT/s

DDR4

Channel B

INTEL

Coffee Lake H

Processor : 6+2

Power : 45 (Watt)

Package : BGA1440

Size : 42 x 28 x 1.5 (mm)

DMI

PEG

X16 Lanes

NVIDIA N18E-G2/G3

Package 37.5 x 37.5mm

TGP: 115W/150W

eDP re-driver IC

TUSB546-DCI

27MHz

HDMI2.0 redriver

PS8409A

DP re-driver

TUSB546-DCI

VRAM GDDR6 * 8 pcs

HDMI2.0

Display port

17.3

eDP Panel FHD/UHD

01

PCI-E x 1

Port15

USB 2.0

B B

WLAN +BT

Cable

SATA Re-driver

PS8527B

TPM

P34

NGFF SSD #1

SATA/PCIE SSD

NGFF SSD #2

PCIE SSD

HDD

CNVI

SATA 6GB/s

PCIE x 4

SATA 6GB/s

PCIE x 4

CNL PCH

HM370

Package : FCBGA837

Size : 23 x 23 (mm)

SPI

USB2.0

DP re-driver

TUSB546-DCI*1

PCIE 4 Lanes

USB 2.0/3.0

CIO_TX_RX (DP/USB3.1)

DSL6540-SLL44

TBT(Apline Ridge)

NV Type-C (Please refer to the next page)

I2C

AUX /LS/SPI

Webcam

(DMIC)

PORT6

USB type C PD

TI

TPS65987*1

7x7x1mm

Metal

Keyboard

U2 re-driver

TUSB212

CC1/CC2

SBU1/SBU2

PORT7

USB TypeC X1

ROM

U3 10G re-timer

C C

Power / Battery LED

Macro Key LED

TP

KBC

ITE IT8987E/BX

MCU PWM/LED Driver

ENE 6K5130

LPC

CPU FAN

GPU FAN

Azalia

PS8817

4.2x8x0.8mm

U3 10G re-timer

PS8817

4.2x8x0.8mm

U2 re-driver

TUSB212 x2

U3 10G re-timer

PS8811

4.2x4.2x0.8mm

PORT1,2,3

USB3.0 Ports

X1

BC1.2

SLGC55544CVTR

USB3.0 Ports

X2

RGB LED for C cover

AUDIO

CODEC

ALC1220

MIC

4

7x7x0.9mm

HP

Daughter board

5

G3@ : NV G3 GPU

D D

ADP@ : For 330W

GSY@ : For G-SYNC panel

NGSY@ : For Non- GSYNC panel

SAM@ : SAMSUNG VRAM

MIC@ : MICRON VRAM

TPM@ : TPM

i9@ : i9 CPU

1

2

3

SLGC55544CVTR

AMP

ALC1001

3x3x0.9mm

AMP

ALC1001

3x3x0.9mm

AMP

ALC1001

3x3x0.9mm

BC1.2

Speaker Center

SubWoofer

Speaker R1/L1

Speaker R2/L2

6

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Nu mber Rev

Size Document Nu mber Rev

Size Document Nu mber Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

7

PROJECT :

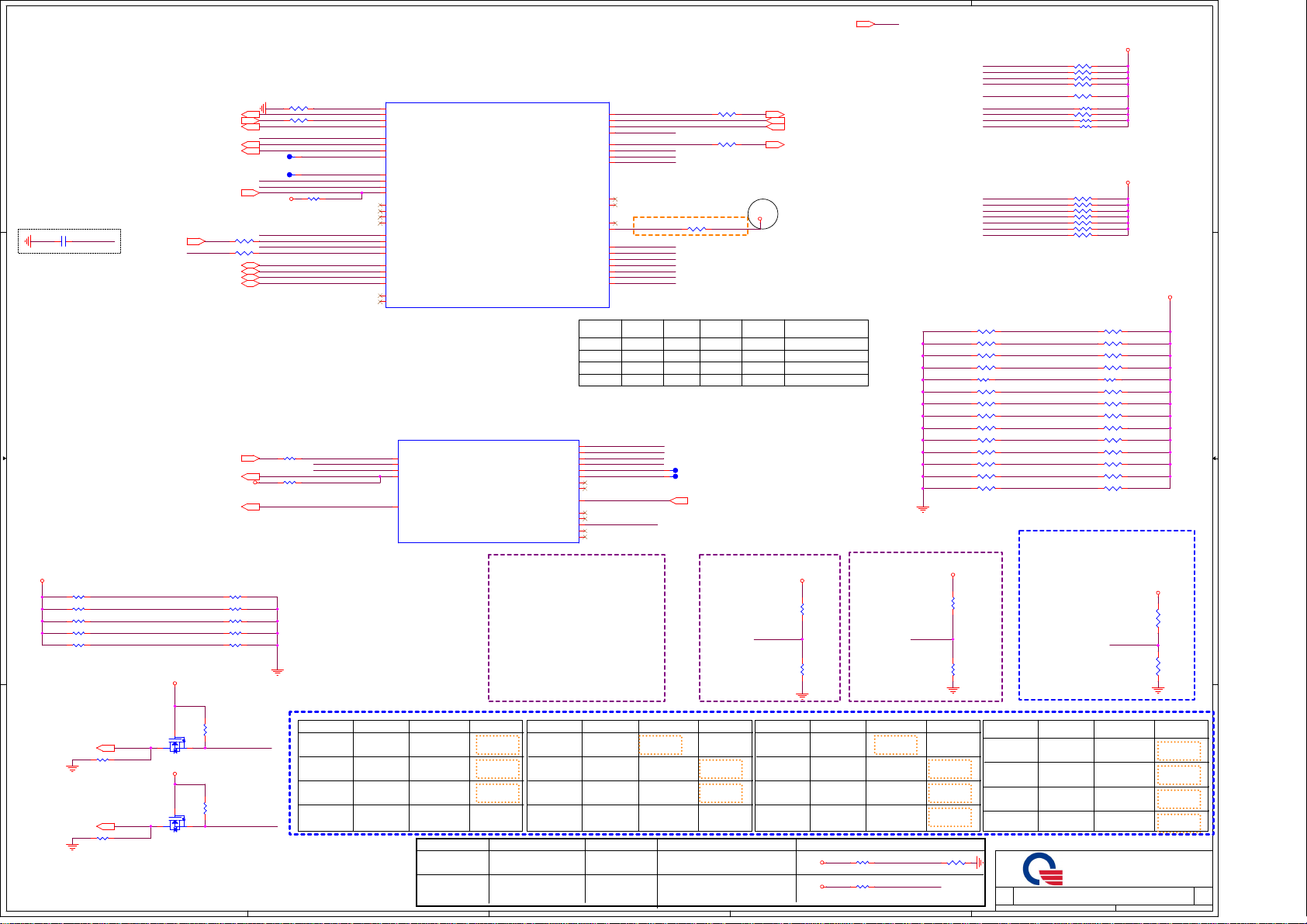

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

ZGE

ZGE

ZGE

8

1 78Friday, May 03, 20 19

1 78Friday, May 03, 20 19

1 78Friday, May 03, 20 19

1A

1A

1A

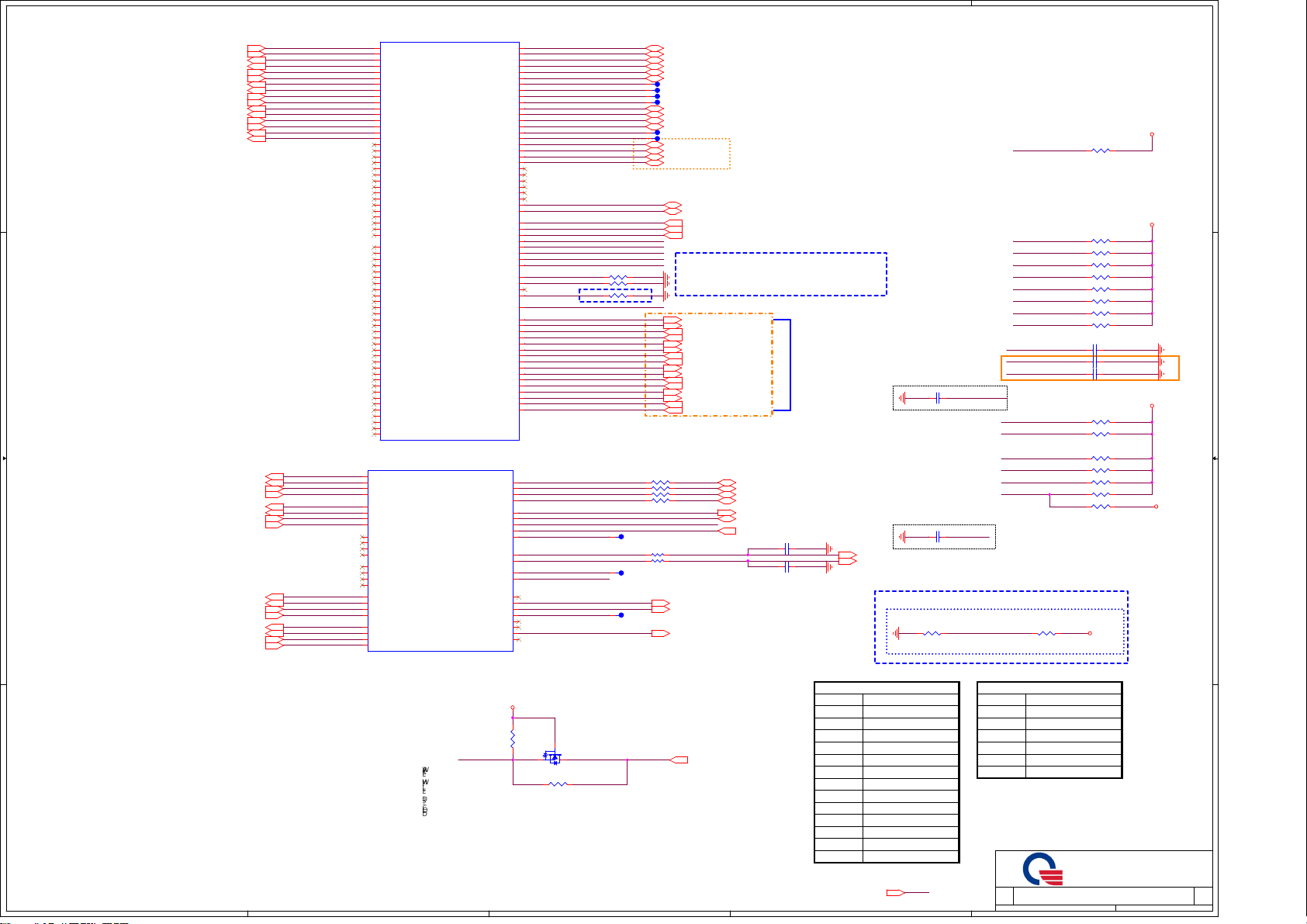

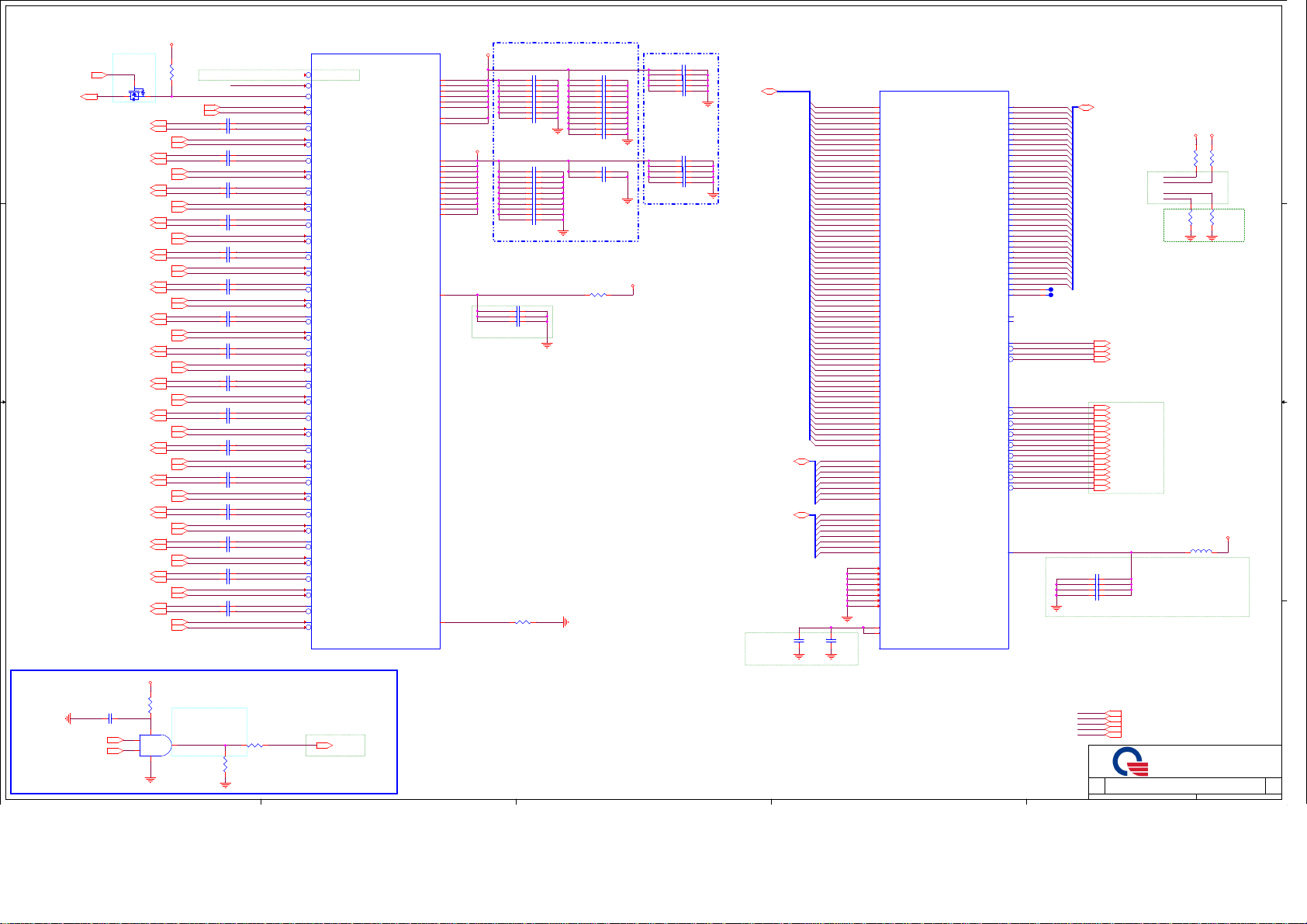

5

For debug only remove from MV

+3V

R83

*4.7K_1%_4

D D

34

Q8A

5

CATERR#

C C

PECI

CPU CORE SVID

Layout note:

1.Need routing together

2.ALERT need between CLK and DATA.

PLACE THE PU RESISTORS

CLOSE TO VR

PULL UP IS IN THE VR MODULE

B B

CLOSE TO CPU

PLACE THE PU RESISTORS

H_CPU_SVIDALRT#

CLOSE TO CPU

PLACE THE PU RESISTORS

A A

*PJX138K

HWPG[57]

+VCCIO

R52 13_1%_4

R47 *short_0402

VR_SVID_CLK_R

R35 220_1%_4

H_CPU_SVIDDAT

+3V

21

61

2

R104 *short_0402

R103 *0_5%_4

R38 *short_0402

5

R85

*360_1%_6

LED1

*White_19-113/T1D-CP2Q2HY/3T

Q8B

*PJX138K

R101

4.7K_1%_4

34

Q16A

5

PJX138K

PCH_PECI [11]

EC_PECI [57]

+VCCST

modify 8/9

R39

*54.9_1%_4

+VCCST

R36

56.2_1%_4

C48

*0.1u/16V_4

+VCCST

R42

100_1%_4

R41 *short_0402

PROCPWRGD

C56

220p/50V_4

+VCCST+3V_DEEP_SUS

modify 8/9

R108

1K_1%_4

H_VCCST_PW RGD

61

Q16B

2

PJX138K

PROCPWRGD (50ohm)

Trace Length: 1~11.25 inches

PM_SYNC (50ohm)

Trace Length: 1~11.25 inches

CPU_PLTRST# (50ohm)

Trace Length: 10~17 inches

Close to CPU

SVID CLK

VR_SVID_CLK [65]

Close to CPU

SVID ALERT

VR_SVID_ALERT# [65]

Close to CPU

SVID DATA

VR_SVID_DATA [65]

4

CLK_CPU_BCLKP[11]

CLK_CPU_BCLKN[11]

CPU_PCI_BCLKP[11]

CPU_PCI_BCLKN[11]

CLK_DPLL_NSCCLKP[11]

Host CLK:

Trace length < 11000 mils

Trace spacing = 15 / 20 mils, Impendence 85 ohm

CLK_DPLL_NSCCLKN[11]

EMI RESERVE

VCCST_PWRGD

EC2 10p/50V_4

R107 60.4/F_4

CPU_PLTRST#R[11]

PM_SYNC[11]

C92

0.1u/16V_4

H_PM_DOWN[11]

SKTOCC_N_R[13]

THERMTRIP# (50ohm)

Trace Length: 1.1~12 inches

IMVP_PWRGD[10,65]

SYS_SHDN#[57,62,68]

PM_THRMTRIP#[11,17,18,19,20,53]

PROCPWRGD[10]

R57 20_1%_4

SKTOCC_N_R

R53 *short_0402

TP6

+VCCST

R62 *100K_1%_4

modify 8/9

Ra Not install in SKL-H

+VCCST

Ra

R98

*10K_1%_4

PROC_SEL#

R97

*0_5%_4

4

3

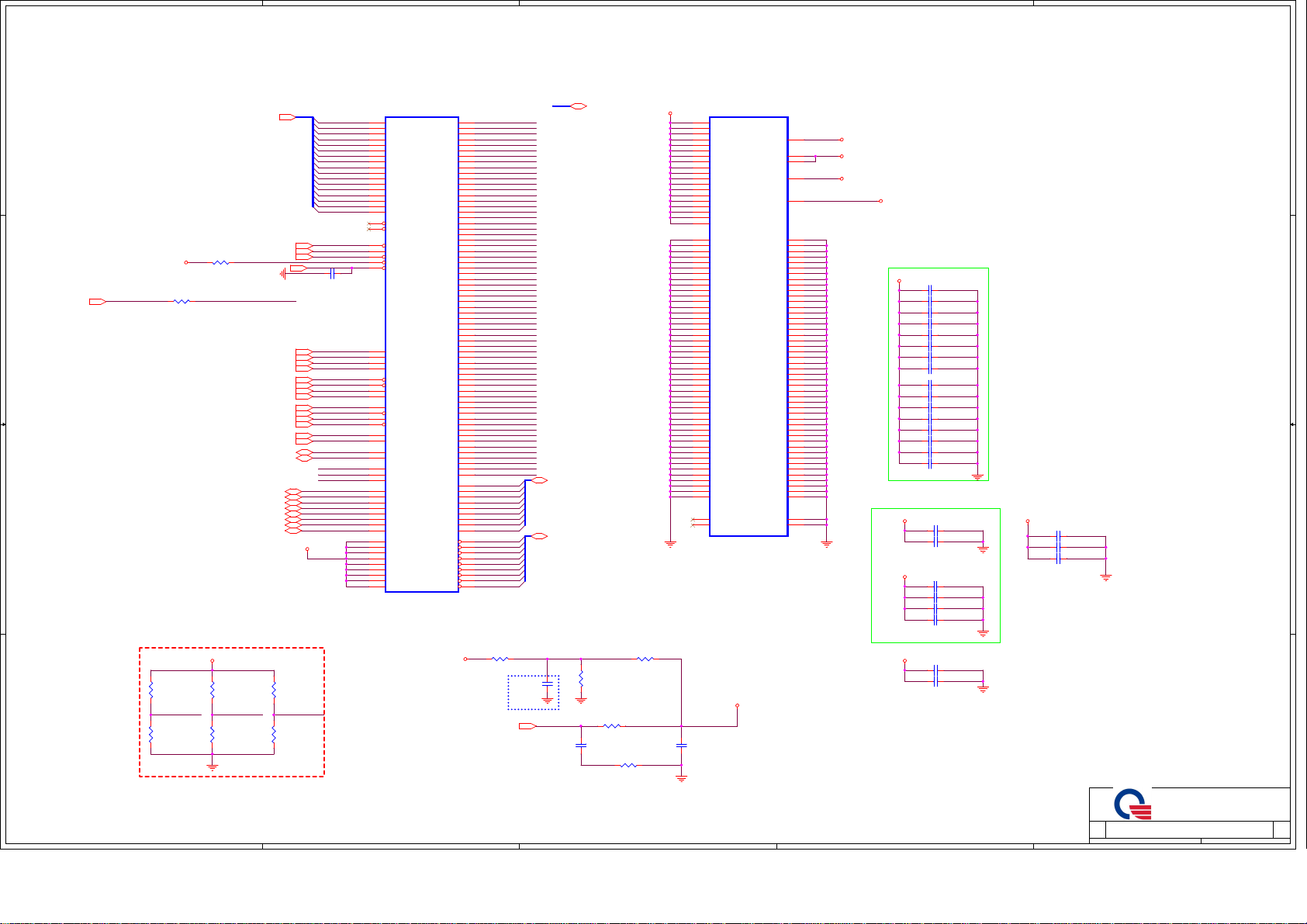

CFL-H Processor (CLK,MISC,JTAG)

CLK_CPU_BCLKP

CLK_CPU_BCLKN

CPU_PCI_BCLKP

CPU_PCI_BCLKN

CLK_DPLL_NSCCLKP

CLK_DPLL_NSCCLKN

H_CPU_SVIDALRT#

VR_SVID_CLK_R

H_CPU_SVIDDAT

H_PROCHOT#_CPU

DDR_PG_CNT L

VCCST_PWRGD

PROCPWRGD

CPU_PLTRST#R

H_PM_DOWN_R

PECI

THERMTRIP#

SKTOCC_N

PROC_SEL#

CATERR#

R78 49.9_1%_6

+VCCST

3

Q6

2

DMG301NU-7

1

R46

R55

1K_1%_4

1K_1%_4

2

13

THERMTRIP#

Q5

METR3904-G

R51 *short_0402

U3E

B31

BCLKP

A32

BCLKN

D35

PCI_BCLKP

C36

PCI_BCLKN

E31

CLK24P

D31

CLK24N

BH31

VIDALERT#

BH32

VIDSCK

BH29

VIDSOUT

BR30

PROCHOT#

BT13

DDR_VTT_CNTL

H13

VCCST_PWRGD

BT31

PROCPWRGD

BP35

RESET#

BM34

PM_SYNC

BP31

PM_DOWN

BT34

PECI

J31

THERMTRIP#

BR33

SKTOCC#

BN1

PROC_SELECT#

BM30

CATERR#

AT13

ZVM#

AW13

MSM#

AU13

RSVD#AU13

AY13

RSVD#AY13

5 OF 13

CPU_CFL-H_1440P

Note: please keep plane is enough for VDDQ 2.8A

Placement close to CPU.

+1.2VSUS

C655 0.1u/16V_4

C657 *0.1u/16V_4

DDR_PG_CNT L

PROCHOT# (50ohm)

Trace Length <11 inches

Cb need placment near VR

modify 8/9

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_17

CFG_16

CFG_19

CFG_18

BPM#_0

BPM#_1

BPM#_2

BPM#_3

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST#

PROC_PREQ#

PROC_PRDY#

CFG_RCOMP

R90 10K_1%_4

+VCCSTG

H_PROCHOT#[57,61,65]

EMI RESERVE

EC1 *10p/50V_4

3

BN25

BN27

BN26

CFG2

BN28

BR20

CFG4

BM20

CFG5

BT20

CFG6

BP20

BR23

BR22

BT23

BT22

BM19

BR19

BP19

BT19

BN23

BP23

BP22

BN22

XDP_BPM0

BR27

XDP_BPM1

BT27

XDP_BPM2

BM31

XDP_BPM3

BT30

H_TDO

BT28

H_TDI

BL32

H_TMS

BP28

H_TCK

BR28

H_TRST#

BP30

H_PREQ#

BL30

H_PRDY#

BP27

CFG_RCOMP

BT25

Design Note(CFG_RCOMP):

DEFENSIVE DESIGN 50-OHM FOR R40PR (SV REQ)

+3V_DEEP_SUS

R96

10K_1%_4

2

Q10

METR3904-G

1 3

R88

100K_1%_4

R67 1K_1%_4

TP7

TP8

TP4

TP5

H_TDO [10]

H_TDI [10]

H_TMS [10]

H_TCK [10]

H_TRST# [15]

H_PREQ# [15]

H_PRDY# [15]

R7749.9_1%_4

+3V_DEEP_SUS

3

2

1

R68 499_1%_4

R95

10K_1%_4

Q12

2N7002KTB

Modify 8/10

H_PROCHOT#_CPU

C60

0.1u/16V_4

2

R92

100K_1%_4

H_PROCHOT#_CPU

2

The CFG signals have a default value of '1' if not terminated on the board.

DDR_VTTT_PG_CTRL [64]

1

Processor pull-up (CPU)

H_TDO

H_TMS

H_TDI

H_PREQ#

H_TCK

H_TRST#

R72 51_5%_4

R71 *51_5%_4

R73 *51_5%_4

R76 *56.2_1%_4

R69 51_5%_4

R65 *51_5%_4

Processor Strapping

R75 1K_1%_4

CFG2

CFG4

R79 *1K_1%_4

CFG5

R84 *1K_1%_4

CFG6

R81 *1K_1%_4

Contiguration Signals: The CFG signals

have a default value of '1' if not

terminated

on the board. Refer to the appropriate

platform design guide for pull-down

recommendations when a logic low is

desired.

Intel recommends placing test points on

the

board for CFG pins.

. CFG[0]:Stall reset sequence after PCU

PLL lock until de-asserted:

-1=(Default) Normal Operation;

No stall.

-0=Stall.

.CFG[1]:Reserved configuration lane.

.CFG[2]:PCI Express*Static x16 Lane

Numbering Reversal.

-1=Normal operation

-0=Lane numbers reversed.

.CFG[3]:Reserved configuration lane.

.CFG[4]:eDP enable:

-1=Disabled.

-0=Enabled.

.CFG[6:5]:PCI Express* Bifurcation

-00=1x8,2x4 PCI Express*

-01=reserved

-10=2x8 PCI Express*

-11=1x16 PCI Express*

.CFG[7]:PEG Training:

-1=(default) PEG Train

immediately following RESET# de

assertion.

-0=PEG Wait for BIOS for

assertion.

.CFG[19:8]:Reserved configuration

lanes.

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

CFL 1/7 (JTAG/MISC)

CFL 1/7 (JTAG/MISC)

CFL 1/7 (JTAG/MISC)

1

+VCCST

modify 8/9

ZGE

ZGE

ZGE

2 78Friday, May 03, 2019

2 78Friday, May 03, 2019

2 78Friday, May 03, 2019

02

1A

1A

1A

5

4

3

2

1

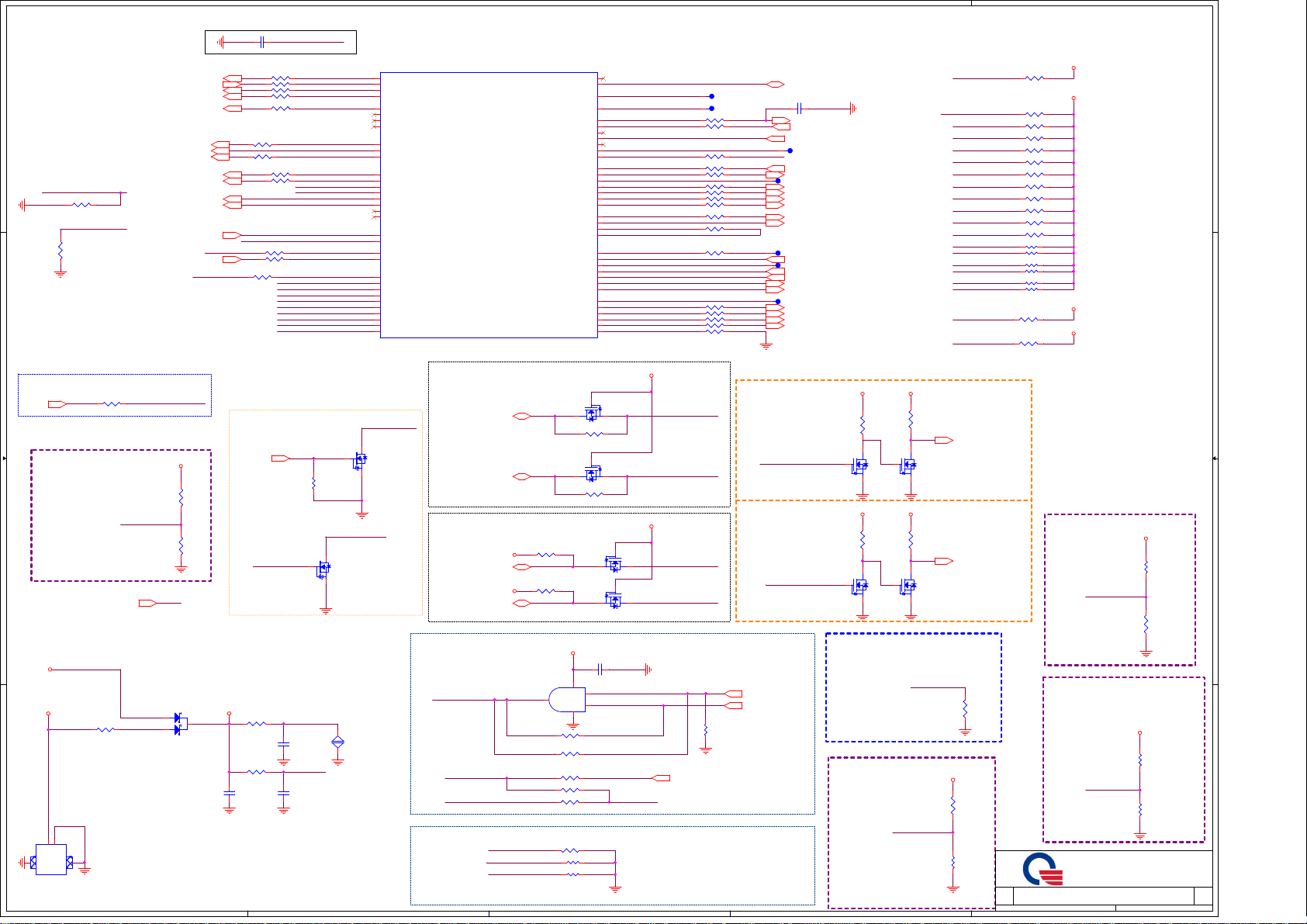

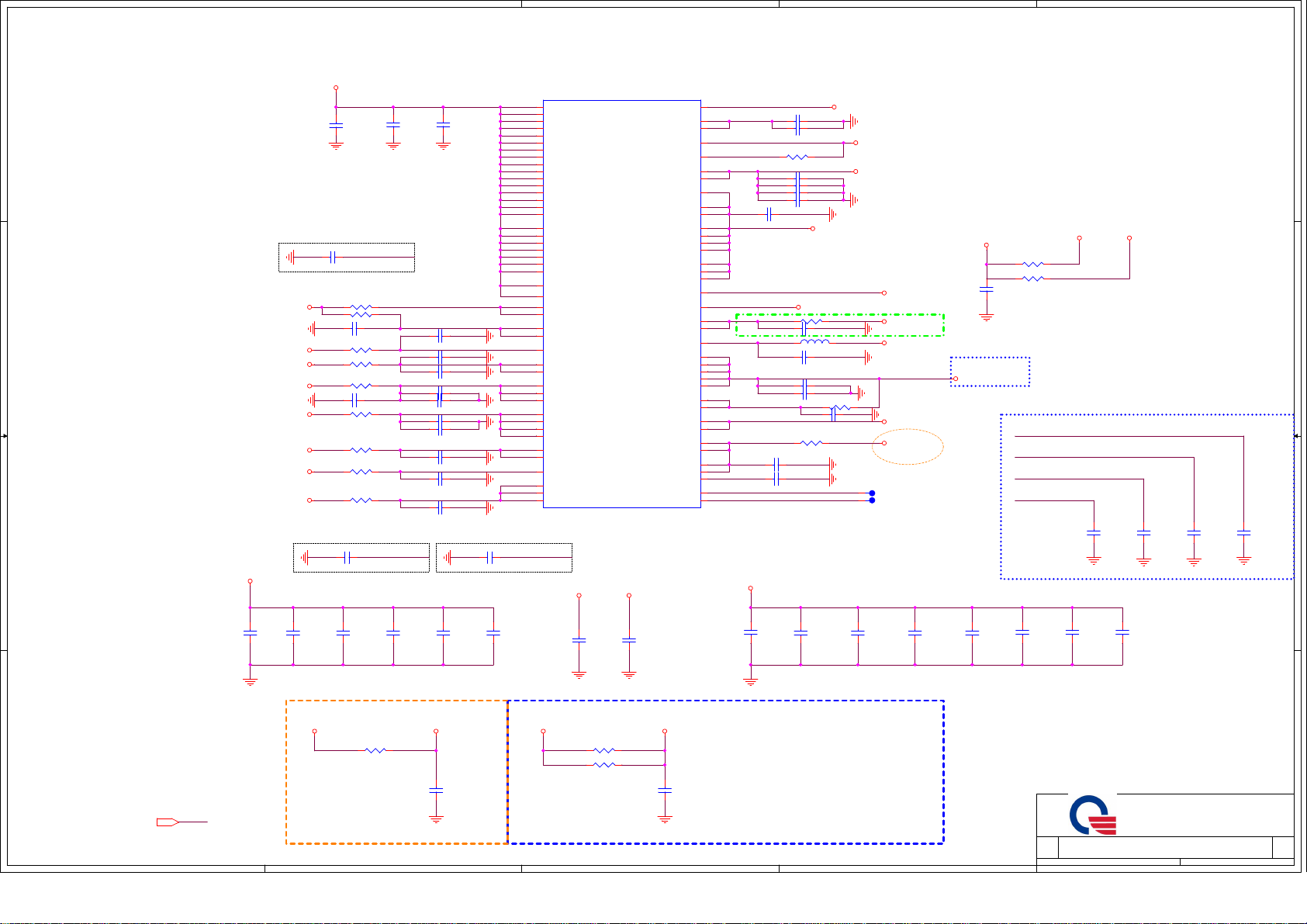

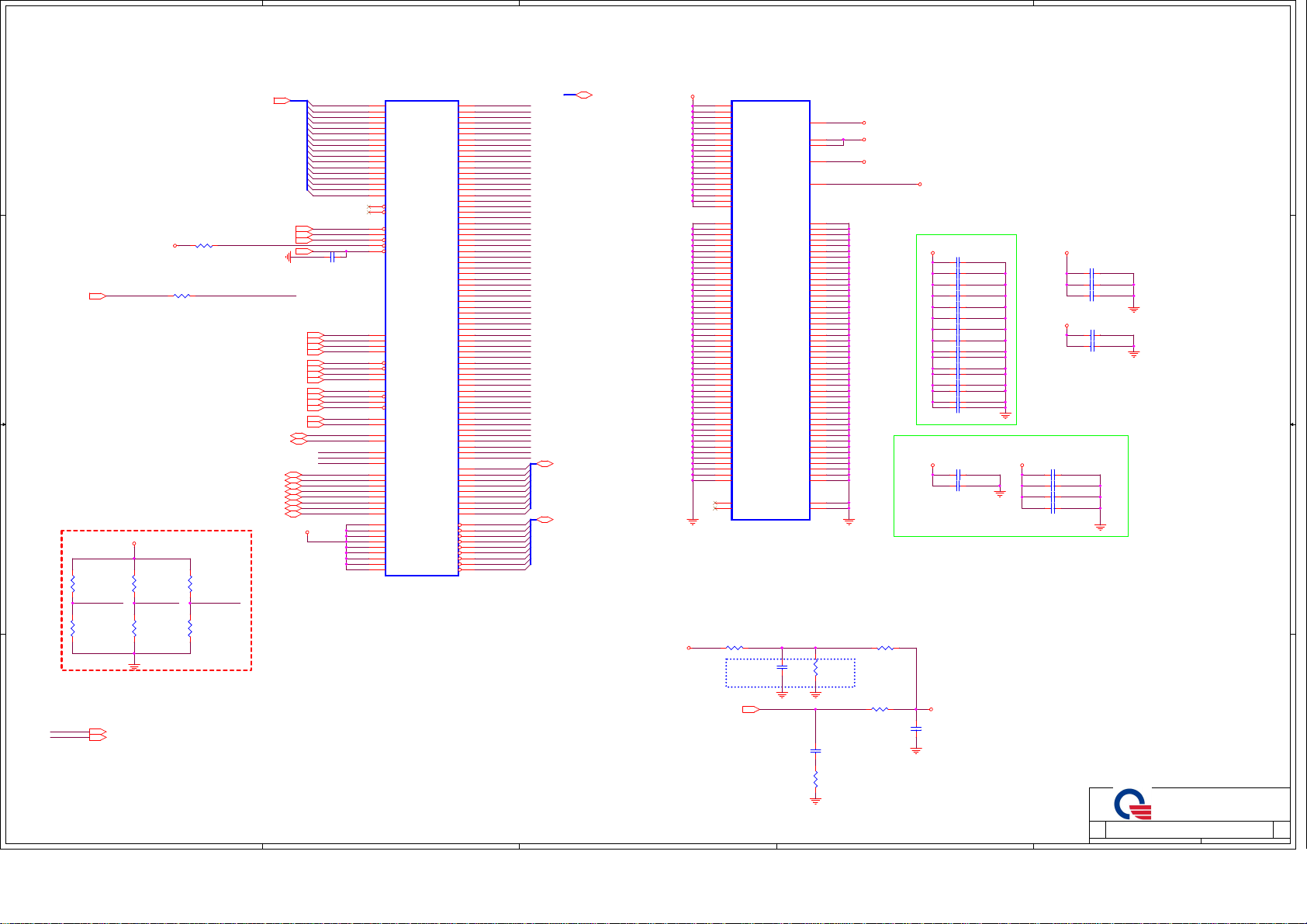

CFL Processor (DMI,PEG,FDI)

03

U3C

PEG_RXP15[21]

D D

C C

B B

+VCCIO

DMI RX

PEG_RXN15[21]

PEG_RXP14[21]

PEG_RXN14[21]

PEG_RXP13[21]

PEG_RXN13[21]

PEG_RXP12[21]

PEG_RXN12[21]

PEG_RXP11[21]

PEG_RXN11[21]

PEG_RXP10[21]

PEG_RXN10[21]

PEG_RXP9[21]

PEG_RXN9[21]

PEG_RXP8[21]

PEG_RXN8[21]

PEG_RXP7[21]

PEG_RXN7[21]

PEG_RXP6[21]

PEG_RXN6[21]

PEG_RXP5[21]

PEG_RXN5[21]

PEG_RXP4[21]

PEG_RXN4[21]

PEG_RXP3[21]

PEG_RXN3[21]

PEG_RXP2[21]

PEG_RXN2[21]

PEG_RXP1[21]

PEG_RXN1[21]

PEG_RXP0[21]

PEG_RXN0[21]

R102 24.9/F_4

DMI_RXP0[9]

DMI_RXN0[9]

DMI_RXP1[9]

DMI_RXN1[9]

DMI_RXP2[9]

DMI_RXN2[9]

DMI_RXP3[9]

DMI_RXN3[9]

PEG_COMP

E25

PEG_RXP_0

D25

PEG_RXN_0

E24

PEG_RXP_1

F24

PEG_RXN_1

E23

PEG_RXP_2

D23

PEG_RXN_2

E22

PEG_RXP_3

F22

PEG_RXN_3

E21

PEG_RXP_4

D21

PEG_RXN_4

E20

PEG_RXP_5

F20

PEG_RXN_5

E19

PEG_RXP_6

D19

PEG_RXN_6

E18

PEG_RXP_7

F18

PEG_RXN_7

D17

PEG_RXP_8

E17

PEG_RXN_8

F16

PEG_RXP_9

E16

PEG_RXN_9

D15

PEG_RXP_10

E15

PEG_RXN_10

F14

PEG_RXP_11

E14

PEG_RXN_11

D13

PEG_RXP_12

E13

PEG_RXN_12

F12

PEG_RXP_13

E12

PEG_RXN_13

D11

PEG_RXP_14

E11

PEG_RXN_14

F10

PEG_RXP_15

E10

PEG_RXN_15

G2

PEG_RCOMP

D8

DMI_RXP_0

E8

DMI_RXN_0

E6

DMI_RXP_1

F6

DMI_RXN_1

D5

DMI_RXP_2

E5

DMI_RXN_2

J8

DMI_RXP_3

J9

DMI_RXN_3

CPU_CFL-H_1440P

PEG_TXP_10

PEG_TXN_10

PEG_TXP_11

PEG_TXN_11

PEG_TXP_12

PEG_TXN_12

PEG_TXP_13

PEG_TXN_13

PEG_TXP_14

PEG_TXN_14

PEG_TXP_15

PEG_TXN_15

3 OF 13

PEG_TXP_0

PEG_TXN_0

PEG_TXP_1

PEG_TXN_1

PEG_TXP_2

PEG_TXN_2

PEG_TXP_3

PEG_TXN_3

PEG_TXP_4

PEG_TXN_4

PEG_TXP_5

PEG_TXN_5

PEG_TXP_6

PEG_TXN_6

PEG_TXP_7

PEG_TXN_7

PEG_TXP_8

PEG_TXN_8

PEG_TXP_9

PEG_TXN_9

DMI_TXP_0

DMI_TXN_0

DMI_TXP_1

DMI_TXN_1

DMI_TXP_2

DMI_TXN_2

DMI_TXP_3

DMI_TXN_3

B25

A25

B24

C24

B23

A23

B22

C22

B21

A21

B20

C20

B19

A19

B18

C18

A17

B17

C16

B16

A15

B15

C14

B14

A13

B13

C12

B12

A11

B11

C10

B10

B8

A8

C6

B6

B5

A5

D4

B4

C_PEG_TXP15

C_PEG_TXN15

C_PEG_TXP14

C_PEG_TXN14

C_PEG_TXP13

C_PEG_TXN13

C_PEG_TXP12

C_PEG_TXN12

C_PEG_TXP11

C_PEG_TXN11

C_PEG_TXP10

C_PEG_TXN10

C_PEG_TXP9

C_PEG_TXN9

C_PEG_TXP8

C_PEG_TXN8

C_PEG_TXP7

C_PEG_TXN7

C_PEG_TXP6

C_PEG_TXN6

C_PEG_TXP5

C_PEG_TXN5

C_PEG_TXP4

C_PEG_TXN4

C_PEG_TXP3

C_PEG_TXN3

C_PEG_TXP2

C_PEG_TXN2

C_PEG_TXP1

C_PEG_TXN1

C_PEG_TXP0

C_PEG_TXN0

C58 0.22u/6.3V_2

C57 0.22u/6.3V_2

C59 0.22u/6.3V_2

C61 0.22u/6.3V_2

C64 0.22u/6.3V_2

C63 0.22u/6.3V_2

C65 0.22u/6.3V_2

C67 0.22u/6.3V_2

C69 0.22u/6.3V_2

C68 0.22u/6.3V_2

C70 0.22u/6.3V_2

C71 0.22u/6.3V_2

C73 0.22u/6.3V_2

C72 0.22u/6.3V_2

C74 0.22u/6.3V_2

C75 0.22u/6.3V_2

C76 0.22u/6.3V_2

C77 0.22u/6.3V_2

C79 0.22u/6.3V_2

C78 0.22u/6.3V_2

C80 0.22u/6.3V_2

C81 0.22u/6.3V_2

C83 0.22u/6.3V_2

C82 0.22u/6.3V_2

C84 0.22u/6.3V_2

C85 0.22u/6.3V_2

C87 0.22u/6.3V_2

C86 0.22u/6.3V_2

C88 0.22u/6.3V_2

C89 0.22u/6.3V_2

C91 0.22u/6.3V_2

C90 0.22u/6.3V_2

DMI_TXP0 [9]

DMI_TXN0 [9]

DMI_TXP1 [9]

DMI_TXN1 [9]

DMI_TXP2 [9]

DMI_TXN2 [9]

DMI_TXP3 [9]

DMI_TXN3 [9]

PEG_TXP15 [21]

PEG_TXN15 [21]

PEG_TXP14 [21]

PEG_TXN14 [21]

PEG_TXP13 [21]

PEG_TXN13 [21]

PEG_TXP12 [21]

PEG_TXN12 [21]

PEG_TXP11 [21]

PEG_TXN11 [21]

PEG_TXP10 [21]

PEG_TXN10 [21]

PEG_TXP9 [21]

PEG_TXN9 [21]

PEG_TXP8 [21]

PEG_TXN8 [21]

PEG_TXP7 [21]

PEG_TXN7 [21]

PEG_TXP6 [21]

PEG_TXN6 [21]

PEG_TXP5 [21]

PEG_TXN5 [21]

PEG_TXP4 [21]

PEG_TXN4 [21]

PEG_TXP3 [21]

PEG_TXN3 [21]

PEG_TXP2 [21]

PEG_TXN2 [21]

PEG_TXP1 [21]

PEG_TXN1 [21]

PEG_TXP0 [21]

PEG_TXN0 [21]

DMI TX

U3D

K36

DDI1_TXP_0

K37

DDI1_TXN_0

J35

DDI1_TXP_1

J34

DDI1_TXN_1

H37

DDI1_TXP_2

H36

DDI1_TXN_2

J37

DDI1_TXP_3

J38

DDI1_TXN_3

D27

DDI1_AUXP

E27

DDI1_AUXN

H34

DDI2_TXP_0

H33

DDI2_TXN_0

F37

DDI2_TXP_1

G38

DDI2_TXN_1

F34

DDI2_TXP_2

F35

DDI2_TXN_2

E37

DDI2_TXP_3

E36

DDI2_TXN_3

F26

DDI2_AUXP

E26

DDI2_AUXN

C34

DDI3_TXP_0

D34

DDI3_TXN_0

B36

DDI3_TXP_1

B34

DDI3_TXN_1

F33

DDI3_TXP_2

E33

DDI3_TXN_2

C33

DDI3_TXP_3

B33

DDI3_TXN_3

A27

DDI3_AUXP

B27

DDI3_AUXN

CPU_CFL-H_1440P

DP & PEG Compensation

y

eDP_RCOMP

Trace length < 100 Mils

Trace Width 5 Mils Trace Spacing 25 Mils

eDP_COMPIO and ICOMPO signals should be shorted

near balls and routed with typical impedance <25 mohms

EDP_TXP_0

EDP_TXN_0

EDP_TXP_1

EDP_TXN_1

EDP_TXP_2

EDP_TXN_2

EDP_TXP_3

EDP_TXN_3

EDP_AUXP

EDP_AUXN

EDP_DISP_UTIL

DISP_RCOMP

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

4 of 13

D29

E29

F28

E28

A29

B29

C28

B28

C26

B26

EDP_DISP_UTIL

A33

EDP_RCOMP

D37

AUD_AZACPU_SCLK

G27

AUD_AZACPU_SDO_R

G25

AUD_AZACPU_SDI_R

G29

TP3

R687 24.9_1%_4

R61 20_1%_4

+VCCIO

AUD_AZACPU_SCLK [10]

AUD_AZACPU_SDO_R [10]

AUD_AZACPU_SDI [10]

PEG_RCOMP

Trace length < 400 MILS

A A

Trace width = 12 MILS

Trace spacing = 15 MILS

5

4

+1.2VSUS [2,6,10,14,17,18,19,20,46,59,60,64,75]

+3V [2,9,10,11,13,17,18,19,20,23,31,32,33,35,37,38,39,46,47,48,50,51,52,53,54,57,59,62,63,64,65,68,70,73,75]

3

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

CFL 2/7 (DMI/EDP/PEG)

CFL 2/7 (DMI/EDP/PEG)

CFL 2/7 (DMI/EDP/PEG)

ZGE

ZGE

ZGE

1A

1A

1A

3 78Friday, May 03, 2019

3 78Friday, May 03, 2019

3 78Friday, May 03, 2019

1

5

4

3

2

1

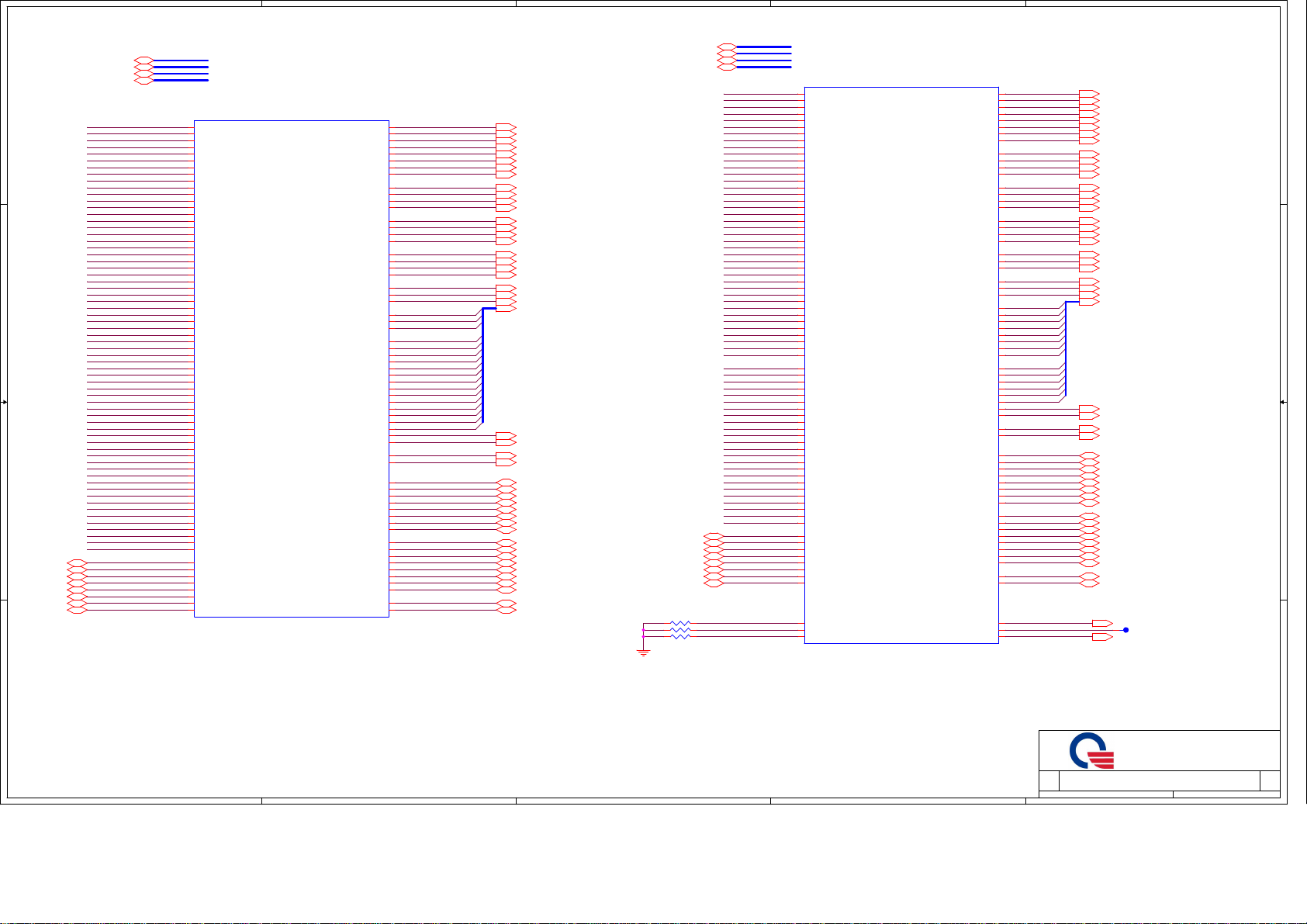

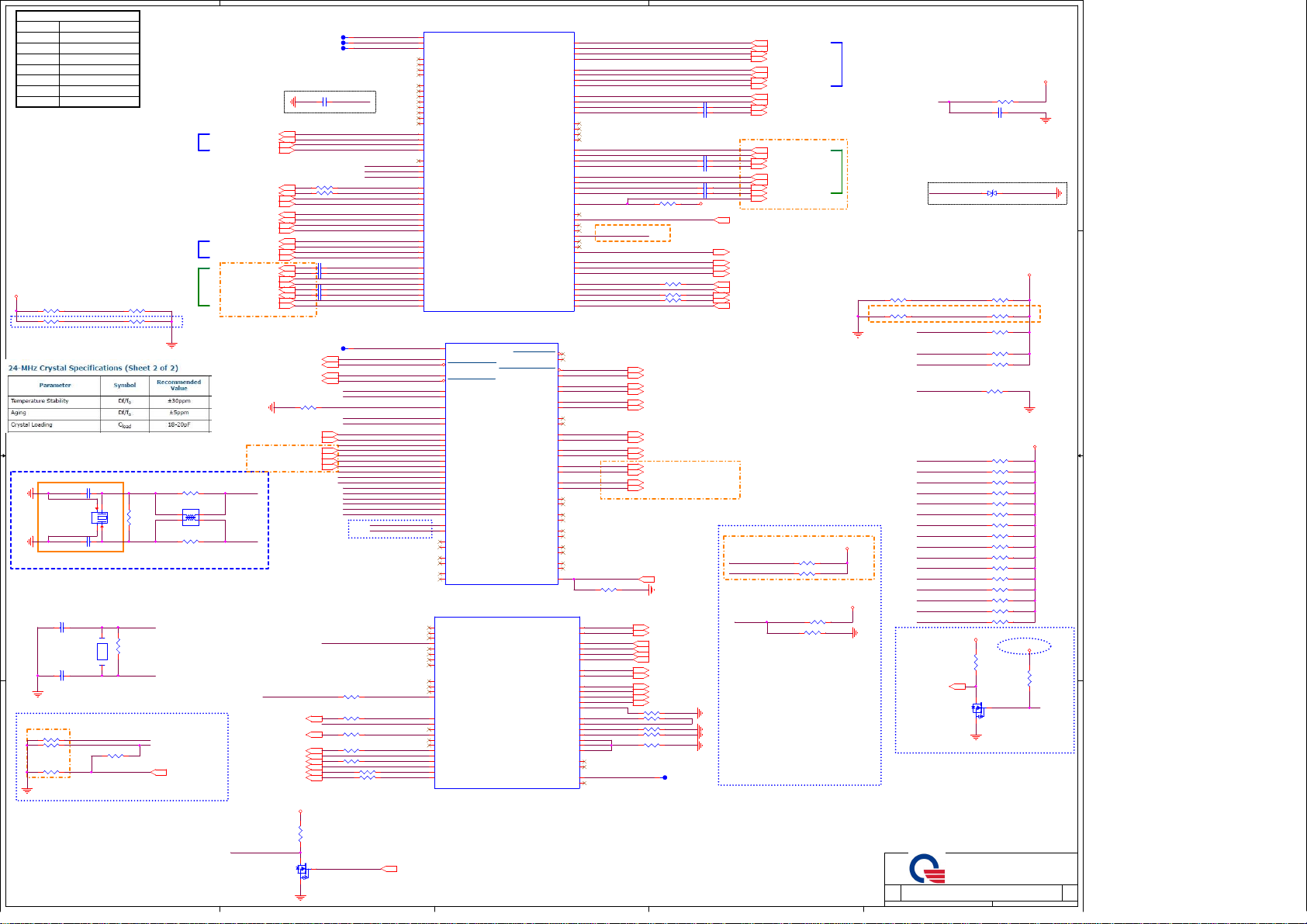

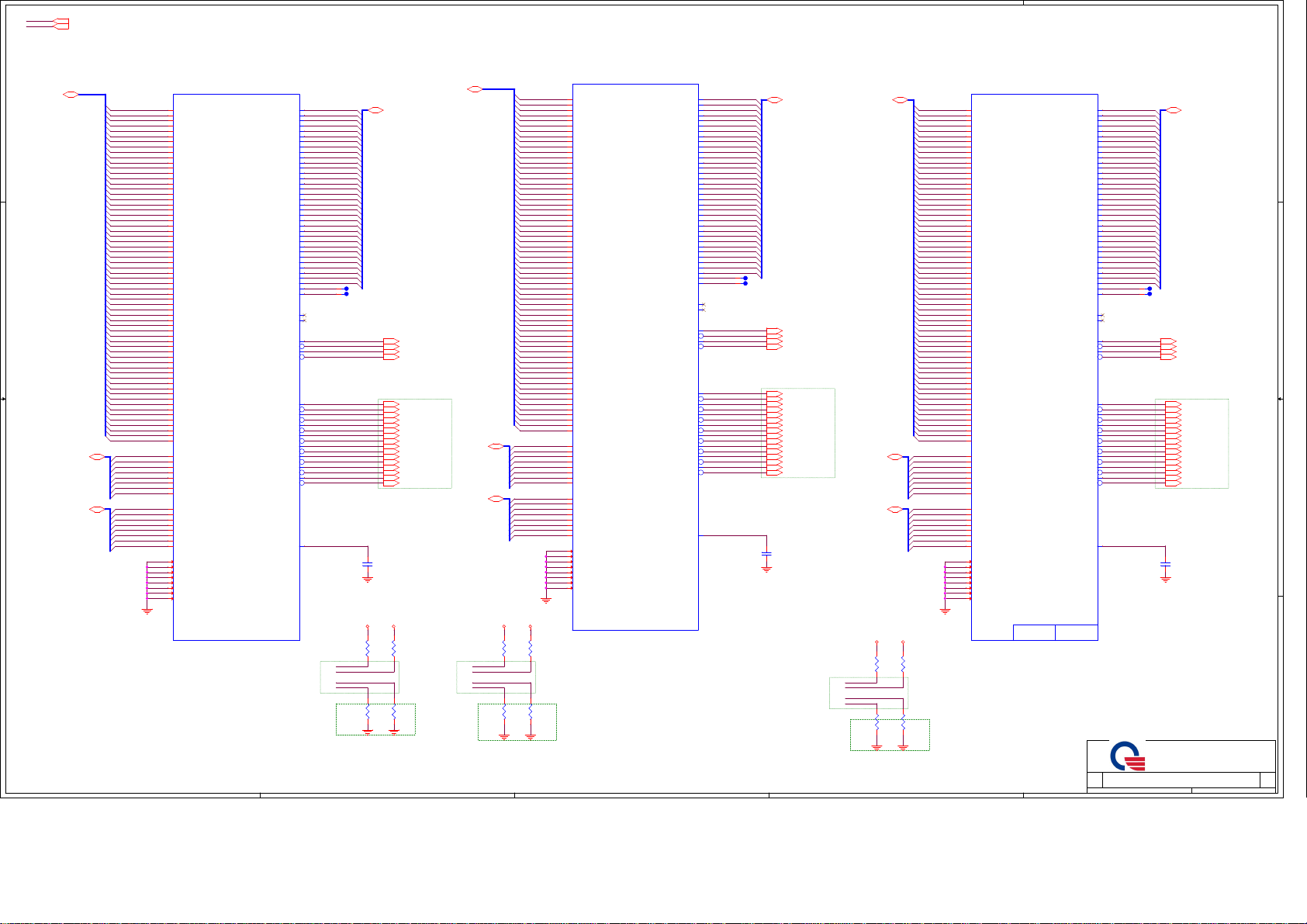

M_A_DQ[15:0][17,19]

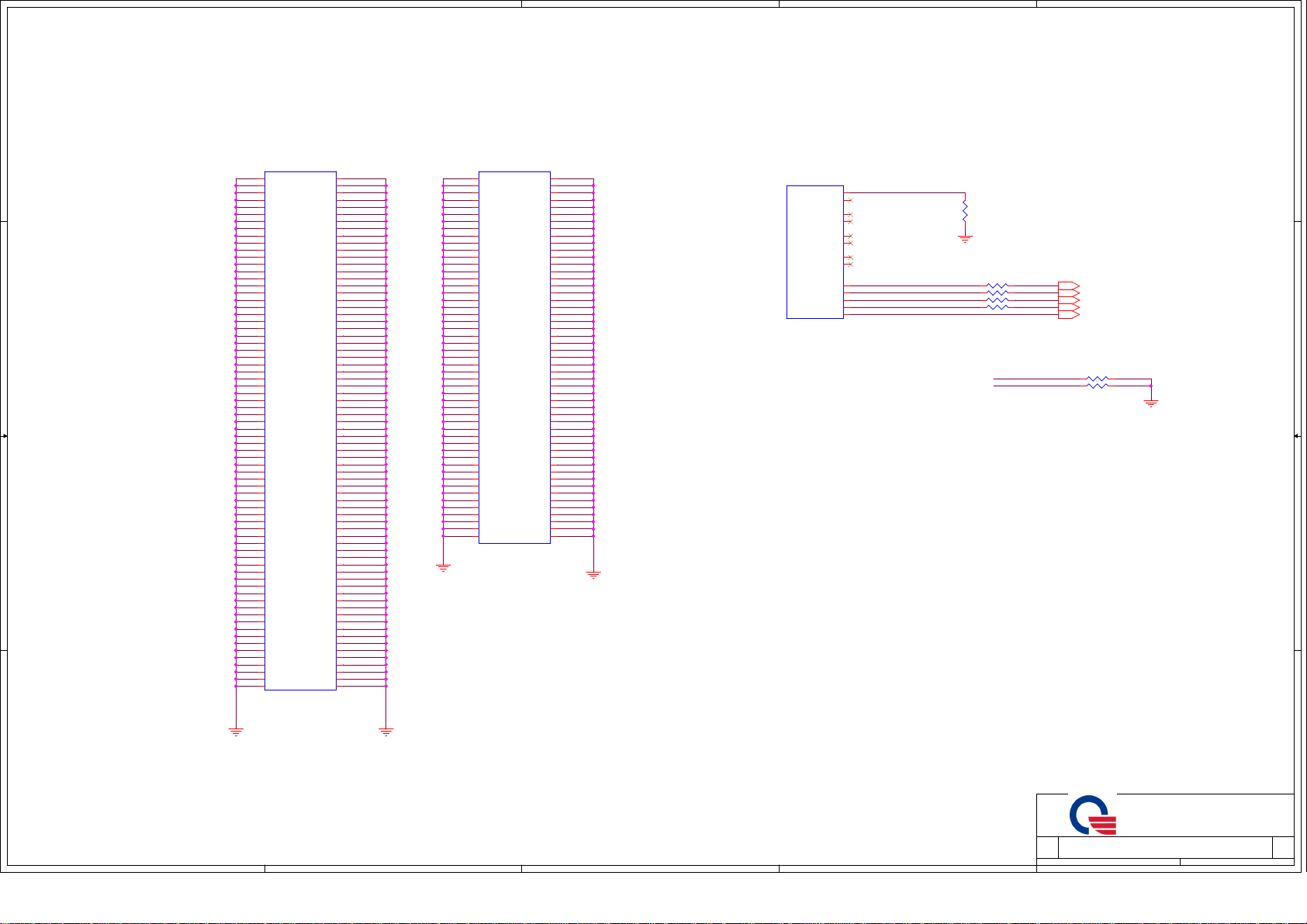

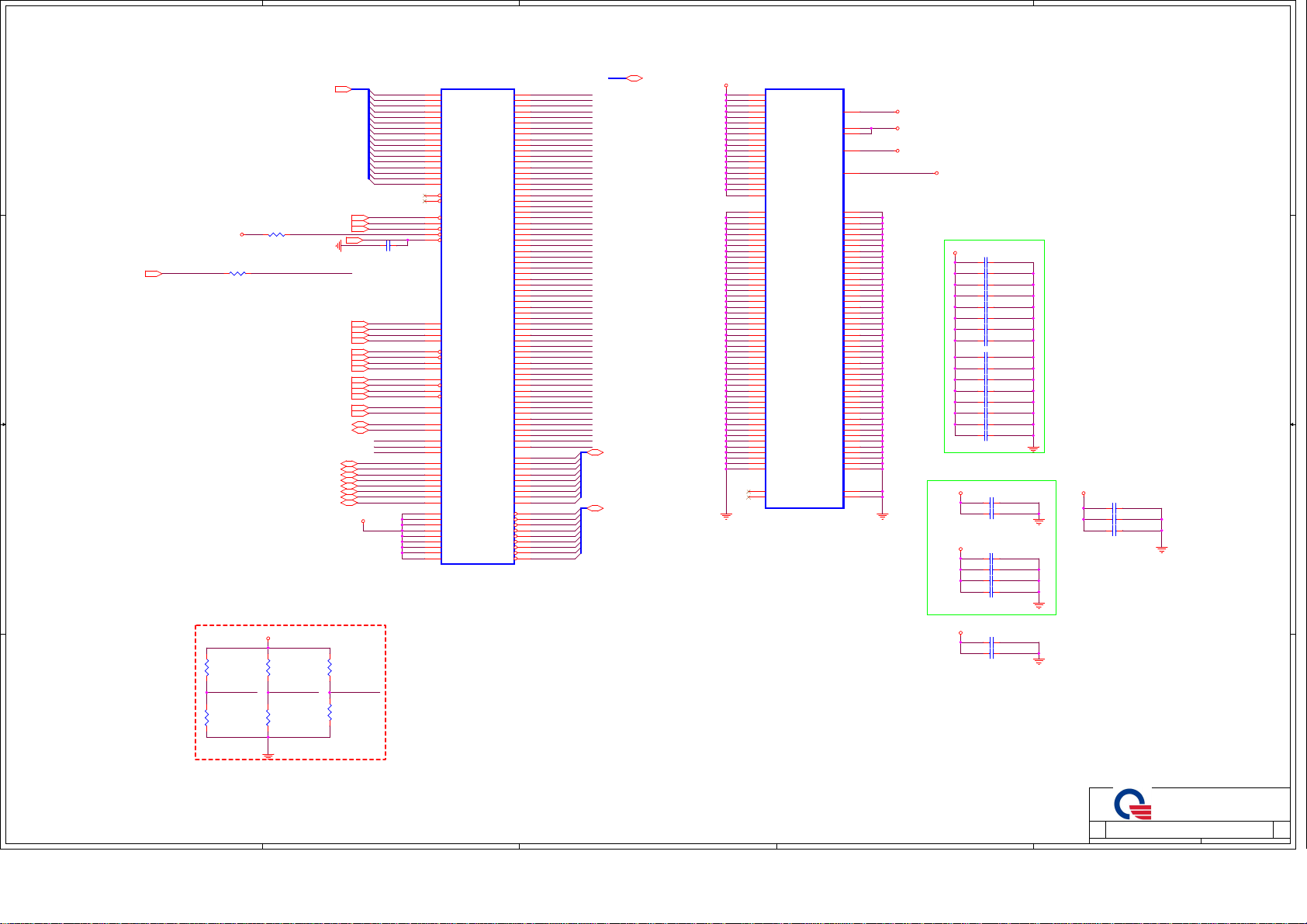

CFL Processor (DDR4)

M_A_DQ[31:16][17,19]

M_A_DQ[47:32][17,19]

M_A_DQ[63:48][17,19]

D D

C C

B B

M_A_CB0[17,19]

M_A_CB1[17,19]

M_A_CB2[17,19]

M_A_CB3[17,19]

M_A_CB4[17,19]

M_A_CB5[17,19]

M_A_CB6[17,19]

M_A_CB7[17,19]

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_CB0

M_A_CB1

M_A_CB2

M_A_CB3

M_A_CB4

M_A_CB5

M_A_CB6

M_A_CB7

Interleave / Non-Interleave

U3A

BR6

DDR0_DQ_0/DDR0_DQ_0

BT6

DDR0_DQ_1/DDR0_DQ_1

BP3

DDR0_DQ_2/DDR0_DQ_2

BR3

DDR0_DQ_3/DDR0_DQ_3

BN5

DDR0_DQ_4/DDR0_DQ_4

BP6

DDR0_DQ_5/DDR0_DQ_5

BP2

DDR0_DQ_6/DDR0_DQ_6

BN3

DDR0_DQ_7/DDR0_DQ_7

BL4

DDR0_DQ_8/DDR0_DQ_8

BL5

DDR0_DQ_9/DDR0_DQ_9

BL2

DDR0_DQ_10/DDR0_DQ_10

BM1

DDR0_DQ_11/DDR0_DQ_11

BK4

DDR0_DQ_12/DDR0_DQ_12

BK5

DDR0_DQ_13/DDR0_DQ_13

BK1

DDR0_DQ_14/DDR0_DQ_14

BK2

DDR0_DQ_15/DDR0_DQ_15

BG4

DDR0_DQ_16/DDR0_DQ_32

BG5

DDR0_DQ_17/DDR0_DQ_33

BF4

DDR0_DQ_18/DDR0_DQ_34

BF5

DDR0_DQ_19/DDR0_DQ_35

BG2

DDR0_DQ_20/DDR0_DQ_36

BG1

DDR0_DQ_21/DDR0_DQ_37

BF1

DDR0_DQ_22/DDR0_DQ_38

BF2

DDR0_DQ_23/DDR0_DQ_39

BD2

DDR0_DQ_24/DDR0_DQ_40

BD1

DDR0_DQ_25/DDR0_DQ_41

BC4

DDR0_DQ_26/DDR0_DQ_42

BC5

DDR0_DQ_27/DDR0_DQ_43

BD5

DDR0_DQ_28/DDR0_DQ_44

BD4

DDR0_DQ_29/DDR0_DQ_45

BC1

DDR0_DQ_30/DDR0_DQ_46

BC2

DDR0_DQ_31/DDR0_DQ_47

AB1

DDR0_DQ_32/DDR1_DQ_0

AB2

DDR0_DQ_33/DDR1_DQ_1

AA4

DDR0_DQ_34/DDR1_DQ_2

AA5

DDR0_DQ_35/DDR1_DQ_3

AB5

DDR0_DQ_36/DDR1_DQ_4

AB4

DDR0_DQ_37/DDR1_DQ_5

AA2

DDR0_DQ_38/DDR1_DQ_6

AA1

DDR0_DQ_39/DDR1_DQ_7

V5

DDR0_DQ_40/DDR1_DQ_8

V2

DDR0_DQ_41/DDR1_DQ_9

U1

DDR0_DQ_42/DDR1_DQ_10

U2

DDR0_DQ_43/DDR1_DQ_11

V1

DDR0_DQ_44/DDR1_DQ_12

V4

DDR0_DQ_45/DDR1_DQ_13

U5

DDR0_DQ_46/DDR1_DQ_14

U4

DDR0_DQ_47/DDR1_DQ_15

R2

DDR0_DQ_48/DDR1_DQ_32

P5

DDR0_DQ_49/DDR1_DQ_33

R4

DDR0_DQ_50/DDR1_DQ_34

P4

DDR0_DQ_51/DDR1_DQ_35

R5

DDR0_DQ_52/DDR1_DQ_36

P2

DDR0_DQ_53/DDR1_DQ_37

R1

DDR0_DQ_54/DDR1_DQ_38

P1

DDR0_DQ_55/DDR1_DQ_39

M4

DDR0_DQ_56/DDR1_DQ_40

M1

DDR0_DQ_57/DDR1_DQ_41

L4

DDR0_DQ_58/DDR1_DQ_42

L2

DDR0_DQ_59/DDR1_DQ_43

M5

DDR0_DQ_60/DDR1_DQ_44

M2

DDR0_DQ_61/DDR1_DQ_45

L5

DDR0_DQ_62/DDR1_DQ_46

L1

DDR0_DQ_63/DDR1_DQ_47

BA2

NC/DDR0_ECC_0

BA1

NC/DDR0_ECC_1

AY4

NC/DDR0_ECC_2

AY5

NC/DDR0_ECC_3

BA5

NC/DDR0_ECC_4

BA4

NC/DDR0_ECC_5

AY1

NC/DDR0_ECC_6

AY2

NC/DDR0_ECC_7

CPU_CFL-H_1440P

1 OF 13

DDR CHANNEL A

DDR0_DQSN_0/DDR0_DQSN_0

DDR0_DQSN_1/DDR0_DQSN_1

DDR0_DQSN_2/DDR0_DQSN_4

DDR0_DQSN_3/DDR0_DQSN_5

DDR0_DQSN_4/DDR1_DQSN_0

DDR0_DQSN_5/DDR1_DQSN_1

DDR0_DQSN_6/DDR1_DQSN_4

DDR0_DQSN_7/DDR1_DQSN_5

DDR0_DQSP_0/DDR0_DQSP_0

DDR0_DQSP_1/DDR0_DQSP_1

DDR0_DQSP_2/DDR0_DQSP_4

DDR0_DQSP_3/DDR0_DQSP_5

DDR0_DQSP_4/DDR1_DQSP_0

DDR0_DQSP_5/DDR1_DQSP_1

DDR0_DQSP_6/DDR1_DQSP_4

DDR0_DQSP_7/DDR1_DQSP_5

DDR0_DQSP_8/DDR0_DQSP_8

DDR0_DQSN_8/DDR0_DQSN_8

DDR0_CKP_0/DDR0_CKP_0

DDR0_CKN_0/DDR0_CKN_0

DDR0_CKP_1/DDR0_CKP_1

DDR0_CKN_1/DDR0_CKN_1

NC/DDR0_CKP_2

NC/DDR0_CKN_2

NC/DDR0_CKP_3

NC/DDR0_CKN_3

DDR0_CKE_0/DDR0_CKE_0

DDR0_CKE_1/DDR0_CKE_1

DDR0_CKE_2/DDR0_CKE_2

DDR0_CKE_3/DDR0_CKE_3

DDR0_CS#_0/DDR0_CS#_0

DDR0_CS#_1/DDR0_CS#_1

NC/DDR0_CS#_2

NC/DDR0_CS#_3

DDR0_ODT_0/DDR0_ODT_0

NC/DDR0_ODT_1

NC/DDR0_ODT_2

NC/DDR0_ODT_3

DDR0_CAB_4/DDR0_BA_0

DDR0_CAB_6/DDR0_BA_1

DDR0_CAA_5/DDR0_BG_0

DDR0_CAB_3/DDR0_MA_16

DDR0_CAB_2/DDR0_MA_14

DDR0_CAB_1/DDR0_MA_15

DDR0_CAB_9/DDR0_MA_0

DDR0_CAB_8/DDR0_MA_1

DDR0_CAB_5/DDR0_MA_2

NC/DDR0_MA_3

NC/DDR0_MA_4

DDR0_CAA_0/DDR0_MA_5

DDR0_CAA_2/DDR0_MA_6

DDR0_CAA_4/DDR0_MA_7

DDR0_CAA_3/DDR0_MA_8

DDR0_CAA_1/DDR0_MA_9

DDR0_CAB_7/DDR0_MA_10

DDR0_CAA_7/DDR0_MA_11

DDR0_CAA_6/DDR0_MA_12

DDR0_CAB_0/DDR0_MA_13

DDR0_CAA_9/DDR0_BG_1

DDR0_CAA_8/DDR0_ACT#

NC/DDR0_PAR

NC/DDR0_ALERT#

AG1

AG2

AK2

AK1

AL3

AK3

AL2

AL1

AT1

AT2

AT3

AT5

AD5

AE2

AD2

AE5

AD3

AE4

AE1

AD4

AH5

AH1

AU1

M_A_A16 M_B_A1

AH4

M_A_A14

AG4

M_A_A15

AD1

M_A_A0

AH3

M_A_A1

AP4

M_A_A2

AN4

M_A_A3

AP5

M_A_A4

AP2

M_A_A5

AP1

M_A_A6

AP3

M_A_A7

AN1

M_A_A8

AN3

M_A_A9

AT4

M_A_A10

AH2

M_A_A11

AN2

M_A_A12

AU4

M_A_A13

AE3

AU2

AU3

AG3

AU5

M_A_DQSN0

BR5

M_A_DQSN1

BL3

M_A_DQSN2

BG3

M_A_DQSN3

BD3

M_A_DQSN4

AA3

M_A_DQSN5 M_B_DQSP0

U3

M_A_DQSN6

P3

M_A_DQSN7

L3

M_A_DQSP0

BP5

M_A_DQSP1

BK3

M_A_DQSP2

BF3

M_A_DQSP3

BC3

M_A_DQSP4

AB3

M_A_DQSP5

V3

M_A_DQSP6

R3

M_A_DQSP7

M3

M_A_DQSP8

AY3

M_A_DQSN8

BA3

M_A_DIM0_CLKP0 [17]

M_A_DIM0_CLKN0 [17]

M_A_DIM0_CLKP1 [17]

M_A_DIM0_CLKN1 [17]

M_A_DIM1_CLKP0 [19]

M_A_DIM1_CLKN0 [19]

M_A_DIM1_CLKP1 [19]

M_A_DIM1_CLKN1 [19]

M_A_CKE0 [17]

M_A_CKE1 [17]

M_A_CKE2 [19]

M_A_CKE3 [19]

M_A_CS#0 [17]

M_A_CS#1 [17]

M_A_CS#2 [19]

M_A_CS#3 [19]

M_A_ODT0 [17]

M_A_ODT1 [17]

M_A_ODT2 [19]

M_A_ODT3 [19]

M_A_BS#0 [17,19]

M_A_BS#1 [17,19]

M_A_BG#0 [17,19]

M_A_A[16:0] [17,19]

M_A_BG#1 [17,19]

DDRA_ACT# [17,19]

DDR0_PAR [17,19]

DDR0_ALERT# [17,19]

M_A_DQSN0 [17,19]

M_A_DQSN1 [17,19]

M_A_DQSN2 [17,19]

M_A_DQSN3 [17,19]

M_A_DQSN4 [17,19]

M_A_DQSN5 [17,19] M_B_DQSP0 [18,20]

M_A_DQSN6 [17,19]

M_A_DQSN7 [17,19]

M_A_DQSP0 [17,19]

M_A_DQSP1 [17,19]

M_A_DQSP2 [17,19]

M_A_DQSP3 [17,19]

M_A_DQSP4 [17,19]

M_A_DQSP5 [17,19]

M_A_DQSP6 [17,19]

M_A_DQSP7 [17,19]

M_A_DQSP8 [17,19]

M_A_DQSN8 [17,19]

M_B_DQ[15:0][18,20]

M_B_DQ[31:16][18,20]

M_B_DQ[47:32][18,20]

M_B_DQ[48:63][18,20]

M_B_CB0[18,20]

M_B_CB1[18,20]

M_B_CB2[18,20]

M_B_CB3[18,20]

M_B_CB4[18,20]

M_B_CB5[18,20]

M_B_CB6[18,20]

M_B_CB7[18,20]

R99 121_1%_4

R105 75_1%_4

R109 100_1%_4

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_CB0

M_B_CB1

M_B_CB2

M_B_CB3

M_B_CB4

M_B_CB5

M_B_CB6

M_B_CB7

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

U3B

BT11

DDR1_DQ_0/DDR0_DQ_16

BR11

DDR1_DQ_1/DDR0_DQ_17

BT9

DDR1_DQ_2/DDR0_DQ_18

BR8

DDR1_DQ_3/DDR0_DQ_19

BP11

DDR1_DQ_4/DDR0_DQ_20

BN11

DDR1_DQ_5/DDR0_DQ_21

BP8

DDR1_DQ_6/DDR0_DQ_22

BN8

DDR1_DQ_7/DDR0_DQ_23

BL12

DDR1_DQ_8/DDR0_DQ_24

BL11

DDR1_DQ_9/DDR0_DQ_25

BL8

DDR1_DQ_10/DDR0_DQ_26

BJ8

DDR1_DQ_11/DDR0_DQ_27

BJ11

DDR1_DQ_12/DDR0_DQ_28

BJ10

DDR1_DQ_13/DDR0_DQ_29

BL7

DDR1_DQ_14/DDR0_DQ_30

BJ7

DDR1_DQ_15/DDR0_DQ_31

BG11

DDR1_DQ_16/DDR0_DQ_48

BG10

DDR1_DQ_17/DDR0_DQ_49

BG8

DDR1_DQ_18/DDR0_DQ_50

BF8

DDR1_DQ_19/DDR0_DQ_51

BF11

DDR1_DQ_20/DDR0_DQ_52

BF10

DDR1_DQ_21/DDR0_DQ_53

BG7

DDR1_DQ_22/DDR0_DQ_54

BF7

DDR1_DQ_23/DDR0_DQ_55

BB11

DDR1_DQ_24/DDR0_DQ_56

BC11

DDR1_DQ_25/DDR0_DQ_57

BB8

DDR1_DQ_26/DDR0_DQ_58

BC8

DDR1_DQ_27/DDR0_DQ_59

BC10

DDR1_DQ_28/DDR0_DQ_60

BB10

DDR1_DQ_29/DDR0_DQ_61

BC7

DDR1_DQ_30/DDR0_DQ_62

BB7

DDR1_DQ_31/DDR0_DQ_63

AA11

DDR1_DQ_32/DDR1_DQ_16

AA10

DDR1_DQ_33/DDR1_DQ_17

AC11

DDR1_DQ_34/DDR1_DQ_18

AC10

DDR1_DQ_35/DDR1_DQ_19

AA7

DDR1_DQ_36/DDR1_DQ_20

AA8

DDR1_DQ_37/DDR1_DQ_21

AC8

DDR1_DQ_38/DDR1_DQ_22

AC7

DDR1_DQ_39/DDR1_DQ_23

W8

DDR1_DQ_40/DDR1_DQ_24

W7

DDR1_DQ_41/DDR1_DQ_25

V10

DDR1_DQ_42/DDR1_DQ_26

V11

DDR1_DQ_43/DDR1_DQ_27

W11

DDR1_DQ_44/DDR1_DQ_28

W10

DDR1_DQ_45/DDR1_DQ_29

V7

DDR1_DQ_46/DDR1_DQ_30

V8

DDR1_DQ_47/DDR1_DQ_31

R11

DDR1_DQ_48/DDR1_DQ_48

P11

DDR1_DQ_49/DDR1_DQ_49

P7

DDR1_DQ_50/DDR1_DQ_50

R8

DDR1_DQ_51/DDR1_DQ_51

R10

DDR1_DQ_52/DDR1_DQ_52

P10

DDR1_DQ_53/DDR1_DQ_53

R7

DDR1_DQ_54/DDR1_DQ_54

P8

DDR1_DQ_55/DDR1_DQ_55

L11

DDR1_DQ_56/DDR1_DQ_56

M11

DDR1_DQ_57/DDR1_DQ_57

L7

DDR1_DQ_58/DDR1_DQ_58

M8

DDR1_DQ_59/DDR1_DQ_59

L10

DDR1_DQ_60/DDR1_DQ_60

M10

DDR1_DQ_61/DDR1_DQ_61

M7

DDR1_DQ_62/DDR1_DQ_62

L8

DDR1_DQ_63/DDR1_DQ_63

AW11

NC/DDR1_ECC_0

AY11

NC/DDR1_ECC_1

AY8

NC/DDR1_ECC_2

AW8

NC/DDR1_ECC_3

AY10

NC/DDR1_ECC_4

AW10

NC/DDR1_ECC_5

AY7

NC/DDR1_ECC_6

AW7

NC/DDR1_ECC_7

G1

DDR_RCOMP_0

H1

DDR_RCOMP_1

J2

DDR_RCOMP_2

CPU_CFL-H_1440P

2 OF 13

DDR CHANNEL B

DDR1_CKP_0/DDR1_CKP_0

DDR1_CKN_0/DDR1_CKN_0

DDR1_CKP_1/DDR1_CKP_1

DDR1_CKN_1/DDR1_CKN_1

NC/DDR1_CKP_2

NC/DDR1_CKN_2

NC/DDR1_CKP_3

NC/DDR1_CKN_3

DDR1_CKE_0/DDR1_CKE_0

DDR1_CKE_1/DDR1_CKE_1

DDR1_CKE_2/DDR1_CKE_2

DDR1_CKE_3/DDR1_CKE_3

DDR1_CS#_0/DDR1_CS#_0

DDR1_CS#_1/DDR1_CS#_1

NC/DDR1_CS#_2

NC/DDR1_CS#_3

DDR1_ODT_0/DDR1_ODT_0

NC/DDR1_ODT_1

NC/DDR1_ODT_2

NC/DDR1_ODT_3

DDR1_CAB_3/DDR1_MA_16

DDR1_CAB_2/DDR1_MA_14

DDR1_CAB_1/DDR1_MA_15

DDR1_CAB_4/DDR1_BA_0

DDR1_CAB_6/DDR1_BA_1

DDR1_CAA_5/DDR1_BG_0

DDR1_CAB_9/DDR1_MA_0

DDR1_CAB_8/DDR1_MA_1

DDR1_CAB_5/DDR1_MA_2

NC/DDR1_MA_3

NC/DDR1_MA_4

DDR1_CAA_0/DDR1_MA_5

DDR1_CAA_2/DDR1_MA_6

DDR1_CAA_4/DDR1_MA_7

DDR1_CAA_3/DDR1_MA_8

DDR1_CAA_1/DDR1_MA_9

DDR1_CAB_7/DDR1_MA_10

DDR1_CAA_7/DDR1_MA_11

DDR1_CAA_6/DDR1_MA_12

DDR1_CAB_0/DDR1_MA_13

DDR1_CAA_9/DDR1_BG_1

DDR1_CAA_8/DDR1_ACT#

NC/DDR1_PAR

NC/DDR1_ALERT#

DDR1_DQSN_0/DDR0_DQSN_2

DDR1_DQSN_1/DDR0_DQSN_3

DDR1_DQSN_2/DDR0_DQSN_6

DDR1_DQSN_3/DDR0_DQSN_7

DDR1_DQSN_4/DDR1_DQSN_2

DDR1_DQSN_5/DDR1_DQSN_3

DDR1_DQSN_6/DDR1_DQSN_6

DDR1_DQSN_7/DDR1_DQSN_7

DDR1_DQSP_0/DDR0_DQSP_2

DDR1_DQSP_1/DDR0_DQSP_3

DDR1_DQSP_2/DDR0_DQSP_6

DDR1_DQSP_3/DDR0_DQSP_7

DDR1_DQSP_4/DDR1_DQSP_2

DDR1_DQSP_5/DDR1_DQSP_3

DDR1_DQSP_6/DDR1_DQSP_6

DDR1_DQSP_7/DDR1_DQSP_7

DDR1_DQSP_8/DDR1_DQSP_8

DDR1_DQSN_8/DDR1_DQSN_8

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

AM9

AN9

AM7

AM8

AM11

AM10

AJ10

AJ11

AT8

AT10

AT7

AT11

AF11

AE7

AF10

AE10

AF7

AE8

AE9

AE11

M_B_A16

AH10

M_B_A14

AH11

M_B_A15

AF8

AH8

AH9

AR9

M_B_A0

AJ9

AK6

M_B_A2

AK5

M_B_A3

AL5

M_B_A4

AL6

M_B_A5

AM6

M_B_A6

AN7

M_B_A7

AN10

M_B_A8

AN8

M_B_A9

AR11

M_B_A10

AH7

M_B_A11

AN11

M_B_A12

AR10

M_B_A13

AF9

AR7

AT9

AJ7

AR8

M_B_DQSN0

BN9

M_B_DQSN1

BL9

M_B_DQSN2

BG9

M_B_DQSN3

BC9

M_B_DQSN4

AC9

M_B_DQSN5

W9

M_B_DQSN6

R9

M_B_DQSN7

M9

BP9

M_B_DQSP1

BJ9

M_B_DQSP2

BF9

M_B_DQSP3

BB9

M_B_DQSP4

AA9

M_B_DQSP5

V9

M_B_DQSP6

P9

M_B_DQSP7

L9

M_B_DQSP8

AW9

M_B_DQSN8

AY9

SMDDR_VREF_CA

BN13

SMDDR_VREF_DQ0_M3

BP13

SMDDR_VREF_DQ1_M3

BR13

M_B_DIM0_CLKP0 [18]

M_B_DIM0_CLKN0 [18]

M_B_DIM0_CLKP1 [18]

M_B_DIM0_CLKN1 [18]

M_B_DIM1_CLKP0 [20]

M_B_DIM1_CLKN0 [20]

M_B_DIM1_CLKP1 [20]

M_B_DIM1_CLKN1 [20]

M_B_CKE0 [18]

M_B_CKE1 [18]

M_B_CKE2 [20]

M_B_CKE3 [20]

M_B_CS#0 [18]

M_B_CS#1 [18]

M_B_CS#2 [20]

M_B_CS#3 [20]

M_B_ODT0 [18]

M_B_ODT1 [18]

M_B_ODT2 [20]

M_B_ODT3 [20]

M_B_A16 [18,20]

M_B_A14 [18,20]

M_B_A15 [18,20]

M_B_BS#0 [18,20]

M_B_BS#1 [18,20]

M_B_BG#0 [18,20]

M_B_A[13:0] [18,20]

M_B_BG#1 [18,20]

DDRB_ACT# [18,20]

DDR1_PAR [18,20]

DDR1_ALERT# [18,20]

M_B_DQSN0 [18,20]

M_B_DQSN1 [18,20]

M_B_DQSN2 [18,20]

M_B_DQSN3 [18,20]

M_B_DQSN4 [18,20]

M_B_DQSN5 [18,20]

M_B_DQSN6 [18,20]

M_B_DQSN7 [18,20]

M_B_DQSP1 [18,20]

M_B_DQSP2 [18,20]

M_B_DQSP3 [18,20]

M_B_DQSP4 [18,20]

M_B_DQSP5 [18,20]

M_B_DQSP6 [18,20]

M_B_DQSP7 [18,20]

M_B_DQSP8 [18,20]

M_B_DQSN8 [18,20]

SMDDR_VREF_CA [17]

TP9

SMDDR_VREF_DQ1_M3 [18]

04

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

CFL 3/7 (DDR4 I/F)

CFL 3/7 (DDR4 I/F)

CFL 3/7 (DDR4 I/F)

ZGE

ZGE

ZGE

1A

1A

4 78Friday, May 03, 2019

4 78Friday, May 03, 2019

1

4 78Friday, May 03, 2019

1A

5

4

3

2

1

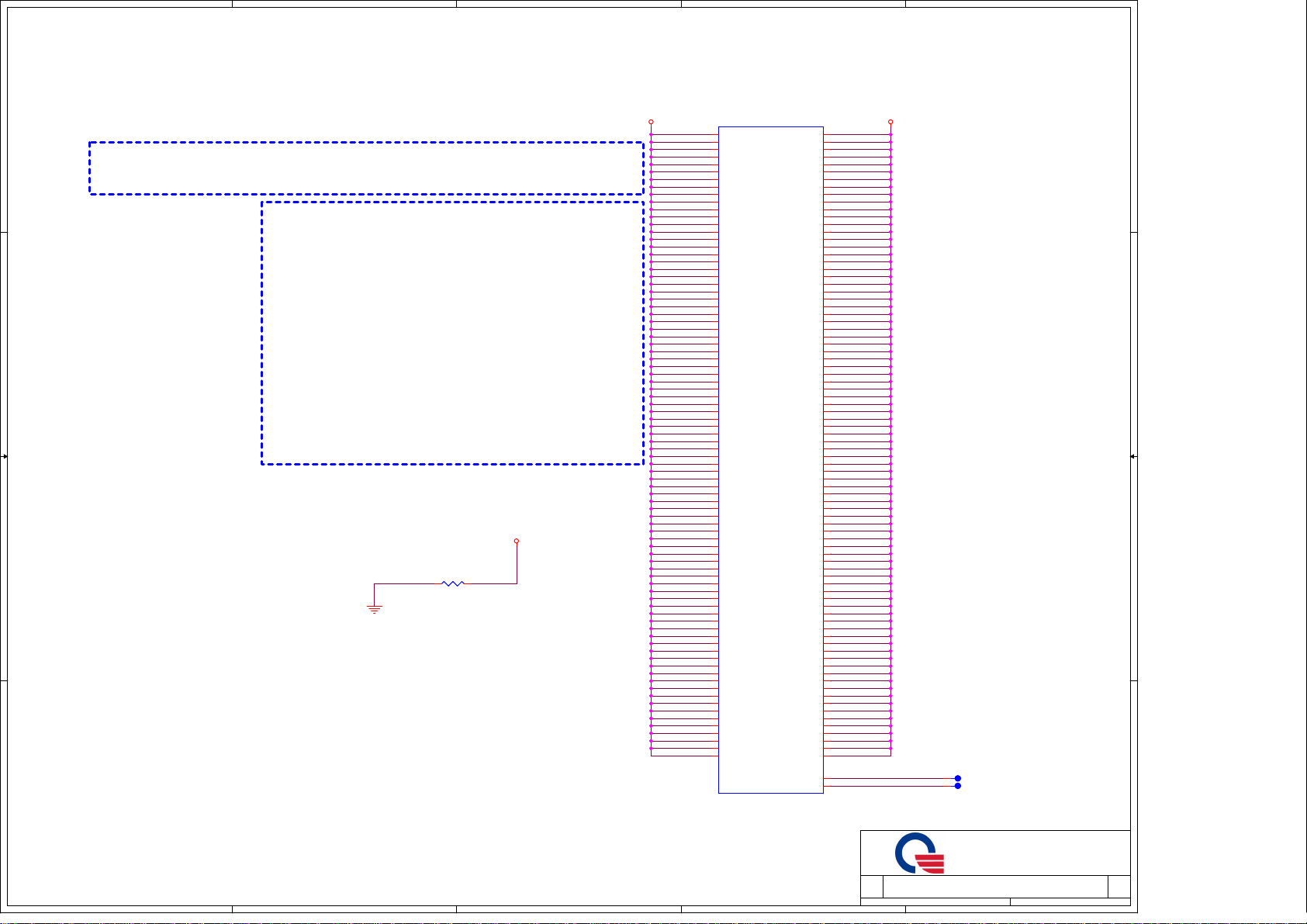

VCCGT

Edge cap

4x 47uF 0805

7x 22uF 0603

CFL Processor (POWER)

05

Backside cap

10x 10uF 0402

D D

12x 1uF 0201

C C

B B

R686

Close CPU

+VCC_GT

*short_0805

Modify 8/15

A A

+VCC_GT +VCC_GT

U3K

AT14

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AU14

AU29

AU30

AU31

AU32

AU35

AU36

AU37

AU38

AV29

AV30

AV31

AV32

AV33

AV34

AV35

AV36

AW14

AW31

AW32

AW33

AW34

AW35

AW36

AW37

AW38

AY29

AY30

AY31

AY32

AY35

AY36

AY37

AY38

BA13

BA14

BA29

BA30

BA31

BA32

BA33

BA34

BA35

BA36

BB13

BB14

BB31

BB32

BB33

BB34

BB35

BB36

BB37

BB38

BC29

BC30

BC31

BC32

BC35

BC36

BC37

BC38

BD13

BD14

BD29

BD30

BD31

BD32

BD33

BD34

BP37

BP38

BR15

BR16

BR17

CPU_CFL-H_1440P

VCCGT1

VCCGT2

VCCGT3

VCCGT4

VCCGT5

VCCGT6

VCCGT7

VCCGT8

VCCGT9

VCCGT10

VCCGT11

VCCGT12

VCCGT13

VCCGT14

VCCGT15

VCCGT16

VCCGT17

VCCGT18

VCCGT19

VCCGT20

VCCGT21

VCCGT22

VCCGT23

VCCGT24

VCCGT25

VCCGT26

VCCGT27

VCCGT28

VCCGT29

VCCGT30

VCCGT31

VCCGT32

VCCGT33

VCCGT34

VCCGT35

VCCGT36

VCCGT37

VCCGT38

VCCGT39

VCCGT40

VCCGT41

VCCGT42

VCCGT43

VCCGT44

VCCGT45

VCCGT46

VCCGT47

VCCGT48

VCCGT49

VCCGT50

VCCGT51

VCCGT52

VCCGT53

VCCGT54

VCCGT55

VCCGT56

VCCGT57

VCCGT58

VCCGT59

VCCGT60

VCCGT61

VCCGT62

VCCGT63

VCCGT64

VCCGT65

VCCGT66

VCCGT67

VCCGT68

VCCGT69

VCCGT70

VCCGT71

VCCGT72

VCCGT73

VCCGT74

VCCGT75

VCCGT76

VCCGT77

VCCGT78

VCCGT79

VCCGT159

VCCGT160

VCCGT161

VCCGT162

VCCGT163

11 OF 13

VCCGT80

VCCGT81

VCCGT82

VCCGT83

VCCGT84

VCCGT85

VCCGT86

VCCGT87

VCCGT88

VCCGT89

VCCGT90

VCCGT91

VCCGT92

VCCGT93

VCCGT94

VCCGT95

VCCGT96

VCCGT97

VCCGT98

VCCGT99

VCCGT100

VCCGT101

VCCGT102

VCCGT103

VCCGT104

VCCGT105

VCCGT106

VCCGT107

VCCGT108

VCCGT109

VCCGT110

VCCGT111

VCCGT112

VCCGT113

VCCGT114

VCCGT115

VCCGT116

VCCGT117

VCCGT118

VCCGT119

VCCGT120

VCCGT121

VCCGT122

VCCGT123

VCCGT124

VCCGT125

VCCGT126

VCCGT127

VCCGT128

VCCGT129

VCCGT130

VCCGT131

VCCGT132

VCCGT133

VCCGT134

VCCGT135

VCCGT136

VCCGT137

VCCGT138

VCCGT139

VCCGT140

VCCGT141

VCCGT142

VCCGT143

VCCGT144

VCCGT145

VCCGT146

VCCGT147

VCCGT148

VCCGT149

VCCGT150

VCCGT151

VCCGT152

VCCGT153

VCCGT154

VCCGT155

VCCGT156

VCCGT157

VCCGT158

VCCGT164

VCCGT165

VCCGT166

VCCGT167

VCCGT168

VSSGT_SENSE

VCCGT_SENSE

BD35

BD36

BE31

BE32

BE33

BE34

BE35

BE36

BE37

BE38

BF13

BF14

BF29

BF30

BF31

BF32

BF35

BF36

BF37

BF38

BG29

BG30

BG31

BG32

BG33

BG34

BG35

BG36

BH33

BH34

BH35

BH36

BH37

BH38

BJ16

BJ17

BJ19

BJ20

BJ21

BJ23

BJ24

BJ26

BJ27

BJ37

BJ38

BK16

BK17

BK19

BK20

BK21

BK23

BK24

BK26

BK27

BL15

BL16

BL17

BL23

BL24

BL25

BL26

BL27

BL28

BL36

BL37

BM15

BM16

BM17

BM36

BM37

BN15

BN16

BN17

BN36

BN37

BN38

BP15

BP16

BP17

BR37

BT15

BT16

BT17

BT37

AH37

AH38

VGT_VSSSENSE

VGT_VCCSENSE

TP2

TP1

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

CFL 4/7 (POWER)

CFL 4/7 (POWER)

CFL 4/7 (POWER)

ZGE

ZGE

ZGE

1A

1A

5 78Friday, May 03, 2019

5 78Friday, May 03, 2019

5 78Friday, May 03, 2019

1

1A

5

4

3

2

1

Follow CFL H EDS page 128 to 45W(GT2): VCCSA=11.1A

+VCC_SA

Edge cap

D D

2x 47uF 0805

2x 22uF 0805

C611

22u/6.3V_6

Close CPU

C620

22u/6.3V_6

C643

47u/6.3V_8

C631

47u/6.3V_8

Backside cap

7x 10uF 0402

C591

10u/6.3V_4

Under CPU

0621Bear

C605

10u/6.3V_4

C598

10u/6.3V_4

C575

1u/6.3V_4

C584

10u/6.3V_4

C547

10u/6.3V_4

+VCCIO

C574

10u/6.3V_4

C562

10u/6.3V_4

Follow CFL H EDS P128 to 45W:

VCCIO,

C C

+VCCIO = 6.4A

+VCC_IO

C618

10u/6.3V_4

C638

10u/6.3V_4

Under CPU

C608

10u/6.3V_4

Backside cap

3x 10uF 0402

+1V_SUS

*0_5%_6

+VCCSTG

B B

R688

R689

modify 8/9

*short_0603

+VCCIO

+VCC_SA

AG12

U3L

J30

VCCSA1

K29

VCCSA2

K30

VCCSA3

K31

VCCSA4

K32

VCCSA5

K33

VCCSA6

K34

VCCSA7

K35

VCCSA8

L31

VCCSA9

L32

VCCSA10

L35

VCCSA11

L36

VCCSA12

L37

VCCSA13

L38

VCCSA14

M29

VCCSA15

M30

VCCSA16

M31

VCCSA17

M32

VCCSA18

M33

VCCSA19

M34

VCCSA20

M35

VCCSA21

M36

VCCSA22

VCCIO1

G15

VCCIO2

G17

VCCIO3

G19

VCCIO4

G21

VCCIO5

H15

VCCIO6

H16

VCCIO7

H17

VCCIO8

H19

VCCIO9

H20

VCCIO10

H21

VCCIO11

H26

VCCIO12

H27

VCCIO13

J15

VCCIO14

J16

VCCIO15

J17

VCCIO16

J19

VCCIO17

J20

VCCIO18

J21

VCCIO19

J26

VCCIO20

J27

VCCIO21

CPU_CFL-H_1440P

11.1 A

6.4 A

12 OF 13

3.3 A

0.13 A

0.06 A

0.02 A

0.15 A

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VDDQ19

VDDQ20

VDDQ21

VDDQ22

VDDQ23

VDDQ24

VDDQ25

VCCPLL_OC1

VCCPLL_OC2

VCCPLL_OC3

VCCST

VCCSTG2

VCCSTG1

VCCPLL1

VCCPLL2

VCCSA_SENSE

VSSSA_SENSE

VCCIO_SENSE

VSSIO_SENSE

AA6

AE12

AF5

AF6

AG5

AG9

AJ12

AL11

AP6

AP7

AR12

AR6

AT12

AW6

AY6

J5

J6

K12

K6

L12

L6

R6

T6

W6

Y12

BH13

BJ13

G11

H30

H29

G30

H28

J28

M38

M37

H14

J14

Follow CFL H EDS page 127 45W: VDDQ=3.3A (LPDDR4)

+1.2VSUS

C662

22u/6.3V_6

C303

22u/6.3V_6

Under CPU

C96

22u/6.3V_6

C663

22u/6.3V_6

VDDQ

Backside cap

4x 22uF 0603

11x 10uF 0402

C667

10u/6.3V_4

C140

10u/6.3V_4

C123

10u/6.3V_4

C666

10u/6.3V_4

C654

10u/6.3V_4

C122

10u/6.3V_4

C658

10u/6.3V_4

C651

10u/6.3V_4

C97

10u/6.3V_4

C668

10u/6.3V_4

VCC_PLL_OC

+VCCPLL_OC

+VCCST

modify 8/9

Backside cap

2x 1uF 0201

VCC_ST

VCCSA_VCCSENSE [65]

VCCIO_VCCSENSE

VSSIO_VCCSENSE

VCCSA_VSSSENSE [65]

modify 8/22

+VCCSTG

+VCCPLL

TP63

TP64

C555

1u/10V_2

Backside cap

1x 1uF 0201

VccSTG

Backside cap

1x 1uF 0201

VCC_PLL

C98

10u/6.3V_4

06

Backside cap

Under CPU

+VCCSTG +VCCPLL_OC +VCCPLL+VCCIO

R110

+VCCPLL_OC+1.2VSUS

*short_0603

4x 22uF 0603

11x 10uF 0404

+VCCST

modify 8/9

C93

22u/6.3V_6

+VCCPLL

C537

22u/6.3V_6

C559

22u/6.3V_6

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

CFL 5/7 (POWER&GND )

CFL 5/7 (POWER&GND )

CFL 5/7 (POWER&GND )

ZGE

ZGE

ZGE

6 78Friday, May 03, 2019

6 78Friday, May 03, 2019

6 78Friday, May 03, 2019

1

1A

1A

1A

C630

C582

1u/10V_2

A A

5

C648

22u/6.3V_6

C659

1u/10V_2

C649

1u/10V_2

modify 8/3

C641

1u/6.3V_4

4

*1u/6.3V_4

C625

*1u/6.3V_4

C589

1u/10V_2

C594

22u/6.3V_6

+1V_SUS

R690

R685

3

*short_0603

*short_0603

5

4

3

2

1

W35

W36

W37

W38

Y29

Y30

Y31

Y32

Y33

Y34

Y35

Y36

07

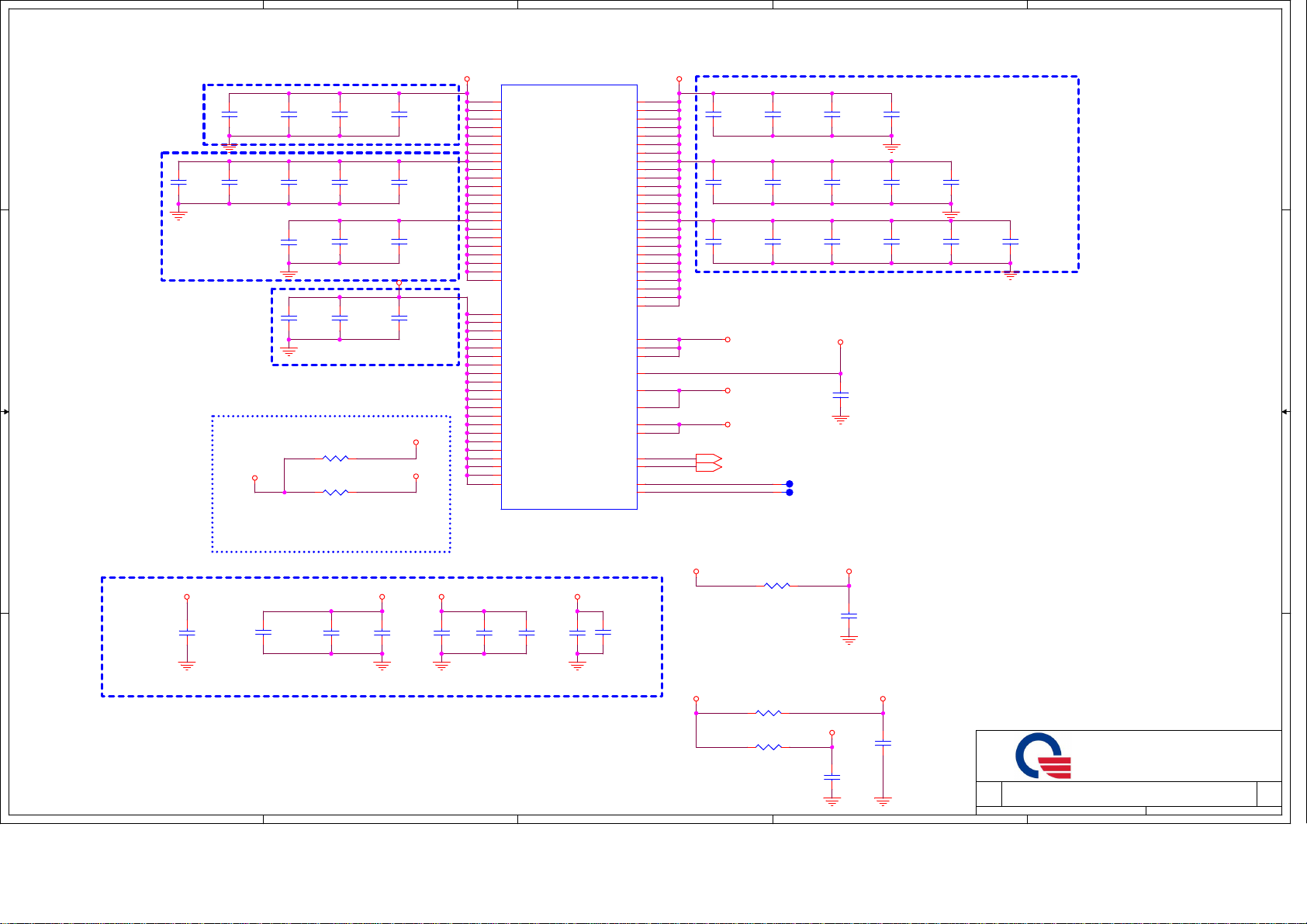

Vcc (VCC_CORE)

Edge cap

8 x 47uF 0805

D D

C C

B B

A A

Backside cap

12x 22uF 0603

42x 10uF 0402

48x 1uF 0201

24x 0201 (placeholder)

Under CPU

C612

C622

22u/6.3V_6

C604

22u/6.3V_6

C558

10u/6.3V_4

C567

10u/6.3V_4

C652

*10u/6.3V_4

22u/6.3V_6

C602

22u/6.3V_6

C580

10u/6.3V_4

C573

10u/6.3V_4

C637

10u/6.3V_4

C627

22u/6.3V_6

C621

22u/6.3V_6

C587

10u/6.3V_4

C554

10u/6.3V_4

C585

*10u/6.3V_4

Follow CFL H EDS page 124 to 45W(GT2): VCC_CORE=96A

Close CPU

C644

47u/6.3V_8

C636

22u/6.3V_6

C614

22u/6.3V_6

C569

10u/6.3V_4

C568

10u/6.3V_4

C607

10u/6.3V_4

modify 8/9

C632

47u/6.3V_8

C623

22u/6.3V_6

C596

10u/6.3V_4

C590

10u/6.3V_4

C578

10u/6.3V_4

C629

*10u/6.3V_4

C645

47u/6.3V_8

C617

22u/6.3V_6

C557

10u/6.3V_4

C600

10u/6.3V_4

C595

10u/6.3V_4

C615

10u/6.3V_4

C646

47u/6.3V_8

C613

22u/6.3V_6

C588

10u/6.3V_4

C609

10u/6.3V_4

C586

10u/6.3V_4

C634

*47u/6.3V_8

+VCC_CORE +VCC_CORE

U3I

AA13

C647

47u/6.3V_8

C603

22u/6.3V_6

C581

10u/6.3V_4

C593

10u/6.3V_4

C583

10u/6.3V_4

C597

10u/6.3V_4

C633

*47u/6.3V_8

AA31

AA32

AA33

AA34

AA35

AA36

AA37

AA38

AB29

AB30

AB31

AB32

AB35

AB36

AB37

AB38

AC13

AC14

AC29

AC30

AC31

AC32

AC33

AC34

AC35

AC36

AD13

AD14

AD31

AD32

AD33

AD34

AD35

AD36

AD37

AD38

AE13

AE14

AE30

AE31

AE32

AE35

AE36

AE37

AE38

AF29

AF30

AF31

AF32

AF33

AF34

AF35

AF36

AF37

AF38

AG14

AG31

AG32

AG33

AG34

AG35

AG36

VCC#AA13

VCC#AA31

VCC#AA32

VCC#AA33

VCC#AA34

VCC#AA35

VCC#AA36

VCC#AA37

VCC#AA38

VCC#AB29

VCC#AB30

VCC#AB31

VCC#AB32

VCC#AB35

VCC#AB36

VCC#AB37

VCC#AB38

VCC#AC13

VCC#AC14

VCC#AC29

VCC#AC30

VCC#AC31

VCC#AC32

VCC#AC33

VCC#AC34

VCC#AC35

VCC#AC36

VCC#AD13

VCC#AD14

VCC#AD31

VCC#AD32

VCC#AD33

VCC#AD34

VCC#AD35

VCC#AD36

VCC#AD37

VCC#AD38

VCC#AE13

VCC#AE14

VCC#AE30

VCC#AE31

VCC#AE32

VCC#AE35

VCC#AE36

VCC#AE37

VCC#AE38

VCC#AF29

VCC#AF30

VCC#AF31

VCC#AF32

VCC#AF33

VCC#AF34

VCC#AF35

VCC#AF36

VCC#AF37

VCC#AF38

VCC#AG14

VCC#AG31

VCC#AG32

VCC#AG33

VCC#AG34

VCC#AG35

VCC#AG36

CPU_CFL-H_1440P

9 OF 13

VCC#AH13

VCC#AH14

VCC#AH29

VCC#AH30

VCC#AH31

VCC#AH32

VCC#AJ14

VCC#AJ29

VCC#AJ30

VCC#AJ31

VCC#AJ32

VCC#AJ33

VCC#AJ34

VCC#AJ35

VCC#AJ36

VCC#AK31

VCC#AK32

VCC#AK33

VCC#AK34

VCC#AK35

VCC#AK36

VCC#AK37

VCC#AK38

VCC#AL13

VCC#AL29

VCC#AL30

VCC#AL31

VCC#AL32

VCC#AL35

VCC#AL36

VCC#AL37

VCC#AL38

VCC#AM13

VCC#AM14

VCC#AM29

VCC#AM30

VCC#AM31

VCC#AM32

VCC#AM33

VCC#AM34

VCC#AM35

VCC#AM36

VCC#AN13

VCC#AN14

VCC#AN31

VCC#AN32

VCC#AN33

VCC#AN34

VCC#AN35

VCC#AN36

VCC#AN37

VCC#AN38

VCC#AP13

VCC#AP30

VCC#AP31

VCC#AP32

VCC#AP35

VCC#AP36

VCC#AP37

VCC#AP38

VCC#K13

VCC_SENSE

VSS_SENSE

AH13

AH14

AH29

AH30

AH31

AH32

AJ14

AJ29

AJ30

AJ31

AJ32

AJ33

AJ34

AJ35

AJ36

AK31

AK32

AK33

AK34

AK35

AK36

AK37

AK38

AL13

AL29

AL30

AL31

AL32

AL35

AL36

AL37

AL38

AM13

AM14

AM29

AM30

AM31

AM32

AM33

AM34

AM35

AM36

AN13

AN14

AN31

AN32

AN33

AN34

AN35

AN36

AN37

AN38

AP13

AP30

AP31

AP32

AP35

AP36

AP37

AP38

K13

AG37

AG38

VCCSENSE

VSSSENSE

Under CPU

C542

1u/10V_2

C545

1u/10V_2

C565

1u/10V_2

C599

*10u/6.3V_4

C40

*1u/10V_2

C47

*1u/10V_2

+VCC_CORE

C656

C553

1u/10V_2

1u/10V_2

C556

C560

1u/10V_2

1u/10V_2

C544

C552

1u/10V_2

1u/10V_2

C576

*10u/6.3V_4

C571

C44

*1u/10V_2

*1u/10V_2

C46

C579

*1u/10V_2

*1u/10V_2

Sense resistor should be placed within 2

inches (50.8 mm) of the processor socket

Trace Impendence 50 ohm

R32

100_1%_4

VCCSENSE [65]

VSSSENSE [65]

R31

100_1%_4

C664

1u/10V_2

C566

1u/10V_2

C549

1u/10V_2

C624

*10u/6.3V_4

C38

*1u/10V_2

C577

*1u/10V_2

modify 8/9

C665

1u/10V_2

C548

1u/10V_2

C550

1u/10V_2

C592

*10u/6.3V_4

C36

*1u/10V_2

C39

*1u/10V_2

+VCC_CORE [65,66]

C541

1u/10V_2

C561

1u/10V_2

C570

1u/10V_2

C564

*10u/6.3V_4

C37

*1u/10V_2

C43

*1u/10V_2

C653

1u/10V_2

C546

1u/10V_2

C642

*10u/6.3V_4

C42

*1u/10V_2

C45

*1u/10V_2

C563

1u/10V_2

C540

1u/10V_2

C661

*10u/6.3V_4

C41

*1u/10V_2

C572

*1u/10V_2

C551

1u/10V_2

C543

1u/10V_2

U3J

K14

VCC#K14

L13

VCC#L13

L14

VCC#L14

N13

VCC#N13

N14

VCC#N14

N30

VCC#N30

N31

VCC#N31

N32

VCC#N32

N35

VCC#N35

N36

VCC#N36

N37

VCC#N37

N38

VCC#N38

P13

VCC#P13

P14

VCC#P14

P29

VCC#P29

P30

VCC#P30

P31

VCC#P31

P32

VCC#P32

P33

VCC#P33

P34

VCC#P34

P35

VCC#P35

P36

VCC#P36

R13

VCC#R13

R31

VCC#R31

R32

VCC#R32

R33

VCC#R33

R34

VCC#R34

R35

VCC#R35

R36

VCC#R36

R37

VCC#R37

R38

VCC#R38

T29

VCC#T29

T30

VCC#T30

T31

VCC#T31

T32

VCC#T32

T35

VCC#T35

T36

VCC#T36

T37

VCC#T37

T38

VCC#T38

U29

VCC#U29

U30

VCC#U30

U31

VCC#U31

U32

VCC#U32

U33

VCC#U33

U34

VCC#U34

U35

VCC#U35

U36

VCC#U36

V13

VCC#V13

V14

VCC#V14

V31

VCC#V31

V32

VCC#V32

V33

VCC#V33

V34

VCC#V34

V35

VCC#V35

V36

VCC#V36

V37

VCC#V37

V38

VCC#V38

W13

VCC#W13

W14

VCC#W14

W29

VCC#W29

W30

VCC#W30

W31

VCC#W31

W32

VCC#W32

CPU_CFL-H_1440P

Need to check/modify

10 OF 13

VCC#W35

VCC#W36

VCC#W37

VCC#W38

VCC#Y29

VCC#Y30

VCC#Y31

VCC#Y32

VCC#Y33

VCC#Y34

VCC#Y35

VCC#Y36

+VCC_CORE +VCC_CORE

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

CFL 6/7 (POWER&GND )

CFL 6/7 (POWER&GND )

CFL 6/7 (POWER&GND )

ZGE

ZGE

ZGE

7 78Friday, May 03, 2019

7 78Friday, May 03, 2019

1

7 78Friday, May 03, 2019

1A

1A

1A

5

4

3

2

1

CFL-H Processor (GND)

U3F

A10

VSS_1

A12

VSS_2

A16

VSS_3

A18

VSS_4

A20

VSS_5

A22

VSS_6

A24

VSS_7

D D

C C

B B

A26

VSS_8

A28

VSS_9

A30

VSS_10

A6

VSS_11

A9

VSS_12

AA12

VSS_13

AA29

VSS_14

AA30

VSS_15

AB33

VSS_16

AB34

VSS_17

AB6

VSS_18

AC1

VSS_19

AC12

VSS_20

AC2

VSS_21

AC3

VSS_22

AC37

VSS_23

AC38

VSS_24

AC4

VSS_25

AC5

VSS_26

AC6

VSS_27

AD10

VSS_28

AD11

VSS_29

AD12

VSS_30

AD29

VSS_31

AD30

VSS_32

AD6

VSS_33

AD8

VSS_34

AD9

VSS_35

AE33

VSS_36

AE34

VSS_37

AE6

VSS_38

AF1

VSS_39

AF12

VSS_40

AF13

VSS_41

AF14

VSS_42

AF2

VSS_43

AF3

VSS_44

AF4

VSS_45

AG10

VSS_46

AG11

VSS_47

AG13

VSS_48

AG29

VSS_49

AG30

VSS_50

AG6

VSS_51

AG7

VSS_52

AG8

VSS_53

AH12

VSS_54

AH33

VSS_55

AH34

VSS_56

AH35

VSS_57

AH36

VSS_58

AH6

VSS_59

AJ1

VSS_60

AJ13

VSS_61

AJ2

VSS_62

AJ3

VSS_63

AJ37

VSS_64

AJ38

VSS_65

AJ4

VSS_66

AJ5

VSS_67

AJ6

VSS_68

W4

VSS_69

W5

VSS_70

Y10

VSS_71

Y11

VSS_72

Y13

VSS_73

Y14

VSS_74

Y37

VSS_75

Y38

VSS_76

Y7

VSS_77

Y8

VSS_78

Y9

VSS_79

AK29

VSS_80

AK30

VSS_81

CPU_CFL-H_1440P

6 OF 13

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

AK4

AL10

AL12

AL14

AL33

AL34

AL4

AL7

AL8

AL9

AM1

AM12

AM2

AM3

AM37

AM38

AM4

AM5

AN12

AN29

AN30

AN5

AN6

AP10

AP11

AP12

AP33

AP34

AP8

AP9

AR1

AR13

AR14

AR2

AR29

AR3

AR30

AR31

AR32

AR33

AR34

AR35

AR36

AR37

AR38

AR4

AR5

AT29

AT30

AT6

AU10

AU11

AU12

AU33

AU34

AU6

AU7

AU8

AU9

AV37

AV38

AW1

AW12

AW2

AW29

AW3

AW30

AW4

U6

V12

V29

V30

A14

AD7

V6

W1

W12

W2

W3

W33

W34

U3G

AW5

VSS_163

AY12

VSS_164

AY33

VSS_165

AY34

VSS_166

B9

VSS_167

BA10

VSS_168

BA11

VSS_169

BA12

VSS_170

BA37

VSS_171

BA38

VSS_172

BA6

VSS_173

BA7

VSS_174

BA8

VSS_175

BA9

VSS_176

BB1

VSS_177

BB12

VSS_178

BB2

VSS_179

BB29

VSS_180

BB3

VSS_181

BB30

VSS_182

BB4

VSS_183

BB5

VSS_184

BB6

VSS_185

BC12

VSS_186

BC13

VSS_187

BC14

VSS_188

BC33

VSS_189

BC34

VSS_190

BC6

VSS_191

BD10

VSS_192

BD11

VSS_193

BD12

VSS_194

BD37

VSS_195

BD6

VSS_196

BD7

VSS_197

BD8

VSS_198

BD9

VSS_199

BE1

VSS_200

BE2

VSS_201

BE29

VSS_202

BE3

VSS_203

BE30

VSS_204

BE4

VSS_205

BE5

VSS_206

BE6

VSS_207

BF12

VSS_208

BF33

VSS_209

BF34

VSS_210

BF6

VSS_211

BG12

VSS_212

BG13

VSS_213

BG14

VSS_214

BG37

VSS_215

BG38

VSS_216

BG6

VSS_217

BH1

VSS_218

BH10

VSS_219

BH11

VSS_220

BH12

VSS_221

BH14

VSS_222

BH2

VSS_223

BH3

VSS_224

BH4

VSS_225

BH5

VSS_226

BH6

VSS_227

BH7

VSS_228

BH8

VSS_229

BH9

VSS_230

T2

VSS_231

T3

VSS_232

T33

VSS_233

T34

VSS_234

T4

VSS_235

T5

VSS_236

T7

VSS_237

T8

VSS_238

T9

VSS_239

U37

VSS_240

U38

VSS_241

BJ12

VSS_242

BJ14

VSS_243

CPU_CFL-H_1440P

7 OF 13

VSS_244

VSS_245

VSS_246

VSS_247

VSS_248

VSS_249

VSS_250

VSS_251

VSS_252

VSS_253

VSS_254

VSS_255

VSS_256

VSS_257

VSS_258

VSS_259

VSS_260

VSS_261

VSS_262

VSS_263

VSS_264

VSS_265

VSS_266

VSS_267

VSS_268

VSS_269

VSS_270

VSS_271

VSS_272

VSS_273

VSS_274

VSS_275

VSS_276

VSS_277

VSS_278

VSS_279

VSS_280

VSS_281

VSS_282

VSS_283

VSS_284

VSS_285

VSS_286

VSS_287

VSS_288

VSS_289

VSS_290

VSS_291

VSS_292

VSS_293

VSS_294

VSS_295

VSS_296

VSS_297

VSS_298

VSS_299

VSS_300

VSS_301

VSS_302

VSS_303

VSS_304

VSS_305

VSS_306

VSS_307

VSS_308

VSS_309

VSS_310

VSS_311

VSS_312

VSS_313

VSS_314

VSS_315

VSS_316

VSS_317

VSS_318

VSS_319

VSS_320

VSS_321

VSS_322

VSS_323

VSS_324

BJ15

BJ18

BJ22

BJ25

BJ29

BJ30

BJ31

BJ32

BJ33

BJ34

BJ35

BJ36

BK13

BK14

BK15

BK18

BK22

BK25

BK29

BK6

BL13

BL14

BL18

BL19

BL20

BL21

BL22

BL29

BL33

BL35

BL38

BL6

BM11

BM12

BM13

BM14

BM18

BM2

BM21

BM22

BM23

BM24

BM25

BM26

BM27

BM28

BM29

BM3

BM33

BM35

BM38

BM5

BM6

BM7

BM8

BM9

BN12

BN14

BN18

BN19

BN2

BN20

BN21

BN24

BN29

BN30

BN31

BN34

P38

P6

R12

R29

AY14

BD38

R30

T1

T10

T11

T12

T13

T14

U3H

BN4

VSS_325

BN7

VSS_326

BP12

VSS_327

BP14

VSS_328

BP18

VSS_329

BP21

VSS_330

BP24

VSS_331

BP25

VSS_332

BP26

VSS_333

BP29

VSS_334

BP33

VSS_335

BP34

VSS_336

BP7

VSS_337

BR12

VSS_338

BR14

VSS_339

BR18

VSS_340

BR21

VSS_341

BR24

VSS_342

BR25

VSS_343

BR26

VSS_344

BR29

VSS_345

BR34

VSS_346

BR36

VSS_347

BR7

VSS_348

BT12

VSS_349

BT14

VSS_350

BT18

VSS_351

BT21

VSS_352

BT24

VSS_353

BT26

VSS_354

BT29

VSS_355

BT32

VSS_356

BT5

VSS_357

C11

VSS_358

C13

VSS_359

C15

VSS_360

C17

VSS_361

C19

VSS_362

C21

VSS_363

C23

VSS_364

C25

VSS_365

C27

VSS_366

C29

VSS_367

C31

VSS_368

C37

VSS_369

C5

VSS_370

C8

VSS_371

C9

VSS_372

D10

VSS_373

D12

VSS_374

D14

VSS_375

D16

VSS_376

D18

VSS_377

D20

VSS_378

D22

VSS_379

D24

VSS_380

D26

VSS_381

D28

VSS_382

D3

VSS_383

D30

VSS_384

D33

VSS_385

D6

VSS_386

D9

VSS_387

E34

VSS_388

E35

VSS_389

E38

VSS_390

E4

VSS_391

E9

VSS_392

N3

VSS_393

N33

VSS_394

N34

VSS_395

N4

VSS_396

N5

VSS_397

N6

VSS_398

N7

VSS_399

N8

VSS_400

N9

VSS_401

P12

VSS_402

P37

VSS_403

M14

VSS_404

M6

VSS_405

N1

VSS_406

F11

VSS_407

F13

VSS_408

CPU_CFL-H_1440P

8 OF 13

VSS_409

VSS_410

VSS_411

VSS_412

VSS_413

VSS_414

VSS_415

VSS_416

VSS_417

VSS_418

VSS_419

VSS_420

VSS_421

VSS_422

VSS_423

VSS_424

VSS_425

VSS_426

VSS_427

VSS_428

VSS_429

VSS_430

VSS_431

VSS_432

VSS_433

VSS_434

VSS_435

VSS_436

VSS_437

VSS_438

VSS_439

VSS_440

VSS_441

VSS_442

VSS_443

VSS_444

VSS_445

VSS_446

VSS_447

VSS_448

VSS_449

VSS_450

VSS_451

VSS_452

VSS_453

VSS_454

VSS_455

VSS_456

VSS_457

VSS_458

VSS_459

VSS_460

VSS_461

VSS_462

VSS_463

VSS_464

VSS_465

VSS_466

VSS_467

VSS_468

VSS_469

VSS_470

VSS_471

VSS_472

VSS_473

VSS_474

VSS_475

VSS_476

VSS_477

VSS_478

VSS_479

VSS_A3

VSS_A34

VSS_A4

VSS_B3

VSS_B37

VSS_BR38

VSS_BT3

VSS_BT35

VSS_BT36

VSS_BT4

VSS_C2

VSS_D38

F15

F17

F19

F2

F21

F23

F25

F27

F29

F3

F31

F36

F4

F5

F8

F9

G10

G12

G14

G16

G18

G20

G22

G23

G24

G26

G28

G4

G5

G6

G8

G9

H11

H12

H18

H22

H25

H32

H35

J10

J18

J22

J25

J32

J33

J36

J4

J7

K1

K10

K11

K2

K3

K38

K4

K5

K7

K8

K9

L29

L30

L33

L34

M12

M13

N10

N11

N12

N2

BT8

BR9

A3

A34

A4

B3

B37

BR38

BT3

BT35

BT36

BT4

C2

D38

Need to check

TPEV_PEG_VIEW_2[11]

PCH_2_CPU_TRIG[15]

R48

*Short_0402

CPU_2_PCH_TRIG[15]

R43

*Short_0402

stuff it for CRB 9/20

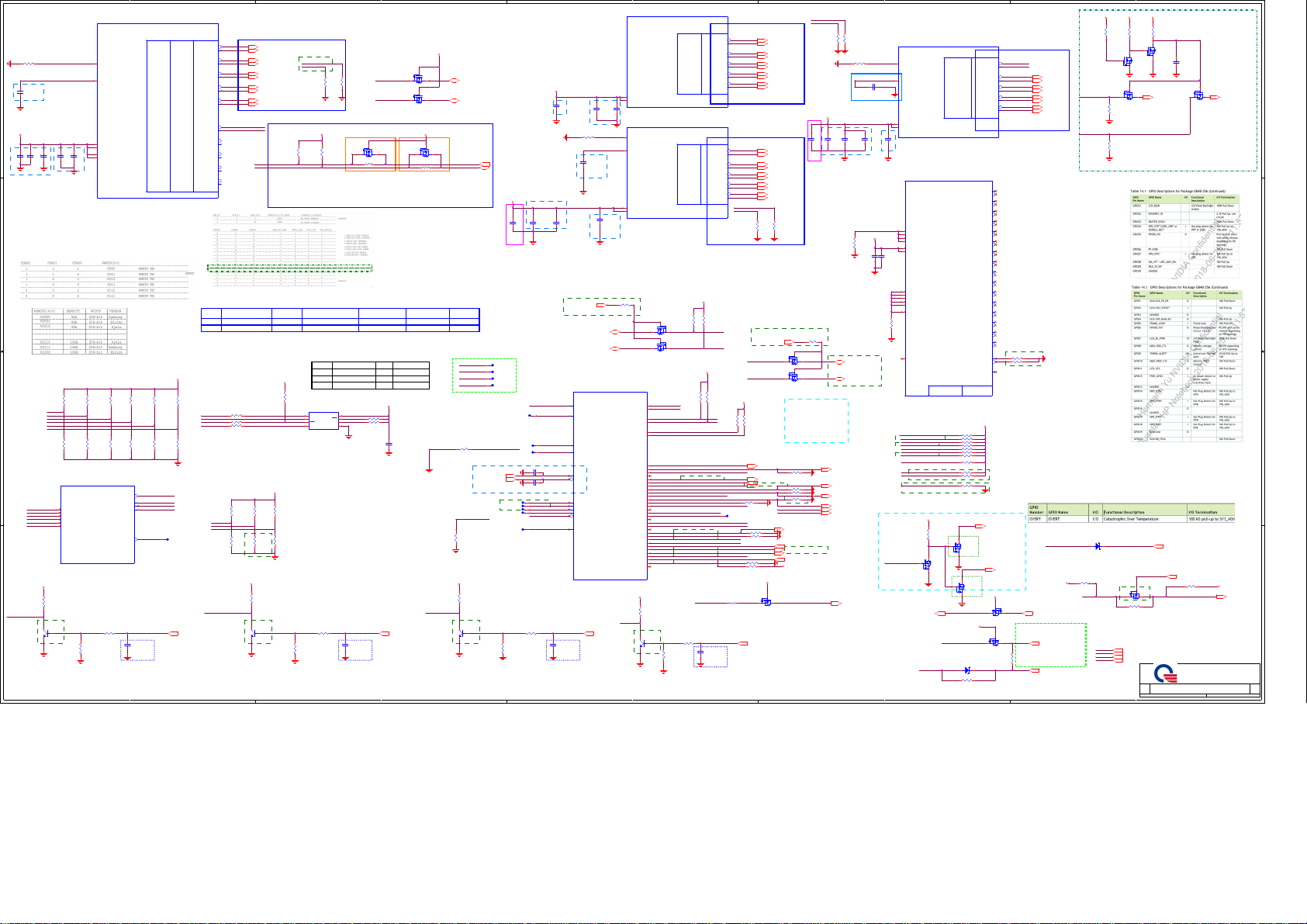

Configuration Signals:

CFG[0] Stall reset sequence after PCU PLL

lock until de-asserted

CFG[2] PCI Express Static Lane Reversal

eDP enable

CFG[4]

CFG[6:5]

PCI Express Bifurcation

CFL-H Processor (RESERVED, CFG)

U3M

E2

TPEV_PEG_VIEW_2

TP11

TP10

R63

*Short_0402

CPU_2_PCH_TRIG_R

The CFG signals have a default value of '1' if not terminated on the board.

Note that some of the Intel reference designs board might connect CFG[0] to

HOOK[2]. This route is not needed on a OxM board.

x1 = Normal operation

x0 = Lane numbers reversed

x1 = Disabled

x0 = Enabled

x00 = 1 x8 & 2 x4 PCI Express

x01 = reserved

x10 = 2 x8 PCI Express

RSVD_TP5

E3

IST_TRIG

E1

RSVD_TP4

D1

RSVD_TP3

BR1

RSVD_TP1

BT2

RSVD_TP2

BN35

RSVD15

J24

RSVD28

H24

RSVD27

BN33

RSVD14

BL34

RSVD13

N29

RSVD30

R14

RSVD31

AE29

RSVD#AE29

AA14

RSVD1

AP29

RSVD5

AP14

RSVD4

A36

VSS_A36

A37

VSS_A37

H23

PROC_TRIGIN

J23

PROC_TRIGOUT

F30

RSVD24

E30

RSVD23

B30

RSVD7

C30

RSVD21

G3

RSVD26

J3

RSVD29

BR35

RSVD19

BR31

RSVD18

BH30

RSVD9

CPU_CFL-H_1440P

13 OF 13

RSVD11

RSVD10

RSVD12

RSVD3

RSVD25

RSVD22

RSVD20

RSVD17

RSVD16

RSVD8

RSVD6

BK28

BJ28

BL31

AJ8

G13

C38

C1

BR2

BP1

B38

B2

x11 = 1 x16 PCI Express

PEG defer training

CFG[7]

A A

x1 = PEG train follow RESETB de-asseted

x0 = PEG wait for BIOS fro training

08

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

CFL 7/7 (GND)

CFL 7/7 (GND)

CFL 7/7 (GND)

ZGE

ZGE

ZGE

1A

1A

8 78Friday, May 03, 2019

8 78Friday, May 03, 2019

1

8 78Friday, May 03, 2019

1A

5

4

3

2

1

U14B

DMI_TXN0[3]

DMI_TXP0[3]

DMI_RXN0[3]

DMI_RXP0[3]

DMI_TXN1[3]

DMI_TXP1[3]

DMI_RXN1[3]

DMI_RXP1[3]

DMI_TXN2[3]

DMI_TXP2[3]

DMI_RXN2[3]

DMI_RXP2[3]

D D

C C

USB3.0 (DB/IO-1)

USB3.0 (DB/IO-2)

B B

USB3.0 (IO-3/Charger)

USB3.0 (NV Type-C)

DMI_TXN3[3]

DMI_TXP3[3]

DMI_RXN3[3]

DMI_RXP3[3]

USB30_TX1-[60]

USB30_TX1+[60]

USB30_RX1-[60]

USB30_RX1+[60]

USB30_TX2-[60]

USB30_TX2+[60]

USB30_RX2-[60]

USB30_RX2+[60]

USB30_TX3+[46]

USB30_TX3-[46]

USB30_RX3+[46]

USB30_RX3-[46]

USB30_TX4+[44]

USB30_TX4-[44]

USB30_RX4+[44]

USB30_RX4-[44]

K34

DMI0_RXN

J35

DMI0_RXP

C33

DMI0_TXN

B33

DMI0_TXP

G33

DMI1_RXN

F34

DMI1_RXP

C32

DMI1_TXN

B32

DMI1_TXP

K32

DMI2_RXN

J32

DMI2_RXP

C31

DMI2_TXN

B31

DMI2_TXP

G30

DMI3_RXN

F30

DMI3_RXP

C29

DMI3_TXN

B29

DMI3_TXP

A25

DMI7_TXP

B25

DMI7_TXN

P24

DMI7_RXP

R24

DMI7_RXN

C26

DMI6_TXP

B26

DMI6_TXN

F26

DMI6_RXP

G26

DMI6_RXN

B27

DMI5_TXP

C27

DMI5_TXN

L26

DMI5_RXP

M26

DMI5_RXN

D29

DMI4_TXP

E28

DMI4_TXN

K29

DMI4_RXP

M29

DMI4_RXN

G17

PCIE1_RXN/USB31_7_RXN

F16

PCIE1_RXP/USB31_7_RXP

A17

PCIE1_TXN/USB31_7_TXN

B17

PCIE1_TXP/USB31_7_TXP

R21

PCIE2_RXN/USB31_8_RXN

P21

PCIE2_RXP/USB31_8_RXP

B18

PCIE2_TXN/USB31_8_TXN

C18

PCIE2_TXP/USB31_8_TXP

K18

PCIE3_RXN/USB31_9_RXN

J18

PCIE3_RXP/USB31_9_RXP

B19

PCIE3_TXN/USB31_9_TXN

C19

PCIE3_TXP/USB31_9_TXP

N18

PCIE4_RXN/USB31_10_RXN

R18

PCIE4_RXP/USB31_10_RXP

D20

PCIE4_TXN/USB31_10_TXN

C20

PCIE4_TXP/USB31_10_TXP

F20

PCIE5_RXN

G20

PCIE5_RXP

B21

PCIE5_TXN

A22

PCIE5_TXP

K21

PCIE6_RXN

J21

PCIE6_RXP

D21

PCIE6_TXN

C21

PCIE6_TXP

B23

PCIE7_TXP

C23

PCIE7_TXN

J24

PCIE7_RXP

L24

PCIE7_RXN

F24

PCIE8_RXN

G24

PCIE8_RXP

B24

PCIE8_TXN

C24

PCIE8_TXP

PCH_CFL-H_874P

U14F

F9

USB31_1_TXN

F7

USB31_1_TXP

D11

USB31_1_RXN

C11

USB31_1_RXP

C3

USB31_2_TXN

D4

USB31_2_TXP

B9

USB31_2_RXN

C9

USB31_2_RXP

C17

USB31_6_TXN

C16

USB31_6_TXP

G14

USB31_6_RXN

F14

USB31_6_RXP

C15

USB31_5_TXN

B15

USB31_5_TXP

J13

USB31_5_RXN

K13

USB31_5_RXP

G12

USB31_3_TXP

F11

USB31_3_TXN

C10

USB31_3_RXP

B10

USB31_3_RXN

C14

USB31_4_TXP

B14

USB31_4_TXN

J15

USB31_4_RXP

K16

USB31_4_RXN

PCH_CFL-H_874P

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_F15/USB2_OC4#

GPP_F16/USB2_OC5#

GPP_F17/USB2_OC6#

GPP_F18/USB2_OC7#

USB2_VBUSSENSE

2 OF 13

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS0#

GPP_A6/SERIRQ/ESPI_CS1#

GPP_A7/PIRQA#/ESPI_ALERT0#

GPP_A0/RCIN#/ESPI_ALERT1#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

GPP_K19/SMI#

GPP_K18/NMI#

GPP_E6/SATA_DEVSLP2

GPP_E5/SATA_DEVSLP1

GPP_E4/SATA_DEVSLP0

GPP_F9/SATA_DEVSLP7

GPP_F8/SATA_DEVSLP6

GPP_F7/SATA_DEVSLP5

GPP_F6/SATA_DEVSLP4

GPP_F5/SATA_DEVSLP3

6 OF 13

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2N_11

USB2P_11

USB2N_12

USB2P_12

USB2N_13

USB2P_13

USB2N_14

USB2P_14

USB2_COMP

RSVD1

USB2_ID

GPD7

PCIE24_TXP

PCIE24_TXN

PCIE24_RXP

PCIE24_RXN

PCIE23_TXP

PCIE23_TXN

PCIE23_RXP

PCIE23_RXN

PCIE22_TXP

PCIE22_TXN

PCIE22_RXP

PCIE22_RXN

PCIE21_TXP

PCIE21_TXN

PCIE21_RXP

PCIE21_RXN

J3

J2

N13

N15

K4

K3

M10

L9

M1

L2

K7

K6

L4

L3

G4

G5

M6

N8

H3

H2

R10

P9

G1

G2

N3

change to BT to Port14 for CNVi 9/20

N2

E5

F6

USB_OC0#

AH36

USB_OC1#

AL40

USB_OC2#

AJ44

USB_OC3#

AL41

USB_OC4#

AV47

USB_OC5#

AR35

USB_OC6#

AR37

USB_OC7#

AV43

USB2_COMP

F4

F3

U13

G3

PCH_GPD7

BE41

G45

G46

Y41

Y40

G48

G49

W44

W43

H48

H47

U41

U40