Page 1

5

4

3

2

1

AMD Geode™ LX EPIC RDK Reference

D D

NOTES:

1) UNLESS OTHERWISE SPECIFIED RESISTORS HAVE 5% TOLERANCE.

2) UNLESS OTHERWISE SPECIFIED CAPACITORS HAVE 20% TOLERANCE.

C C

B B

IMPORTANT NOTICE:

1. THIS DOCUMENT MAY NOT REFLECT THE MOST RECENT CHANGES IN BOARD DEVELOPMENT

AND DEBUG. ANY DEVELOPER INTENDING TO USE THIS SCHEMATIC AS A REFERNCE SHOULD

CONTACT THEIR LOCAL FIELD APPLICATIONS ENGINEER, REGIONAL SALES OFFICE , O R

PROGRAM MANAGER FOR SCHEMATIC UPDATES, DESIGN RECOM MENDA TION S AND PCB L AYOU T

GUIDELINES. AMD ALSO RECOMMENDS A DESIGN REVIEW OF BOTH THE SCHEMATIC DIAGRAM

AND PCB LAYOUT BEFORE CONSIDERING PRODUC TIO N.

2. AMD RESERVES THE RIGHT TO CHANGE DESIGNS OR SPECIFICATIONS WITHOU T NO TICE .

CUSTOMERS ARE ADVISED TO OBTAIN THE LATEST VERSIONS OF PRODUCT SPECIFICATIONS,

WHICH SHOULD BE CONSIDERED IN EVALUATING A PRODUCT'S APPROPRIATENESS FOR A

PARTICULAR USE.

3. AMD MAKES NO WARRANTIES, EXPRESSED OR IMPLIED, FOR MERCHANTABILITY OR FITNESS

FOR A PARTICULAR APPLICATION. IN NO EVENT SHALL AMD BE LIABLE FOR ANY INDIRECT,

SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES AS A RESULT OF THE PE RFOR MAN CE,

A A

OR FAILURE TO PEFORM, OF ANY AMD PRODUCT OR DOCUMENTATION.

© 2007 ADVANCED MICRO DEVICES, INC. ALL RIGHTS RESERVED. AMD, THE AMD ARROW LOGO,

AMD GEODE, AND COMBINATIONS THEREOF ARE TRADEMARKS OF ADVANCED MICRO DEVICES,

INC. OTHER NAMES USED IN THIS PUBLICATION ARE FOR IDENTIFICATION PURPOSES ONLY

AND MAY BE TRADEMARKS OF THEIR RESPECTIVE COMPANIES.

5

4

Schematic

Page Index

------- ------------------------

1

2

3

4

5

6

7

8

9

10

11

12

13

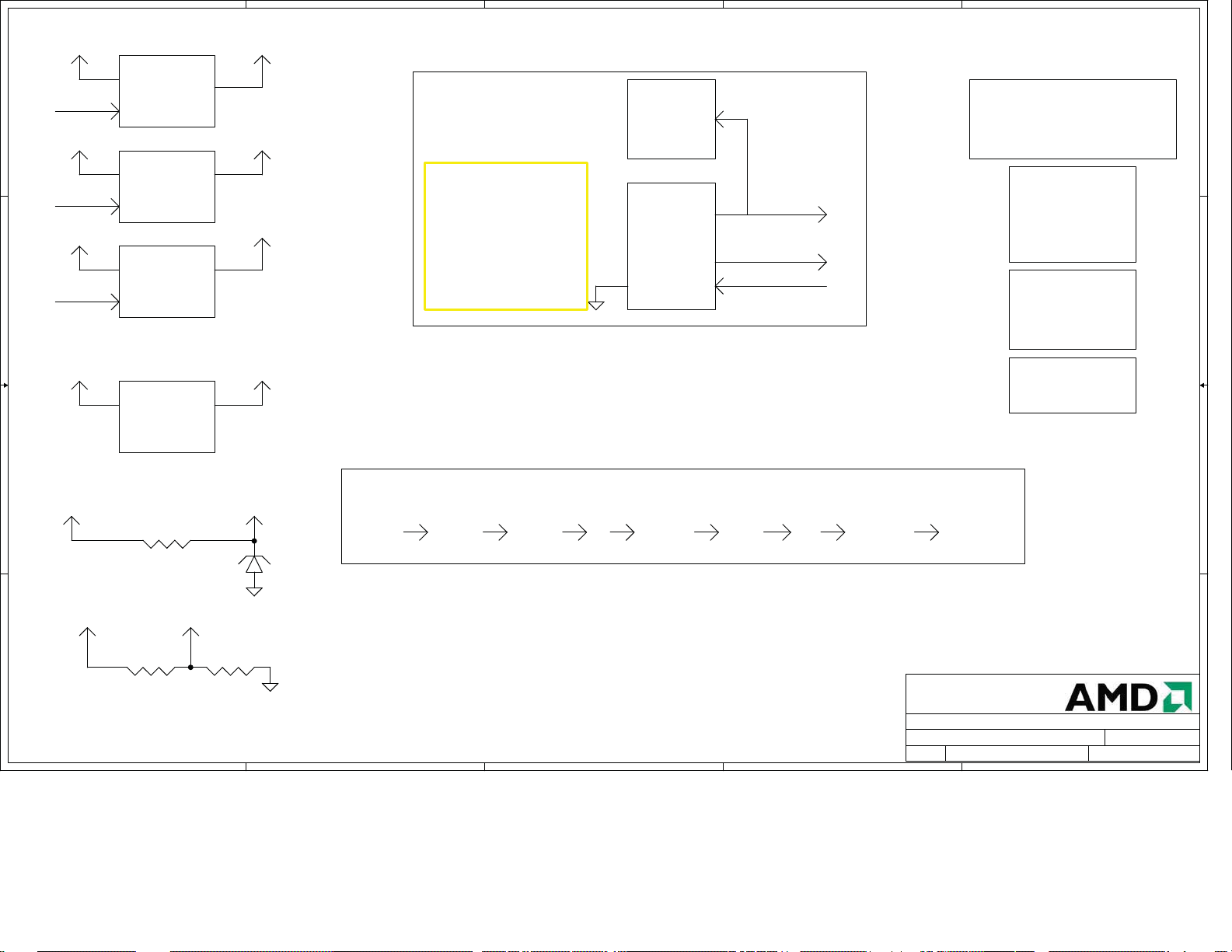

IMPORTANT NOTES ABOUT

THIS SCHEMATIC

DESIGN NOTE: Example

text for the design note to

show the note inside the

colored box.

DESIGN NOTE: Example

text for the design note to

show the note inside the

colored box.

DESIGN NOTE: Example

text for the design note to

show the note inside the

colored box.

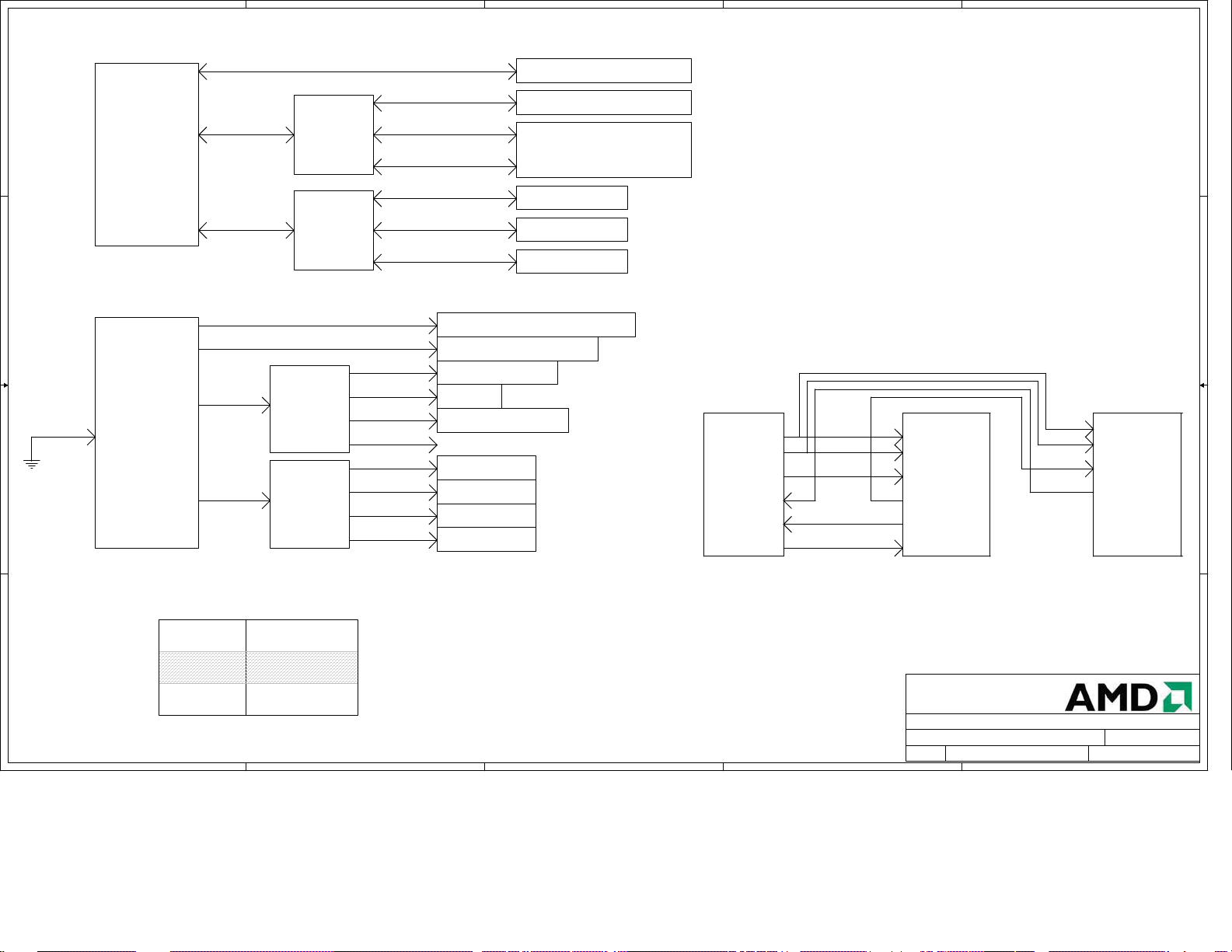

COVER PAGE

REVISION HISTORY

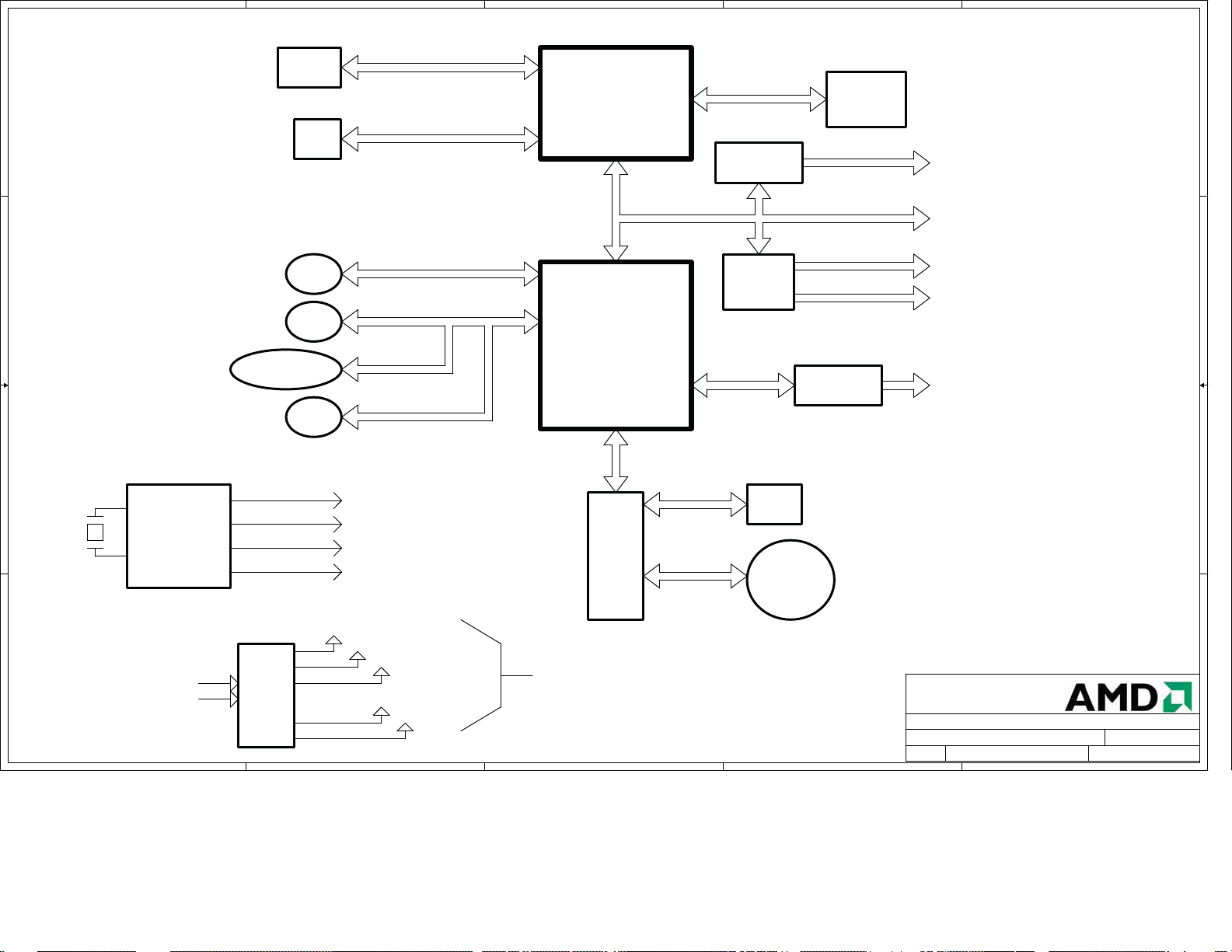

BLOCK DIAGRAM

POWER ON & RESET SEQUENCE

PCI & JTAG BLOCK DIAGRAM

LX PROCESSOR DDR MEMORY

DDR SODIMM CONNECTOR

LX PROCESSOR VGA

LX PROCESSOR PCI / SYSTEM

LX PROCESSOR POWER

CS5536 PCI / SYSTEM / PM / FWH

CS5536 IDE / USB / AC97 / LPC

CS5536 POWER & CLOCK GENERATOR

3

1) DESIGN NOTES in

grey are information

notes.

2) DESIGN NOTES in

yellow are notes of

caution.

3) DESIGN NOTES in

red are critical, and

must be understood and

followed.

Page Index

------- ------------------------

14

15

16

17

18

19

20

21

22

23

24

25

26 TFT & LVDS CONNECTORS

VGA CONNECTOR

ETHERNET - 10 / 100 MICREL KSZ8842

AUDIO CODEC REALTEK ALC655

SUPER IO ITE IT8712F & SPI BOOT FLASH

ETHERNET CONN / USB CONN & PWR / uDOC

MINI PCI

PCI TO ISA BRIDGE ITE IT8888G

IDE CONNECTOR

UART & FLOPPY CONNECTORS

PARALLEL PORT, KEYBOARD, & MOUSE

PC104 CONNECTORS

POWER SUPPLIES

*AMD CONFIDENTIAL*

Advanced Micro Devices

1351 South Sunset St.

Longmont CO 80501

Title

AMD GEODE™ LX EPIC RDK Reference Sc hematic

Document Number Rev

Size

2

B

40744 D

Date: Sheet

Wednesday, April 11, 2007

126

1

of

Page 2

5

D D

4

3

2

1

REVISION HISTORY:

REV DATE NOTES

------- ------------------ ---------------------------------------------------------------------------------------

A Initial Release

07-09-2006

12-04-2006

C 01-19-2007

D Page 13 - Added design note regarding USB VCORE supply.

04-10-2007

C C

*

Page 8 - Changed LX symbol - DRG B 6 p i n f r om Y32 to AH8B

*

Page 10 - Connected C102-C108 to Ground

*

Page 13 - Connected C133-C137 and C149-C152 to Ground

*

*

B B

A A

5

4

3

2

*AMD CONFIDENTIAL*

Advanced Micro Devices

1351 South Sunset St.

Longmont CO 80501

Title

AMD GEODE™ LX EPIC RDK Reference Schematic

Document Number Rev

Size

B

40744 D

Date: Sheet

Wednesday, April 11, 2007

1

226

of

Page 3

5

4

3

2

1

MONITOR

D D

LVDS

HD/CD

C C

X2

HOST

X1

PRIMARY IDE ATA-100

CRT

TFT

USB2.0

AMD Geode™

LX Processor

PCI BUS (33MHz)

AMD Geode™

CS5536

MEMORY BUS

PCI TO ISA

BRIDGE

10 / 100

ETHERNET

2 PORT

SODIMM200

DDR

FULL ISA

Companion

uDOC FLASH

STORAGE

CLIENT

X1

B B

14.318 MHz

Crystal

Clock

Synthesizer

(MK1491-09F)

PCI(33 MHz)

66 MHz

48 MHz

REFCLK

Device

SIO

SPI

AC97

AUDIO CODEC

5.1 SUPPORT

BIOS

FLASH

LEGACY

PARALLEL

SERIAL

KB/MS

VCORE(1.25V)

VMEM (2.6V)

A A

VCC5

VCC5SB

5

DC/DC

VCC3 (3.3V)

VCORESB (1.225V)

VCC3SB (3.3V)

4

BASEBOARD ONLY

3

2

*AMD CONFIDENTIAL*

Advanced Micro Devices

1351 South Sunset St.

Longmont CO 80501

Title

AMD GEODE™ LX EPIC RDK Reference Sc hematic

Document Number Rev

Size

B

40744 D

Date: Sheet

Wednesday, April 11, 2007

1

326

of

Page 4

5

4

3

2

1

5VSB

VMEM @ 2A Max

DC/DC

AOZ1012

D D

WORKING

EN

AMD

Geode™ LX

5V

DC/DC

AOZ1012

WORK AUX

5V

EN

DC/DC

AOZ1012

C C

WORK AUX

5VSB

EN

VCC3 @ 2A Max

VCORE @ 2A Max

VCC3SB

DESIGN NOTE: This design uses

LVD to generate system reset.

Since LVD only monitors Vcore ,

the designer must guarantee that

Vio and other required voltages

are valid at or before Vcore. If this

cannot be guaranteed, then

RESET_WORK# must be used to

hold system in reset until Vio and

Vcore and any other requir ed

voltages are valid.

Processor

AMD

Geode™

CS5536

LVD_EN#

PCIRST#

WORKING

PWRBTN#

LINEAR

LM317

B B

VCC3SB

470

VCORESB

LM4041

5VSB

1.225VSB

Power On and Reset Sequence - Cold start

3.3VSB

PWRBTN# WORKING

5V

VCC3

VCORE

VMEM

LVD

SYS_RST#

SYSTEM POWER

VCC=+5.0V

VCC3=+3.30V - BASEBOARD

VCC3_EXT=+3.30V - PC104 SLOTS

AMD Geode™ LX

Processor

VCORE=+1.25V

VCCMEM=+2.60V

MVREF=+1.3V

VIO=+3.30V

AMD Geode™

CS5536

VCORE=+1.25V

VCORESB=+1.225V

VIO=+3.30V

MEMORY

VMEM=+2.60V

MVREF=+1.3V

PCIRST#

VCCMEM MVREF

A A

10K

5

10K

4

3

2

*AMD CONFIDENTIAL*

Advanced Micro Devices

1351 South Sunset St.

Longmont CO 80501

Title

AMD GEODE™ LX EPIC RDK Reference Schematic

Document Number Rev

Size

B

40744 D

Date: Sheet

Wednesday, April 11, 2007

1

426

of

Page 5

5

4

3

2

1

PCI MASTER SETTING

REQ2#/GNT#2

D D

AMD

REQ1#/GNT#1

Expander

Geode™ LX

REQ_EXT0#/GNT_EXT0#

REQ_EXT1#/GNT_EXT1#

REQ_EXT2#/GNT_EXT2#

Processor

PC_REQ0#/PC_GNT0#

REQ0#/GNT#0

Expander

PC_REQ1#/PC_GNT1#

PC_REQ2#/PC_GNT2#

AMD Geode™ CS5536

PCI to ISA Bridge

Mini PCI

Ethernet Controller

PC104 Slot 3

PC104 Slot 0

PC104 Slot 1

PC104 Slot 2

Jumpers to select

2 of the 3 devices

C C

B B

PCI CLOCK SETTING

CLOCK

GENERATOR

SEL66_33#

MK1491-09

CLK_EXT

PC_CLK

CLK_CPU

CLK_IOC

Expander

Expander

CLK_EXT0

CLK_EXT1

CLK_EXT2

CLK_EXT3

PC_CLK0

PC_CLK1

PC_CLK2

PC_CLK3

AMD Geode™ LX Processor

AMD Geode™ CS5536

PCI to ISA Bridge

Mini PCI

Ethernet Controller

Not Used

PC104 Slot 0

PC104 Slot 1

PC104 Slot 2

PC104 Slot 3

JTAG DAISY CHAIN MODE WITH AMD GEODE™

CS5536 COMPANION DEVICE

TCK

TMS

TDI

TDO

TDEBUG_OUT

TDEBUG_IN

FS2 HEADER

TCK

TMS

TDI

TDO

TDEBUG_OUT

TDEBUG_IN

AMD GEODE™ LX PROCESSOR

TCK

TMS

TDI

TDO

TDEBUG_OUT

TDEBUG_IN

AMD GEODE™ CS5536

FunctionSEL66_33#

A A

1

PCI 66 MHz

PCI 33 MHz0

5

4

3

2

*AMD CONFIDENTIAL*

Advanced Micro Devices

1351 South Sunset St.

Longmont CO 80501

Title

AMD GEODE™ LX EPIC RDK Reference Sc hematic

Document Number Rev

Size

B

40744 D

Date: Sheet

Wednesday, April 11, 2007

1

526

of

Page 6

5

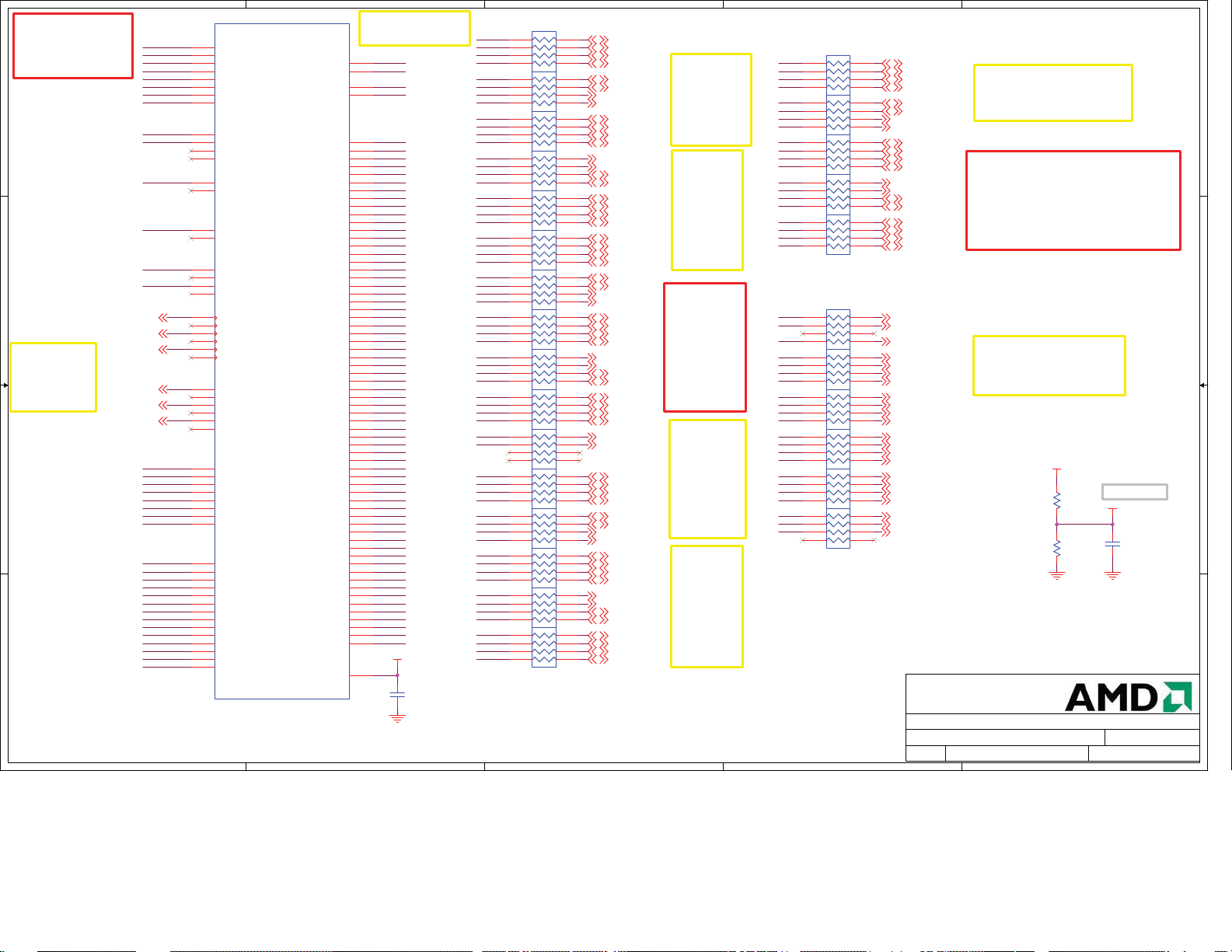

DESIGN NOTE: See LX

layout guidelines for

latest recommendations

on memory routing.

D D

C C

DESIGN NOTE:

Use SDCLK

pairs that are

most convient

for clean routing.

B B

A A

SDCLK0#7

SDCLK2#7

SDCLK4#7

QM0

MD

M1

MDQM1

MDQM2

MDQM3

MDQM4

MDQM5

MDQM6

MDQM7

MCS0#

MCS1#

MCKE0

MWE#

MCAS#

MRAS#

SDCLK07

SDCLK27

SDCLK47

MDQS0

MDQS1

MDQS2

MDQS3

MDQS4

MDQS5

MDQS6

MDQS7

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

DQM0

G2

DQM1

A6 D26

DQM2 BA0

A19

DQM4

C24

DQM5

H29

DQM6

N30

DQM7

B28

CS0#

F28

CS1#

F29

CS2#

D30

CS3#

E4

CKE0

F4

CKE1

C27

WE0#

A28

WE1#

E28

CAS0#

E29

CAS1#

C26

RAS0#

D27

RAS1#

M4

SDCLK0P

J4

SDCLK1P

M28

SDCLK2P

J28

SDCLK3P

D23

SDCLK4P

D20

SDCLK5P

L4

SDCLK0N

H4

SDCLK1N

L28

SDCLK2N

H28

SDCLK3N

D24

SDCLK4N

D21

SDCLK5N

M2

DQS0

H3

DQS1

C6

DQS2

A10

DQS3

C19

DQS4

B23

DQS5

J29

DQS6

N31

DQS7

C16

MA0

C17

MA1

C15

MA2

C13

MA3

D13

MA4

D11

MA5

D12

MA6

D8

MA7

D9

MA8

D6

MA9

D19

MA10

D5

MA11

C5

MA12

F30

MA13

U1A

AMD GEODE™

LX PROCESSOR

5

BA1DQM3

TLA0

TLA1

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

MVREF

4

DESIGN NOTE: BA0,BA1

must be trace length

matched to within 50 mils.

MBA0

MBA1

C20B10

TLA0

B15

TLA1

B13

MD0

P2

MD1

N2

MD2

M3

MD3

K2

MD4

P3

MD5

N1

MD6

L3

MD7

K1

MD8

J2

MD9

J1

MD10

F3

MD11

E3

MD12

J3

MD13

G1

MD14

F2

MD15

F1

MD16

D2

MD17

B4

MD18

B6

MD19

C8

MD20

D1

MD21

A4

MD22

A7

MD23

B7

MD24

B9

MD25

C10

MD26

A12

MD27

B12

MD28

A9

MD29

C9

MD30

C11

MD31

A13

MD32

A15

MD33

B17

MD34

B19

MD35

B22

MD36

B16

MD37

A17

MD38

B20

MD39

A20

MD40

A22

MD41

A23

MD42

A25

MD43

A26

MD44

C22

MD45

C23

MD46

B25

MD47

B26

MD48

D31

MD49

F31

MD50

K30

MD51

K31

MD52

G30

MD53

G31

MD54

J31

MD55

J30

MD56

M31

MD57

M30

MD58

R30

MD59

R31

MD60

L29

MD61

M29

MD62

P30

MD63

R29

MVREF

P1

1

C2

100nF

DGND

4

RN1

33

RN2

33

RN3

33

RN4

33

RN5

33

RN6

33

RN7

33

RN8

33

RN9

33

RN10

33

RN11

33

RN12

33

RN13

33

RN15

33

RN17

33

RN19

33

MD5

MD1

MD4

MD0

MD6

MD2

MDQM0

MDQS0

MD12

MD8

MD7

MD3

MDQM1

MDQS1

MD13

MD9

MD15

MD11

MD14

MD10

MD21

MD17

MD20

MD16

MD22

MD18

MDQM2

MDQS2

MD28

MD24

MD23

MD19

MDQM3

MDQS3

MD29

MD25

MD31

MD27

MD30

MD26

TLA0

TLA1

MD37

MD33

MD36

MD32

MD38

MD34

MDQM4

MDQS4

MD44

MD40

MD39

MD35

MDQM5

MDQS5

MD45

MD41

MD47

MD43

MD46

MD42

3

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

RMD5 7

RMD1 7

RMD4 7

RMD0 7

RMD6 7

RMD2 7

RMDQM0 7

RMDQS0 7

RMD12 7

RMD8 7

RMD7 7

RMD3 7

RMDQM1 7

RMDQS1 7

RMD13 7

RMD9 7

RMD15 7

RMD11 7

RMD14 7

RMD10 7

RMD21 7

RMD17 7

RMD20 7

RMD16 7

RMD22 7

RMD18 7

RMDQM2 7

RMDQS2 7

RMD28 7

RMD24 7

RMD23 7

RMD19 7

RMDQM3 7

RMDQS3 7

RMD29 7

RMD25 7

RMD31 7

RMD27 7

RMD30 7

RMD26 7

RTLA0 7

RTLA1 7

RMD37 7

RMD33 7

RMD36 7

RMD32 7

RMD38 7

RMD34 7

RMDQM4 7

RMDQS4 7

RMD44 7

RMD40 7

RMD39 7

RMD35 7

RMDQM5 7

RMDQS5 7

RMD45 7

RMD41 7

RMD47 7

RMD43 7

RMD46 7

RMD42 7

3

DESIGN NOTE:

Swap series

resistors on the

DQS lines in

order minimize

the number of

vias.

DESIGN

NOTE: Swap

series

resistors on

the address

lines in order

minimize the

number of

vias.

DESIGN NOTE:

Do not swap

series resistors

on the DQS,

DQM or Data

lines with the

Address or

control lines.

DESIGN

NOTE: Swap

series

resistors on

the data lines

in order

minimize the

number of

vias.

DESIGN

NOTE: Place

data bus

series

resistors as

close to the

memory

devices as

possible.

RN21

33

RN23

33

RN24

33

RN26

33

RN27

33

RN14

22

RN16

22

RN18

22

RN20

22

RN22

22

RN25

22

MD53

MD49

MD52

MD48

MD54

MD50

MDQM6

MDQS6

MD60

MD56

MD55

MD51

MDQM7

MDQS7

MD61

MD57

MD63

MD59

MD62

MD58

MA11

MA12

MCKE0

MA6

MA7

MA8

MA9

MA2

MA3

MA4

MA5

MBA1

MA10

MA0

MA1

MCAS#

MWE#

MRAS#

MB

A0

MCS1#

MCS0#

MA13

2

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

1

8

2

7

3

6

45

RMD53 7

RMD49 7

RMD52 7

RMD48 7

RMD54 7

RMD50 7

RMDQM6 7

RMDQS6 7

RMD60 7

RMD56 7

RMD55 7

RMD51 7

RMDQM7 7

RMDQS7 7

RMD61 7

RMD57 7

RMD63 7

RMD59 7

RMD62 7

RMD58 7

RMA11 7

RMA12 7

RMCKE0 7

RMA6 7

RMA7 7

RMA8 7

RMA9 7

RMA2 7

RMA3 7

RMA4 7

RMA5 7

RMBA1 7

RMA10 7

RMA0 7

RMA1 7

RMCAS# 7

RMWE# 7

RMRAS# 7

RMBA0 7

RMCS1# 7

RMCS0# 7

RMA13 7

DESIGN NOTE: Place DQS and

DQM series resistors as close

to the SODIMM connector as

possible.

DESIGN NOTE: This schematic shows a

non-parallel terminated DDR solution.

There may be restrictions as to the total

number of DRAMS and the number of

banks supported on the SODIMM. See LX

layout guidelines for current restrictions.

DESIGN NOTE: Place address

and control series resistors as

close to the processor as

possible.

1

VCCMEM

1

R1

10K

1

R2

10K

DGND DGND

Vout = 1.30

MVREF

1

C1

100nF

*AMD CONFIDENTIAL*

Advanced Micro Devices

1351 South Sunset St.

Longmont CO 80501

Title

AMD GEODE™ LX EPIC RDK Reference Schematic

Document Number Rev

Size

2

B

40744 D

Date: Sheet

Wednesday, April 11, 2007

1

626

of

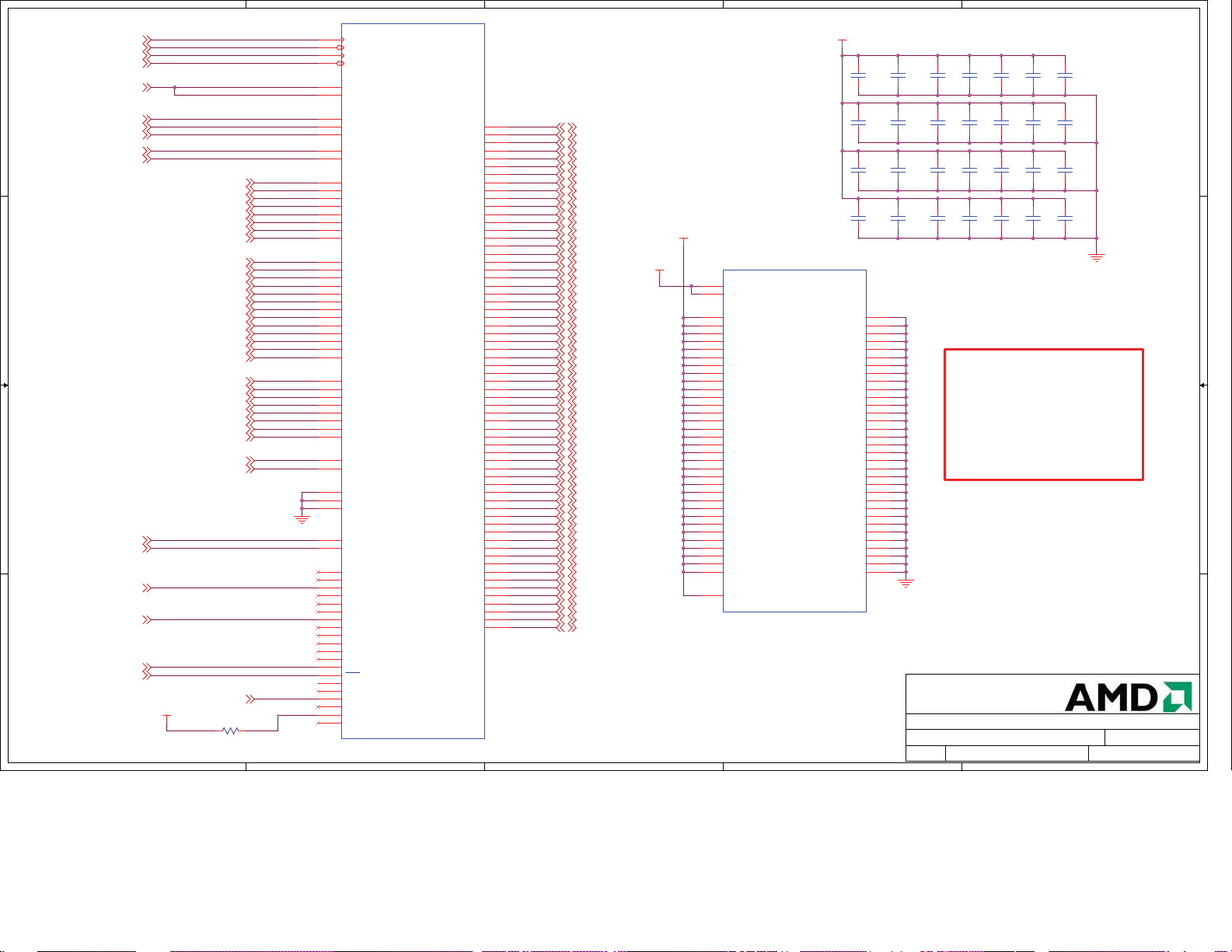

Page 7

5

SDCLK06

SDCLK0#6

SDCLK26

SDCLK2#6

RMCKE06

D D

C C

B B

A A

RMRAS#6

RMCAS#6

RMWE#6

RMCS0#6

RMCS1#6

RMDQS06

RMDQS16

RMDQS26

RMDQS36

RMDQS46

RMDQS56

RMDQS66

RMDQS76

RMA06

RMA16

RMA26

RMA36

RMA46

RMA56

RMA66

RMA76

RMA86

RMA96

RMA106

RMA116

RMA126

RMDQM06

RMDQM16

RMDQM26

RMDQM36

RMDQM46

RMDQM56

RMDQM66

RMDQM76

RMBA06

RMBA16

SMB_SDA12

SMB_SCL12

RTLA16

RTLA06

SDCLK46

SDCLK4#6

VCCMEM

5

RMA136

1

R3 10K

DGND

4

J1A

35

CK0

37

CK0#

160

CK1

158

CK1#

96

CKE0

95

CKE1

118

RAS#

120

CAS#

119

WE#

121

S0#

122

S1#

11

DQS0

25

DQS1

47

DQS2

61

DQS3

133

DQS4

147

DQS5

169

DQS6

183

DQS7

112

A0

111

A1

110

A2

109

A3

108

A4

107

A5

106

A6

105

A7

102

A8

101

A9

115

A10/AP

100

A11

99

A12

12

DM0

26

DM1

48

DM2

62

DM3

134

DM4

148

DM5

170

DM6

184

DM7

117

BA0

116

BA1

194

SA0

196

SA1

198

SA2

193

SDA

195

SDL

85

RFU

86

RFU/RESET

71

CB0

72

CB4

73

CB1

74

CB5

77

DQS8

78

DM8

79

CB2

80

CB6

83

CB3

84

CB7

89

CK2

91

CK2

97

RFU

98

RFU

123

RFU/A13

124

RFU

199

VddID

200

RFU

SODIMM

DDR-SODIMM-200P-RVS

4

DQ00

DQ01

DQ02

DQ03

DQ04

DQ05

DQ06

DQ07

DQ08

DQ09

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

3

5

7

13

17

6

8

14

18

19

23

29

31

20

24

30

32

41

43

49

53

42

44

50

54

55

59

65

67

56

60

66

68

127

129

135

139

128

130

136

140

141

145

151

153

142

146

152

154

163

165

171

175

164

166

172

176

177

181

187

189

178

182

188

190

RMD0 6

RMD1 6

RMD2 6

RMD3 6

RMD4 6

RMD5 6

RMD6 6

RMD7 6

RMD8 6

RMD9 6

RMD10 6

RMD11 6

RMD12 6

RMD13 6

RMD14 6

RMD15 6

RMD16 6

RMD17 6

RMD18 6

RMD19 6

RMD20 6

RMD21 6

RMD22 6

RMD23 6

RMD24 6

RMD25 6

RMD26 6

RMD27 6

RMD28 6

RMD29 6

RMD30 6

RMD31 6

RMD32 6

RMD33 6

RMD34 6

RMD35 6

RMD36 6

RMD37 6

RMD38 6

RMD39 6

RMD40 6

RMD41 6

RMD42 6

RMD43 6

RMD44 6

RMD45 6

RMD46 6

RMD47 6

RMD48 6

RMD49 6

RMD50 6

RMD51 6

RMD52 6

RMD53 6

RMD54 6

RMD55 6

RMD56 6

RMD57 6

RMD58 6

RMD59 6

RMD60 6

RMD61 6

RMD62 6

RMD63 6

MVREF

VCCMEM

J1B

1

VREF

2

VREF

9

VDD

10

VDD

21

VDD

22

VDD

33

VDD

34

VDD

36

VDD

45

VDD

46

VDD

57

VDD

58

VDD

69

VDD

70

VDD

81

VDD

82

VDD

92

VDD

93

VDD

94

VDD

113

VDD

114

VDD

131

VDD

132

VDD

143

VDD

144

VDD

155

VDD

156

VDD

157

VDD

167

VDD

168

VDD

179

VDD

180

VDD

191

VDD

192

VDD

197

VDDSPD

SODIMM

DDR-SODIMM-200P-RVS

2

VCCMEM

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

1

C3

22uF

1

C10

22uF

1

C17

1nF

1

C24

1nF

1

1

1

1

1

1

1

C5

C4

100pF

22uF

1

1

C11

C12

22uF

100pF

1

1

C18

C19

1nF

1nF

1

1

C26

C25

1nF

1nF

3

4

15

16

27

28

38

39

40

51

52

63

64

75

76

87

88

90

103

104

125

126

137

138

149

150

159

161

162

173

174

185

186

DGND

DESIGN NOTE: This schematic

shows a non-parallel terminated

DDR solution. There may be

restrictions as to the total number

of DRAMS and the number of banks

supported on the SODIMM. See LX

layout guidelines for current

restrictions.

C6

100pF

1

C13

100pF

1

C20

10nF

1

C27

10nF

C7

100pF

1

C14

100pF

1

C21

10nF

1

C28

10nF

C8

100pF

1

C15

100pF

1

C22

10nF

1

C29

10nF

C9

1nF

1

C16

1nF

1

C23

10nF

1

C30

10nF

DGND

*AMD CONFIDENTIAL*

Advanced Micro Devices

1351 South Sunset St.

Longmont CO 80501

Title

AMD GEODE™ LX EPIC RDK Reference Sc hematic

Document Number Rev

Size

3

2

B

40744 D

Date: Sheet

Wednesday, April 11, 2007

1

726

of

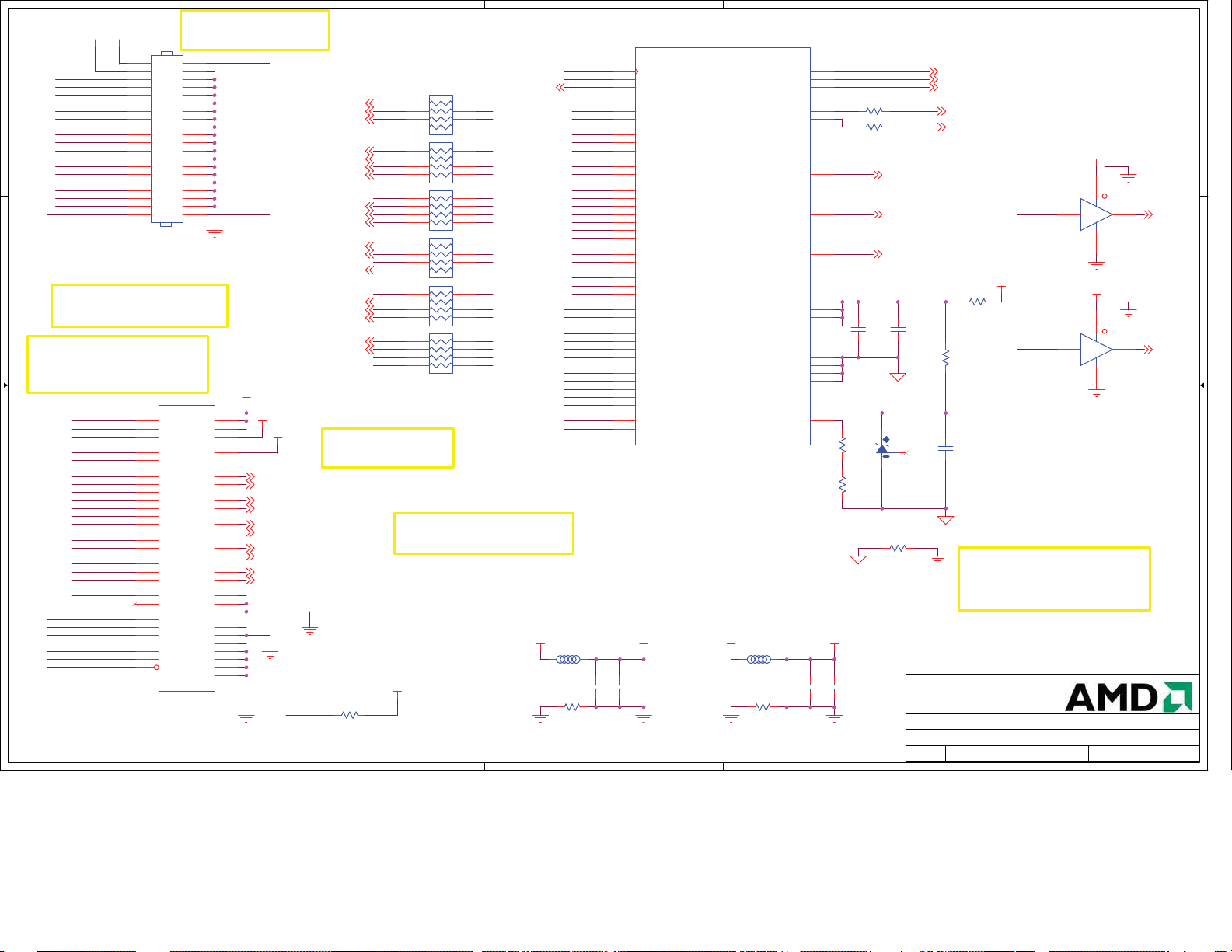

Page 8

5

DESIGN NOTE: 8-bit Data Streaming

VCC3VCC5

HSIP_CLK

HSIP_D0

HSIP_D1

D D

HSIP_D2

HSIP_D3

HSIP_D4

HSIP_D5

HSIP_D6

HSIP_D7

HSIP_D8

HSIP_D9

HSIP_D10

HSIP_D11

HSIP_D12

HSIP_D13

HSIP_D14

HSIP_D15

LDEMOD_HSIP_VSYNC

PFL-2x20-2M0-SMD-S

Mode is the simplest data input mode,

but is limited to 8-bits.

J3

1

3

5

7

9

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

2

4

6

8

10

DGND

HSIP_SYNC

HSIP_HSYNC

High Speed

Input Port

C C

B B

A A

DESIGN NOTE: When using 16 data capture

mode (Mode 4 - BT.601), the TFT interface

cannot be used due to pin sharing conflicts.

DESIGN NOTE: There are two conventions

for connecting 24 bit panels. One is backward

compatible with 18 bit panels. The connections

defined here are backwards compatible.

TFT_R2

TFT_R3

TFT_R4

TFT_R5

TFT_R6

TFT_R1

TFT_R7

TFT_G2

TFT_G3

TFT_G4

TFT_G0

TFT_G1

TFT_G5

TFT_G6

TFT_G7

TFT_B2

TFT_B0

TFT_B1

TFT_B3

TFT_B4

TFT_B5

TFT_B6

TFT_B7

HSYNC_C

VSYNC_C

LDEMOD_HSIP_VSYNC

TFT_R0

TFTCLK

R_F_CLK

DISPEN

51

52

54

55

56

2

3

4

6

7

8

10

11

12

14

15

16

18

19

20

22

23

24

25

27

28

30

50

31

17

32

U2

IN00

IN01

IN02

IN03

IN04

IN05

IN06

IN07

IN08

IN09

IN10

IN11

IN12

IN13

IN14

IN15

IN16

IN17

IN18

IN19

IN20

IN21

IN22

IN23

IN24

IN25

IN26

IN27

CLKIN

R_FB

PD

DS90C385

CLKO-

CLKO+

OUT0-

OUT0+

OUT1-

OUT1+

OUT2-

OUT2+

OUT3-

OUT3+

TSSOP56 Package

24-bit LVDS Transmitter

5

VCC

VCC

VCC

LVCC

PVCC

LGND

LGND

LGND

PGND

PGND

GND

GND

GND

GND

GND

1

9

26

44

34

40

39

48

47

46

45

42

41

38

37

36

43

49

33

35

5

13

21

29

53

VCC3

LVDS_AVCC3

TXCLKOUT- 26

TXCLKOUT+ 26

TXOUT0- 26

TXOUT0+ 26

TXOUT1- 26

TXOUT1+ 26

TXOUT2- 26

TXOUT2+ 26

TXOUT3- 26

TXOUT3+ 26

LVDS_PGND

DGND

LVDS_PVCC3

LDVS_AGND

R_F_CLK

4

TFT_R4

TFT_R426

TFT_R3

TFT_R326

TFT_R2

TFT_R226

TFT_R0

TFT_B6

TFT_B626

TFT_B7

TFT_B726

TFT_R6

TFT_R626

TFT_R5

TFT_R526

TFT_B0

TFT_B3

TFT_B326

TFT_B4

TFT_B426

TFT_B5

TFT_B526

TFT_B2

TFT_B226

TFT_G7

TFT_G726

TFT_B1

TFT_G5

TFT_G526

TFT_G1

TFT_G4

TFT_G426

TFT_G3

TFT_G326

TFT_G6

TFT_G626

TFT_G2

TFT_G226

TFT_R7

TFT_R726

TFT_G0

TFT_R1

DESIGN NOTE: The LSB's for

each color (R0,R1,G0,G1,B0,B1)

are not used in by 18-bit panels.

1

R10 0_NL

4

RN69 22

8

7

6

RN70 22

8

7

6

RN71 22

8

7

6

RN72 22

8

7

6

RN73 22

8

7

6

RN74 22

8

7

6

DESIGN NOTE: For 18-bit panels use OUT0,

OUT1, and OUT2. For 24-bit panels use

OUT0, OUT1, OUT2, and OUT3.

VCC3

3

U26C

HSIP_CLK

HSIP_SYNC

TFTCLK

T_R4

1

T_R3

2

T_R2

3

T_R

45

T_B6

1

T_B7

2

T_R6

3

T_R5

45

T_B0

1

T_B3

2

T_B4

3

T_B5

45

T_B2

1

T_G7

2

T_B1

3

T_G5

45

T_G1

1

T_G4

2

T_G3

3

T_G6

45

T_G2

1

T_R7

2

T_G0

3

T_R1

45

TFTCLK26

0

HSIP_D8

HSIP_D9

HSIP_D10

HSIP_D11

HSIP_D12

HSIP_D13

HSIP_D14

HSIP_D15

HSIP_D0

HSIP_D1

HSIP_D2

HSIP_D3

HSIP_D4

HSIP_D5

HSIP_D6

HSIP_D7

VCC3

FB1

1 2

BLM18PG600SN1

1

R8 0

DGND LVDS_PGND

T_B0

T_B1

T_B2

T_B3

T_B4

T_B5

T_B6

T_B7

T_G0

T_G1

T_G2

T_G3

T_G4

T_G5

T_G6

T_G7

T_R0

T_R1

T_R2

T_R3

T_R4

T_R5

T_R6

T_R7

1

C36

10uF

AL12

AL14

AH11

AJ11

AK10

AL10

AJ10

AH10

AJ15

AK15

AL15

AH13

AJ13

AK13

AL13

AK12

3

VIPCLK

VIPSYNC

AE1

DOTCLK/VOPCLK

AH7

DRGB0/VOP7

AK6

DRGB1/VOP6

AL6

DRGB2/VOP5

AJ7

DRGB3/VOP4

AK7

DRGB4/VOP3

AL7

DRGB5/VOP2

AH8

DRGB6/VOP1

AJ8

DRGB7/VOP0

AJ2

DRGB8/VOP15

AK3

DRGB9/VOP14

AL3

DRGB10/VOP13

AH5

DRGB11/VOP12

AJ4

DRGB12/VOP11

AL4

DRGB13/VOP10

AK4

DRGB14/VOP9

AJ5

DRGB15/VOP8

AF2

DRGB16_VOP23

AF1

DRGB17_VOP22

AG3

DRGB18_VOP21

AG4

DRGB19_VOP20

AH1

DRGB20_VOP19

AH2

DRGB21_VOP18

AH3

DRGB22_VOP17

AJ1

DRGB23_VOP16

DRGB24/VID8

DRGB25/VID9

DRGB26/VID10

DRGB27/VID11

DRGB28/VID12

DRGB29/VID13

AL9

DRGB30/VID14

AK9

DRGB31/VID15

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VID7

LVDS_PVCC3

1

C38

100nF

1

C39

10nF

LDEMOD/VIP_VSYNC

DISPEN/VOP_BLANK

VDDEN/VIP_HSYNC

VSYNC/VOP_VSYNC

HSYNC/VOP_HSYNC

AMD GEODE™

LX PROCESSOR

VCC3

1 2

BLM18PG600SN1

1

R9 0

DGND

FB2

RED

GREEN

BLUE

DAVDD

DAVDD

DAVDD

DAVDD

DAVSS

DAVSS

DAVSS

DAVSS

DVREF

DRSET

1

C37

10uF

2

LDEMOD_HSIP_VSYNC

AD4

AE4

AE2

AD3

AE3

W3

V2

U2

W4

V4

U1

V1

W2

Y2

U3

V3

W1

Y1

1

R6

1.2K

1

R601

10

AGND_VGA

LVDS_AVCC3

1

1

C40

C41

100nF

10nF

LDVS_AGND

2

1

DISPEN

HSIP_HSYNC

VSYNC_C

1

R30 22

HSYNC_C

1

R29 22

RED 14

GREEN 14 VSYNC 14

BLUE 14

DACVDD

1

1

C34

C33

10nF

10uF

AGND_VGA

D1

LM4041AIM3-1.2

2 1

1

R7 0

LDEMOD_HSIP_VSYNC 26

DISPEN 26

HSIP_HSYNC 26

1

1

C35

3

10nF

AGND_VGA

DGND

VSYNC_C 26

HSYNC_C 26

VCC3

53

1

VSYNC_C

VCC3

1

R4 1

R5

10K

DESIGN NOTE: AGND_VGA should be an

island with single point connection to the

full ground plane to reduce noise content.

Zero ohm resistor can be removed as

long as above condition is met.

HSYNC_C

2 4

DGND

VCC3

53

1

2 4

DGND

DGND

U22

NC7SZ125/SC70

DGND

U23

NC7SZ125/SC70

*AMD CONFIDENTIAL*

Advanced Micro Devices

1351 South Sunset St.

Longmont CO 80501

Title

AMD GEODE™ LX EPIC RDK Reference Sc hematic

Document Number Rev

Size

B

40744 D

Date: Sheet

Wednesday, April 11, 2007

1

826

HSYNC 14

of

Page 9

5

DESIGN NOTE: There are 8 PCI

U1B

devices in this design requireing REQ

/ GNT pairs. Two 1 to 3 expanders

are provided, giving a total of 7 pairs.

Two pairs are mapped to the following

three devices: Ethernet, MiniPCI and

PC104 slot 3. Jumpers are provided

D D

to select.

PCI_C/BE0#11,15,19,20,24

PCI_C/BE1#11,15,19,20,24

PCI_C/BE2#11,15,19,20,24

PCI_C/BE3#11,15,19,20,24

PCI_DEVSEL#11,15,19,20,24

PCI_FRAME#11,15,19,20,24

PCI_IRDY#11,15,19,20,24

REQ_EXT0#

REQ_EXT1#

REQ_EXT2#

PW1

AL18

AJ17

AB1

Y31

AB29

AD28

AE29

AC31

AL17

AK17

AB2

AB4

5

PCI_TRDY#11,15,19,20,24

PCI_STOP#11,15,19,20,24

PCI_RST#11,12,15,16,17,19,20,24,25

PW0

PW1

DOTREF

SYSREF

IRQ13

INTA#

CIS

SUSPA#

TDP

TDN

TDBGI

TDBGO

C C

PW0

PW1

B B

CLK_48_DOT12

CLK_CPU13

IRQ13

IRQ1311

PCI_INTA#11,19,24

CIS11

SUSPA#

SUSPA#11

TDP17

TDN17

TDBGI_CPU

A A

TDBGO_CPU

GNT0#

GNT1#

GNT2#

8

7

6

AA28

AB30

AC30

AA29

AB31

AB28

AJ22

AL26

AH27

AH31

AK25

AL28

AH25

AK26

AJ25

Y30

CLPF

MLPF

VLPF

CAVDD

CAVSS

MAVDD

MAVSS

VAVDD

VAVSS

VCC3

DGND

GNT0#

GNT1#

GNT2#

REQ0#

REQ1#

REQ2#

CBE0#

CBE1#

CBE2#

CBE3#

DEVSEL#

FRAME#

IRDY#

TRDY#

STOP#

RESET#

W29

V29

AA3

W31

W30

V31

V30

AA1

AA2

LX PROCESSOR

COREPLLVDD

GNT0#24

GNT2#11

REQ0#

REQ0#24

REQ1#

REQ2#

REQ2#11

PCI_DEVSEL#

PCI_FRAME#

PCI_IRDY#

PCI_TRDY#

PCI_STOP# PCI_AD30

PCI_RST#

RN68 10K

1

2

3

4 5

U1D

AMD GEODE™

LX PROCESSOR

TMS

TDO

TCLK

AB3

TDI

AA4

AC1

AC2

4

AJ27

PAR

PCI_AD0

AJ19

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AMD GEODE™

PCI_DEVSEL#

PCI_FRAME#

PCI_TRDY#

PCI_IRDY#

PCI_STOP#

REQ0#

REQ1#

REQ2#

GLPLLVDD COREPLLVDD

DOTPLLVDD

JTAGTDI

JTAGTMS

JTAGTCK

4

AD30

AD31

RN44 10K

1

2

3

4 5

RN54 10K

1

2

3

4 5

1

C45

220pF

CPLLGND

GLPLLGND

TDO_CPU 12

CPLLGND DGND

DPLLGND

GLPLLGND

1

C46

220pF

AH19

AL20

AK20

AK19

AH21

AJ21

AL19

AK22

AL22

AK23

AH22

AL23

AL25

AH24

AJ24

AJ28

AK28

AL29

AJ30

AK29

AJ31

AH30

AH29

AG29

AG28

AF30

AE28

AF31

AE30

AE31

AD29

8

7

6

8

7

6

1

DPLLGND

1

1

1

PCI_AD1

PCI_AD2

PCI_AD3

PCI_AD4

PCI_AD5

PCI_AD6

PCI_AD7

PCI_AD8

PCI_AD9

PCI_AD10

PCI_AD11

PCI_AD12

PCI_AD13

PCI_AD14

PCI_AD15

PCI_AD16

PCI_AD17

PCI_AD18

PCI_AD19

PCI_AD20

PCI_AD21

PCI_AD22

PCI_AD23

PCI_AD24

PCI_AD25

PCI_AD26

PCI_AD27

PCI_AD28

PCI_AD29

PCI_AD31

VCC3

DESIGN NOTE: CLKFB output

is used internally by the 8209 to

produce the zero delay.

C47

220pF

R35 0

R36 0

DGND

R38 0

DGND

PCI_PAR 11,15,19,20,24

PCI_AD[31:0] 11,15,19,20,24

--- --- --- --- --- --- ---

Off On Off Off Off 500 400

Off On Off Off On 500 333

Off On On On On 433 333

On On On On On Bypass Bypass

REQ_EXT0#20

CLK_EXT13

CLKFB_EXT

DOTPLLVDD

GLPLLVDD

3

5 4 3 2 1 CORE MEM

VCC3

VCC3_EXT1

U3

21

28

96

13

REQ_EXT0#

REQ_EXT1#

REQ_EXT2#

GNT1#

PCI_FRAME#

PCI_STOP#

PCI_RST#

1

C48

10nF

CPLLGND VCC3

1

C51

10nF

DPLLGND VCC3

1

C54

10nF

GLPLLGND

3

NC

5

REQ1

8

REQ2

11

REQ3

1

FRAME

2

STOP

26

RESET

27

CLKIN

14 15

NC NC

1

R31 10K

DGND

1

R33 1

1

R34 1

1

R37 1

1

C49

10nF

1

C52

10nF

1

C55

10nF

VCCVSS

172425

VCC

VSS

NC

AVCC

GNT1

GNT2

GNT3

S_REQS_GNT

CLKFB

CLK1

CLK2

CLK3

CLK4

VSS

AVSS

IT8209R

GND_EXT1

VCC3

1

C50

10uF

1

C53

10uF

1

C56

10uF

PW0

5

SUSPA#

4

GNT2#

3

GNT1#

2

GNT0#

1

Debug

Stall

IRQ13

16

7

GNT_EXT1#

10

GNT_EXT2#

12

REQ1#

34

CLKFB_EXT

23

22

20

19

18

VCC3

BLM18PG600SN1

DGND GND_EXT1

DESIGN NOTE:

COREPLLGND, DOTPLLGND

and GLPLLGND should each

be an island with single point

connection to the full ground

plane to reduce noise content.

Zero ohm resistor can be

removed as long as above

condition is met.

CLK_EXT0 20

CLK_EXT1 19

CLK_EXT2 15

FB3

1 2

1

R32 0

JP-1x2_NL

1

R21 1K_NL

1

R22 10K

GNT_EXT0# 20

1

C42

10uF

2

1

R11 10K_NL

1

R12 1K

1

R13 10K_NL

1

R14 1K

1

R15 10K_NL

1

R16 1K

1

R17 10K_NL

1

R18 1K

1

R19 10K_NL

1

R20 1K

Normal

Setting

2

VCC3

Off

On

Off

On

Off

On

JTAGTCK

TDBGI_CPU

JTAGTDI

JTAGTMS

Off

On

J4

1

1

C43

100nF

2

DGND

VCC3_EXT1

1

C44

10nF

TDBGI_CPU

TDBGO_CPU

Off

On

REQ_EXT1#

REQ_EXT2#

GNT_EXT1#

GNT_EXT2#

DESIGN NOTE: Two REQ/GNT pairs are mapped

to the following three devices: Ethernet, MiniPCI

and PC104 slot 3. Jumpers are provided to select.

DGND DGND

11

13

1

3

5

7

9

J7

PFL-7X2

J5

1

3

5

7

9

11 12

PFL-2x6-2M0-SMD-S

J6

1

3

5

7

9

11 12

PFL-2x6-2M0-SMD-S

2

4

6

8

10

12

14

JTAG HEADER

*AMD CONFIDENTIAL*

Advanced Micro Devices

1351 South Sunset St.

Longmont CO 80501

Title

AMD GEODE™ LX EPIC RDK Reference Schematic

Document Number Rev

Size

B

40744 D

Date: Sheet

Wednesday, April 11, 2007

1

RN28

1

2

3

4 5

4.7K

2

4

6

8

10

2

4

6

8

10

VCC3

JTAGTDI

1

VCC3

8

7

6

REQ#_LAN 15

REQ#_MPCI 19

REQ#_PC3 24

GNT#_LAN 15

GNT#_MPCI 19

GNT#_PC3 24

JTAGTCK 12

JTAGTMS 12

JTAGTDO 12

SYS_RST# 11,17,25

DESIGN NOTE: Add

"JTAG HEADER" to

the silkscreen

926

of

Page 10

5

VCC3

D D

C C

VCCMEM

B B

A A

5

AL11

AG31

AA31

AC29

AD31

AJ3

AD1

AC3

AJ6

AJ9

AJ12

AG1

AF29

AJ14

AJ18

AJ20

AJ23

AJ26

AK1

AJ29

AF3

AK31

AL2

AL8

AL24

AL21

AL5

AL27

AL30

B11

A14

B31

C29

P29

C14

C18

A18

B24

C25

B27

D28

E30

G29

B21

H31

K29

L31

A30

N29

VCORE

P13

P14

D15

P18

P19

R28

U28

U29

U30

U31

V13

V14

V18

V19

V28T1T3

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

Y3

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

D4

VMEM

C7

VMEM

N4

VMEM

VMEM

H1

VMEM

L1

VMEM

B8

VMEM

VMEM

VMEM

VMEM

VMEM

B5

VMEM

VMEM

K3

VMEM

VMEM

VMEM

VMEM

VMEM

VMEM

VMEM

VMEM

VMEM

VMEM

VMEM

VMEM

VMEM

VMEM

VMEM

C3

VMEM

A2

VMEM

B1

VMEM

E2

VMEM

G3

VMEM

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AK27

AK30

AL1

AL16

AH16B3C1P4R2

AL31

AK8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AK18

AK16

AK14

AK11

AK21

AK24

4

N13

N14T4N18

N19

VDD

VDD

VDD

VDD

VDD

VDD

VDD

AMD GEODE™

LX PROCESSOR

VSS

VSS

VSS

VSS

VSS

VSS

VSS

U19

C12

AH23

AH26

AF4

AH18

4

U1E

U18

VDD

VSS

U17

VDD

VSS

U16

VDD

VSS

AH15U4AH17T2Y28

U15

VDD

VSS

W19

U14

VDD

VSS

W18

U13

VDD

VSS

W14

T31

VDD

VSS

W13

T30

VDD

VSS

D17

VDD

VSS

VSS

AF28

VSS

VSS

T29N3K4

3

VCORE

W17A1E1B2R4

AH28

D10

VSS

VSS

A3

VSS

VSS

VSS

VSS

VSS

VSS

B14

VSS

A16

VSS

D18

VSS

AJ16

VSS

V17

VSS

AK2

VSS

V16

VSS

V15

VSS

R15

VSS

R14

VSS

R13

VSS

P28

VSS

L2

VSS

N16

VSS

A31

VSS

A27

VSS

N15

VSS

D16

VSS

D7

VSS

N17

VSS

N28

VSS

P15

VSS

P16

VSS

P17

VSS

H2

VSS

A11

VSS

R16

VSS

R17

VSS

R18

VSS

AH12

VSS

Y29

VSS

AA30

VSS

AD30

VSS

AG2

VSS

AH9

VSS

AH4

VSS

AH6

VSS

AG30

VSS

R19

VSS

AH20

VSS

C2

VSS

C4

VSS

A8

VSS

W16

VSS

W15

VSS

D25

VSS

B18

VSS

AH14

VSS

A24

VSS

A29

VSS

B29

VSS

B30

VSS

C28

VSS

C30

VSS

C31

VSS

D29

VSS

E31

VSS

G28

VSS

K28

VSS

P31

VSS

W28

VSS

AC28

VSS

D3

VSS

A5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

G4

AC4

AD2R1Y4

H30

T13

VCC3

VCCMEM

D14

D22

C21

A21

AK5

R3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L30

T14

T15

T16

T17

T18

T19

T28

1

C57

22uF

1

C64

1nF

1

C72

22uF

1

C79

1nF

1

C87

22uF

1

C94

100pF

1

C102

22uF

1

C109

100pF

1

C65

1nF

1

C80

1nF

1

C95

100pF

1

C110

100pF

2

1

C58

22uF

1

C73

22uF

1

C88

22uF

1

C103

22uF

1

C66

1nF

1

C81

1nF

1

C96

100pF

1

C111

100pF

1

C59

22uF

1

C74

22uF

1

C89

22uF

1

C104

22uF

1

C67

1nF

1

C82

1nF

1

C97

100pF

1

C112

100pF

1

C60

10nF

1

C75

10nF

1

C90

10nF

1

C105

10nF

1

C68

100pF

1

C83

100pF

1

C98

100pF

1

C113

100pF

1

C61

10nF

1

C69

100pF

1

C76

10nF

1

C84

100pF

1

C91

10nF

1

C99

100pF

1

C106

10nF

1

C114

100pF

1

C70

100pF

1

C85

100pF

1

C100

10nF

1

C115

10nF

1

C62

10nF

1

C77

10nF

1

C92

10nF

1

C107

10nF

1

C71

100pF

1

C86

100pF

1

C101

10nF

1

C116

10nF

1

C93

10nF

1

C63

10nF

1

C78

10nF

1

C108

10nF

1

DGND

*AMD CONFIDENTIAL*

Advanced Micro Devices

1351 South Sunset St.

Longmont CO 80501

DGND

3

2

Title

AMD GEODE™ LX EPIC RDK Reference Sc hematic

Document Number Rev

Size

B

40744 D

Date: Sheet

Wednesday, April 11, 2007

1

10 26

of

Page 11

5

PCI_AD[31:0]9,15,19,20,24

D D

DESIGN NOTE: Any

GPIO can be used as

an IRQx or INT#x.

There are significant

bootloader configuration

changes required if

selection is different than

shown. Changes are

highly discouraged.

C C

PCI_PAR9,15,19,20,24

PCI_C/BE0#9,15,19,20,24

PCI_C/BE1#9,15,19,20,24

PCI_C/BE2#9,15,19,20,24

PCI_C/BE3#9,15,19,20,24

PCI_FRAME#9,15,19,20,24

PCI_IRDY#9,15,19,20,24

PCI_DEVSEL#9,15,19,20,24

PCI_TRDY#9,15,19,20,24

PCI_INTA#9,19,24

PCI_STOP#9,15,19,20,24

GNT2#9

REQ2#9

B B

PCI_AD0

PCI_AD1

PCI_AD2

PCI_AD3

PCI_AD4

PCI_AD5

PCI_AD6

PCI_AD8

PCI_AD9

PCI_AD10

PCI_AD11

PCI_AD12

PCI_AD13

PCI_AD14

PCI_AD15

PCI_AD16

PCI_AD17

PCI_AD18

PCI_AD19

PCI_AD20

PCI_AD21

PCI_AD22

PCI_AD23

PCI_AD24

PCI_AD25

PCI_AD26

PCI_AD27

PCI_AD28

PCI_AD29

PCI_AD30

PCI_AD31

PCI_INTA#

R17

T17

R16

T16

P16

T15

R15

P15

T14

R14

U13

T13

R13

U12

T12

R12

U10

U14

U11

R10

R11

T10

T11

U8

R8

U7

R7

U6

U5

R5

R4

U3

U1

R6

U9

R2

R1

T8

T7

T6

T5

T4

T3

T9

T1

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

PAR

C/BE0#

C/BE1#

C/BE2#

C/BE3#

FRAME#

IRDY#

DEVSEL#

TRDY#

GPIO0

STOP#

GNT#

REQ#

U4A

GPIO6/MFGPT0_RS/MFGPT1_C1/MFGPT2_C2

GPIO11/SLP_CLK_EN#/MFGPT1_C2

AMD GEODE™

CS5536

COMPANION

DEVICE

4

PCI_CLK

WORKING

GPIO28/PWR_BUT#

GPIO5/MFGPT1_RS/MFGPT0_C1

GPIO7/MFGPT2_C1/SLEEP_X

GPIO8/UART1_TX/UART1_IR_TX

GPIO9/UART1_RX/UART1_IR_RX

GPIO10/THRM_ALRM#

GPIO24/WORK_AUX

GPIO25/LOW_BAT#/MFGPT7_C2

GPIO26/MFGPT7_RS

GPIO27/MFGPT7_C1/32KHZ

GPIO13/SLEEP_BUT

GPIO12/AC_S_IN2/SLEEP_Y

RESET_OUT#

RESET_STAND#

RESET_WORK#

SUSP#/CIS

SUSPA#

IRQ13

MHZ14_CLK

KHZ32_XCI

KHZ32_XCO

USB_PTEST

TEST_MODE

LVD_TEST

FUNC_TEST

U4

C5

A8

D3

D2

C2

E3

D1

C3

A1

C9

A9

B7

C8

F2

J3

A5

B8

C6

P3

N1

K2

C1

A4

B3

G15

A6

B9

F3

WORKING

PWRBTN#

IDE_CABLEID#

5536_GPIO6

PCI_INTB#PCI_AD7

WORK_AUX

CS5536_GPIO25

PME#

MFGPT7_C1

PCI_INTD#

PCI_INTC#

RST_STB#

SYS_RST#

TEST_MODE

FUNC_TEST

3

CLK_IOC 13

WORKING 25

PWRBTN# 25

IDE_CABLEID# 21

PCI_INTB# 15,19,24

CS5536_GPIO8 17

CS5536_GPIO9 17

OT_ALARM 17

SLP_CLK# 13

WORK_AUX 25

CS5536_GPIO25 17

PME# 15,17,19,25

PCI_INTD# 24

PCI_INTC# 24

PCI_RST# 9,12,15,16,17,19,20,24,25

RST_STB# 25

SYS_RST# 9,17,25

CIS 9

SUSPA# 9

IRQ13 9

CLK_14_IOC 13

RTCXIN

RTCXOUT

DESIGN NOTE:

LED is optional.

5536_GPIO6

MFGPT7_C1

WORK_AUX

PME#

MFGPT7_C1

PWRBTN#

WORKING

CS5536_GPIO25

RST_STB#

SLP_CLK#

IDE_CABLEID#

SYS_RST#

PCI_INTA#

PCI_INTB#

PCI_INTC#

PCI_INTD#

TEST_MODE

FUNC_TEST

1

R94 0_NL

1

R95 0

PWR MANAGEMENT

RED

D2

1

12

LTST-C190EKT

R46 560

1

R39 1K

1

R40 5.6K

1

R41 5.6K

RN29 10K

1

2

3

4 5

RN30 10K

1

2

3

4 5

RN31 10K

1

2

3

4 5

1

R42 1K

1

R43 1K

LAN_PD# 15

CS5536_GPIO6 17

VCC5SB

2

8

7

6

8

7

6

8

7

6

VCC3SB

DGND

RTCXIN

RTCXOUT

VCC3

1

R441M

1

C119

22pF

DGND DGND

C117

1

1pF

1

R4522M

1 4

Y1

32.768KHz

ABS13-32.768KHz-12.5pF - T

C118

22pF

1

1

VCC3

1

1

R91

R93

330R

VCC3SB

DESIGN NOTE: GPIO24/WORK_AUX is an

open drain output, which requires a pullup

resistor to achieve a high state. At initial

standby power application the

GPIO24/WORK_AUX pin defaults to GPIO24

and the GPIO24 defaults as an input. This

A A

default combination will leave the pin in a

high state due to the pullup which is

normally connected to VCC3SB. This circuit

works aournd that behaviour so that Save to

RAM will function correctly.

5

1

C120

100nF

DGND

WORK_AUX

WORKING

1

2

SAVE TO RAM SUPPORT

53

U5

4

NC7SZ08/SC70

DGND

4

1

R48 10K

INVERTER

1

C122

4.7uF

DGND

VCC3SB

1

R47

10K

DGND

Q1

BSS138/SOT

3

1

C121

100nF

PS_ON# 25

2

MFGPT7_C1

IDE_LED21

EXT_PWRBTN#25

EXT_RST#25

*AMD CONFIDENTIAL*

Advanced Micro Devices

1351 South Sunset St.

Longmont CO 80501

Title

AMD GEODE™ LX EPIC RDK Reference Sc hematic

Document Number Rev

Size

Date: Sheet

B

J31

2

1

4

3

6

5

8

7

PFL-2x4-2M0-SMD-S

DGND

40744 D

Wednesday, April 11, 2007

330R

1

11 26

of

Page 12

5

IDE_D[15:0]21

D D

C C

B B

A A

IDE_RST#21

IDE_D7

IDE_D8

IDE_D6

IDE_D9

IDE_D5

IDE_D10

IDE_D4

IDE_D11

IDE_D3

IDE_D12

IDE_D2

IDE_D13

IDE_D1

IDE_D14

IDE_D0

IDE_D15

IDE_DRQ#21

IDE_RDY#21

IDE_ACK#21

DESIGN NOTE: Place series R

near the audio CODEC.

SDATA_IN

BITCLK

DESIGN NOTE: USBPWR_EN1/2 and

USB_OC# are used for a fully compliant

USB design. See Option Schematics for

fully compliant USB design.

IDE_DRQ#

IDE_IOW#21

IDE_IOR#21

IDE_RDY#

IDE_IRQ

IDE_IRQ21

IDE_A121

IDE_A021

IDE_A221

IDE_CS0#21

IDE_CS1#21

1

R65 22

1

R63 22

5

RN32 22

1

2

3

4 5

RN34 22

1

2

3

4 5

RN36 22

1

2

3

4 5

RN37 22

1

2

3

4 5

RN38 22

1

2

3

4 5

RN39 22

1

2

3

4 5

RN40 22

1

2

3

4 5

AC97_DATA_IN 16

AC97_BITCLK 16

I_RST#

8

I_D7

7

I_D8

6

I_D6

I_D9

8

I_D5

7

I_D10

6

I_D4

I_D11

8

I_D3

7

I_D12

6

I_D2

I_D13

8

I_D1

7

I_D14

6

I_D0

I_D15

8

I_DRQ#

7

I_IOW#

6

I_IOR#

I_RDY#

8

I_ACK#

7

I_IRQ

6

I_A1

I_A0

8

I_A2

7

I_CS0#

6

I_CS1#

SDATA_IN

SDATA_OUT_BOS1

PCBEEP16

CLK_48_DOT9

USB_PWR_EN118

USB_PWR_EN218

USB_OC#18

USB0+18

USB0-18

USB1+18

USB1-18

USB2+18

USB2-18

USB3+18

USB3-18

CLK_IDE13

BITCLK

SYNC_BOS0

I_IRQ

I_RST#

I_A0

I_A1

I_A2

I_ACK#

I_DRQ#

I_IOR#

I_IOW#

I_RDY#

I_CS0#

I_CS1#

I_D0

I_D1

I_D2

I_D3

I_D4

I_D5

I_D6

I_D7

I_D8

I_D9

I_D10

I_D11

I_D12

I_D13

I_D14

I_D15

4

B12

GPIO2/IDE_IRQ0

F15

IDE_RESET#

A10

MHZ66_CLK

A11

IDE_AD0/FLASH_AD25/AD0/FLASH_CLE

A12

IDE_AD1/FLASH_AD26/AD1

B11

IDE_AD2/FLASH_AD27/AD2

C12

IDE_DACK0#/FLASH_CS3#/FLASH_CE3#

A14

IDE_DREQ0/FLASH_CS2#/FLASH_CE2#

B13

IDE_IOR0#/FLASH_RE#

C13

IDE_IOW0#/FLASH_WE#

A13

IDE_RDY0/FLASH_IOCHRDY/FLASH_RDY/BUSY#

B10

IDE_CS0#/FLASH_CS0#/FLASH_CE0#

C10

IDE_CS1#/FLASH_CS1#/FLASH_CE1#

B14

IDE_DATA0/FLASH_AD10/IO0

A15

IDE_DATA1/FLASH_AD11/IO1

C15

IDE_DATA2/FLASH_AD12/IO2

C16

IDE_DATA3/FLASH_AD13/IO3

B17

IDE_DATA4/FLASH_AD14/IO4

D15

IDE_DATA5/FLASH_AD15/IO5

E15

IDE_DATA6/FLASH_AD16/IO6

E16

IDE_DATA7/FLASH_AD17/IO7

E17

IDE_DATA8/FLASH_AD18/AD3

D17

IDE_DATA9/FLASH_AD19/AD4

D16

IDE_DATA10/FLASH_AD20/AD5

C17

IDE_DATA11/FLASH_AD21/AD6

A17

IDE_DATA12/FLASH_AD22/AD7

B16

IDE_DATA13/FLASH_AD23/AD8

B15

IDE_DATA14/FLASH_AD24/AD9

C14

IDE_DATA15/FLASH_ALE

K3

GPIO1/AC_BEEP/MFGPT0_C2

M1

AC_CLK

L3

AC_S_SYNC/BOS0

L1

AC_S_IN

L2

AC_S_OUT/BOS1

N17

MHZ48_CLK

P17

USB_PWR_EN1

N16

USB_PWR_EN2

N15

USB_OC_SENS#

K16

USB1_DATPOS

K17

USB1_DATNEG

L16

USB2_DATPOS

L17

USB2_DATNEG

H17

USB3_DATPOS

H16

USB3_DATNEG

G17

USB4_DATPOS

G16

USB4_DATNEG

SDATA_OUT_BOS1

SYNC_BOS0

BOS1

BOS0

4

1

R64 22

1

R66 22

DESIGN NOTE: Place

series R near the IOC.

1

R67 10K_NL

1

R68 1K

1

R69 10K_NL

1

R70 1K

U4B

LPC_SERIRQ/GPIO21/MFGPT2_RS

AMD GEODE™

CS5536

COMPANION

DEVICE

AC97_DATA_OUT 16

AC97_SYNC 16

VCC3

DGND

3

LPC_CLK

LPC_AD0/GPIO16

LPC_AD1/GPIO17

LPC_AD2/GPIO18

LPC_AD3/GPIO19

LPC_DRQ#/GPIO20

LPC_FRAME#/GPIO22

GPIO14/SMB_CLK

GPIO15/SMB_DATA

GPIO3/UART2_RX

GPIO4/UART2_TX

TCK

TDO

TMS

T_DEBUG_IN

T_DEBUG_OUT

LVD_EN#

USB_REXT

USB_VBUS

MHZ48_XCO

MHZ48_XCI

MHZ48_XCEN

BOS10BOS0

0

1

0

1

3

2

LPC Header

VCC3 VCC3

J8

1

3

5

7

9

11

13

15

17

19

DGND

CLK_LPC_IOC

H1

LAD0

H2

LAD1

J2

LAD2

J1

LAD3

K1

LDRQ#

G1

LFRAME#

H3

SERIRQ

G2

SMB_SCL

G3

SMB_SDA

F1

CRT_SCL

E1

CRT_SDA

E2

N2

P1

TDI

P2

N3

TDBGI_IOC

M2

M3

LVD_EN#

C7

CLK_LPC_IOC 13

LAD0 17

LAD1 17

LAD2 17

LAD3 17

LDRQ# 17

LFRAME# 17

SERIRQ 17,20

CRT_SCL 14,26

CRT_SDA 14,26

JTAGTCK 9

TDO_CPU 9

JTAGTDO 9

JTAGTMS 9

PFL-2x10

SMB_SCL 7

SMB_SDA 7

2

4

6

8

10

12

14

16

18

20

PCI_RST# 9,11,15,16,17,19,20,24,25

CLK_LPC_IOC

LAD3

LAD2

LAD1

LAD0

LFRAME#

SERIRQ

LDRQ#

DESIGN NOTE: This design uses LVD (LVD_EN# tied

low) to generate system reset. Since LVD only monit ors

Vcore in the working domain, the designer must

LAD0

LAD1

LAD2

LAD3

LDRQ#

SERIRQ

LFRAME#

XCEN

SMB_SCL

SMB_SDA

TDBGI_IOC

IDE_RDY#

IDE_IRQ

USB_OC#

PCBEEP

IDE_D7

IDE_DRQ#

LVD_EN#

CRT_SCL

CRT_SDA

1

RN33 10K

1

2

3

4 5

RN35 10K

1

2

3

4 5

1

R49 1K

1

R50 2.2K

1

R51 2.2K

1

R52 4.7K

1

R53 10K

1

R54 10K

1

R55 10K

1

R56 10K_NL

1

R57 10K

1

R58 10K

1

R59 10K

1

R60 2.2K

1

R61 2.2K

VCC3

8

7

6

8

7

6

DGND

VCC5

guarantee that Vio and other required voltages are

USB_REXT

K15

M15

XTALO_48

J15

XTALI_48

H15

XCEN

F17

BOOT STRAP OPTIONS

LPC ROM OFF LPC

NOR FLASH OFF IDE INTERFACE

0

RESERVED

1

SST FWH OFF LPC (DEFAULT)

1

1

DGND

R62

3.4K,1%

valid at or before Vcore. If this cannot be guaranteed,

then RESET_WORK# must be used to hold system in

reset until Vio and Vcore and any other required

voltages are valid.

XTALO_48

XTALI_48

*AMD CONFIDENTIAL*

Advanced Micro Devices

1351 South Sunset St.

Longmont CO 80501

Title

AMD GEODE™ LX EPIC RDK Reference Sc hematic

Document Number Rev

Size

2

B

40744 D

Date: Sheet

Wednesday, April 11, 2007

1

C123

18pF

Y2

1 2

48.0000MHz

1

1

C124

18pF

DGNDDGND

12 26

of

Page 13

5

DESIGN NOTE: If this schematic is used

DESIGN NOTE: Without UL approval

of the internal VBAT circuity, a 47 ohm

resistor (R1) is required. UL approval

is in process and is expected. With

D D

UL approval R1 can be removed.

J1

1-2

2-3 Clear CMOS

C C

B B

A A

VCC3

1

C157

22uF

DGND

Normal

1

C158

100nF

5

VCC3SB

VCC5

1

C162

18pF

DGND

1

C159

100nF

SLP_CLK#11

1 2

14.31818MHz

1

R75 10M_NL

for future designs, R72 should be replaced

with a 220_2A ferrite bead.

R1

1

R71 47

12

BT1

+

J1

VBH2032-1

DGND

330_NL

1

R213

DGND

1

C161

100nF

DGND

CLKX1

CLKX2

1

C163

18pF

1 2

1

R215

1K_NL

D19

BAS40_NL

U6

17

10

2

3

330_NL

1

R214

1

C160

100nF

Y3

DGND

J9

PFL-1x3

DGND

PD#

SEL66/33#

XTALIN

XTALOUT

1

C222

220M_NL

1

1

2

3

D17

1 2

BAS40_NL

D18

1 2

BAS40_NL

1211

87

19

VDDGND

VDDGND

VDD

VDD

GND

GND

15

4

1

R73

1K

DGND

VBAT

25428

VDD

VDD

REFCLK1

REFCLK0/SP#

48MHz

48MHz/TS#

66MHz

LCLK2

LCLK1

LCLK0

PCICLK0

PCICLK1

PCICLK2

PCICLK3

GND

GND

MK1491-09F

22

21

DGND

4

1

C127

100nF

26

27

13

14

16

9

6

5

18

20

23

24

VCC3SB

1

C128

22uF

DGND

VCC3

1

FB4

HI1206N101R-00

14_318MHZ0

14_318MHZ1

48MHZ

IDE_CLK

PCI_CLK0

PCI_CLK1

PCI_CLK2

PCI_CLK3

LCLK0

LCLK1

VCORESB

1

C129

10nF

VCC3USB

1

C143

22uF

DGND

VCORE

3

VBAT

1

R72 4.7R

1

C130

10nF

1

C144

10nF

14_318MHZ0

14_318MHZ1

IDE_CLK

PCI_CLK3

PCI_CLK2

PCI_CLK1

PCI_CLK0

48MHZ

LCLK0

LCLK1

1

1

C132

C131

100nF

1uF

VCORE

1

1

C146

C145

100pF

10nF

VCC3

DESIGN NOTE: Enables

spread spectrum. EMI

mitigation technique

RN41

1

2

3

4 5

22

1

R23 22

RN42

1

2

3

4 5

22

RN43

1

2

3

4 5

22

DESIGN NOTE: Swap series resistors

on the clock lines in order minimize

the number of vias.

3

M14

K14

H14

D10

P10

P14

F14

D14

D12

P12

8

7

6

8

7

6

8

7

6

A3

A7

B6

D8

H4

K4

P8

D9

D6

D4

F4

M4

P4

P6

P9

VBAT

VCORE_VSB

VIO_VSB

VDDC_USB1

VDDC_USB0

VCORE

VCORE

VCORE

VCORE

VCORE

VCORE

VDDIO_USB0

VDDIO_USB1

VDDIO_USB2

VDDIO_USB3

VIO

VIO

VIO

VIO

VIO

VIO

VIO

VIO

VIO

VIO

U4C

AMD GEODE™

CS5536

COMPANION

DEVICE

1

R74 10K

DGND

CLK_14_CODEC 16

CLK_14_ISA 24

CLK_14_IOC 11

CLK_IDE 12

PC_CLK 24

CLK_EXT 9

CLK_IOC 11

CLK_CPU 9

SIO_CLK_48 17

CLK_LPC_SIO_EXT 17

CLK_LPC_IOC 12

VSSIO_USB0

VSSIO_USB1

VSSIO_USB2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

2

L15

NC

R9

NC

U17

NC

U16

NC

F16

NC

J16

NC

M16

NC

U15

NC

C11

NC

A16

NC

R3

NC

M17

NC

J17

NC

B5

NC

B4

NC

B1

NC

T2

NC

U2

NC

A2

NC

C4

NC

B2

NC

L14

J14

G14

N14

E14

D13

D11

D7

D5

E4

G4

J4

L4

N4

P5

P7

P11

P13

DGND

VCC3

1

C125

22uF

1

C133

10nF

1

C138

100pF

VCORE

1

C147

22uF

1

C149

10nF

1

C154

100pF

1

C134

10nF

1

C139

100pF

1

C126

22uF

1

C135

10nF

1

C140

100pF

1

C148

22uF

1

C150

10nF

1

C155

100pF

1

1

1

C136

C137

10nF

10nF

1

1

C142

C141

100pF

100pF

1

1

C151

C152

10nF

10nF

1

C156

100pF

DGND

*AMD CONFIDENTIAL*

Advanced Micro Devices

1351 South Sunset St.

Longmont CO 80501

Title

AMD GEODE™ LX EPIC RDK Reference Sc hematic

Document Number Rev

Size

2

B

40744 D

Date: Sheet

Wednesday, April 11, 2007

1

13 26

of

Page 14

5

4

3

2

1

D D

L1

RED8

GREEN8

C C

BLUE8 CRT_SCL 12,26

1

B B

R80

75

1

R81

75

1

R82

75

1

C164

4.7pF

1

1

C165

4.7pF

22nH

L2

1

22nH

INDUCTOR, 22NH, 5%, 0603, 0.48A

L3

1

22nH

INDUCTOR, 22NH, 5%, 0603, 0.48A

1

C166

4.7pF

AGND_VGA

INDUCTOR, 22NH, 5%, 0603, 0.48A

1

C167

4.7pF

VCC3

DGND

1

C168

4.7pF

D4

BAV99/SOT

1

C169

4.7pF

VCC5

1

1

C171

100nF

DGND

D5

BAV99/SOT

F1

1.10A, 16V

D3

BAV99/SOT

MRED

MGREEN MDDAT_UART_TX

MBLUE

DESIGN NOTE: Place

the ESD protection

components as close to

the VGA connector as

VCC3

D6

possible.

BAV99/SOT

DGND

C6

C1

C7

C2

C8

C3

C9

C4

C10

C5

P1C CON-COMBO-DB9-15-25-TRIPLEPORT

VGA

MTG5

MTG6

VGA_CHASSIS

C11

C12

C13

C14

C15

DGND

C170

1

100nF

FB5

BLM18PG600SN1

1

D7

BAV99/SOT

VGA_CHASSIS

D8

BAV99/SOT

D9

BAV99/SOT

MCRT_HSYNC

MCRT_VSYNC

MDDCLK_UART_RX

R76 0

R77 0

R78 0

R79 0

CRT_SDA 12,26

HSYNC 8

VSYNC 8

A A

5

4

3

2

*AMD CONFIDENTIAL*

Advanced Micro Devices

1351 South Sunset St.

Longmont CO 80501

Title

AMD GEODE™ LX EPIC RDK Reference Sc hematic

Document Number Rev

Size

B

40744 D

Date: Sheet

Wednesday, April 11, 2007

1

14 26

of

Page 15

5

D D

1 2

1

C187

22uF

1

C191

100nF

V_LAN_12A

1

C183

22uF

1

C188

100nF

1

C192

100nF

V_LAN_12

V_LAN_12

BLM18PG600SN1

FB8

1 2

1

C181

100nF

VCC3V_LAN

1

C180

22uF

DGND

C C

VCC3

BLM18PG600SN1

B B

A A

1

C182

100nF

FB7

1 2

1

C190

22uF

DGND

FB6

BLM18PG600SN1

V_LAN_12A_PLL

DGND

5

PCI_AD[31:0]9,11,19,20,24

1

1

C185

100nF

1

C186

100nF

PCI_C/BE0#9,11,19,20,24

PCI_C/BE1#9,11,19,20,24

PCI_C/BE2#9,11,19,20,24

PCI_C/BE3#9,11,19,20,24

GNT#_LAN9

REQ#_LAN9

PCI_DEVSEL#9,11,19,20,24

PCI_STOP#9,11,19,20,24

PCI_TRDY#9,11,19,20,24

PCI_IRDY#9,11,19,20,24

PCI_FRAME#9,11,19,20,24

PCI_PAR9,11,19,20,24

PCI_INTC#11,19,24

PCI_RST#9,11,12,16,17,19,20,24,25

CLK_EXT29

C184

100nF

VCC3

1

1

R88

R87

10K

10K

PME#11,17,19,25

25MHZ Crystal

Y4

1

C194

22pF

DGND

4

V_LAN_12A

V_LAN_12

U7

PCI_AD0

128

PCI_AD1

PCI_AD2

PCI_AD3

PCI_AD4

PCI_AD5

PCI_AD6

PCI_AD7

PCI_AD8

PCI_AD9

PCI_AD10

PCI_AD11

PCI_AD12

PCI_AD13

PCI_AD14

PCI_AD15

PCI_AD16

PCI_AD17

PCI_AD18

PCI_AD19

PCI_AD20

PCI_AD21

PCI_AD22

PCI_AD23

PCI_AD24

PCI_AD25

PCI_AD26

PCI_AD27

PCI_AD28

PCI_AD29

PCI_AD30

PCI_AD31

PCI_AD24

100R90

1

1

C195

22pF

4

PAD0

127

PAD1

126

PAD2

122

PAD3

121

PAD4

120

PAD5

119

PAD6

118

PAD7

117

PAD8

116

PAD9

115

PAD10

114

PAD11

113

PAD12

112

PAD13

111

PAD14

110