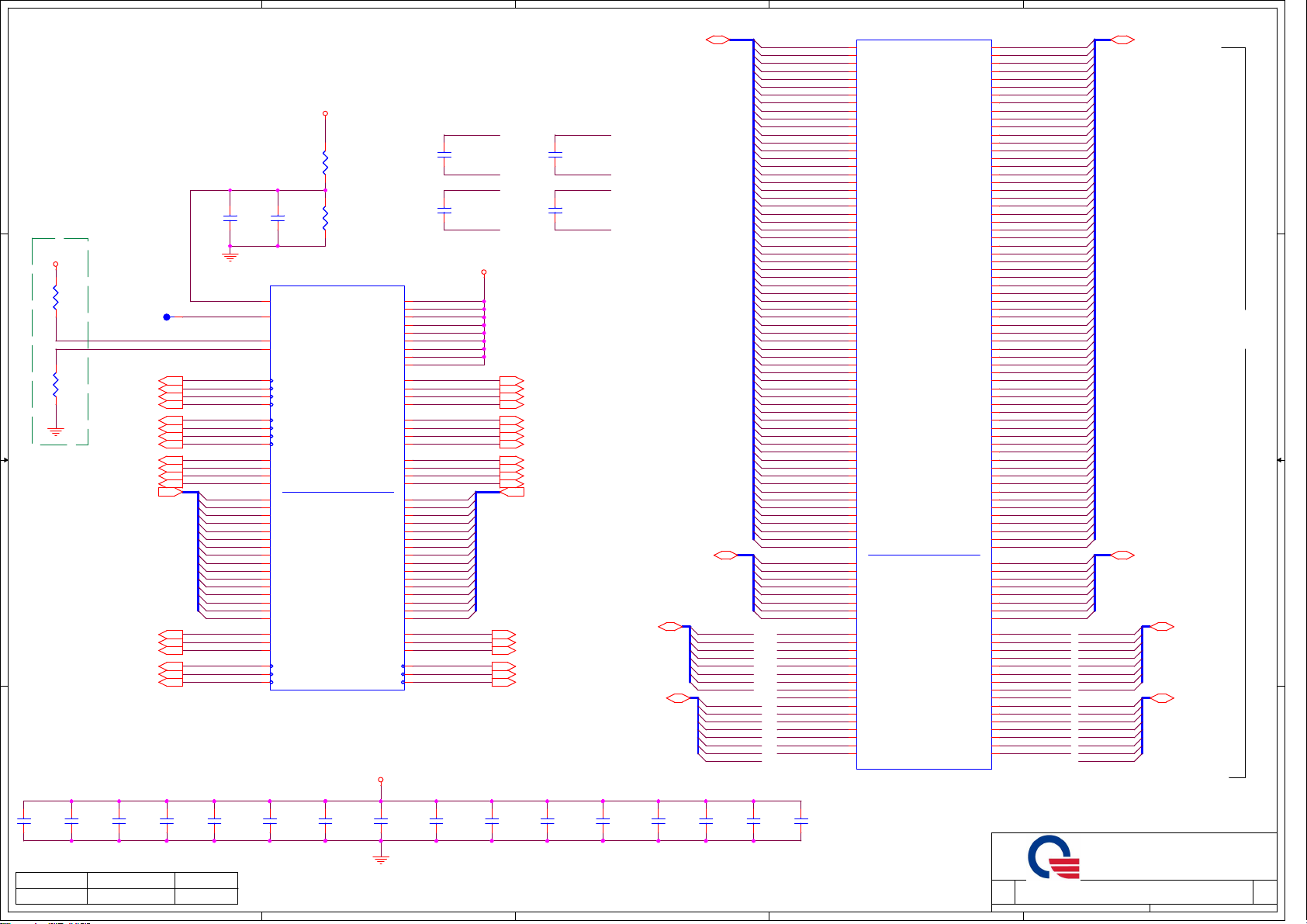

Acer Ferarri 200 Schematics

5

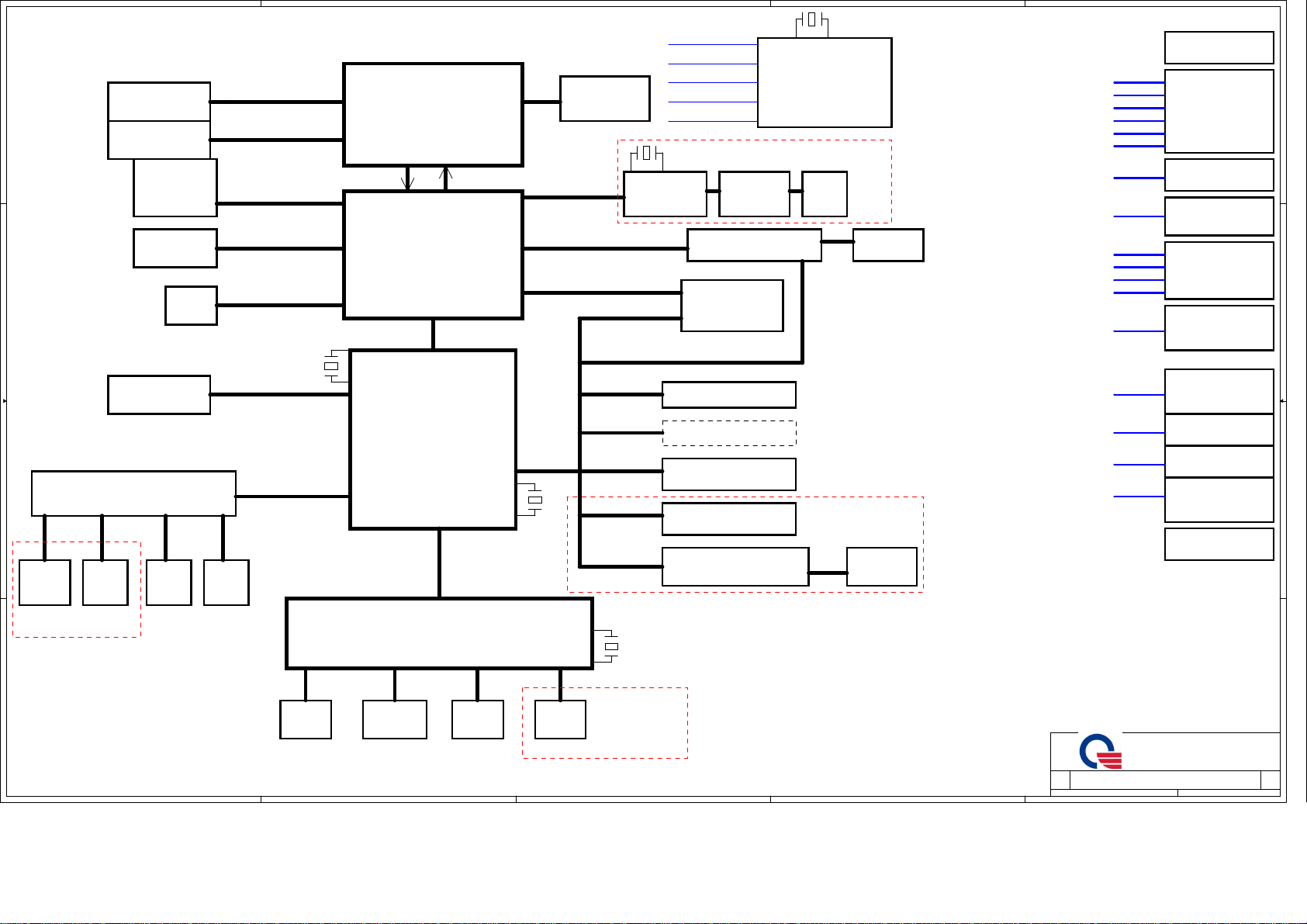

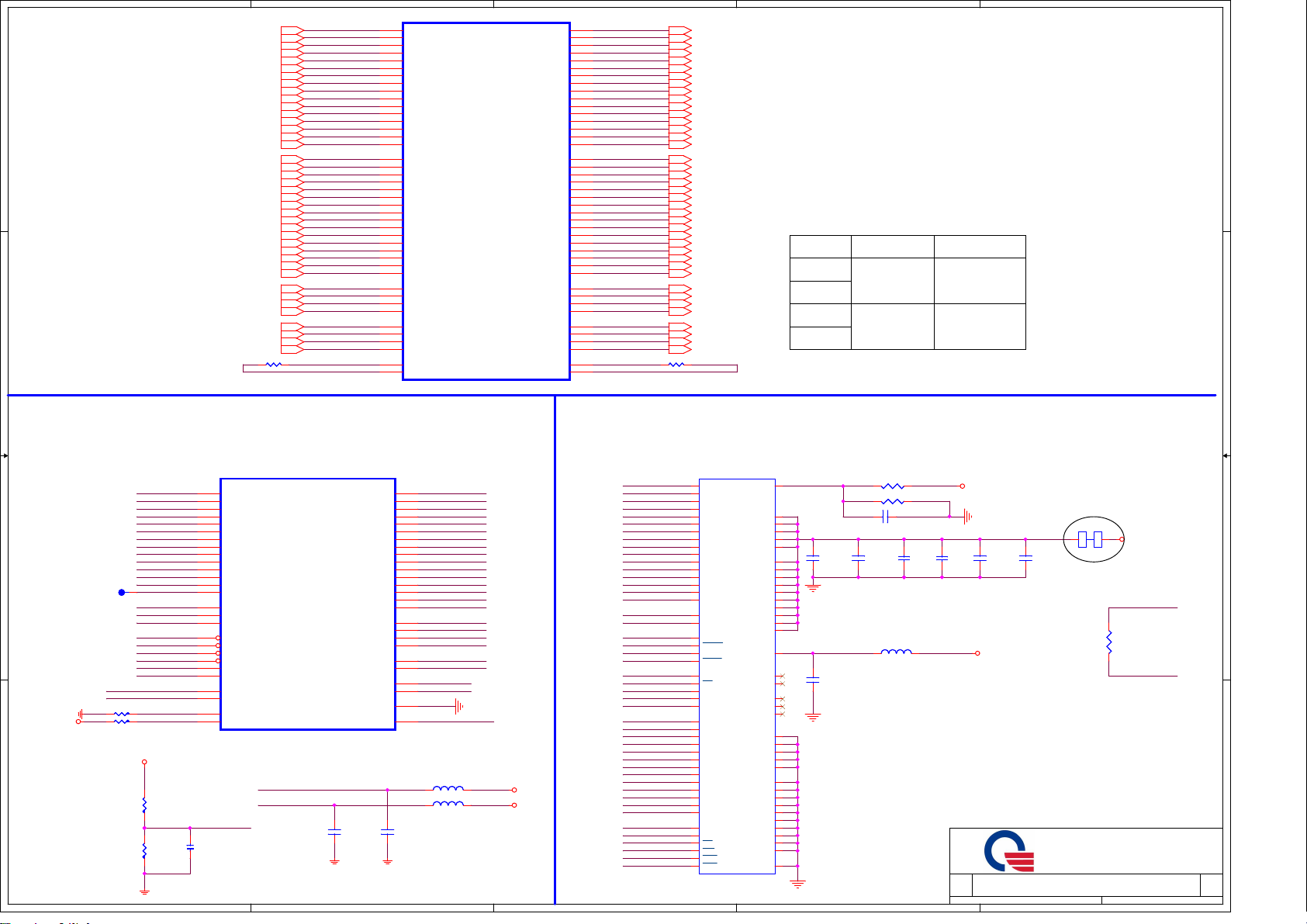

ZH6 Block Diagram

D D

DDRII-SODIMM A

PG 8

DDRII-SODIMM B

PG 8

Side port

memory

128MB

PG 9

LED Panel

(11.6'',1366x768)

PG 18

C C

CRT

PG 18

DDR II 800 MHz

Channel A

DDR II 800 MHz

Channel B

16bit DDR2

LVDS(1ch)

R/G/B

HT1 800MHz

X'TAL

25MHz

4

AMD S1g1

RS780MN

465 FCBGA

21mm*21mm

A_LINK (X4)

L310/S.C 1.2G/13W

PG 4,5,6,7

8W

PG 9,10,11,12

Thermal Sensor

G781

PCIE-2

PCIE-1 (Reserve)

PCIE-3

Port 7

3

HOST 200MHz

PCIE 100MHz

USB 48MHz

REF 14.318MHz

PG 6

HTREF 66MHz

X'TAL

25MHz

LAN(10/100/1000)

AR8131

Transformer

3G Card

Mini Card (WLAN)

PG 21

X'TAL

14.318MHz

CLOCK GENERATOR

PG 3

RJ45

D/B

PG 21

SIM CARD

2

PG 21

+3VPCU

+3V_S5

+3VSUS

+3V

+5VPCU

+5V

CPU_CORE

+NB_CORE

+1.8VSUS

+1.8V

+SMDDR_VTERM

+SMDDR_VREF

+1.1V

1

CHARGER

ISL88731

3V/5V

ISL6237

CPU VCORE

OZ828

NB CORE

UP6111AQDD

DDR

TPS51116

+1.1V

UP6111AQDD

PG 24

PG 25

PG 26

PG 27

PG 28

PG 29

Port 5

SATA - HDD

(SSD option)

PG 22

Azalia Audio Codec

B B

H.P

JACK

MIC

JACK

ALC269

PG 19

Speaker

Int. MIC

Digital

SATA0

Azalia

23mm*23mm

LPC

SB710

PG 13,14,15,16,17

4W

USB2.0

X'TAL

32.768KHz

Port 3

Port 6

Port 0

Port 1/2

Port 8

CCD

BT

(Optional)

USB2.0 I/O Ports X1

USB2.0 I/O Ports X2

Card Reader controller

RTS5159

PG 18

PG 23

PG 22

PG 22

PG 22

D/B

4 in 1

Connector

+2.5V

+1.5V

+1.2V_S5

+1.2V

+2.5V

RT9025

+1.5V

RT9025

+1.2V_S5

RT9025

+1.2V

G9334+AO4466

Thermal

Protection

PG 30

PG 30

PG 30

PG 30

PG 31

PG 19 PG 19 PG 19 PG 19

D/B

EC

WPCE775L

PG 24

X'TAL

SPI

A A

FAN

(PWM)

Keyboard

Flash

ROM

Touch

Pad

PS/2

32.768KHz

PG 24 PG 23PG 23PG 6

TP D/B

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ZH6

ZH6

ZH6

1 33Monday, August 24, 2009

1 33Monday, August 24, 2009

1

1 33Monday, August 24, 2009

1A

1A

1A

5

4

3

2

1

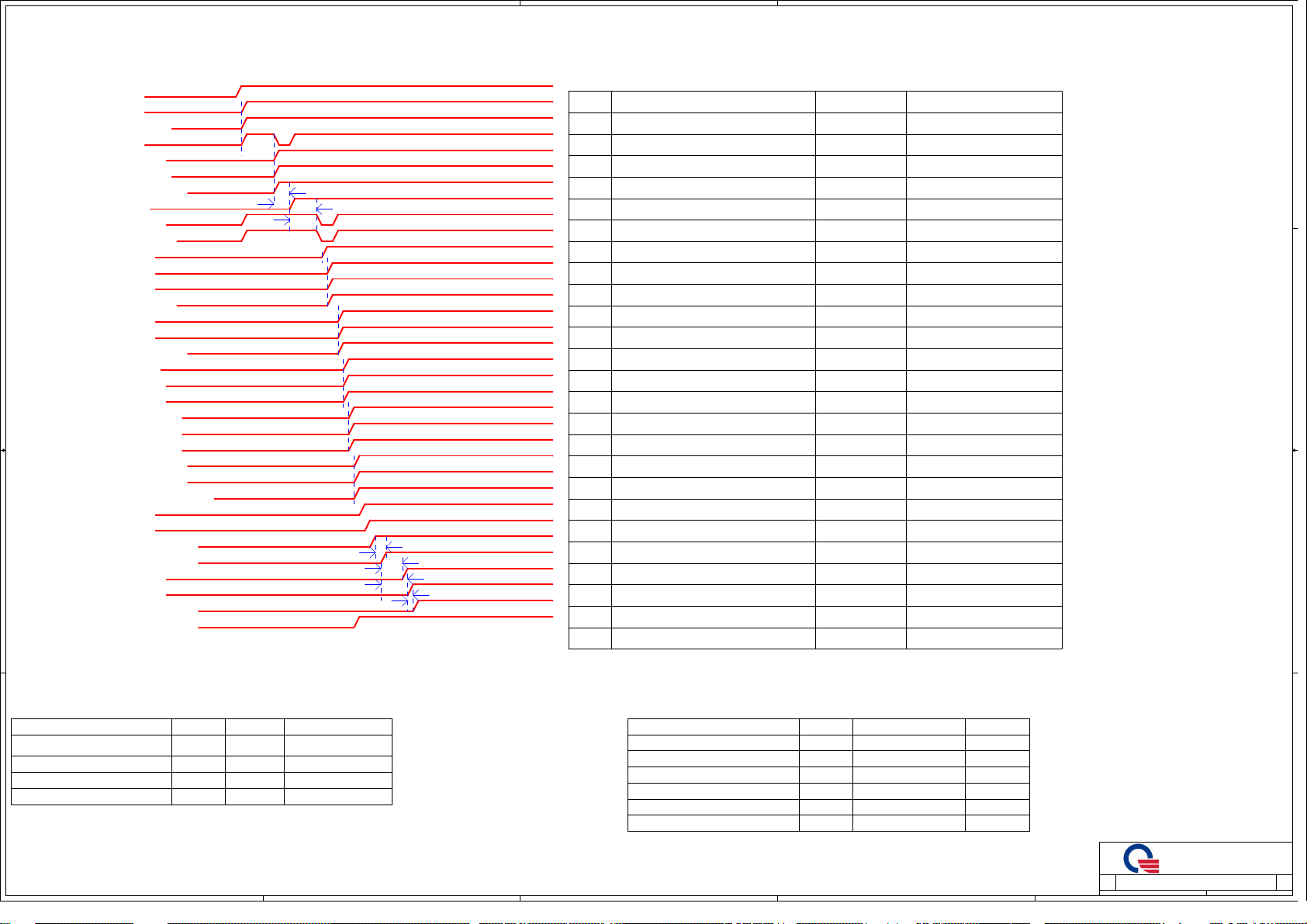

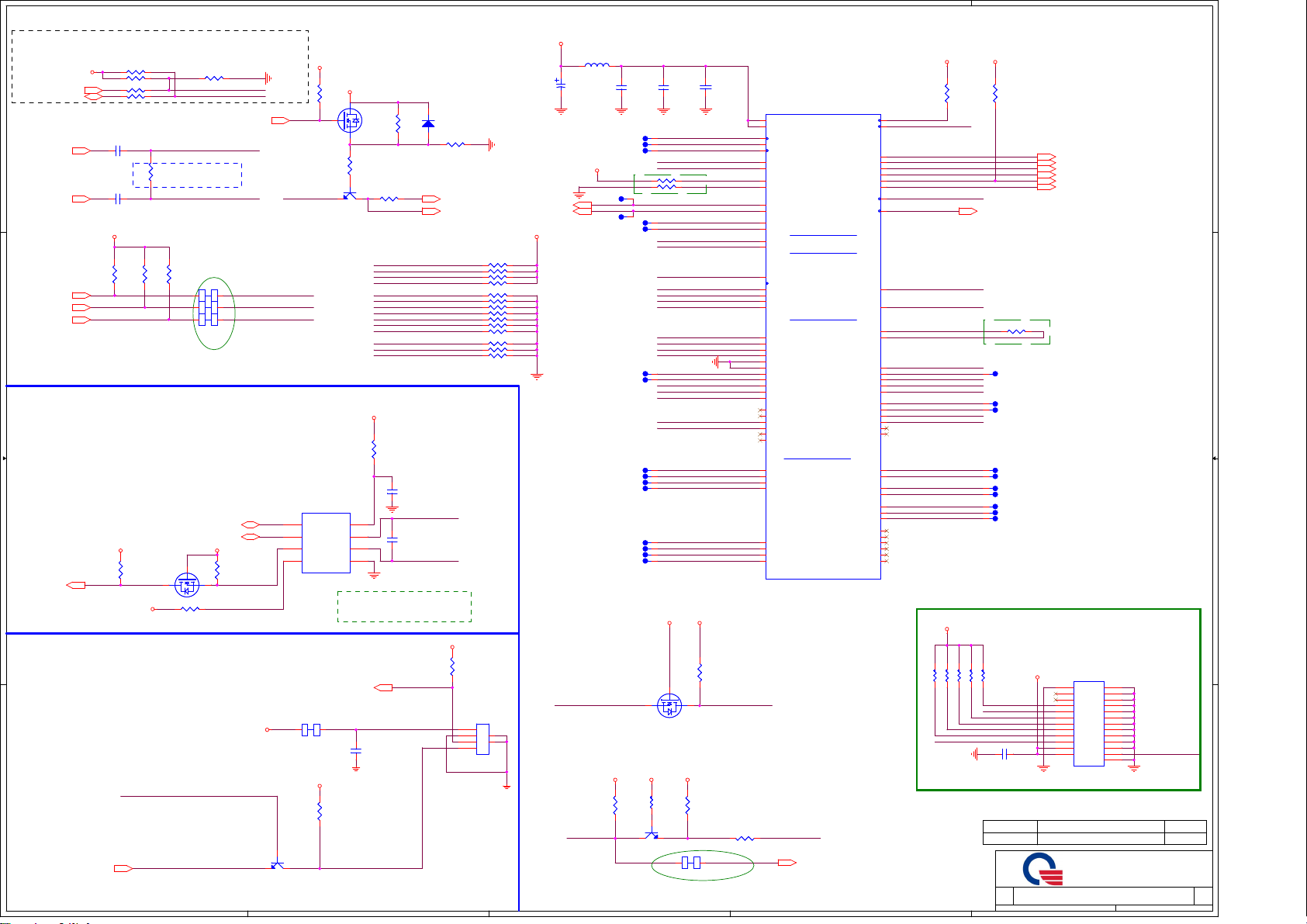

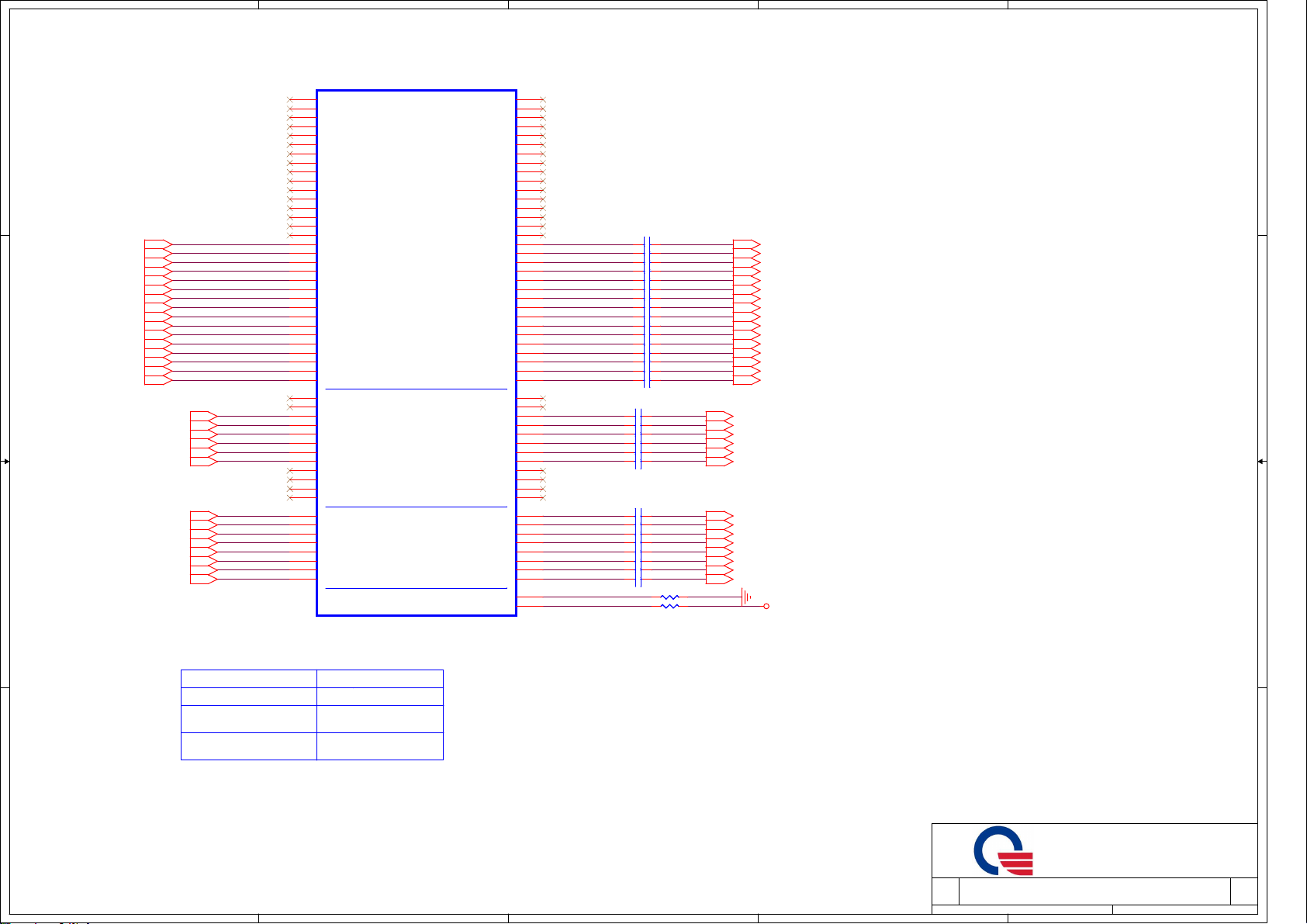

ZH6 Power On Sequence

From AC,Battery VIN

D D

From PWM

From Power Button

From EC

+5VPCU +3VPCU

SYS_HWPG(PCU)

NBSWON#

S5_ON

+3V_S5

From EC

From EC

From SB

From SB to EC

From EC

+1.2V_S5

RSMRST#

DNBSWON#

PCIE_WAKE#

SUSB#,SUSC#

SUSON

>10ms

>100ms

SUSON

+3VSUS +1.8VSUS +SMDDR_VREF +SMDDR_VTERM

From PWM

From EC

C C

From PWM

From EC

HWPG_1.8V (SUS)

MAINON

+5V +3V +2.5V +1.8V +1.5V

HWPG_1.5V,HWPG_2.5V

VRON

MAINON

VRON

+VCC_CORE

From PWM

From EC

CPU_COREPG

+1.2V_ON

+1.2V_ON

+1.2VFrom EC

From PWM

From EC

HWPG_1.2V

+1.2V_ON+RC

+1.2V_ON+RC

+NB_COREFrom EC

From PWM

HWPG_1.2V_NB

HWPG

From EC

B B

From SB

From SB

From SB

From SB

ECPWROK

NB_PWRGD

SB_PWRGD

CPU_PWRGD

PLTRST# PCIRST#

LDT_RST#

LDT_STOP#

-22ms~500ms

47ms~66ms

71ms~73ms

1.9ms~2.1ms

Items Function Name Description

1

3G Module 3G@

2

HDT debug function HDT@

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

BOM naming rule

25

*Note: EC will sampling SUSB# &

SUSC# every 5ms.

AMD SB710 SMBUS Table

CLK GEN RAM Mini Card (WLAN)

SB710 SDATA0/SCLK0(+3V)

SB710 SDATA1/SCLK1(+3V_S5)

Power Plane

A A

MOS CKT

5

V

+3V +3V

Reserve

VV

+3V

ReserveReserve

4

EC775 SDATA1/SCLK1(+3VPCU)

EC775 SDATA2/SCLK2(+3VPCU)

EC775 SDATA3/SCLK3(+3VPCU)

EC775 SDATA4/SCLK4(+3VPCU)

Power Plane

MOS CKT

3

EC SMBUS Table

Battery CPU thermal Sensor EC EEPROM

V

V

+3VPCU +3V +3VPCU

X X

X

2

V

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

SYSTEM INFORMATION

SYSTEM INFORMATION

SYSTEM INFORMATION

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

1

ZH6

ZH6

ZH6

1A

1A

2 33Monday, August 24, 2009

2 33Monday, August 24, 2009

2 33Monday, August 24, 2009

1A

5

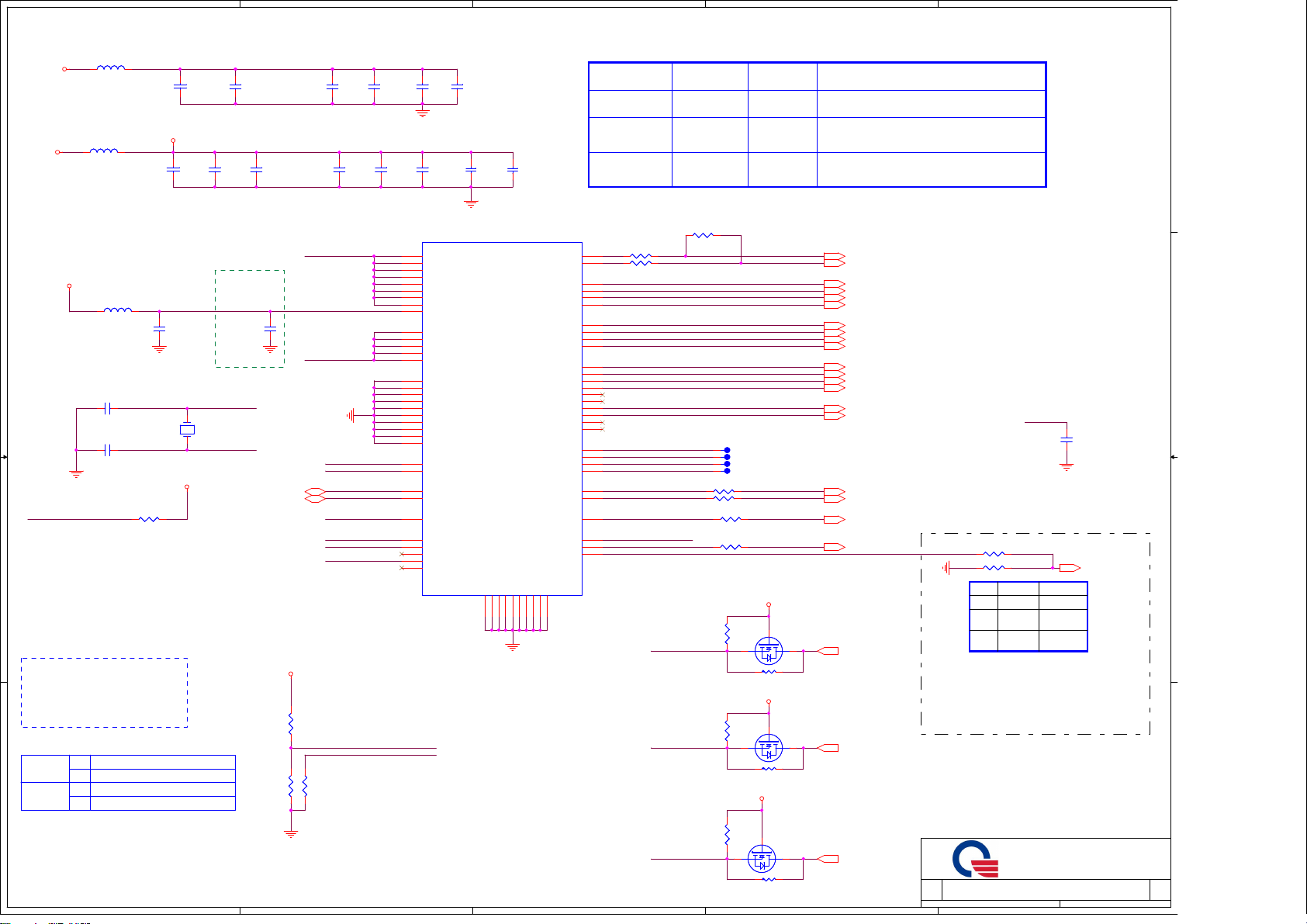

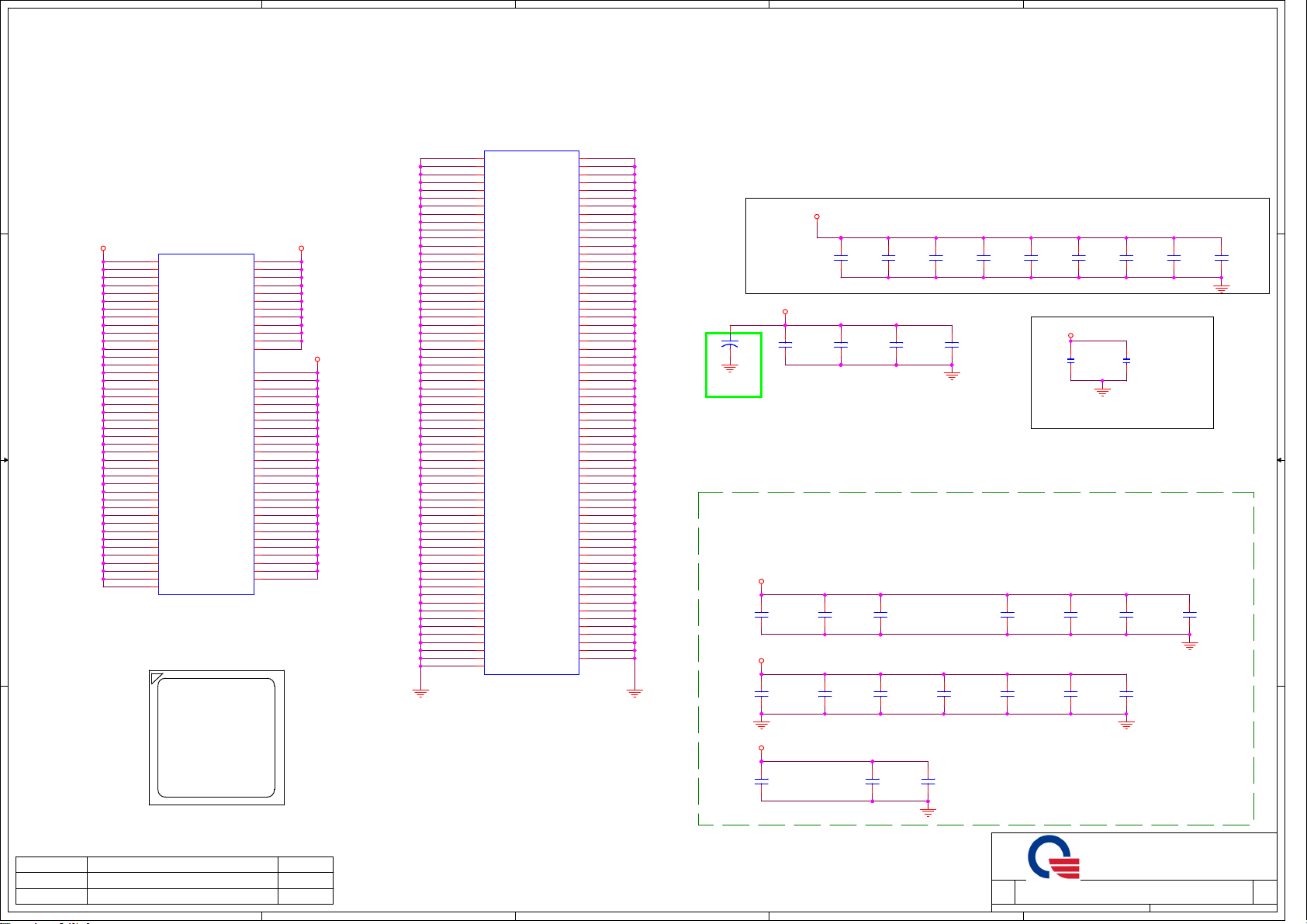

Clock Generator(CLK)

4

3

2

1

60 ohm, 0.5A

L25

L25

+1.2V

BLM18PG221SN1D/1.4A/220ohm_6

BLM18PG221SN1D/1.4A/220ohm_6

600 ohms@100Mhz

D D

+3V

DCR: 0.5 ohm

600 ohms@100Mhz

L37

L37

BLM18PG221SN1D/1.4A/220ohm_6

BLM18PG221SN1D/1.4A/220ohm_6

60 ohm, 0.5A

C252

C252

22U/6.3V_8

22U/6.3V_8

+3V_CLKVDD

C235

C235

22U/6.3V_8

22U/6.3V_8

C228

C228

C224

C224

0.1U/10V_4

0.1U/10V_4

C248

C248

0.1U/10V_4

0.1U/10V_4

0.1U/10V_4

0.1U/10V_4

+1.2V_CLKVDDIO

C247

C247

0.1U/10V_4

0.1U/10V_4

+3V_CLKVDD

C391

C391

0.1U/10V_4

0.1U/10V_4

C246

C246

0.1U/10V_4

0.1U/10V_4

C225

C225

C227

C227

C385

C385

0.1U/10V_4

0.1U/10V_4

0.1U/10V_4

0.1U/10V_4

C226

C226

0.1U/10V_4

0.1U/10V_4

0.1U/10V_4

0.1U/10V_4

C388

C388

C244

C244

0.1U/10V_4

0.1U/10V_4

0.1U/10V_4

0.1U/10V_4

CLOCKS name

NBGFX_CLKP

NBGFX_CLKN

EXT_GFX_CLKP

EXT_GFX_CLKN

NBGPP_CLKP

NBGPP_CLKN

SBLINK_CLKP

SBLINK_CLKN RP51 STUFF RP51 STUFF

UMA DISCRETE

RP49 STUFF

RP48 NC

RP43 NC

RP49 STUFF

RP48 STUFF

RP43 NC

Clock pin function

to NB for VGA reference clock

to M86-M external reference clock

to NB for RX780 for PCIEX2 interface reference clock only

RS780 is internal share with AC-LINK clock,RS780 not need

to NB for AC-LINK reference clock

EMI reserved

U6

U6

+3V_CLKVDD

+3V

Place very

close to

C/G

CG_XIN

Y3

14.318MHzY314.318MHz

CG_XOUT

+3V_CLK_VDDA

C240

C240

0.1u/10V_4

0.1u/10V_4

R191

R191

*8.2K_4

*8.2K_4

SCLK08,14,20

SDATA08,14,20

+3V_CLKVDD

R193

R193

8.2K_4

8.2K_4

+1.2V_CLKVDDIO

CLKREQ0#

CLKREQ1#

CLKREQ3#

R198

R198

8.2K_4

8.2K_4

CG_XIN

CG_XOUT

CLK_PD#

4

+3V

L24

L24

BLM18PG221SN1D/1.4A/220ohm_6

BLM18PG221SN1D/1.4A/220ohm_6

C C

C245

C245

2.2u/6.3V_6

2.2u/6.3V_6

C238 33P/50V_4C238 33P/50V_4

C242 33P/50V_4C242 33P/50V_4

Ver.B update XTAL.

CLK_PD#

B B

Clock chip has internal serial

terminations

for differencial pairs, external resistors

are

reserved for debug purpose.

SEL_HTT66

A A

SEL_SATA

R175 8.2K_4R175 8.2K_4

66 MHz 3.3V single ended HTT clock

1

*0 100 MHz differential HTT clock

100 MHz non-spreading differential SRC clock

1*

0

100 MHz spreading differential SRC clock

* default

5

4

VDDDOT

16

VDDSRC

26

VDDATIG

35

VDDSB_SRC

40

VDDSATA

48

VDDCPU

55

VDDHTT

56

VDDREF

63

VDD48

11

VDDSRC_IO0

17

VDDSRC_IO1

25

VDDATIG_IO

34

VDDSB_SRC_IO

47

VDDCPU_IO

1

GND48

7

GNDDOT

10

GNDSRC0

18

GNDSRC1

24

33

43

46

52

60

61

62

2

3

51

23

45

44

39

38

GNDATIG

GNDSB_SRC

GNDSATA

GNDCPU

GNDHTT

GNDREF

X1

X2

SMBCLK

SMBDAT

PD#

CLKREQ0#

CLKREQ1#

CLKREQ2#

CLKREQ3#

CLKREQ4#

SLG8SP628VTR

SLG8SP628VTR

QFN64

QFN64

REF0/SEL_HTT66

TGND065TGND166TGND267TGND368TGND469TGND570TGND671TGND772TGND873TGND9

ICS9LPRS480 P/N : ALPRS480000

SLG8SP628

RTM880N-796

SEL_SATA

SEL_HT66

P/N : AL8SP628000

P/N : AL000880000

CPUK8_0T

CPUK8_0C

ATIG0T

ATIG0C

ATIG1T

ATIG1C

SB_SRC0T

SB_SRC0C

SB_SRC1T

SB_SRC1C

SRC0T

SRC0C

SRC1T

SRC1C

SRC2T

SRC2C

SRC3T

SRC3C

SRC4T

SRC4C

SRC6T/SATAT

SRC6C/SATAC

SRC7T/27M_SS

SRC7C/27M_NS

HTT0T/66M

HTT0C/66M

48MHz_0

REF1/SEL_SATA

REF2/SEL_27

74

50

49

30

29

28

27

37

36

32

31

22

21

20

19

15

14

13

12

9

8

42

41

6

5

54

53

64

59

58

57

3

R164 0_4R164 0_4

R154 0_4R154 0_4

CLK_VGA_27M_SS

CLK_VGA_27M_NSS

NBHTREFCLK0P

NBHTREFCLK0N

CLK48MUSB

SEL_HT66SEL_HT66SEL_HT66SEL_HT66

SEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATASEL_SATA

SEL_27

R158 *261_4R158 *261_4

CPUCLKP

CPUCLKN

NBGFX_CLKP

NBGFX_CLKN

LASSO_CLKP

LASSO_CLKN

SBSRC_CLKP

SBSRC_CLKN

SBLINK_CLKP

SBLINK_CLKN

PCIE_MINI1_CLKP

PCIE_MINI1_CLKN

PCIE_MINI2_CLKP

PCIE_MINI2_CLKN

PCIE_LAN_CLKP

PCIE_LAN_CLKN

T93T93

T87T87

T108T108

T107T107

1

R148 0_4R148 0_4

1

R196 0_4R196 0_4

1

R147 0_4R147 0_4

NBHT_REFCLKP

NBHT_REFCLKN

CLK_48M_USB

+3V

*RHU002N06

*RHU002N06

2

+3V

*RHU002N06

*RHU002N06

2

+3V

*RHU002N06

*RHU002N06

2

Q10

Q10

3

Q12

Q12

3

Q9

Q9

3

R183 0_4R183 0_4

R176 0_4R176 0_4

R215 33_4R215 33_4

R194 33_4R194 33_4

R153

R153

*10K_4

*10K_4

CLKREQ1#

R195

R195

*10K_4

*10K_4

CLKREQ0#

B:(10/25) Add WLAN & LAN CLKREQ circuit (BOI request)

R152

R152

*10K_4

*10K_4

CLKREQ3#

CPUCLKP 6

CPUCLKN 6

NBGFX_CLKP 11

NBGFX_CLKN 11

LASSO_CLKP 21

LASSO_CLKN 21

SBSRC_CLKP 13

SBSRC_CLKN 13

SBLINK_CLKP 11

SBLINK_CLKN 11

CLK_PCIE_WLAN 20

CLK_PCIE_WLAN# 20

CLK_PCIE_3G 20

CLK_PCIE_3G# 20

CLK_PCIE_LAN 22

CLK_PCIE_LAN# 22

NBHT_REFCLKP 11

NBHT_REFCLKN 11

CLK_48M_USB 14

EXT_SB_OSC 13

CLKREQ_3G# 20

CLKREQ_WLAN# 20

CLKREQ_LAN# 22

2

CLK48MUSB

C249

C249

*10P/50V_4

*10P/50V_4

Ra

R189 158/F_4R189 158/F_4

Rb

R186 90.9/F_4R186 90.9/F_4

EXT_NB_OSC 11

RS780RX780

1.8V

82.5RRa

130RRb

RES CHIP 130 1/16W +-1%(0402)L-F -->CS11302FB15

RES CHIP 158 1/16W +-1%(0402) -->CS11582FB00

RES CHIP 90.9 1/16W +-1%(0402) -->CS09092FB15

RES CHIP 82.5 1/16W +-1%(0402) -->CS08252FB11

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

CLOCK GENERATOR

CLOCK GENERATOR

CLOCK GENERATOR

1.1V

158R

90.9R

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ZH6

3 33Monday, August 24, 2009

3 33Monday, August 24, 2009

3 33Monday, August 24, 2009

1

1A

1A

1A

5

4

3

2

1

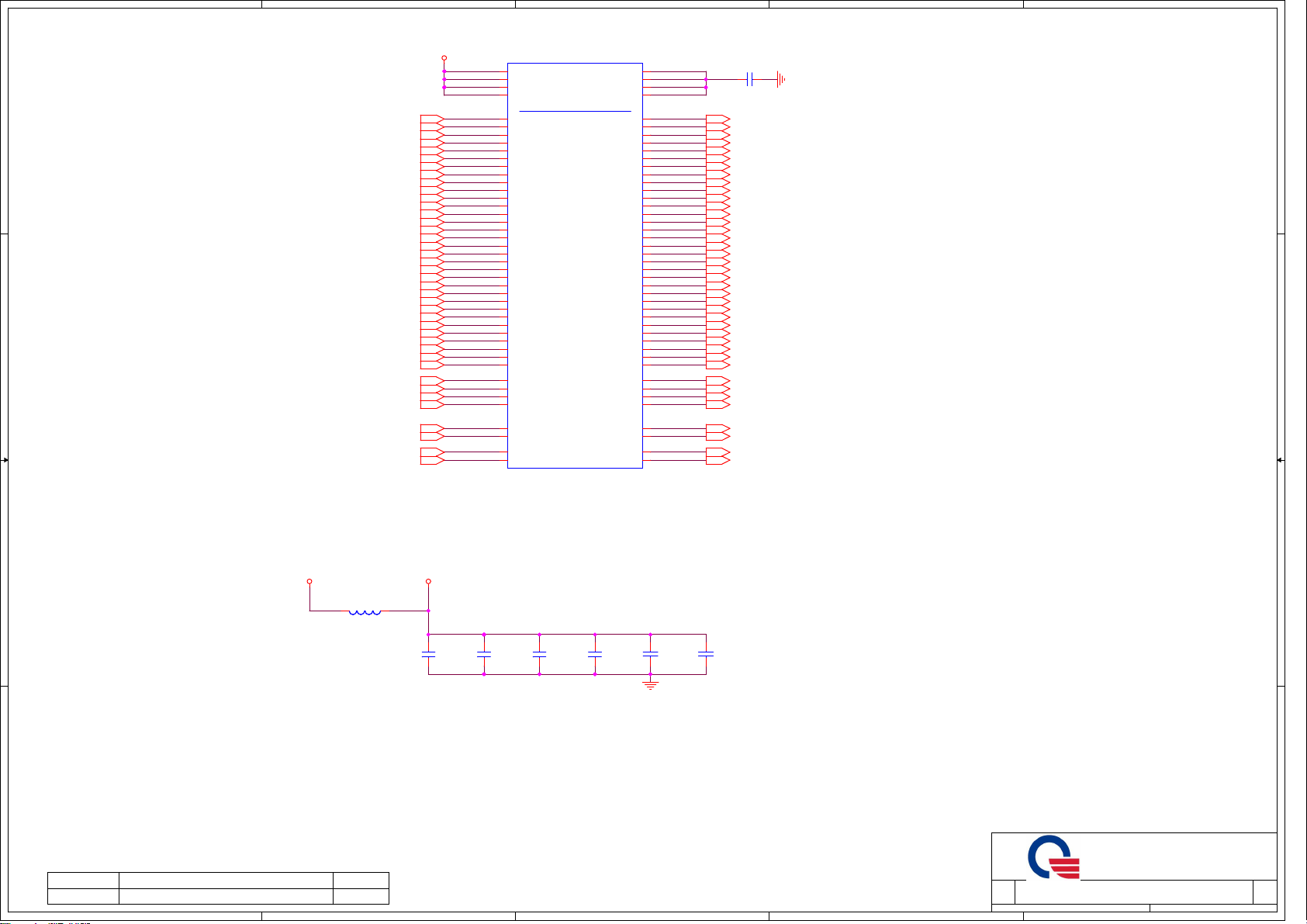

(CPU)

VLDT_RUN

D D

C C

HT_CADIN15_P9

HT_CADIN15_N9

HT_CADIN14_P9

HT_CADIN14_N9

HT_CADIN13_P9

HT_CADIN13_N9

HT_CADIN12_P9

HT_CADIN12_N9

HT_CADIN11_P9

HT_CADIN11_N9

HT_CADIN10_P9

HT_CADIN10_N9

HT_CADIN9_P9

HT_CADIN9_N9

HT_CADIN8_P9

HT_CADIN8_N9

HT_CADIN7_P9

HT_CADIN7_N9

HT_CADIN6_P9

HT_CADIN6_N9

HT_CADIN5_P9

HT_CADIN5_N9

HT_CADIN4_P9

HT_CADIN4_N9

HT_CADIN3_P9

HT_CADIN3_N9

HT_CADIN2_P9

HT_CADIN2_N9

HT_CADIN1_P9

HT_CADIN1_N9

HT_CADIN0_P9

HT_CADIN0_N9

HT_CLKIN1_P9

HT_CLKIN1_N9

HT_CLKIN0_P9

HT_CLKIN0_N9

HT_CTLIN1_P9

HT_CTLIN1_N9

HT_CTLIN0_P9

HT_CTLIN0_N9

D4

D3

D2

D1

N5

P5

M3

M4

L5

M5

K3

K4

H3

H4

G5

H5

F3

F4

E5

F5

N3

N2

L1

M1

L3

L2

J1

K1

G1

H1

G3

G2

E1

F1

E3

E2

J5

K5

J3

J2

P3

P4

N1

P1

Athlon 64 S1

Processor Socket

U19AU19A

VLDT_A3

VLDT_A2

VLDT_A1

VLDT_A0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

VLDT_B3

VLDT_B2

VLDT_B1

VLDT_B0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

AE5

AE4

AE3

AE2

T4

T3

V5

U5

V4

V3

Y5

W5

AB5

AA5

AB4

AB3

AD5

AC5

AD4

AD3

T1

R1

U2

U3

V1

U1

W2

W3

AA2

AA3

AB1

AA1

AC2

AC3

AD1

AC1

Y4

Y3

Y1

W1

T5

R5

R2

R3

C18

20mil20mil

C18

4.7u/6.3V_6

4.7u/6.3V_6

HT_CADOUT15_P 9

HT_CADOUT15_N 9

HT_CADOUT14_P 9

HT_CADOUT14_N 9

HT_CADOUT13_P 9

HT_CADOUT13_N 9

HT_CADOUT12_P 9

HT_CADOUT12_N 9

HT_CADOUT11_P 9

HT_CADOUT11_N 9

HT_CADOUT10_P 9

HT_CADOUT10_N 9

HT_CADOUT9_P 9

HT_CADOUT9_N 9

HT_CADOUT8_P 9

HT_CADOUT8_N 9

HT_CADOUT7_P 9

HT_CADOUT7_N 9

HT_CADOUT6_P 9

HT_CADOUT6_N 9

HT_CADOUT5_P 9

HT_CADOUT5_N 9

HT_CADOUT4_P 9

HT_CADOUT4_N 9

HT_CADOUT3_P 9

HT_CADOUT3_N 9

HT_CADOUT2_P 9

HT_CADOUT2_N 9

HT_CADOUT1_P 9

HT_CADOUT1_N 9

HT_CADOUT0_P 9

HT_CADOUT0_N 9

HT_CLKOUT1_P 9

HT_CLKOUT1_N 9

HT_CLKOUT0_P 9

HT_CLKOUT0_N 9

HT_CTLOUT1_P 9

HT_CTLOUT1_N 9

HT_CTLOUT0_P 9

HT_CTLOUT0_N 9

B B

L43

L43

FBMJ3216HS800-T/4A/80ohm_1206

FBMJ3216HS800-T/4A/80ohm_1206

A A

Power name

VLDT_A/B

Description Voltage

HyperTransport I/O ring power supply

5

1.2V

VLDT_RUN+1.2V

C20

C20

180p/50V_4

180p/50V_4

12

C17

C17

180p/50V_4

180p/50V_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

PROJECT :

TURION 64 HT I/F

TURION 64 HT I/F

TURION 64 HT I/F

ZH6

ZH6

ZH6

1A

1A

1A

4 33Monday, August 24, 2009

4 33Monday, August 24, 2009

4 33Monday, August 24, 2009

1

C15

C14

C14

4.7u/6.3V_6

4.7u/6.3V_6

4

C15

4.7u/6.3V_6

4.7u/6.3V_6

C19

C19

0.22u/10V_4

0.22u/10V_4

C16

C16

0.22u/10V_4

0.22u/10V_4

12

3

5

(CPU)

Processor DDR2 Memory Interface

+1.8VSUS

D D

R82

C76

C76

DDR II: CMD/CTRL/CLK

DDR II: CMD/CTRL/CLK

Athlon 64 S1

Processor Socket

R82

2K/F_4

2K/F_4

R78

R78

2K/F_4

2K/F_4

C185

C185

0.22u/10V_4

0.22u/10V_4

15-20mil

CPU_M_VREF

C72

VTT_SENSE

0.9V

C72

0.1u/10V_4

0.1u/10V_4

M_A_A15

M_A_A14

M_A_A13

M_A_A12

M_A_A11

M_A_A10

M_A_A9

M_A_A8

M_A_A7

M_A_A6

M_A_A5

M_A_A4

M_A_A3

M_A_A2

M_A_A1

M_A_A0

C43

C43

0.22u/10V_4

0.22u/10V_4

W17

Y10

AE10

AF10

V19

V22

T19

Y26

W24

U23

H26

K19

K20

V24

K24

L20

R19

L19

L22

L21

M19

M20

M24

M22

N22

N21

R21

K22

R20

T22

T20

U20

U21

J22

J24

J23

J20

J21

1000p/50V_4

1000p/50V_4

U19B

U19B

MEMVREF

VTT_SENSE

MEMZN

MEMZP

MA0_CS_L3

MA0_CS_L2

MA0_CS_L1

MA0_CS_L0

MB0_CS_L3

MB0_CS_L2

MB0_CS_L1

MB0_CS_L0

MB_CKE1

MB_CKE0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_BANK2

MA_BANK1

MA_BANK0

MA_RAS_L

MA_CAS_L

MA_WE_L

C61

C61

0.22u/10V_4

0.22u/10V_4

PLACE THEM CLOSE TO

CPU WITHIN 1"

+1.8VSUS

R37

R37

39.2/F_4

39.2/F_4

1 2

C C

R39

R39

39.2/F_4

39.2/F_4

1 2

B B

A A

C70

C167

C167

4.7u/6.3V_6

4.7u/6.3V_6

C70

4.7u/6.3V_6

4.7u/6.3V_6

Power name

VTT

T16T16

M_ZN

M_ZP

M_A_CS#38

M_A_CS#28

M_A_CS#18

M_A_CS#08

M_B_CS#38

M_B_CS#28

M_B_CS#18

M_B_CS#08

M_B_CKE18

M_CKE18

M_CKE08

M_A_A[0..15]8

M_A_BS#28

M_A_BS#18

M_A_BS#08

M_A_RAS#8

M_A_CAS#8

M_A_WE#8

C107

C107

4.7u/6.3V_6

4.7u/6.3V_6

C51

C51

4.7u/6.3V_6

4.7u/6.3V_6

Description Voltage

VTT Power

5

4

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

MA0_CLK_H2

MA0_CLK_L2

MA0_CLK_H1

MA0_CLK_L1

MB0_CLK_H2

MB0_CLK_L2

MB0_CLK_H1

MB0_CLK_L1

MB0_ODT1

MB0_ODT0

MA0_ODT1

MA0_ODT0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_BANK2

MB_BANK1

MB_BANK0

MB_RAS_L

MB_CAS_L

MB_WE_L

+SMDDR_VTERM

C186

C186

0.22u/10V_4

0.22u/10V_4

4

D10

C10

B10

AD10

W10

AC10

AB10

AA10

A10

Y16

AA16

E16

F16

AF18

AF17

A17

A18

W23

W26

V20

U19

J25

J26

W25

L23

L25

U25

L24

M26

L26

N23

N24

N25

N26

P24

P26

T24

K26

T26

U26

U24

V26

U22

M_B_A15

M_B_A14

M_B_A13

M_B_A12

M_B_A11

M_B_A10

M_B_A9

M_B_A8

M_B_A7

M_B_A6

M_B_A5

M_B_A4

M_B_A3

M_B_A2

M_B_A1

M_B_A0

C173

C173

1000p/50V_4

1000p/50V_4

M_CLKOUT0

C58

C58

1.5p/50V_4

1.5p/50V_4

M_CLKOUT0#

M_CLKOUT1

C55

C55

1.5p/50V_4

1.5p/50V_4

M_CLKOUT1#

+SMDDR_VTERM

200mil

M_B_BS#2 8

M_B_BS#1 8

M_B_BS#0 8

M_B_RAS# 8

M_B_CAS# 8

M_B_WE# 8

C52

C52

1000p/50V_4

1000p/50V_4

M_B_CLKOUT0

C74

C74

1.5p/50V_4

1.5p/50V_4

M_B_CLKOUT0#

M_B_CLKOUT1

C67

C67

1.5p/50V_4

1.5p/50V_4

M_B_CLKOUT1#

M_CLKOUT1 8

M_CLKOUT1# 8

M_CLKOUT0 8

M_CLKOUT0# 8

M_B_CLKOUT1 8

M_B_CLKOUT1# 8

M_B_CLKOUT0 8

M_B_CLKOUT0# 8

M_B_ODT1 8

M_B_ODT0 8M_B_CKE08

M_ODT1 8

M_ODT0 8

M_B_A[0..15] 8

C46

C46

1000p/50V_4

1000p/50V_4

M_B_DQS[0..7]8

M_B_DQS#[0..7]8

C48

C48

1000p/50V_4

1000p/50V_4

3

3

M_B_DQ[0..63]8

M_B_DM[0..7]8

C168

C168

180p/50V_4

180p/50V_4

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

C54

C54

180p/50V_4

180p/50V_4

M_B_DQ63

M_B_DQ62

M_B_DQ61

M_B_DQ60

M_B_DQ59

M_B_DQ58

M_B_DQ57

M_B_DQ56

M_B_DQ55

M_B_DQ54

M_B_DQ53

M_B_DQ52

M_B_DQ51

M_B_DQ50

M_B_DQ49

M_B_DQ48

M_B_DQ47

M_B_DQ46

M_B_DQ45

M_B_DQ44

M_B_DQ43

M_B_DQ42

M_B_DQ41

M_B_DQ40

M_B_DQ39

M_B_DQ38

M_B_DQ37

M_B_DQ36

M_B_DQ35

M_B_DQ34

M_B_DQ33

M_B_DQ32

M_B_DQ31

M_B_DQ30

M_B_DQ29

M_B_DQ28

M_B_DQ27

M_B_DQ26

M_B_DQ25

M_B_DQ24

M_B_DQ23

M_B_DQ22

M_B_DQ21

M_B_DQ20

M_B_DQ19

M_B_DQ18

M_B_DQ17

M_B_DQ16

M_B_DQ15

M_B_DQ14

M_B_DQ13

M_B_DQ12

M_B_DQ11

M_B_DQ10

M_B_DQ9

M_B_DQ8

M_B_DQ7

M_B_DQ6

M_B_DQ5

M_B_DQ4

M_B_DQ3

M_B_DQ2

M_B_DQ1

M_B_DQ0

M_B_DQS7

M_B_DQS#7

M_B_DQS6

M_B_DQS#6

M_B_DQS5

M_B_DQS#5

M_B_DQS4

M_B_DQS#4

M_B_DQS3

M_B_DQS#3

M_B_DQS2

M_B_DQS#2

M_B_DQS1

M_B_DQS#1

M_B_DQS0

M_B_DQS#0

C201

C201

180p/50V_4

180p/50V_4

M_B_DM7

M_B_DM6

M_B_DM5

M_B_DM4

M_B_DM3

M_B_DM2

M_B_DM1

M_B_DM0

C106

C106

180p/50V_4

180p/50V_4

AD11

AF11

AF14

AE14

Y11

AB11

AC12

AF13

AF15

AF16

AC18

AF19

AD14

AC14

AE18

AD18

AD20

AC20

AF23

AF24

AF20

AE20

AD22

AC22

AE25

AD26

AA25

AA26

AE24

AD24

AA23

AA24

G24

G23

D26

C26

G26

G25

E24

E23

C24

B24

C20

B20

C25

D24

A21

D20

D18

C18

D14

C14

A20

A19

A16

A15

A13

D12

E11

G11

B14

A14

A11

C11

AD12

AC16

AE22

AB26

AF12

AE12

AE16

AD16

AF21

AF22

AC25

AC26

F26

E26

A24

A23

D16

C16

C12

B12

E25

A22

B16

A12

U19C

U19C

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

2

DDR: DATA

DDR: DATA

Athlon 64 S1

Processor Socket

2

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

1

M_A_DQ63

AA12

M_A_DQ62

AB12

M_A_DQ61

AA14

M_A_DQ60

AB14

M_A_DQ59

W11

M_A_DQ58

Y12

M_A_DQ57

AD13

M_A_DQ56

AB13

M_A_DQ55

AD15

M_A_DQ54

AB15

M_A_DQ53

AB17

M_A_DQ52

Y17

M_A_DQ51

Y14

M_A_DQ50

W14

M_A_DQ49

W16

M_A_DQ48

AD17

M_A_DQ47

Y18

M_A_DQ46

AD19

M_A_DQ45

AD21

M_A_DQ44

AB21

M_A_DQ43

AB18

M_A_DQ42

AA18

M_A_DQ41

AA20

M_A_DQ40

Y20

M_A_DQ39

AA22

M_A_DQ38

Y22

M_A_DQ37

W21

M_A_DQ36

W22

M_A_DQ35

AA21

M_A_DQ34

AB22

M_A_DQ33

AB24

M_A_DQ32

Y24

M_A_DQ31

H22

M_A_DQ30

H20

M_A_DQ29

E22

M_A_DQ28

E21

M_A_DQ27

J19

M_A_DQ26

H24

M_A_DQ25

F22

M_A_DQ24

F20

M_A_DQ23

C23

M_A_DQ22

B22

M_A_DQ21

F18

M_A_DQ20

E18

M_A_DQ19

E20

M_A_DQ18

D22

M_A_DQ17

C19

M_A_DQ16

G18

M_A_DQ15

G17

M_A_DQ14

C17

M_A_DQ13

F14

M_A_DQ12

E14

M_A_DQ11

H17

M_A_DQ10

E17

M_A_DQ9

E15

M_A_DQ8

H15

M_A_DQ7

E13

M_A_DQ6

C13

M_A_DQ5

H12

M_A_DQ4

H11

M_A_DQ3

G14

M_A_DQ2

H14

M_A_DQ1

F12

M_A_DQ0

G12

M_A_DM7

Y13

M_A_DM6

AB16

M_A_DM5

Y19

M_A_DM4

AC24

M_A_DM3

F24

M_A_DM2

E19

M_A_DM1

C15

M_A_DM0

E12

M_A_DQS7

W12

M_A_DQS#7

W13

M_A_DQS6

Y15

M_A_DQS#6

W15

M_A_DQS5

AB19

M_A_DQS#5

AB20

M_A_DQS4

AD23

M_A_DQS#4

AC23

M_A_DQS3

G22

M_A_DQS#3

G21

M_A_DQS2

C22

M_A_DQS#2

C21

M_A_DQS1

G16

M_A_DQS#1

G15

M_A_DQS0

G13

M_A_DQS#0

H13

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

TURION 64 DDRII I/F

TURION 64 DDRII I/F

TURION 64 DDRII I/F

M_A_DQ[0..63] 8

To SODIMM socket A (near)

M_A_DM[0..7] 8

M_A_DQS[0..7] 8

M_A_DQS#[0..7] 8

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

ZH6

ZH6

ZH6

5 33Monday, August 24, 2009

5 33Monday, August 24, 2009

5 33Monday, August 24, 2009

1

1A

1A

1A

5

(CPU)

If AMD SI is not used, the SID pin can be left unconnected and SIC

should have a 300-Ω (±5%) pulldown to VSS.

R31 *300_4R31 *300_4

+1.8VSUS

R29 *300_4R29 *300_4

SB_SCLK314

SB_SDATA314

D D

CPUCLKP3

CPUCLKN3

CPU_PWRGD13

LDT_STOP#11,13

LDT_RST#11,13

C C

R28 *0_4R28 *0_4

R30 *0_4R30 *0_4

C37 3900p/50V_4C37 3900p/50V_4

C32 3900p/50V_4C32 3900p/50V_4

+1.8V

R51

R51

300_4

300_4

R70

R70

300_4

300_4

R59

R59

169/F_6

169/F_6

R52

R52

300_4

300_4

R25 300_4R25 300_4

CPU_SIC_R

CPU_SID_R

VRM_PWRGD17,23,26

CPU_CLKIN_SC_P

Close to CPU 600mil

CPU_CLKIN_SC_N

R50 *SHORT 0 0402R50 *SHORT 0 0402

R69 *SHORT 0 0402R69 *SHORT 0 0402

R53 *SHORT 0 0402R53 *SHORT 0 0402

7/26 change to shortpad

CPU_ALL_PWROK

CPU_LDTSTOP# CPU_TDO

CPU_HT_RESET#

H_THERMTRIP#

+3V_S5

R104

R104

10K_4

10K_4

CPU Thermal monitor(THM)

U2

2ND_MBCLK23

2ND_MBDATA23

2

R41 1K_4R41 1K_4

Q6*2N7002E-LF Q6*2N7002E-LF

+3V

R43

R43

10K_4

10K_4

THERM_ALERT#_R

1

THER_OVERT#

+3V

R47

B B

THERM_ALERT#15

R47

*8.2K_4

*8.2K_4

3

+3V

8

SCLK

7

SDA

6

ALERT#

4

OVERT#

G781P8U2G781P8

ADDRESS: 98H

CPU FAN(THM)

R338 *SHORT 0 0603R338 *SHORT 0 0603

+5V

2

Q20

Q20

MMBT3904

MMBT3904

+5V

A A

THER_OVERT#

CPUFAN#23

5

1 3

4

+1.8VSUS

3

Q5

R24

FDV301NQ5FDV301N

R22

R22

10K_4

10K_4

R21 *0_6R21 *0_6

CPU_TEST27_SINGLECHAIN

CPU_TEST26_BURNIN#

CPU_PRESENT#

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

+3V

R42

R42

200_4

200_4

C22

C22

0.1u/10V_4

0.1u/10V_4

C26

C26

2200p/50V_4

2200p/50V_4

TH_FAN_POWER

C454

C454

0.01u/16V_4

0.01u/16V_4

4

R24

*10K_4

*10K_4

2

1

2

1 3

Q4

MMBT3904Q4MMBT3904

1

VCC

2

DXP

3

DXN

5

GND

<check list>

Layout Note:Routing 10:10 mils and away

from noise source with ground gard

FANSIG23

R336

R336

10K_4

10K_4

FAN_PWM_CN

D5

*BAS316D5*BAS316

R23 100K_6R23 100K_6

SB_THERMTRIP# 14

SYS_SHDN# 25,31

H_THERMDA

H_THERMDC

R36 *300_4R36 *300_4

R33 300_4R33 300_4

R32 *1K/F_4R32 *1K/F_4

R63 510/F_4R63 510/F_4

R67 300_4R67 300_4

R34 *300_4R34 *300_4

R38 *300_4R38 *300_4

R35 *300_4R35 *300_4

R68 *300_4R68 *300_4

R57 *300_4R57 *300_4

R44 *300_4R44 *300_4

R64 510/F_4R64 510/F_4

R61 300_4R61 300_4

R66 300_4R66 300_4

+3V

R337

R337

10K_4

10K_4

FAN CONN

FAN CONN

CN15

CN15

3

2

1

ATHLON Control and Debug

+2.5V

PBY201209T-300Y-N/4A/30ohm_8

PBY201209T-300Y-N/4A/30ohm_8

L4

L4

C21

C21

*100u/6.3V_3528

*100u/6.3V_3528

VLDT_RUN

VCCSENSE26

VSSSENSE26

+1.8VSUS

1

2

5

3

6

4

H_PROCHOT#

C25

C25

4.7u/6.3V_6

4.7u/6.3V_6

T7T7

T6T6

T17T17

T5T5

T4T4

T13T13

T11T11

T10T10

T14T14

T164T164

T21T21

T165T165

T22T22

T33T33

T32T32

T34T34

T20T20

R60

R60

300_4

300_4

3

VDDA_RUN

C23

C23

0.22u/10V_4

0.22u/10V_4

CPU_HT_RESET#

CPU_ALL_PWROK

CPU_LDTSTOP#

CPU_SIC_R

CPU_SID_R

R54 44.2/F_4R54 44.2/F_4

R56 44.2/F_4R56 44.2/F_4

place them to CPU within 1"

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_TEST17_BP3

CPU_TEST16_BP2

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST12_SCANSHIFTENB

H_THERMDC

H_THERMDA

CPU_RSVD_MA0_CLK3_P

CPU_RSVD_MA0_CLK3_N

CPU_RSVD_MA0_CLK0_P

CPU_RSVD_MA0_CLK0_N

CPU_RSVD_MB0_CLK3_P

CPU_RSVD_MB0_CLK3_N

CPU_RSVD_MB0_CLK0_P

CPU_RSVD_MB0_CLK0_N

+1.8VSUS

2

1

Q7

Q7

*HDT@FDV301N

*HDT@FDV301N

+1.8VSUS+1.8VSUS

+3V

R48

R48

10K_4

10K_4

2

13

Q8 MMBT3904Q8 MMBT3904

R58 *SHORT 0 0402R58 *SHORT 0 0402

+3V

3

R55

R55

4.7K_4

4.7K_4

12

C24

C24

3300p/50V_4

3300p/50V_4

CPU_HTREF1

CPU_HTREF0

R40

R40

*HDT@2K/F_4

*HDT@2K/F_4

CPU to HDT RESET#CPU_HT_RESET#

U19D

U19D

F8

VDDA2

F9

VDDA1

B7

RESET_L

A7

PWROK

F10

LDTSTOP_L

AF4

SIC

AF5

SID

P6

HT_REF1

R6

HT_REF0

F6

VDD_FB_H

E6

VDD_FB_L

W9

VDDIO_FB_H

Y9

VDDIO_FB_L

A9

CLKIN_H

A8

CLKIN_L

G10

DBRDY

AA9

TMS

AC9

TCK

AD9

TRST_L

AF9

TDI

E9

TEST25_H

E8

TEST25_L

G9

TEST19

H10

TEST18

AA7

TEST13

C2

TEST9

D7

TEST17

E7

TEST16

F7

TEST15

C7

TEST14

AC8

TEST12

C3

TEST7

AA6

TEST6

W7

TEST5

W8

TEST4

Y6

TEST3

AB6

TEST2

P20

RSVD0

P19

RSVD1

N20

RSVD2

N19

RSVD3

R26

RSVD4

R25

RSVD5

P22

RSVD6

R22

RSVD7

R46 *0_4R46 *0_4

7/26 change to shortpad

THERM_ALERT#

THERMTRIP_L

PROCHOT_L

VID5

VID4

VID3

VID2

VID1

VID0

CPU_PRESENT_L

PSI_L

DBREQ_L

TDO

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

2

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

MISC

MISC

AMD NPT S1 SOCKET Processor Socket

CPU_PROCHOT_SB# 13

H_THERMTRIP#

AF6

H_PROCHOT#

AC7

A5

C6

A6

A4

C5

B5

CPU_PRESENT#

AC6

A3

PSI_L is a Power Status Indicator signal. This signal is asserted

when the processor is in a low powerstate. PSI_L should be

connected to the power supply controller, if the controller

supports “skipmode, or diode emulation mode”. PSI_L is asserted by

the processor during the C3 and S1 states.

CPU_DBREQ#

E10

AE9

CPU_TEST29_H_FBCLKOUT_P

C9

CPU_TEST29_L_FBCLKOUT_N

C8

CPU_TEST24_SCANCLK1

AE7

CPU_TEST23_TSTUPD

AD7

CPU_TEST22_SCANSHIFTEN

AE8

CPU_TEST21_SCANEN

AB8

CPU_TEST20_SCANCLK2

AF7

CPU_TEST28_H_PLLCHRZ_P

J7

CPU_TEST28_L_PLLCHRZ_N

H8

CPU_TEST27_SINGLECHAIN

AF8

CPU_TEST26_BURNIN#

AE6

K8

C4

CPU_MA_RESET#

H16

CPU_MB_RESET#

B18

CPU_RSVD_VIDSTRB1

B3

CPU_RSVD_VIDSTRB0

C1

CPU_RSVD_VDDNB_FB_P

H6

CPU_RSVD_VDDNB_FB_N

G6

CPU_RSVD_CORE_TYPE

D5

R24

W18

R23

AA8

H18

H19

+1.8VSUS

R76 *220_4R76 *220_4

NOTE: HDT TERMINATION IS REQUIRED

FOR REV. Ax SILICON ONLY.

+1.8VSUS+1.8VSUS

R27

R27

300_4

300_4

R75 *220_4R75 *220_4

R45

R45

300_4

300_4

H_VID5 26

H_VID4 26

H_VID3 26

H_VID2 26

H_VID1 26

H_VID0 26

PSI# 26

R49 80.6/F_4R49 80.6/F_4

PLACE IT CLOSE TO CPU WITHIN 1"

ROUTE AS 80 Ohm DIFFERENTIAL PAIR

T15T15

T9T9

T12T12

T18T18

T19T19

T168T168

T166T166

T8T8

T3T3

T167T167

IF no use which Net

need pull-up or down

R73 *220_4R73 *220_4

R74 *220_4R74 *220_4

R72 220_4R72 220_4

HDT CONNECTOR

+1.8VSUS

1 2

3 4

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

C69 *0.1u/10V_4C69 *0.1u/10V_4

Power name

VDDA

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

KEY

KEY

CN2

CN2

*HDT CONN

*HDT CONN

Description Voltage

Filtered PLL supply voltage

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

TURION 64 CTRL & DEBUG

TURION 64 CTRL & DEBUG

TURION 64 CTRL & DEBUG

1

25

CPU to HDT RESET#

ZH6

ZH6

ZH6

6 33Monday, August 24, 2009

6 33Monday, August 24, 2009

6 33Monday, August 24, 2009

2.5V

1A

1A

1A

5

4

3

2

1

PROCESSOR POWER AND GROUND(CPU)

D D

U19F

U19F

AA4

VSS1

AA11

VSS2

AA13

VSS3

AA15

VSS4

AA17

VSS5

AA19

VSS6

AB2

VSS7

AB7

VSS8

AB9

VSS9

AB23

VSS10

AB25

CPU_CORE CPU_CORE

C C

B B

A1

AC4

AD2

K10

K12

K14

L11

L13

M10

N11

P10

R11

T10

T12

T14

U11

U13

V10

U19E

U19E

VDD1

VDD2

G4

VDD3

H2

VDD4

J9

VDD5

J11

VDD6

J13

VDD7

K6

VDD8

VDD9

VDD10

VDD11

L4

VDD12

L7

VDD13

L9

VDD14

VDD15

VDD16

M2

VDD17

M6

VDD18

M8

VDD19

VDD20

N7

VDD21

N9

VDD22

VDD23

P8

VDD24

VDD25

R4

VDD26

R7

VDD27

R9

VDD28

VDD29

T2

VDD30

T6

VDD31

T8

VDD32

VDD33

VDD34

VDD35

U7

VDD36

U9

VDD37

VDD38

VDD39

V6

VDD40

V8

VDD41

VDD42

POWER

POWER

Athlon 64 S1

Processor Socket

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

V12

V14

W4

Y2

J15

K16

L15

M16

P16

T16

U15

V16

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

P18

P21

P23

P25

R17

T18

T21

T23

T25

U17

V18

V21

V23

V25

Y25

+1.8VSUS

A26

AC11

AC13

AC15

AC17

AC19

AC21

AD6

AD8

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

D11

D13

D15

D17

D19

D21

D23

D25

H21

H23

B11

B13

B15

B17

B19

B21

B23

B25

F11

F13

F15

F17

F19

F21

F23

F25

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

B4

VSS28

B6

VSS29

B8

VSS30

B9

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

D6

VSS40

D8

VSS41

D9

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

E4

VSS51

F2

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

H7

VSS61

H9

VSS62

VSS63

VSS64

J4

VSS65

GROUND

GROUND

Athlon 64 S1

Processor Socket

Athlon 64 S1g1

uPGA638

Top View

A A

AF1

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

M11

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

+

+

PC21

PC21

*330u/2V_7343

*330u/2V_7343

+1.8VSUS

+1.8VSUS

+1.8VSUS

BOTTOMSIDE DECOUPLING

CPU_CORE

C53

C33

C33

180p/50V_4

180p/50V_4

C53

10u/6.3V_6

10u/6.3V_6

C38

C38

10u/6.3V_6

10u/6.3V_6

CPU_CORE

C30

C30

10u/6.3V_6

10u/6.3V_6

For EMI request.

C50

C50

0.1u/10V_4

0.1u/10V_4

CPU_CORE

C28

C28

0.22u/10V_4

0.22u/10V_4

C44

C44

10u/6.3V_6

10u/6.3V_6

C27

C27

0.22u/10V_4

0.22u/10V_4

C34

C34

10u/6.3V_6

10u/6.3V_6

C29

C29

0.01u/25V_4

0.01u/25V_4

C56

C56

10u/6.3V_6

10u/6.3V_6

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

C62

C71

C71

4.7u/6.3V_6

4.7u/6.3V_6

C64

C64

0.01u/25V_4

0.01u/25V_4

C77

C77

10u/10V_8

10u/10V_8

C68

C68

4.7u/6.3V_6

4.7u/6.3V_6

C80

C80

180p/50V_4

180p/50V_4

C151

C151

4.7u/6.3V_6

4.7u/6.3V_6

C79

C79

180p/50V_4

180p/50V_4

6/10 remove C36, C60

C66

C57

C57

0.22u/10V_4

0.22u/10V_4

C66

0.22u/10V_4

0.22u/10V_4

C75

C75

0.22u/10V_4

0.22u/10V_4

C62

0.22u/10V_4

0.22u/10V_4

C65

C65

0.22u/10V_4

0.22u/10V_4

C63

C63

0.22u/10V_4

0.22u/10V_4

C409

C409

0.01u/25V_4

0.01u/25V_4

C49

C49

10u/6.3V_6

10u/6.3V_6

C47

C47

0.1u/10V_4

0.1u/10V_4

C73

C73

0.22u/10V_4

0.22u/10V_4

C78

C78

180p/50V_4

180p/50V_4

C41

C41

10u/6.3V_6

10u/6.3V_6

C81

C81

0.22u/10V_4

0.22u/10V_4

C40

C40

10u/6.3V_6

10u/6.3V_6

Power name Description Voltage

VDD

Core power supply

1.05V

VDDIO DDR SDRAM I/O ring power supply 1.8V

5

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

PROJECT :

TURION 64 PWR & GND

TURION 64 PWR & GND

TURION 64 PWR & GND

ZH6

ZH6

ZH6

1A

1A

1A

7 33Monday, August 24, 2009

7 33Monday, August 24, 2009

7 33Monday, August 24, 2009

1

5

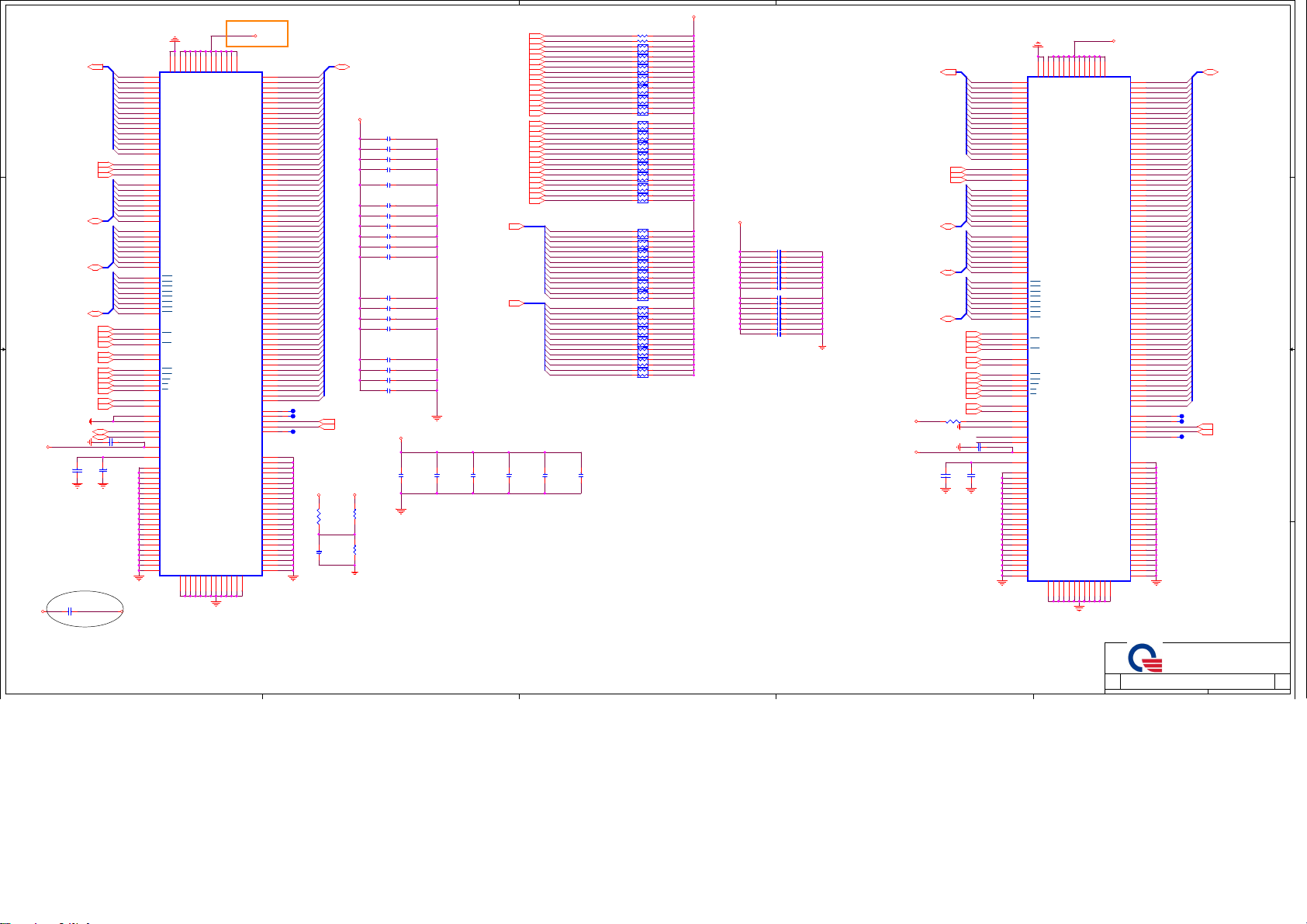

(DDR)

+1.8VSUS

4/14

M_A_A[0..15]5

D D

M_A_BS#05

M_A_BS#15

M_A_BS#25

M_A_DM[0..7]5

C C

B B

A A

M_A_DQS[0..7]5

M_A_DQS#[0..7]5

M_CLKOUT05

M_CLKOUT0#5

M_CLKOUT15

M_CLKOUT1#5

M_CKE05

M_CKE15

M_A_RAS#5

M_A_CAS#5

M_A_WE#5

M_A_CS#05

M_A_CS#15

M_ODT05

M_ODT15

SDATA03,14,20

SCLK03,14,20

+3V

C196

C196

2.2u/10V_8

2.2u/10V_8

1 2

+1.8VSUS MVREF_DIM

C179 *0.1u/10V_4C179 *0.1u/10V_4

C187 0.1u/10V_4C187 0.1u/10V_4

MVREF_DIM

C202

C202

0.1u/10V_4

0.1u/10V_4

MVREF_DIM

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_CLKOUT0

M_CLKOUT0#

M_CLKOUT1

M_CLKOUT1#

SA0_A

SA1_A

SDATA0

SCLK0

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10

90

A11

89

A12

116

A13

86

A14

84

A15

107

BA0

106

BA1

85

BA2

10

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

11

DQS0

29

DQS1

49

DQS2

68

DQS3

129

DQS4

146

DQS5

167

DQS6

186

DQS7

30

CK0

32

CK0

164

CK1

166

CK1

79

CKE0

80

CKE1

108

RAS

113

CAS

109

WE

110

S0

115

S1

114

ODT0

119

ODT1

198

SA0

200

SA1

195

SDA

197

SCL

199

VDDspd

1

VREF

2

VSS0

3

VSS1

8

VSS2

9

VSS3

12

VSS4

15

VSS5

18

VSS6

21

VSS7

24

VSS8

27

VSS9

28

VSS10

33

VSS11

34

VSS12

39

VSS13

40

VSS14

41

VSS15

42

VSS16

47

VSS17

48

VSS18

53

VSS19

54

VSS20

201

202

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

GND PAD0

GND PAD1

SPD Address:0xA0

(H=5.2)

RVS

59

103

111

104

112

117

118

CN14

CN14

M_A_DQ1

5

DQ0

M_A_DQ0

7

DQ1

DQ2

VDD11

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

NC1

NC2

NC3

NC4

NC/TEST

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

DDR2-SODIMM-RVS

DDR2-SODIMM-RVS

132

17

19

4

6

14

16

23

25

35

37

20

22

36

38

43

45

55

57

44

46

56

58

61

63

73

75

62

64

74

76

123

125

135

137

124

126

134

136

141

143

151

153

140

142

152

154

157

159

173

175

158

160

174

176

179

181

189

191

180

182

192

194

50

69

83

120

163

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

M_A_DQ3

M_A_DQ2

M_A_DQ4

M_A_DQ5

M_A_DQ7

M_A_DQ6

M_A_DQ12

M_A_DQ9

M_A_DQ10

M_A_DQ14

M_A_DQ13

M_A_DQ8

M_A_DQ11

M_A_DQ15

M_A_DQ16

M_A_DQ21

M_A_DQ23

M_A_DQ18

M_A_DQ20

M_A_DQ17

M_A_DQ22

M_A_DQ19

M_A_DQ29

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ24

M_A_DQ30

M_A_DQ31

M_A_DQ33

M_A_DQ39

M_A_DQ35

M_A_DQ34

M_A_DQ38

M_A_DQ36

M_A_DQ37

M_A_DQ32

M_A_DQ40

M_A_DQ41

M_A_DQ47

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ42

M_A_DQ52

M_A_DQ49

M_A_DQ55

M_A_DQ54

M_A_DQ48

M_A_DQ53

M_A_DQ50

M_A_DQ51

M_A_DQ61

M_A_DQ57

M_A_DQ63

M_A_DQ62

M_A_DQ56

M_A_DQ60

M_A_DQ58

M_A_DQ59

T57T57

T163T163

T162T162

+SMDDR_VREF +1.8VSUS

M_A_CS#2 5

M_A_CS#3 5

R128

R128

0_6

0_6

MVREF_DIM

C177

C177

1u/6.3V_4

1u/6.3V_4

VDD8

VDD7

VDD9

VDD10

SO-DIMM

SO-DIMM

VSS31

VSS30

VSS29

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

128

127

122

121

4

M_CKE05

M_CKE15

M_A_CS#15

M_ODT15

M_A_CAS#5

C412

C412

*0.1u/10V_4

*0.1u/10V_4

M_A_WE#5

M_ODT05

M_A_CS#35

M_A_CS#05

M_A_BS#05

M_A_BS#25

M_A_CS#25

M_A_A105

M_A_A15

M_A_A135

M_A_RAS#5

M_B_CKE15

M_B_A145

M_B_ODT15

M_B_CS#15

M_B_CAS#5

M_B_A105

M_B_CS#35

M_B_A135

M_B_BS#15

M_B_RAS#5

M_B_CS#25

M_B_CKE05

M_B_BS#05

M_B_WE#5

M_B_CS#05

M_B_ODT05

M_A_A[0..15]5

M_B_A[0..15]5

C161

C161

C194

C194

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

C437

C437

*0.1u/10V_4

*0.1u/10V_4

M_B_A14

M_B_A10

M_B_A0

M_B_A2

M_B_A4

M_B_A6

M_B_A7

M_B_A11

M_B_A5

M_B_A1

M_B_A9

M_B_A3

M_B_BS#2

M_B_A8

M_B_A12

M_B_A15

M_A_A0

M_A_BS#1

M_A_A4

M_A_A2

M_A_A14

M_A_A15

M_A_A12

M_A_A9

M_A_A3

M_A_A6

M_A_A5

M_A_A8

M_A_A7

M_A_A11

C191

C191

0.1u/10V_4

0.1u/10V_4

M_A_DQ[0..63] 5

+1.8VSUS

*10u/10V_8C116 *10u/10V_8C116

*10u/10V_8C137 *10u/10V_8C137

10u/10V_8C142 10u/10V_8C142

10u/10V_8C118 10u/10V_8C118

0.1u/10V_4C190 0.1u/10V_4C190

0.1u/10V_4C163 0.1u/10V_4C163

0.1u/10V_4C417 0.1u/10V_4C417

0.1u/10V_4C192 0.1u/10V_4C192

0.1u/10V_4C189 0.1u/10V_4C189

0.1u/10V_4C165 0.1u/10V_4C165

0.1u/10V_4C162 0.1u/10V_4C162

0.1u/10V_4C418 0.1u/10V_4C418

0.1u/10V_4C193 0.1u/10V_4C193

0.1u/10V_4C188 0.1u/10V_4C188 0.1u/10V_4C171 0.1u/10V_4C171

0.1u/10V_4C425 0.1u/10V_4C425

0.1u/10V_4C426 0.1u/10V_4C426

0.1u/10V_4C416 0.1u/10V_4C416

0.1u/10V_4C411 0.1u/10V_4C411

0.1u/10V_4C414 0.1u/10V_4C414

+1.8VSUS

C413

C413

*0.1u/10V_4

*0.1u/10V_4

R129

R129

*1K/F_4

*1K/F_4

R130

R130

*1K/F_4

*1K/F_4

3

R125 47_4R125 47_4

R127 47_4R127 47_4

RP1 0404-47X2RP1 0404-47X2

1 2

3 4

RP2 0404-47X2RP2 0404-47X2

1 2

3 4

RP8 0404-47X2RP8 0404-47X2

1 2

3 4

RP10 0404-47X2RP10 0404-47X2

1 2

3 4

RP7 0404-47X2RP7 0404-47X2

1 2

3 4

RP3 0404-47X2RP3 0404-47X2

1 2

3 4

RP9 0404-47X2RP9 0404-47X2

1 2

3 4

RP29 0404-47X2RP29 0404-47X2

1 2

3 4

RP15 0404-47X2RP15 0404-47X2

1 2

3 4

RP16 0404-47X2RP16 0404-47X2

1 2

3 4

RP22 0404-47X2RP22 0404-47X2

1 2

3 4

RP24 0404-47X2RP24 0404-47X2

1 2

3 4

RP21 0404-47X2RP21 0404-47X2

1 2

3 4

RP17 0404-47X2RP17 0404-47X2

1 2

3 4

RP23 0404-47X2RP23 0404-47X2

1 2

3 4

RP11 0404-47X2RP11 0404-47X2

1 2

3 4

RP12 0404-47X2RP12 0404-47X2

1 2

3 4

RP14 0404-47X2RP14 0404-47X2

1 2

3 4

RP6 0404-47X2RP6 0404-47X2

1 2

3 4

RP4 0404-47X2RP4 0404-47X2

1 2

3 4

1 2

3 4

RP13 0404-47X2RP13 0404-47X2

1 2

3 4

RP25 0404-47X2RP25 0404-47X2

1 2

3 4

RP26 0404-47X2RP26 0404-47X2

1 2

3 4

RP27 0404-47X2RP27 0404-47X2

1 2

3 4

RP18 0404-47X2RP18 0404-47X2

1 2

3 4

RP19 0404-47X2RP19 0404-47X2

1 2

3 4

RP20 0404-47X2RP20 0404-47X2

1 2

3 4

RP28 0404-47X2RP28 0404-47X2

1 2

3 4

+SMDDR_VTERM

+SMDDR_VTERM

2

M_B_A[0..15]5 M_B_DQ[0..63] 5

M_B_BS#05

M_B_BS#15

M_B_BS#25

M_B_DM[0..7]5

0.1u/10V_4C208 0.1u/10V_4C208

0.1u/10V_4C199 0.1u/10V_4C199

0.1u/10V_4C211 0.1u/10V_4C211

0.1u/10V_4C174 0.1u/10V_4C174

0.1u/10V_4C197 0.1u/10V_4C197

0.1u/10V_4C200 0.1u/10V_4C200

0.1u/10V_4C209 0.1u/10V_4C209RP5 0404-47X2RP5 0404-47X2

0.1u/10V_4C210 0.1u/10V_4C210

0.1u/10V_4C183 0.1u/10V_4C183

0.1u/10V_4C184 0.1u/10V_4C184

0.1u/10V_4C181 0.1u/10V_4C181

0.1u/10V_4C172 0.1u/10V_4C172

0.1u/10V_4C198 0.1u/10V_4C198

0.1u/10V_4C182 0.1u/10V_4C182

0.1u/10V_4C180 0.1u/10V_4C180

M_B_DQS[0..7]5

M_B_DQS#[0..7]5

M_B_CLKOUT05

M_B_CLKOUT0#5

M_B_CLKOUT15

M_B_CLKOUT1#5

M_B_CKE05

M_B_CKE15

M_B_RAS#5

M_B_CAS#5

M_B_WE#5

M_B_CS#05

M_B_CS#15

M_B_ODT05

M_B_ODT15

R126 10K_4R126 10K_4

+3V

+3V

C195

C195

2.2u/10V_8

2.2u/10V_8

C175 0.1u/10V_4C175 0.1u/10V_4

1 2

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

SA0_B

SA1_B

SDATA0

SCLK0

MVREF_DIM

C203

C203

0.1u/10V_4

0.1u/10V_4

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10

90

A11

89

A12

116

A13

86

A14

84

A15

107

BA0

106

BA1

85

BA2

10

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

11

DQS0

29

DQS1

49

DQS2

68

DQS3

129

DQS4

146

DQS5

167

DQS6

186

DQS7

30

CK0

32

CK0

164

CK1

166

CK1

79

CKE0

80

CKE1

108

RAS

113

CAS

109

WE

110

S0

115

S1

114

ODT0

119

ODT1

198

SA0

200

SA1

195

SDA

197

SCL

199

VDDspd

1

VREF

2

VSS0

3

VSS1

8

VSS2

9

VSS3

12

VSS4

15

VSS5

18

VSS6

21

VSS7

24

VSS8

27

VSS9

28

VSS10

33

VSS11

34

VSS12

39

VSS13

40

VSS14

41

VSS15

42

VSS16

47

VSS17

48

VSS18

53

VSS19

54

VSS20

201

202

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

GND PAD0

GND PAD1

SPD Address:0xA1

(H=5.2)

STD

59

103

111

104

112

117

118

VDD8

VDD7

VDD9

VDD10

VDD11

NC/TEST

SO-DIMM

SO-DIMM

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

VSS30

VSS29

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

132

128

127

122

121

+1.8VSUS

CN13

CN13

5

DQ0

7

DQ1

17

DQ2

19

DQ3

4

DQ4

6

DQ5

14

DQ6

16

DQ7

23

DQ8

25

DQ9

35

DQ10

37

DQ11

20

DQ12

22

DQ13

36

DQ14

38

DQ15

43

DQ16

45

DQ17

55

DQ18

57

DQ19

44

DQ20

46

DQ21

56

DQ22

58

DQ23

61

DQ24

63

DQ25

73

DQ26

75

DQ27

62

DQ28

64

DQ29

74

DQ30

76

DQ31

123

DQ32

125

DQ33

135

DQ34

137

DQ35

124

DQ36

126

DQ37

134

DQ38

136

DQ39

141

DQ40

143

DQ41

151

DQ42

153

DQ43

140

DQ44

142

DQ45

152

DQ46

154

DQ47

157

DQ48

159

DQ49

173

DQ50

175

DQ51

158

DQ52

160

DQ53

174

DQ54

176

DQ55

179

DQ56

181

DQ57

189

DQ58

191

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

50

NC1

69

NC2

83

NC3

120

NC4

163

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

DDR2-SODIMM-STD

DDR2-SODIMM-STD

M_B_DQ4

M_B_DQ5

M_B_DQ2

M_B_DQ3

M_B_DQ0

M_B_DQ1

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ14

M_B_DQ13

M_B_DQ12

M_B_DQ15

M_B_DQ11

M_B_DQ23

M_B_DQ19

M_B_DQ21

M_B_DQ16

M_B_DQ17

M_B_DQ22

M_B_DQ20

M_B_DQ18

M_B_DQ25

M_B_DQ24

M_B_DQ30

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ31

M_B_DQ26

M_B_DQ32

M_B_DQ36

M_B_DQ39

M_B_DQ34

M_B_DQ33

M_B_DQ37

M_B_DQ38

M_B_DQ35

M_B_DQ40

M_B_DQ44

M_B_DQ46

M_B_DQ42

M_B_DQ41

M_B_DQ45

M_B_DQ47

M_B_DQ43

M_B_DQ52

M_B_DQ49

M_B_DQ54

M_B_DQ55

M_B_DQ48

M_B_DQ53

M_B_DQ50

M_B_DQ51

M_B_DQ61

M_B_DQ57

M_B_DQ62

M_B_DQ63

M_B_DQ60

M_B_DQ56

M_B_DQ58

M_B_DQ59

1

T64T64

T59T59

M_B_CS#2 5

M_B_CS#3 5

T58T58

8/26 Remove

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

PROJECT :

DDRII SODIMM X 2

DDRII SODIMM X 2

DDRII SODIMM X 2

1

ZH6

ZH6

ZH6

1A

1A

1A

8 33Wednesday, August 26, 2009

8 33Wednesday, August 26, 2009

8 33Wednesday, August 26, 2009

5

RS780(CLG)

D D

C C

HT_CADOUT0_P4

HT_CADOUT0_N4

HT_CADOUT1_P4

HT_CADOUT1_N4

HT_CADOUT2_P4

HT_CADOUT2_N4

HT_CADOUT3_P4

HT_CADOUT3_N4

HT_CADOUT4_P4

HT_CADOUT4_N4

HT_CADOUT5_P4

HT_CADOUT5_N4

HT_CADOUT6_P4

HT_CADOUT6_N4

HT_CADOUT7_P4

HT_CADOUT7_N4

HT_CADOUT8_P4

HT_CADOUT8_N4

HT_CADOUT9_P4

HT_CADOUT9_N4

HT_CADOUT10_P4

HT_CADOUT10_N4

HT_CADOUT11_P4

HT_CADOUT11_N4

HT_CADOUT12_P4

HT_CADOUT12_N4

HT_CADOUT13_P4

HT_CADOUT13_N4

HT_CADOUT14_P4

HT_CADOUT14_N4

HT_CADOUT15_P4

HT_CADOUT15_N4

HT_CLKOUT0_P4

HT_CLKOUT0_N4

HT_CLKOUT1_P4

HT_CLKOUT1_N4

HT_CTLOUT0_P4

HT_CTLOUT0_N4

HT_CTLOUT1_P4

HT_CTLOUT1_N4

R98 301/F_4R98 301/F_4

4

U18A

U18A

Y25

HT_RXCAD0P

Y24

HT_RXCAD0N

V22

HT_RXCAD1P

V23

HT_RXCAD1N

V25

HT_RXCAD2P

V24

HT_RXCAD2N

U24

HT_RXCAD3P

U25

HT_RXCAD3N

T25

HT_RXCAD4P

T24

HT_RXCAD4N

P22

HT_RXCAD5P

P23

HT_RXCAD5N

P25

HT_RXCAD6P

P24

HT_RXCAD6N

N24

HT_RXCAD7P

N25

HT_RXCAD7N

AC24

HT_RXCAD8P

AC25

HT_RXCAD8N

AB25

HT_RXCAD9P

AB24

HT_RXCAD9N

AA24

HT_RXCAD10P

AA25

HT_RXCAD10N

Y22

HT_RXCAD11P

Y23

HT_RXCAD11N

W21

HT_RXCAD12P

W20

HT_RXCAD12N

V21

HT_RXCAD13P

V20

HT_RXCAD13N

U20

HT_RXCAD14P

U21

HT_RXCAD14N

U19

HT_RXCAD15P

U18

HT_RXCAD15N

T22

HT_RXCLK0P

T23

HT_RXCLK0N

AB23

HT_RXCLK1P

AA22

HT_RXCLK1N

M22

HT_RXCTL0P

M23

HT_RXCTL0N

R21

HT_RXCTL1P

R20

HT_RXCALP HT_TXCALP

HT_RXCALN

C23

A24

HT_RXCTL1N

HT_RXCALP

HT_RXCALN

RS780MN

RS780MN

PART 1 OF 6

PART 1 OF 6

HYPER TRANSPORT CPU I/F

HYPER TRANSPORT CPU I/F

HT_TXCAD0P

HT_TXCAD0N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD15P

HT_TXCAD15N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCTL0P

HT_TXCTL0N

HT_TXCTL1P

HT_TXCTL1N

HT_TXCALP

HT_TXCALN

D24

D25

E24

E25

F24

F25

F23

F22

H23

H22

J25

J24

K24

K25

K23

K22

F21

G21

G20

H21

J20

J21

J18

K17

L19

J19

M19

L18

M21

P21

P18

M18

H24

H25

L21

L20

M24

M25

P19

R18

B24

B25

3

HT_TXCALN

R101 301/F_4R101 301/F_4

HT_CADIN0_P 4

HT_CADIN0_N 4

HT_CADIN1_P 4

HT_CADIN1_N 4

HT_CADIN2_P 4

HT_CADIN2_N 4

HT_CADIN3_P 4

HT_CADIN3_N 4

HT_CADIN4_P 4

HT_CADIN4_N 4

HT_CADIN5_P 4

HT_CADIN5_N 4

HT_CADIN6_P 4

HT_CADIN6_N 4

HT_CADIN7_P 4

HT_CADIN7_N 4

HT_CADIN8_P 4

HT_CADIN8_N 4

HT_CADIN9_P 4

HT_CADIN9_N 4

HT_CADIN10_P 4

HT_CADIN10_N 4

HT_CADIN11_P 4

HT_CADIN11_N 4

HT_CADIN12_P 4

HT_CADIN12_N 4

HT_CADIN13_P 4

HT_CADIN13_N 4

HT_CADIN14_P 4

HT_CADIN14_N 4

HT_CADIN15_P 4

HT_CADIN15_N 4

HT_CLKIN0_P 4

HT_CLKIN0_N 4

HT_CLKIN1_P 4

HT_CLKIN1_N 4

HT_CTLIN0_P 4

HT_CTLIN0_N 4

HT_CTLIN1_P 4

HT_CTLIN1_N 4

2

signals RS780 RX780

HT_TXCALP

HT_TXCALN

HT_RXCALP

HT_RXCALN

R2364

301 ohm 1%

R2365

301 ohm 1%

R2364

1.21k ohm 1%

R2365

1.21k ohm 1%

1

RS780(CLG)

SIDE-PORT Reserved

SPM(CLG)

This block is for UMA RS780 only , RX780 NC

U18D

U18D

VMA_MA0

VMA_MA1

VMA_MA2

VMA_MA3

VMA_MA4

VMA_MA5

VMA_MA6

VMA_MA7

VMA_MA8

VMA_MA9

B B

T50T50

+1.8V_SPM

A A

VMA_MA10

VMA_MA11

VMA_MA12

VMA_BA0

VMA_BA1

VMA_BA2

VMA_RAS#

VMA_CAS#

VMA_WE#

VMA_CS0#

VMA_CKE

VMA_ODT

VMA_CLK0

VMA_CLK0#

R11940.2/F_4 R11940.2/F_4

R12040.2/F_4 R12040.2/F_4

+1.8V_SPM

5

MEM_COMPN

MEM_COMPP

R115

R115

1K/F_4

1K/F_4

R114

R114

1K/F_4

1K/F_4

AB12

AE16

V11

AE15

AA12

AB16

AB14

AD14

AD13

AD15

AC16

AE13

AC14

Y14

AD16

AE17

AD17

W12

Y12

AD18

AB13

AB18

V14

V15

W14

AE12

AD12

MEM_VREF1

C147

C147

0.1u/10V_4

0.1u/10V_4

MEM_A0(NC)

MEM_A1(NC)

MEM_A2(NC)

MEM_A3(NC)

MEM_A4(NC)

MEM_A5(NC)

MEM_A6(NC)

MEM_A7(NC)

MEM_A8(NC)

MEM_A9(NC)

MEM_A10(NC)

MEM_A11(NC)

MEM_A12(NC)

MEM_A13(NC)

MEM_BA0(NC)

MEM_BA1(NC)

MEM_BA2(NC)

MEM_RASb(NC)

MEM_CASb(NC)

MEM_WEb(NC)

MEM_CSb(NC)

MEM_CKE(NC)

MEM_ODT(NC)

MEM_CKP(NC)

MEM_CKN(NC)

MEM_COMPP(NC)

MEM_COMPN(NC)

RS780MN

RS780MN

PAR 4 OF 6

PAR 4 OF 6

MEM_DQ0/DVO_VSYNC(NC)

MEM_DQ1/DVO_HSYNC(NC)

MEM_DQ2/DVO_DE(NC)

MEM_DQ3/DVO_D0(NC)

MEM_DQ4(NC)

MEM_DQ5/DVO_D1(NC)

MEM_DQ6/DVO_D2(NC)

MEM_DQ7/DVO_D4(NC)

MEM_DQ8/DVO_D3(NC)

MEM_DQ9/DVO_D5(NC)

MEM_DQ10/DVO_D6(NC)

MEM_DQ11/DVO_D7(NC)

MEM_DQ12(NC)

MEM_DQ13/DVO_D9(NC)

MEM_DQ14/DVO_D10(NC)

MEM_DQ15/DVO_D11(NC)

MEM_DQS0P/DVO_IDCKP(NC)

MEM_DQS0N/DVO_IDCKN(NC)

MEM_DQS1P(NC)

MEM_DQS1N(NC)

MEM_DM0(NC)

MEM_DM1/DVO_D8(NC)

SBD_MEM/DVO_I/F

SBD_MEM/DVO_I/F

IOPLLVDD18

IOPLLVDD11

IOPLLVDD18(NC)

IOPLLVDD(NC)

IOPLLVSS(NC)

MEM_VREF(NC)

C154

C154

4.7u/6.3V_6

4.7u/6.3V_6

VMA_DQ0

AA18

VMA_DQ1

AA20

VMA_DQ2

AA19

VMA_DQ3

Y19

VMA_DQ4

V17

VMA_DQ5

AA17

VMA_DQ6

AA15

VMA_DQ7

Y15

VMA_DQ8

AC20

VMA_DQ9

AD19

VMA_DQ10

AE22