Page 1

5

Dr-Bios.com

D D

C C

4

3

2

1

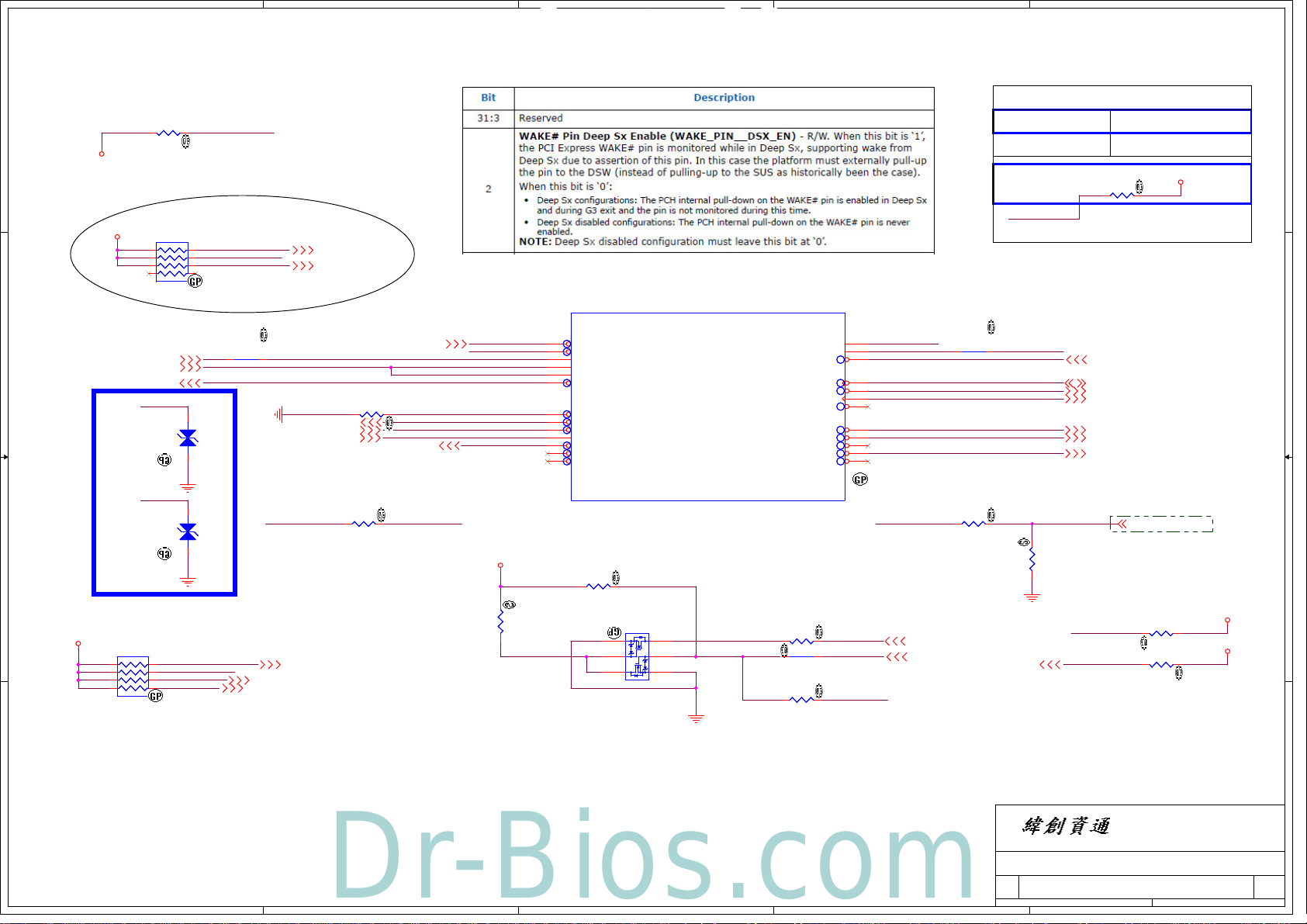

/0,,12/32456

!"#$%&'(")*+,"-%$.'

B B

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

Brook_BH

Brook_BH

Brook_BH

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

5

4

3

A4

Date: Sheet

Date: Sheet

Date: Sheet of

application without get Wistron permission

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Cover Page

Cover Page

Cover Page

Brook_BH

Brook_BH

Wednesday, February 04, 2015

Wednesday, February 04, 2015

Wednesday, February 04, 2015

2

Brook_BH

1 106

of

1 106

of

1 106

1

-1M

-1M

-1M

Page 2

5

Dr-Bios.com

4

3

2

1

D3ACP@C

3?AJ<<<:

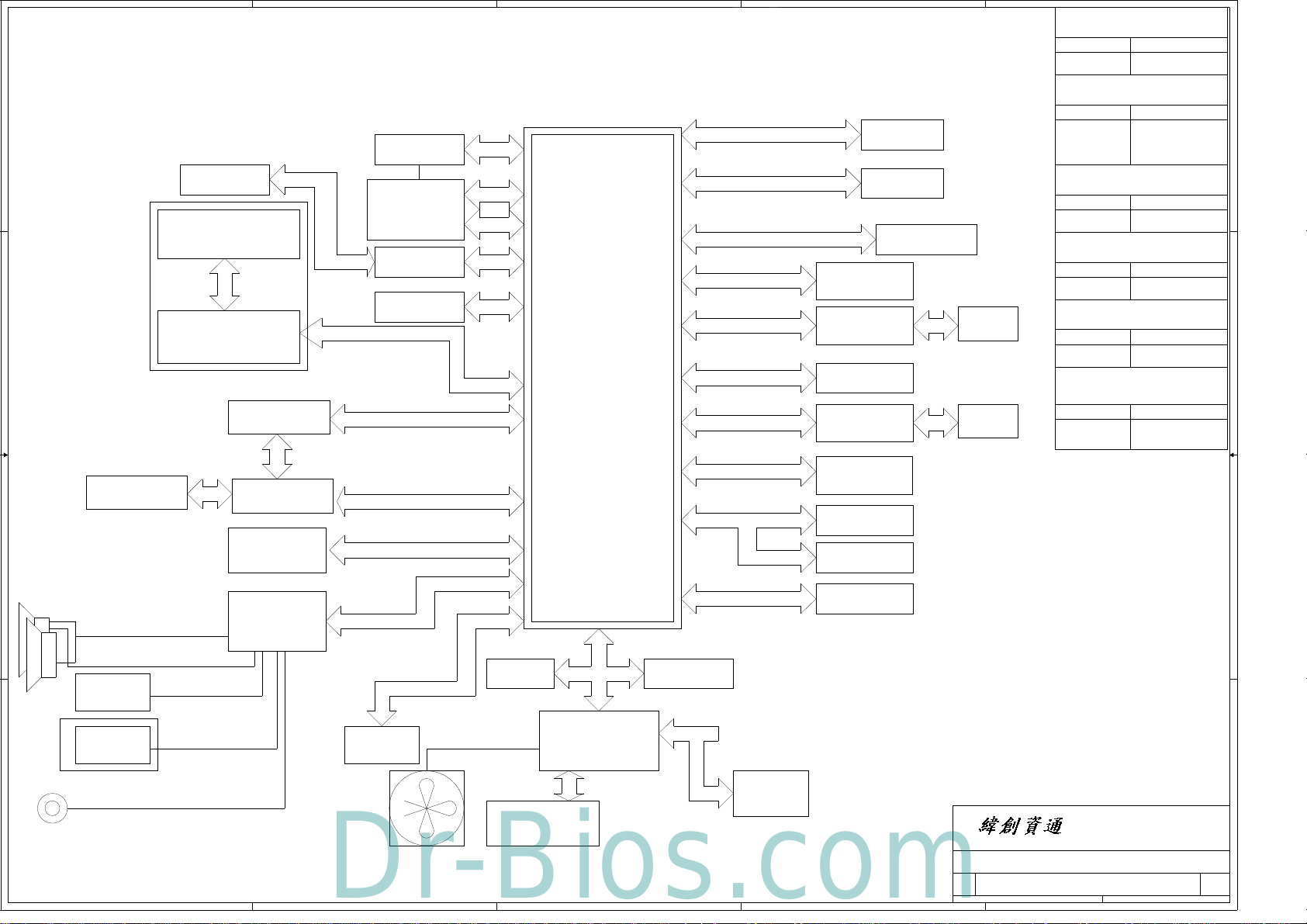

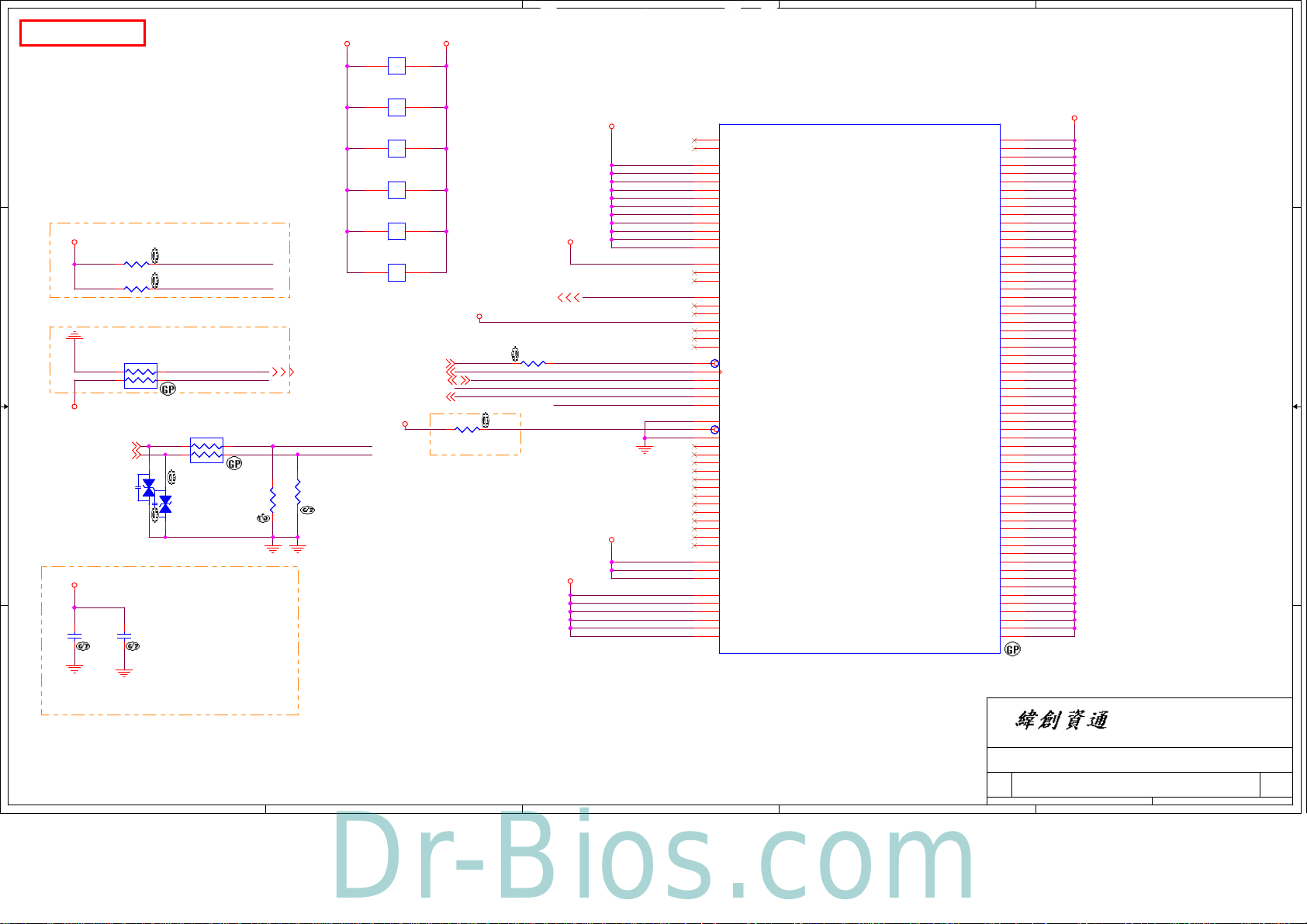

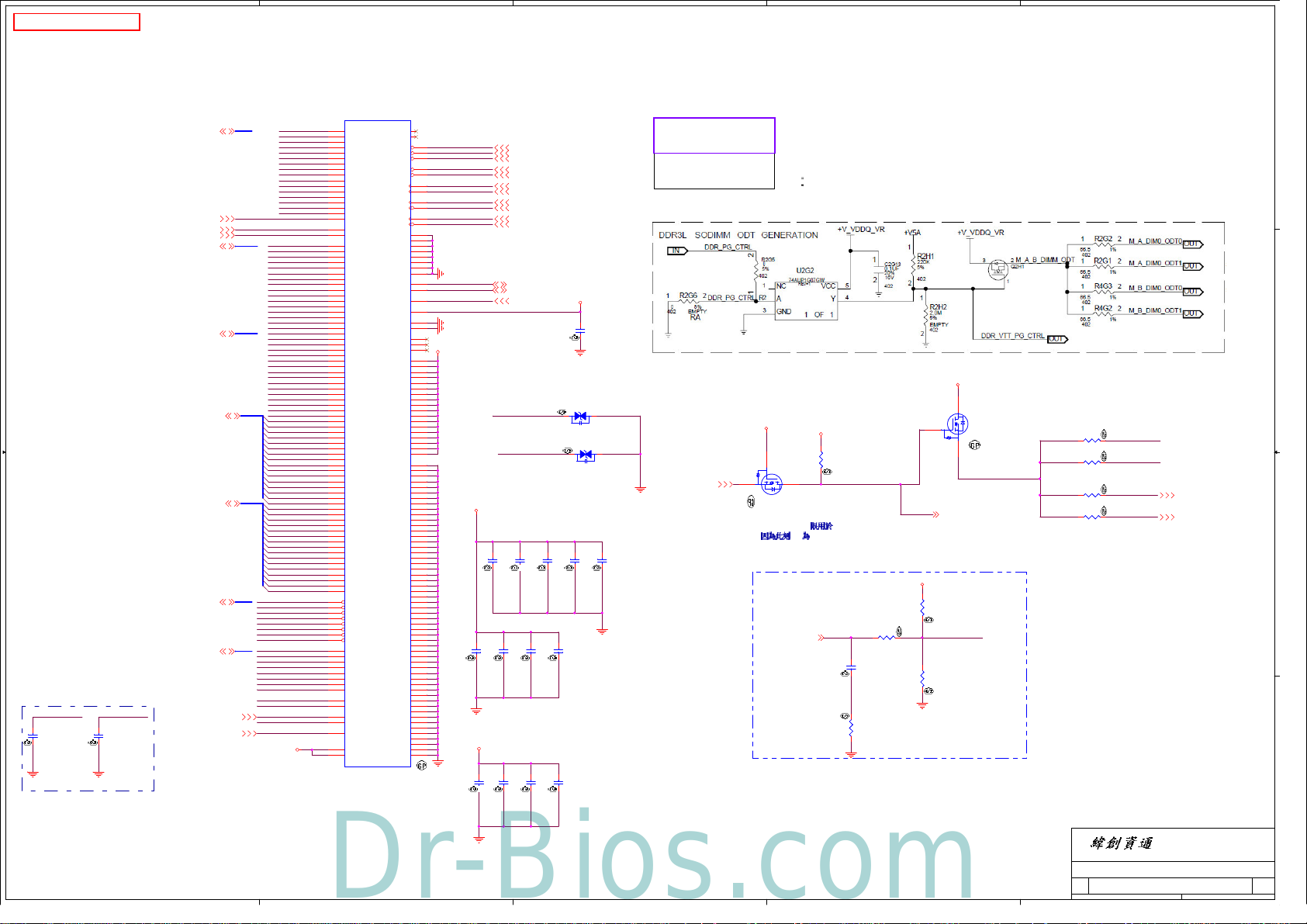

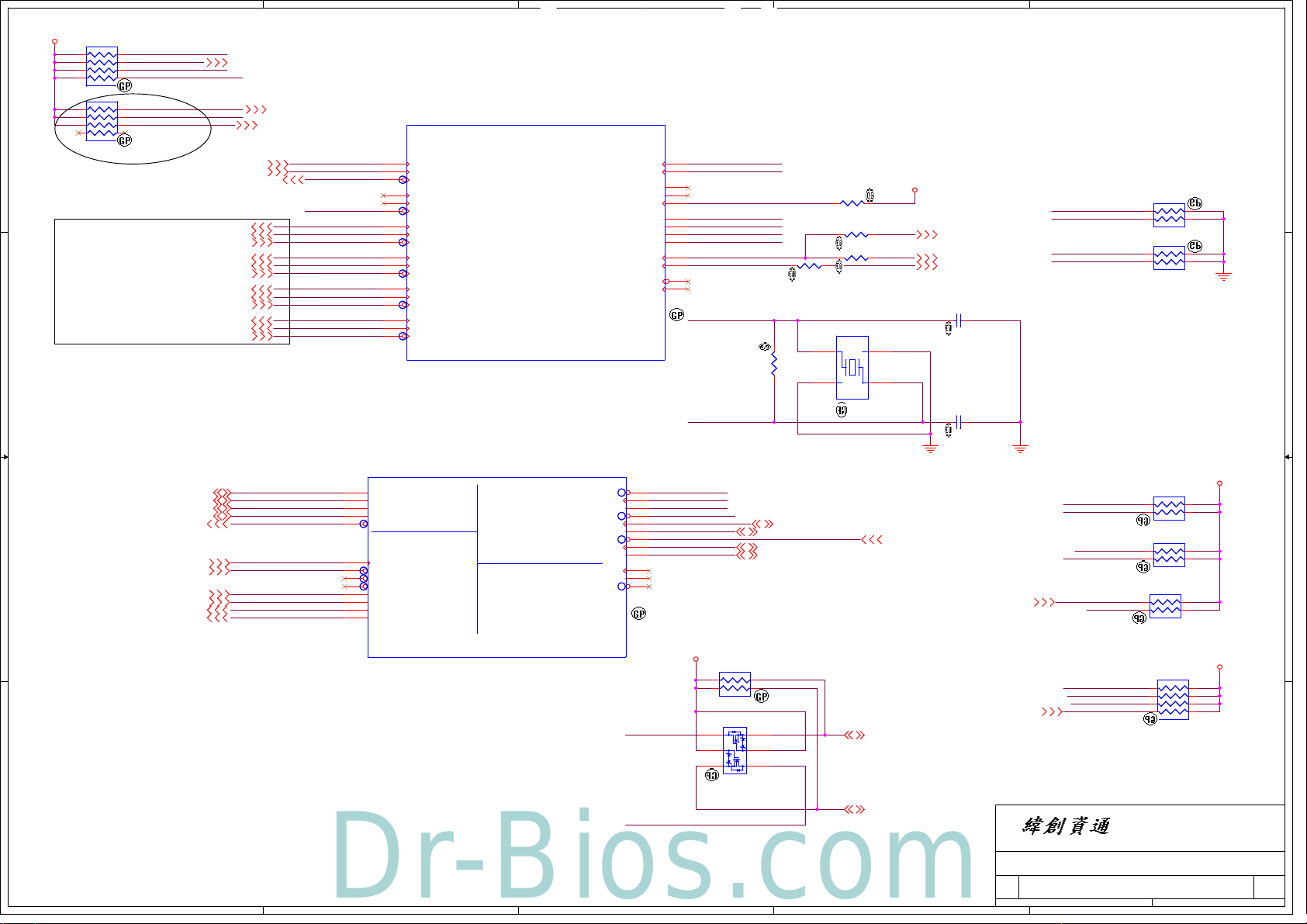

BROOK ULT Board Block Diagram

Project code : 4PD04X010001

PCB P/N : 14276

Revision : -1M

NF?46!

+D/A6E46

!L!6@M*+DQ+D

E46?46!

C679;9/

D D

LCD

CRT PORT

VRAM

DDR3 1500 4Gb

97

4

I>HI:

DDR3

Touch Panel

DP TO VGA

HDMI 1.4b

GPU

C C

N16S-GT-B-A2

;7HIJ

PCIE TO USB

UPD720202

8;

PCIe x 4, DDI

PCIE x 1

99

USB2.0x1

97

9;

eDPx4

I2C x1

DP

HDMI

Intel CPU

Haswell/Broadwell U

15W/28W, GT2/GT3

USB 3.0/2.0 ports (6)

ETHERNET (10/100/1000Mb)

High Definition Audio

SATA ports (3)

PCIe ports (6)

LPC I/F

DDR3L 1333/1600 Channel A

DDR3L 1333/1600 Channel B

USB2.0 x 2

USB3.0 x 1

USB3.0 x 1

PCIe / USB2.0

PCIe x 1

DIM1

DIM2

USB3.0 x 1

USB3.0 x 1

WLAN + BT

(NGFF)

LAN

RTL8111G(S)

><

>8

USB2.0 x 2

89

89

7>

8>

79

USB Charger

TPS2544

RJ45

87

8<

NF?46!

+D/A6E46

D?4*+DQ+D

C679;9/

NF?46!

+D/A6E46

!L!6@M*+DQ+D

6?!9>;>7

NF?46!

+D/A6E46

!L!6@M*+DQ+D

C6I<8>

NF?46!

+D/A6E46

!L!6@M*5+E

!>88=J+>9

NF?46!

8+8K2!9

E46?46!

9K2!9

8+8K2!9

E46?46!

KDD2DEC@

E46?46!

>+J9K2!J

E46?46!

>+89K2!8

E46?46!

>+8K2!9

::

/6O

:9

:7H:;

:I

:=

9>

SATA/ PCIe x 4

3D Camera

(optional)

B B

!?@AB@C

<=

8I

DMIC

<=

DMIC

<=

DEF/E*GADB

A A

<=

USB Redrvier

TPS2544RTER

CardReader

RTS5170

HD Audio Codec

ALC255

8I

78

<;

USB3.0 x 1

USB2.0 x1

SPI Flash

8MB

SATA x 2

HDA

SPI

TPM

NPCT650

LPC BUS

=>

LPC debug port

KBC

<9

KB9028QA

<:

I2C/PS2

7I

SMBus

Charger

HPA02224

Keyboard

79

25

FAN

5

4

3

mSATA

(NGFF)

HDD

SATA3.0

ODD

Touch PAD (PTP)

::

78

7:

7:

79

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

Brook_BH

Brook_BH

Brook_BH

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

application without get Wistron permission

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Block Diagram

Block Diagram

Block Diagram

Brook_BH

Brook_BH

Wednesday, February 04, 2015

Wednesday, February 04, 2015

Wednesday, February 04, 2015

Brook_BH

2 106

2 106

2 106

1

-1M

-1M

-1M

Page 3

5

D

C

B

A

Dr-Bios.com

4

3

2

1

D

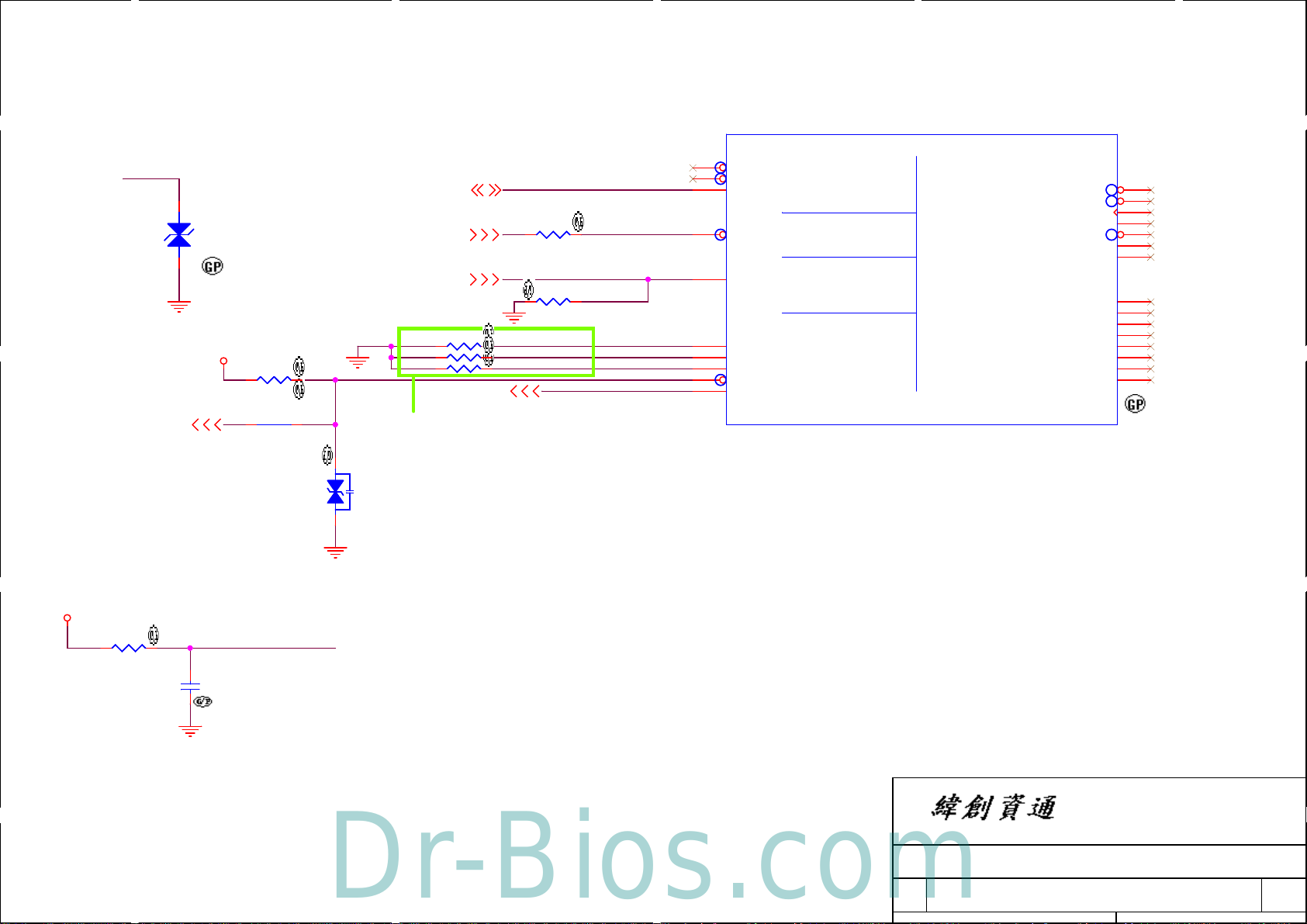

H_CPUPWRGD

12

EC401

EC401

AZ5325-01FDR7G-GP

AZ5325-01FDR7G-GP

DY

DY

C

DDR3_DRAMRST#12,13

1D35V_CPU_VDDQ_S3

R420

R420

1 2

470R2F-GP

470R2F-GP

1 2

0R0402-PAD-1-GP

0R0402-PAD-1-GP

R402

R402

PECI_EC24

R413

PROCHOT#_CPU24,44,46

H_CPUPWRGD89

1 2

R406 200R2F-L1-GPR406 200R2F-L1-GP

1 2

R407 120R2F-GPR407 120R2F-GP

1 2

R408 100R2F-L1-GP-UR408 100R2F-L1-GP-U

1 2

DDR_PG_CTRL12

R413

56R2J-L1-GP

56R2J-L1-GP

R403

R403

10KR2J-L-GP

10KR2J-L-GP

PROCHOT#_CPU_R

12

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

SM_DRAMRST#

Layout Note:

1. SM_RCOMP trace width=12~15mil

CPU1B

CPU1B

D61

PROC_DETECT#

K61

CATERR#

N62

PECI

K63

PROCHOT#

C61

PROCPWRGD

AU60

SM_RCOMP0

AV60

SM_RCOMP1

AU61

SM_RCOMP2

AV15

SM_DRAMRST#

AV61

SM_PG_CNTL1

HASWELL-6-GP-U

HASWELL-6-GP-U

MISC

MISC

THERMAL

THERMAL

PWR

PWR

DDR3L

DDR3L

HSW_ULT_DDR3L

HSW_ULT_DDR3L

JTAG

JTAG

2 OF 19

2 OF 19

PRDY#

PREQ#

PROC_TCK

PROC_TMS

PROC_TRST#

PROC_TDI

PROC_TDO

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

J62

K62

E60

E61

E59

F63

F62

J60

H60

H61

H62

K59

H63

K60

J61

2. Isolation Spacing: 20mil

EC404

TVL-0402-01-AB1-1-GP

TVL-0402-01-AB1-1-GP

EC404

1 2

3. Total trace length<500mil

B

1D05V_S0

1 2

R401

R401

62R2J-GP

62R2J-GP

12

C402

C402

SC47P50V2JN-3GP

SC47P50V2JN-3GP

PROCHOT#_CPU

A

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

Brook_BH

Brook_BH

Brook_BH

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet of

Date: Sheet of

Date: Sheet of

application without get Wistron permission

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CPU (THERMAL/CLOCK/PM)

CPU (THERMAL/CLOCK/PM)

CPU (THERMAL/CLOCK/PM)

Brook_BH

Brook_BH

Wednesday, February 04, 2015

Wednesday, February 04, 2015

Wednesday, February 04, 2015

Brook_BH

4 106

4 106

4 106

-1M

-1M

-1M

Page 4

5

Dr-Bios.com

4

3

2

1

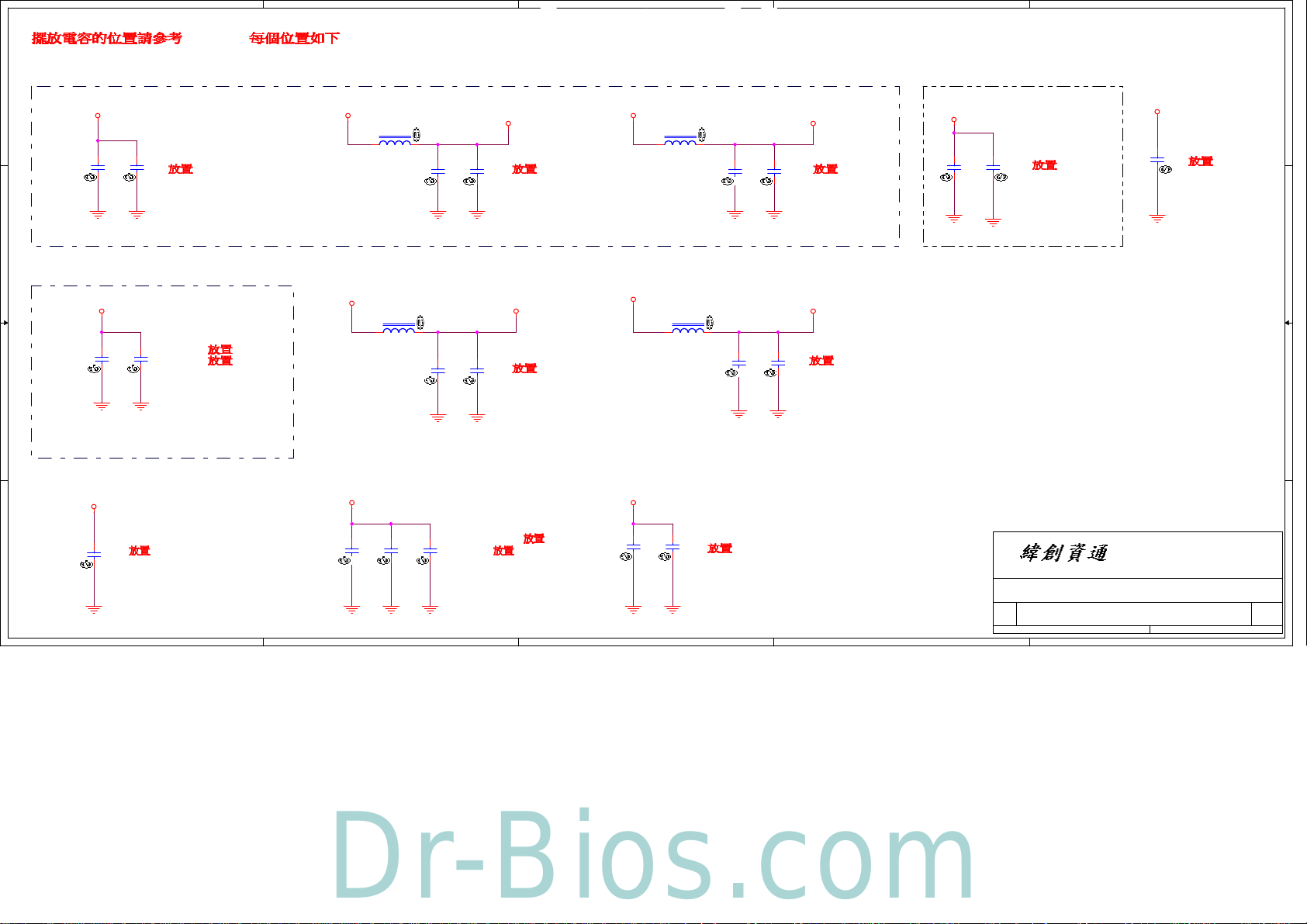

!!N+*R*D?4

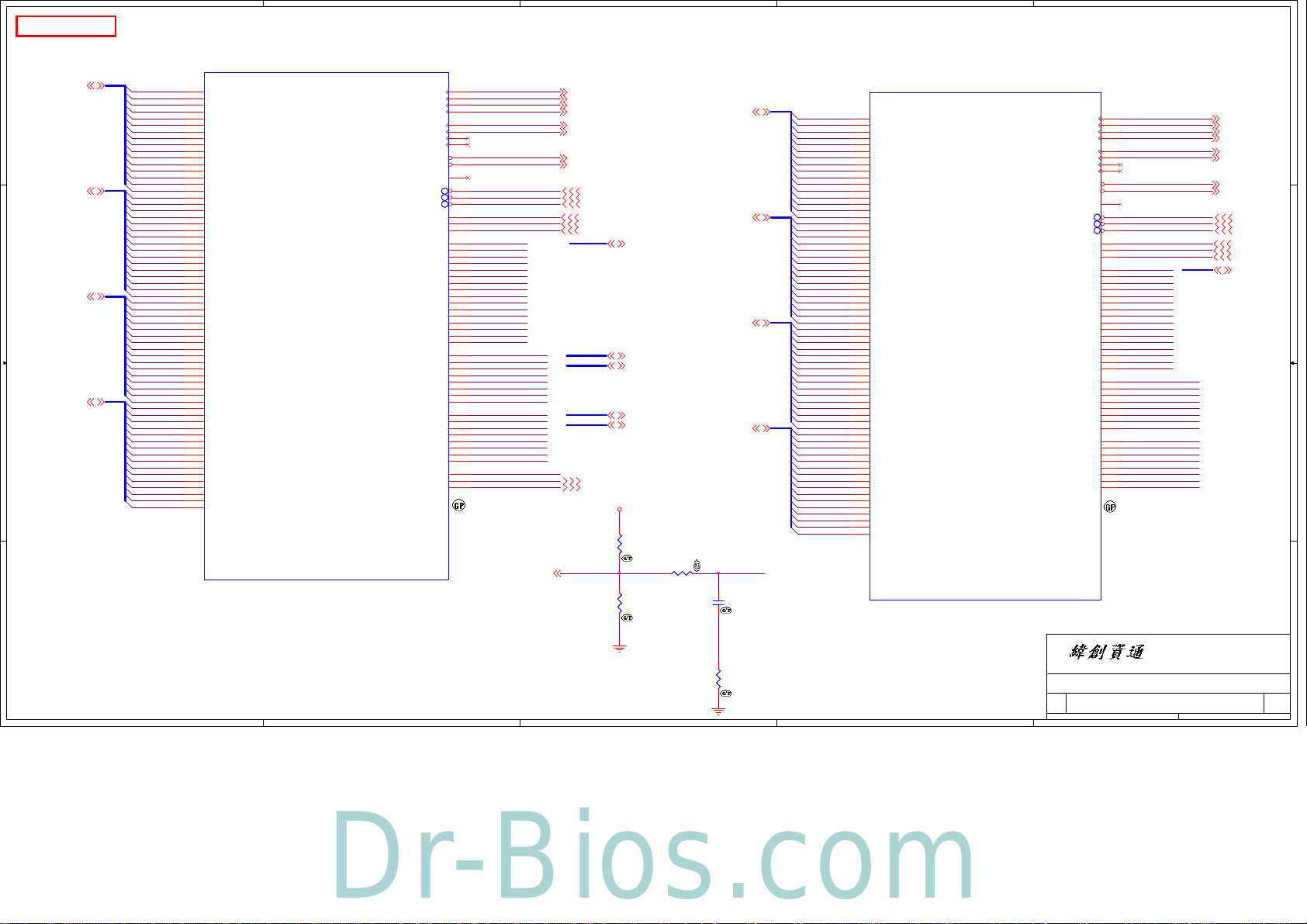

HSW_ULT_DDR3L

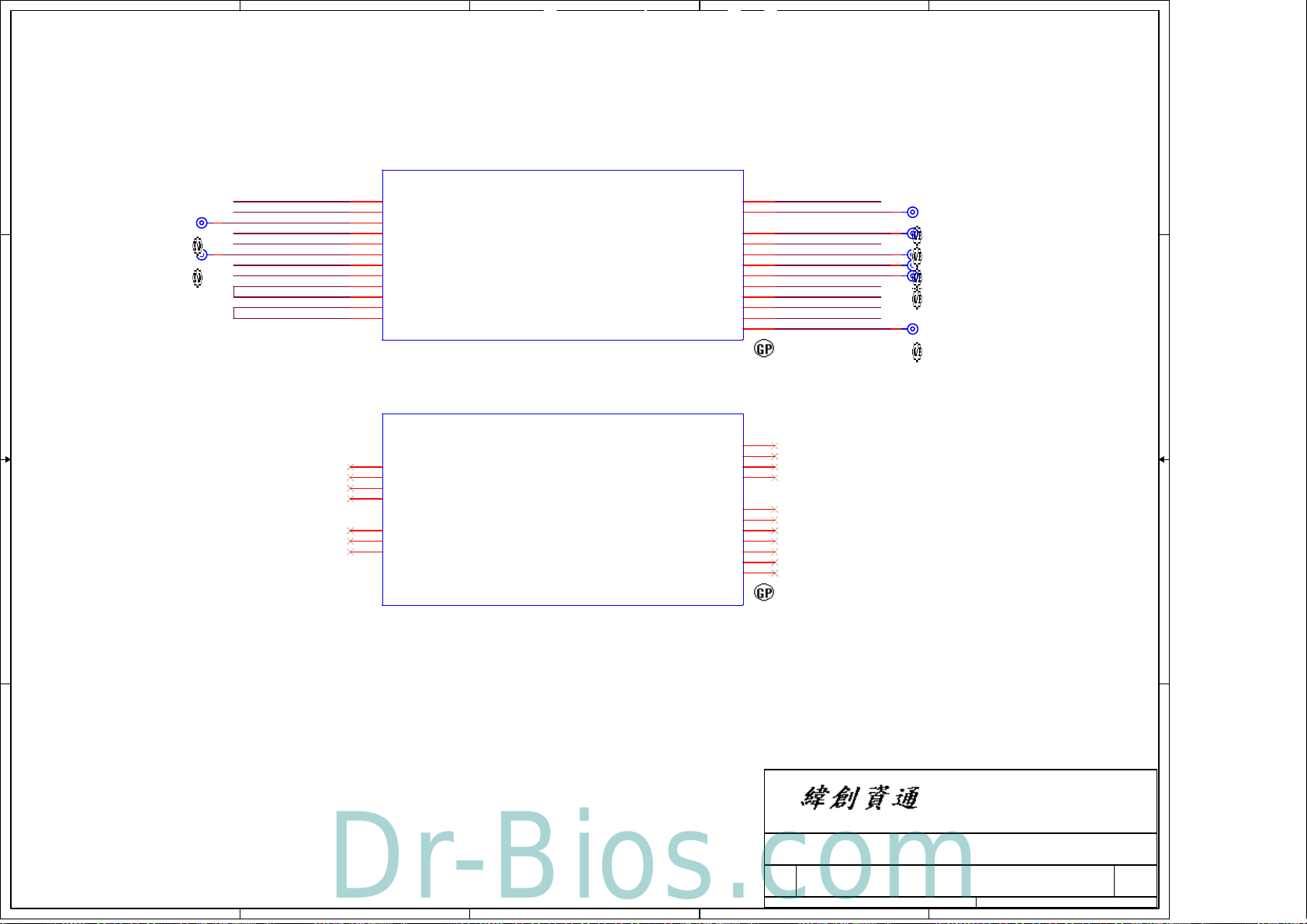

CPU1C

CPU1C

M_A_DQ[15:0]12

D D

M_B_DQ[15:0]13

C C

M_A_DQ[31:16]12

M_B_DQ[31:16]13

B B

A A

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

5

AH63

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

HASWELL-6-GP-U

HASWELL-6-GP-U

HSW_ULT_DDR3L

DDR CHANNEL A

DDR CHANNEL A

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

4

3 OF 19

3 OF 19

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS#

SA_WE#

SA_CAS#

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

AR51

AP51

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DQS_DN0

M_A_DQS_DN1

M_B_DQS_DN0

M_B_DQS_DN1

M_A_DQS_DN2

M_A_DQS_DN3

M_B_DQS_DN2

M_B_DQS_DN3

M_A_DQS_DP0

M_A_DQS_DP1

M_B_DQS_DP0

M_B_DQS_DP1

M_A_DQS_DP2

M_A_DQS_DP3

M_B_DQS_DP2

M_B_DQS_DP3

V_SM_VREF_CNT

VREF_CA12,13

M_A_CLK#0 12

M_A_CLK0 12

M_A_CLK#1 12

M_A_CLK1 12

M_A_CKE0 12

M_A_CKE1 12

M_A_CS#0 12

M_A_CS#1 12

M_A_RAS# 12

M_A_WE# 12

M_A_CAS# 12

M_A_BS0 12

M_A_BS1 12

M_A_BS2 12

M_VREF_DQ_DIM0 12

M_VREF_DQ_DIM1 13

1D35V_S3

M_A_A[15:0] 12

M_A_DQS_DP[7:0] 12

M_B_DQS_DP[7:0] 13

M_A_DQS_DN[7:0] 12

M_B_DQS_DN[7:0] 13

12

R512

R512

1K8R2F-GP

1K8R2F-GP

12

R516

R516

1K8R2F-GP

1K8R2F-GP

3

R503

R503

1 2

2R2J-2-GP

2R2J-2-GP

M_A_DQ[47:32]12

M_B_DQ[47:32]13

M_A_DQ[63:48]12

M_B_DQ[63:48]13

12

VREF_RC

12

V_SM_VREF_CNT

C504

C504

SCD022U16V2KX-3GP

SCD022U16V2KX-3GP

R518

R518

24D9R2F-L-GP

24D9R2F-L-GP

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AY31

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

CPU1D

CPU1D

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

HASWELL-6-GP-U

HASWELL-6-GP-U

2

HSW_ULT_DDR3L

HSW_ULT_DDR3L

DDR CHANNEL B

DDR CHANNEL B

4 OF 19

4 OF 19

AM38

SB_CK#0

AN38

SB_CK0

AK38

SB_CK#1

AL38

SB_CK1

AY49

SB_CKE0

AU50

SB_CKE1

AW49

SB_CKE2

AV50

SB_CKE3

AM32

SB_CS#0

AK32

SB_CS#1

AL32

SB_ODT0

AM35

SB_RAS#

AK35

SB_WE#

AM33

SB_CAS#

AL35

SB_BA0

AM36

SB_BA1

AU49

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

Brook_BH

Brook_BH

Brook_BH

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, February 04, 2015

Wednesday, February 04, 2015

Wednesday, February 04, 2015

Date: Sheet of

Date: Sheet of

Date: Sheet of

M_B_A0

AP40

M_B_A1

AR40

M_B_A2

AP42

M_B_A3

AR42

M_B_A4

AR45

M_B_A5

AP45

M_B_A6

AW46

M_B_A7

AY46

M_B_A8

AY47

M_B_A9

AU46

M_B_A10

AK36

M_B_A11

AV47

M_B_A12

AU47

M_B_A13

AK33

M_B_A14

AR46

M_B_A15

AP46

M_A_DQS_DN4

AW30

M_A_DQS_DN5

AV26

M_B_DQS_DN4

AN28

M_B_DQS_DN5

AN25

M_A_DQS_DN6

AW22

M_A_DQS_DN7

AV18

M_B_DQS_DN6

AN21

M_B_DQS_DN7

AN18

M_A_DQS_DP4

AV30

M_A_DQS_DP5

AW26

M_B_DQS_DP4

AM28

M_B_DQS_DP5

AM25

M_A_DQS_DP6

AV22

M_A_DQS_DP7

AW18

M_B_DQS_DP6

AM21

M_B_DQS_DP7

AM18

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CPU (DDR)

CPU (DDR)

CPU (DDR)

Brook_BH

Brook_BH

Brook_BH

1

M_B_CLK#0 13

M_B_CLK0 13

M_B_CLK#1 13

M_B_CLK1 13

M_B_CKE0 13

M_B_CKE1 13

M_B_CS#0 13

M_B_CS#1 13

M_B_RAS# 13

M_B_WE# 13

M_B_CAS# 13

M_B_BS0 13

M_B_BS1 13

M_B_BS2 13

M_B_A[15:0] 13

5 106

5 106

5 106

-1M

-1M

-1M

Page 5

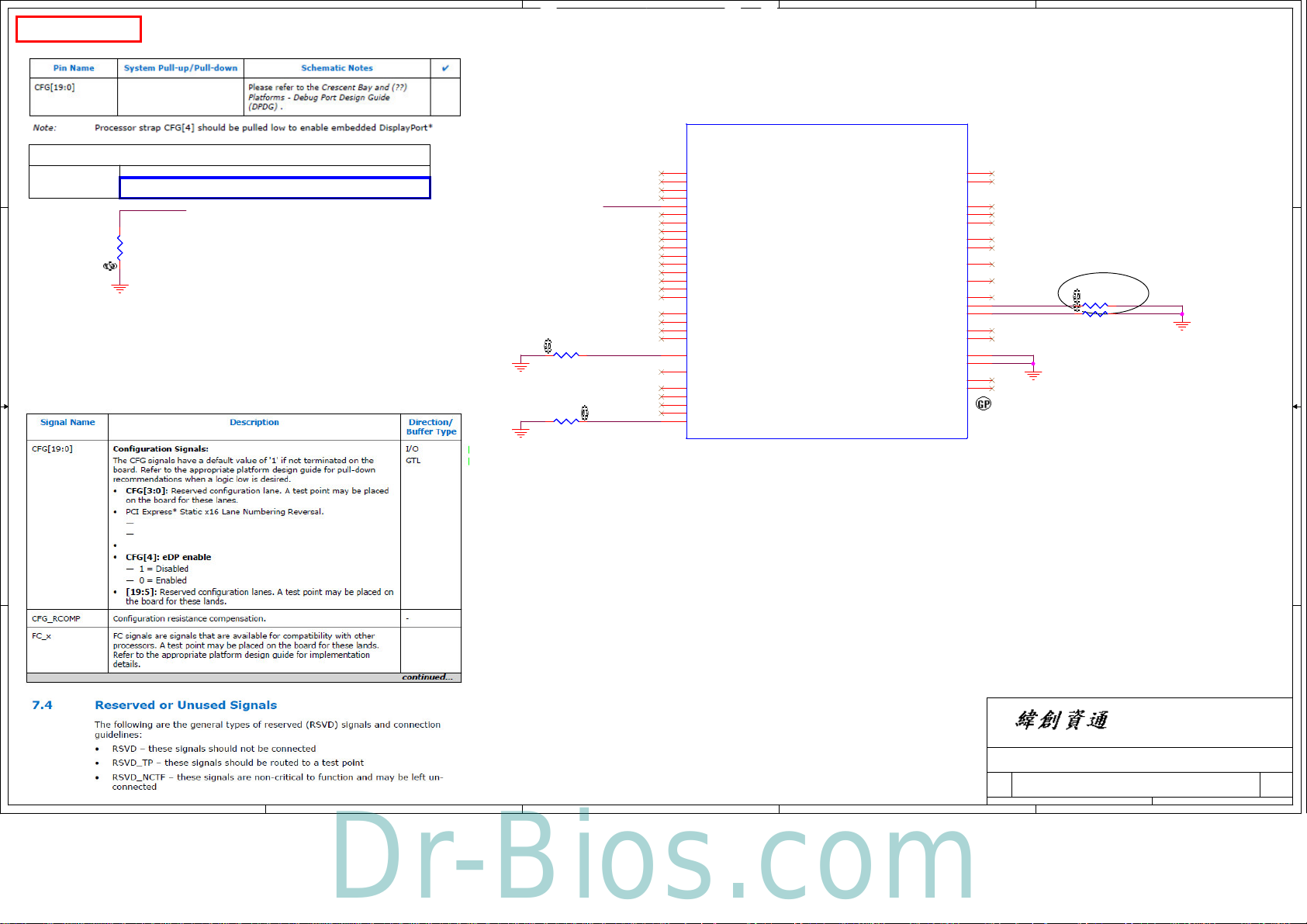

!!N+*R*D?4

Dr-Bios.com

5

4

3

2

1

D D

CPU1S

CPU1S

HSW_ULT_DDR3L

HSW_ULT_DDR3L

19 OF 19

19 OF 19

eDP Enable

CFG4

C C

B B

1:Disable

0:Enable

12

R603

R603

1KR2J-L2-GP

1KR2J-L2-GP

CFG4

R607

R607

49D9R2F-GP

49D9R2F-GP

R606

R606

1 2

8K2R2J-3-GP

8K2R2J-3-GP

12

CFG4

CFG_RCOMP

TD_IREF

AC60

AC62

AC63

AA63

AA60

Y62

Y61

Y60

V62

V61

V60

U60

T63

T62

T61

T60

AA62

U63

AA61

U62

V63

H18

B12

J20

A5

E1

D1

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG18

CFG17

CFG19

CFG_RCOMP

RSVD#A5

RSVD#E1

RSVD#D1

RSVD#J20

RSVD#H18

TD_IREF

RESERVED

RESERVED

RSVD_TP#AV63

RSVD_TP#AU63

RSVD_TP#C63

RSVD_TP#C62

RSVD#B43

RSVD_TP#A51

RSVD_TP#B51

RSVD_TP#L60

RSVD#N60

RSVD#W23

RSVD#Y22

PROC_OPI_RCOMP

RSVD#AV62

RSVD#D58

RSVD#P20

RSVD#R20

VSS

VSS

AV63

AU63

C63

C62

B43

A51

B51

L60

N60

W23

Y22

AY15

AV62

D58

P22

N21

P20

R20

OPI_COMP3

OPI_COMP1

20141216 -1

DY

DY

R611 49D9R2F-GP

R611 49D9R2F-GP

12

R610 49D9R2F-GPR610 49D9R2F-GP

12

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

Brook_BH

Brook_BH

Brook_BH

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

application without get Wistron permission

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221 , Taiwan, R.O.C.

Taipei Hsien 221 , Taiwan, R.O.C.

Taipei Hsien 221 , Taiwan, R.O.C.

CPU (CFG)

CPU (CFG)

CPU (CFG)

Brook_BH

Brook_BH

Wednesday, F ebruary 04, 2015

Wednesday, F ebruary 04, 2015

Wednesday, F ebruary 04, 2015

Brook_BH

6 106

6 106

6 106

1

-1M

-1M

-1M

Page 6

5

Dr-Bios.com

4

3

2

1

!!N+*R*D?4

D D

1D05V_S0

130R2F-1-GP

130R2F-1-GP

75R2F-2-GP

75R2F-2-GP

C C

DT,)$*',*D?4

R703

R703

1 2

R704

R704

1 2

VIDSOUT_CPU

VIDALERT#_CPU

1D35V_S3

C;J>*"T,)$*',*D?4

RN701

RN701

1

2 3

SRN100J-3-GP

SRN100J-3-GP

1V_CPU_CORE

1D05V_S0_PW RGD40,48,51

IMVP_PWRGD26,40,46

TVL-0402-01-AB1 -1-GP

TVL-0402-01-AB1 -1-GP

B B

1D05V_S0

ET701

ET701

12

4

1

2 3

ET702

ET702

1 2

TVL-0402-01-AB1-1-GP

TVL-0402-01-AB1-1-GP

VSS_SENSE

VCC_SENSE

RN702

RN702

4

SRN10KJ-L-GP

SRN10KJ-L-GP

5K1R2-GP

5K1R2-GP

R707

R707

VSS_SENSE 23,46

VCCST_GD_CPU

12

12

IMVP_PWRGD_R

R708

R708

5K1R2-GP

5K1R2-GP

D;J8SD;>9*"T,)$*',*D?4

?NF*AD<<*A@<<*A@<8

DY

12

C703

C703

A A

DY

12

C715

C715

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

5

1D35V_CPU_VDDQ_S 3

PG701

PG701

1 2

GAP-CLOSE-PWR

GAP-CLOSE-PWR

PG702

PG702

1 2

GAP-CLOSE-PWR

GAP-CLOSE-PWR

PG703

PG703

1 2

GAP-CLOSE-PWR

GAP-CLOSE-PWR

PG704

PG704

1 2

GAP-CLOSE-PWR

GAP-CLOSE-PWR

PG705

PG705

1 2

GAP-CLOSE-PWR

GAP-CLOSE-PWR

PG706

PG706

1 2

GAP-CLOSE-PWR

GAP-CLOSE-PWR

VIDALERT#_CPU46

VIDSCK_CPU46

VIDSOUT_CPU46

H_VR_EN46

1D05V_S0

4

1V_VCOMP_OUT

VCCST_GD_CPU

R706

R706

1 2

150R2F-4-L-GP

150R2F-4-L-GP

U,TT,V*N.'$T*DC/

VCC_SENSE46

R705

R705

43R2J-GP

43R2J-GP

1D35V_CPU_VDDQ_S 3

1V_CPU_CORE

12

1V_CPU_CORE

VCC_SENSE

VIDALERT#_CPU_R

IMVP_PWRGD_R

PWR_DEBUG

1D05V_S0

HSW_ULT_DDR3L

CPU1L

CPU1L

L59

RSVD#L59

J58

RSVD#J58

AH26

VDDQ

AJ31

VDDQ

AJ33

VDDQ

AJ37

VDDQ

AN33

VDDQ

AP43

VDDQ

AR48

VDDQ

AY35

VDDQ

AY40

VDDQ

AY44

VDDQ

AY50

VDDQ

F59

VCC

N58

RSVD#N58

AC58

RSVD#AC58

E63

VCC_SENSE

AB23

RSVD#AB23

A59

VCCIO_OUT

E20

VCCIOA_OUT

AD23

RSVD#AD23

AA23

RSVD#AA23

AE59

RSVD#AE59

L62

VIDALERT#

N63

VIDSCLK

L63

VIDSOUT

B59

VCCST_PWRGD

F60

VR_EN

C59

VR_READY

D63

VSS

H59

PWR_DEBUG#

P62

VSS

P60

RSVD_TP#P60

P61

RSVD_TP#P61

N59

RSVD_TP#N59

N61

RSVD_TP#N61

T59

RSVD#T59

AD60

RSVD#AD60

AD59

RSVD#AD59

AA59

RSVD#AA59

AE60

RSVD#AE60

AC59

RSVD#AC59

AG58

RSVD#AG58

U59

RSVD#U59

V59

RSVD#V59

AC22

VCCST

AE22

VCCST

AE23

VCCST

AB57

VCC

AD57

VCC

AG57

VCC

C24

VCC

C28

VCC

C32

VCC

HASWELL-6-GP-U

HASWELL-6-GP-U

3

HSW_ULT_DDR3L

HSW ULT POWER

HSW ULT POWER

2

12 OF 19

12 OF 19

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Brook_BH

Brook_BH

Brook_BH

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

1V_CPU_CORE

C36

C40

C44

C48

C52

C56

E23

E25

E27

E29

E31

E33

E35

E37

E39

E41

E43

E45

E47

E49

E51

E53

E55

E57

F24

F28

F32

F36

F40

F44

F48

F52

F56

G23

G25

G27

G29

G31

G33

G35

G37

G39

G41

G43

G45

G47

G49

G51

G53

G55

G57

H23

J23

K23

K57

L22

M23

M57

P57

U57

W57

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221 , Taiwan, R.O.C.

Taipei Hsien 221 , Taiwan, R.O.C.

Taipei Hsien 221 , Taiwan, R.O.C.

CPU (VCC_CORE)

CPU (VCC_CORE)

CPU (VCC_CORE)

Brook_BH

Brook_BH

Wednesday, F ebruary 04, 2015

Wednesday, F ebruary 04, 2015

Wednesday, F ebruary 04, 2015

Brook_BH

7 106

7 106

7 106

1

-1M

-1M

-1M

Page 7

5

Dr-Bios.com

4

3

2

1

!!N+*R*D?4

D D

HSW_ULT_DDR3L

CPU1A

CPU1A

HSW_ULT_DDR3L

1 OF 19

1 OF 19

C54

DDI1_TXN0

HDMI_DATA_CPU_P257

HDMI_DATA_CPU_N157

3+MN

C C

HDMI_DATA_CPU_P157

HDMI_DATA_CPU_N057

HDMI_DATA_CPU_P057

HDMI_DATA_CPU_N357

HDMI_DATA_CPU_P357

DDI_VGA_DATA_CPU_N056

DDI_VGA_DATA_CPU_P056

DDI_VGA_DATA_CPU_N156

DDI_VGA_DATA_CPU_P156

+?*',*+()YT&Z*?,0'

C55

B58

C58

B55

A55

A57

B57

C51

C50

C53

B54

C49

B50

A53

B53

DDI1_TXP0

DDI1_TXN1

DDI1_TXP1

DDI1_TXN2

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

EDPDDI

EDPDDI

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

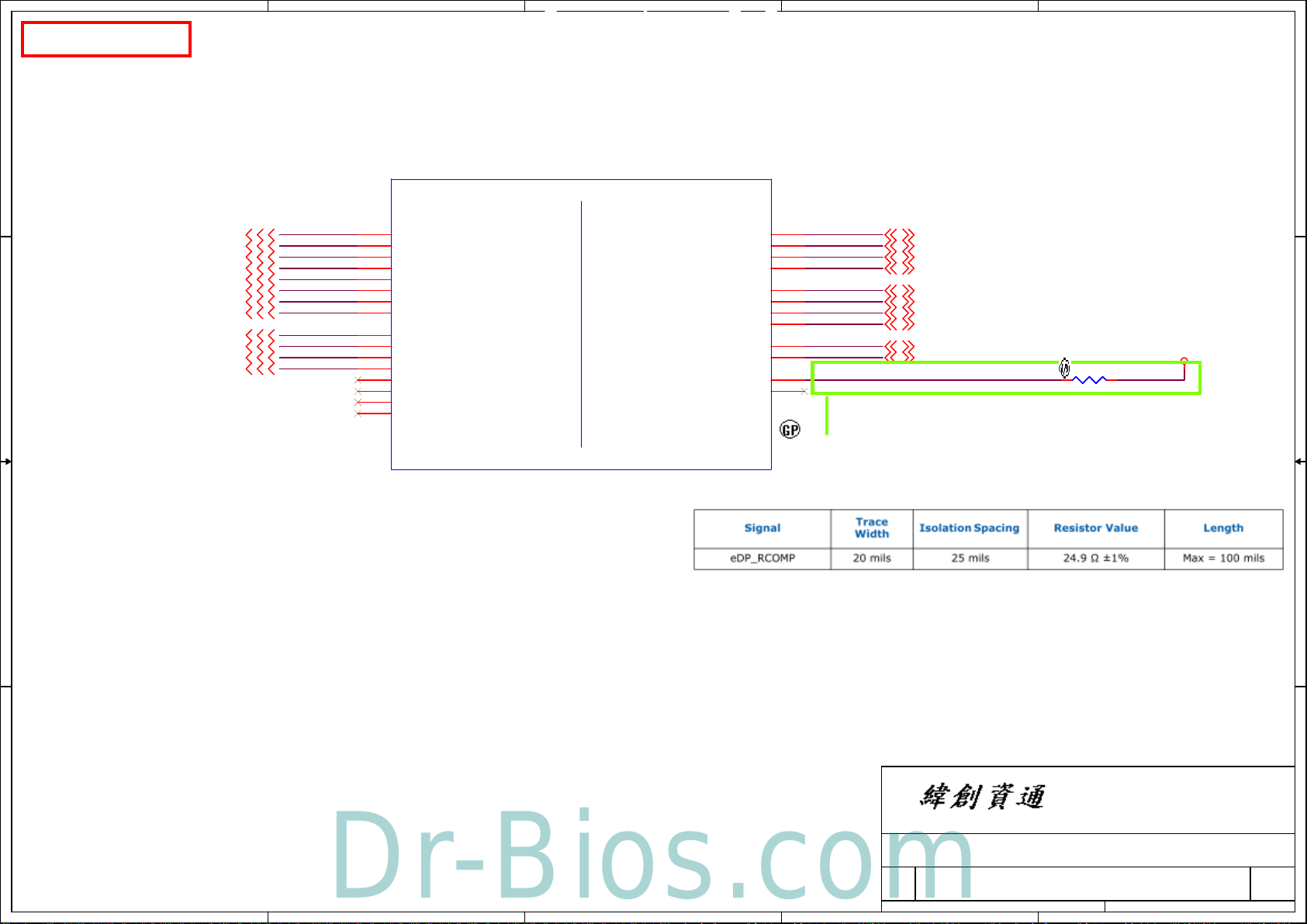

EDP_RCOMP

EDP_DISP_UTIL

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

EDP_RCOMP

eDP_TX_CPU_N0 55HDMI_DATA_CPU_N257

eDP_TX_CPU_P0 55

eDP_TX_CPU_N1 55

eDP_TX_CPU_P1 55

eDP_TX_CPU_N2 55

eDP_TX_CPU_P2 55

eDP_TX_CPU_N3 55

eDP_TX_CPU_P3 55

eDP_AUX_CPU_N 55

eDP_AUX_CPU_P 55

$+?

$+?*W:*0$)$0X$

R801

R801

24D9R2F-L-GP

24D9R2F-L-GP

1V_VCOMP_OUT

12

Layout Note:

HASWELL-6-GP-U

HASWELL-6-GP-U

B B

Design Guideline:

EDP_COMP keep routing length max 100 mils.

Trace Width:20 mils.

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

Brook_BH

Brook_BH

Brook_BH

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

5

4

3

A4

Date: Sheet

Date: Sheet

Date: Sheet of

application without get Wistron permission

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CPU (DDI/EDP)

CPU (DDI/EDP)

CPU (DDI/EDP)

Brook_BH

Brook_BH

Wednesday, February 04, 2015

Wednesday, February 04, 2015

Wednesday, February 04, 2015

2

Brook_BH

8 106

of

8 106

of

8 106

1

-1M

-1M

-1M

Page 8

5

Dr-Bios.com

4

3

2

1

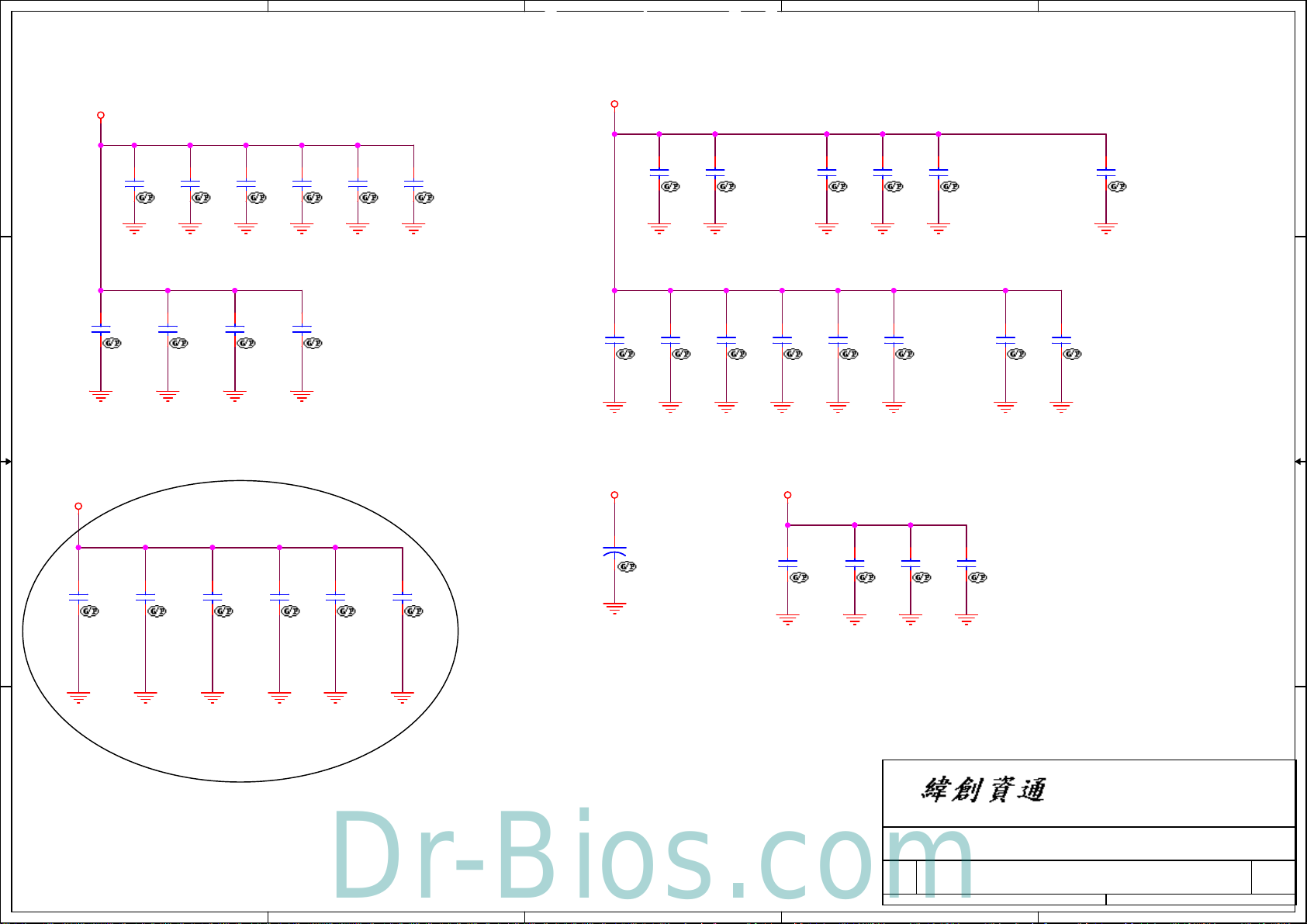

1D35V_CPU_VDDQ_S3

D D

12

EC1006

EC1006

C C

Power current=3A

12

SC2D2U10V3KX-L-GP

SC2D2U10V3KX-L-GP

C1040

C1040

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12

12

DY

DY

EC1007

EC1007

SC2D2U10V3KX-L-GP

SC2D2U10V3KX-L-GP

C1035

C1035

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12

12

C1036

C1036

EC1008

EC1008

SC2D2U10V3KX-L-GP

SC2D2U10V3KX-L-GP

C1037

C1037

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

EC1009

EC1009

SC2D2U10V3KX-L-GP

SC2D2U10V3KX-L-GP

12

C1038

C1038

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12

12

C1039

C1039

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

1V_CPU_CORE

12

PC1020

PC1020

Power current=40A

12

PC1017

PC1017

12

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

PC1007

PC1007

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

12

PC1016

PC1016

12

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

PC1006

PC1006

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

12

PC1015

PC1015

12

PC1005

PC1005

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

12

PC1013

PC1013

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

12

PC1012

PC1012

12

PC1002

PC1002

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

PC1010

PC1010

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

12

PC1019

PC1019

12

PC1009

PC1009

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

12

PC1018

PC1018

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

12

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

U,0*N.'$T*C$",%%$.[ @@*?&0'

1V_CPU_CORE

DY

DY

DY

DY

DY

B B

DY

12

EC1001

EC1001

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

DY

12

EC1002

EC1002

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

12

DY

EC1003

EC1003

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

DY

12

EC1004

EC1004

DY

12

EC1005

EC1005

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

DY

DY

12

EC1016

EC1016

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

1V_CPU_CORE 1V_CPU_CORE

15WDY/28W

15WDY/28W

12

PT1001

PT1001

ST220U2VDM-8-GP

ST220U2VDM-8-GP

12

C1002

C1002

C1003

C1003

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

12

C1004

C1004

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

12

C1005

C1005

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

12

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

U,0*N.'$T*C$",%%$.[

Brook_BH

Brook_BH

Brook_BH

A A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

5

4

3

Date: Sheet of

Date: Sheet of

Date: Sheet of

@@*?&0'

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

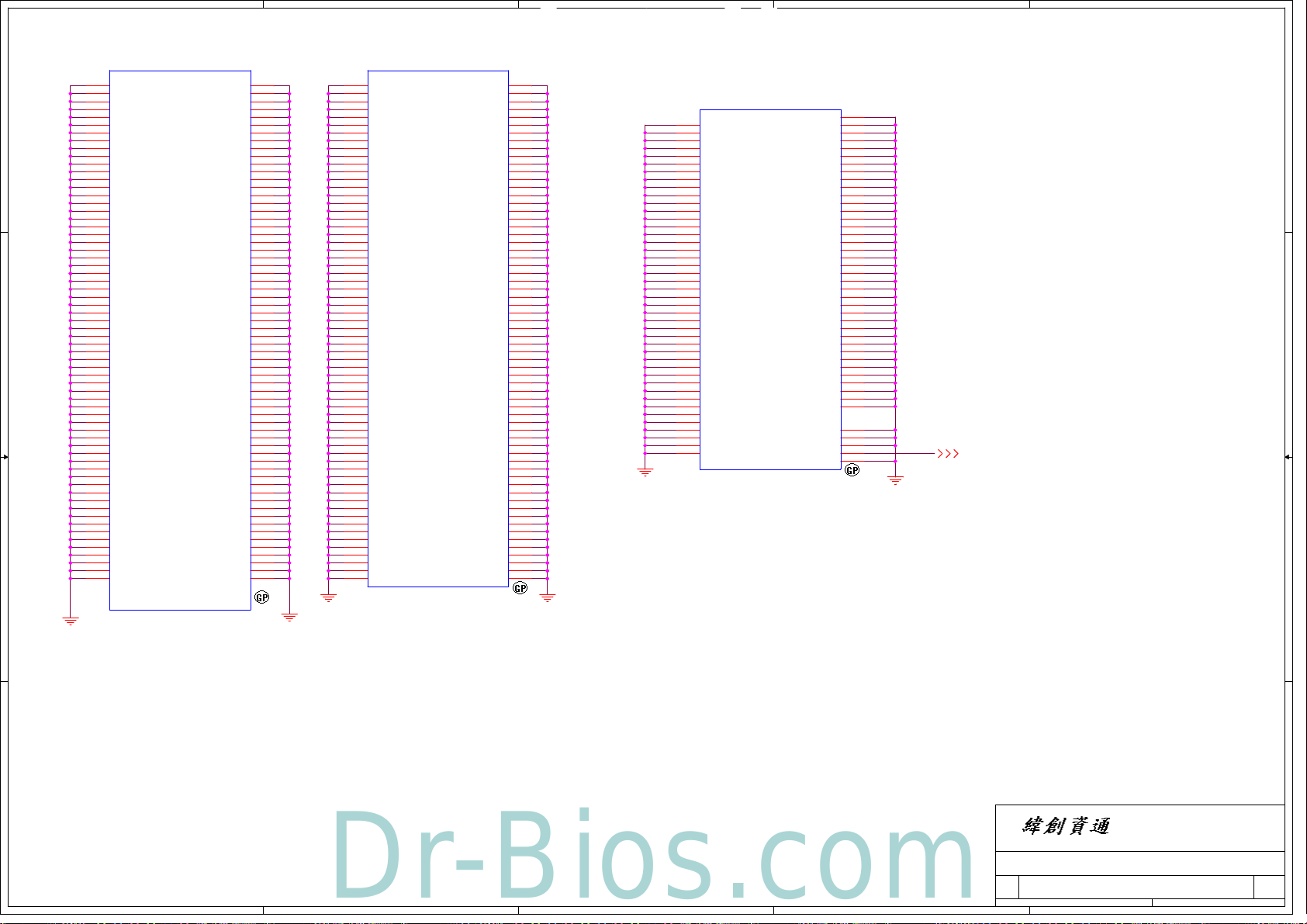

CPU (Power CAP1)

CPU (Power CAP1)

CPU (Power CAP1)

Brook_BH

Brook_BH

Wednesday, February 04, 2015

Wednesday, February 04, 2015

Wednesday, February 04, 2015

2

Brook_BH

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

-1M

-1M

10 106

10 106

10 106

1

-1M

Page 9

5

Dr-Bios.com

4

3

2

1

Page 21,

MA\]*8^J;:A

D D

1D05V_S 0

12

C1102

C1102

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

12

C1103

C1103

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

C1102;C1103

pin K9 L10

1D05V_S 0

L1101

L1101

1 2

IND-2D2UH-1 96-GP

IND-2D2UH-1 96-GP

12

C1108

C1108

SC4D7U6D3V3KX-L-GP

SC4D7U6D3V3KX-L-GP

DY

DY

12

C1109

C1109

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

C1108;C1109

pin B18

1D05V_S 0

L1102

L1102

1 2

IND-2D2UH-1 96-GP

IND-2D2UH-1 96-GP

12

C1104

C1104

SC4D7U6D3V3KX-L-GP

SC4D7U6D3V3KX-L-GP

DY

DY

1D05V_V CCSATA3PLL_S 01D05V_V CCUSB3PLL_S0

12

C1106

C1106

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

C1104;C1106

pin B11

3D3V_RT C_AUX

C1135

C1135

12

C1135;C1136

C1136

C1136

SCD1U25V2KX-L-GP

SCD1U25V2KX-L-GP

pin AG10

12

3D3V_SU S

12

C1116

C1116

C1116

pin AC9

SC10U6D 3V3MX-L-GP

SC10U6D 3V3MX-L-GP

C C

MA\]*J^<I9A

3D3V_S0

12

12

C1119

C1119

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

B B

1D05V_S 0

12

C1144

C1144

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

A A

C1101 pin V8

C1101

C1101

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

C1119 pin K14

!""##

$%&'$()*

5

1D05V_S 0

L1104

L1104

1 2

IND-2D2UH-1 96-GP

IND-2D2UH-1 96-GP

12

1D05V_S 0 1D05V_S 0

12

12

12

C1134

C1134

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

4

C1141

C1141

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

DY

DY

C1110

C1110

1D05V_V CCACLKPLL_S0 1D05V_V CCCLK_S0

C1118;C1120

12

C1120

C1120

C1118

C1118

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC4D7U6D3V3KX-L-GP

SC4D7U6D3V3KX-L-GP

DY

DY

!"""+,!""-#$$ $%&'$.""

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

!""#"$ $%&'$()/

pin A20

1D05V_S 0

12

L1103

L1103

1 2

IND-2D2UH-1 96-GP

IND-2D2UH-1 96-GP

12

C1122

C1122

C1123

C1123

SC4D7U6D3V3KX-L-GP

SC4D7U6D3V3KX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

DY

DY

3

C1122;C1123

pin AA21

12

C1111

C1111

SC4D7U6D3V3KX-L-GP

SC4D7U6D3V3KX-L-GP

MA\]*8^9>A

C1111;C1115

C1115

C1115

12

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

DY

DY

pin J18

SC1U6D3V3KX-L1-GP

SC1U6D3V3KX-L1-GP

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

Brook_BH

Brook_BH

Brook_BH

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

application without get Wistron permission

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CPU (Power CAP2)

CPU (Power CAP2)

CPU (Power CAP2)

Brook_BH

Brook_BH

Wednesd ay, February 04, 2015

Wednesd ay, February 04, 2015

Wednesd ay, February 04, 2015

Brook_BH

11 106

11 106

11 106

1

-1M

-1M

-1M

Page 10

5

Dr-Bios.com

4

3

2

1

SSID = MEMORY

DM2

D D

C C

B B

DT,)$*CAM>*DA*_*+`*Y(.

VREF_CA

12

C1217

C1217

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

A A

VREF_DQ0

12

C1218

C1218

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

5

M_A_A[15:0]5

M_A_BS25

M_A_BS05

M_A_BS15

M_A_DQ[15:0]5

M_A_DQ[31:16]5

M_A_DQ[47:32]5

M_A_DQ[63:48]5

M_A_DQS_DN[7: 0]5

M_A_DQS_DP[7:0]5

VREF_CA5,13

DDR3_DR AMRST#4,13

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_DQS_DN0

M_A_DQS_DN1

M_A_DQS_DN2

M_A_DQS_DN3

M_A_DQS_DN4

M_A_DQS_DN5

M_A_DQS_DN6

M_A_DQS_DN7

M_A_DQS_DP0

M_A_DQS_DP1

M_A_DQS_DP2

M_A_DQS_DP3

M_A_DQS_DP4

M_A_DQS_DP5

M_A_DQS_DP6

M_A_DQS_DP7

M_A_DIM0_ODT0

M_A_DIM0_ODT1

VREF_CA

VREF_DQ0

0D675V_VREF_S0

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

DM2

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12

119

A13

80

A14

78

A15

79

A16/BA2

109

BA0

108

BA1

5

DQ0

7

DQ1

15

DQ2

17

DQ3

4

DQ4

6

DQ5

16

DQ6

18

DQ7

21

DQ8

23

DQ9

33

DQ10

35

DQ11

22

DQ12

24

DQ13

34

DQ14

36

DQ15

39

DQ16

41

DQ17

51

DQ18

53

DQ19

40

DQ20

42

DQ21

50

DQ22

52

DQ23

57

DQ24

59

DQ25

67

DQ26

69

DQ27

56

DQ28

58

DQ29

68

DQ30

70

DQ31

129

DQ32

131

DQ33

141

DQ34

143

DQ35

130

DQ36

132

DQ37

140

DQ38

142

DQ39

147

DQ40

149

DQ41

157

DQ42

159

DQ43

146

DQ44

148

DQ45

158

DQ46

160

DQ47

163

DQ48

165

DQ49

175

DQ50

177

DQ51

164

DQ52

166

DQ53

174

DQ54

176

DQ55

181

DQ56

183

DQ57

191

DQ58

193

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

10

DQS0#

27

DQS1#

45

DQS2#

62

DQS3#

135

DQS4#

152

DQS5#

169

DQS6#

186

DQS7#

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

116

ODT0

120

ODT1

126

VREF_CA

1

VREF_DQ

30

RESET#

203

VTT1

204

VTT2

SKT_DDR 204P SMD

SKT_DDR 204P SMD

DDR3-204P- 263-GP-U

DDR3-204P- 263-GP-U

62.10024.S61

62.10024.S61

2ND = 62.10024.M51

2ND = 62.10024.M51

3RD = 62.10024.Q71

3RD = 62.10024.Q71

4TH = 62.10017.I21

4TH = 62.10017.I21

RAS#

CAS#

CS0#

CS1#

CKE0

CKE1

CK0#

CK1#

EVENT#

VDDSPD

NC#1

NC#2

NC#/TEST

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

4

NP1

NP1

NP2

NP2

110

113

WE#

115

114

121

73

74

101

CK0

103

102

CK1

104

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

200

SDA

202

SCL

SA0

SA1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

TS#_DIMM1_1

198

199

197

201

77

122

1D35V_S3

125

75

76

81

82

87

88

93

94

99

100

105

106

111

112

117

118

123

124

2

3

8

9

13

14

19

20

25

26

31

32

37

38

43

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

205

206

1D35V_S3

12

12

C1223

C1223

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

0D675V_VREF_S0

12

C1214

C1214

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

DY

DY

M_A_RAS# 5

M_A_WE# 5

M_A_CAS# 5

M_A_CS#0 5

M_A_CS#1 5

M_A_CKE0 5

M_A_CKE1 5

M_A_CLK0 5

M_A_CLK#0 5

M_A_CLK1 5

M_A_CLK#1 5

SMB_DATA 13,18

SMB_CLK 13,18

TS#_DIMM1_1 13

DDR3_DR AMRST#

DDR3_DR AMRST#

5&Z,-'*F,'$]

?T&"$*'#$)$*D&Y)*.$&0

!EH+NMMA^

!E+NMM*A*+@DE4?5NFP

12

12

C1208

C1208

C1207

C1207

C1206

C1206

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

12

C1222

C1222

12

C1215

C1215

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

DY

DY

12

12

C1221

C1221

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

?T&"$*'#$)$*"&Y)

"T,)$*',*K66>*&.[*K66<^

12

12

C1219

C1219

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

DY

DY

3D3V_S0

C1203

C1203

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

12

DY

DY

ET1201

ET1201

12

TVL-0402-01-AB1- 1-GP

TVL-0402-01-AB1- 1-GP

ET1202

ET1202

TVL-0402-01-AB1- 1-GP

TVL-0402-01-AB1- 1-GP

12

C1209

C1209

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

DY

DY

C1220

C1220

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

C1216

C1216

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

12

12

C1210

C1210

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

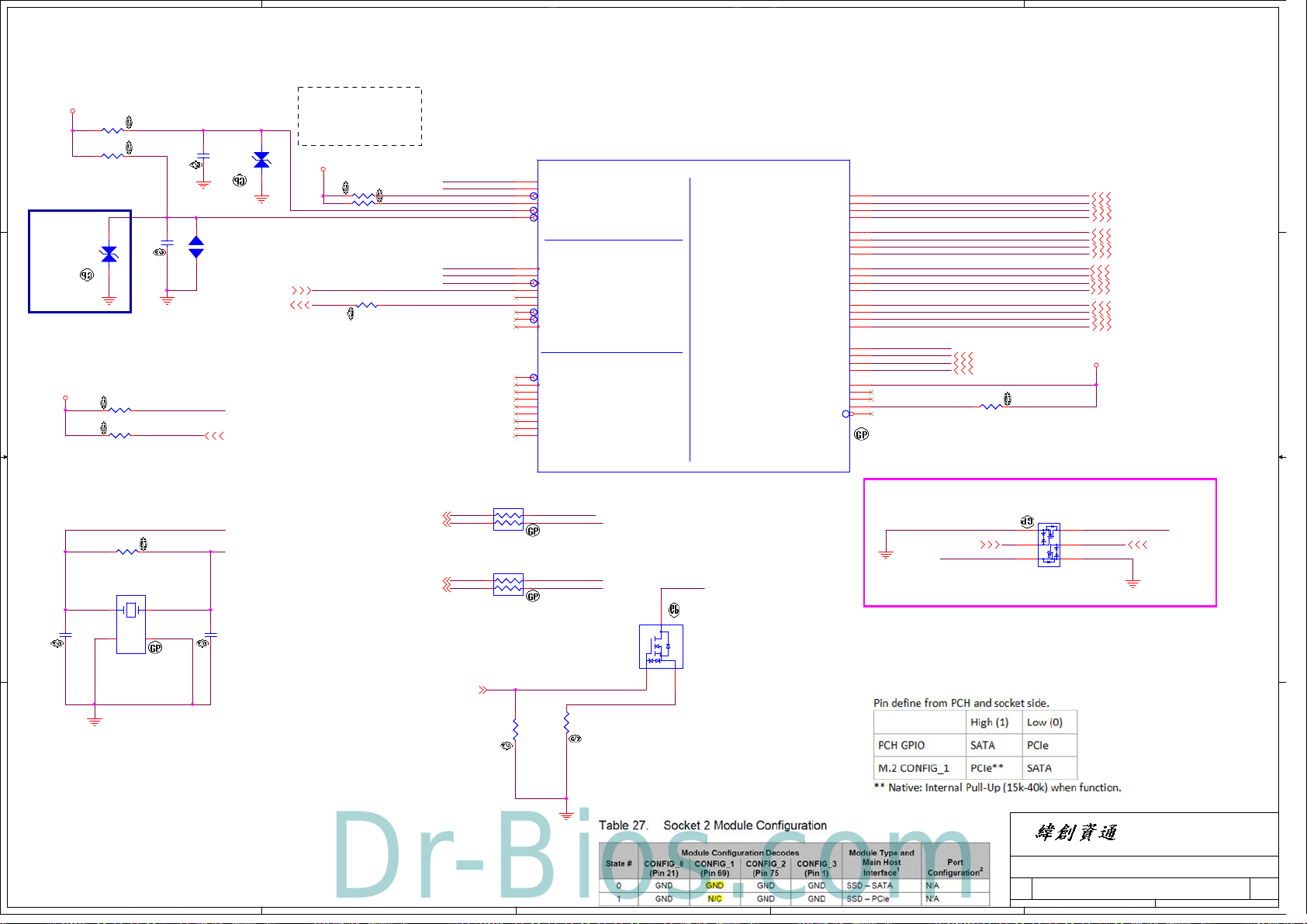

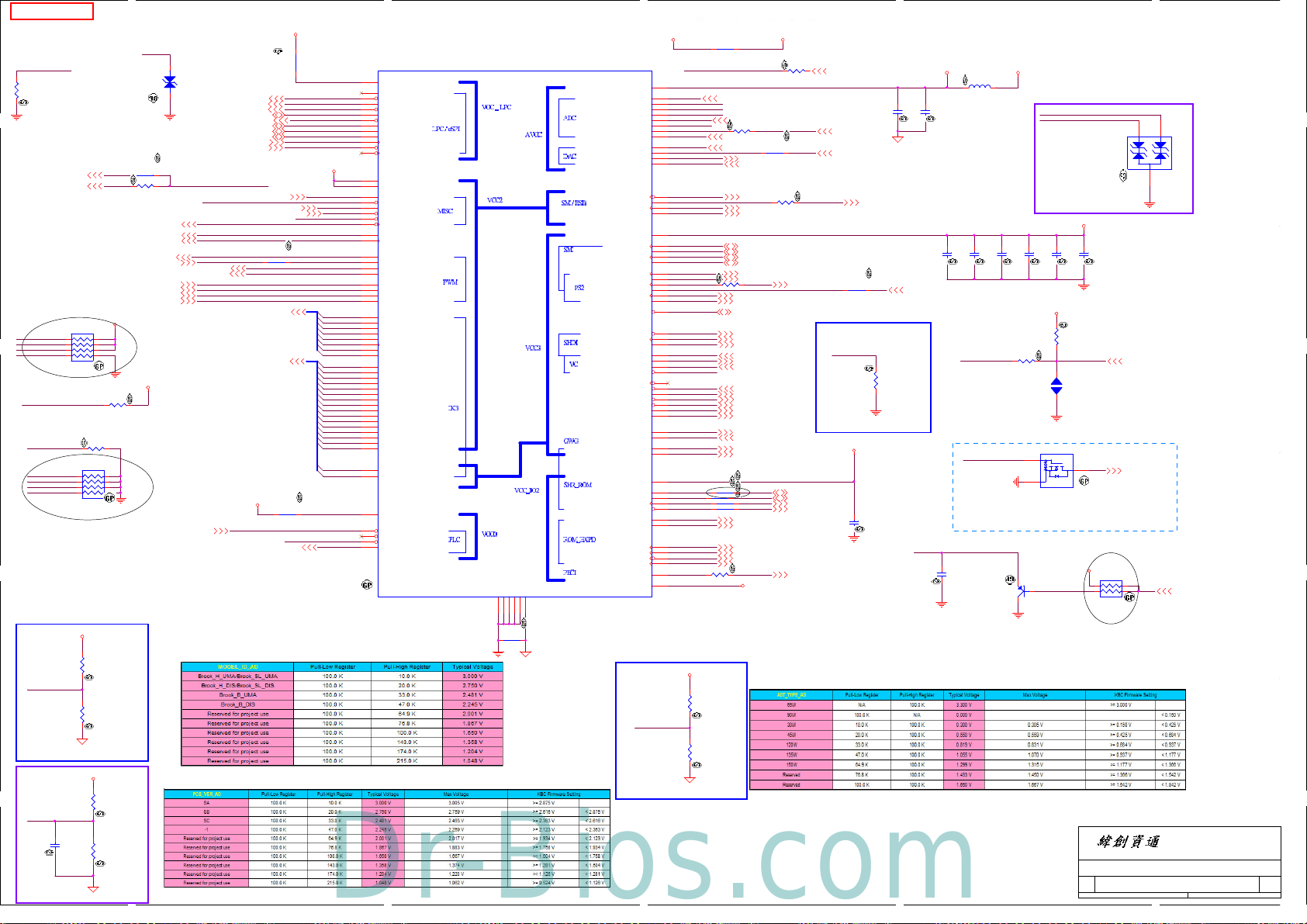

Note:

If SA0 DIM0 = 0, SA1_DIM0 = 0

SO-DIMMA SPD Address is 0xA0

SO-DIMMA TS Address is 0x30

If SA0 DIM0 = 1, SA1_DIM0 = 0

SO-DIMMA SPD Address is 0xA2

SO-DIMMA TS Address is 0x32

DDR_PG_C TRL4

3

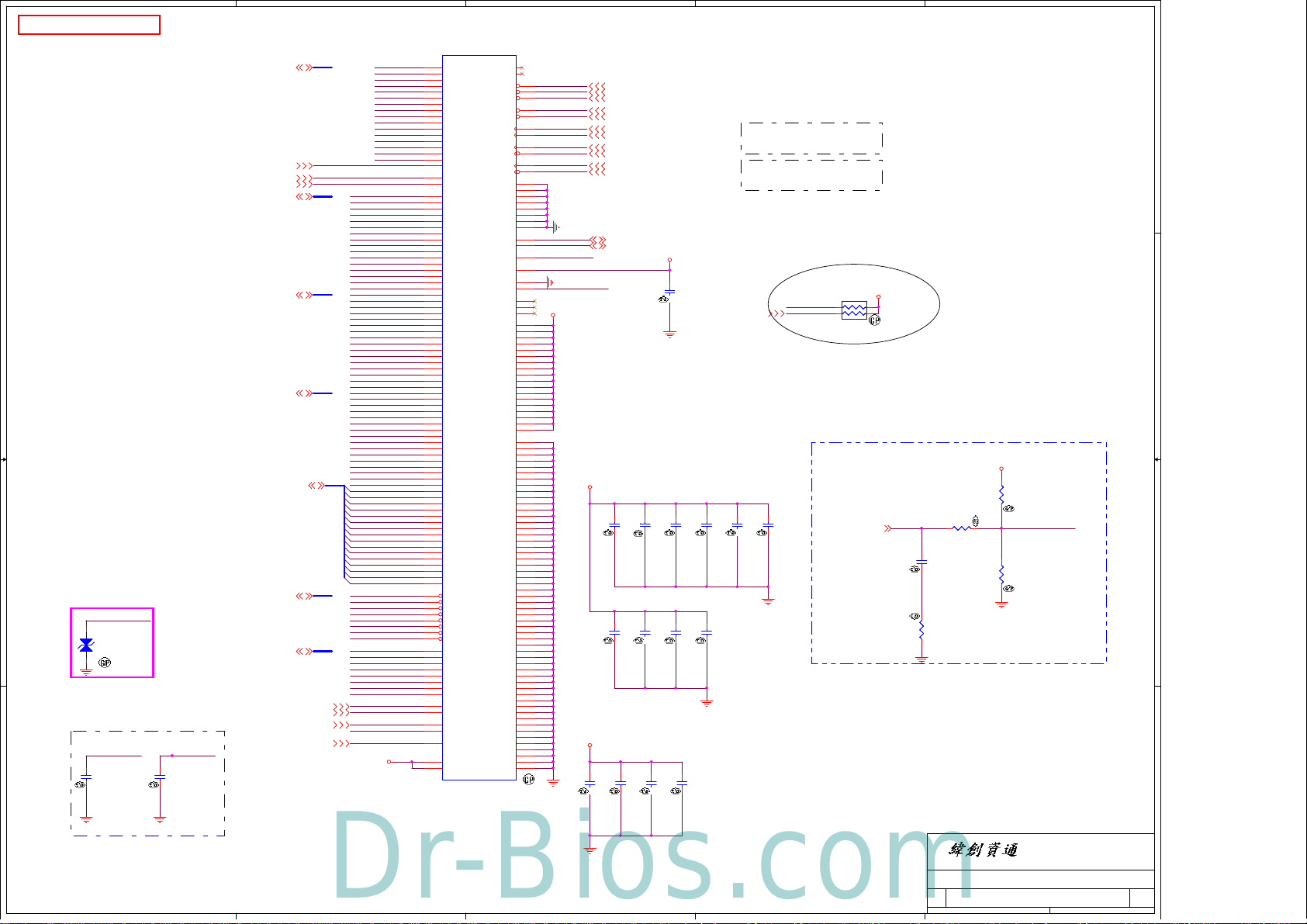

SODIMM Memory Connectivity and Topology

ODT Signal Connectivity and Support

For DDR3L SODIMM designs, Intel recommends ODT signals not to be routed between

CPU and DIMM on platform, leave ODT at CPU as no-connect (open), and tie DIMM

ODT to VDDQ through FET and resistor. The reason for this additional ODT-control

circuitry on the platform is to save power dissipation by turning off VDDQ to VTT path

during low power states, as ODT signal is terminated to VTT through RTT on SODIMM.

The ODT value for DDR3L SODIMM 1-DPC platform will be encoded in the write

command and use RTT_NOM = Off and RTT_WR = (60,120) Ohm.

CPU ODT output would be NOCON

SODIMM ODT input should be tied to VDDQ through a FET and a resistor to

support low power states.

1D35V_S3

DS

Q1203

Q1203

DMN5L06K-7-G P

1D35V_S3

Q1202

Q1202

DMN5L06K-7-G P

DMN5L06K-7-G P

84.05067.031

84.05067.031

`><J<*`><J8 I:^J9J7;^J8>

3D3V_S0

12

R1212

G

R1212

220KR2J-L2-GP

220KR2J-L2-GP

DS

K'# >K

M_VREF_DQ_D IM05

12

C1202

C1202

SCD022U16V2KX-3GP

SCD022U16V2KX-3GP

VREF_DIMM0

R1206

R1206

24D9R2F-L-G P

24D9R2F-L-G P

1 2

R1205

R1205

1 2

2R2J-2-GP

2R2J-2-GP

1D35V_S3

12

12

G

R1203

R1203

1K8R2F-GP

1K8R2F-GP

R1202

R1202

1K8R2F-GP

1K8R2F-GP

DMN5L06K-7-G P

84.05067.031

84.05067.031

M_A_B_DIM_ODT

DDR_PG_OU T 49

VREF_DQ0

U,0*N.'$T*C$",%%$.[*DT,)$*',*+NMM

2

E+6*0$)()',0*%-)'*a$*77^9*,#%

R1208

R1208

M_A_DIM0_ODT0

1 2

66D5R2F-GP

66D5R2F-GP

R1209

R1209

M_A_DIM0_ODT1

1 2

66D5R2F-GP

66D5R2F-GP

R1210

R1210

1 2

66D5R2F-GP

66D5R2F-GP

R1211

R1211

1 2

66D5R2F-GP

66D5R2F-GP

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

Brook_BH

Brook_BH

Brook_BH

Title

Title

Title

DDR3-SODIMM1

DDR3-SODIMM1

DDR3-SODIMM1

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

A2

A2

A2

Wednesd ay, February 04, 2015

Wednesd ay, February 04, 2015

Wednesd ay, February 04, 2015

Date: Sheet of

Date: Sheet of

Date: Sheet of

M_B_DIM0_ODT0 13

M_B_DIM0_ODT1 13

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

21F, 88, Sec.1, Hsin T ai Wu Rd., H sichih,

Taipei Hsie n 221, Taiwan, R.O.C.

Taipei Hsie n 221, Taiwan, R.O.C.

Taipei Hsie n 221, Taiwan, R.O.C.

Brook_BH

Brook_BH

Brook_BH

1

12 106

12 106

12 106

-1M

-1M

-1M

Page 11

5

Dr-Bios.com

4

3

2

1

SSID = MEMORY

DM1

M_B_A[15:0]5

D D

M_B_BS25

M_B_BS05

M_B_BS15

M_B_DQ[15:0]5

M_B_DQ[31:16]5

C C

M_B_DQ[47:32]5

M_B_DQ[63:48]5

B B

M_B_DQS_DN[7:0]5

DDR3_DRAMRST#

12

EC1301

EC1301

AZ5325-01FDR7G-GP

DY

DY

AZ5325-01FDR7G-GP

M_B_DQS_DP[7:0]5

Reserve for EMC

M_B_DIM0_ODT012

M_B_DIM0_ODT112

DT,)$*CAM8*DA*_*+`*Y(.

12

C1302

C1302

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

A A

VREF_DQ1VREF_CA

12

C1304

C1304

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

VREF_CA5,12

DDR3_DRAMRST#4,12

0D675V_VREF_S0

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DQ23

M_B_DQ17

M_B_DQ20

M_B_DQ19

M_B_DQ22

M_B_DQ16

M_B_DQ21

M_B_DQ18

M_B_DQ5

M_B_DQ4

M_B_DQ7

M_B_DQ6

M_B_DQ3

M_B_DQ2

M_B_DQ0

M_B_DQ1

M_B_DQ9

M_B_DQ14

M_B_DQ11

M_B_DQ13

M_B_DQ12

M_B_DQ8

M_B_DQ15

M_B_DQ10

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ31

M_B_DQ29

M_B_DQ30

M_B_DQ28

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ38

M_B_DQ32

M_B_DQ33

M_B_DQ37

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_DQS_DN2

M_B_DQS_DN0

M_B_DQS_DN1

M_B_DQS_DN3

M_B_DQS_DN4

M_B_DQS_DN5

M_B_DQS_DN6

M_B_DQS_DN7

M_B_DQS_DP2

M_B_DQS_DP0

M_B_DQS_DP1

M_B_DQS_DP3

M_B_DQS_DP4

M_B_DQS_DP5

M_B_DQS_DP6

M_B_DQS_DP7

VREF_CA

VREF_DQ1

5

4

DM1

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12

119

A13

80

A14

78

A15

79

A16/BA2

109

BA0

108

BA1

5

DQ0

7

DQ1

15

DQ2

17

DQ3

4

DQ4

6

DQ5

16

DQ6

18

DQ7

21

DQ8

23

DQ9

33

DQ10

35

DQ11

22

DQ12

24

DQ13

34

DQ14

36

DQ15

39

DQ16

41

DQ17

51

DQ18

53

DQ19

40

DQ20

42

DQ21

50

DQ22

52

DQ23

57

DQ24

59

DQ25

67

DQ26

69

DQ27

56

DQ28

58

DQ29

68

DQ30

70

DQ31

129

DQ32

131

DQ33

141

DQ34

143

DQ35

130

DQ36

132

DQ37

140

DQ38

142

DQ39

147

DQ40

149

DQ41

157

DQ42

159

DQ43

146

DQ44

148

DQ45

158

DQ46

160

DQ47

163

DQ48

165

DQ49

175

DQ50

177

DQ51

164

DQ52

166

DQ53

174

DQ54

176

DQ55

181

DQ56

183

DQ57

191

DQ58

193

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

10

DQS0#

27

DQS1#

45

DQS2#

62

DQS3#

135

DQS4#

152

DQS5#

169

DQS6#

186

DQS7#

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

116

ODT0

120

ODT1

126

VREF_CA

1

VREF_DQ

30

RESET#

203

VTT1

204

VTT2

SKT_DDR 204P SMD

SKT_DDR 204P SMD

DDR3-204P-262-GP-U

DDR3-204P-262-GP-U

62.10024.S21

62.10024.S21

2ND = 62.10024.M31

2ND = 62.10024.M31

3RD = 62.10024.Q61

3RD = 62.10024.Q61

4TH = 62.10017.I31

4TH = 62.10017.I31

RAS#

CAS#

CS0#

CS1#

CKE0

CKE1

CK0#

CK1#

EVENT#

VDDSPD

NC#1

NC#2

NC#/TEST

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

WE#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

NP1

NP1

NP2

NP2

110

113

115

114

121

73

74

101

CK0

103

102

CK1

104

11

28

46

63

136

153

170

187

200

SDA

202

SCL

SA0

SA1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

TS#_DIMM1_1

198

199

197

SA1_DIM1

201

77

122

1D35V_S3

125

75

76

81

82

87

88

93

94

99

100

105

106

111

112

117

118

123

124

2

3

8

9

13

14

19

20

25

26

31

32

37

38

43

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

205

206

1D35V_S3

0D675V_VREF_S0

12

C1314

C1314

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

3

M_B_RAS# 5

M_B_WE# 5

M_B_CAS# 5

M_B_CS#0 5

M_B_CS#1 5

M_B_CKE0 5

M_B_CKE1 5

M_B_CLK0 5

M_B_CLK#0 5

M_B_CLK1 5

M_B_CLK#1 5

SMB_DATA 12,18

SMB_CLK 12,18

3D3V_S0

12

C1303

C1303

DY

DY

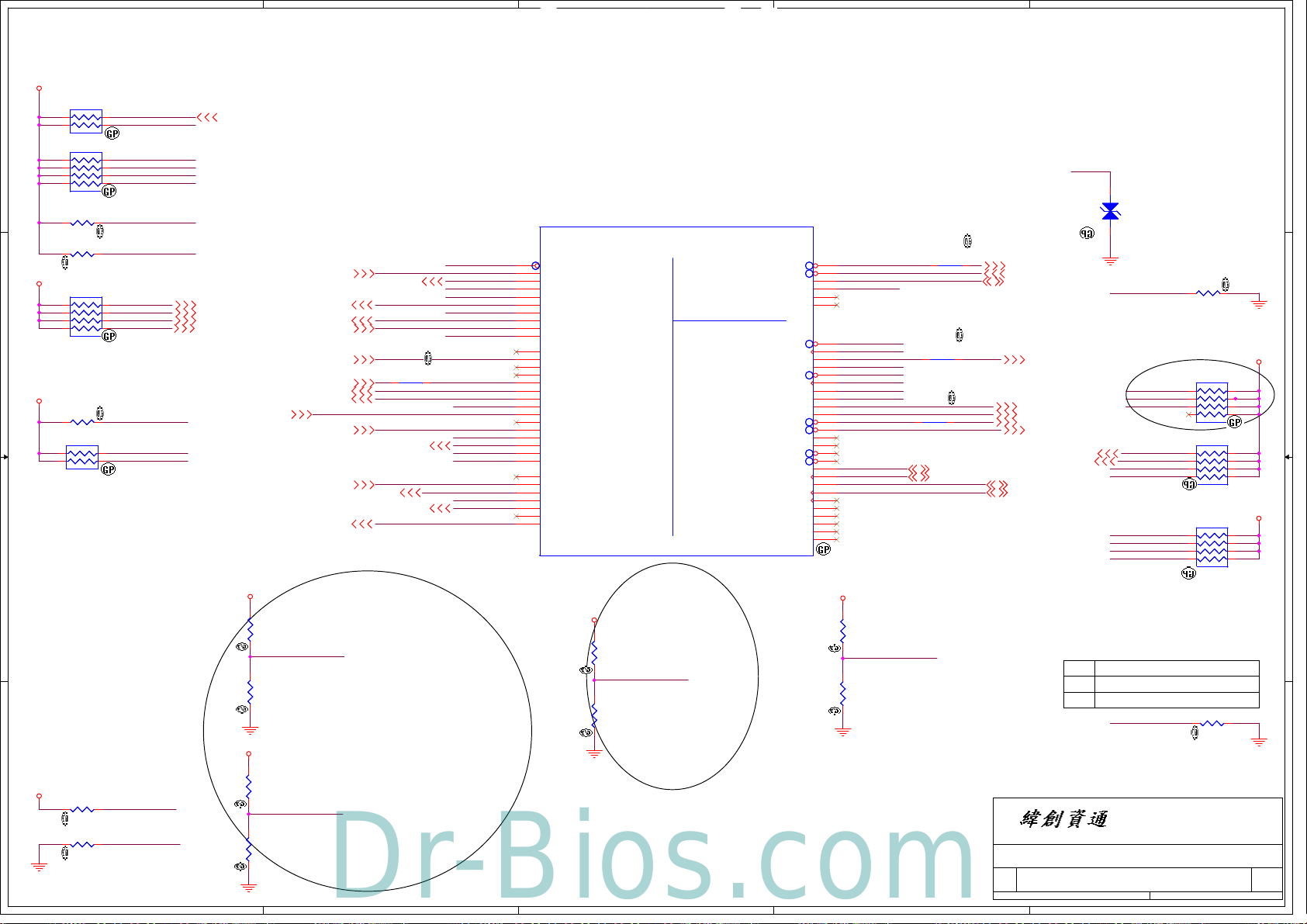

Layout Note:

Place these Caps near

SO-DIMMB.

SODIMM B DECOUPLING

12

12

C1305

C1305

SC5D6P50V2CN-1GP

SC5D6P50V2CN-1GP

12

C1320

C1320

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

?T&"$*'#$)$*"&Y)*"T,)$*',

K66>*&.[*K66<^

12

C1315

C1315

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

12

C1306

C1306

SC56P50V2JN-2GP

SC56P50V2JN-2GP

12

12

C1321

C1321

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

DY

DY

12

C1316

C1316

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

C1307

C1307

C1318

C1318

12

Note:

SO-DIMMB SPD Address is 0xA4

SO-DIMMB TS Address is 0x34

SO-DIMMB is placed farther from

the Processor than SO-DIMMA

Thermal EVENT

12

DY

DY

C1310

C1310

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SA1_DIM1

TS#_DIMM1_1

TS#_DIMM1_112

DY

DY

DY

DY

12

12

C1308

C1308

C1309

C1309

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC10U6D3V3MX-L-GP

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

SC10U6D3V3MX-L-GP

12

C1319

C1319

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

RN1314

RN1314

1

2 3

SRN10KJ-L-GP

SRN10KJ-L-GP

M_VREF_DQ_DIM15

3D3V_S0

4

12

C1311

C1311

SCD022U16V2KX-3GP

SCD022U16V2KX-3GP

VREF_DIMM1

R1307

R1307

24D9R2F-L-GP

24D9R2F-L-GP

1 2

R1306

R1306

1 2

2R2J-2-GP

2R2J-2-GP

1D35V_S3

12

12

R1304

R1304

1K8R2F-GP

1K8R2F-GP

R1303

R1303

1K8R2F-GP

1K8R2F-GP

VREF_DQ1

U,0*N.'$T*C$",%%$.[*DT,)$*',*+NMM

DY

DY

C1317

C1317

SC1U10V2KX-L1-GP

SC1U10V2KX-L1-GP

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

Brook_BH

Brook_BH

Brook_BH

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

DDR3-SODIMM2

DDR3-SODIMM2

DDR3-SODIMM2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Wednesday, February 04, 2015

Wednesday, February 04, 2015

Wednesday, February 04, 2015

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

Brook_BH

Brook_BH

Brook_BH

1

13 106

13 106

13 106

-1M

-1M

-1M

Page 12

5

Dr-Bios.com

3D3V_S0

D D

R1533

R1533

12

8K2R2J-3-GP

RN1504

RN1504

SRN10KJ-6-GP

SRN10KJ-6-GP

1

2

3

4 5

RN1505

RN1505

SRN10KJ-L-GP

SRN10KJ-L-GP

1

2 3

C C

8

7

6

4

8K2R2J-3-GP

INT_PIRQC#

WLAN_CLKREQ_CPU#

INT_PIRQB#

INT_PIRQD#

20141014 Rober

PSW_CLR#

LAN_DIS#

eDP_BLCTRL_CPU55

eDP_BLEN_CPU24

eDP_VDDEN_CPU55

INT_PIRQA#20

DGPU_HOLD_RST#76,79

DGPU_PWR_EN#86,87

TP_IN#20,65

DGPU_PWROK24,85,86

WLAN_CLKREQ_CPU# 18,61,89

LAN_DIS# 20

INT_PIRQA#

INT_PIRQB#

INT_PIRQC#

INT_PIRQD#

PSW_CLR#

4

PEG_CLKREQ_CPU# 18,76

CPU1I

CPU1I

B8

EDP_BKLCTL

A9

EDP_BKLEN

C6

EDP_VDDEN

U6

PIRQA#/GPIO77

P4

PIRQB#/GPIO78

N4

PIRQC#/GPIO79

N2

PIRQD#/GPIO80

AD4

PME#

U7

GPIO55

L1

GPIO52

L3

GPIO54

R5

GPIO51

L4

GPIO53

eDP SIDEBAND

eDP SIDEBAND

PCIE

PCIE

3

HSW_ULT_DDR3L

HSW_ULT_DDR3L

DISPLAY

DISPLAY

9 OF 19

9 OF 19

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

B9

C9

D9

D11

2

3D3V_S0

4

1

2 3

RN1506

RN1506

SRN2K2J-5-GP

SRN2K2J-5-GP

HDMI_CLK_CPU 57

HDMI_DATA_CPU 57

DP_CLK_CPU

DP_CLK_DATA

1

3D3V_S0

23

1

4

11/19 pull high DDPCCTRLCLK & DATA

C5

B6

B5

A6

C8

A8

D6

HDMI_DET_CPU 57

eDP_HPD_CPU 55

PCH_DPC_AUXN 56

PCH_DPC_AUXP 56

CRT_PCH_HPD 56

RN1509

RN1509

SRN2K2J-5-GP

SRN2K2J-5-GP

HASWELL-6-GP-U

B B

eDP_BLEN_CPU

R1501

R1501

100KR2J-4-GP

100KR2J-4-GP

1 2

RN1503

RN1503

SRN10KJ-L-GP

DGPU_PWR_EN#

DGPU_HOLD_RST#

A A

SRN10KJ-L-GP

1

2 3

4

5

4

HASWELL-6-GP-U

PSW_CLR#

21

Pass Word Clear

G1501

G1501

GAP-OPEN

GAP-OPEN

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

CPU(EDP SIDEBAND/GPIO/DDI)

CPU(EDP SIDEBAND/GPIO/DDI)

CPU(EDP SIDEBAND/GPIO/DDI)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A4

A4

A4

Date: Sheet

Date: Sheet

3

Date: Sheet of

application without get Wistron permission

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Brook_BH

Brook_BH

Wednesday, February 04, 2015

Wednesday, February 04, 2015

Wednesday, February 04, 2015

2

Brook_BH

15 106

of

15 106

of

15 106

1

-1M

-1M

-1M

Page 13

5

Dr-Bios.com

4

3

2

1

4!/*6&aT$

CPU1K

CPU1K

P?4*?@P*/4!

D D

5AF*

C C

c5AF

b,0*3&)V$TT*8+*D&%$0&

PEG_RX_ CPU_N076

PEG_RX_ CPU_P076

PEG_TX_ CON_N076

PEG_TX_ CON_P076

PEG_RX_ CPU_N176

PEG_RX_ CPU_P176

PEG_TX_ CON_N176

PEG_TX_ CON_P176

PEG_RX_ CPU_N276

PEG_RX_ CPU_P276

PEG_TX_ CON_N276

PEG_TX_ CON_P276

PEG_RX_ CPU_N376

PEG_RX_ CPU_P376

PEG_TX_ CON_N376

PEG_TX_ CON_P376

PCIE_RX_C PU_N331

PCIE_RX_C PU_P331

PCIE_TX_L AN_N331

PCIE_TX_L AN_P331

PCIE_RX_C PU_N461,8 9

PCIE_RX_C PU_P46 1,89

PCIE_TX_W LAN_N461,89

PCIE_TX_W LAN_P461,89

b,0*/0,&[V$TT*8+*D&%$0&

PCIE_RX_C PU_N237

PCIE_RX_C PU_P237

PCIE_TX_U SB_N237

PCIE_TX_U SB_P237

PX

PX

C1605 SCD1U16 V2KX-L-GP

C1605 SCD1U16 V2KX-L-GP

1 2

C1606 SCD1U16 V2KX-L-GP

C1606 SCD1U16 V2KX-L-GP

1 2

PX

PX

PX

PX

C1607 SCD1U16 V2KX-L-GP

C1607 SCD1U16 V2KX-L-GP

1 2

C1608 SCD1U16 V2KX-L-GP

C1608 SCD1U16 V2KX-L-GP

1 2

PX

PX

PX

PX

C1613 SCD1U16 V2KX-L-GP

C1613 SCD1U16 V2KX-L-GP

1 2

C1614 SCD1U16 V2KX-L-GP

C1614 SCD1U16 V2KX-L-GP

1 2

PX

PX

PX

PX

C1615 SCD1U16 V2KX-L-GP

C1615 SCD1U16 V2KX-L-GP

1 2

C1616 SCD1U16 V2KX-L-GP

C1616 SCD1U16 V2KX-L-GP

1 2

PX

PX

C1621 SCD1U16 V2KX-L-GPC1621 SCD1U16 V2KX-L-GP

1 2

C1622 SCD1U16 V2KX-L-GPC1622 SCD1U16 V2KX-L-GP

1 2

C1619 SCD1U16 V2KX-L-GPC1619 SCD1U16 V2KX-L-GP

1 2

C1620 SCD1U16 V2KX-L-GPC1620 SCD1U16 V2KX-L-GP

1 2

USB30_R X_CPU_N338

USB30_R X_CPU_P338

USB30_T X_CPU_N338

USB30_T X_CPU_P33 8

C1623 SCD1U16 V2KX-L-GP

C1623 SCD1U16 V2KX-L-GP

1 2

C1624 SCD1U16 V2KX-L-GP

C1624 SCD1U16 V2KX-L-GP

1 2

1D05V_V CCUSB3PLL_S0

HW_3D

HW_3D

HW_3D

HW_3D

R1601

R1601

3K01R2F -3-GP

3K01R2F -3-GP

1 2

PEG_TX_ CPU_N0

PEG_TX_ CPU_P0

PEG_TX_ CPU_N1

PEG_TX_ CPU_P1

PEG_TX_ CPU_N2

PEG_TX_ CPU_P2

PEG_TX_ CPU_N3

PEG_TX_ CPU_P3

PCIE_TX_C PU_N3

PCIE_TX_C PU_P3

PCIE_TX_C PU_N4

PCIE_TX_C PU_P4

PCIE_TX_C PU_N2

PCIE_TX_C PU_P2

PCIE_COMP

F10

PERN5_L0

E10

PERP5_L0

C23

PETN5_L0

C22

PETP5_L0

F8

PERN5_L1

E8

PERP5_L1

B23

PETN5_L1

A23

PETP5_L1

H10

PERN5_L2

G10

PERP5_L2

B21

PETN5_L2

C21

PETP5_L2

E6

PERN5_L3

F6

PERP5_L3

B22

PETN5_L3

A21

PETP5_L3

G11

PERN3

F11

PERP3

C29

PETN3

B30

PETP3

F13

PERN4

G13

PERP4

B29

PETN4

A29

PETP4

G17

PERN1/USB3RN3

F17

PERP1/USB3RP3

C30

PETN1/USB3TN3

C31

PETP1/USB3TP3

F15

PERN2/USB3RN4

G15

PERP2/USB3RP4

B31

PETN2/USB3TN4

A31

PETP2/USB3TP4

E15

RSVD#E15

E13

RSVD#E13

A27

PCIE_RCOMP

B27

PCIE_IREF

HSW_ULT_DDR3L

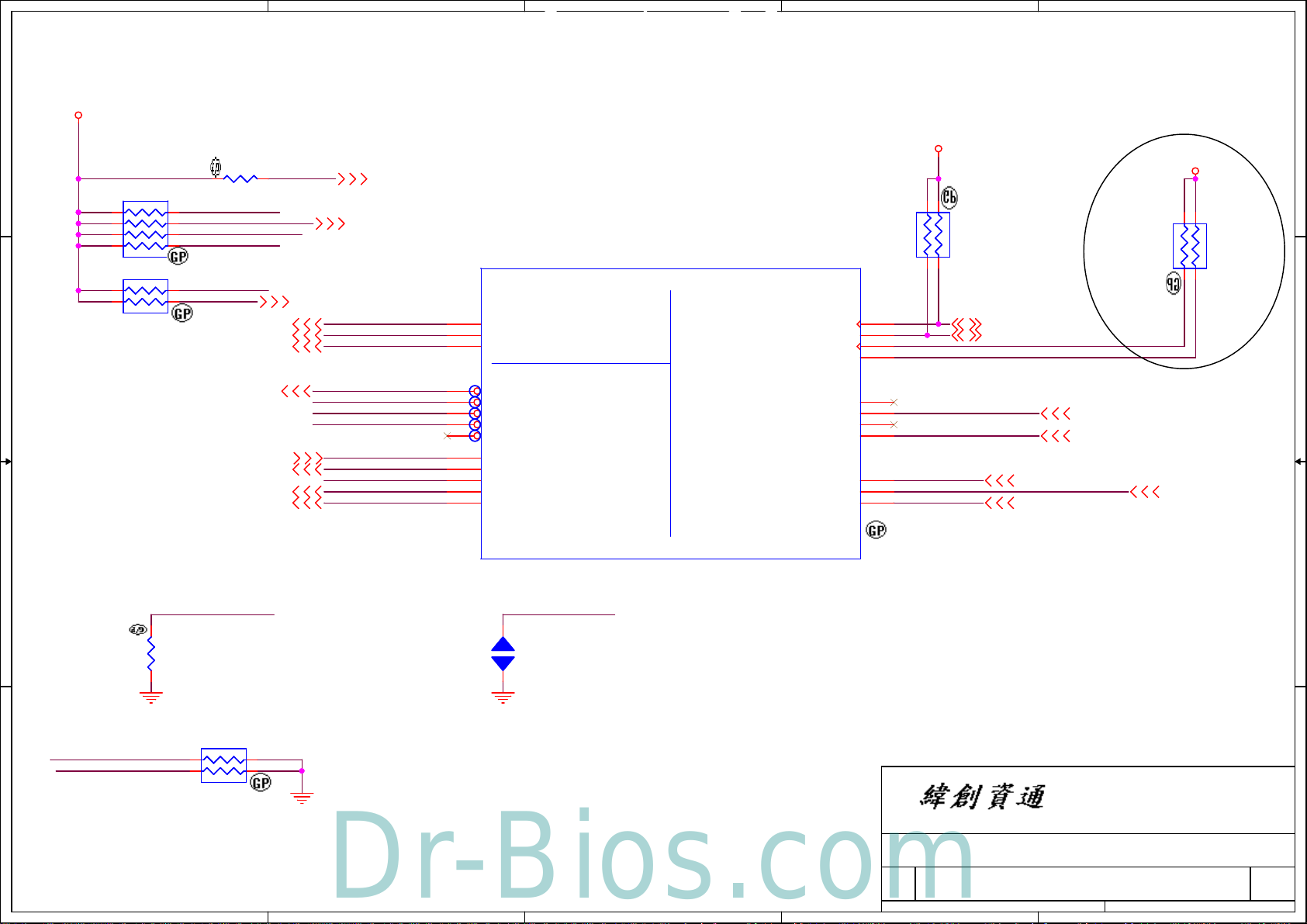

PCIE USB

PCIE USB

11 OF 19

11 OF 19

USB2N0

USB2P0

USB2N1

USB2P1

USB2N2

USB2P2

USB2N3

USB2P3

USB2N4

USB2P4

USB2N5

USB2P5

USB2N6

USB2P6

USB2N7

USB2P7

USB3RN1

USB3RP1

USB3TN1

USB3TP1

USB3RN2

USB3RP2

USB3TN2

USB3TP2

USBRBIAS#

USBRBIAS

RSVD#AN10

RSVD#AM10

OC0/GPIO40#

OC1/GPIO41#

OC2/GPIO42#

OC3/GPIO43#

AN8

AM8

AR7

AT7

AR8

AP8

AR10

AT10

AM15

AL15

AM13

AN13

AP11

AN11

AR13

AP13

G20

H20

C33

B34

E18

F18

B33

A33

AJ10

AJ11

AN10

AM10

AL3

AT1

AH2

AV3

USB_RBIAS

USB_OC#

USB_CPU _PN0 36

USB_CPU _PP0 36

USB_CPU _PN1 35

USB_CPU _PP1 35

USB_CPU _PN2 66

USB_CPU _PP2 6 6

USB_CPU _PN3 66

USB_CPU _PP3 6 6

USB_CPU _PN4 61,89

USB_CPU _PP4 61,89

USB_CPU _PN5 55

USB_CPU _PP5 55

USB_CPU _PN6 55

USB_CPU _PP6 5 5

USB_CPU _PN7 33

USB_CPU _PP7 33

USB30_R X_CPU_N1 35,8 9

USB30_R X_CPU_P1 35,89

USB30_T X_CPU_N1 3 5

USB30_T X_CPU_P1 35

USB30_R X_CPU_N2 35,8 9

USB30_R X_CPU_P2 35,89

USB30_T X_CPU_N2 3 5

USB30_T X_CPU_P2 35

R1611

R1611

22D6R2F -L1-GP

22D6R2F -L1-GP

1 2

3D3V_SU S

R1602

R1602

10KR2J-L -GP

10KR2J-L -GP

1 2

0

1

4!/*Y,0'J

4!/*Y,0'>

4!/*Y,0'<

4!/*Y,0'8

/6

2

3

4

5

6

7

6E4D3*!DC@@F

DD+

D&0[*C$&[$0

4!/*8^J*Y,0'J

4!/*8^J*Y,0'>

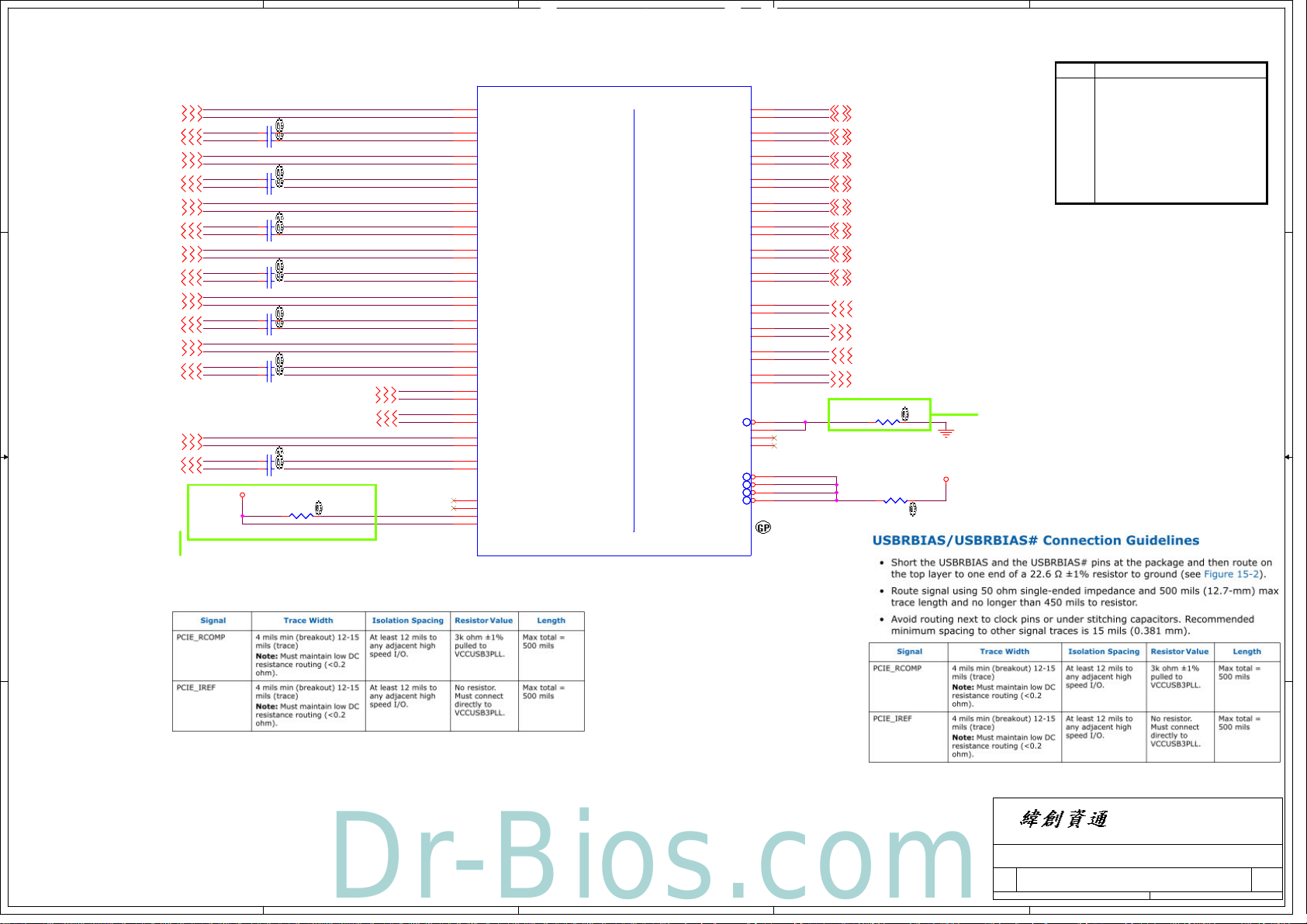

Layout Note:

1. USB_COMP usi ng 50 ohm singl e-ended impeda nce

2. Isolation Sp acing :15mil

3. Total trace length<500mil

HSW_ULT_DDR3L

Pair

Device

4!/8^J*?,0'J

4!/8^J*?,0'>

4!/8^J*?,0'<

4!/8^J*?,0'8

/6

6E4D3*!DC@@F

DD+

D&0[*C$&[$0

HASW ELL-6-GP-U

B B

A A

Layout Note:

1. PCIE_RCOMP/ PCIE_IREF trace width=12~15mi l

2. Isolation Sp acing: 12mil

3. Total trace length<500mil

5

4

HASW ELL-6-GP-U

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

Brook_BH

Brook_BH

Brook_BH

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

application without get Wistron permission

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec .1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CPU (PCI/USB)

CPU (PCI/USB)

CPU (PCI/USB)

Brook_BH

Brook_BH

Wednesd ay, February 04, 2015

Wednesd ay, February 04, 2015

Wednesd ay, February 04, 2015

Brook_BH

16 106

16 106

16 106

1

-1M

-1M

-1M

Page 14

5

Dr-Bios.com

4

3

2

1

DSWODVREN - On Die DSW VR Enable

R1728

SYS_PW ROK24

PLTRST# _PCH24,31,37,4 0,61,63,68,89,91

1 2

1

2

3

4 5

PCH_PW ROK40

PCH_PW ROK

EC1701

EC1701

R1728

10KR2J-L -GP

10KR2J-L -GP

RN1712

RN1712

8

7

6

SRN10KJ -6-GP

SRN10KJ -6-GP

20141216 -1

12

PM_SUS_ STAT#

MSATA_P EDET2

SYS_RESET #

MSATA_P EDET1

R1724 0R0402-PAD-1-GPR1724 0R0402-PAD-1-GP

1 2

DY

DY

MSATA_P EDET2 19

MSATA_P EDET1 19

PM_SUSW ARN#24

PM_PW RBTN#20,24,89

AC_PRES ENT24

R1727

R1727

10KR2J-L -GP

10KR2J-L -GP

1 2

HSW_ULT_DDR3L

CPU1H

CPU1H

PM_SUSA CK#24

BATLOW #20

PM_SUSA CK#

SYS_RESET #

SYS_PW ROK_R

PM_RSMR ST#

PM_SUSW ARN#

BATLOW #

AK2

SUSACK#

AC3

SYS_RESET#

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST#

AW6

RSMRST#

AV4

SUSWARN#/SUSPWRDNACK#/GPIO30

AL7

PWRBTN#

AJ8

ACPRESENT/GPIO31

AN4

BATLOW#/GPIO72

AF3

SLP_S0#

AM5

SLP_WLAN#/GPIO29

HSW_ULT_DDR3L

SYSTEM POWER MANAGEMENT

SYSTEM POWER MANAGEMENT

SUS_STAT#/GPIO61

8 OF 19

8 OF 19

DSWVRMEN

DPWROK

WAKE#

CLKRUN#/GPIO32

SUSCLK/GPIO62

SLP_S5#/GPIO63

SLP_S4#

SLP_S3#

SLP_A#

SLP_SUS#

SLP_LAN#

AW7

AV5

AJ5

V5

AG4

AE6

AP5

AJ6

AT4

AL5

AP4

AJ7

DSWO DVREN

PCH_DPW ROK

SUS_CLK _CPU

PM_SLP_ SUS#

R1739

R1739

1 2

0R0402-P AD-1-GP

0R0402-P AD-1-GP

D D

3D3V_SU S

3D3V_S0

C C

AZ5325-0 1FDR7G-GP

AZ5325-0 1FDR7G-GP

HIGH Enabled (DEFAULT)

LOW Disabled

3D3V_RT C_AUX

R1717

R1717

1 2

330KR2J -L-GP

330KR2J -L-GP

DSWO DVREN

PM_RSMR ST#

PCH_PCIE_ WAKE# 24,31,61,63

PM_CLKR UN#_EC 24,9 1

PM_SUS_ STAT# 91

SUS_CLK _CPU 61,63

PM_SLP_ S4# 24,49

PM_SLP_ S3# 24,40,4 8,51

PM_SLP_ SUS# 2 4,39

PLTRST# _PCH

12

EC1702

AZ5325-0 1FDR7G-GP

AZ5325-0 1FDR7G-GP

B B

EC1702

DY

DY

Cloes to CPU

3D3V_S5

A A

RN1701

RN1701

SRN10KJ -6-GP

SRN10KJ -6-GP

1

2

3

4 5

8

AC_PRES ENT

7

RTC_DET #

6

PCH_PCIE_ WAKE#

MCP_GPIO1 2 20

RTC_DET # 20,2 5

PCH_PCIE_ WAKE# 24,31,61,63

DY

DY

R1738

R1738

0R2J-L-GP

0R2J-L-GP

1 2

PM_SUSA CK#PM_SUSW ARN#

3D3V_AU X_S5

R1716

R1716

10KR2J-L -GP

10KR2J-L -GP

1 2

3V_5V_P OK_#

5

4

HASW ELL-6-GP-U

HASW ELL-6-GP-U

Non_DS3

Non_DS3

R1709

R1709

100KR2J -4-GP

100KR2J -4-GP

1 2

5

6

Q1701

Q1701

34

2

1

2N7002K DW-GP

2N7002K DW-GP