Acer Aspire Z1-621G Schematics

1

www.vinafix.vn

2

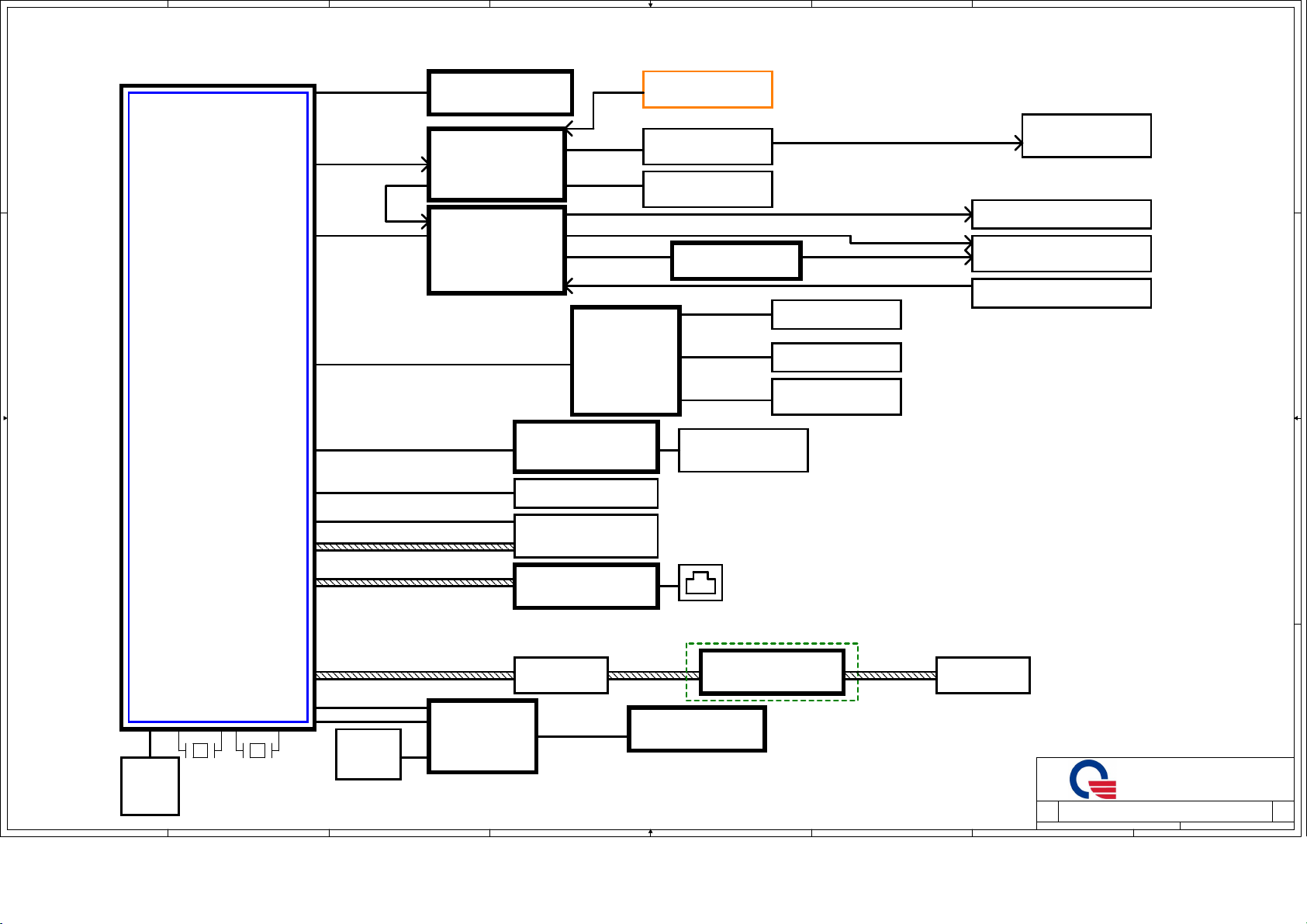

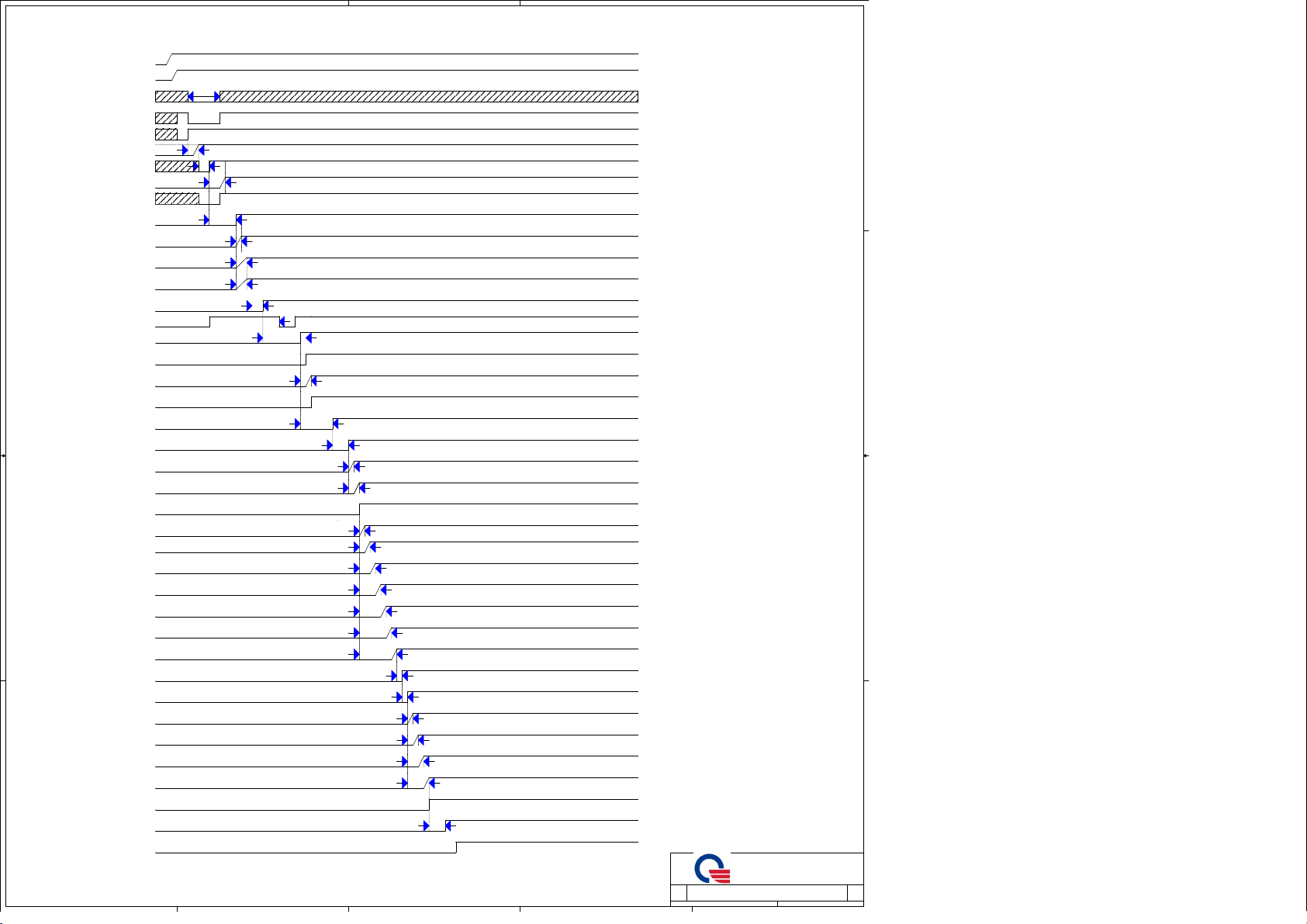

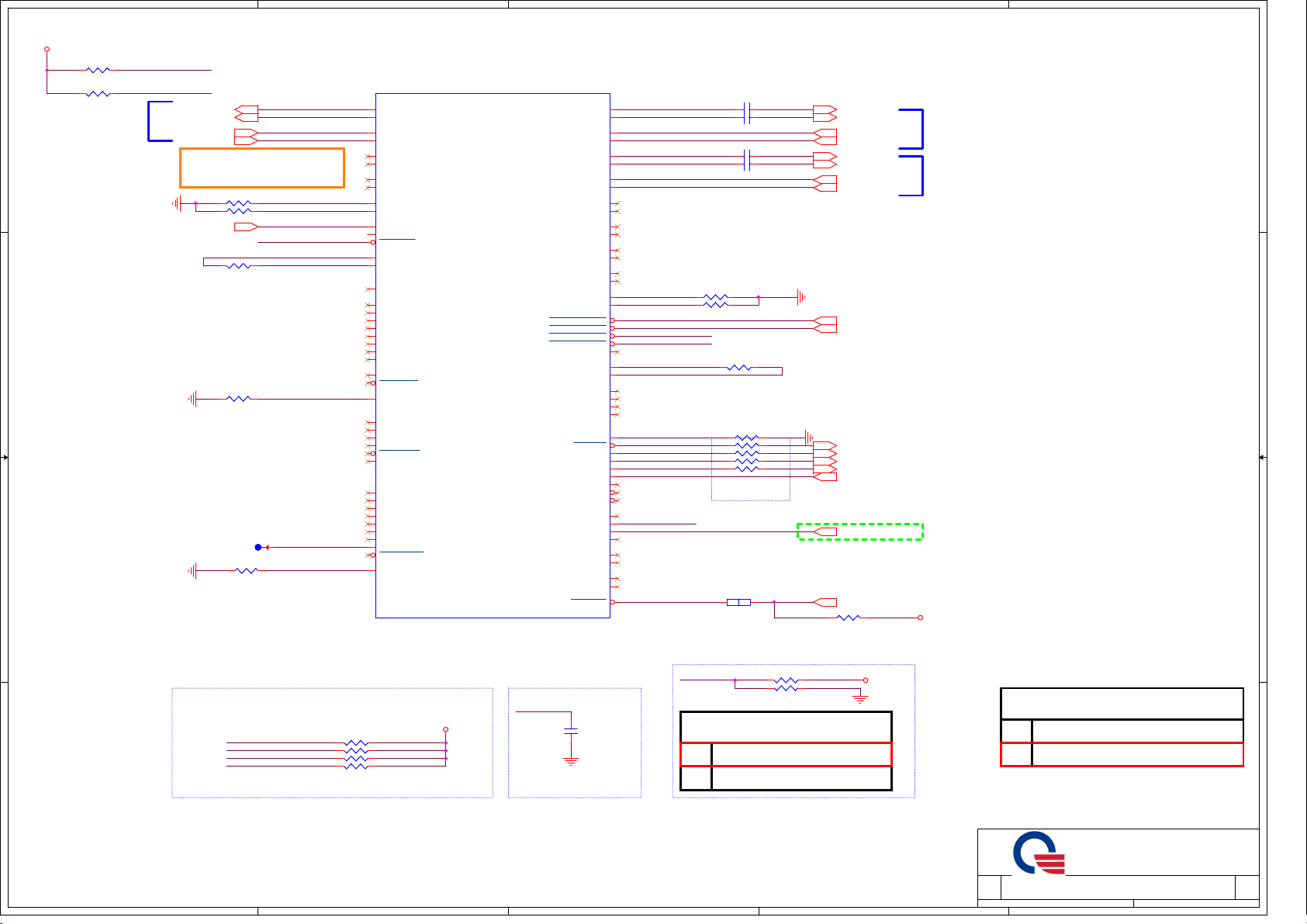

UI2H BLOCK DIAGRAM

3

4

5

6

7

8

1333 MT/s

A A

DVI DDI0

SO-DIMM

Scalar

NT68772

I2S

HDMI

LVDS

AD PIN

HDMI IN Conn

Panel Conn

BOTTON

LVDS

LVDS Panel

Headphone

HDA

Bay Trail M

B B

USB2.0 PORT0

FBGA 1170 Ball

Power : 4.5 (Watt)

25mm*27mm

C C

USB2.0

USB2.0

USB2.0

Codec

ALC290Q

PORT2

PORT1

PORT3

PORT1PCIE

MONO

USB HUB

GL850G

Card Reader

RTL5170

USB conn (debug)

WIFI+BT (HMC)

AMP

APA2619

HUB PORT0

HUB PORT1

HUB PORT2,3

SD Connector

SPK+ Woofer Conn

DMIC (CCD conn)

Touch Screen

Camera

USB Conn *2

PCIE PORT2

LAN

RTL8106E

SATA BD

SATA

PORT0

WTB Conn

LPC

D D

SPI

ROM

24MHz

32.768KHz

SMBUS

ROM

512K

KBC

ITE 8528E

SMBUS

Thermal IC

NCT7718W

8M

1

2

3

4

SATA redriver

PS8520B

5

SATA Conn

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

6

Wednesday, July 30, 2014

7

PROJECT :

Block Diagram

Block Diagram

Block Diagram

UI2H

UI2H

UI2H

148

148

148

8

1B

1B

1B

1

2

3

4

5

6

7

8

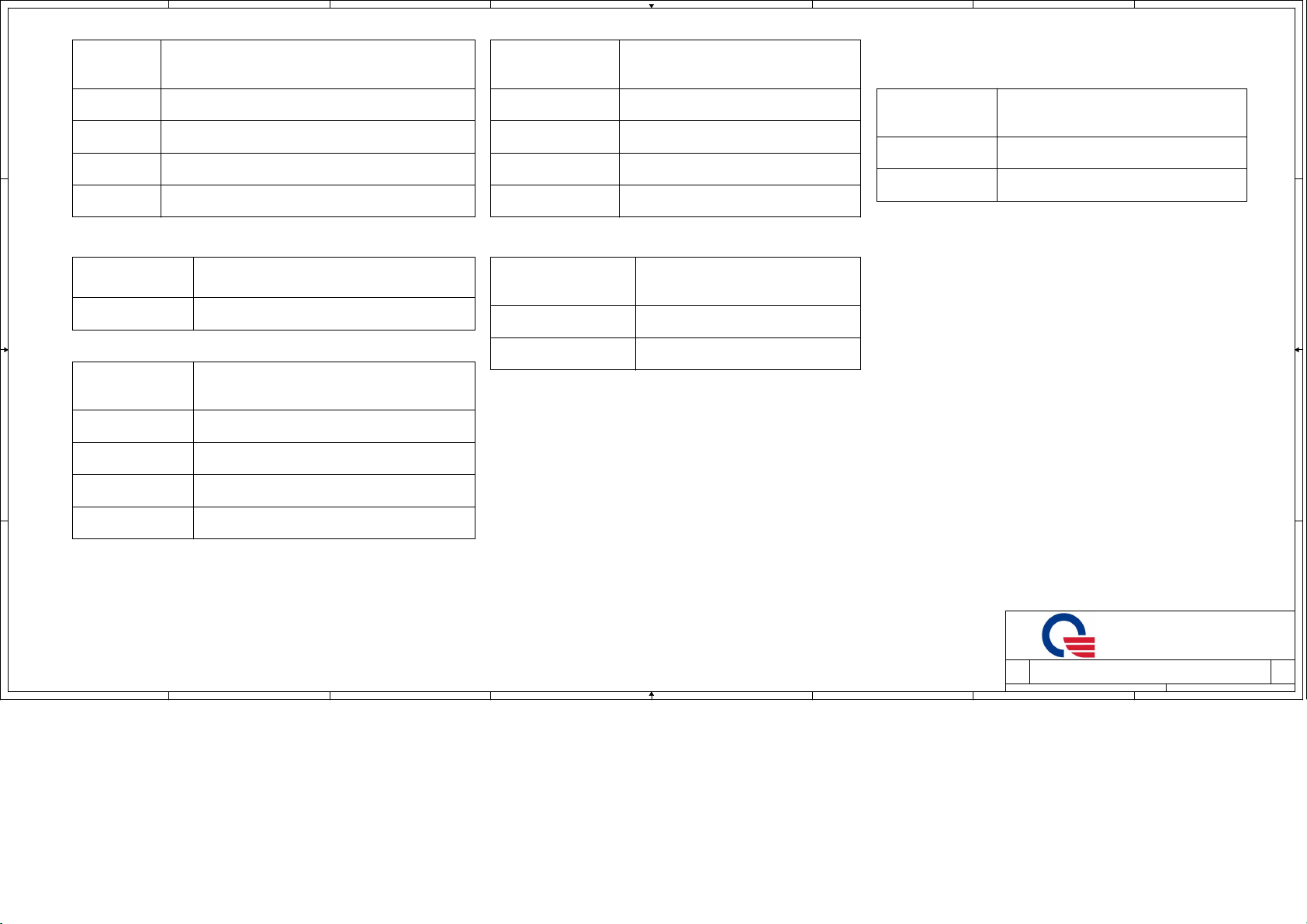

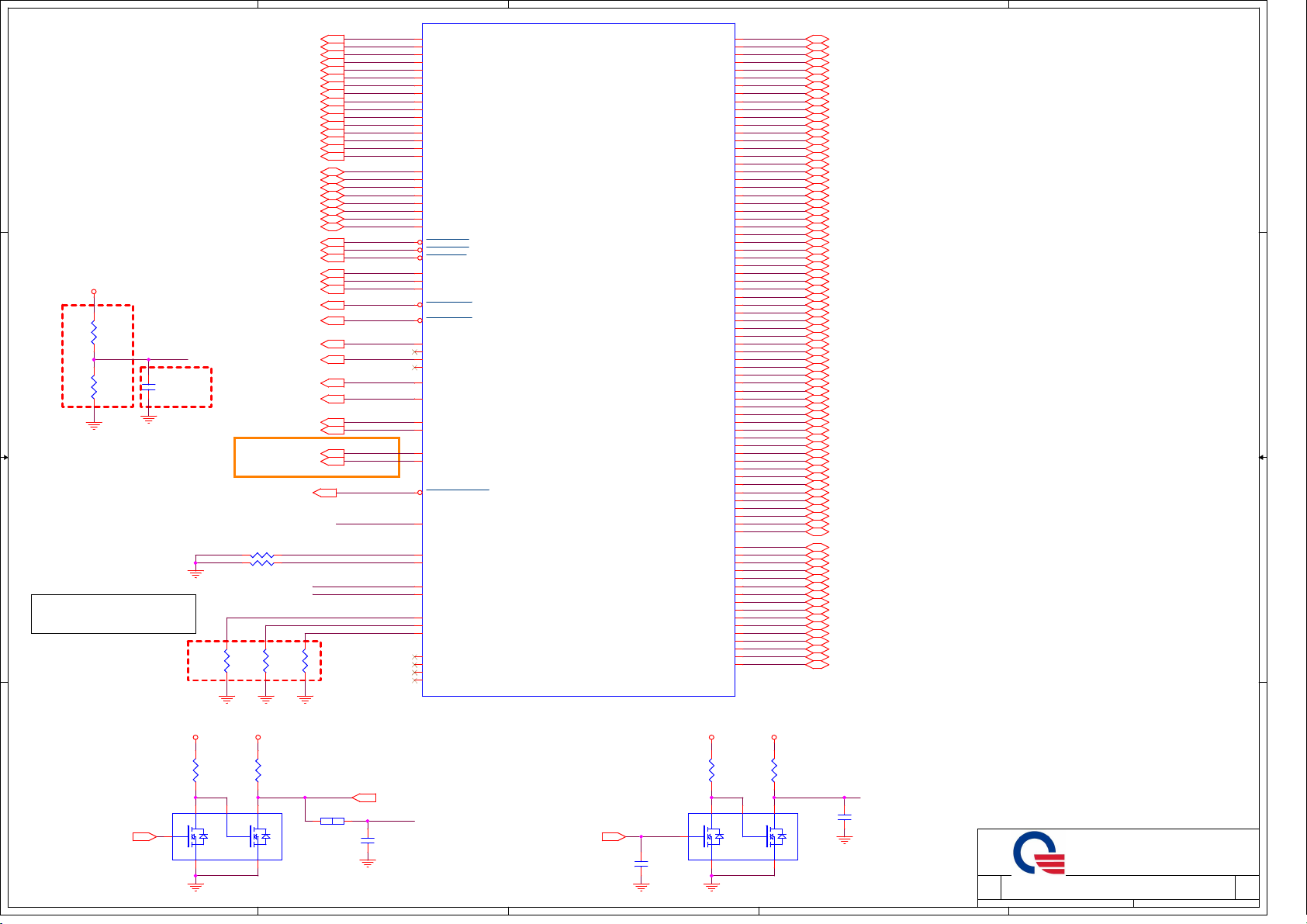

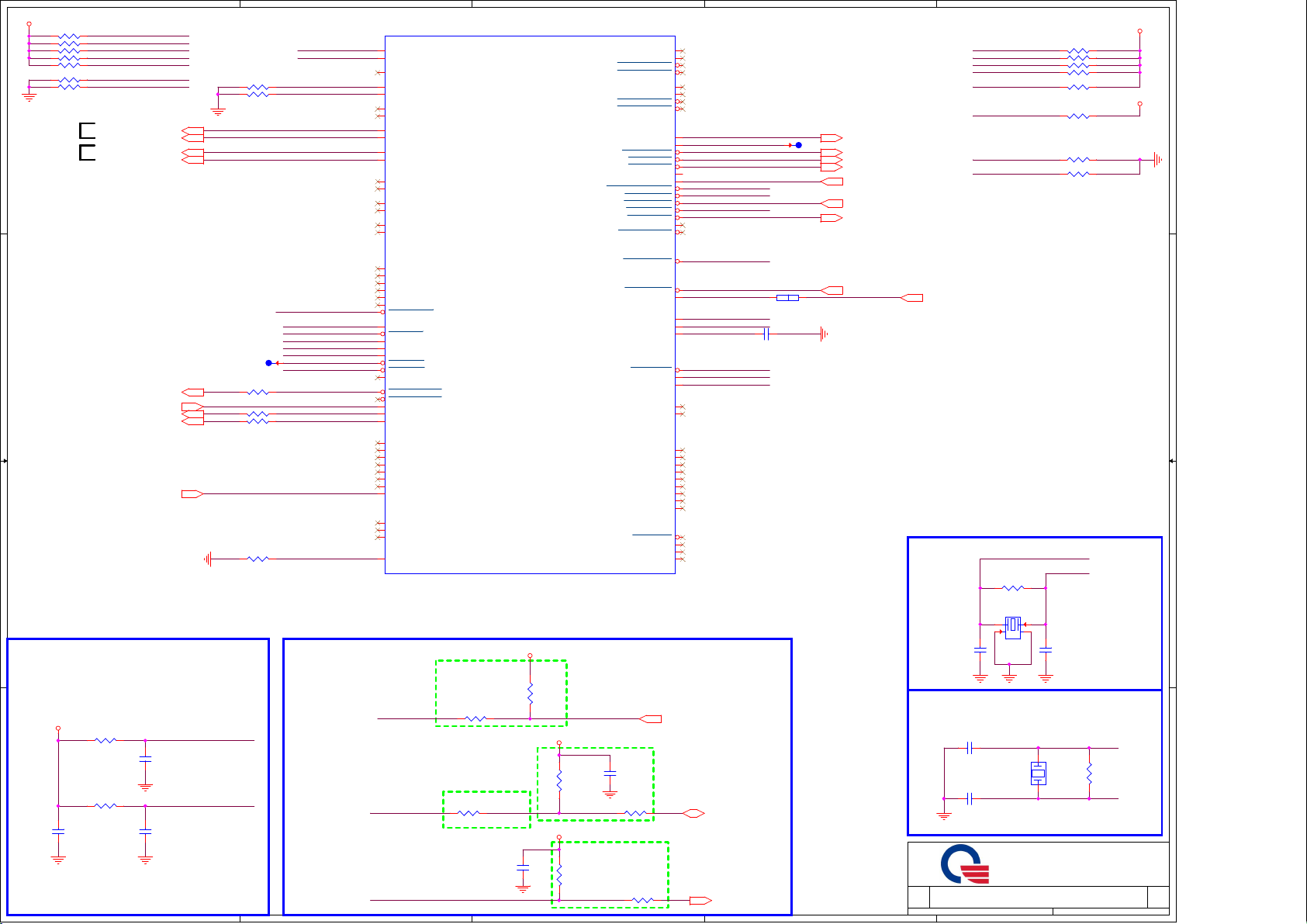

Port AssignmentUSB 2.0

A A

USBP0

USBP1

USBP2

USB HUB

USB CONN

CARDREADER

PCIE 0

PCIE 1

PCIE 2

Port AssignmentPCIE Master

WLAN/BT

LAN

SATA0

(NC)

Port AssignmentSATA Master

HDD

SATA1 NC

USBP3

B B

USBP0

BT

Port AssignmentUSB 3.0

NC

PCIE 3

DDI0

(NC)

Port AssignmentDisplay Port

DVI

DDI1 NC

Port AssignmentUSB HUB

C C

USBP1

USBP2

USBP3

Touch Screen

Camera Front

Connector 1

USBP4 Connector 1

D D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

1

2

3

4

5

6

Wednesday, July 30, 2014

7

PROJECT :

PORT ASSIGNMENT

PORT ASSIGNMENT

PORT ASSIGNMENT

UI2H

UI2H

UI2H

248

248

248

8

1B

1B

1B

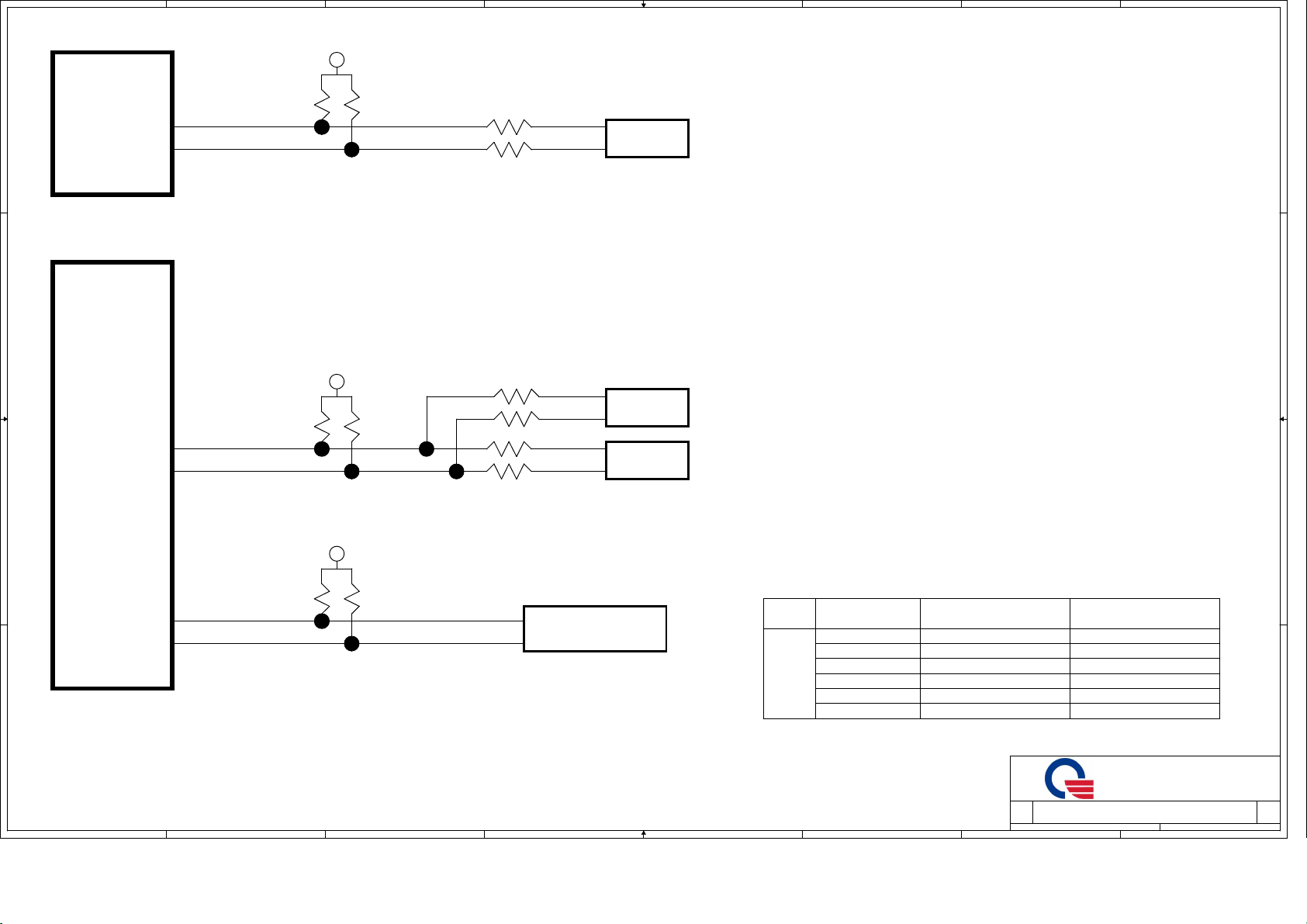

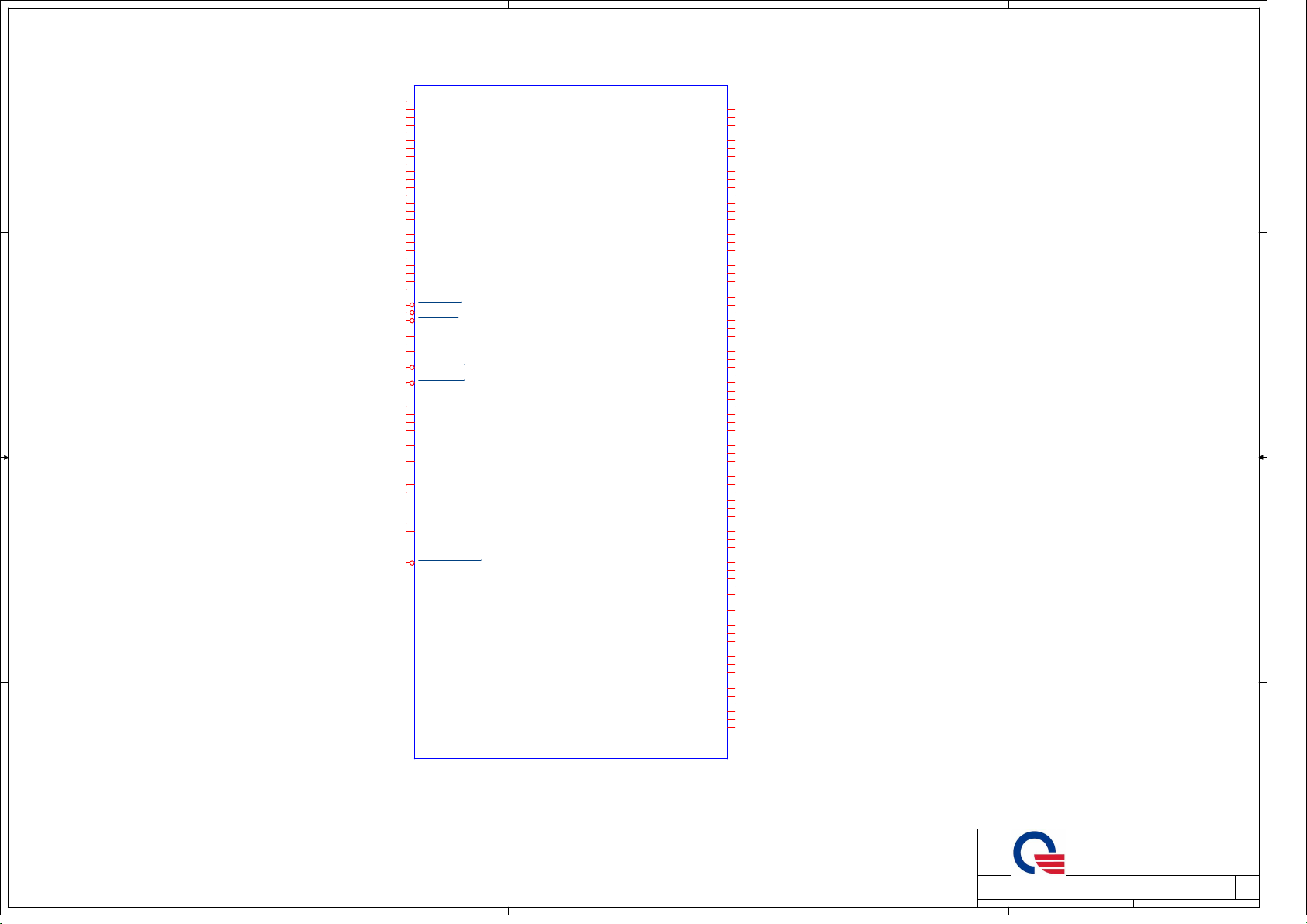

JW8B

1

MB

2

3

4

5

6

7

8

+1.8V_RUN

*4.7K_NC*4.7K_NC

A A

Bay Trail

M

B B

MB

SMB_SOC_CLK

BH10

SMB_SOC_DATA

BG12

0

0

SO-DIMM

+3.3V_ALW

100

SIO

4.7K4.7K

ITE8528E

C C

110

SMBCLK0

111 SMBDAT0

100

0

0

B7

B6

9

8

Battery

Charger

+3.3V_RUN

4.7K4.7K

94

SMBCLK3

95

SMBDAT3

D D

1

2

3

8

THERMAL(NCT7718)

7

4

Function

Thermal IC

SMBUS

Charge IC

Battery

5

6

NCT7718 1001100xb (98h)

Battery 00010110 (0X16h)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

Wednesday, July 30, 2014

7

AddressIC

00010010 (0x12h)BQ24737RGRR

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

SMBUS

SMBUS

SMBUS

UI2H

UI2H

UI2H

1B

1B

348

348

348

8

1B

5

4

3

2

1

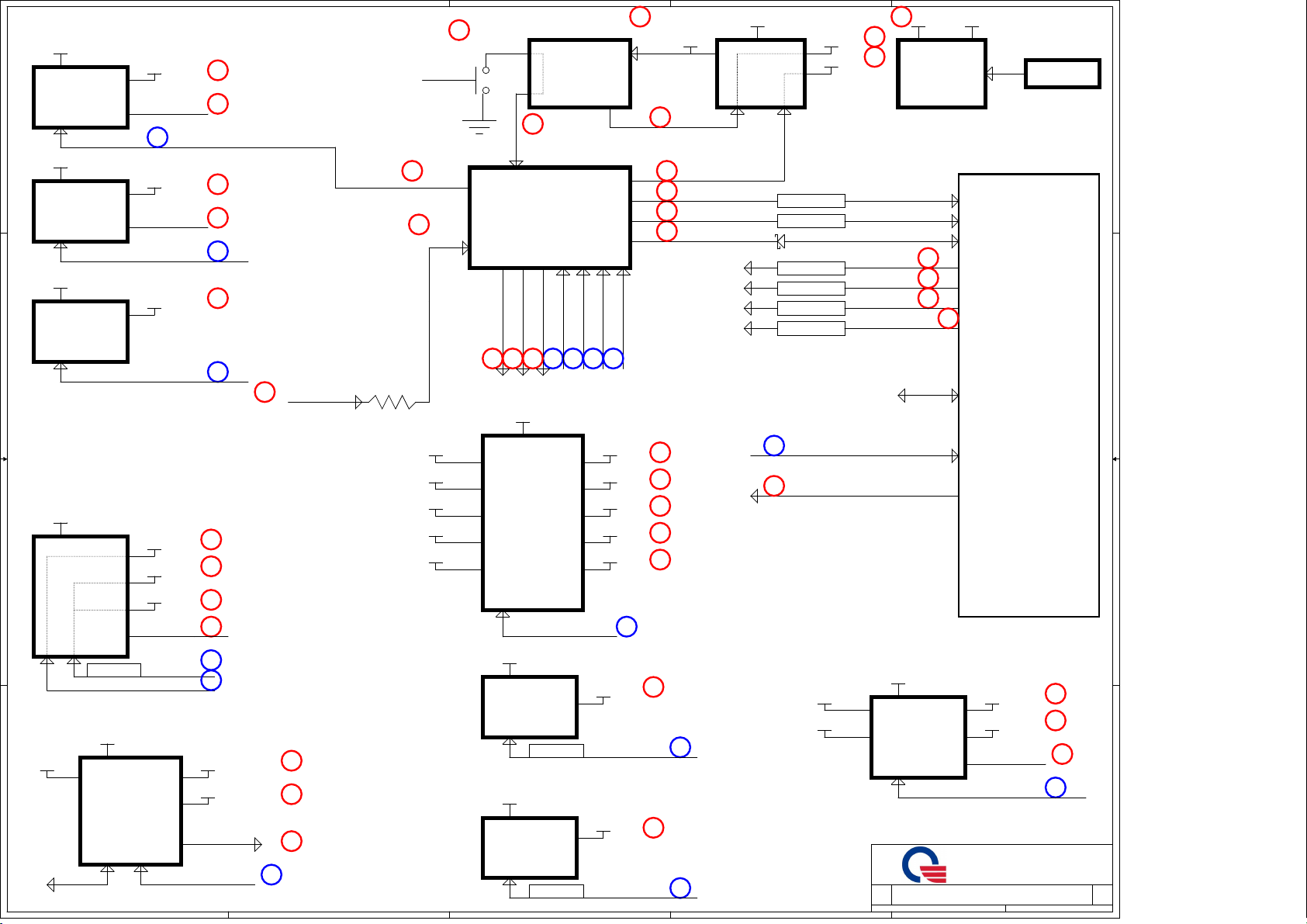

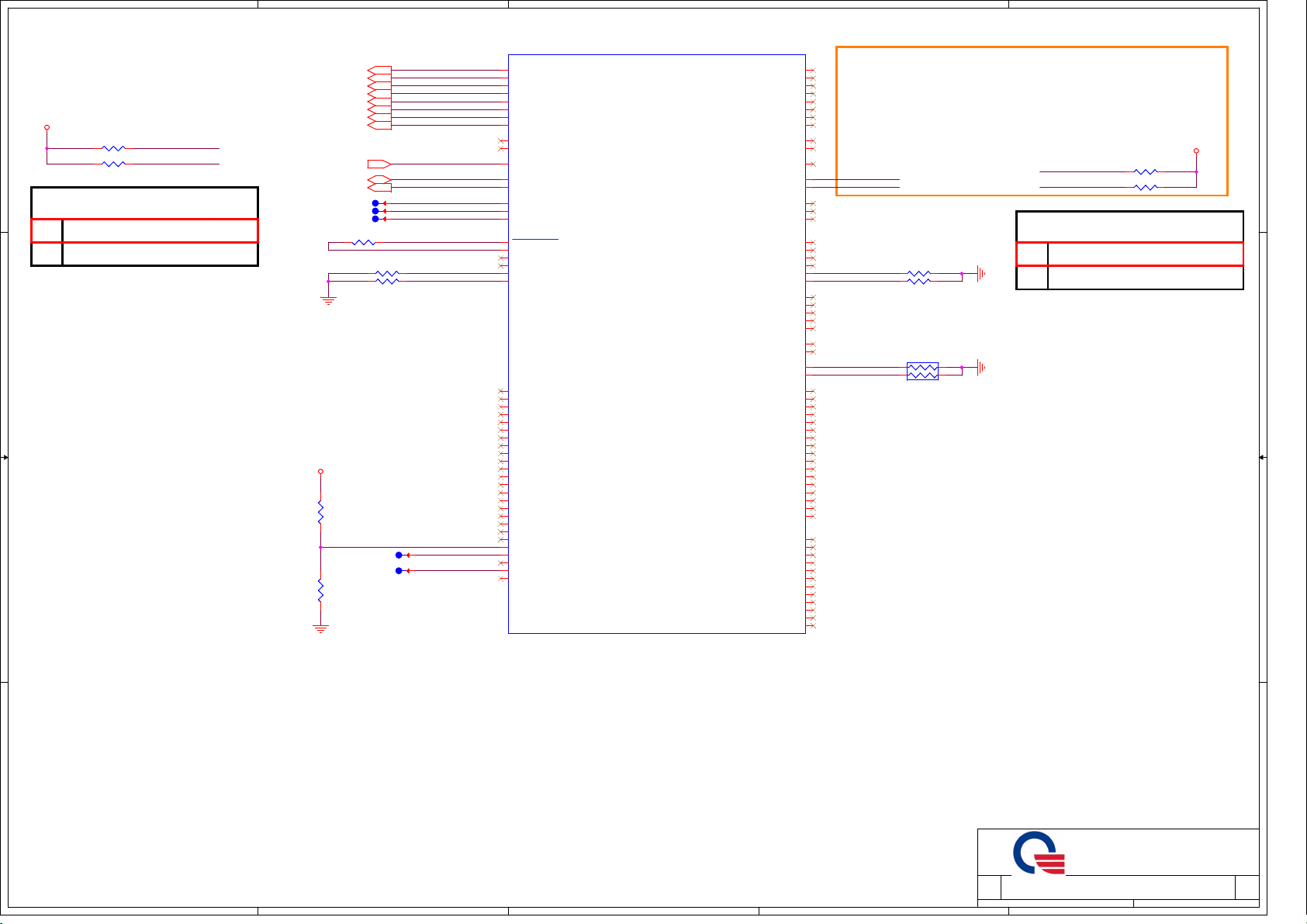

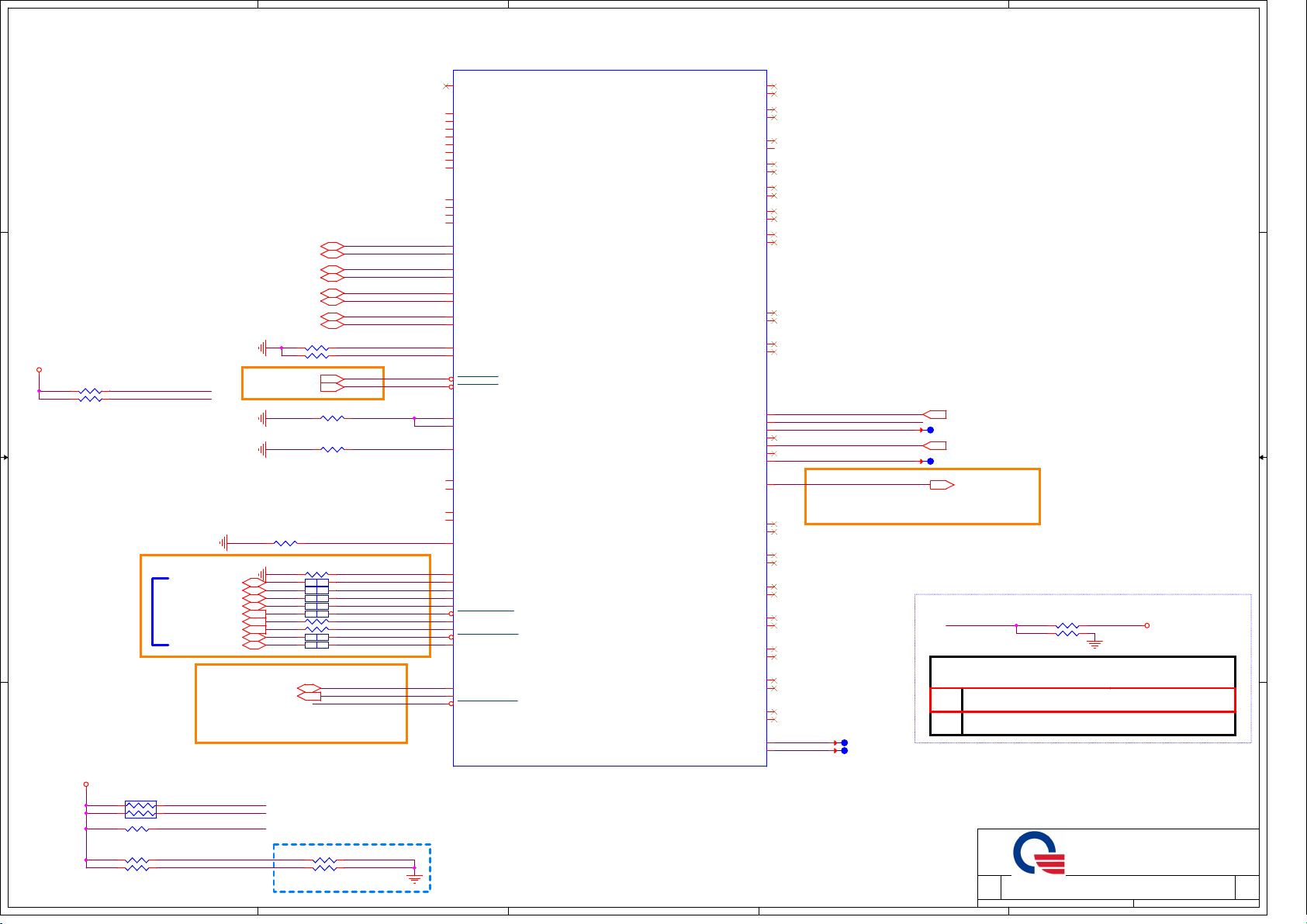

Adapter 65W

VER : 1A

04

Charger

(BQ24737RGRR)

D D

Battery 3S1P

ALW_ON

MPS

NB671L

C C

+5V_ALW

Load Switch

FDC655BN_G

B B

+5V_RUN

+PWR_SRC

+15V_ALW

1.8V_SUS_PWRGD

+3.3V_SUS

+3.3V_EN2

MPS

NB670

+3.3V_ALW

Load Switch

FDMC8884

IMVP_PWRGDIMVP_PWRGD

+3.3V_RUN

ANPEC

APW8824

+1.05V_RUN

RUN_ON

+VCC_CORE

ANPEC

APW8824

+1.5V_RUN

INTERSIL

ISL95833HRTZ

RUN_ON

GMT

G9661-25ADJF12U

RUN_ON

+VCC_GFX_CORE

1.0V_SUS_PWRGD

+1.8V_SUS

+DDR_VTT

ANPEC

APW8804QBI

+1.0V_SUS

SUS_ON

SLP_S0IX#ON

ANPEC

APW8819QAI

IMVP_PWRGD

SIO_SLP_S4#

Load Switch

FDC655BN_G

+1.35V_RUN

+V_VDDQ

SLP_S0IX#_ON

Load Switch

FDC655BN_G

+1.35V_VSFR

IMVP_PWRGD

Load Switch

FDC655BN_G

Load Switch

RQ3E150BNFU7TB

+1.8V_RUN

A A

5

4

3

IMVP_PWRGD SLP_S0IX#_ON

Load Switch

RQ3E150BNFU7TB

+1.0V_RUN

2

+1.0V_SX

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, July 30, 2014 4 48

Date: Sheet of

Wednesday, July 30, 2014 4 48

Date: Sheet of

Wednesday, July 30, 2014 4 48

PROJECT :

Power Block Diagram

Power Block Diagram

Power Block Diagram

UI2H

UI2H

UI2H

1

1B

1B

1B

5

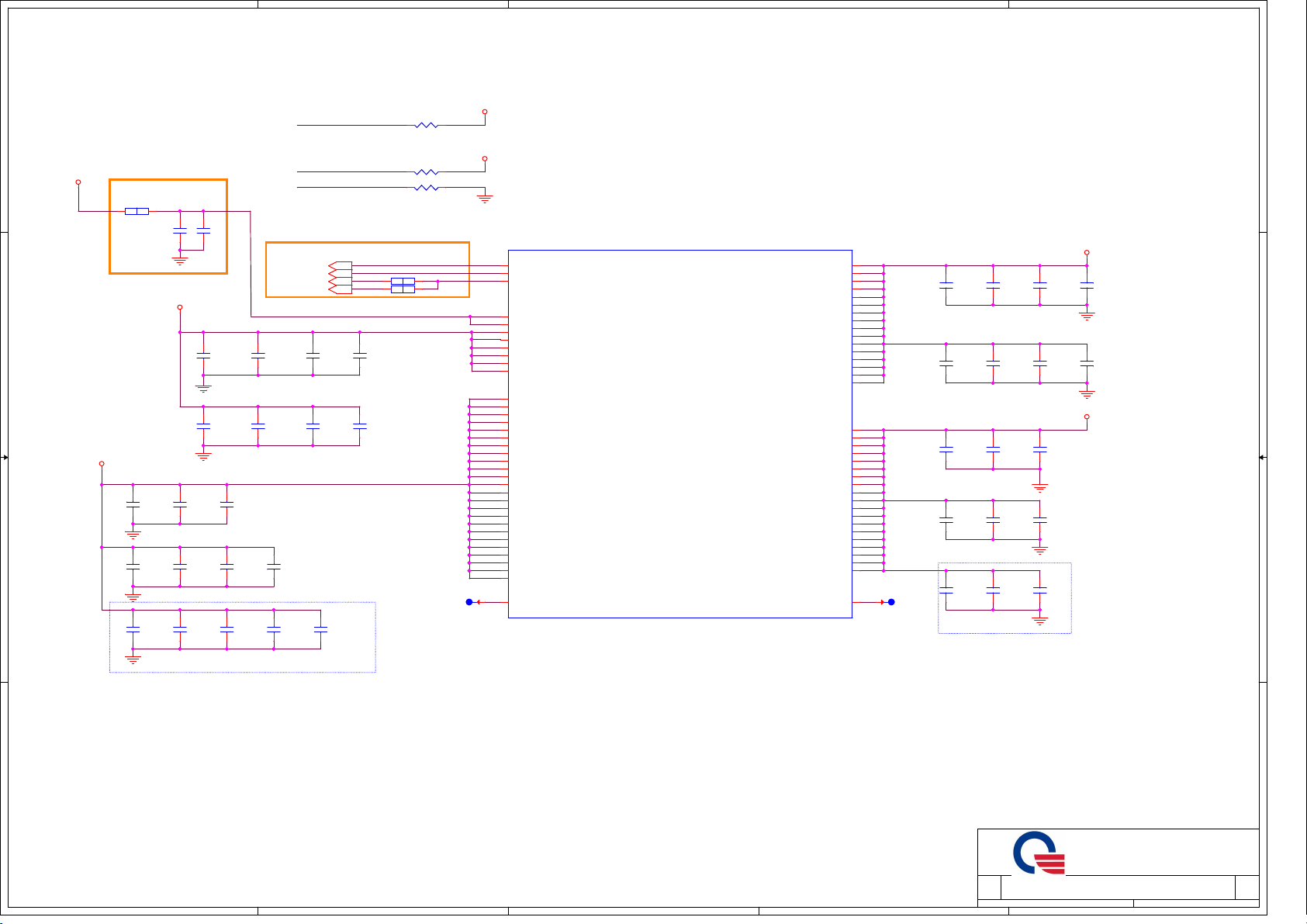

Battery Mode

+PWR_SRC

+1.0V_SUS

1.0V

VR

D D

EN

+3.3V_ALW

PG

SUS_ON

1.0V_SUS_PWRGD

8

+1.8V_SUS

1.8V

VR

EN

+PWR_SRC

1.8V_SUS_PWRGD

PG

1.0V_SUS_PWRGD

+3.3V_SUS

3.3V

SW

C C

+PWR_SRC

DDR/VTT

VR

B B

EN

PG

1.8V_SUS_PWRGD

+V_VDDQ

+DDR_VTTREF

+DDR_VTT

19

35

36

10

11

12

10

13

12

9

39

1.0V_SX_PWRGD

4

LATCH

(POWER_SW_IN0#)

SUS_ON

8

3

40

SOC_PWROK

RUN_ON

22

41

0 ohm

+1.0V_SUS

+V_VDDQ

+1.8V_SUS

+3.3V_SUS

+5V_ALW

SIO_SLP_S3# to RUN_ON delay 5ms

+5V_ALW2

RUN MOS

SWITCH

EN

3

BTN

6

SYS_PWR_SW#

(S5 start point.

(Only available when S5 -> S0)

EC

EC_PWROK

34

SLP_S0IX#

SLP_S0IX#_ON

SIO_SUSPWRDNACK#

182121

33

SIO_SLP_S4#

SIO_SLP_S3#

17

+1.0V_RUN

+1.35V_RUN

+1.8V_RUN

+3.3V_RUN

+5V_RUN

2

+5V_ALW2

+3.3V_RTC_LDO

+PWR_SRC

3V/5VPWR

+3.3V_ALW

+5V_ALW

5

7

VR

3.3V_ALW_ON

4

ALW_ON

6

14

RSMRST#

15

AC_PRESENT

16

SIO_PWRBTN#

SUS_ON to RSMRST# delay 5ms(suspend power stable)

EN2

1.0V_SX_PWRGD to EC_PWROK delay 100ms

26

28

30

31

32

EN1

Level Shift

Level Shift

Level Shift

Level Shift

Level Shift

Level Shift

41

42

SIO_SLP_S4#

SIO_SLP_S3#

SLP_S0IX#

SIO_SUSPWRDNACK#

EC_PWROK

PLTRST#

12

CHARGER

17

33

SVID

+VCHGR+PWR_SRC

Bay Trail-M

PMC_RSMRST#

PMC_ACPRESENT

PMC_PWRBTN#

PMC_SLP_S4#

PMC_SLP_S3#

PMC_SLP_S0IX#

18

PMC_SUSPWRDNACK

MCP

DRAM_CORE_PWROK

PMC_CORE_PWROK

PLTRST#

1

Battery

PG

20

34

17

+VCC_GFX_CORE+5V_ALW

+VCC_CORE

IMVP_PWRGD

RUN_ON

22

23

24

25

+1.35V_SUS

1.05V

VR

EN

RC Delay

+1.35V_SUS

1.5V

IMVP_PWRGD

PG

25

+1.05V_RUN

RUN_ON

+1.5V_RUN

27

29

22

+V_VDDQ

+1.0V_SUS

+5V_ALW2

SOIX

MOS SW

EN

+1.35VSFR

+1.0V_SX

PG

SLP_S0IX#

1.0V_SX_PWRGD

37

38

39

34

VR

Quanta Computer Inc.

Quanta Computer Inc.

EN

4

PG

RC Delay

3

RUN_ON

22

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

2

Wednesday, July 30, 2014

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

POWER SEQUENCE

POWER SEQUENCE

POWER SEQUENCE

UI2H

UI2H

UI2H

1

1B

1B

548

548

548

1B

DDR_PWRGD

PG

S3

S4

RC Delay

VDD

A A

Vcc Core

SLP_S0IX#_ON

SIO_SLP_S4#

+PWR_SRC

iGPU Core

EN

SVID

5

5

ZM6 Power Sequence

4

3

Bay Trail-M EDS 512177, Rev1.2

2

1

(G3 to S0)

+PWR_SRC

+5V_ALW2 and +3.3V_RTC_LDO

POWER_ SW_IN0#

D D

LATCH

3.3V_ALW_ON

+3.3V_ALW

(EC on)

ALW_ON(EC)

+5V_ALW

SYS_PWR_SW#

SUS_ON(EC)

+1.0V_SUS

(V1P0A)

+1.8V_SUS

(V1P8A)

+3.3V_SUS

(V3P3A)

RSMRST#(EC)

(suspend power well)

SIO_PWRBTN#(EC)

C C

SIO_SLP_S4#(SOC)

SIO_SUSPWRDNACK#(SOC)

+V_VDDQ

(VRAM_VDD)

DDR_PWRGD

SIO_SLP_S3#(SOC)

RUN_ON(EC)

+VCC_GFX_CORE

(UNCORE_VNN )

+VCC_CORE

(CORE_VCC)

IMVP_PWRGD

(VR_READY)

+1.0V_RUN

(V1P0S)

+1.05V_RUN

(V1P05S)

B B

+1.35V_RUN

(V1P35S)

+1.5V_RUN

(V1P5V1P8S )

+1.8V_RUN

(V1P8S)

+3.3V_RUN

(V3P3S / V1P8 V3P3S)

+5V_RUN

SLP_S0IX#(SOC)

SLP_S0IX#_ON(EC)

+DDR_VTTREF

+DDR_VTT

+1.35VSFR

(V1P35Sx)

+1.0V_SX

A A

1.0V_SX_PWRGD/ SOC_PWROK

(All power ready)

(V1P0Sx)

EC_PWROK(EC)

(PMC_CORE_PWROK)

PLTRST#(SPC)

5

G3 mode: > EC reset time + output ALW_ON

S5 mode: > Power button DE-BOUNCE time

G3 mode: Asserted by HW latch of power button event

S0 mode: Be keeped on high by ALW_ON

? ms (3.3_ALW _ON to +3.3V_ALW)

? ms (EC, EC reset tim e about 50.4ms, 1650 Tick*(1/32.768K))

? ms (ALW _ON to +5V_ALW)

G3 mode: EC don't care this event.

S5 mode: Upon power always exist, and this pin keeped on high . Star t from this event.

? ms (EC, ALW _ON to SUS_ON, EC)

? ms (SUS_ON to +1.0_SUS )

? ms (SUS_ON to +1.8V_S US)

? ms (SUS_ON to +3.3V_S US)

? ms (+3.3V_SUS t o RSMRST#, T3=min 10us)

? ms (SUS_ON to RSMRST#)

? ms(EC, RSMRST# to SI O_PWRBTN#)

? ms(RSMRST# to SIO_SLP_S 4#)

4

(VR ramp up tim e from 10% to 90% voltage level <2ms)

(EC: SUS_ON to RSMRST # delay 5ms)

? ms (EC, SIO_S LP_S4# to +V_VDDQ )

? ms (EC, SIO_S LP_S4# to SIO_SLP_S3# )

? ms (EC, SLP_S 3# to RUN_ON)

? ms (EC, RUN_ON to +VCC_GFX _CORE)

? ms (EC, RUN_ON to +VCC_CORE)

? ms (EC, IMVP_P WRGD to +1.0V_RUN)

? ms (EC, IMVP_P WRGD to +1.05V_RUN)

? ms (EC, IMVP_P WRGD to +1.35V_RUN)

? ms (EC, IMVP_P WRGD to +1.5V_RUN)

? ms (EC, IMVP_P WRGD to +1.8V_RUN)

? ms (EC, IMVP_P WRGD to +3.3V_RUN)

? ms (EC, IMVP_P WRGD to +5V_RUN)

? ms (+5V_RUN to SLP_S0I X#,SOC)

(EC: SIO_SLP_S 3# to RUN_ON# delay 5ms)

? ms (SOC,SLP_S0I X# to SLP_S0IX#_ON,EC)

? ms (SOC,SLP_S0I X# to +DDR_VTTREF)

? ms (SOC,SLP_S0I X# to +DDR_VTT)

? ms (SOC,SLP_S0I X# to +1.35VSFR)

? ms (SOC,SLP_S0I X# to +1.0V_SX)

? ms(S and SX rails stable to EC_PW ROK, T6>99ms)

(EC: SOC_PW ROK to EC_PWROK delay 120ms)

? ms (EC,EC_PW ROK to PLTRST#)

S0G3

3

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

2

Wednesday, July 30, 2014

G3 to S0

G3 to S0

G3 to S0

PROJECT :

UI2H

UI2H

UI2H

648

648

648

1

1B

1B

1B

5

DRAM: V1P35U (+V_VDDQ_VR)

M_A_A0[19]

M_A_A1[19]

M_A_A2[19]

M_A_A3[19]

M_A_A4[19]

M_A_A5[19]

M_A_A6[19]

M_A_A7[19]

M_A_A8[19]

M_A_A9[19]

DDR3_DRAMRST#[19]

1 2

1 2

R213

29.4/F_4

M_A_A10[19]

M_A_A11[19]

M_A_A12[19]

M_A_A13[19]

M_A_A14[19]

M_A_A15[19]

M_A_DM0[19]

M_A_DM1[19]

M_A_DM2[19]

M_A_DM3[19]

M_A_DM4[19]

M_A_DM5[19]

M_A_DM6[19]

M_A_DM7[19]

M_A_RAS#[19]

M_A_CAS#[19]

M_A_WE#[1 9]

M_A_BS0[19]

M_A_BS1[19]

M_A_BS2[19]

M_A_CS#0[19 ]

M_A_CS#1[19 ]

M_A_CKE0[19]

M_A_CKE1[19]

DRAM_ODT0[19]

DRAM_ODT2[19]

M_A_CLKP0[19]

M_A_CLKN0[19]

M_A_CLKP1[19]

M_A_CLKN1[19]

R16

162/F_4

ICLK _DRAM _1

ICLK _DRAM _2

DRAM_PWROK

VCCA_PWROK

DDR3_RCOMP0

DDR3_RCOMP1

DDR3_RCOMP2

D D

+V_VDDQ

R215

C C

4.7K/F_4

R216

4.7K/F_4

CPU_VREF

C209

0.1U/16V_4

close to SoCclose to SoC AF44

#add for SO-DIM

R20 100K/F_4

B B

The DRAM_RCOMP[2:0] signals should be

referenced to either Vss or Vdd planes

(avoid referencing to noisy planes)

R17 100K/F_4

R18

23.2/F_4

close to SoC

12

R205

*4.7K_4_ NC

A A

5

5

2

4 3

The circuit is pointless.

R212

10K_4

6

112

SR211 *SR_0402

Q13

*PJ4N3K DW_NC

1

PJ4N3KDW:

Vth=0.8~1.5V

4

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_RAS#

M_A_CAS#

M_A_WE#

M_A_BS0

M_A_BS1

M_A_BS2

M_A_CS#0

M_A_CS#1

M_A_CKE0

M_A_CKE1

DRAM_ODT0

DRAM_ODT2

M_A_CLKP0

M_A_CLKN0

M_A_CLKP1

M_A_CLKN1

DDR3_DRAMRST#

CPU_VREF

DDR_PWRGD [41]

2

DRAM_PWROK

C198

*0.1U/16V _4_NC

4

U5A

K45

DRAM0_MA_00

H47

DRAM0_MA_11

L41

DRAM0_MA_22

H44

DRAM0_MA_33

H50

DRAM0_MA_44

G53

DRAM0_MA_55

H49

DRAM0_MA_66

D50

DRAM0_MA_77

G52

DRAM0_MA_88

E52

DRAM0_MA_99

K48

DRAM0_MA_1010

E51

DRAM0_MA_1111

F47

DRAM0_MA_1212

J51

DRAM0_MA_1313

B49

DRAM0_MA_1414

B50

DRAM0_MA_1515

G36

DRAM0_DM_00

B36

DRAM0_DM_11

F38

DRAM0_DM_22

B42

DRAM0_DM_33

P51

DRAM0_DM_44

V42

DRAM0_DM_55

Y50

DRAM0_DM_66

Y52

DRAM0_DM_77

M45

DRAM0_RAS

M44

DRAM0_CAS

H51

DRAM0_WE

K47

DRAM0_BS_00

K44

DRAM0_BS_11

D52

DRAM0_BS_22

P44

DRAM0_CS_0

P45

DRAM0_CS_2

C47

DRAM0_CKE_00

D48

RESERVED_D48

F44

DRAM0_CKE_22

E46

RESERVED_E46

T41

DRAM0_ODT_0

P42

DRAM0_ODT_2

M50

DRAM0_CKP_0

M48

DRAM0_CKN_0

P50

DRAM0_CKP_2

P48

DRAM0_CKN_2

P41

DRAM0_DRAMRST

AF44

DRAM_VREF

AH42

ICLK_DRAM_TERM_1

AF42

ICLK_DRAM_TERMN_AF42

AD42

DRAM_VDD_S4_PWROK

AB42

DRAM_CORE_PWROK

AD44

DRAM_RCOMP_00

AF45

DRAM_RCOMP_11

AD45

DRAM_RCOMP_22

AF40

RESERVED_AF40

AF41

RESERVED_AF41

AD40

RESERVED_AD40

AD41

RESERVED_AD41

VLV_M_D/BGA

REV = 2.0

3

12

4 3

R206

4.7K_4

M36

J36

P40

M40

P36

N36

K40

K42

B32

C32

C36

A37

C33

A33

C37

B38

F36

G38

F42

J42

G40

C38

G44

D42

A41

C41

A45

B46

C40

B40

B48

B47

K52

K51

T52

T51

L51

L53

R51

R53

T47

T45

Y40

V41

T48

T50

Y42

AB40

V45

V47

AD48

AD50

V48

V50

AB44

Y45

V52

W51

AC53

AC51

W53

Y51

AD52

AD51

J38

K38

C35

B34

D40

F40

B44

C43

N53

M52

T42

T44

Y47

Y48

AB52

AA51

2

R214

10K_4

VCCA_PWROK

6

Q14

PJ4N3KDW

1

PJ4N3KDW:

Vth=0.8~1.5V

Si0x power ok ,Dram_core_pwrok high.

DRAM0_DQ_00

DRAM0_DQ_11

DRAM0_DQ_22

DRAM0_DQ_33

DRAM0_DQ_44

DRAM0_DQ_55

DRAM0_DQ_66

DRAM0_DQ_77

DRAM0_DQ_88

DRAM0_DQ09_C32

DRAM0_DQ_1010

DRAM0_DQ_1111

DRAM0_DQ_1212

DRAM0_DQ_1313

DRAM0_DQ_1414

DRAM0_DQ_1515

DRAM0_DQ_1616

DRAM0_DQ_1717

DRAM0_DQ_1818

DRAM0_DQ_1919

DRAM0_DQ_2020

DRAM0_DQ_2121

DRAM0_DQ_2222

DRAM0_DQ_2323

DRAM0_DQ_2424

DRAM0_DQ_2525

DRAM0_DQ_2626

DRAM0_DQ_2727

DRAM0_DQ_2828

DRAM0_DQ_2929

DRAM0_DQ_3030

DRAM0_DQ_3131

DRAM0_DQ_3232

DRAM0_DQ_3333

DRAM0_DQ_3434

DRAM0_DQ_3535

DRAM0_DQ_3636

DRAM0_DQ_3737

DRAM0_DQ_3838

DRAM0_DQ_3939

DRAM0_DQ_4040

DRAM0_DQ_4141

DRAM0_DQ_4242

DRAM0_DQ_4343

DRAM0_DQ_4444

DRAM0_DQ_4545

DRAM0_DQ_4646

DRAM0_DQ_4747

DRAM0_DQ_4848

DRAM0_DQ_4949

DRAM0_DQ_5050

DRAM0_DQ_5151

DRAM0_DQ_5252

DRAM0_DQ_5353

DRAM0_DQ_5454

DRAM0_DQ_5555

DRAM0_DQ_5656

DRAM0_DQ_5757

DRAM0_DQ_5858

DRAM0_DQ_5959

DRAM0_DQ_6060

DRAM0_DQ_6161

DRAM0_DQ_6262

DRAM0_DQ_6363

DRAM0_DQSP_00

DRAM0_DQSN_00

DRAM0_DQSP_11

DRAM0_DQSN_11

DRAM0_DQSP_22

DRAM0_DQSN_22

DRAM0_DQSP_33

DRAM0_DQSN_33

DRAM0_DQSP_44

DRAM0_DQSN_44

DRAM0_DQSP_55

DRAM0_DQSN_55

DRAM0_DQSP_66

DRAM0_DQSN_66

DRAM0_DQSP_77

DRAM0_DQSN_77

1 OF 13

+3.3V_SUS +V_VDDQ+3.3V_SUS +V_VDDQ

C203

*0.1U/16V _4_NC

3

5

EC_PWROK[1 1,32,36]SIO_SLP_S4#[16 ,32,41]

2

M_A_DQ0 [19]

M_A_DQ1 [19]

M_A_DQ2 [19]

M_A_DQ3 [19]

M_A_DQ4 [19]

M_A_DQ5 [19]

M_A_DQ6 [19]

M_A_DQ7 [19]

M_A_DQ8 [19]

M_A_DQ9 [19]

M_A_DQ10 [19]

M_A_DQ11 [19]

M_A_DQ12 [19]

M_A_DQ13 [19]

M_A_DQ14 [19]

M_A_DQ15 [19]

M_A_DQ16 [19]

M_A_DQ17 [19]

M_A_DQ18 [19]

M_A_DQ19 [19]

M_A_DQ20 [19]

M_A_DQ21 [19]

M_A_DQ22 [19]

M_A_DQ23 [19]

M_A_DQ24 [19]

M_A_DQ25 [19]

M_A_DQ26 [19]

M_A_DQ27 [19]

M_A_DQ28 [19]

M_A_DQ29 [19]

M_A_DQ30 [19]

M_A_DQ31 [19]

M_A_DQ32 [19]

M_A_DQ33 [19]

M_A_DQ34 [19]

M_A_DQ35 [19]

M_A_DQ36 [19]

M_A_DQ37 [19]

M_A_DQ38 [19]

M_A_DQ39 [19]

M_A_DQ40 [19]

M_A_DQ41 [19]

M_A_DQ42 [19]

M_A_DQ43 [19]

M_A_DQ44 [19]

M_A_DQ45 [19]

M_A_DQ46 [19]

M_A_DQ47 [19]

M_A_DQ48 [19]

M_A_DQ49 [19]

M_A_DQ50 [19]

M_A_DQ51 [19]

M_A_DQ52 [19]

M_A_DQ53 [19]

M_A_DQ54 [19]

M_A_DQ55 [19]

M_A_DQ56 [19]

M_A_DQ57 [19]

M_A_DQ58 [19]

M_A_DQ59 [19]

M_A_DQ60 [19]

M_A_DQ61 [19]

M_A_DQ62 [19]

M_A_DQ63 [19]

M_A_DQSP0 [19]

M_A_DQSN0 [19]

M_A_DQSP1 [19]

M_A_DQSN1 [19]

M_A_DQSP2 [19]

M_A_DQSN2 [19]

M_A_DQSP3 [19]

M_A_DQSN3 [19]

M_A_DQSP4 [19]

M_A_DQSN4 [19]

M_A_DQSP5 [19]

M_A_DQSN5 [19]

M_A_DQSP6 [19]

M_A_DQSN6 [19]

M_A_DQSP7 [19]

M_A_DQSN7 [19]

C197

*0.1U/16V _4_NC

2

1

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

Wednesday, July 30, 2014

PROJECT :

Bay Trail M (Memory 0,1)

Bay Trail M (Memory 0,1)

Bay Trail M (Memory 0,1)

UI2H

UI2H

UI2H

748

748

748

1

1B

1B

1B

5

4

3

2

1

U5B

AY45

DRAM1_MA_00

BB47

DRAM1_MA_11

AW41

DRAM1_MA_22

D D

C C

B B

A A

BB44

BB50

BC53

BB49

BF50

BC52

BE52

AY48

BE51

BD47

BA51

BH49

BH50

BD38

BH36

BC36

BH42

AT51

AM42

AK50

AK52

AV45

AV44

BB51

AY47

AY44

BF52

AT44

AT45

BG47

BE46

BD44

BF48

AP41

AT42

AV50

AV48

AT50

AT48

AT41

DRAM1_MA_33

DRAM1_MA_44

DRAM1_MA_55

DRAM1_MA_66

DRAM1_MA_77

DRAM1_MA_88

DRAM1_MA_99

DRAM1_MA_1010

DRAM1_MA_1111

DRAM1_MA_1212

DRAM1_MA_1313

DRAM1_MA_1414

DRAM1_MA_1515

DRAM1_DM_00

DRAM1_DM_11

DRAM1_DM_22

DRAM1_DM_33

DRAM1_DM_44

DRAM1_DM_55

DRAM1_DM_66

DRAM1_DM_77

DRAM1_RAS

DRAM1_CAS

DRAM1_WE

DRAM1_BS_00

DRAM1_BS_11

DRAM1_BS_22

DRAM1_CS_0

DRAM1_CS_2

DRAM1_CKE_00

RESERVED_BE46

DRAM1_CKE_22

RESERVED_BF48

DRAM1_ODT_0

DRAM1_ODT_2

DRAM1_CKP_0

DRAM1_CKN_0

DRAM1_CKP_2

DRAM1_CKN_2

DRAM1_DRAMRST

VLV_M_D/BGA

REV = 2.0

2 OF 13

DRAM1_DQ_00

DRAM1_DQ_11

DRAM1_DQ_22

DRAM1_DQ_33

DRAM1_DQ_44

DRAM1_DQ_55

DRAM1_DQ_66

DRAM1_DQ_77

DRAM1_DQ_88

DRAM1_DQ_99

DRAM1_DQ_1010

DRAM1_DQ_1111

DRAM1_DQ_1212

DRAM1_DQ_1313

DRAM1_DQ_1414

DRAM1_DQ_1515

DRAM1_DQ_1616

DRAM1_DQ_1717

DRAM1_DQ_1818

DRAM1_DQ_1919

DRAM1_DQ_2020

DRAM1_DQ_2121

DRAM1_DQ_2222

DRAM1_DQ_2323

DRAM1_DQ_2424

DRAM1_DQ_2525

DRAM1_DQ_2626

DRAM1_DQ_2727

DRAM1_DQ_2828

DRAM1_DQ_2929

DRAM1_DQ_3030

DRAM1_DQ_3131

DRAM1_DQ_3232

DRAM1_DQ_3333

DRAM1_DQ_3434

DRAM1_DQ_3535

DRAM1_DQ_3636

DRAM1_DQ_3737

DRAM1_DQ_3838

DRAM1_DQ_3939

DRAM1_DQ_4040

DRAM1_DQ_4141

DRAM1_DQ_4242

DRAM1_DQ_4343

DRAM1_DQ_4444

DRAM1_DQ_4545

DRAM1_DQ_4646

DRAM1_DQ_4747

DRAM1_DQ_4848

DRAM1_DQ_4949

DRAM1_DQ_5050

DRAM1_DQ_5151

DRAM1_DQ_5252

DRAM1_DQ_5353

DRAM1_DQ_5454

DRAM1_DQ_5555

DRAM1_DQ_5656

DRAM1_DQ_5757

DRAM1_DQ_5858

DRAM1_DQ_5959

DRAM1_DQ_6060

DRAM1_DQ_6161

DRAM1_DQ_6262

DRAM1_DQ_6363

DRAM1_DQSP_00

DRAM1_DQSN_00

DRAM1_DQSP_11

DRAM1_DQSN_11

DRAM1_DQSP_22

DRAM1_DQSN_22

DRAM1_DQSP_33

DRAM1_DQSN_33

DRAM1_DQSP_44

DRAM1_DQSN_44

DRAM1_DQSP_55

DRAM1_DQSN_55

DRAM1_DQSP_66

DRAM1_DQSN_66

DRAM1_DQSP_77

DRAM1_DQSN_77

BG38

BC40

BA42

BD42

BC38

BD36

BF42

BC44

BH32

BG32

BG36

BJ37

BG33

BJ33

BG37

BH38

AU36

AT36

AV40

AT40

BA36

AV36

AY42

AY40

BJ41

BG41

BJ45

BH46

BG40

BH40

BH48

BH47

AY52

AY51

AP52

AP51

AW51

AW53

AR51

AR53

AP47

AP45

AK40

AM41

AP48

AP50

AK42

AH40

AM45

AM47

AF48

AF50

AM48

AM50

AH44

AK45

AM52

AL51

AG53

AG51

AL53

AK51

AF52

AF51

BF40

BD40

BG35

BH34

BA38

AY38

BH44

BG43

AU53

AV52

AP42

AP44

AK47

AK48

AH52

AJ51

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

5

4

3

2

Wednesday, July 30, 2014

PROJECT :

Bay Trail M (Memory 0,1)

Bay Trail M (Memory 0,1)

Bay Trail M (Memory 0,1)

UI2H

UI2H

UI2H

848

848

848

1

1B

1B

1B

5

DDIx TX/AUX: V1P0Sx (+1.0V_SX)

DDIx HPD/DDC/VDDEN/BKLT: V1P8S (+1.8V_RUN)

DVI_TXP2[21]

DVI_TXN2[21 ]

DVI_TXP1[21]

DVI_TXN1[21 ]

DVI_TXP0[21]

DVI_TXN0[21 ]

+1.8V_RUN

D D

R33 2.2K_4

R226 2.2K_4

DDI0_DDCCLK

DDI0_DDCDATA

HW Strap:DDI0 Detect

DVI_CLKP[21]

DVI_CLKN[21]

DVI_HPD#[21]

DDI0_DDCDATA[21]

DDI0_DDCCLK[21]

DDI0_DDCDATA

PU

1 = DDI0 detected

PD

0 = DDI0 not detected(Default)

C C

B B

R249 402/F_4

+1.8V_RUN

R28

*10K_4_ NC

R31

10K_4

4

U5C

AV3

DDI0_TXP_0

AV2

DDI0_TXN_0

AT2

DDI0_TXP_1

AT3

DDI0_TXN_1

AR3

DDI0_TXP_2

AR1

DDI0_TXN_2

AP3

DDI0_TXP_3

AP2

DDI0_TXN_3

AL3

DDI0_AUXP

AL1

DDI0_AUXN

D27

DDI0_HPD

DDI0_DDCDATA

DDI0_DDCCLK

TP3

TP4

DDI0_VDDEN

DDI0_BL

DDI0_BKTCTL

SOC_DDI0_RCOMP

SOC_DDI0_RCOMP_P

SOC_AM3

SOC_AM2

GPIO_S0_NC13

GPIO_S0_NC14

GPIO_S0_NC12

TP6

TP5

TP25

R71 0_4 R75 0_4

R70 0_4

C26

C28

C27

AK13

AK12

AM14

AM13

AM3

AM2

AB3

AB2

AD6

AD4

AB9

AB7

C29

AB14

C30

B28

B26

T2

T3

Y3

Y2

W3

W1

V2

V3

R3

R1

Y4

Y6

V4

V6

A29

B30

DDI0_DDCDATA

DDI0_DDCCLK

DDI0_VDDEN

DDI0_BKLTEN

DDI0_BKLTCTL

DDI0_RCOMP

DDI0_RCOMP_P

RESERVED_AM14

RESERVED_AM13

RESERVED_VSS0

RESERVED_VSS1

RESERVED_T2

RESERVED_T3

RESERVED_AB3

RESERVED_AB2

RESERVED_Y3

RESERVED_Y2

RESERVED_W3

RESERVED_W1

RESERVED_V2

RESERVED_V3

RESERVED_R3

RESERVED_R1

RESERVED_AD6

RESERVED_AD4

RESERVED_AB9

RESERVED_AB7

RESERVED_Y4

RESERVED_Y6

RESERVED_V4

RESERVED_V6

RESERVED_A29

RESERVED_C29

RESERVED_AB14

GPIO_S0_NC12

RESERVED_C30

VLV_M_D/BGA

REV = 2.0

3

DDI1_HPD

VGA_RED

VGA_BLUE

VGA_IREF

VGA_IRTN

AG3

AG1

AF3

AF2

AD3

AD2

AC3

AC1

AK3

AK2

K30

P30

G30

N30

J30

M30

AH14

AH13

AF14

AF13

AH3

AH2

BA3

AY2

BA1

AW1

AY3

BD2

BF2

BC1

VGA_DDCCLK

BC2

VGA_DDCDATA

T7

T9

AB13

AB12

Y12

Y13

V10

V9

T12

T10

V14

V13

T14

T13

T6

T4

P14

K34

D32

N32

J34

K28

F28

F32

D34

J28

D28

M32

F34

3 OF 13

DDI1_TXP_0

DDI1_TXN_0

DDI1_TXP_1

DDI1_TXN_1

DDI1_TXP_2

DDI1_TXN_2

DDI1_TXP_3

DDI1_TXN_3

DDI1_AUXP

DDI1_AUXN

DDI1_DDCDATA

DDI1_DDCCLK

DDI1_VDDEN

DDI1_BKLTEN

DDI1_BKLTCTL

RESERVED_AH14

RESERVED_AH13

RESERVED_AF14

RESERVED_AF13

RESERVED_VSS2

RESERVED_VSS3

VGA_GREEN

VGA_HSYNC

VGA_VSYNC

VGA_DDCCLK

VGA_DDCDATA

RESERVED_T7

RESERVED_T9

RESERVED_AB13

RESERVED_AB12

RESERVED_Y12

RESERVED_Y13

RESERVED_V10

RESERVED_V9

RESERVED_T12

RESERVED_T10

RESERVED_V14

RESERVED_V13

RESERVED_T14

RESERVED_T13

RESERVED_T6

RESERVED_T4

RESERVED_P14

RESERVED_K34

RESERVED_D32

RESERVED_N32

RESERVED_J34

RESERVED_K28

RESERVED_F28

RESERVED_F32

RESERVED_D34

RESERVED_J28

RESERVED_D28

RESERVED_M32

RESERVED_F34

2

#Delete HDMI circiut

HDMI_OUT_SDA

HDMI_OUT_SCL

VSS_AH3

VSS_AH2

R74 0_4

RP6

4

2

2.2KX2

3

1

PDG page 135.

1

HDMI_OUT_SDA

HDMI_OUT_SCL

R221 *2.2K_4_NC

R222 *2.2K_4_NC

HW Strap:DDI1 Detect

DDI1_DDCDATA

PU

1 = DDI1 detected

PD

0 = DDI1 not detected(Default)

+1.8V_RUN

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

5

4

3

2

Wednesday, July 30, 2014

PROJECT :

Bay Trail M (DISPLAY)

Bay Trail M (DISPLAY)

Bay Trail M (DISPLAY)

UI2H

UI2H

UI2H

948

948

948

1

1B

1B

1B

5

+1.8V_RUN

R239 2.2K_4

R235 *10K_4_NC

D D

HDD

SIO_EXT_SCI#

SOC_SATA_LED#

SATA_TXP0[30 ]

SATA_TXN0[30]

SATA_RXP0[30]

SATA_RXN0[30]

#Delete MSATA circiut

R260 0_4

SATA LED/GP: V1P8S (+1.8V_RUN)

R251 0_4

SIO_EXT_SCI#[32]

R234 402/F_4

MMC: V1P8S(+1.8V_RUN)

C C

SD2: V1P8S(+1.8V_RUN)

SD3(CMD/CLK/Dx): SD3_V1P8V3P3_S3(+1.8V_RUN)

SD3(PWREN/CD/1P8EN):V1P8S(+1.8V_RUN)

B B

R238 49.9/F_4

TP14

R30 49.9/F_4

ICLK _SATA _TERM P

ICLK _SATA _TERM N

SIO_EXT_SCI#

SOC_SATA_LED#

SATA_RCOMP_P

SATA_RCOMP_N

MMC1_RCOMP

SDIO_RCOMP

4

U5D

BF6

SATA_TXP_0

BG7

SATA_TXN_0

AU16

SATA_RXP_0

AV16

SATA_RXN_0

BD10

SATA_TXP1

BF10

SATA_TXN_1

AY16

SATA_RXP_1

BA16

SATA_RXN_1

BB10

RESERVED_VSS4

BC10

RESERVED_VSS5

BA12

SATA_GP0

AY14

SATA_GP1

AY12

SATA_LED

AU18

SATA_RCOMP_P_AU18

AT18

SATA_RCOMP_N_AT18

AT22

MMC1_CLK

AV20

MMC1_D0

AU22

MMC1_D1

AV22

MMC1_D2

AT20

MMC1_D3

AY24

MMC1_D4

AU26

MMC1_D5

AT26

MMC1_D6

AU20

MMC1_D7

AV26

MMC1_CMD

BA24

MMC1_RST

AY18

MMC1_RCOMP

BA18

SD2_CLK

AY20

SD2_D0

BD20

SD2_D1

BA20

SD2_D2

BD18

SD2_D3_CD

BC18

SD2_CMD

AY26

SD3_CLK

AT28

SD3_D0

BD26

SD3_D1

AU28

SD3_D2

BA26

SD3_D3

BC24

SD3_CD#

AV28

SD3_CMD

BF22

SD3_1P8EN

BD22

SD3_PWREN

BF26

SD3_RCOMP

VLV_M_D/BGA

REV = 2.0

PCIE_RCOMP_P_AP14_AP14

PCIE_RCOMP_N_AP13_AP13

HDA_LPE_RCOMP

LPE_I2S2_DATAOUT

LPE_I2S2_DATAIN

4 OF 13

PCIE_TXP_0

PCIE_TXN_0

PCIE_RXP_0

PCIE_RXN_0

PCIE_TXP_1

PCIE_TXN_1

PCIE_RXP_1

PCIE_RXN_1

PCIE_TXP_2

PCIE_TXN_2

PCIE_RXP_2

PCIE_RXN_2

PCIE_TXP_3

PCIE_TXN_3

PCIE_RXP_3

PCIE_RXN_3

RESERVED_VSS6

RESERVED_VSS7

PCIE_CLKREQ_0

PCIE_CLKREQ_1

PCIE_CLKREQ_2

PCIE_CLKREQ_3

SD3_WP_BD5

RESERVED_BB4

RESERVED_BB3

RESERVED_AV10

RESERVED_AV9

HDA_RST

HDA_SYNC

HDA_CLK

HDA_SDO

HDA_SDI0

HDA_SDI1

GPIO_S0_SC_14

GPIO_S0_SC_15

LPE_I2S2_CLK

LPE_I2S2_FRM

RESERVED_P34

RESERVED_N34

RESERVED_AK9

RESERVED_AK7

PROCHOT

3

AY7

PCIE_TXP0_C

AY6

PCIE_TXN0_C

AT14

AT13

AV6

PCIE_TXP1_C

AV4

PCIE_TXN1_C

AT10

AT9

AT7

AT6

AP12

AP10

AP6

AP4

AP9

AP7

BB5

VSS_BB7

BB7

VSS_BB5

BG3

PCIE_CLKREQ_WLAN#

BD7

PCIE_CLKREQ_LAN#

BG5

PCIE_CLK_REQ2#

BE3

PCIE_CLK_REQ3#

BD5

AP14

PCIE_RCOMP_P

AP13

PCIE_RCOMP_N

BB4

BB3

AV10

AV9

BF20

HDA_LPE_RCOMP

BG22

HDA_RST#_R

BH20

HDA_SYNC_R

BJ21

HDA_BITCLK_R

BG20

HDA_SDOUT_R

BG19

BG21

BH18

BG18

BF28

BA30

I2S_ SFRM_ OUT

BC30

SOC_OVERRIDE#

BD28

P34

N34

AK9

AK7

C24

SOC_PROCHOT#

R262 0_4

R264 0_4

R250 402/F_4

R232 49.9/F_4

R29 33_4

R37 33_4

R34 33_4

R35 33_4

Close SOC

SR43 *SR_0402

112

2

C2820.1U/16V_4

C2810.1U/16V_4

C2840.1U/16V_4

C2830.1U/16V_4

PCIE_TXP0 [31]

PCIE_TXN0 [31]

PCIE_RXP0 [31]

PCIE_RXN0 [31]

PCIE_TXP1 [24]

PCIE_TXN1 [24]

PCIE_RXP1 [24]

PCIE_RXN1 [24]

PCIE CLKREQ: V1P8A (+1.8V_SUS)

OD pin->depends on device

PCIE_CLKREQ_WLAN# [31]

PCIE_CLKREQ_LAN# [24]

WLAN/BT

LAN

1

HDA: HDA_LPE_V1P5V1P8_S3(+1.8V_RUN)

HDA_RST# [25]

HDA_SYNC [25]

HDA_BITCLK [25]

HDA_SDOUT [25]

HDA_SDIN0 [25]

SOC_OVERRIDE# [32]

LPE: V1P8S(+1.8V_RUN)

Internal PU

2

IMVP 7_PRO CHOT# [ 32,45]

R48 71.5/F_4

+1.0V_RUN

I2S_ SFRM_ OUT

+1.8V_RUN

PCIE_CLKREQ_WLAN#

PCIE_CLKREQ_LAN#

PCIE_CLK_REQ2#

PCIE_CLK_REQ3#

A A

5

1 2

R265 10K_4

1 2

R266 10K_4

1 2

R263 10K_4

1 2

R261 10K_4

4

HDA_RST#_R

Close SOC

C37

*22P/50V _4_NC

3

HW Strap: BIOS Boot Selection

GPIO_S0_SC[063]/LPE_I2S2_FRM

PD 0 = LPC

R218 *10K_4_NC

R219 *10K_4_NC

1 = SPI(Default)PU

+1.8V_RUN

2

HW Strap: Security Flash Descriptors

GPIO_S0_SC[065]/ LPE_I2S2_DATAOUT

1 = Normal Operation(Default)PU

PD 0 = Override

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

Wednesday, July 30, 2014

PROJECT :

Bay Trail M (SATA&PCIE)

Bay Trail M (SATA&PCIE)

Bay Trail M (SATA&PCIE)

1

UI2H

UI2H

UI2H

10 48

10 48

10 48

1B

1B

1B

+1.8V_SUS

R236 51/F_4

R240 51/F_4

R254 51/F_4

R241 200/F_4

R59 2.2K_4

R248 51/F_4

R244 51/F_4

GND

D D

WLAN/BT

LAN

C C

5

XDP_H_TDO

XDP_H_TMS

XDP_H_TDI

XDP_H_PREQ#

SIO_EXT_SMI#

XDP_H_TRST#

XDP_H_TCK

PCIE CLK: V1P0S

CLK_PCIE_WLANN[31]

CLK_PCIE_WLANP[31]

CLK_PCIE_LANN[24]

CLK_PCIE_LANP[24]

TAP signal: V1P8A (+1.8V_SUS)

PCU SPI: V1P8A(+1.8V_SUS)

SOC_SPI_CS#[33]

SOC_SPI_MISO[33]

SOC_SPI_MOSI[33]

SOC_SPI_CLK[33]

R245 4.02K/F_4

R256 47.5/F_4

TP18

R45 22_4

R55 22_4

R51 22_4

12

12

12

SOC_XTAL_IN

SOC_XTAL_OUT

RTC_RST#

XDP_H_TCK

XDP_H_TRST#

XDP_H_TMS

XDP_H_TDI

XDP_H_TDO

XDP_H_PRDY#

XDP_H_PREQ#

SOC_SPI_CS#_R

SOC_SPI_MOSI_R

SOC_SPI_CLK_R

GPIO_S5_[0:7]: PMC_V1P8_G3 (+1.8V_SUS)

SIO_EXT_SMI#[32]

B B

SIO_EXT_SMI#

R231 49.9/F_4

SOC_GPIO_RCOMP

SVID_ALERT:

RTC Circuitry (RTC)

(non Rechargable BATT)

+RTC_CELL

R63 20K_4

30mils

A A

R61 20K_4

C42

*1U/6.3V_4_NC

+RTC_VCC to RTC_TEST# de-assertion

Min :9 ms

C41

1U/6.3V_4

C40

1U/6.3V_4

5

RTC_TEST#

RTC_RST#

SVID_DATA

SVID_CLK

ICLK_ICOM P

ICLK_RCO MP

4

U5E

AH12

ICLK_OSCIN

AH10

ICLK_OSCOUT

AD9

RESERVED_AD9

AD14

ICLK_ICOMP

AD13

ICLK_RCOMP

AD10

RESERVED_AD10

AD12

RESERVED_AD12

AF6

PCIE_CLKN_00

AF4

PCIE_CLKP_00

AF9

PCIE_CLKN_11

AF7

PCIE_CLKP_11

AK4

PCIE_CLKN_22

AK6

PCIE_CLKP_22

AM4

PCIE_CLKN_33

AM6

PCIE_CLKP_33

AM10

RESERVED_AM10

AM9

RESERVED_AM9

BH7

PMC_PLT_CLK_00

BH5

PMC_PLT_CLK_11

BH4

PMC_PLT_CLK_22

BH8

PMC_PLT_CLK_33

BH6

PMC_PLT_CLK_44

BJ9

PMC_PLT_CLK_55

C12

ILB_RTC_RST

D14

TAP_TCK

G12

TAP_TRST

F14

TAP_TMS

F12

TAP_TDI

G16

TAP_TDO

D18

TAP_PRDY

F16

TAP_PREQ

AT34

RESERVED

C23

PCU_SPI_CS_00

C21

PCU_SPI_CS_11

B22

PCU_SPI_MISO

A21

PCU_SPI_MOSI

C22

PCU_SPI_CLK

B18

GPIO_S5_0

B16

GPIO_S5_1

C18

GPIO_S5_2

A17

GPIO_S5_3

C17

GPIO_S5_4

C16

GPIO_S5_5

B14

GPIO_S5_6

C15

GPIO_S5_7

C13

GPIO_S5_8

A13

GPIO_S5_9

C19

GPIO_S5_10

N26

GPIO_RCOMP

VLV_M_D/BGA

REV = 2.0

+1.0V_RUN

close to the SoC.

SVID_ALERT#

SVID_DATA SVID_DATA_R

SVID_CLK

4

R40 20/F_4

close to the SoC.

R36 16.9/F_4

0.1U/16V_4

5 OF 13

R42

71.5/F_4

+1.0V_RUN

+1.0V_RUN

C64

3

PMC_SUSPWRDNACK

close to the VR

R274

71.5/F_4

R275

71.5/F_4

close to the VR

3

SIO_UART1_RXD

SIO_UART1_TXD

SIO_UART1_RTS

SIO_UART1_CTS

SIO_UART2_RXD

SIO_UART2_TXD

SIO_UART2_RTS

SIO_UART2_CTS

PMC_SUSCLK0_G24

PMC_SLP_S0IX

PMC_SLP_S4

PMC_SLP_S3

GPIO_S5_14

PMC_ACPRESENT

PMC_WAKE_PCIE_0

PMC_BATLOW

PMC_PWRBTN

PMC_RSTBTN

PMC_PLTRST

GPIO_S5_17

PMC_SUS_STAT

ILB_RTC_TEST

PMC_RSMRST

PMC_CORE_PWROK

ILB_RTC_X1

ILB_RTC_X2

ILB_RTC_EXTPAD

SVID_ALERT

SVID_DATA

SVID_CLK

SIO_PWM_00

SIO_PWM_11

GPIO_S5_22

GPIO_S5_23

GPIO_S5_24

GPIO_S5_25

GPIO_S5_26

GPIO_S5_27

GPIO_S5_28

GPIO_S5_29

GPIO_S5_30

SIO_SPI_CS

SIO_SPI_MISO

SIO_SPI_MOSI

SIO_SPI_CLK

C52

0.1U/16V_4

R271 16.9/F_4

R272 20/F_4

AU34

AV34

BA34

AY34

BF34

BD34

BD32

BF32

D26

SOC_SUSPWRDNACK

G24

SUSCLK

F18

PMC_SLP_S0IX#

F22

PMC_SLP_S4#

D22

PMC_SLP_S3#

J20

D20

AC_PRESENT

F26

WL_HOST_WAKE#

K26

PMU_BATTLOW#

J26

SIO_PWRBTN#

BG9

DBG_RESETBTN#

F20

PMC_PLTRST#

J24

G18

C11

RTC_TEST#

B10

RSMRST#

B7

CORE_PWROK

C9

RTC_X1

A9

RTC_X2

B8

RTC_EXTPAD

B24

SVID_ALERT#

A25

SVID_DATA

C25

SVID_CLK

AU32

AT32

K24

N24

M20

J18

M18

K18

K20

M22

M24

AV32

BA28

AY28

SIO SPI: V1P8S(+1.8V_RUN)

AY30

VR_SVID_ALERT# [45]

VR_SVID_DATA [45]

VR_SVID_CLK [45]

2

UART: V1P8S(+1.8V_RUN)

PMC signal: V1P8A (+1.8V_SUS)

PMC_RSTBTN#l: V1P8S (+1.8V_RUN)

TP17

PMC_CORE_PWROK/PMC_RSMRST#: VRTC(+VCCRTC3)

2

112

SR73 *SR_0402

C51 0.1U/16V_4

2

SOC_SUSPWRDNACK [16]

PMC_SLP_S0IX# [16]

PMC_SLP_S4# [16]

PMC_SLP_S3# [16]

AC_PRESENT [32]

SIO_PWRBTN# [32]

PMC_PLTRST# [16]

RSMRST# [32]

EC_PWROK [7,32,36]

ILB RTC: VRTC (+VCCRTC3)

SVID: V1P0S (+1.0V_RUN)

10P/50V_4

RTC Clock 32.768KHz

C45 15P/50V/_4

C50 15P/50V/_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

Wednesday, July 30, 2014

1

WL_HOST_WAKE#

AC_PRESENT

PMU_BATTLOW#

SOC_SUSPWRDNACK

SIO_PWRBTN#

DBG_RESETBTN#

CORE_PWROK

RSMRST#

R68

C56

Bay Trail M (CLK&PMC)

Bay Trail M (CLK&PMC)

Bay Trail M (CLK&PMC)

R223 10K_4

R233 2.2K_4

R224 10K_4

R227 10K_4

R220 10K_4

R259 10K_4

R69 100K_4

R64 100K_4

SOC_XTAL_IN

SOC_XTAL_OUT

1M_4

Y2

1

3

4

2

25MHz

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

12

C57

10P/50V_4

Y1

32.768KHZ

1

UI2H

UI2H

UI2H

11 48

11 48

11 48

RTC_X1

R66

10M_4

RTC_X2

+1.8V_SUS

+1.8V_RUN

1B

1B

1B

5

4

3

2

1

U5F

G2

GPIO_S5_31

M3

GPIO_S5_32

L1

D D

USB Hub

Debug

USB OC: V1P8A (+1.8V_SUS)

Cardreader

BT

C C

+1.8V_SUS

R56 10K_4

R54 10K_4

USB_OC0#

USB_OC1#

USBP0P[17]

USBP0N[17]

USBP1P[29]

USBP1N[29]

USBP2P[27]

USBP2N[27]

USBP3P[31]

USBP3N[31]

R253 1K/F_4

R258 1K/F_4

USB_OC0#[29]

USB_OC1#[29]

R257 45.3/F_4

R252 *0_4_NC

USBP0P

USBP0N

USBP1P

USBP1N

USBP2P

USBP2N

USBP3P

USBP3N

ICLK _USB_ TERMN _0

ICLK _USB_ TERMN _1

USB_OC0#

USB_OC1#

USB_RCOMP

USB_PLL_MON

USB 2.0 HSIC: V1P2A (+1.2V_SUS)

R72 45.3/F_4

ILB LPC(AD/FRAME/CLKRUN/CLK/):LPC_V1P8V3P3_S3 (+3.3V_RUN)

ILB LPC(SERIRQ): V1P8S (+1.8V_RUN)

B B

LPC

LPC_LAD0[31,32]

LPC_LAD1[31,32]

LPC_LAD2[31,32]

LPC_LAD3[31,32]

LPC_LFRAME#[31,32]

LPC_CLK_EC[32]

LPC_CLK_DEBUG[31]

CLKRUN#[32]

IRQ_ SERIRQ[16]

PCU SMB: V1P8S (+1.8V_RUN)

SR44 *SR_0402

SR41 *SR_0402

SR52 *SR_0402

SR46 *SR_0402

SR39 *SR_0402

SR47 *SR_0402

SR62 *SR_0402

SMB_SOC_DATA[16]

SMB_SOC_CLK[16]

USB_HSIC_RCOMP

R237 49.9/F_4

2

112

2

112

2

112

2

112

2

112

R53 33_4

R50 33_4

2

112

2

112

SMB_SOC_DATA

SMB_SOC_CLK

SMB_INT#

LPC_RCOMP

ILB_ LPC_A D0

ILB_ LPC_A D1

ILB_ LPC_A D2

ILB_ LPC_A D3

ILB_ LPC_F RAME#

ILB_ LPC_C LK_00

ILB_ LPC_C LK_11

ILB_ LPC_C LKRUN #

ILB_ LPC_S ERIRQ

GPIO_S5_33

K2

GPIO_S5_34

K3

GPIO_S5_35

M2

GPIO_S5_36

N3

GPIO_S5_37

P2

GPIO_S5_38

L3

GPIO_S5_39

J3

GPIO_S5_40

P3

GPIO_S5_41

H3

GPIO_S5_42

B12

GPIO_S5_43

M16

USB_DP0

K16

USB_DN0

J14

USB_DP1

G14

USB_DN1

K12

USB_DP2

J12

USB_DN2

K10

USB_DP3

H10

USB_DN3

D10

ICLK_USB_TERM_1

F10

ICLK_USB_TERMN

C20

USB_OC_00

B20

USB_OC_11

D6

USB_RCOMPO

C7

USB_RCOMPI

M13

USB_PLL_MON

B4

USB_HSIC0_DATA

B5

USB_HSIC0_STROBE

E2

USB_HSIC1_DATA

D2

USB_HSIC1_STROBE

A7

USB_HSIC_RCOMP

BF18

LPC_RCOMP

BH16

ILB_LPC_AD_00

BJ17

ILB_LPC_AD_11

BJ13

ILB_LPC_AD_22

BG14

ILB_LPC_AD_33

BG17

ILB_LPC_FRAME

BG15

ILB_LPC_CLK_00

BH14

ILB_LPC_CLK_11

BG16

ILB_LPC_CLKRUN

BG13

ILB_LPC_SERIRQ

BG12

PCU_SMB_DATA

BH10

PCU_SMB_CLK

BG11

PCU_SMB_ALERT

#Add off-page for SO-DIMM

+1.8V_RUN

A A

RP5 4.7KX2

R255 *2.2K_4_NC

R247 *10K_4

R243 *10K_4

2

1

4

3

5

SMB_SOC_CLK

SMB_SOC_DATA

SMB_INT#

PCIE_MCARD1_DET#

USB_MCARD1_DET#

Pull down 10K for WIFI/BT detect pin [20140518]

R396 10K_4

R397 10K_4

4

VLV_M_D/BGA

REV = 2.0

6 OF 13

3

RESERVED_M10

RESERVED_M9

RESERVED_P7

RESERVED_P6

RESERVED_M7

USB3_REXT0

RESERVED_P10

RESERVED_P12

RESERVED_M4

RESERVED_M6

USB3_RXP0

USB3_RXN0

USB3_TXP0

USB3_TXN0

RESERVED_H8

RESERVED_H7

RESERVED_H5

RESERVED_H4

GPIO_S0_SC_55

GPIO_S0_SC_56

GPIO_S0_SC_57

GPIO_S0_SC_58

GPIO_S0_SC_59

GPIO_S0_SC_60

GPIO_S0_SC_61

ILB_8254_SPKR

SIO_I2C0_DATA

SIO_I2C0_CLK

SIO_I2C1_DATA

SIO_I2C1_CLK

SIO_I2C2_DATA

SIO_I2C2_CLK

SIO_I2C3_DATA

SIO_I2C3_CLK

SIO_I2C4_DATA

SIO_I2C4_CLK

SIO_I2C5_DATA

SIO_I2C5_CLK

SIO_I2C6_DATA

SIO_I2C6_CLK

GPIO_S0_SC_092

GPIO_S0_SC_093

M10

M9

P7

P6

M7

USB3_REXT0 ,PDG Rev1.5 ,page 149:

M12

Unused USB ports can be left no connect.

P10

P12

M4

M6

D4

E3

K6

K7

H8

H7

H5

H4

BD12

BC12

BD14

BC14

BF14

BD16

BC16

BH12

PCIE_MCARD1_DET#

GPIO_S0_SC_56

GPIO_S0_SC_57

USB_MCARD1_DET#

GPIO_S0_SC_61

ACZ_SPKR

PCIE_MCARD1_DET# [31]

TP20

USB_MCARD1_DET# [31]

TP16

ACZ_SPKR [25]

#Add PCBeep net

BH22

BG23

BG24

BH24

BG25

BJ25

BG26

BH26

BF27

BG27

BH28

BG28

BJ29

BG29

BH30

BG30

*for TXE firmware debug

TP2

TP1

2

GPIO_S0_SC_56

HW Strap:Top Swap (A16 Override)

GPIO_S0_SC[056]

1 = Top address bit is inverted (Default)PU

PD 0 = Top address bit is unchanged

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

USB3: V1P0A (+1.0V_SUS)

*GPIO_S0_SC_57 & GPIO_S0_SC_57 for UART RMT use

ILB_8254_SPKR: V1P8S (+1.8V_RUN)

SIO I2C: V1P8S (+1.8V_RUN)

R246 *10K_4_NC

R242 *10K_4_NC

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Bay Trail M (USB&MISC)

Bay Trail M (USB&MISC)

Bay Trail M (USB&MISC)

Wednesday, July 30, 2014

Wednesday, July 30, 2014

Wednesday, July 30, 2014

1

+1.8V_RUN

UI2H

UI2H

UI2H

12 48

12 48

12 48

1B

1B

1B

5

D D

VCC_AXG_SENSE

4

+VCC_GFX_CORE

R67 100/F_4

12

3

2

1

VDD (+V_VDDQ)

Max current 1.25A

+V_VDDQ

112

1U/6.3V_4

C295

22U/6.3V_6

C246

22U/6.3V_6

C245

10U/6.3V_6

2

C218

+V_VDDQ

0.1U/16V_4

C224

C204

0.1U/16V_4

C61

22U/6.3V_6

C290

22U/6.3V_6

C60

4.7U/6.3V_6

C220

2.2U/10V_4

C240

22U/6.3V_6

C289

22U/6.3V_6

C58

4.7U/6.3V_6

SR217 *SR_0402

C C

VCC (+VCC_CORE)

Max current 12A

+VCC_CORE

B B

VCC_AXG_SENSE[45]

VSS_AXG_SENSE[45]

C216

2.2U/10V_4

C210

0.1U/16V_4

22U/6.3V_6

C242

2.2U/10V_4

VCCSENSE

CORE_VSS_SENSE

VCCSENSE[45]

VSSSENSE[45 ]

C213

2.2U/10V_4

C217

0.1U/16V_4

C294

R25 100/F_4

R26 100/F_4

SR361 *SR_0402

112

SR65 *SR_0402

112

C205

2.2U/10V_4

C214

0.1U/16V_4

C249

2.2U/10V_4

VCCDDRCLK

12

12

2

CORE_VSS_SENSE

2

TP13

+VCC_CORE

P28

BB8

N28

AD38

AF38

A48

AK38

AM38

AV41

AV42

BB46

AA27

AA29

AA30

AC27

AC29

AC30

AD27

AD29

AD30

AF27

AF29

AG27

AG29

AG30

P26

P27

U27

U29

V27

V29

V30

Y27

Y29

Y30

AF30

U5G

CORE_VCC_SENSE_P28

UNCORE_VNN_SENSE

CORE_VSS_SENSE_N28

DRAM_VDD_S4_AD38

DRAM_VDD_S4_AF38

DRAM_VDD_S4

DRAM_VDD_S4_AK38

DRAM_VDD_S4_AM38

DRAM_VDD_S4_AV41

DRAM_VDD_S4_AV42

DRAM_VDD_S4_BB46

CORE_VCC_S0IX_AA27

CORE_VCC_S0IX_AA29

CORE_VCC_S0IX_AA30

CORE_VCC_S0IX_AC27

CORE_VCC_S0IX_AC29

CORE_VCC_S0IX_AC30

CORE_VCC_S0IX_AD27

CORE_VCC_S0IX_AD29

CORE_VCC_S0IX_AD30

CORE_VCC_S0IX_AF27

CORE_VCC_S0IX_AF29

CORE_VCC_S0IX_AG27

CORE_VCC_S0IX_AG29

CORE_VCC_S0IX_AG30

CORE_VCC_S0IX_P26

CORE_VCC_S0IX_P27

CORE_VCC_S0IX_U27

CORE_VCC_S0IX_U29

CORE_VCC_S0IX_V27

CORE_VCC_S0IX_V29

CORE_VCC_S0IX_V30

CORE_VCC_S0IX_Y27

CORE_VCC_S0IX_Y29

CORE_VCC_S0IX_Y30

TP_CORE_V1P05_S4

VLV_M_D/BGA

REV = 2.0

7 OF 13

DRAM_VDD_S4_BD49

DRAM_VDD_S4_BD52

DRAM_VDD_S4_BD53

DRAM_VDD_S4_BF44

DRAM_VDD_S4_BG51

DRAM_VDD_S4_BJ48

DRAM_VDD_S4_C51

DRAM_VDD_S4_D44

DRAM_VDD_S4_F49

DRAM_VDD_S4_F52

DRAM_VDD_S4_F53

DRAM_VDD_S4_H46

DRAM_VDD_S4_M41

DRAM_VDD_S4_M42

DRAM_VDD_S4_V38

DRAM_VDD_S4_Y38

UNCORE_VNN_S3_AA24

UNCORE_VNN_S3_AC22

UNCORE_VNN_S3_AC24

UNCORE_VNN_S3_AD22

UNCORE_VNN_S3_AD24

UNCORE_VNN_S3_AF22

UNCORE_VNN_S3_AF24

UNCORE_VNN_S3_AG22

UNCORE_VNN_S3_AG24

UNCORE_VNN_S3_AJ22

UNCORE_VNN_S3_AJ24

UNCORE_VNN_S3_AK22

UNCORE_VNN_S3_AK24

UNCORE_VNN_S3_AK25

UNCORE_VNN_S3_AK27

UNCORE_VNN_S3_AK29

UNCORE_VNN_S3_AK30

UNCORE_VNN_S3_AK32

UNCORE_VNN_S3_AM22

TP2_CORE_VCC_S0IX

BD49

BD52

BD53

BF44

BG51

BJ48

C51

D44

F49

F52

F53

H46

M41

M42

V38

Y38

AA24

AC22

AC24

AD22

AD24

AF22

AF24

AG22

AG24

AJ22

AJ24

AK22

AK24

AK25

AK27

AK29

AK30

AK32

AM22

AA22

TP15

C206

2.2U/10V_4

C212

0.1U/16V_4

C257

10U/6.3V_6

C229

22U/6.3V_6

C233

1U/6.3V_4

Back side

C179

2.2U/10V_4

C208

0.1U/16V_4

C254

10U/6.3V_6

C255

22U/6.3V_6

C250

1U/6.3V_4

C200

2.2U/10V_4

C201

0.1U/16V_4

C297

10U/6.3V_6

C256

22U/6.3V_6

C241

1U/6.3V_4

+V_VDDQ

C202

2.2U/10V_4

C207

0.1U/16V_4

+VCC_GFX_CORE

VNN (+VCC_GFX_CORE)

Max current 14A

Back side

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

5

4

3

2

Wednesday, July 30, 2014

PROJECT :

Bay Trail M (POWER1/2)

Bay Trail M (POWER1/2)

Bay Trail M (POWER1/2)

1

UI2H

UI2H

UI2H

13 48

13 48

13 48

1B

1B

1B

5

V1P0S(+1.0V_RUN)

Max current 850mA

V1P0Sx(+1.0V_SX)

Max current 1.9 A

D D

C C

V1P0A(+1.0V_SUS)

Max current 325mA

V1P05S(+1.05V_RUN)

Max current 1A

V1P35Sx(+1.35VSFR)

Max current 375mA

V1P35S(+1.35V_RUN)

Max current 45mA

B B

A A

+1.0V_RUN

+1.0V_SX

+1.0V_SX

+1.0V_SX

+1.0V_SX

+1.0V_SX

+1.0V_SX

+1.0V_SX

+1.0V_RUN

+1.0V_RUN

+1.0V_RUN

+1.0V_RUN

+1.0V_RUN

+1.0V_SUS

+1.05V_RUN

+1.35VSFR

+1.35V_RUN

+1.35VSFR

+1.35V_RUN

CORE_V1P05_S3_PWR

SOC_V1P0_SOIX

SOC_V1P0_SOIX_PWR

SOC_V1P0_SOIX_AF36

SOC_PWR_V1P0_S3

SOC_V1P35_S3

SOC_PWR_V1P0_S3_AN18

SOC_PWR_V1P0_S3_M14

SOC_PWR_V1P0_S3_U18U19

SOC_PWR_V1P0_S3_PW R

SOC_PWR_V1P0_S3_Y18G1

UNCORE_V1P35_S0IX_AFG19

5

C49 1U/6.3V_4

SR21 *SR_0805

112

SR4 *SR_0402

112

SR5 *SR_0402

112

SR6 *SR_0603

112

SR7 *SR_0402

112

SR8 *SR_0402

112

SR9 *SR_0402

112

SR10 *SR_0402

112

SR11 *SR_0402

112

SR2 *SR_0402

112

SR13 *SR_0402

112

C247 1U/6.3V_4

C244 1U/6.3V_4

SR15 *SR_0402

112

SR16 *SR_0402

112

SR22 *SR_0603

112

C280 1U/6.3V_4

C278 1U/6.3V_4

SR17 *SR_0402

112

SR29 *SR_0603

112

C287 1U/6.3V_4

C292 1U/6.3V_4

SR3 *SR_0402

112

SR19 *SR_0402

112

SR20 *SR_0402

112

C261 1U/6.3V_4

C269 1U/6.3V_4

C232 1U/6.3V_4

C219 1U/6.3V_4

C236 22U/6.3V_6

C253 22U/6.3V_6

C222 1U/6.3V_4

C223 1U/6.3V_4

C251 1U/6.3V_4

C259 1U/6.3V_4

C54 *1U/6.3V_4_NC

C258 1U/6.3V_4

C277 *1U/6.3V_4_NC

C267 0.1U/16V_4

C275 1U/6.3V_4

C55 0.01U/16V_4

C293 1U/6.3V_4

C288 1U/6.3V_4

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

SOC_PWR_V1P0_S3

SOC_V1P0_SOIX_PWR

SOC_V1P0_SOIX_AF36

SOC_V1P0_SOIX_PWR2

SOC_V1P0_SOIX_DDI

SOC_V1P0_SOIX_DDI_AJ18

SOC_V1P0_SOIX_DDI_AM16

SOC_V1P0_G3

SOC_V1P0_SOIX

SOC_PWR_V1P0_S3_PW R

SOC_PWR_V1P0_S3_Y18G1

SOC_PWR_V1P0_S3

SOC_PWR_V1P0_S3_AN18

SOC_PWR_V1P0_S3

CORE_V1P05_S3

SOC_V1P0_SOIX

SOC_PWR_V1P0_S3_M14

SOC_PWR_V1P0_S3_U18U19

SOC_PWR_V1P0_S3

SOC_V1P0_G3

CORE_V1P05_S3_PWR

UNCORE_V1P35_S0IX

SOC_V1P35_S3

UNCORE_V1P35_S0IX_AFG19

SOC_V1P35_S3_AJ18AG19

4

SOC_V1P0_SOIX_PWR2

SOC_V1P0_SOIX_DDI_AJ18

SOC_V1P0_SOIX_DDI

SOC_V1P0_SOIX_DDI_AM16

SOC_V1P0_G3

UNCORE_V1P8_G3_AA18

UNCORE_V1P8_S3

UNCORE_V1P8_G3

VGA_V3P3_S3

LPC_V3P3V_S3

USB_HSIC_V1P2_G3

4

U5H

V32

SVID_V1P0_S3_V32

BJ6

VGA_V1P0_S3_BJ6

AD35

DRAM_V1P0_S0IX_AD35

AF35

DRAM_V1P0_S0IX_AF35

AF36

DRAM_V1P0_S0IX_AF36

AA36

DRAM_V1P0_S0IX_AA36

AJ36

DRAM_V1P0_S0IX_AJ36

AK35

DRAM_V1P0_S0IX_AK35

AK36

DRAM_V1P0_S0IX_AK36

Y35

DRAM_V1P0_S0IX_Y35

Y36

DRAM_V1P0_S0IX_Y36

AK19

DDI_V1P0_S0IX_AK19

AK21

DDI_V1P0_S0IX_AK21

AJ18

DDI_V1P0_S0IX_AJ 18

AM16

DDI_V1P0_S0IX_AM16

U22

UNCORE_V1P0_G3_U22

V22

UNCORE_V1P0_G3_V22

AN29

UNCORE_V1P0_S0IX_AN29

AN30

UNCORE_V1P0_S0IX_AN30

AF16

UNCORE_V1P0_S3_AF16

AF18

UNCORE_V1P0_S3_AF18

Y18

UNCORE_V1P0_S3_Y18

G1

UNCORE_V1P0_S3_G1

AM21

PCIE_V1P0_S3_AM21

AN21

PCIE_V1P0_S3_AN21

AN18

PCIE_SATA_V1P0_S3_AN18

AN19

SATA_V1P0_S3_AN19

AA33

CORE_V1P05_S3_AA33

AF21

UNCORE_V1P0_S0IX_AF21

AG21

UNCORE_V1P0_S0IX_AG 21

V24

UNCORE_V1P0_S0IX_V24

Y22

UNCORE_V1P0_S0IX_Y22

Y24

UNCORE_V1P0_S0IX_Y24

M14

USB_V1P0_S3_M14

U18

USB_V1P0_S3_U18

U19

USB_V1P0_S3_U19

AN25

GPIO_V1P0_S3_AN25

Y19

USB3_V1P0_G3_Y19

C3

USB3_V1P0_G3_C3

C5

UNCORE_V1P0_G3_C5

B6

UNCORE_V1P0_G3_B6

AC32

CORE_V1P05_S3_AC32

Y32

CORE_V1P05_S3_Y32

U36

UNCORE_V1P35_S0IX_F4 _U36

AA25

UNCORE_V1P35_S0IX_F5 _AA25

AG32

UNCORE_V1P35_S0IX_F2 _AG32

V36

UNCORE_V1P35_S0IX_F3 _V36

BD1

VGA_V1P35_S3_F1_BD1

AF19

UNCORE_V1P35_S0IX_F6

AG19

UNCORE_V1P35_S0IX_F1 _AG19

AJ19

ICLK_V1P35_S3_F1_AJ19

AG18

ICLK_V1P35_S3_F2

AN16

VSSA_AN16

U16

USB_VSSA_U16

VLV_M_D/BGA

REV = 2.0

C225 1U/6.3V_4

C215 1U/6.3V_4

C279 1U/6.3V_4

C296 1U/6.3V_4

C265 1U/6.3V_4

C271 1U/6.3V_4

C273 1U/6.3V_4

C270 1U/6.3V_4

C276 0.01U/16V_4C237 22U/6.3V_6

C286 1U/6.3V_4

C248 1U/6.3V_4

C235 1U/6.3V_4

C239 1U/6.3V_4

C226 1U/6.3V_4

C260 1U/6.3V_4

C252 *1U/6.3V_4_NC

C243 1U/6.3V_4

C285 1U/6.3V_4

8 OF 13

3

DRAM_V1P35_S0IX_F1_AD3 6

HDA_LPE_V1P5V1P8_S3_AM32

UNCORE_V1P8_S3_AM30

UNCORE_V1P8_S3_AN32

LPC_V1P8V3P3_S3_AM27

UNCORE_V1P8_G3_U24

UNCORE_V1P8_S3_U38

SD3_V1P8V3P3_S3_AN27

USB_HSIC_V1P24_G3_V 18

UNCORE_V1P8_G3_AA18

CORE_V1P05_S3_AF33

CORE_V1P05_S3_AG33

CORE_V1P05_S3_AG35

3

USB_V3P3_G3_N18

USB_V3P3_G3_P18

VGA_V3P3_S3_AN24

PCU_V1P8_G3_V25

PCU_V3P3_G3_N22

VSS_AD16

VSS_AD18

RTC_VCC_P22

USB_V1P8_G3_N20

PMU_V1P8_G3_U25

CORE_V1P05_S3_U33

CORE_V1P05_S3_U35

CORE_V1P05_S3_V33

VSS_A3_A3

VSS_A49_A49

VSS_A5_A5

VSS_A51_A51

VSS_A52_A52

VSS_A6_A6

VSS_B2_B2

VSS_B52_B52

VSS_B53_B53

VSS_BE1_BE1

VSS_BE53_BE53

VSS_BG1_BG1

VSS_BG53_BG53

VSS_BH1_BH1

VSS_BH2_BH2

VSS_BH52_BH52

VSS_BH53_BH53

VSS_BJ2_BJ2

VSS_BJ3_BJ3

VSS_BJ5_BJ5

VSS_BJ49_BJ49

VSS_BJ51_BJ51

VSS_BJ52_BJ52

VSS_C1_C1

VSS_C53_C53

VSS_E1_E1

VSS_E53_E53

RESERVED_F1

PCIE_V1P0_S3_AK18

PCIE_V1P0_S3_AM18

AD36

AM32

AM30

AN32

AM27

U24

N18

P18

U38

AN24

V25

N22

AN27

AD16

AD18

V18

AA18

P22

N20

U25

AF33

AG33

AG35

U33

U35

V33

A3

A49

A5

A51

A52

A6

B2

B52

B53

BE1

BE53

BG1

BG53

BH1

BH2

BH52

BH53

BJ2

BJ3

BJ5

BJ49

BJ51

BJ52

C1

C53

E1

E53

F1

AK18

AM18

2

C228 1U/6.3V_4

UNCORE_V1P35_S0IX

HDA_V1P5_AM32_PWR

UNCORE_V1P8_S3

LPC_V3P3V_S3

UNCORE_V1P8_G3

SOC_V3P3V_G3

UNCORE_V1P8_S3

VGA_V3P3_S3

UNCORE_V1P8_G3

SOC_V3P3V_G3

UNCORE_V1P8_S3

VSS_AD18_AD16

USB_HSIC_V1P2_G3

UNCORE_V1P8_G3_AA18

RTC_VCC_P22_PWR

UNCORE_V1P8_G3

CORE_V1P05_S3

C238

1U/6.3V_4

TP7

PCIE_V1P0_S3

1U/6.3V_4

1U/6.3V_4

C266

C211

C291

1U/6.3V_4

2

LPC_V3P3V_S3

C234 1U/6.3V_4

SR225 *SR_0402

SR14 *SR_0603

SR23 *SR_0402

SR24 *SR_0402

SR18 *SR_0603

SR25 *SR_0402

SR26 *SR_0402

SR27 *SR_0402

SR28 *SR_0402

SR1 *SR_0402

SR12 *SR_0603

SR93 *SR_0402

1

R228 *0_4_NC

2

112

2

112

2

112

2

112

2

112

C262 1U/6.3V_4

C264 0.1U/16V_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

2

112

2

112

2

112

2

112

2

112

2

112

2

112

Wednesday, July 30, 2014

Wednesday, July 30, 2014

Wednesday, July 30, 2014

+1.8V_RUN

V1P8S / V1P5V1P8S (+1.8V_RUN)

+1.8V_RUN

Max current 10mA

+1.8V_RUN

V1P8A(+1.8V_SUS)

+3.3V_RUN

Max current 65 mA

+1.8V_SUS

+3.3V_SUS

V3P3A(+3.3V_SUS)

Max current 50 mA

+3.3V_RUN

V3P3S / V1P8V3P3S(+3.3V_RUN)

Max current 25+8mA

V1P0A(+1.0V_SUS)

+1.0V_SUS

Max current 35 mA

+1.8V_SUS

+RTC_CELL

VRTC(+RTC_CELL)

Max current 140u uA

+1.05V_RUN

+1.0V_RUN

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Bay Trail M (POWER2/2)

Bay Trail M (POWER2/2)

Bay Trail M (POWER2/2)

1

UI2H

UI2H

UI2H

14 48

14 48

14 48

1B

1B

1B

5

4

3

2

1

U5I

A11

VSS1

A15

VSS2

AA1

AA16

AA19

AA21

AA3

AA32

AA35

AA38

AA53

AB10

AB4

AB41

AB45

AB47

AB48

AB50

AB51

AB6

AC16

AC18

AC19

AC21

AC25

AC33

AC35

BF30

BF36

BG31

BG34

BG39

BG42

BG45

BG49

BJ11

BJ15

BJ19

BJ23

BJ27

BJ31

BJ35

BJ39

BJ43

BJ47

A19

A23

A27

A31

A35

A39

A43

A47

BF4

BJ7

C14

C31

C34

C39

C42

C45

C49

D12

D16

D24

D30

D36

D38

E19

E35

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VLV_M_D/BGA

REV = 2.0

U5L

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VLV_M_D/BGA

REV = 2.0

9 OF 13

12 OF 13

D D

C C

B B

A A

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

AC36

AC38

AD19

AD21

AD25

AD32

AD33

AD47

AD7

AE1

AE11

AE12

AE14

AE3

AE4

AE40

AE42

AE43

AE45

AE46

AE48

AE50

AE51

AE53

AE6

AE8

AE9

AF10

AF12

AF25

AF32

AF47

AG16

AG25

AG36

E8

F19

F2

F24

F27

F30

F35

F5

F7

G10

G20

G22

G26

G28

G32

G34

G42

H19

H27

H35

J1

J16

J19

J22

J27

J32

J35

J40

J53

K14

K22

K32

K36

K4

K50

AG38

AH4

AH41

AH45

AH7

AH9

AJ16

AJ21

AJ25

AJ27

AJ29

AJ30

AJ32

AJ33

AJ35

AJ38

AJ53

AK10

AK14

AK16

AK33

AK41

AK44

AM12

AM19

AM24

AM25

AM29

AM33

AM35

AM36

AM40

M28

M19

M26

M27

M34

M35

M38

M47

M51

N16

N38

N51

P13

P16

P19

P20

P24

P32

P35

P38

P47

P52

U11

U12

U14

U21

AJ1

AJ3

K9

L13

L19

L27

L35

N1

P4

P9

T40

U1

U5J

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VLV_M_D/BGA

REV = 2.0

U5M

VSS281

VSS282

VSS283

VSS284

VSS285

VSS286

VSS287

VSS288

VSS289

VSS290

VSS291

VSS292

VSS293

VSS294

VSS295

VSS296

VSS297

VSS298

VSS299

VSS300

VSS301

VSS302

VSS303

VSS304

VSS305

VSS306

VSS307

VSS308

VSS309

VSS310

VSS311

VSS312

VSS313

VSS314

VSS315

VLV_M_D/BGA

REV = 2.0

10 OF 13

13 OF 13

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS316

VSS317

VSS318

VSS319

VSS320

VSS321

VSS322

VSS323

VSS324

VSS325

VSS326

VSS327

VSS328

VSS329

VSS330

VSS331

VSS332

VSS333

VSS334

VSS335

VSS336

VSS337

VSS338

VSS339

VSS340

VSS341

VSS342

VSS343

VSS344

VSS345

VSS346

VSS347

VSS348

VSS349

VSS350

AH47

AH48

AH50

AH51

AH6

AM44

AM51

AM7

AN1

AN11

AN12

AN14

AN22

AN3

AN33

AN35

AN36

AN38

AN40

AN42

AN43

AN45

AN46

AN48

AN49

AN5

AN51

AN53

AN6

AN8

AN9

AP40

AT12

AT16

AT19

U3

U30

U32

U40

U42

U43

U45

U46

U48

U49

U5

U51

U53

U6

U8

U9

V12

V16

V19

V21

V35

V40

V44

V51

V7

Y10

Y14

Y16

Y21

Y25

Y33

Y41

Y44

Y7

Y9

AT24

AT27

AT30

AT35

AT38

AT4

AT47

AT52

AU1

AU24

AU3

AU30

AU38

AU51

AV12

AV13

AV14

AV18

AV19

AV24

AV27

AV30

AV35

AV38

AV47

AV51

AV7

AW13

AW19

AW27

AW3

AW35

AY10

AY22

AY32

U5K

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VLV_M_D/BGA

REV = 2.0

11 OF 13

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

AY36

AY4

AY50

AY9

BA14

BA19

BA22

BA27

BA32

BA35

BA40

BA53

BB19

BB27

BB35

BC20

BC22

BC26

BC28

BC32

BC34

BC42

BD19

BD24

BD27

BD30

BD35

BE19

BE2

BE35

BE8

BF12

BF16

BF24

BF38

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

Wednesday, July 30, 2014

Date: Sheet of

5

4

3

2

Wednesday, July 30, 2014

PROJECT :

Bay Trail M (GND)

Bay Trail M (GND)

Bay Trail M (GND)

1

UI2H

UI2H

UI2H

15 48

15 48

15 48

1B

1B

1B

Loading...

Loading...