5

4

3

2

1

VER : 1A

BOM P/N

D D

Description

Memory Down

256MB*16

Max. 2G

P13

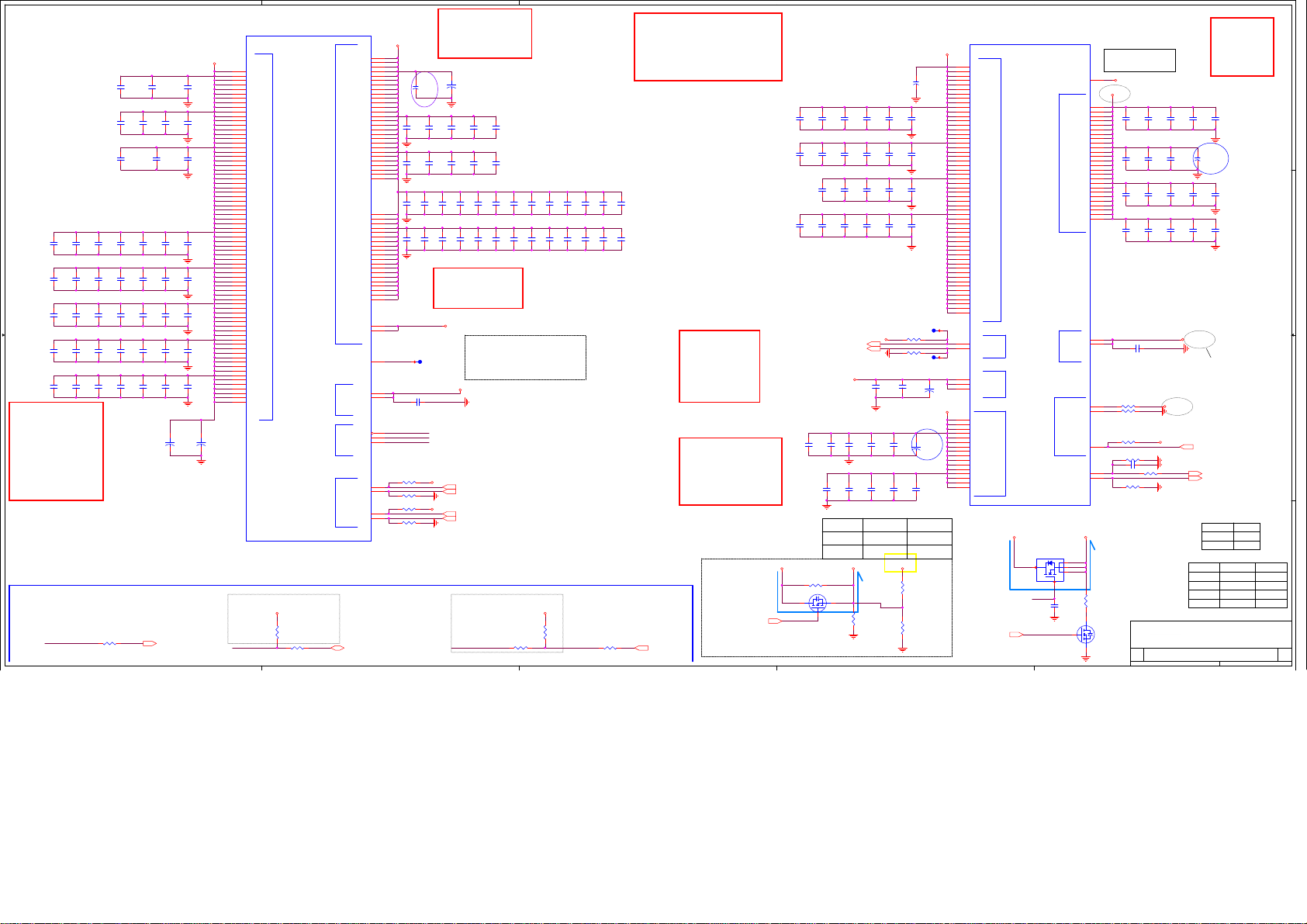

Tablet SYSTEM BLOCK DIAGRAM

DDR III 1333/1600 MHZ

mSATA - HDD

P20

IMC

SATA

Ivy Bridge

BGA 1023

8

W

P2,3,4,5,6

DI

F

FDI

DMI

DMI

MI(x4)

D

eDP

USB-2

eDP Conn.

TOUCH PANEL

P15

C C

Gyroscope

ST

L3GD20

P17

USB Port

USB3.0 *1

P19

USB3.0

USB-1

USB3.0

Display

HDMI

HDMI Conn.

P16

Sensor Hub

e-compass/

G sensor

ST

LSM303DLHC

Light sensor

CLM

CM3218A3OP

B B

P17

P17

DMIC

BOM Option Table

A A

Reference

EV@

SNB@

IVB@

IV@

* do not stuff

Description

Optimize SKU

For Sandy bridge.

For Ivy bridge.

or UMA.

F

5

ST

STM32F103RCY6TR

CCD Conn.

FRONT

CCD Conn.

REAR

POGO CONN

P15

P19

P19

AUDIO CODEC

REALTEK

ALC271-VB6

Speaker

P17

Azalia

4

P8

BATTERY

MIC/HP JACK

USB-11

USB-0

USB-8

USB-12

P14

Panther Point

USB2.0

RTC

I

HDA

PCH

BGA 989

P7, 8, 9, 10, 11, 12

EC

NUVOTON

WPCE885

W25X16VSS1G

SPI FLASH

P8

LPC

3

PCI-E x1

PCI-E x1

SPI

LPC

Fan Driver

P22

P19

X'TAL

32.768KHz

X'TAL

25MHz

SPI ROM

2M+4M

PCIE-8

P8

TPM

INFINEON

SLB9655

P18

2

Batery Charger

3V/5V

WLAN+BT

USB-10

P31

P32

FOXCONN

T77H372.00

+1.05V

+1.8V/+1V

+VGPU_IO

P20

P34

P37

P38

+VGFX_AXG

CPU core

Discharger

Thermal Protection

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROJECT :

Block Diagram

Block Diagram

Block Diagram

1

EE3

EE3

EE3

P33

P33

P37

P37

3A

3A

1 32Wednesday, September 12, 2012

1 32Wednesday, September 12, 2012

1 32Wednesday, September 12, 2012

3A

5

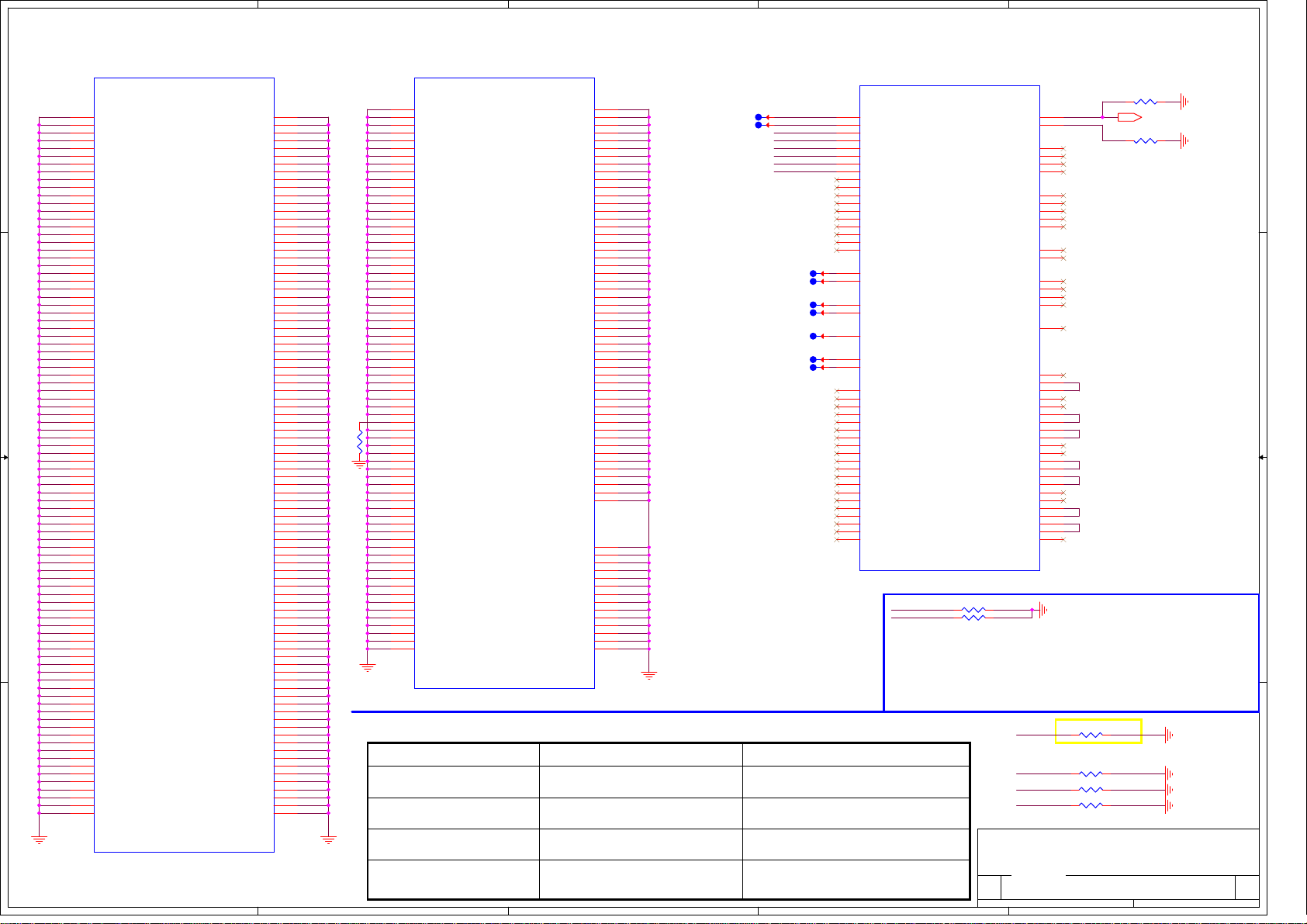

Ivy Bridge Processor (DMI,PEG,FDI)

DMI_TXN0(7)

DMI_TXN1(7)

DMI_TXN2(7)

D D

C C

eDP_ICOMPO 12mil

eDP_COMPIO 4mil

B B

DP_COMPIO and ICOMPO signals

should be shorted near balls and routed with

- typical impedance < 25 mohms

DMI_TXN3(7)

DMI_TXP0(7)

DMI_TXP1(7)

DMI_TXP2(7)

DMI_TXP3(7)

DMI_RXN0(7)

DMI_RXN1(7)

DMI_RXN2(7)

DMI_RXN3(7)

DMI_RXP0(7)

DMI_RXP1(7)

DMI_RXP2(7)

DMI_RXP3(7)

FDI_TXN0(7)

FDI_TXN1(7)

FDI_TXN2(7)

FDI_TXN3(7)

FDI_TXN4(7)

FDI_TXN5(7)

FDI_TXN6(7)

FDI_TXN7(7)

FDI_TXP0(7)

FDI_TXP1(7)

FDI_TXP2(7)

FDI_TXP3(7)

FDI_TXP4(7)

FDI_TXP5(7)

FDI_TXP6(7)

FDI_TXP7(7)

FDI_FSYNC0(7)

FDI_FSYNC1(7)

FDI_INT(7)

FDI_LSYNC0(7)

FDI_LSYNC1(7)

EDP_COMP

INT_EDP_HPD#

EDP_AUX#(15)

EDP_AUX(15)

EDP_TX0#(15)

EDP_TX1#(15)

EDP_TX0(15)

EDP_TX1(15)

DP & PEG Compensation

+1.05V_VTT

A A

EDP_COMP

PEG_COMP

R235 24.9/F_4

+1.05V_VTT

R258 24.9/F_4

5

M2

P6

P1

P10

N3

P7

P3

P11

K1

M8

N4

R2

K3

M7

P4

T3

U7

W11

W1

AA6

W6

V4

Y2

AC9

U6

W10

W3

AA7

W7

T4

AA3

AC8

AA11

AC12

U11

AA10

AG8

AF3

AD2

AG11

AG4

AF4

AC3

AC4

AE11

AE7

AC1

AA4

AE10

AE6

eDP Hot-plug (Disable)

CAD Note: Place PU resistor

within 2 inches of CPU

HPD PU/PD resistor values based

on CRB and different to DG

4

U24A

DMI_RX#[0]

DMI_RX#[1]

DMI_RX#[2]

DMI_RX#[3]

DMI_RX[0]

DMI_RX[1]

DMI_RX[2]

DMI_RX[3]

DMI_TX#[0]

DMI_TX#[1]

DMI_TX#[2]

DMI_TX#[3]

DMI_TX[0]

DMI_TX[1]

DMI_TX[2]

DMI_TX[3]

FDI0_TX#[0]

FDI0_TX#[1]

FDI0_TX#[2]

FDI0_TX#[3]

FDI1_TX#[0]

FDI1_TX#[1]

FDI1_TX#[2]

FDI1_TX#[3]

FDI0_TX[0]

FDI0_TX[1]

FDI0_TX[2]

FDI0_TX[3]

FDI1_TX[0]

FDI1_TX[1]

FDI1_TX[2]

FDI1_TX[3]

FDI0_FSYNC

FDI1_FSYNC

FDI_INT

FDI0_LSYNC

FDI1_LSYNC

eDP_COMPIO

eDP_ICOMPO

eDP_HPD

eDP_AUX#

eDP_AUX

eDP_TX#[0]

eDP_TX#[1]

eDP_TX#[2]

eDP_TX#[3]

eDP_TX[0]

eDP_TX[1]

eDP_TX[2]

eDP_TX[3]

SNB_2CBGA_1P0

DG 1.0 :

he recommended AC cap value is changed to 220nF for compatibility with

T

PCIe Gen3 on future platforms.

For Gen2 only designs, it is acceptable to continue to use the 100nF capacitor.

DMI Intel(R) FDI DP

4

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PCI EXPRESS -- GRAPHICS

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

+1.05V_VTT

INT_EDP_HPD#

Q25

2N7002D

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

R468

1K_4

3

1

G3

G1

G4

H22

J21

B22

D21

A19

D17

B14

D13

A11

B10

G8

A8

B6

H8

E5

K7

K22

K19

C21

D19

C19

D16

C13

D12

C11

C9

F8

C8

C5

H6

F6

K6

G22

C23

D23

F21

H19

C17

K15

F17

F14

A15

J14

H13

M10

F10

D9

J4

F22

A23

D24

E21

G19

B18

K17

G17

E14

C15

K13

G13

K10

G10

D8

K4

0.22uF AC coupling Caps for PCIE GEN1/2/3

2

EDP_HPD

R467

100K_4

3

PEG_COMP

EDP_HPD (15)

3

PEG_ICOMPO 12mil

PEG_ICOMPI, PEG_RCOMPO 4mil,

Thermal Sensor

+3V

C413

0.1u/10V_4

10u/6.3V_4

C412

2

U14

1

VDD

2

D+

THERMAL-(18)

THM_TCRIT#

+3V +3V

3

D-

4

TCRIT#

NCT7718W

R417

10K_4

THM_ALERT# THM_TCRIT#

ALERT# Pull Up Value

2K ohm

7.5K ohm

10.5K ohm

14K ohm

18.7K ohm

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet

1

PEG_ICOMPI and RCOMPO signals

should be shorted and routed with

- max length = 500 mils

- typical impedance = 43 mohms

PEG_ICOMPO signals should be routed with

- max length = 500 mils

- typical impedance = 14.5 mohms

SCLK

SDAT

ALERT#

GND

8

7

6

5

THM_ALERT#

R320

10K_4

THM_CLK (22)

THM_DATA (22)THERMAL+(18)

Alert temperature point

75 degree

90 degree

100 degree

105 degree

110 degree

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Ivy Bridge 1/5

Ivy Bridge 1/5

Ivy Bridge 1/5

Wednesday, September 12, 2012

Wednesday, September 12, 2012

Wednesday, September 12, 2012

1

EE3

EE3

EE3

of

2 32

2 32

2 32

3A

3A

3A

5

4

3

2

1

Boot S3 S3 RSM

+1.5V_CPU

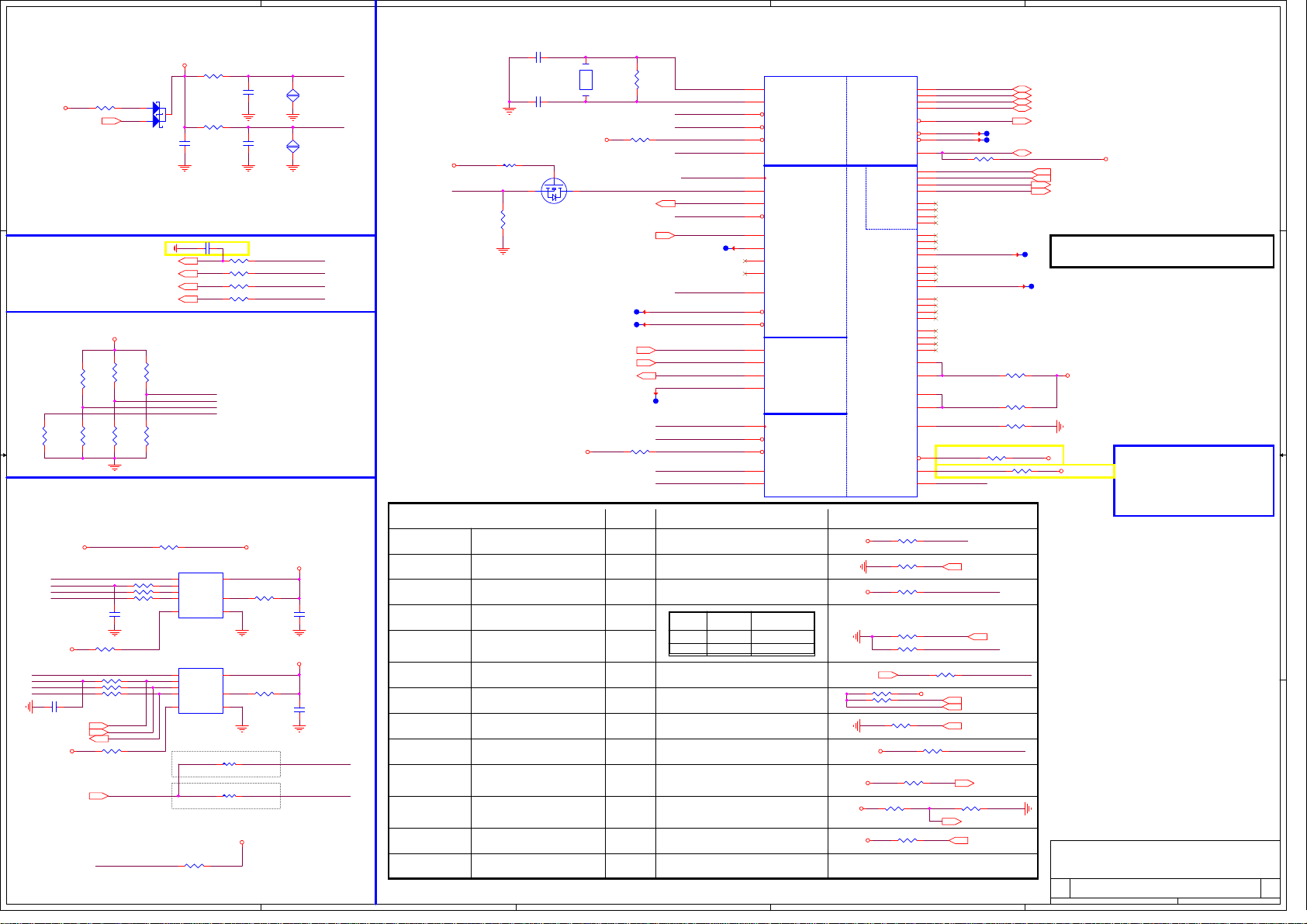

Ivy Bridge Processor (CLK,MISC,JTAG)

D D

H_SNB_IVB#(8)

TP71

TP_CATERR#

TP95

EC_PECI(22)

TP80

H_PROCHOT#_R

12

*43P/50V_4N

CPU_PLTRST#_RCPU_PLTRST#

R289

*750/F_4

H_PROCHOT#(22,23,28)

PM_THRMTRIP#(10)

C C

Over 130 degree C will

rive low

d

PM_SYNC(7)

H_PWRGOOD(10)

Isolate Space:20mils

+1.05V_VTT

B B

R287 75/F_4

C503

C493 0.1U/10V_4

R519 10K_4

PM_DRAM_PWRGD_R

R288 43_4

U24B

F49

PROC_SELECT#

C57

PROC_DETECT#

C49

CATERR#

A48

PECI

C45

PROCHOT#

D45

THERMTRIP#

C48

PM_SYNC

B46

UNCOREPWRGOOD

BE45

SM_DRAMPWROK

D44

RESET#

SNB_2CBGA_1P0

MISC THERMAL PWR MANAGEMENT

CLOCKS

DDR3

MISC

JTAG & BPM

BCLK

BCLK#

DPLL_REF_CLK

DPLL_REF_CLK#

BCLK_ITP

BCLK_ITP#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PRDY#

PREQ#

TCK

TMS

TRST#

TDO

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

TDI

J3

H2

AG3

AG1

N59

CLK_PCIE_XDPP_R

N58

CLK_PCIE_XDPN_R

AT30

BF44

SM_RCOMP_0

BE43

SM_RCOMP_1

BG43

SM_RCOMP_2

N53

N55

L56

L55

J58

M60

L59

K58

XDP_DBRST#_R

G58

E55

E59

G55

G59

H60

J59

J61

XDP_PRDY#

XDP_PREQ#

XDP_TCLK

XDP_TMS

XDP_TRST#

XDP_TDI

XDP_TDO

CLK_CPU_BCLKP (9)

TP88

TP89

CLK_CPU_BCLKN (9)

R483 *0_4

R480 *0_4

Isolate Space:20mils

CPU_DRAMRST# (4,22)

R448 140/F_4

R449 25.5/F_4R512 56_4

R450 200/F_4

Impedance 85ohm

TP69

XDP_TCLK (8)

XDP_TMS (8)

XDP_TDO (8)

R255 0_4

TP74

TP73

TP76

TP70

TP93

TP92

TP91

TP90

CLK_DPLL_SSCLKP (9)

CLK_DPLL_SSCLKN (9)

CLK_PCIE_XDPP (9)

CLK_PCIE_XDPN (9)

CAD NOTE: All DDR_COMP signals

should be routed such that :-

- max length = 500 mils

- trace width = 15mils and

- MB trace impedance < 68 mohms

(worst case resistance)

XDP_DBRST# (7)

DRAM_PWRGD

SYS_PWROK

SM_DRAMPWROK

If motherboard only supports external graphics or if

Processor Graphics but without eDP:

Connect DPLL_REF_SSCLK on Processor to GND through 1K +/5% resistor.

Connect DPLL_REF_SSCLK# on Processor to VCCP through 1K +/

- 5% resistor

Option for Prochot# function

68 ohm for unused, 62 ohm for used

H_PROCHOT#

XDP_TMS

TP101

XDP_TDI

TP97

XDP_TDO

XDP_PREQ#

XDP_TCLK

TP102

XDP_TRST#

When MP, JTAG PU/PD resistor can be

removed? (Yes Intel, TDI, TDO, TMS, TRST#,

TCK,PREQ#, PRDY#)

R520 62_4

R252 51_4

R254 51_4

R253 51_4

R250 *51_4

R261 51_4

R256 51_4

100 ns after +1.5V_CPU

reaches 80%

it supports

+1.05V_VTT

+3V

4

CPU_PLTRST#

CPU_PLTRST#_R

3 32

3 32

3 32

C507

0.1U/10V_4

3A

3A

3A

Thermal Trip

IMVP_PWRGD(7,28)

A A

<CPU>

PM_THRMTRIP#

5

2

1 3

+1.05V_VTT

3

1

R508

1K_4

2

Q32

2N7002D

Q33

MMBT3904

SYS_SHDN# (19,24,29)

4

+3V_S5

+1.35V_CPU

5

PM_DRAM_PWRGD(7)

s3 leakage circuit

R229

R222

*10K_4

*1K_4

SYS_PWROK(7)

6

2

*2N7002DW

Q24

1

4 3

R466 0_4

If PM_DRAM_PWEGD connector,the R5180 must stuff.

+3V_S5

+1.35V_CPU

R224

200/F_4

R227 130/F_4

R447 *39_4

MAINON_ON_G(5,29)

2

1

3

C466

0.1u/10V_4

U23

4

74AHC1G09

3 5

R228 *0_4

PM_DRAM_PWRGD_RPM_DRAM_PWRGD_Q

Q16 *2N7002D

3

2

2

U28

1

VCC5NC

PCI_PLTRST#(9,22)

2

74LVC1G07GW_NC

R290 *1.5K/F_4

IN

GND3OUT

IN OUT

L L

1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Ivy Bridge 2/5

Ivy Bridge 2/5

Ivy Bridge 2/5

Wednesday, September 12, 2012

Wednesday, September 12, 2012

Wednesday, September 12, 2012

H High-Z

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

EE3

EE3

EE3

1

5

4

3

2

1

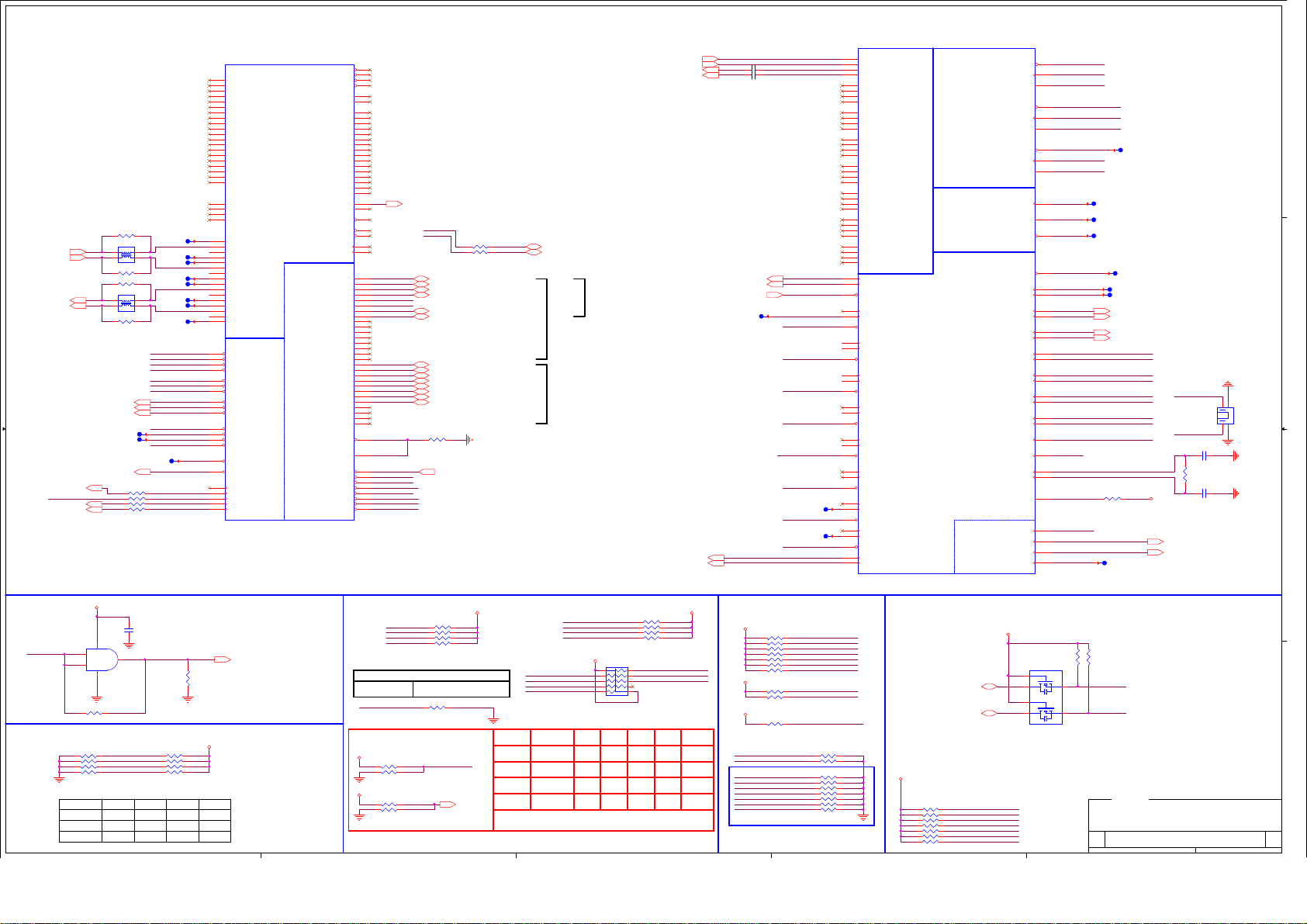

Sandy Bridge Processor (DDR3)

BD13

BF12

BD10

BD14

BE13

BF16

BE17

BE18

BE21

BE14

BG14

BG18

BF19

BD50

BF48

BD53

BF52

BD49

BE49

BD54

BE53

BF56

BE57

BC59

AY60

BE54

BG54

BA58

AW59

AW58

AU58

AN61

AN59

AU59

AU61

AN58

AR58

AK58

AL58

AG58

AG59

AM60

AL59

AF61

AH60

BG39

BD42

AT22

AV43

BF40

BD45

U24D

AL4

SB_DQ[0]

AL1

SB_DQ[1]

AN3

SB_DQ[2]

AR4

SB_DQ[3]

AK4

SB_DQ[4]

AK3

SB_DQ[5]

AN4

SB_DQ[6]

AR1

SB_DQ[7]

AU4

SB_DQ[8]

AT2

SB_DQ[9]

AV4

SB_DQ[10]

BA4

SB_DQ[11]

AU3

SB_DQ[12]

AR3

SB_DQ[13]

AY2

SB_DQ[14]

BA3

SB_DQ[15]

BE9

SB_DQ[16]

BD9

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

BF8

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

DDR SYSTEM MEMORY B

SB_CLK[0]

SB_CLK#[0]

SB_CKE[0]

SB_CLK[1]

SB_CLK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

BA34

AY34

AR22

BA36

BB36

BF27

BE41

BE47

AT43

BG47

AL3

AV3

BG11

BD17

BG51

BA59

AT60

AK59

AM2

AV1

BE11

BD18

BE51

BA61

AR59

AK61

BF32

BE33

BD33

AU30

BD30

AV30

BG30

BD29

BE30

BE28

BD43

AT28

AV28

BD46

AT26

AU22

AP11

AJ10

AR11

AT13

AU13

BA13

BB11

AY13

AV14

AR14

AY17

AR19

BA14

AU14

BB14

BB17

BA45

AR43

AW48

BC48

BC45

AR45

AT48

AY48

BA49

AV49

BB51

AY53

BB49

AU49

BA53

BB55

BA55

AV56

AP50

AP53

AV54

AT54

AP56

AP52

AN57

AN53

AG56

AG53

AN55

AN52

AG55

AK56

BD37

BF36

BA28

BE39

BD39

AT41

U24C

AG6

SA_DQ[0]

AJ6

SA_DQ[1]

SA_DQ[2]

AL6

SA_DQ[3]

SA_DQ[4]

AJ8

SA_DQ[5]

AL8

SA_DQ[6]

AL7

SA_DQ[7]

SA_DQ[8]

AP6

SA_DQ[9]

AU6

SA_DQ[10]

AV9

SA_DQ[11]

AR6

SA_DQ[12]

AP8

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

BC7

SA_DQ[16]

BB7

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

BA7

SA_DQ[20]

BA9

SA_DQ[21]

BB9

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

DDR SYSTEM MEMORY A

SA_CLK[0]

SA_CLK#[0]

SA_CKE[0]

SA_CLK[1]

SA_CLK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AU36

AV36

AY26

AT40

AU40

BB26

BB40

BC41

AY40

BA41

AL11

AR8

AV11

AT17

AV45

AY51

AT55

AK55

AJ11

AR10

AY11

AU17

AW45

AV51

AT56

AK54

BG35

BB34

BE35

BD35

AT34

AU34

BB32

AT32

AY32

AV32

BE37

BA30

BC30

AW41

AY28

AU26

M_A_CLK1

M_A_CLK1#

M_A_CKE1

M_A_CS#1

M_A_ODT1

M_A_DQSN0

M_A_DQSN1

M_A_DQSN2

M_A_DQSN3

M_A_DQSN4

M_A_DQSN5

M_A_DQSN6

M_A_DQSN7

M_A_DQSP0

M_A_DQSP1

M_A_DQSP2

M_A_DQSP3

M_A_DQSP4

M_A_DQSP5

M_A_DQSP6

M_A_DQSP7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

TP49

TP43

TP44

M_A_DQSN[7:0] (13)

M_A_DQSP[7:0] (13)

M_A_CLK0 (13)

M_A_CLK0# (13)

M_A_CKE0 (13)

M_A_CS#0 (13)

M_A_ODT0 (13)

M_A_A[15:0] (13)

M_A_DQ[63:0](13)

D D

C C

M_A_BS#0(13)

M_A_BS#1(13)

M_A_BS#2(13)

B B

M_A_CAS#(13)

M_A_RAS#(13)

M_A_WE#(13)

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_WE#

M_A_CAS#

M_A_RAS#

M_A_BS#0

M_A_BS#2

M_A_CKE0

M_A_ODT0

M_A_CS#0

M_A_BS#1

SNB_2CBGA_1P0

C46

C1

1u/6.3V_4

1u/6.3V_4

R46 36_4

R91 36_4

R95 36_4

R24 36_4

R17 36_4

R80 36_4

R39 36_4

R66 36_4

R13 36_4

C17

1u/6.3V_4

2

C3

C79

1u/6.3V_4

1u/6.3V_4

+0.675V_DDR_VTT

C2

C7

1u/6.3V_4

10u/6.3V_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, September 12, 2012

Date: Sheet of

Wednesday, September 12, 2012

Date: Sheet of

Wednesday, September 12, 2012

PROJECT :

Ivy Bridge 3/5

Ivy Bridge 3/5

Ivy Bridge 3/5

1

EE3

EE3

EE3

4 32

4 32

4 32

3A

3A

3A

SNB_2CBGA_1P0

M_A_CLK1

R223

75/F_4

M_A_CLK1#

+3V_S5

s3 leakage circuit

S3 circuit:- DRAM_RST# to memory should be high during S3

A A

DDR3_DRAMRST#(13) CPU_DRAMRST# (3,22)

EC_DRAMRST_CNTRL(22)

DEEPS3_EC(13)

R48 1K/F_4

20120204 Change to EC for new BIOS 0.6

5

+1.35V_SUS

201201119 move R358 to near Q38 and del net DRAMRST_CNTRL_PCH,

and EC_DRAMRST_CNTRL and R616.

R59

1K_4

R53 *0_4

Q5 2N7002D

3

2

C30

0.047u/10V_4

1

R44

4.99K/F_4R47 0_4

4

R54

1K/F_4

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

R7 36_4

R3 36_4

R15 36_4

R1 36_4

R4 36_4

R10 36_4

R14 36_4

R2 36_4

R12 36_4

R8 36_4

R29 36_4

R16 36_4

R5 36_4

R11 36_4

R9 36_4

R34 36_4

3

+0.675V_DDR_VTT

+0.675V_DDR_VTT

5

Sandy Bridge Processor (POWER)

U24F

20120120 remove C621 for debug IC.

C327

D D

C492

C342

C504

2.2u/10V_4

2.2u/10V_4

C351

2.2u/10V_4

C491

2.2u/10V_4

C343

2.2u/10V_4

C510

2.2u/10V_4

SVID CLK

H_CPU_SVIDCLK

2.2u/10V_4

C497

2.2u/10V_4

C350

2.2u/10V_4

C352

2.2u/10V_4

C499

2.2u/10V_4

C369

2.2u/10V_4

C358

2.2u/10V_4

C505

2.2u/10V_4

C500

2.2u/10V_4

R516 0_4

C C

CPU Core Power

IVY 17W:TDC 33A

B B

IVY SPEC

1.9mΩ/LoadlineDesign

total : 2.2uF x 35

total : 22uF x 12

tatal : 470u x3(Power side*1)

Cose down

IVY SPEC

1.9mΩ/LoadlineDesign

total : 2.2uF x 35

total : 10uF x 12

tatal : 470u x1(Power side*1)

A A

Layout note: need routing

together and ALERT need

between CLK and DATA

C339

10u/6.3V_4

10u/6.3V_4

C375

C366

10u/6.3V_4

10u/6.3V_4

20120120 remove C622 for debug IC.

C371

10u/6.3V_4

C365

C367

2.2u/10V_4

2.2u/10V_4

C353

C370

2.2u/10V_4

2.2u/10V_4

C319

C344

2.2u/10V_4

2.2u/10V_4

C325

C326

2.2u/10V_4

2.2u/10V_4

C496

C364

2.2u/10V_4

2.2u/10V_4

5

C328

10u/6.3V_4

C490

C372

10u/6.3V_4

10u/6.3V_4

C506

C318

10u/6.3V_4

10u/6.3V_4

C498

C338

2.2u/10V_4

2.2u/10V_4

C508

C341

2.2u/10V_4

2.2u/10V_4

C320

C340

2.2u/10V_4

2.2u/10V_4

C355

C495

2.2u/10V_4

2.2u/10V_4

C509

C317

2.2u/10V_4

2.2u/10V_4

C501

+

470u/2V_7343

VR_SVID_CLK (28 )

+VCC_CORE

A26

VCC[1]

A29

VCC[2]

A31

VCC[3]

A34

VCC[4]

A35

VCC[5]

A38

VCC[6]

A39

VCC[7]

A42

VCC[8]

C26

VCC[9]

C27

VCC[10]

C32

VCC[11]

C34

VCC[12]

C37

VCC[13]

C39

VCC[14]

C42

VCC[15]

D27

VCC[16]

D32

VCC[17]

D34

VCC[18]

D37

VCC[19]

D39

VCC[20]

D42

VCC[21]

E26

VCC[22]

E28

VCC[23]

E32

VCC[24]

E34

VCC[25]

E37

VCC[26]

E38

VCC[27]

F25

VCC[28]

F26

VCC[29]

F28

VCC[30]

F32

VCC[31]

F34

VCC[32]

F37

VCC[33]

F38

VCC[34]

F42

VCC[35]

G42

VCC[36]

H25

VCC[37]

H26

VCC[38]

H28

VCC[39]

H29

VCC[40]

H32

VCC[41]

H34

VCC[42]

H35

VCC[43]

H37

VCC[44]

H38

VCC[45]

H40

VCC[46]

J25

VCC[47]

J26

VCC[48]

J28

VCC[49]

J29

VCC[50]

J32

VCC[51]

J34

VCC[52]

J35

VCC[53]

J37

VCC[54]

J38

VCC[55]

J40

VCC[56]

J42

VCC[57]

K26

VCC[58]

K27

VCC[59]

K29

VCC[60]

K32

VCC[61]

K34

VCC[62]

K35

VCC[63]

K37

VCC[64]

K39

VCC[66]

K42

VCC[67]

L25

VCC[68]

L28

VCC[69]

L33

VCC[70]

L36

VCC[71]

L40

VCC[72]

N26

VCC[73]

N30

VCC[74]

N34

VCC[75]

N38

VCC[76]

C502

+

470u/2V_7343

SNB_2CBGA_1P0

Place PU resistor close to CPU

SVID DATA

H_CPU_SVIDDAT

CORE SUPPLY

PEG AND DDRSENSE LINES SVID QUIET RAILS

POWER

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSS_SENSE_VCCIO

+1.05V_VTT +1.05V_VTT

R513

130/F_4

R514 0_4

VR_SVID_DATA (28 )

VCCIO[1]

VCCIO[3]

VCCIO[4]

VCCIO[5]

VCCIO[6]

VCCIO[7]

VCCIO[8]

VCCIO[9]

VCCIO[10]

VCCIO[11]

VCCIO[12]

VCCIO[13]

VCCIO[14]

VCCIO[15]

VCCIO[16]

VCCIO[17]

VCCIO[18]

VCCIO[19]

VCCIO[20]

VCCIO[21]

VCCIO[22]

VCCIO[23]

VCCIO[24]

VCCIO[25]

VCCIO[26]

VCCIO[27]

VCCIO[28]

VCCIO[29]

VCCIO[30]

VCCIO[31]

VCCIO[32]

VCCIO[33]

VCCIO[34]

VCCIO[35]

VCCIO[36]

VCCIO[37]

VCCIO[38]

VCCIO[39]

VCCIO[40]

VCCIO[41]

VCCIO[42]

VCCIO[43]

VCCIO[44]

VCCIO[45]

VCCIO[46]

VCCIO[47]

VCCIO[48]

VCCIO[49]

VCCIO50

VCCIO51

VCCIO_SEL

VCCPQE[1]

VCCPQE[2]

VIDALERT#

VIDSCLK

VIDSOUT

AF46

AG48

AG50

AG51

AJ17

AJ21

AJ25

AJ43

AJ47

AK50

AK51

AL14

AL15

AL16

AL20

AL22

AL26

AL45

AL48

AM16

AM17

AM21

AM43

AM47

AN20

AN42

AN45

AN48

AA14

AA15

AB17

AB20

AC13

AD16

AD18

AD21

AE14

AE15

AF16

AF18

AF20

AG15

AG16

AG17

AG20

AG21

AJ14

AJ15

W16

W17

BC22

AM25

AN22

A44

B43

C44

F43

G43

AN16

AN17

4

+1.05V_VTT

C249

10u/6.3V_4

C234

10u/6.3V_4

C270

1u/6.3V_4

C287

1u/6.3V_4

VCCIO_SEL

C228 1U/6.3V_4

H_CPU_SVIDALRT#

H_CPU_SVIDCLK

H_CPU_SVIDDAT

R259 100_4

R251 100_4

R231 10_4

R226 10_4

4

CPU VCCIO

IVY 17W:8.5A

SNB : Spec

330uF/6mohm x 2

10uF x 10

1uF x 26

8/3 Change form

7343 to 3528

+

+

C455

C465

330u/2V_7343

220u/2.5V_352 8

C291

10u/6.3V_4

10u/6.3V_4

C289

C301

10u/6.3V_4

10u/6.3V_4

C258

C248

C220

1u/6.3V_4

1u/6.3V_4

1u/6.3V_4

C293

C241

C297

1u/6.3V_4

1u/6.3V_4

1u/6.3V_4

IVY SPEC

2uF_8 x7 Socket TOP cavity

2

22uF_8 x5 Socket BOT cavity

22uF_8 x2 Socket TOP cavity (no stuff)

22uF_8 x5 Socket BOT cavity (no stuff)

330uF_7343 x2

+1.05V_VTT

TP47

+1.05V_VTT

+VCC_CORE

VCC_SENSE (28)

VSS_SENSE (28)

+1.05V_VTT

VCCP_SENSE (26)

VSSP_SENSE (26)

Place PU resistor close to CPU

C

ose down

330uF/6mohm x 1

10

uF x 10

1uF x 26

C235

C288

10u/6.3V_4

10u/6.3V_4

C268

C242

10u/6.3V_4

10u/6.3V_4

C294

C250

C295

1u/6.3V_4

1u/6.3V_4

1u/6.3V_4

C252

C239

C247

1u/6.3V_4

1u/6.3V_4

1u/6.3V_4

Voltage selection for VCCIO:

his pin must be pulled high

t

on the motherboard

On CRB

H_SNB_IVB#_PWRC TRL = low, 1.0 V

H_SNB_IVB#_PWRC TRL = high/NC, 1.05V

R515 43_4

C300

1u/6.3V_4

C240

1u/6.3V_4

C238

1u/6.3V_4

C266

1u/6.3V_4

R521

75/F_4

VR_SVID_ALERT#_RH_CPU_SVIDALRT#

C255

1u/6.3V_4

C243

1u/6.3V_4

C292

1u/6.3V_4

C299

1u/6.3V_4

C290

1u/6.3V_4

C269

1u/6.3V_4

SVID ALERT

R518 0_4

C231

1u/6.3V_4

C251

1u/6.3V_4

3

CPU VCCAXG

IVY 17W:TDC 18A

Spec

3.9mΩ/

LoadlineDesign

total : 1uF x 11

total : 10uF x 6

total : 22uF x 6

tatal : 470u x 1(power side*2)

CPU VCCPL

IVY 17W:1.5A

Spec

330uF/7mohm x 1

1uF x 2 1uF x 2

IVY SPEC

330uF x1, 10uF_8 x1, 1uF_4 x2

Socket BOT edge.

IVY SPEC

30uF x1, 10uF_8 x1 Socket BOT edge,

3

10uF_8 x2 Socket BOT cavity.

CPU VCCSA

IVY 17W: 6A

Spec

330uF/7mohm x 1

10uF x 5

1uF x 5

VR_SVID_ALERT# (28)

3

Cose down

3.9mΩ/LoadlineDesign

total : 1uF x 11

total : 10uF x 12

tatal : 470u x 1(power side*2)

C278

10u/6.3V_4

C273

10u/6.3V_4

C335

1u/6.3V_4

VCCAXG_SENSE/V SSAXG_SENSE R= 100,

Trace impedanc e 15.5~34.5, < 25mils.

Real

10uF x 1

C336

10u/6.3V_4

Real

10uF x 3

+SMDDR_VREF +VDDR_REF_CPU +1 .35V_CPU

R443 *0_8

3

2

MAIND

MAIND(24,29)

S3 circuit: 1.5V input to IVB is gated &

IVB Read Vref 0.75V is gated

2

S

andy Bridge Processor (GRAPHIC POWER)

+

C469

220u/2.5V_352 8

C330

C307

10u/6.3V_4

10u/6.3V_4

C306

C272

10u/6.3V_4

10u/6.3V_4

C277

C276

1u/6.3V_4

1u/6.3V_4

C309

C334

1u/6.3V_4

1u/6.3V_4

CPU_VCCPLL

C198

1u/6.3V_4

8/3 Change form

7343 to 3528

C346

10u/6.3V_4

C345

1u/6.3V_4

R5347/R6362

C310

10u/6.3V_4C296

C333

10u/6.3V_4

C308

1u/6.3V_4

C274

1u/6.3V_4

R236 100_4

R244 100_4

C202

1u/6.3V_4

C337

+

10u/6.3V_4

C323

C321

1u/6.3V_4

1u/6.3V_4

R5347/R6362

R453

*1K/F_4

R436

*1K/F_4

change to 1K/F_4

2

TP56

TP59

C489

330u/2V_7343

C332

C331

10u/6.3V_4

10u/6.3V_4

C304

C305

10u/6.3V_4

10u/6.3V_4

C329

C303

1u/6.3V_4

1u/6.3V_4

C275

C271

1u/6.3V_4

1u/6.3V_4

+VCC_GFX

VCC_AXG_SENSE(2 8)

VSS_AXG_SENSE(28)

+1.35V_CPU

C322

C348

10u/6.3V_4

10u/6.3V_4

C349

C347

1u/6.3V_4

1u/6.3V_4

S3 S TUFF NO _STUFF

enable -

disable -

1

Q17

2N7002D

R442

100K_4

+VCC_GFX

+

C452

*330u/2V_7343

+VCCSA

U24G

AA46

VAXG[1]

AB47

VAXG[2]

AB50

VAXG[3]

AB51

VAXG[4]

AB52

VAXG[5]

AB53

VAXG[6]

AB55

VAXG[7]

AB56

VAXG[8]

AB58

VAXG[9]

AB59

VAXG[10]

AC61

VAXG[11]

AD47

VAXG[12]

AD48

VAXG[13]

AD50

VAXG[14]

AD51

VAXG[15]

AD52

VAXG[16]

AD53

VAXG[17]

AD55

VAXG[18]

AD56

VAXG[19]

AD58

VAXG[20]

AD59

VAXG[21]

AE46

VAXG[22]

N45

VAXG[23]

P47

VAXG[24]

P48

VAXG[25]

P50

VAXG[26]

P51

VAXG[27]

P52

VAXG[28]

P53

VAXG[29]

P55

VAXG[30]

P56

VAXG[31]

P61

VAXG[32]

T48

VAXG[33]

T58

VAXG[34]

T59

VAXG[35]

T61

VAXG[36]

U46

VAXG[37]

V47

VAXG[38]

V48

VAXG[39]

V50

VAXG[40]

V51

VAXG[41]

V52

VAXG[42]

V53

VAXG[43]

V55

VAXG[44]

V56

VAXG[45]

V58

VAXG[46]

V59

VAXG[47]

W50

VAXG[48]

W51

VAXG[49]

W52

VAXG[50]

W53

VAXG[51]

W55

VAXG[52]

W56

VAXG[53]

W61

VAXG[54]

Y48

VAXG[55]

Y61

VAXG[56]

F45

VAXG_SENSE

G45

VSSAXG_SENSE

BB3

VCCPLL[1]

BC1

VCCPLL[2]

BC4

VCCPLL[3]

L17

VCCSA[1]

L21

VCCSA[2]

N16

VCCSA[3]

N20

VCCSA[4]

N22

VCCSA[5]

P17

VCCSA[6]

P20

VCCSA[7]

R16

VCCSA[8]

R18

VCCSA[9]

R21

VCCSA[10]

U15

VCCSA[11]

V16

VCCSA[12]

V17

VCCSA[13]

V18

VCCSA[14]

V21

VCCSA[15]

W20

VCCSA[16]

SNB_2CBGA_1P0

20120807 Intel PDDG change

4.5A

MAINON_ON_G(3,29)

GRAPHICS

SENSE

LINES

1.8V RAIL

SA RAIL

SM_VREF

VDDQ[10]

VDDQ[11]

VDDQ[12]

VDDQ[13]

VDDQ[14]

VDDQ[15]

VDDQ[16]

VDDQ[17]

VDDQ[18]

VDDQ[19]

VDDQ[20]

VDDQ[21]

VDDQ[22]

DDR3 - 1.5V RAILS

POWER

VDDQ[23]

VDDQ[24]

VDDQ[25]

VDDQ[26]

VCCDQ[1]

VCCDQ[2]

QUIET RAILS

VDDQ_SENSE

VSS_SENSE_VDDQ

SENSE LINES

VCCSA_SENSE

VCCSA_VID[0]

VCCSA_VID[1]

Q19

MDV1528Q

1

5 2

3

4

MAIND

C449

470P/50V_4

MAINON_G

CAD Note: +VDDR_REF_CPU

should have 10 mil trace width

AY43

+VDDR_REF_CPU

+1.35V_CPU

20120807 Intel PDDG change

AJ28

VDDQ[1]

AJ33

VDDQ[2]

AJ36

VDDQ[3]

VDDQ[4]

VDDQ[5]

VDDQ[6]

VDDQ[7]

VDDQ[8]

VDDQ[9]

C232

AJ40

AL30

10u/6.3V_4

AL34

AL38

AL42

AM33

AM36

AM40

AN30

C219

AN34

AN38

10u/6.3V_4

AR26

AR28

AR30

AR32

AR34

AR36

C260

AR40

AV41

1u/6.3V_4

AW26

BA40

BB28

BG33

C265

1u/6.3V_4

AM28

AN26

C229 1U/6.3V_4

BC43

R203 *51_4

BA43

R212 *51_4

R247 *100/F_4

U10

SNB_IVB# N.A at SNB EDS #27637 0.7v1

R507 *10K_4

C494 *33n/10V_4

D48

D49

R517 0_4

R511 *10K_4

R94 for SN Bridge

20120807 Intel PDDG change to 1.35V

+1.35V_CPU+1.35V_SUS

R441

220_8

3

2

Q15

DMN601K-7

Size Document Number Rev

Size Document Number Rev

Size Document Number Re

1

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

CPU VDDQ

IVY 45W: 5A

Spec

330uF/6mohm x 1

1

0uF x 8

1uF x 10

C217

C216

C203

10u/6.3V_4

C244

*10u/6.3V_4

C261

1u/6.3V_4

C246

1u/6.3V_4

+1.35V_CPU

+VCCSA

201201117 C767 for Intel fw issue, if solve need un-stuff.

Wednesday, S eptember 12, 2012

Wednesday, S eptember 12, 2012

Wednesday, S eptember 12, 2012

1

C230

10u/6.3V_4

10u/6.3V_4

10u/6.3V_4

8/3 Change form

7343 to 3528

+

C197

C451

*10u/6.3V_4

220u/2.5V_352 8

C245

C263

C264

1u/6.3V_4

1u/6.3V_4

1u/6.3V_4

C208

C262

C259

1u/6.3V_4

1u/6.3V_4

1u/6.3V_4

+1.35V_CPU

20120807 Intel PDDG change

20120807 Intel PDDG change

VCCSA_SENSE (27)

VCCSA_VID0 (27)

VCCSA_VID1 (27)

A 1-K pull-down resistor should be placed on the

VCCSA VID lines. This will ensure the VID

is 00 prior to VCCIO stability..

For SN Bridge

VID[1] +VCCSA

0.9V

0

0.8V

1

For IV Bridge

VID[1]

VID[0]

0

0

1

0

0

1

1

1

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

EE3

PROJECT :

EE3

PROJECT :

Ivy Bridge 4/5

Ivy Bridge 4/5

Ivy Bridge 4/5

EE3

5 3 2

5 3 2

5 3 2

+VCCSA

0.9V

0.8V

0.725V

0.675V

v

3A

3A

3A

5

4

3

2

1

Sandy Bridge Processor (GND)

U24H

A13

VSS[1]

D D

C C

B B

A A

A17

A21

A25

A28

A33

A37

A40

A45

A49

A53

AA1

AA13

AA50

AA51

AA52

AA53

AA55

AA56

AA8

AB16

AB18

AB21

AB48

AB61

AC10

AC14

AC46

AC6

AD17

AD20

AD4

AD61

AE13

AE8

AF1

AF17

AF21

AF47

AF48

AF50

AF51

AF52

AF53

AF55

AF56

AF58

AF59

AG10

AG14

AG18

AG47

AG52

AG61

AG7

AH4

AH58

AJ13

AJ16

AJ20

AJ22

AJ26

AJ30

AJ34

AJ38

AJ42

AJ45

AJ48

AJ7

AK1

AK52

AL10

AL13

AL17

AL21

AL25

AL28

AL33

AL36

AL40

AL43

AL47

AL61

AM13

AM20

AM22

AM26

AM30

AM34

A9

VSS[2]

VSS[3]

VSS[4]

VSS[5]

VSS[6]

VSS[7]

VSS[8]

VSS[9]

VSS[10]

VSS[11]

VSS[12]

VSS[13]

VSS[14]

VSS[15]

VSS[16]

VSS[17]

VSS[18]

VSS[19]

VSS[20]

VSS[21]

VSS[22]

VSS[23]

VSS[24]

VSS[25]

VSS[26]

VSS[27]

VSS[28]

VSS[29]

VSS[30]

VSS[31]

VSS[32]

VSS[33]

VSS[34]

VSS[35]

VSS[36]

VSS[37]

VSS[38]

VSS[39]

VSS[40]

VSS[41]

VSS[42]

VSS[43]

VSS[44]

VSS[45]

VSS[46]

VSS[47]

VSS[48]

VSS[49]

VSS[50]

VSS[51]

VSS[52]

VSS[53]

VSS[54]

VSS[55]

VSS[56]

VSS[57]

VSS[58]

VSS[59]

VSS[60]

VSS[61]

VSS[62]

VSS[63]

VSS[64]

VSS[65]

VSS[66]

VSS[67]

VSS[68]

VSS[69]

VSS[70]

VSS[71]

VSS[72]

VSS[73]

VSS[74]

VSS[75]

VSS[76]

VSS[77]

VSS[78]

VSS[79]

VSS[80]

VSS[81]

VSS[82]

VSS[83]

VSS[84]

VSS[85]

VSS[86]

VSS[87]

VSS[88]

VSS[89]

VSS[90]

SNB_2CBGA_1P0

5

VSS

VSS[91]

VSS[92]

VSS[93]

VSS[94]

VSS[95]

VSS[96]

VSS[97]

VSS[98]

VSS[99]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

VSS[163]

VSS[164]

VSS[165]

VSS[166]

VSS[167]

VSS[168]

VSS[169]

VSS[170]

VSS[171]

VSS[172]

VSS[173]

VSS[174]

VSS[175]

VSS[176]

VSS[177]

VSS[178]

VSS[179]

VSS[180]

AM38

AM4

AM42

AM45

AM48

AM58

AN1

AN21

AN25

AN28

AN33

AN36

AN40

AN43

AN47

AN50

AN54

AP10

AP51

AP55

AP7

AR13

AR17

AR21

AR41

AR48

AR61

AR7

AT14

AT19

AT36

AT4

AT45

AT52

AT58

AU1

AU11

AU28

AU32

AU51

AU7

AV17

AV21

AV22

AV34

AV40

AV48

AV55

AW13

AW43

AW61

AW7

AY14

AY19

AY30

AY36

AY4

AY41

AY45

AY49

AY55

AY58

AY9

BA1

BA11

BA17

BA21

BA26

BA32

BA48

BA51

BB53

BC13

BC5

BC57

BD12

BD16

BD19

BD23

BD27

BD32

BD36

BD40

BD44

BD48

BD52

BD56

BD8

BE5

BG13

R257

*0_4

U24I

BG17

VSS[181]

BG21

VSS[182]

BG24

VSS[183]

BG28

VSS[184]

BG37

VSS[185]

BG41

VSS[186]

BG45

VSS[187]

BG49

VSS[188]

BG53

VSS[189]

BG9

VSS[190]

C29

VSS[191]

C35

VSS[192]

C40

VSS[193]

D10

VSS[194]

D14

VSS[195]

D18

VSS[196]

D22

VSS[197]

D26

VSS[198]

D29

VSS[199]

D35

VSS[200]

D4

VSS[201]

D40

VSS[202]

D43

VSS[203]

D46

VSS[204]

D50

VSS[205]

D54

VSS[206]

D58

VSS[207]

D6

VSS[208]

E25

VSS[209]

E29

VSS[210]

E3

VSS[211]

E35

VSS[212]

E40

VSS[213]

F13

VSS[214]

F15

VSS[215]

F19

VSS[216]

F29

VSS[217]

F35

VSS[218]

F40

VSS[219]

F55

VSS[220]

G48

VSS[221]

G51

VSS[222]

G6

VSS[223]

G61

VSS[224]

H10

VSS[225]

H14

VSS[226]

H17

VSS[227]

H21

VSS[228]

H4

VSS[229]

H53

VSS[230]

H58

VSS[231]

J1

VSS[232]

J49

VSS[233]

J55

VSS[234]

K11

VSS[235]

K21

VSS[236]

K51

VSS[237]

K8

VSS[238]

L16

VSS[239]

L20

VSS[240]

L22

VSS[241]

L26

VSS[242]

L30

VSS[243]

L34

VSS[244]

L38

VSS[245]

L43

VSS[246]

L48

VSS[247]

L61

VSS[248]

M11

VSS[249]

M15

VSS[250]

SNB_2CBGA_1P0

VSS

Processor Strapping

CFG2

(PCI-E Static x16 Lane Reversal)

CFG3

(PCI-E Static x4 Lane Reversal)

CFG4

(DP Presence Strap)

CFG7

(PEG Defer Training)

4

M4

VSS[251]

M58

VSS[252]

M6

VSS[253]

N1

VSS[254]

N17

VSS[255]

N21

VSS[256]

N25

VSS[257]

N28

VSS[258]

N33

VSS[259]

N36

VSS[260]

N40

VSS[261]

N43

VSS[262]

N47

VSS[263]

N48

VSS[264]

N51

VSS[265]

N52

VSS[266]

N56

VSS[267]

N61

VSS[268]

P14

VSS[269]

P16

VSS[270]

P18

VSS[271]

P21

VSS[272]

P58

VSS[273]

P59

VSS[274]

P9

VSS[275]

R17

VSS[276]

R20

VSS[277]

R4

VSS[278]

R46

VSS[279]

T1

VSS[280]

T47

VSS[281]

T50

VSS[282]

T51

VSS[283]

T52

VSS[284]

T53

VSS[285]

T55

VSS[286]

T56

VSS[287]

U13

VSS[288]

U8

VSS[289]

V20

VSS[290]

V61

VSS[291]

W13

VSS[292]

W15

VSS[293]

W18

VSS[294]

W21

VSS[295]

W46

VSS[296]

W8

VSS[297]

Y4

VSS[298]

Y47

VSS[299]

Y58

VSS[300]

Y59

VSS[301]

VSS_NCTF_1

VSS_NCTF_2

VSS_NCTF_3

VSS_NCTF_4

VSS_NCTF_5

VSS_NCTF_6

VSS_NCTF_7

VSS_NCTF_8

VSS_NCTF_9

VSS_NCTF_10

NCTF

VSS_NCTF_11

VSS_NCTF_12

VSS_NCTF_13

VSS_NCTF_14

A5

A57

BC61

BD3

BD59

BE4

BE58

BG5

BG57

C3

C58

D59

E1

E61

The CFG signals have a default value of '1' if not terminated on the board.

1 0

Normal Operation

Normal Operation

Disable; No physical DP attached to eDP

PEG train immediately following

xxRESETB de assertion

3

TP96

TP94

Lane Reversed

Lane Reversed

Enable; An ext DP device is connected to eDP

PEG wait for BIOS training

Sandy Bridge Processor (RESERVED, CFG)

BE7 SA_DIMM_VREFDQ

BG7 SB_DIMM_VREFDQ

BE7

BG7

N42

L42

L45

L47

M13

M14

U14

W14

P13

AT49

K24

AH2

AG13

AM14

AM15

N50

A4

C4

D3

D1

A58

A59

C59

A61

C61

D61

BD61

BE61

BE59

BG61

BG59

BG58

BG4

BG3

BE3

BG1

BE1

BD1

CFG2

R501 1K/F_4

R451 *1K_4

R452 *1K_4

processor signal balls BF3 and BG4 for

Ivy Bridge 4-core and balls BE7

and BG7 for Ivy Bridge 2-core

20111102 stuff for revers

CFG3

R509 *1K/F_4

CFG4

R510 1K/F_4

CFG7

R260 *1K/F_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Ivy Bridge 5/5

Ivy Bridge 5/5

Ivy Bridge 5/5

1

SMDDR_VREF_DQ0_M3 (13)

for M3 solution

n

eed R5265/R5266,

W/O M3 then NC

EE3

EE3

EE3

CFG1

CFG2

CFG3

CFG4CFG4

CFG5

CFG6

CFG7

TP75

TP66

TP65

TP64

TP72

TP68

TP67

U24E

B50

CFG[0]

C51

CFG[1]

B54

CFG[2]

D53

CFG[3]

A51

CFG[4]

C53

CFG[5]

C55

CFG[6]

H49

CFG[7]

A55

CFG[8]

H51

CFG[9]

K49

CFG[10]

K53

CFG[11]

F53

CFG[12]

G53

CFG[13]

L51

CFG[14]

F51

CFG[15]

D52

CFG[16]

L53

CFG[17]

H43

VCC_VAL_SENSE

K43

VSS_VAL_SENSE

H45

VAXG_VAL_SENSE

K45

VSSAXG_VAL_SENSE

F48

VCC_DIE_SENSE

H48

RSVD6

K48

RSVD7

BA19

RSVD8

AV19

RSVD9

AT21

RSVD10

BB21

RSVD11

BB19

RSVD12

AY21

RSVD13

BA22

RSVD14

AY22

RSVD15

AU19

RSVD16

AU21

RSVD17

BD21

RSVD18

BD22

RSVD19

BD25

RSVD20

BD26

RSVD21

BG22

RSVD22

BE22

RSVD23

BG26

RSVD24

BE26

RSVD25

BF23

RSVD26

BE24

RSVD27

SNB_2CBGA_1P0

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

CFG5

CFG6

RESERVED

R503 *1K/F_4

R498 *1K/F_4

RSVD45

DC_TEST_A4

DC_TEST_C4

DC_TEST_D3

DC_TEST_D1

DC_TEST_A58

DC_TEST_A59

DC_TEST_C59

DC_TEST_A61

DC_TEST_C61

DC_TEST_D61

DC_TEST_BD61

DC_TEST_BE61

DC_TEST_BE59

DC_TEST_BG61

DC_TEST_BG59

DC_TEST_BG58

DC_TEST_BG4

DC_TEST_BG3

DC_TEST_BE3

DC_TEST_BG1

DC_TEST_BE1

DC_TEST_BD1

CFG[6:5] (PCIE Port Bifurcation Straps)

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2 disabled

01: Reserved - (Device 1 function 1 disabled ; function 2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, September 12, 2012

Date: Sheet of

Wednesday, September 12, 2012

Date: Sheet of

2

Wednesday, September 12, 2012

6 32

6 32

6 32

3A

3A

3A

5

4

3

2

1

CPT/PPT (LVDS,DDI)

U21D

AM47

AM49

M45

AF37

AF36

AE48

AE47

AK39

AK40

AN48

AK47

AJ48

AN47

AK49

AJ47

AF40

AF39

AH45

AH47

AF49

AF45

AH43

AH49

AF47

AF43

M40

M47

M49

J47

P45

T40

K47

T45

P39

N48

P49

T49

T39

T43

T42

L_BKLTEN

L_VDD_EN

L_BKLTCTL

L_DDC_CLK

L_DDC_DATA

L_CTRL_CLK

L_CTRL_DATA

LVD_IBG

LVD_VBG

LVD_VREFH

LVD_VREFL

LVDSA_CLK#

LVDSA_CLK

LVDSA_DATA#0

LVDSA_DATA#1

LVDSA_DATA#2

LVDSA_DATA#3

LVDSA_DATA0

LVDSA_DATA1

LVDSA_DATA2

LVDSA_DATA3

LVDSB_CLK#

LVDSB_CLK

LVDSB_DATA#0

LVDSB_DATA#1

LVDSB_DATA#2

LVDSB_DATA#3

LVDSB_DATA0

LVDSB_DATA1

LVDSB_DATA2

LVDSB_DATA3

CRT_BLUE

CRT_GREEN

CRT_RED

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_VSYNC

DAC_IREF

CRT_IRTN

Panther Point_R1P0

SDVO_TVCLKINN

SDVO_TVCLKINP

SDVO_CTRLCLK

SDVO_CTRLDATA

LVDS

DDPC_CTRLCLK

DDPC_CTRLDATA

Digital Display Interface

DDPD_CTRLCLK

DDPD_CTRLDATA

CRT

CPT/PPT (DMI,FDI,PM)

U21C

D D

C C

XDP_DBRST#(3)

SYS_PWROK

PWROK_EC

PM_DRAM_PWRGD(3)

PCH_RSMRST#(22)

IOAC_PCIERST#(20,22)

DNBSWON#(22)

B B

ACPRESENT(23)

DMI_RXN0(2)

DMI_RXN1(2)

DMI_RXN2(2)

DMI_RXN3(2)

DMI_RXP0(2)

DMI_RXP1(2)

DMI_RXP2(2)

DMI_RXP3(2)

DMI_TXN0(2)

DMI_TXN1(2)

DMI_TXN2(2)

DMI_TXN3(2)

DMI_TXP0(2)

DMI_TXP1(2)

DMI_TXP2(2)

DMI_TXP3(2)

R486 49.9/F_4

+1.05V_VTT

R485 750/F_4

20110214 add SUSWAEN to SUSACK connector.

SUSWARN#_R

SUSACK#(22)

R184 0_4

R173 *0_4

R160 0_4

R395 0_4

R369 *0_4

C178 *1U/10V_4

R166 0_4

R150 *0_4

R370 *0_4

TP24

ACPRESENT

XDP_DBRST#

PM_DRAM_PWRGD

BC24

DMI0RXN

BE20

DMI1RXN

BG18

DMI2RXN

BG20

DMI3RXN

BE24

DMI0RXP

BC20

DMI1RXP

BJ18

DMI2RXP

BJ20

DMI3RXP

AW24

DMI0TXN

AW20

DMI1TXN

BB18

DMI2TXN

AV18

DMI3TXN

AY24

DMI0TXP

AY20

DMI1TXP

AY18

DMI2TXP

AU18

DMI3TXP

BJ24

DMI_ZCOMP

BG25

DMI_COMP

SUSACK#_R

SYS_PWROK_R

EC_PWROK_R

APWROK_R

PCH_RSMRST#PCH_RSMRST#

SUSWARN#_R DAC_IREF

PM_BATLOW#

PM_RI#

DMI_IRCOMP

BH21

DMI2RBIAS

C12

SUSACK#

K3

SYS_RESET#

P12

SYS_PWROK

L22

PWROK

L10

APWROK

B13

DRAMPWROK

C21

RSMRST#

K16

SUSWARN#/SUSPWRDNACK/GPIO30

E20

PWRBTN#

H20

ACPRESENT / GPIO31

E10

BATLOW# / GPIO72

A10

RI#

Panther Point_R1P0

+3V_S5

+3V_S5

+3V_S5

D

+3V_S5

+3V_S5

FDI_RXN0

FDI_RXN1

FDI_RXN2

FDI_RXN3

FDI_RXN4

FDI_RXN5

FDI_RXN6

FDI_RXN7

FDI_RXP0

FDI_RXP1

FDI_RXP2

FDI_RXP3

FDI_RXP4

FDI_RXP5

FDI_RXP6

DMI

FDI

FDI_RXP7

FDI_INT

FDI_FSYNC0

FDI_FSYNC1

FDI_LSYNC0

FDI_LSYNC1

DSWVRMEN

DPWROK

WAKE#

+3V

CLKRUN# / GPIO32

SUS_STAT# / GPIO61

SUSCLK / GPIO62

SLP_S5# / GPIO63

SLP_S4#

System Power Management

+3V_S5

SLP_S3#

SLP_A#

SW

SLP_SUS#

PMSYNCH

SLP_LAN# / GPIO29

Need notice BIOS if DMI or FDI reverse.

BJ14

AY14

BE14

BH13

BC12

BJ12

BG10

BG9

BG14

BB14

BF14

BG13

BE12

BG12

BJ10

BH9

AW16

AV12

BC10

AV14

BB10

A18

E22

B9

PCIE_WAKE#_LAN

N3

CLKRUN#

G8

N14

D10

H4

F4

G10

G16

AP14

K14

DPWROK_R

PCH_SUSCLK

SLP_A#

SLP_SUS#

SLP_LAN#

FDI_TXN0 (2)

FDI_TXN1 (2)

FDI_TXN2 (2)

FDI_TXN3 (2)

FDI_TXN4 (2)

FDI_TXN5 (2)

FDI_TXN6 (2)

FDI_TXN7 (2)

FDI_TXP0 (2)

FDI_TXP1 (2)

FDI_TXP2 (2)

FDI_TXP3 (2)

FDI_TXP4 (2)

FDI_TXP5 (2)

FDI_TXP6 (2)

FDI_TXP7 (2)

FDI_INT (2)

FDI_FSYNC0 (2)

FDI_FSYNC1 (2)

FDI_LSYNC0 (2)

FDI_LSYNC1 (2)

DSWVREN (8)

R349 0_4

CLKRUN# (18,22)

TP31

TP41

TP20

SUSC# (22)

SUSB# (22)

TP29

PM_SYNC (3)

DPWROK need to be

shorted to RSMRST# when Deep S4/S5 state is not support

DPWROK (22)

SLP_SUS# (11,22)

20111102 FDI reverse

20111111 FDI change to normal

20120104 change DPWROK from PCH_Rsmrst# to EC control.

INT_LVDS_BLON(15)

INT_LVDS_DIGON(15)

INT_LVDS_BRIGHT(15)

UM77 VGA/LVDS disable

R460

1K/F_4

1% or 5%

SDVO_STALLN

SDVO_STALLP

SDVO_INTN

SDVO_INTP

DDPB_AUXN

DDPB_AUXP

DDPB_HPD

DDPB_0N

DDPB_0P

DDPB_1N

DDPB_1P

DDPB_2N

DDPB_2P

DDPB_3N

DDPB_3P

DDPC_AUXN

DDPC_AUXP

DDPC_HPD

DDPC_0N

DDPC_0P

DDPC_1N

DDPC_1P

DDPC_2N

DDPC_2P

DDPC_3N

DDPC_3P

DDPD_AUXN

DDPD_AUXP

DDPD_HPD

DDPD_0N

DDPD_0P

DDPD_1N

DDPD_1P

DDPD_2N

DDPD_2P

DDPD_3N

DDPD_3P

AP43

AP45

AM42

AM40

AP39

AP40

P38

M39

AT49

AT47

AT40

AV42

AV40

AV45

AV46

AU48

AU47

AV47

AV49

P46

P42

AP47

AP49

AT38

AY47

AY49

AY43

AY45

BA47

BA48

BB47

BB49

M43

M36

AT45

AT43

BH41

BB43

BB45

BF44

BE44

BF42

BE42

BJ42

BG42

INT_HDMITX2N_C

INT_HDMITX2P_C

INT_HDMITX1N_C

INT_HDMITX1P_C

INT_HDMITX0N_C

INT_HDMITX0P_C

INT_HDMICLK-_C

INT_HDMICLK+_C

DisplayPort C DisplayPort D

HDMI_DDCCLK_SW (16)

HDMI_DDCDATA_SW (16)

INT_HDMITX2N_C (16)

INT_HDMITX2P_C (16)

INT_HDMITX1N_C (16)

INT_HDMITX1P_C (16)

INT_HDMITX0N_C (16)

INT_HDMITX0P_C (16)

INT_HDMICLK-_C (16)

INT_HDMICLK+_C (16)

HDMI_HP (16)

07

INT. HDMI

PCH Pull-high/low(CLG) System PWR_OK(CLG)

+3V

CLKRUN#

XDP_DBRST#

R424 4.99K/F_4

R430 *1K_4

PCH_RSMRST#

SYS_PWROK

R350 10K_4

R180 *10K_4

A A

PM_RI#

PM_BATLOW#

PCIE_WAKE#_LAN

SLP_LAN#

SUSWARN#_R

ACPRESENT

PM_DRAM_PWRGD

R347 10K_4R439 8.2K_4

R368 10K_4

R115 *10K_4

R333 10K_4

R55 *10K_4

R335 200/F_4

wo S3 leakage, un-stuff R5180

5

+3V_S5

to PCH Pin12, XDP and EE debug

SYS_PWROK(3)

SYS_PWROK

4

U7

4

TC7SH08FU

IMVP_PWRGD PU +3V

PWROK_EC PD

+3V_S5

so AND gate output dont need PD again

C415

0.1u/10V_4R101 8.2K_4

2

1

PWROK_EC

3 5

R52 *0_4

R79

100K_4

PWROK_EC (22)

+3V_S5

C436

*0.1U/10V_4

U13

IMVP_PWRGD_R

include GFX_PWRGD to SYS_PWROK for PCH check

3

4

*TC7SH08

R92 0_4

20111128 add 0ohm to passed IMVP_PERGD

2

1

3 5

IMVP_PWRGD (3,28)

GFX_PWRGD (22,28)

20121013 ADD FWSC for 200msce timing.

FWSC(22)

+0.75V_ON(22,25)

2

R559 0_4

R159 *0_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, September 12, 2012

Date: Sheet of

Wednesday, September 12, 2012

Date: Sheet of

Wednesday, September 12, 2012

APWROK_R

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Panther Point 1/6

Panther Point 1/6

Panther Point 1/6

EE3

EE3

EE3

1

R140

10K_4

7 32

7 32

7 32

3A

3A

3A

5

RTC Circuitry(RTC)

+3V_RTC

D10

BAT54C

R123

210/F_4

XDP_TMS

XDP_TDO

PCH_JTAG_TDO

XDP_TCLK

R124

100/F_4

1

6

5

2

3

1

6

5

2

3

R399 47K_4

R86 20K_4

30mils

R94 20K_4

C134

1u/6.3V_4

For EMI solution.

C420 *22p/50V_4

R387 33_4

R305 33_4

R356 33_4

R388 33_4

U18

CE#

VDD

SCK

SI

SO

HOLD#

WP#

VSS

ROM-2M_ME

U17

CE#

VDD

SCK

SI

SO

HOLD#

WP#

VSS

ROM-4M_EC

R407 *0_4

R416 0_4

+3V_PCH_ME

C40

1u/6.3V_4

C55

1u/6.3V_4

+3V_PCH_ME

8

7

R409 3.3K_4

4

8

7

R410 3.3K_4

4

20mils

D D

VCCRTC_1(19)

20MIL

R366 0_6

+3VPCU

HDA Bus(CLG)

PCH_AZ_CODEC_BITCLK(14)

PCH_AZ_CODEC_SYNC(14)

PCH_AZ_CODEC_RST#(14)

PCH_AZ_CODEC_SDOUT(14)

PCH JTAG Debug (CLG)

C C

R411

51_4

PCH Dual SPI

(CLG)

B B

+3V_PCH_ME

PCH_SPI_CS1#

PCH_SPI_CLK

PCH_SPI_SI

PCH_SPI_SO

C437 *22p/50V_4

PCH_SPI_CLK_EC(22)

PCH_SPI_SI_EC(22)

PCH_SPI_SO_EC(22)

+3V_PCH_ME

A A

SPI_CS0#_UR_ME(22)

+3V_S5

PCH_SPI_CS0#

PCH_SPI_CLK

PCH_SPI_SI

PCH_SPI_SO

R379 3.3K_4

R385 33_4

R107 33_4

R401 33_4

+3V_S5

R131

R420

210/F_4

210/F_4

R132

R419

100/F_4

100/F_4

W25Q32BVSSIG / AKE391P0N00----->4MB

AKE39GN0Q00 (realtek)

W25Q16BVSSIG / AKE38FP0N01----->2MB

AKE38GN0Q00 (realtek)

R423 0_6

R402 33_4

R381 33_4

R394 33_4

C433

*22p/50V_4

R393 3.3K_4

SPI_CS0#_UR_ME

5

RTC_RST#

12

J2

*SHORT_ PAD1

SRTC_RST#

12

J1

*SHORT_ PAD1

ACZ_BITCLK_RACZ_BITCLK_R

ACZ_SYNC_CODEC

ACZ_RST#_R

ACZ_SDOUT_R

+3V_PCH_ME

C442

0.1u/10V_4

+3V_PCH_ME

C441

0.1u/10V_4

PCH_SPI_CS0#

PCH_SPI_CS1#

4

3

PCH2(CLG)

C435 18p/50V_4

C434 18p/50V_4

Add MOSFET to separate CODEC SYNC signal

+5V

R311 0_4

ACZ_SYNC_CODEC

CRB 1.0

R304

1M_4

1

2

Q6

2N7002D

+3V_PCH_ME

12

+3V_RTC

3

PCH_AZ_CODEC_SDIN0(14)

Y4

32.768KHZ

R148 1M_4

TP18

TP28

XDP_TCLK(3)

XDP_TMS(3)

XDP_TDO(3)

R408 *47K_4

R396

10M_4

SPKR(14)

TP86

PCH Strap Table

Pin Name

KR

GNT3# / GPIO55 To

Strap description

No reboot mode setting PWROKSP

p-Block Swap Override

INTVRMEN Integrated 1.05V VRM enable ALWAYS Should be always pull-up

GNT1# / GPIO51

GPIO19

Boot BIOS Selection 1 [bit-1]

Boot BIOS Selection 0 [bit-0]

HDA_SDO Flash Descriptor Security RSMRST

DF_TVS

GPIO28

DMI/FDI Termination voltage

On-die PLL Voltage Regulator RSMRST#

HDA_SYNC On-Die PLL VR Voltage Select RSMRST

GPIO15

DSWVREN DSW

NV_ALE In

4

Intel ME Crypto Transport Layer

Security (TLS) cipher suite

internal PD

DEEP S4/S5 well

On Die DSW VR Enable

tel Anti-Theft HDD protection

Only for Interposer

Sampled

Configuration

0

1 = Setting to No-Reboot mode

PWROK

0 = "top-block swap" mode

1 = Default (weak pull-up 20K)

PWROK

PWROK

0 = effect (default)(weak pull-down 20K)

1 = overridden

PWROK

0 = Set to Vss (weak pull-down 20K)

1 = Set to Vcc

0 = Disable

1 = Enable (weak pull-up 20K)

0 = Support by 1.8V (weak pull-down)

1 = Support by 1.5V

RSMRST

0

1 = Enable

High = Enable (Default)

Low = Disable

PWROK 0 = Disable (Internal pull-down 20kohm)

3

CPT/PPT (HDA,JTAG,SATA)

RTC_X1

RTC_X2

RTC_RST#

SRTC_RST#

SM_INTRUDER#

PCH_INVRMEN

ACZ_BITCLK_R

ACZ_SYNC_R

SPKR

ACZ_RST#_R

TP22

ACZ_SDOUT_R

PCH_GPIO33

PCH_GPIO13

XDP_TCLK

XDP_TMS

XDP_TDO

PCH_JTAG_TDO

PCH_SPI_CLK

PCH_SPI_CS0#

PCH_SPI_CS1#

PCH_SPI_SI

PCH_SPI_SO

= Default (weak pull-down 20K)

GNT0#GNT1#

11

00

= Disable (Default)

U21A

A20

RTCX1

C20

RTCX2

D20

RTCRST#

G22

SRTCRST#

K22

INTRUDER#

C17

INTVRMEN

N34

HDA_BCLK

L34

HDA_SYNC

T10

SPKR

K34

HDA_RST#

E34

HDA_SDIN0

G34

HDA_SDIN1

C34

HDA_SDIN2

A34

HDA_SDIN3

A36

HDA_SDO

C36

HDA_DOCK_EN# / GPIO33

N32

HDA_DOCK_RST# / GPIO13

J3

JTAG_TCK

H7

JTAG_TMS

K5

JTAG_TDI

H1

JTAG_TDO

T3

SPI_CLK

Y14

SPI_CS0#

T1

SPI_CS1#

V4

SPI_MOSI

U3

SPI_MISO

Panther Point_R1P0

Boot Location

SPI

*

LPC

2

C38

FWH0 / LAD0

A38

FWH1 / LAD1

B37

FWH2 / LAD2

C37

FWH3 / LAD3

LPC

FWH4 / LFRAME#

+3V

LDRQ1# / GPIO23

RTCIHDA

SATA 6G

+3V

SATA

+3V_S5

JTAG

SATA3RCOMPO

SPI

+3V

SATA0GP / GPIO21

+3V

SATA1GP / GPIO19

+3V

+3V_RTC

ME_WR#(22)

R470 2.2K_4

R472 1K_4

R198 *1K_4

+3V_S5

+3V_S5

R327 330K_4

+3V_RTC

+1.35V_SUS

C-test change to +1.35V_SUS

LDRQ0#

SERIRQ

SATA0RXN

SATA0RXP

SATA0TXN

SATA0TXP

SATA1RXN

SATA1RXP

SATA1TXN

SATA1TXP

SATA2RXN

SATA2RXP

SATA2TXN

SATA2TXP

SATA3RXN

SATA3RXP

SATA3TXN

SATA3TXP

SATA4RXN

SATA4RXP

SATA4TXN

SATA4TXP

SATA5RXN

SATA5RXP

SATA5TXN

SATA5TXP

SATAICOMPO

SATAICOMPI

SATA3COMPI

SATA3RBIAS

SATALED#

R187 *1K_4

R161 *1K_4

R126 330K_4

R383 *1K_4

R456 *1K_4

R321 1K_4

R412 1K_4

R469 *1K_4

2

D36

E36

K36

V5

AM3

AM1

AP7

AP5

AM10

AM8

AP11

AP10

AD7

AD5

AH5

AH4

AB8

AB10

AF3

AF1

Y7

Y5

AD3

AD1

Y3

Y1

AB3

AB1

Y11

Y10

AB12

AB13

AH1

P3

V14

P1

R389 0_4

C-test change to +1.35V_SUS

+1.35V_SUS

LPC_LAD0 (18,20,22)

LPC_LAD1 (18,20,22)

LPC_LAD2 (18,20,22)

LPC_LAD3 (18,20,22)

PCH_DRQ#0

PCH_DRQ#1

R209 8.2K_4

TP26

TP23

LPC_LFRAME# (18,20,22)

SERIRQ (18,22)

SATA_RXN0 (20)

SATA_RXP0 (20)

SATA_TXN0 (20)

SATA_TXP0 (20)

UM77 SATA port 1,3 disable.

DG recommended that AC coupling capacitors should be

close to the connector (<100 mils) for optimal signal quality.

TP50

TP87

SATA_COMP

R200 37.4/F_4

SATA3_COMP

R204 49.9/F_4

SATA3_RBIAS

R465 750/F_4

PU 10k to +3V, becaue no sata LED.

SATA_ACT#

R455 10K_4

PCH_ODD_EN

BBS_BIT0

20111127 add R444 PU 10K to +3V for PCH_ODD_EN not use.

SPKR

PCH_INVRMEN

R376 *330K_4

R225 10K_4

PCI_GNT3# (9)

BBS_BIT1 (9)

BBS_BIT0

ACZ_SDOUT_R

DF_TVS (10)

H_SNB_IVB# (3)

PLL_ODVR_EN (10)

ACZ_SYNC_R

PCH_GPIO15 (10)

DSWVREN (7)

NV_ALE (9)

+1.05V_VTT

+3V

+3V

Used as GPIO only. at chklist 1.2

efault weak pull-up on GNT0/1#

D

[Need external pull-down for LPC BIOS]

ME_WR default EC setting folating

for future CPU, Sandy Bridge NC

DF_TVS needs to be pulled up to VccDFTERM power rail

through 2.2 kOhm ±5% - R8361 change to 0 or not??

Needs to be pulled High for Huron River platform.

chklist 1.2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Wednesday, September 12, 2012

Date: Sheet of

Wednesday, September 12, 2012

Date: Sheet of

Wednesday, September 12, 2012

1

+3V

mSATA

SATA0GP/GPIO21

S

ATA4GP/GPIO16

SATA5GP/GPIO49

If these pins are unused use 8.2k

to 10k pull-up to +Vcc3_3 or 8.2k

to 10k pull-down to ground

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Panther Point 2/6

Panther Point 2/6

Panther Point 2/6

EE3

EE3

EE3

8 32

8 32

1

8 32

08

3A

3A

3A

5

4

3

2

1

CPT/PPT (PCI-E,SMBUS,CLK)

PCIE_TX1-(20)

PCIE_TX1+(20)

CLK_PCIE_XDPN(3)

CLK_PCIE_XDPP(3)

+3V

dGPU_SELECT#

UMA boot

GPU boot

UMA boot

UMA boot

PCIE port 1 for commeral model S3 can't weak up.

C316 0.1 u/10V_4

C315 0.1 u/10V_4

PCIE_TXN1_C

PCIE_TXP1_C

UM77 4~7 PCIE port disable

CLK_PCIE_WLAN#(20)

CLK_PCIE_WLAN(20)

PCIE_CLKREQ0#(20)

PCIE_CLKREQ0#

TP45

PCIE_CLKREQ1#

PCIE_CLKREQ2#

PCIE_CLKREQ3#

PCIE_CLKREQ4#

PCIE_CLKREQ5#

CLK_PCIE_LAN_REQ#

TP40

CLK_PCIE_REQ6#

TP42

CLK_PCIE_REQ7#

CLK_REQ/Strap Pin(CLG)

+3V_S5

R104 10K_4R83 8.2K_4

R172 10K_4

R425 10K_4

R367 10K_4

R404 10K_4

R218 10K_4

R103 10K_4

+3V

R438 10K_4

R206 10K_4

+3V_S5

R165 10K_4

CLK_BUF_BCLKN

CLK_BUF_BCLKP

CLK_BUF_PCIE_3GPLLN

CLK_BUF_PCIE_3GPLLP

CLK_BUF_DREFCLKN

CLK_BUF_DREFCLKP

CLK_BUF_DREFSSCLKN

CLK_BUF_DREFSSCLKP

CLK_PCH_14M

CLOCK TERMINATION for FCIM

PCIE_CLKREQ4#

PCIE_CLKREQ5#

PCIE_CLKREQ0#

PCIE_CLKREQ3#

CLK_PCIE_LAN_REQ#

CLK_PCIE_REQ6#

CLK_PCIE_REQ7#

PCIE_CLKREQ1#

PCIE_CLKREQ2#

PCIE_CLKREQ_PEG#_R

R249 10K_4

R248 10K_4

R245 10K_4

R243 10K_4

R169 10K_4

R162 10K_4

R216 10K_4

R221 10K_4

R175 10K_4

CPT/PPT (PCI,USB,NVRAM)

R149 8.2K_4

R82 8.2K_4

R352 8.2K_4

1

DGPU_HOLD_RST#

2

DGPU_EDIDSEL#

3

56

Setup

VGA H/W

Menu

Signal

UMA

Hidden

GPU

Hidden

UMA+GPU

dGPU/SG

UMA

UMA/SG

or Optimize)

3

PCIE_RX1-(20)

PCIE_RX1+(20)

U21E

BG26

TP1

BJ26

TP2

BH25

TP3

BJ16

TP4

BG16

TP5

AH38

TP6

TP58

TP61

TP63

TP60

TP53

TP55

TP57

TP54

PCI_PME#

PCLK_TPM_R

CLK_LPC_DEBUG_C

CLK_PCI_775_C

R189

100K_4

+3V_S5

AH37

AH12

BG46

BC30

BC28

BG32

AU28

AU26

AW30

AK43

AK45

C18

N30

H3

AM4

AM5

Y13

K24

L24

AB46

AB45

B21

M20

AY16

BE28

BE32

BJ32

BE30

BF32

AV26

BB26

AY30

AY26

AV28

K40

K38

H38

G38

C46

C44

E40

D47

E42

F46

G42

G40

C42

D44

K10

C6

H49

H43

J48

K42

H40

000

TP7

TP8

TP9

TP10

TP11

TP12

TP13

TP14

TP15

TP16

TP17

TP18

TP19

TP20

TP21

TP22

TP23

TP24

USB3.0

USB30_RX1N

TP25

USB30_RX2N

TP26

USB30_RX3N

TP27

USB30_RX4N

TP28

USB30_RX1P

TP29

USB30_RX2P

TP30

USB30_RX3P

TP31

USB30_RX4P

TP32

USB30_TX1N

TP33

USB30_TX2N

TP34

USB30_TX3N

TP35

USB30_TX4N

TP36

USB30_TX1P

TP37

USB30_TX2P

TP38

USB30_TX3P

TP39

USB30_TX4P

TP40

PIRQA#

PIRQB#

PIRQC#

PIRQD#

REQ1# / GPIO50

REQ2# / GPIO52

REQ3# / GPIO54

GNT1# / GPIO51

GNT2# / GPIO53

GNT3# / GPIO55

PIRQE# / GPIO2

PIRQF# / GPIO3

PIRQG# / GPIO4

PIRQH# / GPIO5

PME#

PLTRST#

CLKOUT_PCI0

CLKOUT_PCI1

CLKOUT_PCI2

CLKOUT_PCI3

CLKOUT_PCI4

Panther Point_R1P0

PLTRST# (18,20,22)

RSVD

PCI

+3V

+3V

+3V

USB

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

D D

TX AC cap plac e at connector side, AC cap to

connector < 40 0mils

R489 15_4

L16

1

USB30_RX2-(19)

USB30_RX2+(19)

USB30_TX2-(19)

USB30_TX2+(19)

C C

PCLK_TPM(18)

CLK_PCI_FB CLK_PCI_FB_C

CLK_LPC_DEBUG(20)

CLK_PCI_EC(22)

B B

PLTRST#(CLG)

PCI_PLTRST#

2

1

R188 *0_4

2

4 3

*MCM2012B900GBE/400mA/90ohm

R490 15_4

R487 15_4

L15

1

2

4 3

*MCM2012B900GBE/400mA/90ohm

R488 15_4

BBS_BIT1(8)

BOARD_ID2(10)