Acer Aspire ES1-572 Schematics

A

1 1

2 2

B

C

D

E

Compal Confidential

B5W1S MB Schematic Document

LA-D671P

3 3

Rev: 1.0

2016.01.18

4 4

Security Classification

Security Classification

Security Classification

Issued D ate

Issued D ate

Issued D ate

THIS SHEET OF ENGINEE RING DRAW ING I S THE PROP RIETARY PROPERTY OF COMPAL ELECTRON ICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEE RING DRAW ING I S THE PROP RIETARY PROPERTY OF COMPAL ELECTRON ICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEE RING DRAW ING I S THE PROP RIETARY PROPERTY OF COMPAL ELECTRON ICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPA L ELECTRONICS, IN C. NEITHER THIS S HEET NOR THE INF ORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPA L ELECTRONICS, IN C. NEITHER THIS S HEET NOR THE INF ORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPA L ELECTRONICS, IN C. NEITHER THIS S HEET NOR THE INF ORMATION IT CONTAINS

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT O F COMPAL ELECTRONIC S, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT O F COMPAL ELECTRONIC S, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT O F COMPAL ELECTRONIC S, INC.

A

B

2016/07/18 2016/11/10

2016/07/18 2016/11/10

2016/07/18 2016/11/10

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal+Electronics,+Inc.

Compal+Electronics,+Inc.

Compal+Electronics,+Inc.

Title

Title

Title

Cover+Sheet

Cover+Sheet

Cover+Sheet

Size Docum ent N umber Rev

Size Docum ent N umber Rev

Size Docum ent N umber Rev

Custom

Custom

Custom

B5W1S

B5W1

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

144Monday, July 18, 2016

144Monday, July 18, 2016

144Monday, July 18, 2016

E

1.0

1.0

1.0

A

B

C

D

E

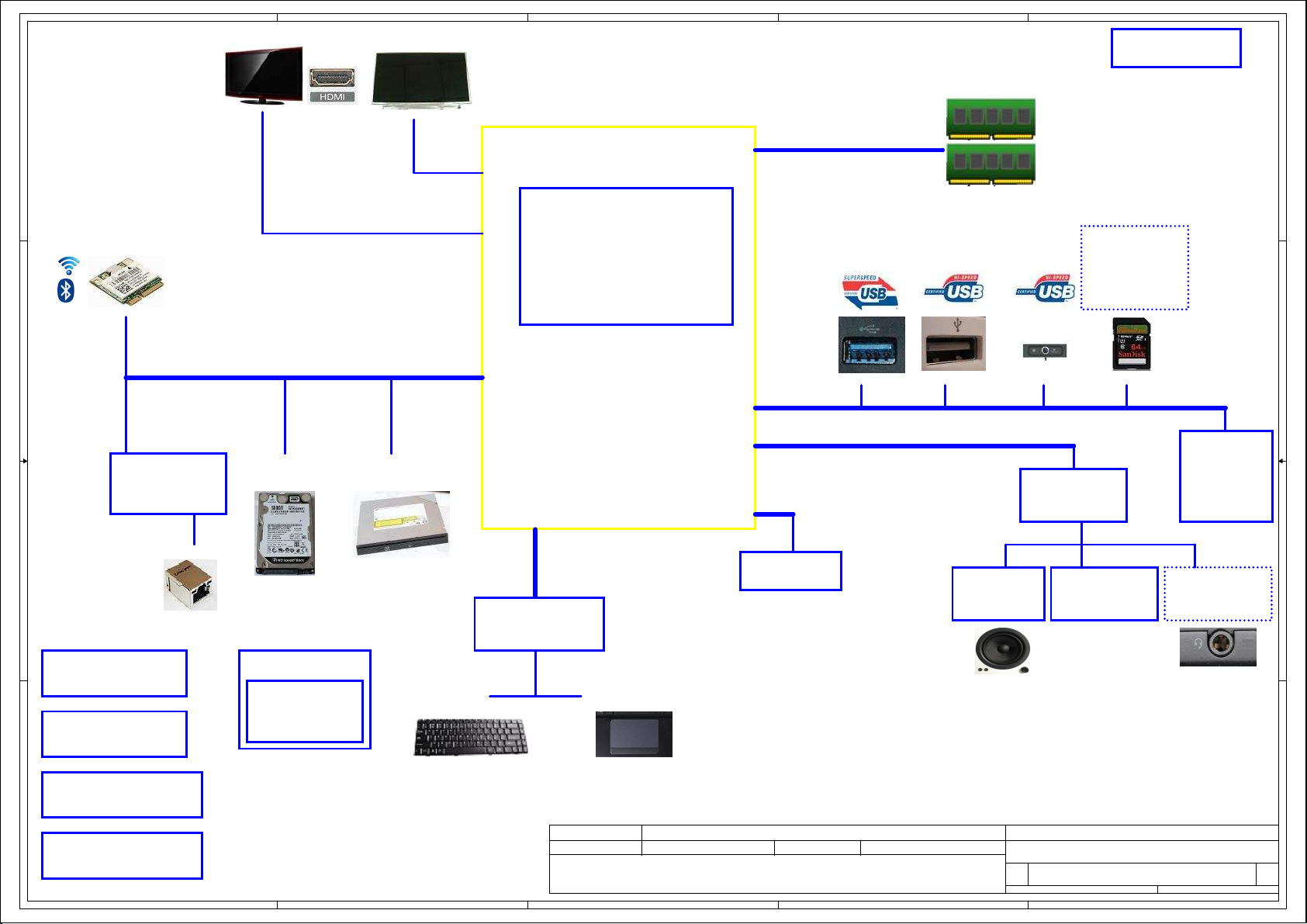

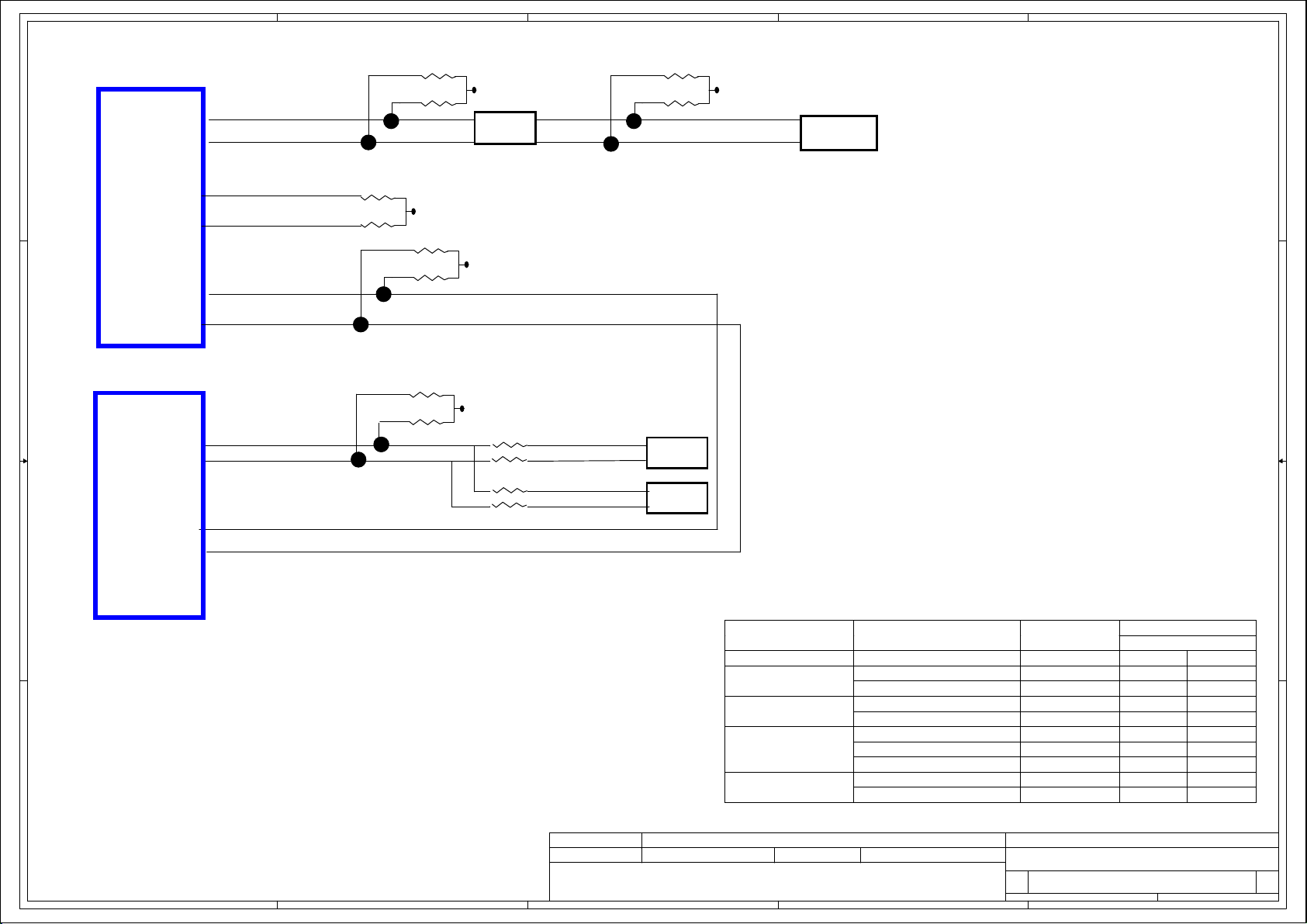

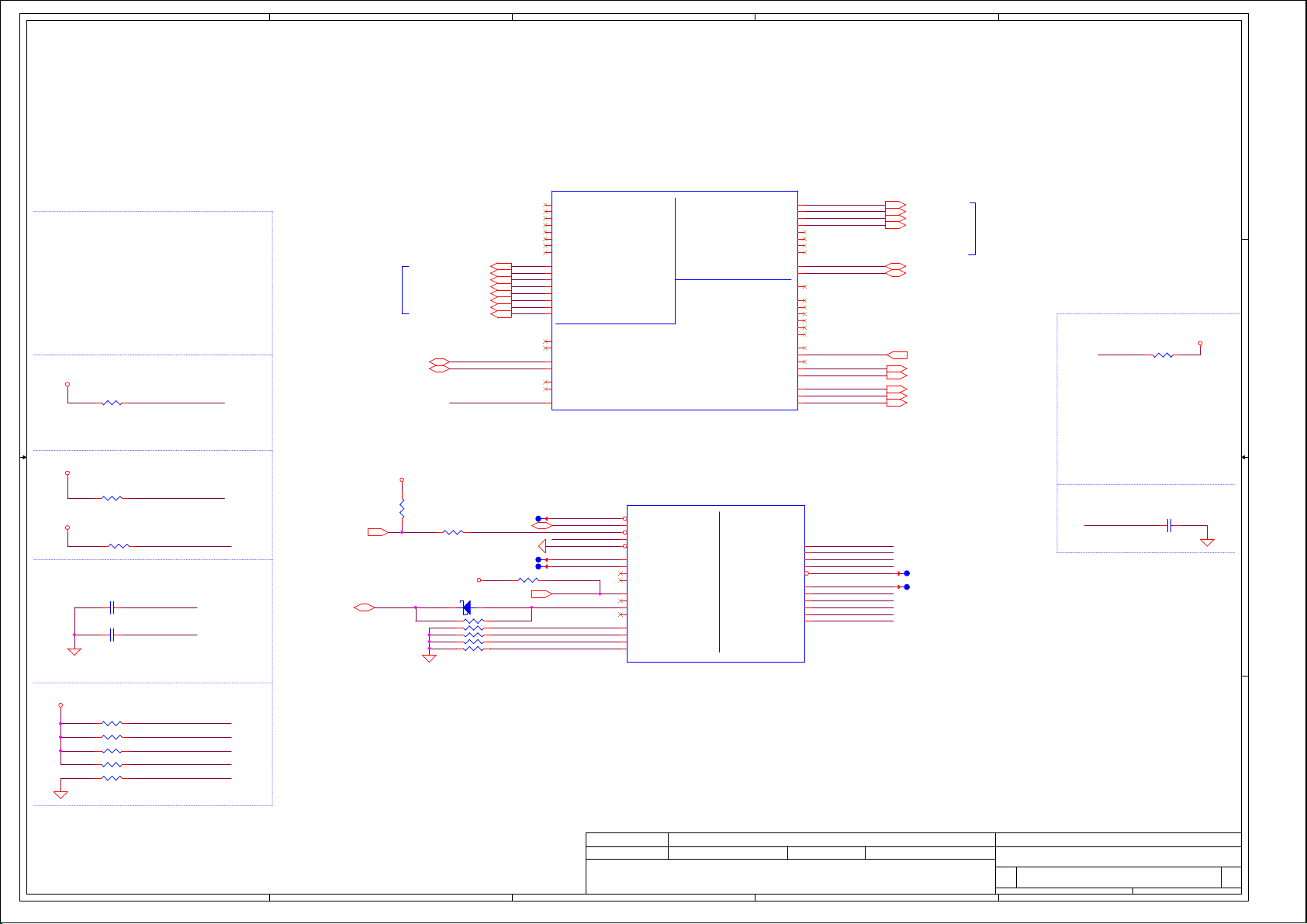

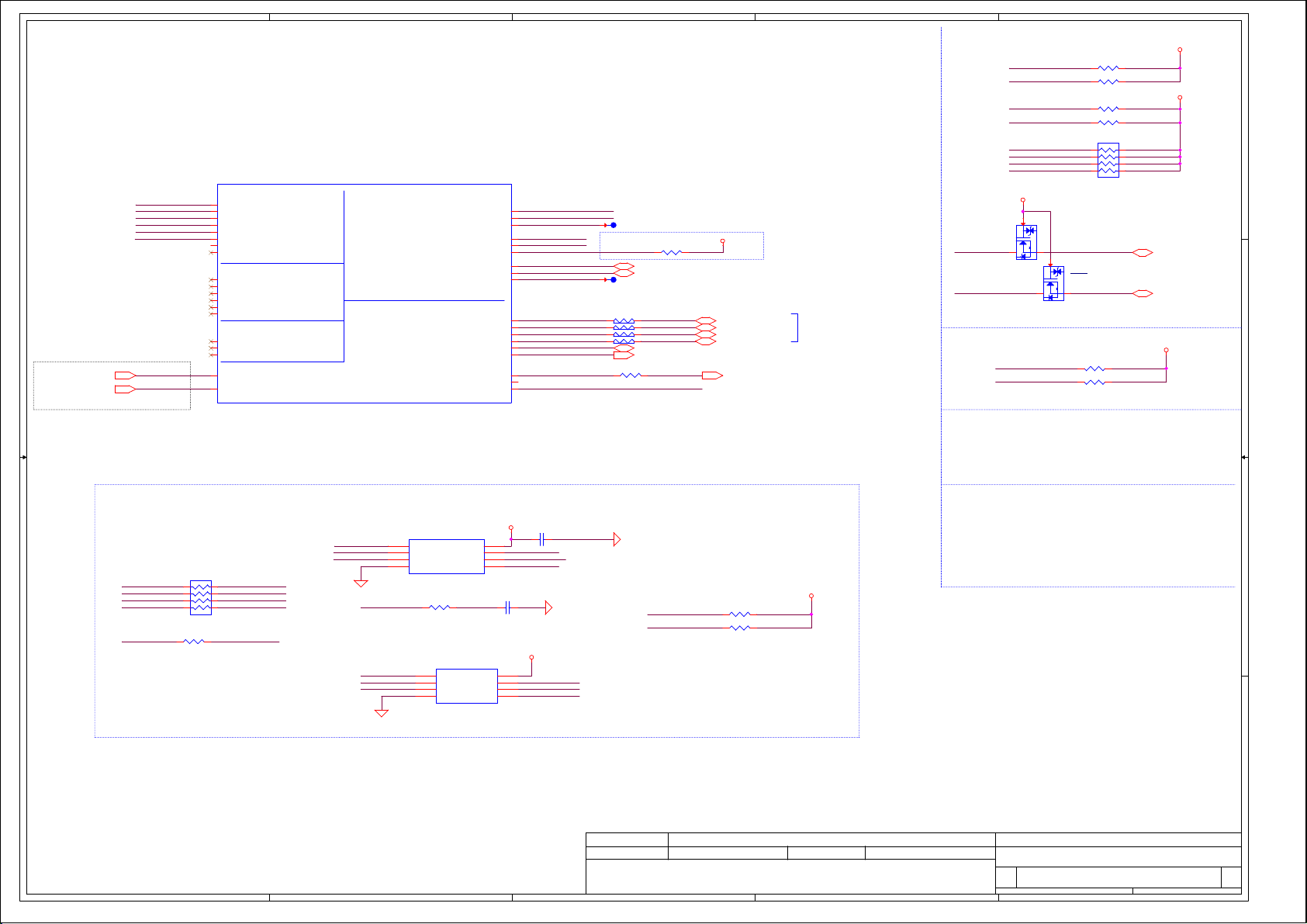

HDMI Conn.

eDP

Fan Control

page 31

Interleaved Memory

page 22

1 1

DDI2

HDMI x 4 lanes

page 21

eDP

DDI

Intel Kabylake U

Kabylake U

Kabylake PCH-LP(MCP)

(KBL-U_2+2)

page 24

NGFF

WLAN

2 2

USB port 5

PCIe 1.0

2.5GT /s

port 6

PCIe 1.0

2.5GT /s

port 5

LAN(GbE)

Realtek 8111H

page 23

LAN(GbE)

SATA3.0 SATA3.0

port 7

(SATA0) (SATA1)

SATA HDD

Conn.

Flexible IO

6.0 Gb/s6.0 Gb/s

port 8

SATA CDROM

Conn.

Processor

Dual Core + GT2

15W

1356pin BGA

page 07 ~18

Memory BUS

Dual Channel

1.2V DDR4 1866/2133

USBx8

48MH z

HD Audio

SPI

USB 3.0

conn x1

USB port 1 USB port 7

page 28 page 21

conn x2

USB port2,3

Port3 on Sub/B

page 28

3.3V 24MHz

USB 2.0

page 19

260pin DDR4-SO-DIMM X2

page 20

CMOS

Camera

Card Reader

RTS5170

SD only

USB port 8

on Sub/B

page 28

HDA Codec

ALC233

page 25

Touc h

Screen

I2C (PORT1)

USB port 6

page 21

RJ45 conn.

3 3

page 23

RTC CKT.

page 15

page 26

Sub Board

LS-D671

page 26

ENE

KB9022

Int.KBD

LPC/eSPI BUS

CLK= 24 MH z

page 29

Touch Pad

PS2 (from EC) / I2C (from SOC)

SPI ROM

64Mb

page 9

Int. Speaker

page 25

Int. AMIC

page 25 page 28

UAJ

on Sub/B

IO/B

Power On/Of f CKT.

page 30

4 4

DC/DC Interface CKT.

page 32

Power Circuit DC/DC

page 33 ~43

A

page 28

page 30

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEE RING DRAW ING I S THE PROP RIETARY PROPERTY OF COMPAL ELECTRON ICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEE RING DRAW ING I S THE PROP RIETARY PROPERTY OF COMPAL ELECTRON ICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEE RING DRAW ING I S THE PROP RIETARY PROPERTY OF COMPAL ELECTRON ICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPA L ELECTRONICS, IN C. NEITHER THIS S HEET NOR THE INF ORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPA L ELECTRONICS, IN C. NEITHER THIS S HEET NOR THE INF ORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPA L ELECTRONICS, IN C. NEITHER THIS S HEET NOR THE INF ORMATION IT CONTAINS

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT O F COMPAL ELECTRONIC S, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT O F COMPAL ELECTRONIC S, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT O F COMPAL ELECTRONIC S, INC.

B

Issued D ate

Issued D ate

Issued D ate

page 30

Compal Secret Data

Compal Secret Data

2016/07/18 2016/11/10

2016/07/18 2016/11/10

2016/07/18 2016/11/10

C

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Docum ent N umber Rev

Size Docum ent N umber Rev

Size Docum ent N umber Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

B5W1S

1.0

1.0

244Monday, July 18, 2016

244Monday, July 18, 2016

244Monday, July 18, 2016

E

1.0

A

B

C

D

E

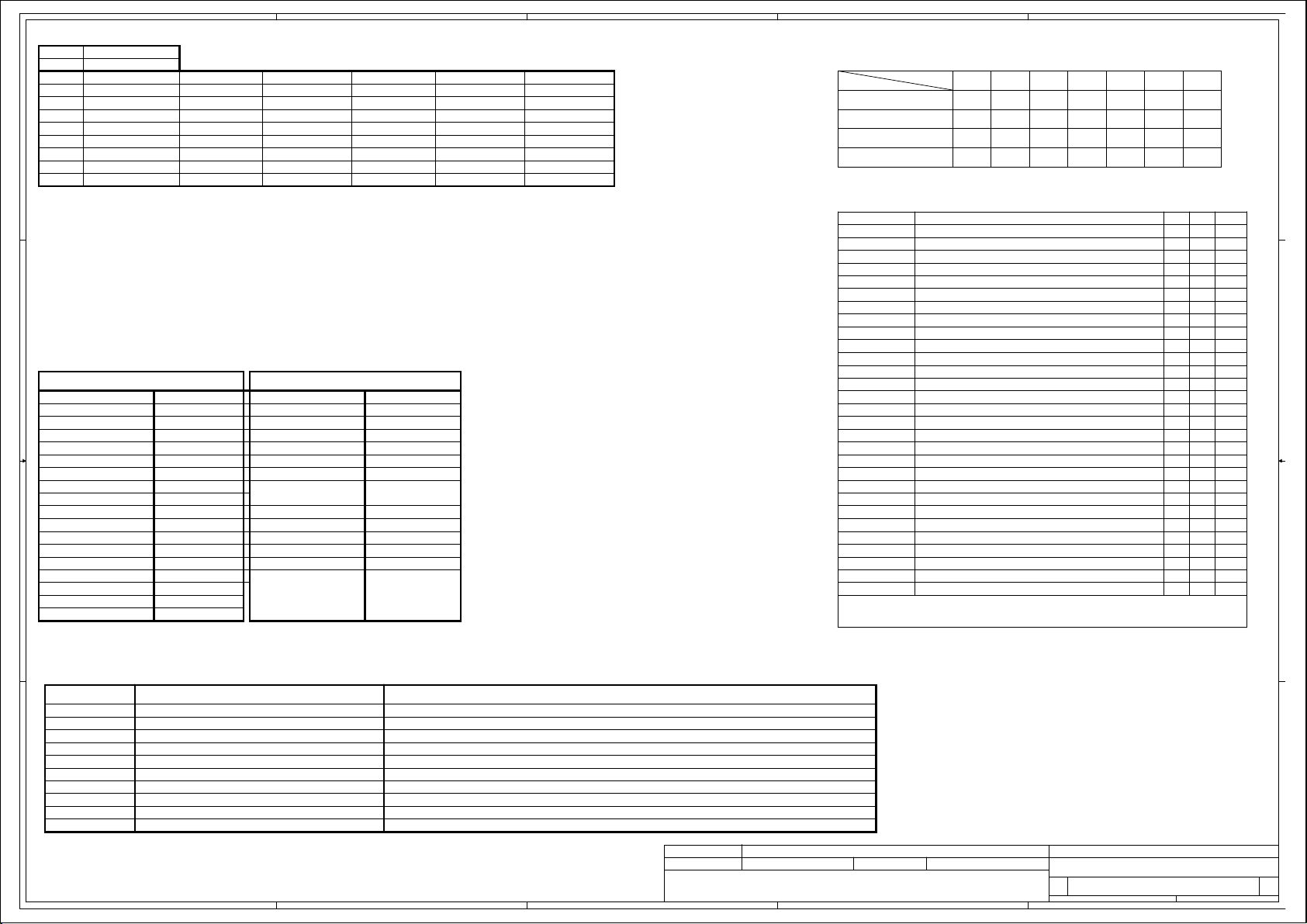

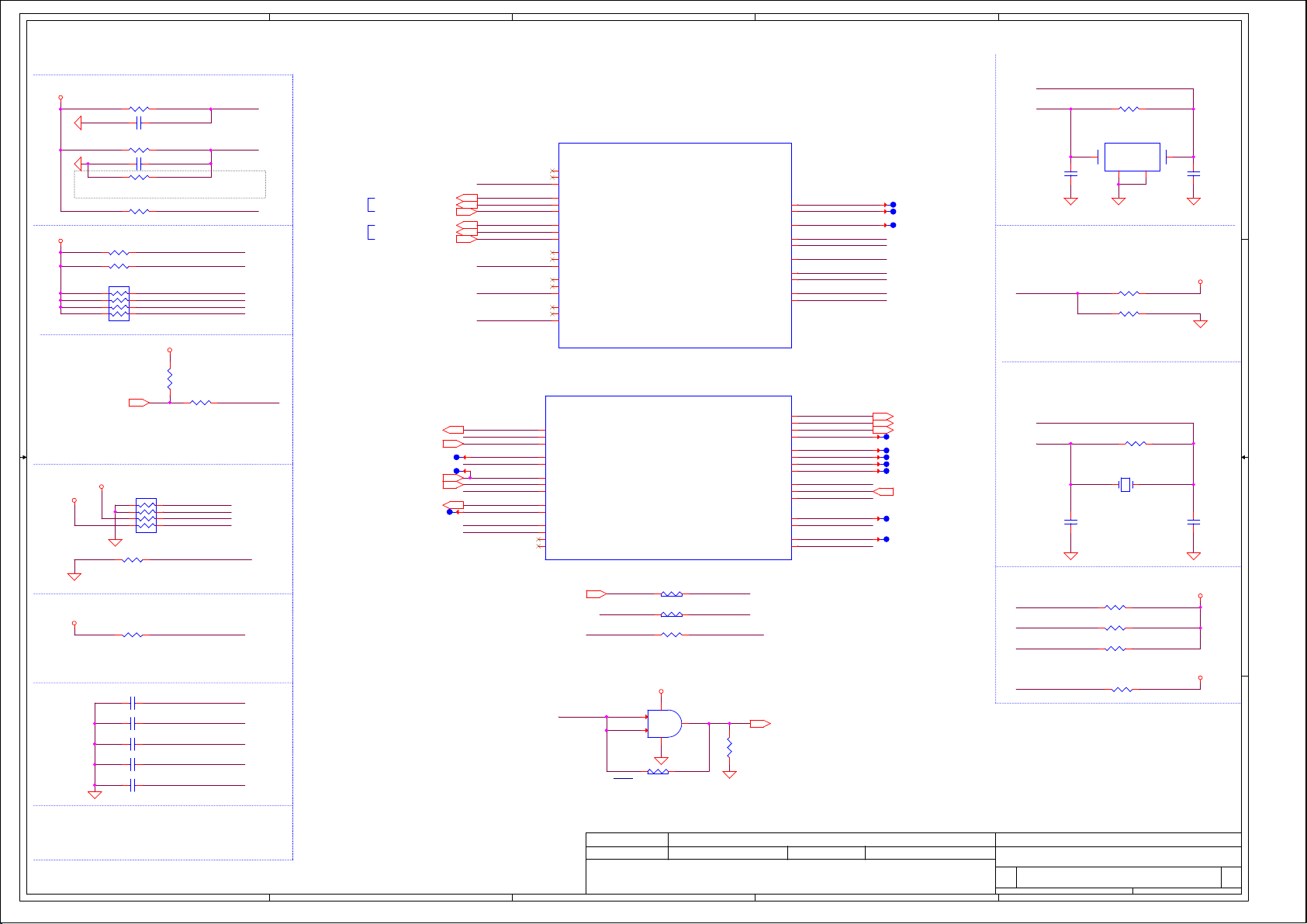

Board ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

1 1

100K +/- 1%Ra

0

1

2

3

4

5

6

7

00 V

12K +/- 1% 0.347 V 0.345 V 0.360 V

15K +/- 1%

20K +/- 1%

27K +/- 1%

33K +/- 1%

43K +/- 1%

56K +/- 1%

Rb V min

BID

0.423 V 0.430 V 0.438 V

Vtyp

BID

0 V 0.300 V

V

BID

max

EC AD3

0x00 - 0x13

0x14 - 0x1E

0x1F - 0x25

PCB Revision

0.1

0.1

0x26 - 0x300.541 V 0.550 V 0.559 V

0x31 - 0x3A0.691 V 0.702 V 0.713 V

0x3B - 0x450.807 V 0.819 V 0.831 V

0x46 - 0x540.978 V 0.992 V 1.006 V

0x55 - 0x641.169 V 1.185 V 1.200 V

Power State

STATE

S0 (Full ON) ON ON ON ONHIGH HIGH HIGH

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SIGNAL

SLP_S3# SLP_S4# SLP_S5 # +VALW +V +V S Clock

LOW HIGH

LOWLOW

HIGH

HIGH

ONONON

ON

OFF

OFFLOW LOW LOW

OFF

OFF

OFF

OFF

OFF

OFF

Voltage Rails

Power Plane

+19V_VI N

+17.4V_BATT

+19VB

+VCC_CORE

+VCC_G T

+VCC _SA

+0.6VS_VTT

+1.0VALW_P RIM +1.0V Always pow er rail

+1.0 V_VCC ST U Sustain voltage f or processor in Standby modes

2 2

BOM Structure Table

BOM Option Table

Item BOM Structure

Unpop

Connector

For Acer BYOC BYOC@

No Acer BYOC NBYOC@

@

CONN@

BOM Option Table

Item BOM Structure

SkyLake plat f or m

KabyLake plat f or m KBL@

SKL@

255@CODEC(ALC255)

CODEC(ALC233) 233@

+VCC IO

+1.0VS_VCCST G +1.0VALW_PRIM Gated version of VCCST

+1.2V_V DD Q

+1.8VALW_P RIM +1.8V Always pow er rail

+1.8VS System +1.8V power rail

+3VLP +19VB to +3VLP power rail for suspend power

+3VALW System +3VALW always on power rail

+3VS

+5VALW

+5VS System +5V power rail

+RTCVCC

LPC MODE for EC LPC@

ESPI MODE for EC ESPI@

For Intel CMC

EMI requirement

EMI requirement depop

ESD requirement

3 3

ESD requirement depop

LAN(8111GUS)

LAN(8111H) 8111H@

RF requirement

CMC@

EMI@

@EMI@

ESD@

@ESD@

8111GUS@

RF@

CPU Code

QKJW@

Note : ON*1 means pow er p lane is ON only when WOL enable and RT C wake at BIOS setting, other wise it is OF F.

Description

Adap ter pow er suppl y

Batt ery power supply

AC or batte ry power rail for power circuit.

Processor IA Cores Power Rail

Processor Graphics Power Rails

System Agent power rail

DDR +0.6VS pow er rail for DDR termina tor .

CPU IO power ra il

DDR4 +1.2V Power Rail

System +3V power rail

+5V Always power rail

RTC Battery Power

S0

N/A

N/A

N/A

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

S3

S4/S5

N/AN/A

N/A N/A

N/AN/A

OFF OFF

OFF

OFF

OFF OFF

OFFOFF

ON

ON*1

OFF

ON

OFF OFF

OFFOFF

OFF

ON

ON

ON*1

OFF

OFF

ON

ON

ON

ON*1

OFF

OFF

ON

ON

OFFOFF

ON ON

43 level BOM table

431A3EBOL01

4 4

A

BOM Structure43 Level Description

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET O F ENGINEERING DRAWING IS THE PROPRIETARY PR OPERTY O F COMPAL ELECTRO NICS, INC. AND CON TAINS CONFIDENTIAL

THIS SHEET O F ENGINEERING DRAWING IS THE PROPRIETARY PR OPERTY O F COMPAL ELECTRO NICS, INC. AND CON TAINS CONFIDENTIAL

THIS SHEET O F ENGINEERING DRAWING IS THE PROPRIETARY PR OPERTY O F COMPAL ELECTRO NICS, INC. AND CON TAINS CONFIDENTIAL

AND TRADE SECRET INF ORMATION. THIS SHEET MAY NOT B E TRANSFER ED FRO M THE CUS TODY OF THE COMP ETENT DIVIS ION OF R&D

AND TRADE SECRET INF ORMATION. THIS SHEET MAY NOT B E TRANSFER ED FRO M THE CUS TODY OF THE COMP ETENT DIVIS ION OF R&D

AND TRADE SECRET INF ORMATION. THIS SHEET MAY NOT B E TRANSFER ED FRO M THE CUS TODY OF THE COMP ETENT DIVIS ION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY CO MPAL ELEC TRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY CO MPAL ELEC TRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY CO MPAL ELEC TRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USE D BY OR DISC LOSED TO AN Y THIRD PARTY W ITHOUT PRIOR WRITTEN CON SENT OF C OMPAL ELECTRO NICS, INC .

MAY BE USE D BY OR DISC LOSED TO AN Y THIRD PARTY W ITHOUT PRIOR WRITTEN CON SENT OF C OMPAL ELECTRO NICS, INC .

B

MAY BE USE D BY OR DISC LOSED TO AN Y THIRD PARTY W ITHOUT PRIOR WRITTEN CON SENT OF C OMPAL ELECTRO NICS, INC .

C

2016/07/18 2016/11/10

2016/07/18 2016/11/10

2016/07/18 2016/11/10

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal+Electronics,+Inc.

Compal+Electronics,+Inc.

Compal+Electronics,+Inc.

Tit le

Tit le

Tit le

Notes List

Notes List

Notes List

Size Document Num ber Rev

Size Document Num ber Rev

Size Document Num ber Rev

Custom

Custom

Custom

B5W1S

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

E

344Monday, July 18, 2016

344Monday, July 18, 2016

344Monday, July 18, 2016

1.0

1.0

1.0

A

B

C

D

E

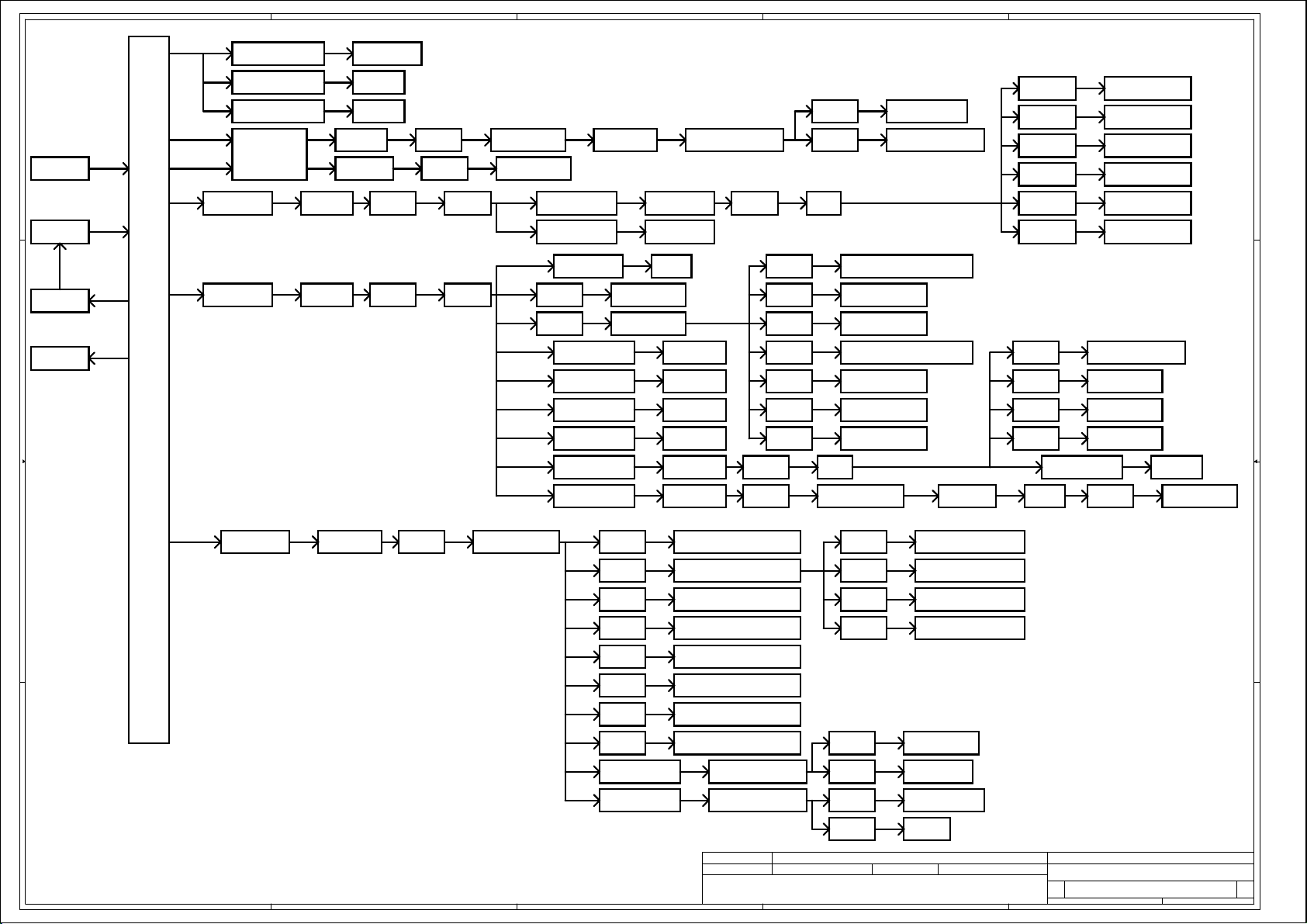

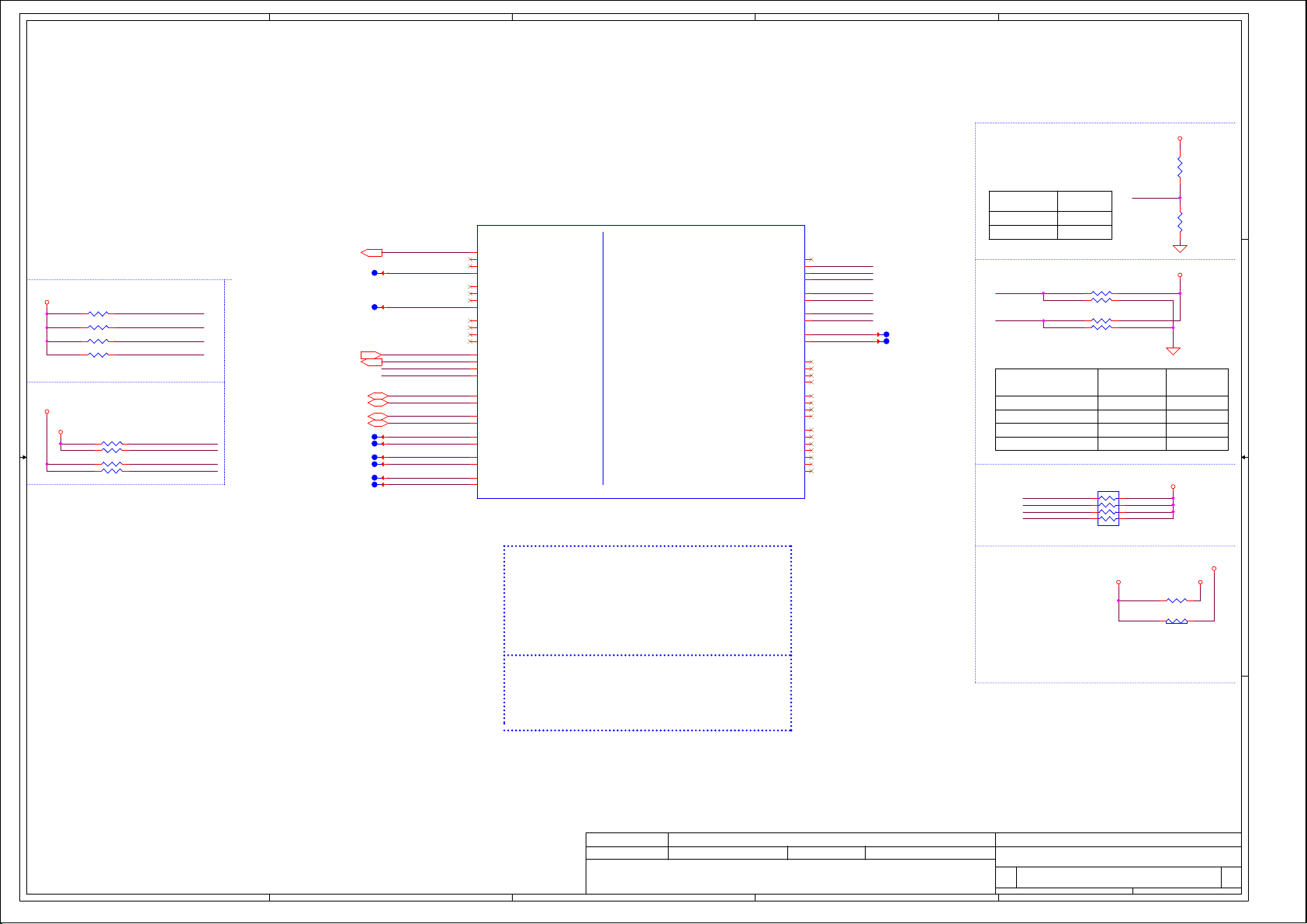

DRVON

1 1

ADAPTER

BATTERY

SYSON

SM_PG_CTR L

5V_EN

+19V B

3V_EN

CHARGER

2 2

+3VLP

LDO

NCP81253MNTBG

(PU 900 1)

NCP81151MNTBG

(PU 900 3)

NCP81253MNTBG

(PU 900 4)

RT8207KGQW

(PU501)

SY8286 CRAC

(PU402)

SY8286BRAC

(PU401)

+5VALWP

+VCC_CO RE

+VCC_GT

+VCC_SA

+1.2VP

+0.6VSP

JUMP

(PJ402)

JUMP

(PJ401)

JUMP

(PJ501)

JUMP

(PJ502)

+5VALW

+3VALW+3VALWP

+1.2V_VDDQ

+0.6VS_VTT

SUSP #

USB_EN

SYSON

SYSON

LAN_PWR_E N

TP_PWR_E N

WLAN_ON

SUSP #

SPOK

JUMP

(JPC1,JPC2 )

EM5209VF

(UQ1)

SY6288C2 0AAC

(US21)

APL5336KAI

(PU502)

R-Shor t

(RC173)

JUMP

(JPC7)

APL5336KAI

(PU502)

SY6288C2 0AAC

(UL1)

SY6288C2 0AAC

(UK1 )

SY6288C2 0AAC

(UM1)

EM5209VF

(UQ1)

G971ADJF11U

(PU702)

+5VS_OUT

+USB3_VCCA

+2.5VP

+3VALW_ DSW

+3VALW_PRIM

+2.5VP

+3V_LAN

+3V_PTP

+3VS_WLAN

+3VS_OUT

+1.8VALWP

+1.2V_VDDQ_CPU

JUMP

(JPQ2)

JUMP

(JPQ1)

JUMP

(PJ702)

R-Shor t

(RC197)

R-Shor t

(RC161)

R-Shor t

(RC163)

R-Shor t

(RC172)

R-Shor t

(RC167)

R-Shor t

(RC187)

R-Shor t

(RC171)

R-Shor t

(RC208)

R-Shor t

(RC141)

+5VS

+3VALW_1.8VALW_ PGPPA

+3VALW_P GPPB

+3VALW_PGPP C

+3VALW_ 1.8VALW_PG PPD

+3VALW_PGPPE

+3VALW_PGPP G

+3VALW_RTC

+3VS

+1.8VALW_PRIM

+1.2V_VDDQC

+1.2V_VCCSFR_OC

SUSP #

EM5209VF

(UC5)

R-Shor t

(RC178)

0 ohm

(RM1)

R-Shor t

(RA2)

R-Shor t

(RA5)

SOC_ENVDD

R-Shor t

(RX8)

AP2330W

(UY1)

R-Shor t

(RO3)

0 ohm

(RO2)

JUMP

(JPA1)

R-Shor t

(RF1)

SY6288C2 0AAC

(UX1)

+1.8VS

+TS_PWR

+HDMI_5V_OUT

+5VS_HDD

+5VS_ODD

+VDDA

+VCC_ FAN1

+1.8VS_3VS _PGPPA

+3VS_WLAN

+3VS_DVDDIO

+3VS_DVDD

+LCDVDD

R-Shor t

(RA6)

+1.8VS_VDDA

EN_1VALW

3 3

4 4

A

SY828 8RAC

(PU601)

JUMP

(PJ601)

B

SYSON

SUSP #

R-Shor t

(RC148)

JUMP

(JPC9)

R-Shor t

(RC162)

R-Shor t

(RC169)

R-Shor t

(RC164)

R-Shor t

(RC190)

R-Shor t

(RC152)

R-Shor t

(RC175)

EM5209VF

(UC5)

AOZ1 336

(UC8)

C

+1.0VALW_APLL

+1.0VALW_MPH YPLL

+1.0VALW_DT S

+1.0VALW_CLK6_ 24T BT

+1.0VALW_VCCC LK2

+1.0VALW_C LK4_F1 00O C

+1.0VALW_CLK 5_F 24N S

+1.0VALW_MPHYAON

+1.0V_VCCSTU

+1.0VS_VCCSTG_IO

Security Cla ssification

Security Cla ssification

Security Cla ssification

Issued Date

Issued Date

Issued Date

THIS SHE ET OF ENGINEE RING DRAWING IS THE PR OPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHE ET OF ENGINEE RING DRAWING IS THE PR OPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHE ET OF ENGINEE RING DRAWING IS THE PR OPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TR ADE S ECRET INFORM ATION. THIS SHEE T MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TR ADE S ECRET INFORM ATION. THIS SHEE T MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TR ADE S ECRET INFORM ATION. THIS SHEE T MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED B Y COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED B Y COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED B Y COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY O R DI SCLOSED TO ANY THIRD P ARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY O R DI SCLOSED TO ANY THIRD P ARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY O R DI SCLOSED TO ANY THIRD P ARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

+1.0VALW_PRIM+1.0VALWP

R-Shor t

(RC209)

R-Shor t

(RC149)

R-Shor t

(RC176)

R-Shor t

(RC156)

R-Shor t

(RC143)

R-Shor t

(RC140)

R-Shor t

(RC188)

JUMP

(JPC5)

Compal Secret Data

Compal Secret Data

2016/07/18 2014/04/12

2016/07/18 2014/04/12

2016/07/18 2014/04/12

Compal Secret Data

+1.0VALW_MP HYG T

+1.0VALW_AM PHY PLL

+1.0VALW_SRAM

+1.0VALW_AP LLEBB

+1.0V_VCCSFR

+1.0V_VCCST

+1.0VS_VCCSTG

+VCCIO

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Shee t of

Date: Shee t of

Date: Shee t of

B5W1S

Power Rail

Power Rail

Power Rail

E

444Monday, July 18, 2016

444Monday, July 18, 2016

444Monday, July 18, 2016

1.0

1.0

1.0

A

B

C

D

E

2.2K

BH10

2.2K

SOC_SMBCLK

SOC_SMBDATA

1 1

Skylake

BG12

+3VALW_PRIM

2N7002DW

2.2K

2.2K

+3VS

SO-DIMM 2

SOC

SOC_S ML0 CLK

SOC_SML 0DATA

SOC_S ML1 CLK

SOC_SML 1DATA

2 2

77

SCL1

SDA1

KBC

3 3

KB9022

SCL2

SDA2

78

79

80

EC_SMB_CK 1

EC_SMB_D A1

SOC_S ML1 CLK

SOC_SML 1DATA

499

499

+3VALW_PRIM

2.2K

2.2K

2.2K

2.2K

+3VALW_PRIM

+3VLP_EC

100 ohm

100 ohm

0 ohm

0 ohm

EC_SMB_CK1_CHGR

EC_SMB_DA1_CHGR

7

6

12

11

BATTERY

CONN

Charger

Need check

I2C Address Table

BUS

I2C_0 (+3VS)

I2C_1 (+3VS)

SOC_SMBCLK +3VS

SOC_SML1CLK

Device

Reserved (Touch Panel)

TM-P2969-001 (TP)

SB8787-1200 (TP-ELAN)

DIMM 2

PCH-LP (SOC)

Address(7 bit)

0x2C

0x15

0xA4

0x90

+3VALW _PRIM

4 4

EC_SMB_CK1 +3VLP

BQ24780 (Charger IC)

BATTERY PACK

0x12

0x16

Addres s(8b it)

Write

Read

Security Classification

Security Classification

Security Classification

Issued D ate

Issued D ate

Issued D ate

THIS SHEET OF ENGINEE RING DRAW ING I S THE PROP RIETARY PROPERTY OF COMPAL ELECTRON ICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEE RING DRAW ING I S THE PROP RIETARY PROPERTY OF COMPAL ELECTRON ICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEE RING DRAW ING I S THE PROP RIETARY PROPERTY OF COMPAL ELECTRON ICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPA L ELECTRONICS, IN C. NEITHER THIS S HEET NOR THE INF ORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPA L ELECTRONICS, IN C. NEITHER THIS S HEET NOR THE INF ORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPA L ELECTRONICS, IN C. NEITHER THIS S HEET NOR THE INF ORMATION IT CONTAINS

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT O F COMPAL ELECTRONIC S, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT O F COMPAL ELECTRONIC S, INC.

MAY BE USED BY OR DIS CLOSED TO ANY THIRD PARTY WITHOUT PRIO R WRITTEN CONSENT O F COMPAL ELECTRONIC S, INC.

A

B

2016/07/18 2016/11/10

2016/07/18 2016/11/10

2016/07/18 2016/11/10

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal+Electronics,+Inc.

Compal+Electronics,+Inc.

Compal+Electronics,+Inc.

Title

Title

Title

SMBUS_Routing_Table

SMBUS_Routing_Table

SMBUS_Routing_Table

Size Docum ent N umber Rev

Size Docum ent N umber Rev

Size Docum ent N umber Rev

Custom

Custom

Custom

B5W1S

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

544Monday, July 18, 2016

544Monday, July 18, 2016

544Monday, July 18, 2016

E

1.0

1.0

1.0

A

B

C

D

E

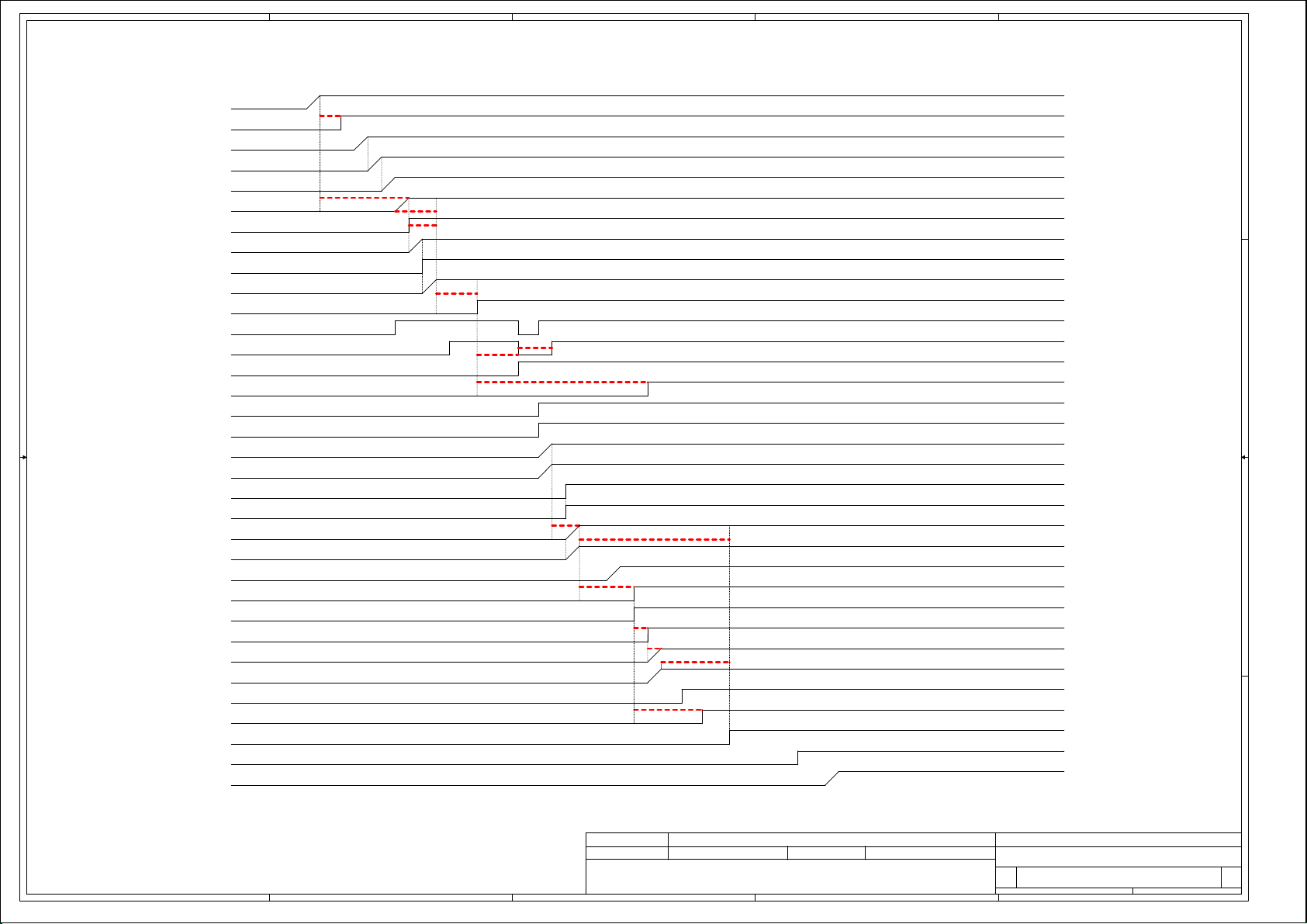

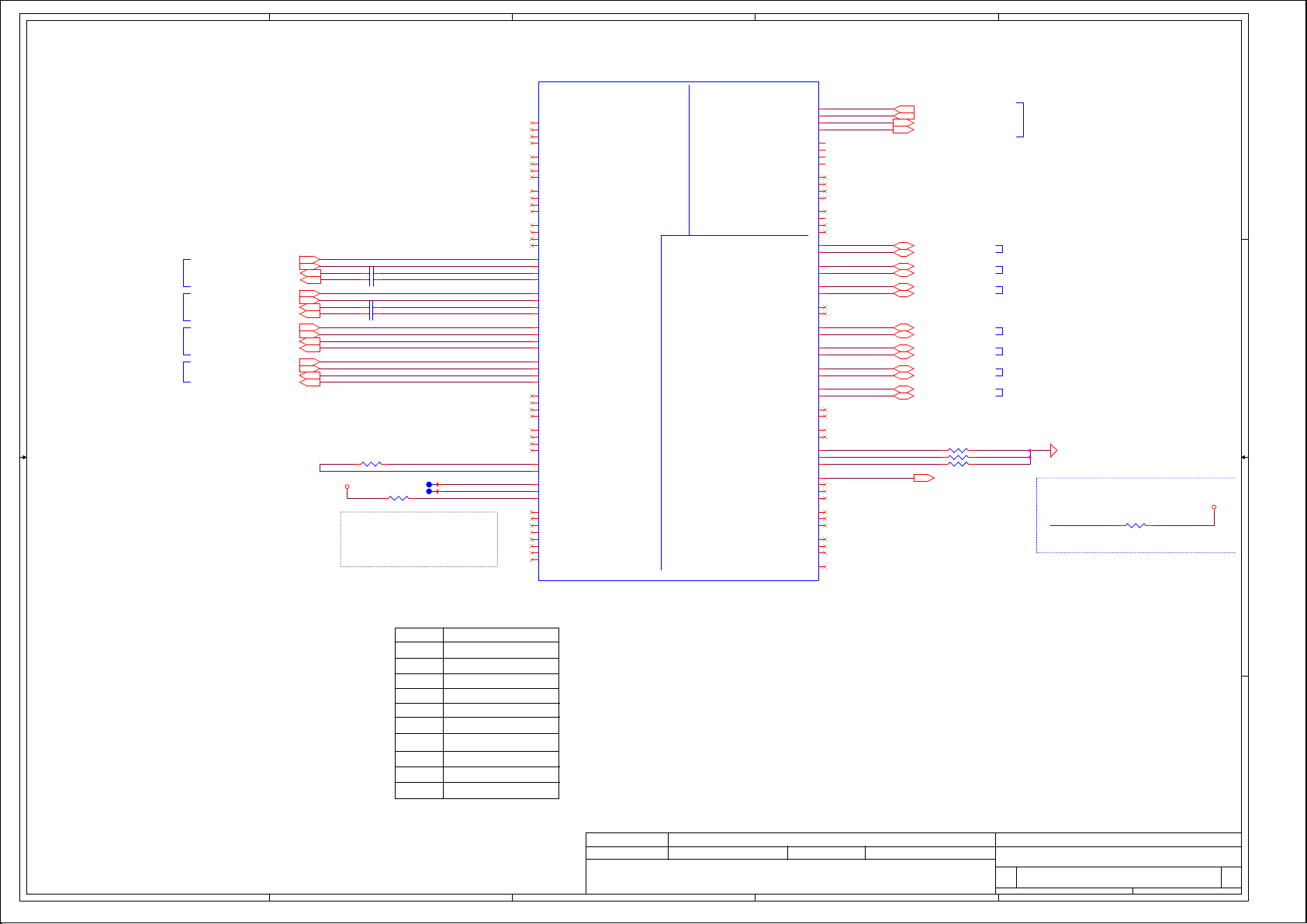

PWR Sequence_SKL-U2+2_DDR3L_Value_NON CS

+RTCVCC

1 1

SOC_RTCRST#

+19VB

+3VLP

EC_ON

+5VALW/+3VALW(+3VALW_DSW...)

SPOK tPCH06_Min : 200 us (+3VALW stable (@95% of full value) to +1.0VALW_PRIM starting to ramp)

+1.8VALW_PRIM

+1.8VALW_PG

+VCCPRIM_CORE/+1.0 VALW _PRI M

EC_RSMRST#

ON/OFF

2 2

PBT N_OUT #

PM_SLP_S5 #

ESPI_RST#

PM_SLP_S4 #

SYSON

+1.0V_VCCSTU

+1.2V_VDDQ

PM_SLP_S3 #

SUSP#

+1.0VS_VCCSTG

+VCCIO

3 3

+5VS/+3VS/+ 1.8 VS /+ 1.5V S

EC_VCCST_PG

VR_ON

SM_PG_C TR L

+0.6VS_ VT T

+VCC_S A

VR_PWRG D

PCH_PW ROK ( SYS_PWR OK)

H_CPUPWR GD

PLT_R ST #

4 4

+VCC_CORE / +VCC_GT

tPCH01_Min : 9 ms

tPCH43_Min : 95 ms

tPCH04_Min : 9 ms

tPCH34_Max : 20 ms

tPCH03_Min : 10 ms

Minimum duration of PWRBTN# assertion = 16mS. PWRBTN# can assert before or after RSMRST#

tPCH18_Min : 90 us

tCPU04 Min : 100 ns

tCPU10 Min : 1 ms

tCPU00 Min : 1 ms

tCPU19 Max : 100 ns

tCPU18 Max : 35 us

tCPU09 Min : 1 ms

tCPU16 Min : 0 ns

tPLT05 Min : Platform dependent

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Issued Da te

Issued Da te

Issued Da te

THIS SHEE T OF EN GINEE RING DRAW ING IS THE PROP RIETARY PROP ERTY OF COMPAL ELEC TRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEE T OF EN GINEE RING DRAW ING IS THE PROP RIETARY PROP ERTY OF COMPAL ELEC TRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEE T OF EN GINEE RING DRAW ING IS THE PROP RIETARY PROP ERTY OF COMPAL ELEC TRONICS, INC. AND C ONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION I T CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION I T CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCL OSED TO ANY THIRD P ARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCL OSED TO ANY THIRD P ARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCL OSED TO ANY THIRD P ARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2016/07/18 2016/11/10

2016/07/18 2016/11/10

2016/07/18 2016/11/10

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphere d Date

Deciphere d Date

Deciphere d Date

Compal+Electronics,+Inc.

Compal+Electronics,+Inc.

Compal+Electronics,+Inc.

Title

Title

Title

Power+Sequence

Power+Sequence

Power+Sequence

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

B5W1S

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

E

644Monday, July 18, 2016

644Monday, July 18, 2016

644Monday, July 18, 2016

1.0

1.0

1.0

A

1 1

B

C

D

E

DDI

DISPLAY SIDEBANDS

UC1D

D63

CATERR#

A54

PECI

C65

PROCHOT#

C63

THERMTRIP#

A65

SKTOCC#

C55

BPM#[0]

D55

BPM#[1]

B54

BPM#[2]

C56

BPM#[3]

A6

GPP_E3/ CPU_GP0

A7

GPP_E7/ CPU_GP1

BA5

GPP_B3/ CPU_GP2

AY5

GPP_B4/ CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

H66

OPCE_RC OMP

H65

OPC_RC OMP

SKL-U_BGA1356

@

SKL-U

1 OF 20

CPU MISC

EDP

SKL-U

4 OF 20

Rev_0.53

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

GPP_E13 /DDPB_HP D0

GPP_E14 /DDPC_HP D1

GPP_E15 /DDPD_HP D2

GPP_E16 /DDPE_HP D3

GPP_E17 /EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

Rev_0.53

JTAG

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_TRST#

JTAGX

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

B61

D60

A61

C60

B59

B56

D59

A56

C59

C61

A59

SOC_DP2_HPD

EC_SCI#

CPU_EDP_HPD

ENBKL

SOC_BKL_PWM

SOC_ENVDD

CPU_XDP_TCK0

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TMS

SOC_XDP_TRST#

PCH_JTAG_TCK1

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TMS

SOC_XDP_TRST#

CPU_XDP_TCK0

EDP_TXN0 <21>

EDP_TXP0 < 21>

EDP_TXN1 <21>

EDP_TXP1 < 21>

EDP_AUXN <21>

EDP_AUXP <21>

SOC_DP2_HPD <22>

EC_SCI# <29>

CPU_EDP_HPD <21>

ENBKL <29>

SOC_BKL_PWM <21>

SOC_ENVDD <21>

T194 @

T195 @

eDP

From HDMI

From eDP

1 2

@

+3VS

EC_SCI#

RC212

10K_0402_5%

EC_SCI# SOC internal PU

#545659 PCH EDS1.51 P.131

SCI capability is available on all GPIOs, while

NMI and SMI capability is available on only

select GPIOs.

Below are the PCH GPIOs that can be

routed to generate SMI# or NMI:

GPP_B14, GPP_B20, GPP_B23‧‧‧‧

GPP_C [23 : 22 ]‧‧‧‧

GPP_D [4 : 0 ]‧‧‧‧

GPP_E [8 : 0 ] , GPP_E [16 : 13 ]‧‧‧‧

CC81

@ESD@

SOC_XDP_TRST#

.1U_04 02_16V7K

1 2

UC1A

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

Funct i onal Str ap Def ini t i ons

#543016 PDG2.0 P.844

DDPB_CTRLDATA

DDPC_CTRLDATA

Display Port B/C Detected

NC =Port is not detected.

PU =Port is detected.

2 2

+VCCIO

H_THERMTRIP#

H_PECI

H_PROCHOT#_R

EDP_COMP

TP_INT#

SOC_XDP_TMS

SOC_XDP_TDI

SOC_XDP_TDO

SOC_XDP_TDO

CPU_XDP_TCK0

EC_TP_INT#<29,30>

CPU side

CMC side

1 2

RC1 24.9_0402_1%

#543016 PDG2.0 P.225

COMPENSATI ON PU for eDP

Trace width=5 mils,Spacing=25mil,Max length=600mils

+1.0V_VCCST

3 3

+1.0VS_VCCSTG

4 4

#543016 PDG2.0 P.857

PU 1K to VCCST

1 2

RC2 1K_0402_5%

+3VS

1 2

RC157 100K_0402_5%

@

CC52

@ESD@

.1U_04 02_16V7K

12

CC53

@ESD@

.1U_04 02_16V7K

12

For Intel debug, place to CPU side.

#543016 PDG2.0 P.629

RC11 51_0402_5%CMC@

RC13 51_0402_5%CMC@

RC15 100_0402_5%CMC@

RC17 100_0402_5%CMC@

RC35 51_0402_5%CMC@

12

12

12

12

12

HDMI DDC (Port C)

H_PROCHOT#<29>

HDMI

SOC_DP2_CTRL_CLK<22>

SOC_DP2_CTRL_DATA<22>

+1.0VS_VCCSTG

SPI touch INT follow CRB

SOC_DP2_N0<22>

SOC_DP2_P0<22>

SOC_DP2_N1<22>

SOC_DP2_P1<22>

SOC_DP2_N2<22>

SOC_DP2_P2<22>

SOC_DP2_N3<22>

SOC_DP2_P3<22>

SOC_DP2_CTRL_CLK

SOC_DP2_CTRL_DATA

EDP_COMP

12

RC3

1K_0402_5%

RC4

499_0402_1%

1 2

+3VS

@

1 2

RC137 0_0402_5%

RC5 49.9_0402_1%

RC6 49.9_0402_1%

RC7 49.9_0402_1%

RC8 49.9_0402_1%

#543016 PDG2.0 P.873

PROC_POPIRCOMP /PCH_ OPIRC OMP

PD 50ohm

#544669 CRB1.1 P.52

EDRAM_OPIO_RCOMP /EOPI O_RCO MP

PD 50ohm

12

12

12

12

12

F56

G56

C50

D50

C52

D52

A50

B50

D51

C51

L13

L12

N7

N8

N11

N12

E52

Reserved CATERR# for

sight i ngs i ss ue c heck

T166@

H_PECI<29>

T160@

T161@

1 2

RC9 100K_0402_5%

I2C_TS _INT#<21>

DC2RB751V-40_SOD323-2

CPU_POPIRCOMP

PCH_OPIRCOMP

EDRAM_OPIO_RCOMP

EOPIO_RCOMP

DDI1_TXN[3]

DDI1_TXP[3]

DDI2_TXN[0]

DDI2_TXP[0]

DDI2_TXN[1]

DDI2_TXP[1]

DDI2_TXN[2]

DDI2_TXP[2]

DDI2_TXN[3]

DDI2_TXP[3]

GPP_E18 /DDPB_CT RLCLK

GPP_E1 9/DDPB_C TRLDATA

GPP_E20 /DDPC_CT RLCLK

GPP_E2 1/DDPC_ CTRLDATA

GPP_E22 /DDPD_CT RLCLK

GPP_E2 3/DDPD_ CTRLDATA

EDP_RCOMP

SKL-U_BGA1356

@

H_CATERR#

H_PECI

H_PROCHOT#_R

H_THERMTRIP#

XDP_BPM#0

XDP_BPM#1

I2C_TS _INT#

TP_INT#

AT16

AU16

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Issued Da te

Issued Da te

Issued Da te

THIS SHEE T OF EN GINEE RING DRAW ING IS THE PROP RIETARY PROP ERTY OF COMPAL ELEC TRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEE T OF EN GINEE RING DRAW ING IS THE PROP RIETARY PROP ERTY OF COMPAL ELEC TRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEE T OF EN GINEE RING DRAW ING IS THE PROP RIETARY PROP ERTY OF COMPAL ELEC TRONICS, INC. AND C ONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION I T CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION I T CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCL OSED TO ANY THIRD P ARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCL OSED TO ANY THIRD P ARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCL OSED TO ANY THIRD P ARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2016/07/18 2016/11/10

2016/07/18 2016/11/10

2016/07/18 2016/11/10

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphere d Date

Deciphere d Date

Deciphere d Date

Compal+Electronics,+Inc.

Compal+Electronics,+Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal+Electronics,+Inc.

SKL-U(1/12)DDI,MSIC,XDP,EDP

SKL-U(1/12)DDI,MSIC,XDP,EDP

SKL-U(1/12)DDI,MSIC,XDP,EDP

B5W1S

E

744Monday, July 18, 2016

744Monday, July 18, 2016

744Monday, July 18, 2016

1.0

1.0

1.0

A

B

C

D

E

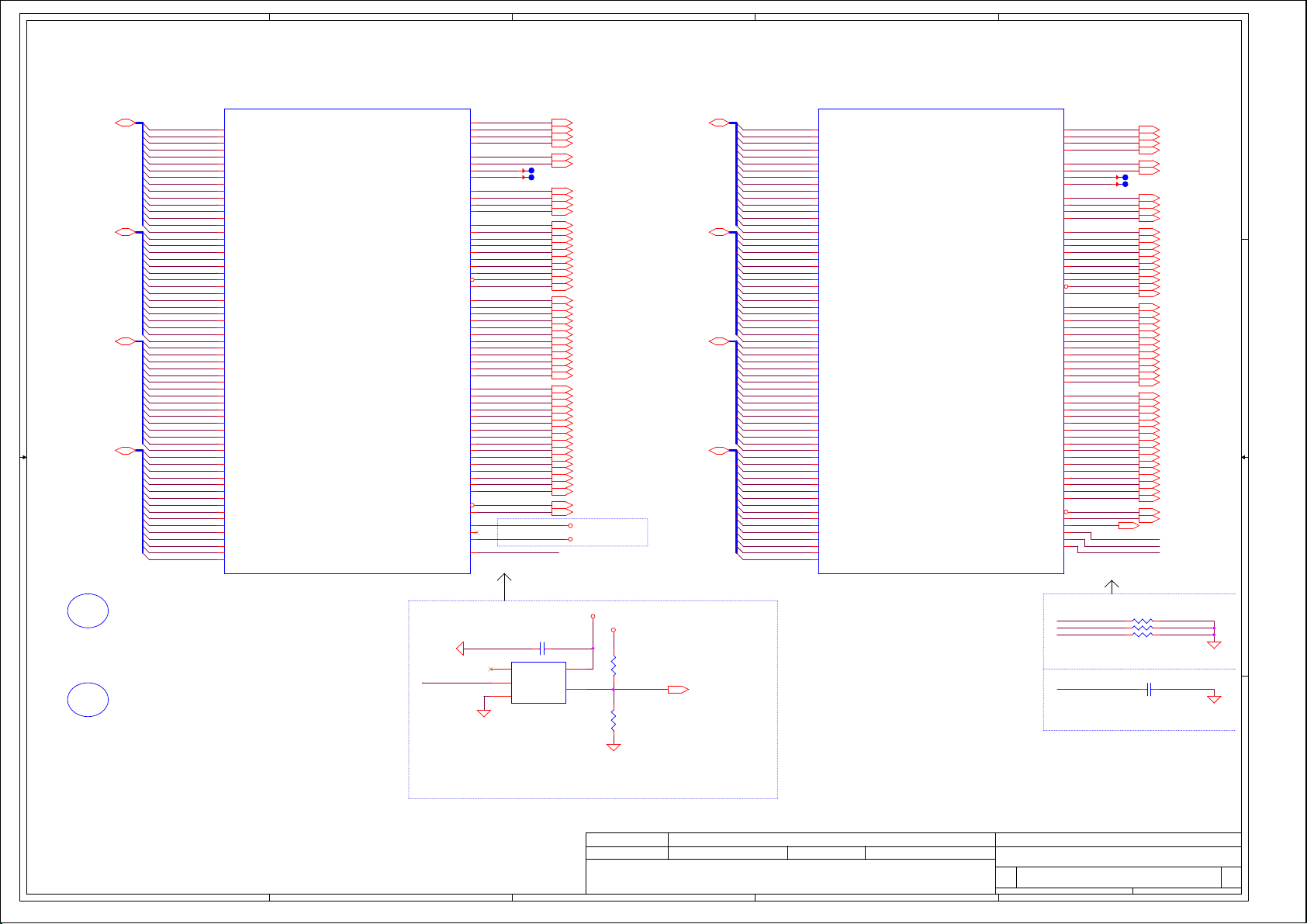

Interleaved Memory

UC1B

DDR_A_D[0..15]<19>

1 1

DDR_A_D[16..31]<19>

DDR_A_D[32..47]<19>

2 2

DDR_A_D[48..63]<19>

3 3

ZZZ

PCB B5W11 LA-E061P LS-D671P

DAZ1P500100

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

AL71

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

SKL-U_BGA1356

@

ES Sample

UC1

CPU_G0 2.6G

QKJW@

SA00009UR10

SKL-U

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR CH - A

2 OF 20

DDR0_ODT[1]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

DDR_PG_CTRL

DDR_A_CLK#0

AU53

DDR_A_CLK0

AT53

DDR_A_CLK#1

AU55

DDR_A_CLK1

AT55

DDR_A_CKE0

BA56

DDR_A_CKE1

BB56

AW56

AY56

DDR_A_CS#0

AU45

DDR_A_CS#1

AU43

DDR_A_ODT0

AT45

DDR_A_ODT1

AT43

DDR_A_MA5

BA51

DDR_A_MA9

BB54

DDR_A_MA6

BA52

DDR_A_MA8

AY52

DDR_A_MA7

AW52

DDR_A_BG0

AY55

DDR_A_MA12

AW54

DDR_A_MA11

BA54

DDR_A_ACT#

BA55

DDR_A_BG1

AY54

DDR_A_MA13

AU46

DDR_A_MA15

AU48

DDR_A_MA14

AT46

DDR_A_MA16

AU50

DDR_A_BA0

AU52

DDR_A_MA2

AY51

DDR_A_BA1

AT48

DDR_A_MA10

AT50

DDR_A_MA1

BB50

DDR_A_MA0

AY50

DDR_A_MA3

BA50

DDR_A_MA4

BB52

DDR_A_DQS#0

AM70

DDR_A_DQS0

AM69

DDR_A_DQS#1

AT69

DDR_A_DQS1

AT70

DDR_A_DQS#2

BA64

DDR_A_DQS2

AY64

DDR_A_DQS#3

AY60

DDR_A_DQS3

BA60

DDR_A_DQS#4

BA38

DDR_A_DQS4

AY38

DDR_A_DQS#5

AY34

DDR_A_DQS5

BA34

DDR_A_DQS#6

BA30

DDR_A_DQS6

AY30

DDR_A_DQS#7

AY26

DDR_A_DQS7

BA26

DDR_A_ALERT#

AW50

DDR_A_PAR DDR_B_ALERT#

AT52

+0.6V_A_VREFCA

AY67

AY68

+0.6V_B_VREFCA

BA67

DDR_PG_CTRL

AW67

NC1VCC

2

A

3

GND

74AUP1G07GW_TSS OP5

Change PN to SA00007UR00.

DDR_A_CLK#0 <19>

DDR_A_CLK0 <19>

DDR_A_CLK#1 <19>

DDR_A_CLK1 <19>

DDR_A_CKE0 <19>

DDR_A_CKE1 <19>

T14@

T15@

DDR_A_CS#0 <19>

DDR_A_CS#1 <19>

DDR_A_ODT1 <19>

DDR_A_MA5 <19>

DDR_A_MA9 <19>

DDR_A_MA6 <19>

DDR_A_MA8 <19>

DDR_A_MA7 <19>

DDR_A_BG0 <19>

DDR_A_MA12 <19>

DDR_A_MA11 <19>

DDR_A_ACT# <19>

DDR_A_BG1 <19>

DDR_A_MA13 <19>

DDR_A_MA15 <19>

DDR_A_MA14 <19>

DDR_A_MA16 <19>

DDR_A_BA0 <19>

DDR_A_MA2 <19>

DDR_A_BA1 <19>

DDR_A_MA10 <19>

DDR_A_MA1 <19>

DDR_A_MA0 <19>

DDR_A_MA3 <19>

DDR_A_MA4 <19>

DDR_A_DQS#0 <19>

DDR_A_DQS0 <19>

DDR_A_DQS#1 <19>

DDR_A_DQS1 <19>

DDR_A_DQS#2 <19>

DDR_A_DQS2 <19>

DDR_A_DQS#3 <19>

DDR_A_DQS3 <19>

DDR_A_DQS#4 <19>

DDR_A_DQS4 <19>

DDR_A_DQS#5 <19>

DDR_A_DQS5 <19>

DDR_A_DQS#6 <19>

DDR_A_DQS6 <19>

DDR_A_DQS#7 <19>

DDR_A_DQS7 <19>

DDR_A_ALERT# <19>

DDR_A_PAR <19> DDR_B_ALERT# <20>

+0.6V_A_VREFCA

+0.6V_B_VREFCA

#543016 PDG2.0 P.190

Trace width/Spacing >= 20mils

Place componment near SODIMM

+1.2V_VDDQ

+3VS

12

CC57.1U_04 02_16V7K

UC7

Y

12

5

4

1 2

RC10

100K_0402_5%

RC16

1M_0402_5%@

DDR_B_D[0..15]<20>

DDR_B_D[16..31]<20>

DDR_B_D[32..47]<20>

DDR_B_D[48..63]<20>

SM_PG_CTRL <37>

DDR_VTT_CNTL to DDR

VTT suppl ied ramped

<35uS

(tCPU18)

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

UC1C

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKL-U_BGA1356

@

SKL-U

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DRAM_RESET#

DDR_RCOMP[0]

DDR CH - B

3 OF 20

DDR_RCOMP[1]

DDR_RCOMP[2]

Rev_0.53Rev_0.53

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DDR_B_CLK#0

AN45

DDR_B_CLK#1

AN46

DDR_B_CLK0

AP45

DDR_B_CLK1

AP46

DDR_B_CKE0

AN56

DDR_B_CKE1

AP55

AN55

AP53

DDR_B_CS#0

BB42

DDR_B_CS#1

AY42

DDR_B_ODT0

BA42

DDR_B_ODT1

AW42

DDR_B_MA5

AY48

DDR_B_MA9

AP50

DDR_B_MA6

BA48

DDR_B_MA8

BB48

DDR_B_MA7

AP48

DDR_B_BG0

AP52

DDR_B_MA12

AN50

DDR_B_MA11

AN48

DDR_B_ACT#

AN53

DDR_B_BG1

AN52

DDR_B_MA13

BA43

DDR_B_MA15

AY43

DDR_B_MA14

AY44

DDR_B_MA16

AW44

DDR_B_BA0

BB44

DDR_B_MA2

AY47

DDR_B_BA1

BA44

DDR_B_MA10

AW46

DDR_B_MA1

AY46

DDR_B_MA0

BA46

DDR_B_MA3

BB46

DDR_B_MA4

BA47

DDR_B_DQS#0

AH66

DDR_B_DQS0

AH65

DDR_B_DQS#1

AG69

DDR_B_DQS1

AG70

DDR_B_DQS#2

AR66

DDR_B_DQS2

AR65

DDR_B_DQS#3

AR61

DDR_B_DQS3

AR60

DDR_B_DQS#4

AT38

DDR_B_DQS4

AR38

DDR_B_DQS#5

AT32

DDR_B_DQS5

AR32

DDR_B_DQS#6

AR25

DDR_B_DQS6

AR27

DDR_B_DQS#7

AR22

DDR_B_DQS7

AR21

AN43

DDR_B_PAR

AP43

AT13

AR18

SM_RCOMP0

AT18

SM_RCOMP1

AU18

SM_RCOMP2

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

#543016 PDG2.0 P.139

W=12-15 Space= 20/25 L=500mil

DDR_DRAMRST#

T17@

T18@

DDR_DRAMRST# <19,20>

1 2

RC38 121_0402_1%

1 2

RC39 80.6_0402_1%

1 2

RC40 100_0402_1%

@ESD@

1 2

CC70 .1U_0402_16V7K

2015MOW02, Can't install Cap on DRAMRST

DDR_B_CLK#0 <20>

DDR_B_CLK#1 <20>

DDR_B_CLK0 <20>

DDR_B_CLK1 <20>

DDR_B_CKE0 <20>

DDR_B_CKE1 <20>

DDR_B_CS#0 <20>

DDR_B_CS#1 <20>DDR_A_ODT0 <19>

DDR_B_ODT0 <20>

DDR_B_ODT1 <20>

DDR_B_MA5 <20 >

DDR_B_MA9 <20 >

DDR_B_MA6 <20 >

DDR_B_MA8 <20 >

DDR_B_MA7 <20 >

DDR_B_BG0 <20>

DDR_B_MA12 <20>

DDR_B_MA11 <20>

DDR_B_ACT# <20>

DDR_B_BG1 <20>

DDR_B_MA13 <20>

DDR_B_MA15 <20>

DDR_B_MA14 <20>

DDR_B_MA16 <20>

DDR_B_BA0 <20>

DDR_B_MA2 <20 >

DDR_B_BA1 <20>

DDR_B_MA10 <20>

DDR_B_MA1 <20 >

DDR_B_MA0 <20 >

DDR_B_MA3 <20 >

DDR_B_MA4 <20 >

DDR_B_DQS#0 <20>

DDR_B_DQS0 <20>

DDR_B_DQS#1 <20>

DDR_B_DQS1 <20>

DDR_B_DQS#2 <20>

DDR_B_DQS2 <20>

DDR_B_DQS#3 <20>

DDR_B_DQS3 <20>

DDR_B_DQS#4 <20>

DDR_B_DQS4 <20>

DDR_B_DQS#5 <20>

DDR_B_DQS5 <20>

DDR_B_DQS#6 <20>

DDR_B_DQS6 <20>

DDR_B_DQS#7 <20>

DDR_B_DQS7 <20>

DDR_B_PAR <20>

4 4

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Issued Da te

Issued Da te

Issued Da te

THIS SHEE T OF EN GINEE RING DRAW ING IS THE PROP RIETARY PROP ERTY OF COMPAL ELEC TRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEE T OF EN GINEE RING DRAW ING IS THE PROP RIETARY PROP ERTY OF COMPAL ELEC TRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEE T OF EN GINEE RING DRAW ING IS THE PROP RIETARY PROP ERTY OF COMPAL ELEC TRONICS, INC. AND C ONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION I T CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION I T CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCL OSED TO ANY THIRD P ARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCL OSED TO ANY THIRD P ARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCL OSED TO ANY THIRD P ARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2016/07/18 2016/11/10

2016/07/18 2016/11/10

2016/07/18 2016/11/10

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphere d Date

Deciphere d Date

Deciphere d Date

Compal+Electronics,+Inc.

Compal+Electronics,+Inc.

Compal+Electronics,+Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

SKL-U(2/12)DDR4

SKL-U(2/12)DDR4

SKL-U(2/12)DDR4

B5W1S

Monday, July 18, 2016

Monday, July 18, 2016

Monday, July 18, 2016

E

8

1.0

1.0

1.0

44

44

44

8

8

A

1 1

UC1E

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

M2

GPP_D1/ SPI1_CLK

M3

GPP_D2 /SPI1_MIS O

J4

GPP_D3 /SPI1_MOS I

V1

GPP_D21 /SPI1_IO2

V2

GPP_D22 /SPI1_IO3

M1

GPP_D0/ SPI1_CS#

G3

CL_CLK

G2

CL_DATA

G1

CL_RST#

GPP_A0/R CIN#

GPP_A6/ SERIRQ

SKL-U_BGA1356

@

18

27

36

45

12

SPI - F LASH

SPI - TOUCH

C LINK

SPI ROM

SOC_SPI_CLK

SOC_SPI_SO

SOC_SPI_SI

SOC_SPI_IO2

SOC_SPI_IO3

SOC_SPI_CS#0

AW3

AW2

AV2

AV3

AU4

AU3

AU2

AU1

SPI Touch

2 2

EC_KBRST#_R<29>

TPM_SERIRQ<29>

3 3

EC_KBRST#_R

TPM_SERIRQ

LPC Mode

RPC5 and RC52 are close UC2

SOC_SPI_IO3 SOC_ SPI_IO3_0_R

SOC_SPI_SI SOC_SPI_SI_0_R

SOC_SPI_CLK SOC_SPI_CLK_0_R

SOC_SPI_SO SOC_SPI_SO_0_R

SOC_SPI_IO2 SOC_SPI_IO2_0_R

AW13

AY11

RPC5

15_0804_8P4R_5 %

RC52 15_0402_5%

SKL-U

SOC_SPI_CS#0

SOC_SPI_IO2_0_R

B

SMBUS, SMLINK

GPP_C0/ SMBCLK

GPP_C1/SMBDATA

GPP_C2 /SMBALERT #

GPP_C3 /SML0CLK

GPP_C4/SML0DATA

GPP_C5 /SML0ALE RT#

GPP_C6 /SML1CLK

GPP_C7/SML1DATA

GPP_B2 3/SML1ALE RT#/PCHH OT#

LPC

5 OF 20

SOC_SPI_CLK_0_R

ROM Socket, co-lay with UC2.

SOC_SPI_CS#0

SOC_SPI_IO2_0_R

SOC_SPI_IO3_0_R

GPP_A1/ LAD0/ESP I_IO0

GPP_A2/ LAD1/ESP I_IO1

GPP_A3/ LAD2/ESP I_IO2

GPP_A4/ LAD3/ESP I_IO3

GPP_A5/ LFRAME#/E SPI_CS#

GPP_A1 4/SUS_STA T#/ESPI_R ESET#

GPP_A9/ CLKOUT_L PC0/ESPI_ CLK

GPP_A10 /CLKOUT_LP C1

GPP_A8/ CLKRUN#

SPI ROM ( 8MByte )

UC2

1

/CS

2

DO(IO1)

3

4

/HOLD(IO3 )

/WP(IO2)

GND

W25Q64FVSSI Q_SO8

DI(IO0)

1 2

@EMI@

RC24 0_0402_5%

JC1

1

CS#

3

WP#

7

HOLD#

4

GND

ACES_91960-0084N_MX25 L3206EM2I

CONN@

VCC

CLK

SI/SIO0

SO/SIO1

VCC

SCLK

C

SOC_SMBCLK

R7

SOC_SMBDATA

R8

SOC_SMBALERT#

R10

SOC_SML0CLK

R9

SOC_SML0DATA

W2

SOC_SML0ALERT#

W1

SOC_SML1CLK

W3

SOC_SML1DATA

V3

SOC_SML1ALERT#

AM7

Change RC144~RC147, RC45 to 15o hm when use ESPI

LPC_AD0

+3VALW_SPI

8

SOC_SPI_IO3_0_RSOC_SPI_SO_0_R

7

SOC_SPI_CLK_0_R

6

SOC_SPI_SI_0_R

5

AY13

BA13

BB13

AY12

BA12

BA11

AW9

AY9

AW11

1 2

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

ESPI_RST#

CLKOUT_LPC0

PM_CLKRUN#

CC8

.1U_04 02_16V7K

RC144 0_0402_5%@

RC145 0_0402_5%@

RC146 0_0402_5%@

RC147 0_0402_5%@

T239@

Strap Pin

SOC_SML1CLK <29>

SOC_SML1DATA <29>

T234@

1 2

1 2

1 2

1 2

LPC_FRAME# <29>

ESPI_RST# <29>

LPC@

12

RC45 22_0402_5%

2015MOW06 no need PU1K on SPI_IO2/IO3

1 2

CC9

@EMI@

10P_0402_50V8 J

+3VALW_SPI

8

SOC_SPI_CLK_0_R

6

SOC_SPI_SI_0_R

5

SOC_SPI_SO_0_R

2

SOC_SPI_IO2

SOC_SPI_IO3

12

RC2024.7K_0402_5% ESPI@

SMB

+3VALW_PRIM

SML1

LPC_AD0_R <29>

LPC_AD1_R <29>

LPC_AD2_R <29>

LPC_AD3_R <29>

CLK_LPC_EC <29>

1 2

RC47 1K_0402_1%@

1 2

RC48 1K_0402_1%@

(to DDR, G sensor)

( to EC, Thermal sensor)

ESPI / L PC B us

ESPI : +1.8V

LPC : +3.3V

*

To EC

+3VALW_SPI

D

SOC_SMBCLK_1

SOC_SMBDATA_1

SOC_SML0CLK

SOC_SML0DATA

SOC_SML1CLK

SOC_SML1DATA

SOC_SMBCLK

SOC_SMBDATA

+3VS

SOC_SMBCLK

SOC_SMBDATA

*

*

3 4

D

PM_CLKRUN#

TPM_SERIRQ

SML0ALERT# / GPP_C5 (Internal P ull Down):

(Sampled: Rising edge of RSMRST# )

eSPI or LPC

0 = LPC is selected for EC --> For KB9022/9032 Use

1 = eSPI is selected for EC --> For KB9032 Only.

SMBALERT# / GPP_C2 (Internal Pull Down):

(Sampled: Rising edge of RSMRST# )

TLS Conf i dent ial i ty

0 = Disable Intel ME Crypto Transport Layer Security

(TLS) cipher suite (no conf i den tial i ty).

1 = Enable Intel ME Crypto (TLS) (with conf i dent iality).

Must be pulled up to support Intel AMT with TLS and Intel

SBA (Small Business Advantage) with TLS.

5

G

6 1

RC222 2.2K_0402_5%

RC223 2.2K_0402_5%

RC49 499_0402_1%

RC50 499_0402_1%

QC2B

2N7002KDW_S OT363-6

SOC_SMBCLK_1

S

2

G

QC2A

2N7002KDW_S OT363-6

S

D

RC107 10K_0402_5%

RC112 10K_0402_5%

1 2

1 2

1 2

1 2

RPC7

1 8

2 7

3 6

4 5

2.2K_0804_8P4R _5%

SOC_SMBDATA_1

1 2

1 2

E

+3VS

+3VALW_PRIM

SOC_SMBCLK_1 <19,20>

SOC_SMBDATA_1 <19,20>

+1.8VS_3VS_PGPPA

4 4

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Issued Da te

Issued Da te

Issued Da te

THIS SHEE T OF EN GINEE RING DRAW ING IS THE PROP RIETARY PROP ERTY OF COMPAL ELEC TRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEE T OF EN GINEE RING DRAW ING IS THE PROP RIETARY PROP ERTY OF COMPAL ELEC TRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEE T OF EN GINEE RING DRAW ING IS THE PROP RIETARY PROP ERTY OF COMPAL ELEC TRONICS, INC. AND C ONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION I T CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION I T CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCL OSED TO ANY THIRD P ARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCL OSED TO ANY THIRD P ARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCL OSED TO ANY THIRD P ARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2016/07/18 2016/11/10

2016/07/18 2016/11/10

2016/07/18 2016/11/10

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphere d Date

Deciphere d Date

Deciphere d Date

Compal+Electronics,+Inc.

Compal+Electronics,+Inc.

Compal+Electronics,+Inc.

Title

Title

Title

SKL-U(3/12)SPI,ESPI,SMB,LPC

SKL-U(3/12)SPI,ESPI,SMB,LPC

SKL-U(3/12)SPI,ESPI,SMB,LPC

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

B5W1S

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

E

944Monday, July 18, 2016

944Monday, July 18, 2016

944Monday, July 18, 2016

1.0

1.0

1.0

A

1 1

B

C

D

E

9 OF 20

SKL-U

7 OF 20

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/ FLASHTRI G

EMMC

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21 /EMMC_RC LK

GPP_F2 2/EMMC_CL K

GPP_F12/EMMC_CMD

EMMC_RCOMP

SDIO/SDXC

GPP_G0/S D_CMD

GPP_G1/S D_DATA0

GPP_G2/S D_DATA1

GPP_G3/S D_DATA2

GPP_G4/S D_DATA3

GPP_G5/SD _CD#

GPP_G6/SD _CLK

GPP_A1 7/SD_PWR _EN#/ISH_ GP7

Rev_0.53

GPP_G7/SD_WP

GPP_A16 /SD_1P8_S EL

C37

D37

C32

D32

C29

D29

B26

A26

CSI2_COMP

E13

DGPU_PRSNT#

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

EMMC_RCOMP

AT1

Rev_0.53

AB11

AB13

AB12

W12

W11

W10

W8

W7

BA9

BB9

AB7

SD_RCOMP

AF13

GPP_F23

#543016 PDG2.0 P.551

RC80 100_0402_1%

RC89 200_0402_1%

#543016 PDG2.0 P.393

#543016 PDG2.0 P.403

SDIO signals are mult i pl exe d wi t h GPI Os an d defa ult

to GPIO funct i onalit y ( as i nput). I f S DI O i nt erf ac e is

not u sed, the s ignals can be used as GPIOs instead.

If the GPIO funct i onalit y i s als o not used, t he si gnals

can be lef t as no-c onnect.

RC76

200_0402_1%

SD_RCOMP

12

#543016 PDG2.0 P.879

12

12

+3VALW_1.8VALW_PGPPD

DGPU_PRSNT#

12

RC133

10K_0402_5%

UC1G

HDA for AUDIO

HDA_SDIN0<25>

HDA_SYNC_R<25>

HDA_SDOUT_R<25>

HDA_BIT_CLK_R<25>

HDA_RST#_R<25>

ME_EN<29>

HDA_SDO / I2S_TXD0 (Internal Pull Down):

(Sampled: Rising edge of PCH_PWROK )

Flash Descriptor Security Override

0 = En able security measures def i ne d i n t he Fl as h

2 2

Descriptor.

1 = D isable Flash Des criptor Securi ty ( override). Thi s

strap should only be asserted high using external

33_0804_8P4R_5 %

RC77 0_0402_5%

RPC9

1 8

2 7

3 6

4 5

1 2

@

HDA_SDIN0

HDA_SYNC

HDA_SDOUT

HDA_BIT_CLK

HDA_RST#

PCH_SPKR<25>

HDA_SYNC

HDA_BIT_CLK

HDA_SDOUT

HDA_SDIN0

HDA_RST#

PCH_SPKR

BA22

AY22

BB22

BA21

AY21

AW22

AY20

AW20

AK10

AW5

AK7

AK6

AK9

pull-up in manufacturing/debug environments ONLY.

SPKR / GPP_B14 (Internal Pull Down):

(Sampled:Rising edg e of PCH_PWROK)

TOP Swap Override

0 = Disable TOP Swap mode.

*

1 = Enable TOP Swap Mode.

Intel HD Audio link capabilit i es

> Two SDI sign als to support two external codecs.

> Drivers variable requency (5MHz to 24MHz) B CLK to support:

-- SDO double pumped up to 48 Mb/s

-- SDI's single pumped up to 24 Mb/s

> Provides cadence for 44.1 kHz based sample rate output.

> Support 1.5V, 1.8V, and 3.3V modes.

3 3

A36

B36

C38

D38

C36

D36

A38

B38

C31

D31

C33

D33

A31

B31

A33

B33

A29

B29

C28

D28

A27

B27

C27

D27

HDA_SYNC/I2S0_SFRM

HDA_BLK/I2S0_SCLK

HDA_SDO/I2S0_TXD

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_RST#/I2S1_SCLK

J5

GPP_D2 3/I2S_MCL K

I2S1_S FRM

I2S1_TX D

GPP_F1 /I2S2_SFR M

GPP_F0/ I2S2_SCLK

GPP_F2/ I2S2_TXD

GPP_F3/ I2S2_RXD

H5

GPP_D19 /DMIC_CL K0

D7

GPP_D20/DMIC_DATA0

D8

GPP_D17 /DMIC_CL K1

C8

GPP_D18/DMIC_DATA1

GPP_B14 /SPKR

SKL-U_BGA1356

@

UC1I

CSI-2

CSI2_DN0

CSI2_DP0

CSI2_DN1

CSI2_DP1

CSI2_DN2

CSI2_DP2

CSI2_DN3

CSI2_DP3

CSI2_DN4

CSI2_DP4

CSI2_DN5

CSI2_DP5

CSI2_DN6

CSI2_DP6

CSI2_DN7

CSI2_DP7

CSI2_DN8

CSI2_DP8

CSI2_DN9

CSI2_DP9

CSI2_DN10

CSI2_DP10

CSI2_DN11

CSI2_DP11

SKL-U_BGA1356

@

AUDIO

SKL_ULT

4 4

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Issued Da te

Issued Da te

Issued Da te

THIS SHEE T OF EN GINEE RING DRAW ING IS THE PROP RIETARY PROP ERTY OF COMPAL ELEC TRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEE T OF EN GINEE RING DRAW ING IS THE PROP RIETARY PROP ERTY OF COMPAL ELEC TRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEE T OF EN GINEE RING DRAW ING IS THE PROP RIETARY PROP ERTY OF COMPAL ELEC TRONICS, INC. AND C ONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION I T CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION I T CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCL OSED TO ANY THIRD P ARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCL OSED TO ANY THIRD P ARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCL OSED TO ANY THIRD P ARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2016/07/18 2016/11/10

2016/07/18 2016/11/10

2016/07/18 2016/11/10

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphere d Date

Deciphere d Date

Deciphere d Date

Compal+Electronics,+Inc.

Compal+Electronics,+Inc.

Compal+Electronics,+Inc.

Title

Title

Title

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

SKL-U(4/12)HDA,EMMC,SDIO,CSI2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

B5W1S

Date: Sheet of

Monday, July 18, 2016

Date: Sheet of

Monday, July 18, 2016

Date: Sheet of

D

Monday, July 18, 2016

E

10

10

10

1.0

1.0

1.0

44

44

44

A

B

C

D

E

+RTCVCC

1 1

+3VS

2 2

From EC(open-drain)

Note for VCCST_PWRGD

1. 1.0V tolerance

2. PDG2.0 P.598 Figure43-5 note17: when failure events,

VCCST_PWRGD and PCH_PWROK de-assert at the same t i me

+3VALW_DSW

3 3

+3VALW_DSW

4 4

1 2

RC91 20K_0402_5%

1 2

CC10 1U_0402_6.3V6K

1 2

RC93 20K_0402_5%

1 2

CC11 1U_0402_6.3V6K

1 2

JCMOS1 0_0603_5%@

SOC_RTCRST#

CLR CMOS

Place at RAM DOOR

12

RC113

1K_0402_5%

RC116

60.4_0402_1%

1 2

SM_INTRUDER#

CLKREQ_PCIE#1

CLKREQ_PCIE#2

CLKREQ_PCIE#5

CLKREQ_PCIE#4

CLKREQ_PCIE#3

CLKREQ_PCIE#0

PCH_PWROK

EC_RSMRST#

SYS_RESET#

LAN_WAKE #

SYS_PWROK

WAKE#

SYS_RESET#

H_CPUPWRGD

SYS_PWROK

PCH_PWROK

EC_RSMRST#

EC_VCCST_PG

1 2

RC94 1M_0402_5%

1 2

RC121 10K_0402_5%

1 2

RC123 10K_0402_5%

RPC12

18

27

36

45

10K_0804_8P4R_5 %

+1.0V_VCCST

EC_VCCST_PG_R<29,32>

+3VALW_PRIM

RC110 10K_0402_5%

RC104 1K_0402_5%

WAKE# (DSX wake event)

10 KΩ pull- up t o Vcc DS W 3_3.

The pull-up is required even if PCIe* interface

is not used on the plat f or m.

RPC11

18

27

36

45

10K_0804_8P4R_5 %

12

1 2

@ESD@

12

CC51 .1U_0402_16V7K

@ESD@

12

CC50 .1U_0402_16V7K

@ESD@

12

CC66 .1U_0402_16V7K

@ESD@

12

CC65 .1U_0402_16V7K

@ESD@

12

CC69 .1U_0402_16V7K

GLAN

NGFF

UC1J

D42

CLKOUT_PCIE_N0

C42

CLKREQ_PCIE#0

CLK_PCIE_N1<23>

CLK_PCIE_P1<23>

CLKREQ_PCIE#1<23>

CLK_PCIE_N2<24>

CLK_PCIE_P2<24>

CLKREQ_PCIE#2<24>

PLT_RST#<29>

EC_RSMRST#<29>

T95 @

T89 @

SYS_PWROK<29,32>

PCH_PWROK<29,32>

SUSPWRDNACK<29>

T92 @

CLK_PCIE_N1

CLK_PCIE_P1

CLKREQ_PCIE#1

CLK_PCIE_N2

CLK_PCIE_P2

CLKREQ_PCIE#2

CLKREQ_PCIE#3

CLKREQ_PCIE#4

CLKREQ_PCIE#5

PLT_RST#

SYS_RESET#

EC_RSMRST#

H_CPUPWRGD

EC_VCCST_PG

SYS_PWROK

PCH_PWROK

PCH_DPWROK

SUSPWRDNACK

SUSACK#

WAKE#

LAN_WAKE #

CLKOUT_PCIE_P0

AR10

GPP_B5/S RCCLKR EQ0#

B42

CLKOUT_PCIE_N1

A42

CLKOUT_PCIE_P1

AT7

GPP_B6/S RCCLKR EQ1#

D41

CLKOUT_PCIE_N2

C41

CLKOUT_PCIE_P2

AT8

GPP_B7/S RCCLKR EQ2#

D40

CLKOUT_PCIE_N3

C40

CLKOUT_PCIE_P3

AT10

GPP_B8/S RCCLKR EQ3#

B40

CLKOUT_PCIE_N4

A40

CLKOUT_PCIE_P4

AU8

GPP_B9/S RCCLKR EQ4#

E40

CLKOUT_PCIE_N5

E38

CLKOUT_PCIE_P5

AU7

GPP_B10 /SRCCLKR EQ5#

SKL-U_BGA1356

@

UC1K

SYSTEM POWER MANAGEMENT

AN10

GPP_B13 /PLTRST#

B5

SYS_RESET#

AY17

RSMRST#

A68

PROCPWRGD

B65

VCCST_PWRGD

B6

SYS_PWROK

BA20

PCH_PWROK

BB20

DSW_PWROK

AR13

GPP_A1 3/SUSWA RN#/SUS PWRDNAC K

AP11

GPP_A15 /SUSACK#

BB15

WAKE#

AM15

GPD2/LA N_WAKE#

AW17

GPD11/LAN PHYPC

AT15

GPD7/RSV D

SKL-U_BGA1356

@

PBTN_OUT#<29>

EC_RSMRST# PCH_DPWROK

PCH PLTRST Buf f er

PLT_RST#

UC3

MC74VHC 1G08DFT2G_ SC70-5

RC125 0_0402_5%@

SKL_ULT

CLOCK SIGNAL S

10 OF 20

SKL-U

GPP_B11/EXT_PWR_GATE#

11 OF 20

PBTN_OUT#_R

12

@

RC109 0_0402_5%

RC114 0_0402_5%

RC122 0_0402_5%

2

1

B

A

+3VS

12

@

PCH_PWROKSYS_PWROK

12

@

5

P

PLT_RST_BUF#

4

Y

G

@

3

12

Rev_0.53

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

GPD8/SU SCLK

XTAL24_IN

XTAL24_OUT

XCLK_BIASREF

RTCX1

RTCX2

SRTCRST#

RTCRST #

Rev_0.53

GPP_B12 /SLP_S0#

GPD4/SLP _S3#

GPD5/SLP _S4#

GPD10/S LP_S5#

SLP_SUS#

SLP_LAN#

GPD9/SLP_WLAN#

GPD6/SL P_A#

GPD3/PWRBTN#

GPD1/ACP RESENT

GPD0/BATLOW#

GPP_A11/PME#

INTRUD ER#

GPP_B2/ VRALERT#

PLT_RST_BUF# <23,24 >

12

RC118

100K_0402_5%

F43

E43

BA17

E37

E35

E42

AM18

AM20

AN18

AM16

AT11

AP15

BA16

AY16

AN15

AW15

BB17

AN16

BA15

AY15

AU13

AU11

AP16

AM10

AM11

CLK_CPU_ITP#

CLK_CPU_ITP

SUSCLK

SOC_XTAL24_IN

SOC_XTAL24_OUT

XCLK_BIASREF

SOC_RTCX1

SOC_RTCX2

SOC_SRTCRST#

SOC_RTCRST#

PM_SLP_S0#

PM_SLP_S3#

PM_SLP_S4#

PM_SLP_S5#

SLP_SUS#

SLP_LAN#

SLP_WLAN#

PM_SLP_A#

PBTN_OUT#_R

AC_PRESENT

PM_BATLOW#

SM_INTRUDER#

EXT_PWR_GATE#

SOC_VRALERT#

T164 @

T165 @

T185 @

PM_SLP_S0# <29>

PM_SLP_S3# <29,32>

PM_SLP_S4# <29,32>

T84@

T90@

T87@

T88@

T94@

AC_PRESENT <29>

T91@

T93@

SOC_XTAL24_IN

SOC_XTAL24_OUTSOC_SRTCRST#

Follow 2014MOW4 8

Skylake U PU 2.7k ohm to 1V

Cannon lake U PD 60.4 ohm

XCLK_BIASREF

XCLK_BIASR EF

T:50ohm S:12/15 L:1000 Via:2

2014MOW4 8:

Skylake-U use 24M 50 ohm ESR

Cannonlake U use 38.4M 30 ohm ESR

SOC_RTCX2

SOC_RTCX1

CC15

6.8P_0402_50V8C

PBTN_OUT#_R

AC_PRESENT

PM_BATLOW#

SOC_VRALERT#

RC92 1M_0402_5%

YC1

24MHZ_12PF_7V 24000020

3

3

CC12

15P_0402_50V8 J

12

RC96 2.7K_0402_1%

RC136 60.4_0402_1%@

RC98 10M_0402_5%

32.768KHZ_9PF_ X1A000141000200

Change PN to SJ10000Q400

1

2

PCH internal PU

1 2

RC111 100K_0402_5%@

EC intern al PU

1 2

RC106 10K_0402_5%@

1 2

RC103 10K_0402_5%

Default : GPI

RC115 10K_0402_5%@

1 2

GND

4

1 2

1 2

1 2

YC2

1 2

CC16

8.2P_0402_50V8D

1

1

GND

2

+1.0VALW_CLK5_F24NS

12

15P_0402_50V8 J

12

1

2

+3VALW_DSW

+3VALW_PRIM

CC13

#543016 PDG2.0 P.599

PROCPWR GD is used only f or power seq uence

debug and is not required to be connected to

anything on the plat f or m .

A

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Secur ity Cla ssifica tion

Issued Da te

Issued Da te

Issued Da te

THIS SHEE T OF EN GINEE RING DRAW ING IS THE PROP RIETARY PROP ERTY OF COMPAL ELEC TRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEE T OF EN GINEE RING DRAW ING IS THE PROP RIETARY PROP ERTY OF COMPAL ELEC TRONICS, INC. AND C ONTAINS CONFIDENTIAL

THIS SHEE T OF EN GINEE RING DRAW ING IS THE PROP RIETARY PROP ERTY OF COMPAL ELEC TRONICS, INC. AND C ONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION I T CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION I T CONTAINS

DEPARTMENT EXCEP T AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NO R THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCL OSED TO ANY THIRD P ARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCL OSED TO ANY THIRD P ARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B