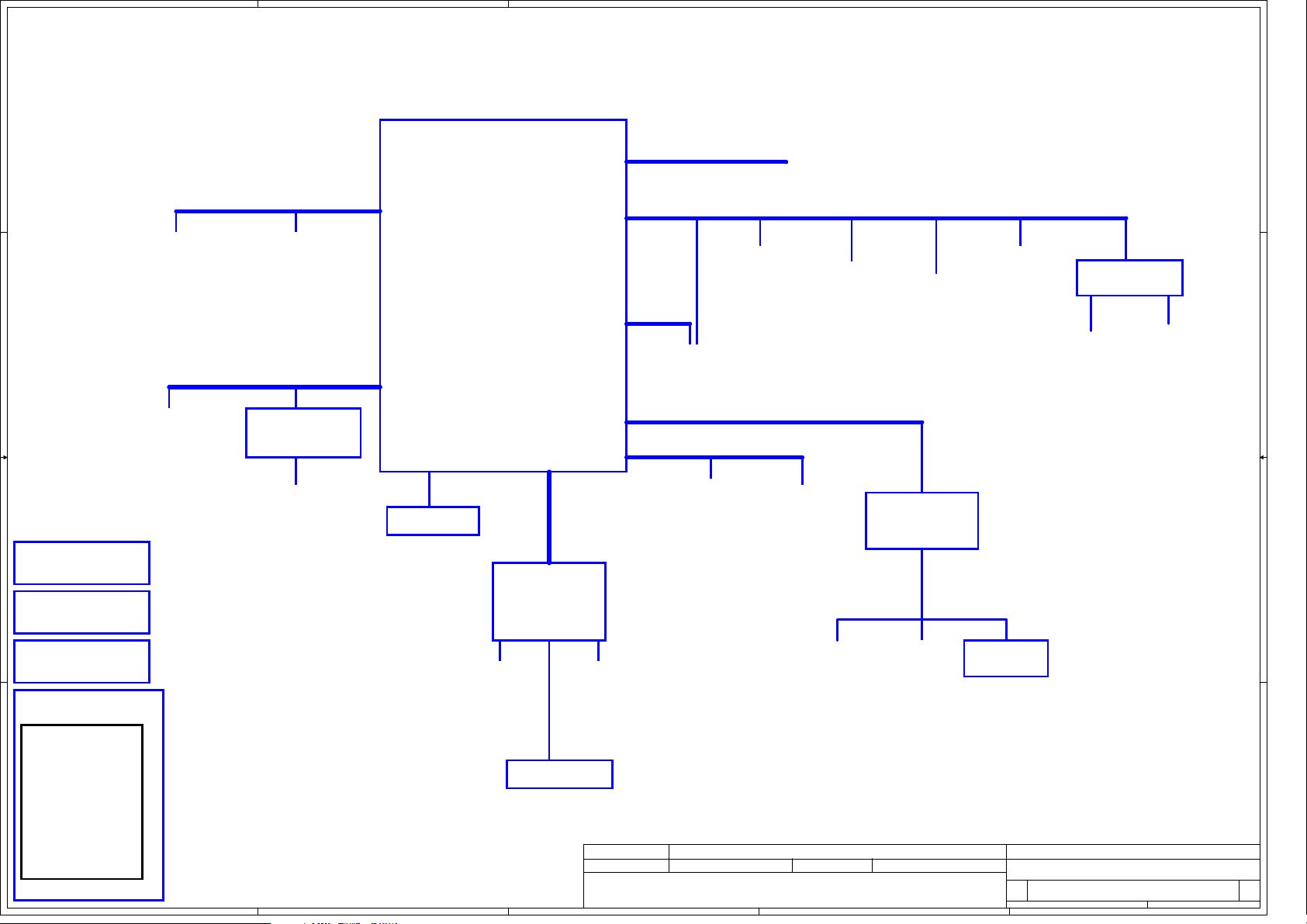

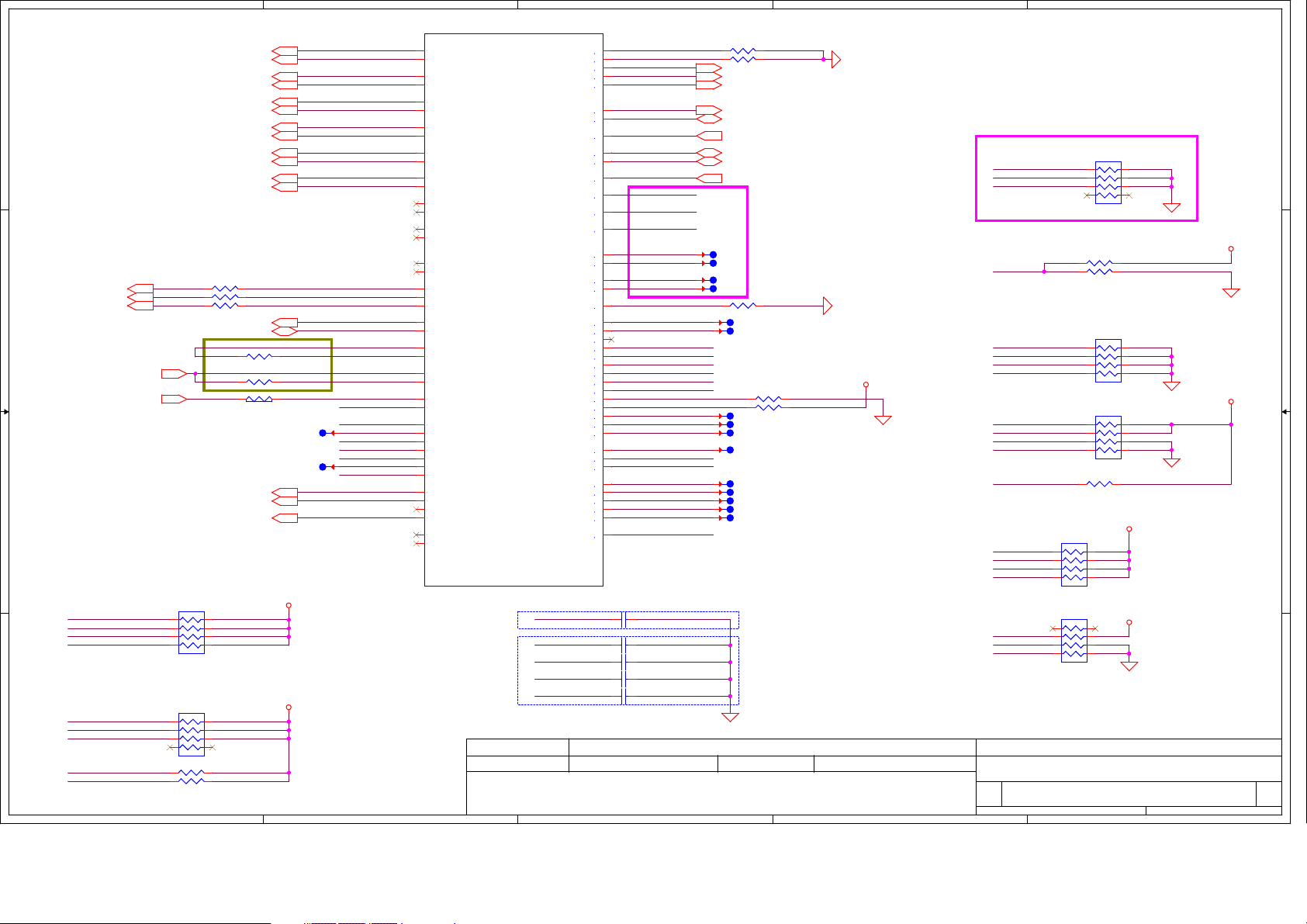

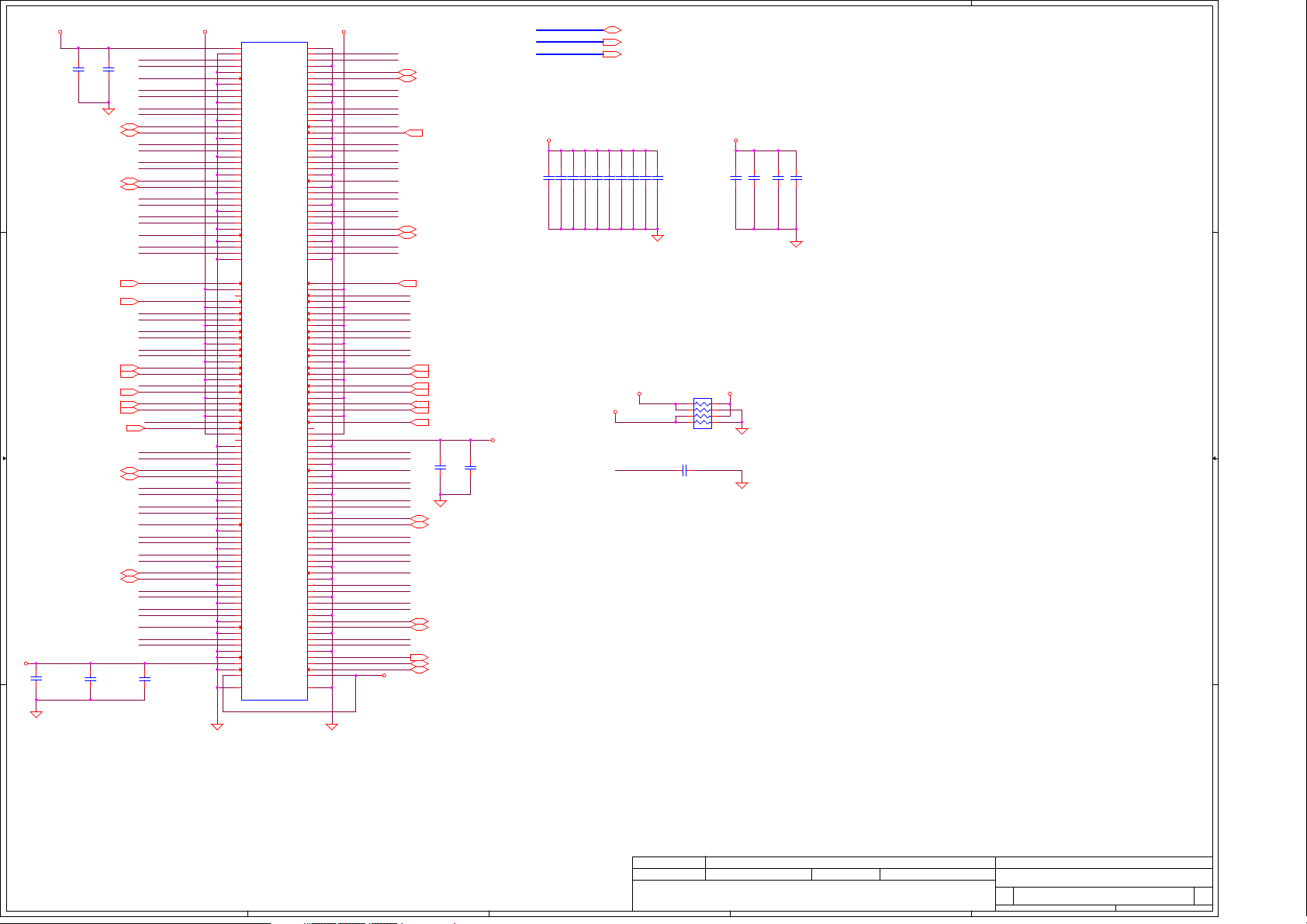

Acer Aspire ES1-521, Aspire ES1-522 Schematics

A

B C D

E

Com

1 1

2 2

pal Confidential

Mod

el Name : Bellemere_BE

Com

pal Project Name : B5W1E

File Name : LA-D121P

Comp

al Confidential

B5W1E Schematics Document

AM

AM

D "Beema" Platform

D 15W APU With Puma+ Core

3 3

LA-D121P REV: 1.0

2015-04-16

4 4

Sec

Sec

Sec

urity Classification

urity Classification

urity Classification

ued Date

ued Date

ued Date

Iss

Iss

Iss

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

A

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

2014/03/27 2016/03/27

2014/03/27 2016/03/27

2014/03/27 2016/03/27

Com

Com

Com

pal Secret Data

pal Secret Data

pal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Co

Co

Co

mpal Electronics, Inc.

mpal Electronics, Inc.

le

le

le

Tit

Tit

Tit

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

mpal Electronics, Inc.

CO

CO

CO

B5W

B5W

uesday, April 21, 2015

uesday, April 21, 2015

uesday, April 21, 2015

B5W

ER PAGE

ER PAGE

ER PAGE

V

V

V

1E_LA-D121P

1E_LA-D121P

1E_LA-D121P

133T

133T

133T

E

1.0

1.0

1.0

A

B

C

D

E

Com

1 1

pal Confidential

Mod

el Name : B5W1E

5W1K

B

B

5W1R

Display Port

Port 0Port 1

AMD

Beema/

Kabini/

Memory BUS(DDR3) Single Channel

1.5V

DDRIII 1600MHz

USB2.0

or

t 8

P

204pin

DDR3-SO-DIMM X2

Page 10,11

or

t 2

P

or

t 3Port 0

P

or

t 5

P

Carrizo-L

Sub B

HDMI

Conn.

Page 13

2 2

MIN

I Card

(WLAN/BT)

Page 17

Fan

Control

3 3

DC/

DC Interface CKT.

r Circuit DC/DC

Powe

Sub B

B471P

LS-

Page

oard

Page 22

Page

24

24~33

eDP Conn.

LAN

(GbE)

RTL

Tra

RJ45

Pag

e 12

GPP

8111GUS

Page 15

nsformer

Page 15

AMD

FT3b APU

USB3.0

Por

MB 2.0 Conn.

t 0

BT M

Pag

e 19 Page 17 Page 12 Page 12

ini Card

USB

Camera

Touch Screen

Puma+ Core

PCIE

1GPP2

BGA 769-balls

SPI L

PC

Page

5~9

HD Audio(AZ)

SATA III

BIOS (8M)

8

Page

HDD Conn.

ENE

U3.

0 Conn.

Page 19

Por

t 0 Port 1

Pag

e 18

ODD C

onn.

Pag

e 18

Audio

ALC233-VB2

Page

USB

16

KBC9022

Page 14

Un

versal Jack

i

Touch PadInt.KBD

Page 20Page 20

Page 16

Int

. Speaker

Conn.

Page 16

Ana

log MIC

Page

16

oard

Port 1

2.0 Conn.

LS-B471P

Card Reader

RTS5170

SD only

Pag

Port 4

e 19

s

crete TPM

Card Reader

RTS5170

4 4

2 in 1 (

SD)

2.0

USB

conn x1

USB

port 2

P.21

A

B

Di

Page 20

Sec

Sec

Sec

urity Classification

urity Classification

urity Classification

ued Date

ued Date

ued Date

Iss

Iss

Iss

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

C

2014/03/27 2016/03/27

2014/03/27 2016/03/27

2014/03/27 2016/03/27

Com

Com

Com

pal Secret Data

pal Secret Data

pal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Co

Co

Co

mpal Electronics, Inc.

mpal Electronics, Inc.

le

le

le

Tit

Tit

Tit

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Cus

Cus

Cus

tom

tom

tom

Date: Sheet of

Date: Sheet of

Date: Sheet of

mpal Electronics, Inc.

BL

BL

BL

CK DIAGRAMS

CK DIAGRAMS

CK DIAGRAMS

O

O

O

1E_LA-D121P

1E_LA-D121P

1E_LA-D121P

B5W

B5W

B5W

233Thursday, April 16, 2015

233Thursday, April 16, 2015

E

233Thursday, April 16, 2015

1.0

1.0

1.0

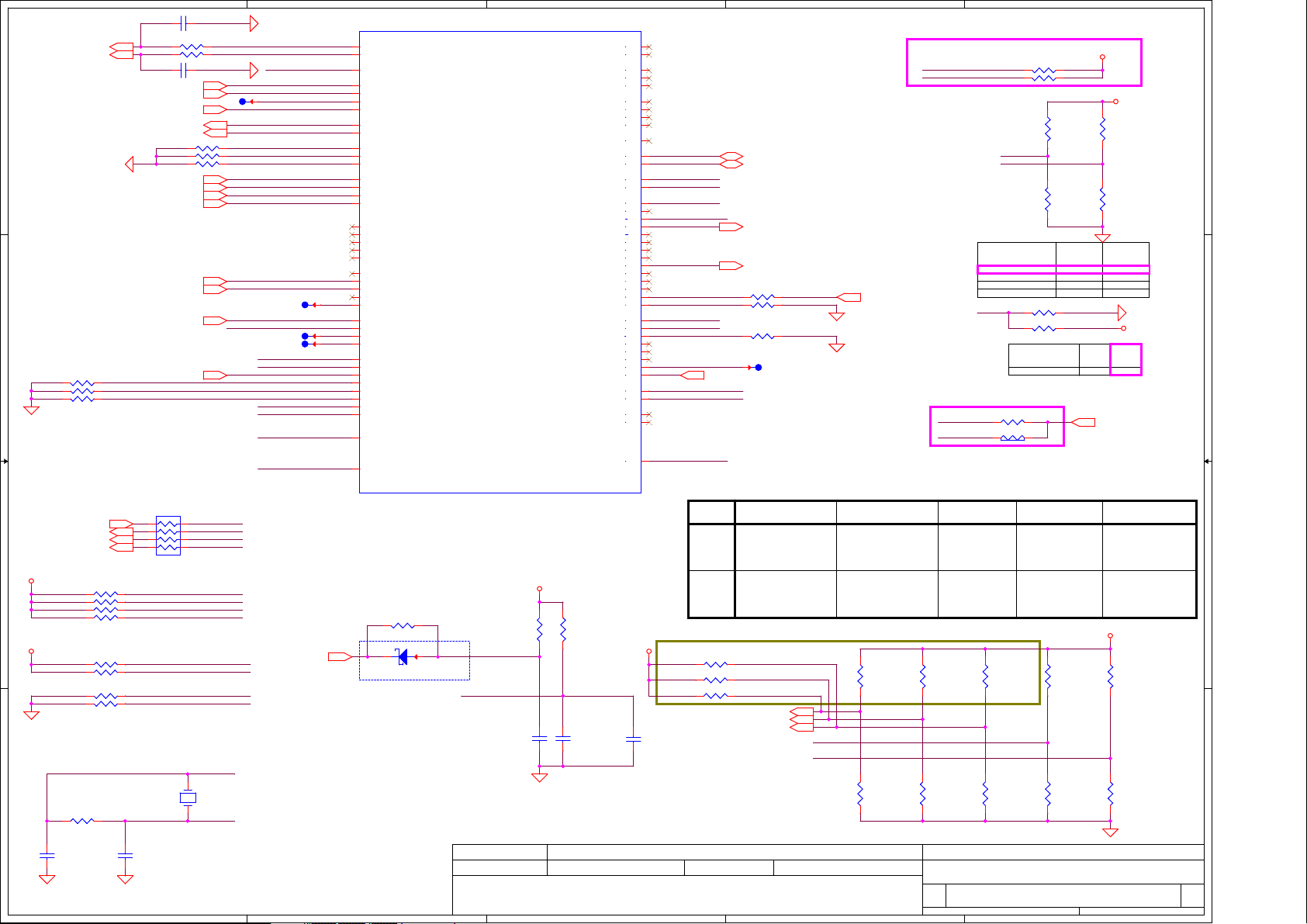

5

D D

AC ADAPTOR

19V 65W

VIN

PU301

CHARGER

BQ24725ARGRR

BAT

T+

BAT

TERY

HDMI

+5V

C C

B B

S_DISP

1

HDD x

ODD x1

S_HDD @ 1.1A

+5V

+5VS_ODD @ 2A

io

Aud

ALC233-VB2-CG

+AVDD1_HDA

+PVDD_HDA

+3VS_DVDD

+1.5VS_VDDA

+1.5VS_DVDDIO

FAN

+VCC_FAN1

USB2.0 x1

USB3.0 x1

+USB3_VCCA

+5VS

+5VS

+5VS

+3VS

+1.5VS

+5VS

+5VALW

EC

+EC_VCC

panel

LCD

14"

+INVPWR_B+

+LCDVDD @ 1.4A

+3VLP

+19VB

+3VS

4

VB

+19

PU1000

8880CGQW

RT

PU501

8207PGQW

RT

PU601

SY8288RAC

PU401

SY8286BRAC

3

+1.5V

+0.75VS

+0.95VALW

PU602

SY8003DFC

+3VALW

+5VALW

DDRIII SODIMMX2

RAM

5V

+1.

+0.75VS

+APU_CORE

+APU_CORE_NB

+1.8VALW

U2

EM5209VF

VDD_MEM 8A

VTT_MEM 2A

U4

304L

AO4

U3

EM5209VF

+3VS

+5VS

2

+1.8VS

+1.5VS

+0.95VS

AMD

APU FT3b Beema (15W )

+0

5~+1.4V

.

+0.

7~1.325V

+1.5V

VDDCR_CPU @ 21A(EDC)

VDDCR_NB @ 17A(EDC)

VDDIO_MEM_S @ 3A

VDDIO_AZ_ALW @ 0.1A+1.5VS

+0.95VALW

+0.95VS

+1.8VS

+1.8VALW

+3VALW

VDD_095_USB3_Dual @ 1A

VDD_095_ALW @ 0.5A

VDD

_095 @ 5A

VDD_095_GFX @ 0.6A

VDD_18 @ 1.5A

VDD_18_ALW @ 0.5A

VDD_33_ALW @ 0.2A

+3VS VDD_33 @ 0.2A

1

+1.5V_RTC VDDBT_RTC_G @ 4.5uA

PU402

SY8286CRAC

+RTC_APU

PU101

AP

2138N-1.5TRG1

+RTCCONN

RTC

Bettary

/CR Combo

LAN

RTL8411B-CG

+3V

A A

_LAN @ 1A

Card(WLAN)

M.2

S_WLAN @ 2A

+3V

+3VALW

+3VALW

5

HD Camera

+3V

S_CMOS

ch Screen

Tou

S_TS

+5V

+3VS

+5VS

Security Classificati on

Security Classificati on

Security Classificati on

Issued Date

Issued Date

Issued Date

S SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

S SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

S SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THI

THI

THI

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

2014/03/27 2016/03/27

2014/03/27 2016/03/27

2014/03/27 2016/03/27

3

Com

Com

Com

pal Secret Data

pal Secret Data

pal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Co

Co

Co

pal Electronics, Inc.

pal Electronics, Inc.

pal Electronics, Inc.

m

m

le

le

le

Tit

Tit

Tit

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

m

POW

POW

POW

B5W

B5W

B5W

ursday, April 16, 2015

ursday, April 16, 2015

ursday, April 16, 2015

ER MAP

ER MAP

ER MAP

1E_LA-D121P

1E_LA-D121P

1E_LA-D121P

1

1.0

1.0

1.0

333Th

333Th

333Th

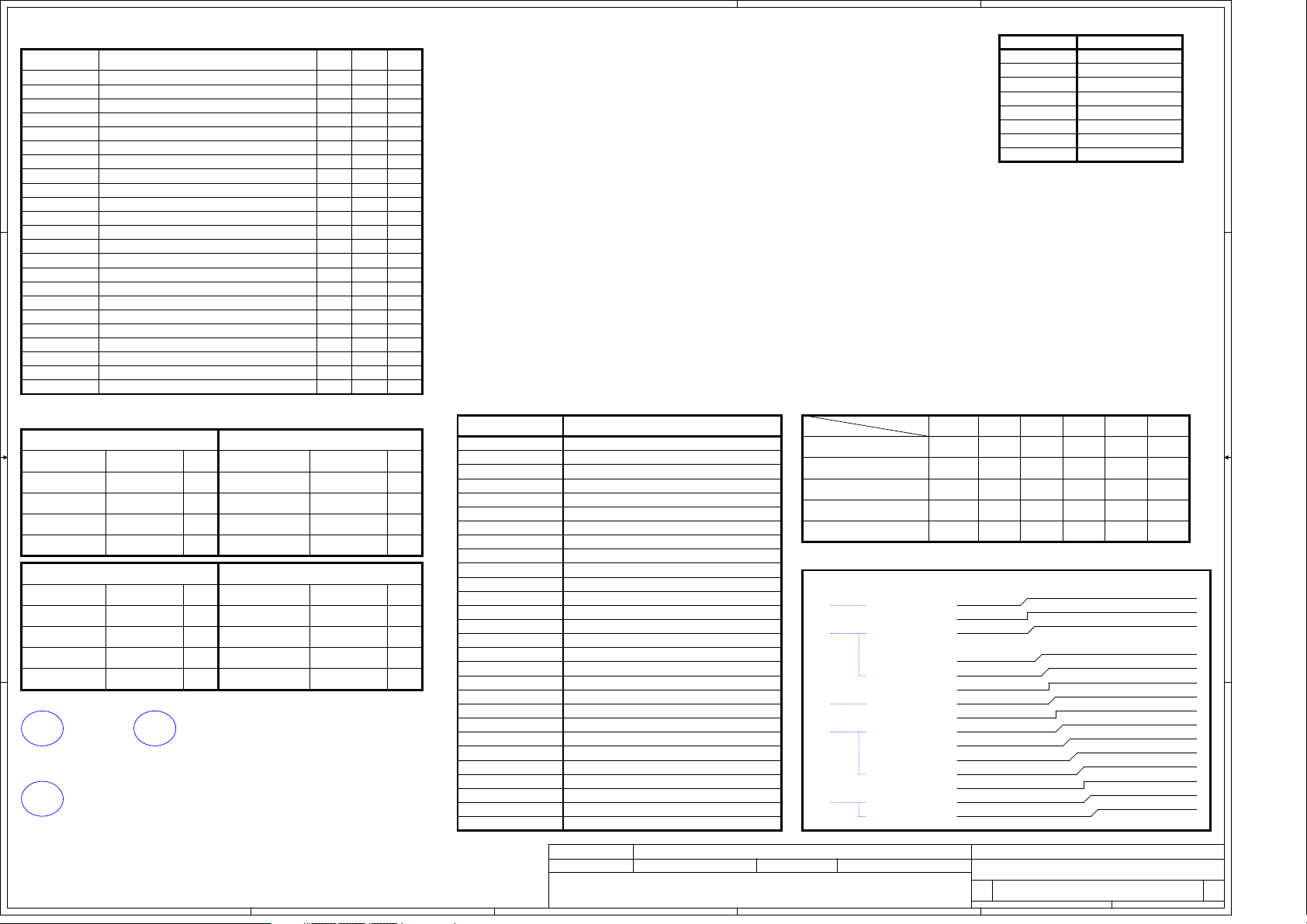

A

tage Rails

Vol

VIN

B+

+AP

U_CORE OFFON

1 1

+0.95VALW

+0.95VS

+1.8VALW

+1.8VS

+1.5V

+1.5VS

+3VALW

+3V

S

+5VALW ON

+5VS

+RTC_APU

2 2

us List

SMB

EC

SMBus Port1 (+3VALW)

rt Battery

Sma

3 3

4 4

SMBus Port0 (+3VS)

APU

DDR DI

MM1

DDR DI

MM2

ZZZ

PC

B

t Number = DAZ1GS00100

Par

PCB B5W1E LA-D121P LS-D121P

ZZZ

HDMI_ROYALTY

ROY

ALTY HDMI W/LOGO+HDCP

RO0

000003HM

45@

DescriptionPower Plane

Adapte r power supply (19V)

AC or batter y power rail fo r power circuit .

Core voltage f or APU

Vol

tage for On-die VGA of APU OFFOFFON+APU_CORE_NB

0.95V always on power rail

0.95V switched power rail

1.8V always on power rail

1.8V switched power rail

1.5V power rail for APU and DDR

1.5V switched power rail

0.75V switched power rail for DDR terminator

3.3V always on power rail

3.3V switched power rail

5V always on power rail

5V switched power rail

RTC power

EC

SMBus Port2 (+3VS)

ice HEXAddres s

Dev

HEXAddres sDevice

b

0001 011X

Add

ressDevice

1010 000X

1010 001X

U44

EC

t Number = SA000075S30

Par

S IC KB9022QD LQFP 128P EC CONTROLLER

A

16H

HEX

b

A0

b

A2H

9022@

SI (APU)

SB-T

SMBus Port1(+3VALW)

APU

Dev

ice Address

H

1001 100X

B C D

Boa

rd ID / SKU ID Table for AD channel

S5S3S0

ONONON

ON ON

ON

ON

ON+0.75VS

ON OFFOFF

OFF

ONON

ON

OFFON

OFF

ON ON

OFFOFFON

ON OFFON

OFFON OFF

OFF OFF

ON

ONON

OFFOFFON

ONON

ONONON

Structure Table

BOM

BTO ItemBOM Structure

@

CONN@

b

98H

KBN@

BMA@

CZL@

233@

255@

283@

EMC@

@EMC@

SP@

HEX

HDT@

RS@

45@

9012@

9022@

BL@

TPM@

ECI2C@

TPUSB@

BYOC@

NBYOC@

JP@

TP@

Unpop

Connector part control by ME

Stuff when use Kabini APU

Stuff when use Beema APU

Stuff when use CZ-L APU

Use for Audio Codec ALC233-VB2

Use for Audio Codec ALC255

Use for Audio Codec ALC283

EMI pop component

EMI unpop component

Short pad for clear CMOS

HDT+ for test phase, MP remove

R-short

HDMI royalty

Use KBC9012

Use KBC9022

Keyboard backlight

Use discrete TPM module

Use EC I2C T/P

Use USB to I2C IC for T/P

Stuff when support BYOC

Stuff when non-support BYOC

Jump

Test point

Sec

Sec

Sec

urity Classification

urity Classification

urity Classification

ued Date

ued Date

ued Date

Iss

Iss

Iss

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE C OMPETENT DIVISION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRON ICS, INC.

2014/03/27 2016/03/27

2014/03/27 2016/03/27

2014/03/27 2016/03/27

Com

Com

Com

pal Secret Data

pal Secret Data

pal Secret Data

STATE

SIGNAL

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

APU POWER SEQUENCE

G-A

G-B

G-C

G-D

G-E

Deciphered Date

Deciphered Date

Deciphered Date

+RTC

EC_ON

+3VALW/+5VALW

+1.8VALW

+0.95VALW

SYSON

+1.5V

SUSP#

+3VS

+1.8VS

+1.5VS

+0.95VS

VR_ON

+APU_CORE

+APU_CORE_NB

D

E

BOARD

Board ID

ID Table

12

13

14*

15

PCB Revision

EVT

DVT

PVT

Pre-MP

16

17

18

19

SLP_S3#

HIGH HIGH

LOW

LOW

LOWS5 (Soft OFF)

re check

Tit

Tit

Tit

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

+VALWSLP_S5# +VS+V Clock

ON

HIGHHIGH

HIGH

HIGH

le

le

le

ON

ON

ON

ON

ON

ON

OFF

ONLOW

OFF

Co

Co

Co

mpal Electronics, Inc.

mpal Electronics, Inc.

mpal Electronics, Inc.

NO

NO

NO

B5W

B5W

uesday, April 21, 2015

uesday, April 21, 2015

uesday, April 21, 2015

B5W

ON

OFF

OFF

OFF

ES LIST

ES LIST

ES LIST

T

T

T

1E_LA-D121P

1E_LA-D121P

1E_LA-D121P

E

ONON

LOW

OFF

OFF

OFF

1.0

1.0

433T

433T

433T

1.0

5

@

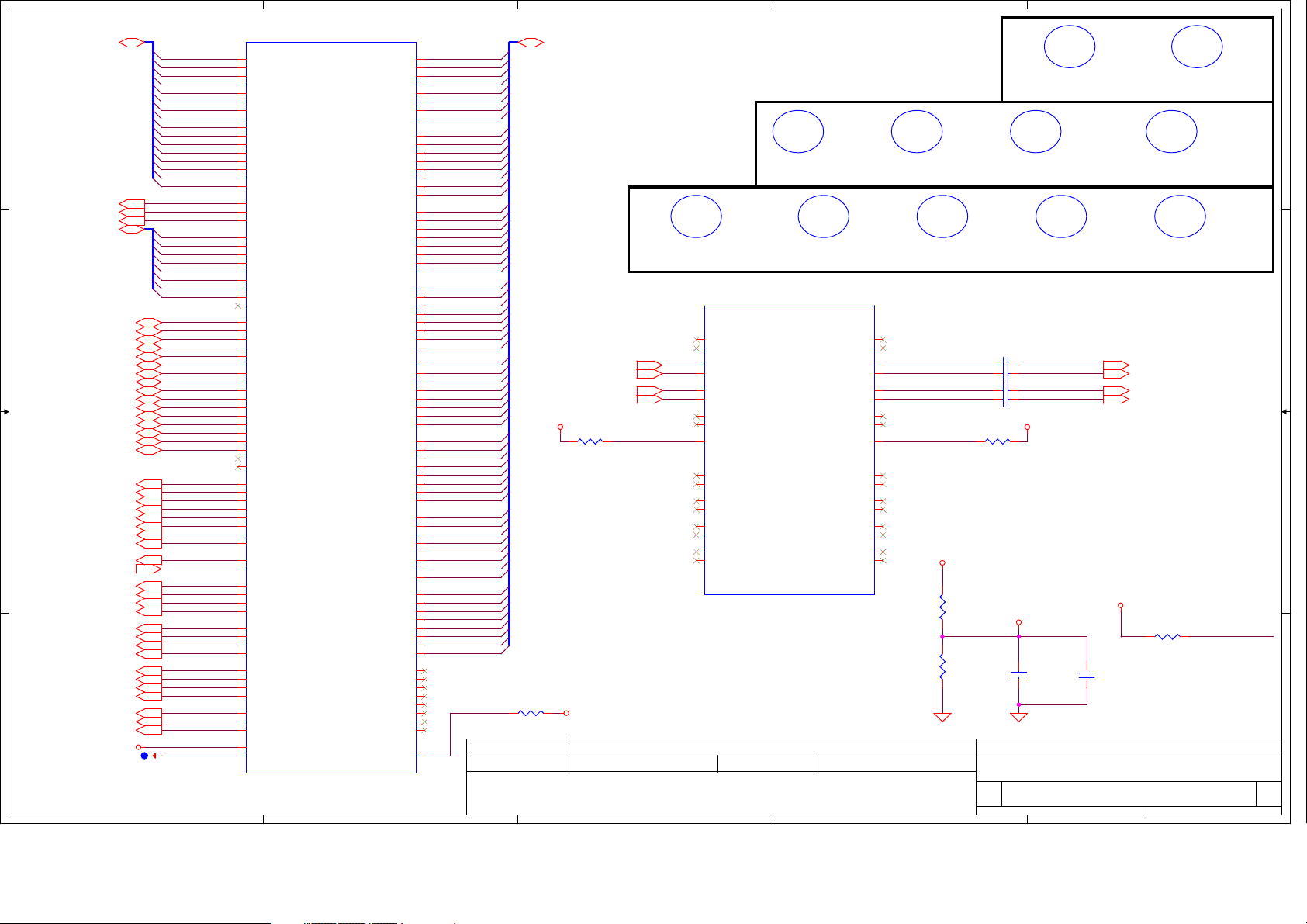

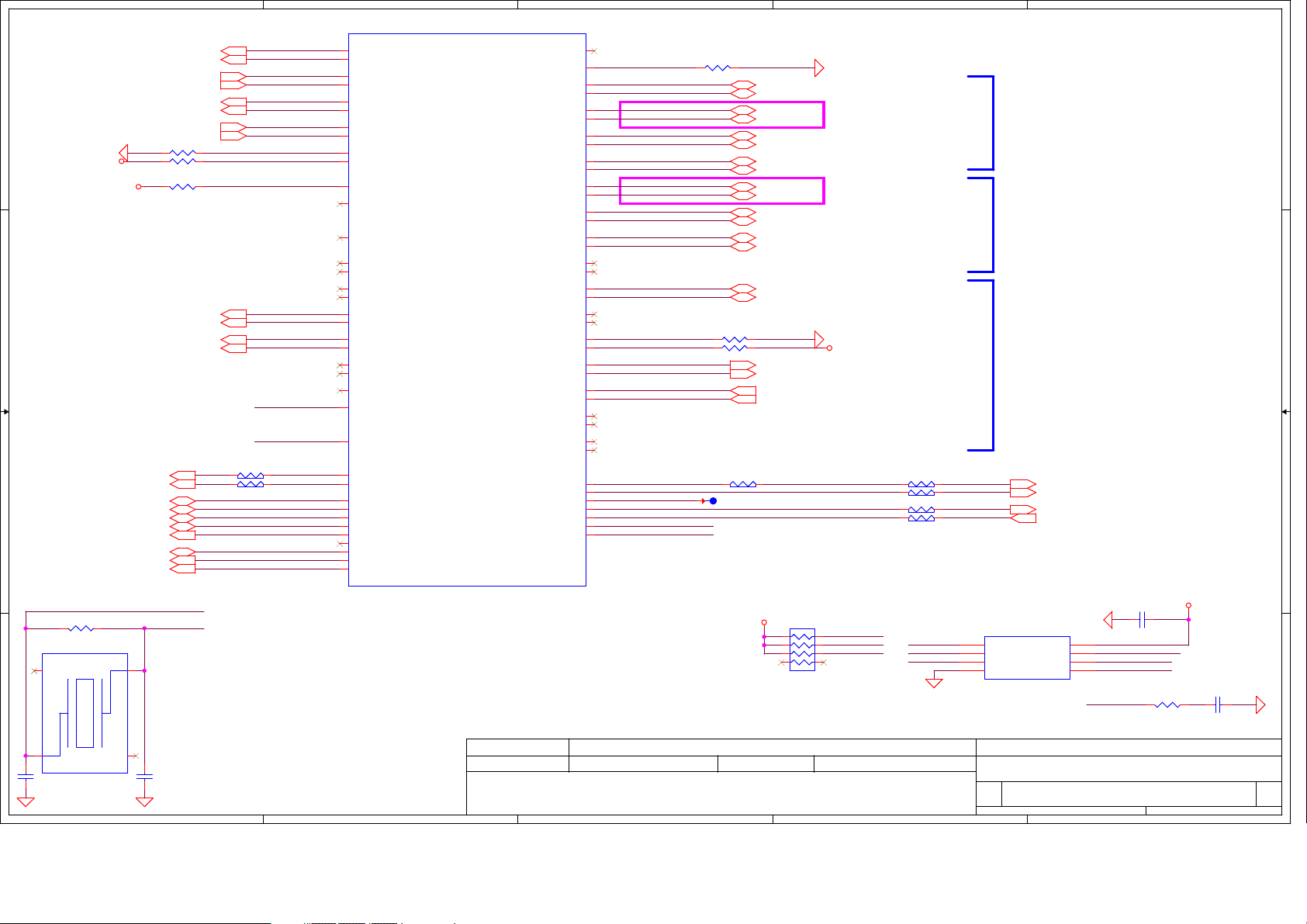

U1A

_SMA[15..0]<10,11>

DDRAB

D D

_SBS0#<10,11>

DDRAB

_SBS1#<10,11>

DDRAB

DDRAB

_SBS2#<10,11>

DDRAB

_SDM[7..0]<10,11>

C C

B B

A A

MEM_

MEM_

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRA

DDRAB

DDRAB

DDRAB_SDQS6<10,11>

DDRAB

DDRAB

DDRAB

DDRA_

DDRA_

DDRA_CLK1<10>

DDRA_

DDRB_

DDRB

DDRB_

DDRB_

MAB_RST #<10,11>

MAB_EVEN T#<10,11>

DDRA_

DDRA_

DDRB

DDRB_

DDRA_

DDRA_

DDRB_

DDRB_

DDRA_

DDRA_

DDRB_

DDRB_

DDRAB

DDRAB

DDRAB

+ME

_SDQS0<10,11>

_SDQS0#<10,11>

_SDQS1<10,11>

_SDQS1#<10,11>

_SDQS2<10,11>

_SDQS2#<10,11>

_SDQS3<10,11>

_SDQS3#<10,11>

_SDQS4<10,11>

B

_SDQS4#<10,11>

_SDQS5<10,11>

_SDQS5#<10,11>

_SDQS6#<10,11>

_SDQS7<10,11>

_SDQS7#<10,11>

CLK0<10>

CLK0#<10>

CLK1#<10>

CLK0<11>

_

CLK0#<11>

CLK1<11>

CLK1#<11>

CKE0<10>

CKE1<10>

_

CKE0<11>

CKE1<11>

ODT0<10>

ODT1<10>

ODT0<11>

ODT1<11>

SCS0#<10>

SCS1#<10>

SCS0#<11>

SCS1#<11>

_SRAS#<10,11>

_SCAS#<10,11>

_SWE#<10,11>

M_VREF

T33

5

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

DDRAB

APU_

_SMA0

_SMA1

_SMA2

_SMA3

_SMA4

_SMA5

_SMA6

_SMA7

_SMA8

_SMA9

_SMA10

_SMA11

_SMA12

_SMA13

_SMA14

_SMA15

_SDM0

_SDM1

_SDM2

_SDM3

_SDM4

_SDM5

_SDM6

_SDM7

VREFDQ

UAP

AG3

8

W35

W38

W34

U38

U37

U34

R35

R38

N38

AG3

4

R34

N37

AN34

L38

L35

8

AJ3

AG3

5

N34

B32

B38

G40

N41

AG4

0

1

AN4

0

AY4

AY3

4

Y40

B33

A33

B40

A40

H41

H40

P41

P40

AH4

1

AH4

0

AP41

AP40

BA40

AY4

1

AY3

3

BA34

AA40

Y41

AC3

5

4

AC3

AA34

AA32

AE38

AE37

AA37

AA38

G38

AE34

L34

J38

J37

J34

8

AN3

AU3

8

AN3

7

AR3

7

4

AJ3

AR3

8

AL3

8

AN3

5

7

AJ3

AL3

4

AL3

5

0

AD4

8

AC3

FT3_BGA_769P-T

Part Number =

M_ADD0

ADD1

M_

ADD2

M_

M_

ADD3

M_

ADD4

M_

ADD5

ADD6

M_

ADD7

M_

M_

ADD8

M_

ADD9

M_ADD1 0

ADD11

M_

ADD12

M_

M_ADD1 3

M_A

DD14

M_A

DD15

M_BANK0

M_BANK1

M_

BANK2

DM0

M_

DM1

M_

M_

DM2

M_

DM3

M_DM4

M_DM5

M_DM6

M_DM7

M_

DM8

DQS_H 0

M_

DQS_L 0

M_

M_

DQS_H 1

M_

DQS_L 1

M_

DQS_H 2

DQS_L 2

M_

DQS_H 3

M_

M_

DQS_L 3

M_DQS_ H4

M_DQS_ L4

DQS_H 5

M_

DQS_L 5

M_

M_

DQS_H 6

M_DQS_ L6

M_DQS_ H7

DQS_L 7

M_

DQS_H 8

M_

M_

DQS_L 8

M_CLK_ H0

M_CLK_ L0

CLK_H 1

M_

M_

CLK_L 1

M_

CLK_H 2

M_

CLK_L 2

CLK_H 3

M_

CLK_L 3

M_

M_

RESET _L

M_

EVENT _L

CKE0

M0_

M0

_CKE1

M1

_CKE0

M1

_CKE1

M0_ODT 0

M0_ODT 1

M1_ODT 0

M1_ODT 1

M0_CS_ L0

M0_CS_ L1

M1_CS_ L0

M1_CS_ L1

M_RAS_ L

M_CAS_ L

M_WE_ L

M_VREF

M_VREFD Q

MEMO

RY

M_ZVDD IO_MEM_S

4

M_

DATA0

DATA1

M_

DATA2

M_

M_

DATA3

M_

DATA4

M_

DATA5

DATA6

M_

DATA7

M_

M_

DATA8

M_

DATA9

DATA1 0

M_

DATA1 1

M_

M_DAT A12

M_

DATA1 3

M_

DATA1 4

M_

DATA1 5

M_

DATA1 6

M_

DATA1 7

M_

DATA1 8

DATA1 9

M_

DATA2 0

M_

M_

DATA2 1

M_

DATA2 2

M_

DATA2 3

DATA2 4

M_

M_

DATA2 5

M_

DATA2 6

M_

DATA2 7

M_

ATA28

D

DATA2 9

M_

M_

DATA3 0

M_

DATA3 1

M_DAT A32

M_DAT A33

M_

DATA3 4

M_

DATA3 5

M_

DATA3 6

DATA3 7

M_

M_DAT A38

M_DAT A39

M_DAT A40

M_DAT A41

M_DAT A42

M_DAT A43

M_DAT A44

M_DAT A45

M_DAT A46

M_DAT A47

M_

DATA4 8

M_DAT A49

DATA5 0

M_

M_DAT A51

M_DAT A52

M_

DATA5 3

M_DAT A54

M_DAT A55

M_

DATA5 6

M_DAT A57

M_

DATA5 8

M_DAT A59

DATA6 0

M_

M_DAT A61

M_

DATA6 2

M_DAT A63

CHECK 0

M_

M_

CHECK 1

M_

CHECK 2

M_CHEC K3

CHECK 4

M_

CHECK 5

M_

M_

CHECK 6

M_

CHECK 7

4

B30

A32

B35

A36

B29

A30

A34

B34

B37

A38

D40

D41

B36

A37

B41

C4

F40

F41

K40

K41

E40

E41

J40

J41

M41

N40

T41

U40

L40

M40

R40

T40

AF4

AF4

AK40

AK41

AE40

AE41

AJ4

AJ4

AM4

AN4

AT4

AU4

AL4

AM4

AR4

AT4

AV41

AW4

BA38

AY3

AU4

AV40

AY3

AY3

BA36

AY3

BA32

AY3

BA37

AY3

BA33

AY3

V41

W40

AB40

AC4

U41

V40

AA41

AB41

AD4

3

_SDQ[63..0] <10,11>

1 2

R74

39.

2_0402_1%

DDRAB

Beema

E_ARX_DTX_P1<15>

PCI

E_ARX_DTX_N1<15>

PCI

PCI

E_ARX_DTX_P2<17>

I

E_ARX_DTX_N2<17>

PC

95VS

+0.

1 2

R40

1.69K_0402_1%

+1.

UAP

U1

CZ-L

AM7210ITJ44JB 1.8G BG A 769P

A4_7210@

SA00008R420

UAP

U1

EM6010IUJ23JB 1.35G BG A 769P

E1_6010@

SA00007RC20

@

UAP

U1B

R10

P_

GPP_RXP0

R8

P_G

PP_RXN0

R5

P_

PP_RXP1

G

R4

PP_RXN1

P_G

N5

P_G

PP_RXP2

N4

P_G

PP_RXN2

N10

GPP_RXP3

P_

N8

P_G

PP_RXN3

X_ZVDD_095

P_T

4

5V

2014/03/27 2016/03/27

2014/03/27 2016/03/27

2014/03/27 2016/03/27

W8

P_T

X_ZVDD_095

L5

P_G

FX_RXP0

L4

G

FX_RXN0

P_

J5

FX_RXP1

P_G

J4

P_G

FX_RXN1

G5

G

FX_RXP2

P_

G4

FX_RXN2

P_G

D7

P_G

FX_RXP3

E7

P_G

FX_RXN3

FT3_BGA_769P-T

Part Number =

Com

Com

Com

pal Secret Data

pal Secret Data

pal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

3

UAP

U1

EM6110ITJ44JB 1.5G BG A 769P

E2_6110@

SA00007RB20

E

PCI

P_G

P_G

P_

LAN

WLAN

P_G

P_G

P_

P_G

P_G

R

X_ZVDD_095

P_

P_G

P_

P_G

P_G

P_

P_G

P_G

P_G

G

G

PP_TXP0

PP_TXN0

PP_TXP1

PP_TXN1

PP_TXP2

PP_TXN2

PP_TXP3

PP_TXN3

FX_TXP0

G

FX_TXN0

FX_TXP1

FX_TXN1

G

FX_TXP2

FX_TXN2

FX_TXP3

FX_TXN3

L2

L1

K2

K1

J2

J1

H2

H1

W7

G2

G1

F2

F1

E2

E1

D2

D1

_SDQ0

DDRAB

DDRAB

_SDQ1

DDRAB

_SDQ2

_SDQ3

DDRAB

_SDQ4

DDRAB

_SDQ5

DDRAB

DDRAB

_SDQ6

DDRAB

_SDQ7

_SDQ8

DDRAB

_SDQ9

DDRAB

DDRAB

_SDQ10

DDRAB

_SDQ11

_SDQ12

DDRAB

_SDQ13

DDRAB

_SDQ14

DDRAB

0

DDRAB

_SDQ15

_SDQ16

DDRAB

_SDQ17

DDRAB

_SDQ18

DDRAB

DDRAB

_SDQ19

DDRAB

_SDQ20

_SDQ21

DDRAB

_SDQ22

DDRAB

_SDQ23

DDRAB

DDRAB

_SDQ24

_SDQ25

DDRAB

_SDQ26

DDRAB

_SDQ27

DDRAB

DDRAB

_SDQ28

DDRAB

_SDQ29

_SDQ30

DDRAB

_SDQ31

DDRAB

0

DDRAB

_SDQ32

1

DDRAB

_SDQ33

_SDQ34

DDRAB

_SDQ35

DDRAB

_SDQ36

DDRAB

DDRAB

_SDQ37

0

DDRAB

_SDQ38

1

_SDQ39

DDRAB

1

_SDQ40

DDRAB

0

DDRAB

_SDQ41

1

DDRAB

_SDQ42

0

_SDQ43

DDRAB

0

_SDQ44

DDRAB

0

_SDQ45

DDRAB

0

DDRAB

_SDQ46

0

DDRAB

_SDQ47

_SDQ48

DDRAB

0

_SDQ49

DDRAB

DDRAB

_SDQ50

7

DDRAB

_SDQ51

1

_SDQ52

DDRAB

_SDQ53

DDRAB

9

_SDQ54

DDRAB

8

DDRAB

_SDQ55

_SDQ56

DDRAB

5

_SDQ57

DDRAB

_SDQ58

DDRAB

1

DDRAB

_SDQ59

DDRAB

_SDQ60

6

_SDQ61

DDRAB

_SDQ62

DDRAB

2

_SDQ63

DDRAB

0

VDDIO

M_Z

Security Classificati on

Security Classificati on

Security Classificati on

1

Issued Date

Issued Date

Issued Date

S SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

S SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

S SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THI

THI

THI

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

KABINI

UAP

U1

AM7310ITJ44JB 2G FC BGA 769P

A6_7310@

SA00008K930

UAP

U1

AM6210ITJ44JB 1.8G BG A 769P

A4_6210@

SA00007RA20

PCI

E_ATX_DRX_P1

PCI

E_ATX_DRX_N1

E_ATX_DRX_P2

PCI

E_ATX_DRX_N2

PCI

X_ZVDD_095

P_R

+1.5V

2

12

12

1 2

9 .

C1

1 2

C20 .

1 2

C17 .

1 2

C18 .

R73

1K

_0402_1%

R75

1K

_0402_1%

R76

_0402_1%

1K

le

le

le

Tit

Tit

Tit

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

UAP

U1

EM2100CJ23HM 1G BGA7 69

E1_2100@

SA00

006QX70

UAP

U1

AM7410ITJ44JB 2.2G F CBGA 769P

A8_7410@

SA00008K660

UAP

U1

AM6310ITJ44JB 1.8G BG A 769P

A6_6310@

SA00007R920

1U_0402_16V7K

1U_0402_16V7K

1U_0402_16V7K

1U_0402_16V7K

95VS

+0.

12

UAP

EM2500BJ23HM 1.4G BGA

E1_2500@

SA00

UAP

U1

EM7110ITJ44JB 1.8G F CBGA 769P

E2_7110@

SA00008MA20

UAP

U1

AM6410ITJ44JB 2G BGA 7 69P

A8_6410@

SA00007TQ80

E_ATX_C_DRX_ P1 <15>

PCI

E_ATX_C_DRX_ N1 <15>

PCI

PCI

E_ATX_C_DRX_ P2 <17>

I

E_ATX_C_DRX_ N2 <17>

PC

MEMORY VREF

+1.

5V

+ME

M_VREF

7

R7

1K

1

C33

7

1U_0402_6.3V6K

2

P05

P05

P05

B5W

B5W

B5W

ursday, April 16, 2015

ursday, April 16, 2015

ursday, April 16, 2015

2

C16

3

.1U_0402_1 6V7K

1

Co

Co

Co

pal Electronics, Inc.

pal Electronics, Inc.

pal Electronics, Inc.

m

m

m

-FT3 MEMORY INTERFACE/PCIE

-FT3 MEMORY INTERFACE/PCIE

-FT3 MEMORY INTERFACE/PCIE

1E_LA-D121P

1E_LA-D121P

1E_LA-D121P

_0402_1%

1

U1

006R670

12

MEM_

533Th

533Th

533Th

MAB_EVEN T#

1.0

1.0

1.0

A

APU_

DP1_P0<13>

APU_

DP1_N0<13>

DP1_P1<13>

APU_

DP1_N1<13>

HDMI

1 1

eD

P

SVT<30>

APU_

SVC<30>

APU_

APU_

APU_

EC_

APU_

EC_

SVD<30>

APU_

PR

ALERT#

SMB_DA2

PROCHOT#

SMB_CK2

A4W1E D VT

PWRGD<30>

O

CHOT#<7,14,30>

2 2

3 3

PU +1.8VS

4 4

SVT_R

APU_

SVC_R

APU_

APU_

SVD_R

APU_RST#

APU_

PWRGD

R80 3

R82 3

A

APU_

APU_

DP1_P2<13>

DP1_N2<13>

APU_

DP1_P3<13>

APU_

APU_

DP1_N3<13>

TXP0<12>

EDP_

TXN0<12>

EDP_

EDP_

TXP1<12>

EDP_

TXN1<12>

1 2

4 33_0402_5%

R67

1 2

9 33_0402_5%

R66

1 2

R67

0 33_0402_5%

SMB_CK2<14>

EC_

SMB_DA2<14>

EC_

1 2

R11

7 0_0402_5%KBN@

1 2

8 0_0402_5%KBN@

R11

1 2

R12

0 0_0402_5%RS@

VDDNB_SEN<30>

APU_

APU_VDD_SEN<30>

VDD_RUN_FB_ L<30>

APU_

RP4

1 8

2 7

3 6

4 5

_0804_8P4R_5%

1K

@

RP5

1 8

2 7

3 6

4 5

1K

_0804_8P4R_5%

1 2

1 2

00_0402_5%

00_0402_5%

APU_

APU_

APU_

APU_

LDT

APU_

LDT

APU_

APU_

APU_

APU_

T15

APU_

APU_

APU_

APU_

T18

APU_

+3V

S

8VS

+1.

SVT_R

SVC_R

SVD_R

RST#

_RST#

PWRGD

_PWRGD

PROCHOT#

ALERT#

TDI

TDO

TCK

TMS

TRST#

DBRDY

DBREQ#

B

@

U1C

UAP

A9

TDP

1_TXP0

B9

TDP

1_TXN0

A10

P1_TXP1

TD

B10

TD

P1_TXN1

A11

TD

P1_TXP2

B11

P1_TXN2

TD

A12

TD

P1_TXP3

B12

TD

P1_TXN3

A4

LT

P0_TXP0

D

B4

P0_TXN0

LTD

A5

LTD

P0_TXP1

B5

LTD

P0_TXN1

A6

P0_TXP2

LTD

B6

LTD

P0_TXN2

A7

LTD

P0_TXP3

B7

LT

P0_TXN3

D

K15

DI

SP_CLKIN_H

H15

DI

SP_CLKIN_L

G31

SVT

D27

SVC

E29

SVD

B22

C

SI

B21

D

SI

B20

APU

_RST_L

A20

LD

T_RST_L

B19

_PWROK

APU

A19

LD

T_PWROK

A22

PR

OCHOT_L

B18

ERT_L

AL

D29

TD

I

D31

TD

O

D35

TC

K

D33

S

TM

G27

ST_L

TR

B25

DB

RDY

A25

DB

REQ_L

D23

DCR_NB_SENSE

VD

G23

DCR_CPU_SEN SE

VD

E25

VD

DIO_MEM_S_SENSE

E23

VSS_

SENSE

AV33

D_095_FB_H

VD

3

AU3

VDD_095_FB_L

FT3_BGA_769P-T

Part Number =

Close To PU1000

Close To APU's Pin

B

C

DISP

LAY/SVI2/JTAG/TEST

HDM

Security Classificati on

Security Classificati on

Security Classificati on

Issued Date

Issued Date

Issued Date

S SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

S SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

S SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THI

THI

THI

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DP

_150_ZVSS

DP

_2K_ZVSS

DP

DP

DP

_VARY_BL

P1_AUXP

TD

P1_AUXN

TD

TD

DP0_AUXP

LT

DP0_AUXN

LT

LT

DP0_HPD

DA

DA

C_GREEN

DA

DA

C_HSYNC

DA

C_VSYNC

DA

DA

DA

TH

TH

DI

ECRACKMON

PL

PL

BY

PASSCLK_H

PASSCLK_L

BY

LCHRZ_H

PL

PLLCHRZ_L

O_TSTDTM0_SERIALCLK

GI

GI

O_TSTDTM0_CLKINIT

USB_ATEST0

B_ATEST1

US

ANALO GIN

M_

M_

ANALO GOUT

TM

I_EN/DP_STEREOSYNC

APU_

PWRGD

PWRGD

APU_

APU_

RST#

PROCHOT#

APU_

APU_ALERT#

B16

150_ZVSS

DP_

A21

2K_ZVSS

DP_

B17

_BLON

A17

_DIGON

A18

D17

E17

H19

P1_HPD

D15

E15

H17

4

B1

DAC_

C_RED

C_BLUE

C_SCL

C_SDA

C_ZVSS

ERMDA

ERMDC

BP0

BP1

BP2

BP3

LTEST1

LTEST0

M_

TEST

EE_2

FR

ON_CAL

C12

72 33P_0402_50V8J

70 33P_0402_50V8J

C12

C12

73 33P_0402_50V8J

76 100P_0402_50V8J

C12

77 100P_0402_50V8J

C12

RED

A14

GRN

DAC_

B15

BLU

DAC_

G19

HSYNC

DAC_

E19

VSYNC

DAC_

D19

DAC_

DDC_CLK

D21

DAC_

DDC_DATA

A16

ZVSS

DAC_

H27

APU_

TEST4

H29

APU_

TEST5

D25

A27

TEST14

APU_

B27

TEST15

APU_

A26

APU_

TEST16

B26

APU_

TEST17

B28

TEST18

APU_

A28

TEST19

APU_

B24

TEST25_H

APU_

A24

APU_

TEST25_L

AV35

APU_

TEST28_H

AU3

5

TEST28_L

APU_

E33

TEST31

APU_

A29

APU_

TEST34_L

H21

APU_

TEST36

H25

TEST37

APU_

AJ1

0

TEST42

APU_

AJ8

APU_

TEST43

R32

APU_

TEST39

N32

TEST40

APU_

AP29

TEST41

APU_

E21

APU_

TEST35

1 2

EMC@

1 2

EMC@

1 2

EMC@

1 2

@EMC@

1 2

@EMC@

2014/03/27 2016/03/27

2014/03/27 2016/03/27

2014/03/27 2016/03/27

C

1 2

R40

1 150_0402_1%

1 2

R40

0 2K_0402_1%

ENBKL

<14>

D <12>

ENVD

TPW M < 12>

INV

_CLK <13>

HDMI

_DATA <13>

HDMI

HDMI

_HPD <13>

EDP_

AUXP <12>

EDP_

AUXN <12>

EDP_

HPD <12>

CRT

A4W1E

03

T25

04

T25

T25

01

02

T25

1 2

R41

6 499_0402_1%

T13

T14

1 2

R19 5

1 2

R18 5

T4

T5

T6

T7

0

T1

T8

T9

T11

T12

Com

Com

Com

pal Secret Data

pal Secret Data

pal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

11_0402_1%

11_0402_1%

+1

D

.

8VS

D

E

A4W1E

RED

DAC_

GRN

DAC_

BLU

DAC_

R11

HSYNC

DAC_

NOTE:

DAC_HSYNC

PU FOR HDMI ENABLE

PD FOR CUSTOMER (DNI)

APU_

APU_

APU_

APU_

APU_

APU_

APU_

APU_

APU_

APU_

APU_

APU_

APU_

APU_

APU_

APU_

le

le

le

Tit

Tit

Tit

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

R11

TEST16

TEST17

TEST14

TEST15

TEST37

TEST36

TEST37

TEST36

TEST35

R11

RP6

1 8

TDI

2 7

TMS

3 6

TCK

4 5

DBREQ#

1K_0804_8P4R_5%

RP8

1 8

2 7

TRST#

3 6

TEST19

4 5

TEST18

1K

Co

Co

Co

FT3

FT3

FT3

ursday, April 16, 2015

ursday, April 16, 2015

ursday, April 16, 2015

3

RP2

1 8

2 7

3 6

4 5

75_0804_8P4R_1%

1 2

5 1K_0402_5%

1 2

3 1K_0402_5%

@

@

RP7

1 8

2 7

3 6

4 5

_0804_8P4R_5%

1K

@

RP3

1 8

2 7

3 6

4 5

_0804_8P4R_5%

1K

1 2

4 1K_0402_5%@

+1.

8VS

+1.

8VS

_0804_8P4R_5%

pal Electronics, Inc.

pal Electronics, Inc.

pal Electronics, Inc.

m

m

m

DISP/MISC/HDT

DISP/MISC/HDT

DISP/MISC/HDT

1E_LA-D121P

1E_LA-D121P

1E_LA-D121P

B5W

B5W

B5W

E

+3V

S

8VS

+1.

633Th

633Th

633Th

1.0

1.0

1.0

A

1 2

5 150P_0402_50V8J

C61

1 2

2 33_0402_5%

_RST#<14,20>

LPC

E_RST#<15,17>

APU_PCI

1 1

2 2

1 2

@

1 2

R3

@

39 10K_0402_5%

9

1 2

R39

@

38 10K_0402_5%

R39

37 10K_0402_5%

Che

cklist suggestion

#_AUDIO<16>

HDA_RST

SY

NC_AUDIO<16>

HDA_

HDA_SDO

UT_AUDIO<16>

HDA_BI

TCLK_AUDIO<16>

+3VALW

3 3

+3VS

1 2

1 100K_0402_5%@

R90

1 2

5 100K_0402_5%

R90

1 2

6 100K_0402_5%@

R90

1 2

R6

5 1K_0402_5%@

7

1 2

6 2.2K_0402_5%

R67

1 2

7 2.2K_0402_5%

R67

1 2

R68

4 10K_0402_5%@

1 2

R68

8 10K_0402_5%@

R60

1 2

R90

7 33_0402_5%

1 2

C912 150P_0402_50V8J

PBTN_

OUT#<14>

SYS_

PWRGD_EC<14>

E_WAKE#<15>

APU_PCI

S3#<14>

SLP_

S5#<14>

SLP_

1 2

R40 1

1 2

R41 1

1 2

R42 1

#<14>

KBRST

GAT

EA20<14>

EC_SCI

#<14>

EC_SMI

#<14>

_CLKREQ#<15>

LAN

N_CLKREQ#<17>

WLA

USB_O

C0#<19>

HDA_SDI

N0<16>

EMC@

RP13

1 8

2 7

3 6

4 5

33_0804_8P

APU_PCI

USB_O

USB_O

EC_

APU_SCL

APU_SDAT

HDA_BI

HDA_SDI

HDA_RST

HDA_SY

HDA_SDO

HDA_BI

4R_5%

C0#

C1#

ID_OUT#

L

TCLK

T16

#

NC

UT

TCLK

E_WAKE#

K0

A0

N0

LPC

APU_PCI

EC_RSMRST

APU_PCI

5K_0402_5%

5K_0402_5%

5K_0402_5%

LAN

WLA

USB_O

USB_

HDA_BITCLK

HDA_SDO

HDA_SDI

HDA_SDI

HDA_

HDA_SDI

HDA_SY

HDA_RST

32K_X

32K_X

_RST_A#

E_RST#_R

E_WAKE#

APU_T

APU_T

APU_T

_CLKREQ#

N_CLKREQ#

T21

C0#

C1#

O

T19

T20

UT

N0

N1

N2

SDI

N3

NC

#

1

2

EC_RSMRST

#_R

EST0

EST1

EST2

#<14>

32.768KMHz CRYSTAL

1

32K_X

12

1

2

C68

18P_0402_50V8J

2

A

Y3

32K_X

2

4 4

32.768K

R91

20M_0402_5%

1

6

C68

18P_0402_50V8J

2

SJ100001K00

HZ_12.5PF_CM31532768DZFT

12

4

B

@

UAPU1D

AY4

LPC

_RST_L

AY9

RST_L

PCIE_

AM1

AW1

AW2

AY5

BA8

AY7

AY3

BA5

AU1

AY10

AY6

AR2

AR

AN5

AL7

AP15

AV13

BA9

BA10

AV15

AU2

AR2

AV27

AY29

AY8

AW1

AV1

AY1

AN2

AN

AK2

AK1

AM1

AL2

AM2

AL1

AJ2

AJ1

_L

RSMRST

PWR_

BTN_L

9

PWR_

GOOD

SYS_

RESET_L/GEVENT19_L

1

WAKE_L/GEVENT8_L

S3_L

SLP_

S5_L

SLP_

3

TES

T0

TES

T1/TMS

T2

TES

3

L

KBRST_

3

1

2

0IN/GEVENT0_L

GA

LPC

_PME_L/GEVENT3_L

LPC

_SMI_L/GEVENT23_L

IR_RX0/GEVENT16_L

AC_PRES/

TX0 /GEVEN T21_ L

IR_

TX1 /GEVEN T6_L

IR_

IR_

RX1 /GEVEN T20_ L

IR_

LED _L/LLB _L/GP IO184

9

CLK_

REQ0_L/SATA_IS0_L/SATA_ZP0_L/GPIO60

9

REQ1_L/GPIO61

CLK_

7

REQ2_L/GPIO62

CLK_

REQ3_L/SATA_IS1_L/SATA_ZP1_L/GPIO63

CLK_

CL

REQG_L/GPIO65/OSCIN

K_

USB_O

C0_L/SPI_TPM_CS_L/TRST_L/GEVENT12_L

USB_O

C1_L/TDI/GEVENT13_L

C2_L/TCK/GEVENT14_L

USB_O

C3_L/TDO/GEVENT15_L

USB_O

AZ

BITCLK

_

1

AZ_

SDOUT

AZ_

SDIN0/GPIO167

AZ_

SDIN1/GPIO168

AZ_SDIN2/GPIO169

SDIN3/GPIO170

AZ_

SYNC

AZ_

RST_L

AZ_

X32

K_X1

K_X2

X32

GA_769P-T

FT3_B

Part Number =

A4W1 E

1 2

R39

45 0_0402_5%@

1 2

D3

1V-40 SOD-323

RB75

RB751 Max Vf=0.37V

B

ACPI

/SD/AZ/GPIO/RTC/MISC

C

SD_PW

R_CTRL

K/GPIO73

SD_CL

GPIO74

SD_CMD/

SD_

GPIO75

CD/

SD_W

P/GPIO76

SD_DAT

A0/GPIO77

SD_DATA1/GPIO78

A2/GPIO79

SD_DAT

A3/GPIO80

SD_DAT

SD_L

ED/GPIO45

SCL0

/GPIO43

GPIO47

SDA0/

/GPIO227

SCL1

/

GPIO228

SDA1

GPI

GPI

GPI

GPI

GPI

GPI

GPI

GPI

SPKR/G

PIO66

GPI

GPI

GPI

GPI

O174

GPI

GEV

ENT2_L

GEV

ENT4_L

ENT7_L

GEV

ENT10_L

GEV

ENT11_L

GEV

GE

ENT17_L

V

BLI

NK/GEVENT18_L

GEV

ENT22_L

GENINT1_L/GPIO32

INT2_L/GPIO33

GEN

OUT0/GPIO52

FAN

FA

IN0/GPIO56

N

RTCCL

O49

O50

O51

O55

O57

O58

O59

O64

O68

O69

O70

O71

BA23

AY22

AY23

AY20

BA20

BA2

2

AY21

AY24

BA24

AY25

5

AU2

AV25

AY11

BA1

AP27

AY28

BA2

AV23

AP21

BA26

AV19

AY27

BA27

AU2

AY26

AV21

AM2

BA3

AV17

BA4

AR

AP17

AP11

AN8

AU

BA6

BA29

AP23

AV31

AU3

AV11

K

APU_SCL

APU_SDAT

APU_SCL

1

APU_SDAT

APU_G

8

APU_G

1

1

APU_G

APU_G

GEV

GE

1

5

7

1

GE

GEN

1

V

N

RTC_

PIO49

PIO51

PIO71

PIO174

ENT2#

ENT4#

INT1_L

INT2_L

K0

A0

K1

A1

1 2

R66

1 0_0402_5%@

1 2

6 10K_0402_5%

R68

1 2

R68

9 10K_0402_5%

EC_L

ID_OUT# <14>

CLK

APU_SCL

APU_SDAT

DEVSLP0

APU_SPKR

T17

K0 <10,11,17>

A0 <10,11,17>

<18>

D

<16>

PROCHO

STRAPS OF APU

LPC_FRAME# LPC_CLK0_EC

SPI ROM

_FRAME#<8,14>

LPC

_CLK0_EC<8,14>

LPC

_CLK1<8,20>

LPC

iphered Date

iphered Date

iphered Date

(DEFAULT)

LPC ROM

A4W1 E DV T

H

+1.8VALW

L

5

9

1 2

1

2

R68

5

10K_0402_5%

1 2

1

2

C21

1U_0402_6.3V6K

2

2014/03/

2014/03/

2014/03/

+3VS

1 2

46 10K_0402_5%

R39

1 2

9

47 10K_0402_5%@

R3

1 2

R39

48 10K_0402_5%

2

8

C94

.1U_040 2_16V7K

1

@EMC@

pal Secret Data

pal Secret Data

pal Secret Data

Com

Com

Com

27 2016/03/27

27 2016/03/27

27 2016/03/27

C

Dec

Dec

Dec

R34

47K_0402_5%

#_R

EC_RSMRST

SYS_

PWRGD_EC

C20

1U_0402_6.3V6K

urity Classification

urity Classification

urity Classification

Sec

Sec

Sec

Issued Date

Issued Date

Issued Date

THI

THI

THI

S SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

S SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

S SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

BOOT FAIL TIMER

ENABLED

BOOT FAIL TIMER

DISABLED

(DEFAULT)

ENT2#

GEV

CLK

RTC_

D

12

@

0

2

R9

10K_0402_5%

12

@

R90

3

2K_0402_5%

E

APU_SCL

K1

APU_SDATA1

A4W1 E

APU_G

APU_G

PIO51

PIO49

1K_0402_5%

1 2

12

10K_0402_5%

12

12

CZL@

R69

R69

4

2

R39

R39444.7K_0402_5%

+3VALW

434.7K_0402_5%

+3VS

KBN@

5

R69

1K_0402_5%

1 2

12

1

R69

10K_0402_5%

GPIO51 GPIO49Platform identify

Be

ma

e

Kabini

Carrizo_L (Reserve)

T# <6,14,30>

NA (Reserve)

ENT4#

GEV

1 2

1 2

oject identify

GEV

1 2

GEN

GEN

INT1_L

INT2_L

@

200_0402_5%

R39

1 2

RS@

R39

230_0402_5%

LPC_CLK1 GEVENT2_L

CLKGEN

ENABLE

(DEFAULT)

CLKGEN

DISABLED

12

@

0

4

R9

10K_0402_5%

12

R92

6

2K_0402_5%

Tit

le

le

le

Tit

Tit

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

tom

tom

tom

Cus

Cus

Cus

Date: Sheet

Date: Sheet of

Date: Sheet of

1.8V SPI ROM

3.3V SPI ROM

(DEFAULT)

12

@

2

5

R9

10K_0402_5%

12

@

R92

7

2K_0402_5%

pal Electronics, Inc.

pal Electronics, Inc.

pal Electronics, Inc.

Com

Com

Com

GPIO/AZ/MISC/STRAPS

GPIO/AZ/MISC/STRAPS

GPIO/AZ/MISC/STRAPS

FT3

FT3

FT3

1E_LA-D121P

1E_LA-D121P

1E_LA-D121P

B5W

B5W

B5W

0

0

1

11

7 10K_0402_5%@

R68

R6

8 10K_0402_5%

6

14" 15"Pr

ENT4# 0 1

TP_I

NORMAL POWR

UP/RESET TIMING

(DEFAULT)

FAST POWER

UP/RESET TIMING

FOR SIMULATION

+3VALW

12

@

R9

10K_0402_5%

12

R92

2K_0402_5%

12

2

8

12

9

E

0

1

0

+3VALW

2C_INT#_APU <20>

RTC_CLK

4

R9

10K_0402_5%

@

R95

2.2K_0402_5%

733Thursday, April 16, 2015

733Thursday, April 16, 2015

733Thursday, April 16, 2015

(DEFAULT)

9

0

of

1.0

1.0

1.0

A

SATA_

FTX_DRX_P0<18>

SATA_

HDD

1 1

ODD

95VS

+0.

2 2

LAN

WLAN

C

_CLK0_EC<7,14>

LP

LPC

_CLK1<7,20>

3 3

LPC

1 2

R93

8

1M_0402_5%

2

2

4 4

3

3

12

C79

4

6.8P_0402_50V8C

FTX_DRX_N0<18>

FRX_DTX_N0<18>

SATA_

FRX_DTX_P0<18>

SATA_

SATA_

FTX_DRX_P1<18>

FTX_DRX_N1<18>

SATA_

FRX_DTX_N1<18>

SATA_

SATA_

FRX_DTX_P1<18>

R90 1

R96 1

+3V

S

R63

10K_0402_5%

CLK

_PCIE_LAN<15>

_PCIE_LAN#<15>

CLK

_PCIE_WLAN<17>

CLK

CLK

_PCIE_WLAN#<17>

LPC_AD0<14>

LPC

_AD1<14>

_AD2<14>

LPC

C

_AD3<14>

LP

_FRAME#<7,14>

SERI

RQ<14>

CLK

RUN#<20>

PD#<20>

LPC

48M_X

48M_X

1

1

Y1

48MH

Z_8PF_X3S048000D81H-W

Part Number = SJ10000AF00

4

4

12

C79

5

5.6P_0402_50V8D

SE07156AD80

A

12

K_0402_1%

12

K_0402_1%

12

@

3

R10

3 0_0402_5%RS@

4 0_0402_5%RS@

R10

2

1

48M_X

48M_X

1 2

1 2

SATA_

SATA_

SATA_

BA14

AY1

4

BA16

AY1

6

AY1

9

BA19

AY1

7

BA17

9

AR1

ZVSS

AP19

ZVDD

BA30

ACT#

2

AY1

BA12

U4

U5

AC8

AC1

0

AE4

AE5

AC4

AC5

AA5

AA4

AP13

AY2

AW2

AT2

AT1

AR2

AR1

AP2

AP1

AV29

AP25

AV2

N2

N1

1

2

B

@

U1E

UAP

SAT

A_TX0P

SATA_TX0N

A_RX0N

SAT

SATA_RX0P

SATA_TX1P

A_TX1N

SAT

SATA_RX1N

SAT

A_RX1P

SATA_ZVSS

A_ZVDD_095

SAT

SAT

A_ACT_L/GPIO67

SATA_X1

A_X2

SAT

GFX

_CLKP

GFX

_CLKN

P_CLK0P

GP

GPP_CLK0N

GPP

_CLK1P

GP

_CLK1N

P

GP

P_CLK2P

GP

P_CLK2N

GP

_CLK3P

P

_CLK3N

GPP

X1

4M_25M_48M_OSC

M_X1

X48

X48

M_X2

LP

CCLK0

LP

CCLK1

D0

LA

LA

D1

LA

D2

LA

D3

AME_L

LFR

Q0_L

LDR

SER

IRQ/GPIO48

LP

C_CLKRUN_L

LPC

_PD_L/GEVENT5_L/SPI_TPM_CS_L

FT3_BGA_769P-T

Part Number =

B

/SATA/USB/SPI/LPC

CLK

USB

CLK/14M_25M_48M_OSC

US

US

US

US

US

US

US

USB_HSD3N

US

US

USB

USB

US

US

US

US

USB

USB

USB

US

USB

_SS_ZVDD_095_USB3_DUAL

US

US

USB

USB

USB

USB

USB

USB

USB

SPI

_CLK/GPIO162

_CS1_L/GPIO165

SPI

_CS2_L/GPIO166

SPI

SPI_DO/GPIO163

SPI

SPI_HOLD_L/GEVENT9 _L

_DI/GPIO164

_WP_L/GPIO161

SPI

B_ZVSS

US

B_HSD0P

B_HSD0N

B_HSD1P

B_HSD1N

B_HSD2P

B_HSD2N

B_HSD3P

B_HSD4P

B_HSD4N

_HSD5P

_HSD5N

B_HSD6P

B_HSD6N

B_HSD7P

B_HSD7N

_HSD8P

_HSD8N

_HSD9P

_HSD9N

B

B_SS_ZVSS

_SS_0TXP

B

_SS_0TXN

_SS_0RXP

_SS_0RXN

_SS_1TXP

_SS_1TXN

_SS_1RXP

_SS_1RXN

W4

AG4

AL4

AL5

AJ4

AJ5

AG7

AG8

AG1

AG2

AF1

AF

AE1

AE2

AD1

AD2

AC1

AC2

AB1

AB2

AA1

AA2

AE10

AE8

T2

T1

V2

V1

R1

R2

W1

W2

AU7

AW9

AR4

AR1

AR7

AU1

AU9

C

USB

_ZVSS

2

SS_ZVSS

USB

SS_ZVDD

USB

APU_

APU_

1

APU_

APU_

1

APU_

APU_

1 2

R64

1 11.8K_0402_1%

1 2

4 1K_0402_1%

R64

1 2

R64

5 1K_0402_1%

SPI_CLK_R

SPI_CS1#

SPI_MOSI

SPI_MISO

SPI_HOLD#

SPI_WP#

R10

5 0_0402_5%RS@

T37

1 2

20_P0 <19>

USB

USB

20_N0 <19>

20_P1 <19>

USB

20_N1 <19>

USB

USB

20_P2 <17>

USB

20_N2 <17>

20_P3 <12>

USB

20_N3 <12>

USB

USB

20_P4 <19>

20_N4 <19>

USB

20_P5 <12>

USB

USB

20_N5 <12>

20_P6 <21>

USB

20_N6 <21>

USB

20_P8 <19>

USB

20_N8 <19>

USB

3_FTX_DRX_P0 <19>

USB

3_FTX_DRX_N0 <19>

USB

USB

3_FRX_DTX_P0 <19>

B

3_FRX_DTX_N0 <19>

US

APU_

95VALW

+0.

SPI_CLK

D

USB/

B port 0

SUB/B USB2

WLAN/BT combo

CAMERA

SUB/B CR

Touch Screen

USB 2 I2C Bridge

MB USB3.0 port0 (2.0)

1 2

76 0_0402_5%RS@

R16

1 2

6

77 0_0402_5%RS@

R1

1 2

R16

78 0_0402_5%RS@

1 2

R1

79 0_0402_5%RS@

6

8MB SPI ROM48MHz CRYSTAL

+3V

ALW

RP1

2

1 8

2 7

3 6

4 5

10K_0804_8P4R_5%

Security Classificati on

Security Classificati on

Security Classificati on

2014/03/27 2016/03/27

2014/03/27 2016/03/27

Issued Date

Issued Date

Issued Date

S SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

S SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

S SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THI

THI

THI

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVIS ION OF R&D

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2014/03/27 2016/03/27

C

Com

Com

Com

pal Secret Data

pal Secret Data

pal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

APU_

APU_

APU_

SPI_CS1#

SPI_WP#

SPI_HOLD#

SPI_CS1#

APU_

SPI_MISO

APU_

APU_

SPI_WP#

D

E

Port 0-3 USB OHCI1 ( Dev 12 Func 0 )

Port 4-7 USB OHCI2 ( Dev 13 Func 0 )

USB2.0 Only

Port 8-9 USB OHCI2 ( Dev 16 Func 0 )

USB3.0

Port 0-1 USB XHCI ( Dev 10 Func 0 )

U56

1

CS#

2

DO(

HOL

IO1)

3

WP#

4

GN

W2

SA000039A30

A4W1E

le

le

le

Tit

Tit

Tit

Size Documen t Number Rev

Size Documen t Number Rev

Size Documen t Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

D#(IO3)

(IO2)

D

5Q64FVSSIQ_SO8

ursday, April 16, 2015

ursday, April 16, 2015

ursday, April 16, 2015

EHCI1 ( Dev 12 Func 2 )

EHCI2 ( Dev 13 Func 2 )

EHCI2 ( Dev 16 Func 2 )

EC_

SPI_CLK <14>

SPI_CS1# <14>

EC_

EC_

SPI_MOSI <14>

SPI_MISO <14>

EC_

C63

.1U_0402_1 6V7K

8

VCC

DI

CLK

(

IO0)

Co

Co

Co

FT3

FT3

FT3

B5W

B5W

B5W

m

m

m

7

6

5

SPI_HOLD#

APU_

APU_

SPI_CLK

APU

SPI_MOSI

_

APU_

SPI_CLK

R61

10_0402_5%

pal Electronics, Inc.

pal Electronics, Inc.

pal Electronics, Inc.

SATA/CLK/USB/SPI

SATA/CLK/USB/SPI

SATA/CLK/USB/SPI

1E_LA-D121P

1E_LA-D121P

1E_LA-D121P

12

5

@

1 2

7

@EMC@

E

+3V

ALW

1 2

C63

6

10P_0402_50V8J

833Th

833Th

833Th

@EMC@

1.0

1.0

1.0

CORE POWER OF APU

+AP

U_CORE

VDDCR_CPU

C17

9 1U_0402_6.3V6K

C18

0 1U_0402_6.3V6K

1

1

2

2

A

C18

C18

C182 1U_0402_6.3V6K

1 1U_0402_6.3V6K

3 1U_0402_6.3V6K

1

1

1

2

2

2

C18

C18

C1

C18

6 1U_0402_6.3V6K

4 1U_0402_6.3V6K

1

1

2

2

C19

C18

8

8 1U_0402_6.3V6K

7 1U_0402_6.3V6K

0 180P_0402_50V8J

9 1U_0402_6.3V6K

1

1

1

1

2

2

2

2

B

C

D

E

1 1

INTEGRATED GPU POWER OF APU

U_CORE_NB

+AP

+1.5V/+1.5VS OF APU

5V

+1.

2 2

VDDIO_MEM_S

C94

C92

C92

9 10U_0603_6.3V6M

5 10U_0603_6.3V6M

4 10U_0603_6.3V6M

1

1

1

2

2

2

@

+0.95VALW/+0.95VS OF APU

VDD_095

+0.

95VS

C19

C93

5 10U_0603_6.3V6M

1

2

3 3

VDD_095_USB3_DUAL

C20

C93

C19

9 1U_0402_6.3V6K

5 1U_0402_6.3V6K

4 10U_0603_6.3V6M

8 1U_0402_6.3V6K

1

1

1

1

2

2

2

2

@

@

95VALW

+0.

C93

C93

7 10U_0603_6.3V6M

8 10U_0603_6.3V6M

1

1

2

2

VDDCR_NB

C92

C92

3 1U_0402_6.3V6K

6 .1U_0402_16V7K

1

1

2

2

C2

C20

C26

0

4 1U_0402_6.3V6K

6 1U_0402_6.3V6K

0 1U_0402_6.3V6K

1

1

2

2

C21

C21

6 1U_0402_6.3V6K

4 1U_0402_6.3V6K

1

2

@

+3VALW/+3VS OF APU

C25

C25

5 1U_0402_6.3V6K

4 1U_0402_6.3V6K

1

2

2

1

C24

5 180P_0402_50V8J

1

2

+3V

C25

6 180P_0402_50V8J

1

1

2

2

C94

6

.1U_0402_16V7K

@EMC@

ALW

C25

2 1U_0402_6.3V6K

C25

3 1U_0402_6.3V6K

1

1

2

2

2

1

+RT

C94

7

.1U_0402_16V7K

@EMC@

C_APU_R

+1.

+1.

8VALW

ALW

+3V

+0.95VALW

95VALW

+0.

+RT

5VS

C_APU_R

+1.

5V

3A

AG32

AG3

AM1

AA31

AA35

AC3

AC3

AE31

AE35

AJ3

AL3

AL3

AR3

AL1

AL11

AL1

AW5

AE11

AE13

AJ11

AJ1

J35

L32

L37

N35

R31

R37

U32

U35

W3

1

W32

W37

2

7

7

5

2

7

5

0

B1

B2

3

3

AR5

AU4

AV7

3

AN4

@

UAP

U1F

IO_MEM_S_1

VDD

IO_MEM_S_2

VDD

VDD

IO_MEM_S_3

IO_MEM_S_4

VDD

VDDIO_MEM_S_5

IO_MEM_S_6

VDD

IO_MEM_S_7

VDD

VDD

IO_MEM_S_8

IO_MEM_S_9

VDD

IO_MEM_S_10

VDD

VDD

IO_MEM_S_11

VDD

IO_MEM_S_12

IO_MEM_S_13

VDD

D

IO_MEM_S_14

VD

IO_MEM_S_15

VDD

VDD

IO_MEM_S_16

VDD

IO_MEM_S_17

IO_MEM_S_18

VDD

VDD

IO_MEM_S_19

VDD

IO_MEM_S_20

IO_MEM_S_21

VDD

VDDIO_MEM_S_22

IO_MEM_S_23

VDD

VDD

IO_AZ_ALW_1

VDD

IO_AZ_ALW_2

VDD

_18_ALW_1

_18_ALW_2

VDD

_33_ALW_1

VDD

VDD

_33_ALW_2

VDD_095_USB3_DUAL_1

VDD

_095_USB3_DUAL_2

_095_USB3_DUAL_3

VDD

VDD_095_USB3_DUAL_4

_095_ALW_1

VDD

VDD

_095_ALW_2

VDD

_095_ALW_3

_095_ALW_4

VDD

VDD

BT_RTC_G

FT3_BGA_769P-T

Part Number =

POW

ER

VDD

VDD

VDD

VDD

VD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDCR_CPU_22

VDD

VDD

VDD

VDD

VDD

VDD

VDD

CR_CPU_1

VDD

CR_CPU_2

VDD

VDD

CR_CPU_3

CR_CPU_4

VDD

VDDCR_CPU_5

CR_CPU_6

VDD

CR_CPU_7

VDD

VDD

CR_CPU_8

CR_CPU_9

VDD

CR_CPU_10

CR_CPU_11

CR_CPU_12

CR_CPU_13

D

CR_CPU_14

CR_CPU_15

CR_CPU_16

CR_CPU_17

CR_CPU_18

CR_CPU_19

CR_CPU_20

CR_CPU_21

CR_CPU_23

CR_CPU_24

CR_CPU_25

CR_CPU_26

CR_NB_1

VDD

VDD

CR_NB_2

VDD

CR_NB_3

CR_NB_4

VDD

D

CR_NB_5

VD

CR_NB_6

VDD

VDD

CR_NB_7

VDD

CR_NB_8

CR_NB_9

VDD

VDD

CR_NB_10

CR_NB_11

VDD

VD

CR_NB_12

D

CR_NB_13

VDD

VDD

CR_NB_14

VDD

CR_NB_15

CR_NB_16

VDD

VDD

CR_NB_17

VDD

CR_NB_18

VDD

CR_NB_19

CR_NB_20

VDD

VDD

CR_NB_21

VDD

VDD

VDD

VDD

VDD

VDD

VDD_095_1

VDD

_095_2

_095_3

VDD

VDD_095_4

VDD

_095_5

_095_6

VDD

VDD

_095_7

VDD

_095_8

_095_9

VDD

_095_GFX_1

_095_GFX_2

_095_GFX_3

_18_1

_18_2

_18_3

_18_4

_33_1

_33_2

L21

L23

L25

L27

L29

N21

N23

N27

R2

R23

R27

U21

U23

U27

W21

W23

W27

AA21

AA23

AA27

AC2

AC2

AC2

AE21

AE23

AE2

L13

L17

N11

N13

N17

R11

R1

R17

U13

U17

W13

W17

AA13

AA17

AC1

AC1

AE15

AE17

AE19

AG1

AG2

A2

A3

B3

C3

AM1

AM1

AG2

AG2

AJ2

AJ2

AL2

AL2

AL2

AM23

AM2

U10

W10

AA10

AA1

AA15

AA19

AA25

AA29

AA39

AC1

AC15

AC1

AC2

AC2

AC3

AC3

AC4

AE25

AE29

AE32

AE39

AG1

AG

AG13

AG1

AG1

AG2

AG2

AG3

AG3

AG4

W29

W39

W41

Y1

Y2

AA3

AA7

AA8

1

AC3

AC7

1

9

5

9

1

9

1

AE3

AE7

AG3

AG5

0

1

1

5

9

5

9

1

9

1

AH1

AH2

AJ3

AJ7

AJ1

5

7

AJ1

AJ19

AJ2

3

5

AJ2

AJ29

AJ3

1

2

AJ3

AJ39

AL3

AL8

AL15

AL1

7

9

AL1

AL2

5

9

AL2

@

UAP

U1H

25

VSS_1

26

VSS_1

VSS_1

27

28

VSS_1

VSS_129

30

VSS_1

31

VSS_1

VSS_1

32

33

VSS_1

34

VSS_1

VSS_1

35

VSS_1

36

37

VSS_1

1

38

VSS_

39

VSS_1

VSS_1

40

VSS_1

41

42

VSS_1

VSS_1

43

VSS_1

44

45

VSS_1

VSS_146

47

VSS_1

VSS_1

48

VSS_1

49

50

VSS_1

51

VSS_1

VSS_1

52

53

VSS_1

54

VSS_1

1

55

VSS_

56

VSS_1

VSS_1

57

58

VSS_1

59

VSS_1

VSS_1

60

VSS_1

61

62

VSS_1

VSS_

63

1

64

VSS_1

VSS_1

65

VSS_1

66

67

VSS_1

VSS_1

68

VSS_1

69

VSS_1

70

71

VSS_1

VSS_1

72

VSS_1

73

74

VSS_1

VSS_1

75

76

VSS_1

77

VSS_1

VSS_1

78

79

VSS_1

80

VSS_1

VSS_1

81

82

VSS_1

VSS_183

VSS_1

84

85

VSS_1

VSS_186

FT3_BGA_769P-T

Part Number =

GND

VSSBG_

VSS_1

VSS_1

VSS_1

VSS_1

VSS_191

VSS_1

VSS_1

VSS_1

VSS_1

VSS_1

VSS_1

VSS_1

VSS_1

VSS_

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_208

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VSS_2

VBURN

PSEN

AL3

9

87

AL4

1

88

1

AM1

89

7

AM2

90

AM3

1

AN3

92

AN7

93

AN3

9

94

AP3

1

95

AR3

96

AR1

3

97

7

AR1

98

AR2

1

99

AR2

5

2

00

9

AR2

01

9

AR3

02

AR4

1

03

AU1

04

AU2

05

AU3

06

5

AU1

07

AU1

9

3

AU2

09

7

AU2

10

AU3

9

11

AV9

12

AW3

13

AW7

14

3

AW1

15

AW1

5

16

AW1

7

2

17

9

AW1

18

AW2

1

19

AW

3

2

20

AW25

21

AW2

7

22

1

AW3

23

AW3

3

24

AW3

5

25

2

7

AW3

26

9

AW3

27

AW4

1

28

AY13

29

AY15

30

AY18

31

AY30

32

BA2

33

BA7

34

BA13

35

BA15

36

BA18

37

BA21

38

BA25

39

BA31

40