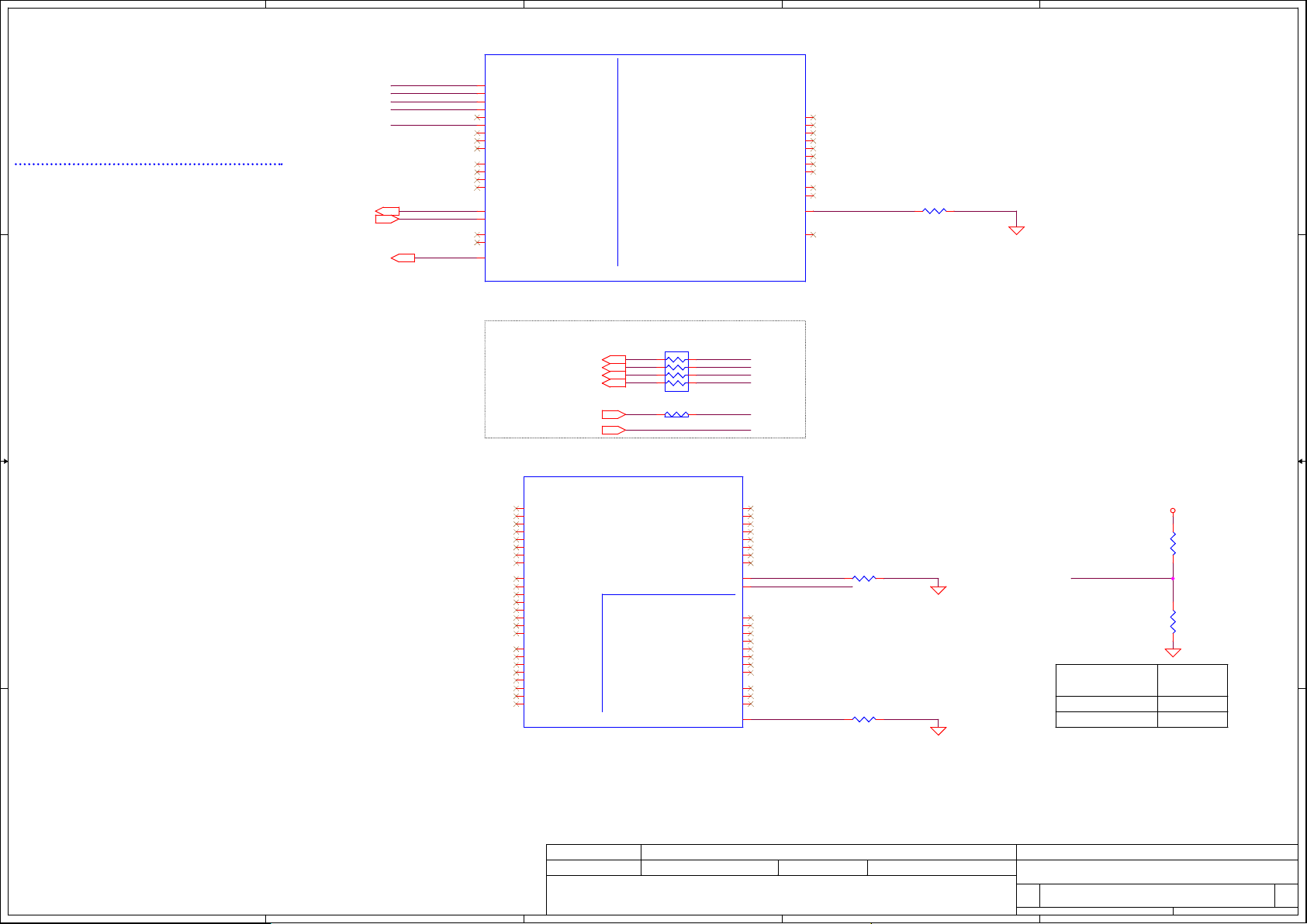

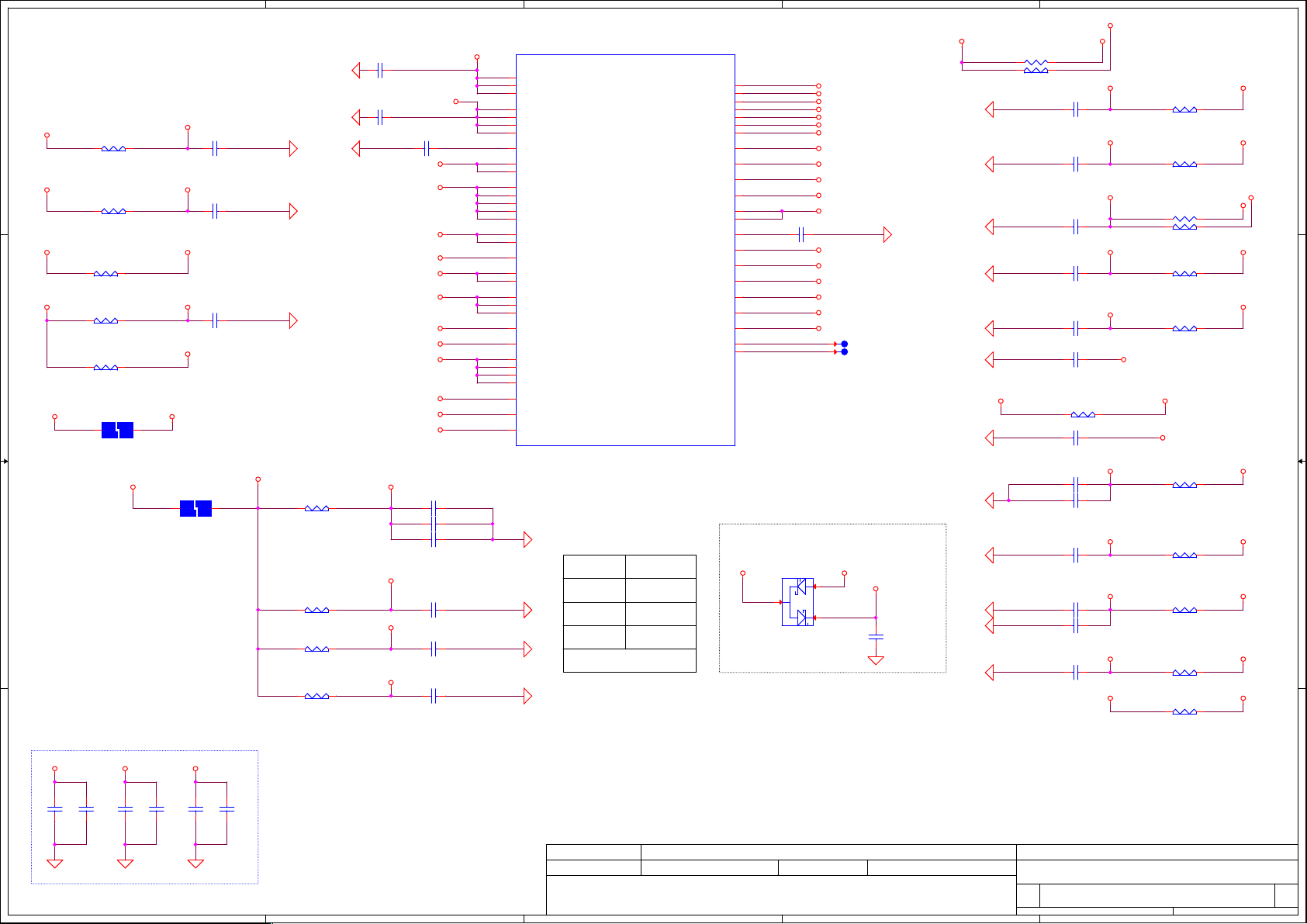

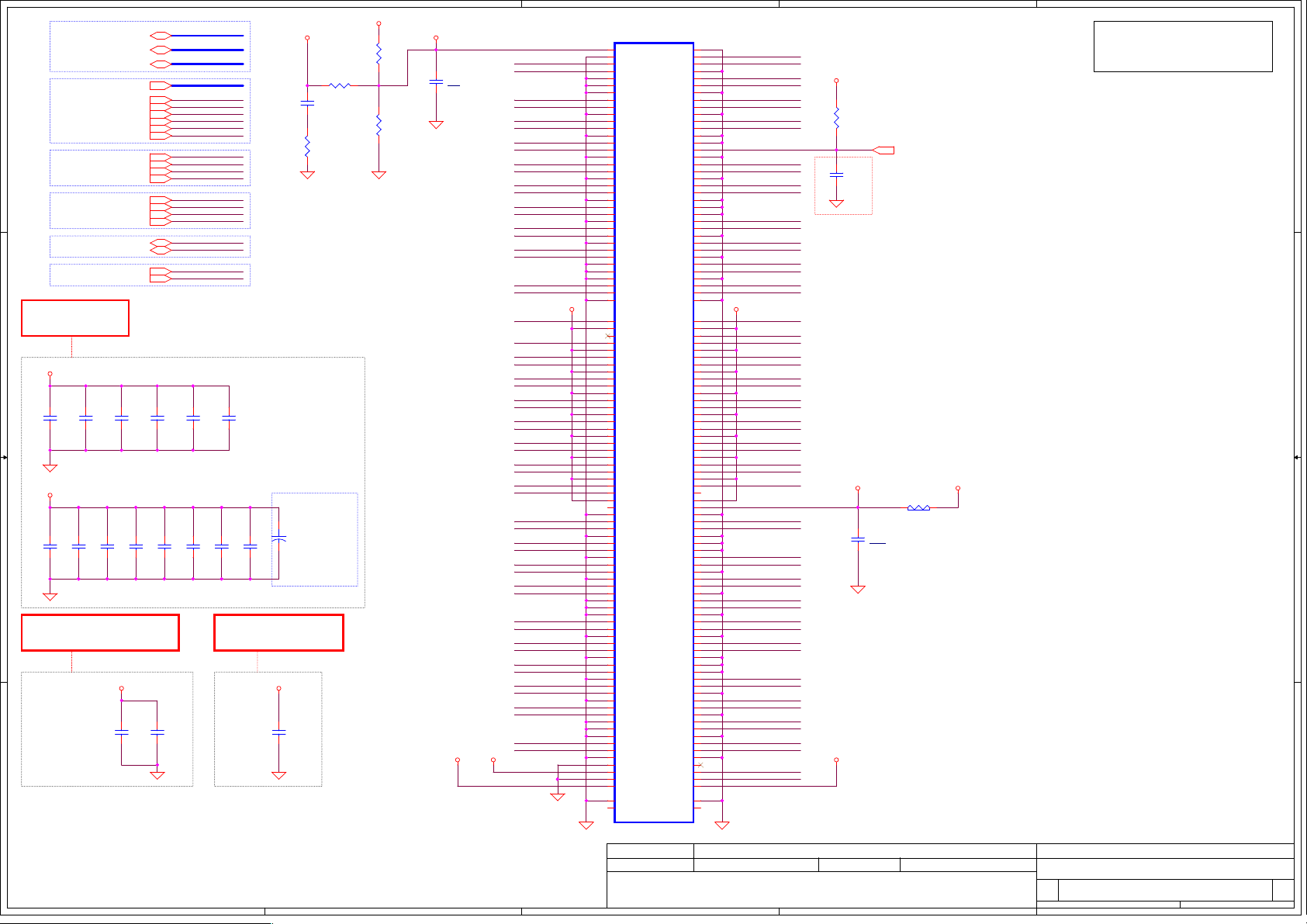

Acer Aspire E5-474G Schematics

A

1 1

2 2

Co

B

C

D

mpal Confidential

E

A4

3 3

WAS MB Schematic Document

LA-C611

P

Rev: 1.0

2015.07.17

4 4

DAX

Number

Part

1DR00100 PCB A4WAS LA-C611P LS-C341P

DAZ

WAS_PCB_REV10

A4

Description

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

TH

TH

TH

IS SHEET OF ENGINEE RING D RAWING IS THE PROPRIE TARY PRO PERTY OF C OMPAL ELEC TRONIC S, INC. A ND CONTAI NS CONFIDENTIAL

IS SHEET OF ENGINEE RING D RAWING IS THE PROPRIE TARY PRO PERTY OF C OMPAL ELEC TRONIC S, INC. A ND CONTAI NS CONFIDENTIAL

IS SHEET OF ENGINEE RING D RAWING IS THE PROPRIE TARY PRO PERTY OF C OMPAL ELEC TRONIC S, INC. A ND CONTAI NS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THI S SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THI S SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THI S SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

C

11/10 2016/11/10

11/10 2016/11/10

11/10 2016/11/10

2014/

2014/

2014/

mpal Secret Data

mpal Secret Data

mpal Secret Data

Co

Co

Co

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

tle

tle

tle

Ti

Ti

Ti

Cover Sheet

Cover Sheet

Cover Sheet

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

stom

stom

stom

Cu

Cu

Cu

A4WAS M/B LA-C611P

A4WAS M/B LA-C611P

A4WAS M/B LA-C611P

Date: Sheet

Date: Sheet

D

Date: Sheet

160Friday, July 17, 2015

160Friday, July 17, 2015

160Friday, July 17, 2015

of

of

E

of

0

0

0

1.

1.

1.

A

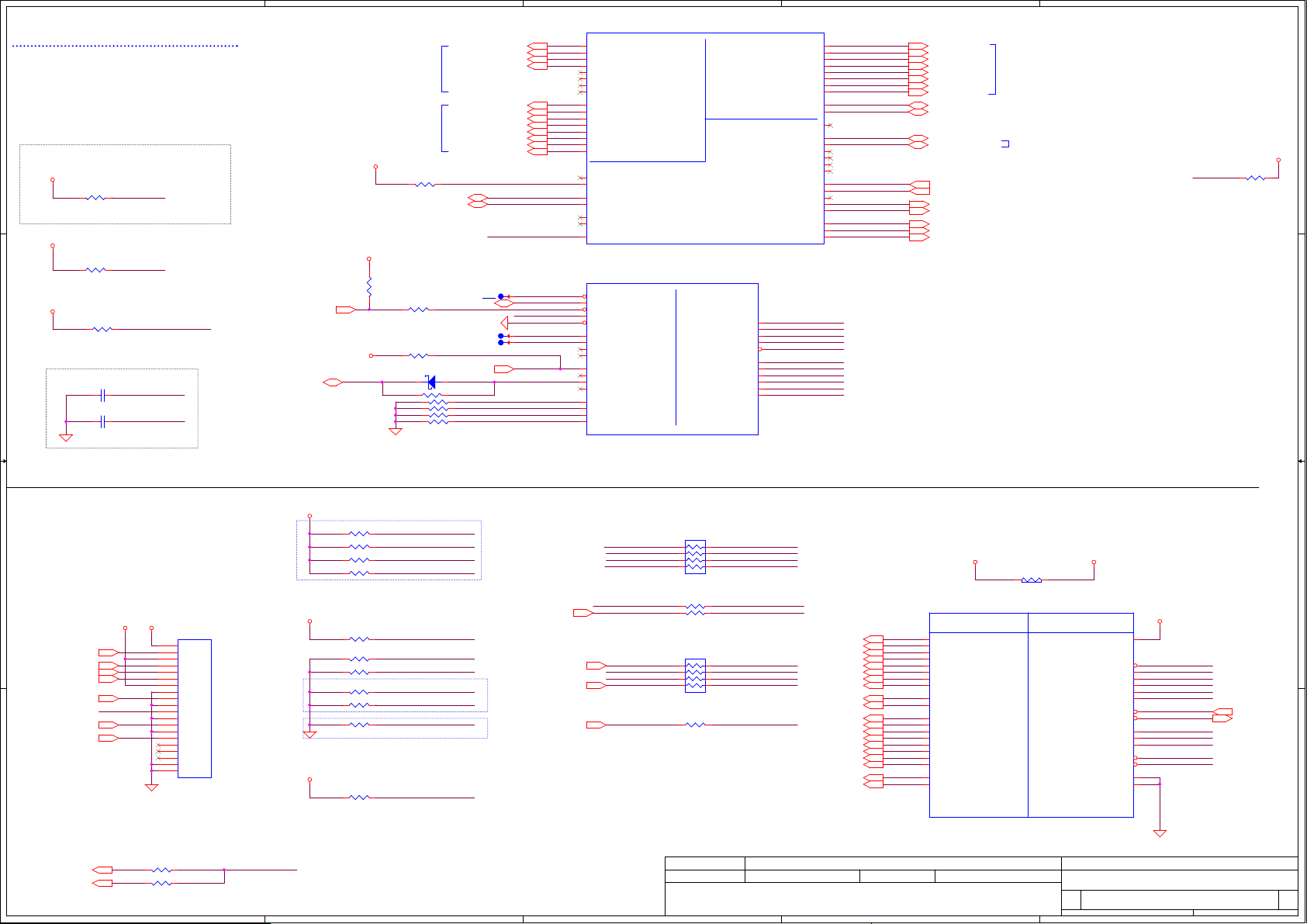

VG

A

32

page

1 1

DP

to VGA

Realtek RTD2168

31

page

x 2 lanes

DP

HDMI Conn.

I

HDM

PS8407A

page 30

Nv

idia N16x

DD

HDM

I2DDI1

I x 4 lanes

B

eD

P

page

eD

DD

C

29

P

I

Intel Skylake U

ylake U

Sk

Skylake PCH-LP(MCP)

(SKL-U_2+2)

Me

mory BUS

Du

al Channel

35V DDR3L 1333/1600

1.

US

conn x2

USB port 1,2

B 3.0

D

nterleaved Memory

I

Fan Control

204pi

204pi

B 2.0

US

conn x1

(p

B/B

US

E

41

page

n DDR3L-SO-DIMM X1

BAN

K 0, 1, 2, 3

n DDR3L-SO-DIMM X1

K 4, 5, 6, 7

BAN

OS

CM

Camera

ort 3)

US

B port 7

page

page

18

19

with DDR3 x4

Pr

35

FF

NG

AN

WL

US

B port 5

2 2

page

PC

Ie 1.0

2.5GT/s

t 6

por

PCIe 1.0

2.5GT/s

por

t 5

TA HDD

LA

N(GbE)/ Card Reader

altek 8411B

Re

page

33

SA

Conn.

20~28

page

PC

Ie 3.0 x4

8GT/s

t 1-4

por

SA

TA3.0 SATA3.0

por

t 7

(S

ATA0) (SATA1)

TA CDROM

SA

Conn.

Fl

exible IO

6.0 Gb/s6.0 Gb/s

por

t 8

ocessor

al Core + GT2

Du

15

W

1356pi

page

n BGA

06~17

US

Bx8

HD

SP

48M

Audio

I

Hz

37 page 29

page

3.3V 24MHz

page

HDA

C255

AL

37

Codec

page

Touch

Screen

I2

C (PORT1)

B port 6

40

US

page

29

Ca

rd Reader

in 1 (SD)

2

3 3

page

34

RT

C CKT.

Power On/Off CKT.

DC/DC Interface CKT.

4 4

wer Circuit DC/DC

Po

RJ

45 conn.

page

14

page

39

page

page

42

page 43~55

A

C/eSPI BUS

LP

page 36

34

Sub

Board

LS-C341

US

B+Audio/B

page

37

page

36

Int.KBD

B

page

ENE

KB9022

39

CLK

=24MHz

TP

page

38

Touch Pad

2 (from EC) / I2C (from SOC)

PS

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGIN EERING DRAWING IS THE PROPRI ETARY PRO PERTY OF C OMPAL ELE CTRONI CS, INC . A ND CONTAI NS CONFIDENTIAL

THIS SHEET OF ENGIN EERING DRAWING IS THE PROPRI ETARY PRO PERTY OF C OMPAL ELE CTRONI CS, INC . A ND CONTAI NS CONFIDENTIAL

THIS SHEET OF ENGIN EERING DRAWING IS THE PROPRI ETARY PRO PERTY OF C OMPAL ELE CTRONI CS, INC . A ND CONTAI NS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THI S SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THI S SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THI S SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

M

page

39

page

39

2014/11/10 2016/11/10

2014/11/10 2016/11/10

2014/11/10 2016/11/10

C

I ROM x2

SP

mpal Secret Data

mpal Secret Data

mpal Secret Data

Co

Co

Co

Deciphered Date

Deciphered Date

Deciphered Date

page

UA

In

8

D

t. Speaker

page

tle

tle

tle

Ti

Ti

Ti

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

stom

stom

stom

Cu

Cu

Cu

Date: Sheet

Date: Sheet

Date: Sheet

In

t. MIC

40

WAS M/B LA-C611P

WAS M/B LA-C611P

WAS M/B LA-C611P

A4

A4

A4

page

mpal Electronics, Inc.

mpal Electronics, Inc.

mpal Electronics, Inc.

Co

Co

Co

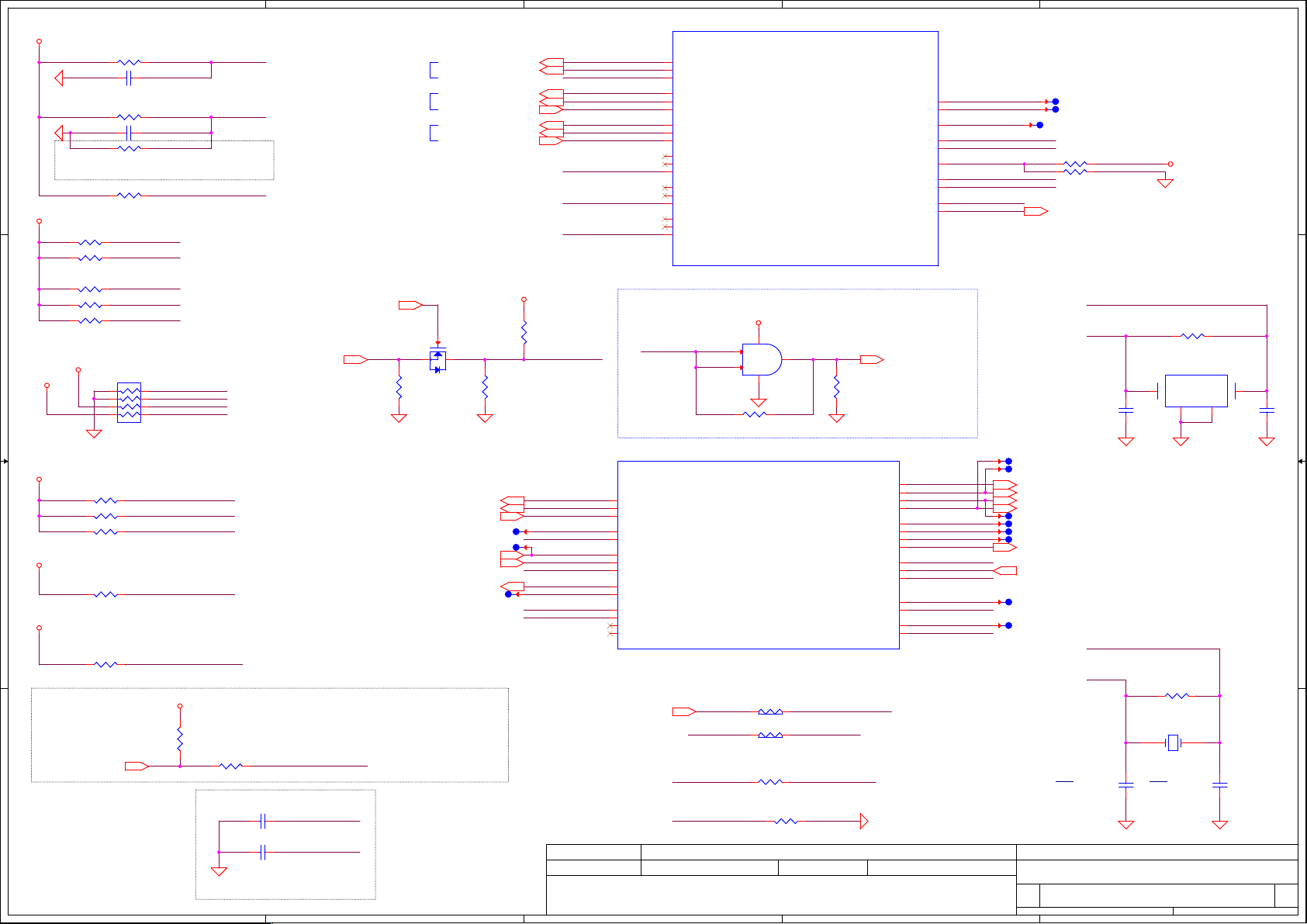

Bl

Bl

Bl

ock Diagrams

ock Diagrams

ock Diagrams

40 page 37

E

J

on Sub/B

260Tuesday, June 16, 2015

260Tuesday, June 16, 2015

260Tuesday, June 16, 2015

of

of

of

0

0

0

1.

1.

1.

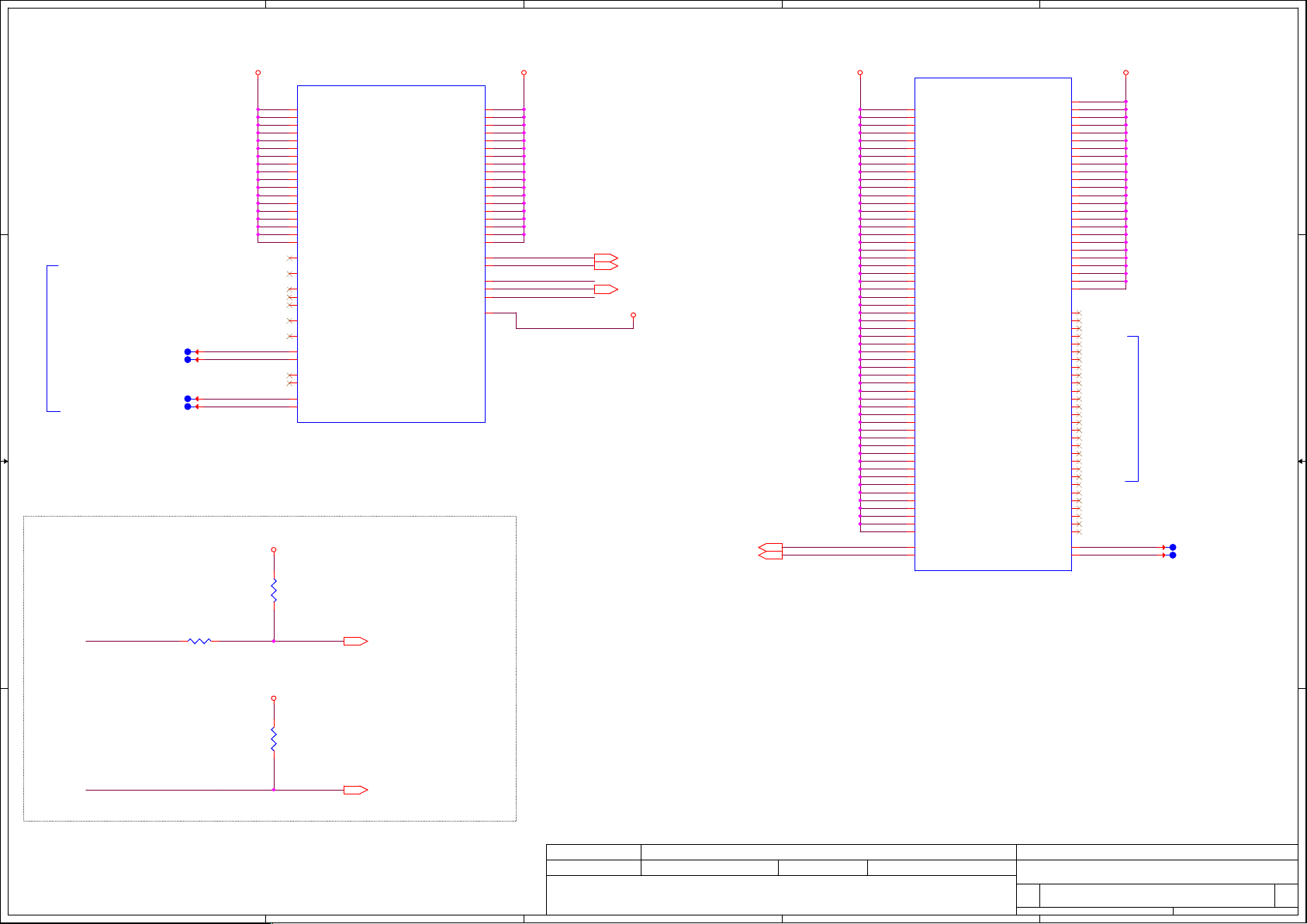

A

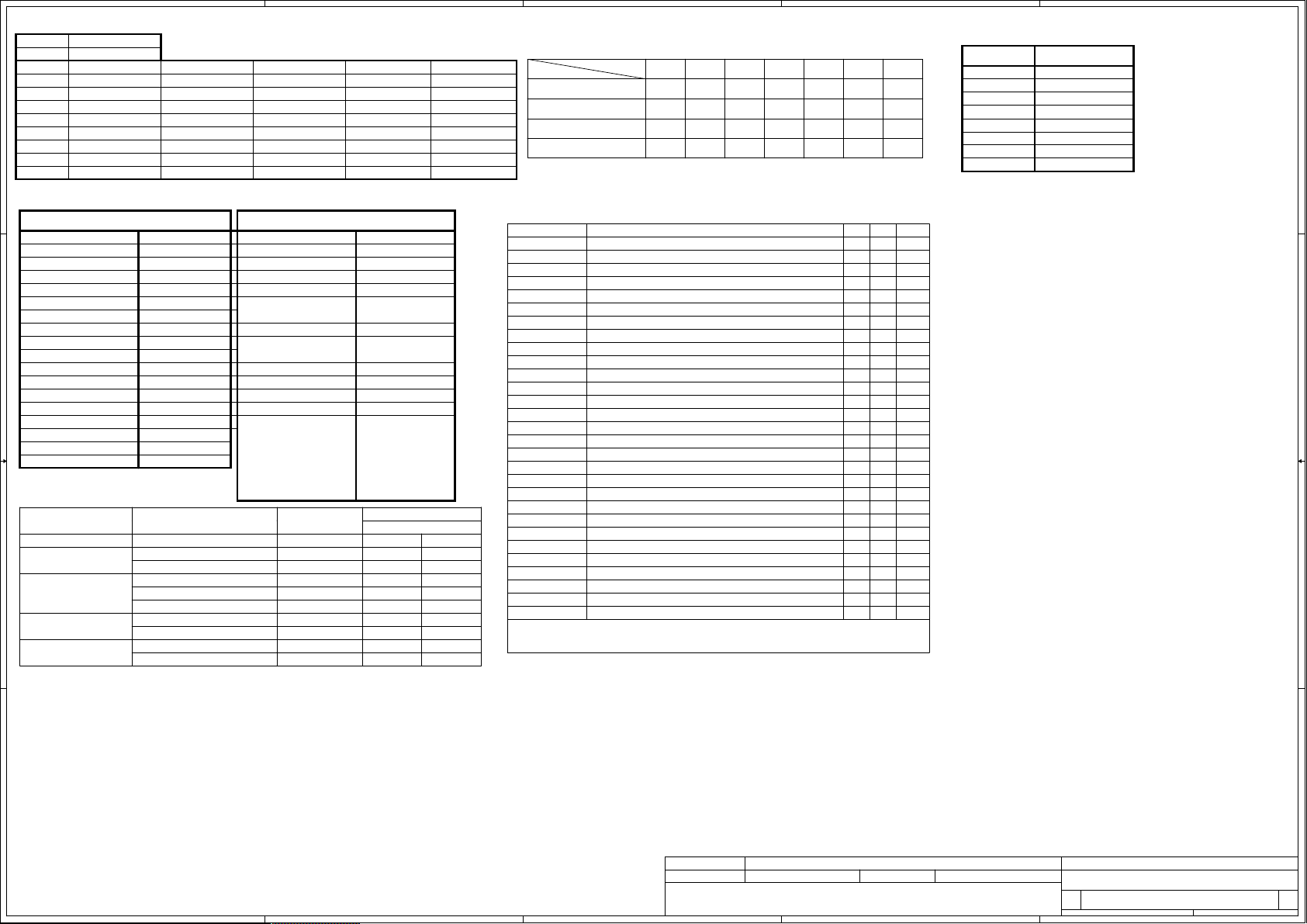

ard ID Table for AD channel

Bo

Vcc 3.3V

Board

ID

0

1

2

3

1 1

4

5

6

7

M Structure Table

BO

em BOM Structure

It

pop

Un

onnector

C

C requirement

EM

MC requirement depop

E

DEC(ALC255)

+/- 5%

100K +/- 5%Ra

Rb V min

D

BI

00 V

12K

+/- 1% 0.347 V 0.345 V 0.360 V

15K +/- 1%

+/- 1%

20K

0.423 V 0.430 V 0.438 V

Vtyp

D

BI

0 V 0.300 V

27K +/- 1%

33K +/- 1%

43K +/- 1%

56K +/- 1%

BO

M Option Table

@

CONN@

EMC@

@EMC@

255@CO

BO

M Option Table

em BOM Structure

It

PU

dG

6S-GT

N1

6V-GM SKU

N1

GPU

CG6 / Non GC6

VRAM BOM Select X76@/X7601@ ~

CODEC(ALC283) 283@

SPI ROM 8M*2 8M_DUAL@

8M

SP

I ROM 8M*1

2 2

UMA only

TP

M

_SINGLE@

A@

UM

TP

M@

CMC@For Intel CMC

@For ES Sampel Only

Keyboard bac klight

LPC MODE for EC

ES

KB@

LPC@

Memory

Door/

No Memory Door

IC*2 2DMIC@

DM

No Acer IOAC NIOAC@

CPU Code PreES:QH7Y@

ESPI@ESPI MODE for EC

BA

Serial

BA

@

HDD@EA Seria l

C Address Table

I2

ess(7 bit)

S

BU

I2C_0 (+3VS)

3 3

SO

C_SMBCLK +3VS

vice

De

Reserved (Touch Panel)

TM

-P2969-001 (TP)I2C_1 (+3VS)

SB8

787-1200 (TP-ELAN)

MM1

DI

DIMM2

LIS3D

HTR(G-Sensor)

N1

6S-GT (VGA)

PCH-LP (SOC)

BQ

EC_SMB_CK1 +3VLP

24780 (Charger IC)

BATTERY PACK

Addr

0x

2C

0x15

0x

A0

0xA4

0x

30

9ESOC_SML1CLK +3VS

0x

0x

90

0x

12

16

0x

B

V

max

D

BI

VGA@

SGT@

M@

VG

/

GC6@

NGC6@

X7614@

SR@/DR@Single/Dual Rank

MD

Y@/ MDN@

1DMIC@DMIC*1

IOAC@For Acer IOAC

ES:QHMF@, QHM G@

QS:QJFC@, QJ8N@,

QJ8L@

:SR2EU@,

MP

SR2EY@, SR2EZ@

Address(8bit)

Wr

ite

EC AD3

0x00 - 0x0B

0x0C - 0x1C

0x1D - 0x26

0x27

- 0x300.541 V 0.550 V 0.559 V

0x31 - 0x3B0.691 V 0.702 V 0.713 V

0x3C - 0x460.807 V 0.819 V 0.831 V

0x47 - 0x540.978 V 0.992 V 1.006 V

0x55 - 0x641.169 V 1.185 V 1.200 V

ad

Re

C

Po

wer State

E

STAT

S0 (Full ON) ON ON ON ONHIGH HIGH HIGH

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

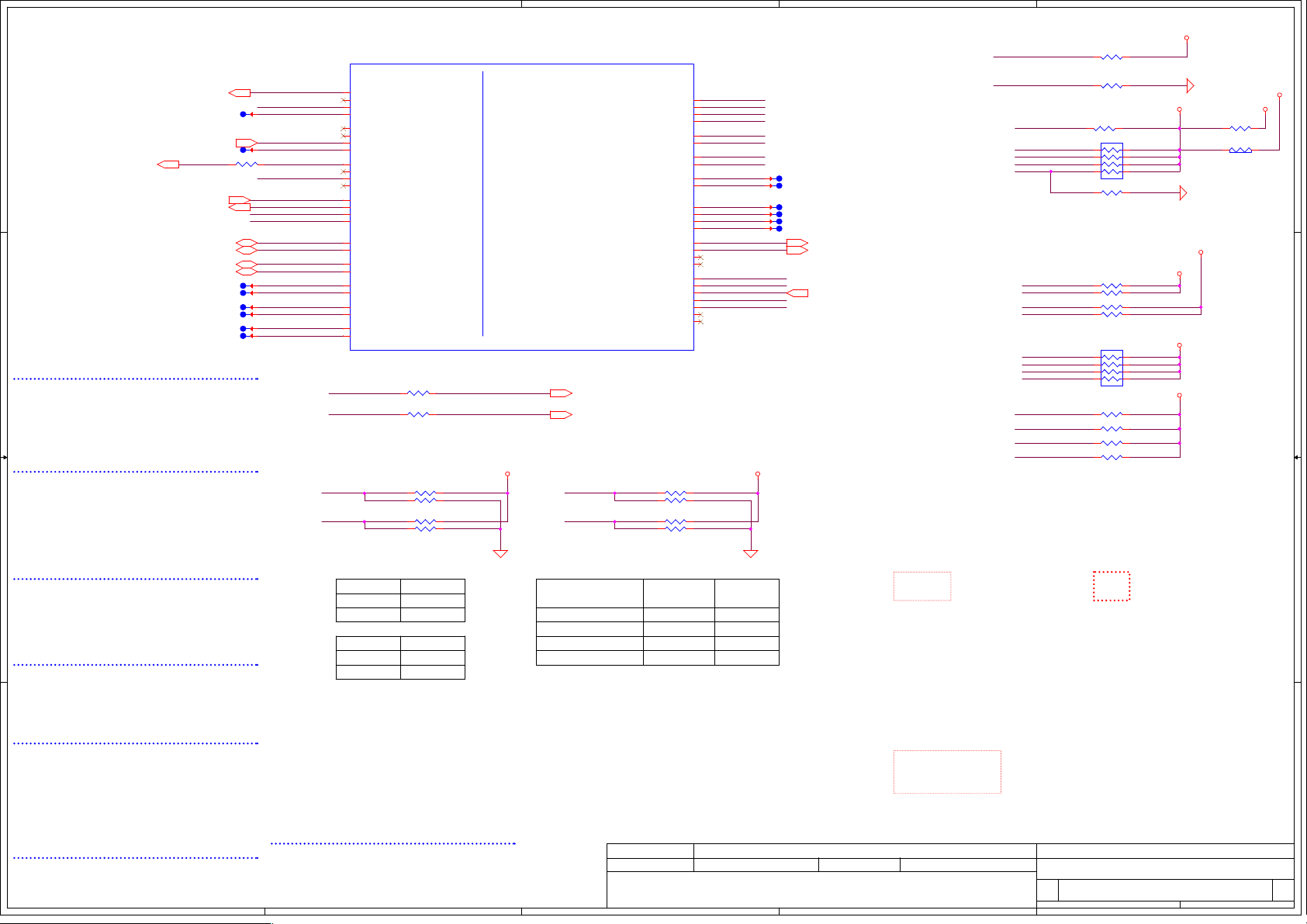

Vo

ltage Rail s

wer Plane

Po

+1

9V_VIN

+17.4V_BATT

+19VB

+VCC_CORE

+VCC_GT

CC_SA

+V

+0

.675VS_VTT

.0VALW_PRIM +1.0V Always power rail

+1

+1

.0V_VCCSTU Sustain voltage for processor in Standby modes

+VCCIO

.0VS_VCCSTG +1.0VALW_PRIM Gated version of VCCST

+1

+1

.35V_VDDQ

+1.8VALW_P RIM +1.8V Always power rail

+1

.8VS System +1.8V power rail

VLP +19VB to +3VLP power rail for suspend power

+3

+3

VALW System +3VALW always on power rail

VS

+3

+5VALW

VS System +5V power rail

+5

+RTCVCC

+1

.05VSDGPU +1.05VS power rail for GPU

.5VSDGPU +1.5VS power rail for GPU

+1

+3VSDGPU_AON +3VS pow er rail for GPU(AON rails)

VSDGPU_MAIN +3VS power rail for GPU GC 62.0

+3

+VGA_CORE

te : ON*1 means power plane is ON only when WOL enable and RTC w ake at BIOS setting, otherwise it is OFF.

No

SIGNAL

SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

LOW HIGH

scription

De

Adap ter p owe r sup ply

Ba

ttery power supply

AC or ba tte ry pow er ra il for p owe r c irc uit .

Pr

ocessor IA Cores Power Rail

Processor Graphics Power Rails

Sy

stem Agent power rail

DDR

+0.675VS power rail for DDR terminator .

CP

U IO power rail

DDRIIIL +1.35V Power Rail

stem +3V power rail

Sy

+5V Always power rail

RT

C Battery Power

re power for descrete GPU

Co

HIGH

LOWLOW

HIGH

ONONON

ON

OFF

OFFLOW LOW LOW

S0

N/A

N/A

N/A

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

OFF

OFF

OFF

S3

N/A N/A

OFF

OFF

OFF

ON

ON

OFF OFF

ON

ON

OFF

ON

ON

OFF

ON

ON ON

OFF OFF

OFF

OFF

OFF

OFF

OFF

S4

N/AN/A

N/AN/A

OFF

OFF

OFF

OFFOFF

ON

OFF

OFFOFF

OFF

ON*1

OFF

ON

ON

OFF

ON

OFFOFF

OFFOFF

OFF

OFF

OFFOFF

D

BO

ARD ID Table

Board ID

0

1

2

3

4

PCB Revision

0.

1

2

0.

0.3

0

1.

E

5

6

7

/S5

*1

*1

4 4

curity Classification

curity Classificat ion

curity Classificat ion

Se

Se

Se

Is

Is

Is

sued Date

sued Date

sued Date

S SHEE T OF ENGINEERI NG DR AWING IS THE PROPRIE TARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

S SHEE T OF ENGINEERI NG DR AWING IS THE PROPRIE TARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

S SHEE T OF ENGINEERI NG DR AWING IS THE PROPRIE TARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THI

THI

THI

AND TRADE SECRET INFORM ATION. THIS SHEET M AY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORM ATION. THIS SHEET M AY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORM ATION. THIS SHEET M AY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRI TTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRI TTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRI TTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2014/

2014/

2014/

11/10 2016/11/10

11/10 2016/11/10

11/10 2016/11/10

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Dat e

Deciphered Dat e

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Ti

Ti

Ti

tle

tle

tle

tes List

tes List

tes List

No

No

No

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

stom

stom

stom

Cu

Cu

Cu

A4WAS M/B LA-C611P

A4WAS M/B LA-C611P

A4WAS M/B LA-C611P

Date: Sheet

Date: Sheet

D

Date: Sheet

E

360Thursday, July 16, 2015

360Thursday, July 16, 2015

360Thursday, July 16, 2015

0

0

0

1.

1.

1.

of

of

of

5

D D

C C

4

3

2

1

B B

A A

Se

Se

Se

curity Clas sification

curity Clas sification

curity Clas sification

sued Da te

sued Da te

sued Da te

Is

Is

Is

IS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPER TY OF COMPA L ELE CTRONI CS, I NC. AND CONTA INS CONFIDENTIAL

IS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPER TY OF COMPA L ELE CTRONI CS, I NC. AND CONTA INS CONFIDENTIAL

IS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPER TY OF COMPA L ELE CTRONI CS, I NC. AND CONTA INS CONFIDENTIAL

TH

TH

TH

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USE D BY O R DI SCLO SED TO ANY THI RD PA RTY WIT HOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USE D BY O R DI SCLO SED TO ANY THI RD PA RTY WIT HOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

3

MAY BE USE D BY O R DI SCLO SED TO ANY THI RD PA RTY WIT HOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

11/10 2016/11/10

11/10 2016/11/10

11/10 2016/11/10

2014/

2014/

2014/

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Power Map

Power Map

Power Map

Size

Size

Size

cument Number Rev

cument Number Rev

cument Number Rev

Do

Do

Do

stom

stom

stom

Cu

Cu

Cu

A4WAS M/B LA-C611P

A4WAS M/B LA-C611P

A4WAS M/B LA-C611P

Date: Sheet

Date: Sheet

Date: Sheet

1

1.

1.

1.

of

of

of

460Thursday, July 16, 2015

460Thursday, July 16, 2015

460Thursday, July 16, 2015

0

0

0

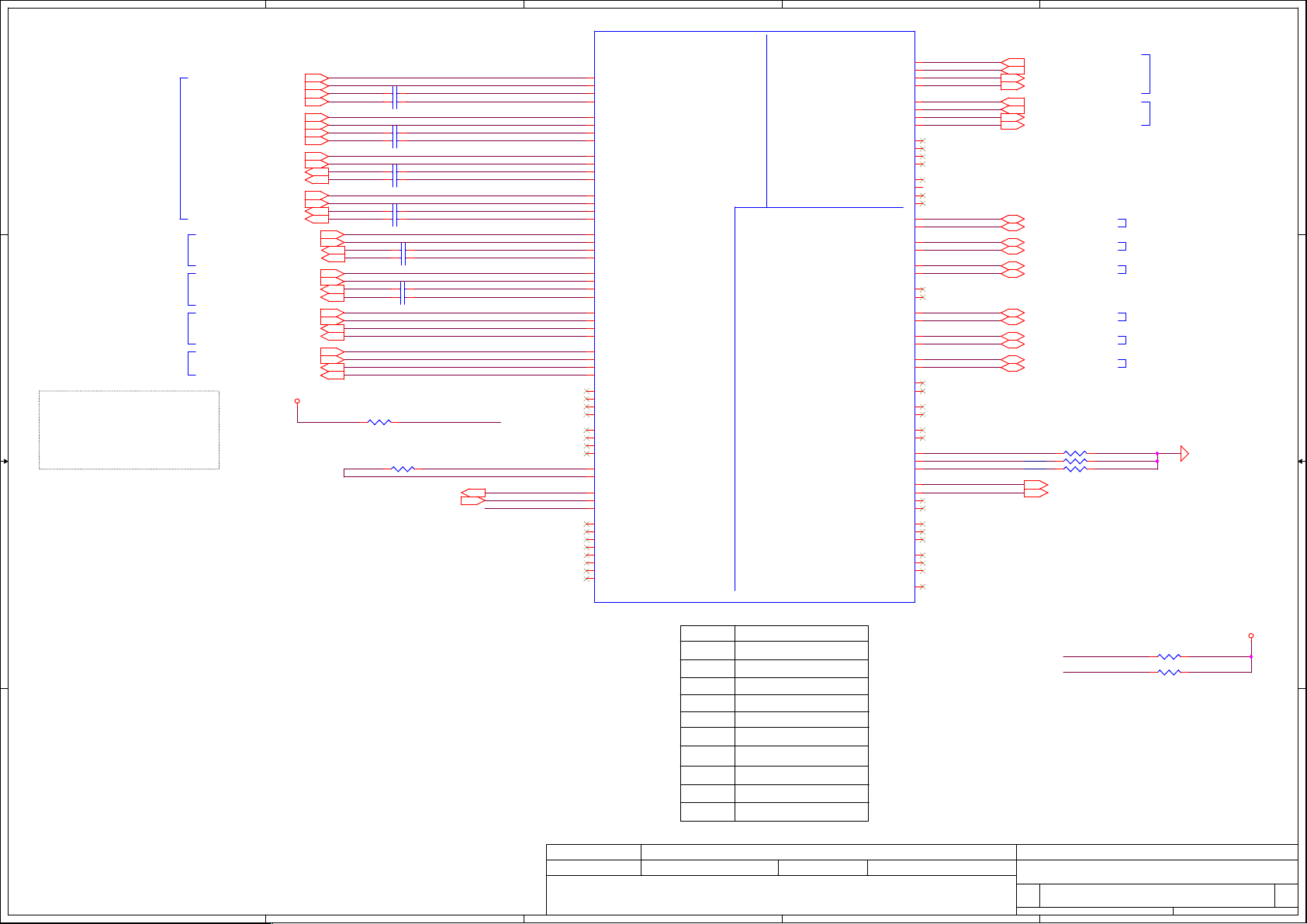

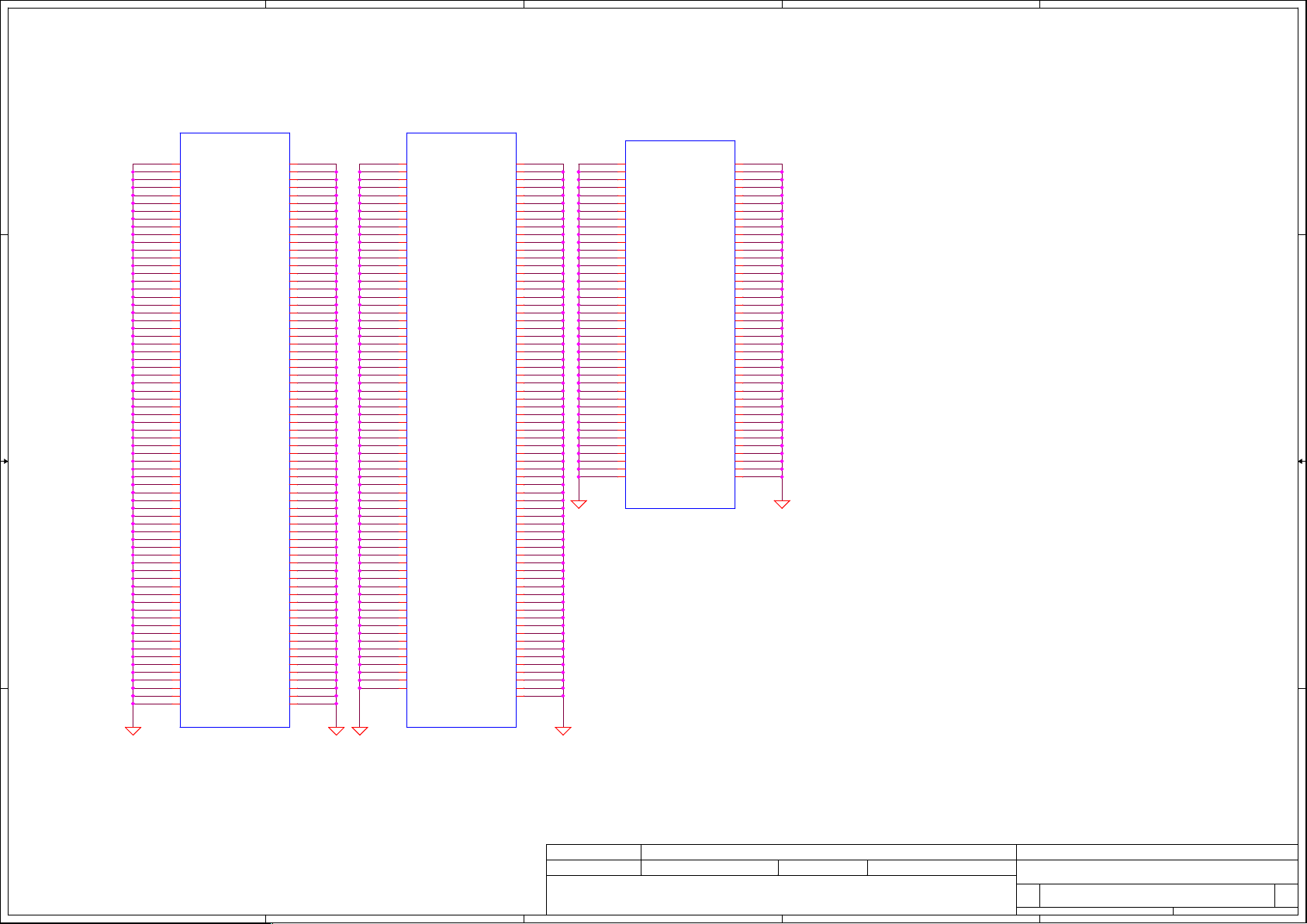

A

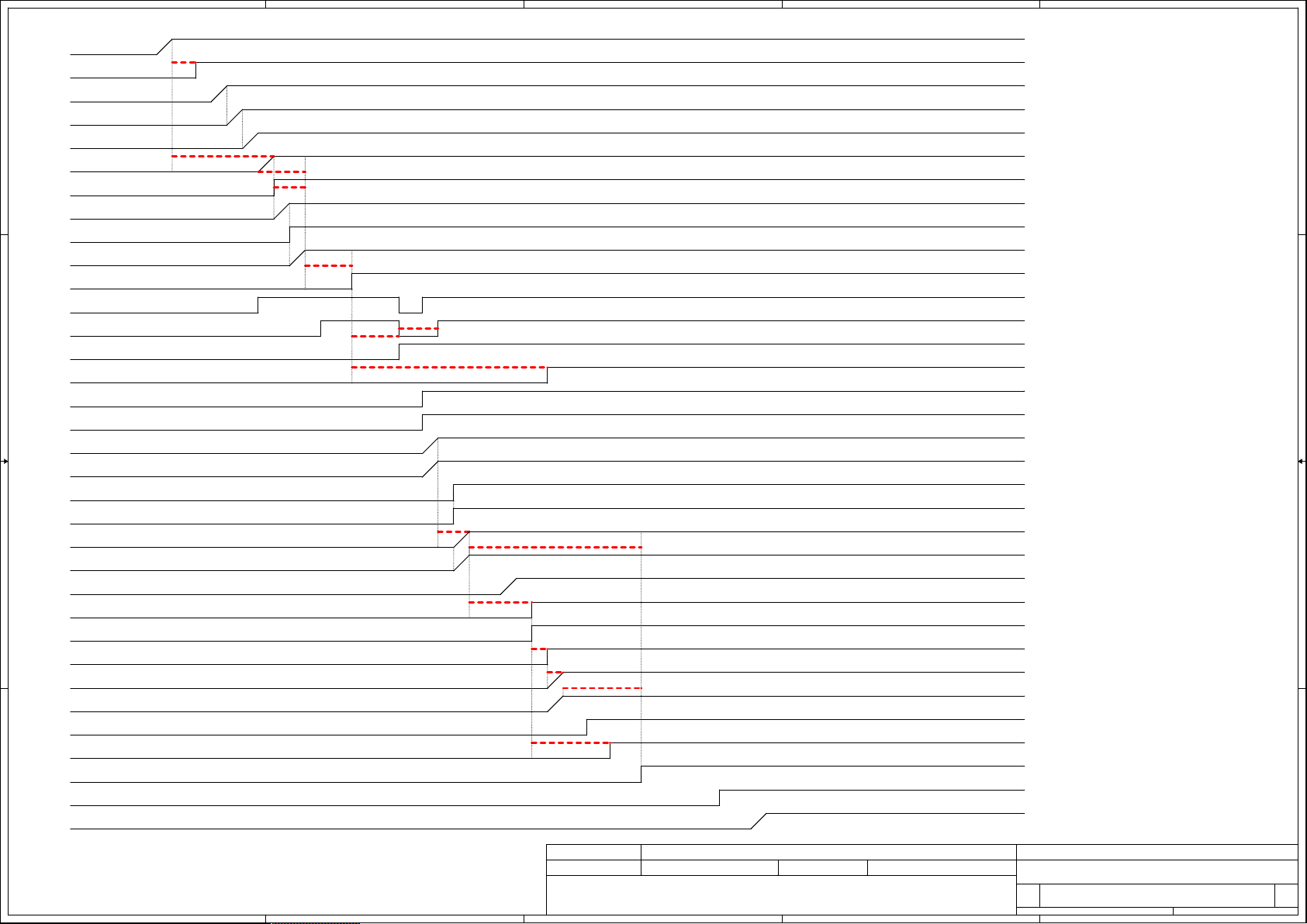

R Sequence_SKL-U2+2_DDR3L_NON CS

PW

+RTCVCC

tPCH01_Min : 9 ms

B

C

D

E

SOC_RTCRST#

+19VB

+3

1 1

VLP

_ON

EC

VALW/+3VALW(+3VALW_DSW...)

+5

tPCH04_Min : 9 ms

tPCH34_Max : 20 ms

SPOK tPCH06_Min : 200 us (+3VALW stable (@95% of full value) to +1.0VALW_PRIM starting to ramp)

+1.8VALW_PRIM

+1.8VALW_PG

+V

CCPRIM_CORE/+1.0VALW_PRIM

_RSMRST#

EC

tPCH03_Min : 10 ms

ON/OFF

PB

TN_OUT#

2 2

_SLP_S5#

PM

tPCH43_Min : 95 ms

Minimum duration of PWRBTN# assertion = 16mS. PWRBTN# can assert before or after RSMRST#

tP

CH18_Min : 90 us

ESPI_RST#

PM_SLP_S4#

SYSON

+1.0V_VCCSTU

+1.35V_VDDQ

PM_SLP_S3#

SUSP#

+1.0VS_VCCSTG

U04 Min : 100 ns

tCP

tCPU10 Min : 1 ms

+VCCIO

3 3

+5VS/+3VS/+1.8VS/+1.5VS

_VCCST_PG

EC

VR

_ON

SM_PG_CTRL

+0.675VS_VTT

tCPU00 Min : 1 ms

tCPU19 Max : 100 ns

tCPU18 Max : 35 us

tCPU09 Min : 1 ms

+VCC_SA

VR_PWRGD

PCH_PWROK (SYS_PWROK)

tCPU16 Min : 0 ns

tPLT05 Min : Platform dependent

H_CPUPWRGD

4 4

PLT_RST#

+V

CC_CORE / +VCC_GT

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

TH

TH

TH

IS SHEET OF ENGINEE RING D RAWING IS THE PROPRIE TARY PRO PERTY OF C OMPAL ELEC TRONIC S, INC. A ND CONTAI NS CONFIDENTIAL

IS SHEET OF ENGINEE RING D RAWING IS THE PROPRIE TARY PRO PERTY OF C OMPAL ELEC TRONIC S, INC. A ND CONTAI NS CONFIDENTIAL

IS SHEET OF ENGINEE RING D RAWING IS THE PROPRIE TARY PRO PERTY OF C OMPAL ELEC TRONIC S, INC. A ND CONTAI NS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THI S SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THI S SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THI S SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

C

11/10 2016/11/10

11/10 2016/11/10

11/10 2016/11/10

2014/

2014/

2014/

mpal Secret Data

mpal Secret Data

mpal Secret Data

Co

Co

Co

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

tle

tle

tle

Ti

Ti

Ti

Power Sequence

Power Sequence

Power Sequence

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

stom

stom

stom

Cu

Cu

Cu

A4WAS M/B LA-C611P

A4WAS M/B LA-C611P

A4WAS M/B LA-C611P

Date: Sheet

Date: Sheet

D

Date: Sheet

560Thursday, July 16, 2015

560Thursday, July 16, 2015

560Thursday, July 16, 2015

of

of

E

of

0

0

0

1.

1.

1.

A

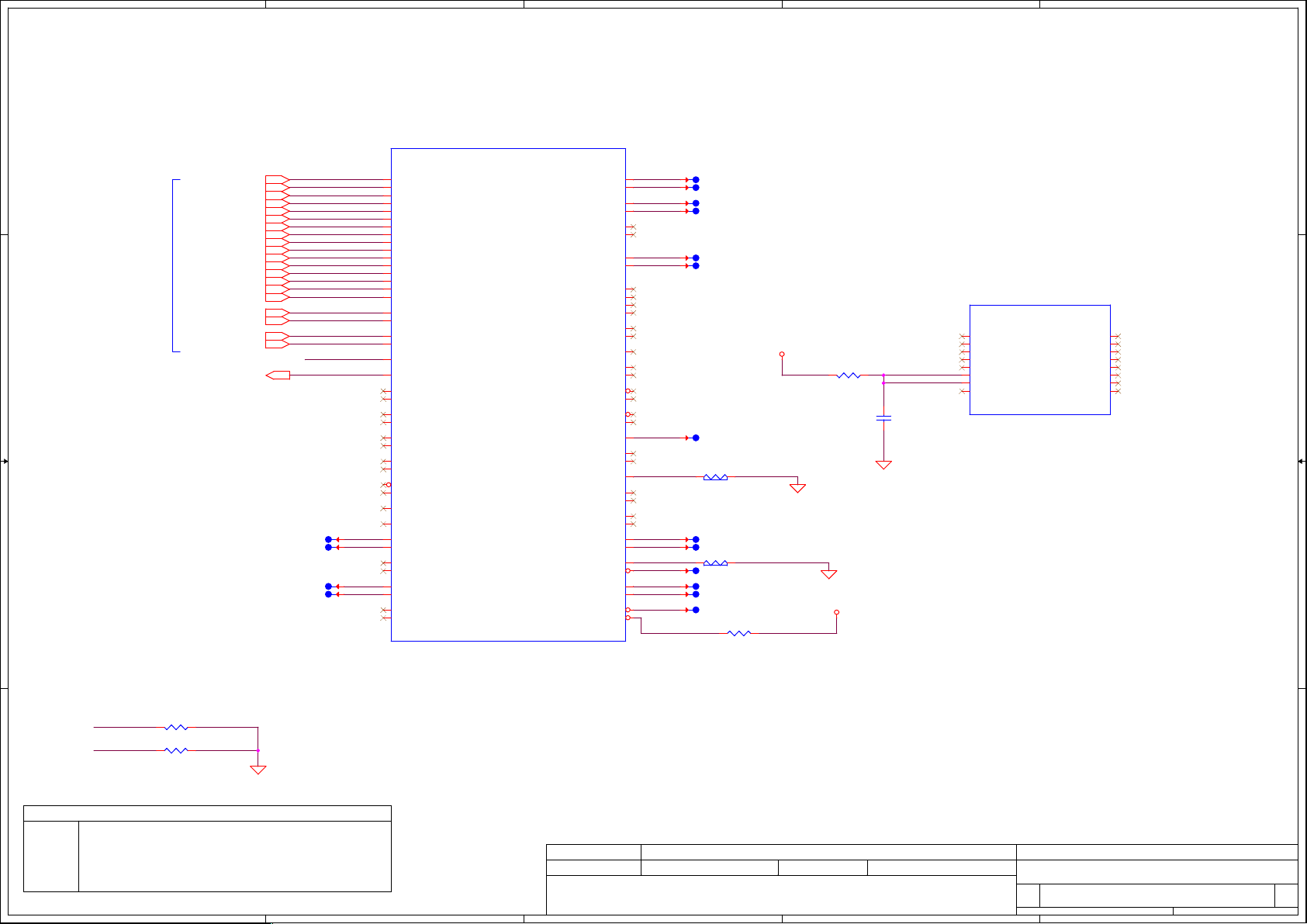

Func

tional Strap Definitions

PDG0.9 P.775

#543016

B_CTRLDATA/ GPP_E19 (Internal Pull Down):

DDP

DDPC_CTRLDATA/ GPP_E21 (Internal Pull Down):

DDPD_CTRLDATA/ GPP_E23 (Internal Pull Down):

(Sampled:Rising edge of PCH_PWROK)

Display Port B/C/ D Detected

0 =Port is not detected.

1 1

1 =Port is detected.

CO

MPENSATION PU FOR eDP

+V

CCIO

ED

RC1

1 2

#5

43016 PDG0.9 P.186

Trace widt h=20 m ils, Spac ing= 25mi l,Ma x le ngth= 100m ils

.0V_VCCST

+1

1 2

RC2

+3

VS

RC1

57 100K_0402_5%

2 2

Reserved for ESD 2014/9/17

P_COMP

24.9_0402_1%

#5

43016 PDG0.9 P.753

PH 1K to VCCST

CPU over 130 degree will output low force S0->S5

THERMTRIP#

H_

1K_0402_5%

_INT#

H_

PECI

PROCHOT#_R

H_

TP

1 2

CC5

.1U_0402_16V7K

CC5

.1U_0402_16V7K

2

12

3

12

@EMC@

@EMC@

HDMI DDC (Port C)

SPI touch RST follow CRB #544669 P.8

+1

H_

PROCHOT#38,45

SPI touch INT follow CRB

_TP_INT#38,39

EC

PDG0.9

P.771

PROC_POPIR COMP/PCH_ OPIRCOMP

PD 50ohm

CRB RVP7 1.0

#544669

EDRAM_OPIO_ RCOMP/EOP IO_RCOMP

PD50ohm

+3

<DP

<HDMI>

VS

+3

R4

955 2.2K_0402_5%

.0VS_VCCSTG

12

RC3

1K

_0402_5%

RC4

15 100K_0402_5%

R6

VS

D2

2

RB751V-40_SOD323-2

RC1

B

to VGA>

SO

C_DP2_CTRL_CLK30

SO

C_DP2_CTRL_DATA30

1 2

1 2

1 2

37 0_0402_5%@

RC5

RC6

RC7

RC8

12

Reserved

sightings issue check

499_0402_1%

C_TS_INT#29

I2

12

12

49.9_0402_1%

12

49.9_0402_1%

49.9_0402_1%

12

12

49.9_0402_1%

H_

SO

C_DP1_N031

SO

C_DP1_P031

SO

C_DP1_N131

SO

C_DP1_P131

SO

C_DP2_N030

SO

C_DP2_P030

SO

C_DP2_N130

C_DP2_P130

SO

C_DP2_N230

SO

C_DP2_P230

SO

SO

C_DP2_N330

SO

C_DP2_P330

T166@

PECI38

T1

T1

C_DP1_CTRL_DATA

SO

SO

C_DP2_CTRL_CLK

SO

C_DP2_CTRL_DATA

P_COMP

ED

CATERR# for

60@

61@

I2

C_TS_INT#

CP

U_POPIRCOMP

PC

H_OPIRCOMP

RAM_OPIO_RCOMP

ED

PIO_RCOMP

EO

H_

CATERR#

H_

PECI

H_

PROCHOT#_R

THERMTRIP#

H_

P_BPM#0

XD

XD

P_BPM#1

C_TS_INT#

I2

_INT#

TP

UC1A

E55

DDI

1_TXN[0]

F55

DDI

1_TXP[0]

E58

1_TXN[1]

DDI

F58

1_TXP[1]

DDI

F53

DDI1_TXN[2]

G53

DDI

1_TXP[2]

F56

DDI

1_TXN[3]

G56

DDI

1_TXP[3]

C50

2_TXN[0]

DDI

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI

2_TXP[1]

A50

DDI

2_TXN[2]

B50

2_TXP[2]

DDI

D51

2_TXN[3]

DDI

C51

2_TXP[3]

DDI

L13

P_E18/DDPB_CTRLCLK

GP

L12

P_E19/DDPB_CTRLDATA

GP

N7

P_E20/DDPC_CTRLCLK

GP

N8

GPP_E21/DDPC_CTRLDATA

N11

GP

P_E22/DDPD_CTRLCLK

N12

GP

P_E23/DDPD_CTRLDATA

E52

P_RCOMP

ED

SKL-U_BGA1356

@

UC1D

D63

CATERR#

A54

PEC

I

C65

PR

OCHOT#

C63

TH

ERMTRIP#

A65

OCC#

SKT

C55

BPM#[0]

D55

BPM

#[1]

B54

BPM

#[2]

C56

BPM

#[3]

A6

P_E3/CPU_GP0

GP

A7

GPP_E7/CPU_GP1

BA5

GPP_B3/CPU_GP2

AY5

GP

P_B4/CPU_GP3

AT16

PR

OC_POPIRCOMP

AU16

H_OPIRCOMP

PC

H66

CE_RCOMP

OP

H65

OPC_RCOMP

SKL-U_BGA1356

@

CP

U MISC

C

DDI

DISPLAY SIDEBANDS

SKL-U

OF 20

4

-U

SKL

1

OF 20

JT

AG

PR

PROC_TDO

PR

PR

PC

H_JTAG_TCK

H_JTAG_TDI

PC

PCH_JTAG_TDO

PCH_JTAG_TMS

PC

ED

P

Rev_0.53

OC_TCK

OC_TDI

PR

OC_TMS

OC_TRST#

H_TRST#

JT

AGX

Rev

_0.53

ED

P_TXN[0]

ED

P_TXP[0]

P_TXN[1]

ED

P_TXP[1]

ED

EDP_TXN[2]

ED

P_TXP[2]

ED

P_TXN[3]

ED

P_TXP[3]

P_AUXN

ED

EDP_AUXP

ED

P_DISP_UTIL

1_AUXN

DDI

1_AUXP

DDI

2_AUXN

DDI

DDI2_AUXP

DDI3_AUXN

DDI

3_AUXP

P_E13/DDPB_HPD0

GP

P_E14/DDPC_HPD1

GP

P_E15/DDPD_HPD2

GP

GPP_E16/DDPE_HPD3

GP

P_E17/EDP_HPD

ED

P_BKLTEN

ED

P_BKLTCTL

P_VDDEN

ED

U_XDP_TCK0

CP

B61

C_XDP_TDI

SO

D60

C_XDP_TDO

SO

A61

SO

C_XDP_TMS

C60

SO

C_XDP_TRST#

B59

H_JTAG_TCK1

PC

B56

C_XDP_TDI

SO

D59

C_XDP_TDO

SO

A56

C_XDP_TMS

SO

C59

SO

C_XDP_TRST#

C61

CP

U_XDP_TCK0

A59

D

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

C_DP1_AUXN

SO

G50

C_DP1_AUXP

SO

F50

E48

F48

G46

F46

C_DP1_HPD

SO

L9

C_DP2_HPD

SO

L7

L6

EC

_SCI#

N9

CP

U_EDP_HPD

L10

R12

EN

BKL

C_BKL_PWM

SO

R11

C_ENVDD

SO

U13

#545659 PCH EDS 0.7 P.108

SCI capability is available on all GPIOs,

while NMI and SMI capability is available on

selected GPIOs only.

Below are the PCH GPIOs that can be routed to

generate SMI# or NMI:

ED

P_TXN0 29

ED

P_TXP0 29

ED

P_TXN1 29

ED

P_TXP1 29

ED

P_TXN2 29

P_TXP2 29

ED

P_TXN3 29

ED

ED

P_TXP3 29

ED

P_AUXN 29

ED

P_AUXP 29

C_DP1_AUXN 31

SO

SO

C_DP1_AUXP 31

SO

C_DP1_HPD 31

SO

C_DP2_HPD 30

EC

_SCI# 38

CP

U_EDP_HPD 29

BKL 38

EN

C_BKL_PWM 29

SO

C_ENVDD 29

SO

GPP_B14, GPP_B20, GPP_B23

GPP

_C[23: 22]

GPP_

D[4:0]

GPP_E[8:0],

GPP_E[16:13]

<eDP>

DP Aux (Port B for VGA)

From VGA Trans.

From HDMI

eDP

From

E

12

RC2

10K_0402_5%

_SCI#

EC

1 2

EC_SCI# SOC internal PU

VS

+3

@

+1

.0VS_VCCSTG

SO

B

C_XDP_TMS

SO

C_XDP_TDI

C_XDP_TDO

SO

C_XDP_TDO

SO

P_ITP_PMODE

XD

XDP_PRSENT_CPU

P_PRSENT_PCH

XD

CPU_XDP_TCK0

H_JTAG_TCK1

PC

CF

G0

P_SPI_SI

XD

CMC@

C2

SO

C_XDP_TMS

SO

C_XDP_TDI

C_XDP_TRST#

SO

C_XDP_TDO

SO

CF

G3

P_ITP_PMODE17

XD

P_SPI_SI8

XD

P_SPI_IO28

XD

EC

_RSMRST#10,38

XDP_ITP_PMODE XDP_HOOK6

P_SPI_SI

XD

H_JTAG_TCK1

PC

CPU_XDP_TCK0 XDP_TCK0

P_SPI_IO2

XD

RP

1 8

2 7

3 6

4 5

0_0804_8P4R_5%

1 2

RC5

5 0_0402_5%CMC@

RC56 0_0402_5%CMC@

1 2

CMC@

RPC15

1 8

2 7

3 6

4 5

0_0804_8P4R_5%

RC23 1K_0402_5%CMC@

1 2

curity Classification

curity Classificat ion

curity Classificat ion

Se

Se

Se

Is

Is

Is

sued Date

sued Date

sued Date

S SHEE T OF ENGINEERI NG DR AWING IS THE PROPRIE TARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

S SHEE T OF ENGINEERI NG DR AWING IS THE PROPRIE TARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

S SHEE T OF ENGINEERI NG DR AWING IS THE PROPRIE TARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THI

THI

THI

AND TRADE SECRET INFORM ATION. THIS SHEET M AY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORM ATION. THIS SHEET M AY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORM ATION. THIS SHEET M AY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRI TTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRI TTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRI TTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

XD

P_TMS

XD

P_TDI

P_TRST#

XD

P_TDO

XD

P_PRSENT_CPU

XD

P_HOOK3

XD

P_TCK1

XD

P_PRSENT_PCH

XD

XDP_HOOK0EC_RSMRST#

JPCMC1

1

CF

CF

G017

CF

G117

CF

G217

CF

G317

CFG417

CF

G517

CFG617

CF

G717

CFG1717

CF

G1617

CF

G817

CFG917

CFG1017

CF

G1117

CFG1217

CF

G1317

CFG1417

G1517

CF

CFG1917

CF

G1817

Compal Secret Data

Compal Secret Data

2014/

2014/

2014/

11/10 2016/11/10

11/10 2016/11/10

11/10 2016/11/10

Compal Secret Data

G0

CF

G1

CF

G2

G3

CF

CF

G4

CF

G5

CF

G6

CF

G7

CF

G17

CFG16

CF

G8

CF

G9

CF

G10

CFG11

CF

G12

CFG13

CF

G14

CF

G15

CF

G19

CFG18

Deciphered Date

Deciphered Dat e

Deciphered Dat e

D

DATA_0

3

DATA_1

5

TA_2

DA

7

TA_3

DA

9

DA

TA_4

11

DA

TA_5

13

DA

TA_6

15

DATA_7

17

TA_CLK_1P

DA

21

DA

TA_CLK_1N

2

DA

TA_8

4

DA

TA_9

6

DATA_10

8

TA_11

DA

10

TA_12

DA

12

DA

TA_13

14

DA

TA_14

16

DA

TA_15

18

DATA_CLK_2P

20

TA_CLK_2N

DA

INTEL_CMC_PRIMARY

CONN@

+1

.0VALW_PRIM

OB

S DATA

XD

P CONN

1 2

RC1

2 0_0603_5%@

CMC_

+1

.0V_XDP

DEBUG_36P

JT

AG/RC/HOOKS

VCCOBS_AB

XD

P_TRST*

XD

XD

XDP_TCK0

XDP_TCK1

XD

XD

P_PREQ*

XD

P_PRDY*

HOOK_0

HO

HO

XD

P_PRSNT_PCH*

XD

P_PRSNT_CPU*

<M

Ti

Ti

Titl e

tle

tle

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

stom

stom

stom

Cu

Cu

Cu

Date: Sheet

Date: Sheet

Date: Sheet

+1

.0V_XDP

22

P_TRST#

XD

28

P_TDI

XD

29

P_TDI

XDP_TMS

30

P_TMS

P_TDO

OK_3

OK_6

T> GND

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SKL-U(1/12)DDI,MSIC,XDP,EDP

SKL-U(1/12)DDI,MSIC,XDP,EDP

SKL-U(1/12)DDI,MSIC,XDP,EDP

P_TCK0

XD

32

XDP_TCK1

31

P_TDO

XD

35

P_PREQ#

XD

33

P_PRDY#

XD

34

P_HOOK0

XD

27

P_HOOK3

XD

25

P_HOOK6

XD

26

P_PRSENT_PCH

XD

24

P_PRSENT_CPU

XD

23

19

GND

36

A4WAS M/B LA-C611P

A4WAS M/B LA-C611P

A4WAS M/B LA-C611P

E

XD

XD

660Monday, Jun e 22, 2015

660Monday, Jun e 22, 2015

660Monday, Jun e 22, 2015

P_PREQ# 12

P_PRDY# 12

of

of

of

0

0

0

1.

1.

1.

12

1 51_0402_5%CMC@

RC1

3 51_0402_5%CMC@

+1

.0V_XDP

VALW_PRIM

+3

RC1

RC1

RC1

RC3

RC43 0_0402_5%@

RC4

RC35 51_0402_1%CMC@

RC37 51_0402_5%@

RC151 1K_0402_5%@

RC9 1K_0402_5%CMC@

Place to CPU side

3 3

S CONN

AP

+3VALW_PRIM+3VALW

JA

PS1

1

1

_SLP_S3#10,38,42

PM

_SLP_S5#10

PM

PM

_SLP_S4#10,38,42

_SLP_A#10

PM

C_RTCRST#10

SO

SYS_

RESET#10

PM

_SLP_S0#10, 38

4 4

PBTN_OUT#10,38

ON

/OFFBTN#38,39

PBT

N_OUT#_R2

RC5

RC5

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

GN

D

20

GND

ACES_50506-01841-P01

CONN@

AC

ES_50506-01841-P01_1 8P-NPM

12

3 0_0402_5%@

12

4 0_0402_5%@

A

Place to CPU side

PBT

N_OUT#_R2

12

12

5 51_0402_5%CMC@

12

7 51_0402_5%CMC@

1 2

1 1K_0402_5%CMC@

12

12

6 0_0402_5%@

12

12

12

Follow 544924_Skylake_EDS_Vol_1_ Rev_0.93

1 2

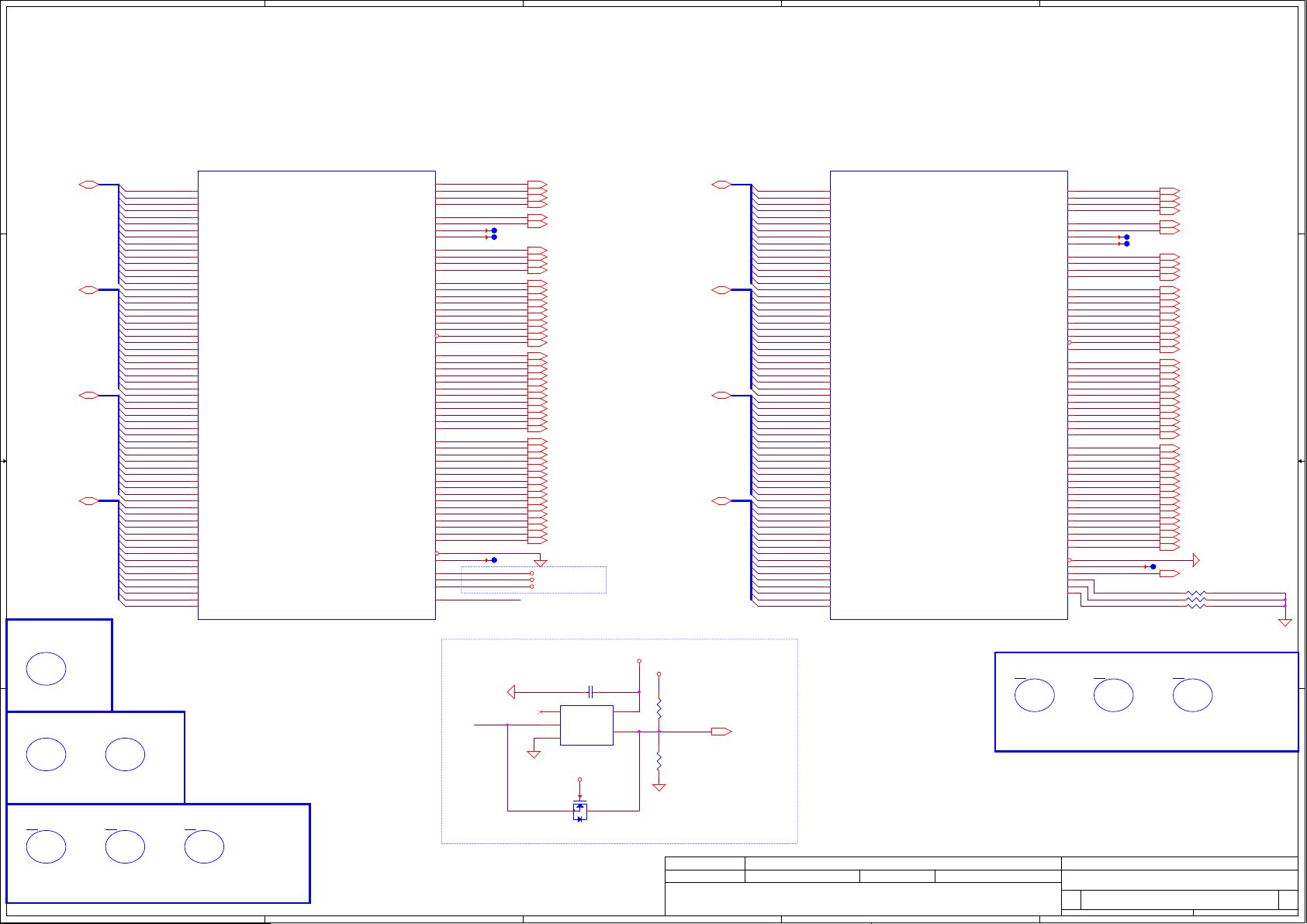

A

nterleaved Memory

I

1 1

SKL

UC1B

A_D[0..15]18

DDR_

DDR_

A_D[16..31]18

2 2

DDR_

A_D[32..47]18

DDR_

A_D[48..63]18

3 3

Sample

Pre_ES

UC1

CP

U_QH7Y_A2_1.6G

QH7Y@

SA0

0008A400

ES Sample

UC1

CPU_QHMF_C0_2.3G

QHMF@

SA0

0008M420

4 4

QS Sample

UC1

UC1

CPU_QHMG_C0_1.6G

QHMG@

SA0

UC1

0008M320

A_D0

DDR_

DDR_

A_D1

DDR_

A_D2

DDR_

A_D3

A_D4

DDR_

A_D5

DDR_

A_D6

DDR_

A_D7

DDR_

A_D8

DDR_

DDR_

A_D9

DDR_

A_D10

A_D11

DDR_

A_D12

DDR_

A_D13

DDR_

A_D14

DDR_

A_D15

DDR_

DDR_

A_D16

DDR_

A_D17

DDR_

A_D18

A_D19

DDR_

A_D20

DDR_

A_D21

DDR_

A_D22

DDR_

DDR_

A_D23

DDR_

A_D24

DDR_

A_D25

A_D26

DDR_

A_D27

DDR_

A_D28

DDR_

A_D29

DDR_

DDR_

A_D30

DDR_

A_D31

DDR_

A_D32

DDR_

A_D33

A_D34

DDR_

A_D35

DDR_

A_D36

DDR_

DDR_

A_D37

DDR_

A_D38

DDR_

A_D39

DDR_

A_D40

A_D41

DDR_

A_D42

DDR_

A_D43

DDR_

DDR_

A_D44

DDR_

A_D45

DDR_

A_D46

DDR_

A_D47

DDR_

A_D48

A_D49

DDR_

A_D50

DDR_

DDR_

A_D51

DDR_

A_D52

A_D53

DDR_

DDR_

A_D54

DDR_

A_D55

A_D56

DDR_

A_D57

DDR_

A_D58

DDR_

DDR_

A_D59

DDR_A_D60

DDR_

A_D61

DDR_A_D62

A_D63

DDR_

AL71

DDR0

AL68

DDR0

AN68

DDR0_DQ[2]

AN69

DDR0

AL70

DDR0

AL69

DDR0

AN70

DDR0

AN71

DDR0

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0

AU68

DDR0

AR71

DDR0

AR69

DDR0

AU70

DDR0

AU69

DDR0_DQ[15]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0

AW63

DDR0

AY63

DDR0

BA65

DDR0

AY65

DDR0

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0

BA61

DDR0

AW61

DDR0

BB59

DDR0

AW59

DDR0

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0

AY59

DDR0

AY39

DDR0

AW39

DDR0

AY37

DDR0

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0

BA37

DDR0

BB37

DDR0

AY35

DDR0

AW35

DDR0

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0

BB35

DDR0

BA35

DDR0

BA33

DDR0

BB33

DDR0

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0

AW29

DDR0

BB31

DDR0

BA31

DDR0

BA29

DDR0

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0

AY25

DDR0

AW25

DDR0

BB27

DDR0

BA27

DDR0

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0

SKL-U_BGA1356

@

UC1

_DQ[0]

_DQ[1]

_DQ[3]

_DQ[4]

_DQ[5]

_DQ[6]

_DQ[7]

_DQ[10]

_DQ[11]

_DQ[12]

_DQ[13]

_DQ[14]

_DQ[17]/DDR0_DQ[33]

_DQ[18]/DDR0_DQ[34]

_DQ[19]/DDR0_DQ[35]

_DQ[20]/DDR0_DQ[36]

_DQ[21]/DDR0_DQ[37]

_DQ[23]/DDR0_DQ[39]

_DQ[24]/DDR0_DQ[40]

_DQ[25]/DDR0_DQ[41]

_DQ[26]/DDR0_DQ[42]

_DQ[27]/DDR0_DQ[43]

_DQ[30]/DDR0_DQ[46]

_DQ[31]/DDR0_DQ[47]

_DQ[32]/DDR1_DQ[0]

_DQ[33]/DDR1_DQ[1]

_DQ[34]/DDR1_DQ[2]

_DQ[37]/DDR1_DQ[5]

_DQ[38]/DDR1_DQ[6]

_DQ[39]/DDR1_DQ[7]

_DQ[40]/DDR1_DQ[8]

_DQ[41]/DDR1_DQ[9]

_DQ[43]/DDR1_DQ[11]

_DQ[44]/DDR1_DQ[12]

_DQ[45]/DDR1_DQ[13]

_DQ[46]/DDR1_DQ[14]

_DQ[47]/DDR1_DQ[15]

_DQ[50]/DDR1_DQ[34]

_DQ[51]/DDR1_DQ[35]

_DQ[52]/DDR1_DQ[36]

_DQ[53]/DDR1_DQ[37]

_DQ[54]/DDR1_DQ[38]

_DQ[57]/DDR1_DQ[41]

_DQ[58]/DDR1_DQ[42]

_DQ[59]/DDR1_DQ[43]

_DQ[60]/DDR1_DQ[44]

_DQ[61]/DDR1_DQ[45]

_DQ[63]/DDR1_DQ[47]

-U

_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0

_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0

_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0

_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0

_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0

_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0

_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0

_CAS#/DDR0_CAB[1]/DDR0_MA[15]

_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0

_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0

_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0

_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0

_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0

DDR0

DDR0

DDR0

DDR0

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0

DDR0

DDR0

DDR0

DDR

CH - A

2 OF 20

B

_CKN[0]

DDR0

_CKP[0]

DDR0

_CKN[1]

DDR0

DDR0_CKP[1]

DDR0

_CKE[0]

DDR0

_CKE[1]

DDR0

_CKE[2]

_CKE[3]

DDR0

DDR0_CS#[0]

DDR0

_CS#[1]

DDR0

_ODT[0]

DDR0

_ODT[1]

DDR0_MA[3]

DDR0_MA[4]

DDR0

_DQSN[0]

DDR0

_DQSP[0]

_DQSN[1]

DDR0

_DQSP[1]

DDR0

_DQSP[2]/DDR0_DQSP[4]

_DQSN[3]/DDR0_DQSN[5]

_DQSP[3]/DDR0_DQSP[5]

_DQSN[4]/DDR1_DQSN[0]

_DQSP[4]/DDR1_DQSP[0]

_DQSN[6]/DDR1_DQSN[4]

_DQSP[6]/DDR1_DQSP[4]

_DQSN[7]/DDR1_DQSN[5]

_DQSP[7]/DDR1_DQSP[5]

DDR0_ALERT#

DDR0_PAR

DDR_

VREF_CA

DDR0

_VREF_DQ

_VREF_DQ

DDR1

DDR_VTT_CNTL

A_CLK#0

DDR_

AU53

A_CLK0

DDR_

AT53

DDR_

A_CLK#1

AU55

DDR_

A_CLK1

AT55

A_CKE0

DDR_

BA56

A_CKE1

DDR_

BB56

AW56

AY56

DDR_

A_CS#0

AU45

DDR_

A_CS#1

AU43

A_ODT0

DDR_

AT45

A_ODT1

DDR_

AT43

A_MA5

DDR_

BA51

A_MA9

DDR_

BB54

DDR_

A_MA6

BA52

DDR_

A_MA8

AY52

DDR_

A_MA7

AW52

A_BS2

DDR_

AY55

A_MA12

DDR_

AW54

A_MA11

DDR_

BA54

A_MA15

DDR_

BA55

DDR_

A_MA14

AY54

DDR_

A_MA13

AU46

A_CAS#

DDR_

AU48

A_WE#

DDR_

AT46

A_RAS#

DDR_

AU50

A_BS0

DDR_

AU52

DDR_

A_MA2

AY51

DDR_

A_BS1

AT48

DDR_

A_MA10

AT50

DDR_

A_MA1

BB50

A_MA0

DDR_

AY50

A_MA3

DDR_

BA50

A_MA4

DDR_

BB52

DDR_

A_DQS#0

AM70

DDR_

A_DQS0

AM69

DDR_

A_DQS#1

AT69

A_DQS1

DDR_

AT70

A_DQS#2

DDR_

BA64

A_DQS2

DDR_

AY64

DDR_

A_DQS#3

AY60

DDR_

A_DQS3

BA60

DDR_

A_DQS#4

BA38

DDR_

A_DQS4

AY38

DDR_

A_DQS#5

AY34

A_DQS5

DDR_

BA34

A_DQS#6

DDR_

BA30

DDR_

A_DQS6

AY30

DDR_

A_DQS#7

AY26

A_DQS7

DDR_

BA26

AW50

AT52

.675V_VREFCA

+0

AY67

+0

.675V_A_VREFDQ

AY68

+0.675V_B_VREFDQ

BA67

DDR_PG_CTRL

AW67

D

DR_VTT_CNTL to DDR

VTT supplied ramped

<35uS

(tCPU18)

DDR_PG_CTRL

Re

serve for cost test.

4@

T1

T1

5@

2@

T2

+0

+0.675V_A_VREFDQ

+0

DDR_

A_CLK#0 18

DDR_

A_CLK0 18

DDR_

A_CLK#1 18

DDR_

A_CLK1 18

A_CKE0 18

DDR_

A_CKE1 18

DDR_

DDR_

A_CS#0 18

DDR_

A_CS#1 18

DDR_

A_ODT0 18

A_ODT1 18

DDR_

DDR_

A_MA5 18

DDR_

A_MA9 18

DDR_

A_MA6 18

DDR_

A_MA8 18

DDR_

A_MA7 18

A_BS2 18

DDR_

A_MA12 18

DDR_

A_MA11 18

DDR_

DDR_

A_MA15 18

DDR_

A_MA14 18

DDR_

A_MA13 18

DDR_A_CAS# 18

A_WE# 1 8

DDR_

A_RAS# 18

DDR_

DDR_

A_BS0 18

DDR_

A_MA2 18

DDR_

A_BS1 18

DDR_

A_MA10 18

DDR_A_MA1 18

A_MA0 18

DDR_

A_MA3 18

DDR_

A_MA4 18

DDR_

DDR_

A_DQS#0 18

DDR_

A_DQS0 18

DDR_A_DQS#1 18

A_DQS1 18

DDR_

A_DQS#2 18

DDR_

A_DQS2 18

DDR_

DDR_

A_DQS#3 18

DDR_

A_DQS3 18

DDR_

A_DQS#4 18

DDR_A_DQS4 18

A_DQS#5 18

DDR_

A_DQS5 18

DDR_

A_DQS#6 18

DDR_

A_DQS6 18

DDR_

DDR_

A_DQS#7 18

DDR_

A_DQS7 18

.675V_VREFCA

.675V_B_VREFDQ

NC1VC

2

A

3

D

GN

74AUP1G07GW_TSS OP5

.35V_VDDQ

+1

G

S

Q2009

@

MESS138W -G_SOT3 23-3

C

B_D[0..15]19

DDR_

DDR_

B_D[16..31]19

DDR_

B_D[32..47]19

DDR_

B_D[48..63]19

Trace

width/Spacing >= 20mils

Place componment near SODIMM

#543016 PDG0.9 P.163 RC place near SODIMM

+1.35V_VDDQ

+3VS

12

CC57.1U_0402_16V7K

UC7

C

Y

12

5

4

RC10

220K_0402_5%

RC16

2M_0402_5%@

1 2

123

D

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_

DDR_B_D60

DDR_

DDR_B_D62

DDR_

SM_PG_CTRL 47

B_D0

B_D1

B_D2

B_D3

B_D4

B_D5

B_D6

B_D7

B_D8

B_D9

B_D10

B_D11

B_D12

B_D13

B_D14

B_D15

B_D16

B_D17

B_D18

B_D19

B_D20

B_D21

B_D22

B_D23

B_D24

B_D25

B_D26

B_D27

B_D28

B_D29

B_D30

B_D31

B_D32

B_D33

B_D34

B_D35

B_D36

B_D37

B_D38

B_D39

B_D40

B_D41

B_D42

B_D43

B_D44

B_D45

B_D46

B_D47

B_D48

B_D49

B_D50

B_D51

B_D52

B_D53

B_D54

B_D55

B_D56

B_D57

B_D58

B_D59

B_D61

B_D63

UC1C

AF65

_DQ[0]/DDR0_DQ[16]

DDR1

AF64

_DQ[1]/DDR0_DQ[17]

DDR1

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1

_DQ[3]/DDR0_DQ[19]

AF66

DDR1

_DQ[4]/DDR0_DQ[20]

AF67

DDR1

_DQ[5]/DDR0_DQ[21]

AK67

DDR1

_DQ[6]/DDR0_DQ[22]

AK66

_DQ[7]/DDR0_DQ[23]

DDR1

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1

_DQ[10]/DDR0_DQ[26]

AH68

DDR1

_DQ[11]/DDR0_DQ[27]

AF71

DDR1

_DQ[12]/DDR0_DQ[28]

AF69

_DQ[13]/DDR0_DQ[29]

DDR1

AH70

_DQ[14]/DDR0_DQ[30]

DDR1

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1

_DQ[17]/DDR0_DQ[49]

AP65

DDR1

_DQ[18]/DDR0_DQ[50]

AN65

DDR1

_DQ[19]/DDR0_DQ[51]

AN66

_DQ[20]/DDR0_DQ[52]

DDR1

AP66

_DQ[21]/DDR0_DQ[53]

DDR1

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1

_DQ[23]/DDR0_DQ[55]

AT61

DDR1

_DQ[24]/DDR0_DQ[56]

AU61

DDR1

_DQ[25]/DDR0_DQ[57]

AP60

DDR1

_DQ[26]/DDR0_DQ[58]

AN60

_DQ[27]/DDR0_DQ[59]

DDR1

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1

_DQ[30]/DDR0_DQ[62]

AU60

DDR1

_DQ[31]/DDR0_DQ[63]

AU40

DDR1

_DQ[32]/DDR1_DQ[16]

AT40

_DQ[33]/DDR1_DQ[17]

DDR1

AT37

_DQ[34]/DDR1_DQ[18]

DDR1

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1

_DQ[37]/DDR1_DQ[21]

AP37

DDR1

_DQ[38]/DDR1_DQ[22]

AR37

DDR1

_DQ[39]/DDR1_DQ[23]

AT33

_DQ[40]/DDR1_DQ[24]

DDR1

AU33

_DQ[41]/DDR1_DQ[25]

DDR1

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1

_DQ[43]/DDR1_DQ[27]

AR33

DDR1

_DQ[44]/DDR1_DQ[28]

AP33

DDR1

_DQ[45]/DDR1_DQ[29]

AR30

DDR1

_DQ[46]/DDR1_DQ[30]

AP30

_DQ[47]/DDR1_DQ[31]

DDR1

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1

_DQ[50]

AU25

DDR1

_DQ[51]

AP27

DDR1

_DQ[52]

AN27

_DQ[53]

DDR1

AN25

_DQ[54]

DDR1

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1

_DQ[57]

AU21

DDR1

_DQ[58]

AT21

DDR1

_DQ[59]

AN22

_DQ[60]

DDR1

AP22

DDR1

_DQ[61]

AP21

DDR1_DQ[62]

AN21

_DQ[63]

DDR1

SKL-U_BGA1356

@

D

-U

SKL

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1

_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1

_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1

_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1

_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1

_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1

_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1

_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1

_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1

_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1

_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1

_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1

DDR1

DDR1

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1

DDR1

DDR1

DDR1

DDR1

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1

DDR

CH - B

3 OF 20

Rev

_0.53Rev_0.53

_CKN[0]

DDR1

_CKN[1]

DDR1

DDR1_CKP[0]

DDR1

_CKP[1]

DDR1

_CKE[0]

DDR1

_CKE[1]

_CKE[2]

DDR1

DDR1_CKE[3]

DDR1

_CS#[0]

DDR1

_CS#[1]

DDR1

_ODT[0]

_ODT[1]

DDR1

DDR1_MA[3]

DDR1

_DQSN[0]/DDR0_DQSN[2]

_DQSP[0]/DDR0_DQSP[2]

_DQSN[1]/DDR0_DQSN[3]

_DQSN[2]/DDR0_DQSN[6]

_DQSP[2]/DDR0_DQSP[6]

_DQSN[3]/DDR0_DQSN[7]

_DQSP[3]/DDR0_DQSP[7]

_DQSN[4]/DDR1_DQSN[2]

_DQSP[5]/DDR1_DQSP[3]

_MA[4]

DDR1

_DQSN[6]

DDR1

_DQSP[6]

_DQSN[7]

DDR1

_DQSP[7]

DDR1

DDR1_ALERT#

DDR1

_PAR

DRA

M_RESET#

DDR_

RCOMP[0]

RCOMP[1]

DDR_

DDR_

RCOMP[2]

MP Sample Add on 7/14

UC1

CP

U_ i3-6100U_D1_2.3G

SR2EU@

00092NB0

SA0

B_CLK#0

DDR_

AN45

DDR_

B_CLK#1

AN46

DDR_

B_CLK0

AP45

DDR_

B_CLK1

AP46

B_CKE0

DDR_

AN56

B_CKE1

DDR_

AP55

AN55

AP53

DDR_

B_CS#0

BB42

B_CS#1

DDR_

AY42

B_ODT0

DDR_

BA42

B_ODT1

DDR_

AW42

B_MA5

DDR_

AY48

DDR_

B_MA9

AP50

DDR_

B_MA6

BA48

DDR_

B_MA8

BB48

B_MA7

DDR_

AP48

B_BS2

DDR_

AP52

B_MA12

DDR_

AN50

B_MA11

DDR_

AN48

DDR_

B_MA15

AN53

DDR_

B_MA14

AN52

B_MA13

DDR_

BA43

B_CAS#

DDR_

AY43

B_WE#

DDR_

AY44

B_RAS#

DDR_

AW44

DDR_

B_BS0

BB44

DDR_

B_MA2

AY47

DDR_

B_BS1

BA44

DDR_

B_MA10

AW46

B_MA1

DDR_

AY46

B_MA0

DDR_

BA46

B_MA3

DDR_

BB46

DDR_

B_MA4

BA47

DDR_

B_DQS#0

AH66

DDR_

B_DQS0

AH65

B_DQS#1

DDR_

AG69

B_DQS1

DDR_

AG70

B_DQS#2

DDR_

AR66

DDR_

B_DQS2

AR65

DDR_

B_DQS#3

AR61

DDR_

B_DQS3

AR60

DDR_

B_DQS#4

AT38

DDR_

B_DQS4

AR38

B_DQS#5

DDR_

AT32

B_DQS5

DDR_

AR32

DDR_

B_DQS#6

AR25

DDR_

B_DQS6

AR27

B_DQS#7

DDR_

AR22

DDR_

B_DQS7

AR21

AN43

AP43

DRAMRST#

DDR_

AT13

AR18

AT18

SM

_RCOMP0

AU18

SM_RCOMP1

_RCOMP2

SM

#543016 PDG0.9 P.117

W=12-15 Space= 20/25 L=500mil

UC1

CP

U_i5-6200U_D1_2.3G

SR2EY@

00092OB0

SA0

T1

7@

T1

8@

E

3@

T2

RC3

8 121_0402_1%

1 2

1 2

RC3

9 80.6_0402_1%

1 2

RC4

0 100_0402_1%

UC1

CP

U_i7-6500U_D1_2.5G

SR2EZ@

SA0

DDR_

B_CLK#0 19

DDR_

B_CLK#1 19

DDR_

B_CLK0 19

DDR_

B_CLK1 19

B_CKE0 19

DDR_

B_CKE1 19

DDR_

DDR_

B_CS#0 19

DDR_

B_CS#1 19

B_ODT0 1 9

DDR_

B_ODT1 1 9

DDR_

DDR_

B_MA5 19

DDR_

B_MA9 19

DDR_

B_MA6 19

DDR_

B_MA8 19

B_MA7 19

DDR_

B_BS2 19

DDR_

B_MA12 19

DDR_

DDR_

B_MA11 19

DDR_

B_MA15 19

DDR_

B_MA14 19

DDR_B_MA13 19

B_CAS# 19

DDR_

B_WE# 19

DDR_

DDR_

B_RAS# 19

DDR_

B_BS0 19

DDR_

B_MA2 19

DDR_

B_BS1 19

DDR_B_MA10 19

B_MA1 19

DDR_

B_MA0 19

DDR_

B_MA3 19

DDR_

DDR_

B_MA4 19

DDR_

B_DQS#0 19

DDR_B_DQS0 19

B_DQS#1 19

DDR_

B_DQS1 19

DDR_

B_DQS#2 19

DDR_

DDR_

B_DQS2 19

DDR_

B_DQS#3 19

DDR_

B_DQS3 19

DDR_B_DQS#4 19

B_DQS4 19

DDR_

B_DQS#5 19

DDR_

B_DQS5 19

DDR_

B_DQS#6 19

DDR_

DDR_

B_DQS6 19

DDR_

B_DQS#7 19

DDR_B_DQS7 19

DRAMRST# 18,19

DDR_

00092P90

U_ i3-6100U_D0_2.3G

CP

QJFC@

SA0

00092N30

U_i5-6200U_D0_2.3G

CP

QJ8N@

SA0

00092O30

A

U_i7-6500U_D0_2.5G

CP

QJ8L@

SA0

00092P20

curity Classification

curity Classificat ion

curity Classificat ion

Se

Se

Se

Is

Is

Is

sued Date

sued Date

sued Date

S SHEE T OF ENGINEERI NG DR AWING IS THE PROPRIE TARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

S SHEE T OF ENGINEERI NG DR AWING IS THE PROPRIE TARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

S SHEE T OF ENGINEERI NG DR AWING IS THE PROPRIE TARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THI

THI

THI

AND TRADE SECRET INFORM ATION. THIS SHEET M AY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORM ATION. THIS SHEET M AY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORM ATION. THIS SHEET M AY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRI TTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRI TTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRI TTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2014/

2014/

2014/

11/10 2016/11/10

11/10 2016/11/10

11/10 2016/11/10

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Dat e

Deciphered Dat e

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Ti

Ti

Ti

tle

tle

tle

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

stom

stom

stom

Cu

Cu

Cu

Date: Sheet

Date: Sheet

D

Date: Sheet

L-U(2/12)DDRIII

L-U(2/12)DDRIII

L-U(2/12)DDRIII

SK

SK

SK

A4WAS M/B LA-C611P

A4WAS M/B LA-C611P

A4WAS M/B LA-C611P

Tuesday, July 14, 2015

Tuesday, July 14, 2015

Tuesday, July 14, 2015

E

0

0

0

1.

1.

1.

60

60

60

7

7

7

of

of

of

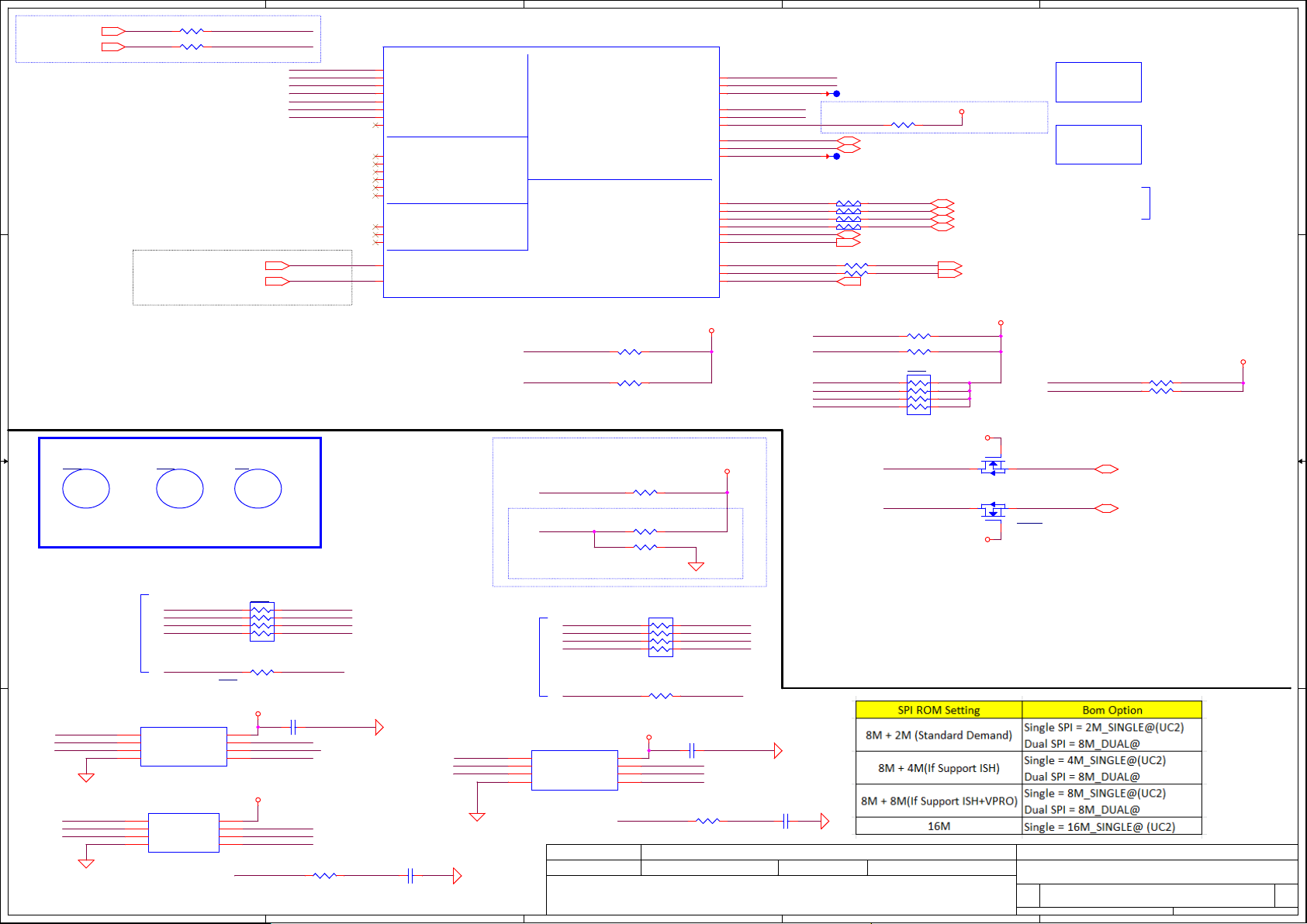

A

C_SPI_SI

ROM

SO

C_SPI_IO2

SO

SO

C_SPI_CLK

SO

C_SPI_SO

SOC_SPI_SI

C_SPI_IO2

SO

C_SPI_IO3

SO

C_SPI_CS#0

SO

SO

C_SPI_CS#1

1 2

4 1K_0402_1%CMC@

XDP_

SPI_SI6

SPI_IO26

XDP_

RC2

1/44 place to within 1100 mil of SPIO_MOSI/SPI0_IO2 pin for XDP

RC4

RC2

1 1K_0402_1%CMC@

1 2

SPI

1 1

SPI Touch

KBRST#_R

LPC

SO

SO

SO

SO

SO

15_0402_5%

1 2

C_SPI_IO3_0_R

C_SPI_CLK_0_R

C_SPI_SI_0_R

_SPI

C_SPI_CLK_0_R

C_SPI_SI_0_R

C_SPI_SO_0_R

EC_

M_SERIRQ

TP

Mode

C_SPI_IO3

C_SPI_SI

C_SPI_CLK

C_SPI_SO

C_SPI_IO2

CC8

.1

U_0402 _16V7K

1 2

EC_

KBRST#_R38

M_SERIRQ38,39

To TPM

2 2

RPC5

33_0804_8P

4R_5%

8M_DUAL@

SD

309330A80

3 3

Single SPI ROM_CS0#

To SPI ROM

SPI

ROM ( 8MByte )

SO

C_SPI_CS#0

SO

C_SPI_SO_0_R

SO

C_SPI_IO2_0_R

M Socket

4 4

RO

SO

C_SPI_CS#0

SO

C_SPI_IO2_0_R

SO

C_SPI_IO3_0_R

RC5

2

33_0402_5%

8M

_DUAL@

SD

028330A80

RPC5

UC2

1

/C

S

2

DO

(IO1)

3

P(IO2)

/W

4

D

GN

W25Q64FVSSIQ_SO8

8M_SINGLE@

JC

1

1

CS#

3

WP#

7

LD#

HO

4

D

GN

ACES_91960-0084N_MX25L3206EM2I

CONN@

A

TP

UC2

W2

5Q64FVSSIQ_SO8

8M_DUAL@

SA0

00039A30

and RC52 are close UC2

C_SPI_IO3_0_R

SO

C_SPI_SI_0_R

SO

C_SPI_CLK_0_R

SO

SO

C_SPI_SO_0_R

C_SPI_IO2_0_R

SO

/H

OLD(IO3)

DI

VCC

SCLK

/SIO0

SI

/SIO1

SO

VC

CL

(IO0)

RC5

8M

_SINGLE@

C

K

8

6

5

2

2

8

7

6

5

RPC5

1 8

2 7

3 6

4 5

15_0804_8P4R_5%

8M_SINGLE@

1 2

+3VALW_SPI

SO

SO

SO

+3VALW

SO

SO

SO

C_SPI_CLK_0_R

SO

RC2

0_0402_5%@EMC@

AW3

AW2

AW13

AY11

AV2

SPI

SPI0_MISO

AV3

SPI

SPI

AU4

SPI

AU3

SPI

AU2

SPI

AU1

SPI

M2

GP

M3

GP

J4

GP

V1

GP

V2

GP

M1

GP

G3

CL_CLK

G2

CL

G1

CL

GP

GP

SKL-U_BGA1356

@

4

B

UC1E

SPI

- FLASH

0_CLK

0_MOSI

0_IO2

0_IO3

0_CS0#

0_CS1#

0_CS2#

SPI - TOUCH

P_D1/SPI1_CLK

P_D2/SPI1_MISO

P_D3/SPI1_MOSI

P_D21/SPI1_IO2

P_D22/SPI1_IO3

P_D0/SPI1_CS#

C LINK

_DATA

_RST#

P_A0/RCIN#

P_A6/SERIRQ

1 2

CC9

_0402_50V8J

10P

@EMC@

B

Dua

l SPI ROM_CS1#

ROM ( 2/4/8/16MByte )

SPI

C_SPI_CS#1

SO

C_SPI_SO_1_R

SO

C_SPI_IO2_1_R

SO

C

-U

SKL

SMBUS, SMLINK

GPP_C0/SMBCLK

GP

GP

P_C2/SMBALERT#

GP

GP

GP

P_C5/SML0ALERT#

GP

GP

P_B23/SML1ALERT#/PCHHOT#

P_A1/LAD0/ESPI_IO0

GP

P_A2/LAD1/ESPI_IO1

GP

GP

P_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

P_A5/LFRAME#/ESPI_CS#

GP

P_A14/SUS_STAT#/ESPI_RESET#

P_A9/CLKOUT_LPC0/ESPI_CLK

GP

P_A10/CLKOUT_LPC1

GP

1 2

1 2

LPC

PM_

CLKRUN#

M_SERIRQ

TP

GP

GP

GP

5

OF 20

RC107 10K_0402_5%

RC1

12 10K_0402_5%

2015MOW06 no need PU1K on SPI_IO2/IO3

C_SPI_IO2

SO

SO

C_SPI_IO3

add PD 1K depop PH 1K

MOW36

only for SKL U ES sample

7 1K_0402_1%@

RC4

RC4

8 1K_0402_1%@

1 1K_0402_1%ES@

RC5

1 2

1 2

1 2

RPC23 and RC59 are close UC9

RPC2

1 8

2 7

3 6

4 5

33_0804_8P4R_5%

8M_DUAL@

8M_DUAL@

RC5

9 33_0402_5%

+3VALW_SPI

8

C

C_SPI_IO3_1_R

SO

7

C_SPI_CLK_1_R

SO

6

K

C_SPI_SI_1_R

SO

5

SO

C_SPI_CLK_1_R

C

To SPI ROM

C_SPI_IO3_1_R

SO

SO

C_SPI_CLK_1_R

SO

C_SPI_SI_1_R

SO

C_SPI_SO_1_R

SO

C_SPI_IO2_1_R

UC9

1

S

/C

2

(IO1)

DO

3

P(IO2)

/W

4

GN

D

W2

5Q16DVSSIQ_SO8

8M_DUAL@

Security Classification

Security Classification

Security Classification

TH

TH

TH

AND TRADE SECRET INFORMATION. THI S SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THI S SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THI S SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

VC

OLD(IO3)

/H

CL

DI

(IO0)

Issued Date

Issued Date

Issued Date

IS SHEET OF ENGINEE RING D RAWING IS THE PROPRIE TARY PRO PERTY OF C OMPAL ELEC TRONIC S, INC. A ND CONTAI NS CONFIDENTIAL

IS SHEET OF ENGINEE RING D RAWING IS THE PROPRIE TARY PRO PERTY OF C OMPAL ELEC TRONIC S, INC. A ND CONTAI NS CONFIDENTIAL

IS SHEET OF ENGINEE RING D RAWING IS THE PROPRIE TARY PRO PERTY OF C OMPAL ELEC TRONIC S, INC. A ND CONTAI NS CONFIDENTIAL

Rev_0.5

3

SO

C_SMBCLK_1

R7

SOC_SMBDATA_1

P_C1/SMBDATA

P_C3/SML0CLK

P_C4/SML0DATA

P_C6/SML1CLK

P_C7/SML1DATA

P_A8/CLKRUN#

+1.

3

12

1 2

R8

C_SMBALERT#

SO

R10

C_SML0CLK

SO

R9

SO

C_SML0DATA

W2

SO

C_SML0ALERT#

W1

SO

C_SML1CLK

W3

C_SML1DATA

SO

V3

C_SML1ALERT#

SO

AM7

C_AD0

LP

AY13

C_AD1

LP

BA13

C_AD2

LP

BB13

C_AD3

LP

AY12

LP

C_FRAME#

BA12

ESPI

_RST#

BA11

_CLK

ESPI

AW9

LPC_TPM_R

CK_

AY9

CLKRUN#

PM_

AW11

8VS_3VS_PGPPA

+3VALW

_SPI

C_SPI_IO3

SO

SO

C_SPI_CLK

SO

C_SPI_SI

SO

C_SPI_SO

SO

C_SPI_IO2

CC1

01

.1U_040 2_16V7K

8M_DUAL@

RC2

6

1 2

11/10 2016/11/10

11/10 2016/11/10

11/10 2016/11/10

2014/

2014/

2014/

0_0402_5%@EMC@

CC7

Co

Co

Co

1 2

0

10P_0402_50V8J

mpal Secret Data

mpal Secret Data

mpal Secret Data

1 2

44 0_0402_5%@

RC1

1 2

45 0_0402_5%@

RC1

1 2

RC1

46 0_0402_5%@

1 2

RC1

47 0_0402_5%@

5 22_0402_5%

RC4

LP

R3

TP

95 22_0402_5 %

C_SML0CLK

SO

SO

C_SML0DATA

C_SMBCLK_1

SO

C_SMBDATA_1

SO

C_SML1CLK

SO

SO

C_SML1DATA

@EMC@

Deciphered Date

Deciphered Date

Deciphered Date

T239@

SO

C_SML1CLK 20,31,38

SO

C_SML1DATA 20,31,38

T234@

C_FRAME# 38,39

LP

ESPI

_RST# 38

12

C@

12

M@

CLKRUN# 39

PM_

1 2

RC4

9 499_0402_1%

1 2

RC5

0 499_0402_1%

1 8

2 7

3 6

4 5

SO

C_SMBCLK_1

C_SMBDATA_1

SO

D

+3VALW

12

RC2

024.7K_0402_5% ESPI@

RPC7

2K_0804_8P4R_5%

2.

D

_PRIM

St

rap Pin

LP

C_AD0_R 38,39

LPC_AD1_R 38,39

C_AD2_R 38,39

LP

C_AD3_R 38,39

LP

ESPI

_CLK_R 38

LPC_TPM 39

CK_

For TPM

+3VALW

+3VS

5

3 4

6 1

2

+3VS

E

SM

B

(Link to XDP, DDR)

SML1

(Link to EC,DGPU)

ESPI

/ LPC Bus

ESPI

: +1.8V

LPC : +3.3V

Change RC144~RC147, RC45 to

15ohm when use ESPI

To

EC

_PRIM

+3VS

C_SMBCLK

SO

C_SMBDATA

SO

Q2

017B

DMN66D0LDW-7_SOT363-6

SO

C_SMBCLK

C_SMBDATA

SO

Q2

017A

DM

N66D0LDW-7_SOT363-6

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

tle

tle

tle

Ti

Ti

Ti

L-U(3/12)SPI,ESPI,SMB,LPC

L-U(3/12)SPI,ESPI,SMB,LPC

L-U(3/12)SPI,ESPI,SMB,LPC

SK

SK

SK

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

stom

stom

stom

Cu

Cu

Cu

A4WAS M/B LA-C611P

A4WAS M/B LA-C611P

A4WAS M/B LA-C611P

Date: Sheet

Date: Sheet

Date: Sheet

1 2

22 2.2K_0402_5%

RC2

1 2

RC2

23 2.2K_0402_5%

SO

C_SMBCLK 18,19,41

C_SMBDATA 18,19,41

SO

860Tuesday, June 16, 2015

860Tuesday, June 16, 2015

860Tuesday, June 16, 2015

of

of

E

of

0

0

0

1.

1.

1.

A

SKL_PCH_EDS_R0.7 P.84

#545659

1 1

tional Strap Definitions

Func

SPK

R / GPP_B14 (Internal Pull Down):

(Sampled:Rising edge of PCH_PWROK)

TOP Swap Overr ide

0 = Disable TOP Swap mode.---> AAX05 Use

1 = Enable TOP Swap Mode.

2 2

PCH_

PCH_

DMIC_CLK40

DMIC_DATA40

B

UC1G

AU

HDA_SYNC

HDA_

HDA_

HDA_

HDA_

PCH_

PCH_

SPKR40

BIT_CLK

SDOUT

SDIN0

RST#

DMIC_CLK

DMIC_DATA

SPKR

BA22

AY22

BB22

BA21

AY21

AW22

AY20

AW20

AK7

AK6

AK9

AK10

AW5

J5

H5

D7

D8

C8

SKL-U_BGA1356

@

DIO

_SYNC/I2S0_SFRM

HDA

HDA

_BLK/I2S0_SCLK

HDA

_SDO/I2S0_TXD

_SDI0/I2S0_RXD

HDA

_SDI1/I2S1_RXD

HDA

HDA

_RST#/I2S1_SCLK

GP

P_D23/I2S_MCLK

S1_SFRM

I2

S1_TXD

I2

GP

P_F1/I2S2_SFRM

P_F0/I2S2_SCLK

GP

P_F2/I2S2_TXD

GP

GP

P_F3/I2S2_RXD

P_D19/DMIC_CLK0

GP

GP

P_D20/DMIC_DATA0

P_D17/DMIC_CLK1

GP

GP

P_D18/DMIC_DATA1

P_B14/SPKR

GP

HDA

for AUDIO

HDA_

HDA_

HDA_

HDA_

SYNC_R40

SDOUT_R40

BIT_CLK_R40

RST#_R40

HDA_

ME_

EN38

SDIN040

C

-U

SKL

7

OF 20

RPC9

1 8

2 7

3 6

4 5

33_0804_8P

1 2

7 0_0402_5%

RC7

SDIO/SDX C

GP

GP

GP

GP

GP

P_A17/SD_PWR_EN#/ISH_GP7

GP

P_A16/SD_1P8_SEL

HDA_

SYNC

HDA_

SDOUT

HDA_BIT_CLK

RST#

HDA_

4R_5%

HDA_

HDA_

SDOUT

SDIN0

@

Rev_0.5

P_G0/SD_CMD

GP

P_G1/SD_DATA0

P_G2/SD_DATA1

P_G3/SD_DATA2

P_G4/SD_DATA3

GP

P_G5/SD_CD#

GP

P_G6/SD_CLK

P_G7/SD_WP

GP

_RCOMP

SD

P_F23

GP

D

3

#543016 PDG0.9 P.321

Terminating Unused SDIO/SDXC Signals

SDIO signals are multiplexed with GPIOs and

default to GPIO functionality (as input). If

AB11

AB13

AB12

W12

W11

W10

W8

W7

BA9

BB9

AB7

AF13

SDIO interface is not used, the signals

can be used as GPIOs instead. If the GPIO

functionality is also not used, the signals can

be left as no-connect.

RCOMP

SD_

RC7

6 200_0402_1%

12

E

_ULT

UC1I

CSI-2

A36

CS

I2_DN0

B36

CS

I2_DP0

C38

CSI2_DN1

D38

I2_DP1

CS

C36

I2_DN2

CS

D36

CS

I2_DP2

A38

I2_DN3

CS

B38

I2_DP3

CS

3 3

4 4

A

B

C31

CS

D31

CS

C33

CS

D33

CS

A31

CS

B31

CS

A33

CS

B33

CS

A29

CS

B29

CS

C28

CS

D28

CSI2_DP9

A27

CS

B27

CS

C27

CS

D27

CS

SKL-U_BGA1356

@

I2_DN4

I2_DP4

I2_DN5

I2_DP5

I2_DN6

I2_DP6

I2_DN7

I2_DP7

I2_DN8

I2_DP8

I2_DN9

I2_DN10

I2_DP10

I2_DN11

I2_DP11

SKL

GP

GP

GP

GP

GP

GP

GP

GPP_F20/EMMC_DATA7

GP

9

OF 20

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

TH

TH

TH

IS SHEET OF ENGINEE RING D RAWING IS THE PROPRIE TARY PRO PERTY OF C OMPAL ELEC TRONIC S, INC. A ND CONTAI NS CONFIDENTIAL