5

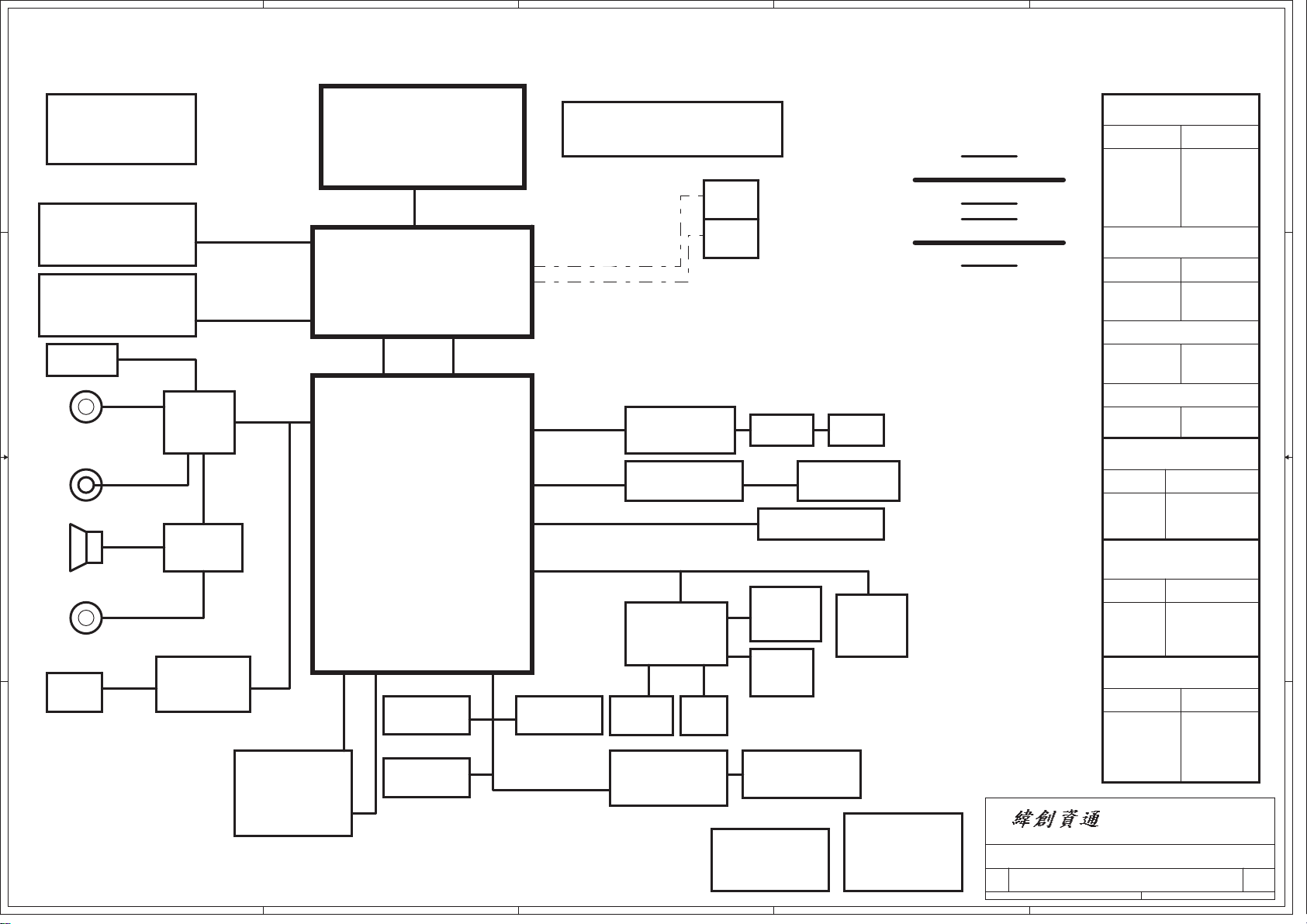

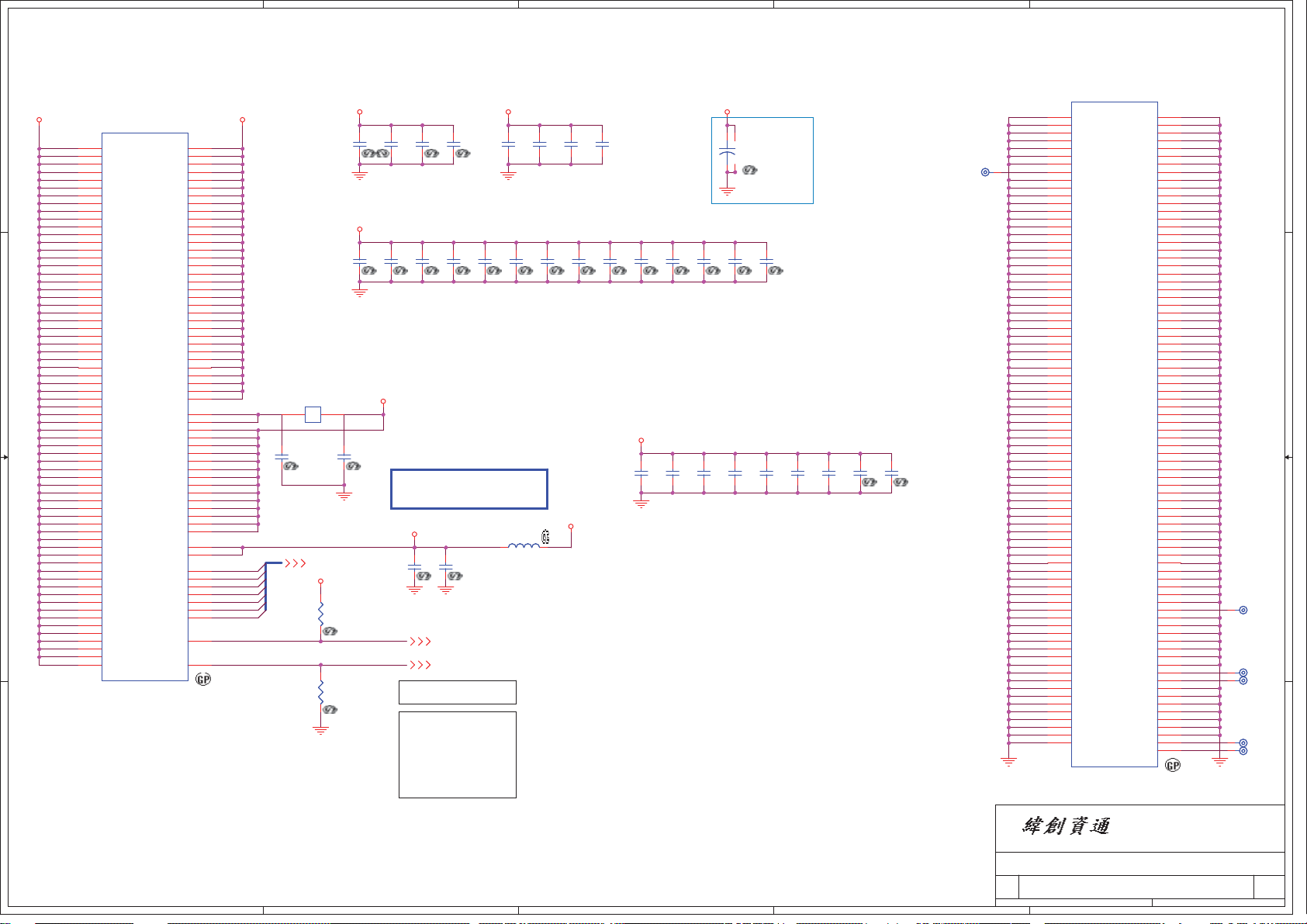

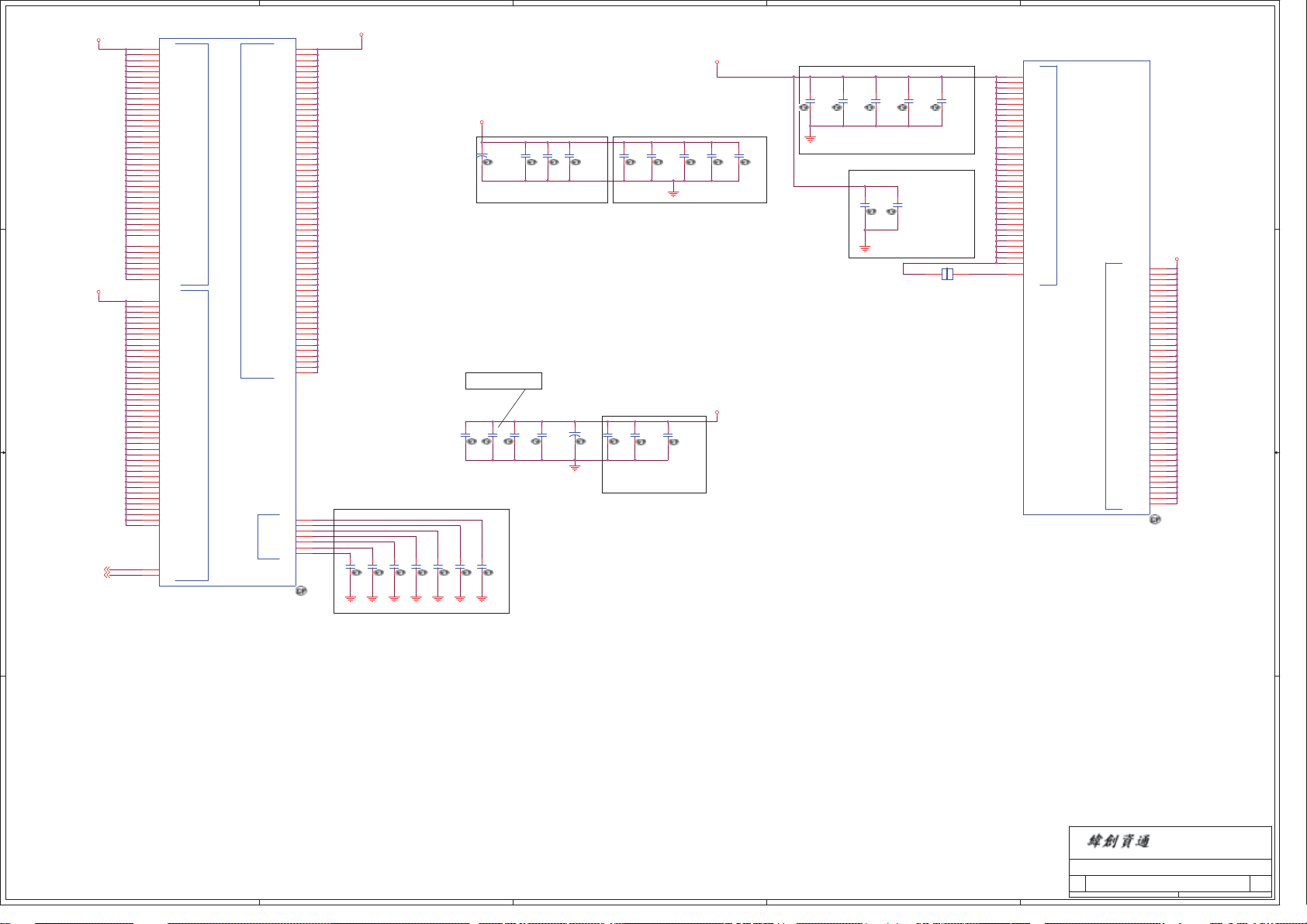

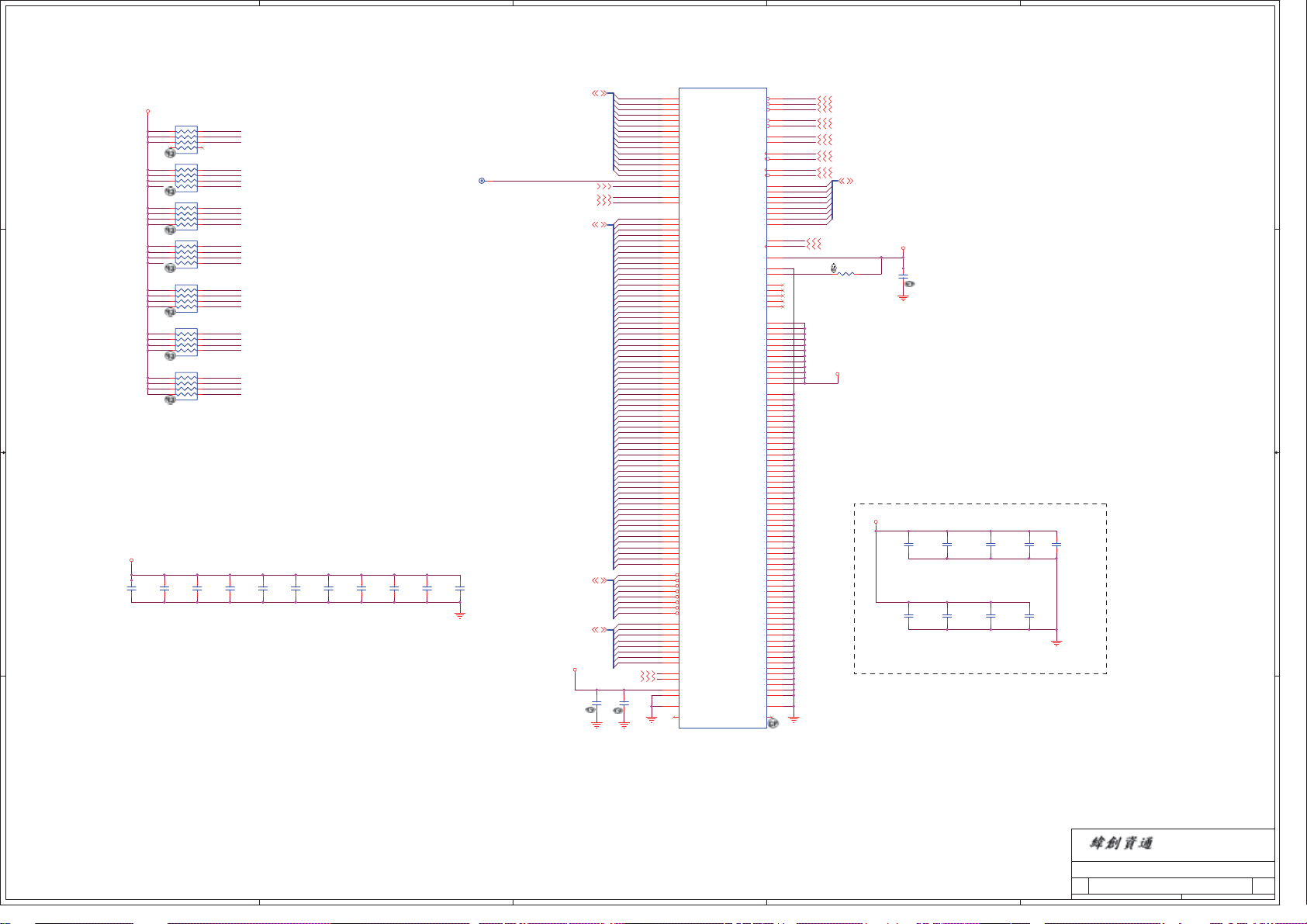

Cathedral Peak Block Diagram

4

3

2

1

Project code: 91.4J501.001

PCB P/N : 48.4J501.001

REVISION : 07261 - 1

D D

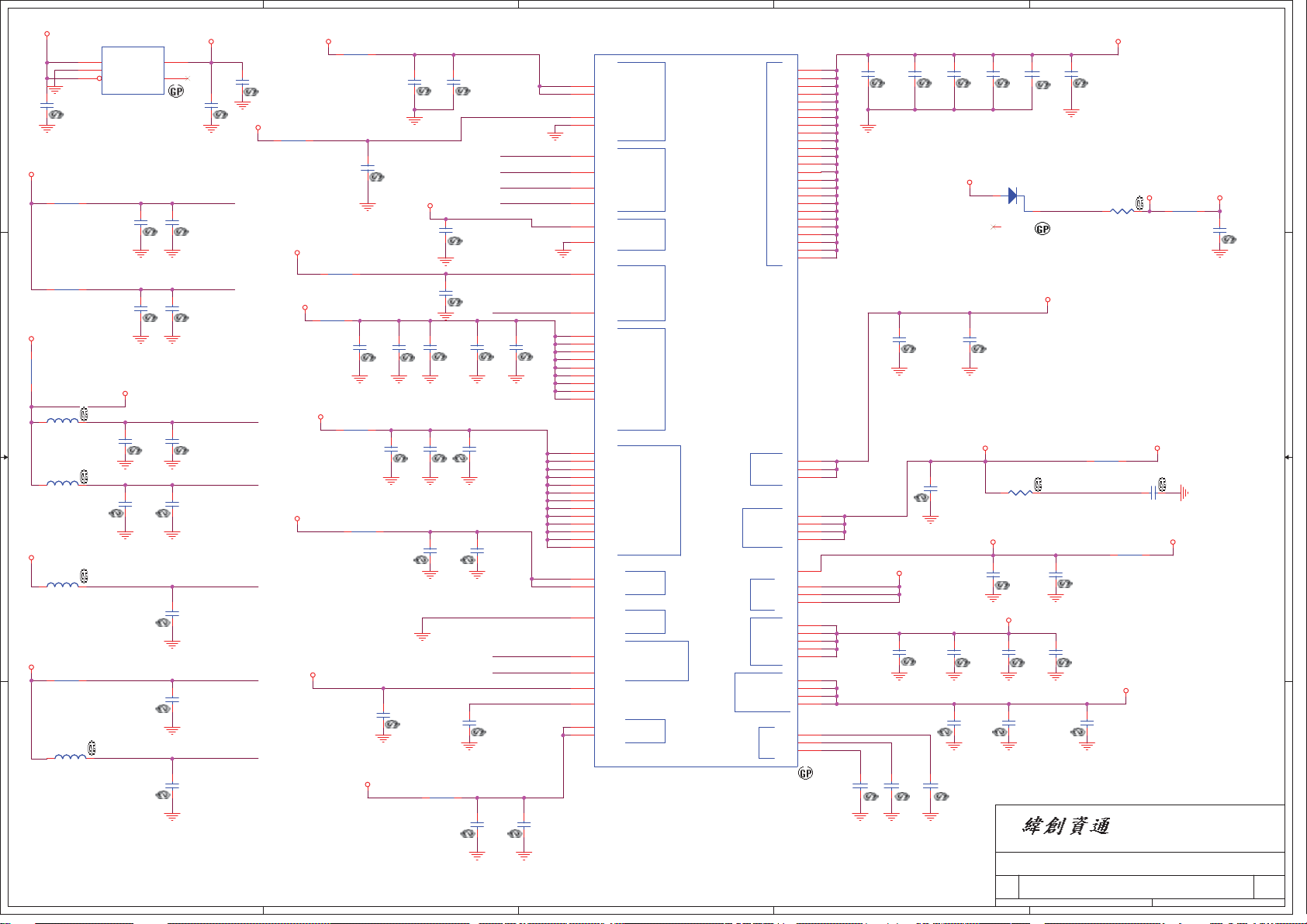

CLK GEN.

ICS 9LPRS365BKLFT (71.09365.A03)

RTM 875N-606-LFT (71.00875.003)

3

DDR2 DIMM1

667/800 MHz

12

667/800MHz

DDR2 DIMM2

667/800 MHz

13

C C

INT.MIC

29

667/800MHz

Mobile CPU

Penryn 479

4, 5

HOST BUS 667/800/1067MHz@1.05V

THERMAL EMC2102

Cantiga

AGTL+ CPU I/F

DDR Memory I/F

INTEGRATED GRAHPICS

LVDS, CRT I/F

6,7,8,9,10,11

X4 DMI

400MHz

C-Link0

21

CRT

LCD

15

14

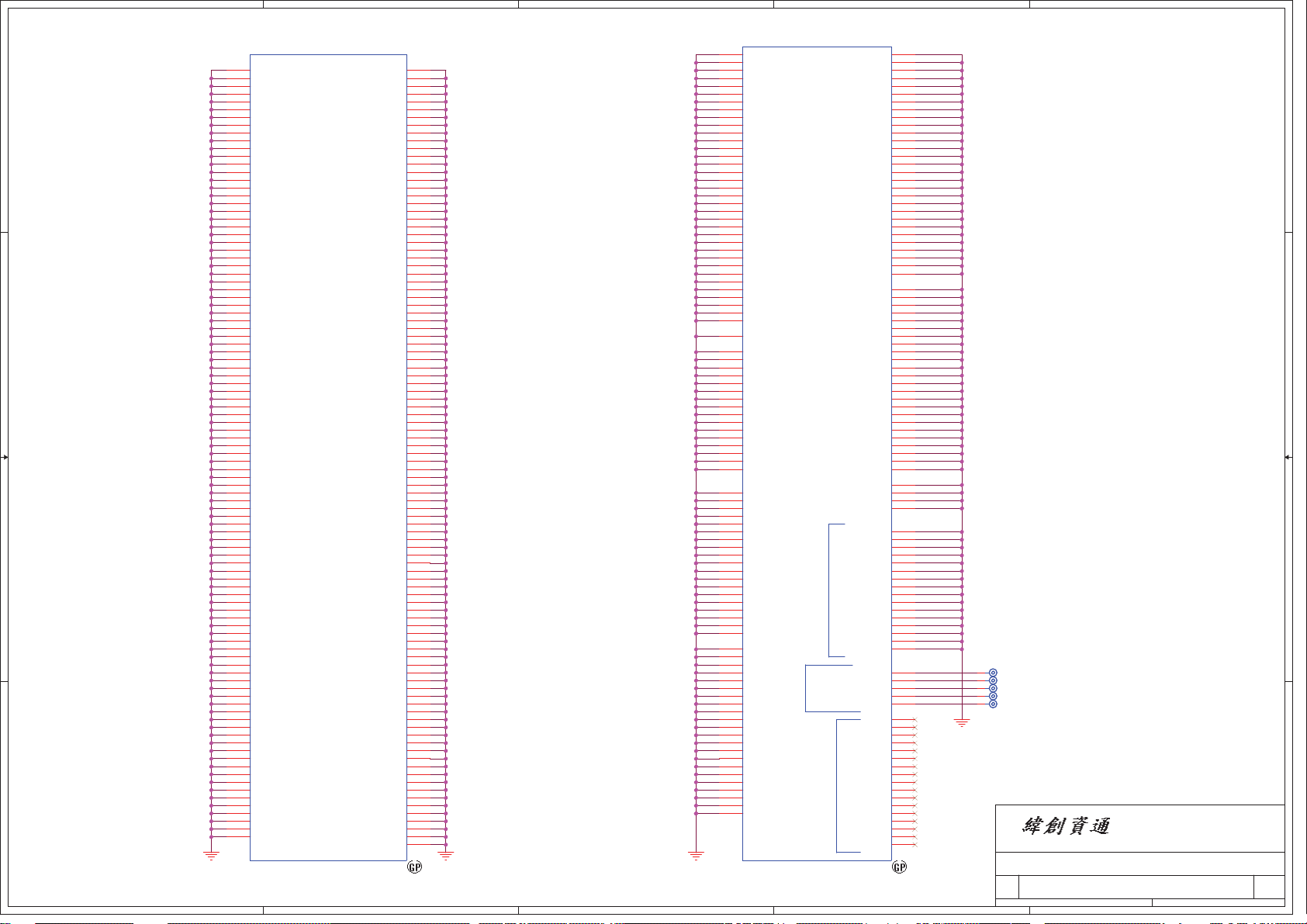

PCB STACKUP

TOP

VCC

S

S

GND

BOTTOM

SYSTEM DC/DC

TPS51125

INPUTS

DCBATOUT

OUTPUTS

5V_S5

3D3V_S5

SYSTEM DC/DC

TPS51124

INPUTS OUTPUTS

DCBATOUT

RT9026

1D8V_S3

1D05V_S0

1D8V_S3

DDR_VREF_S0

DDR_VREF_S3

43

45

44

Line In

29

Codec

ALC268

28

AZALIA

MIC In

29

29

B B

INT.SPKR

29

OP AMP

APA2057

29

Line Out

(NO SPDIF)

MODEM

RJ11

MDC Card

23

ICH9M

6 PCIe ports

PCI/PCI BRIDGE

ACPI 2.0

4 SATA

12 USB 2.0/1.1 ports

ETHERNET (10/100/1000MbE)

High Definition Audio

LPC I/F

Serial Peripheral I/F

Matrix Storage Technology(DO)

Active Managemnet Technology(DO)

17,18,19,20

Blue Tooth

(USB)

23

USB

PCIex1

PCIex1

PCIex1

LPC BUS

Camera

(USB)

LAN

Giga LAN

88E8071

25

New card

KBC

ENE3310

Touch

14

Pad

30 30

30

INT.

KB

TXFM RJ45

26 26

PWR SW

27 27

BIOS

Winbond

W25X80

8M Bits

Launch

Buttom

G577BR91U

Mini Card

Kedron

a/b/g/n

31

16

27

LPC

DEBUG

CONN.

31

SATA

HDD SATA

A A

ODD SATA

5

22

22

SATA

USB

2 Port

4

23

USB

http://hobi-elektronika.net

CardReader

Realtek

RTS5158E

3

MS/MS Pro/xD

/MMC/SD

5 in 1

27

Daughter Board

LED Board

07950 07951

27

Daughter Board

USB Board

2 Port + e-Key

16

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

23

2

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

RT9018A

1D8V_S3 1D5V_S0

CFXCORE DC/DC

ISL6263

INPUTS

DCBATOUT

OUTPUTS

VGFXCORE

0.7~1.25V

CPU DC/DC

ISL6266A

INPUTS

DCBATOUT

CHARGER

BQ24750

DCBATOUT

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Cathedral Peak

Cathedral Peak

Cathedral Peak

OUTPUTS

VCC_CORE_S0

0.35~1.5V

OUTPUTSINPUTS

BT+

DCBATOUT

142Monday, May 05, 2008

142Monday, May 05, 2008

142Monday, May 05, 2008

1

44

35,36

42

47

-1

-1

-1

A

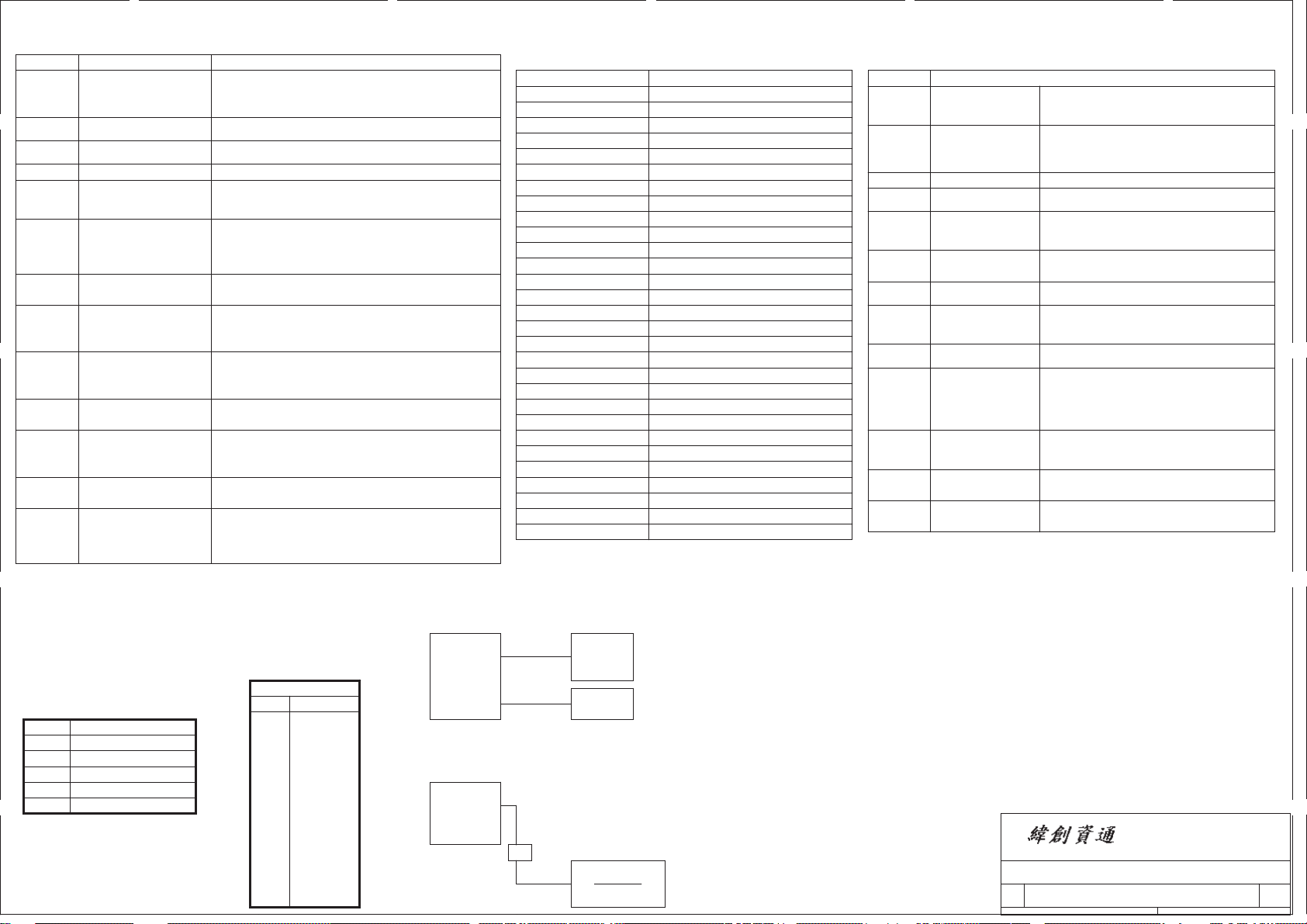

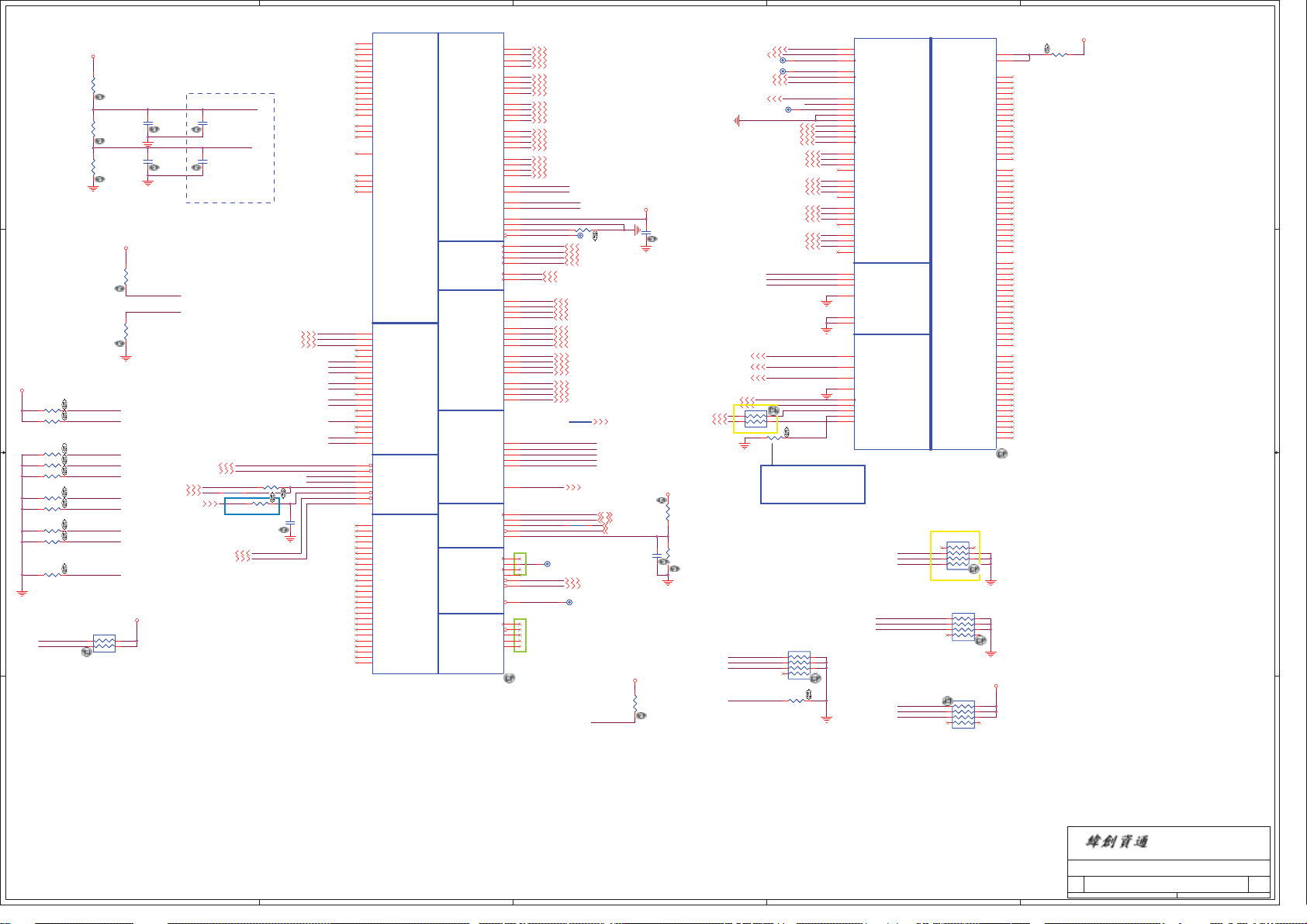

ICH9M Functional Strap Definitions

Signal

HDA_SDOUT

HDA_SYNC

4 4

GNT2#/

GPIO53

GPIO20

GNT1#/

GPIO51

GNT3#/

GPIO55

GNT0#:

SPI_CS1#/

GPIO58

SPI_MOSI

3 3

GPIO49

SATALED#

SPKR

TP3

GPIO33/

HDA_DOCK

_EN#

Usage/When Sampled

XOR Chain Entrance/

PCIE Port Config1 bit1,

Rising Edge of PWROK

PCIE config1 bit0,

Rising Edge of PWROK.

PCIE config2 bit2,

Rising Edge of PWROK.

Reserved

ESI Strap (Server Only)

Rising Edge of PWROK

Top-Block

Swap Override.

Rising Edge of PWROK.

Boot BIOS Destination

Selection 0:1.

Rising Edge of PWROK.

Integrated TPM Enable,

Rising Edge of CLPWROK

DMI Termination Voltage,

Rising Edge of PWROK.

PCI Express Lane

Reversal. Rising Edge

of PWROK.

No Reboot.

Rising Edge of PWROK.

XOR Chain Entrance.

Rising Edge of PWROK.

Flash Descriptor

Security Override Strap

Rising Edge of PWROK

Allows entrance to XOR Chain testing when TP3

pulled low.When TP3 not pulled low at rising edge

of PWROK,sets bit1 of RPC.PC(Config Registers:

offset 224h). This signal has weak internal pull-down

This signal has a weak internal pull-down.

Sets bit0 of RPC.PC(Config Registers:Offset 224h)

This signal has a weak internal pull-up.

Sets bit2 of RPC.PC2(Config Registers:Offset 0224h)

This signal should not be pulled high.

ESI compatible mode is for server platforms only.

This signal should not be pulled low for desttop

and mobile.

Sampled low:Top-Block Swap mode(inverts A16 for

all cycles targeting FWH BIOS space).

Note: Software will not be able to clear the

Top-Swap bit until the system is rebooted

without GNT3# being pulled down.

Controllable via Boot BIOS Destination bit

(Config Registers:Offset 3410h:bit 11:10).

GNT0# is MSB, 01-SPI, 10-PCI, 11-LPC.

Sample low: the Integrated TPM will be disabled.

Sample high: the MCH TPM enable strap is sampled

low and the TPM Disable bit is clear, the

Integrated TPM will be enable.

The signal is required to be low for desktop

applications and required to be high for

mobile applications.

Signal has weak internal pull-up. Sets bit 27

of MPC.LR(Device 28:Function 0:Offset D8)

If sampled high, the system is strapped to the

"No Reboot" mode(ICH9 will disable the TCO Timer

system reboot feature). The status is readable

via the NO REBOOT bit.

This signal should not be pull low unless using

XOR Chain testing.

Sampled low:the Flash Descriptor Security will be

overridden. If high,the security measures will be

in effect.This should only be enabled in manufacturing

environments using an external pull-up resister.

ICH9 EDS 642879 Rev.1.5

Comment

2 2

B

ICH9M Integrated Pull-up

page 92

and Pull-down Resistors

SIGNAL Resistor Type/Value

CL_CLK[1:0]

CL_DATA[1:0]

CL_RST0#

DPRSLPVR/GPIO16

ENERGY_DETECT

HDA_BIT_CLK

HDA_DOCK_EN#/GPIO33

HDA_RST#

HDA_SDIN[3:0]

HDA_SDOUT

HDA_SYNC

GLAN_DOCK#

GNT[3:0]#/GPIO[55,53,51]

GPIO[20]

GPIO[49]

LDA[3:0]#/FHW[3:0]#

LAN_RXD[2:0]

LDRQ[0]

LDRQ[1]/GPIO23

PME#

PWRBTN#

SATALED#

SPI_CS1#/GPIO58/CLGPIO6

SPI_MOSI

SPI_MISO

SPKR

TACH_[3:0]

TP[3]

USB[11:0][P,N]

C

Cantiga chipset and ICH9M I/O controller

Hub strapping configuration

ICH9 EDS 642879 Rev.1.5

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-DOWN 20K

PULL-DOWN 20K

PULL-DOWN 20K

The pull-up or pull-down active when configured for native

GLAN_DOCK# functionality and determined by LAN controller

PULL-DOWN 20K

PULL-UP 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 15K

PULL-UP 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-UP 20K

PULL-DOWN 15K

SDVO_CTRLDATA

D

Montevina Platform Design guide 22339 0.5

Pin Name

CFG[2:0]

CFG[4:3]

CFG8

CFG[15:14]

CFG[18:17]

CFG5

CFG6

CFG7

CFG9

CFG10 PCIE Loopback enable

CFG[13:12]

CFG16

CFG19

CFG20

L_DDC_DATA

NOTE:

1. All strap signals are sampled with respect to the leading edge of

the (G)MCH Power OK (PWROK) signal.

2. iTPM can be disabled by a 'Soft-Strap' option in the

Flash-decriptor section of the Firmware. This 'Soft-Strap' is

activated only after enabling iTPM via CFG6.

Only one of the CFG10/CFG/12/CFG13 straps can be enabled at any time.

Strap Description

FSB Frequency

Select

Reserved

DMI x2 Select

iTPM Host

Interface

Intel Management

engine Crypto strap

PCIE Graphics Lane

XOR/ALL

FSB Dynamic ODT

DMI Lane Reversal

Digital Display Port

(SDVO/DP/iHDMI)

Concurrent with PCIe

SDVO Present

Local Flat Panel

(LFP) Present

Configuration

000 = FSB1067

011 = FSB667

010 = FSB800

others = Reserved

0 = DMI x2

1 = DMI x4

0= The iTPM Host Interface is enabled(Note2)

1=The iTPM Host Interface is disalbed(default)

0 = Transport Layer Security (TLS) cipher

suite with no confidentiality

1 = TLS cipher suite with

confidentiality (default)

0 = Reverse Lanes,15->0,14->1 ect..

1= Normal operation(Default):Lane

Numbered in order

0 = Enable (Note 3)

1= Disabled (default)

00 = Reserve

10 = XOR mode Enabled

01 = ALLZ mode Enabled (Note 3)

11 = Disabled (default)

0 = Dynamic ODT Disabled

1 = Dynamic ODT Enabled

0 = Normal operation(Default):

Lane Numbered in Order

1 = Reverse Lanes

DMI x4 mode[MCH -> ICH]:(3->0,2->1,1->2and0->3)

DMI x2 mode[MCH -> ICH]:(3->0,2->1)

0 = Only Digital Display Port

or PCIE is operational (Default)

1 =Digital display Port and PCIe are

operting simulataneously via the PEG port

0 =No SDVO Card Present (Default)

1 = SDVO Card Present

0 = LFP Disabled (Default)

1= LFP Card Present; PCIE disabled

E

page 218

(Default)

(Default)

SMBus

EMC2102

USB Table

USB

0

1

2

3

4

5

6

7

8

Device

USB1

USB4

USB2

NC

USB3

Bluetooth

NC

MINIC1

WEBCAM

PCIE Routing

LANE1

LANE2

LANE3

LANE4

LANE5

LANE6

1 1

LAN MARVELL 88E8071

MiniCard WLAN

NC

NC

NewCard

NC

Pair

KBC

BAT_SCL

ICH9M

9 NEW1

10

Card Reader

SMBC_ICH

11 NC

Thermal

BATTERY

9LPRS365BKLFT

http://hobi-elektronika.net

DDR

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Reference

Reference

Reference

Cathedral Peak

Cathedral Peak

Cathedral Peak

242Monday, May 05, 2008

242Monday, May 05, 2008

242Monday, May 05, 2008

-1

-1

-1

3D3V_S0

R146

R146

1 2

0R0603-PAD

0R0603-PAD

A

12

C190

C190

DY

DY

12

C183

C183

SC1U16V3ZY-GP

SC1U16V3ZY-GP

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

12

DY

DY

12

EC58

EC58

C463

C463

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

DY

DY

12

C235

C235

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

B

12

C459

C459

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C465

C465

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

DY

DY

12

C231

C231

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

R197

R197

1 2

0R0603-PAD

0R0603-PAD

12

C462

C462

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

3D3V_S0

12

DY

DY

C246

C246

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

C

12

C195

C195

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

DY

DY

D

12

C214

C214

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

12

C453

C453

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

3D3V_CLKGEN_S03D3V_48MPWR_S0 3D3V_CLKPLL_S0

12

C198

C198

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

E

R157

R157

1 2

0R0603-PAD

0R0603-PAD

12

C234

C234

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

3D3V_S0

12

DY

DY

C184

C184

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

4 4

PCLK_ICH

-1

3 3

3D3V_S0

123

PCLK_KBC

2 2

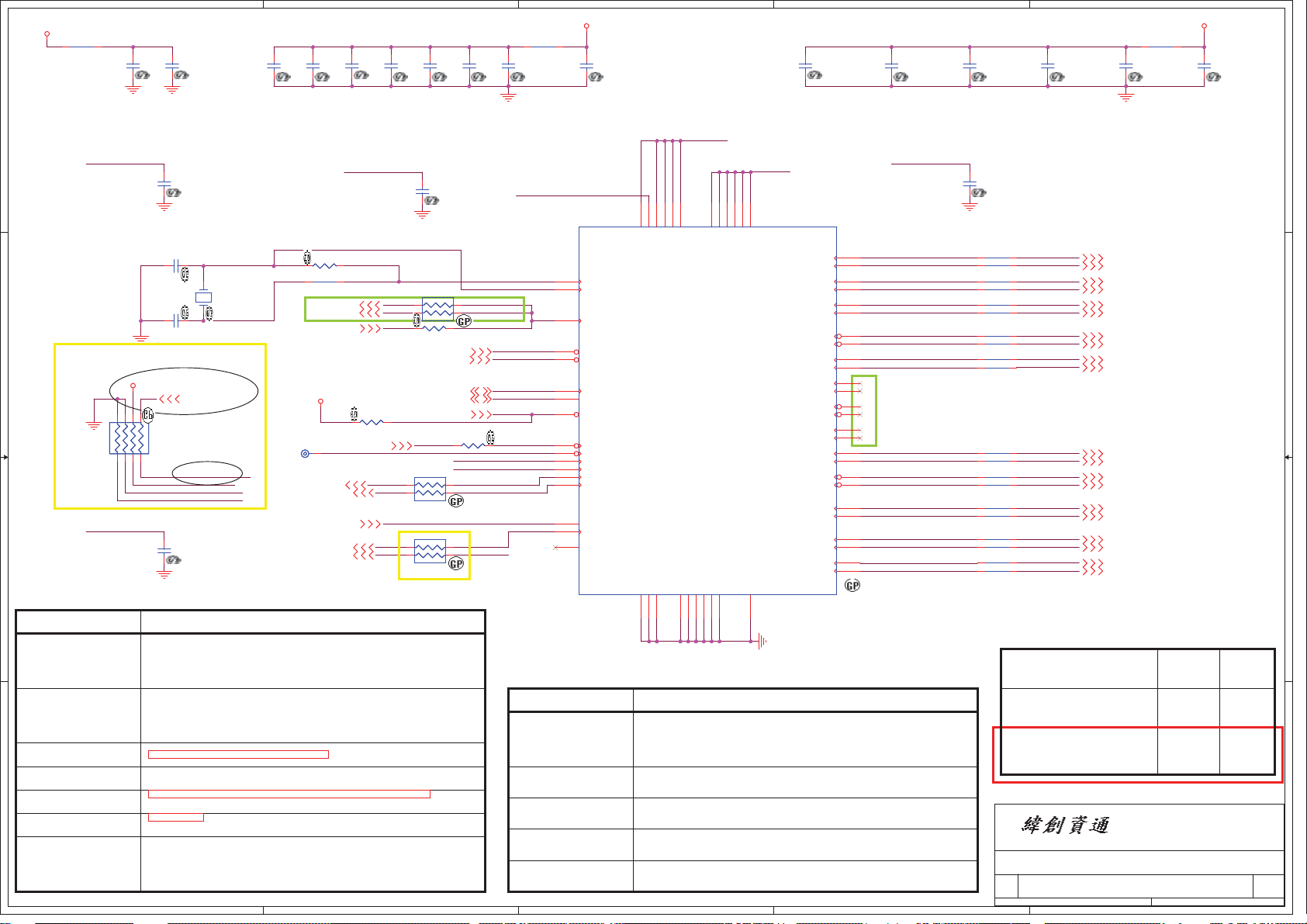

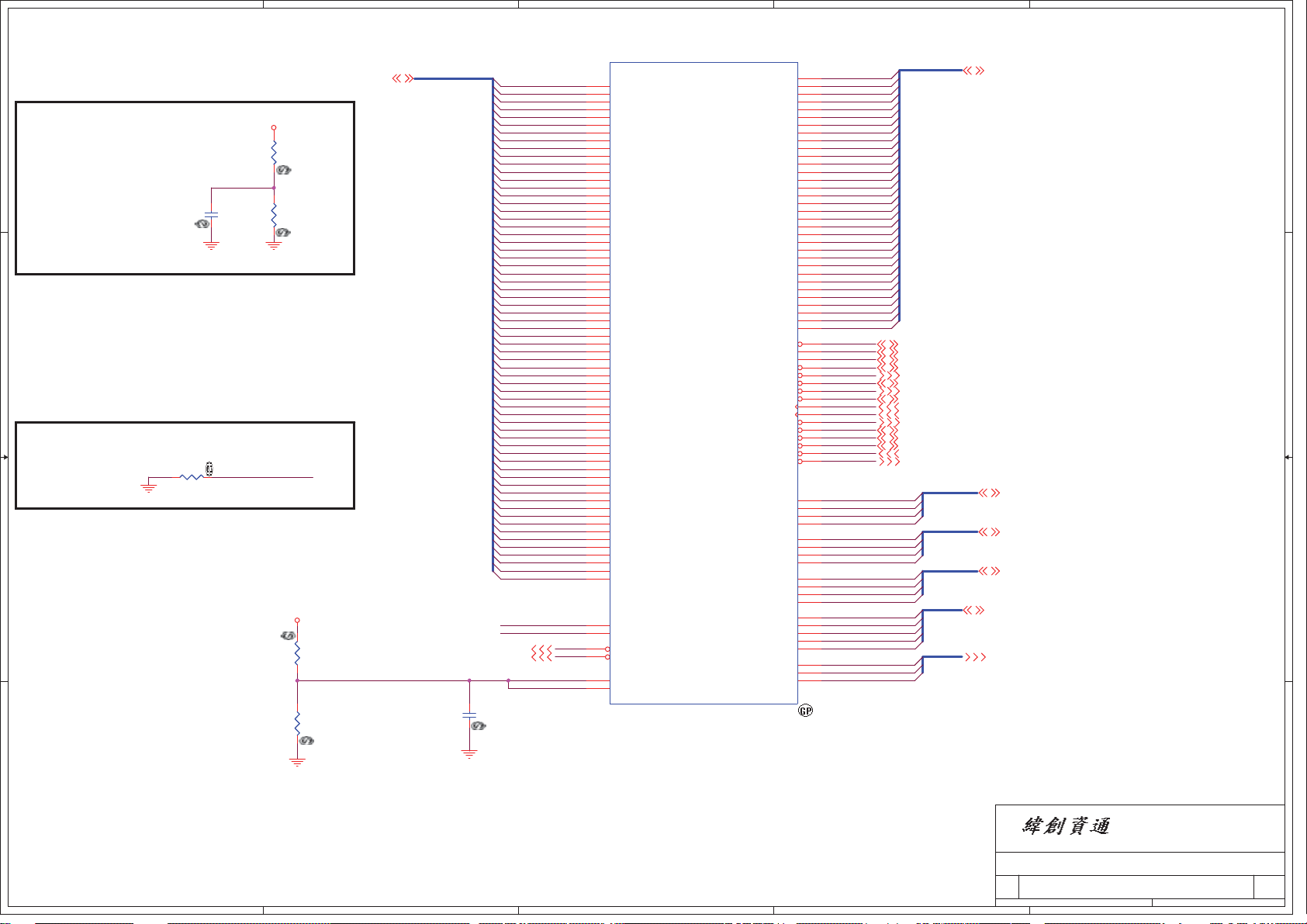

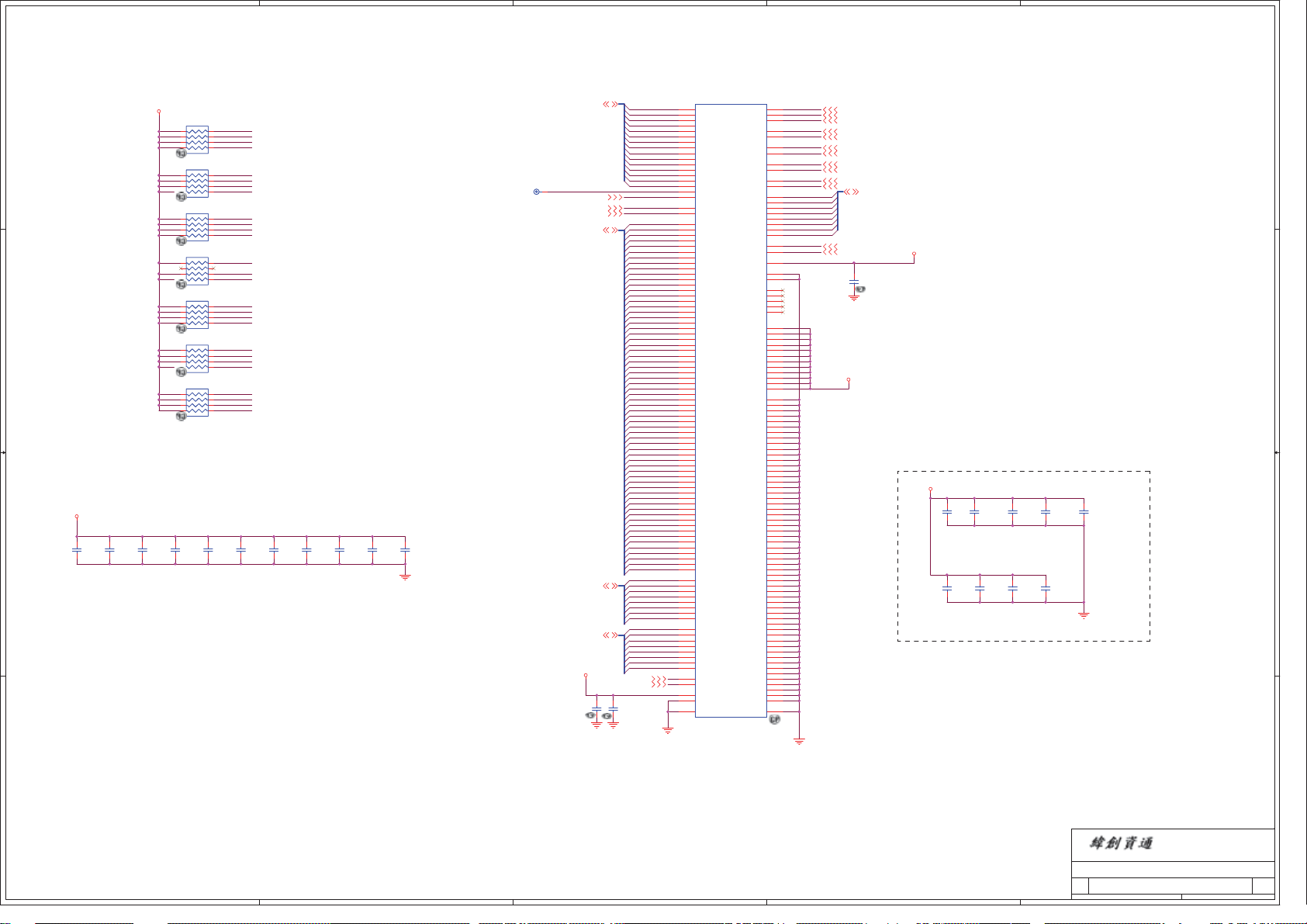

ICS9LPRS365BKLFT setting table

PIN NAME DESCRIPTION

PCI0/CR#_A

PCI1/CR#_B

PCI2/TME

PCI3

1 1

PCI4/27M_SEL

PCI_F5/ITP_EN

SRCT3/CR#_C

12

EC57

EC57

SC5P50V2CN-2GP

SC5P50V2CN-2GP

DY

DY

12

EC137

EC137

SC5P50V2CN-2GP

SC5P50V2CN-2GP

DY

DY

CL=20pF±0.2pF

C177

C177

SC27P50V2JN-2-GP

SC27P50V2JN-2-GP

1 2

1 2

C176

C176

SC27P50V2JN-2-GP

SC27P50V2JN-2-GP

0505 Sawp nets for PCLKCLK2 and CPU_SEL2_R

0505 Sawp nets for 3D3V_S0 and CPU_SEL2

678

RN59

RN59

SRN10KJ-6-GP

SRN10KJ-6-GP

4 5

12

Byte 5, bit 7

0 = PCI0 enabled (default)

1= CR#_A enabled. Byte 5, bit 6 controls whether CR#_A controls SRC0 or SRC2 pair

Byte 5, bit 6

0 = CR#_A controls SRC0 pair (default),

1= CR#_A controls SRC2 pair

Byte 5, bit 5

0 = PCI1 enabled (default)

1= CR#_B enabled. Byte 5, bit 6 controls whether CR#_B controls SRC1 or SRC4 pair

Byte 5, bit 4

0 = CR#_B controls SRC1 pair (default)

1= CR#_B controls SRC4 pair

0 = Overclocking of CPU and SRC Allowed

1 = Overclocking of CPU and SRC NOT allowed

3.3V PCI clock output

0 = Pin24 as SRC-1, Pin25 as SRC-1#, Pin20 as DOT96, Pin21 as DOT96#

1 = Pin24 as 27MHz, Pin25 as 27MHz_SS, Pin20 as SRC-0, Pin21 as SRC-0#

0 =SRC8/SRC8#

1 = ITP/ITP#

Byte 5, bit 3

0 = SRC3 enabled (default)

1= CR#_C enabled. Byte 5, bit 2 controls whether CR#_C controls SRC0 or SRC2 pair

Byte 5, bit 2

0 = CR#_C controls SRC0 pair (default),

1= CR#_C controls SRC2 pair

A

GEN_XTAL_IN

12

X3

X3

X-14D31818M-44GP

X-14D31818M-44GP

82.30005.951

82.30005.951

GEN_XTAL_OUT_R

CPU_SEL2 4,7

CPU_SEL2_R

PCLKCLK2

PCLKCLK4

PCLKCLK5

EC56

EC56

SC5P50V2CN-2GP

SC5P50V2CN-2GP

DY

DY

R154 10MR2J-L-GP

R154 10MR2J-L-GP

R153 0R0402-PADR153 0R0402-PAD

TP158TPAD30 TP158TPAD30

DY

DY

CLK48_5158E24

CLK48_ICH18

CPU_SEL04,7

3D3V_S0

PCLK_KBC30

PCLK_ICH18

CPU_SEL14,7

CLK_ICH1418

PCLK_FWH31

12

12

DY

DY

R155 10KR2J-3-GP

R155 10KR2J-3-GP

CLK_MCH_OE#7

RN17

RN17

-1

GEN_XTAL_OUT

RN51

RN51

1

2 3

R156 2K2R2J-2-GPR156 2K2R2J-2-GP

PM_STPPCI#18

PM_STPCPU#18

SMBC_ICH12,13,20

SMBD_ICH12,13,20

CLK_PWRGD18

12

R150

R150

1

2 3

SRN33J-5-GP-U

SRN33J-5-GP-U

1

2 3

RN70

RN70

SRN33J-5-GP-U

SRN33J-5-GP-U

B

SRN33J-5-GP-U

SRN33J-5-GP-U

4

12

1 2

DY

DY

475R2F-L1-GP

475R2F-L1-GP

4

4

PCLKCLK3

3D3V_48MPWR_S0

U19

U19

3

X1

2

X2

SA

CLK48

17

USB_48MHZ/FSLA

45

PCI_STOP#

44

CPU_STOP#

7

SCLK

6

SDATA

63

CK_PWRGD/PD#

PCLKCLK0

PCLKCLK1

PCLKCLK2

PCLKCLK3

PCLKCLK4

PCLKCLK5

CPU_SEL2_R

8

PCI0/CR#_A

10

PCI1/CR#_B

11

PCI2/TME

12

PCI3

13

PCI4/27_SELECT

14

PCI_F5/ITP_EN

64

FSLB/TEST_MODE

5

REF0/FSLC/TEST_SEL

55

NC#55

ICS9LPRS365BKLFT-GP

ICS9LPRS365BKLFT-GP

71.09365.A03

71.09365.A03

PIN NAME DESCRIPTION

SRCC3/CR#_D

SRCC7/CR#_E

SRCT7/CR#_F

SRCC11/CR#_G

SRCT11/CR#_H

http://hobi-elektronika.net

3D3V_CLKGEN_S0

3D3V_CLKPLL_S0CLK48_ICH

46

62

16

4

23

9

VDD48

VDDPCI

VDDREF

VDDSRC

VDDCPU

VDDPLL3

GNDREF

GNDPCI

GND48

GND

GNDSRC

1

15

18

22

30

36

Byte 5, bit 1

0 = SRC3 enabled (default)

1= CR#_D enabled. Byte 5, bit 0 controls whether CR#_D controls SRC1 or SRC4 pair

Byte 5, bit 0

0 = CR#_D controls SRC1 pair (default)

1= CR#_D controls SRC4 pair

Byte 6, bit 7

0 = SRC7# enabled (default)

1= CR#_F controls SRC6

Byte 6, bit 6

0 = SRC7 enabled (default)

1= CR#_F controls SRC8

Byte 6, bit 5

0 = SRC11# enabled (default)

1= CR#_G controls SRC9

Byte 6, bit 4

0 = SRC11 enabled (default)

1= CR#_H controls SRC10

C

43

52

19

27

VDD96_IO

VDDSRC_IO

VDDSRC_IO

VDDPLL3_IO

GND

GNDSRC

GNDSRC

GNDCPU

26

49

59

33

56

CPUT0

VDDSRC_IO

VDDCPU_IO

27MHZ_NONSS/SRCT1/SE1

27MHZ_SS/SRCC1/SE2

GND

65

CPUC0

CPUT1_F

CPUC1_F

CPUT2_ITP/SRCT8

CPUC2_ITP/SRCC8

SRCT7/CR#_F

SRCC7/CR#_E

SRCT6

SRCC6

SRCT10

SRCC10

SRCT11/CR#_H

SRCC11/CR#_G

SRCT9

SRCC9

SRCT4

SRCC4

SRCT3/CR#_C

SRCC3/CR#_D

SRCT2/SATAT

SRCC2/SATAC

SRCT0/DOTT_96

SRCC0/DOTC_96

2nd:

71.00875.C03

RTM875N-606-LFT QFN 64P

61

60

58

57

54

53

51

50

48

47

41

42

40

39

37

38

34

35

31

32

28

29

24

25

20

21

CLK_ICH14

CLK_CPU_BCLK_1

CLK_CPU_BCLK_1#

CLK_MCH_BCLK_1

CLK_MCH_BCLK_1#

CLK_PCIE_LAN_R

CLK_PCIE_LAN#_R

CLK_PCIE_NEW_R

CLK_PCIE_NEW#_R

CLK_PCIE_ICH_1

CLK_PCIE_ICH_1#

SA

CLK_PCIE_MINI_1

CLK_PCIE_MINI_1#

CLK_MCH_3GPLL_1

CLK_MCH_3GPLL_1#

CLK_PCIE_SATA_1

CLK_PCIE_SATA_1#

DREFSSCLK_1

DREFSSCLK#_1

DREFCLK_1

DREFCLK#_1

D

R160 0R0402-PADR160 0R0402-PAD

R166 0R0402-PADR166 0R0402-PAD

R167 0R0402-PADR167 0R0402-PAD

R169 0R0402-PADR169 0R0402-PAD

R173 0R0402-PADR173 0R0402-PAD

R176 0R0402-PADR176 0R0402-PAD

R182 0R0402-PADR182 0R0402-PAD

R181 0R0402-PADR181 0R0402-PAD

R195 0R0402-PADR195 0R0402-PAD

R194 0R0402-PADR194 0R0402-PAD

R192 0R0402-PADR192 0R0402-PAD

R193 0R0402-PADR193 0R0402-PAD

R180 0R0402-PADR180 0R0402-PAD

R184 0R0402-PADR184 0R0402-PAD

R174 0R0402-PADR174 0R0402-PAD

R177 0R0402-PADR177 0R0402-PAD

R168 0R0402-PADR168 0R0402-PAD

R171 0R0402-PADR171 0R0402-PAD

R158 0R0402-PADR158 0R0402-PAD

R161 0R0402-PADR161 0R0402-PAD

12

EC55

EC55

SC5P50V2CN-2GP

SC5P50V2CN-2GP

DY

DY

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

SEL2

FSC

1

0

01

0

SEL1

FSB

01

01

CLK_CPU_BCLK 4

CLK_CPU_BCLK# 4

CLK_MCH_BCLK 6

CLK_MCH_BCLK# 6

CLK_PCIE_LAN 25

CLK_PCIE_LAN# 25

CLK_PCIE_NEW 27

CLK_PCIE_NEW# 27

CLK_PCIE_ICH 18

CLK_PCIE_ICH# 18

CLK_PCIE_MINI1 27

CLK_PCIE_MINI1# 27

CLK_MCH_3GPLL 7

CLK_MCH_3GPLL# 7

CLK_PCIE_SATA 17

CLK_PCIE_SATA# 17

DREFSSCLK 7

DREFSSCLK# 7

DREFCLK 7

DREFCLK# 7

SEL0

FSA

1

01

CPU

100M

133M

166M

200M

00 0

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Clock Generator

Clock Generator

Clock Generator

Cathedral Peak

Cathedral Peak

Cathedral Peak

342Friday, May 16, 2008

342Friday, May 16, 2008

342Friday, May 16, 2008

E

CPU

NB

LAN

New Card

SB DMI

MINI1

NB CLK

SB SATA

NB CLK

NB CLK

(96 MHz)

FSB

X

533M

667M

800M

1066M266M

-1

-1

-1

A

B

C

D

E

H_A#[35..3]6

4 4

H_ADSTB#06

H_REQ#[4..0]6

3 3

Side Band

Non GTL

H_ADSTB#16

H_A20M#17

H_FERR#17

H_IGNNE#17

H_STPCLK#17

H_INTR17

H_NMI17

H_SMI#17

TP52TPAD30 TP52TPAD30

TP49TPAD30 TP49TPAD30

TP48TPAD30 TP48TPAD30

TP89TPAD30 TP89TPAD30

TP92TPAD30 TP92TPAD30

TP87TPAD30 TP87TPAD30

2 2

1 1

TP90TPAD30 TP90TPAD30

TP88TPAD30 TP88TPAD30

TP72TPAD30 TP72TPAD30

TP93TPAD30 TP93TPAD30

XDP_TMS

XDP_TDI

XDP_BPM#5

H_CPURST#

XDP_TCK

XDP_TRST#

H_A#[35..3]

U33A

U33A

H_A#3

J4

L5

L4

K5

M3

N2

J1

N3

P5

P2

L2

P4

P1

R1

M1

K3

H2

K2

J3

L1

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

U2

V4

W3

AA4

AB2

AA3

V1

A6

A5

C4

D5

C6

B4

A3

M4

N5

T2

V3

B2

C3

D2

D22

D3

F6

B1

1 2

1 2

1 2

1 2

DY

DY

1 2

1 2

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

ADSTB0#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

A32#

A33#

A34#

A35#

ADSTB1#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD#M4

RSVD#N5

RSVD#T2

RSVD#V3

RSVD#B2

RSVD#C3

RSVD#D2

RSVD#D22

RSVD#D3

RSVD#F6

KEY_NC

BGA479-SKT6-GPU6

BGA479-SKT6-GPU6

62.10079.001

62.10079.001

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

RSVD_CPU_1

RSVD_CPU_2

RSVD_CPU_3

RSVD_CPU_4

RSVD_CPU_5

RSVD_CPU_6

RSVD_CPU_7

RSVD_CPU_8

RSVD_CPU_9

RSVD_CPU_10

RSVD_CPU_11

R102 54D9R2F-L1-GPR102 54D9R2F-L1-GP

R101 54D9R2F-L1-GPR101 54D9R2F-L1-GP

R97 54D9R2F-L1-GPR97 54D9R2F-L1-GP

R116 51R2F-2-GP

R116 51R2F-2-GP

R94 54D9R2F-L1-GPR94 54D9R2F-L1-GP

R96 54D9R2F-L1-GPR96 54D9R2F-L1-GP

All place within 2" to CPU

A

1 OF 4

1 OF 4

ADDR GROUP 0

ADDR GROUP 0

ADDR GROUP 1

ADDR GROUP 1

ICH

ICH

RESERVED

RESERVED

2nd: 62.10053.401

1D05V_S0

DEFER#

DRDY#

DBSY#

IERR#

LOCK#

RESET#

TRDY#

HITM#

BPM0#

BPM1#

BPM2#

BPM3#

PRDY#

PREQ#

TRST#

XDP/ITP SIGNALS CONTROL

XDP/ITP SIGNALS CONTROL

THERMAL

THERMAL

PROCHOT#

THRMDA

THRMDC

THERMTRIP#

HCLK

HCLK

BCLK0

BCLK1

ADS#

BNR#

BPRI#

BR0#

INIT#

RS0#

RS1#

RS2#

HIT#

TCK

TDI

TDO

TMS

DBR#

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

C1

F3

F4

G3

G2

G6

E4

XDP_BPM#0

AD4

XDP_BPM#1

AD3

XDP_BPM#2

AD1

XDP_BPM#3

AC4

XDP_BPM#4

AC2

XDP_BPM#5

AC1

XDP_TCK

AC5

XDP_TDI

AA6

XDP_TDO

AB3

XDP_TMS

AB5

XDP_TRST#

AB6

XDP_DBRESET#

C20

D21

A24

B25

C7

A22

A21

H_IERR#

H_RS#0

H_RS#1

H_RS#2

PM_THRMTRIP#

should connect to

ICH9 and MCH

without T-ing

( No stub)

B

TP57 TPAD30TP57 TPAD30

H_ADS# 6

H_BNR# 6

H_BPRI# 6

H_DEFER# 6

H_DRDY# 6

H_DBSY# 6

H_BREQ#0 6

H_INIT# 17

H_LOCK# 6

H_CPURST# 6,41

H_TRDY# 6

H_HIT# 6

H_HITM# 6

TP27 TPAD30TP27 TPAD30

TP25 TPAD30TP25 TPAD30

TP28 TPAD30TP28 TPAD30

TP41 TPAD30TP41 TPAD30

TP30 TPAD30TP30 TPAD30

TP37 TPAD30TP37 TPAD30

TP29 TPAD30TP29 TPAD30

TP39 TPAD30TP39 TPAD30

TP40 TPAD30TP40 TPAD30

TP44 TPAD30TP44 TPAD30

TP34 TPAD30TP34 TPAD30

TP91 TPAD30TP91 TPAD30

CPU_PROCHOT#

H_THERMDA 21

H_THERMDC 21

PM_THRMTRIP-A# 7,17,32

CLK_CPU_BCLK 3

CLK_CPU_BCLK# 3

1D05V_S0

12

R125

R125

56R2J-4-GP

56R2J-4-GP

H_RS#[2..0] 6

1D05V_S0

Layout Note:

"CPU_GTLREF0"

0.5" max length.

TP95 TPAD30TP95 TPAD30

12

R123

R123

68R2-GP

68R2-GP

DY

DY

1 2

R124

R124

0R2J-2-GP

0R2J-2-GP

Place testpoint on

H_IERR# with a GND

0.1" away

H_THERMDA

DY

DY

H_THERMDC

CPU_PROCHOT#_R 34

1D05V_S0

R263

R263

1KR2F-3-GP

1KR2F-3-GPTP47TPAD30 TP47TPAD30

2KR2F-3-GP

2KR2F-3-GP

R266

R266

1 2

12

12

C136

C136

SC2200P50V2KX-2GP

SC2200P50V2KX-2GP

Follow Demo Circuit

DY

DY

DY

DY

12

DY

DY

1 2

DY

DY

1 2

DY

DY

TEST1

TEST2

TEST4

C

1 2

R118 1KR2J-1-GP

R118 1KR2J-1-GP

1 2

R295 1KR2J-1-GP

R295 1KR2J-1-GP

C351 SCD1U10V2KX-4GP

C351 SCD1U10V2KX-4GP

XDP_DBRESET#

XDP_TDO

R121 1KR2J-1-GP

R121 1KR2J-1-GP

R100 54D9R2F-L1-GP

R100 54D9R2F-L1-GP

http://hobi-elektronika.net

CPU_GTLREF0

12

DY

DY

C352

C352

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

3D3V_S0

1D05V_S0

2 OF 4

2 OF 4

U33B

U33B

H_D#0

E22

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_DSTBN#06

H_DSTBP#06

H_DINV#06

H_DSTBN#16

H_DSTBP#16

H_DINV#16

TP86TPAD30 TP86TPAD30

TP21TPAD30 TP21TPAD30

TP150TPAD30 TP150TPAD30

CPU_SEL03,7

CPU_SEL13,7

CPU_SEL23,7

Net "TEST4" as short as possible,

make sure "TEST4" routing is

reference to GND and away other

noisy signals

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

TEST1

TEST2

RSVD_CPU_12

TEST4

RSVD_CPU_13

RSVD_CPU_14

D0#

F24

D1#

E26

D2#

G22

D3#

F23

D4#

G25

D5#

E25

D6#

E23

D7#

K24

D8#

G24

D9#

J24

D10#

J23

D11#

H22

D12#

F26

D13#

K22

D14#

H23

D15#

J26

DSTBN0#

H26

DSTBP0#

H25

DINV0#

N22

D16#

K25

D17#

P26

D18#

R23

D19#

L23

D20#

M24

D21#

L22

D22#

M23

D23#

P25

D24#

P23

D25#

P22

D26#

T24

D27#

R24

D28#

L25

D29#

T25

D30#

N25

D31#

L26

DSTBN1#

M26

DSTBP1#

N24

DINV1#

AD26

GTLREF

C23

TEST1

D25

TEST2

C24

TEST3

AF26

TEST4

AF1

TEST5

A26

TEST6

B22

BSEL0

B23

BSEL1

C21

BSEL2

BGA479-SKT6-GPU6

BGA479-SKT6-GPU6

62.10079.001

62.10079.001

D

DATA GRP0 DATA GRP1

DATA GRP0 DATA GRP1

MISC

MISC

H_DINV#[3..0]

H_DSTBN#[3..0]

H_DSTBP#[3..0]

H_D#[63..0]

H_D#32

Y22

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

DATA GRP2DATA GRP3

DATA GRP2DATA GRP3

D43#

D44#

D45#

D46#

D47#

DSTBN2#

DSTBP2#

DINV2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN3#

DSTBP3#

DINV3#

COMP0

COMP1

COMP2

COMP3

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

H_D#33

AB24

H_D#34

V24

H_D#35

V26

H_D#36

V23

H_D#37

T22

H_D#38

U25

H_D#39

U23

H_D#40

Y25

H_D#41

W22

H_D#42

Y23

H_D#43

W24

H_D#44

W25

H_D#45

AA23

H_D#46

AA24

H_D#47

AB25

Y26

AA26

U22

H_D#48

AE24

H_D#49

AD24

H_D#50

AA21

H_D#51

AB22

H_D#52

AB21

H_D#53

AC26

H_D#54

AD20

H_D#55

AE22

H_D#56

AF23

H_D#57

AC25

H_D#58

AE21

H_D#59

AD21

H_D#60

AC22

H_D#61

AD23

H_D#62

AF22

H_D#63

AC23

AE25

AF24

AC20

COMP0

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

R105 27D4R2F-L1-GPR105 27D4R2F-L1-GP

COMP1

R104 54D9R2F-L1-GPR104 54D9R2F-L1-GP

COMP2

R98 27D4R2F-L1-GPR98 27D4R2F-L1-GP

COMP3

R99 54D9R2F-L1-GPR99 54D9R2F-L1-GP

Layout Note:

Comp0, 2 connect with Zo=27.4 ohm, make

trace length shorter than 0.5" .

Comp1, 3 connect with Zo=55 ohm, make

trace length shorter than 0.5" .

H_DINV#[3..0] 6

H_DSTBN#[3..0] 6

H_DSTBP#[3..0] 6

H_D#[63..0] 6

H_DSTBN#2 6

H_DSTBP#2 6

H_DINV#2 6

H_DSTBN#3 6

H_DSTBP#3 6

H_DINV#3 6

1 2

1 2

1 2

1 2

H_DPRSTP# 7,17,34

H_DPSLP# 17

H_DPWR# 6

H_PWRGD 17,32,41

H_CPUSLP# 6

PSI# 34

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CPU (1 of 2)

CPU (1 of 2)

CPU (1 of 2)

Cathedral Peak

Cathedral Peak

Cathedral Peak

E

-1

-1

442Friday, May 16, 2008

442Friday, May 16, 2008

442Friday, May 16, 2008

-1

A

G5

G5

1 2

GAP-CLOSE-PWR-2U

GAP-CLOSE-PWR-2U

C114

C114

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

DY

DY

H_VID[6..0] 34

VCC_CORE

12

12

VCC_CORE

DY

DY

VCC_CORE

CAP

CAP

12

R77

R77

100R2F-L1-GP-U

100R2F-L1-GP-U

R88

R88

100R2F-L1-GP-U

100R2F-L1-GP-U

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AF7

AE7

VCC_CORE

VCCP_1D05

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

12

VCC_CORE

4 4

3 3

AA10

AA12

2 2

1 1

AA13

AA15

AA17

AA18

AA20

AC10

AB10

AB12

AB14

AB15

AB17

AB18

U33C

U33C

A7

VCC

A9

VCC

A10

VCC

A12

VCC

A13

VCC

A15

VCC

A17

VCC

A18

VCC

A20

VCC

B7

VCC

B9

VCC

B10

VCC

B12

VCC

B14

VCC

B15

VCC

B17

VCC

B18

VCC

B20

VCC

C9

VCC

C10

VCC

C12

VCC

C13

VCC

C15

VCC

C17

VCC

C18

VCC

D9

VCC

D10

VCC

D12

VCC

D14

VCC

D15

VCC

D17

VCC

D18

VCC

E7

VCC

E9

VCC

E10

VCC

E12

VCC

E13

VCC

E15

VCC

E17

VCC

E18

VCC

E20

VCC

F7

VCC

F9

VCC

F10

VCC

F12

VCC

F14

VCC

F15

VCC

F17

VCC

F18

VCC

F20

VCC

AA7

VCC

AA9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AB9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

BGA479-SKT6-GPU6

BGA479-SKT6-GPU6

62.10079.001

62.10079.001

3 OF 4

3 OF 4

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCA

VCCA

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VCCSENSE

VSSSENSE

B

12

12

C86

C86

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

DY

DY

12

12

C123

C123

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

CAP

CAP

1D05V_S0

C100

C100

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

1D5V_VCCA_S0

VCC_CORE

12

C120

C120

C102

C102

layout note: "1D5V_VCCA_S0"

as short as possible

DY

DY

Layout Note:

VCCSENSE and VSSSENSE lines

should be of equal length.

Layout Note:

Provide a test point (with

no stub) to connect a

differential probe

between VCCSENSE and

VSSSENSE at the location

where the two 54.9ohm

resistors terminate the

55 ohm transmission line.

12

C122

C122

C88

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

DY

DY

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

CAP

CAP

12

C88

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

DY

DY

12

12

C135

C135

C93

C93

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

CAP

CAP

12

C421

C421

C427

C427

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

VCC_SENSE 34

VSS_SENSE 34

12

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

DY

DY

12

C380

C380

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

CAP

CAP

CAP

CAP

L11

L11

1 2

PBY160808T-121Y-GP

PBY160808T-121Y-GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

68.00206.021

68.00206.021

C90

C90

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

DY

DY

12

C375

C375

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

12

C130

C130

C124

C124

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

DY

DY

12

12

C381

C381

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

DY

DY

DY

DY

1D5V_S0

12

C89

C89

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

DY

DY

12

C70

C70

C374

C374

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

DY

DY

DY

DY

1D05V_S0

C

12

12

C106

C106

C94

C94

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

DY

DY

12

12

C101

C101

C104

C104

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

VCC_CORE

12

3 4

12

12

C71

C71

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

DY

DY

DY

DY

12

12

C108

C108

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SB

TC9

TC9

ST900U2D5VM-1-GP

ST900U2D5VM-1-GP

NEC

NEC

77.E9071.011

77.E9071.011

12

C103

C103

C105

C105

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

DY

DY

12

C110

C110

C112

C112

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

DY

DY

12

12

C98

C98

C95

C95

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

12

C99

C99

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

DY

DY

D

C433

C433

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

TP22

TP22

TPAD30

TPAD30

U33D

U33D

A4

VSS

A8

VSS

A11

VSS

A14

VSS

A16

VSS

A19

VSS

A23

VSS

AF2

VSS

B6

VSS

B8

VSS

B11

VSS

B13

VSS

B16

VSS

B19

VSS

B21

VSS

B24

VSS

C5

VSS

C8

VSS

C11

VSS

C14

VSS

C16

VSS

C19

VSS

C2

VSS

C22

VSS

C25

VSS

D1

VSS

D4

VSS

D8

VSS

D11

VSS

D13

VSS

D16

VSS

D19

VSS

D23

VSS

D26

VSS

E3

VSS

E6

VSS

E8

VSS

E11

VSS

E14

VSS

E16

VSS

E19

VSS

E21

VSS

E24

VSS

F5

VSS

F8

VSS

F11

VSS

F13

VSS

F16

VSS

F19

VSS

F2

VSS

F22

VSS

F25

VSS

G4

VSS

G1

VSS

G23

VSS

G26

VSS

H3

VSS

H6

VSS

H21

VSS

H24

VSS

J2

VSS

J5

VSS

J22

VSS

J25

VSS

K1

VSS

K4

VSS

K23

VSS

K26

VSS

L3

VSS

L6

VSS

L21

VSS

L24

VSS

M2

VSS

M5

VSS

M22

VSS

M25

VSS

N1

VSS

N4

VSS

N23

VSS

N26

VSS

P3

VSS

BGA479-SKT6-GPU6

BGA479-SKT6-GPU6

62.10079.001

62.10079.001

4 OF 4

4 OF 4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

TPAD30

TPAD30

TP24

TP24

TPAD30

TPAD30

TP26

TP26

TP94

TP94

TPAD30

TPAD30

TP151

TP151

TPAD30

TPAD30

TP23

TP23

TPAD30

TPAD30

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A

B

http://hobi-elektronika.net

C

D

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU (2 of 2)

CPU (2 of 2)

CPU (2 of 2)

Cathedral Peak

Cathedral Peak

Cathedral Peak

-1

-1

542Friday, May 16, 2008

542Friday, May 16, 2008

542Friday, May 16, 2008

E

-1

5

H_SWING

1D05V_S0

12

R317

R317

221R2F-2-GP

221R2F-2-GP

12

R316

R316

100R2F-L1-GP-U

100R2F-L1-GP-U

H_RCOMP

D D

H_SWING routing Trace width and

Spacing use 10 / 20 mil

H_SWING Resistors and

Capacitors close MCH

500 mil ( MAX )

12

C450

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

C C

H_RCOMP routing Trace width and

Spacing use 10 / 20 mil

C450

1 2

R312

R312

24D9R2F-L-GP

24D9R2F-L-GP

Place them near to the chip ( < 0.5")

B B

1D05V_S0

R322

R322

1KR2F-3-GP

1KR2F-3-GP

1 2

12

R318

R318

2KR2F-3-GP

2KR2F-3-GP

4

H_AVREF

H_D#[63..0]

H_CPURST#4,41

H_CPUSLP#4

12

C455

C455

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_RCOMP

M11

N12

P13

N10

AD14

Y10

Y12

Y14

AA8

AA13

AA9

AA11

AD11

AD10

AD13

AE12

AE9

AA2

AD8

AA3

AD3

AD7

AE14

AF3

AC1

AE3

AC3

AE11

AE8

AG2

AD6

C12

E11

A11

B11

F2

G8

F8

E6

G2

H6

H2

F6

D4

H3

M9

J1

J2

J6

P2

L2

R2

N9

L6

M5

J3

N2

R1

N5

N6

N8

L7

M3

Y3

Y6

Y7

W2

Y9

C5

E3

H_D#[63..0]4

3

U35A

U35A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_SWING

H_RCOMP

H_CPURST#

H_CPUSLP#

H_AVREF

H_DVREF

CANTIGA-GM-GP-U-NF

CANTIGA-GM-GP-U-NF

71.CNTIG.00U

71.CNTIG.00U

HOST

HOST

1 OF 10

1 OF 10

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

A14

C15

F16

H13

C18

M16

J13

P16

R16

N17

M13

E17

P17

F17

G20

B19

J16

E20

H16

J20

L17

A17

B17

L16

C21

J17

H20

B18

K17

B20

F21

K21

L20

H12

B16

G17

A9

F11

G12

E9

B10

AH7

AH6

J11

F9

H9

E12

H11

C9

J8

L3

Y13

Y1

L10

M7

AA5

AE6

L9

M8

AA6

AE5

B15

K13

F13

B13

B14

B6

F12

C8

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

2

H_A#[35..3]

H_ADS# 4

H_ADSTB#0 4

H_ADSTB#1 4

H_BNR# 4

H_BPRI# 4

H_BREQ#0 4

H_DEFER# 4

H_DBSY# 4

CLK_MCH_BCLK 3

CLK_MCH_BCLK# 3

H_DPWR# 4

H_DRDY# 4

H_HIT# 4

H_HITM# 4

H_LOCK# 4

H_TRDY# 4

H_DINV#[3..0]

H_DSTBN#[3..0]

H_DSTBP#[3..0]

1

H_A#[35..3] 4

H_DINV#[3..0] 4

H_DSTBN#[3..0] 4

H_DSTBP#[3..0] 4

H_REQ#[4..0] 4

H_RS#[2..0] 4

A A

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Cantiga (1 of 6)

Cantiga (1 of 6)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

5

4

http://hobi-elektronika.net

3

2

Date: Sheet of

Date: Sheet of

Date: Sheet of

Cantiga (1 of 6)

Cathedral Peak

Cathedral Peak

Cathedral Peak

1

-1

-1

642Monday, May 05, 2008

642Monday, May 05, 2008

642Monday, May 05, 2008

-1

5

1D8V_S3

12

R339

R339

1KR2F-3-GP

1KR2F-3-GP

D D

12

R338

R338

3K01R2F-3-GP

3K01R2F-3-GP

12

R334

R334

1KR2F-3-GP

1KR2F-3-GP

12

C475

C475

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

12

C472

C472

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

SM_RCOMP_VOH

12

C477

C477

SC2D2U6D3V3MX-1-GP

SC2D2U6D3V3MX-1-GP

SM_RCOMP_VOL

12

C470

C470

SC2D2U6D3V3MX-1-GP

SC2D2U6D3V3MX-1-GP

layout take note

1D8V_S3

12

R331

R331

80D6R2F-L-GP

80D6R2F-L-GP

M_RCOMPP

M_RCOMPN

12

R330

R330

80D6R2F-L-GP

RN32

RN32

4

SRN10KJ-5-GP

SRN10KJ-5-GP

CFG19

CFG20

CFG5

CFG6

CFG7

CFG9

CFG10

CFG12

CFG13

CFG16

1

23

3D3V_S0

80D6R2F-L-GP

VGATE_PWRGD18,34

PWROK18,32

PM_SYNC#18

H_DPRSTP#4,17,34

PLT_RST1#18,25,27,30,31

PM_THRMTRIP-A#4,17,32

R353 0R0402-PADR353 0R0402-PAD

SB

PM_DPRSLPVR18,34

C C

3D3V_S0

R207 4K02R2F-GP

R207 4K02R2F-GP

1 2

DY

DY

R208 4K02R2F-GP

R208 4K02R2F-GP

1 2

DY

DY

R345 2K21R2F-GP

R345 2K21R2F-GP

1 2

DY

DY

R186 2K21R2F-GP

R186 2K21R2F-GP

1 2

DY

DY

R188 2K21R2F-GP

R188 2K21R2F-GP

1 2

DY

DY

R332 2K21R2F-GP

R332 2K21R2F-GP

1 2

DY

DY

R336 2K21R2F-GP

R336 2K21R2F-GP

1 2

DY

DY

R190 2K21R2F-GP

R190 2K21R2F-GP

1 2

DY

DY

R185 2K21R2F-GP

R185 2K21R2F-GP

1 2

DY

DY

B B

R189 2K21R2F-GP

R189 2K21R2F-GP

1 2

DY

DY

PM_EXTTS#0

PM_EXTTS#1

R354 0R2J-2-GP

R354 0R2J-2-GP

1 2

12

1 2

R140 300R2F-GPR140 300R2F-GP

SC100P50V2JN-3GP

SC100P50V2JN-3GP

CPU_SEL03,4

CPU_SEL13,4

CPU_SEL23,4

DY

DY

C165

C165

12

DY

DY

CFG5

CFG6

CFG7

CFG9

CFG10

CFG12

CFG13

CFG16

CFG19

CFG20

PM_SYNC#

H_DPRSTP#

PM_EXTTS#0

PM_EXTTS#1

PWROK_GD

RSTIN#

PM_THRMTRIP-A#

PM_DPRSLPVR

U35B

U35B

M36

RESERVED#M36

N36

RESERVED#N36

R33

RESERVED#R33

T33

RESERVED#T33

AH9

RESERVED#AH9

AH10

RESERVED#AH10

AH12

RESERVED#AH12

AH13

RESERVED#AH13

K12

RESERVED#K12

AL34

RESERVED#AL34

AK34

RESERVED#AK34

AN35

RESERVED#AN35

AM35

RESERVED#AM35

T24

RESERVED#T24

B31

RESERVED#B31

B2

RESERVED#B2

M1

RESERVED#M1

AY21

RESERVED#AY21

BG23

RESERVED#BG23

BF23

RESERVED#BF23

BH18

RESERVED#BH18

BF18

RESERVED#BF18

T25

CFG_0

R25

CFG_1

P25

CFG_2

P20

CFG_3

P24

CFG_4

C25

CFG_5

N24

CFG_6

M24

CFG_7

E21

CFG_8

C23

CFG_9

C24

CFG_10

N21

CFG_11

P21

CFG_12

T21

CFG_13

R20

CFG_14

M20

CFG_15

L21

CFG_16

H21

CFG_17

P29

CFG_18

R28

CFG_19

T28

CFG_20

R29

PM_SYNC#

B7

PM_DPRSTP#

N33

PM_EXT_TS#_0

P32

PM_EXT_TS#_1

AT40

PWROK

AT11

RSTIN#

T20

THERMTRIP#

R32

DPRSLPVR

BG48

NC#BG48

BF48

NC#BF48

BD48

NC#BD48

BC48

NC#BC48

BH47

NC#BH47

BG47

NC#BG47

BE47

NC#BE47

BH46

NC#BH46

BF46

NC#BF46

BG45

NC#BG45

BH44

NC#BH44

BH43

NC#BH43

BH6

NC#BH6

BH5

NC#BH5

BG4

NC#BG4

BH3

NC#BH3

BF3

NC#BF3

BH2

NC#BH2

BG2

NC#BG2

BE2

NC#BE2

BG1

NC#BG1

BF1

NC#BF1

BD1

NC#BD1

BC1

NC#BC1

F1

NC#F1

A47

NC#A47

CANTIGA-GM-GP-U-NF

CANTIGA-GM-GP-U-NF

71.CNTIG.00U

71.CNTIG.00U

4

2 OF 10

2 OF 10

AP24

AT21

AV24

AU20

AR24

AR21

AU24

AV20

BC28

AY28

AY36

BB36

BA17

AY16

AV16

AR13

BD17

AY17

BF15

AY13

BG22

BH21

BF28

BH28

AV42

AR36

BF17

BC36

DREFCLK

B38

DREFCLK#

A38

DREFSSCLK

E41

DREFSSCLK#

F41

F43

E43

AE41

AE37

AE47

AH39

AE40

AE38

AE48

AH40

AE35

AE43

AE46

AH42

AD35

AE44

AF46

AH43

B33

B32

G33

F33

E33

C34

AH37

AH36

CLPWROK_MCH

AN36

AJ35

MCH_CLVREF

AH34

N28

M28

G36

E36

K36

H36

B12

B28

B30

B29

C29

A28

M_CLK_DDR0 12

M_CLK_DDR1 12

M_CLK_DDR2 13

M_CLK_DDR3 13

M_CLK_DDR#0 12

M_CLK_DDR#1 12

M_CLK_DDR#2 13

M_CLK_DDR#3 13

M_CKE0 12

M_CKE1 12

M_CKE2 13

M_CKE3 13

M_CS0# 12

M_CS1# 12

M_CS2# 13

M_CS3# 13

M_ODT0 12

M_ODT1 12

M_ODT2 13

M_ODT3 13

M_RCOMPP

M_RCOMPN

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_REXT

TP_SM_DRAMRST#

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

GFX_VID0

GFX_VID1

GFX_VID2

GFX_VID3

GFX_VID4

GFXVR_EN

SA

TP115TPAD30TP115TPAD30

MCH_TSATN#

SA

R328

R328

1 2

TP120TPAD30TP120TPAD30

DREFCLK 3

DREFCLK# 3

DREFSSCLK 3

DREFSSCLK# 3

CLK_MCH_3GPLL 3

CLK_MCH_3GPLL# 3

DMI_TXN0 18

DMI_TXN1 18

DMI_TXN2 18

DMI_TXN3 18

DMI_TXP0 18

DMI_TXP1 18

DMI_TXP2 18

DMI_TXP3 18

DMI_RXN0 18

DMI_RXN1 18

DMI_RXN2 18

DMI_RXN3 18

DMI_RXP0 18

DMI_RXP1 18

DMI_RXP2 18

DMI_RXP3 18

GFXVR_EN 38

R352

R352

12

0R0402-PAD

0R0402-PAD

CLK_MCH_OE# 3

MCH_ICH_SYNC# 18

TP110TPAD30TP110TPAD30

MCH_TSATN#

SA_CK_0

SA_CK_1

SB_CK_0

SB_CK_1

SA_CK#_0

SA_CK#_1

SB_CK#_0

SB_CK#_1

SA_CKE_0

SA_CKE_1

SB_CKE_0

RSVD

RSVD

SB_CKE_1

SA_CS#_0

SA_CS#_1

SB_CS#_0

SB_CS#_1

SA_ODT_0

SA_ODT_1

SB_ODT_0

SB_ODT_1

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF

SM_PWROK

SM_REXT

SM_DRAMRST#

DDR CLK/ CONTROL/COMPENSATION

DDR CLK/ CONTROL/COMPENSATION

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

PEG_CLK

PEG_CLK#

CLK

CLK

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

CFG

CFG

PM

PM

NC

NC

DMI_TXN_2

DMI_TXN_3

DMI

DMI

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VID_4

GFX_VR_EN

GRAPHICS VID

GRAPHICS VID

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

MEHDA

MEHDA

CL_VREF

DDPC_CTRLCLK

DDPC_CTRLDATA

SDVO_CTRLCLK

SDVO_CTRLDATA

CLKREQ#

ICH_SYNC#

MISC

MISC

TSATN#

HDA_BCLK

HDA_RST#

HDA_SDI

HDA_SDO

HDA_SYNC

3

DDR_VREF_S3

499R2F-2-GP

499R2F-2-GP

GFX_VID[4..0] 38

0505 Modify RN71

CL_CLK0 18

CL_DATA0 18

PWROK 18,32

CL_RST#0 18

C270

C270

1D05V_S0

12

12

C487

C487

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

1D05V_S0

12

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

R324

R324

56R2J-4-GP

56R2J-4-GP

GMCH_GREEN15

GMCH_DDCCLK15

GMCH_DDCDATA15

GMCH_HSYNC15

GMCH_VSYNC15

R355

R355

1KR2F-3-GP

1KR2F-3-GP

1 2

12

R356

R356

511R2F-2-GP

511R2F-2-GP

FOR Cantiga:500 ohm

Teenah: 392 ohm

L_BKLTCTL14

GMCH_BL_ON30

CLK_DDC_EDID14

DAT_DDC_EDID14

GMCH_LCDVDD_ON14

GMCH_BLUE15

GMCH_RED15

2 3

1

SRN33J-5-GP-U

SRN33J-5-GP-U

-1

GMCH_LCDVDD_ON

GMCH_BL_ON

GFXVR_EN

LIBG

L_BKLTCTL

GMCH_BL_ON

LCTLA_CLK

TP119TPAD30 TP119TPAD30

LCTLB_DATA

TP118TPAD30 TP118TPAD30

CLK_DDC_EDID

DAT_DDC_EDID

GMCH_LCDVDD_ON

TP121TPAD30 TP121TPAD30

GMCH_TXACLK-14

GMCH_TXACLK+14

GMCH_TXBCLK-14

GMCH_TXBCLK+14

GMCH_TXAOUT0-14

GMCH_TXAOUT1-14

GMCH_TXAOUT2-14

GMCH_TXAOUT0+14

GMCH_TXAOUT1+14

GMCH_TXAOUT2+14

GMCH_TXBOUT0-14

GMCH_TXBOUT1-14

GMCH_TXBOUT2-14

GMCH_TXBOUT0+14

GMCH_TXBOUT1+14

GMCH_TXBOUT2+14

TVA_DAC

TVB_DAC

TVC_DAC

GMCH_BLUE

GMCH_GREEN

GMCH_RED

GMCH_DDCCLK

GMCH_DDCDATA

GMCH_HS

GMCH_VS

4

CRT_IREF

RN71

RN71

1 2

R347 1K02R2F-1-GPR347 1K02R2F-1-GP

FOR Cantiga: 1.02k_1% ohm

Teenah: 1.3k ohm

CRT_IREF routing Trace

width use 20 mil

RN63

RN63

1

2

3

4 5

SRN100KJ-8-GP-U

SRN100KJ-8-GP-U

R216

R216

1 2

2K37R2F-GP

2K37R2F-GP

LIBG

L_LVBG

2

3 OF 10

U35C

U35C

L32

L_BKLT_CTRL

G32

L_BKLT_EN

M32

L_CTRL_CLK

M33

L_CTRL_DATA

K33

L_DDC_CLK

J33

L_DDC_DATA

M29

L_VDD_EN

C44

LVDS_IBG

B43

LVDS_VBG

E37

LVDS_VREFH

E38

LVDS_VREFL

C41

LVDSA_CLK#

C40

LVDSA_CLK

B37

LVDSB_CLK#

A37

LVDSB_CLK

H47

LVDSA_DATA#_0

E46

LVDSA_DATA#_1

G40

LVDSA_DATA#_2

A40

LVDSA_DATA#_3

H48

LVDSA_DATA_0

D45

LVDSA_DATA_1

F40

LVDSA_DATA_2

B40

LVDSA_DATA_3

A41

LVDSB_DATA#_0

H38

LVDSB_DATA#_1

G37

LVDSB_DATA#_2

J37

LVDSB_DATA#_3

B42

LVDSB_DATA_0

G38

LVDSB_DATA_1

F37

LVDSB_DATA_2

K37

LVDSB_DATA_3

F25

TVA_DAC

H25

TVB_DAC

K25

TVC_DAC

H24

TV_RTN

C31

TV_DCONSEL_0

E32

TV_DCONSEL_1

E28

CRT_BLUE

G28

CRT_GREEN

J28

CRT_RED

G29

CRT_IRTN

H32

CRT_DDC_CLK

J32

CRT_DDC_DATA

J29

CRT_HSYNC

E29

CRT_TVO_IREF

L29

CRT_VSYNC

CANTIGA-GM-GP-U-NF

CANTIGA-GM-GP-U-NF

71.CNTIG.00U

71.CNTIG.00U

LVDS

LVDS

TV VGA

TV VGA

3 OF 10

PEG_CMP

T37

PEG_COMPI

T36

PEG_COMPO

H44

PEG_RX#_0

J46

PEG_RX#_1

L44

PEG_RX#_2

L40

PEG_RX#_3

N41

PEG_RX#_4

P48

PEG_RX#_5

N44

PEG_RX#_6

T43

PEG_RX#_7

U43

PEG_RX#_8

Y43

PEG_RX#_9

Y48

PEG_RX#_10

Y36

PEG_RX#_11

AA43

PEG_RX#_12

AD37

PEG_RX#_13

AC47

PEG_RX#_14

AD39

PEG_RX#_15

H43

PEG_RX_0

J44

PEG_RX_1

L43

PEG_RX_2

L41

PEG_RX_3

N40

PEG_RX_4

P47

PEG_RX_5

N43

PEG_RX_6

T42

PEG_RX_7

U42

PEG_RX_8

Y42

PEG_RX_9

W47

PEG_RX_10

Y37

PEG_RX_11

AA42

PEG_RX_12

AD36

PEG_RX_13

AC48

PEG_RX_14

AD40

PEG_RX_15

J41

PEG_TX#_0

M46

PEG_TX#_1

M47

PEG_TX#_2

M40

PEG_TX#_3

M42

PEG_TX#_4

R48

PEG_TX#_5

N38

PEG_TX#_6

T40

PEG_TX#_7

U37

PEG_TX#_8

U40

PEG_TX#_9

Y40

PEG_TX#_10

AA46

PEG_TX#_11

AA37

PEG_TX#_12

PCI-EXPRESS GRAPHICS

PCI-EXPRESS GRAPHICS

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

PEG_TX_10

PEG_TX_11

PEG_TX_12

PEG_TX_13

PEG_TX_14

PEG_TX_15

AA40

AD43

AC46

J42

L46

M48

M39

M43

R47

N37

T39

U36

U39

Y39

Y46

AA36

AA39

AD42

AD46

-1

RN72

RN72

1

2

3

4 5

SRN150F-1-GP

SRN150F-1-GP

8

7

6

GMCH_RED

GMCH_BLUE

GMCH_GREEN

0505 modidy nets(GMCH_RED,GMCH_BLUE,GMCH_GREEN,GND)

RN62

TVA_DAC

TVB_DAC

TVC_DAC

8

7

6

LCTLB_DATA

LCTLA_CLK

CLK_MCH_OE#

RN62

1

2

3

4 5

SRN75J-1-GP

SRN75J-1-GP

RN33

RN33

6

7

8

SRN10KJ-6-GP

SRN10KJ-6-GP

8

7

6

45

3

2

1

3D3V_S0

1

1D05V_S0

R214

R214

12

49D9R2F-GP

49D9R2F-GP

Close to GMCH as 500 mils.

Pin Name Strap Description Configuration

A A

CFG20

Digital DisplayPort

(SDVO/DP/HDMI)

Concurrent with

PCIE

5

Low = Only digital DisplayPort

(SDVO/DP/HDMI) or

PCIE is operational (default)

High = Digital DisplayPort

(SDVO/DP/HDMI) and

PCIE are operating simultaneously via the PEG port

4

http://hobi-elektronika.net

3

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

Cantiga (2 of 6)

Cantiga (2 of 6)

Cantiga (2 of 6)

Cathedral Peak

Cathedral Peak

Cathedral Peak

1

-1

-1

-1

of

742Friday, May 16, 2008

of

742Friday, May 16, 2008

of

742Friday, May 16, 2008

5

U35D

M_A_DQ[63..0]12

D D

C C

B B

M_A_DQ[63..0]

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

U35D

AJ38

SA_DQ_0

AJ41

SA_DQ_1

AN38

SA_DQ_2

AM38

SA_DQ_3

AJ36

SA_DQ_4

AJ40

SA_DQ_5

AM44

SA_DQ_6

AM42

SA_DQ_7

AN43

SA_DQ_8

AN44

SA_DQ_9

AU40

SA_DQ_10

AT38

SA_DQ_11

AN41

SA_DQ_12

AN39

SA_DQ_13

AU44

SA_DQ_14

AU42

SA_DQ_15

AV39

SA_DQ_16

AY44

SA_DQ_17

BA40

SA_DQ_18

BD43

SA_DQ_19

AV41

SA_DQ_20

AY43

SA_DQ_21

BB41

SA_DQ_22

BC40

SA_DQ_23

AY37

SA_DQ_24

BD38

SA_DQ_25

AV37

SA_DQ_26

AT36

SA_DQ_27

AY38

SA_DQ_28

BB38

SA_DQ_29

AV36

SA_DQ_30

AW36

SA_DQ_31

BD13

SA_DQ_32

AU11

SA_DQ_33

BC11

SA_DQ_34

BA12

SA_DQ_35

AU13

SA_DQ_36

AV13

SA_DQ_37

BD12

SA_DQ_38

BC12

SA_DQ_39

BB9

SA_DQ_40

BA9

SA_DQ_41

AU10

SA_DQ_42

AV9

SA_DQ_43

BA11

SA_DQ_44

BD9

SA_DQ_45

AY8

SA_DQ_46

BA6

SA_DQ_47

AV5

SA_DQ_48

AV7

SA_DQ_49

AT9

SA_DQ_50

AN8

SA_DQ_51

AU5

SA_DQ_52

AU6

SA_DQ_53

AT5

SA_DQ_54

AN10

SA_DQ_55

AM11

SA_DQ_56

AM5

SA_DQ_57

AJ9

SA_DQ_58

AJ8

SA_DQ_59

AN12

SA_DQ_60

AM13

SA_DQ_61

AJ11

SA_DQ_62

AJ12

SA_DQ_63

CANTIGA-GM-GP-U-NF

CANTIGA-GM-GP-U-NF

71.CNTIG.00U

71.CNTIG.00U

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

4 OF 10

4 OF 10

SA_BS_0

SA_BS_1

SA_BS_2

SA_RAS#

SA_CAS#

SA_WE#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

4

BD21

BG18

AT25

BB20

BD20

AY20

AM37

AT41

AY41

AU39

BB12

AY6

AT7

AJ5

AJ44

AT44

BA43

BC37

AW12

BC8

AU8

AM7

AJ43

AT43

BA44

BD37

AY12

BD8

AU9

AM8

BA21

BC24

BG24

BH24

BG25

BA24

BD24

BG27

BF25

AW24

BC21

BG26

BH26

BH17

AY25

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_DM[7..0]

M_A_DQS[7..0]

M_A_DQS#[7..0]

M_A_A[14..0]

M_A_BS#0 12

M_A_BS#1 12

M_A_BS#2 12

M_A_RAS# 12

M_A_CAS# 12

M_A_WE# 12

M_A_DM[7..0] 12

M_A_DQS[7..0] 12

M_A_DQS#[7..0] 12

M_A_A[14..0] 12

3

U35E

M_B_DQ[63..0]13

M_B_DQ[63..0]

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

U35E

AK47

SB_DQ_0

AH46

SB_DQ_1

AP47

SB_DQ_2

AP46

SB_DQ_3

AJ46

SB_DQ_4

AJ48

SB_DQ_5

AM48

SB_DQ_6

AP48

SB_DQ_7

AU47

SB_DQ_8

AU46

SB_DQ_9

BA48

SB_DQ_10

AY48

SB_DQ_11

AT47

SB_DQ_12

AR47

SB_DQ_13

BA47

SB_DQ_14

BC47

SB_DQ_15

BC46

SB_DQ_16

BC44

SB_DQ_17

BG43

SB_DQ_18

BF43

SB_DQ_19

BE45

SB_DQ_20

BC41

SB_DQ_21

BF40

SB_DQ_22

BF41

SB_DQ_23

BG38

SB_DQ_24

BF38

SB_DQ_25

BH35

SB_DQ_26

BG35

SB_DQ_27

BH40

SB_DQ_28

BG39

SB_DQ_29

BG34

SB_DQ_30

BH34

SB_DQ_31

BH14

SB_DQ_32

BG12

SB_DQ_33

BH11

SB_DQ_34

BG8

SB_DQ_35

BH12

SB_DQ_36

BF11