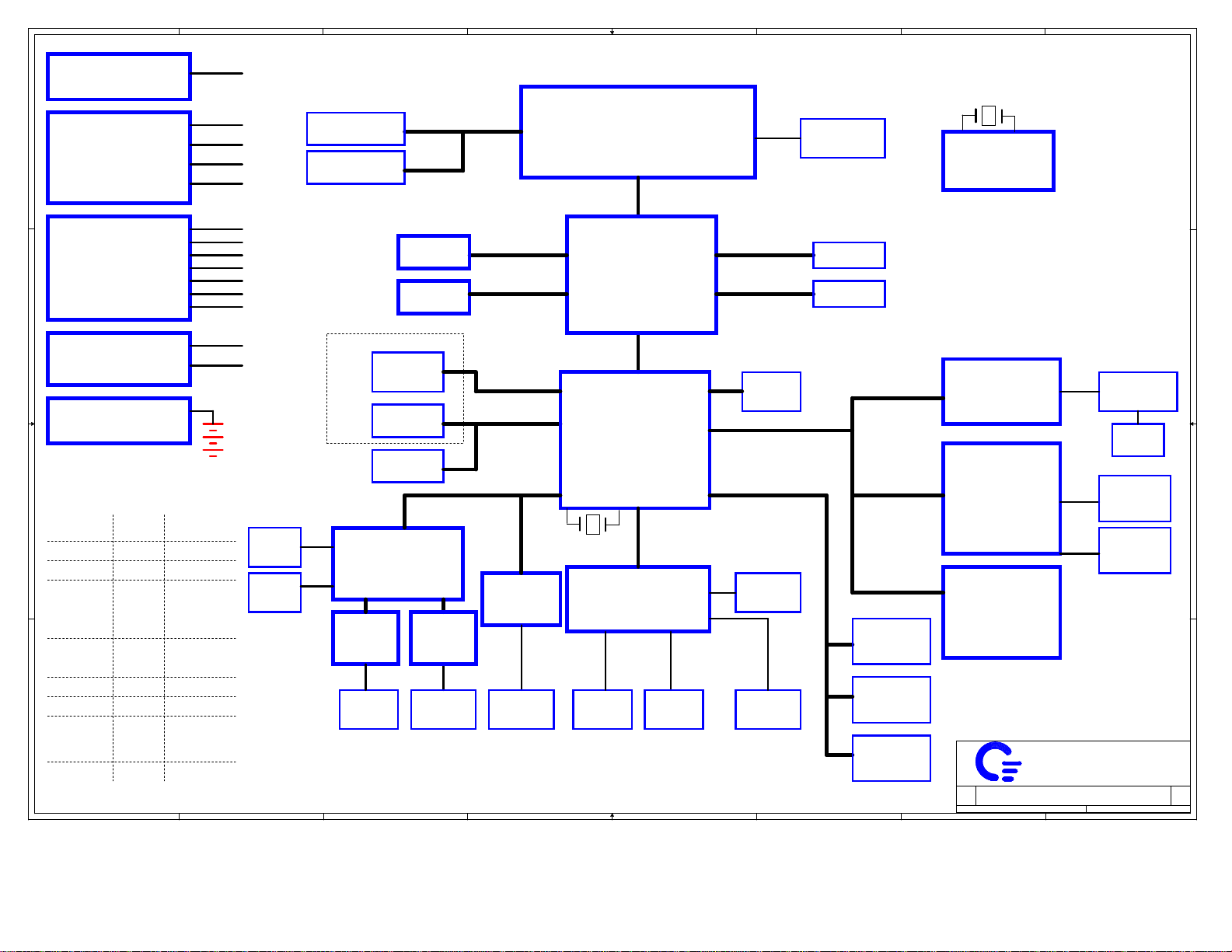

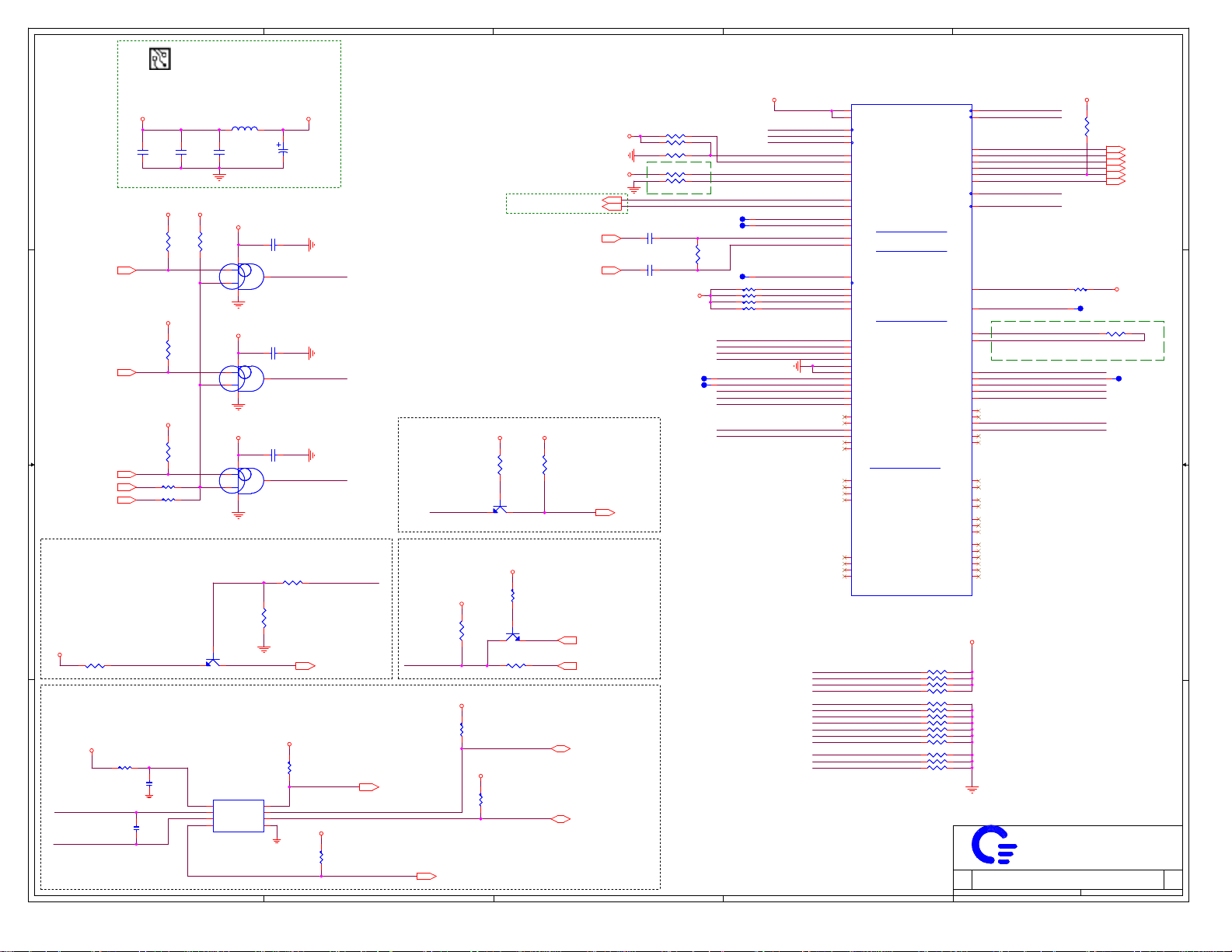

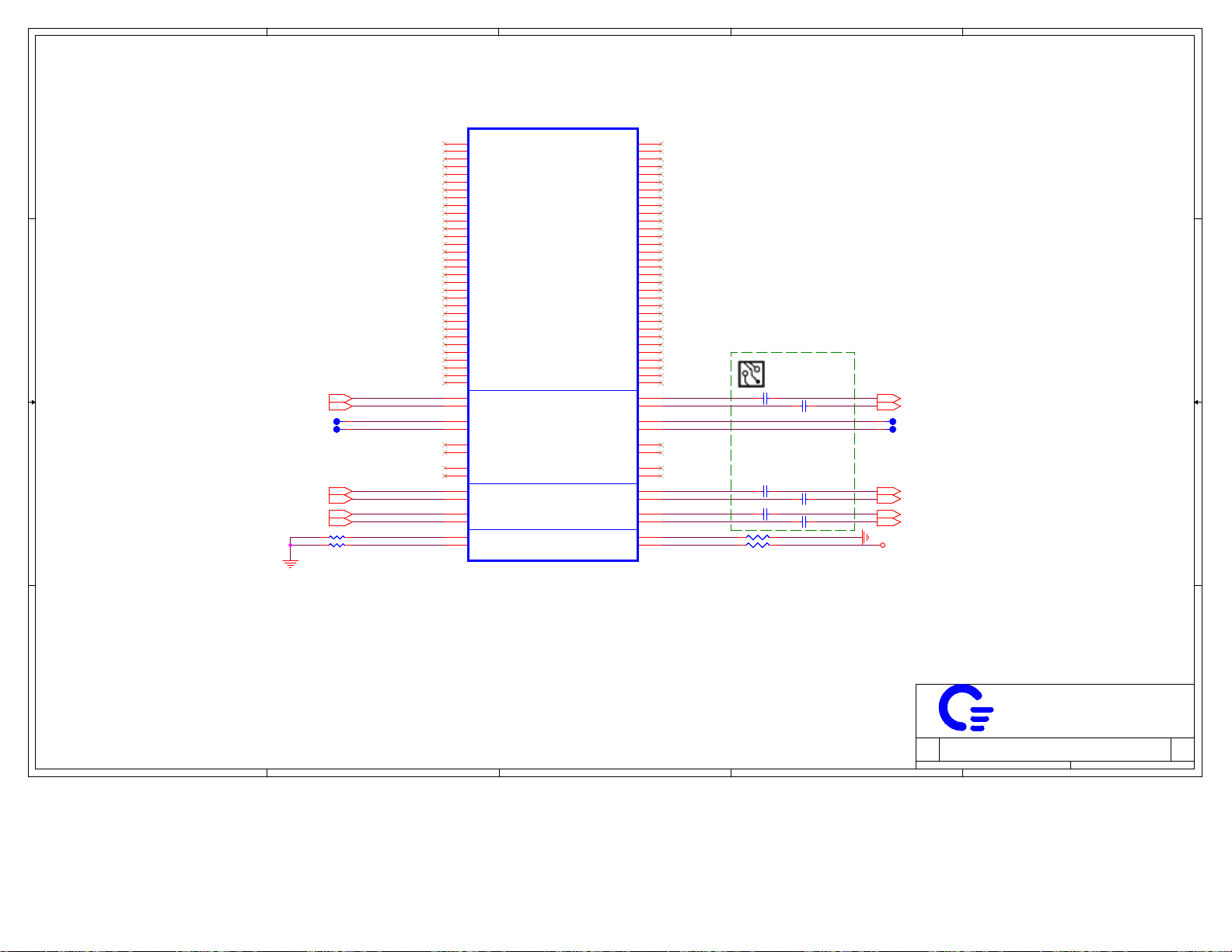

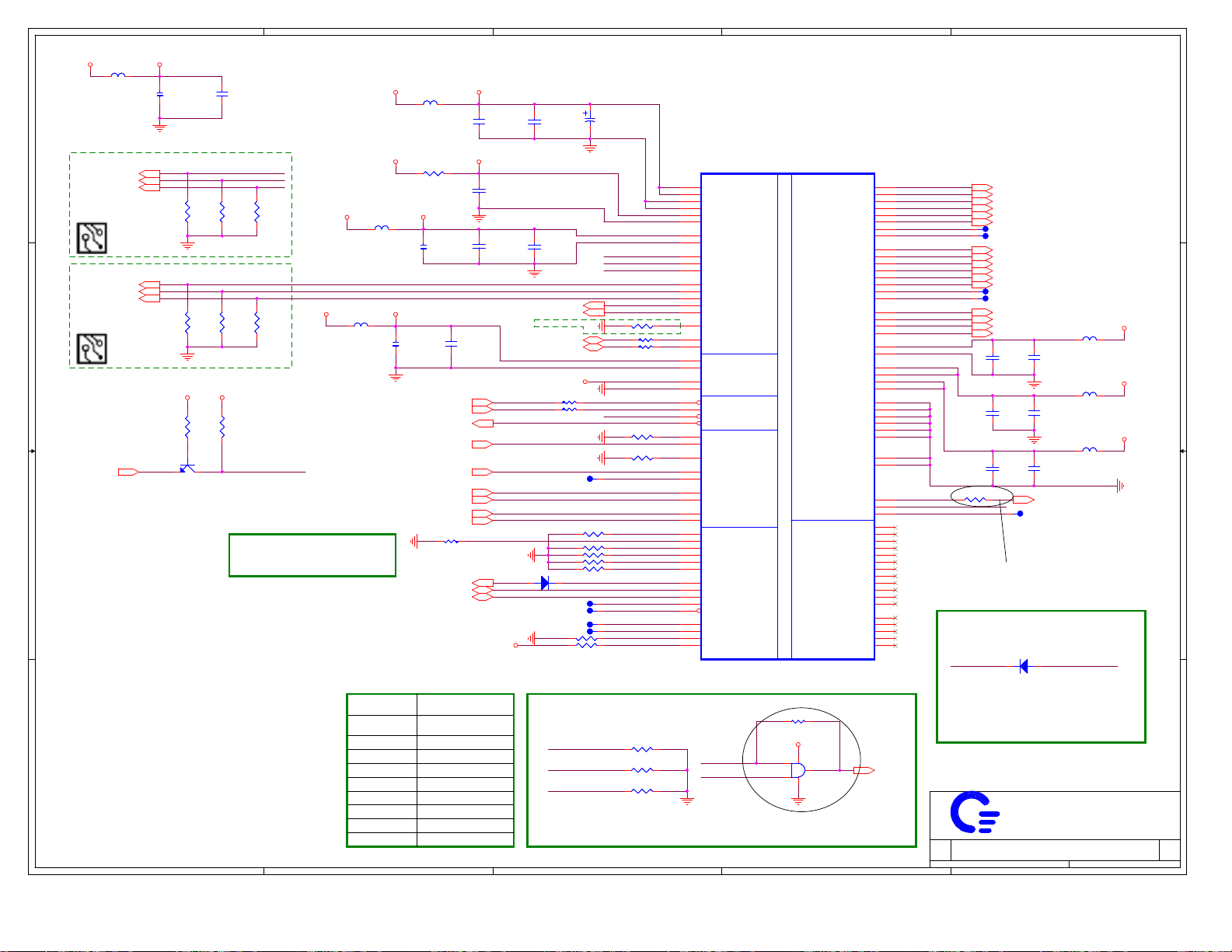

Acer Aspire 3050, Aspire 5050, Aspire 5070 Schematics

1

2

3

4

5

6

7

8

Page:29

VCC_CORE

+1.2V

+1.8VSUS

+1.8V

+0.9V_VTER

+3VPCU

+3V_S5

+3VSUS

+3V

+5VPCU

+5VSUS

+5V

+1.5V

+2.5V

BATTERY

DDR-II SODIMM1

DDR-II SODIMM2

Page: 7

Page: 7

Manufacturing Option

SATA HDD

PATA HDD

IDE-ODD

DDR-II 533/667MHz

S-Video

Page: 21

mini CARD

Page: 20

Page: 22

Page: 22

Page: 22

Turion 64 Rev.F Dual-Core/

Sempron Rev.F Single-Core

TV-OUT

PCIE

SATA

ATA 66/100

CPU CORE

MAXIM

MAX8774

AA

+1.2V

Page:28

+1.8VSUS/+1.8V

+0.9V_VTER

TI

TPS51116/51117

+3VPCU/+5VPCU

+3V_S5

+3V/+5V

+3VSUS/+5VSUS

TI

TPS51120

BB

Page:30

+1.5V/+2.5V

GMT

G966/913-C

BATTERY CHARGER

MAXIM

ISL6251

Page:31

Page:27

Azalia

Power State Table

Power

CC

Name

+VCC_CORE

+2.5V

+3VPCU

+3VS5

+3VSUS

+3V

+5VPCU

+5VSUS

+5V

+1.2V

+0.9V_VTER

DD

+1.8VS5

+1.8VSUS

+1.8V

+1.5V

Control

Signal

VRON

MAINON

N/A

S5_ON

SUSD

MAIND

N/A

SUSD

MAIND

MAINON

MAINON

S5_ON

SUSON

MAIND

MAINON

1

Power

State

S0

S0

ALWAYS

S0-S5

S0-S3

S0

ALWAYS

S0-S3

S0

S0

S0

S0-S5

S0-S3

S0

S0

MIC-IN

Page: 24

LINE-IN

Page: 24

2

AUDIO CODEC

REALTEK- ALC883

48-pins Package

Page: 23

Audio AMP

Audio AMP

MAX4411

Page: 23

LINEOUT

Page: 24

SPEAKER

3

MAX9710

Page: 24

Page: 24

MODEM

FOXCONNMDC

Page: 23

RJ11

(External)

4

ZR3

AMD S1

Dual-Core 35W / Single-Core 25W

(638 S1g1 socket)

NB

ATi RS485

465-Pins FCBGA Package

Page: 8, 9 ,10, 11

SB

ATi SB460

549-Pins BGA Package

Page: 13, 14, 15, 16

X'TAL

32.768KHz

KBC

NS PC97541V

176-Pins Package

Touchpad

Page: 26

Page:3, 4, 5, 6

HT_LINK

2X PCIE

LPC 33MHZ

Page: 25

Keyboard

Page: 26

5

RGB

LVDS

RTC

Page: 14

PCI BUS 33MHZ

USB 2.0

BIOS

SST39VF080

Page: 25

FAN

Page: 26

CPU THERMAL

SENSOR

Page:5

CRT

Page: 21

LVDS

Page: 21

6

Bluetooth

USB

interface

Page:20

USB6

SYSTEM

USB PORT*3

Page: 20

USB0,1,4

USB CAMERA

Page: 20

USB2

X'TAL

14.31818MHz

Clock generator

ICS951462

Page:12

REALTEK 8100SBL/CL

10/100 LAN

AD18

REQ0# / GNT0#

INTE#

Page: 17

ENE CB714/1410

TRANSFORMER

Page: 17

RJ45

Page: 17

Cardbus controller

AD17

REQ3# / GNT3#

INTH#,INTG#

Page: 18

PCMCIA

SLOT

Page: 19

CARD

READER

Page: 19

MINI-PCI

Wireless LAN

AD20

REQ2# / GNT2#

INTG#,

INTE#

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Date:Sheet

Date:Sheet

Date:Sheet of

Page: 20

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

7

PROJECT : ZR3

PROJECT : ZR3

Quanta Computer Inc.

Quanta Computer Inc.

131Wednesday, October 18, 2006

131Wednesday, October 18, 2006

131Wednesday, October 18, 2006

of

of

8

1A

1A

1A

5

4

3

2

1

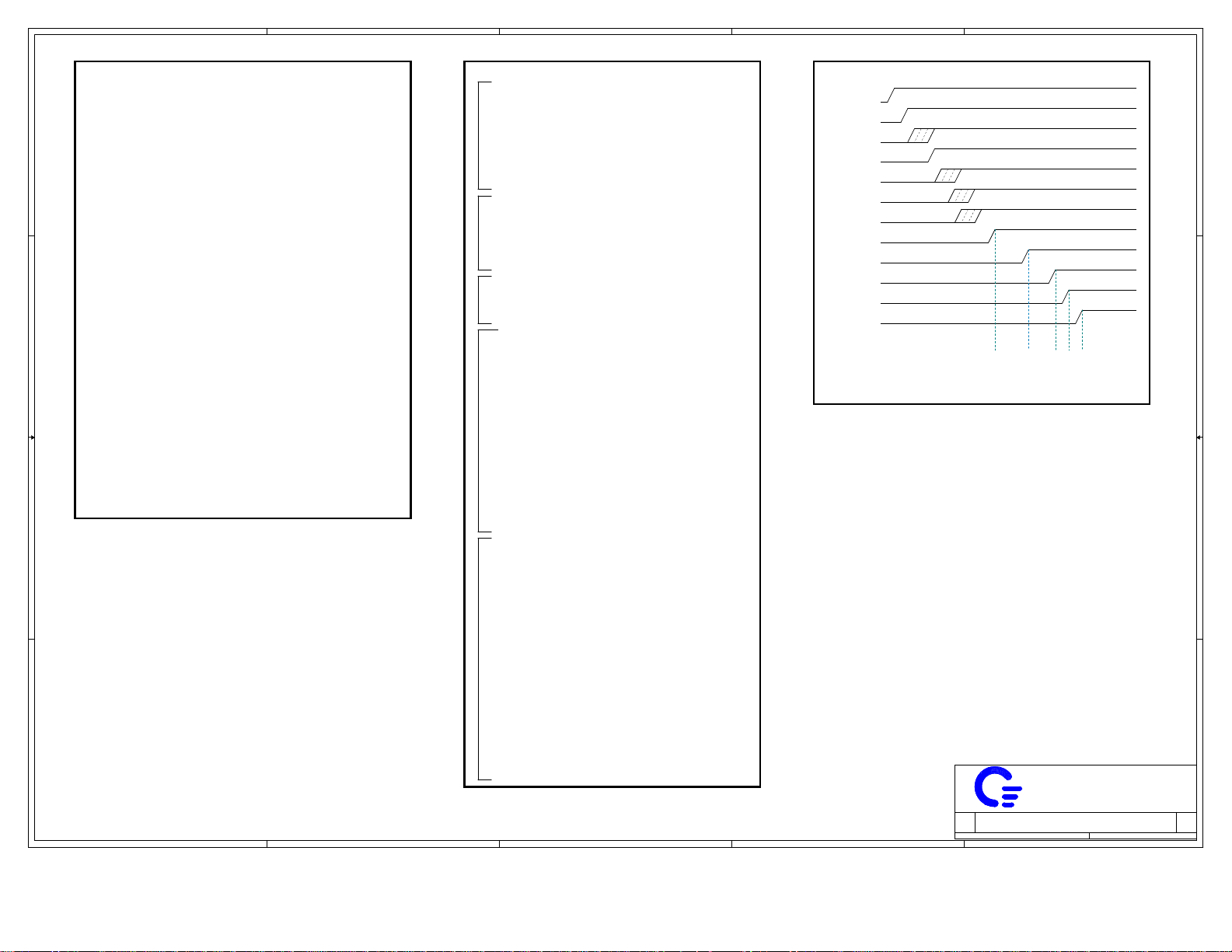

TABLE OF CONTENTS

Page 01 : BLOCK DIAGRAM

Page 02 : TABLE OF CONTENTS

DD

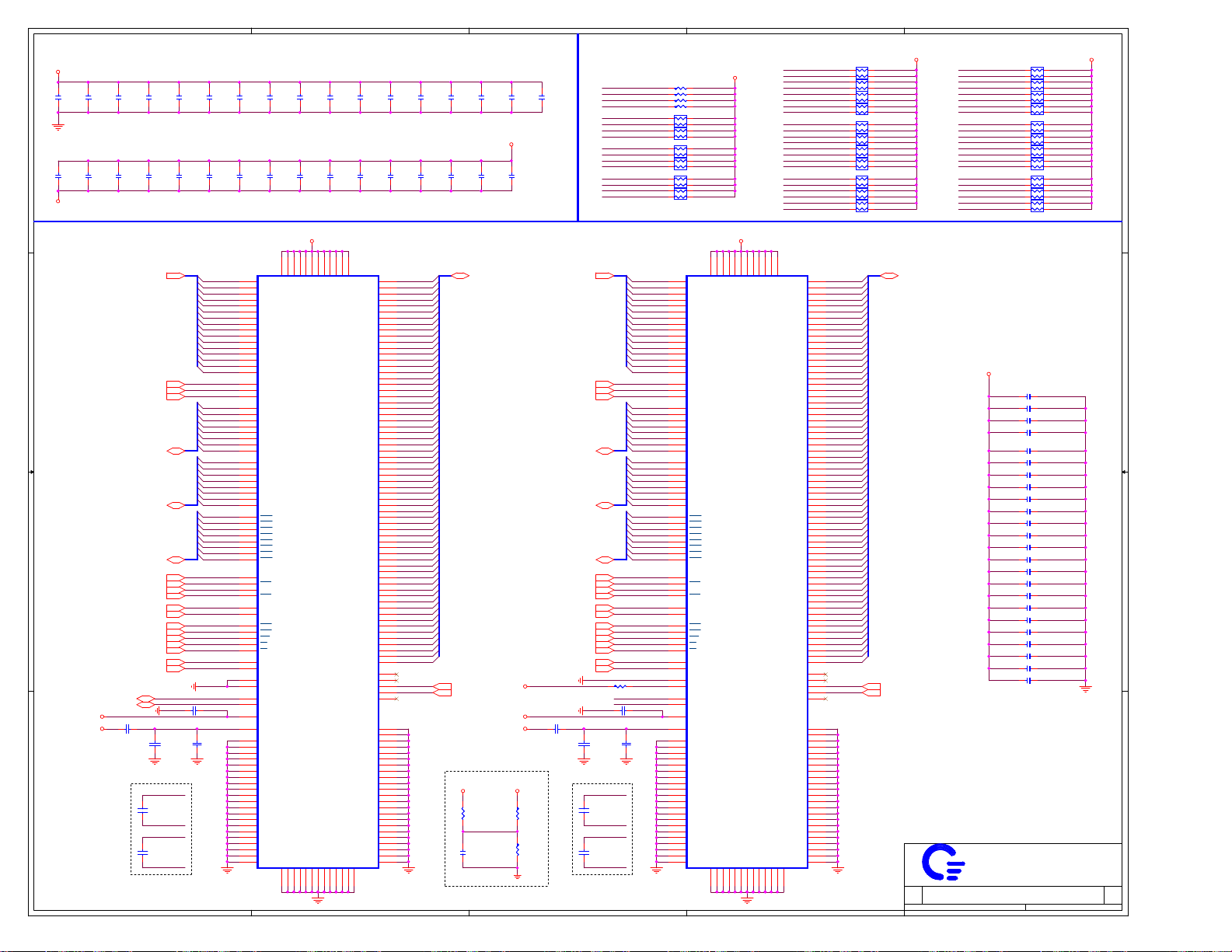

Page 03 : ATHLON64 HT I/F

Page 04 : ATHLON64 DDRII MEMORY I/F

Page 05 : ATHLON64 CTRL & DEBUG

Page 06 : ATHLON64 PWR & GND

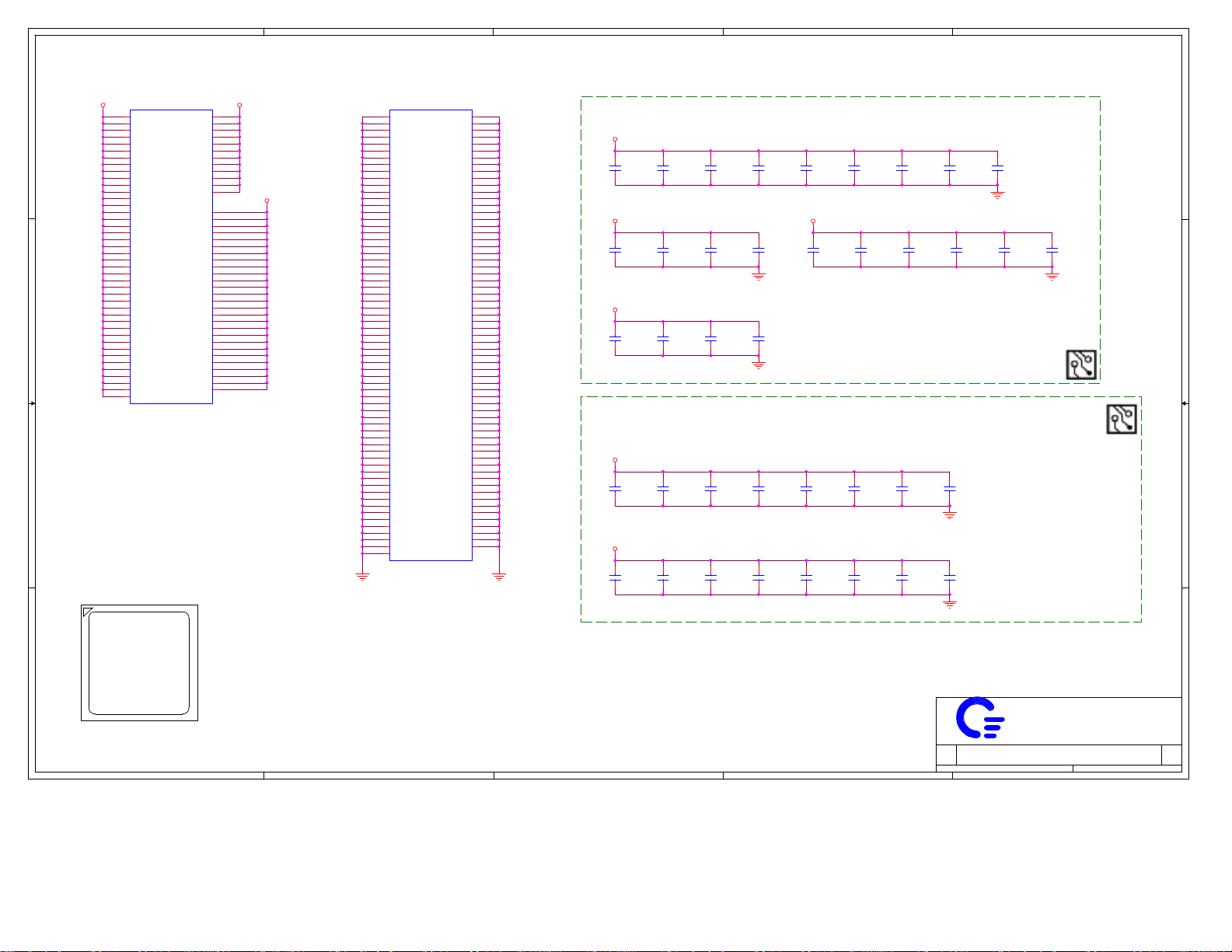

Page 07 : DDRII SODIMMX2

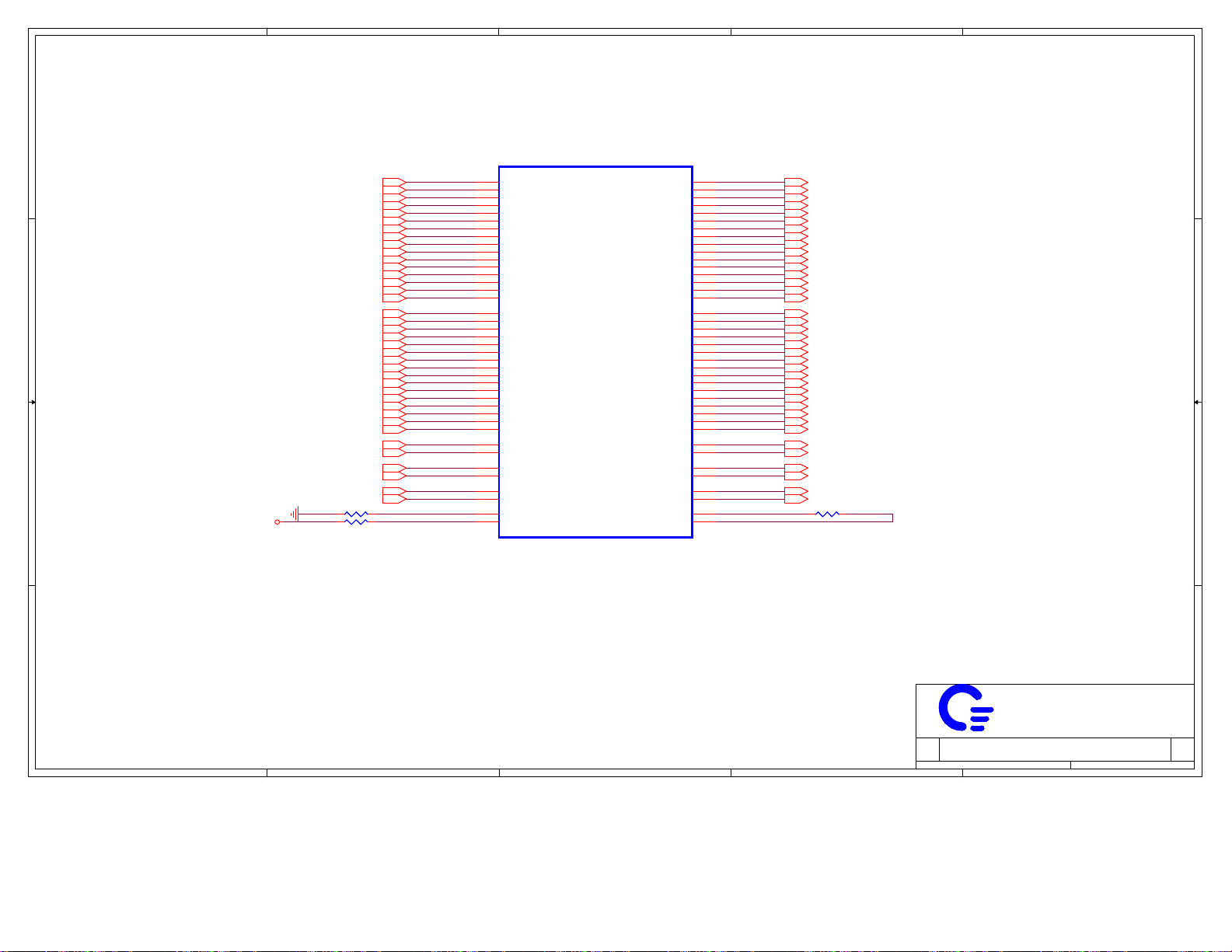

Page 08 : RS485-HT LINK0 I/F

Page 09 : RS485-PCIE LINK I/F

Page 10 : RS485-SYSTEM I/F & DVO

Page 11 : RS485-POWER

Page 12 : External CLOCK GENERATOR

Page 13 : SB460M PCIE/PCI/CPU/LPC I/F

Page 14 : SB460M ACPI/GPIO/USB/AC97

Page 15 : SB460M HDD/POWER/DECOUPLING

Page 16 : SB460M STRAPS

Page 17 : LAN RTL8110SBL/CL

CC

Page 18 : ENE CB714/1410

Page 19 : CARD READ & CARDBUS SLOT

Page 20 : MINI PCI & PCI-E,USB PORT,BLUETOOTH

Page 21 : CRT & LVDS & S-Video

Page 22 : HDD & CDROM & HOLES

Page 23 : ALC883 & MDC & HP AMP

Page 24 : SPEAKER AMP / JACK

Page 25 : 97551 & FLASH

Page 26 : T/P,FAN,SWITCH,LED,K/B

Page 27 : BATTERY CHARGER

Page 28 : VCORE MAX8774

Page 29 : TPS51116/51117 1.8V/1.2V

Page 30 : TPS51120 3/5V

Page 31 : +1.5V / 2.5V

BB

AA

5

4

POWERVOLTAGEACTIVE SCOPE

+12V

+5V

+3V

+5VPCU

+3VPCU

+5VSUS

SYSTEMRC485 NBSB460 SB

+3VSUS

+3V_S5

VCCCORE

VDDA_RUN

VLDT_RUN

CPU

+0.9V_VTER

+1.8V

+1.8VSUS

+1.8V

+1.8VSUS

DDR2

+0.9V_VTER

+1.8V

+1.8VSUS

+3V

VDDC

VDD_HT

VDDA12

VDD18

VDDA18

VDD_DVO

VDDR3

AVDD_NB

AVDDQ

PLLVDD

LPVDD

LPVDD18A

+3V

+1.8V

+3V_S5

+1.8V_S5

VDD

AVDD_CK

AVDD_SATA

XTLVDD_ATA

PLLVDD_ATA

PCIE_PVDD

PCIE_VDDR

CPU-PWR

VDDQ

V5_VREF

+1.8V_SUB_PHY

+3VSUS

+SB_S5_3V

+SB_S5_1.8V

+12V

+5V

+3.3V

+5V

+3.3V

+5V

+3.3V

+3.3VS0

VID[0..5]

+2.5V

+1.2VS0

+0.9V

+1.8VS0

+1.8VS0-S3

+1.8VS0

+1.8VS0-S3

+0.9VS0

+1.8VS0

+1.8VS0-S3

+3.3V

+1.2V

+1.2V

+1.2V

+1.8VS0

+1.8V

+1.8V

+3.3V

+3.3VS0

+1.8VS0

+1.8VS0

+1.8VS0

+1.8VS0

+3.3VS0

+1.8VS0

+3.3VS0

+1.8VS0

+1.8V

+1.8VS0

+1.8V

+1.8V

+1.8V

+1.8V

+1.8V

+1.2V

+3.3VS0

+5V

+1.8V

+3.3VS0-S3

+3.3VS0

+1.8VS0

S0

S0

S0

ALWAYS

ALWAYS

S0-S3

S0-S3

S0

S0

S0

S0

S0

S0

S0

S0

S0

S0

S0

S0

S0

S0

S0

S0

S0

S0

S0

3

PAGE

+5VPCU

RSMRST#

SUSB#, SUSC#

+12V,5V,3.3V

HWPG_1.2V

HWPG_1.8V

CPU_COREPG

NB_PWRGD

EC_PWRGD

CPU_PWRGD

PCI_RST#

CPU_RST#

2

POWER UP SEQUENCE

T2

T3T1

T1>= 70 ms

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Date:Sheet of

Date:Sheet of

Date:Sheet of

1ms < T2 < 10ms

1ms < T3 < 5ms

PROJECT : ZR3

PROJECT : ZR3

Quanta Computer Inc.

Quanta Computer Inc.

TABLE OF CONTENTS

TABLE OF CONTENTS

TABLE OF CONTENTS

231Wednesday, October 18, 2006

231Wednesday, October 18, 2006

231Wednesday, October 18, 2006

1

1A

1A

1A

5

4

3

2

1

DD

HT_CADIN15_P(8)

HT_CADIN15_N(8)

HT_CADIN14_P(8)

HT_CADIN14_N(8)

HT_CADIN13_P(8)

CC

BB

VLDT_RUN

HT_CADIN13_N(8)

HT_CADIN12_P(8)

HT_CADIN12_N(8)

HT_CADIN11_P(8)

HT_CADIN11_N(8)

HT_CADIN10_P(8)

HT_CADIN10_N(8)

HT_CADIN9_P(8)

HT_CADIN9_N(8)

HT_CADIN8_P(8)

HT_CADIN8_N(8)

HT_CADIN7_P(8)

HT_CADIN7_N(8)

HT_CADIN6_P(8)

HT_CADIN6_N(8)

HT_CADIN5_P(8)

HT_CADIN5_N(8)

HT_CADIN4_P(8)

HT_CADIN4_N(8)

HT_CADIN3_P(8)

HT_CADIN3_N(8)

HT_CADIN2_P(8)

HT_CADIN2_N(8)

HT_CADIN1_P(8)

HT_CADIN1_N(8)

HT_CADIN0_P(8)

HT_CADIN0_N(8)

HT_CLKIN1_P(8)

HT_CLKIN1_N(8)

HT_CLKIN0_P(8)

HT_CLKIN0_N(8)

R2249.9/F_4R2249.9/F_4

49.9/F_4

49.9/F_4

R23

R23

HT_CTLIN0_P(8)

HT_CTLIN0_N(8)

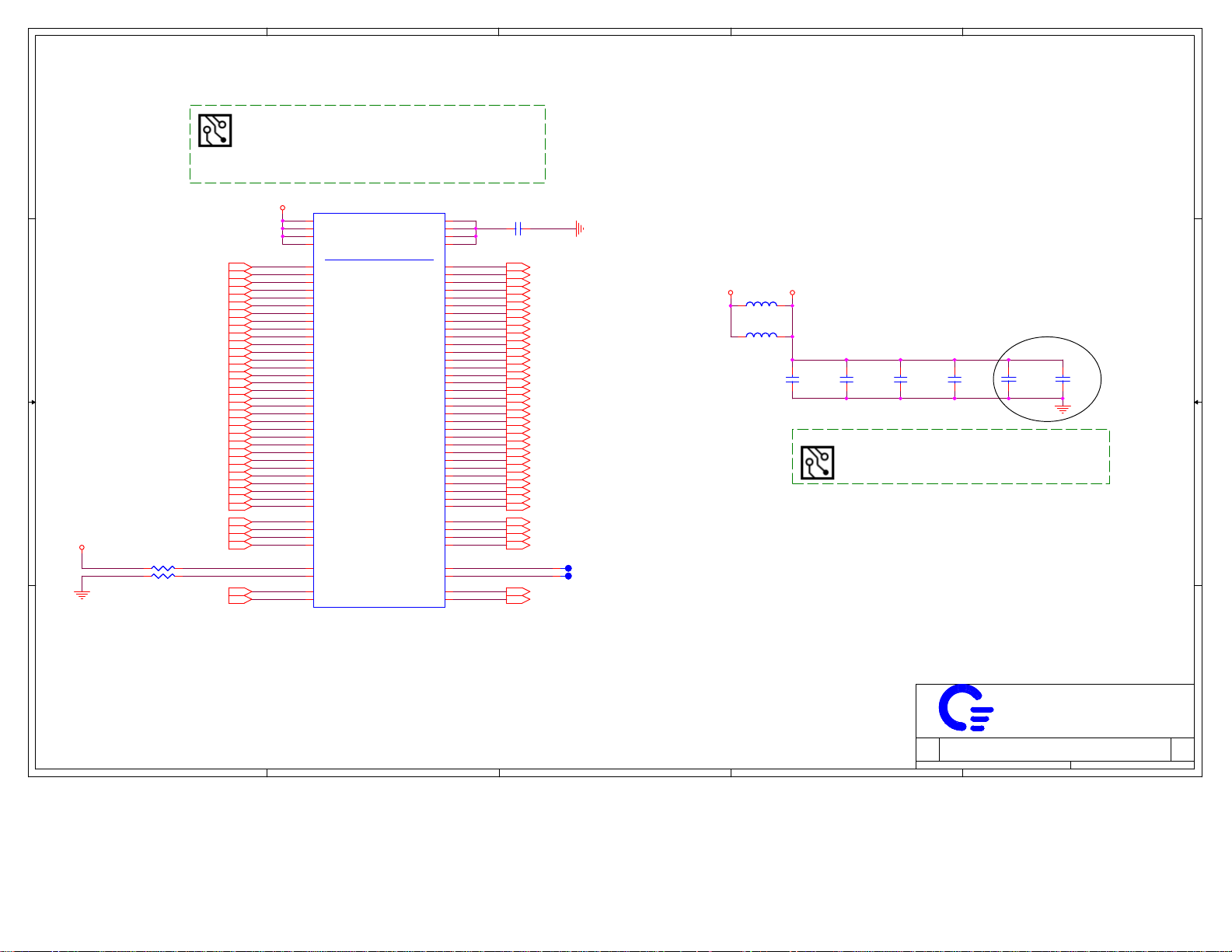

PROCESSOR HYPERTRANSPORT INTERFACE

VLDT_Ax AND VLDT_Bx ARE CONNECTED TO THE LDT_RUN POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

VLDT_RUN

U16AU16A

D4

VLDT_A3

D3

VLDT_A2

D2

VLDT_A1

D1

VLDT_A0

N5

L0_CADIN_H15

P5

L0_CADIN_L15

M3

L0_CADIN_H14

M4

L0_CADIN_L14

L5

L0_CADIN_H13

M5

L0_CADIN_L13

K3

L0_CADIN_H12

K4

L0_CADIN_L12

H3

L0_CADIN_H11

H4

L0_CADIN_L11

G5

L0_CADIN_H10

H5

L0_CADIN_L10

F3

L0_CADIN_H9

F4

L0_CADIN_L9

E5

L0_CADIN_H8

F5

L0_CADIN_L8

N3

L0_CADIN_H7

N2

L0_CADIN_L7

L1

L0_CADIN_H6

M1

L0_CADIN_L6

L3

L0_CADIN_H5

L2

L0_CADIN_L5

J1

L0_CADIN_H4

K1

L0_CADIN_L4

G1

L0_CADIN_H3

H1

L0_CADIN_L3

G3

L0_CADIN_H2

G2

L0_CADIN_L2

E1

L0_CADIN_H1

F1

L0_CADIN_L1

E3

L0_CADIN_H0

E2

L0_CADIN_L0

J5

L0_CLKIN_H1

K5

L0_CLKIN_L1

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

P3

L0_CTLIN_H1

P4

L0_CTLIN_L1

N1

L0_CTLIN_H0

P1

L0_CTLIN_L0

VLDT_B3

VLDT_B2

VLDT_B1

VLDT_B0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

Athlon 64 S1

Processor Socket

AE5

AE4

AE3

AE2

T4

T3

V5

U5

V4

V3

Y5

W5

AB5

AA5

AB4

AB3

AD5

AC5

AD4

AD3

T1

R1

U2

U3

V1

U1

W2

W3

AA2

AA3

AB1

AA1

AC2

AC3

AD1

AC1

Y4

Y3

Y1

W1

T5

R5

R2

R3

HT_CPU_CTLOUT1_PHT_CTLIN1_P

HT_CPU_CTLOUT1_NHT_CTLIN1_N

C214.7U/6.3V_6C214.7U/6.3V_6

HT_CADOUT15_P(8)

HT_CADOUT15_N(8)

HT_CADOUT14_P(8)

HT_CADOUT14_N(8)

HT_CADOUT13_P(8)

HT_CADOUT13_N(8)

HT_CADOUT12_P(8)

HT_CADOUT12_N(8)

HT_CADOUT11_P(8)

HT_CADOUT11_N(8)

HT_CADOUT10_P(8)

HT_CADOUT10_N(8)

HT_CADOUT9_P(8)

HT_CADOUT9_N(8)

HT_CADOUT8_P(8)

HT_CADOUT8_N(8)

HT_CADOUT7_P(8)

HT_CADOUT7_N(8)

HT_CADOUT6_P(8)

HT_CADOUT6_N(8)

HT_CADOUT5_P(8)

HT_CADOUT5_N(8)

HT_CADOUT4_P(8)

HT_CADOUT4_N(8)

HT_CADOUT3_P(8)

HT_CADOUT3_N(8)

HT_CADOUT2_P(8)

HT_CADOUT2_N(8)

HT_CADOUT1_P(8)

HT_CADOUT1_N(8)

HT_CADOUT0_P(8)

HT_CADOUT0_N(8)

HT_CLKOUT1_P(8)

HT_CLKOUT1_N(8)

HT_CLKOUT0_P(8)

HT_CLKOUT0_N(8)

T7T7

T11T11

HT_CTLOUT0_P(8)

HT_CTLOUT0_N(8)

+1.2V

FBJ3216HS800

FBJ3216HS800

FBJ3216HS800

FBJ3216HS800

VLDT_RUN

L45

L45

L47

L47

8/17 Change 180pF to placed on the VLDT power fill.

80 ohm(4A)

C128

C129

C123

C123

4.7U/6.3V_6

4.7U/6.3V_6

LAYOUT: Place bypass cap on topside of board

C116

C116

4.7U/6.3V_6

4.7U/6.3V_6

NEAR HT POWER PINS THAT ARE NOT CONNECTED DIRECTLY

TO DOWNSTREAM HT DEVICE, BUT CONNECTED INTERNALLY

TO OTHER HT POWER PINS

PLACE CLOSE TO VLDT0 POWER PINS

C129

.22U/6V_4

.22U/6V_4

C128

.22U/6V_4

.22U/6V_4

12

C135

C135

180P_4

180P_4

12

C134

C134

180P_4

180P_4

AA

5

4

3

2

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

ATHLON64 HT I/F

ATHLON64 HT I/F

ATHLON64 HT I/F

Date:Sheet

Date:Sheet

Date:Sheet of

PROJECT : ZR3

PROJECT : ZR3

Quanta Computer Inc.

Quanta Computer Inc.

331Wednesday, October 18, 2006

331Wednesday, October 18, 2006

331Wednesday, October 18, 2006

of

1

of

1A

1A

1A

A

B

C

D

E

C447

C447

1000p/50V_4

1000p/50V_4

U16B

U16B

MEMVREF

VTT_SENSE

MEMZN

MEMZP

MA0_CS_L3

MA0_CS_L2

MA0_CS_L1

MA0_CS_L0

MB0_CS_L3

MB0_CS_L2

MB0_CS_L1

MB0_CS_L0

MB_CKE1

MB_CKE0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_BANK2

MA_BANK1

MA_BANK0

MA_RAS_L

MA_CAS_L

MA_WE_L

C136

C136

.22U/6V_4

.22U/6V_4

C9

180P_4C9180P_4

+1.8VSUS

R268

R268

1K/F_4

1K/F_4

R269

R269

1K/F_4

1K/F_4

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

MA0_CLK_H2

MA0_CLK_L2

MA0_CLK_H1

MA0_CLK_L1

MB0_CLK_H2

MB0_CLK_L2

MB0_CLK_H1

MB0_CLK_L1

MB0_ODT1

MB0_ODT0

MA0_ODT1

MA0_ODT0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_BANK2

MB_BANK1

MB_BANK0

MB_RAS_L

MB_CAS_L

MB_WE_L

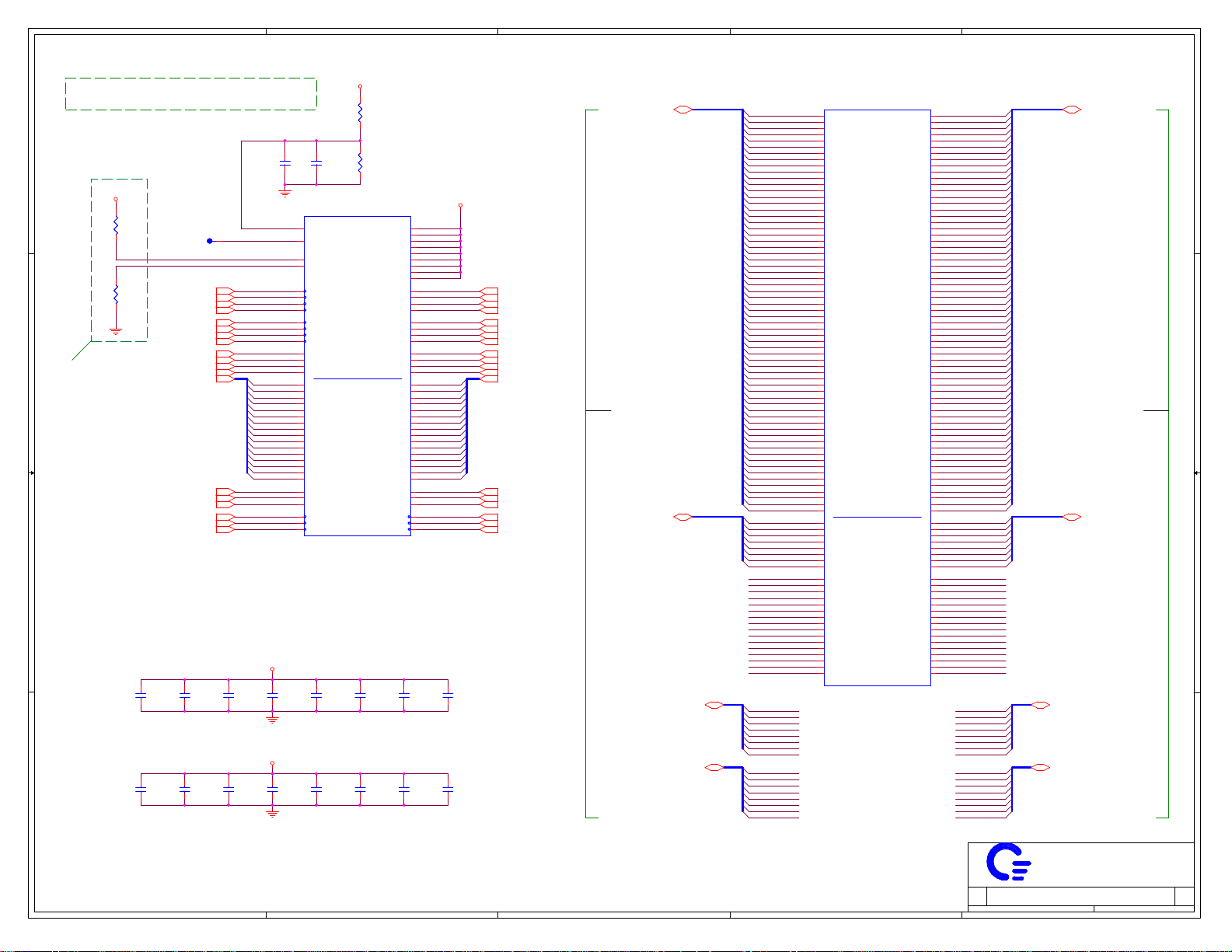

DDR II: CMD/CTRL/CLK

DDR II: CMD/CTRL/CLK

Athlon 64 S1

Processor Socket

C18

C18

.22U/6V_4

.22U/6V_4

C146

C146

180P_4

180P_4

D10

C10

B10

AD10

W10

AC10

AB10

AA10

A10

Y16

AA16

E16

F16

AF18

AF17

A17

A18

W23

W26

V20

U19

J25

J26

W25

L23

L25

U25

L24

M26

L26

N23

N24

N25

N26

P24

P26

T24

K26

T26

U26

U24

V26

U22

C16

C16

.22U/6V_4

.22U/6V_4

C12

C12

180P_4

180P_4

M_B_A15

M_B_A14

M_B_A13

M_B_A12

M_B_A11

M_B_A10

M_B_A9

M_B_A8

M_B_A7

M_B_A6

M_B_A5

M_B_A4

M_B_A3

M_B_A2

M_B_A1

M_B_A0

+0.9V_VTER

C143

C143

.22U/6V_4

.22U/6V_4

C42

C42

180P_4

180P_4

M_CLKOUT1(7)

M_CLKOUT1#(7)

M_CLKOUT0(7)

M_CLKOUT0#(7)

M_CLKOUT4(7)

M_CLKOUT4#(7)

M_CLKOUT3(7)

M_CLKOUT3#(7)

M_ODT3(7)

M_ODT2(7)

M_ODT1(7)

M_ODT0(7)

M_B_A[0..15](7)

M_B_BS#2(7)

M_B_BS#1(7)

M_B_BS#0(7)

M_B_RAS#(7)

M_B_CAS#(7)

M_B_WE#(7)

M_B_DQ[0..63](7)

M_B_DQ[0..63]

To SODIMM socket B (Far)

M_B_DM[0..7](7)

M_B_DM[0..7]

M_B_DQS[0..7](7)

M_B_DQS#[0..7](7)

VDD_VTT_SUS_CPU IS CONNECTED TO THE VDD_VTT_SUS POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

44

+1.8VSUS

12

R274

R274

39.2F_4

39.2F_4

12

R273

R273

39.2F_4

39.2F_4

PLACE THEM CLOSE TO

33

CPU WITHIN 1"

22

11

C5

4.7U/6.3V_6C54.7U/6.3V_6

C13

C13

1000p/50V_4

1000p/50V_4

T3T3

M_A_CS#3(7)

M_A_CS#2(7)

M_A_CS#1(7)

M_A_CS#0(7)

M_B_CS#3(7)

M_B_CS#2(7)

M_B_CS#1(7)

M_B_CS#0(7)

M_CKE3(7)

M_CKE2(7)

M_CKE1(7)

M_CKE0(7)

M_A_A[0..15](7)

M_A_BS#2(7)

M_A_BS#1(7)

M_A_BS#0(7)

M_A_RAS#(7)

M_A_CAS#(7)

M_A_WE#(7)

C151

C151

4.7U/6.3V_6

4.7U/6.3V_6C74.7U/6.3V_6C74.7U/6.3V_6

C150

C150

1000p/50V_4

1000p/50V_4

CPU_M_VREF

VTT_SENSE

M_ZN

M_ZP

C145

C145

1000p/50V_4

1000p/50V_4

M_A_A15

M_A_A14

M_A_A13

M_A_A12

M_A_A11

M_A_A10

M_A_A9

M_A_A8

M_A_A7

M_A_A6

M_A_A5

M_A_A4

M_A_A3

M_A_A2

M_A_A1

M_A_A0

+0.9V_VTER

C6

4.7U/6.3V_6C64.7U/6.3V_6

+0.9V_VTER

C142

C142

1000p/50V_4

1000p/50V_4

AE10

AF10

C448

C448

.1U_4

.1U_4

W17

Y10

V19

J22

V22

T19

Y26

J24

W24

U23

H26

J23

J20

J21

K19

K20

V24

K24

L20

R19

L19

L22

L21

M19

M20

M24

M22

N22

N21

R21

K22

R20

T22

T20

U20

U21

Processor DDR2 Memory Interface

U16C

M_B_DQ63

M_B_DQ62

M_B_DQ61

M_B_DQ60

M_B_DQ59

M_B_DQ58

M_B_DQ57

M_B_DQ56

M_B_DQ55

M_B_DQ54

M_B_DQ53

M_B_DQ52

M_B_DQ51

M_B_DQ50

M_B_DQ49

M_B_DQ48

M_B_DQ47

M_B_DQ46

M_B_DQ45

M_B_DQ44

M_B_DQ43

M_B_DQ42

M_B_DQ41

M_B_DQ40

M_B_DQ39

M_B_DQ38

M_B_DQ37

M_B_DQ36

M_B_DQ35

M_B_DQ34

M_B_DQ33

M_B_DQ32

M_B_DQ31

M_B_DQ30

M_B_DQ29

M_B_DQ28

M_B_DQ27

M_B_DQ26

M_B_DQ25

M_B_DQ24

M_B_DQ23

M_B_DQ22

M_B_DQ21

M_B_DQ20

M_B_DQ19

M_B_DQ18

M_B_DQ17

M_B_DQ16

M_B_DQ15

M_B_DQ14

M_B_DQ13

M_B_DQ12

M_B_DQ11

M_B_DQ10

M_B_DQ9

M_B_DQ8

M_B_DQ7

M_B_DQ6

M_B_DQ5

M_B_DQ4

M_B_DQ3

M_B_DQ2

M_B_DQ1

M_B_DQ0

M_B_DM7

M_B_DM6

M_B_DM5

M_B_DM4

M_B_DM3

M_B_DM2

M_B_DM1

M_B_DM0

M_B_DQS7

M_B_DQS#7

M_B_DQS6

M_B_DQS#6

M_B_DQS5

M_B_DQS#5

M_B_DQS4

M_B_DQS#4

M_B_DQS3

M_B_DQS#3

M_B_DQS2

M_B_DQS#2

M_B_DQS1

M_B_DQS#1

M_B_DQS0

M_B_DQS#0

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

AD11

AF11

AF14

AE14

AB11

AC12

AF13

AF15

AF16

AC18

AF19

AD14

AC14

AE18

AD18

AD20

AC20

AF23

AF24

AF20

AE20

AD22

AC22

AE25

AD26

AA25

AA26

AE24

AD24

AA23

AA24

AD12

AC16

AE22

AB26

AF12

AE12

AE16

AD16

AF21

AF22

AC25

AC26

Y11

G24

G23

D26

C26

G26

G25

E24

E23

C24

B24

C20

B20

C25

D24

A21

D20

D18

C18

D14

C14

A20

A19

A16

A15

A13

D12

E11

G11

B14

A14

A11

C11

E25

A22

B16

A12

F26

E26

A24

A23

D16

C16

C12

B12

U16C

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

DDR: DATA

DDR: DATA

Athlon 64 S1

Processor Socket

AA12

AB12

AA14

AB14

W11

Y12

AD13

AB13

AD15

AB15

AB17

Y17

Y14

W14

W16

AD17

Y18

AD19

AD21

AB21

AB18

AA18

AA20

Y20

AA22

Y22

W21

W22

AA21

AB22

AB24

Y24

H22

H20

E22

E21

J19

H24

F22

F20

C23

B22

F18

E18

E20

D22

C19

G18

G17

C17

F14

E14

H17

E17

E15

H15

E13

C13

H12

H11

G14

H14

F12

G12

Y13

AB16

Y19

AC24

F24

E19

C15

E12

W12

W13

Y15

W15

AB19

AB20

AD23

AC23

G22

G21

C22

C21

G16

G15

G13

H13

M_A_DQ63

M_A_DQ62

M_A_DQ61

M_A_DQ60

M_A_DQ59

M_A_DQ58

M_A_DQ57

M_A_DQ56

M_A_DQ55

M_A_DQ54

M_A_DQ53

M_A_DQ52

M_A_DQ51

M_A_DQ50

M_A_DQ49

M_A_DQ48

M_A_DQ47

M_A_DQ46

M_A_DQ45

M_A_DQ44

M_A_DQ43

M_A_DQ42

M_A_DQ41

M_A_DQ40

M_A_DQ39

M_A_DQ38

M_A_DQ37

M_A_DQ36

M_A_DQ35

M_A_DQ34

M_A_DQ33

M_A_DQ32

M_A_DQ31

M_A_DQ30

M_A_DQ29

M_A_DQ28

M_A_DQ27

M_A_DQ26

M_A_DQ25

M_A_DQ24

M_A_DQ23

M_A_DQ22

M_A_DQ21

M_A_DQ20

M_A_DQ19

M_A_DQ18

M_A_DQ17

M_A_DQ16

M_A_DQ15

M_A_DQ14

M_A_DQ13

M_A_DQ12

M_A_DQ11

M_A_DQ10

M_A_DQ9

M_A_DQ8

M_A_DQ7

M_A_DQ6

M_A_DQ5

M_A_DQ4

M_A_DQ3

M_A_DQ2

M_A_DQ1

M_A_DQ0

M_A_DM7

M_A_DM6

M_A_DM5

M_A_DM4

M_A_DM3

M_A_DM2

M_A_DM1

M_A_DM0

M_A_DQS7

M_A_DQS#7

M_A_DQS6

M_A_DQS#6

M_A_DQS5

M_A_DQS#5

M_A_DQS4

M_A_DQS#4

M_A_DQS3

M_A_DQS#3

M_A_DQS2

M_A_DQS#2

M_A_DQS1

M_A_DQS#1

M_A_DQS0

M_A_DQS#0

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQ[0..63]

M_A_DM[0..7]

M_A_DQ[0..63](7)

To SODIMM socket A (near)

M_A_DM[0..7](7)

M_A_DQS[0..7](7)

M_A_DQS#[0..7](7)

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

ATHLON64 DDRII MEMORY I/F

ATHLON64 DDRII MEMORY I/F

ATHLON64 DDRII MEMORY I/F

Date:Sheet of

Date:Sheet of

A

B

C

D

Date:Sheet of

PROJECT : ZR3

PROJECT : ZR3

Quanta Computer Inc.

Quanta Computer Inc.

431Wednesday, October 18, 2006

431Wednesday, October 18, 2006

E

431Wednesday, October 18, 2006

1A

1A

1A

5

LAYOUT: ROUTE VDDA TRACE APPROX.

50 mils WIDE (USE 2x25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

CPU_VDDA_RUN

CPU_VDDA_RUN

DD

CPU_PWRGD(13,14)

CC

LDT_STOP#(10,13,14)

LDT_RST#(13)

EC_PWRGD(13,14,25)

NB_PWRGD(10,25)

BB

+1.8VSUS

R16300_4R16300_4

C452

C452

C93

C93

4.7U/6.3V_6

4.7U/6.3V_6

.22U/6V_4

.22U/6V_4

+1.8V

R287

R287

300_4

300_4

+1.8V

R46

R46

300_4

300_4

+1.8V

R286

R286

300_4

300_4 R280

R2840_4R2840_4

R285*0_4R285*0_4

H_THERMTRIP# H_PROCHOT#

+3V

R288

R288

4.7K/F_4

4.7K/F_4

1 3

BLM18PG330SN1D

BLM18PG330SN1D

C92

C92

3900p/25V_4

3900p/25V_4

+1.8VSUS

1

2

+1.8VSUS

1

2

+1.8VSUS

1

2

Q3

2

MMBT3904Q3MMBT3904

L49

L49

C454.1U_4C454.1U_4

5

U17

U17

3

NC7SZ08P5X_NL

NC7SZ08P5X_NL

5

U2

U2

3

NC7SZ08P5X_NL

NC7SZ08P5X_NL

C453.1U_4C453.1U_4

5

U18

U18

3

NC7SZ08P5X_NL

NC7SZ08P5X_NL

CPU H/W MONITOR

+3V

AA

CPU_TEST4_THERMDA

10 mil trace /

10 mil space

R1347/F_6R1347/F_6

15 MIL

3V_THM

C8

.1U_4C8.1U_4

C15

C15

2200P/50V_4

2200P/50V_4

5

Address 98H

U1G784U1G784

1

VCC

-ALT

3

DXN

SMDATA

2

DXP

SMCLK

-OVT4GND

+2.5V

C458

C458

100U/6.3V_3528

100U/6.3V_3528

CPU_ALL_PWROK

4

C153.1U_4C153.1U_4

CPU_LDTSTOP#

4

CPU_HT_RESET#

4

separated input voltage

R154.7K/F_4R154.7K/F_4

R14

R14

4.7K/F_4

4.7K/F_4

+3V

R279

R279

*10K_4

*10K_4

6

KBSMDATCPU_TEST5_THERMDC

7

KBSMCLK

8

5

+3V

THERM_SYS_PWR(30)

R12

R12

10K_4

10K_4

EC_PWRGD

4

To SB GPIO

MAX6648_AL#(14)

To FAN

4

+1.8VSUS

R19

R19

300_4

300_4

+3V

R11

R11

10K_4

10K_4

+3V

MAX6648_OV#(26)

3

If AMD SI is not used, the SID pin can be left unconnected and SIC

should have a 300- (5%) pulldown to VSS.

Place them to CPU within 1"

To Power

+1.8VSUS +3V

R280

10K_4

10K_4

Q20

Q20

2

MMBT3904

MMBT3904

1 3

+1.8V

R18

R18

330_4

330_4

Q4

2

MMBT3904Q4MMBT3904

13

R20*0_4R20*0_4

R10

R10

10K_4

10K_4

∮

COREFB+V(28)

COREFB-(28)

CPUCLK(12)

CPUCLK#(12)

R281

R281

10K_4

10K_4

PSI#PSI_L

CPU_EC_PROCHOT#(25)

CPU_PROCHOT#(14)

MBDATA_CPU(25)

MBCLK_CPU(25)

+1.8V

VLDT_RUN

C4553900p/25V_4C4553900p/25V_4

C4563900p/25V_4C4563900p/25V_4

PSI#(28)

SMBus SLAVE ADDRESS: 98h

3

R278*300_4R278*300_4

R267*300_4R267*300_4

R266300_4R266300_4

R2144.2F_4R2144.2F_4

R1744.2F_4R1744.2F_4

+1.8VSUS

T23T23

T21T21

2

ATHLON Control and Debug

CPU_VDDA_RUN

CPU_HT_RESET#

CPU_ALL_PWROK

CPU_LDTSTOP#

CPU_SIC_R

CPU_SID_R

CPU_HTREF1

CPU_HTREF0

CPU_VDDIO_SUS_FB_H

T9T9

CPU_VDDIO_SUS_FB_L

T4T4

CPU_CLKIN_SC_P

R282

R282

169/F_6

169/F_6

CPU_CLKIN_SC_N

T17T17

R262220_4R262220_4 R40220_4R40220_4

R261220_4R261220_4

R260220_4R260220_4

R275220_4R275220_4

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_TEST17_BP3

CPU_TEST16_BP2

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST12_SCANSHIFTENB

CPU_TEST5_THERMDC

CPU_TEST4_THERMDA

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

U16D

U16D

F8

VDDA2

F9

VDDA1

B7

RESET_L

A7

PWROK

F10

LDTSTOP_L

AF4

SIC

AF5

SID

P6

HT_REF1

R6

HT_REF0

F6

VDD_FB_H

E6

VDD_FB_L

W9

VDDIO_FB_H

Y9

VDDIO_FB_L

A9

CLKIN_H

A8

CLKIN_L

G10

DBRDY

AA9

TMS

AC9

TCK

AD9

TRST_L

AF9

TDI

E9

TEST25_H

E8

TEST25_L

G9

TEST19

H10

TEST18

AA7

TEST13

C2

TEST9

D7

TEST17

E7

TEST16

F7

TEST15

C7

TEST14

AC8

TEST12

C3

TEST7

AA6

TEST6

W7

TEST5

W8

TEST4

Y6

TEST3

AB6

TEST2

P20

RSVD0

P19

RSVD1

N20

RSVD2

N19

RSVD3

R26

RSVD4

R25

RSVD5

P22

RSVD6

R22

RSVD7

CPU_TEST27_SINGLECHAIN

CPU_TEST26_BURNIN#

CPU_PRESENT#

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

IF no use which Net

need pull-up or down

2

THERMTRIP_L

PROCHOT_L

CPU_PRESENT_L

MISC

MISC

AMD NPT S1 SOCKET

Processor Socket

R276*300_4R276*300_4

R272300_4R272300_4

R2651K/F_4R2651K/F_4

R39510/F_4R39510/F_4

R264300_4R264300_4

R271300_4R271300_4

R270300_4R270300_4

R277300_4R277300_4

R263300_4R263300_4

R25300_4R25300_4

R34300_4R34300_4

R35510/F_4R35510/F_4

R28300_4R28300_4

R27300_4R27300_4

H_THERMTRIP#CPU_VDDA_RUN

AF6

H_PROCHOT#

AC7

A5

VID5

C6

VID4

A6

VID3

A4

VID2

C5

VID1

B5

VID0

PSI_L

DBREQ_L

TDO

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

Date:Sheet of

Date:Sheet of

Date:Sheet of

CPU_PRESENT#

AC6

PSI_L

A3

PSI_L is a Power Status Indicator signal. This signal is asserted

when the processor is in a low powerstate. PSI_L should be

connected to the power supply controller, if the controller supports

¨skipmode, or diode emulation mode〃. PSI_L is asserted by the

processor during the C3 and S1 states.

CPU_DBREQ#

E10

CPU_TDO

AE9

CPU_TEST29_H_FBCLKOUT_P

C9

CPU_TEST29_L_FBCLKOUT_N

C8

AE7

AD7

AE8

AB8

AF7

J7

H8

AF8

AE6

K8

C4

H16

B18

B3

C1

H6

G6

D5

R24

W18

R23

AA8

H18

H19

+1.8VSUS

ATHLON64 CTRL & DEBUG

ATHLON64 CTRL & DEBUG

ATHLON64 CTRL & DEBUG

ROUTE AS 80 Ohm DIFFERENTIAL PAIR

PLACE IT CLOSE TO CPU WITHIN 1"

CPU_TEST24_SCANCLK1

CPU_TEST23_TSTUPD

CPU_TEST22_SCANSHIFTEN

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST27_SINGLECHAIN

CPU_TEST26_BURNIN#

PROJECT : ZR3

PROJECT : ZR3

Quanta Computer Inc.

Quanta Computer Inc.

1

+1.8VSUS

R41

R41

300_4

300_4

T2T2

R3380.6F_4R3380.6F_4

1

+1.8VSUS

531Wednesday, October 18, 2006

531Wednesday, October 18, 2006

531Wednesday, October 18, 2006

VID5(28)

VID4(28)

VID3(28)

VID2(28)

VID1(28)

VID0(28)

T78T78

1A

1A

1A

5

4

3

2

1

VCC_CORE VCC_CORE

DD

CC

BB

A1

AC4

AD2

G4

H2

J9

J11

J13

K6

K10

K12

K14

L4

L7

L9

L11

L13

M2

M6

M8

M10

N7

N9

N11

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

V6

V8

V10

U16E

U16E

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

Athlon 64 S1

Processor Socket

POWER

POWER

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

A26

U16F

V12

V14

W4

Y2

J15

K16

L15

M16

P16

T16

U15

V16

+1.8VSUS

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

P18

P21

P23

P25

R17

T18

T21

T23

T25

U17

V18

V21

V23

V25

Y25

AA11

AA13

AA15

AA17

AA19

AB23

AB25

AC11

AC13

AC15

AC17

AC19

AC21

AD6

AD8

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

AA4

AB2

AB7

AB9

B11

B13

B15

B17

B19

B21

B23

B25

D11

D13

D15

D17

D19

D21

D23

D25

F11

F13

F15

F17

F19

F21

F23

F25

H21

H23

U16F

B4

B6

B8

B9

D6

D8

D9

E4

F2

H7

H9

J4

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

GROUND

GROUND

Athlon 64 S1

Processor Socket

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

M11

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

VCC_CORE

C79

C79

22U/10V_8

22U/10V_8

VCC_CORE

C74

C74

.22U/6V_4

.22U/6V_4

+1.8VSUS

C56

C56

22U/10V_8

22U/10V_8

+1.8VSUS

C61

C61

4.7U/6.3V_6

4.7U/6.3V_6

+1.8VSUS

C59

C59

.01U_4

.01U_4

BOTTOMSIDE DECOUPLING

C78

C78

22U/10V_8

22U/10V_8

C54

C54

.22U/6V_4

.22U/6V_4

C46

C46

22U/10V_8

22U/10V_8

C445

22U/10V_8

22U/10V_8

C89

C89

.01U_4

.01U_4

C91

C91

.22U/6V_4

.22U/6V_4

C446

C446

22U/10V_8

22U/10V_8

C47

C47

180P_4

180P_4

C90

C90

.22U/6V_4

.22U/6V_4

C77

C77

22U/10V_8

22U/10V_8

VCC_CORE

C162

C162

.22U/6V_4

.22U/6V_4

C62

C51

C51

22U/10V_8

22U/10V_8

C62

22U/10V_8

22U/10V_8

Near ATI RS485 Chipset

C183

C183

.22U/6V_4

.22U/6V_4

C115

C115

.01U_4

.01U_4

C63

C63

22U/10V_8

22U/10V_8

C65

C65

.01U_4

.01U_4

C80

C80

22U/10V_8

22U/10V_8

C445

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

C82

C75

C75

4.7U/6.3V_6

4.7U/6.3V_6

C44

C44

.01U_4

.01U_4

C70

C70

4.7U/6.3V_6

4.7U/6.3V_6

C66

C66

10P_4

10P_4

C84

C84

4.7U/6.3V_6

4.7U/6.3V_6

C71

C71

180P_4

180P_4

C58

C58

.22U/6V_4

.22U/6V_4

C103

C103

180P_4

180P_4

C83

C83

.22U/6V_4

.22U/6V_4

C41

C41

180P_4

180P_4

C82

.22U/6V_4

.22U/6V_4

C94

C94

180P_4

180P_4

C45

C45

.22U/6V_4

.22U/6V_4

C34

C34

180P_4

180P_4

C52

C52

.01U_4

.01U_4

C35

C35

.01U_4

.01U_4

Athlon 64 S1g1

PROCESSOR POWER AND GROUND

uPGA638

AA

AF1

Top View

PROJECT : ZR3

PROJECT : ZR3

Quanta Computer Inc.

Quanta Computer Inc.

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

ATHLON64 PWR & GND

ATHLON64 PWR & GND

ATHLON64 PWR & GND

Date:Sheet of

Date:Sheet of

5

4

3

2

Date:Sheet of

631Wednesday, October 18, 2006

631Wednesday, October 18, 2006

631Wednesday, October 18, 2006

1

1A

1A

1A

A

TERMINATOR DECOUPLING CAPACITORDDR2 TERMINATOR

+0.9V_VTER

C27

C27

C101

C23

C23

C111

C111

10U/6.3V_8

10U/6.3V_8

.1U-16V_4

.1U-16V_4

44

C10

C10

C11

C11

.1U-16V_4

.1U-16V_4

.1U-16V_4

.1U-16V_4

+1.8VSUS

.1U-16V_4

.1U-16V_4

C118

C118

.1U-16V_4

.1U-16V_4

C101

.1U-16V_4

.1U-16V_4

C37

C37

.1U-16V_4

.1U-16V_4

C106

C106

.1U-16V_4

.1U-16V_4

C125

C125

.1U-16V_4

.1U-16V_4

C33

C33

.1U-16V_4

.1U-16V_4

C19

C19

.1U-16V_4

.1U-16V_4

C102

C102

.1U-16V_4

.1U-16V_4

C53

C53

.1U-16V_4

.1U-16V_4

C100

C100

.1U-16V_4

.1U-16V_4

C76

C76

.1U-16V_4

.1U-16V_4

C107

C107

.1U-16V_4

.1U-16V_4

C43

C43

.1U-16V_4

.1U-16V_4

C104

C104

.1U-16V_4

.1U-16V_4

C113

C113

.1U-16V_4

.1U-16V_4

B

C108

C108

.1U-16V_4

.1U-16V_4

C64

C64

.1U-16V_4

.1U-16V_4

C109

C109

.1U-16V_4

.1U-16V_4

C26

C26

.1U-16V_4

.1U-16V_4

C28

C28

.1U-16V_4

.1U-16V_4

C98

C98

.1U-16V_4

.1U-16V_4

C32

C32

.1U-16V_4

.1U-16V_4

C110

C110

.1U-16V_4

.1U-16V_4

C29

C29

.1U-16V_4

.1U-16V_4

C87

C87

.1U-16V_4

.1U-16V_4

C24

C24

.1U-16V_4

.1U-16V_4

+0.9V_VTER

C31

C31

.1U-16V_4

.1U-16V_4

C119

C119

.1U-16V_4

.1U-16V_4

C

M_CKE0

M_CKE1

M_CKE2

M_CKE3

M_A_CS#3

M_A_A13

M_A_CAS#

M_ODT0

M_ODT3

M_B_WE#

M_B_A13

M_B_CS#3

M_A_CS#1

M_ODT1

M_B_CAS#

M_B_CS#1

R3047_4R3047_4

R3247_4R3247_4

R3147_4R3147_4

R2947_4R2947_4

RN247_4P2R_SRN247_4P2R_S

1 2

RN147_4P2R_SRN147_4P2R_S

1 2

RN547_4P2R_SRN547_4P2R_S

1 2

RN347_4P2R_SRN347_4P2R_S

1 2

RN447_4P2R_SRN447_4P2R_S

1 2

RN847_4P2R_SRN847_4P2R_S

1 2

+0.9V_VTER

43

43

43

43

43

43

D

M_A_A2

M_A_A4

M_A_A3

M_A_A5

M_A_BS#1

M_A_A0

M_A_A7

M_A_A6

M_A_A1

M_A_A10

M_A_WE#

M_A_BS#0

M_A_A12

M_A_BS#2

M_A_A8

M_A_A11

M_A_CS#2

M_A_A9

M_A_RAS#

M_A_CS#0

M_A_A14

M_A_A15

RN1447_4P2R_SRN1447_4P2R_S

1 2

43

RN1747_4P2R_SRN1747_4P2R_S

1 2

43

RN1047_4P2R_SRN1047_4P2R_S

1 2

43

RN1847_4P2R_SRN1847_4P2R_S

1 2

43

RN1347_4P2R_SRN1347_4P2R_S

1 2

43

RN947_4P2R_SRN947_4P2R_S

1 2

43

RN2047_4P2R_SRN2047_4P2R_S

1 2

43

RN2247_4P2R_SRN2247_4P2R_S

1 2

43

RN2447_4P2R_SRN2447_4P2R_S

1 2

43

RN647_4P2R_SRN647_4P2R_S

1 2

43

RN2647_4P2R_SRN2647_4P2R_S

1 2

43

M_B_A10

M_B_BS#0

M_B_A4

M_B_A2

M_B_A5

M_B_A1

M_B_A6

M_B_A0

M_B_A3

M_B_A8

M_B_A11

M_B_A7

M_B_BS#2

M_B_CS#2

M_B_RAS#

M_B_BS#1

M_ODT2

M_B_CS#0

M_B_A12

M_B_A9

M_B_A15

M_B_A14

E

RN1247_4P2R_SRN1247_4P2R_S

1 2

43

RN1547_4P2R_SRN1547_4P2R_S

1 2

43

RN1647_4P2R_SRN1647_4P2R_S

1 2

43

RN1947_4P2R_SRN1947_4P2R_S

1 2

43

RN2547_4P2R_SRN2547_4P2R_S

1 2

43

RN2347_4P2R_SRN2347_4P2R_S

1 2

43

RN2847_4P2R_SRN2847_4P2R_S

1 2

43

RN1147_4P2R_SRN1147_4P2R_S

1 2

43

RN747_4P2R_SRN747_4P2R_S

1 2

43

RN2147_4P2R_SRN2147_4P2R_S

1 2

43

RN2747_4P2R_SRN2747_4P2R_S

1 2

43

+0.9V_VTER+0.9V_VTER

+1.8VSUS

103

111

104

112

117

M_A_A[0..15](4)

33

M_A_BS#0(4)

M_A_BS#1(4)

M_A_BS#2(4)

M_A_DM[0..7](4)

M_A_DQS[0..7](4)

M_A_DQS#[0..7](4)

+3V

M_CLKOUT0(4)

M_CLKOUT0#(4)

M_CLKOUT1(4)

M_CLKOUT1#(4)

PDAT_SMB(12,14,20)

PCLK_SMB(12,14,20)

C167.1U_4C167.1U_4

M_CKE0(4)

M_CKE1(4)

M_A_RAS#(4)

M_A_CAS#(4)

M_A_WE#(4)

M_A_CS#0(4)

M_A_CS#1(4)

M_ODT0(4)

M_ODT1(4)

MVREF_DIM

C161

C161

2.2U/10V/X5R_8

2.2U/10V/X5R_8

1 2

M_CLKOUT0

C138

C138

1.5P_4

1.5P_4

M_CLKOUT0#

M_CLKOUT1

C17

C17

1.5P_4

1.5P_4

M_CLKOUT1#

22

+1.8VSUS

11

M_CLKOUT0

M_CLKOUT0#

M_CLKOUT1

M_CLKOUT1#

C4.1U_4C4.1U_4

C166

C166

.1U_4

.1U_4

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

102

A0

101

A1

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

CN11

A8

A9

A10

A11

A12

A13

A14

A15

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

CK0

CK0

CK1

CK1

CKE0

CKE1

RAS

CAS

WE

S0

S1

ODT0

ODT1

SA0

SA1

SDA

SCL

VDDspd

VREF

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

CN11

REVERSE

(H=4)

59

93

91

105

90

89

116

86

84

107

106

85

10

26

52

67

130

147

170

185

13

31

51

70

131

148

169

188

11

29

49

68

129

146

167

186

30

32

164

166

79

80

108

113

109

110

115

114

119

198

200

195

197

199

1

2

3

8

9

12

15

18

21

24

27

28

33

34

39

40

41

42

47

48

53

54

SMBus ADDRESS: A0hSMBus ADDRESS: A4h

A

VDD7

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

SO-DIMM

SO-DIMM

VDD8

VSS29

122

121

118

DQ0

DQ1

VDD9

VDD10

VDD11

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

NC1

NC2

NC3

NC4

NC/TEST

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

VSS30

132

128

127

DDRII_SODIMM_R

DDRII_SODIMM_R

B

5

7

17

19

4

6

14

16

23

25

35

37

20

22

36

38

43

45

55

57

44

46

56

58

61

63

73

75

62

64

74

76

123

125

135

137

124

126

134

136

141

143

151

153

140

142

152

154

157

159

173

175

158

160

174

176

179

181

189

191

180

182

192

194

50

69

83

120

163

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

M_A_DQ1

M_A_DQ0

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ7

M_A_DQ6

M_A_DQ12

M_A_DQ8

M_A_DQ10

M_A_DQ11

M_A_DQ9

M_A_DQ13

M_A_DQ15

M_A_DQ14

M_A_DQ17

M_A_DQ21

M_A_DQ23

M_A_DQ18

M_A_DQ20

M_A_DQ19

M_A_DQ22

M_A_DQ16

M_A_DQ29

M_A_DQ28

M_A_DQ31

M_A_DQ30

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ32

M_A_DQ36

M_A_DQ37

M_A_DQ35

M_A_DQ33

M_A_DQ38

M_A_DQ34

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ46

M_A_DQ44

M_A_DQ45

M_A_DQ43

M_A_DQ47

M_A_DQ49

M_A_DQ52

M_A_DQ50

M_A_DQ51

M_A_DQ53

M_A_DQ48

M_A_DQ55

M_A_DQ54

M_A_DQ60

M_A_DQ56

M_A_DQ58

M_A_DQ63

M_A_DQ57

M_A_DQ61

M_A_DQ59

M_A_DQ62

M_A_CS#2(4)

M_A_CS#3(4)

+0.9V_REF

M_A_DQ[0..63](4)

+1.8VSUS

R47

R47

*0_4

*0_4

MVREF_DIM

C175

C175

1U/10V_4

1U/10V_4

+3V

+3V

+1.8VSUS

C163.1U_4C163.1U_4

R48

R48

1K/F_4

1K/F_4

R49

R49

1K/F_4

1K/F_4

M_B_A[0..15](4)

M_B_DM[0..7](4)

M_B_DQS[0..7](4)

M_B_DQS#[0..7](4)

M_CLKOUT3#(4)

M_CLKOUT4#(4)

M_B_BS#0(4)

M_B_BS#1(4)

M_B_BS#2(4)

M_CLKOUT3(4)

M_CLKOUT4(4)

M_CKE2(4)

M_CKE3(4)

M_B_RAS#(4)

M_B_CAS#(4)

M_B_WE#(4)

M_B_CS#0(4)

M_B_CS#1(4)

M_ODT2(4)

M_ODT3(4)

C

R910K_4R910K_4

C3.1U_4C3.1U_4

MVREF_DIM

C180

C180

2.2U/10V/X5R_8

2.2U/10V/X5R_8

1 2

M_CLKOUT3

C137

C137

1.5P_4

1.5P_4

M_CLKOUT3#

M_CLKOUT4

C14

C14

1.5P_4

1.5P_4

M_CLKOUT4#

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_CLKOUT3

M_CLKOUT3#

M_CLKOUT4

M_CLKOUT4#

PDAT_SMB

PCLK_SMB

C168

C168

.1U_4

.1U_4

102

101

100

99

98

97

94

92

93

91

105

90

89

116

86

84

107

106

85

10

26

52

67

130

147

170

185

13

31

51

70

131

148

169

188

11

29

49

68

129

146

167

186

30

32

164

166

79

80

108

113

109

110

115

114

119

198

200

195

197

199

1

2

3

8

9

12

15

18

21

24

27

28

33

34

39

40

41

42

47

48

53

54

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

CK0

CK0

CK1

CK1

CKE0

CKE1

RAS

CAS

WE

S0

S1

ODT0

ODT1

SA0

SA1

SDA

SCL

VDDspd

VREF

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

+1.8VSUS

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

CN10

CN10

REVERSE

(H=8)

59

103

111

104

VDD8

VDD7

SO-DIMM

SO-DIMM

VSS29

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

121

112

117

118

VDD9

VDD10

VDD11

NC/TEST

VSS33

VSS32

VSS31

VSS30

132

128

127

122

M_B_DQ4

5

DQ0

M_B_DQ1

7

DQ1

M_B_DQ7

17

DQ2

M_B_DQ3

19

DQ3

M_B_DQ5

4

DQ4

M_B_DQ0

6

DQ5

M_B_DQ6

14

DQ6

M_B_DQ2

16

DQ7

M_B_DQ8

23

DQ8

M_B_DQ9

25

DQ9

M_B_DQ15

35

DQ10

M_B_DQ11

37

DQ11

M_B_DQ13

20

DQ12

M_B_DQ12

22

DQ13

M_B_DQ14

36

DQ14

M_B_DQ10

38

DQ15

M_B_DQ16

43

DQ16

M_B_DQ17

45

DQ17

M_B_DQ18

55

DQ18

M_B_DQ19

57

DQ19

M_B_DQ20

44

DQ20

M_B_DQ21

46

DQ21

M_B_DQ22

56

DQ22

M_B_DQ23

58

DQ23

M_B_DQ25

61

DQ24

M_B_DQ29

63

DQ25

M_B_DQ27

73

DQ26

M_B_DQ26

75

DQ27

M_B_DQ28

62

DQ28

M_B_DQ24

64

DQ29

M_B_DQ30

74

DQ30

M_B_DQ31

76

DQ31

M_B_DQ32

123

DQ32

M_B_DQ36

125

DQ33

M_B_DQ34

135

DQ34

M_B_DQ38

137

DQ35

M_B_DQ33

124

DQ36

M_B_DQ37

126

DQ37

M_B_DQ39

134

DQ38

M_B_DQ35

136

DQ39

M_B_DQ41

141

DQ40

M_B_DQ40

143

DQ41

M_B_DQ42

151

DQ42

M_B_DQ43

153

DQ43

M_B_DQ45

140

DQ44

M_B_DQ44

142

DQ45

M_B_DQ46

152

DQ46

M_B_DQ47

154

DQ47

M_B_DQ48

157

DQ48

M_B_DQ49

159

DQ49

M_B_DQ50

173

DQ50

M_B_DQ51

175

DQ51

M_B_DQ52

158

DQ52

M_B_DQ53

160

DQ53

M_B_DQ55

174

DQ54

M_B_DQ54

176

DQ55

M_B_DQ61

179

DQ56

M_B_DQ57

181

DQ57

M_B_DQ58

189

DQ58

M_B_DQ62

191

DQ59

M_B_DQ56

180

DQ60

M_B_DQ60

182

DQ61

M_B_DQ59

192

DQ62

M_B_DQ63

194

DQ63

50

NC1

69

NC2

83

NC3

120

NC4

163

196

VSS56

193

VSS55

190

VSS54

187

VSS53

184

VSS52

183

VSS51

178

VSS50

177

VSS49

172

VSS48

171

VSS47

168

VSS46

165

VSS45

162

VSS44

161

VSS43

156

VSS42

155

VSS41

150

VSS40

149

VSS39

145

VSS38

144

VSS37

139

VSS36

138

VSS35

133

VSS34

DDRII_SODIMM_R

DDRII_SODIMM_R

D

M_B_DQ[0..63](4)

+1.8VSUS

*10U/6.3V/X5R_8C22 *10U/6.3V/X5R_8C22

*10U/6.3V/X5R_8C25 *10U/6.3V/X5R_8C25

10U/10V/X5R_8C20 10U/10V/X5R_8C20

10U/10V/X5R_8C114 10U/10V/X5R_8C114

.1U_4C85 .1U_4C85

.1U_4C95 .1U_4C95

.1U_4C40 .1U_4C40

.1U_4C50 .1U_4C50

.1U_4C88 .1U_4C88

.1U_4C36 .1U_4C36

.1U_4C38 .1U_4C38

.1U_4C73 .1U_4C73

.1U_4C49 .1U_4C49

.1U_4C48 .1U_4C48

.1U_4C39 .1U_4C39

.1U_4C81 .1U_4C81

.1U_4C69 .1U_4C69

.1U_4C68 .1U_4C68

.1U_4C55 .1U_4C55

.1U_4C57 .1U_4C57

.1U_4C60 .1U_4C60

.1U_4C30 .1U_4C30

.1U_4C72 .1U_4C72

M_B_CS#2(4)

M_B_CS#3(4)

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

DDR2 SO-DIMM

DDR2 SO-DIMM

DDR2 SO-DIMM

Date:Sheet of

Date:Sheet of

Date:Sheet of

Quanta Computer Inc.

Quanta Computer Inc.

.1U_4C67 .1U_4C67

PROJECT : ZR3

PROJECT : ZR3

E

1A

1A

731Wednesday, October 18, 2006

731Wednesday, October 18, 2006

731Wednesday, October 18, 2006

1A

5

DD

HT_CADOUT15_P(3)

HT_CADOUT15_N(3)

HT_CADOUT14_P(3)

HT_CADOUT14_N(3)

HT_CADOUT13_P(3)

HT_CADOUT13_N(3)

HT_CADOUT12_P(3)

HT_CADOUT12_N(3)

HT_CADOUT11_P(3)

HT_CADOUT11_N(3)

HT_CADOUT10_P(3)

HT_CADOUT10_N(3)

HT_CADOUT9_P(3)

HT_CADOUT9_N(3)

HT_CADOUT8_P(3)

CC

BB

VDDHT_PKG

HT_CADOUT8_N(3)

HT_CADOUT7_P(3)

HT_CADOUT7_N(3)

HT_CADOUT6_P(3)

HT_CADOUT6_N(3)

HT_CADOUT5_P(3)

HT_CADOUT5_N(3)

HT_CADOUT4_P(3)

HT_CADOUT4_N(3)

HT_CADOUT3_P(3)

HT_CADOUT3_N(3)

HT_CADOUT2_P(3)

HT_CADOUT2_N(3)

HT_CADOUT1_P(3)

HT_CADOUT1_N(3)

HT_CADOUT0_P(3)

HT_CADOUT0_N(3)

HT_CLKOUT1_P(3)

HT_CLKOUT1_N(3)

HT_CLKOUT0_P(3)

HT_CLKOUT0_N(3)

HT_CTLOUT0_P(3)

HT_CTLOUT0_N(3)

R31349.9/F_4R31349.9/F_4 R65100/F_4R65100/F_4

R56

R56

49.9/F_4

49.9/F_4

4

U19A

U19A

R19

HT_RXCAD15P

R18

HT_RXCAD15N

R21

HT_RXCAD14P

R22

HT_RXCAD14N

U22

HT_RXCAD13P

U21

HT_RXCAD13N

U18

HT_RXCAD12P

U19

HT_RXCAD12N

W19

HT_RXCAD11P

W20

HT_RXCAD11N

AC21

HT_RXCAD10P

AB22

HT_RXCAD10N

AB20

HT_RXCAD9P

AA20

HT_RXCAD9N

AA19

HT_RXCAD8P

Y19

HT_RXCAD8N

T24

HT_RXCAD7P

R25

HT_RXCAD7N

U25

HT_RXCAD6P

U24

HT_RXCAD6N

V23

HT_RXCAD5P

U23

HT_RXCAD5N

V24

HT_RXCAD4P

V25

HT_RXCAD4N

AA25

HT_RXCAD3P

AA24

HT_RXCAD3N

AB23

HT_RXCAD2P

AA23

HT_RXCAD2N

AB24

HT_RXCAD1P

AB25

HT_RXCAD1N

AC24

HT_RXCAD0P

AC25

HT_RXCAD0N

W21

HT_RXCLK1P

W22

HT_RXCLK1N

Y24

HT_RXCLK0P

W25

HT_RXCLK0N

P24

HT_RXCTLP

P25

HT_RXCALP

HT_RXCALN

HT_RXCTLN

A24

HT_RXCALP

C24

HT_RXCALN

RS485M A11 HT

RS485M A11 HT

3

PART 1 OF 5

PART 1 OF 5

HYPER TRANSPORT CPU I/F

HYPER TRANSPORT CPU I/F

HT_TXCAD15P

HT_TXCAD15N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD0P

HT_TXCAD0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCTLP

HT_TXCTLN

HT_TXCALP

HT_TXCALN

P21

P22

P18

P19

M22

M21

M18

M19

L18

L19

G22

G21

J20

J21

F21

F22

N24

N25

L25

M24

K25

K24

J23

K23

G25

H24

F25

F24

E23

F23

E24

E25

L21

L22

J24

J25

N23

P23

C25

D24

HT_TXCALP

HT_TXCALN

2

HT_CADIN15_P(3)

HT_CADIN15_N(3)

HT_CADIN14_P(3)

HT_CADIN14_N(3)

HT_CADIN13_P(3)

HT_CADIN13_N(3)

HT_CADIN12_P(3)

HT_CADIN12_N(3)

HT_CADIN11_P(3)

HT_CADIN11_N(3)

HT_CADIN10_P(3)

HT_CADIN10_N(3)

HT_CADIN9_P(3)

HT_CADIN9_N(3)

HT_CADIN8_P(3)

HT_CADIN8_N(3)

HT_CADIN7_P(3)

HT_CADIN7_N(3)

HT_CADIN6_P(3)

HT_CADIN6_N(3)

HT_CADIN5_P(3)

HT_CADIN5_N(3)

HT_CADIN4_P(3)

HT_CADIN4_N(3)

HT_CADIN3_P(3)

HT_CADIN3_N(3)

HT_CADIN2_P(3)

HT_CADIN2_N(3)

HT_CADIN1_P(3)

HT_CADIN1_N(3)

HT_CADIN0_P(3)

HT_CADIN0_N(3)

HT_CLKIN1_P(3)

HT_CLKIN1_N(3)

HT_CLKIN0_P(3)

HT_CLKIN0_N(3)

HT_CTLIN0_P(3)

HT_CTLIN0_N(3)

1

AA

5

4

3

2

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

RS485-HT LINK0 I/F

RS485-HT LINK0 I/F

RS485-HT LINK0 I/F

Date:Sheet

Date:Sheet

Date:Sheet of

PROJECT : ZR3

PROJECT : ZR3

Quanta Computer Inc.

Quanta Computer Inc.

831Wednesday, October 18, 2006

831Wednesday, October 18, 2006

831Wednesday, October 18, 2006

of

1

of

1A

1A

1A

5

DD

CC

WLAN MINI CARDWLAN MINI CARD

BB

MINI_PCIE_RXP0(20)

MINI_PCIE_RXN0(20)

T31T31

T83T83

A_RX0P(13)

A_RX0N(13)

A_RX1P(13)

A_RX1N(13)

R4310K_6R4310K_6

R378.25K/F_6R378.25K/F_6

R27:

R29:

4

PCE_ISET

PCE_TXISET

10KOhm FOR RS485

1.47KOhm FOR RS690

8.25KOhm FOR RS485

DNI FOR RS690

U19B

U19B

G5

GFX_RX0P

G4

GFX_RX0N

J8

GFX_RX1P

J7

GFX_RX1N

J4

GFX_RX2P

J5

GFX_RX2N

L8

GFX_RX3P

L7

GFX_RX3N

L4

GFX_RX4P

L5

GFX_RX4N

M8

GFX_RX5P

M7

GFX_RX5N

M4

GFX_RX6P

M5

GFX_RX6N

P8

GFX_RX7P

P7

GFX_RX7N

P4

GFX_RX8P

P5

GFX_RX8N

R4

GFX_RX9P

R5

GFX_RX9N

R7

GFX_RX10P

R8

GFX_RX10N

U4

GFX_RX11P

U5

GFX_RX11N

W4

GFX_RX12P

W5

GFX_RX12N

Y4

GFX_RX13P

Y5

GFX_RX13N

V9

GFX_RX14P

W9

GFX_RX14N

AB7

GFX_RX15P

AB6

GFX_RX15N

W11

GPP_RX0P

W12

GPP_RX0N

AA11

GPP_RX1P

AB11

GPP_RX1N

Y7

GPP_RX2P

AA7

GPP_RX2N

AB9

GPP_RX3P

AA9

GPP_RX3N

W14

SB_RX0P

W15

SB_RX0N

AB12

SB_RX1P

AA12

SB_RX1N

AA14

PCE_ISET(PCE_CALI)

AB14

PCE_TXISET(NC)

RS485M A11 HT

RS485M A11 HT

PART 2 OF 5

PART 2 OF 5

PCIE I/F GFX

PCIE I/F GFX

PCIE I/F GPP

PCIE I/F GPP

PCIE I/F SB

PCIE I/F SB

PCE_PCAL(PCE_CALRP)

PCE_NCAL(PCE_CALRN)

3

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

J1

H2

K2

K1

K3

L3

L1

L2

N2

N1

P2

P1

P3

R3

R1

R2

T2

U1

V2

V1

V3

W3

W1

W2

Y2

AA1

AA2

AB2

AB1

AC1

AE3

AE4

AD8

AE8

AD7

AE7

AD4

AE5

AD5

AD6

AE9

AD10

AC8

AD9

AD11

AE11

GPP_TX0P_C

GPP_TX0N_C

A_TX0P_C

A_TX0N_C

A_TX1P_C

A_TX1N_C

PCE_PCAL

PCE_NCAL

Place these caps

close to connector

C126.1U_4C126.1U_4

C122.1U_4C122.1U_4

C120.1U_4C120.1U_4

C121.1U_4C121.1U_4

C139.1U_4C139.1U_4

R36150/F_6R36150/F_6

R38100/F_6R38100/F_6

R28:

R26:

C140.1U_4C140.1U_4

150 Ohm FOR RS485

562 Ohm FOR RS690

Ward update to 100 Ohm FOR RS485

2KOhm FOR RS690

2

MINI_PCIE_TXP0(20)

MINI_PCIE_TXN0(20)

T84T84

T82T82

A_TX0P(13)

A_TX0N(13)

A_TX1P(13)

A_TX1N(13)

VDDA12_PKG2

1

AA

5

4

3

2

SizeDocument NumberRev

SizeDocument NumberRev

SizeDocument NumberRev

RS485-PCIE LINK I/F

RS485-PCIE LINK I/F

RS485-PCIE LINK I/F

Date:Sheet

Date:Sheet

Date:Sheet of

PROJECT : ZR3

PROJECT : ZR3

Quanta Computer Inc.

Quanta Computer Inc.

931Wednesday, October 18, 2006

931Wednesday, October 18, 2006

931Wednesday, October 18, 2006

of

1

of

1A

1A

1A

5

HTPVDD+1.8V

L9

L9

BK1608HS330_6

BK1608HS330_6

DD

TV_C/R_SYS(21)

TV_Y/G_SYS(21)

TV_COMP_SYS(21)

VGA_RED(21)

VGA_GRN(21)

VGA_BLU(21)

CC

LDT_STOP#(5,13,14)

HTPVDD

C468

C468

10U/10V/X5R_8

10U/10V/X5R_8

close to NB

R344

R344

150/F_4

150/F_4

close to NB

R54

R54

150/F_4

150/F_4

+1.8V

R42

R42

10K_4

10K_4

2

Q5

Q5

1 3

MMBT3904

MMBT3904

C186

C186

4.7U/6.3V_6

4.7U/6.3V_6

TV_C/R_SYS

TV_Y/G_SYS

TV_COMP_SYS

R345

R345

150/F_4

150/F_4

R50

R50

150/F_4

150/F_4

+3V

R64

R64

1K/F_4

1K/F_4

R346

R346

150/F_4

150/F_4

R52

R52

150/F_4

150/F_4

LDT_STOP#_NB

LOAD_ROM#: LOAD ROM STRAP ENABLE

BB

AA

5

High, LOAD ROM STRAP DISABLE

Low, LOAD ROM STRAP ENABLE

4

+3V

+1.8V

R3280/F_6R3280/F_6

+1.8V

L54

L54

BK1608HS330_6

BK1608HS330_6

PLLVDD+1.8V

L55

L55

BK1608HS330_6

BK1608HS330_6

C488

C488

10U/10V/X5R_8

10U/10V/X5R_8

OSCOUT(A11)

DVO_D0(AD14)

DVO_D1(AD15) DVO_D1

DVO_D3(AD16)

DVO_D7(AE19)

DVO_D8(AD19)

DVO_D9(AE20)

4

L14

L14

BK1608HS330_6

BK1608HS330_6

AVDDQ

C486

C486

10U/10V/X5R_8

10U/10V/X5R_8

ALINK_RST#(13,20,22)

NB_PWRGD(5,25)

ALLOW_LDTSTOP(13)

HTREFCLK(12)

NB_OSC(12)

NBSRC_CLKP(12)

NBSRC_CLKN(12)

SBLINK_CLKP(12)

SBLINK_CLKN(12)

R593K/F_4R593K/F_4

BMREQ#(13)

PHL_CLK(21)

PHL_DATA(21)

RS485

OSCOUT

DVO_D0

DVO_D3

DVO_D4

DVO_D7

DVO_D8

DVO_D9

DVO_D10DVO_D10(AD20)

AVDD_NB

AVDD1

12

12

C479

4.7U/6.3V_6

4.7U/6.3V_6

RS690

PLLVDD12

GPP_TX4P

GPP_TX4N

GPP_RX4P

GPP_RX4NDVO_D4(AE16)

GPP_TX5N

GPP_TX5P

GPP_RX5N

GPP_RX5P

C189

C189

10U/6.3V_6

10U/6.3V_6

C484

C484

2.2U/10V_8

2.2U/10V_8

C485

C485

2.2U/10V/X5R_8

2.2U/10V/X5R_8

LOAD_ROM#

+3V

C184

C184

.1U_4

.1U_4

C481

C481

.1U_4

.1U_4

VSYNC(21)

HSYNC(21)

DDCCLK(21)

DDCDAT(21)

HTPVDD

R3340_4R3340_4

R3410_4R3410_4

D27

D27

2 1

R584.7K/F_4R584.7K/F_4

R682K/FR682K/F

LCD_PON

LVDS_BLON

LVDS_BLEN

3

C199

C199

*100U/6.3V_3528

*100U/6.3V_3528

TV_C/R_SYS

TV_Y/G_SYS

TV_COMP_SYS

R327715/F_6R327715/F_6

R7110K_4R7110K_4

R6210K_4R6210K_4

T88T88

R57*2.7K_4R57*2.7K_4

R63*2.7K_4R63*2.7K_4

R326*2.7K_4R326*2.7K_4

R335*2.7K_4R335*2.7K_4

R325*2.7K_4R325*2.7K_4

RB751

RB751

T27T27

T25T25

T86T86

T87T87

R3302K/F_4R3302K/F_4

R532.7K/F_4R532.7K/F_4

R76*2.7K/F_4R76*2.7K/F_4

3

R700_4R700_4C479

R690_4R690_4

NB_RST#

LDT_STOP#_NB

PLLVDD12

DFT_GPIO0

DFT_GPIO2

DFT_GPIO3

DFT_GPIO4

DFT_GPIO5

STRP_DATA

U19C

U19C

B22

AVDD1

C22

AVDD2

G17

AVSSN1

H17

AVSSN2

A20

AVDDDI

B20

AVSSDI

A21

AVDDQ

A22

AVSSQ

C21

C_R

C20

Y_G

D19

COMP_B

E19

RED

F19

GREEN

G19

BLUE

C6

DACVSYNC

A5

DACHSYNC

B21

RSET

B6

DACSCL

A6

DACSDA

A10

PLLVDD(PLLVDD18)

B10

PLLVSS

B24

HTPVDD

B25

HTPVSS

C10

SYSRESET#

C11

POWERGOOD

C5

LDTSTOP#

B5

ALLOW_LDTSTOP

C23

HTTSTCLK

B23

HTREFCLK

C2

TVCLKIN

B11

OSCIN

A11

OSCOUT(PLLVDD12)

F2

GFX_CLKP

E1

GFX_CLKN

G1

SB_CLKP

G2

SB_CLKN

D6

DFT_GPIO0

D7

DFT_GPIO1

C8

DFT_GPIO2

C7

DFT_GPIO3

B8

DFT_GPIO4

A8

DFT_GPIO5

B2

BMREQb

A2

I2C_CLK

B4

I2C_DATA

AA15

THERMALDIODE_P

AB15

THERMALDIODE_N

C14

TMDS_HPD

B3

DDC_DATA

C3

TESTMODE

A3

STRP_DATA

RS485M A11 HT

RS485M A11 HT

LVDS_BLON