A

Vinafix.com

1 1

B

C

D

E

Compal Confidential

FH5LI MB Schematic Document

2 2

3 3

LA-J801P

Rev:1.0

2019.10.30

4 4

Security Class ification

Security Class ification

Security Class ification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2017/11/ 23 2018/09/ 01

2017/11/ 23 2018/09/ 01

2017/11/ 23 2018/09/ 01

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Cover Sheet

Cover Sheet

Cover Sheet

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

D

FH5LI M/B LA-H801P

FH5LI M/B LA-H801P

FH5LI M/B LA-H801P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1 102Wednesd ay, October 30, 20 19

1 102Wednesd ay, October 30, 20 19

1 102Wednesd ay, October 30, 20 19

E

1.0

1.0

1.0

A

Vinafix.com

B

C

D

E

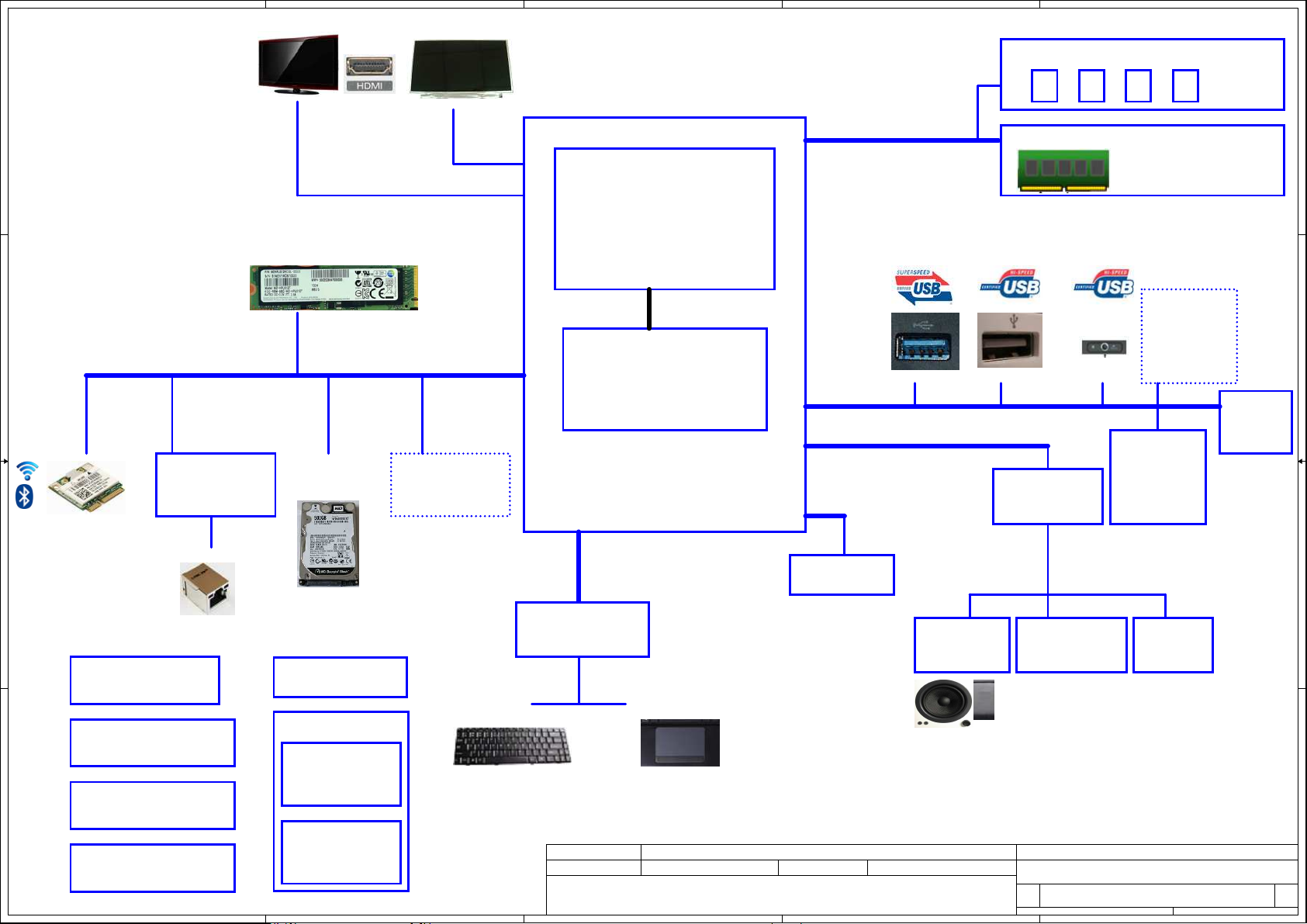

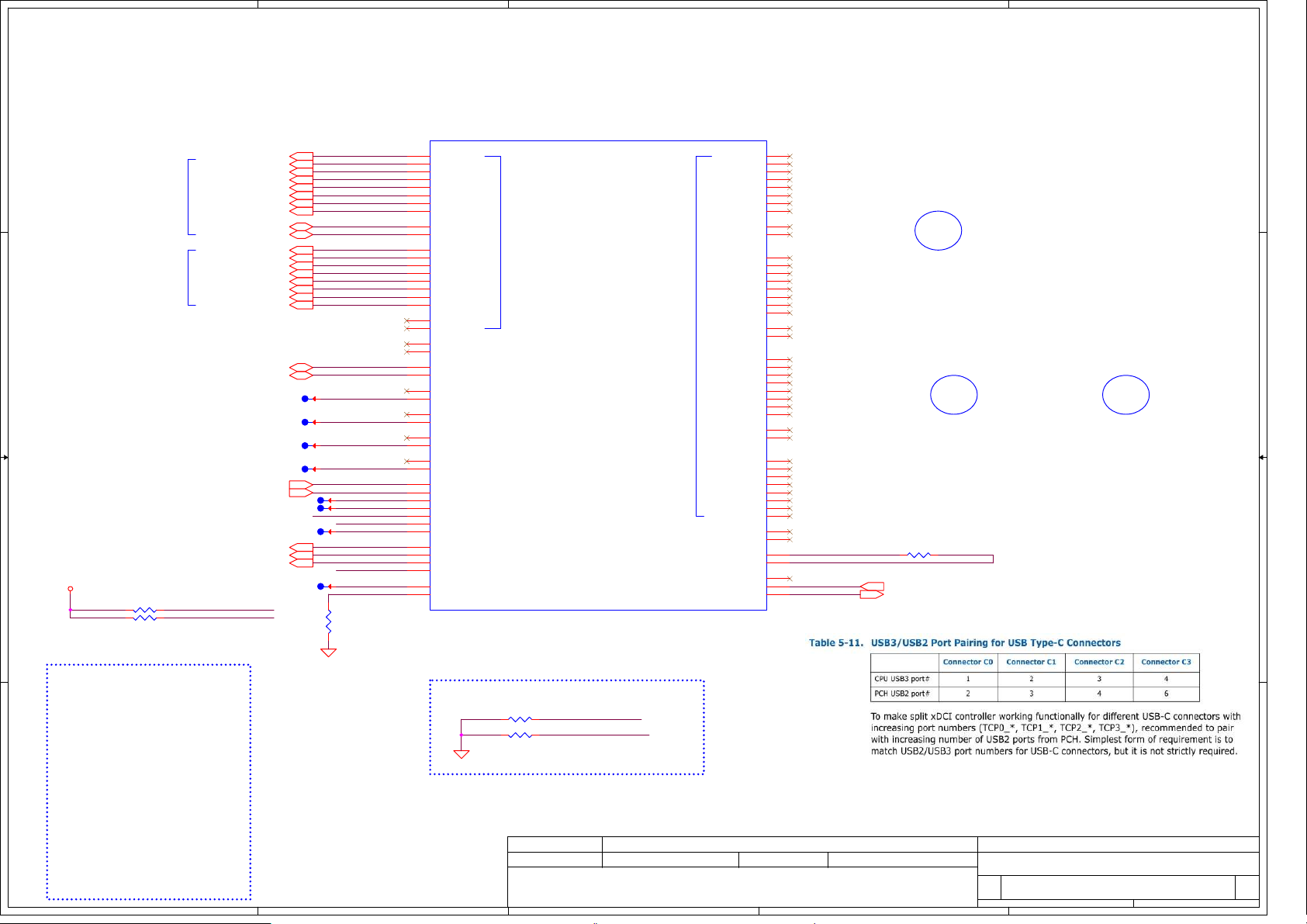

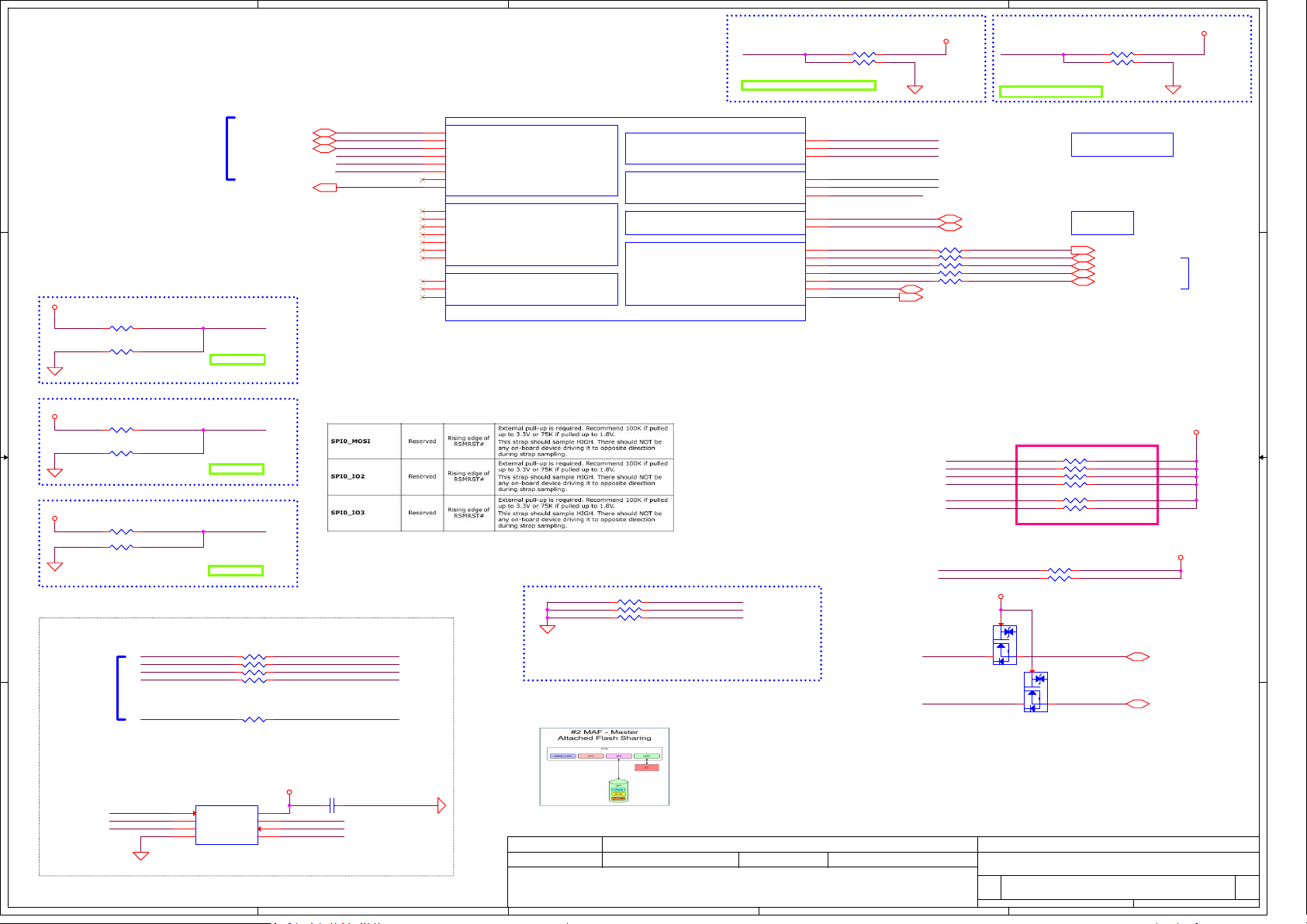

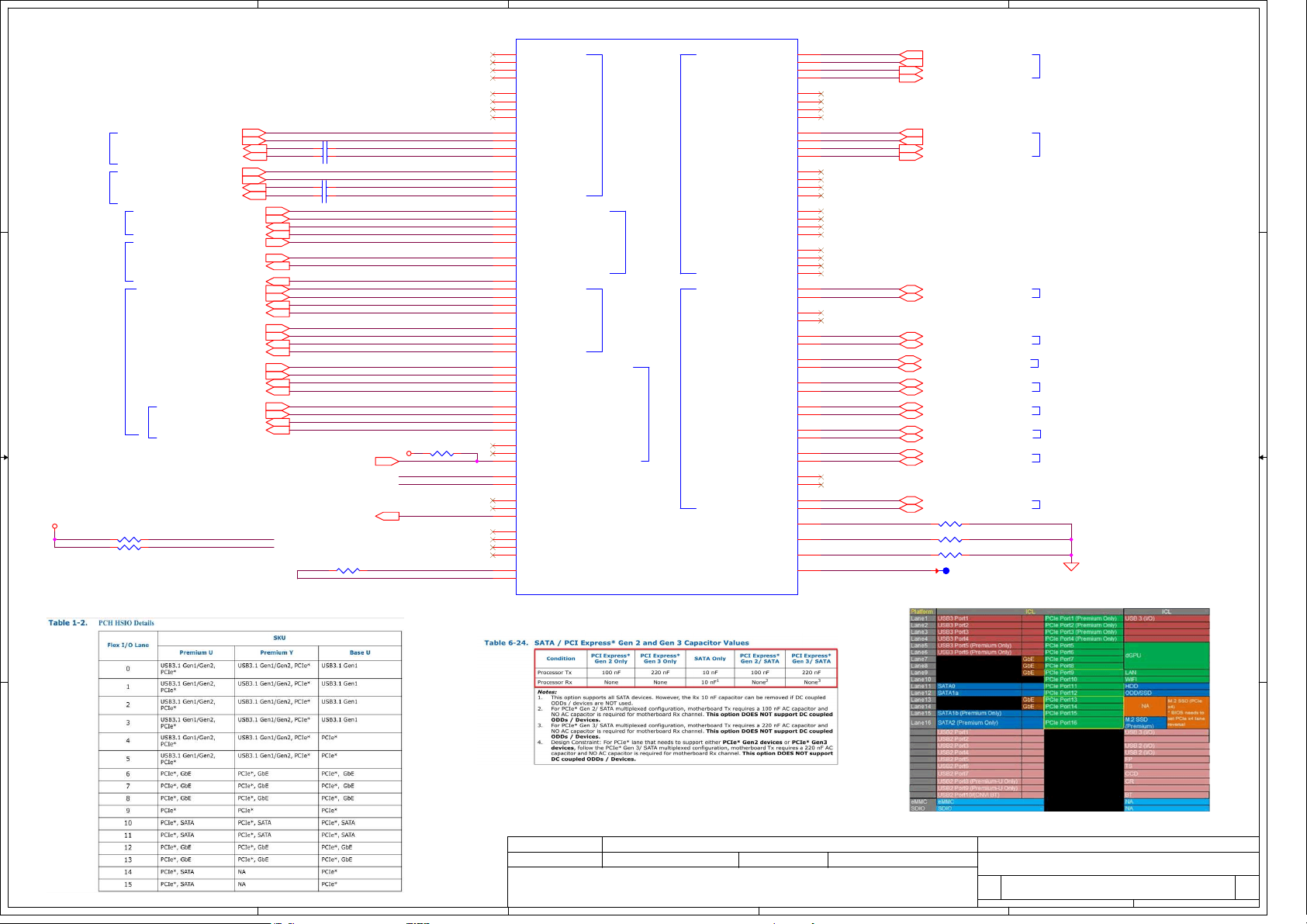

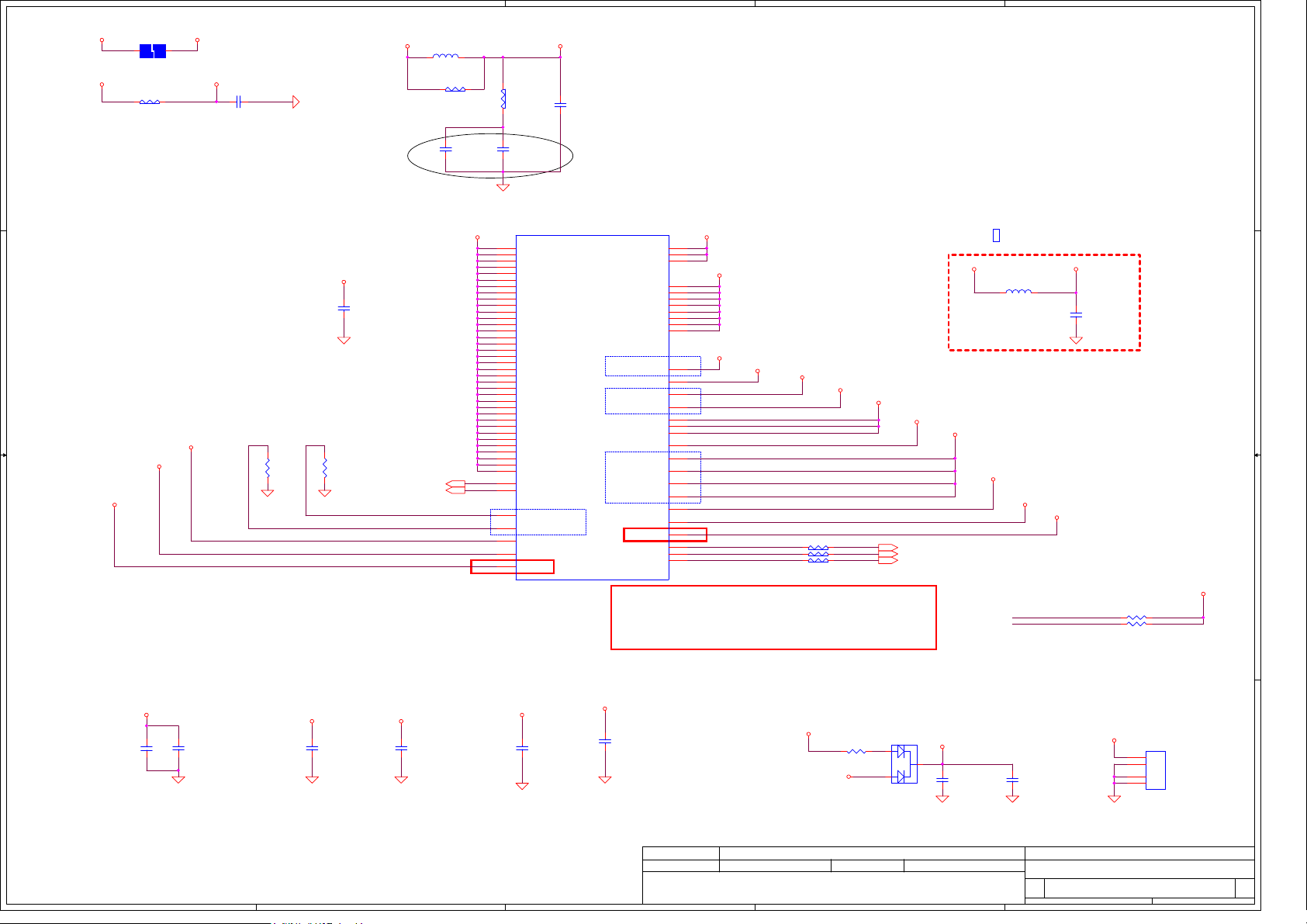

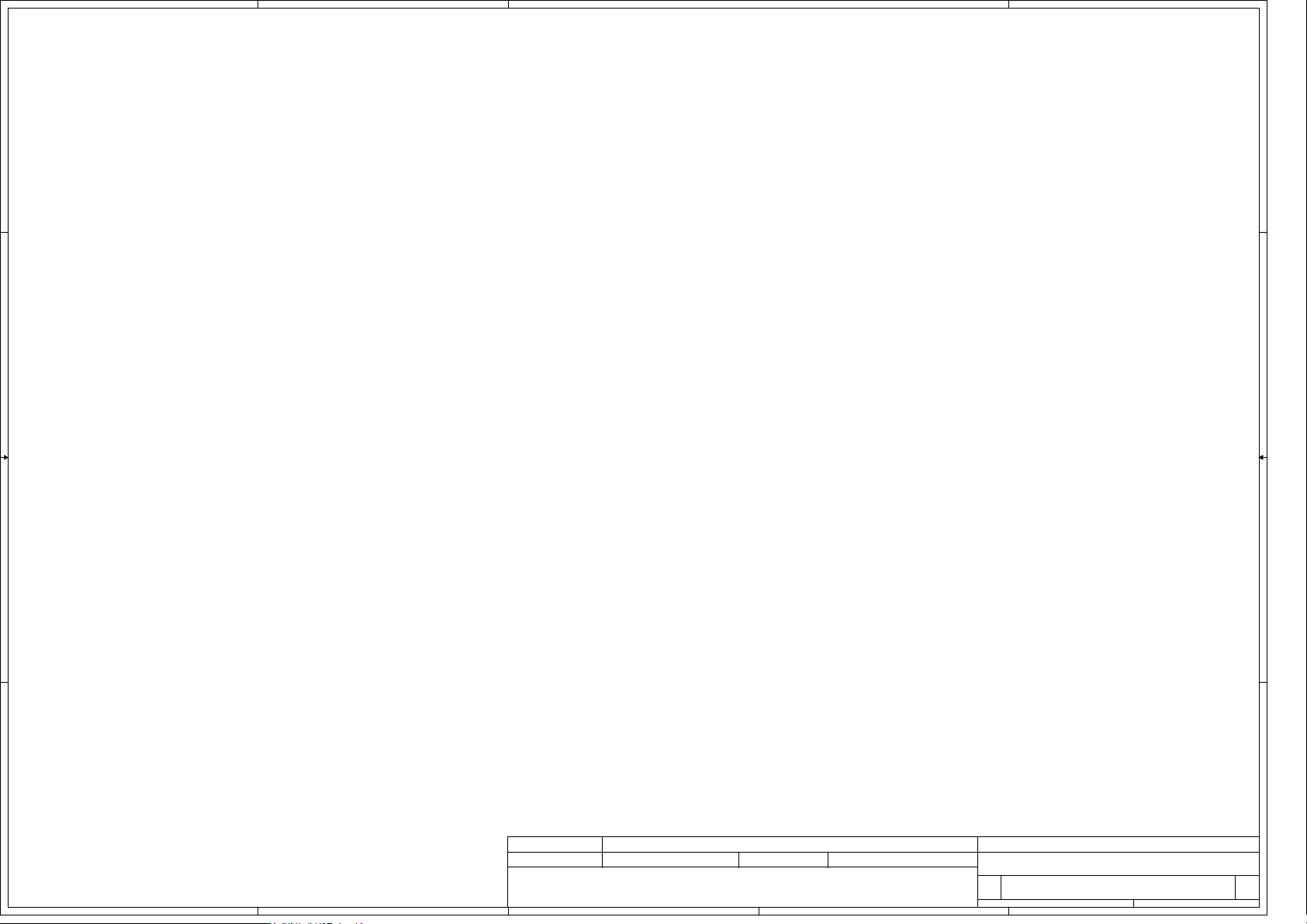

HDMI Conn.

eDP

Interleaved Memory

DDR4-ON BOARD 4G 8Gbx16

page 40

1 1

DDI2

HDMI x 4 lanes

page 38

eDP

DDI

Intel Ice Lake U

Memory BUS

Dual Channel

1.2V DDR4 2666/3200

USB 3.0

conn x1

USB3 port 1

USB2 port 1

260pin DDR4-SO-DIMM X1

USB 2.0

conn x2

USB2 port3 (MB)

USB2 port4(SUB)

CMOS

Camera

USB2 port 7

page 24

page 23

Processor

page 68

2 2

6.0 Gb/s

(SATA2)

SATA Gen 3

NGFF

WLAN

USB2 port 10

PCIe 1.0

2.5GT/s

port 10support CNVi

page 52

PCIe 1.0

2.5GT/s

port 9

LAN(GbE)

Realtek 8111H

page 51

PCIE 3.0 x4

8GT/s

Port 13-16

SATA Gen 3

6.0 Gb/s

port 0

(

SATA0)

SATA HDD

Conn.

Flexible IO

SATA Gen 1

1.5. Gb/s

port 1

(SATA1A)

SATA ODD

Conn.

ICL-U 4+2

Ice Lake PCH-LP

50x25 mm

15W

1526pin BGA

page 06~19

USBx8

HD Audio

SPI

page 72 page 38

48MHz

3.3V 24MHz

page 71

HDA Codec

ALC255

page 56

Card Reader

RTS5140

Reserved

USB2 port 8(SUB)

Touch

Screen

USB2 port 6

page 38

Finger

Printer

USB2 port 5

RJ45 conn.

3 3

page 67

eSPI BUS

CLK=24MHz

SPI ROM

128Mb

page 9

ENE

KB9052

RTC CKT.

page 11

Fan Control

page 77

Int.KBD

Power On/Off CKT.

page 63

4 4

DC/DC Interface CKT.

page 78

Power Circuit DC/DC

page 81~100

A

Sub Board

LS-H781P

IO/B

page 73

LS-H783P

LID/B

page 63

page 63

B

page 58

Touch Pad

PS2 (from EC) / I2C (from SOC)

USB2 port 8 (FP)

page 63

Security Class ification

Security Class ification

Security Class ification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2018/12/ 27 2019/12/ 27

2018/12/ 27 2019/12/ 27

2018/12/ 27 2019/12/ 27

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Int. Speaker UAJ

page 56

D

Int. DMIC

on Camera

page 38

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

FH5LI M/B LA-H801P

FH5LI M/B LA-H801P

FH5LI M/B LA-H801P

page 56

1.0

1.0

1.0

2 102Tuesday, October 15 , 2019

2 102Tuesday, October 15 , 2019

2 102Tuesday, October 15 , 2019

E

A

Vinafix.com

B

C

D

E

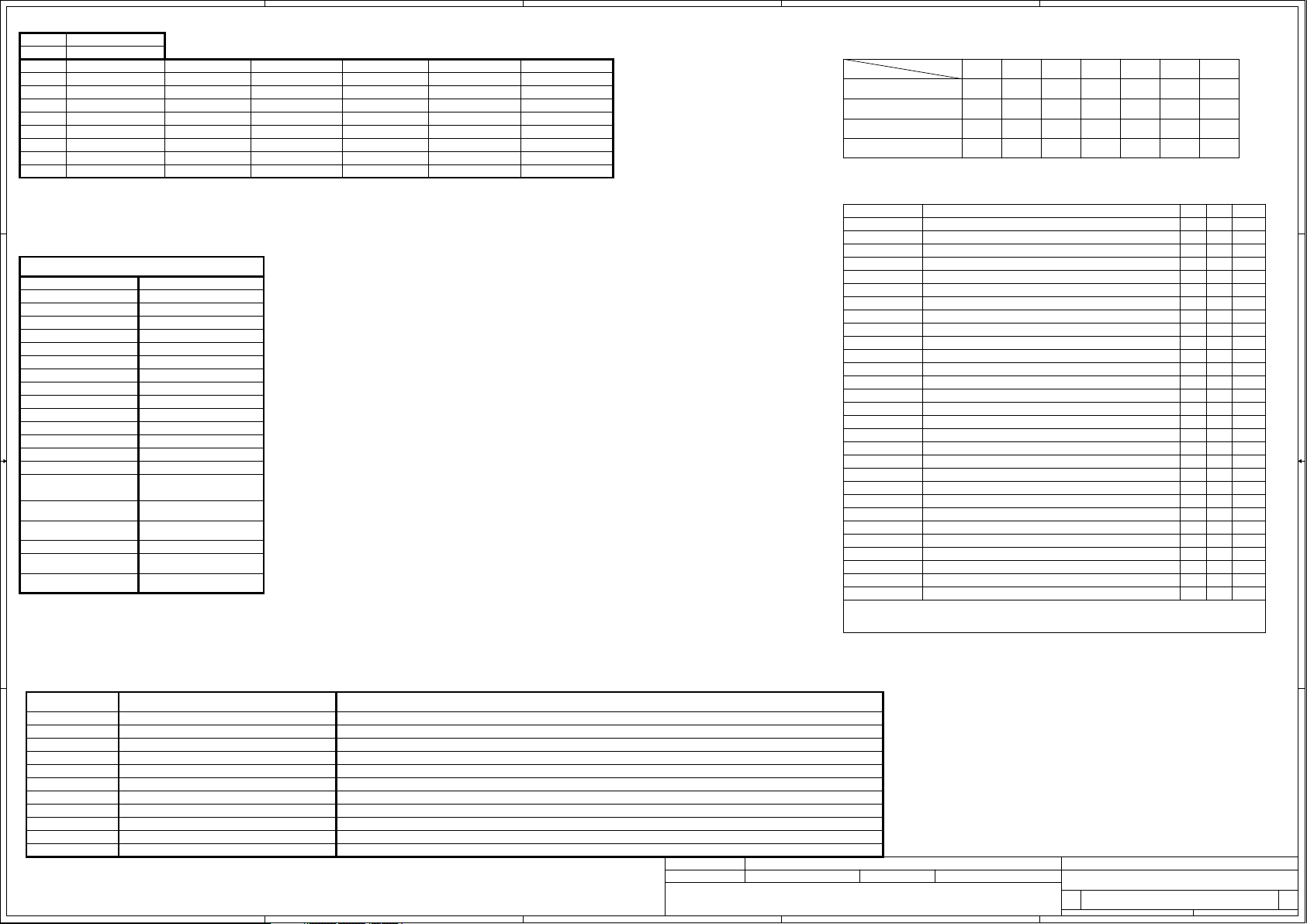

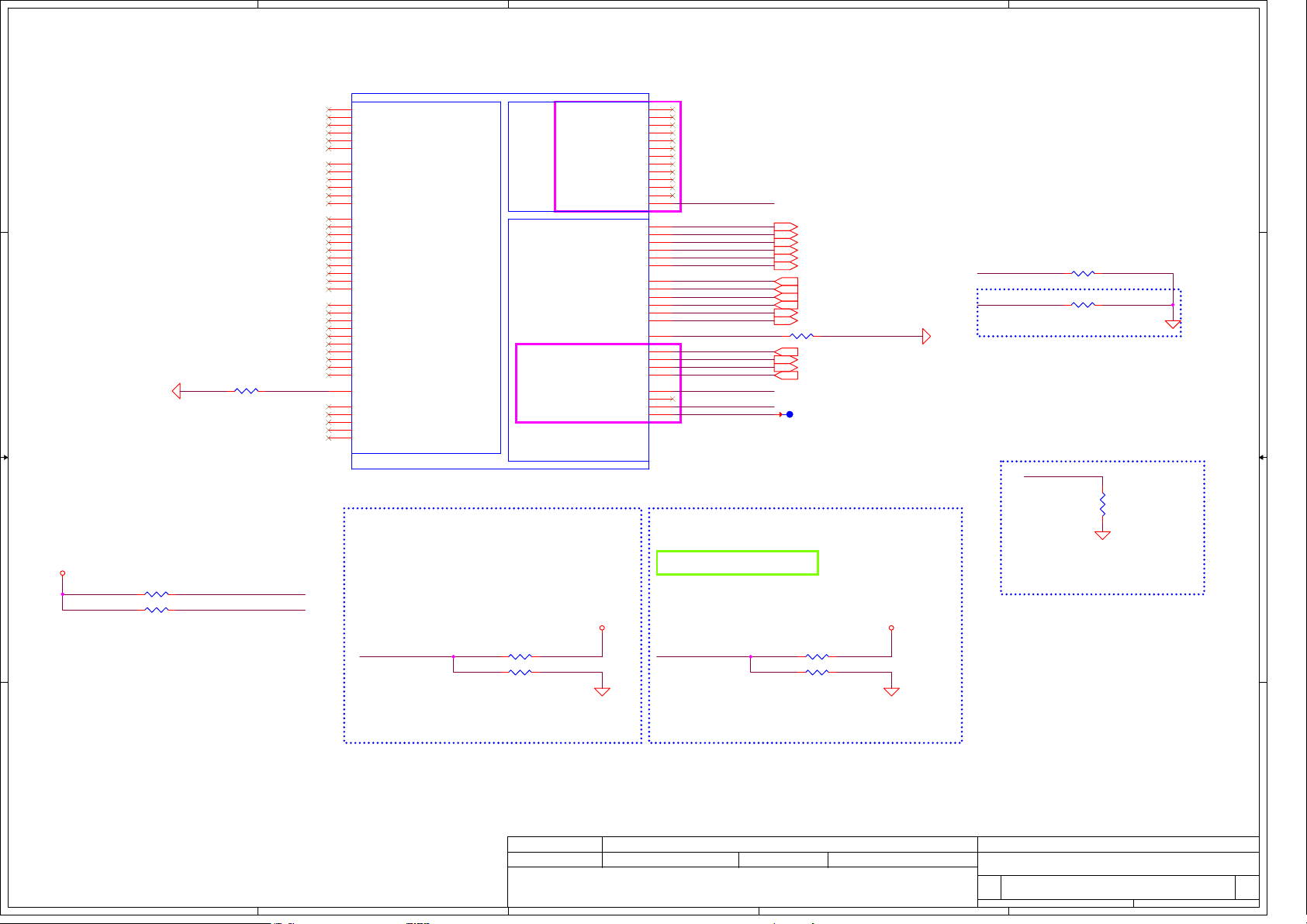

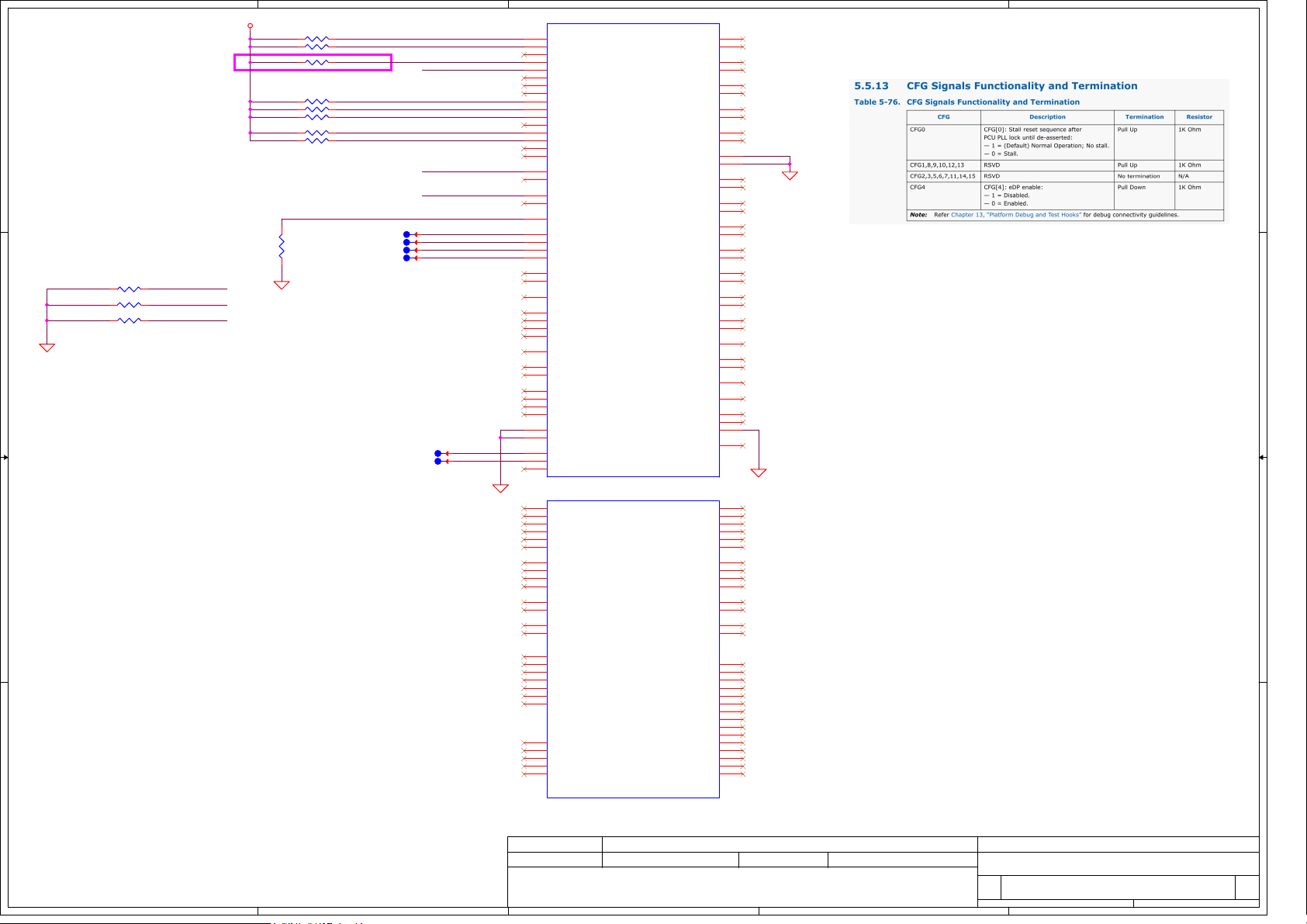

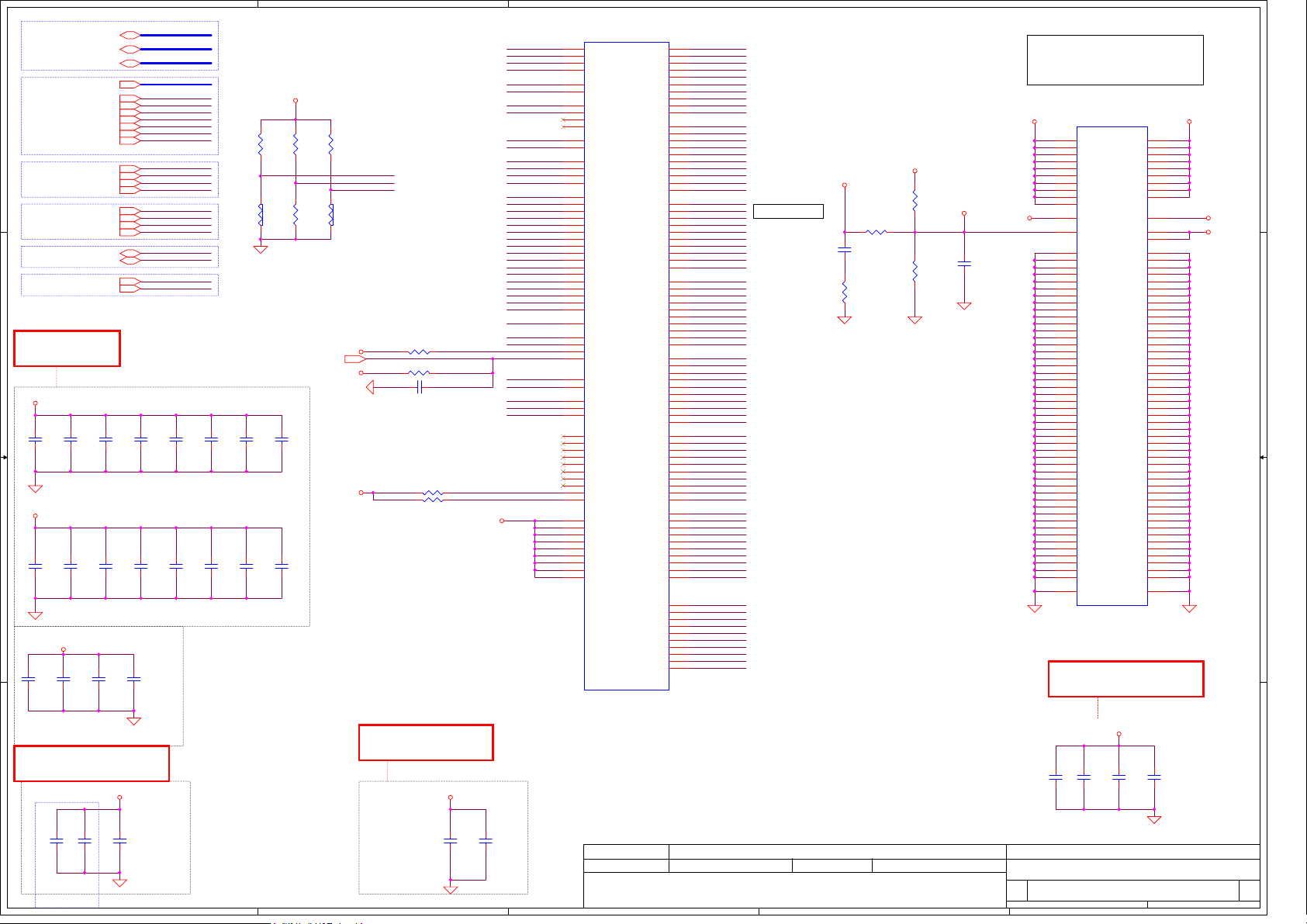

Board ID Table for AD channel

Vcc 3.3V +/- 5%

Board ID

1 1

100K +/- 1%Ra

0

1

2

3

4

5

6

7

0 0 V

12K +/- 1% 0.347 V 0.345 V 0.360 V

15K +/- 1%

20K +/- 1%

27K +/- 1%

33K +/- 1%

43K +/- 1%

56K +/- 1%

Rb V min

BID

0.423 V 0.430 V 0.438 V

V typ

BID

0 V 0.300 V

V

BID

max

EC AD3

0x00 - 0x13

0x14 - 0x1E

0x1F - 0x25

PCB Revision

0.1(EVT)

1.0(PVT)

1.0(MP)

0x26 - 0x300.541 V 0.550 V 0.559 V

0x31 - 0x3A0.691 V 0.702 V 0.713 V

0x3B - 0x450.807 V 0.819 V 0.831 V

0x46 - 0x540.978 V 0.992 V 1.006 V

0x55 - 0x641.169 V 1.185 V 1.200 V

Power State

STATE

S0 (Full ON) ON ON ON ONHIGH HIGH HIGH

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SIGNAL

SLP_S3# SLP_S4# SLP_S5# +VALW +V +VS Clock

LOW HIGH

LOWLOW

HIGH

HIGH

ONONON

ON

OFF

OFFLOW LOW LOW

OFF

OFF

OFF

OFF

OFF

OFF

Voltage Rails

Power Plane Description

+19V_VIN

BOM Structure Table

BOM Option Table

Item BOM Structure

Unpop @

G Sensor GSEN@

2 2

For Intel CMC

CNVi CNVI@

EMI/ESD requirement EMC@ / XEMC@

BOM select 15@

TPM TPM@

Finger Print

SATA/ODD select

MD BOM Select

CONN@Connector

255@/256@CODEC

3S@For over 3 cell battery

CMC@

@RF@RF requirement

FP@/FPEMC@

FP3V@/FP5V@Finger print power

RD@/NRD@/ODD@

NOX76@/X76DSAM@/

X76DMIC@/X76DHYN@/

+12.6V_BATT Battery power supply N/A

+19VB

+VCCIN

+VCCIN_AUX CPU and PCH merged auxiliary power rail

+0.6VS_VTT DDR +0.6VS power rail for DDR terminator .

+1.05VO_OUT_FET FIVR output of PCH to platform 1.05V Power Gates ON

+1.05V_VCCST Sustain voltage for CPU standby modes ON

+1.05VS_VCCSTG Gated sustain voltage for CPU standby modes ON

+1.2V_VDDQ

+1.8VALW_PRIM +1.8V Always power rail

+1.8VS System +1.8V power rail ON

+3VLP +19VB to +3VLP power rail for suspend power ON

+3VALW System +3VALW always on power rail ON

+3VS ONSystem +3V power rail

+5VALW ON

+5VS System +5V power rail

+RTCVCC RTC Battery Power ON

Adapter power supply

AC or battery power rail for power circuit.

Core voltage for CPU

DDR4 +1.2V Power Rail

1.2V power rail for CPU digital PLL+1.2V_VCCPLL_OC

+3VALW power for PCH suspend rails+3VALW_PRIM

+5V Always power rail

Memory related SPD@/DDP@/MEM@

MB Stage EVT@/DVT@/PVT@/MP@

Premium/Volume PREM@/VOL@

CPU i3@/i5@

3 3

DAZ PCB@

S0

N/A

N/A

ON

ON

ON

ON

ON

ON

ON

S3

S4/S5

N/AN/A

N/A N/A

N/AN/A

OFF OFF

OFF

OFF

OFFOFF

ON

OFF

OFFON

OFF/ON OFF

OFF

ON

ON OFF

ON

ON*1

OFF

OFF

ON

ON

ON

ON*1

ON ON*1ON

OFF

OFF

ON

ON

OFFOFF

ON ON

Note : ON*1 means power plane is ON only when WOL enable and RTC wake at BIOS setting, otherwise it is OFF.

ON*2 power plane is ON when DGPU turn on

43 level BOM table

431ALBBOL01

431ALBBOL02

4 4

SMT MB AJ801 FH 5LI I31005D1 H DMI

SMT MB AJ801 FH 5LI I51035D1 H DMI

A

BOM Structure43 Level Description

255@/3S@/MEM@/15@/VOL@/CNVI@/CMC@/SDP@/MP@/FP@/FP3V@/i3@/NRD@/PCB@

255@/3S@/MEM@/15@/VOL@/CNVI@/CMC@/SDP@/MP@/FP@/FP3V@/i5@/NRD@/PCB@

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Compal Secret Data

Compal Secret Data

2018/12/27 2019/12/27

2018/12/27 2019/12/27

2018/12/27 2019/12/27

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Notes List

Notes List

Notes List

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

FH5LI M/B LA-H801P

FH5LI M/B LA-H801P

FH5LI M/B LA-H801P

Date: Sheet of

Date: Sheet of

Date: Sheet of

E

3 102Tuesday, October 15, 2019

3 102Tuesday, October 15, 2019

3 102Tuesday, October 15, 2019

1.0

1.0

1.0

A

Vinafix.com

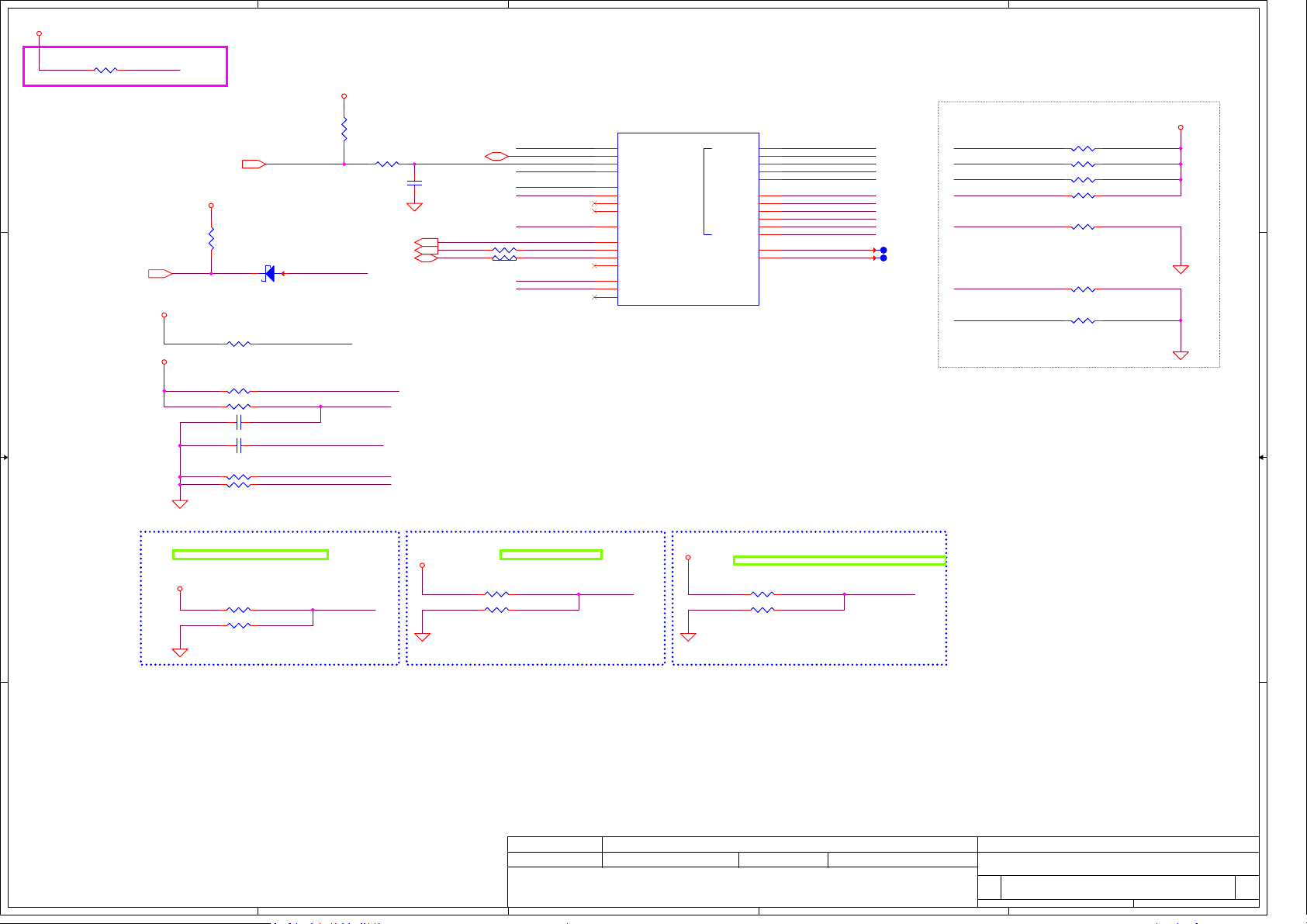

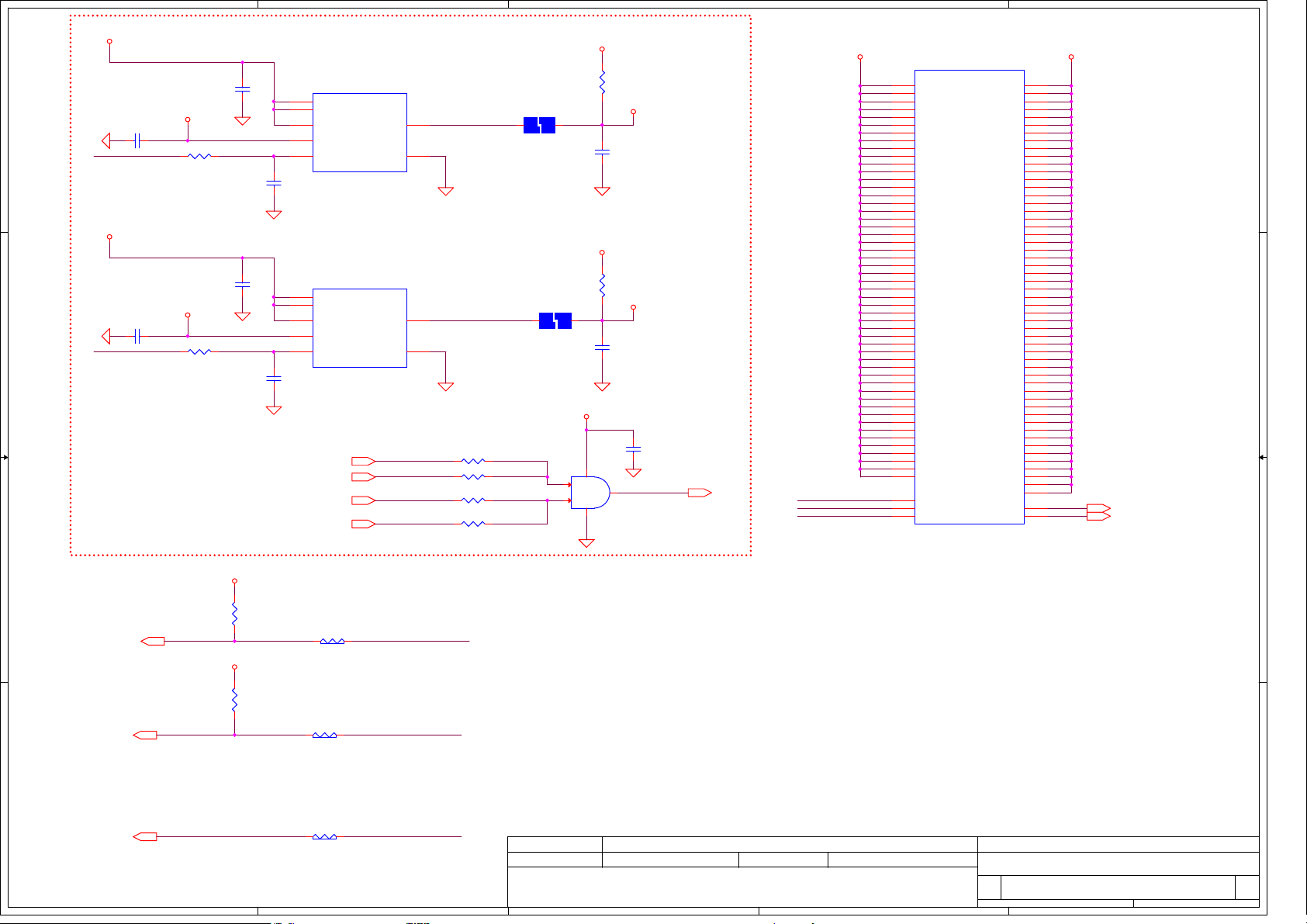

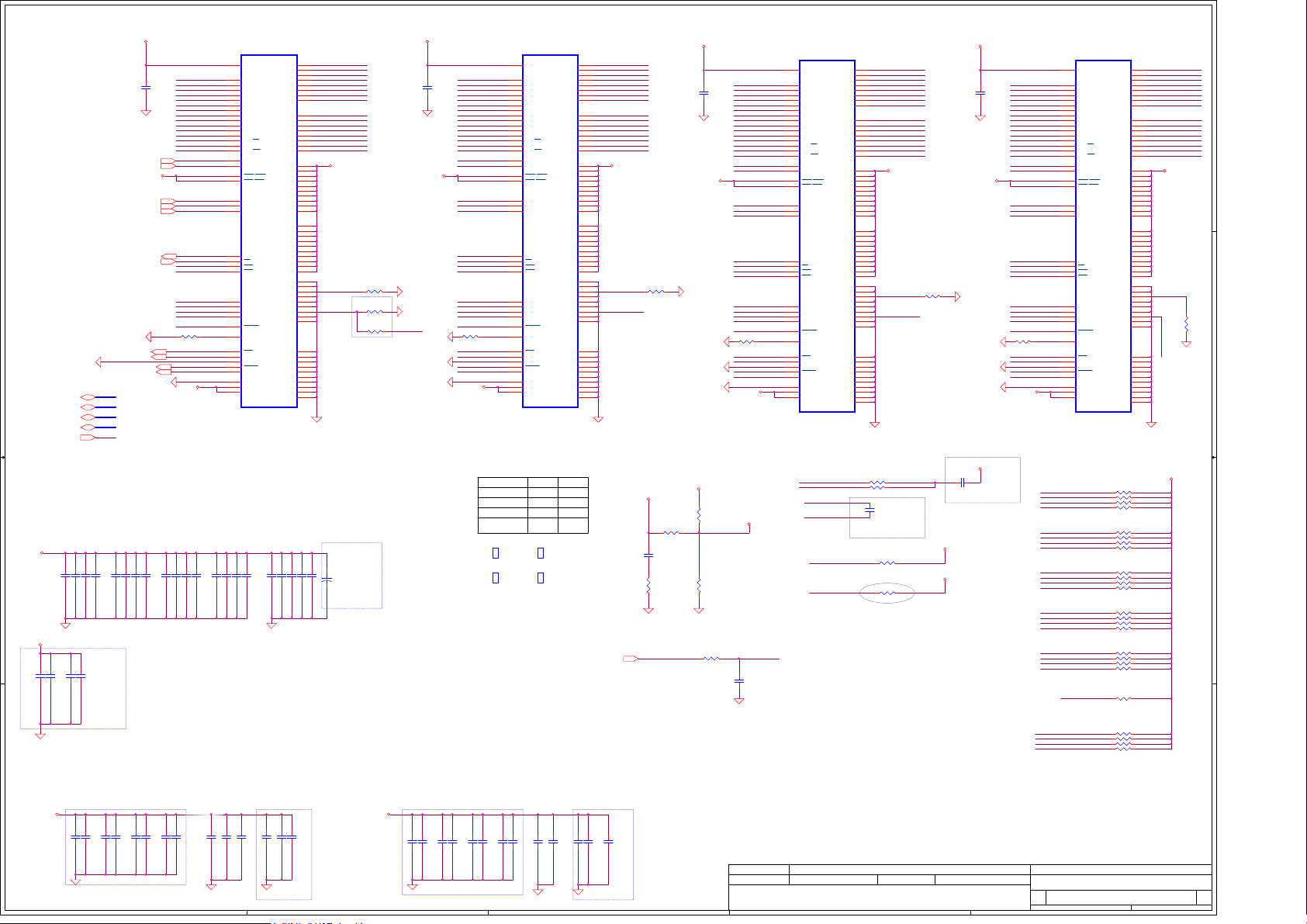

VR_ON

JUMP

(PJZ1)

JUMP

(PJG1)

ADAPTER

1 1

BATTERY

CHARGER

(PU301)

LDO

+3VLP

+19VB

SYSON

SM_PG_CTRL

EC_ON

RT8207PGQW

(PUM1)

SY8288CRAC

(PU501)

1.8VALW_PG

RT3612EBGQW

(PUZ1)

RT6543AGQW

(PUG1)

+1.2VP

+0.6VSP

+5VALWP

JUMP

(PJ501)

JUMP

(PJM3)

JUMP

(PJM4)

+5VALW

+VCCIN

+VCCIN_AUX

+1.2V_VDDQ

+0.6VS_VTT

SUSP#

USB_EN

B

AOZ1331DI

(UQ1)

JLID1

(LID/B)

JIO1

(IO/B)

EM5201V

(UC11)

SY6288C20AAC

(US21)

+1.2V_VCCPLL_OC_P

+5VS_OUT

+USB3_VCCB

PREM@

VOL@

R-Short

(RC3970)

JUMP

(JPQ2)

JUMP

(JPC10)

+5VS

JUMP

(JPC6)

C

+USB3_VCCA

+1.2V_VCCPLL_OC

KBL_EN

R-Short

(RX8)

AP2330W

(UY1)

0 ohm

(RO3)

0 ohm

(RO26)

JUMP

(JPA1)

R-Short

(RF1)

SY6288C20AAC

(U1)

+TS_PWR

+HDMI_5V_OUT

+5VS_HDD

+5VS_ODD

+VDDA

+VCC_FAN1

+5VS_BL

D

E

SY8286BRAC

3V_EN

(PU301)

2 2

3 3

ICL-U FIVR

(UC1)

JUMP

(PJ301)

+1.05VO_OUT_FET

(BY2,CB2,CC1)

+3VALW+3VALWP

VCCST_EN_LS

VCCSTG_EN_LS

SYSON

LAN_PWR_EN

TP_PWR_EN

WLAN_ON

FP_PWR_EN

SUSP#

EN_1.8VALW

EM5201V

(UC9)

G2898KD1U

(UC14)

R-Short

(RC173)

JUMP

(JPC7)

G9661MF11U

(PUM2)

SY6288C20AAC

(UL1)

SY6288C20AAC

(UK1)

SY6288C20AAC

(UM1)

SY6288C20AAC

(UK6)FP@

R-Short

(RW1)

AOZ1331DI

(UQ2)

SY8032ABC

(PU1801)

+3VALW_DSW

+3VALW_PRIM

+2.5VP

+3V_LAN

+3V_PTP

+3VS_WLAN

+FP_VCC

+3VALW_TPM

+3VS_OUT

PREM@

+1.05V_VCCST_SINGLE

VOL@

+1.05V_VCCST_DUAL

+1.8VALWP

0Ohm

(RC3989)

0Ohm

(RC3981)

JUMP

(JPQ1)

JUMP

(JPC16)

PREM@

R-Short

(LC2)

R-Short

(RC154)

+3VS

JUMP

(PJ1802)

+1.05V_VCCST

0Ohm

(RC414)

+1.05V_VCCST_P

0Ohm

(RC413)

+1.05VS_VCCSTG

+3VALW_HDA

+3VALW_SPI

+1.8VALW_PRIM

SUSP#

G2898KD1U

(UC14)

EM5201V

(UC12)

SOC_ENVDD

0 ohm

(RK3)@

0 ohm

(RM9)

R-Short

(RW2)@

R-Short

(RA2)

R-Short

(RA5)

JEDP1

(CAMERA)

JMIC1

(4DMIC)

+1.8V_PRIM_SOC_P

+1.8VS

SY6288C20AAC

(UX1)

+3V_PTP

+3VS_SSD_NGFF

+3VS_TPM

+3VS_DVDDIO

+3VS_DVDD

VOL@

R-Short

(RC407)

PREM@

R-Short

(RA6)

+LCDVDD

JUMP

(JPC5)

+1.8VS_VDDA

+1.8V_PRIM_SOC

4 4

HCB2012KF

(LX1) 3S@

A

+INVPWR_B+

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

C

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

D

Compal Secret Data

Compal Secret Data

Compal Secret Data

2018/12/27 2019/12/27

2018/12/27 2019/12/27

2018/12/27 2019/12/27

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Power Rail

Power Rail

Power Rail

Size Document Numb er Rev

Size Document Numb er Rev

Size Document Numb er Rev

Custom

Custom

Custom

FH5LI M/B LA -H801P

FH5LI M/B LA -H801P

FH5LI M/B LA -H801P

Date: Sheet of

Date: Sheet of

Date: Sheet of

E

4 102T uesday, Oc tober 15, 2 019

4 102T uesday, Oc tober 15, 2 019

4 102T uesday, Oc tober 15, 2 019

1.0

1.0

1.0

5

Vinafix.com

4

3

2

1

D D

C C

B B

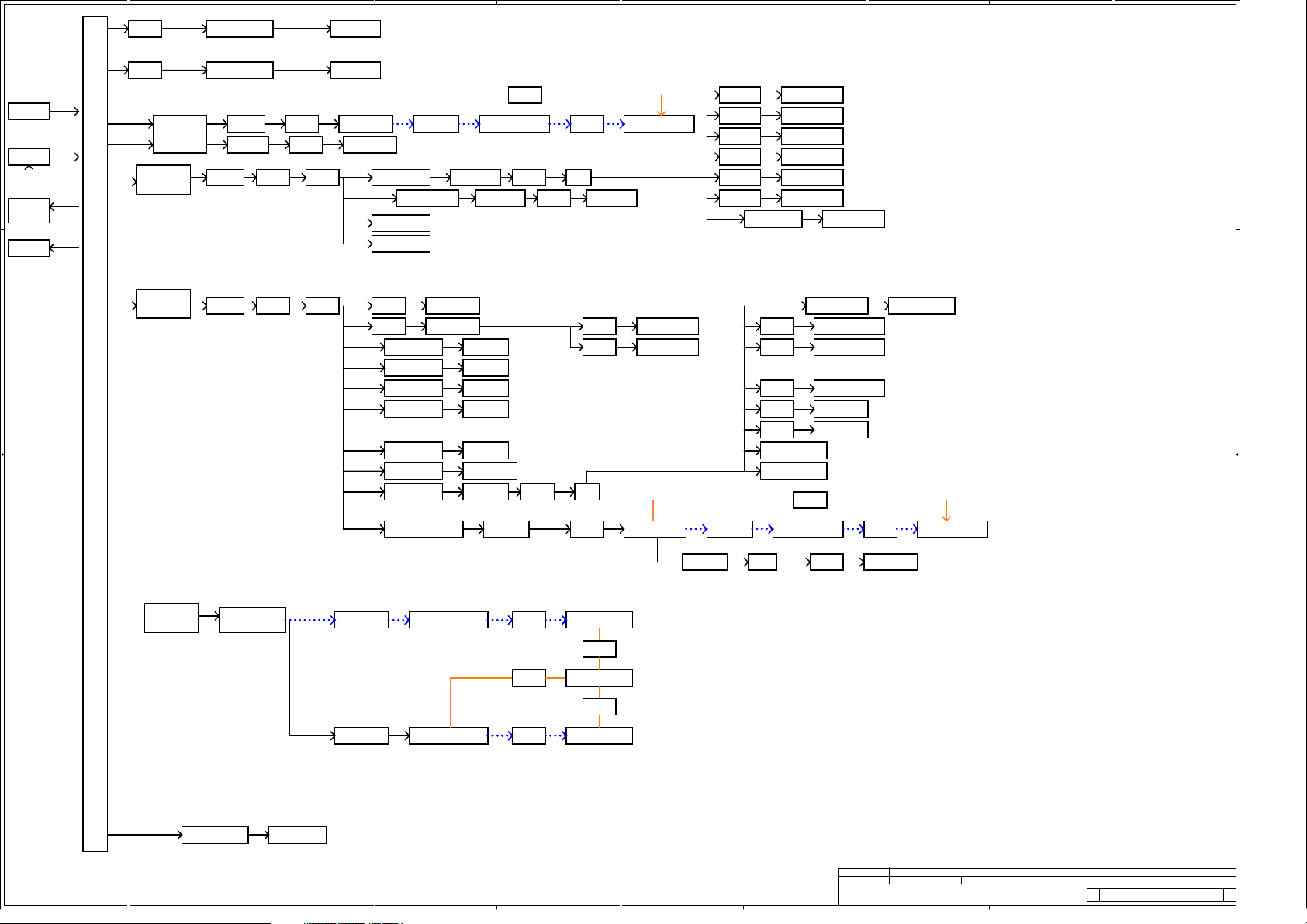

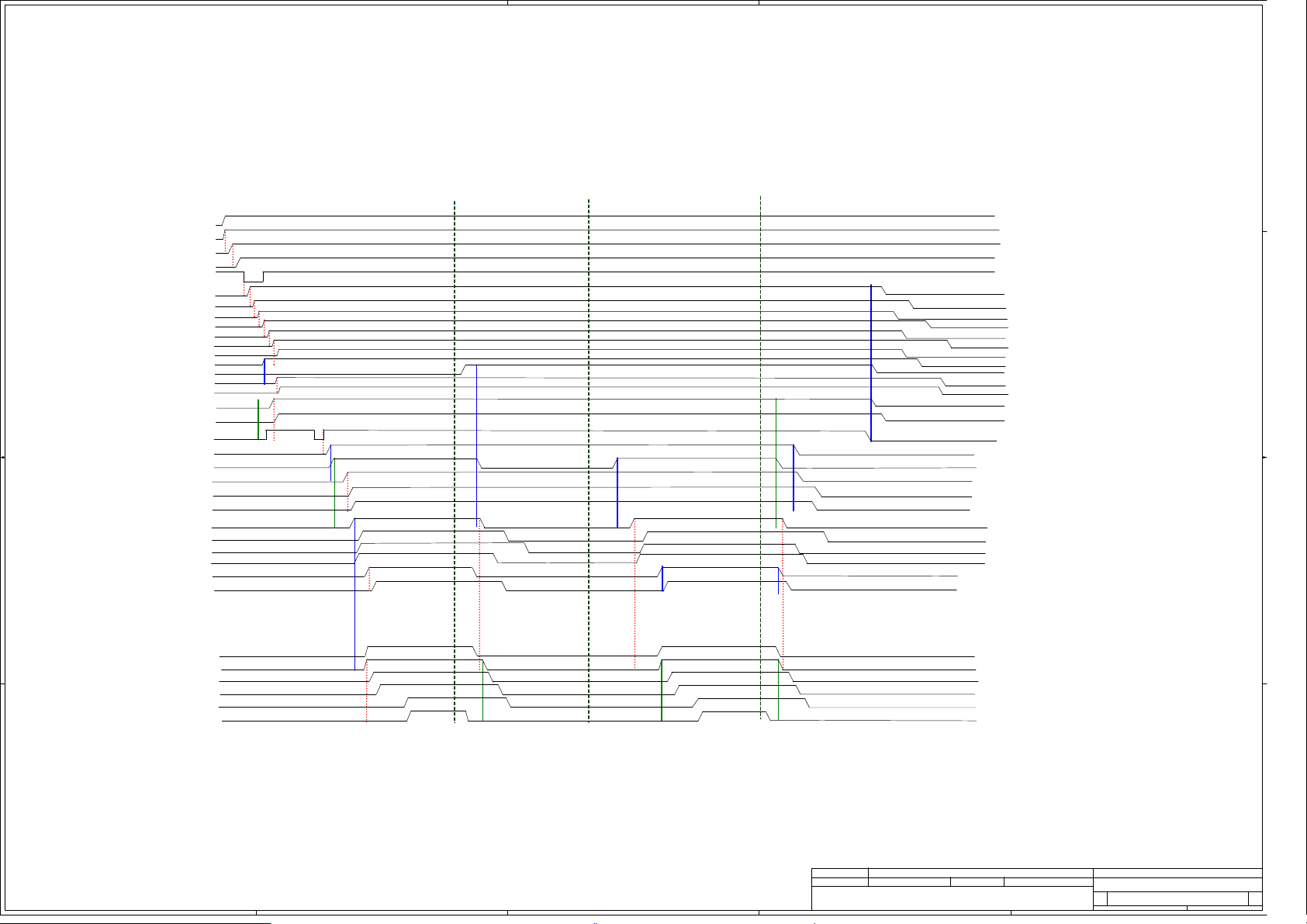

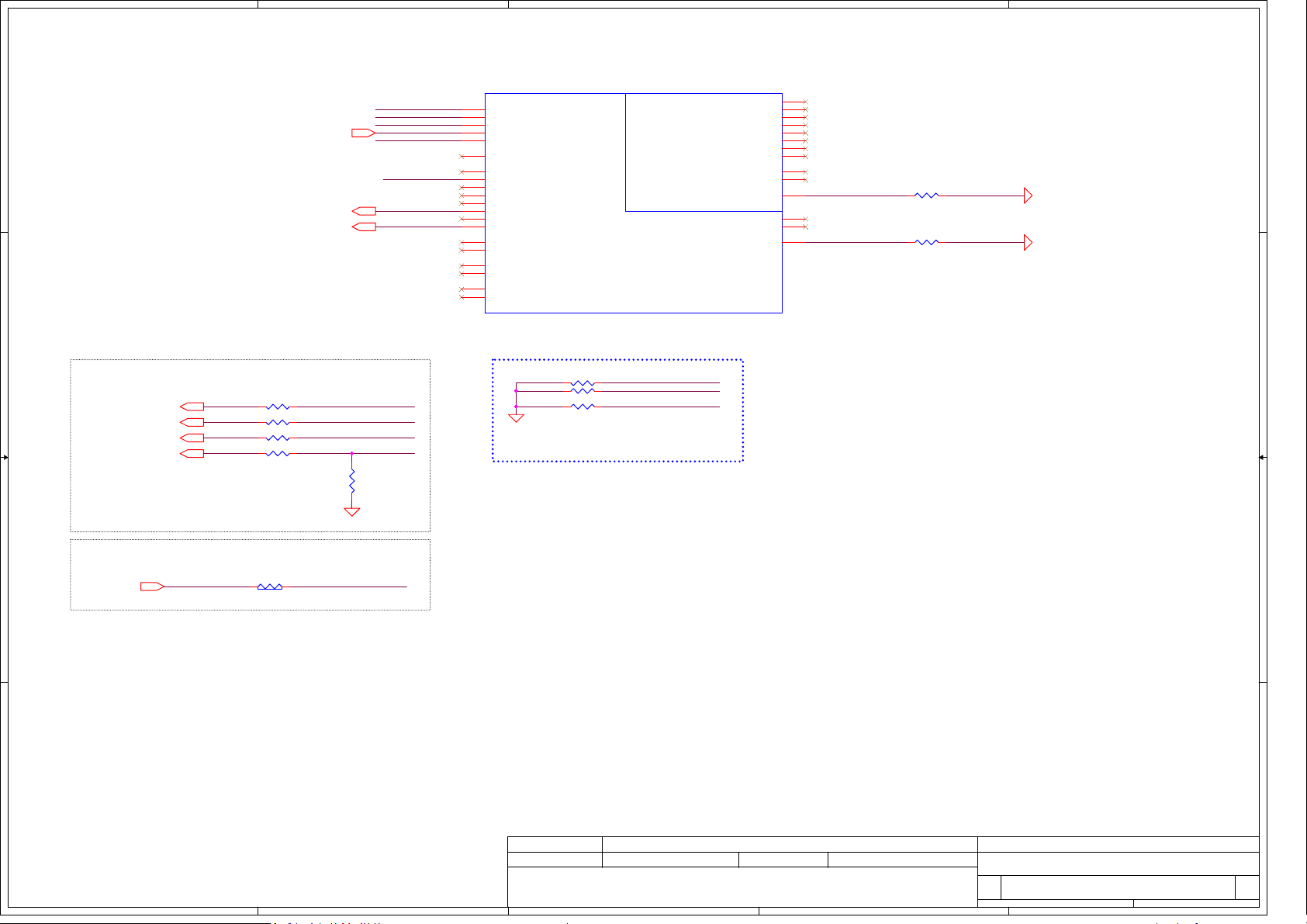

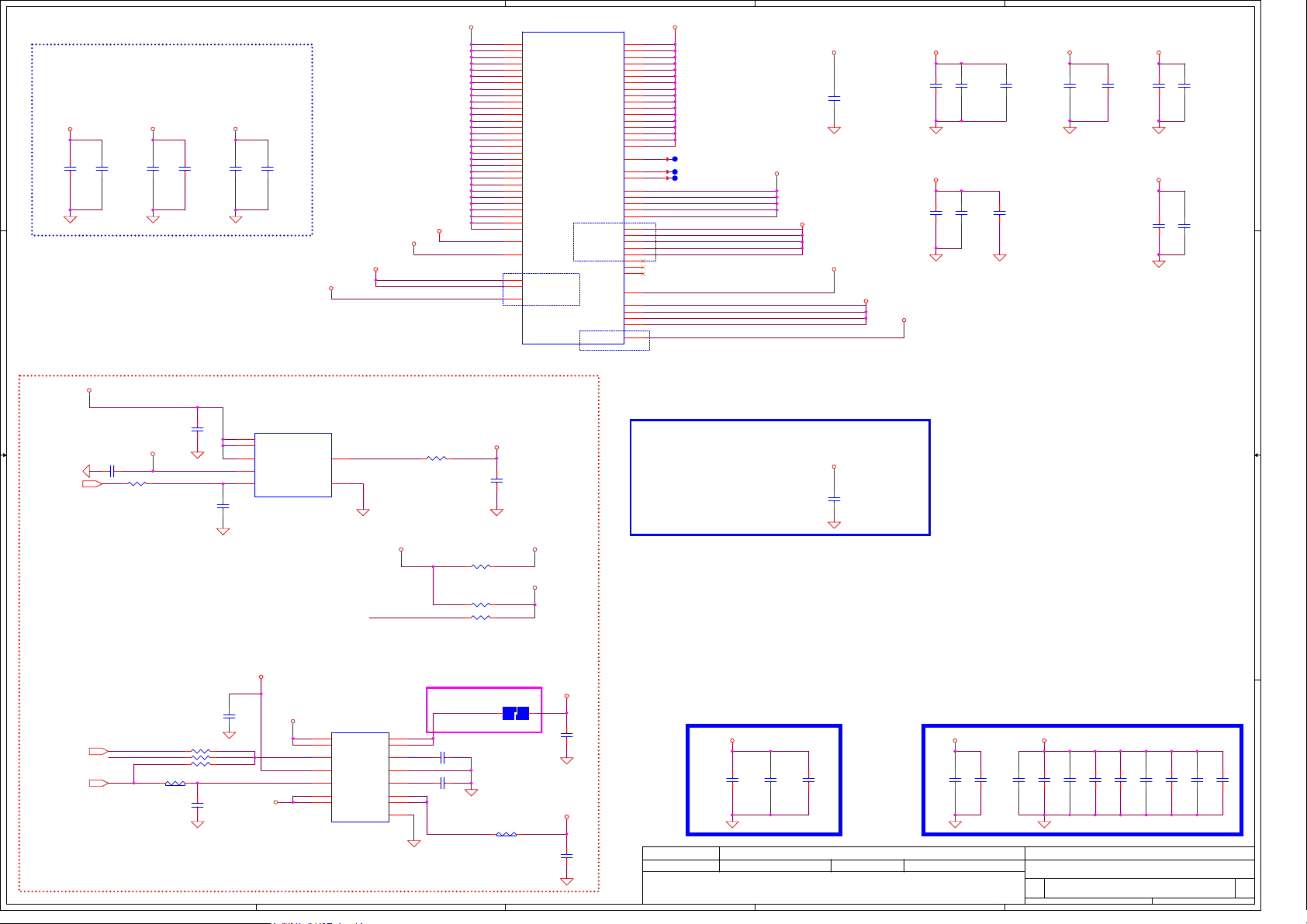

FH5LI_EVT Power Sequence

BIOS ver: V0.01T015

EC: ver: V0.01T08B

Plug in

+19VB

+3VLP

→

EC_ON

+5VALW

ON/OFFBTN#

3V_EN

+3VALW

SPOK_3V

+1.8VALW_PRIM

1.8VALW_PG

+VCCIN_AUX

VCC_AUX_PWRGD

VCCIN_AUX_CORE_VID

VCCST_OVERRIDE_LS VCCST_OVERRIDE_LS

EC_VCCST_EN

+1.05V_VCCST

EC_RSMRST#

(DSW_PWROK)

AC_PRESENT

PBTN_OUT#

SLP_S4#

SLP_S3#

SYSON

+1.2V_VDDQ

+2.5V_VPP

USP#

S

+5VS

+3VS

+1.8VS

SM_PG_CTRL

+0.6VS_VTT

209.9us

→

2.144ms

★

→

98.52ms

→

567.3us

→

702.5us

→

644.6us

→

279.6us

→

779.9us

→

314.7us

2.383ms

→

→

4.565ms

→

4.261ms

★

→

31.4ms

→

10.09ms

→

121.1ms

11.52ms

AC mode

Power On

←→

→

20ms

→

23.76ms

6.44ms

→

→

515.9us

→

1.25ms

→

28.04ms

→

→

→

S3

S3 Resume

Power Off

+19VB

+3VLP

EC_ON

+5VALW

ON/OFFBTN#

→

19.97us

683us

→

→

38.59us

→

1.118ms

→

43.75us

→

43.89us

13.7ms

811us

→

→

4.906ms

→

4.223ms

814.3us

→

→

121.1us

→

3.463us

→

1.006ms

→

922.5us

25.83ms

→ 7.833us

→

1.56ms

1.18ms

741us

→

20.21ms

→

4.897us

2.588ms

→

8.698ms

→

600.9us

→

4.599us

693.9us

→

→

→

1.563ms

→

1.170ms

→

763.3us

→

20.19ms

→

5.291us

9.894us

→

→

→

4.841us

→

392.9us

2.163ms

→

402.6us

923us

→

→

→

3.976us

9.59s

→

→

10.99us

9.301us

→

3V_EN

+3VALW

SPOK_3V

+1.8VALW_PRIM

1.8VALW_PG

+VCCIN_AUX

EC_VCCST_EN

+1.05V_VCCST

EC_RSMRST#

(DSW_PWROK)

AC_PRESENT

PBTN_OUT#

SLP_S4#

SLP_S3#

SYSON

+1.2V_VDDQ

+2.5V_VPP

SUSP#

+1.8VS

SM_PG_CTRL

+0.6VS_VTT

+5VS

+3VS

6.098us

→

EC_VCCST_PG_R

VR_ON

+

VCCIN

PCH_PWROK

SYSPWROK

PLT_RST#

A A

5

20.26ms

→

20.28ms

→

1.964ms

9.98ms

→

120.5ms

→

122ms

→

4

→

4.772us

→

1.742us

32.3us

→

174.3us

→

182.2us

→

319.3us

→

→

20.16ms

20.18ms

→

1.966ms

→

9.940ms

→

120.9ms

→

124.7ms

→

3

→

2.198us

→

105.7us

→

147.6us

→

155.5us

→

348.8us

→

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2019/07/12 2019/12/31

2019/07/12 2019/12/31

2019/07/12 2019/12/31

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

EC_VCCST_PG_R

VR_ON

+

VCCIN

CH_PWROK

P

SYSPWROK

PLT_RST#

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Power Sequence

Power Sequence

Power Sequence

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

FH5LI M/B LA-H801P

FH5LI M/B LA-H801P

FH5LI M/B LA-H801P

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

5 100Tuesday, October 15, 2019

5 100Tuesday, October 15, 2019

5 100Tuesday, October 15, 2019

1.0

1.0

1.0

A

Vinafix.com

B

C

D

E

1 1

EDP_TXN 0<38>

EDP_TXP 0<38>

EDP_TXN 1<38>

EDP_TXP 1<38>

<eDP>

<HDMI>

2 2

HDMI DDC (Port 2)

EDP_VDDEN:

100K PD on load swith side

3 3

+3VALW _PRIM

1 2

RC164 10K_040 2_5%

1 2

RC165 10K_040 2_5%

EDP_TXN 2<38>

EDP_TXP 2<38>

EDP_TXN 3<38>

EDP_TXP 3<38>

EDP_AUX N<38>

EDP_AUX P<38>

SOC_DP2 _N0<40>

SOC_DP2 _P0<40>

SOC_DP2 _N1<40>

SOC_DP2 _P1<40>

SOC_DP2 _N2<40>

SOC_DP2 _P2<40>

SOC_DP2 _N3<40>

SOC_DP2 _P3<40>

SOC_DP2 _CTRL_CLK<40>

SOC_DP2 _CTRL_DATA<40>

SOC_GPP _E19

1

TP@

CPU_EDP _HPD<38>

SOC_DP2 _HPD<40>

SOC_ENV DD<38 >

SOC_BKL _PWM<38>

USB_OC1 #

USB_OC2 #

T302

T509

T510

T511

ENBKL<58>

TP@

TP@

TP@

T512

T303

T306

T301

TP@

TP@

TP@

TP@

SOC_GPP _E21

1

SOC_GPP _D10

1

SOC_GPP _D12

1

SOC_GPP _A19

1

SOC_GPP _A20

1

USB_OC1 #

USB_OC2 #

SOC_GPP _E17

1

ENBKL

RSVD_1

DISP_UTILS

1

DISP_RCOM P

12

RC350

150_040 2_1%

UC1A

Y5

DDIA_TXN_0

Y3

DDIA_TXP_0

Y1

DDIA_TXN_1

Y2

DDIA_TXP_1

V2

DDIA_TXN_2

V1

DDIA_TXP_2

V3

DDIA_TXN_3

V5

DDIA_TXP_3

W4

DDIA_AUX_N

W3

DDIA_AUX_P

AE3

DDIB_TXN_0

AE5

DDIB_TXP_0

AE2

DDIB_TXN_1

AE1

DDIB_TXP_1

AC5

DDIB_TXN_2

AC3

DDIB_TXP_2

AC1

DDIB_TXN_3

AC2

DDIB_TXP_3

AD3

DDIB_AUX_N

AD4

DDIB_AUX_P

DP15

GPP_E22/DDPA_CTRLCLK/PCIE_LNK_DOWN

DJ17

GPP_E23/DDPA_CTRLDATA/BK4/SBK4

DL40

GPP_H16/DDPB_CTRLCLK

DP42

GPP_H17/DDPB_CTRLDATA

DL17

GPP_E18/DDP1_CTRLCLK/TBT_LSX0_TXD

DK17

GPP_E19/DDP1_CTRLDATA/TBT_LSX0_RXD

DN17

GPP_E20/DDP2_CTRLCLK/TBT_LSX1_TXD

DP17

GPP_E21/DDP2_CTRLDATA/TBT_LSX1_RXD

DK34

GPP_D9/ISH_SPI_CS_N/DDP3_CTRLCLK/GSPI2_CS0_N/TBT_LSX2_TXD

DL34

GPP_D10/ISH_SPI_CLK/DDP3_CTRLDATA/GSPI2_CLK/TBT_LSX2_RXD

DN33

GPP_D11/ISH_SPI_MISO/DDP4_CTRLCLK/GSPI2_MISO/TBT_LSX3_TXD

DL33

GPP_D12/ISH_SPI_MOSI/DDP4_CTRLDATA/GSPI2_MOSI/TBT_LSX3_RXD

DW11

GPP_E14/DPPE_HPDA/DISP_MISCA

CV42

GPP_A18/DDSP_HPDB/DISP_MISCB

CV39

GPP_A19/DDSP_HPD1/DISP_MISC1

CY43

GPP_A20/DDSP_HPD2/DISP_MISC2

CR41

GPP_A14/USB_OC1_N/DDSP_HPD3/DISP_MISC3

CT41

GPP_A15/USB_OC2_N/DDSP_HPD4/DISP_MISC4

DV14

GPP_E17

DN21

EDP_VDDEN

DL19

EDP_BKLTEN

DU19

EDP_BKLTCTL

J3

RSVD_1

D2

DISP_UTILS

R2

DISP_RCOMP

ICL-U_BGA1 526

@

DDI

1 0f 19

TBT / USB / DP

GPP_A17/DISP_MISCC

TCP0_TX_N0

TCP0_TX_P0

TCP0_TX_N1

TCP0_TX_P1

TCP0_TXRX_N0

TCP0_TXRX_P0

TCP0_TXRX_N1

TCP0_TXRX_P1

TCP0_AUX_N

TCP0_AUX_P

TCP1_TX_N0

TCP1_TX_P0

TCP1_TX_N1

TCP1_TX_P1

TCP1_TXRX_N0

TCP1_TXRX_P0

TCP1_TXRX_N1

TCP1_TXRX_P1

TCP1_AUX_N

TCP1_AUX_P

TCP2_TX_N0

TCP2_TX_P0

TCP2_TX_N1

TCP2_TX_P1

TCP2_TXRX_N0

TCP2_TXRX_P0

TCP2_TXRX_N1

TCP2_TXRX_P1

TCP2_AUX_N

TCP2_AUX_P

TCP3_TX_N0

TCP3_TX_P0

TCP3_TX_N1

TCP3_TX_P1

TCP3_TXRX_N0

TCP3_TXRX_P0

TCP3_TXRX_N1

TCP3_TXRX_P1

TCP3_AUX_N

TCP3_AUX_P

TC_RCOMP_N

TC_RCOMP_P

GPP_A21

GPP_A22

BB5

BB6

AV6

AV5

BH2

BH1

BF1

BF2

AY5

AY6

AR5

AR6

AL5

AL3

BD2

BD1

BB1

BB2

AN3

AN5

BF6

BF5

BJ5

BJ6

BL1

BL2

BM2

BM1

BG6

BG5

BP6

BP5

BV5

BV6

BR1

BR2

BT2

BT1

BT6

BT5

AY1

AY2

CT38

CV43

CV41

TC_RCOM P_N

TC_RCOM P_P

TPM_PIRQ#

TS_EN

PCB DAZ

ZZZ

PCB@ DAZ2W V00100

PCB FH5L I LA-J801P LS-H781P/H783P

Ice Lake-U CPU SKU

i3-1005G1 i5-1035G1

UC1

ICL-U_BGA1 526

S IC FJ8068 904310007 SRG KF D1 1.2G FCBGA

SA0000C VQ30

i3@

1 2

RC351 150_040 2_1%

TPM_PIRQ# < 66>

TS_EN <38,58 >

UC1

ICL-U_BGA1 526

S IC FJ8068 904368700 SRG KG D1 1G FCBGA

SA0000C UQ20

i5@

Reserve Test Po int

GPP_E19

TBT LSX #0 PINS VCCIO CONFIGURATION

NO INTERNAL PU/PD

HIGH: 3.3V

LOW: 1.8V

GPP_E21

TBT LSX #1 PINS VCCIO CONFIGURATION

INTERNAL PD 20K

HIGH: 3.3V

LOW: 1.8V

4 4

GPP_D10

TBT LSX #2 PINS VCCIO CONFIGURATION

NO INTERNAL PU/PD

HIGH: 3.3V

LOW: 1.8V

GPP_D12

TBT LSX #3 PINS VCCIO CONFIGURATION

NO INTERNAL PU/PD

HIGH: 3.3V

LOW: 1.8V

A

B

RSVD_1:

Follow 573129_I CL_U_DDR4_SODI MM_HW_SCH_RN

1 2

RC348 100K_04 02_5%

1 2

RC422 100K_04 02_5%

Security Class ification

Security Class ification

Security Class ification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

RSVD_1

ENBKL

2019/04/ 12 2020/04/ 12

2019/04/ 12 2020/04/ 12

2019/04/ 12 2020/04/ 12

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

ICL-U(1/14)DDI,EDP

ICL-U(1/14)DDI,EDP

ICL-U(1/14)DDI,EDP

FH5LI M/B LA-H801P

FH5LI M/B LA-H801P

FH5LI M/B LA-H801P

1.0

1.0

1.0

6 102Tuesday, October 15 , 2019

6 102Tuesday, October 15 , 2019

6 102Tuesday, October 15 , 2019

E

+3VS

Vinafix.com

A

B

C

D

E

1 2

@

RC3984

10K_040 2_5%

Reserve

1 1

VCCIN_AUX _CORE_ALERT# _R<17>

2 2

EC_SCI#_R

+3VALW _PRIM

+1.05V_V CCST

H_PROCH OT#<58,84>

+3VALW _PRIM

12

RC371

100K_04 02_5%

1 2

RC3990 1 00K_0402_5%

1 2

RC11 49.9_040 2_1%

1 2

RC12 1K_0402 _5%

CC4 0.1U_02 01_10V6K

EMC@

CC130 0.1U_020 1_10V6K

XEMC@

1 2

RC366 49.9_ 0402_1%

1 2

RC365 49.9_ 0402_1%

H_PROCH OT#

DC10

1 2

RB751V-4 0_SOD323-2

SCS0000 0Z00

EC_SLP_ S0IX#

12

12

+1.05VS_ VCCSTG_OUT_L GC

12

RC6

1K_0402 _5%

1 2

RC7

499_040 2_1%

EC_SLP_ S0IX#<58>

EC_SCI#<58>

H_PROCH OT#

EC_TP_INT #<58,63>

CATERR#

H_THERM TRIP#

H_PECI

PROC_PO PIRCOMP

PCH_OPIRC OMP

H_PECI<58>

1

CC1

EMC@

100P_02 01_50V8J

2

EC_SLP_ S0IX#

CATERR#

H_PECI

H_PROCH OT#_R

H_THERM TRIP#

PROC_PO PIRCOMP

PCH_OPIRC OMP

XDP_ITP_P MODE

EC_SCI#_R

12

RC39910_04 02_5% @

TP_INT#

12

RC39630_04 02_5%

SOC_GPP _E6

SOC_GPP _H2

UC1D

J4

CATERR#

CD5

PECI

C3

PROCHOT#

E3

THRMTRIP#

CJ41

PROC_POPIRCOMP

DU3

PCH_OPIRCOMP

A14

RSVD_25

B14

RSVD_26

DL15

DBG_PMODE

DV11

GPP_E3/CPU_GP0

DT11

GPP_E7/CPU_GP1

CR38

GPP_B3/CPU_GP2

CR39

GPP_B4/CPU_GP3

DT12

GPP_E6

DJ38

GPP_H2/CNV_BT_I2S_SDO

DL38

GPP_H19/TIME_SYNC0

ICL-U_BGA1 526

@

JTAG

4 of 19

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_TRST#

PCH_TCK

PCH_TDI

PCH_TDO

PCH_TMS

PCH_JTAGX

PROC_PRDY#

PROC_PREQ#

check XDP /DCI

< PU/PD for CMC Debug >

P3

K5

K3

P4

N1

N5

R5

K1

K2

N3

N2

P6

M6

SOC_XDP _TCK0

SOC_XDP _TDI

SOC_XDP _TDO

SOC_XDP _TMS

SOC_XDP _TRST#

SOC_XDP _TRST#

PCH_JTA G_TCK1

SOC_XDP _TDI

SOC_XDP _TDO

SOC_XDP _TMS

SOC_XDP _TCK0

XDP_PRD Y#

XDP_PRE Q#

T497TP@

T2TP@

SOC_XDP _TMS

SOC_XDP _TDI

SOC_XDP _TDO

XDP_PRE Q#

SOC_XDP _TCK0

PCH_JTA G_TCK1

SOC_XDP _TRST#

1 2

RC13 51_04 02_5%CMC@

1 2

RC14 51_04 02_5%CMC@

1 2

RC15 51_04 02_5%CMC@

1 2

RC17 51_04 02_5%@

CMC@

1 2

RC20 51_04 02_5%

1 2

RC22 51_04 02_5%@

1 2

RC21 51_04 02_5%@

+1.05VS_ VCCSTG_OUT_L GC

XDP_ITP_PMODE

DFX TEST MODE

INTERNAL PD 20K

HIGH: DFX TEST MODE DISABLED(DEFAULT)

3 3

4 4

A

LOW: DFX TES TMODE ENABLED

+1.05VO_ OUT_FET

RC18 1K_0402 _5%CMC@

RC19 1K_0402 _5%@

1 2

1 2

XDP_ITP_P MODE

+3VALW _PRIM

RC370 100K_04 02_5%

RC3965 100K_04 02_5%@

B

SOC_GPP_E6

JTAG ODT DISABLE

NO INTERNAL PU/PD

HIGH: JTAG ODT ENABLED

LOW: JTAG ODT DISABLED

1 2

1 2

Security Class ification

Security Class ification

Security Class ification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

SOC_GPP _E6

+3VALW _PRIM

2019/04/ 12 2020/04/ 12

2019/04/ 12 2020/04/ 12

2019/04/ 12 2020/04/ 12

C

GPP_H2

MAF/SAF STRAP

INTERNAL PD 20K

HIGH: Slave Attached Flash Sharing (SAFS) is enabled.

LOW: Master Attached Flash Sharing (MAFS) is enabled.

(Default)

1 2

RC389 2.2K_040 2_5%@

1 2

RC3966 2.2K_040 2_5%@

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

SOC_GPP _H2

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

ICL-U(1/14)DDI,MSIC,XDP

ICL-U(1/14)DDI,MSIC,XDP

ICL-U(1/14)DDI,MSIC,XDP

FH5LI M/B LA-H801P

FH5LI M/B LA-H801P

FH5LI M/B LA-H801P

E

7 102Tuesday, October 15 , 2019

7 102Tuesday, October 15 , 2019

7 102Tuesday, October 15 , 2019

1.0

1.0

1.0

5

Vinafix.com

4

3

2

1

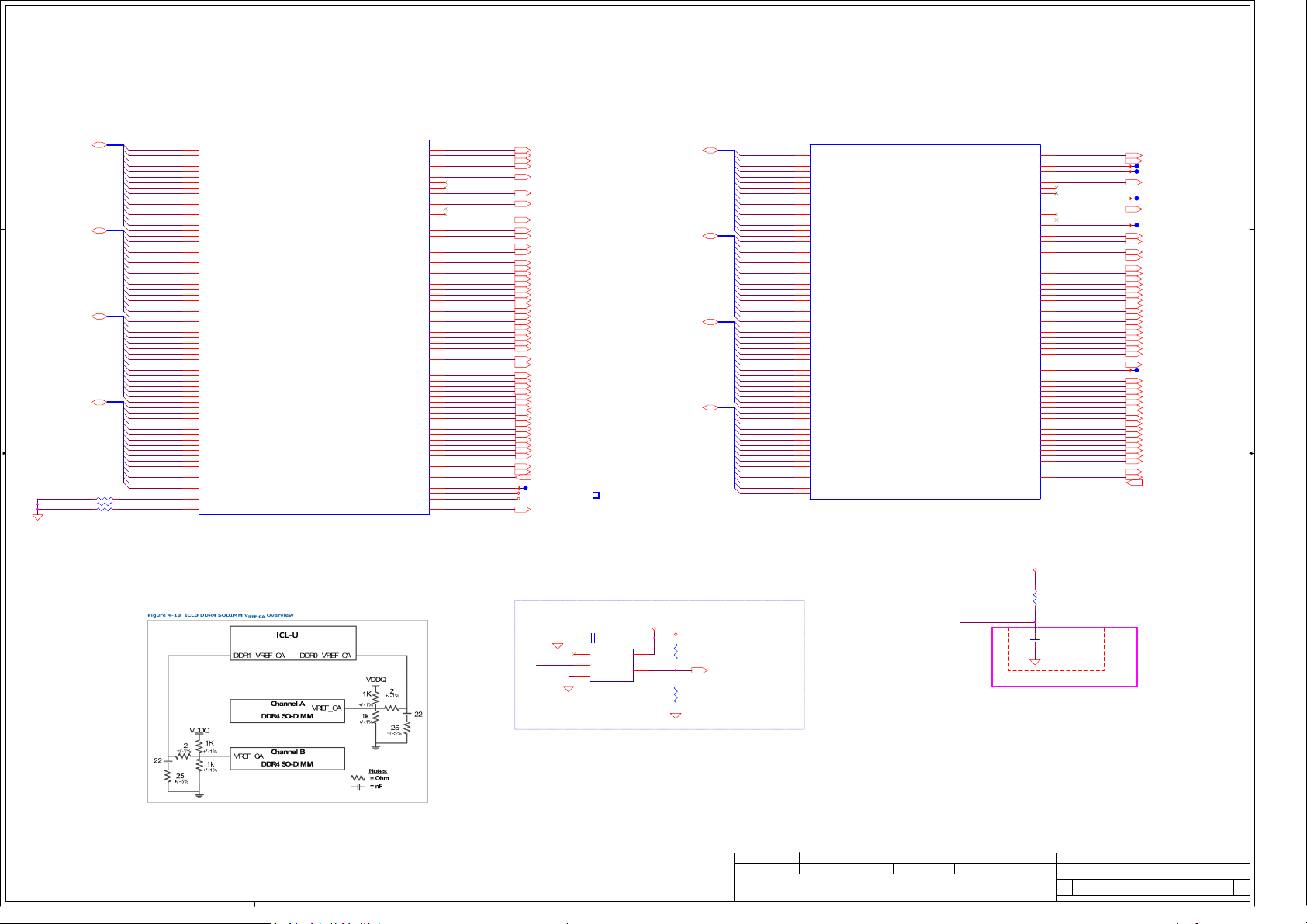

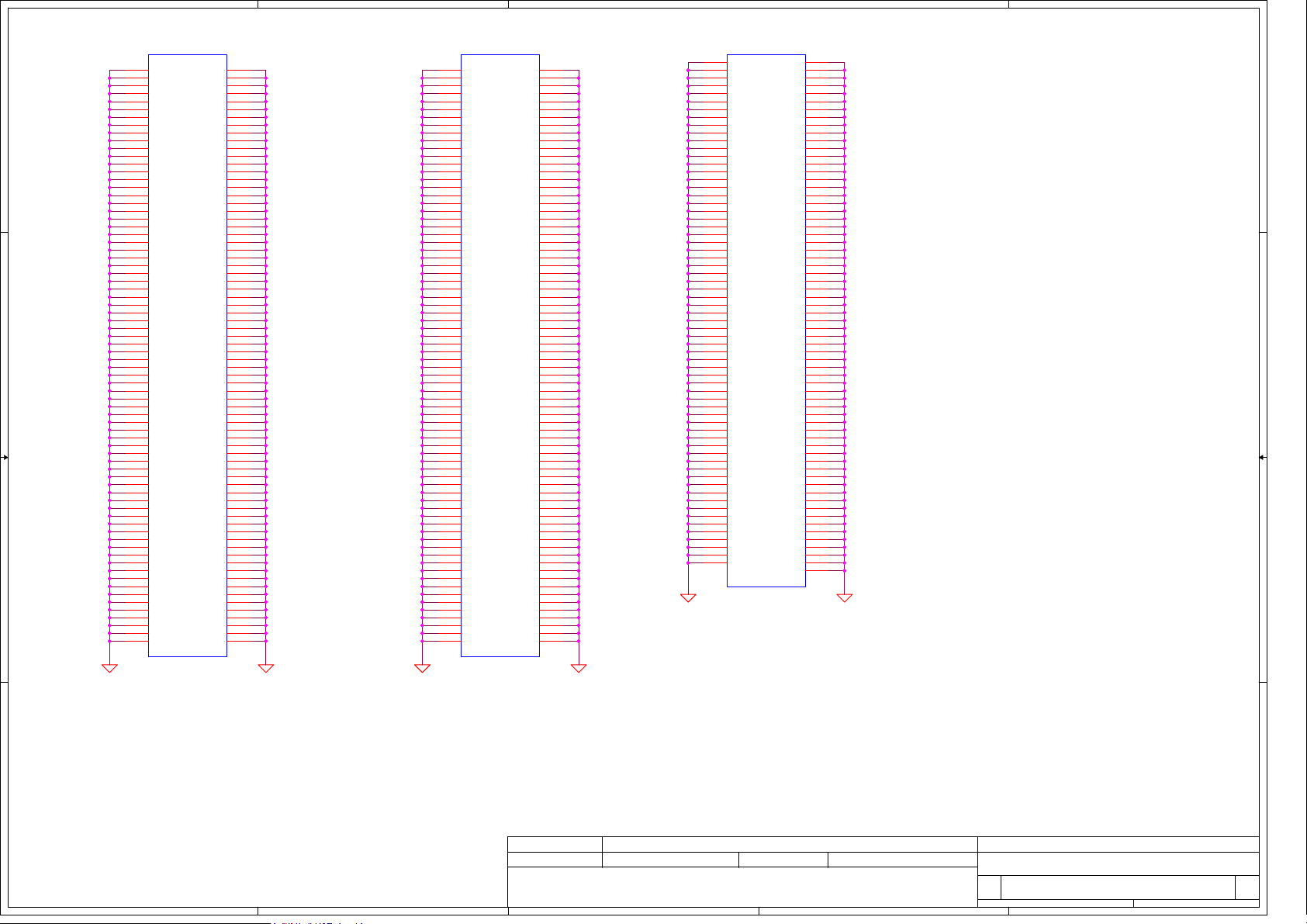

Follow Intel DDR4 NIL

DDR4: Refer to 575034_ICL_U42_DDR4_T3_6L_Core_Schematics_Rev0p7

D D

DDR_A_D[0..15]<23>

DDR_A_D[16..31]<23>

DDR_A_D[32..47]<23>

C C

DDR_A_D[48..63]<23>

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

SM_RCOMP0

12

RC25100_0402_1%

SM_RCOMP1

12

RC26100_0402_1%

SM_RCOMP2

12

RC27100_0402_1%

UC1B

LP4(NIL) / DDR4(NIL) LP4(NIL) / DDR4(NIL)

CA48

DDRA_DQ0_0/DDR0_DQ0_0

CA47

DDRA_DQ0_1/DDR0_DQ0_1

CA49

DDRA_DQ0_2/DDR0_DQ0_2

BV49

DDRA_DQ0_3/DDR0_DQ0_3

CA45

DDRA_DQ0_4/DDR0_DQ0_4

BV47

DDRA_DQ0_5/DDR0_DQ0_5

BV45

DDRA_DQ0_6/DDR0_DQ0_6

BV48

DDRA_DQ0_7/DDR0_DQ0_7

CC42

DDRA_DQ1_0/DDR0_DQ1_0

CC39

DDRA_DQ1_1/DDR0_DQ1_1

CC43

DDRA_DQ1_2/DDR0_DQ1_2

CE38

DDRA_DQ1_3/DDR0_DQ1_3

CC38

DDRA_DQ1_4/DDR0_DQ1_4

CE39

DDRA_DQ1_5/DDR0_DQ1_5

CE42

DDRA_DQ1_6/DDR0_DQ1_6

CE43

DDRA_DQ1_7/DDR0_DQ1_7

BT48

DDRA_DQ2_0/DDR0_DQ2_0

BT47

DDRA_DQ2_1/DDR0_DQ2_1

BT49

DDRA_DQ2_2/DDR0_DQ2_2

BN49

DDRA_DQ2_3/DDR0_DQ2_3

BT45

DDRA_DQ2_4/DDR0_DQ2_4

BN47

DDRA_DQ2_5/DDR0_DQ2_5

BN45

DDRA_DQ2_6/DDR0_DQ2_6

BN48

DDRA_DQ2_7/DDR0_DQ2_7

BV42

DDRA_DQ3_0/DDR0_DQ3_0

BV39

DDRA_DQ3_1/DDR0_DQ3_1

BV43

DDRA_DQ3_2/DDR0_DQ3_2

BW38

DDRA_DQ3_3/DDR0_DQ3_3

BV38

DDRA_DQ3_4/DDR0_DQ3_4

BW39

DDRA_DQ3_5/DDR0_DQ3_5

BW42

DDRA_DQ3_6/DDR0_DQ3_6

BW43

DDRA_DQ3_7/DDR0_DQ3_7

AY48

DDRB_DQ0_0/DDR0_DQ4_0

AY47

DDRB_DQ0_1/DDR0_DQ4_1

AY49

DDRB_DQ0_2/DDR0_DQ4_2

AU45

DDRB_DQ0_3/DDR0_DQ4_3

AY45

DDRB_DQ0_4/DDR0_DQ4_4

AU47

DDRB_DQ0_5/DDR0_DQ4_5

AU48

DDRB_DQ0_6/DDR0_DQ4_6

AU49

DDRB_DQ0_7/DDR0_DQ4_7

AY42

DDRB_DQ1_0/DDR0_DQ5_0

AY38

DDRB_DQ1_1/DDR0_DQ5_1

AY43

DDRB_DQ1_2/DDR0_DQ5_2

BB39

DDRB_DQ1_3/DDR0_DQ5_3

AY39

DDRB_DQ1_4/DDR0_DQ5_4

BB38

DDRB_DQ1_5/DDR0_DQ5_5

BB42

DDRB_DQ1_6/DDR0_DQ5_6

BB43

DDRB_DQ1_7/DDR0_DQ5_7

AR48

DDRB_DQ2_0/DDR0_DQ6_0

AR47

DDRB_DQ2_1/DDR0_DQ6_1

AR49

DDRB_DQ2_2/DDR0_DQ6_2

AM45

DDRB_DQ2_3/DDR0_DQ6_3

AR45

DDRB_DQ2_4/DDR0_DQ6_4

AM47

DDRB_DQ2_5/DDR0_DQ6_5

AM48

DDRB_DQ2_6/DDR0_DQ6_6

AM49

DDRB_DQ2_7/DDR0_DQ6_7

AT42

DDRB_DQ3_0/DDR0_DQ7_0

AT39

DDRB_DQ3_1/DDR0_DQ7_1

AR43

DDRB_DQ3_2/DDR0_DQ7_2

AT38

DDRB_DQ3_3/DDR0_DQ7_3

AR38

DDRB_DQ3_4/DDR0_DQ7_4

AR39

DDRB_DQ3_5/DDR0_DQ7_5

AR42

DDRB_DQ3_6/DDR0_DQ7_6

AT43

DDRB_DQ3_7/DDR0_DQ7_7

D47

DDR_RCOMP_0

E46

DDR_RCOMP_1

C47

DDR_RCOMP_2

ICL-U_BGA1526

@

2 of 19

DDRA_CLK_N/DDR0_CLK_N_0

DDRA_CLK_P/DDR0_CLK_P_0

DDRB_CLK_N/DDR0_CLK_N_1

DDRB_CLK_P/DDR0_CLK_P_1

DDRA_CKE0/DDR0_CKE0

DDRA_CKE1/NC

DDRB_CKE0/NC

DDRB_CKE1/DDR0_CKE1

DDRA_CS_0/DDR0_CS#0

DDRA_CS_1/NC

DDRB_CS_0/NC

DDRB_CS_1/DDR0_CS#1

DDRB_CA4/DDR0_BA0

NC/DDR0_BA1

DDRA_CA5/DDR0_BG0

NC/DDR0_BG1

NC/DDR0_MA0

NC/DDR0_MA1

DDRB_CA5/DDR0_MA2

NC/DDR0_MA3

NC/DDR0_MA4

DDRA_CA0/DDR0_MA5

DDRA_CA2/DDR0_MA6

DDRA_CA4/DDR0_MA7

DDRA_CA3/DDR0_MA8

DDRA_CA1/DDR0_MA9

NC/DDR0_MA10

NC/DDR0_MA11

NC/DDR0_MA12

DDRB_CA0/DDR0_MA13

DDRB_CA2/DDR0_MA14WE#

DDRB_CA1/DDR0_MA15CAS#

DDRB_CA3/DDR0_MA16RAS#

NC/DDR0_ODT_0

NC/DDR0_ODT_1

DDRA_DQSN_0/DDR0_DQSN_0

DDRA_DQSP_0/DDR0_DQSP_0

DDRA_DQSN_1/DDR0_DQSN_1

DDRA_DQSP_1/DDR0_DQSP_1

DDRA_DQSN_2/DDR0_DQSN_2

DDRA_DQSP_2/DDR0_DQSP_2

DDRA_DQSN_3/DDR0_DQSN_3

DDRA_DQSP_3/DDR0_DQSP_3

DDRB_DQSN_0/DDR0_DQSN_4

DDRB_DQSP_0/DDR0_DQSP_4

DDRB_DQSN_1/DDR0_DQSN_5

DDRB_DQSP_1/DDR0_DQSP_5

DDRB_DQSN_2/DDR0_DQSN_6

DDRB_DQSP_2/DDR0_DQSP_6

DDRB_DQSN_3/DDR0_DQSN_7

DDRB_DQSP_3/DDR0_DQSP_7

NC/DDR0_PAR

NC/DDR0_ACT#

NC/DDR0_ALERT#

RSVD_73

DDR0_VREF_CA

DDR1_VREF_CA

DDR_VTT_CTL

DRAM_RESET#

BL48

BL47

BF42

BF43

BG49

BJ47

BF38

BF41

BM38

BM42

BP42

BG42

BM43

BG39

BB49

BD47

BB48

BL49

BG38

BL45

BJ46

BG48

BE45

BG45

BG47

BE47

BJ38

BB47

BE48

BM39

BG43

BJ42

BM41

BJ39

BB45

BY47

BY46

CC41

CE41

BR47

BR46

BV41

BW41

AV46

AV47

AY41

BB41

AN46

AN47

AR41

AT41

BF39

BE49

BD46

M38

C44

B45

M39

DK47

DDR_PG_CTRL

DDR_DRAMRST#

DDR_A_CLK#0 <23>

DDR_A_CLK0 <23>

DDR_A_CLK#1 <23>

DDR_A_CLK1 <23>

DDR_A_CKE0 <23>

DDR_A_CKE1 <23>

DDR_A_CS#0 <23>

DDR_A_CS#1 <23>

DDR_A_BA0 < 23>

DDR_A_BA1 < 23>

DDR_A_BG0 <23>

DDR_A_BG1 <23>

DDR_A_MA0 <23>

DDR_A_MA1 <23>

DDR_A_MA2 <23>

DDR_A_MA3 <23>

DDR_A_MA4 <23>

DDR_A_MA5 <23>

DDR_A_MA6 <23>

DDR_A_MA7 <23>

DDR_A_MA8 <23>

DDR_A_MA9 <23>

DDR_A_MA10 <23>

DDR_A_MA11 <23>

DDR_A_MA12 <23>

DDR_A_MA13 <23>

DDR_A_MA14 <23>

DDR_A_MA15 <23>

DDR_A_MA16 <23>

DDR_A_ODT0 <23>

DDR_A_ODT1 <23>

DDR_A_DQS#0 <23>

DDR_A_DQS0 <23>

DDR_A_DQS#1 <23>

DDR_A_DQS1 <23>

DDR_A_DQS#2 <23>

DDR_A_DQS2 <23>

DDR_A_DQS#3 <23>

DDR_A_DQS3 <23>

DDR_A_DQS#4 <23>

DDR_A_DQS4 <23>

DDR_A_DQS#5 <23>

DDR_A_DQS5 <23>

DDR_A_DQS#6 <23>

DDR_A_DQS6 <23>

DDR_A_DQS#7 <23>

DDR_A_DQS7 <23>

DDR_A_PAR <23>

DDR_A_ACT# <23>

DDR_A_ALERT# <23>

1

T244TP@

+0.6V_A_VREFCA

+0.6V_B_VREFCA

DDR_DRAMRST# <23,24>

DDR_B_D[0..15]<24>

DDR_B_D[16..31]<24>

DDR_B_D[32..47]<24>

DDR_B_D[48..63]<24>

Trace width/Spacing >= 20mils

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

UC1C

LP4(NIL) / DDR4(NIL)

AK48

DDRC_DQ0_0/DDR1_DQ0_0

AK45

DDRC_DQ0_1/DDR1_DQ0_1

AK49

DDRC_DQ0_2/DDR1_DQ0_2

AG47

DDRC_DQ0_3/DDR1_DQ0_3

AK47

DDRC_DQ0_4/DDR1_DQ0_4

AG45

DDRC_DQ0_5/DDR1_DQ0_5

AG48

DDRC_DQ0_6/DDR1_DQ0_6

AG49

DDRC_DQ0_7/DDR1_DQ0_7

AJ38

DDRC_DQ1_0/DDR1_DQ1_0

AL39

DDRC_DQ1_1/DDR1_DQ1_1

AJ39

DDRC_DQ1_2/DDR1_DQ1_2

AL43

DDRC_DQ1_3/DDR1_DQ1_3

AL38

DDRC_DQ1_4/DDR1_DQ1_4

AJ42

DDRC_DQ1_5/DDR1_DQ1_5

AL42

DDRC_DQ1_6/DDR1_DQ1_6

AJ43

DDRC_DQ1_7/DDR1_DQ1_7

AB49

DDRC_DQ2_0/DDR1_DQ2_0

AB48

DDRC_DQ2_1/DDR1_DQ2_1

AE49

DDRC_DQ2_2/DDR1_DQ2_2

AE47

DDRC_DQ2_3/DDR1_DQ2_3

AE48

DDRC_DQ2_4/DDR1_DQ2_4

AB47

DDRC_DQ2_5/DDR1_DQ2_5

AB45

DDRC_DQ2_6/DDR1_DQ2_6

AE45

DDRC_DQ2_7/DDR1_DQ2_7

AD38

DDRC_DQ3_0/DDR1_DQ3_0

AD39

DDRC_DQ3_1/DDR1_DQ3_1

AE39

DDRC_DQ3_2/DDR1_DQ3_2

AE43

DDRC_DQ3_3/DDR1_DQ3_3

AE38

DDRC_DQ3_4/DDR1_DQ3_4

AD43

DDRC_DQ3_5/DDR1_DQ3_5

AD42

DDRC_DQ3_6/DDR1_DQ3_6

AE42

DDRC_DQ3_7/DDR1_DQ3_7

J48

DDRD_DQ0_0/DDR1_DQ4_0

J45

DDRD_DQ0_1/DDR1_DQ4_1

J49

DDRD_DQ0_2/DDR1_DQ4_2

G47

DDRD_DQ0_3/DDR1_DQ4_3

J47

DDRD_DQ0_4/DDR1_DQ4_4

G45

DDRD_DQ0_5/DDR1_DQ4_5

G48

DDRD_DQ0_6/DDR1_DQ4_6

E48

DDRD_DQ0_7/DDR1_DQ4_7

J38

DDRD_DQ1_0/DDR1_DQ5_0

G39

DDRD_DQ1_1/DDR1_DQ5_1

G38

DDRD_DQ1_2/DDR1_DQ5_2

G42

DDRD_DQ1_3/DDR1_DQ5_3

J39

DDRD_DQ1_4/DDR1_DQ5_4

J42

DDRD_DQ1_5/DDR1_DQ5_5

G43

DDRD_DQ1_6/DDR1_DQ5_6

J43

DDRD_DQ1_7/DDR1_DQ5_7

B43

DDRD_DQ2_0/DDR1_DQ6_0

D43

DDRD_DQ2_1/DDR1_DQ6_1

A43

DDRD_DQ2_2/DDR1_DQ6_2

C40

DDRD_DQ2_3/DDR1_DQ6_3

C43

DDRD_DQ2_4/DDR1_DQ6_4

D40

DDRD_DQ2_5/DDR1_DQ6_5

B40

DDRD_DQ2_6/DDR1_DQ6_6

A40

DDRD_DQ2_7/DDR1_DQ6_7

B35

DDRD_DQ3_0/DDR1_DQ7_0

D35

DDRD_DQ3_1/DDR1_DQ7_1

A35

DDRD_DQ3_2/DDR1_DQ7_2

D38

DDRD_DQ3_3/DDR1_DQ7_3

C35

DDRD_DQ3_4/DDR1_DQ7_4

C38

DDRD_DQ3_5/DDR1_DQ7_5

B38

DDRD_DQ3_6/DDR1_DQ7_6

A38

DDRD_DQ3_7/DDR1_DQ7_7

ICL-U_BGA1526

@

DDRC_CLK_N/DDR1_CLK_N_0

DDRC_CLK_P/DDR1_CLK_P_0

DDRD_CLK_N/DDR1_CLK_N_1

DDRD_CLK_P/DDR1_CLK_P_1

DDRC_CKE0/DDR1_CKE0

DDRD_CKE1/DDR1_CKE1

DDRC_CS_0/DDR1_CS#0

DDRD_CS_1/DDR1_CS#1

DDRD_CA2/DDR1_MA14WE#

DDRD_CA1/DDR1_MA15CAS#

DDRD_CA3/DDR1_MA16RAS#

DDRC_DQSN_0/DDR1_DQSN_0

DDRC_DQSP_0/DDR1_DQSP_0

DDRC_DQSN_1/DDR1_DQSN_1

DDRC_DQSP_1/DDR1_DQSP_1

DDRC_DQSN_2/DDR1_DQSN_2

DDRC_DQSP_2/DDR1_DQSP_2

DDRC_DQSN_3/DDR1_DQSN_3

DDRC_DQSP_3/DDR1_DQSP_3

DDRD_DQSN_0/DDR1_DQSN_4

DDRD_DQSP_0/DDR1_DQSP_4

DDRD_DQSN_1/DDR1_DQSN_5

DDRD_DQSP_1/DDR1_DQSP_5

DDRD_DQSN_2/DDR1_DQSN_6

DDRD_DQSP_2/DDR1_DQSP_6

DDRD_DQSN_3/DDR1_DQSN_7

DDRD_DQSP_3/DDR1_DQSP_7

3 of 19

LP4(NIL) / DDR4(NIL)

DDRC_CKE1/NC

DDRD_CKE0/NC

DDRC_CS_1/NC

DDRD_CS_0/NC

DDRD_CA4/DDR1_BA0

NC/DDR1_BA1

DDRC_CA5/DDR1_BG0

NC/DDR1_BG1

NC/DDR1_MA0

NC/DDR1_MA1

DDRD_CA5/DDR1_MA2

NC/DDR1_MA3

NC/DDR1_MA4

DDRC_CA0/DDR1_MA5

DDRC_CA2/DDR1_MA6

DDRC_CA4/DDR1_MA7

DDRC_CA3/DDR1_MA8

DDRC_CA1/DDR1_MA9

NC/DDR1_MA10

NC/DDR1_MA11

NC/DDR1_MA12

DDRD_CA0/DDR1_MA13

NC/DDR1_ODT_0

NC/DDR1_ODT_1

NC/DDR1_PAR

NC/DDR1_ACT#

NC/DDR1_ALERT#

Y48

Y47

M43

M42

U45

V46

M41

P43

V42

V39

Y39

T39

T38

T42

R45

N47

P42

Y49

U48

Y45

U47

R49

U49

M47

M45

R47

P39

N46

R48

Y41

V41

Y42

V47

V43

V38

AH46

AH47

AJ41

AL41

AC47

AC46

AE41

AD41

H47

H46

G41

J41

C42

D42

D36

C36

P38

M48

M49

DDR_B_CLK#1

DDR_B_CLK1

DDR_B_CKE1

DDR_B_CS#1

DDR_B_ODT1

DDR_B_CLK#0 <24>

DDR_B_CLK0 <24>

T3TP@

T4TP@

DDR_B_CKE0 <24>

T504TP@

DDR_B_CS#0 <24>

T498TP@

DDR_B_BA0 < 24>

DDR_B_BA1 < 24>

DDR_B_BG0 <24>

DDR_B_BG1 <24>

DDR_B_MA0 <24>

DDR_B_MA1 <24>

DDR_B_MA2 <24>

DDR_B_MA3 <24>

DDR_B_MA4 <24>

DDR_B_MA5 <24>

DDR_B_MA6 <24>

DDR_B_MA7 <24>

DDR_B_MA8 <24>

DDR_B_MA9 <24>

DDR_B_MA10 <24>

DDR_B_MA11 <24>

DDR_B_MA12 <24>

DDR_B_MA13 <24>

DDR_B_MA14 <24>

DDR_B_MA15 <24>

DDR_B_MA16 <24>

DDR_B_ODT0 <24>

T500TP@

DDR_B_DQS#0 <24>

DDR_B_DQS0 <24>

DDR_B_DQS#1 <24>

DDR_B_DQS1 <24>

DDR_B_DQS#2 <24>

DDR_B_DQS2 <24>

DDR_B_DQS#3 <24>

DDR_B_DQS3 <24>

DDR_B_DQS#4 <24>

DDR_B_DQS4 <24>

DDR_B_DQS#5 <24>

DDR_B_DQS5 <24>

DDR_B_DQS#6 <24>

DDR_B_DQS6 <24>

DDR_B_DQS#7 <24>

DDR_B_DQS7 <24>

DDR_B_PAR <24>

DDR_B_ACT# <24>

DDR_B_ALERT# <24>

B B

Buffer with Ope n Drain Output

For VTT power c ontrol

12

CC6 0.1U_0201_10V6K

UC3

DDR_PG_CTRL

A A

5

4

NC1VCC

2

A

3

GND

74AUP1G07GW_TSSOP5

SA00005U600

+1.2V_VDDQ

+3VS

12

RC28

5

100K_0402_5%

4

Y

3

RC16

1M_0402_5%@

1 2

SM_PG_CTRL <86>

SM_PG_CTRL to DDR

VTT supplied ramped

<35uS

(tCPU18)

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELE CTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELE CTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WI THOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WI THOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WI THOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2019/04/12 2020/04/12

2019/04/12 2020/04/12

2019/04/12 2020/04/12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

DDR_DRAMRST#

+1.2V_VDDQ

12

RC30

470_0402_5%

1

CC9

100P_0402_50V8J

EMC@

2

PDG & CKL no st uff

Title

Title

Title

ICL-U(3/14)DDR4

ICL-U(3/14)DDR4

ICL-U(3/14)DDR4

Size Doc ument Number Rev

Size Doc ument Number Rev

Size Doc ument Number Rev

FH5LI M/B LA-H801P

FH5LI M/B LA-H801P

FH5LI M/B LA-H801P

Date: Sheet of

Date: Sheet of

Date: Sheet of

ESD

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

1

8 102Tuesday, October 15, 2019

8 102Tuesday, October 15, 2019

8 102Tuesday, October 15, 2019

1.0

1.0

1.0

5

Vinafix.com

D D

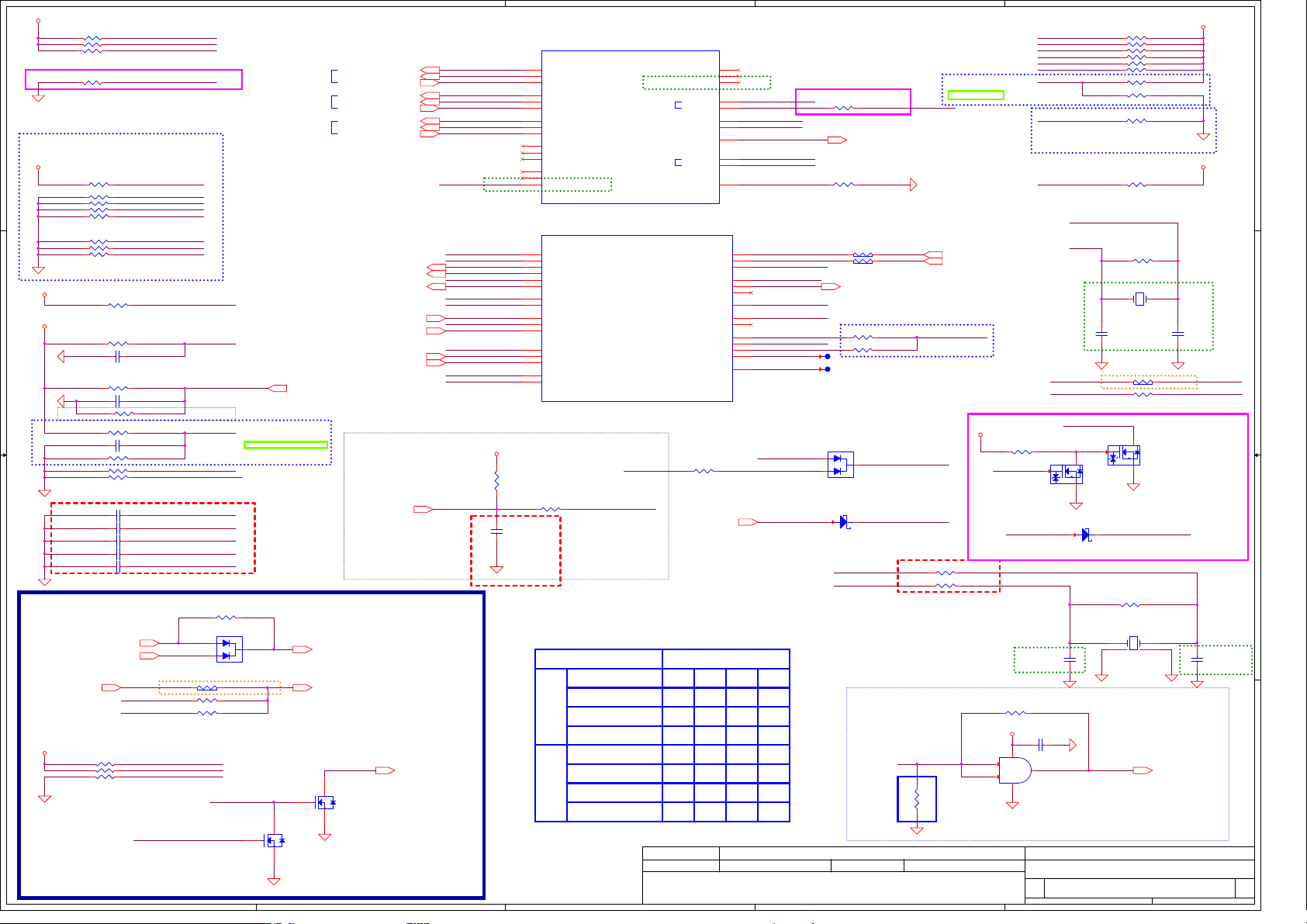

SPI ROM

TPM<-

+3VALW _PRIM

1 2

RC37 100K_0402 _5%

C C

+3VALW _PRIM

+3VALW _PRIM

B B

1 2

RC3968 100K_04 02_5%@

1 2

RC38 100K_0402 _5%

1 2

RC3967 100K_04 02_5%@

1 2

RC39 100K_0402 _5%

1 2

RC3943 100K_04 02_5%@

SOC_SPI_0 _CLK<66>

SOC_SPI_0 _SI<66>

SOC_SPI_0 _SO<66>

SOC_SPI_0 _CS#2<66>

SOC_SPI_0 _SI

SOC_SPI_0_SI

BOOT HALT

NO INTERNAL PU/PD

HIGH: DISABLE

LOW: ENABLE

SOC_SPI_0 _IO2

SOC_SPI_0_IO2

CONSENT STRAP

NO INTERNAL PU/PD

HIGH: DISABLE

LOW: ENABLE

SOC_SPI_0 _IO3

SOC_SPI_0_IO3

A0 PERSONALITY STRAP

NO INTERNAL PU/PD

HIGH: DISABLE

LOW: ENABLE

close to SPI RO M

SOC_SPI_0 _SO_R

SOC_SPI_0 _CLK_R

SOC_SPI_0 _SI_R

SOC_SPI_0 _IO3_R

SOC_SPI_0 _IO2_R

From SOC

SOC_SPI_0 _SO

SOC_SPI_0 _CLK

SOC_SPI_0 _SI

SOC_SPI_0 _IO3

SOC_SPI_0 _IO2

1 2

RC2 49.9_040 2_1%

1 2

RC3 49.9_040 2_1%EMC@

1 2

RC4 49.9_040 2_1%

1 2

RC5 49.9_040 2_1%

1 2

RC1 49.9_040 2_1%

4

SOC_SPI_0 _CLK

SOC_SPI_0 _SI

SOC_SPI_0 _SO

SOC_SPI_0 _IO2

SOC_SPI_0 _IO3

SOC_SPI_0 _CS#0

SOC_SPI_0 _CS#2

UC1E

DB42

SPI0_CLK

DD43

SPI0_MOSI

DF43

SPI0_MISO

DF42

SPI0_IO2

DD41

SPI0_IO3

DB43

SPI0_CS0#

DF41

SPI0_CS1#

DB41

SPI0_CS2#

DV16

GPP_E11/SPI1_CLK/BK1/SBK1

DT16

GPP_E13/SPI1_MOSI/BK3/SBK3

DU18

GPP_E12/SPI1_MISO/BK2/SBK2

DT18

GPP_E1/SPI1_IO2

DW18

GPP_E2/SPI1_IO3

DW16

GPP_E10/SPI1_CS_N/BK0/SBK0

DU16

GPP_E8/SATALED#/SPI1_CS1#

DV19

CL_CLK

DW19

CL_DATA

DT19

CL_RST#

ICL-U_BGA1 526

@

3

SMBUS

SPI 0

SML 0

GPP_C6/SML1CLK/SUSWARN_N/SUSPWRDNACK

SML1

SPI 1

eSPI

MLINK

5 of 19

1 2

1 2

1 2

RC44375K_040 2_5% @

RC44475K_040 2_5% @

RC441100K_04 02_5%

ESPI_RST#

ESPI_CS#

SOC_SPI_0 _CLK

Follow 572907_ICL_UY_PDG for Glitch

MAF - Master Attached Flash

Single SPI Flash attached to SPI Bus

EC FW access through eSPI Bus

SOC_GPP _C2

GPP_C2

TLS CONFIDENTIALITY

INTERNAL PD 20K

HIGH: TLS CONFIDENTIALITY ENABLE

LOW: TLS CONFIDENTIALITY DISABLE

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C7/SML1DATA/SUSACK#

GPP_A5/ESPI_CLK

GPP_A0/ESPI_IO0

GPP_A1/ESPI_IO1

GPP_A2/ESPI_IO2

GPP_A3/ESPI_IO3

GPP_A4/ESPI_CS#

GPP_A6/ESPI_RESET#

2

1 2

RC86 4.7K_040 2_5%

1 2

RC3969 4.7K_040 2_5%@

SOC_SMB CLK

DK27

SOC_SMB DATA

DP24

SOC_GPP _C2

DL24

SOC_SML 0CLK

DK24

SOC_SML 0DATA

DJ24

SOC_SML 0ALERT#

DP22

EC_SMB_ CK2

DN22

EC_SMB_ DA2

DL22

ESPI_CLK

CR47

CN45

CN48

CN49

CN47

CT45

CR46

ESPI_IO0

ESPI_IO1

ESPI_IO2

ESPI_IO3

ESPI_CS#

ESPI_RST#

RC34 49.9_040 2_1%EMC@

RC32 10_0402 _1%

RC33 10_0402 _1%

RC35 10_0402 _1%

RC36 10_0402 _1%

+3VALW _PRIM

1 2

1 2

1 2

1 2

1 2

ESPI_CS# <58>

ESPI_RST# <58>

SOC_SMB CLK

SOC_SMB DATA

SOC_SML 0CLK

SOC_SML 0DATA

EC_SMB_ CK2

EC_SMB_ DA2

SOC_SMB CLK_1

SOC_SMB DATA_1

SOC_SMB CLK

SOC_SMB DATA

SOC_SML 0ALERT#

SOC_SML0ALERT#

ESPI OR EC LESS

INTERNAL PD 20K

HIGH: ESPI DISABLE

LOW: ESPI ENABLE (Default)

EC_SMB_ CK2 <5 8>

EC_SMB_ DA2 <5 8>

Follow CRB

RC383 1K_0402 _5%

RC384 1K_0402 _5%

RC316 499_040 2_1%

RC315 499_040 2_1%

RC381 1K_0402 _5%

RC382 1K_0402 _5%

1 2

RC3961 2.2K_040 2_5%

1 2

RC3962 2.2K_040 2_5%

+3VS

5

G

QC4B

3 4

D

2N7002K DW_SOT36 3-6

S

2

G

6 1

D

1 2

RC3944 4.7K_040 2_5%@

1 2

RC3945 4.7K_040 2_5%@

SMB

(Link to DDR& G sensor)

SML1

(Link to EC)

ESPI_CLK_ R <58>

ESPI_IO0_R <58>

ESPI_IO1_R <58>

ESPI_IO2_R <58>

ESPI_IO3_R <58>

ESPI

Follow

572907_ICL_UY_P DG

1 2

1 2

1 2

1 2

1 2

1 2

SOC_SMB CLK_1

QC4A

2N7002K DW_SOT36 3-6

SOC_SMB DATA_1

S

1

+3VALW _PRIM

To EC

+3VALW _PRIM

+3VS

SOC_SMB CLK_1 <23,66 >

SOC_SMB DATA_1 <23,66>

< SPI ROM - 16M >

A A

SOC_SPI_0 _CS#0

SOC_SPI_0 _SO_R SOC_SPI_0 _IO3_R

5

UC2

1

CS#

2

DO(IO1)

3

IO2

4

GND

XM25QH1 28AHIG SOP 8P

SA0000B 8400

VCC

CLK

DI(IO0)

IO

+3VALW _PRIM

8

7

6

5

@

1 2

CC3 0.1U_0201_ 10V6K

SOC_SPI_0 _CLK_RSOC_SPI_0 _IO2_R

SOC_SPI_0 _SI_R

Security Class ification

Security Class ification

Security Class ification

2019/04/ 12 2020/04/ 12

2019/04/ 12 2020/04/ 12

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2019/04/ 12 2020/04/ 12

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

ICL-U(3/12)SPI,ESPI,SMB,LPC

ICL-U(3/12)SPI,ESPI,SMB,LPC

ICL-U(3/12)SPI,ESPI,SMB,LPC

FH5LI M/B LA-H801P

FH5LI M/B LA-H801P

FH5LI M/B LA-H801P

9 102Tuesday, October 15 , 2019

9 102Tuesday, October 15 , 2019

9 102Tuesday, October 15 , 2019

1

1.0

1.0

1.0

5

Vinafix.com

4

3

2

1

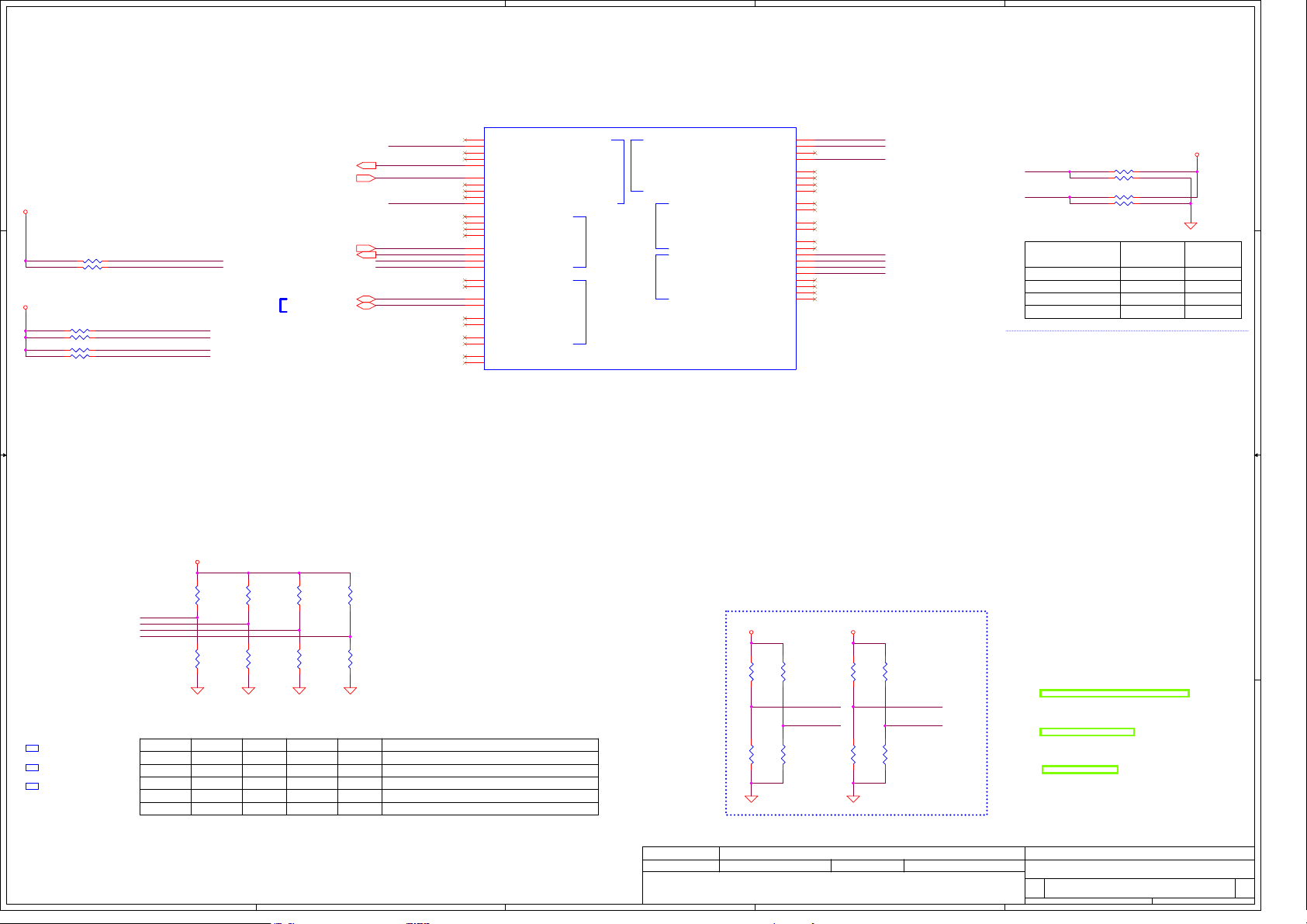

HDA_BIT_C LK

HDA_SYNC

D D

C C

HDA_SDIN0<56>

CNV_RF_ RESET#<52>

CLKREQ_ CNV#<52>

HDA_SDO UT

HDA_RST #

HDA_SDIN1

CNV_RF_ RESET#

< HD AUDIO >

1 2

HDA_RST #_R<56>

HDA_BIT_C LK_R<56>

HDA_SYNC_ R<56>

HDA_SDO UT_R<56>

RC3947 3 3_0402_5%

1 2

RC46 33_0402_5 %EMC@

1 2

RC48 33_0402_5 %

1 2

RC47 33_0402_5 %

12

@

HDA_BIT_C LK

HDA_SYNC

HDA_SDO UT

RC49

499_040 2_1%

UC1G

CY46

GPP_R0/HDA_BCLK/I2S0_SCLK

CV49

GPP_R1/HDA_SYNC/I2S0_SFRM

CY47

GPP_R2/HDA_SDO/I2S0_TXD

CV45

GPP_R3/HDA_SDI0/I2S0_RXD

DA47

GPP_R4/HDA_RST#

DP33

GPP_D19/I2S_MCLK

DC45

GPP_A23/I2S1_SCLK

DA49

GPP_R5/HDA_SDI1/I2S1_SFRM

DA45

GPP_R6/I2S1_TXD

DA48

GPP_R7/I2S1_RXD

CT49

GPP_A7/I2S2_SCLK

CT48

GPP_A8/I2S2_SFRM/CNV_RF_RESET#

CV47

GPP_A10/I2S2_RXD

CT47

GPP_A9/I2S2_TXD/MODEM_CLKREQ

CY39

GPP_S0/SNDW1_CLK

CY38

GPP_S1/SNDW1_DATA

DB39

GPP_S2/SNDW2_CLK

DD38

GPP_S3/SNDW2_DATA

DF38

GPP_S4/SNDW3_CLK/DMIC_CLK1

DD39

GPP_S5/SNDW3_DATA/DMIC_DATA1

ICL-U_BGA1 526

@

RC448 100K_04 02_5%

RC449 33K_040 2_5%

RC3946 33K_040 2_5%@

Follow

572907_ICL_UY_PDG for Glitch

1 2

1 2

1 2

SD3.0

GPP_H1/SD_PWR_EN_N/CNV_BT_I2S_SDO

GPP_S6/SNDW4_CLK/DMIC_CLK0

GPP_S7/SNDW4_DATA/DMIC_DATA0

AUDIO

7 of 19

HDA_BIT_C LK

HDA_RST #

HDA_SDIN1HDA_RST #

GPP_G6/SD_CLK

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G0/SD_CMD

GPP_G7/SD_WP

GPP_G5/SD_CD#

GPP_H0/CNV_BT_I2S_SDO

SD3_RCOMP

SNDW_RCOMP

CE46

CC48

CC49

CC47

CF45

CC45

CF49

CE47

DK38

DG38

CJ43

DG36

DG34

CV38

SD3_RCO MP

SNDW _RCOMP

1 2

RC358 200_040 2_1%

1 2

RC359 200_040 2_1%

< To Enable ME Override >

B B

A A

ME_EN<58 >

5

1 2

RC51 0_0402_ 5%

HDA_SDO UT

4

Security Class ification

Security Class ification

Security Class ification

2019/04/ 12 2020/04/ 12

2019/04/ 12 2020/04/ 12

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2019/04/ 12 2020/04/ 12

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

ICL-U(4/12)HDA,SD

ICL-U(4/12)HDA,SD

ICL-U(4/12)HDA,SD

FH5LI M/B LA-H801P

FH5LI M/B LA-H801P

FH5LI M/B LA-H801P

10 102Tuesday, October 15 , 2019

10 102Tuesday, October 15 , 2019

10 102Tuesday, October 15 , 2019

1

1.0

1.0

1.0

1 2

Vinafix.com

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

5

12

12

12

12

12

12

12

12

PVT modify

PM_SLP_S3#

PM_SLP_S4#

VCCST_OVERRIDE_LS

RC417100K_04 02_5%

VCCST_OVERRIDE_N

RC418100K_04 02_5%

VCCST_OVERRIDE_R

RC419100K_04 02_5%

VCCST_OVERRIDE_R

5

CLKREQ_PCIE#0

CLKREQ_PCIE#1

CLKREQ_PCIE#2

CLKREQ_PCIE#4

PM_SLP_S0#

SLP_SUS#

PM_SLP_S5#

PM_SLP_S4#

PM_SLP_S3#

PM_SLP_A#

PM_SLP_LAN#

PM_SLP_W LAN#

SYS_RESET#

SOC_SRTCRS T#

SOC_RTCRST #

CLR CMOS

SM_INTRUDER#

EC_RSMRST#

PCH_PWR OK

SYS_RESET#

EC_RSMRST#

SYS_PWROK

PLT_RST#

PCH_PWR OK

ESD

cost down plan

1 2

R345 0_0 402_5%@

D14

2

3

LRB715FT1G_ SOT323-3

SCS00008E0 0

1 2

R344 0_0 402_5%

@

1 2

R342 0_0 402_5%

@

1 2

R343 0_0 402_5%

VCCST_OVERRIDE_N

VGS(Max) : 1.5 V

M.2/SSD

G

LAN

WLAN

SOC_RTCRST # <58>

SM_INTRUDER#

NO INTERNAL PU/PD

HIGH: SPI VOLTAGE IS 1.8V

LOW: SPI VOLTAGE IS 3.3V

1

2

G

VGS(Max) : 1.5 V

13

D

2

QC2

BSS138W-7 -F_SOT323-3

G

SB00001GC00

S

VCCIN_AUX_CORE_VID <58>

VCCST_EN_LS <16>

13

D

S

+3VS

1 2

RC352 10K_0402_5%

1 2

RC353 10K_0402_5%

1 2

RC64 10K_0402 _5%

1 2

RC68 10K_0402 _5%@

reserve

D D

Follow

573129_ICL_U_DDR4_SODIMM_HW_SCH_RN

& 572907_ICL_UY_PDG for Glitch

+3VALW_PRIM +3VS

1 2

RC3959 100K_0402 _5%

1 2

RC394 100K_0402_ 5%

1 2

RC395 100K_0402_ 5%@

1 2

RC396 100K_0402_ 5%

1 2

RC397 100K_0402_ 5%

1 2

RC398 100K_0402_ 5%

1 2

RC399 100K_0402_ 5%

1 2

RC400 100K_0402_ 5%

+3VALW_PRIM

RC428 10K_0402_5 %

+RTCVCC

C C

B B

RC56 20K_0402_5%

CC13 1U_0201_6.3V6M

RC58 20K_0402_5%

CC14 1U_0201_6.3V6M

JCMOS1 0_0603_5%@

RC377 1M_0402_5 %@

CC319 0.1U_0201_10V6K@

RC427 10K_0402_5 %

RC386 100K_0402_ 5%

RC78 8.2K_ 0402_5%

CC20 100P_0402_50V8JEMC@

CC21 100P_0402_50V8JEMC@

CC376 100P_0402_50V8J@E MC@

CC23 100P_0402_50V8JEMC@

CC377 100P_0402_50V8J@E MC@

VCCST_EN

VCCIN_AUX_CORE_VID0_R<17,91>

VCCIN_AUX_CORE_VID1_R<17,58,91>

EC_VCCST_EN< 58>

+3VALW

A A

4

CLK_PCIE_N0<68>

CLK_PCIE_P0<68>

CLKREQ_PCIE#0<68>

CLK_PCIE_N1<51>

CLK_PCIE_P1<51>

CLKREQ_PCIE#1<51>

CLK_PCIE_N2<52>

CLK_PCIE_P2<52>

CLKREQ_PCIE#2<52>

PM_SLP_S4#<78>

PM_SLP_S3#<15,78>

PM_SLP_S0#<15 ,58,66>

EC_RSMRST#<58>

PLT_RST#<66>

PCH_PWROK<58,78>

SYS_PWROK<58,78>

From EC (Open-Drain)

EC_VCCST_PG_ R<5 8,78>

To EC

From EC to VCCST

VR Power SW Enable

To EC

VCCST_OVERRIDE_LS < 58>

QC3

BSS138W-7 -F_SOT323-3

SB00001GC00

4

3

UC1J

CJ3

CLKOUT_PCIE_N0

CJ5

CLKREQ_PCIE#0

CLKREQ_PCIE#1

CLKREQ_PCIE#2

CLKREQ_PCIE#4

SLP_SUS#

PM_SLP_S5#

PM_SLP_S4#

PM_SLP_S3#

PM_SLP_A#

PM_SLP_W LAN#

PM_SLP_LAN#

EC_RSMRST#

SYS_RESET#

PLT_RST#

PCH_DPW ROK

PCH_PWR OK

SYS_PWROK

INPUT3VSEL

SM_INTRUDER#

+1.05V_VCCST

12

EC_VCCST_PG_ R EC_VCCST_PG

CLKOUT_PCIE_P0

DK33

GPP_D5/SRCCLKREQ0#

CL2

CLKOUT_PCIE_N1

CL1

CLKOUT_PCIE_P1

DN34

GPP_D6/SRCCLKREQ1#

CL3

CLKOUT_PCIE_N2

CL5

CLKOUT_PCIE_P2

DP34

GPP_D7/SRCCLKREQ2#

CK3

CLKOUT_PCIE_N3

CK4

CLKOUT_PCIE_P3

DP36

GPP_D8/SRCCLKREQ3#

CJ2

CLKOUT_PCIE_N4

CJ1

CLKOUT_PCIE_P4

DN40

GPP_H10/SRCCLKREQ4#

ICL-U_BGA1526

@

UC1K

DM49

SLP_SUS#

DF45

GPD10/SLP_S5#

DC48

GPD5/SLP_S4#

DF47

GPD4/SLP_S3#

DH47

GPD6/SLP_A#

CL45

GPP_B12/SLP_S0#

DE49

GPD9/SPL_WLAN#

DN48

SLP_LAN#

DG49

RSMRST#

DK19

SYS_RESET#

CM49

GPP_B13/PLTRST#

DR48

DSW_PWROK

DN47

PCH_PWROK

DP19

SYS_PWROK

DN49

INPUT3VSEL

DR47

INTRUDER#

ICL-U_BGA1526

@

RC76

1K_0402_5%

1 2

RC77 60.4 _0402_1%

1

CC15

100P_0402_ 50V8J

EMC@

2

Follow Check list NC for un-used

10 of 19

GPP_H3/SX_EXIT_HOLDOFF_N/CNV_BT_I2S_SDO

GPD11/LANPHYPC/DSWLDO_MON

11 of 19

PCH_PWR OK PCH_PWR OK_R

ESD

Singal Name Input

VCCIN_AUX_CORE_VID

VCCST_OVERRIDE_LS

PM_SLP_S3# (SUSP#)

EC_VCCST_EN Output H

CCIN_AUX_CORE_VID

V

VCCST_OVERRIDE_LS

PM_SLP_S4# (SYSON)

Volume Premium

EC_VCCST_EN Output H

3

2

CLKOUT_PCIE_N5

CLKOUT_PCIE_P5

GPP_H11/SRCCLKREQ5#

RTCX1

RTC

RTCX2

RTCRST#

SRTCRST#

GPD8/SUSCLK

XTAL_IN

XTAL

XTAL_OUT

XCLK_BIASREF

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

GPP_B11/PMCALERT#

GPP_H18/CPU_C10_GATE#

GPD2/LAN_WAKE#

VCCST_OVERRIDE

VCCST_PWRGD

VCCSTPWRGOOD_TCSS

PROCPWRGD

1 2

RC537 0_04 02_5%@

WAKE#

GPD7

VR_ON<58,78,88>

CF5

CF3

DP40

DL48

DL49

DT47

DK46

DF49

DW8

DU8

DU6

CY42

DE46

DH48

CL39

DU40

DG40

DL45

DE47

DF48

CE4

CF2

CE3

CF1

DC47

SOC_RTCX1

SOC_RTCRST #

SOC_SRTCRS T#

SUSCLK

SOC_XTAL38.4_IN

SOC_XTAL38.4_OUT

XCLK_BIASREF

PBTN_OUT# _R

AC_PRESENT_R

PM_BATLOW#

PMCALERT#

CPU_C10_GAT E#PM_SLP_S0#

WAKE#

LAN_WAKE#

VCCST_OVERRIDE

EC_VCCST_PG

VCCSTPWR GOOD_TCSS

H_PROCPW RGD

GPD7

EC_VCCST_PG_ R

need to check

573129 RVP reserve both side,

but ORB only reserve on RTCX2

1 2

RC61 0_0 402_5%

SUSCLK <52 >

1 2

RC59 60.4_0402_1%

1 2

RC3954 0_0402_5%

1 2

RC66 0_0 402_5%

CPU_C10_GAT E# <15>

1 2

RC388 0_04 02_5%

1 2

RC453 0_04 02_5%

T503TP@

Only For Power Sequence Debug

T501TP@

tCPU22/ tPCH28b

D15

@

2

3

LRB715FT1G_ SOT323-3

SCS00008E0 0

PLT17

t

D32

RB751V-40_SOD 323-2

SCS00000Z00

SOC_XTAL38.4_IN SOC_XTAL38.4_IN_R

SOC_XTAL38.4_OUT SOC_XTAL38.4_OU T_R

PM_SLP_S3#

1

@

PM_SLP_S3#VR_ON

12

INPUT3VSEL

3V SELECT STRAP

HIGH: 3.0V +/-5%

LOW: 3.3V +/-5%

Follow 573129_ICL_U_DDR4_SODIMM_HW_SCH_RN

SOC_RTCX2_RSOC_RTCX2

PBTN_OUT# <58>

AC_PRESENT <58>

Close SOC ASAP

VCCST_OVERRIDE_R

+3VALW_PRIM

1 2

RC54 0_0 402_5%EMC@

1 2

RC55 0_0 402_5%EMC@

PM_SLP_S3#

EMI

EMI want to change 33 ohm, but ORB &CRB is 0ohm

H

DDD

D H

H H

H

D

H

D

D

D

H H

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D