Acer aspire 3600,aspire 5500,travelmate 3220,travelmate 2400la,travelmate 2761la,travelmate 2766p Schematics

5

D D

4

3

2

1

機 K : B, D等級

C C

EFL50 VGA/B SCHEMATIC DOCUMENT

ATI M24P/M26P

LS-2741 Revision: 0.2 2005/03/08 (DVT)

B B

A A

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2005/03/08 2006/03/08

3

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

2

Date: Sheet

Compal Electronics, Inc.

Cover Sheet

EFL50 LS-2741

0.2

111Monday, March 14, 2005

1

of

5

4

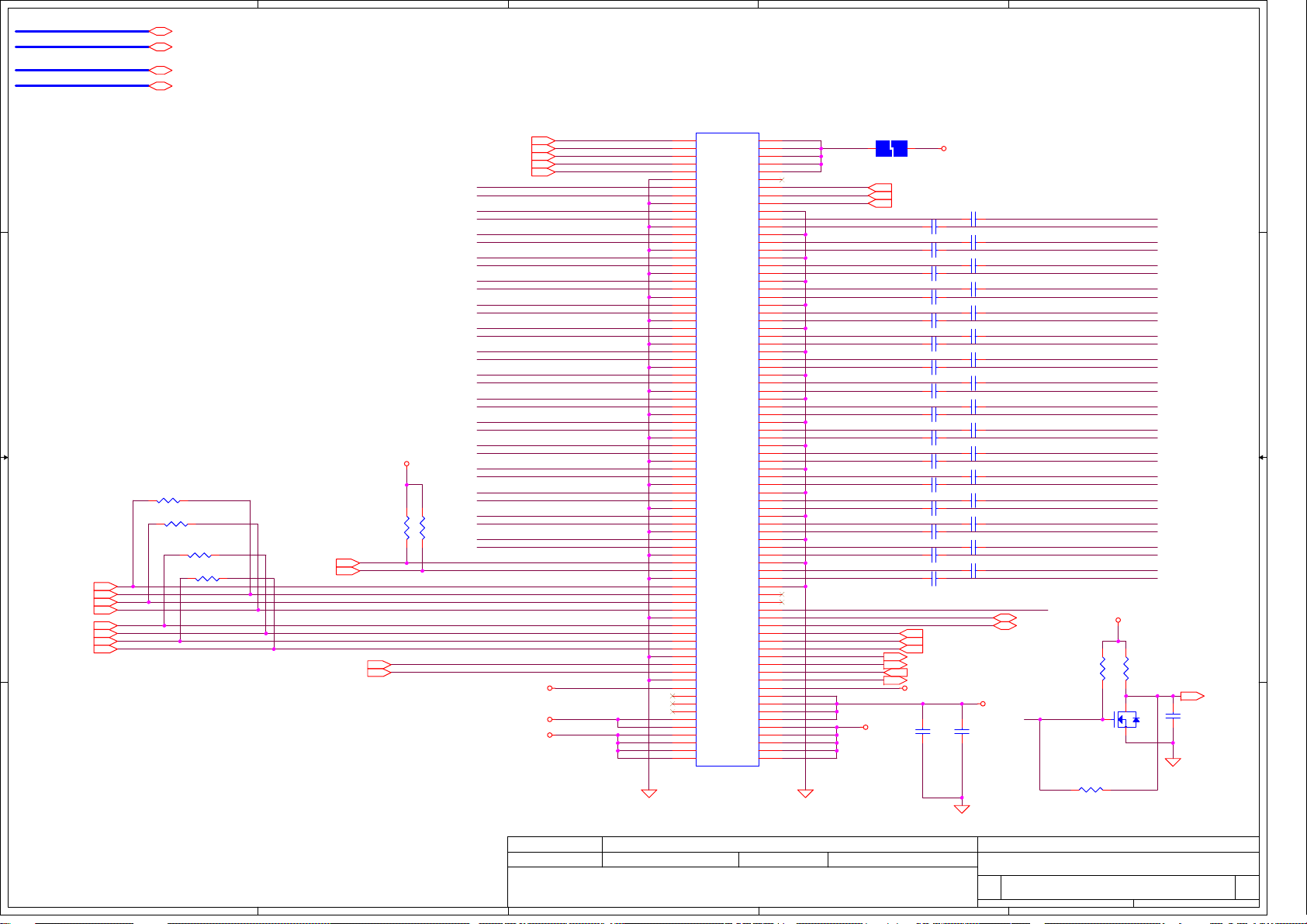

LS-2741 M22P/M24P/M26P BLOCK DIAGRAM

3

2

1

D D

K4D55323QF-GC33

Samsung

DDRB

C C

K4D55323QF-GC33

Samsung

B B

A A

DDRA M22P/M24P/26P PCIE

8M*32

DQ[0:31]

A[0:11]

CLK/CLK#

PAGE 8

8M*32

DQ[0:31]

A[0:11]

CLK/CLK#

PAGE 9

27MHz

SPREAD

CLOCK

ASM3P1819N-SR

PAGE 4

THERMAL

SENSOR

MAX6649MUA

PAGE 7

MDA[0:63]

NMAA[0:13]

NMCLKA0/A0#

NMCLKA1/A1#

MDA[0:63]

NMAA[0:13]

NMCLKB0/B0#

NMCLKB1/B1#

OSC_OUT

OSC_SPREAD

D+/D-

I2CC_SCL, I2CC_SDA

THER_ALERT

DQA[0:63]

MAA[0:13]

CLKA[0:1]

CLKA[0:1]#

MDA[0:63]

NMAA[0:13]

CLKB[0:1]

CLKB[0:1]#

GPIO_AUXWIN

PAGE 4,5,6,7

PCIE_TX[0:15]P, PCIE_TX[0:15]N

PCIE_RX[0:15]P, PCIE_RX[0:15]N

PCIE_REFCLKP, PCIE_REFCLKN

DVPDATA[18:19]

PWRGD

DVI

TV_OUT

VGA_OUT

DDC1_I2C

DIGON

PCIE_VDDR_12

PCIE_PVDD_12

VDDC

GPIO5

VDDR1

VDDR3

VDDR4

PCIE_PVDD_18

LVDDR_25

PCIE_MTX_C_GRX_P[0:15], PCIE_MTX_C_GRX_N[0:15]

PCIE_GT_MRX_P[0:15], PCIE_GTX_MRX_N[0:15]

CLK_PCIE_VGA CLK_PCIE_VGA# PLTRST_VGA#

DVI_TXD[0:2](+,-); DVI_TXC+(-)

VGA_TV_LUMA,VGA_TV_CRMA

VGA_CRT_R, VGA_CRT_G, VGA_CRT_B, DACA_HSYNC, DACA_VSYNC

VGA_DDC_CLK, VGA_DDC_DAT

LVDS Bus

I2CC_SCL

I2CC_SDA

+LCDVDD B+ENVDD

LCD

POWER

PAGE 10

GMCH_ENBKLBLON

+1.2VS

IF +VDD_CORE is fix

at 1.2V, we can short

+VDD_CORE and +1.2VS

+VDD_CORE

POWER_SEL

+FBVDD

+3.3VS

+1.8VS

+2.5VS

LCD

Connector

ACES 88017-4000

PAGE 10

+1.2VS

APW7057KC-TR

PAGE 11

1. +VDD_CORE=1.2V(M24) or 1.1V (M22)

2. POWER_SEL reduce +VDD_CORE to 1.0V (M22/24)

3. FBVDD=1.8V

+VDD_CORE

+FBVDD

SL6225BCA-T

PAGE 11

DAC_BRIG

INVT_PWM

DISPOFF#

+3VS

+5VALW

B+

Connector

+3VALW

+5VALW

B+

+3VS

+1.8VS

+2.5VS

ACES 88069-1600A

PAGE 3

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2005/03/08 2006/03/08

3

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

2

Date: Sheet

Compal Electronics, Inc.

Block Diagram

EFL50 LS-2741

0.2

211Monday, March 14, 2005

1

of

PCIE_GTX_MRX_P[0:15]

PCIE_GTX_MRX_N[0:15]

PCIE_MTX_C_GRX_P[0:15]

PCIE_MTX_C_GRX_N[0:15]

5

PCIE_GTX_MRX_P[0:15] 4

PCIE_GTX_MRX_N[0:15] 4

PCIE_MTX_C_GRX_P[0:15] 4

PCIE_MTX_C_GRX_N[0:15] 4

4

3

2

1

D D

VGA_CRT_R4

VGA_CRT_G4

VGA_CRT_B4

DACA_VSYNC4

DACA_HSYNC4

PCIE_MTX_C_GRX_P0

PCIE_MTX_C_GRX_N0

PCIE_MTX_C_GRX_P1

PCIE_MTX_C_GRX_N1

PCIE_MTX_C_GRX_P2

PCIE_MTX_C_GRX_N2

PCIE_MTX_C_GRX_P3

PCIE_MTX_C_GRX_N3

PCIE_MTX_C_GRX_P4

PCIE_MTX_C_GRX_N4

PCIE_MTX_C_GRX_P5

PCIE_MTX_C_GRX_N5

PCIE_MTX_C_GRX_P6

C C

+3VS

R48

12

330_0402_5%DVI@

R49

12

330_0402_5%DVI@

R50

DVI termination

Please close to U1

B B

DVI_TXC+4

DVI_TXC-4

DVI_TXD0+4

DVI_TXD0-4

DVI_TXD1+4

DVI_TXD1-4

DVI_TXD2+4

DVI_TXD2-4

A A

12

330_0402_5%DVI@

R51

12

330_0402_5%DVI@

VGA_DDC_CLK4

VGA_DDC_DAT4

4.7K_0402_5%

CLK_PCIE_VGA4

CLK_PCIE_VGA#4

R44

12

12

4.7K_0402_5%

R47

PCIE_MTX_C_GRX_N6

PCIE_MTX_C_GRX_P7

PCIE_MTX_C_GRX_N7

PCIE_MTX_C_GRX_P8

PCIE_MTX_C_GRX_N8

PCIE_MTX_C_GRX_P9

PCIE_MTX_C_GRX_N9

PCIE_MTX_C_GRX_P10

PCIE_MTX_C_GRX_N10

PCIE_MTX_C_GRX_P11

PCIE_MTX_C_GRX_N11

PCIE_MTX_C_GRX_P12

PCIE_MTX_C_GRX_N12

PCIE_MTX_C_GRX_P13

PCIE_MTX_C_GRX_N13

PCIE_MTX_C_GRX_P14

PCIE_MTX_C_GRX_N14

PCIE_MTX_C_GRX_P15

PCIE_MTX_C_GRX_N15

VGA_DDC_CLK

VGA_DDC_DAT

+5VALW

+2.5VS

+1.8VS

VGA_CRT_R

VGA_CRT_G

VGA_CRT_B

DACA_VSYNC

DACA_HSYNC

JP2

101102

103104

105106

107108

109110

111112

113114

115116

117118

119120

121122

123124

125126

127128

129130

131132

133134

135136

137138

139140

141142

143144

145146

147148

149150

151152

153154

155156

157158

ACES_88062-1600

159160

DAC_BRIG

DISPOFF#

INVT_PWM

LCD_ID#

PJ6

2

112

JUMP_43X118

VGA_TV_LUMA 4

VGA_TV_CRMA 4

VGA_TV_COMPS 4

C178 0.1U_0402_16V4Z

C179 0.1U_0402_16V4Z

C180 0.1U_0402_16V4Z

C181 0.1U_0402_16V4Z

C182 0.1U_0402_16V4Z

C183 0.1U_0402_16V4Z

C184 0.1U_0402_16V4Z

C185 0.1U_0402_16V4Z

C186 0.1U_0402_16V4Z

C187 0.1U_0402_16V4Z

C188 0.1U_0402_16V4Z

C189 0.1U_0402_16V4Z

C190 0.1U_0402_16V4Z

C191 0.1U_0402_16V4Z

C192 0.1U_0402_16V4Z

C193 0.1U_0402_16V4Z

C194 0.1U_0402_16V4Z

C195 0.1U_0402_16V4Z

C196 0.1U_0402_16V4Z

C197 0.1U_0402_16V4Z

C198 0.1U_0402_16V4Z

C199 0.1U_0402_16V4Z

C200 0.1U_0402_16V4Z

C201 0.1U_0402_16V4Z

C202 0.1U_0402_16V4Z

C203 0.1U_0402_16V4Z

C204 0.1U_0402_16V4Z

C205 0.1U_0402_16V4Z

C206 0.1U_0402_16V4Z

C211 0.1U_0402_16V4Z

C212 0.1U_0402_16V4Z

C215 0.1U_0402_16V4Z

C225

+1.8VS

B+

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

DAC_BRIG 10

DISPOFF# 10

INVT_PWM 10

PLTRST_VGA# 4

susp# 11

GMCH_ENBKL 4

LCD_ID# 10

+1.5VS

C226

2

1

22U_1206_10V4Z

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

2

1

10U_0805_10V4Z

+3VS

DVI_DET#

DVI_SCLK 4

DVI_SDATA 4

DVI_DET#

PCIE_GTX_MRX_P0

PCIE_GTX_MRX_N0

PCIE_GTX_MRX_P1

PCIE_GTX_MRX_N1

PCIE_GTX_MRX_P2

PCIE_GTX_MRX_N2

PCIE_GTX_MRX_P3

PCIE_GTX_MRX_N3

PCIE_GTX_MRX_P4

PCIE_GTX_MRX_N4

PCIE_GTX_MRX_P5

PCIE_GTX_MRX_N5

PCIE_GTX_MRX_P6

PCIE_GTX_MRX_N6

PCIE_GTX_MRX_P7

PCIE_GTX_MRX_N7

PCIE_GTX_MRX_P8

PCIE_GTX_MRX_N8

PCIE_GTX_MRX_P9

PCIE_GTX_MRX_N9

PCIE_GTX_MRX_P10

PCIE_GTX_MRX_N10

PCIE_GTX_MRX_P11

PCIE_GTX_MRX_N11

PCIE_GTX_MRX_P12

PCIE_GTX_MRX_N12

PCIE_GTX_MRX_P13

PCIE_GTX_MRX_N13

PCIE_GTX_MRX_P14

PCIE_GTX_MRX_N14

PCIE_GTX_MRX_P15

PCIE_GTX_MRX_N15

+3VS

12

R89

4.7K_0402_5%

DVI@

2

G

2N7002_SOT23@

1 2

R95 0_0402_5%

DVI@

12

13

D

S

R90

DVI@

Q7

4.7K_0402_5%

2

C218

1

DVI_DET 4

0.1U_0402_16V4ZDVI@

12

34

56

78

910

1112

1314

1516

1718

1920

2122

2324

2526

2728

2930

3132

3334

3536

3738

3940

4142

4344

4546

4748

4950

5152

5354

5556

5758

5960

6162

6364

6566

6768

6970

7172

7374

7576

7778

7980

8182

8384

8586

8788

8990

9192

9394

9596

9798

99100

VGA_TV_LUMA

VGA_TV_CRMA

VGA_TV_COMPS

PCIE_GTX_C_MRX_P0

PCIE_GTX_C_MRX_N0

PCIE_GTX_C_MRX_P1

PCIE_GTX_C_MRX_N1

PCIE_GTX_C_MRX_P2

PCIE_GTX_C_MRX_N2

PCIE_GTX_C_MRX_P3

PCIE_GTX_C_MRX_N3

PCIE_GTX_C_MRX_P4

PCIE_GTX_C_MRX_N4

PCIE_GTX_C_MRX_P5

PCIE_GTX_C_MRX_N5

PCIE_GTX_C_MRX_P6

PCIE_GTX_C_MRX_N6

PCIE_GTX_C_MRX_P7

PCIE_GTX_C_MRX_N7

PCIE_GTX_C_MRX_P8

PCIE_GTX_C_MRX_N8

PCIE_GTX_C_MRX_P9

PCIE_GTX_C_MRX_N9

PCIE_GTX_C_MRX_P10

PCIE_GTX_C_MRX_N10

PCIE_GTX_C_MRX_P11

PCIE_GTX_C_MRX_N11

PCIE_GTX_C_MRX_P12

PCIE_GTX_C_MRX_N12

PCIE_GTX_C_MRX_P13

PCIE_GTX_C_MRX_N13

PCIE_GTX_C_MRX_P14

PCIE_GTX_C_MRX_N14

PCIE_GTX_C_MRX_P15

PCIE_GTX_C_MRX_N15

DVI_SCLK

DVI_SDATA

PLTRST_VGA#

GMCH_ENBKL

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2005/03/08 2006/03/08

3

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

Custom

2

Date: Sheet of

Compal Electronics, Inc.

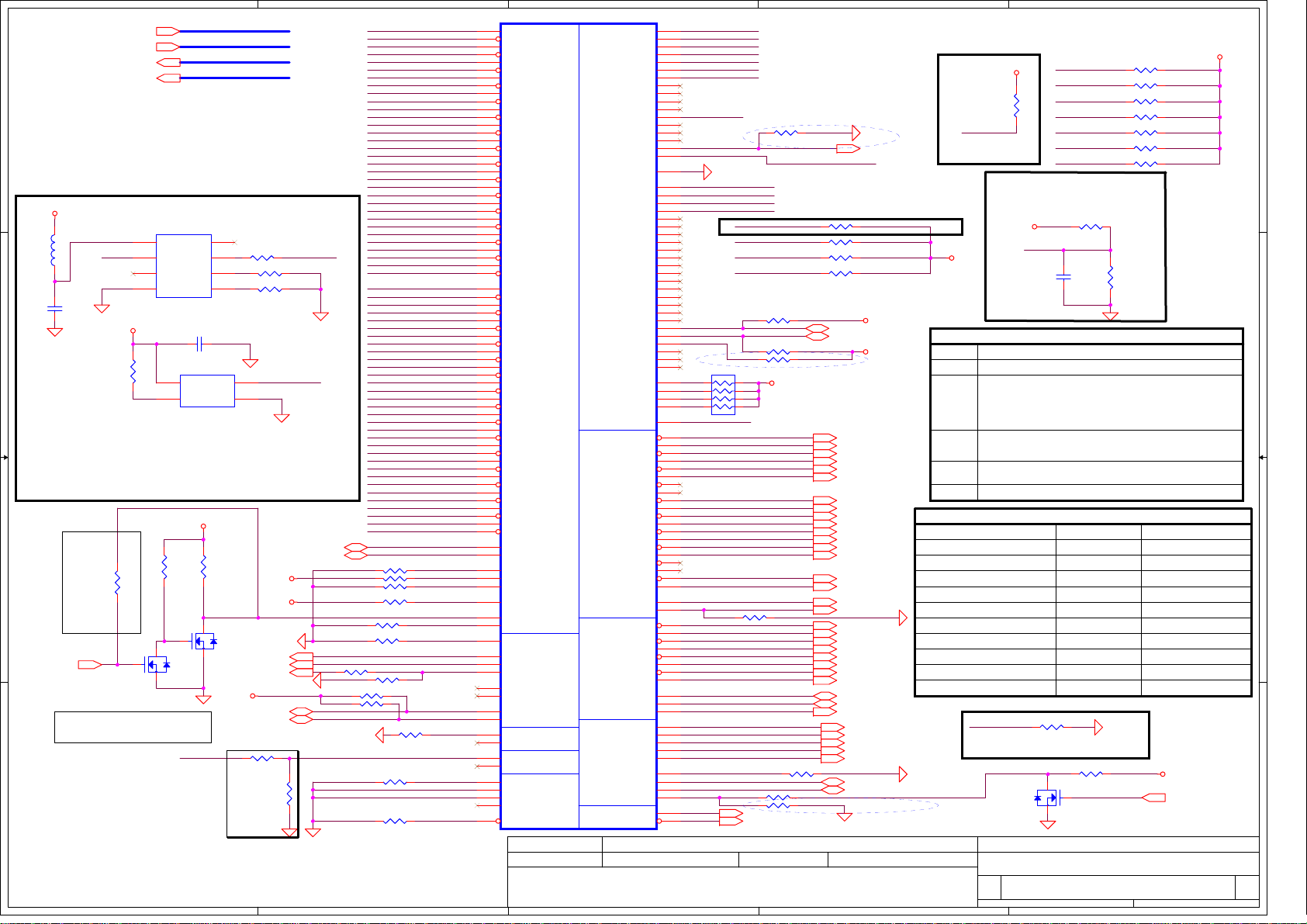

PCIE Connector

EFL50 LS-2741

0.2

311Monday, March 14, 2005

1

5

PCIE_MTX_C_GRX_P[0:15]3

PCIE_MTX_C_GRX_N[0:15]3

PCIE_GTX_MRX_P[0:15]3

PCIE_GTX_MRX_N[0:15]3

D D

For EMI request 10/28

+3VS

L5

1 2

BLM11A121SPT_0603

1

C177

2

C C

0.1U_0402_16V4Z

VGA termination, close chip

Spread spectrum

osc_in

+3VS

12

R76

1K_0402_5%

PCIE_MTX_C_GRX_P[0:15]

PCIE_MTX_C_GRX_N[0:15]

PCIE_GTX_MRX_P[0:15]

PCIE_GTX_MRX_N[0:15]

U2

7

REF

VDD

1

MODOUT

XIN

8

XOUT

2

NC

PD#

VSS

ASM3P1819N-SR_SO8

1 2

C176

0.1U_0402_16V4Z

X1

4

VDD

1

OE

27MHZ_15P

5

4

3

6

OUT

GND

1 2

R59 22_0402_5%

R77 10K_0402_5%@

R78 10K_0402_5%@

3

2

OSC_SPREAD

12

12

osc_in

Keep away from other signal at last 25mils

+3VS

12

12

B B

@

PLTRST_VGA#3

use 4pin or 7pin connector

R47

R27

0_0402_5%

1 2

Q4

2

G

2N7002_SOT23

R26

13

D

S

R25

100K_0402_5%

100K_0402_5%

Q3

13

D

2

G

S

2N7002_SOT23

VGA_TV_LUMA3

VGA_TV_CRMA3

VGA_TV_COMPS3

+3VS

osc_in

A A

Voltage divider

Reduce Voltage from 3.3V to 1.2V

5

71.5_0402_1%

+1.2VS

THERM_SCL7

THERM_SDA7

R63

1 2

121_0603_1%

+3VS

R64

CLK_PCIE_VGA3

CLK_PCIE_VGA#3

1 2

0_0402_5%

R30 4.7K_0402_5%

R31 4.7K_0402_5%

12

4

PCIE_MTX_C_GRX_P0

PCIE_MTX_C_GRX_N0

PCIE_MTX_C_GRX_P1

PCIE_MTX_C_GRX_N1

PCIE_MTX_C_GRX_P2

PCIE_MTX_C_GRX_N2

PCIE_MTX_C_GRX_P3

PCIE_MTX_C_GRX_N3

PCIE_MTX_C_GRX_P4

PCIE_MTX_C_GRX_N4

PCIE_MTX_C_GRX_P5

PCIE_MTX_C_GRX_N5

PCIE_MTX_C_GRX_P6

PCIE_MTX_C_GRX_N6

PCIE_MTX_C_GRX_P7

PCIE_MTX_C_GRX_N7

PCIE_MTX_C_GRX_P8

PCIE_MTX_C_GRX_N8

PCIE_MTX_C_GRX_P9

PCIE_MTX_C_GRX_N9

PCIE_MTX_C_GRX_P10

PCIE_MTX_C_GRX_N10

PCIE_MTX_C_GRX_P11

PCIE_MTX_C_GRX_N11

PCIE_MTX_C_GRX_P12

PCIE_MTX_C_GRX_N12

PCIE_MTX_C_GRX_P13

PCIE_MTX_C_GRX_N13

PCIE_MTX_C_GRX_P14

PCIE_MTX_C_GRX_N14

PCIE_MTX_C_GRX_P15

PCIE_MTX_C_GRX_N15

PCIE_GTX_MRX_P0

PCIE_GTX_MRX_N0

PCIE_GTX_MRX_P1

PCIE_GTX_MRX_N1

PCIE_GTX_MRX_P2

PCIE_GTX_MRX_N2

PCIE_GTX_MRX_P3

PCIE_GTX_MRX_N3

PCIE_GTX_MRX_P4

PCIE_GTX_MRX_N4

PCIE_GTX_MRX_P5

PCIE_GTX_MRX_N5

PCIE_GTX_MRX_P6

PCIE_GTX_MRX_N6

PCIE_GTX_MRX_P7

PCIE_GTX_MRX_N7

PCIE_GTX_MRX_P8

PCIE_GTX_MRX_N8

PCIE_GTX_MRX_P9

PCIE_GTX_MRX_N9

PCIE_GTX_MRX_P10

PCIE_GTX_MRX_N10

PCIE_GTX_MRX_P11

PCIE_GTX_MRX_N11

PCIE_GTX_MRX_P12

PCIE_GTX_MRX_N12

PCIE_GTX_MRX_P13

PCIE_GTX_MRX_N13

PCIE_GTX_MRX_P14

PCIE_GTX_MRX_N14

PCIE_GTX_MRX_P15

PCIE_GTX_MRX_N15

CLK_PCIE_VGA

CLK_PCIE_VGA#

R29 150_0402_1%

1 2

R28 100_0402_1%

1 2

R32 10K_0402_1%

R34 10K_0402_5%@

R33 1K_0402_5%

R16 715_0402_1%

R61

12

1 2

R_PLTRST_VGA#

1 2

12

VGA_TV_LUMA

VGA_TV_CRMA

R_VGA_TV_COMPS

R62

1 2

75_0402_5%

12

12

THERM_CLK

THERM_DAT

12

XTALIN

12

R18 1K_0402_5%

12

R17 10K_0402_5%

4

R6510K_0402_5%

3

U5A

AH30

AG30

AG29

AF29

AE29

AE30

AD30

AD29

AC29

AB29

AB30

AA30

AA29

Y29

W29

W30

V30

V29

U29

T29

T30

R30

R29

P29

N29

N30

M30

M29

L29

K29

K30

J30

AF26

AE26

AC25

AB25

AC27

AB27

AC26

AB26

Y25

W25

Y27

W27

Y26

W26

U25

T25

U27

T27

U26

T26

P25

N25

P27

N27

P26

N26

L25

K25

L27

K27

L26

K26

AF27

AE27

AC23

AB24

AB23

AE25

AD25

AD24

AH21

AK21

AJ22

AK22

AJ24

AK24

AG22

AG23

AJ23

AH24

AH28

AJ29

AH27

AF25

AH25

E8

B6

PCIE_RX0P

PCIE_RX0N

PCIE_RX1P

PCIE_RX1N

PCIE_RX2P

PCIE_RX2N

PCIE_RX3P

PCIE_RX3N

PCIE_RX4P

PCIE_RX4N

PCIE_RX5P

PCIE_RX5N

PCIE_RX6P

PCIE_RX6N

PCIE_RX7P

PCIE_RX7N

PCIE_RX8P

PCIE_RX8N

PCIE_RX9P

PCIE_RX9N

PCIE_RX10P

PCIE_RX10N

PCIE_RX11P

PCIE_RX11N

PCIE_RX12P

PCIE_RX12N

PCIE_RX13P

PCIE_RX13N

PCIE_RX14P

PCIE_RX14N

PCIE_RX15P

PCIE_RX15N

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

PCIE_REFCLKP

PCIE_REFCLKN

PCIE_CALRP

PCIE_CALRN

PCIE_CALI

PCIE_TESTIN

PWRGD

PWRGD_MASK

R2SET

Y_G

C_R_PR

COMP_B_PB

H2SYNC

V2SYNC

DDC3CLK

DDC3DATA

SSIN

SSOUT

XTALIN

XTALOUT

TESTEN

TEST_YCLK

TEST_MCLK

PLLTEST

STEREOSYNC

M24C_BGA708

PCI EXPRESS

DAC2CLK

SS

Part 1 of 5

GPIO_PWRCNTL

GPIO_MEMSSIN

DVOMODE

DVPDATA_0

DVPDATA_1

DVPDATA_2

DVPDATA_3

DVPDATA_4

DVPDATA_5

DVPDATA_6

DVPDATA_7

DVPDATA_8

DVPDATA_9

DVPDATA_10

DVPDATA_11

DVPDATA_12

DVPDATA_13

DVPDATA_14

DPVDATA_15

DVO / EXT TMDS / GPIOTMDSDAC1

DVPDATA_16

DVPDATA_17

DVPDATA_18

DVPDATA_19

DVPDATA_20

DVPDATA_21

DVPDATA_22

DVPDATA_23

DVPCNTL_0

DVPCNTL_1

DVPCNTL_2

DVPCNTL_3

TXOUT_L0N

TXOUT_L0P

TXOUT_L1N

TXOUT_L1P

TXOUT_L2N

TXOUT_L2P

TXOUT_L3N

TXOUT_L3P

TXCLK_LN

TXCLK_LP

TXOUT_U0N

TXOUT_U0P

TXOUT_U1N

TXOUT_U1P

TXOUT_U2N

LVDS

TXOUT_U2P

TXOUT_U3N

TXOUT_U3P

TXCLK_UN

TXCLK_UP

DDC2CLK

DDC2DATA

DDC1DATA

DDC1CLK

GPIO_AUXWIN

THERM

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

VREFG

DIGON

BLON

TX0M

TX0P

TX1M

TX1P

TX2M

TX2P

TXCM

TXCP

HPD1

HSYNC

VSYNC

RSET

DPLUS

DMINUS

R

G

B

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2005/03/08 2006/03/08

3

VGA_GPIO0

AJ5

VGA_GPIO1

AH5

VGA_GPIO2

AJ4

VGA_GPIO3

AK4

VGA_GPIO4

AH4

VGA_GPIO5

AF4

VGA_GPIO6

AJ3

AK3

AH3

AJ2

AH2

ROMCFG

AH1

AG3

AG1

AG2

POWER_SEL

AF3

AF2

AE10

AH6

AJ6

AK6

AH7

AK7

AJ7

AH8

AJ8

AH9

AJ9

AK9

AH10

AE6

AG6

AF6

AE7

AF7

AE8

AG8

AF8

AE9

AF9

AG10

AF10

1 8

AJ10

2 7

AK10

3 6

AJ11

4 5

AH11

RP1 10K_0804_8P4R_5%

+VREFG

AG4

(15mils)

AH15

AH16

AJ16

AJ17

AJ18

AK18

AJ20

AJ21

AK19

AJ19

AG16

AG17

AF16

AF17

AE18

AE19

AF19

AF20

AG19

AG20

AE12

AG12

AK13

AJ13

AJ14

AJ15

AK15

AK16

AJ12

AK12

AE13

AE14

AF12

AK27

AJ27

AJ26

AJ25

AK25

AH26

AG25

AF24

AG24

AF11

AE11

R24 10K_0402_5%

DVI_TXD0DVI_TXD0+

DVI_TXD1DVI_TXD1+

DVI_TXD2DVI_TXD2+

DVI_TXCDVI_TXC+

DACA_VSYNC

DAC_RSET

R_HEAT_ALERT HEAT_ALERT

D+

D-

R75 10K_0402_5%

MEM_ID0

MEM_ID1

MEM_ID2

MEM_ID3

MEM_ID3

MEM_ID2

MEM_ID1

MEM_ID0

R12 4.7K_0402_5%

1 2

R11 4.7K_0402_5%

1 2

R13 10K_0402_5%

1 2

LVDSA0LVDSA0+

LVDSA1LVDSA1+

LVDSA2LVDSA2+

LVDSACLVDSAC+

LVDSB0LVDSB0+

LVDSB1LVDSB1+

LVDSB2LVDSB2+

LVDSBCLVDSBC+

ENVDD

GMCH_ENBKL

1 2

DVI_SCLK

DVI_SDATA

DVI_DET

VGA_CRT_R

VGA_CRT_G

VGA_CRT_B

DACA_HSYNC

R20 499_0402_1%

VGA_DDC_DAT

VGA_DDC_CLK

R57 0_0402_5%@

1 2

R58 10K_0402_5%

D+ 7

D- 7

Compal Secret Data

Deciphered Date

M22 Core speed MAX 300MHz

M24 Core speed MAX 400MHz

POWER_SEL(High 3.3V):VDDC=1.05V

(Low 0V ):VDDC=1.20V

1 2

OSC_SPREAD

R14 10K_0402_5%

1 2

@

R68 10K_0402_5%

1 2

R67 10K_0402_5%

1 2

R66 10K_0402_5%

1 2

X76@

X76@

I2CC_SDA 10

I2CC_SCL 10

RESRRVED FOR M24 TEST

M24@

+3VS

DVI_SCLK 3

DVI_SDATA 3

1 2

12

2

POWER_SEL 11

+3VS

+3VS

LVDSA0- 10

LVDSA0+ 10

LVDSA1- 10

LVDSA1+ 10

LVDSA2- 10

LVDSA2+ 10

LVDSAC- 10

LVDSAC+ 10

LVDSB0- 10

LVDSB0+ 10

LVDSB1- 10

LVDSB1+ 10

LVDSB2- 10

LVDSB2+ 10

LVDSBC- 10

LVDSBC+ 10

ENVDD 10

GMCH_ENBKL 3

DVI_TXD0- 3

DVI_TXD0+ 3

DVI_TXD1- 3

DVI_TXD1+ 3

DVI_TXD2- 3

DVI_TXD2+ 3

DVI_TXC- 3

DVI_TXC+ 3

DVI_DET 3

VGA_CRT_R 3

VGA_CRT_G 3

VGA_CRT_B 3

DACA_HSYNC 3

DACA_VSYNC 3

VGA_DDC_DAT 3

VGA_DDC_CLK 3

If GPIO_AUXWIN not used,

pulled it to GND.

2

1

***

10K_0402_5%

M26 VRAM config

High vram=256M

Low vram=128M

***

+3VS

R74

@

ROMCFG

+3VS

1 2

VGA_GPIO0

VGA_GPIO1

VGA_GPIO2

VGA_GPIO3

VGA_GPIO4

VGA_GPIO5

VGA_GPIO6

***R13 ,R15 change to 100ohm

Place +VREFG divider Res

and decoupling Cap close

to Ball AG4

+3VS

+VREFG

1 2

R23

1

C34

2

0.1U_0402_16V4Z

100_0402_1%

1 2

R70 10K_0402_5%

1 2

R69 10K_0402_5%@

1 2

R72 10K_0402_5% @

1 2

R71 10K_0402_5%@

1 2

R10 10K_0402_5%@

1 2

R9 10K_0402_5%@

1 2

R73 10K_0402_5%@

R22

100_0402_1%

1 2

General Straping (V G A Interna l PD) 0:Disable, 1:Enable

GPIO0 DEFAULT : 1

GPIO1

GPIO(3:2)

GPIO4

GPIO5

GPIO6

Full Transm it ter O utput Swi ng Power

Transmitter De-emphasis Enable

00: PCI Express 1.0A mode

01: Kyrene-compat ible mode

10: PCI Express 1.0 mode

11: PCI Express 1.0A mode and short-circuit internal

loopback mode (Rx connected directly to Tx of PHY)

Transmitter Extra Current

PCI-E Lane Reversal Enable

Force chip to go to compliance state quickly

for test purposes

Reduced PLL bandwidth

DEFAULT : 0

DEFAULT : 00

DEFAULT : 0

DEFAULT : 0

DEFAULT : 0

Vedio Memory Config. (VGA Internal PD) 1.8V only

MEM_ID1

0

1

0

1

1

0

MEM_ID2

DVI_DET

1

1

1

1

0

0

0

0

MEM_ID3

0

0

0

0

0

0

0

0

R15

1 2

100K_0402_1%@

Default

64MB

128MB

64MB

128MB

32MB

64MB

32MB

64MB

256MB 1

256MB 1 1 0 0

Size Vendor Chips

8Mx32 Samsung x2

8Mx32 Samsung x4

8Mx32 Hynix x2

8Mx32 Hynix x4

4Mx32 Samsung x2

4Mx32 Samsung x4

4Mx32 Hynix x2

4Mx32 Hynix x4

16Mx32 Hynix x4

16Mx32 Samsung x4

***

MEM_ID0

0

0

1

1

0 0

0

1

1 1

0 0 0

if no DVI , dvi_det pull low

R56 100K_0402_5%@

1 2

Q5

13

D

S

Title

Size Document Number Rev

Custom

Date: Sheet of

THER_ALERT#

2

G

2N7002_SOT23@

Compal Electronics, Inc.

M22/M24/M26P Main

EFL50 LS-2741

1

+3VS

THER_ALERT# 7

411Monday, March 14, 2005

+3VS

0.2

Loading...

Loading...