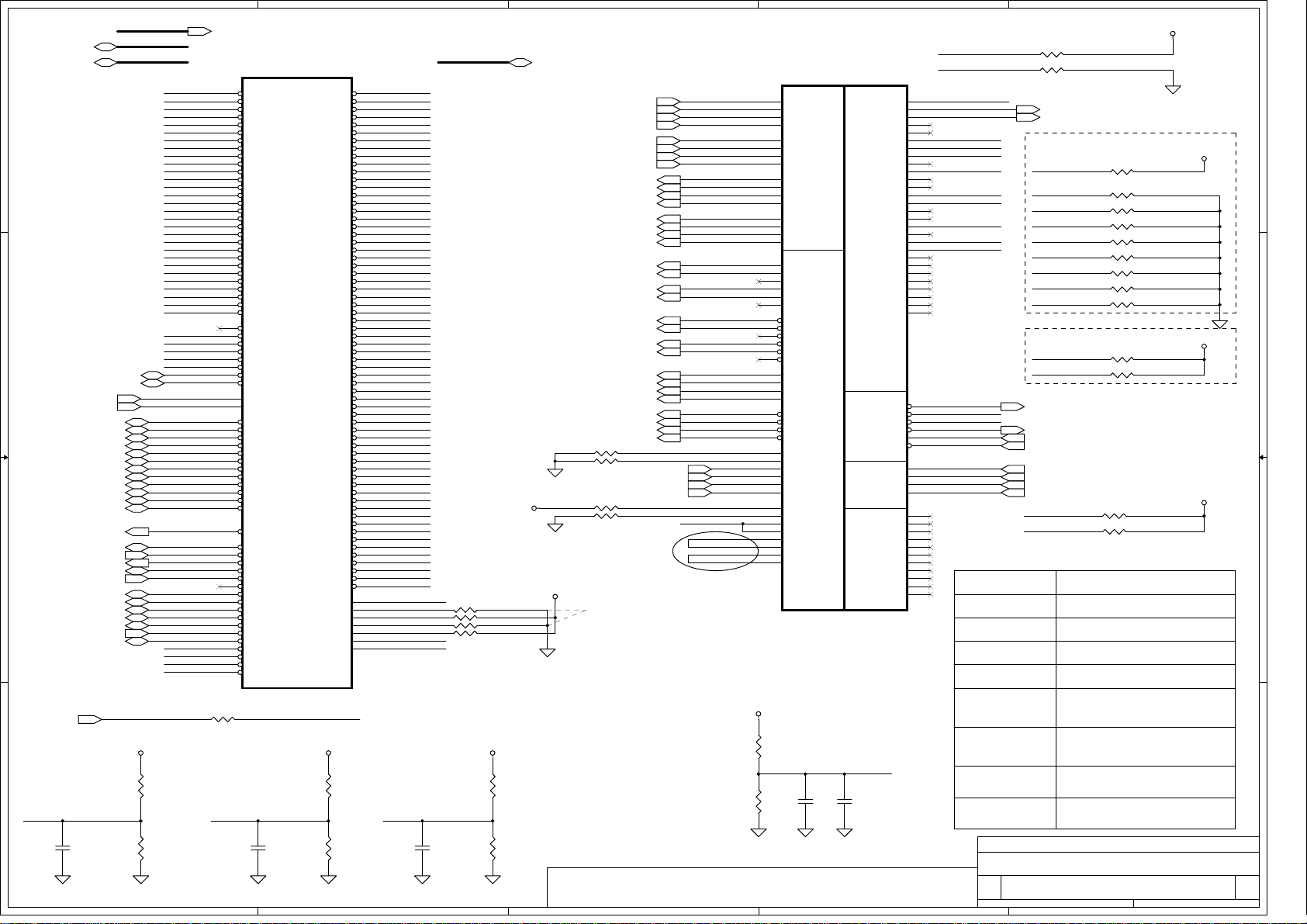

Acer aspire 3600,aspire 5500,travelmate 3220,travelmate 2400la,travelmate 2761la,travelmate 2766p Schematics

A

B

C

D

E

Page Index

===============

P01-Cover Page

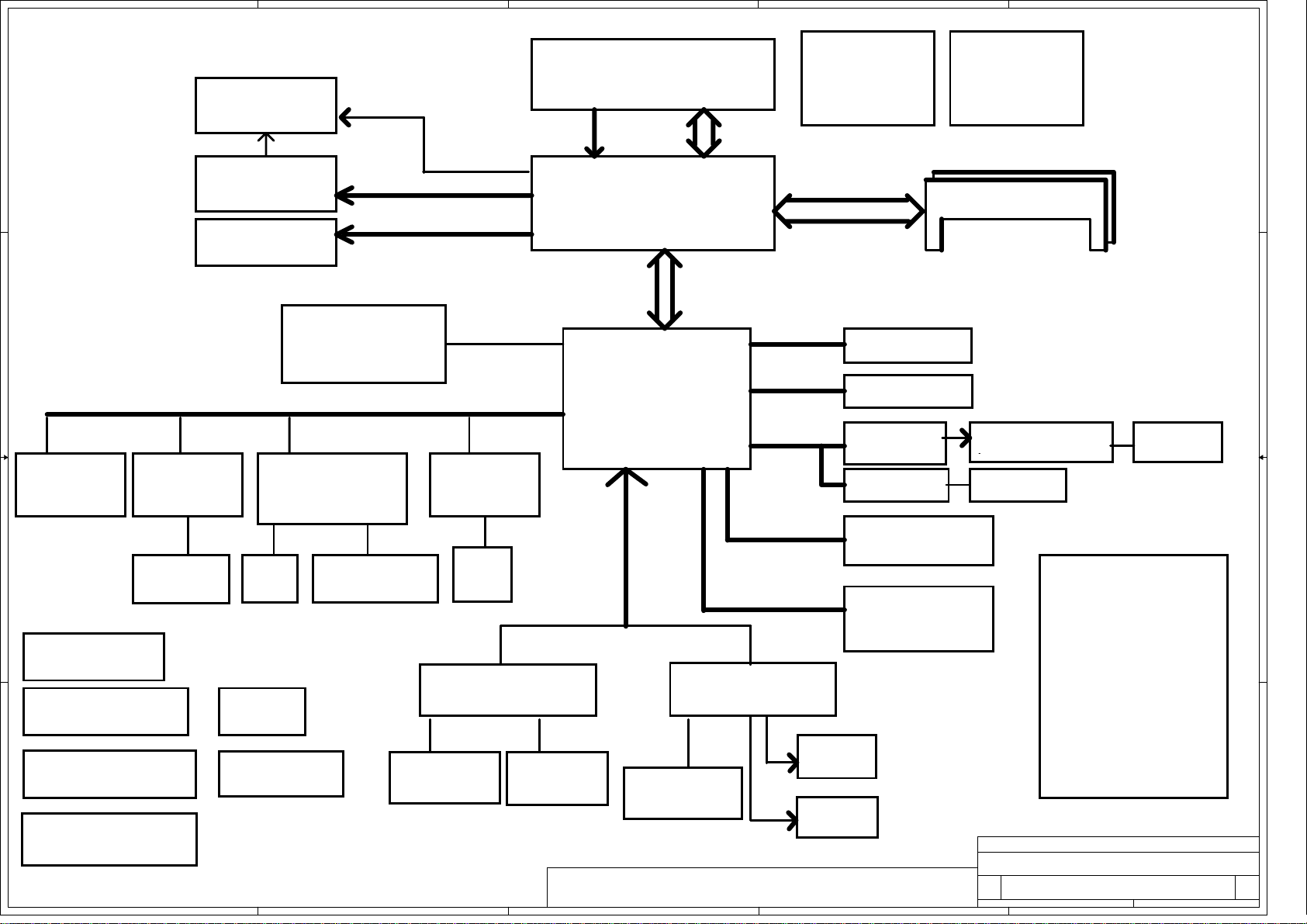

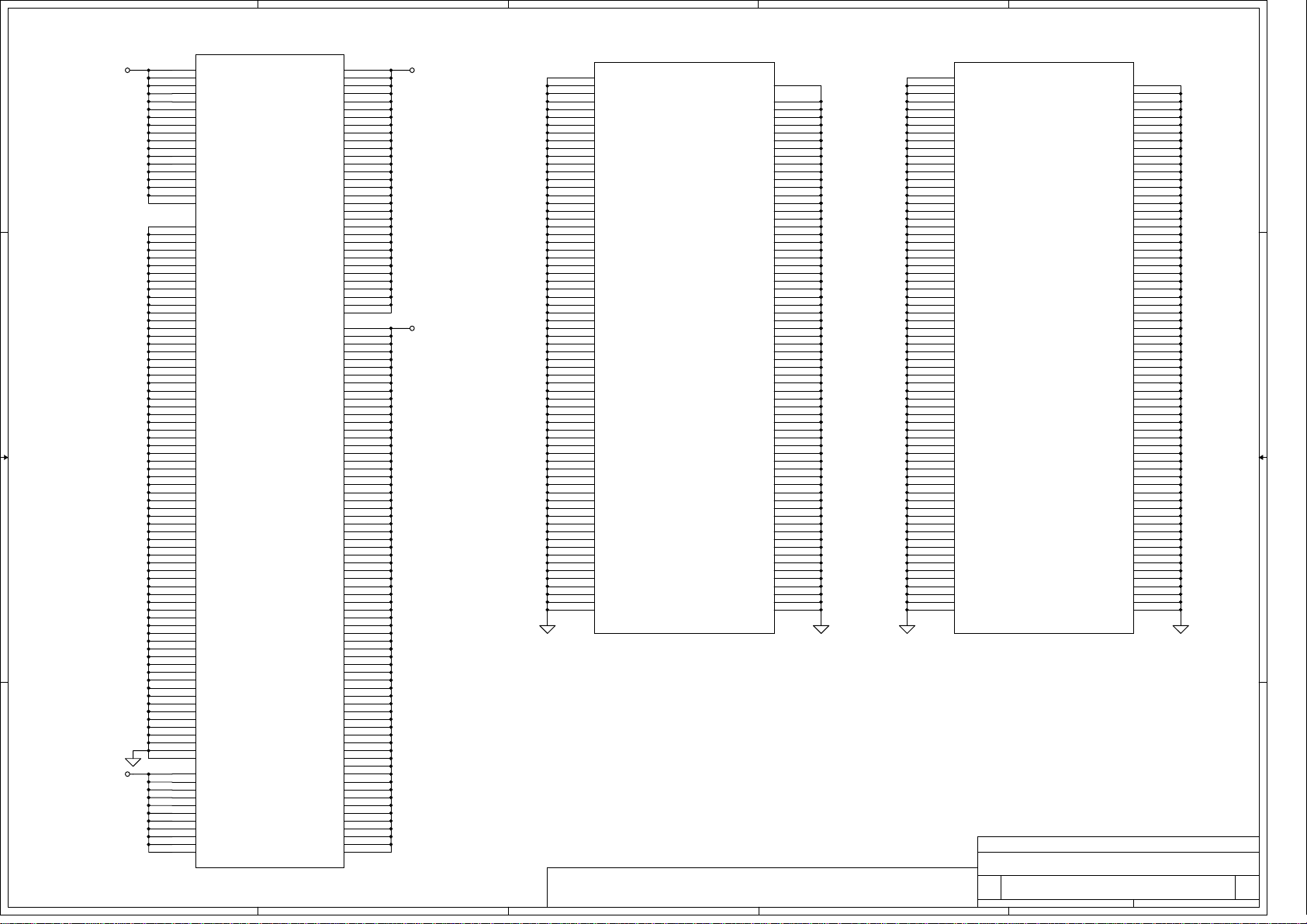

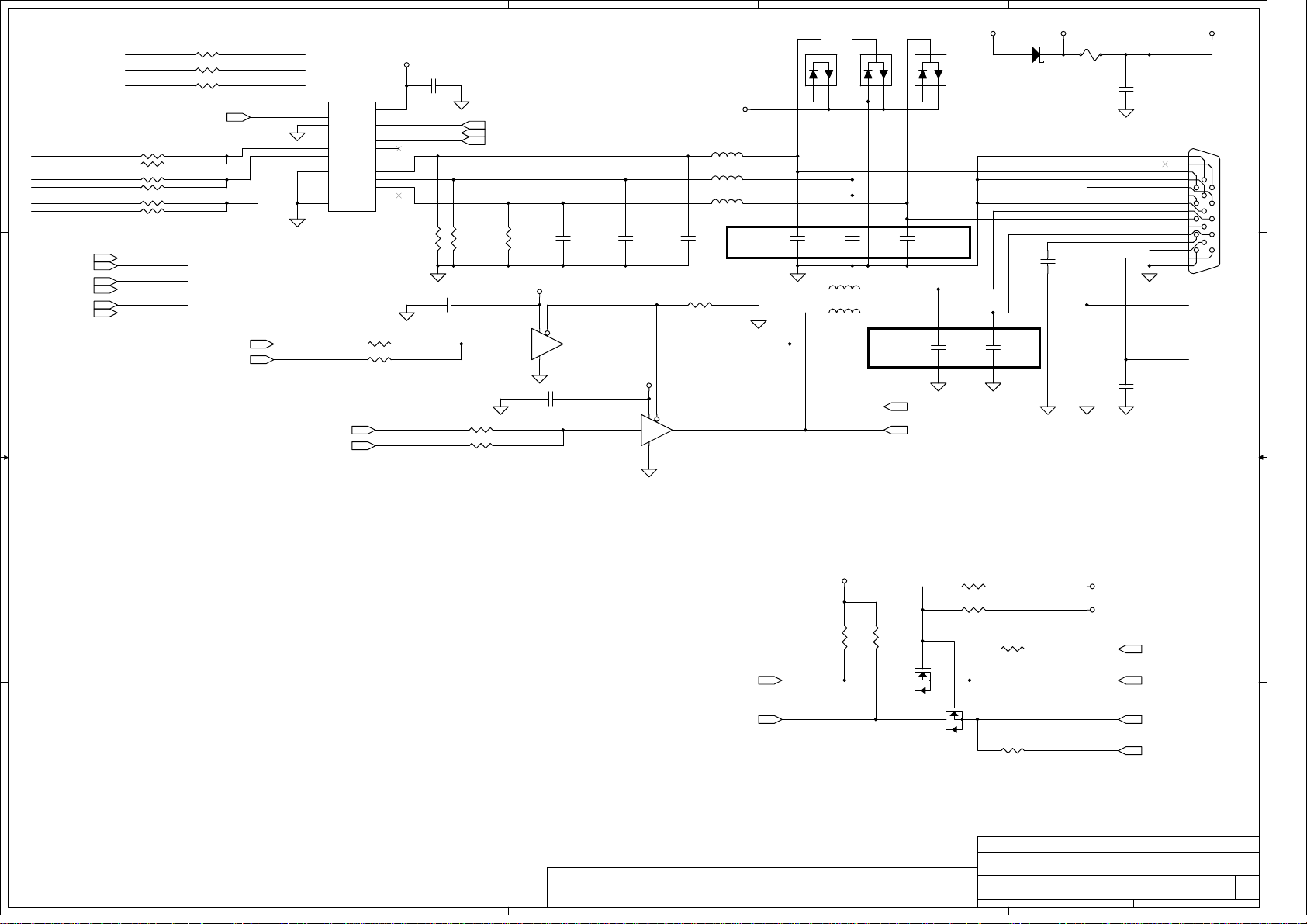

P02-Block Diagram

機密等 : B, D級

1 1

Compal Confidential

EFL50/ EFT51 Schematics Document

2 2

Intel Dothan/ Celeron M/ Alviso GM(PM) / DDR-2 / ICH6-M

(Daughter Card: ATi M24P/ M26P)

2005 / 02 / 03 (A-Test EVT)

Rev:0.1

3 3

4 4

P03-Notes List

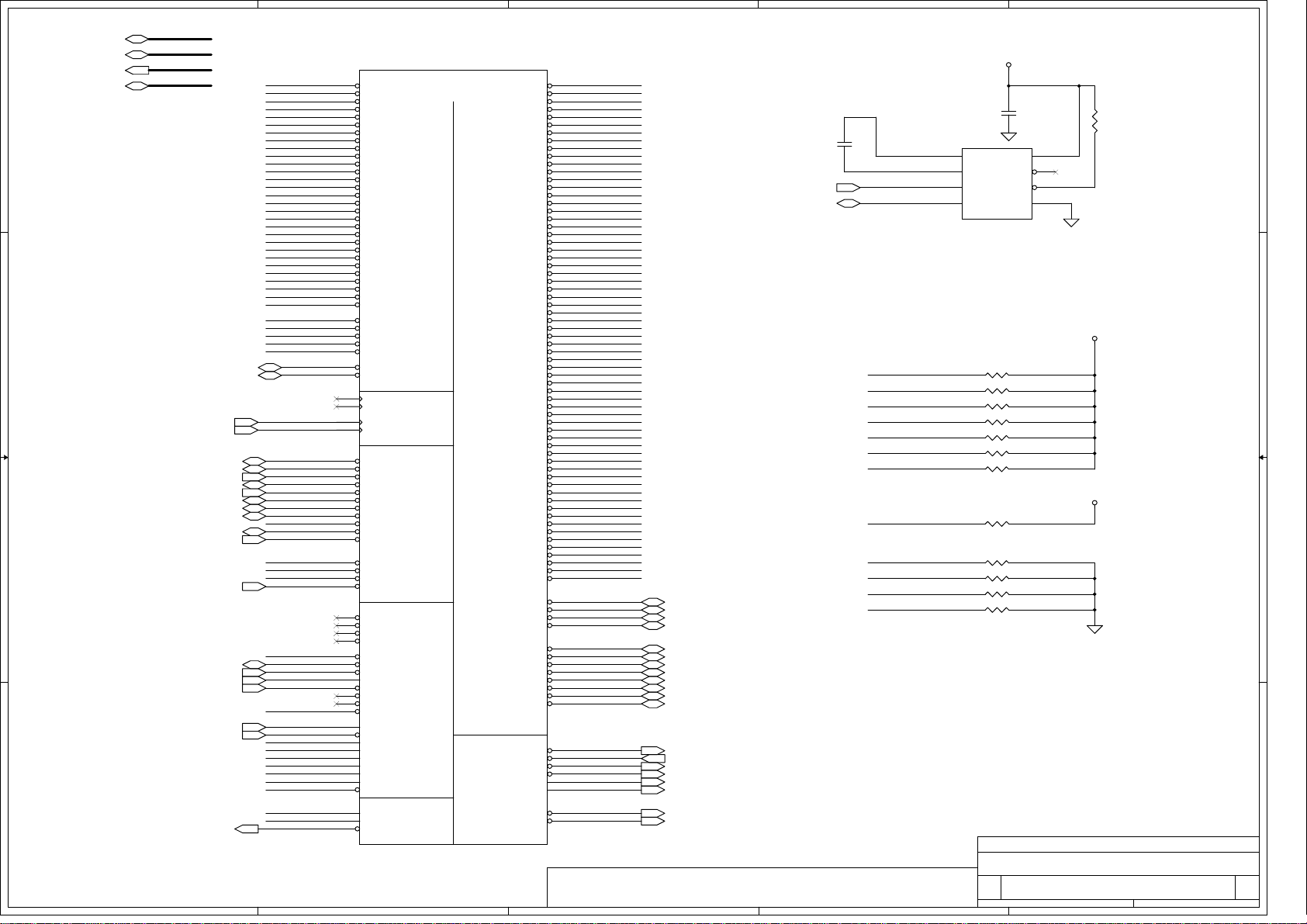

P04-Dothan(1/2)

P05-Dothan(2/2)

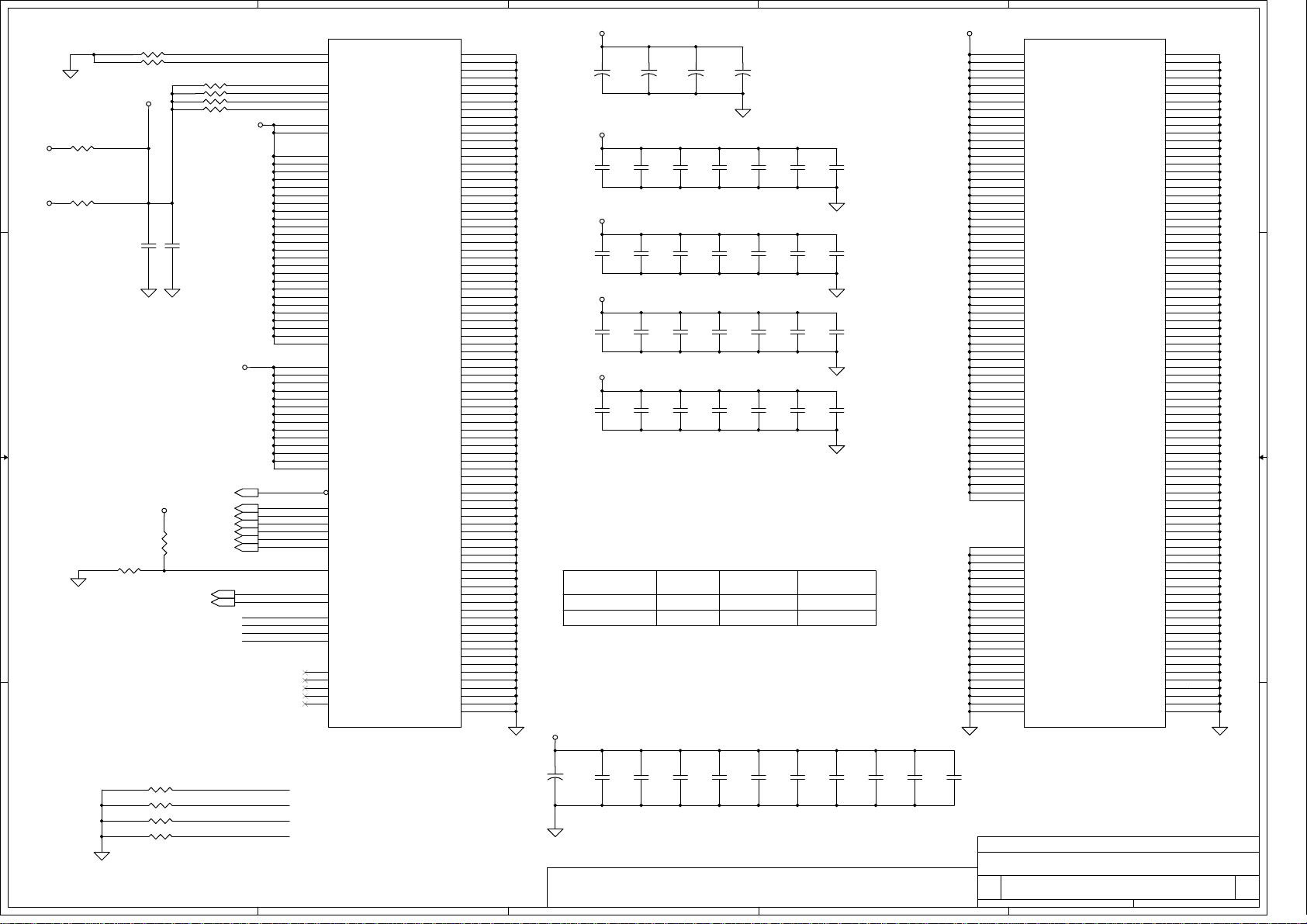

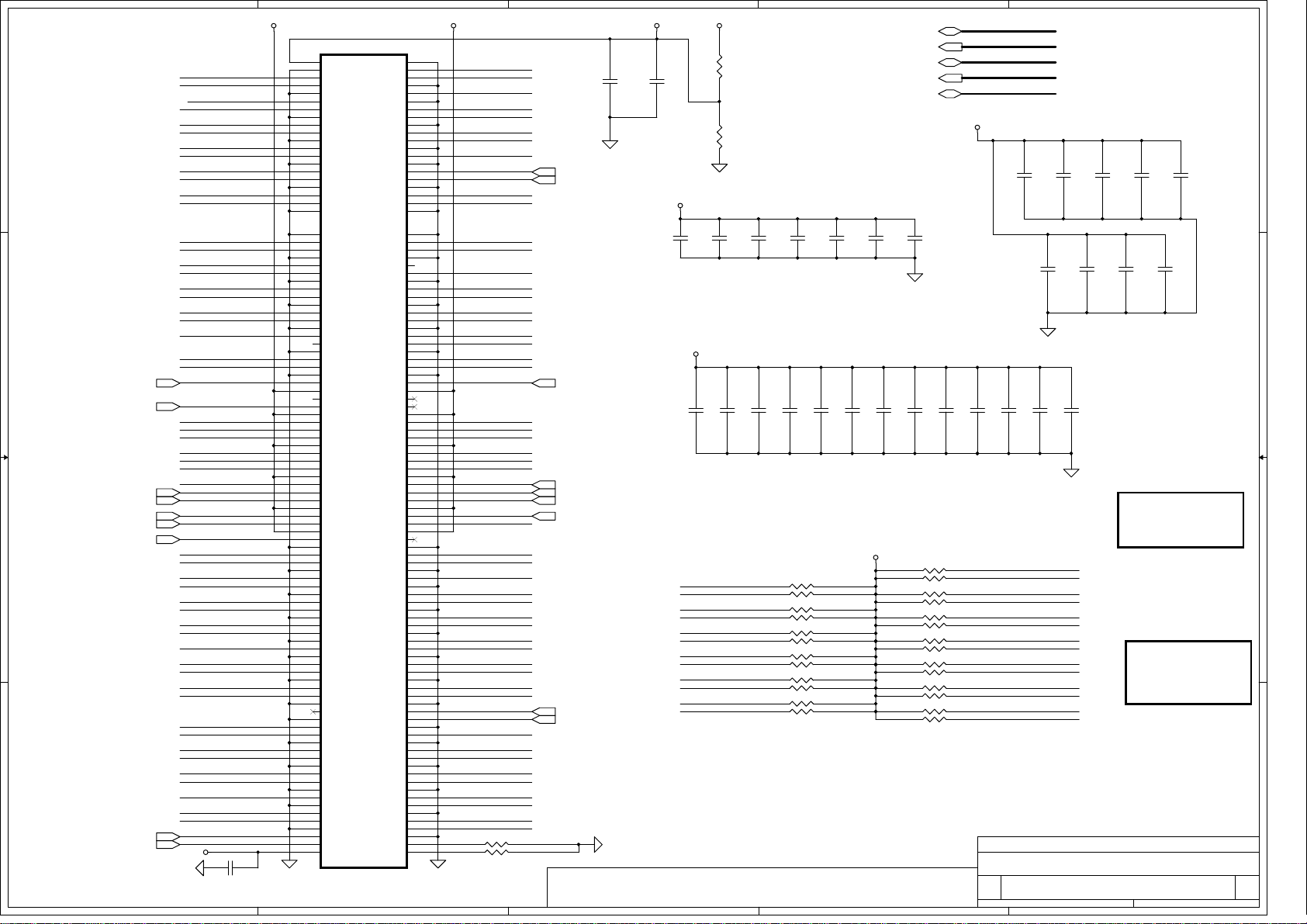

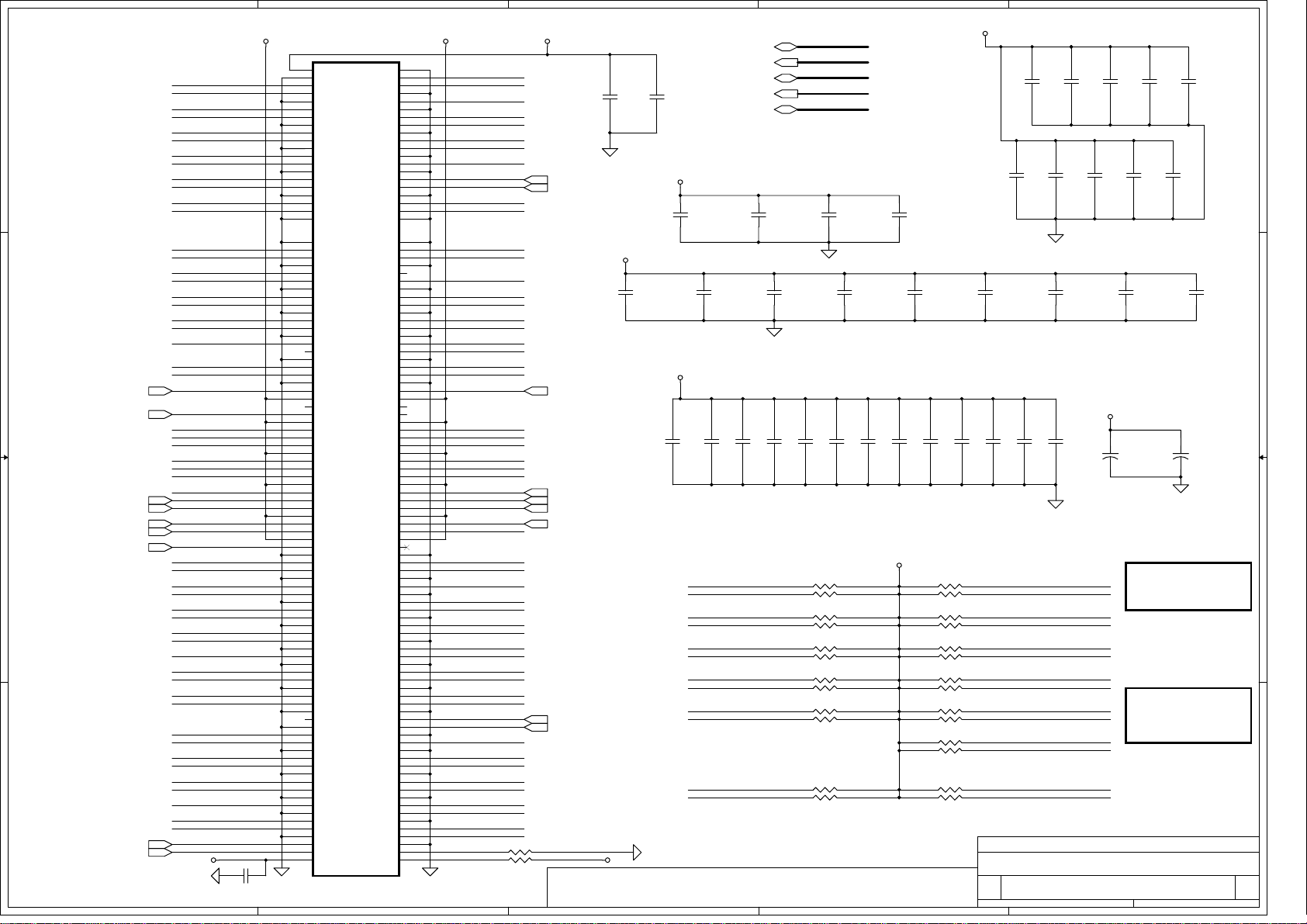

P06-Alviso HOST(1/5)

P07-Alviso DDR(2/5)

P08-Alviso PCI-E(3/5)

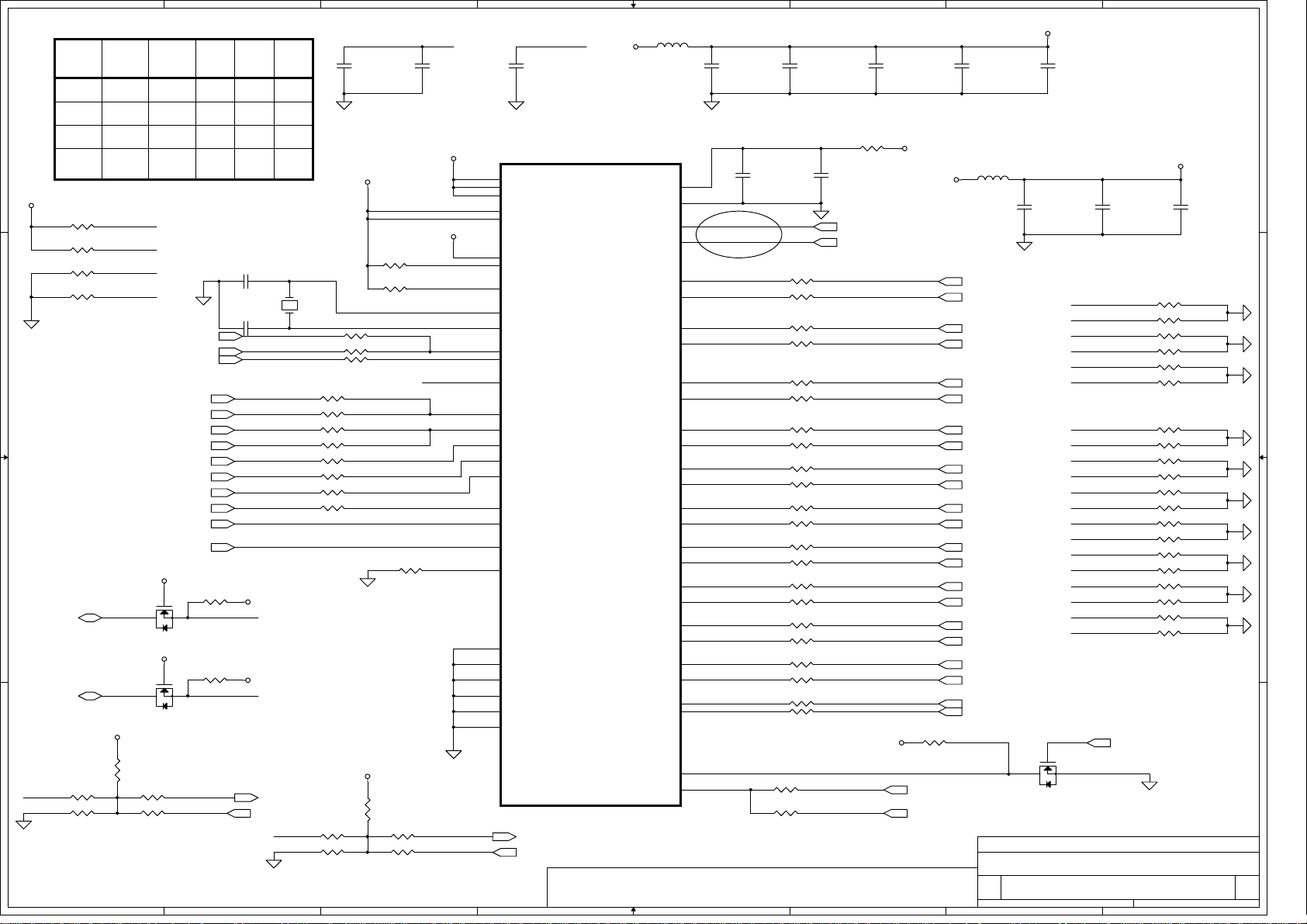

P09-Alviso POWER(4/5)

P10-Alviso POWER(5/5)

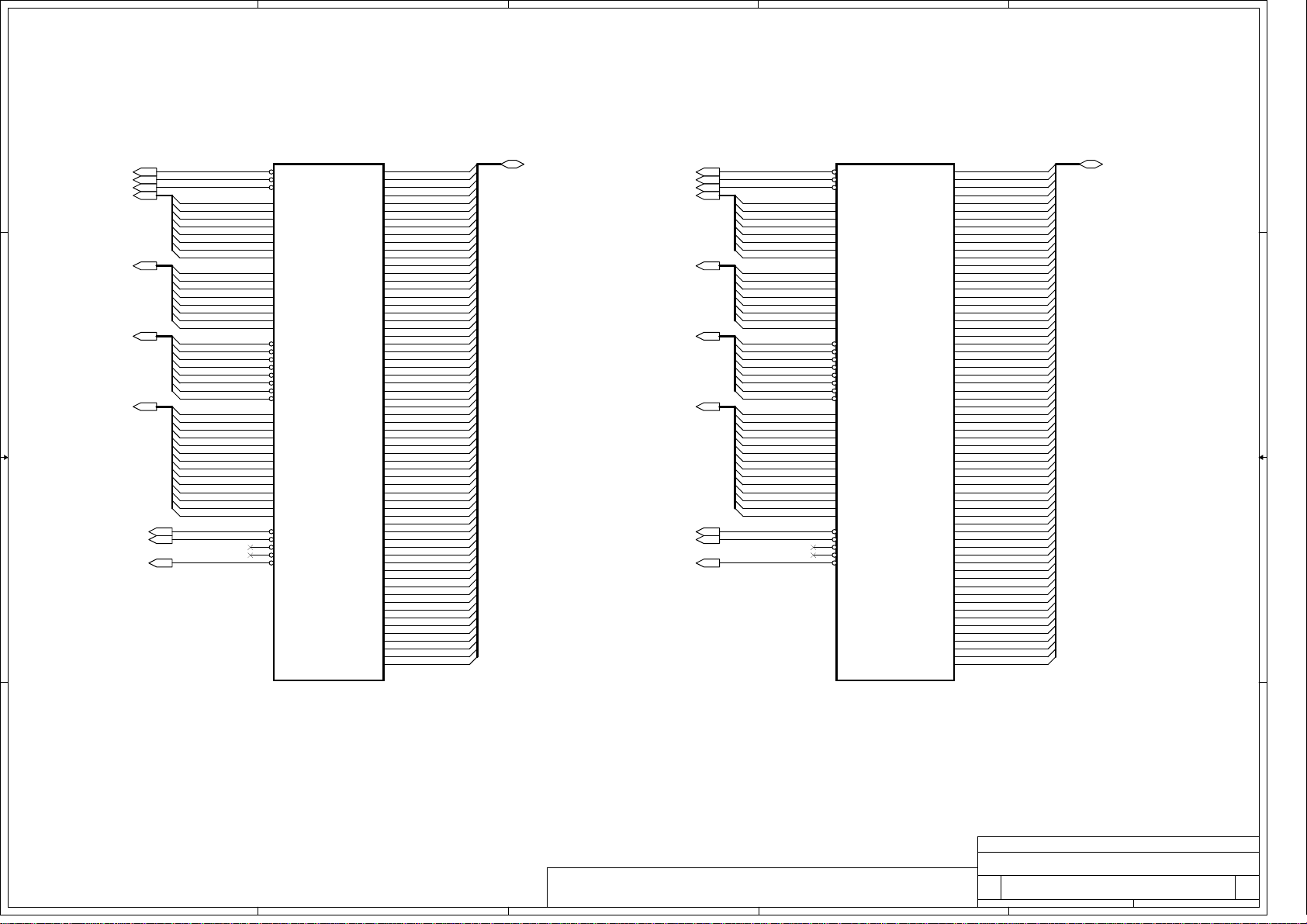

P11-DDRI-SODIMM0

P12-DDRI-SODIMM1

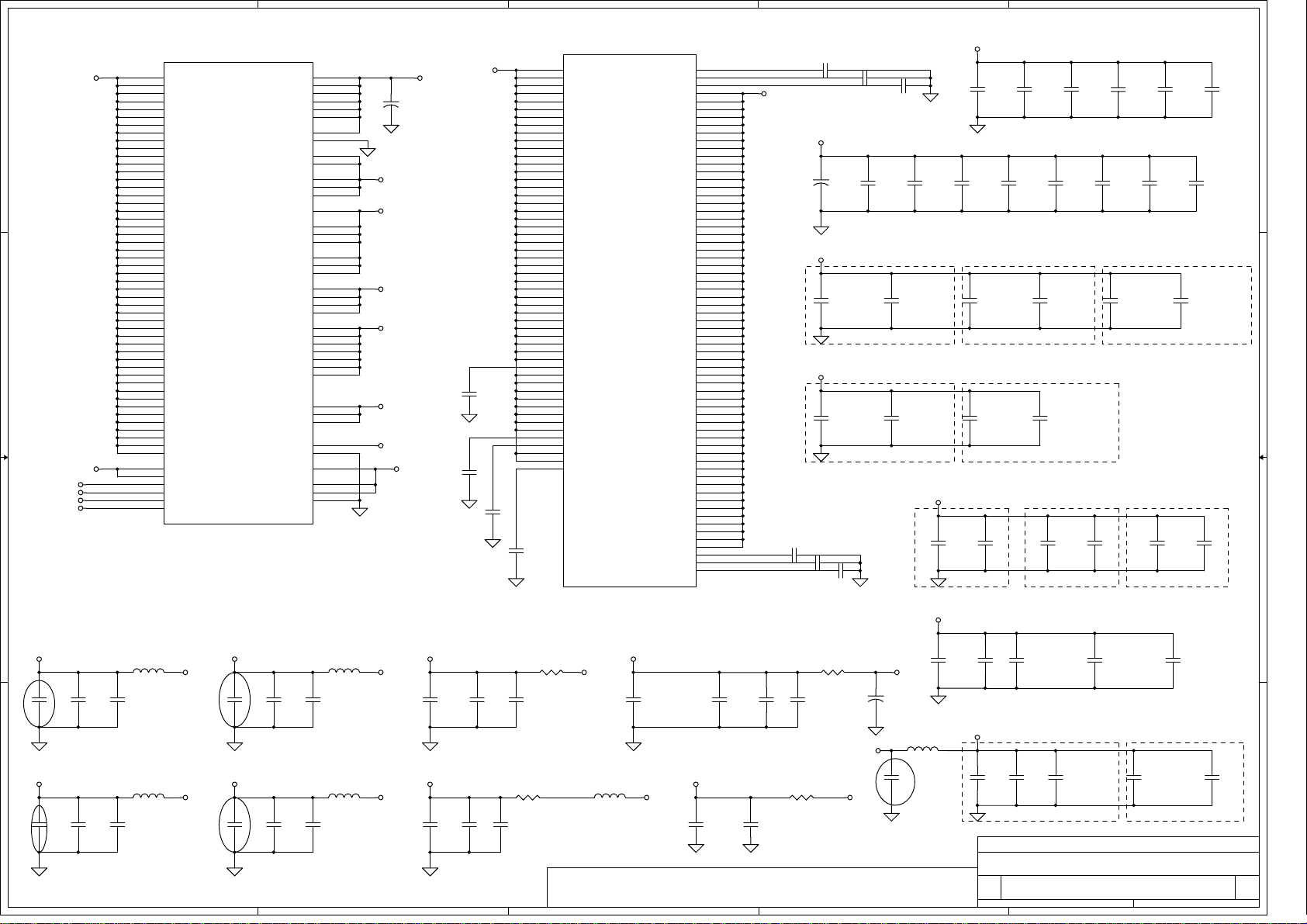

P13-DDR Decoupling

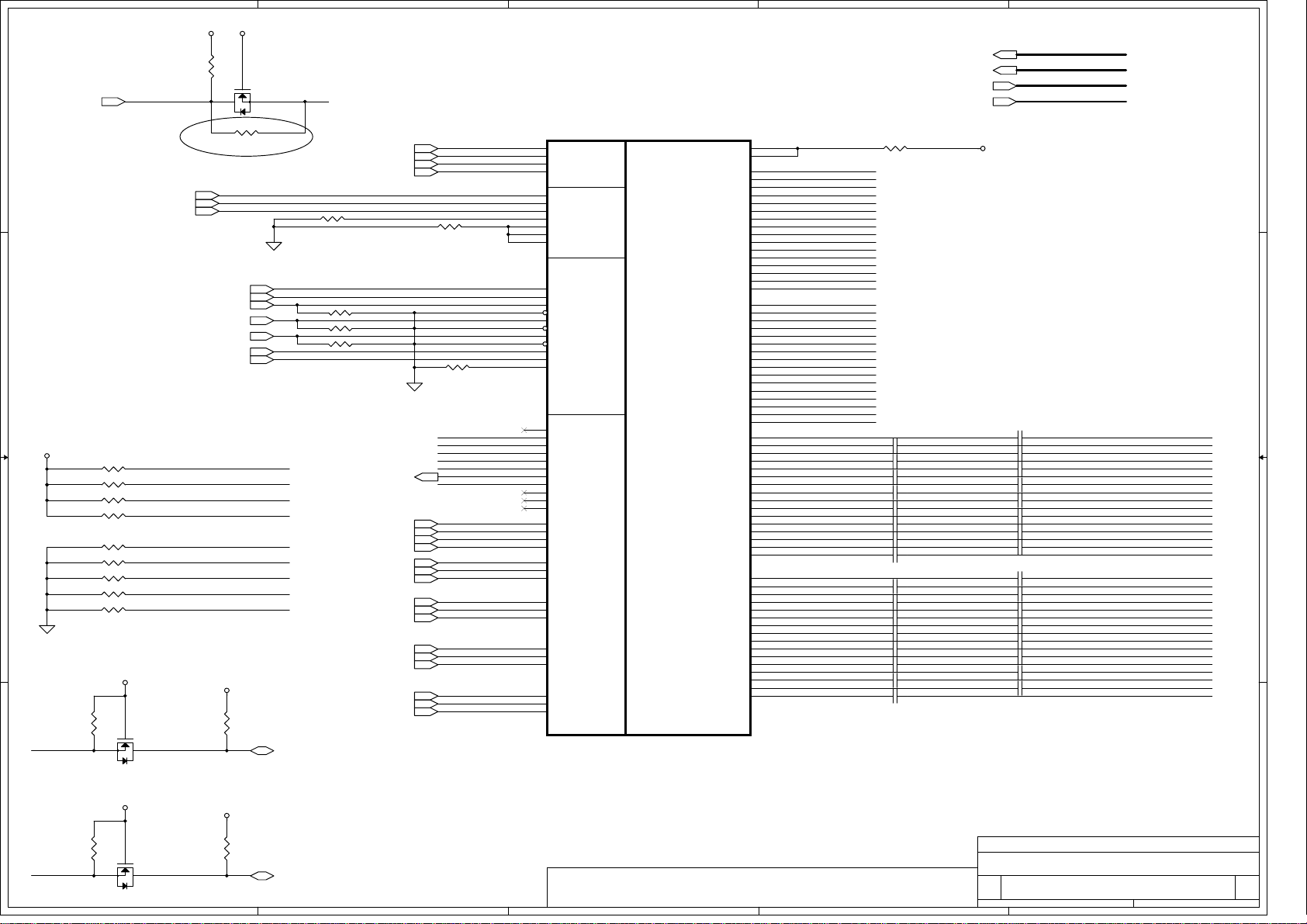

P14-Clock Generator

P15-CRT Conn.

P16-VGA / LCD Conn.

P17-ICH6(1/4)_HUB,PCI,HOST

P18-ICH6(2/4)_CPU,AC97,IDE,LPC

P19-ICH6(3/4)_USB,PM,LAN,GPIO

P20-ICH6(4/4)_POWER&GND

P21-HDD/CDROM

P22-DVI / TV_Out Conn

P23-PCMCIA ENE CB1410 & CB714

P24-PCMCIA SOCKET

P25-TI 1394A TSB43AB21A

P26-LAN BCM5788M

P27-LAN Magnetic & RJ45/RJ11

P28-Mimi-PCI Slot

P29-AC97 Codec_ALC250D

P30-Audio Line in Switch

P31-AMP & Audio Jack

P32-Super IO SMC217

P33-ENE-KB910

P34-MDC / BT / KBD / TP Conn.

P35-BIOS & I/O Port & SATA HDD

P36-RJ11/LID Switch / Fan / FIR

P37-USB2.0 Conn

P38-Docking Conn.

P39-PWR_OK / RTC

P40-DC INTERFACE

P41-Screws

P42-PWR-DCIN / Precharge

P43-PWR-Charger

P44-PWR-Battery Select

P45-PWR-3V/5V/12V

P46-PWR-GMCH_CORE/1.8V/0.9V

P47-PWR-1.5V/2.5V

P48-PWR-CPU_CORE

P49-PWR-OTP

P50-PWR-PIR

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Size Do cum e nt Number R e v

Dat e : Sheet

Compal Electronics, Inc.

SCHEM A T I C , M / B L A -2761

401344

期三 四月

E

A

of

151¬P , 27, 2005

A

Compal confidential

B

C

D

E

Project Code: EFL50/ EFT51

File Name : LA-2761

CRT & TV-OUT

1 1

page 15

Intel Dothan/ Celeron M CPU

page 4,5

H_A#(3 ..31)

FSB

400 / 533 Mhz

Therma l Sensor

ADM1032ARM

page 4

H_D#(0..63)

Clock Generator

ICS954226AGT

page 14

ATi M24P/ M26P

VGA Board

page 16

Intel Alviso GM(PM)

DDR-2

DDRII-SO-DIMM X2

BANK 0, 1, 2, 3

page 11,12,13

PCBGA 1257

LCD CONN

page 16

page 6,7,8,9,10

Two Channel DDR-2

DMI

2 2

Daughter Card Slot

PCI-E BUS

USB 2.0

USB conn x 3

page 37

PCI-Express x16

Intel ICH6-M

PCI BUS

Mini PCI

Socket

page 28

3 3

BroadCOM

BCM4 401KFB

BC M5788M

page 26

RJ45 CONN

page 27

ENE Controller

CB712

Slot 0

page 24

3in1 CardReader

Slot

page 23,24

page 24

1394 Controller

TSB43AB21

page 25

1394

Conn.

page 25

LPC BUS

Power On/Off CKT.

page 39

SMsC LPC47N217

DC/DC Interface CKT.

page 40

RTC CKT.

page 39

page 32

mBGA-609

page 17,18,19,20

ENE KB910Q

USB 2.0

AC-LINK

SATA

PATA

page 33

BT Conn

page 34

Audio CKT

ALC250-D

MDC Conn.

page 29

page 36

SATA HDD Conn.

page 21

HDD Conn.

CDROM Conn.

page 21

AMP & Audio Jack

RJ11 CONN

page 31

page 36

Docking Conn.

PCI-E Bridge

RJ45

VGA

DVI

TV-Out

HP-Out/ Line-Out

Mic-in/ Line-in

SPDIF

Parallel Port

Jack x2

page 36

Serial Port

Int. KBD

Power Circuit DC/DC

4 4

page 42~49

Power OK CKT.

page 39

Parellel Port

page 38

Serial Port

DOCKING CONNDOCKING CONN

page 38

Touch Pad

CONN.

page 34

Button

LED

page 38

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

page 34

BIOS

page 35

Title

Size Do cum e nt Number R e v

D

Dat e : Sheet

KB/ Mou se (PS/2)

Compal Electronics, Inc.

SCHEM A T I C , M / B L A -2761

401344

期三 四月

E

page 39

251¬P , 27, 2005

A

of

A

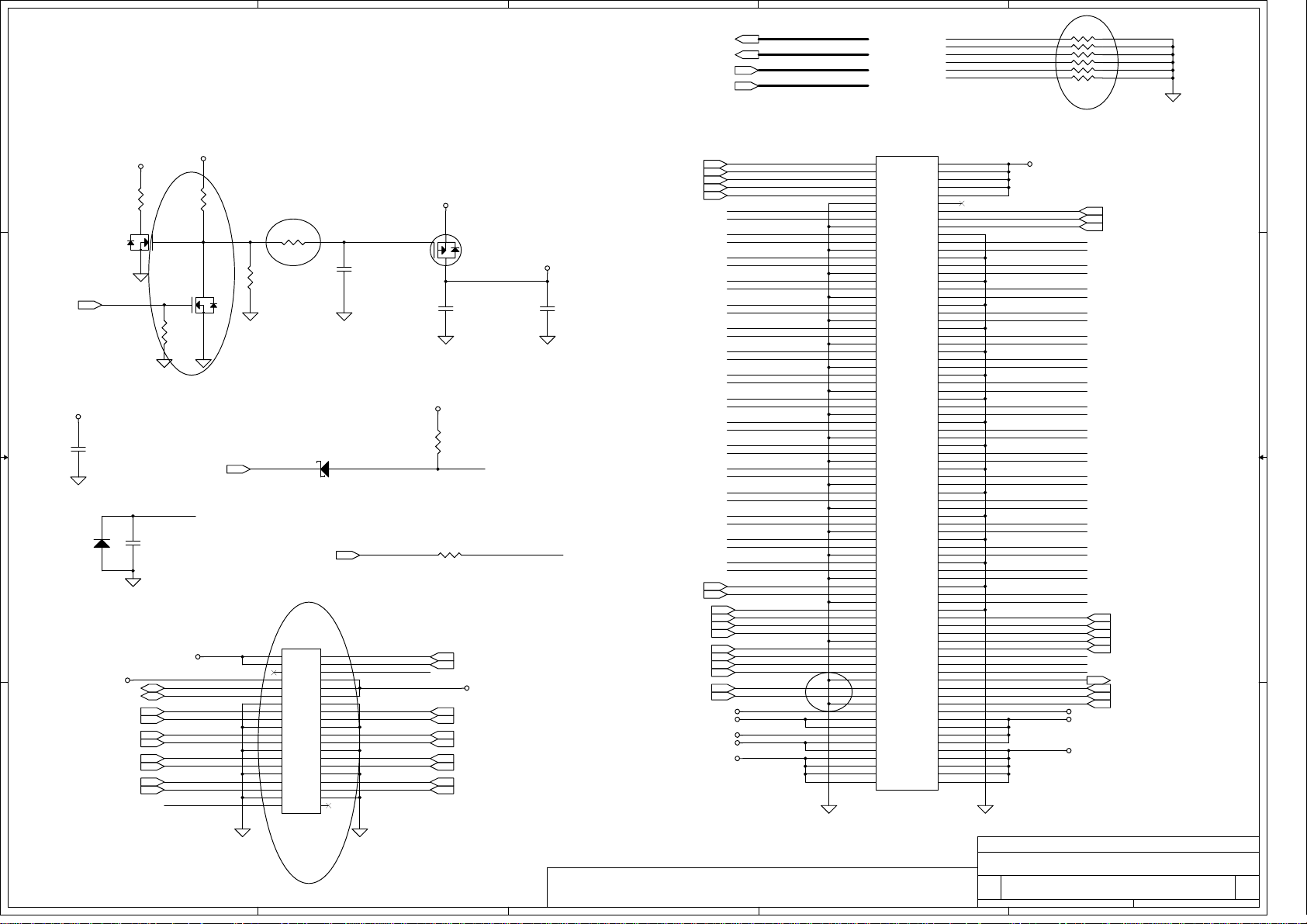

Voltage Rails

Power Plane Description

1 1

2 2

VIN

B+

+CPU_CORE

+1.05VS

+D DR VTT 0.9V switched power r a il f o r DDR t e r minator

+1.5VALW 1.5V always on power rail

+1.5VS

+1.8VS 1.8V switched power rail

+DDRVCC

+2.5VS

+3VALW

+3V

+3VS

+5VALW

+5VS

+5VMOD 5V switched power rail for Module Bay

+12VALW 12V always on power rail

+RTC VCC RTC power

Adapte r power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

1.05V switched power rail

1.5V switched power rail

1.8V power rail for DDR

2.5V switched power rail

3.3V always on power rail

3.3V power rail

3.3V switched power rail

5V always on power rail

5V switched power rail

B

S1 S3 S4/ S5

N/A N/A N/A

ON OFF

ON OFF

ON OFF O FF

ON

ON OFF O FF

ON OFF OFF

ON

ON

ON

ON

ON

ON

ON ONON

N/AN/AN/A

OFF

OFF

ON*ON

OFF

ON

OFF

OFF

ON ON*

OFF

ON

OFF

OFF

ON

ON*

OFF

OFFON

OFF OFFON

ONON ON*

C

STATE

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

SIGNAL

SLP_S1# SLP_S3#

HIGH HIGH HIGH HIGH

LOW

LOW

LOW LOW LOW LOW

D

LOW

Board ID / SKU I D Ta ble for A D c hanne l

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7NC

100K +/- 5%Ra / Rc

Rb / Rd V min

AD_BID

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

E

SLP_S4# SLP_S5# +VALW +V +VS Clock

0 V

HIGH

LOWLOWLOW

ON

HIGHHIGHHIGH

HIGH

HIGH

Vtyp

ON

ON

ON

ON

AD_BID

0 V 0 V

0.503 V

0.819 V

ON

ON

ON

OFF

OFF

V

AD_BID

0.538 V

0.875 V

ON ON

ON

OFF

OFF

OFF

max

1.185 V 1.264 V

2.200 V

3.300 V

2.341 V

3.300 V

LOW

OFF

OFF

OFF

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

External PCI Devices

Device IDSEL# REQ# / G NT # Interrupts

CardBus

1394

SD

Mini-PCI

LAN

3 3

AD20

AD16 0

AD20

AD18

AD17 3

2

2

1

PIRQ A/PI RQB

PIRQE

PIRQ A/PI RQB

PIRQG/PIRQH

PIRQF

BOARD ID Table

Board ID

0

1

2

3

4

5

6

7

PCB Revision

0.1

BTO Item BOM Structure

UMA

Discrete

LAN 10/100

LAN GIGA

1 Spindle 1S@

2 Spindle 2S@

2 Spindle with SATA

1 Spindle with SATA

EC SM Bus1 address

Device

Smart Battery

EEPROM( 24C16/ 02)

(24C04)

Address Address

1010 000X b

1011 000Xb

EC SM Bus2 address

Device

ADM1032

1001 110X b0001 011X b

SKU ID Table

SKU ID

0

1

2

SKU

1 Spindle with PATA

With Docking

Without Docking

With 1394

With 1394 4pin

With 1394 6pin

BTO Opt ion Ta ble

GM@

PM@

4401@

5788@

2SS@

2SP@2 Spindle with PATA

1SS@

1SP@

WD@

ND@

1394@

1394<4>@

1394<6>@

3

4

5

ICH6M SM Bus address

Device

4 4

Clock G e ne rator

(ICS 954226AGT)

DDRII DIMM0

DDRII DIMM2

A

Address

1101 001Xb

1001 000Xb

1001 010Xb

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

6

7

Title

Size Do cum e nt Number R e v

D

Dat e : Sheet

Compal Electronics, Inc.

SCHEM A T I C , M / B L A -2761

401344

期三 四月

E

A

of

351¬P , 27, 2005

5

4

3

2

1

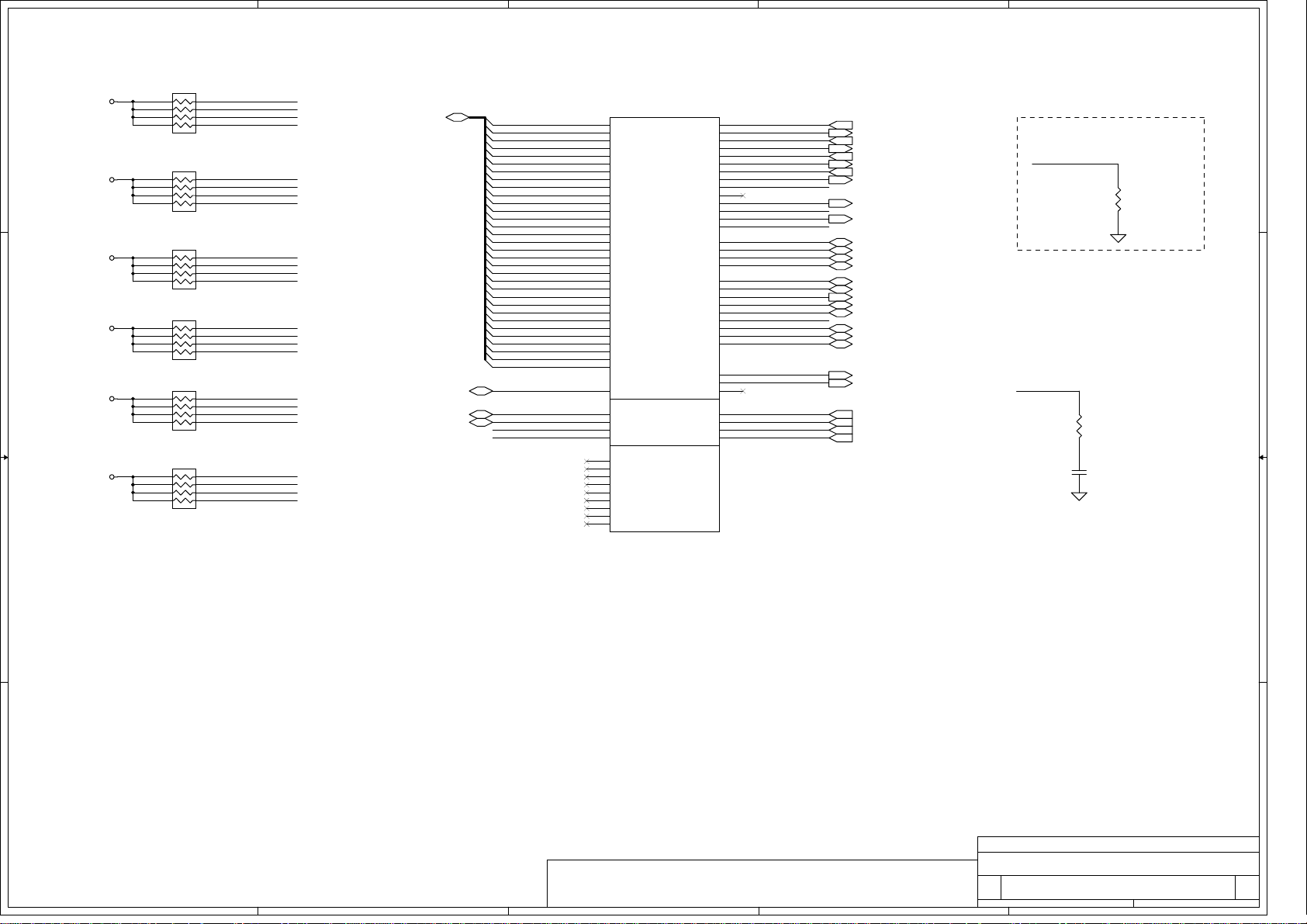

H_A#[3..31]6

H_REQ#[0..4]6

H_RS#[0..2]6

H_D#[0..63]6

D D

C C

B B

A A

H_A#[3..31]

H_REQ#[0..4]

H_RS#[0..2]

H_D#[0..63]

CLK_CPU_BCLK13

CLK_CPU_BCLK#13

H_THERMTRIP#6,17

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#06

H_ADSTB#16

H_ADS#6

H_BNR#6

H_BPRI#6

H_BR0#6

H_DEFER#6

H_DRDY#6

H_HIT#6

H_HITM#6

H_LOCK#6

H_CPURST#6

H_TRDY#6

H_DBSY#6

H_DPSLP#17

H_DPRSTP#17

H_DPWR#6

H_PWRGOOD17

H_CPUSLP#6,17

H_ADSTB#0

H_ADSTB#1

CLK_CPU_BCLK

CLK_CPU_BCLK#

H_ADS#

H_BNR#

H_BPRI#

H_BR0#

H_DEFER#

H_DRDY#

H_HIT#

H_HITM#

H_IERR#

H_LOCK#

H_CPURST#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

ITP_DBRRESET#

H_DBSY#

H_DPSLP#

H_DPRSTP#

H_DPWR#

PRO_CHOT#

H_PWRGOOD

H_CPUSLP#

ITP_TCK

ITP_TDI

ITP_TDO

TEST1

TEST2

ITP_TMS

ITP_TRST#

THERMDA

THERMDC

H_THERMTRIP#

JP20A

P4

A3#

U4

A4#

V3

A5#

R3

A6#

V2

A7#

W1

A8#

T4

A9#

W2

A10#

Y4

A11#

Y1

A12#

U1

A13#

AA3

A14#

Y3

A15#

AA2

A16#

AF4

A17#

AC4

A18#

AC7

A19#

AC3

A20#

AD3

A21#

AE4

A22#

AD2

A23#

AB4

A24#

AC6

A25#

AD5

A26#

AE2

A27#

AD6

A28#

AF3

A29#

AE1

A30#

AF1

A31#

R2

REQ0#

P3

REQ1#

T2

REQ2#

P1

REQ3#

T1

REQ4#

U3

ADSTB0#

AE5

ADSTB1#

A16

ITP_CLK0

A15

ITP_CLK1

B15

BCLK0

B14

BCLK1

N2

ADS#

L1

BNR#

J3

BPRI#

N4

BR0#

L4

DEFER#

H2

DRDY#

K3

HIT#

K4

HITM#

A4

IERR#

J2

LOCK#

B11

RESET#

H1

RS0#

K1

RS1#

L2

RS2#

M3

TRDY#

C8

BPM0#

B8

BPM1#

A9

BPM2#

C9

BPM3#

A7

DBR#

M2

DBSY#

B7

DPSLP#

G1

DPRSTP#

C19

DPWR#

A10

PRDY#

B10

PREQ#

B17

PROCHOT#

E4

PWRGOOD

A6

SLP#

A13

TCK

C12

TDI

A12

TDO

C5

TEST1

F23

TEST2

C11

TMS

B13

TRST#

B18

THERMDA

A18

THERMDC

C17

THERMTRIP#

TYCO_1612365-1_Dothan

THERMDA & THERMDC Trace / Space = 10 / 10 mil

5

Dothan

ADDR GROUP

HOST CLK

CONTROL GROUP

MISC

THERMAL

DIODE

4

DATA GROUP

LEGACY CPU

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DINV0#

DINV1#

DINV2#

DINV3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

A20M#

FERR#

IGNNE#

INIT#

LINT0

LINT1

STPCLK#

SMI#

H_D#1

A25

H_D#2

A22

H_D#3

B21

H_D#4

A24

H_D#5

B26

H_D#6

A21

H_D#7

B20

H_D#8

C20

H_D#9

B24

H_D#10

D24

H_D#11

E24

H_D#12

C26

H_D#13

B23

H_D#14

E23

H_D#15

C25

H_D#16

H23

H_D#17

G25

H_D#18

L23

H_D#19

M26

H_D#20

H24

H_D#21

F25

H_D#22

G24

H_D#23

J23

H_D#24

M23

H_D#25

J25

H_D#26

L26

H_D#27

N24

H_D#28

M25

H_D#29

H26

H_D#30

N25

H_D#31

K25

H_D#32

Y26

H_D#33

AA24

H_D#34

T25

H_D#35

U23

H_D#36

V23

H_D#37

R24

H_D#38

R26

H_D#39

R23

H_D#40

AA23

H_D#41

U26

H_D#42

V24

H_D#43

U25

H_D#44

V26

H_D#45

Y23

H_D#46

AA26

H_D#47

Y25

H_D#48

AB25

H_D#49

AC23

H_D#50

AB24

H_D#51

AC20

H_D#52

AC22

H_D#53

AC25

H_D#54

AD23

H_D#55

AE22

H_D#56

AF23

H_D#57

AD24

H_D#58

AF20

H_D#59

AE21

H_D#60

AD21

H_D#61

AF25

H_D#62

AF22

H_D#63

AF26

H_DINV#0

D25

H_DINV#1

J26

H_DINV#2

T24

H_DINV#3

AD20

H_DSTBN#0

C23

H_DSTBN#1

K24

H_DSTBN#2

W25

H_DSTBN#3

AE24

H_DSTBP#0

C22

H_DSTBP#1

L24

H_DSTBP#2

W24

H_DSTBP#3

AE25

H_A20M#

C2

H_FERR#

D3

H_IGNNE#

A3

H_INIT#

B5

H_INTR

D1

H_NMI

D4

H_STPCLK#

C6

H_SMI#

B4

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

H_DINV#0 6

H_DINV#1 6

H_DINV#2 6

H_DINV#3 6

H_DSTBN#0 6

H_DSTBN#1 6

H_DSTBN#2 6

H_DSTBN#3 6

H_DSTBP#0 6

H_DSTBP#1 6

H_DSTBP#2 6

H_DSTBP#3 6

H_A20M# 17

H_FERR# 17

H_IGNNE# 17

H_INIT# 17

H_INTR 17

H_NMI 17

H_STPCLK# 17

H_SMI# 17

2200P_0402_50V7K

EC_SMB_CK233

EC_SMB_DA233

C402

1

2

H_D#0

A19

THERMDA

THERMDC

EC_SMB_CK2

EC_SMB_DA2

U29

2

D+

3

D-

8

SCLK

7

SDATA

ADM1032ARM_RM8

SMBus Address: 1001110X (b)

ITP_TDI

ITP_TDO

H_CPURST#

ITP_TMS

PRO_CHOT#

H_PWRGOOD

H_IERR#

ITP_DBRRESET#

ITP_TRST#

ITP_TCK

TEST1

TEST2

2

R53 150_0402_5%

R383 54.9_0402_1%@

R382 54.9_0402_1%@

R54 40.2_0402_1%

R386 56_0402_5%

R56 200_0402_5%

R380 56_0402_5%

R381 150_0402_5%

R384 680_0402_5%

R385 27.4_0402_1%

R55 1K_0402_5%@

R401 1K_0402_5%@

+3VS

1

C401

0.1U_0402_16V4Z

2

VDD1

ALERT#

THERM#

GND

1

6

4

5

12

+1.05VS

R379

10K_0402_5%@

12

12

12

12

12

12

12

+3VS

12

12

12

12

12

Title

Size Do cum e nt Number R e v

Dat e : Sheet

Compal Electronics, Inc.

SCHEM A T I C , M / B L A -2761

401344

期三 四月

1

of

451¬P , 27, 2005

A

5

JP20B

+1.05VS

VCCSENSE

VSSSENSE

VCCA0

VCCA1

VCCA2

VCCA3

PSI#

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPU_VID5

GTL_REF0

CPU_BSEL0

CPU_BSEL1

COMP0

COMP1

COMP2

COMP3

AE7

VCCSENSE

AF6

VSSSENSE

F26

VCCA0

B1

VCCA1

N1

VCCA2

AC26

VCCA3

P23

VCCQ0

W4

VCCQ1

D10

VCCP

D12

VCCP

D14

VCCP

D16

VCCP

E11

VCCP

E13

VCCP

E15

VCCP

F10

VCCP

F12

VCCP

F14

VCCP

F16

VCCP

K6

VCCP

L5

VCCP

L21

VCCP

M6

VCCP

M22

VCCP

N5

VCCP

N21

VCCP

P6

VCCP

P22

VCCP

R5

VCCP

R21

VCCP

T6

VCCP

T22

VCCP

U21

VCCP

D6

VCC

D8

VCC

D18

VCC

D20

VCC

D22

VCC

E5

VCC

E7

VCC

E9

VCC

E17

VCC

E19

VCC

E21

VCC

F6

VCC

F8

VCC

F18

VCC

E1

PSI#

E2

VID0

F2

VID1

F3

VID2

G3

VID3

G4

VID4

H4

VID5

AD26

GTLREF

C16

BSEL0

C14

BSEL1

P25

COMP0

P26

COMP1

AB2

COMP2

AB1

COMP3

B2

RSVD

C3

RSVD

E26

RSVD

AF7

RSVD

AC1

RSVD

TYCO_1612365-1_Dothan

R144 54.9_0402_1%@

1 2

R141 54.9_0402_1%@

1 2

30 mils

R393 0_0603_5%

1 2

R388 0_0603_5%@

+VCCA

D D

1.8V FOR DOTHAN-A

1 2

+1.8VS

R419 0_1206_5%@

1 2

R387 0_0603_5%@

1 2

R417 0_0603_5%@

1 2

1.5V FOR DOTHAN-B

1 2

+1.5VS

R399 0_1206_5%

Trace Width>= 40 mils

C C

B B

+VCCA

0.01U_0402_16V7K

C405

R422

1K_0402_1%

1 2

R420 2K_0402_1%

1

2

+1.05VS

12

CPU_BSEL013

CPU_BSEL113

1

C463

2

10U_0805_10V4Z

+CPU_CORE

PSI#46

CPU_VID046

CPU_VID146

CPU_VID246

CPU_VID346

CPU_VID446

CPU_VID546

500 mils

R408 27.4_0402_1%

A A

50 mils

1 2

R407 54.9_0402_1%

1 2

R424 27.4_0402_1%

1 2

R425 54.9_0402_1%

1 2

COMP0

COMP1

COMP2

COMP3

TRACE CLOSELY CPU > 50 mils

COMP0, COMP2 layout : Width 18mils and Space 25mils

COMP1, COMP3 layout : Space 25mils

5

4

Dothan

POWER, GROUNG, RESERVED SIGNALS AND NC

4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

A2

A5

A8

A11

A14

A17

A20

A23

A26

B3

B6

B9

B12

B16

B19

B22

B25

C1

C4

C7

C10

C13

C15

C18

C21

C24

D2

D5

D7

D9

D11

D13

D15

D17

D19

D21

D23

D26

E3

E6

E8

E10

E12

E14

E16

E18

E20

E22

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

L22

L25

M1

3

+CPU_CORE

220U_D2_4VM_R12

1

C49

2

220U_D2_4VM_R12

+CPU_CORE

1

2

10U_0805_10V4Z

+CPU_CORE

1

2

10U_0805_10V4Z

+CPU_CORE

1

2

10U_0805_10V4Z

+CPU_CORE

1

2

10U_0805_10V4Z

Vcc-core

Decoupling

SPCAP,Polymer

MLCC 0805 X5R

+1.05VS

0.1U_0402_16V4Z

1

2

150U_D2_6.3VM

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

+

C404

2

+

10U_0805_10V4Z

C455

10U_0805_10V4Z

C423

10U_0805_10V4Z

C60

10U_0805_10V4Z

C71

C63

0.1U_0402_16V4Z

3

1

+

C50

2

220U_D2_4VM_R12

1

C456

2

10U_0805_10V4Z

1

C112

2

10U_0805_10V4Z

1

C57

2

10U_0805_10V4Z

1

C81

2

10U_0805_10V4Z

C,uF ESR, mohm ESL,nH

3X330uF 9m ohm/3 3.5nH/4

35X10uF 5m ohm/35 0.6nH/35

0.1U_0402_16V4Z

1

C68

2

1

+

C150

2

10U_0805_10V4Z

1

C424

2

10U_0805_10V4Z

1

C421

2

10U_0805_10V4Z

1

C61

2

10U_0805_10V4Z

1

C452

2

1

C78

2

220U_D2_4VM_R12

1

+

C151

2

1

1

C435

2

2

10U_0805_10V4Z

1

1

C420

2

2

10U_0805_10V4Z

1

1

C72

2

2

10U_0805_10V4Z

1

1

C113

2

2

10U_0805_10V4Z

0.1U_0402_16V4Z

1

1

C90

2

2

0.1U_0402_16V4Z

10U_0805_10V4Z

1

C443

2

10U_0805_10V4Z

1

C434

2

10U_0805_10V4Z

1

C82

2

10U_0805_10V4Z

1

C96

2

1

C75

2

0.1U_0402_16V4Z

1

C448

2

10U_0805_10V4Z

1

C442

2

10U_0805_10V4Z

1

C97

2

10U_0805_10V4Z

1

C108

2

10U_0805_10V4Z

0.1U_0402_16V4Z

1

C85

2

C453

C447

C109

C58

C43

0.1U_0402_16V4Z

2

0.1U_0402_16V4Z

1

C42

2

2

1

2

+CPU_CORE

1

C41

2

0.1U_0402_16V4Z

1

JP20C

F20

VCC

F22

VCC

G5

VCC

G21

VCC

H6

VCC

H22

VCC

J5

VCC

J21

VCC

K22

VCC

U5

VCC

V6

VCC

V22

VCC

W5

VCC

W21

VCC

Y6

VCC

Y22

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AB6

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC9

AC11

AC13

AC15

AC17

AC19

AD8

AD10

AD12

AD14

AD16

AD18

AE9

AE11

AE13

AE15

AE17

AE19

AF8

AF10

AF12

AF14

AF16

AF18

M4

M5

M21

M24

N3

N6

N22

N23

N26

P2

P5

P21

P24

R1

R4

R6

R22

R25

T3

T5

T21

T23

TYCO_1612365-1_Dothan

C98

Title

Size Do cum e nt Number R e v

Dat e : Sheet

Dothan

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

POWER, GROUND

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Compal Electronics, Inc.

SCHEM A T I C , M / B L A -2761

期三 四月

401344

T26

VSS

U2

VSS

U6

VSS

U22

VSS

U24

VSS

V1

VSS

V4

VSS

V5

VSS

V21

VSS

V25

VSS

W3

VSS

W6

VSS

W22

VSS

W23

VSS

W26

VSS

Y2

VSS

Y5

VSS

Y21

VSS

Y24

VSS

AA1

VSS

AA4

VSS

AA6

VSS

AA8

VSS

AA10

VSS

AA12

VSS

AA14

VSS

AA16

VSS

AA18

VSS

AA20

VSS

AA22

VSS

AA25

VSS

AB3

VSS

AB5

VSS

AB7

VSS

AB9

VSS

AB11

VSS

AB13

VSS

AB15

VSS

AB17

VSS

AB19

VSS

AB21

VSS

AB23

VSS

AB26

VSS

AC2

VSS

AC5

VSS

AC8

VSS

AC10

VSS

AC12

VSS

AC14

VSS

AC16

VSS

AC18

VSS

AC21

VSS

AC24

VSS

AD1

VSS

AD4

VSS

AD7

VSS

AD9

VSS

AD11

VSS

AD13

VSS

AD15

VSS

AD17

VSS

AD19

VSS

AD22

VSS

AD25

VSS

AE3

VSS

AE6

VSS

AE8

VSS

AE10

VSS

AE12

VSS

AE14

VSS

AE16

VSS

AE18

VSS

AE20

VSS

AE23

VSS

AE26

VSS

AF2

VSS

AF5

VSS

AF9

VSS

AF11

VSS

AF13

VSS

AF15

VSS

AF17

VSS

AF19

VSS

AF21

VSS

AF24

VSS

of

551¬P , 27, 2005

1

A

5

H_RS#[0..2]

H_A#[3..31]4

H_REQ#[0..4]4

D D

C C

CLK_MCH_BCLK#13

CLK_MCH_BCLK13

B B

H_A#[3..31]

H_ADSTB#04

H_ADSTB#14

H_DSTBN#04

H_DSTBN#14

H_DSTBN#24

H_DSTBN#34

H_DSTBP#04

H_DSTBP#14

H_DSTBP#24

H_DSTBP#34

H_DINV#04

H_DINV#14

H_DINV#24

H_DINV#34

H_CPURST#4

H_ADS#4

H_TRDY#4

H_DPWR#4

H_DRDY#4

H_DEFER#4

H_HITM#4

H_HIT#4

H_LOCK#4

H_BR0#4

H_BNR#4

H_BPRI#4

H_DBSY#4

CLK_MCH_BCLK#

CLK_MCH_BCLK

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_CPURST#

H_ADS#

H_TRDY#

H_DPWR#

H_DRDY#

H_DEFER#

H_HITM#

H_HIT#

H_LOCK#

H_BR0#

H_BNR#

H_BPRI#

H_DBSY#

Un-pop for Dothan-A

H_CPUSLP#4,17

A A

(5mil:15mil) (12mil:10mil)

H_VREF H_XSWING H_YSWING

1

C138

0.1U_0402_16V4Z

2

H_CPUSLP# CPU_SLP#

12

R405

100_0603_1%

12

R406

200_0603_1%

5

H_RS#[0..2] 4

U31A

H_A#3

G9

HA3#

A10

B10

E10

G10

E11

F10

G11

G13

C10

C11

D11

C12

B13

A12

F12

G12

E12

C13

B11

D13

A13

F13

A11

E13

AB1

AB2

H10

C9

E9

B7

F9

D8

D9

A7

D7

B8

C7

A8

B9

G4

K1

R3

V3

G5

K2

R2

W4

H8

K3

T7

U5

F8

B5

G6

F7

E6

F6

D6

D4

B3

E7

A5

D5

C6

G8

A4

C5

B4

Alviso

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HPCREQ#

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HADSTB#0

HADSTB#1

HCLKN

HCLKP

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

HDINV#0

HDINV#1

HDINV#2

HDINV#3

HCPURST#

HADS#

HTRDY#

HDPWR#

HDRDY#

HDEFER#

HEDRDY#

HHITM#

HHIT#

HLOCK#

HBREQ0#

HBNR#

HBPRI#

HDBSY#

HCPUSLP#

HRS0#

HRS1#

HRS2#

1

C459

0.1U_0402_16V4Z

2

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CPU_SLP#

H_RS#0

H_RS#1

H_RS#2

R130 0_0402_5%

1 2

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HOST

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HVREF

HXRCOMP

HXSCOMP

HYRCOMP

HYSCOMP

HXSWING

HYSWING

ALVISO_BGA1257

+1.05VS +1.05VS+1.05VS

12

R409

221_0603_1%

12

R411

100_0603_1%

E4

E1

F4

H7

E2

F1

E3

D3

K7

F2

J7

J8

H6

F3

K8

H5

H1

H2

K5

K6

J4

G3

H3

J1

L5

K4

J5

P7

L7

J3

P5

L3

U7

V6

R6

R5

P3

T8

R7

R8

U8

R4

T4

T5

R1

T3

V8

U6

W6

U3

V5

W8

W7

U2

U1

Y5

Y2

V4

Y7

W1

W3

Y3

Y6

W2

J11

C1

C2

T1

L1

D1

P1

4

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_VREF

H_XRCOMP

H_XSCOMP

H_YRCOMP

H_YSCOMP

H_XSWING

H_YSWING

H_D#[0..63]H_REQ#[0..4]

+1.8V

R120 24.9_0402_1%

R111 54.9_0402_1%

R151 24.9_0402_1%

R145 54.9_0402_1%

1 2

1 2

12

12

H_D#[0..63] 4

R162 40.2_0402_1%

1 2

R163 40.2_0402_1%

1 2

R165 80.6_0402_1%

1 2

R166 80.6_0402_1%

1 2

+1.05VS

3

DMI_ITX_MRX_N018

DMI_ITX_MRX_N118

DMI_ITX_MRX_N218

DMI_ITX_MRX_N318

DMI_ITX_MRX_P018

DMI_ITX_MRX_P118

DMI_ITX_MRX_P218

DMI_ITX_MRX_P318

DMI_MTX_IRX_N018

DMI_MTX_IRX_N118

DMI_MTX_IRX_N218

DMI_MTX_IRX_N318

DMI_MTX_IRX_P018

DMI_MTX_IRX_P118

DMI_MTX_IRX_P218

DMI_MTX_IRX_P318

M_CLK_DDR011

M_CLK_DDR111

M_CLK_DDR312

M_CLK_DDR412

M_CLK_DDR#011

M_CLK_DDR#111

M_CLK_DDR#312

M_CLK_DDR#412

DDR_CKE0_DIMMA11

DDR_CKE1_DIMMA11

DDR_CKE2_DIMMB12

DDR_CKE3_DIMMB12

DDR_CS0_DIMMA#11

DDR_CS1_DIMMA#11

DDR_CS2_DIMMB#12

DDR_CS3_DIMMB#12

10mils

10mils

(10mil:20mil)

H_XRCOMP & H_YRCOMP Trace / Space = 10 / 20 mil

12

R421

221_0603_1%

(12mil:10mil)

1

C149

0.1U_0402_16V4Z

2

4

12

R423

100_0603_1%

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

M_ODT011

M_ODT111

M_ODT212

M_ODT312

DMI_ITX_MRX_N0

DMI_ITX_MRX_N1

DMI_ITX_MRX_N2

DMI_ITX_MRX_N3

DMI_ITX_MRX_P0

DMI_ITX_MRX_P1

DMI_ITX_MRX_P2

DMI_ITX_MRX_P3

DMI_MTX_IRX_N0

DMI_MTX_IRX_N1

DMI_MTX_IRX_N2

DMI_MTX_IRX_N3

DMI_MTX_IRX_P0

DMI_MTX_IRX_P1

DMI_MTX_IRX_P2

DMI_MTX_IRX_P3

M_CLK_DDR0

M_CLK_DDR1

M_CLK_DDR3

M_CLK_DDR4

M_CLK_DDR#0

M_CLK_DDR#1

M_CLK_DDR#3

M_CLK_DDR#4

DDR_CKE0_DIMMA

DDR_CKE1_DIMMA

DDR_CKE2_DIMMB

DDR_CKE3_DIMMB

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

DDR_CS2_DIMMB#

DDR_CS3_DIMMB#

M_OCDCOMP0

M_OCDCOMP1

M_ODT0

M_ODT1

M_ODT2

M_ODT3

M_RCOMPN

M_RCOMPP

SMVREF

M_XSLEW

M_YSLEW

10mils

+1.8V

R164

1K_0402_1%

R158

1K_0402_1%

U31B

AA31

DMIRXN0

AB35

DMIRXN1

AC31

DMIRXN2

AD35

DMIRXN3

Y31

DMIRXP0

AA35

DMIRXP1

AB31

DMIRXP2

AC35

DMIRXP3

AA33

DMITXN0

AB37

DMITXN1

AC33

DMITXN2

AD37

DMITXN3

Y33

DMITXP0

AA37

DMITXP1

AB33

DMITXP2

AC37

DMITXP3

AM33

SM_CK0

AL1

SM_CK1

AE11

SM_CK2

AJ34

SM_CK3

AF6

SM_CK4

AC10

SM_CK5

AN33

SM_CK0#

AK1

SM_CK1#

AE10

SM_CK2#

AJ33

SM_CK3#

AF5

SM_CK4#

AD10

SM_CK5#

AP21

SM_CKE0

AM21

SM_CKE1

AH21

SM_CKE2

AK21

SM_CKE3

AN16

SM_CS0#

AM14

SM_CS1#

AH15

SM_CS2#

AG16

SM_CS3#

AF22

SM_OCDCOMP0

AF16

SM_OCDCOMP1

AP14

SM_ODT0

AL15

SM_ODT1

AM11

SM_ODT2

AN10

SM_ODT3

AK10

SMRCOMPN

AK11

SMRCOMPP

AF37

SMVREF0

AD1

SMVREF1

AE27

SMXSLEWIN

AE28

SMXSLEWOUT

AF9

SMYSLEWIN

AF10

SMYSLEWOUT

ALVISO_BGA1257

12

0.1U_0402_16V4Z

12

C185

1

2

CFG10

CFG11

CFG12

DMIDDR MUXING

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

RSVD21

RSVD22

CFG/RSVD

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

BM_BUSY#

EXT_TS0#

EXT_TS1#

THRMTRIP#

PWROK

RSTIN#

PM

DREF_CLKN

DREF_CLKP

DREF_SSCLKP

CLK

DREF_SSCLKN

NC

SMVREF

1

C179

0.1U_0402_16V4Z

2

2

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

2

CLK_DREF_SSC

CLK_DREF_SSC#

CFG0

G16

MCH_CLKSEL1

H13

MCH_CLKSEL0

G14

F16

F15

CFG5

G15

CFG6

E16

CFG7

D17

J16

CFG9

D15

E15

D14

CFG12

E14

CFG13

H12

C14

H15

CFG16 CFG6

J15

H14

CFG18

G22

CFG19

G23

D23

G25

G24

J17

A31

A30

D26

D25

PM_BMBUSY#

J23

EXT_TS#0

J21

EXT_TS#1

H22

H_THERMTRIP#

F5

VGATE

AD30

PLT_RST#

AE29

CLK_DREF_96M#

A24

CLK_DREF_96M

A23

CLK_DREF_SSC

D37

CLK_DREF_SSC#

C37

AP37

AN37

AP36

AP2

AP1

AN1

B1

A2

B37

A36

A37

CFG[2:0]

CFG5

CFG6

CFG7

CFG9

CFG[13:12]

CFG16

(FSB Dynamic

ODT)

CFG18

(VCC Se lect)

CFG19

(VTT Se l e c t )

Title

Size Do cum e nt Number R e v

Dat e : Sheet

R114 0_0402_5%PM@

1 2

R122 0_0402_5%PM@

1 2

MCH_CLKSEL1 13

MCH_CLKSEL0 13

CFG0

R131 10K_0402_5%

1 2

CFG0

R132 1K_0402_5%@

CFG5

CFG7

CFG9

CFG12

CFG13

CFG16

1 2

R127 1K_0402_5%@

1 2

R124 1K_0402_5%

1 2

R117 1K_0402_5%@

1 2

R119 1K_0402_5%@

1 2

R125 1K_0402_5%@

1 2

R137 1K_0402_5%@

1 2

R140 1K_0402_5%@

1 2

CFG[17:3]: internal pu ll-u p

CFG18

R128 1K_0402_5%@

CFG19

1 2

R135 1K_0402_5%@

1 2

CFG[19:1 8 ] : i n t e rnal pu l l - down

PM_BMBUSY# 18

H_THERMTRIP# 4,17

VGATE 13,18,46

PLT_RST# 16,18,20,32,33,41

CLK_DREF_96M# 13

CLK_DREF_96M 13

CLK_DREF_SSC 13

CLK_DREF_SSC# 13

EXT_TS#0

R139 10K_0402_5%

EXT_TS#1

1 2

R136 10K_0402_5%

1 2

Refer to sheet 6 for FSB

frequency select

Low = DMI x 2

High = DMI x 4

Low = DDR-II

High = DDR-I

Low = DT/Tr a n s p ortable CPU

High = Mobile CPU

Low = Reverse Lane

High = N o rmal Operation

00 = Reserved

01 = XOR Mode Enabled

10 = Al l Z Mode Enabled

11 = Normal Operation (Default)

Low = Disabled

High = Enabled

Low = 1.05V (Default)

High = 1.5V

Low = 1.05V (Default)

High = 1.2V

Compal Electronics, Inc.

SCHEM A T I C , M / B L A -2761

401344

期三 四月

1

+1.5VS

+1.05VS

+2.5VS

+2.5VS

*

*

*

*

*

*

*

*

A

of

651¬P , 27, 2005

1

5

D D

4

3

2

1

DDR_A_BS#011

DDR_A_BS#111

DDR_A_BS#211

DDR_A_DM[0..7]11

DDR_A_DQS[0..7]11

C C

B B

DDR_A_DQS#[0..7]11

DDR_A_MA[0..13]11

DDR_A_CAS#11

DDR_A_RAS#11

DDR_A_WE#11 DDR_B_WE#12

DDR_A_BS#0

DDR_A_BS#1

DDR_A_BS#2

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_CAS#

DDR_A_RAS#

DDR_A_WE# DDR_B_WE#

AK15

AK16

AL21

AJ37

AP35

AL29

AP24

AP9

AP4

AJ2

AD3

AK36

AP33

AN29

AP23

AM8

AM4

AJ1

AE5

AK35

AP34

AN30

AN23

AN8

AM5

AH1

AE4

AL17

AP17

AP18

AM17

AN18

AM18

AL19

AP20

AM19

AL20

AM16

AN20

AM20

AM15

AN15

AP16

AF29

AF28

AP15

SA_BS0#

SA_BS1#

SA_BS2#

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS#

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

SA_WE#

U31C

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQ32

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SADQ38

SADQ39

SADQ40

SADQ41

SADQ42

SADQ43

DDR MEMORY SYSTEM A

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SADQ55

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

ALVISO_BGA1257

AG35

AH35

AL35

AL37

AH36

AJ35

AK37

AL34

AM36

AN35

AP32

AM31

AM34

AM35

AL32

AM32

AN31

AP31

AN28

AP28

AL30

AM30

AM28

AL28

AP27

AM27

AM23

AM22

AL23

AM24

AN22

AP22

AM9

AL9

AL6

AP7

AP11

AP10

AL7

AM7

AN5

AN6

AN3

AP3

AP6

AM6

AL4

AM3

AK2

AK3

AG2

AG1

AL3

AM2

AH3

AG3

AF3

AE3

AD6

AC4

AF2

AF1

AD4

AD5

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_BS#012

DDR_B_BS#112

DDR_B_BS#212

DDR_B_DM[0..7]12

DDR_B_DQS[0..7]12

DDR_B_DQS#[0..7]12

DDR_B_MA[0..13]12

DDR_B_CAS#12

DDR_B_RAS#12

DDR_B_BS#0

DDR_B_BS#1

DDR_B_BS#2

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_CAS#

DDR_B_RAS#

AJ15

AG17

AG21

AF32

AK34

AK27

AK24

AJ10

AK5

AE7

AB7

AF34

AK32

AJ28

AK23

AM10

AH6

AF8

AB4

AF35

AK33

AK28

AJ23

AL10

AH7

AF7

AB5

AH17

AK17

AH18

AJ18

AK18

AJ19

AK19

AH19

AJ20

AH20

AJ16

AG18

AG20

AG15

AH14

AK14

AF15

AF14

AH16

SB_BS0#

SB_BS1#

SB_BS2#

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_DQS0#

SB_DQS1#

SB_DQS2#

SB_DQS3#

SB_DQS4#

SB_DQS5#

SB_DQS6#

SB_DQS7#

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_CAS#

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

SB_WE#

U31D

SBDQ0

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

SBDQ15

SBDQ16

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQ24

SBDQ25

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQ32

SBDQ33

SBDQ34

SBDQ35

SBDQ36

SBDQ37

SBDQ38

SBDQ39

SBDQ40

SBDQ41

SBDQ42

DDR SYSTEM MEMORY B

SBDQ43

SBDQ44

SBDQ45

SBDQ46

SBDQ47

SBDQ48

SBDQ49

SBDQ50

SBDQ51

SBDQ52

SBDQ53

SBDQ54

SBDQ55

SBDQ56

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

ALVISO_BGA1257

AE31

AE32

AG32

AG36

AE34

AE33

AF31

AF30

AH33

AH32

AK31

AG30

AG34

AG33

AH31

AJ31

AK30

AJ30

AH29

AH28

AK29

AH30

AH27

AG28

AF24

AG23

AJ22

AK22

AH24

AH23

AG22

AJ21

AG10

AG9

AG8

AH8

AH11

AH10

AJ9

AK9

AJ7

AK6

AJ4

AH5

AK8

AJ8

AJ5

AK4

AG5

AG4

AD8

AD9

AH4

AG6

AE8

AD7

AC5

AB8

AB6

AA8

AC8

AC7

AA4

AA5

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_B_D[0..63] 12DDR_A_D[0..63] 11

A A

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Size Do cum e nt Number R e v

Dat e : Sheet

Compal Electronics, Inc.

SCHEMATIC, M/B LA-2761

401344

期三 四月

1

A

of

751¬P , 27, 2005

5

+3VS +2.5VS

12

R92

2.2K_0402_5%GM@

+2.5VS

S

GMCH_TV_COMPS21

GMCH_TV_LUMA21

GMCH_TV_CRMA21

G

2

GMCH_ENBKL

GMCH_LCD_CLK

13

D

Q9

2N7002_SOT23GM@

GMCH_CRT_CLK14

GMCH_CRT_DATA14

GMCH_CRT_B14

GMCH_CRT_G14

GMCH_CRT_R14

GMCH_CRT_VSYNC14

GMCH_CRT_HSYNC14

GMCH_ENBKL15,33

D D

C C

+2.5VS

R97 4.7K_0402_5%

1 2

R98 4.7K_0402_5%

1 2

R100 2.2K_0402_5%

1 2

R99 2.2K_0402_5%

1 2

R134 100K_0402_5%

1 2

R112 1.5K_0402_1%

B B

GM@

4.7K_0402_5%

LDDC_CLK

1 2

R109 150_0402_5%PM@

1 2

R118 150_0402_5%PM@

1 2

R101 150_0402_5%PM@

1 2

R104

1 2

2

G

1 3

D

S

Q10

R88 0_0402_5%@

GMCH_TV_COMPS

GMCH_TV_LUMA

GMCH_TV_CRMA

GMCH_CRT_CLK

GMCH_CRT_DATA

LCTLB_DATA

LCTLA_CLK

LBKLT_EN

LIBG

GMCH_TV_COMPS

GMCH_TV_LUMA

GMCH_TV_CRMA

+3VS

R87

4.7K_0402_5%GM@

1 2

BSS138_SOT23GM@

LBKLT_EN

12

R143 4.99K_0603_1%

GMCH_CRT_CLK

GMCH_CRT_DATA

R121 150_0402_5%PM@

R107 150_0402_5%PM@

R403 150_0402_5%PM@

GMCH_LCD_CLK 15

4

SDVO_SDAT15,41

SDVO_SCLK15,41

CLK_MCH_3GPLL#13

CLK_MCH_3GPLL13

12

12

12

12

GMCH_ENVDD15

GMCH_TXCLK-15

GMCH_TXCLK+15

GMCH_TZCLK-15

GMCH_TZCLK+15

GMCH_TXOUT0-15

GMCH_TXOUT1-15

GMCH_TXOUT2-15

GMCH_TXOUT0+15

GMCH_TXOUT1+15

GMCH_TXOUT2+15

GMCH_TZOUT0-15

GMCH_TZOUT1-15

GMCH_TZOUT2-15

GMCH_TZOUT0+15

GMCH_TZOUT1+15

GMCH_TZOUT2+15

SDVO_SDAT

SDVO_SCLK

CLK_MCH_3GPLL#

CLK_MCH_3GPLL

TV_REFSET

12

R108 0_0402_5%

GMCH_CRT_B

GMCH_CRT_G

GMCH_CRT_R

GMCH_ CRT_VSYNC

GMCH_CRT_HSYNC

1 2

R142 255_0402_1%

REFSET

LBKLT_EN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

GMCH_ENVDD

LIBG

GMCH_TXCLKGMCH_TXCLK+

GMCH_TZCLKGMCH_TZCLK+

GMCH_TXOUT0GMCH_TXOUT1GMCH_TXOUT2-

GMCH_TXOUT0+

GMCH_TXOUT1+

GMCH_TXOUT2+

GMCH_TZOUT0GMCH_TZOUT1GMCH_TZOUT2-

GMCH_TZOUT0+

GMCH_TZOUT1+

GMCH_TZOUT2+

U31G

H24

H25

AB29

AC29

A15

C16

A17

J18

B15

B16

B17

E24

E23

E21

D21

C20

B20

A19

B19

H21

G21

J20

E25

F25

C23

C22

F23

F22

F26

C33

C31

F28

F27

B30

B29

C25

C24

B34

B33

B32

A34

A33

B31

C29

D28

C27

C28

D27

C26

ALVISO_BGA1257

SDVOCTRL_DATA

SDVOCTRL_CLK

GCLKN

GCLKP

TVDAC_A

TVDAC_B

TVDAC_C

TV_REFSET

TV_IRTNA

TV_IRTNB

TV_IRTNC

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CTL

LBKLT_EN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

3

EXP_RXN0/SDVO_TVCLKIN#

MISCTVVGALVDS

EXP_RXN1/SDVO_INT#

EXP_RXN2/SDVO_FLDSTALL#

EXP_RXP0/SDVO_TVCLKIN

EXP_RXP1/SDVO_INT

EXP_RXP2/SDVO_FLDSTALL

EXP_TXN0/SDVOB_RED#

EXP_TXN1/SDVOB_GREEN#

EXP_TXN2/SDVOB_BLUE#

EXP_TXN3/SDVOB_CLKN

EXP_TXN4/SDVOC_RED#

EXP_TXN5/SDVOC_GREEN#

EXP_TXN6/SDVOC_BLUE#

EXP_TXN7/SDVOC_CLKN

PCI - EXPRESS GRAPHICS

EXP_TXP0/SDVOB_RED

EXP_TXP1/SDVOB_GREEN

EXP_TXP2/SDVOB_BLUE

EXP_TXP3/SDVOB_CLKP

EXP_TXP4/SDVOC_RED

EXP_TXP5/SDVOC_GREEN

EXP_TXP6/SDVOC_BLUE

EXP_TXP7/SDVOC_CLKP

EXP_COMPI

EXP_ICOMPO

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN8

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

2

PCIE_MTX_C_GRX_N[0..15]15,41

PCIE_MTX_C_GRX_P[0..15]15,41

PCEI_GTX_C_MRX_N[0..15]15,41

PCEI_GTX_C_MRX_P[0..15]15,41

PEG_COMP

D36

D34

PCEI_GTX_C_MRX_N0

E30

PCEI_GTX_C_MRX_N1

F34

PCEI_GTX_C_MRX_N2

G30

PCEI_GTX_C_MRX_N3

H34

PCEI_GTX_C_MRX_N4

J30

PCEI_GTX_C_MRX_N5

K34

PCEI_GTX_C_MRX_N6

L30

PCEI_GTX_C_MRX_N7

M34

PCEI_GTX_C_MRX_N8

N30

PCEI_GTX_C_MRX_N9

P34

PCEI_GTX_C_MRX_N10

R30

PCEI_GTX_C_MRX_N11

T34

PCEI_GTX_C_MRX_N12

U30

PCEI_GTX_C_MRX_N13

V34

PCEI_GTX_C_MRX_N14

W30

PCEI_GTX_C_MRX_N15

Y34

PCEI_GTX_C_MRX_P0

D30

PCEI_GTX_C_MRX_P1

E34

PCEI_GTX_C_MRX_P2

F30

PCEI_GTX_C_MRX_P3

G34

PCEI_GTX_C_MRX_P4

H30

PCEI_GTX_C_MRX_P5

J34

PCEI_GTX_C_MRX_P6

K30

PCEI_GTX_C_MRX_P7

L34

PCEI_GTX_C_MRX_P8

M30

PCEI_GTX_C_MRX_P9

N34

PCEI_GTX_C_MRX_P10

P30

PCEI_GTX_C_MRX_P11

R34

PCEI_GTX_C_MRX_P12

T30

PCEI_GTX_C_MRX_P13

U34

PCEI_GTX_C_MRX_P14

V30

PCEI_GTX_C_MRX_P15

W34

PCIE_MTX_GRX_N0

E32

PCIE_MTX_GRX_N1

F36

PCIE_MTX_GRX_N2

G32

PCIE_MTX_GRX_N3

H36

PCIE_MTX_GRX_N4 PCIE_MTX_C_GRX_N4

J32

PCIE_MTX_GRX_N5

K36

PCIE_MTX_GRX_N6

L32

PCIE_MTX_GRX_N7

M36

PCIE_MTX_GRX_N8

N32

PCIE_MTX_GRX_N9

P36

PCIE_MTX_GRX_N10

R32

PCIE_MTX_GRX_N11

T36

PCIE_MTX_GRX_N12

U32

PCIE_MTX_GRX_N13

V36

PCIE_MTX_GRX_N14

W32

PCIE_MTX_GRX_N15

Y36

PCIE_MTX_GRX_P0

D32

PCIE_MTX_GRX_P1

E36

PCIE_MTX_GRX_P2

F32

PCIE_MTX_GRX_P3

G36

PCIE_MTX_GRX_P4

H32

PCIE_MTX_GRX_P5

J36

PCIE_MTX_GRX_P6

K32

PCIE_MTX_GRX_P7

L36

PCIE_MTX_GRX_P8

M32

PCIE_MTX_GRX_P9

N36

PCIE_MTX_GRX_P10

P32

PCIE_MTX_GRX_P11

R36

PCIE_MTX_GRX_P12

T32

PCIE_MTX_GRX_P13

U36

PCIE_MTX_GRX_P14

V32

PCIE_MTX_GRX_P15

W36

1 2

R115 24.9_0402_1%

C422 0.1U_0402_16V4Z

1 2

C437 0.1U_0402_16V4Z

1 2

C445 0.1U_0402_16V4Z

1 2

C451 0.1U_0402_16V4Z

1 2

C460 0.1U_0402_16V4Z

1 2

C465 0.1U_0402_16V4Z

1 2

C469 0.1U_0402_16V4Z

1 2

C476 0.1U_0402_16V4Z

1 2

C418 0.1U_0402_16V4Z

1 2

C430 0.1U_0402_16V4Z

1 2

C444 0.1U_0402_16V4Z

1 2

C450 0.1U_0402_16V4Z

1 2

C458 0.1U_0402_16V4Z

1 2

C464 0.1U_0402_16V4Z

1 2

C468 0.1U_0402_16V4Z

1 2

C475 0.1U_0402_16V4Z

1 2

PCIE_MTX_C_GRX_N[0..15]

PCIE_MTX_C_GRX_P[0..15]

PCEI_GTX_C_MRX_N[0..15]

PCEI_GTX_C_MRX_P[0..15]

+1.5VS

C416 0.1U_0402_16V4Z

1 2

C428 0.1U_0402_16V4Z

1 2

C440 0.1U_0402_16V4Z

1 2

C449 0.1U_0402_16V4Z

1 2

C457 0.1U_0402_16V4Z

1 2

C462 0.1U_0402_16V4Z

1 2

C467 0.1U_0402_16V4Z

1 2

C474 0.1U_0402_16V4Z

1 2

C413 0.1U_0402_16V4Z

1 2

C425 0.1U_0402_16V4Z

1 2

C438 0.1U_0402_16V4Z

1 2

C446 0.1U_0402_16V4Z

1 2

C454 0.1U_0402_16V4Z

1 2

C461 0.1U_0402_16V4Z

1 2

C466 0.1U_0402_16V4Z

1 2

C470 0.1U_0402_16V4Z

1 2

1

PCIE_MTX_C_GRX_N0

PCIE_MTX_C_GRX_N1

PCIE_MTX_C_GRX_N2

PCIE_MTX_C_GRX_N3

PCIE_MTX_C_GRX_N5

PCIE_MTX_C_GRX_N6

PCIE_MTX_C_GRX_N7

PCIE_MTX_C_GRX_N8

PCIE_MTX_C_GRX_N9

PCIE_MTX_C_GRX_N10

PCIE_MTX_C_GRX_N11

PCIE_MTX_C_GRX_N12

PCIE_MTX_C_GRX_N13

PCIE_MTX_C_GRX_N14

PCIE_MTX_C_GRX_N15

PCIE_MTX_C_GRX_P0

PCIE_MTX_C_GRX_P1

PCIE_MTX_C_GRX_P2

PCIE_MTX_C_GRX_P3

PCIE_MTX_C_GRX_P4

PCIE_MTX_C_GRX_P5

PCIE_MTX_C_GRX_P6

PCIE_MTX_C_GRX_P7

PCIE_MTX_C_GRX_P8

PCIE_MTX_C_GRX_P9

PCIE_MTX_C_GRX_P10

PCIE_MTX_C_GRX_P11

PCIE_MTX_C_GRX_P12

PCIE_MTX_C_GRX_P13

PCIE_MTX_C_GRX_P14

PCIE_MTX_C_GRX_P15

A A

GM@

4.7K_0402_5%

LDDC_DATA

R105

+2.5VS

G

2

1 2

S

GMCH_LCD_DATA

13

D

Q32

5

2N7002_SOT23GM@

+3VS

R404

4.7K_0402_5%GM@

1 2

GMCH_LCD_DATA 15

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Title

Size Do cum e nt Number R e v

Dat e : Sheet

Compal Electronics, Inc.

SCHEMATIC, M/B LA-2761

期三 四月

401344

1

A

of

851¬P , 27, 2005

5

4

3

2

1

10U_1206_16V4Z

0.1U_0402_16V4Z

1

C188

2

+1.5VS

1

C93

2

+1.05VS

1

C165

2

2.2U_0603_6.3V6K

+1.05VS

1

2

VCCHV(Ball A21,B21,B22)

C104

0.1U_0402_16V4Z

1000P_0402_50V7K@

+3VS_TVDAC

U31E

+1.05VS

D D

C C

+1.5VS

+1.5VS_DPLLA

+1.5VS_DPLLB

+1.5VS_HPLL

+1.5VS_MPLL

B B

+1.5VS_DPLLA

1

2

+1.5VS_HPLL

A A

1

2

+1.5VS_DPLLA

+1.5VS_DPLLB

+1.5VS_HPLL

+1.5VS_MPLL

60mA

1

C59

C70

2

10U_1206_16V4Z

1000P_0402_50V7K@

60mA

+1.5VS_HPLL

1

C481

C478

2

10U_1206_16V4Z

1000P_0402_50V7K@

T29

R29

N29

M29

K29

J29

V28

U28

T28

R28

P28

N28

M28

L28

K28

J28

H28

G28

V27

U27

T27

R27

P27

N27

M27

L27

K27

J27

H27

K26

H26

K25

J25

K24

K23

K22

K21

W20

U20

T20

K20

V19

U19

K19

W18

V18

T18

K18

K17

AC1

AC2

B23

C35

AA1

AA2

ALVISO_BGA1257

L15

CHB1608U301_0603

1 2

1

C77

2

0.1U_0402_16V4Z

L31

CHB1608U301_0603

1 2

1

C477

2

0.1U_0402_16V4Z

5

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

POWER

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCCD_HMPLL1

VCCD_HMPLL2

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

VCCA_MPLL

+1.5VS

+1.5VS

+1.5VS_DPLLB

+1.5VS_DPLLB

1

C73

2

10U_1206_16V4Z

1000P_0402_50V7K@

+1.5VS_MPLL

+1.5VS_MPLL

1

C161

2

10U_1206_16V4Z

1000P_0402_50V7K@

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVDACB0

VCCA_TVDACB1

VCCA_TVDACC0

VCCA_TVDACC1

VCCA_TVBG

VSSA_TVBG

VCCD_TVDAC

VCCDQ_TVDAC

VCCD_LVDS0

VCCD_LVDS1

VCCD_LVDS2

VCCA_LVDS

VCCHV0

VCCHV1

VCCHV2

VCCTX_LVDS0

VCCTX_LVDS1

VCCTX_LVDS2

VCCA_SM0

VCCA_SM1

VCCA_SM2

VCCA_SM3

VCC3G0

VCC3G1

VCC3G2

VCC3G3

VCC3G4

VCC3G5

VCC3G6

VCCA_3GPLL0

VCCA_3GPLL1

VCCA_3GPLL2

VCCA_3GBG

VSSA_3GBG

VCC_SYNC

VCCA_CRTDAC0

VCCA_CRTDAC1

VSSA_CRTDAC

60mA

1

C87

2

60mA

1

C167

2

120mA

F17

E17

D18

C18

F18

E18

H18

G18

D19

H17

24mA

B26

B25

A25

60mA

A35

10mA

B22

B21

2mA

A21

B28

A28

60mA

A27

AF20

AP19

AF19

AF18

AE37

W37

U37

R37

1500mA

N37

L37

J37

Y29

Y28

Y27

F37

0.15mA

G37

H20

F19

E19

G19

L16

CHB1608U301_0603

1 2

1

C80

2

0.1U_0402_16V4Z

L21

CHB1608U301_0603

1 2

1

C155

2

0.1U_0402_16V4Z

+3VS_TVDAC

1

+

C55

2

+1.5VS

+2.5VS

+1.5VS_DDRDLL

+1.5VS_PEG

0.47U_0603_16V4Z

+1.5VS_3GPLL

+2.5VS_3GBG

+2.5VS

70mA

0.47U_0603_16V4Z

+1.5VS_DDRDLL

+1.5VS

+1.5VS_3GPLL

+1.5VS

4

+1.05VS

150U_D2_6.3VMTV@

C432

1

2

1

C431

2

1

C163

0.22U_0402_10V4Z

0.22U_0402_10V4Z

1

C183

2

10U_1206_16V4Z

1000P_0402_50V7K@

+1.5VS_3GPLL +2.5VS_3GBG

1

C184

2

10U_1206_16V4Z

1000P_0402_50V7K@

2

C131

+1.5VS_DDRDLL

1

C181

2

1

C171

2

1

2

1

2

R159

0.5_0603_1%

1 2

1

C170

2

0.1U_0402_16V4Z

U31F

1

2

AM37

AH37

AP29

AD28

AD27

AC27

AP26

AN26

AM26

AL26

AK26

AJ26

AH26

AG26

AF26

AE26

AP25

AN25

AM25

AL25

AK25

AJ25

AH25

AG25

AF25

AE25

AE24

AE23

AE22

AE21

AE20

AE19

AE18

AE17

AE16

AE15

AE14

AP13

AN13

AM13

AL13

AK13

AJ13

AH13

AG13

AF13

AE13

AP12

AN12

AM12

AL12

AK12

AJ12

AH12

AG12

AF12

AE12

AD11

AC11

AB11

AB10

AB9

AP8

AM1

AE1

C129

V1.8_DDR_CAP1

V1.8_DDR_CAP2

V1.8_DDR_CAP5

V1.8_DDR_CAP6

V1.8_DDR_CAP4

V1.8_DDR_CAP3

1

C153

2

4.7U_0805_10V4Z

1000P_0402_50V7K@

1000P_0402_50V7K@

K13

VTT0

J13

VTT1

K12

VTT2

W11

VTT3

V11

VTT4

U11

VTT5

T11

VTT6

R11

VTT7

P11

N11

M11

L11

K11

W10

V10

U10

T10

R10

P10

N10

M10

K10

J10

W9

M9

M8

M7

M6

M5

M4

M3

M2

M1

G1

R160

0_0603_5%

1 2

C186

0.1U_0402_16V4Z

POWER

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

Y9

VTT23

VTT24

U9

VTT25

R9

VTT26

P9

VTT27

N9

VTT28

VTT29

L9

VTT30

J9

VTT31

N8

VTT32

VTT33

N7

VTT34

VTT35

N6

VTT36

VTT37

A6

VTT38

N5

VTT39

VTT40

N4

VTT41

VTT42

N3

VTT43

VTT44

N2

VTT45

VTT46

B2

VTT47

V1

VTT48

N1

VTT49

VTT50

VTT51

ALVISO_BGA1257

+1.5VS_PEG

+1.5VS

L24

CHB1608U301_0603

+3GPLL

1 2

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VCCSM52

VCCSM53

VCCSM54

VCCSM55

VCCSM56

VCCSM57

VCCSM58

VCCSM59

VCCSM60

VCCSM61

VCCSM62

VCCSM63

VCCSM64

+1.5VS_PEG+1.5VS_DPLLA

1

C146

2

10U_1206_16V4Z

+2.5VS_3GBG

+1.5VS

0.1U_0402_16V4Z

3

C195

0.1U_0402_16V4Z

+1.8V

330U_D2E_2.5VM

C199

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C141

2

1 2

R123 0_0603_5%

1

C128

2

C189

0.1U_0402_16V4Z

12

12

C198

0.1U_0402_16V4Z

+1.8V

2200mA

0.1U_0402_16V4Z

C200

1

2

+2.5VS

1

2

+

C174

C101

0.1U_0402_16V4Z

1

2

0.1U_0402_16V4Z

VCCA_LVDS (Ball A35)

+2.5VS

1

C91

2

4.7U_0805_10V4Z

VCC_SYNC(Ball H20)

C197

0.1U_0402_16V4Z

12

12

C182

R153

1 2

0_0805_5%

1

C157

2

4.7U_0805_10V4Z

12

+3VS

+2.5VS

4.7U_0805_10V4Z

1

+

2

2

12

C175

1

C100

2

0.01U_0402_16V7K

1

C133

2

0.1U_0402_16V4Z

+1.5VS

C168

470U_D2_2.5VM

L17

CHB1608U301_0603

1 2

1

C65

2

10U_1206_16V4Z

1000P_0402_50V7K

4000mA

2.2U_0603_6.3V6K

1

C169

C160

2

1

C176

2

0.1U_0402_16V4Z

1

C94

2

4.7U_0805_10V4Z

1

2

0.1U_0402_16V4Z

1

C154

2

2.2U_0603_6.3V6K

1

C172

2

0.1U_0402_16V4Z

1

C107

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C144

2

0.1U_0402_16V4Z

1

C178

2

1

C92

2

4.7U_0805_10V4Z

0.1U_0402_16V4Z

C177

1

C152

2

1

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

C143

2

1

C187

2

1

C102

2

0.1U_0402_16V4Z

VCCTX_LVDS(Ball A27,A28,B28)

VCCA_CRTDAC(Ball F19,E19)

1

C126

2

0.1U_0402_16V4Z

1

C103

2

0.022U_0402_16V7K

VCCD_TVDAC (Ball D19)

0.1U_0402_16V4Z

1

C140

2

1

C134

2

0.022U_0402_16V7K

1

2

0.1U_0402_16V4Z

1

C120

2

1

C122

2

0.022U_0402_16V7K

VCCDQ_TVDAC (Ball H17)VCCD_LVDS(Ball A25,B25,B26)

950mA

1

C166

2

1

C158

2

2.2U_0603_6.3V6K

1

C159

2

2.2U_0603_6.3V6K

1

C132

2

2.2U_0603_6.3V6K

VCCA_TVDAC VCCA_TVBG (Ball H18)

1

1

C74

2

1

C139

C123

2

2

1000P_0402_50V7K

0.1U_0402_16V4Z

1

C136

2

0.1U_0402_16V4Z

0.022U_0402_16V7K

1

C130

2

120mA

Title

Size Do cum e nt Number R e v

Dat e : Sheet

Compal Electronics, Inc.

SCHEMATIC, M/B LA-2761

期三 四月

401344

1

of

951¬P , 27, 2005

A

5

4

3

2

1

U31H

+1.05VS

D D

C C

B B

+1.05VS

A A

L12

VTT_NCTF17

M12

VTT_NCTF16

N12

VTT_NCTF15

P12