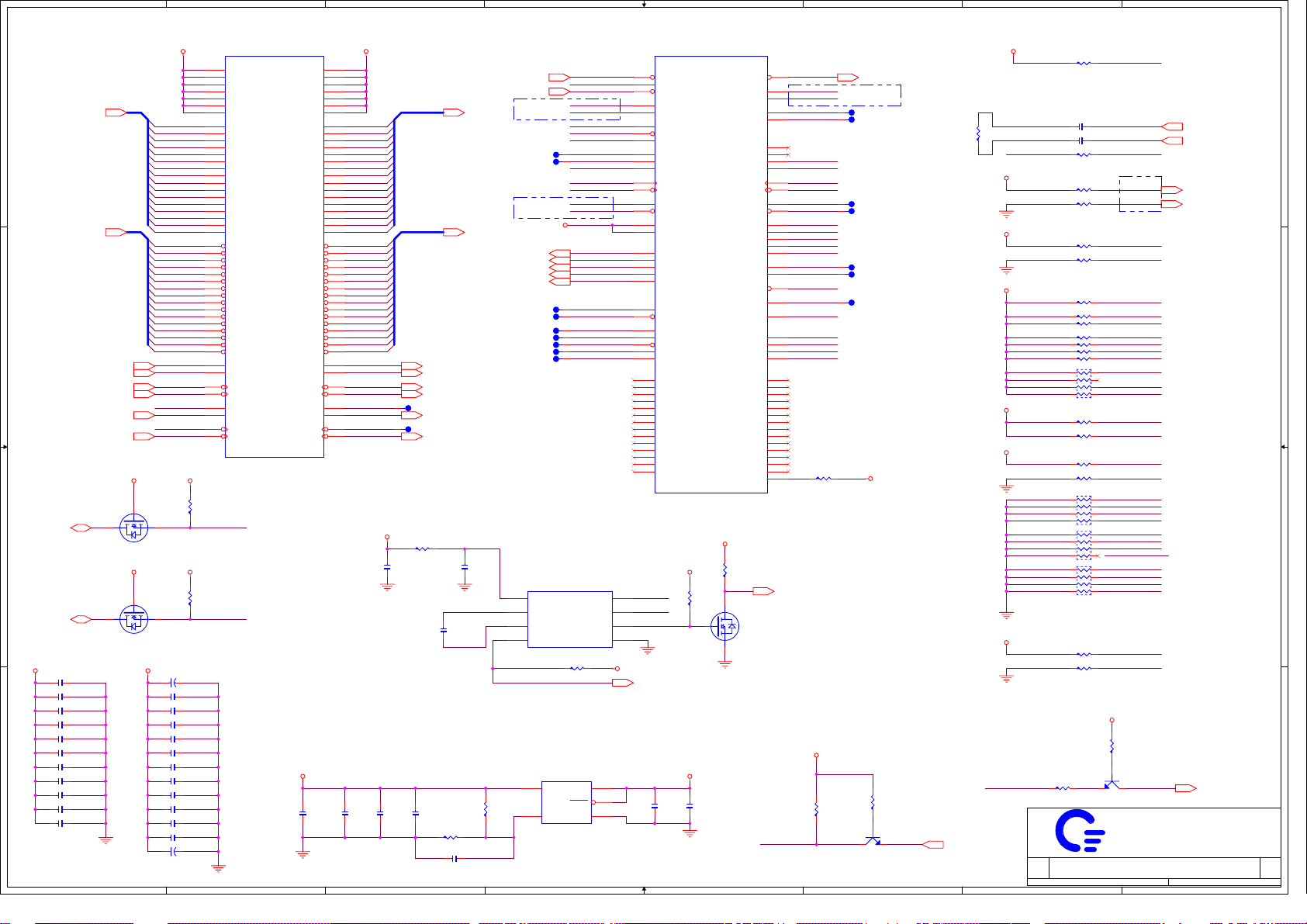

Acer Aspire 3002 Schematics

5

MODEL:

REV:

CHANGE LIST:

FIRST RELEASE1A

01. Page2 : Unstaff R202 for correct clock setting

2A

02. Page3 : Delete JP2, Unstaff C561 and C559 ~ C562, C567 change P/N to CH6101M9A07 due to the height limitaion

ZL5

D D

MotherBoard

03. Page5 : Change DDR MD terminator resistor array to 56ohm 4P2R type

04. Page9 : Change R20 to 6.2K, Unstaff C13

05. Page10 : Modify the CRT circuit due to the bad signal quality of CM2009 (Delete U1, Add D25, D28 ~ D32, Q35, Q36, R405, R404, R406, U31, U32)

06. Page11 : RN5, RN7, RN8, RN11, RN20, RN21 change P/N to CJ282084N01

07. Page12 : Modify the power good circuit (Delete D15, Add R402, R403)

08. Page16 : Modify the lan led circuit to fit to the right led color definition (R350, R353 change to pull high, Add D26, D27, CN3 change footprint)

09. Page17 : CN7, CN8 change footprint

10. Page19 : HOLE25 change to TOP layer

11. Page20 : Cancel the HOLD# ciruit (Unstaff R95, R111, D5, D7, Q17, Staff Q15, R99)

12. Page21 : SW2, SW3 change P/N to DHPPS11BD0

13. Page22 : Add PR123, PD16, PC149; PD13 change P/N to BC05FA20Z01; PU12 change P/N to AL001999W16

14. Page23 : PR63 change to 11K/F; PD15 change P/N to BC10QS04C01; Staff PC77 1000P

15. Page25 : PL8, PL9 change size to RC0805; PD8, PD9 change P/N to BC10QS04C01

C C

16. Page26 : Unstaff PQ4; PR101, PR105 change P/N to CS31003B919; PU9 change P/N to AJ017720W06

17. Delete JP1, JP2 ~ JP6

18. U20 change P/N to AJ007600T25

19. L7, L8, L9, L10, L11, L12, L13, L14, L15, L16, L18, L24, L26, L27, L40, L43, L47, L48, L49, L50 change P/N to CX0QNT03004

20. PQ3, PQ4, PQ5, PQ6, PQ8, PQ9, PQ10, PQ12, PQ13, PQ14, PQ15, PQ16, PQ18, PQ24, PQ32, PQ33, PQ35, Q2, Q3, Q4, Q5, Q6, Q8, Q9, Q11, Q26, Q27, Q34 change P/N to BAM70020074

3A 01. Page2 : Staff R176 33ohm for 302ELV clock

02. Page4 : Staff C131, C175, C188, C189

03. Page9 : Staff R295(0ohm), R294 change P/N to CS00002JB03, Unstaff Y4, C31, C554 for 302ELV clock; Add C710 ~ C713, R407 ~ R410 for EMI reserved.

04. Page10 : D17 change p/n to BC05FA20Z01 to enlarge the current limit; L1 ~ L3 change p/n to CX808600101 for EMI

05. Page12 : C633, C634 change P/N to CH01806JB07 to adjust RTC accuracy; Add JP1 for RTC reset

06. Page15 : Add C709

07. Page17 : Unstaff CN8, CN10; Add C700 ~ C708 for EMI

B B

08. Page19 : Delete HOLE18; Staff PAD4 for modem cable

3B

01. Page17 : L36, R274, R279 change p/n to CX8HS121001; Staff R270, R273 100pF

4

3

2

1

MODEL : ZL5 MB

FROM

PAGE

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

TO

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

3A

3B

02. Page18 : L54, L55 change p/n to CX8HS121001; Unstaff R260, R261, R265, R271, R278

03. Page19 : Staff PAD9(FDMK1004010) for EMI

04. Page22 : Unstaff PR112 for thermal shutdown working properly

05. Q2, Q3, Q4, Q5, Q6, Q8, Q9, Q11, Q18, Q26, Q27, Q34, Q35, Q36, PQ3, PQ4, PQ5, PQ6, PQ8, PQ9, PQ10, PQ12, PQ13, PQ14, PQ15, PQ16,

PQ18, PQ24, PQ32, PQ33, PQ35 change p/n to BAN70020Z13

A A

PROJECT : ZL5

APPROVE BY: SAINT LIN DRAWING BY:DILBERT YU

REV 3B

COVER SHEET 1 OF 1

Quanta Computer Inc.

5

MB ASSY'S P/N : 31ZL5MB0009

4

PROJECT LEADER: SAINT LIN DOCUMENT NO:

3

2

DATE :2005/3/9

1

8

HOST 200MHz

ZCLK 133MHz

CLK-GEN

D D

ICS 952801

3V/5V

C C

Page 22

2.5V/1.25V

B B

Page 23

AGP 66MHz

PCI 33MHz

USB 48MHz

REF 14.318MHz

Page 2

3V_ALWAYS

5VPCU

3V_S5

1.8V_S5

3VSUS

5VSUS

+3V

+5V

15V

2.5VSUS

1.25VREF

+2.5V

DDR_VTT

7

6

5

4

3

2

1

CPU

ZL5

Block Diagram

CRT

1x D-SUB 15-Pin

LCD

15" XGA/WXGA

IDSEL : AD22

Antenna

Page 15

PC Card

1x type-I/II

RJ-45

RJ-11MDC1.5

Page 17

Page 10

Page 10

Page 16

Page 16

DDR SO-DIMM

HDD

Primary Master

ODD

Secondary Master

USB

3x connector

MINI USB

(BLUETOOTH)

Page 19

Page 19

Page 15

Page 15

DDR 333

ATA 66/100

ATA 66/100

USB 2.0

AMD Athlon64

SMT uPGA754

Page 3,4Page 5

HyperTransport

16x16

1600MT/s

NB

SIS M760GX

(698 PIN BGA)

Page 6,7,8 Page 9

MuTIOL(1GB/s)

SB

SIS 963L

(371 PIN BGA)

Thermal sensor & Fan

INTA#

DVO

LVDS

Transmitter

133MB/s (33MHZ)

PCI 2.2

REQ1#, GNT1#

INTD#

MII

AC'97 2.1

Thermal

SIS302ELV

IDSEL : AD17

CardBus

TI PCI1410

LAN PHY

RTL8201CP

RGB

LVDS

REQ0#, GNT0#

INTB#, INTC#

Mini PCI

WLAN 802.11A/G

Page 14

Transformer

Page 16 Page 16

56K MODEM

1.2V/1.5V

1.8V

Page 24

+1.2V_HT

+1.5V

+1.8V

Int. Keyboard

CPU CORE

Page 25

A A

VCC_CORE

87-Key

Touch Pad

6-Button

Page 21

NS PC97551

Page 21

BATTERY

CHARGER

Page 26

8

7

6

5

EC

Page 11,12,13

AC97 Codec

LPC

Page 20 Page 20

4

ALC203

BIOS

3

Page 17

AMP

MAX9755

Page 18

Size Document Number Rev

BLOCK DIAGRAM

Date: Sheet

2

Quanta Computer Inc.

MIC-In Jack

Line-In Jack

HP-Out Jack

Int. Speaker

PROJECT : ZL5

3B

of

126Thursday, March 10, 2005

1

8

7

6

5

4

3

2

1

+3V

L23

FBM2125

D D

C C

B B

C291

.1U_4

C356

10U/10V_8

VCC3_CLKGN

C281

.1U_4

C280

.1U_4

C277

.1U_4

+3V

STP_PCI#

+3V

+3V

C355

10U/10V_8

C314

.1U_4

C350

.1U_4

R197 *0_4

R156 10K_4

R158 4.7K_4

+3V

R153 *0_4

L22

FBM2125

C289

.1U_4

C257

.1U_4

+3V

VCC3_CLKGN_VDDA

C284

.1U_4

C353

C354

.1U_4

10P_4

C301

.1U_4

R205

4.7K_4

MGN_PD#

C292

10P_4

C288

.1U_4

CPUSTP#[12]

STP_PCI#[12]

1

11

15

24

31

33

43

44

5

8

16

23

28

36

40

47

48

37

12

38

39

U12

VDDREF

VDDZ

VDDPCI

VDDPCI

VDD48

VDDAGP

VDDCPU

VDDCPU

GNDREF

GNDZ

GNDPCI

GNDPCI

GND48

GNDF

GNDCPU

GNDCPU

CPUSTOP#*

PD#*

PCI_STOP#*

VDDA

GNDA

ICS952801

FS3/PCICLK_F0**

FS4/PCICLK_F1**

* INTERNAL PULL-HIGH 150K

** INTERNAL PULL-lOW 150K

X1

6

C298

10P_4

Y2

14.318MHz

X2

7

C271

10P_4

CPU_1T

CPU_1C

CPU_0T

CPU_0C

AGPCLK0

AGPCLK1

ZCLK0

ZCLK1

FS0/REF0**

FS1/REF0**

FS2/REF0**

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

PCICLK6

PCICLK7

48MHz

24_48MHz

SCLK

SDATA

MGN_CPU1T

42

MGN_CPU1C

41

MGN_CPU0T

46

MGN_CPU0C

45

MGN_AGPCLK0

35

34

MGN_ZCLK0

9

MGN_ZCLK1

10

2

3

4

13

14

MGN_PCICLK1

17

MGN_PCICLK2

18

MGN_PCICLK3

19

MGN_PCICLK4

20

21

22

25

26

30

29

32

27

Damping Resistors

Place Close to Clk Generator

R182 15_4

R174 15_4

R198 15_4

R189 15_4

R147 22_4

R175 22_4

R171 22_4

R203 33_4

FS0

FS1

FS2

FS3

FS4

CLK48M

R204 33_4

R192 33_4

R185 33_4

R176 33_4

R143 33_4

R135 33_4

R133 33_4

R130 33_4

R140 22_4

CPUCLK1_H [6]

CPUCLK1_L [6]

CPUCLK+ [3]

CPUCLK- [3]

AGPCLK0 [6]

ZCLK0 [7]

ZCLK1 [11]

14M_CODEC [17]

VOSCI [7]

REFCLK1 [12]

VOSCIE [7]

VBRCLK [9]

96XPCLK [11]

PCLK_MP [15]

PCLK_PCM [14]

PCLK_591 [20]

UCLK48M [13]

SMBCLK [5,12]

SMBDAT [5,12]

By-Pass Capacitors

Place Close to Clock Generator

CPUCLK1_H

CPUCLK1_L

AGPCLK0

ZCLK0

ZCLK1

96XPCLK

PCLK_MP

PCLK_PCM

PCLK_591

VBRCLK

REFCLK1

VOSCI

VOSCIE

UCLK48M

+3V

C313 *10P_4

C300 *10P_4

C279 *10P_4

C302 *10P_4

C297 *10P_4

C278 *10P_4

C275 *10P_4

C270 *10P_4

C261 *10P_4

C303 *10P_4

C324 *10P_4

C337 *10P_4

C317 *10P_4

C276 *10P_4

Frequency Selection

R202 *2.7K_4

R191 2.7K_4

R184 *2.7K_4

R155 *2.7K_4

R150 *2.7K_4

R201 *2.7K_4

FS0

R190 *2.7K_4

FS1

R183 *2.7K_4

FS2

R154 *2.7K_4

FS3

R149 *2.7K_4

FS4

CLK Table for SiS M760 ( Not For ICS ICS-952801)

(FS1)

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

SiS 755/M760 CLOCK

CPU(FS3)

(MHz)(MHz)

00

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

180

185

190

195

205

210

215

220

66.66

100

133

133

166

166

ZCLK

(MHz)(MHz)

135 67.5

132.14

135.71

130

136.66

140

129

132

66.66

100

100

133.33

100

133.33

100

133.33

4

AGPCLK(FS3)(FS2) CPU

(MHz)

66.07

67.08

65

68.33

70

64.5

66 33

66.66

66.66

66.66

66.66

66.66

66.66

66.66

66.66

PCI(FS1)

(MHz)

33.75

33.04

33.93

32.5

34.17

35

32.25

33.33

33.33

33.33

33.33

33.33

33.33

33.33

33.33

Size Document Number Rev

CLOCK GENERATOR

3

Date: Sheet

2

PROJECT : ZL5

Quanta Computer Inc.

226Thursday, March 10, 2005

of

1

3B

SiS 755/M760 CLOCK

(FS4) (FS0)

00000

200

0

0

0

0

0

A A

0

0

0

0

0

0

0

0

0

0

0

8

0

0

0

0

0

0

1

0

1

0

1

0

1

1

0

1

0

1

0

1

0

1

1

1

1

1

1

1

1

1

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

200

0

200

1 1000

200

0

233

1

233

0

233

1

233

266

0

266

1

266

0

266 100

1

200

0

200

1

200

0

200

1

7

ZCLK

66.66

100

133.33

166.66

66.66

93.2

133.28

139.8

66.66

106.4

133

159.6

133

114

142

160

AGPCLK(FS0)

(MHz)

66.66

66.66

66.66

66.66

66.66

66.66

66.66

69.9

66.66

66.5

66.5

66.5

50

66.66

66.66

66.66

PCI

VCO

(MHz)

(MHz)

400

33.33

400

33.33

400

33.33

33.33

466

33.33

466

33.33

933

33.33

699

33.33

266

33.33

532 66.66

33.33

532

33.33

798

33.33

400

33.33

800

33.33

1000

33.33

800

33.33

6

(FS4)

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

(FS2)

0

000

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

5

8

7

6

5

4

3

2

1

+1.2V_HT

D D

C C

B B

A A

CADIP[15..0][6]

CADIN[15..0][6]

CLKIP1[6]

CLKIP0[6]

CLKIN1[6]

CLKIN0[6]

CTLIP0[6]

CTLIN0[6]

+5V +5V

2

Q8

2N7002E

MBCLK[20,26]

MBDATA[20,26]

+1.2V_HT +1.2V_HT

C80 *4.7U/10V_8

C560 *10U/6.3V_8

C63 4.7U/10V_8

C562 10U/6.3V_8

3

2

Q9

2N7002E

3

.22U_4C68

.22U_4C84

.22U_4C83

.22U_4C86

.22U_4C52

.22U_4C51

.22U_4C81

8

CADIP15

CADIP14

CADIP13

CADIP12

CADIP11

CADIP10

CADIP9

CADIP8

CADIP7

CADIP6

CADIP5

CADIP4

CADIP3

CADIP2

CADIP1

CADIP0

CADIN15

CADIN14

CADIN13

CADIN12

CADIN11

CADIN10

CADIN9

CADIN8

CADIN7

CADIN6

CADIN5

CADIN4

CADIN3

CADIN2

CADIN1

CADIN0

CLKIP1

CLKIP0

CLKIN1

CLKIN0

CTLIP1

CTLIP0 CTLOP0

CTLIN1

CTLIN0

1

1

C558 150U/4V_3528

+

C94 *4.7U/10V_8

C60 *4.7U/10V_8

C559 10U/6.3V_8

C561 *10U/6.3V_8

.22U_4C76

.22U_4C75

.22U_4C69

.22U_4C74

.22U_4C563

.22U_4C71

.22U_4C87

C55 150U/4V_3528

+

U21A

AMD K8

V_HT0_A0

V_HT0_A1

V_HT0_A2

V_HT0_A3

V_HT0_A4

V_HT0_A5

V_HT0_A6

HT_RXD15

HT_RXD14

HT_RXD13

HT_RXD12

HT_RXD11

HT_RXD10

HT_RXD9

HT_RXD8

HT_RXD7

HT_RXD6

HT_RXD5

HT_RXD4

HT_RXD3

HT_RXD2

HT_RXD1

HT_RXD0

HT_RXD#15

HT_RXD#14

HT_RXD#13

HT_RXD#12

HT_RXD#11

HT_RXD#10

HT_RXD#9

HT_RXD#8

HT_RXD#7

HT_RXD#6

HT_RXD#5

HT_RXD#4

HT_RXD#3

HT_RXD#2

HT_RXD#1

HT_RXD#0

HT_RXCLK1

HT_RXCLK0

HT_RXCLK#1

HT_RXCLK#0

HT_RXCTL1

HT_RXCTL0

HT_RXCTL#1

HT_RXCTL#0

7

LDT

HT_TXCLK#1

HT_TXCLK#0

HT_TXCTL#1

HT_TXCTL#0

V_HT0_B0

V_HT0_B1

V_HT0_B2

V_HT0_B3

V_HT0_B4

V_HT0_B5

V_HT0_B6

HT_TXD15

HT_TXD14

HT_TXD13

HT_TXD12

HT_TXD11

HT_TXD10

HT_TXD9

HT_TXD8

HT_TXD7

HT_TXD6

HT_TXD5

HT_TXD4

HT_TXD3

HT_TXD2

HT_TXD1

HT_TXD0

HT_TXD#15

HT_TXD#14

HT_TXD#13

HT_TXD#12

HT_TXD#11

HT_TXD#10

HT_TXD#9

HT_TXD#8

HT_TXD#7

HT_TXD#6

HT_TXD#5

HT_TXD#4

HT_TXD#3

HT_TXD#2

HT_TXD#1

HT_TXD#0

HT_TXCLK1

HT_TXCLK0

HT_TXCTL1

HT_TXCTL0

B27

B29

C26

C28

D25

D27

D29

T25

U27

V25

W27

AA27

AB25

AC27

AD25

T27

V29

V27

Y29

AB29

AB27

AD29

AD27

R25

U26

U25

W26

AA26

AA25

AC26

AC25

T28

U29

V28

W29

AA29

AB28

AC29

AD28

Y25

Y27

W25

Y28

R27

T29

R26

R29

R55

10K_4

THMCLK

+5V+5V

R61

10K_4

THMDAT

+1.2V_HT VCC_CORE

AF25

AE28

AF29

AG26

AG28

AH27

AH29

N26

L25

L26

J25

G25

G26

E25

E26

N29

M28

L29

K28

H28

G29

F28

E29

N27

M25

L27

K25

H25

G27

F25

E27

P29

M27

M29

K27

H27

H29

F27

F29

J26

J29

J27

K29

N25

P28

P25

P27

C567

10U/6.3V_8

CADOP15

CADOP14

CADOP13

CADOP12

CADOP11

CADOP10

CADOP9

CADOP8

CADOP7

CADOP6

CADOP5

CADOP4

CADOP3

CADOP2

CADOP1

CADOP0

CADON15

CADON14

CADON13

CADON12

CADON11

CADON10

CADON9

CADON8

CADON7

CADON6

CADON5

CADON4

CADON3

CADON2

CADON1

CADON0

CLKOP1

CLKOP0

CLKON1

CLKON0

CTLOP1

CTLON1

CTLON0

C564

.22U_4

+3V

R51 200_4

C195

.1U_4

C196

3300P_4

6

CLKOP1 [6]

CLKOP0 [6]

CLKON1 [6]

CLKON0 [6]

T1

CTLOP0 [6]

T2

CTLON0 [6]

C565

.1U_4

R84 10K/F_4

CADOP[15..0] [6]

CADON[15..0] [6]

T20W-THERVCC

THERMDA

C152

2200P_6

THERMDC

105mA

470P_4C211

C137

2.2U_6

LDTREST#[6]

LDTSTOP#[6]

Length < 1"

T17

T18

Diff. Pair

Zdiff=80ohm

CPU_VCCA

CPU_VID0[25]

CPU_VID1[25]

CPU_VID2[25]

CPU_VID3[25]

CPU_VID4[25]

JTAG7

JTAG3

JTAG1

JTAG2

JTAG6

JTAG5

JTAG4

U4

1

VCC

2

DXP

ADM1032

3

/MAX6657

DXN

4 5

-OVT GND

G781

MAX6648_OV#

R78

10K/F_4

R68 10K_4

U5

4

OUT

5

SET

MAX8863

Max8863

Vset=1.25V

V=2.5

CPU_PWROK

L0_REF1

L0_REF0

COREFB

COREFB#

CORE_SENSE

VDDIO_SENSE

CPU_CLK

CPU_CLKFBCLKOUT

FBCLKOUT-

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

DBRDY

DBREQ-

TMS

TCK

TRSTTDI

TDO

SMCLK

SMDATA

IN

SHDN

GND

5

-ALT

3

1

2

AF20

AE18

AJ27

AF27

AE26

A23

A24

B23

AE12

AF12

AE11

AJ21

AH21

AH19

AJ19

AH25

AJ25

AE15

AF15

AG14

AF14

AG13

AH17

AE19

E20

E17

B21

A21

A22

A25

B7

B13

B18

C1

C3

C6

C9

C20

C23

C24

D3

F3

J3

THMCLK

8

THMDAT

7

MAX6648_AL#

6

+3V

MAX6648_OV# [21]

U21C

AMD K8

RESET#

PWROK

HT_STOP#

L0_REF1

L0_REF0

COREFB

COREFB#

CORE_SENSE

VDDIOFB

VDDIOFB#

VDDIO_SENSE

CLKIN

CLKIN#

FBCLKOUT

FBCLKOUT#

VDDA1

VDDA2

VID0

VID1

VID2

VID3

VID4

DBRDY

DBREQ#

TMS

TCK

TRST#

TDI

TDO

NC_A25

NC_B7

NC_B13

NC_B18

NC_C1

NC_C3

NC_C6

NC_C9

NC_C20

NC_C23

NC_C24

NC_D3

NC_F3

NC_J3

C209

.01U_4

+3V

+3VCPU_VCCA

CTL & DBG

NC_SCANCLK1

NC_SCANCLK2

NC_SCANSHENB

NC_SCANSHENA

NC_RSVD_SCL

NC_RSVD_SDA

NC_DCLKTWO

NC_ANALOG0

NC_ANALOG1

NC_ANALOG2

NC_ANALOG3

+3V

R67

10K_4

2

C197

.1U_4

THERMTRIP#

THERMDA

THERMDC

KEY0

KEY1

NC_BP3

NC_BP2

NC_BP1

NC_BP0

NC_BPSCLK

NC_BPSCLK#

NC_PLLCHZ

NC_PLLCHZ#

NC_SCANEN

NC_BRN#

NC_SINCHN

NC_K1

NC_R2

NC_R3

NC_AA2

NC_AA3

NC_AE9

NC_AE21

NC_AE22

NC_AG2

NC_AG4

NC_AG6

NC_AG7

NC_AG9

NC_AH1

NC_AF18

R69

10K_4

3

Q11

2N7002E

1

4

THERMTRIP#

A20

THERMDA

A26

THERMDC

A27

AJ28

A28

AG18

AH18

BP1

AG17

BP0

AJ18

BPSCLK

AJ23

BPSCLK-

AH23

AE24

AF24

SCANCLK1

D20

SCANCLK2

C21

SCANEN

D18

SCANSHENB

C19

SCANSHENA

B19

D22

C22

BRN-

A19

C15

SINCHN

C18

K8_ANALOG0

AF21

K8_ANALOG1

AF22

K8_ANALOG2

AF23

K8_ANALOG3

AE23

K1

R2

R3

AA2

AA3

AE9

AE21

AE22

AG2

AG4

AG6

AG7

AG9

AH1

R301 0_4

AF18

MAX6648_AL [12,20]

CPU_VCCA

CPU_PWROK

R309

680_4

THERMTRIP# [12]

Length < 1"

Width : 10mil

T47

T50

T49

T48

T3

T51

T5

CPU_VCCA

R310

10K_4

2

MMBT3904

Q28

13

3

R305

169/F_6

NPWROK [12]

R304 *51.1/F_6

CORE_SENSE

Near Socket754

R308 80.6/F_6

R302 51.1/F_6

R297 51.1/F_6

R46 44.2/F_6

R47 44.2/F_6

R298 680_4

R296 680_4

R312 680_4

R313 680_4

R314 680_4

R307 680_4

R303 680_4

1

3

5

7

RP49 680_8P4R

R306 680_4

R91 51.1/F_6

R300 820_4

R299 820_4

1

3

5

7

RP51 680_8P4R

1

3

5

7

RP48 680_8P4R

1

3

5

7

RP50 680_8P4R

R43 49.9/F_6

R44 49.9/F_6

CPU(HT LINK)

2

3900P_6C570

3900P_6C569

COREFB

COREFB#

Trace route

as 10/10/10

L0_REF1

L0_REF0

LDTREST#

LDTSTOP#

THERMTRIP#

BRN-

SINCHN

DBRDY

DBREQ-

TDI

2

4

TRST-

6

TMS

8

TDO

VDDIO_SENSE

K8_ANALOG2

2

K8_ANALOG3

4

K8_ANALOG1

6

K8_ANALOG0

8

BP1

2

BP0

4

SCANSHENA

6

SCANCLK2

8

SCANSHENB

2

SCANCLK1

4

TCK

6

SCANEN

8

CPU_VCCA

R71

330_4

2

1 3

Q10 MMBT3904

BPSCLK

BPSCLK-

CTLIP1

CTLIN1

1999_SHT#THERMTRIP#

Must shut down

when asserted

PROJECT : ZL5

Quanta Computer Inc.

CPU_CLK

CPU_CLKFBCLKOUT- FBCLKOUT

VCC_CORE

+1.2V_HT

CPU_VCCA

2.5VSUS

2.5VSUS

+1.2V_HT

R58 33_4

Size Document Number Rev

Date: Sheet

CPUCLK+ [2]

CPUCLK- [2]

COREFB [25]

COREFB# [25]

1999_SHT# [22]

326Thursday, March 10, 2005

1

3B

of

8

CPU DDR/POWER I/F

U21E

AMD K8

GROUND

B2

VSS1

B4

VSS2

B6

VSS3

B8

VSS4

B10

VSS5

B12

VSS6

B14

VSS7

B16

VSS8

B22

VSS9

D D

C C

B B

A A

B25

VSS10

B26

VSS11

B28

VSS12

C25

VSS13

C27

VSS14

C29

VSS15

D2

VSS16

D16

VSS17

D19

VSS18

D21

VSS19

D23

VSS20

D26

VSS21

D28

VSS22

E15

VSS23

E16

VSS24

E18

VSS25

E22

VSS26

E24

VSS27

F2

VSS28

F7

VSS29

F9

VSS30

F11

VSS31

F13

VSS32

F15

VSS33

F17

VSS34

F19

VSS35

F21

VSS36

F23

VSS37

G6

VSS38

G8

VSS39

G10

VSS40

G12

VSS41

G14

VSS42

G16

VSS43

G18

VSS44

G20

VSS45

G22

VSS46

G24

VSS47

G28

VSS48

H2

VSS49

H7

VSS50

H9

VSS51

H11

VSS52

H13

VSS53

H15

VSS54

H17

VSS55

H19

VSS56

H21

VSS57

H23

VSS58

H26

VSS59

J6

VSS60

J8

VSS61

J10

VSS62

J12

VSS63

J14

VSS64

J16

VSS65

J18

VSS66

J20

VSS67

J22

VSS68

J24

VSS69

K2

VSS70

K7

VSS71

K9

VSS72

K11

VSS73

K13

VSS74

K15

VSS75

K17

VSS76

K19

VSS77

K21

VSS78

K23

VSS79

L6

VSS80

L8

VSS81

L10

VSS82

L20

VSS83

L22

VSS84

L24

VSS85

L28

VSS86

M2

VSS87

M7

VSS88

M9

VSS89

M21

VSS90

M23

VSS91

M26

VSS92

N6

VSS93

N8

VSS94

N10

VSS95

N20

VSS96

N22

VSS97

N24

VSS98

P2

VSS99

P7

VSS100

P9

VSS101

P21

VSS102

P23

VSS103

R6

VSS104

R8

VSS105

R10

VSS106

R20

VSS107

R22

VSS108

R24

VSS109

8

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

R28

T2

T7

T9

T21

T23

T26

U6

U8

U10

U20

U22

U24

V2

V7

V9

V21

V23

W6

W8

W10

W20

W22

W24

W28

Y2

Y7

Y9

Y11

Y13

Y15

Y17

Y19

Y21

Y23

Y26

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA24

AB2

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AC6

AC8

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AC24

AC28

AD2

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD21

AD23

AD26

AE14

AE16

AE20

AE29

AF2

AF17

AF19

AF26

AF28

AG20

AG21

AG22

AG23

AG24

AG25

AG27

AG29

AH2

AH4

AH6

AH8

AH10

AH12

AH14

AH20

AH22

AH26

AH28

AJ20

AJ22

AJ24

AJ26

MEMZN

MEMZP

MD63

MD62

MD61

MD60

MD59

MD58

MD57

MD56

MD55

MD54

MD53

MD52

MD51

MD50

MD49

MD48

MD47

MD46

MD45

MD44

MD43

MD42

MD41

MD40

MD39

MD38

MD37

MD36

MD35

MD34

MD33

MD32

MD31

MD30

MD29

MD28

MD27

MD26

MD25

MD24

MD23

MD22

MD21

MD20

MD19

MD18

MD17

MD16

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

DM7

DM6

DM5

DM4

DM3

DM2

DM1

DM0

DQS7

DQS6

DQS5

DQS4

DQS3

DQS2

DQS1

DQS0

7

U21B

AMD K8

A18

B17

C16

C17

D17

AE13

D14

C14

A16

B15

A12

B11

A17

A15

C13

A11

A10

B9

C7

A6

C11

A9

A5

B5

C5

A4

E2

E1

A3

B3

E3

F1

G2

G1

L3

L1

G3

J2

L2

M1

W1

W3

AC1

AC3

W2

Y1

AC2

AD1

AE1

AE3

AG3

AJ4

AE2

AF1

AH3

AJ3

AJ5

AJ6

AJ7

AH9

AG5

AH5

AJ9

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

R1

T23

A13

A7

C2

H1

AA1

AG1

AH7

AH13

T1

T27

A14

A8

D1

J1

AB1

AJ2

AJ8

AJ13 M3

7

MEMORY

VTT_A1

VTT_A2

VTT_A3

VTT_A4

VTT_A5

VTT_SENSE

MEMZN

MEMZP

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDQS17

MEMDQS16

MEMDQS15

MEMDQS14

MEMDQS13

MEMDQS12

MEMDQS11

MEMDQS10

MEMDQS9

MEMDQS8

MEMDQS7

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0 MEMADDB0

VTT_B1

VTT_B2

VTT_B3

VTT_B4

VTT_B5

MEMRESET#

MEMVREF1

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

MEMCS#7

MEMCS#6

MEMCS#5

MEMCS#4

MEMCS#3

MEMCS#2

MEMCS#1

MEMCS#0

MEMCKEB

MEMCKEA

MEMCLK#7

MEMCLK7

MEMCLK#6

MEMCLK6

MEMCLK#5

MEMCLK5

MEMCLK#4

MEMCLK4

MEMCLK#3

MEMCLK3

MEMCLK#2

MEMCLK2

MEMCLK#1

MEMCLK1

MEMCLK#0

MEMCLK0

MEMBANKA1

MEMBANKA0

MEMRASA#

MEMCASA#

MEMWEA#

NC_MEMADDA15

NC_MEMADDA14

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMBANKB1

MEMBANKB0

MEMRASB#

MEMCASB#

MEMWEB#

NC_MEMADDB15

NC_MEMADDB14

MEMADDB13

MEMADDB12

MEMADDB11

MEMADDB10

MEMADDB9

MEMADDB8

MEMADDB7

MEMADDB6

MEMADDB5

MEMADDB4

MEMADDB3

MEMADDB2

MEMADDB1

6

AF16

AG15

AG16

AH16

AJ17

AG10

AG12

N3

N1

U3

V1

N2

P1

U1

U2

D8

C8

E8

E7

D6

E6

C4

E5

AE7

AE8

C10

D10

E11

E12

AG8

AF8

AE10

AF10

V4

V3

K4

K5

P5

R5

P4

P3

K3

H3

H5

D4

G5

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

L5

J5

H4

F5

F4

E14

D12

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

2.5VSUS

6

DDR_VTTDDR_VTT

MEMRST#

1.25VREF_CPU

CS#7

CS#6

CS#5

CS#4

CS#3

CS#2

CS#1

CS#0

CKE1

CKE0

DCLK#7

DCLK7

DCLK#6

DCLK6

DCLK#5

DCLK5

DCLK#4

DCLK4

DCLK#3

DCLK3

DCLK#2

DCLK2

DCLK#1

DCLK1

DCLK#0

DCLK0

MEMBAA1

MEMBAA0

RAS#A

CAS#A

WE#A

MAA13

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

MEMBAB1

MEMBAB0

RAS#B

CAS#B

WE#B

MAB13

MAB12

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

R89

100/F_4

R88

100/F_4

C225

.1U_4

C213

.1U_4

T21

T12

T10

T9

T11

CS#3 [5]

CS#2 [5]

CS#1 [5]

CS#0 [5]

CKE1 [5]

CKE0 [5]

DCLK#7 [5]

DCLK7 [5]

DCLK#6 [5]

DCLK6 [5]

DCLK#5 [5]

DCLK5 [5]

DCLK#4 [5]

DCLK4 [5]

T22

T26

T24

T25

MEMBAA1 [5]

MEMBAA0 [5]

RAS#A [5]

CAS#A [5]

WE#A [5]

T6

T8

MEMBAB1 [5]

MEMBAB0 [5]

RAS#B [5]

CAS#B [5]

WE#B [5]

T4

T7

> 10mil

1.25VREF_CPU

C214

5

MD4

MD1

MD5

MD0

MD6

RP18 10_8P4R_4

MD7

MD3

MD2

MD11

RP20 10_8P4R_4

MD15

MD14

MD10

MD13

RP4 10_8P4R_4

MD9

MD8

MD12

MD23

RP2 10_8P4R_4

MD19

MD18

MD22

MD17

RP7 10_8P4R_4

MD20

MD21

MD16

MD29

RP5 10_8P4R_4

MD25

MD28

MD24

MD26

RP8 10_8P4R_4

MD31

MD30

MD27

MD35

RP9 10_8P4R_4

MD38

MD39

MD34

MD33

RP11 10_8P4R_4

MD32

MD36

MD37

MD43

RP10 10_8P4R_4

MD46

MD47

MD42

MD44

RP14 10_8P4R_4

MD41

MD40

MD45

MD53

RP12 10_8P4R_4

MD52

MD48

MD49

MD51

RP15 10_8P4R_4

MD55

MD54

MD50

MD57

RP17 10_8P4R_4

MD61

MD60

MD56

MD59

RP23 10_8P4R_4

MD63

MD62

MD58

RP24 10_8P4R_4

DQS0

DM0

RP19 10_4P2R_4

DQS3

DM3

DQS4

RP21 10_4P2R_4

DM4

DM7

RP22 10_4P2R_4

DQS7

DM1

RP1 10_4P2R_4

DQS1

DQS2

RP3 10_4P2R_4

DM5

RP6 10_4P2R_4

DQS5

DM6

RP13 10_4P2R_4

DQS6

RP16 10_4P2R_4

DCLK#7

DCLK#6

Trace length between resistor &

CPU must be less than 1000mil

R87 *0_4

C591

C194

.01U_4

*100P_4

5

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1 2

43

1 2

43

1 2

43

1 2

43

1 2

43

1 2

43

1 2

43

1 2

43

R82 120_4

R76 120_4

R86 120_4

R81 120_4

R103 *120_4

R104 *120_4

1.25VREF

4

MD_4

MD_1

MD_5

MD_0

MD_6

MD_7

MD_3

MD_2

MD_11

MD_15

MD_14

MD_10

MD_13

MD_9

MD_8

MD_12

MD_23

MD_19

MD_18

MD_22

MD_17

MD_20

MD_21

MD_16

MD_29

MD_25

MD_28

MD_24

MD_26

MD_31

MD_30

MD_27

MD_35

MD_38

MD_39

MD_34

MD_33

MD_32

MD_36

MD_37

MD_43

MD_46

MD_47

MD_42

MD_44

MD_41

MD_40

MD_45

MD_53

MD_52

MD_48

MD_49

MD_51

MD_55

MD_54

MD_50

MD_57

MD_61

MD_60

MD_56

MD_59

MD_63

MD_62

MD_58

DQS_0

DM_0

DQS_3

DM_3

DQS_4

DM_4

DM_7

DQS_7

DM_1

DQS_1

DQS_2

DM_2DM2

DM_5

DQS_5

DM_6

DQS_6

DCLK7

DCLK6

DCLK5DCLK#5

DCLK4DCLK#4

DCLK1DCLK#1

DCLK0DCLK#0

VCC_CORE 2.5VSUS

DCLK#1

R107 10K_4

DCLK#0

R109 10K_4

DCLK1 MEMZN

R106 10K_4

DCLK0

R108 10K_41000P_4

4

U21D

AMD K8

B20

VDD1

B24

VDD2

D24

VDD3

E19

VDD4

E21

VDD5

E23

VDD6

E28

VDD7

F18

VDD8

F20

VDD9

F22

VDD10

F24

VDD11

F26

VDD12

G11

VDD13

G13

VDD14

G15

VDD15

G17

VDD16

G19

VDD17

G21

VDD18

G23

VDD19

H10

VDD20

H12

VDD21

H14

VDD22

H16

VDD23

H18

VDD24

H20

VDD25

H22

VDD26

H24

VDD27

J9

VDD28

J11

VDD29

J13

VDD30

J15

VDD31

J17

VDD32

J19

VDD33

J21

VDD34

J23

VDD35

J28

VDD36

K8

VDD37

K10

VDD38

K12

VDD39

K14

VDD40

K16

VDD41

K18

VDD42

K20

VDD43

K22

VDD44

K24

VDD45

K26

VDD46

L7

VDD47

L9

VDD48

L21

VDD49

L23

VDD50

M8

VDD51

M10

VDD52

M20

VDD53

M22

VDD54

M24

VDD55

N7

VDD56

N9

VDD57

N21

VDD58

N23

VDD59

N28

VDD60

P8

VDD61

P10

VDD62

P20

VDD63

P22

VDD64

P24

VDD65

P26

VDD66

R7

VDD67

R9

VDD68

R21

VDD69

R23

VDD70

T8

VDD71

T10

VDD72

T20

VDD73

T22

VDD74

T24

VDD75

U7

VDD76

U9

VDD77

U21

VDD78

U23

VDD79

U28

VDD80

V8

VDD81

V10

VDD82

V20

VDD83

V22

VDD84

V24

VDD85

V26

VDD86

W7

VDD87

W9

VDD88

W21

VDD89

W23

VDD90

Y8

VDD91

Y10 AH24

VDD92 VDD133

2.5VSUS

POWER

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VDDIO46

VDDIO47

VDDIO48

VDDIO49

VDDIO50

VDD93

VDD94

VDD95

VDD96

VDD97

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD130

VDD131

VDD132

Trace length < 1"

MEMZP

3

D5

D7

D9

D11

D13

D15

E4

F6

F8

F10

F12

F14

F16

G4

G7

G9

H6

H8

J4

J7

K6

L4

M6

N4

P6

R4

T6

U4

V6

W4

Y6

AA4

AA7

AB6

AB8

AC4

AC7

AC9

AD6

AD8

AD10

AD12

AD14

AD16

AE4

AF5

AF7

AF9

AF11

AF13

Y12

Y14

Y16

Y18

Y20

Y22

Y24

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AA28

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AB24

AB26

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD18

AD20

AD22

AD24

AE17

AE25

AE27

AG19

R72 34.8/F_6

R73 34.8/F_6

3

2

2.5VSUS VCC_CORE VCC_CORE

C580 150U/4V_3528

C236 150U/4V_3528

C224 *4.7U/10V_6

C185 *4.7U/10V_6

C173 4.7U/10V_6

C237 4.7U/10V_6

C215 4.7U/10V_6

C234 4.7U/10V_6

C232 4.7U/10V_6

C222 4.7U/10V_6

2.5VSUS

+

+

.1U_4C220

.1U_4C235

.1U_4C216

.1U_4C217

.1U_4C171

.1U_4C223

.22U_4C208

.1U_4C193

.1U_4C238

.1U_4C200

.22U_4C191 .1U_4C108

.22U_4C179

.1U_4C162

.22U_4C219

.1U_4C218

Size Document Number Rev

CPU(DDR/POWER)

Date: Sheet

2

.22U_4C96

.1U_4C203

.1U_4C202

.1U_4C198

.22U_4C82

.22U_4C104

.1U_4C204

.22U_4C109

.1U_4C192

.1U_4C105

.1U_4C199

.22U_4C110

.1U_4C201

.1U_4C207

.1U_4C123

.1U_4C206

.1U_4C581

.22U_4C583

.1U_4C584

.22U_4C582

.22U_4C95

.22U_4C577

.1U_4C106

DDR_VTT

MD_[63..0]

DQS_[7..0]

DM_[7..0]

MAA[13..0]

MAB[13..0]

PROJECT : ZL5

Quanta Computer Inc.

1

C182 150U/4V_3528

+

C183 150U/4V_3528

+

C130 4.7U/10V_6

C177 4.7U/10V_6

C129 4.7U/10V_6

C132 4.7U/10V_6

C133 4.7U/10V_6

C176 4.7U/10V_6

C190 4.7U/10V_6

C134 4.7U/10V_6

C188 4.7U/10V_6

C189 4.7U/10V_6

C175 4.7U/10V_6

C131 4.7U/10V_6

.1U_4C574

.22U_4C575

.1U_4C205

.1U_4C576

.1U_4C111

.1U_4C107

C422 150U/4V_3528

+

C579 10U/10V_8

C210 10U/10V_8

.22U_4C148

.22U_4C158

.1U_4C156

.1U_4C174

.1U_4C157

.1U_4C146

.1U_4C163

.1U_4C143

.1U_4C149

.1U_4C164

MD_[63..0] [5]

DQS_[7..0] [5]

DM_[7..0] [5]

MAA[13..0] [5]

MAB[13..0] [5]

426Thursday, March 10, 2005

of

1

3B

8

91021223334364546575869708182929394113

CN21

VDD

VDD

MAB0

112

MAB1

MAB2

MAB3

MAB4

D D

MEMBAB0[4] MEMBAA0[4]

MEMBAB1[4]

C C

DCLK#4[4]

DCLK#6[4]

2.5VSUS

SMBCLK[2,12]

B B

+3V

A A

C334

1U_6

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

MEMBAB0

MEMBAB1 MEMBAA1

DM_0

DM_1

DM_2

DM_3

DM_4

DM_5

DM_6

DM_7

DQS_0

DQS_1

DQS_2

DQS_3

DQS_4

DQS_5

DQS_6

DQS_7

RAS#B

RAS#B[4]

WE#B

WE#B[4]

CAS#B

CAS#B[4]

CS#2

CS#2[4]

CS#3

CS#3[4]

CKE1[4]

DCLK4

DCLK4[4]

DCLK#4

DCLK6

DCLK6[4]

DCLK#6

R206 10K_4

R212 10K_4

MVREF_DM0

C321

.1U_4

2.5VSUS 2.5VSUS

100/F_6

R208

100/F_6

8

A0

111

A1

110

A2

109

A3

108

A4

107

A5

106

A6

105

A7

102

A8

101

A9

115

A10/AP

100

A11

99

A12

97

DU/A13

117

BA0

116

BA1

12

DM0

26

DM1

48

DM2

62

DM3

134

DM4

148

DM5

170

DM6

184

DM7

78

DM8

11

DQS0

25

DQS1

47

DQS2

61

DQS3

133

DQS4

147

DQS5

169

DQS6

183

DQS7

77

DQS8

118

RAS#

119

WE#

120

CAS#

121

S0#

122

S1#

96

CKE0

95

CKE1

35

CK0

37

CK0#

160

CK1

158

CK1#

89

CK2

91

CK2#

193

SDA

195

SCL

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

84

CB7

1

VREF

2

VREF

197

VDDSPD

199

VDDID

R213

*10K_4

MD_[63..0]

DQS_[7..0]

DM_[7..0]

C387

.01U_4

MVREF_DM0 MVREF_DM1

C386

C385

.1U_4

.01U_4

VDD

VSS

VSS

VSS

3415162728383940515263647576878890103

7

114

131

132

143

144

155

156

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

UP DOWN

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

104

125

126

137

138

149

150

MD_[63..0] [4]

DQS_[7..0] [4]

DM_[7..0] [4]

C398

1U_6

R179

100/F_6

R146

100/F_6

7

MAA[13..0]

MAB[13..0]

C312

.01U_4

C311

.01U_4

20mil20mil

C310

.1U_4

157

167

168

179

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

159

161

162

173

MAA[13..0] [4]

MAB[13..0] [4]

DDR_VTT

6

180

191

192

VDD

VDD

VDD

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DU

DU

DU

DU

DU/RESET#

DU/BA2

SA0

SA1

SA2

VSS

VSS

VSS

174

185

186

DDR-SODIMM-STD-H4.0

10U/10V_8C366

10U/10V_8C381

10U/10V_8C409

10U/10V_8C315

.1U_4C453

6

5

2.5VSUS2.5VSUS

91021223334364546575869708182929394113

CN20

VDD

VDD

VDD

VDD

MD_1

5

MD_4

7

MD_6

13

MD_7

17

MD_0

6

MD_5

8

MD_2

14

MD_3

18

MD_8

19

MD_12

23

MD_14

29

MD_10

31

MD_9

20

MD_13

24

MD_11

30

MD_15

32

MD_20

41

MD_17

43

MD_23

49

MD_19

53

MD_16

42

MD_21

44

MD_22

50

MD_18

54

MD_28

55

MD_25

59

MD_30

65

MD_27

67

MD_29

56

MD_24

60

MD_26

66

MD_31

68

MD_32

127

MD_33

129

MD_35

135

MD_38

139

MD_37

128

MD_36

130

MD_34

136

MD_39

140

MD_41

141

MD_40

145

MD_47

151

MD_46

153

MD_44

142

MD_45

146

MD_42

152

MD_43

154

MD_48

163

MD_52

165

MD_54

171

MD_50

175

MD_53

164

MD_49

166

MD_55

172

MD_51

176

MD_60

177

MD_56

181

MD_62

187

MD_58

189

MD_61

178

MD_57

182

MD_63

188

MD_59

190

85

MAB13

123

124

200

86

98

194

196

198

DDR_VTT DDR_VTT DDR_VTT DDR_VTT

R217

10K_4

+3V

2.5VSUS

.1U_4C454

.1U_4C450

.1U_4C465

.1U_4C452

.1U_4C451

.1U_4C449

.1U_4C472

.1U_4C419

.1U_4C474

.1U_4C425

.1U_4C475

.1U_4C480

.1U_4C468

.1U_4C478

.1U_4C467

.1U_4C466

MEMBAA1[4]

DCLK#5[4]

DCLK#7[4]

SMBDAT[2,12]SMBDAT[2,12]

SMBCLK[2,12]

+3V

RAS#A[4]

WE#A[4]

CAS#A[4]

CS#0[4]

CS#1[4]

CKE0[4]

DCLK5[4]

DCLK7[4]

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MEMBAA0

DM_0

DM_1

DM_2

DM_3

DM_4

DM_5

DM_6

DM_7

DQS_0

DQS_1

DQS_2

DQS_3

DQS_4

DQS_5

DQS_6

DQS_7

RAS#A

WE#A

CAS#A

CS#0

CS#1

DCLK5

DCLK#5

DCLK7

DCLK#7

R144 10K_4

R148 10K_4

MVREF_DM1

C305

.1U_4

5

.01U_4C448

.01U_4C441

.01U_4C440

.01U_4C423

.01U_4C471

.01U_4C447

.01U_4C444

.01U_4C442

.01U_4C455

.01U_4C479

.01U_4C470

.01U_4C446

.01U_4C445

.01U_4C443

R132

*10K_4

112

A0

111

A1

110

A2

109

A3

108

A4

107

A5

106

A6

105

A7

102

A8

101

A9

115

A10/AP

100

A11

99

A12

97

DU/A13

117

BA0

116

BA1

12

DM0

26

DM1

48

DM2

62

DM3

134

DM4

148

DM5

170

DM6

184

DM7

78

DM8

11

DQS0

25

DQS1

47

DQS2

61

DQS3

133

DQS4

147

DQS5

169

DQS6

183

DQS7

77

DQS8

118

RAS#

119

WE#

120

CAS#

121

S0#

122

S1#

96

CKE0

95

CKE1

35

CK0

37

CK0#

160

CK1

158

CK1#

89

CK2

91

CK2#

193

SDA

195

SCL

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

84

CB7

1

VREF

2

VREF

197

VDDSPD

199

VDDID

VDD

VSS

VSS

VSS

VSS

VSS

3415162728383940515263647576878890103

1000P_4C476

1000P_4C418

1000P_4C469

1000P_4C285

1000P_4C473.01U_4C319

1000P_4C464

1000P_4C424

1000P_4C457

1000P_4C456

1000P_4C458

1000P_4C274

1000P_4C439

1000P_4C477

1000P_4C438

VDD

VSS

VDD

VSS

4

114

131

132

143

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

DIMM0DIMM1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

104

125

126

137

RAS#A

R181 47_4

WE#A

R180 47_4

CAS#A

R200 47_4

R218 47_4

RAS#B

WE#B

R210 47_4

CAS#B

R220 47_4R209

CS#0

R145 47_4

CS#1

R195 47_4

CS#2

R211 47_4

CS#3

R219 47_4

CKE0

R137 47_4

CKE1

R214 47_4

4

3

144

155

156

157

167

168

179

180

191

192

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DU/RESET#

DU/BA2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

138

149

150

159

161

162

173

174

185

186

DDR-SODIMM-STD-H8.0

MAA6

1 2

MAA4

3 4

MAA8

5 6

MAA11

7 8

MAB12

1 2

MAB9

3 4

MAB7

5 6

MAB5

7 8

MEMBAB0

1 2

MAB13

MAA2

1 2

MAA0

MEMBAA1

1 2

MEMBAA0

MAB3

1 2

MAB1

3

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

MD_1

5

MD_4

7

MD_6

13

MD_7

17

MD_0

6

MD_5

8

MD_2

14

MD_3

18

MD_8

19

MD_12

23

MD_14

29

MD_10

31

MD_9

20

MD_13

24

MD_11

30

MD_15

32

MD_20

41

MD_17

43

MD_23

49

MD_19

53

MD_16

42

MD_21

44

MD_22

50

MD_18

54

MD_28

55

MD_25

59

MD_30

65

MD_27

67

MD_29

56

MD_24

60

MD_26

66

MD_31

68

MD_32

127

MD_33

129

MD_35

135

MD_38

139

MD_37

128

MD_36

130

MD_34

136

MD_39

140

MD_41

141

MD_40

145

MD_47

151

MD_46

153

MD_44

142

MD_45

146

MD_42

152

MD_43

154

MD_48

163

MD_52

165

MD_54

171

MD_50

175

MD_53

164

MD_49

166

MD_55

172

MD_51

176

MD_60

177

MD_56

181

MD_62

187

MD_58

189

MD_61

178

MD_57

182

MD_63

188

MD_59

190

85

DU

MAA13

123

DU

124

DU

200

DU

86

98

194

SA0

196

SA1

198

SA2

DDR_VTT

47_8P4R_4

RN4

47_8P4R_4

RN6

RP28

47_4P2R_4

43

RP25

47_4P2R_4

43

RP26

47_4P2R_4

43

RP27

47_4P2R_4

43

2

MD_0

MD_1

MD_5

MD_4

MD_6

MD_7

MD_3

MD_2

MD_10

MD_14

MD_15

MD_11

MD_8

MD_12

MD_13

MD_9

MD_23

MD_19

MD_18

MD_22

MD_16

MD_21

MD_20

MD_17

MD_30

MD_27

MD_26

MD_31

MD_25

MD_28

MD_24

MD_29

MD_37

MD_36

MD_32

MD_33

MD_38

MD_35

MD_34

MD_39

MD_46

MD_47

MD_42

MD_43

MD_40

MD_41

MD_45

MD_44

MD_50

MD_54

MD_51

MD_55

MD_49

MD_53

MD_52

MD_48

MD_56

MD_60

MD_57

MD_61

MD_62

MD_58

MD_59

MD_63

DM_0

DQS_0

DM_1

DQS_1

DQS_2

DM_2

DQS_3

DM_3

DM_4

DQS_4

DQS_5

DM_5

DM_6

DQS_6

DQS_7

DM_7

MEMBAB1

MAB10

MAB0

MAB2

MAA13

MAA10

MAA1

MAA3

MAB4

MAB6

MAB8

MAB11

MAA5

MAA7

MAA9

MAA12

Size Document Number Rev

DDR SO-DIMM

Date: Sheet

2

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

3

1

3

1

3

1

3

1

3

1

3

1

3

1

3

1

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

DDR_VTT

RN22

2

56_4P2R_4

4

RN23

2

56_4P2R_4

4

RN24

2

56_4P2R_4

4

RN25

2

56_4P2R_4

4

RN26

2

56_4P2R_4

4

RN27

2

56_4P2R_4

4

RN28

2

56_4P2R_4

4

RN29

2

56_4P2R_4

4

RN30

2

56_4P2R_4

4

RN31

2

56_4P2R_4

4

RN32

2

56_4P2R_4

4

RN33

2

56_4P2R_4

4

RN34

2

56_4P2R_4

4

RN35

2

56_4P2R_4

4

RN36

2

56_4P2R_4

4

RN37

2

56_4P2R_4

4

RN38

2

56_4P2R_4

4

RN39

2

56_4P2R_4

4

RN40

2

56_4P2R_4

4

RN41

2

56_4P2R_4

4

RN42

2

56_4P2R_4

4

RN43

2

56_4P2R_4

4

RN44

2

56_4P2R_4

4

RN45

2

56_4P2R_4

4

RN46

2

56_4P2R_4

4

RN47

2

56_4P2R_4

4

RN48

2

56_4P2R_4

4

RN49

2

56_4P2R_4

4

RN50

2

56_4P2R_4

4

RN51

2

56_4P2R_4

4

RN52

2

56_4P2R_4

4

RN53

2

56_4P2R_4

4

DDR_VTT

RN17

4

68_4P2R_4

2

RN16

4

68_4P2R_4

2

RN18

4

68_4P2R_4

2

RN19

4

68_4P2R_4

2

RN12

4

68_4P2R_4

2

RN13

4

68_4P2R_4

2

RN14

4

68_4P2R_4

2

RN15

4

68_4P2R_4

2

DDR_VTT

47_8P4R_4

RN10

47_8P4R_4

RN2

47_8P4R_4

RN9

47_8P4R_4

RN1

PROJECT : ZL5

Quanta Computer Inc.

1

2.5VSUS

C373 10U/10V_8

C322 10U/10V_8

C370 10U/10V_8

C365 10U/10V_8

C390 10U/10V_8

C397 10U/10V_8

C367 10U/10V_8

C369 10U/10V_8

C400 .1U_4

2.5VSUS

C320 .1U_4

C272 .1U_4

C259 .1U_4

C348 .1U_4

C339 .1U_4

2.5VSUS

C391 .1U_4

C345 .1U_4

C269 .1U_4

C343 .1U_4

C352 .1U_4

2.5VSUS

C282 .01U_4

C258 .01U_4

C273 .01U_4

C255 .01U_4

C330 .01U_4

2.5VSUS

C254 .01U_4

C323 .01U_4

C351 .01U_4

C342 .01U_4

C327 .01U_4

2.5VSUS

C267 1000P_4

C401 1000P_4

C349 1000P_4

C318 1000P_4

C402 1000P_4

526Thursday, March 10, 2005

1

.1U_4C399

.1U_4C392

.1U_4C326

.1U_4C393

.1U_4C325

.1U_4C411

.1U_4C395

.1U_4C307

.1U_4C413

.1U_4C359

.1U_4C346

.1U_4C262

.1U_4C394

.1U_4C308

.1U_4C405

.01U_4C329

.01U_4C335

.01U_4C341

.01U_4C347

.01U_4C263

.01U_4C264

.01U_4C331

.01U_4C260

.01U_4C256

.01U_4C336

1000P_4C403

1000P_4C406

1000P_4C404

1000P_4C333

1000P_4C332

1000P_4C296

1000P_4C328

1000P_4C316

1000P_4C344

of

3B

8

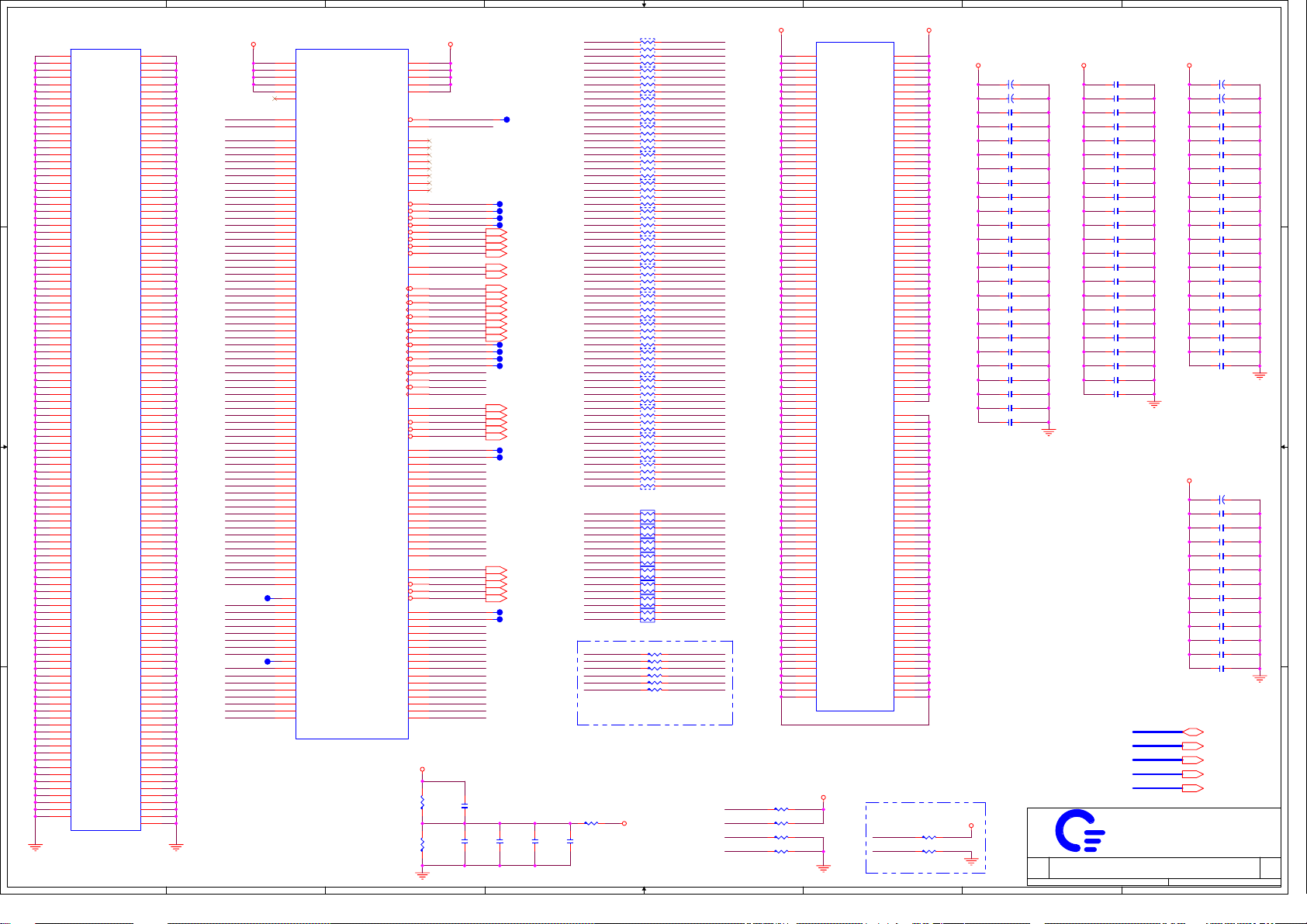

CADON0

CADOP0

CADON1

CADOP1

CADON2

CADOP2

CADON3

CADOP3

CADON4

CADOP4

CADON5

CADOP5

CADON6

CADOP6

CADON7

CADOP7

CADON8

CADOP8

CADON9

CADOP9

CADON10

CADOP10

CADON11

CADOP11

CADON12

CADOP12

CADON13

CADOP13

CADON14

CADOP14

CADON15

CADOP15

LRCOMP

755CLK755CLK+

HTAVDD

HTAVSS

HTPHYAVDD

HTPHYAVSS

CPUCLK1_L

CPUCLK1_H

CADIP[15..0]

CADIN[15..0]

CADOP[15..0]

CADON[15..0]

R49 75_4

R50 75_4

C136 3900P_6

C122 3900P_6

CADIP[15..0][3]

CADIN[15..0][3]

CADOP[15..0][3]

CADON[15..0][3]

D D

C C

CLKON1[3]

CLKOP1[3]

CLKON0[3]

B B

A A

CLKOP0[3]

CTLON0[3]

CTLOP0[3]

LDTSTOP#[3]

LDTREQ#[12]

LDTREST#[3]

+1.2V_HT

CPUCLK1_L[2]

CPUCLK1_H[2]

8

N27

P27

M29

N29

L27

M27

K29

L29

H29

J29

G27

H27

F29

G29

E27

F27

N24

P24

M25

N25

L26

M26

K24

L24

H26

J26

G24

H24

F25

G25

E26

F26

C28

J25

K25

J27

K27

D29

E29

A11

A12

C11

B11

C12

B12

E11

D12

D11

7

U20A

LRCAD_N0

LRCAD_P0

LRCAD_N1

LRCAD_P1

LRCAD_N2

LRCAD_P2

LRCAD_N3

LRCAD_P3

LRCAD_N4

LRCAD_P4

LRCAD_N5

LRCAD_P5

LRCAD_N6

LRCAD_P6

LRCAD_N7

LRCAD_P7

LRCAD_N8

LRACD_P8

LRCAD_N9

LRCAD_P9

LRCAD_N10

LRCAD_P10

LRCAD_N11

LRCAD_P11

LRCAD_N12

LRCAD_P12

LRCAD_N13

LRCAD_P13

LRCAD_N14

LRCAD_P14

LRCAD_N15

LRCAD_P15

LRCOMP

LRCLK_N1

LRCLK_P1

LRCLK_N0

LRCLK_P0

LRCTLN

LRCTLP

HTCLKN

HTCLKP

HTAVDD

HTAVSS

HTPHYAVDD

HTPHYAVSS

LDTSTOP#

LDTREQ#

LDTRESET#

M760GX

VBCLK[9]

7

6

CADIP12

CADIN13

CADIP13

F22

F23

D21

LTCAD_P13

LTCAD_N14

LTCAD_N13

CADIN11

CADIP10

CADIN9

CADIN10

CADIN12

CADIP11

D22

F19

LTCAD_P12

LTCAD_P11

LTCAD_N12

F20

D18

D19

LTCAD_P10

LTCAD_N11

CADIP8

CADIP9

E17

E18

F16

LTCAD_P9

LTCAD_N9

LTCAD_N10

CADIP7

CADIN8

F17

A24

LTCAD_P8

LTCAD_P7

LTCAD_N8

CADIN7

HOST_TX

CADIN15

CADIP14

CADIN14

CADIP15

D24

D25

E23

E24

LTCAD_P15

LTCAD_P14

LTCAD_N15

HOST_RX

CADIP6

A25

C23

LTCAD_P6

LTCAD_N7

CADIP5

CADIN6

C24

A22

LTCAD_N6

CADIN5

CADIP4

A23

C21

LTCAD_P5

LTCAD_P4

LTCAD_N5

CADIN4

CADIP3

C22

C19

LTCAD_N4

CADIP2

CADIN3

C20

A18

LTCAD_P3

LTCAD_P2

LTCAD_N3

CADIN2

CADIP1

A19

C17

LTCAD_N2

5

CADIN1

CADIP0

C18

A16

LTCAD_P1

LTCAD_P0

LTCAD_N1

CADIN0

A17

LTCAD_N0

A20

A21

LTCLK_N0

LTCLK_P0

M760-1

LVDS/AGP

SBA7

SBA6

SBA5

SBA4

SBA3

SBA2

SBA1

SBA0

ST0

ST1

ST2

AAD0

AAD1

AAD2

AAD3

AAD4

AAD5

AAD6

AAD7

AAD8

AAD9

AAD10

AAD11

AAD12

AAD13

AAD14

AAD15

AAD16

AAD17

AAD18

AAD19

AAD20

AAD21

AAD22

D2G5D3F4F5E4B3D5C5A5B4V5U6U1U4U3T5T3T6R2P1R5P3P4N2P6N3L3K2K5K6K3J4J1J5G2H4G3F1F2H6E1E3

VAD11

VAD10

5

VAVSYNC

VADE

VBD11

VAHSYNC

VBD10

VBD8

VBD9

R80 10_4

755CLK755CLK+

MVBCLK

R53

169/F_6

VBD3

VBD2

VBD1

VBD0

VAD6

VAD5

VAD7

VAD8

VBD5

VBD7

VBD6

VBD4

6

VAD4

VAD9

E20

E21

LTCLK_P1

LTCLK_N1

AAD23

AAD24

VAD0

VAD1

C26

LTCTLN

AAD25

AAD26

VAD3

VAD2

LTCOMPN

LTCOMPP

C25

A27

B28

LTCTLP

LTCOMP_P

LTCOMP_N

AC/BE#3

AC/BE#2

AC/BE#1

AC/BE#0

AREQ#

AGNT#

AFRAME#

AIRDY#

ATRDY#

ADEVSEL#

ASERR#

ASTOP#

GC_DET#

PIPE#/ADBIH

SB_STB

SB_STB#

AD_STB0

AD_STB#0

AD_STB1

AD_STB#1

AGPCLK

AGPCOMP_P

AGPCOMP_N

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

AGPVREF

AGPVSSREF

AAD27

AAD28

AAD29

AAD30

VBDE

VBCTL0

VBCTL1

VBHSYNC

APAR

RBF#

WBF#

ADBIL

AAD31

VBVSYNC

4

CLKIN0 [3]

CLKIP0 [3]

CLKIN1 [3]

CLKIP1 [3]

CTLIN0 [3]

CTLIP0 [3]

+1.8V

H3

L4

N5

R4

A6

B6

L6

L1

M4

M5

M1

M2

N6

C4

A3

D6

G6

E6

C1

C2

T2

R1

J2

H1

AA1

V2

V3

AA4

AA5

AA2

AA3

V1

V4

GCDET-

R_VAGCLK

R_VBGCLK

AGPRCOMP

AGPRCOMN

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

AVREFGC

R315

4.7K_4

R319 10_4

R85 10_4

Near 200mil

4

R320

*33_4

C606

*22P_4

3

VAD[11..0][9]

VAGCLK[9]

VAHSYNC[9]

VAVSYNC[9]

VADE[9]

VBD[11..0][9]

VBGCLK[9]

VBHSYNC[9]

VBVSYNC[9]

VBDE[9]

VBCTL1[9]

VBCTL0[9]

VBCAD [9]

VBHCLK [9]

AGPCLK0 [2]

20mil

3

VAGCLK

VBGCLK

+1.8V

Near 200mil

2

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

HTAVDD

HTAVSS

HTPHYAVDD

HTPHYAVSS

R62 0_6

C230

.1U_4

C597

.1U_4

C145

.1U_4

C566

.1U_4

Place close to chip

AGPRCOMN

LDTREQ#

R318

124/F_6

R323

124/F_6

Size Document Number Rev

M760GX(HT LINK/AGP)

Date: Sheet

LRCOMP

LTCOMPN

LTCOMPP

AGPRCOMP

VAGCLK

VBGCLK

MVBCLK

Quanta Computer Inc.

2

R90 49.9/F_6

R52 1K_4

R29 100/F_6

R30 49.9/F_6

R36 49.9/F_6

R322 43.2/F_6

C604 *10P_4

C227 *10P_4

C212 *10P_4

PROJECT : ZL5

1

+3V

C181

.01U_4

+3V

L48

WB201209B121QNT03

C601

.01U_4

+3V

L16

WB201209B121QNT03

C153

.01U_4

+3V

L40

WB201209B121QNT03

C568

.01U_4

+1.8V

CPU_VCCA

+1.2V_HT

of

626Thursday, March 10, 2005

1

C59

10U/10V_8

C56

10U/10V_8

C47

10U/10V_8

3B

8

7

6

5

4

3

2

1

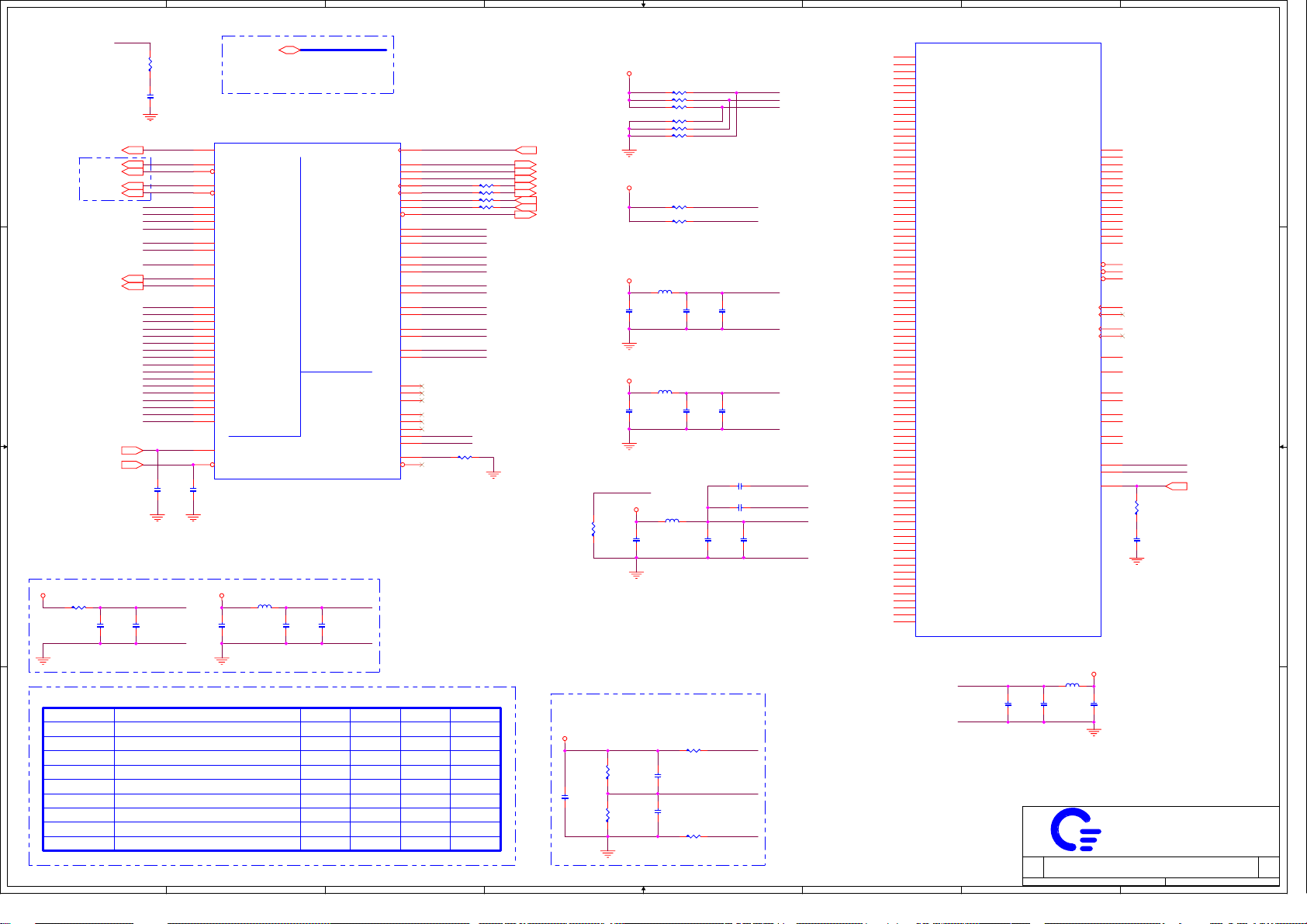

ZCLK0

R321

*33_4

C605

*22P_4

D D

C602

.01U_4

ZCLK0

ZSTB0

ZSTB-0

ZSTB1

ZSTB-1

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

ZCMP_N

ZCMP_P

ZVREF

ZUREQ

ZDREQ

Z1XAVDD

C598

.1U_4

Z1XAVSS

ZCLK0[2]

ZSTB0[11]

ZSTB-0[11]

ZSTB1[11]

ZSTB-1[11]

The differences between

the traces of MuTIOL

Strobes and Data in each

group should be smaller

than 0.05",and strobes

need ground guard trace

ZUREQ[11]

ZDREQ[11]

C C

PWROK[12,20]

PCIRST#[9,11,14,15,16,19,20]

B B

+3V +3V

R324 0_6 L18

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZAD16

C144

*.1U_4

AE1

AH6

AG1

AH2

AB1

AB2

AD3

AD4

AD6

AC6

AD5

AE8

AF8

AG7

AE7

AD7

AG5

AF6

AH4

AG3

AF4

AE5

AE2

AF2

AE3

AF1

AG8

AJ5

AJ7

AJ4

AJ3

F10

C135

*.1U_4

ZAD[0..16][11]

The differences between the

traces of MuTIOL Strobes and

Data should be smaller than 0.05"

U20C

M760GX

ZCLK

ZSTB0

ZSTB#0

ZSTB1

ZSTB#1

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

ZCMP_N

ZCMP_P

ZVREF

ZUREQ

ZDREQ

MuTIOL

ZAD0

ZAD1

ZAD2

ZAD3

M760-3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZAD16

PWROK

WB201209B121QNT03

C62

10U/10V_8

ZAD[0..16]

VOSCI

ROUT

GOUT

BOUT

HSYNC

VSYNC

VGPIO1

VGPIO0

INTA#

RSYNC

LSYNC

CSYNC

VCOMP

VRSET

VVBWN

DACAVDD1

DACAVSS1

DACAVDD2

DACAVSS2

VGA (For 760 Only)

DCLKAVDD

DCLKAVSS

MCLKAVDD

MCLKAVSS

TESTMODE0

TESTMODE1

TESTMODE2

TRAP0

TRAP1

TRAP2

TRAP3

TRAP4

ENTEST

DLLEN#PCIRST#

Control & Hardware

Trap

Z4XAVDD

C228

C231

.1U_4

.01U_4

Z4XAVSS

B10

B8

A8

A9

D8

F9

C7

C8

F8

D7

F7

E8

C9

A10

B9