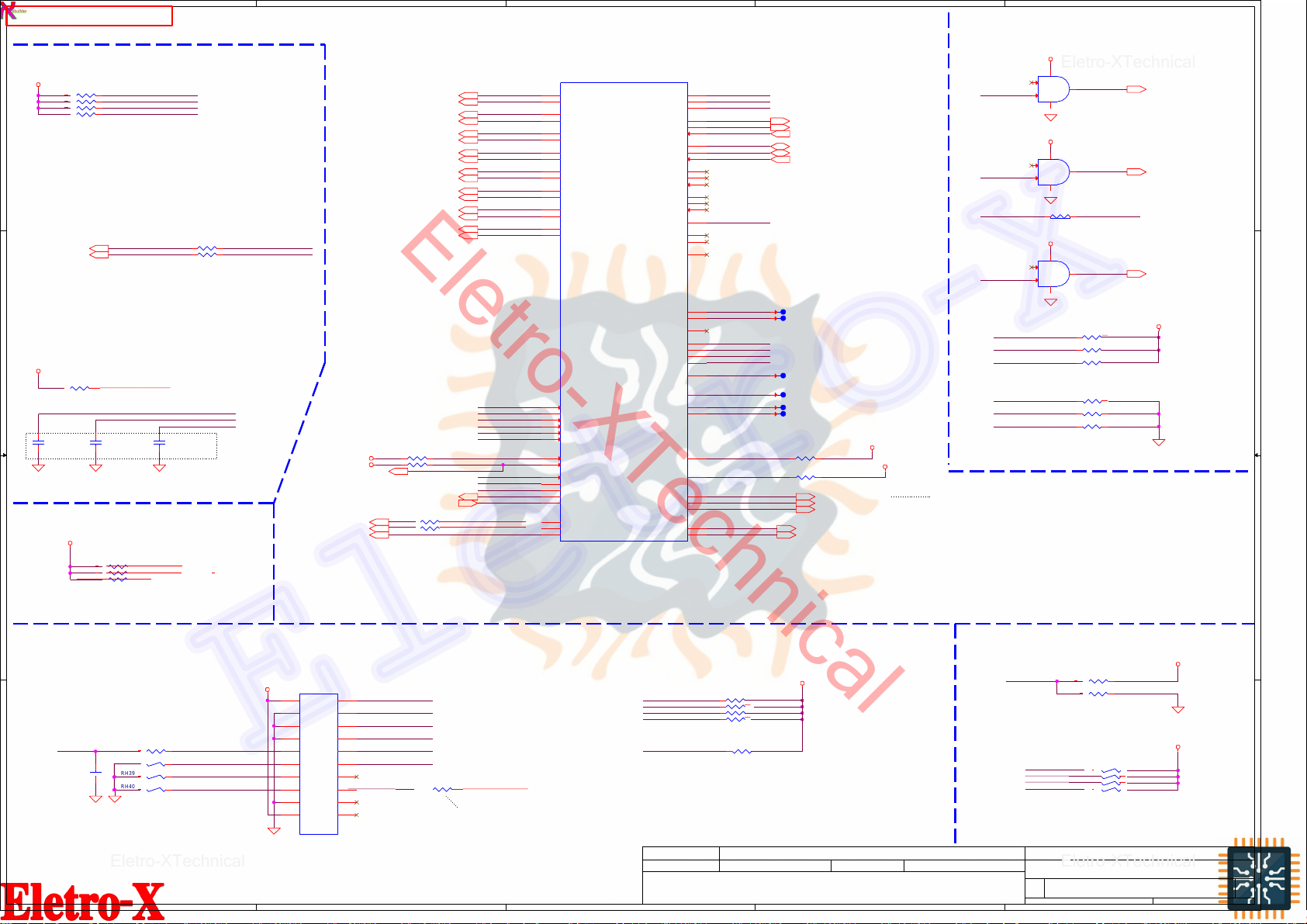

acer a715-41g Schematics

A

1 1

B

C D

E

Compal Confidential

FH5VQ MB Schematics Document

2 2

AMD Picasso Platform

nVidia N18P-G61/G62

3 3

LA-J812P REV:1A

2020-03-09

4 4

SecurityClassification

IssuedDate

THIS SHEET OF ENGINEERING DRAWING IS T HE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPET ENT DIVISION OF R&D

DEPART MENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY

BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN C ONS ENT OF C OMPAL ELECTRONICS, INC.

A

B

Shared wiiith Compalll

2019/08/30 2020/08/30

C D

Compal Secret Data

DecipheredDate

Tiiitllle

Siiize Document Number

Custom

FH5VQ M/B LA-J812P

Compal Electronics, Inc.

COVER PAGE

Sheet

1 112Date: Fridii ay, March 20,2020

E

Rev

of

1A

A

CompalConfidential

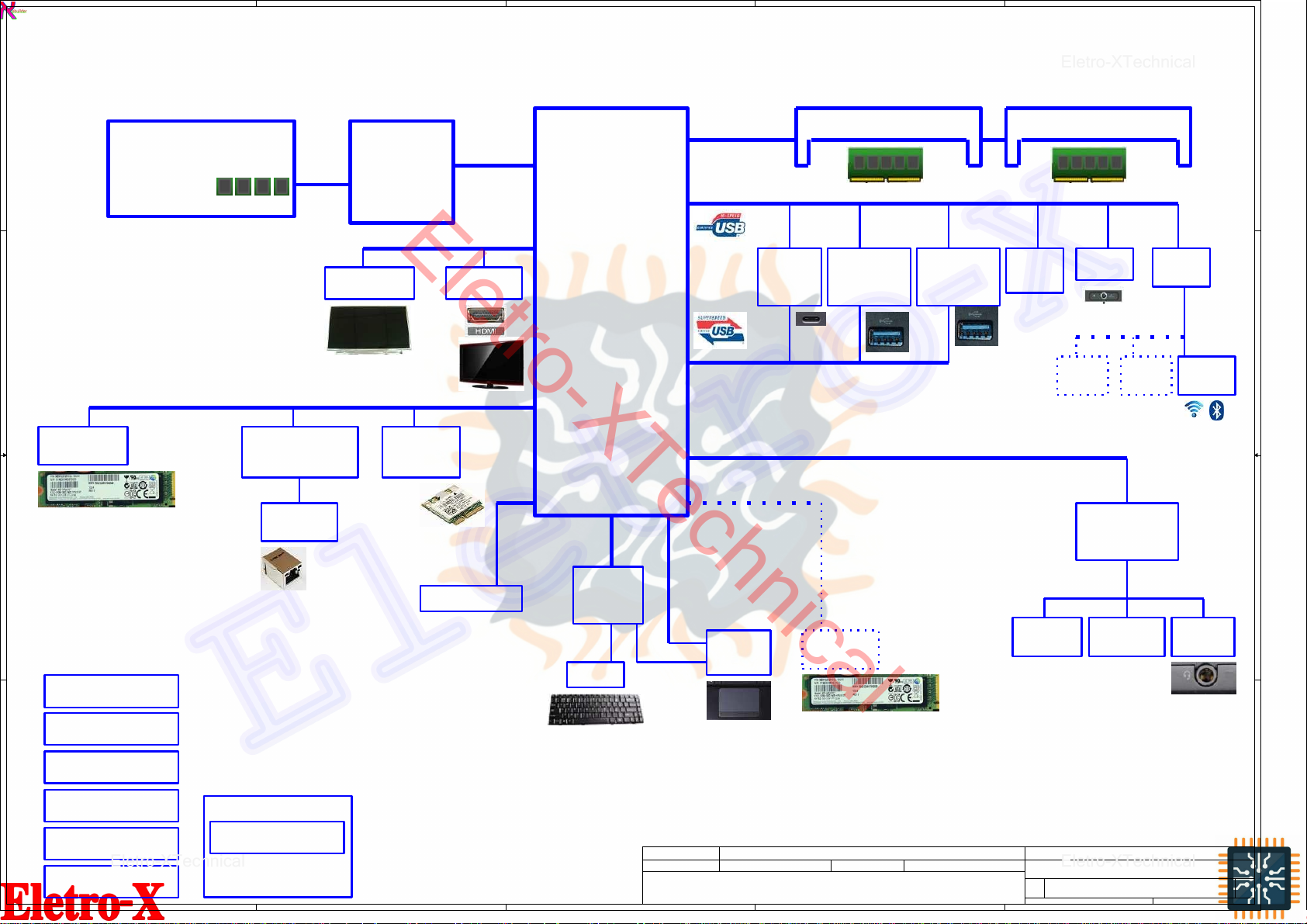

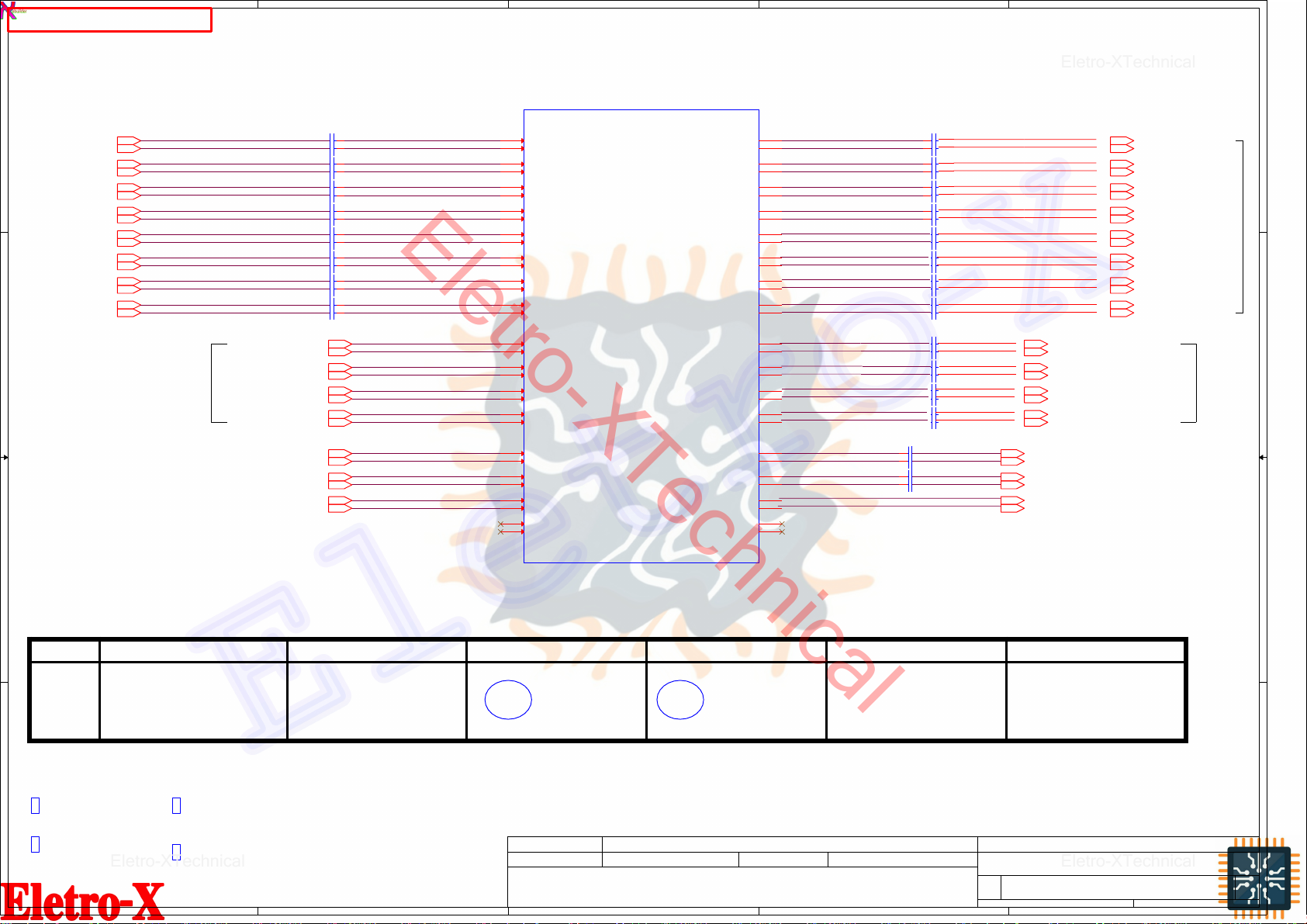

Model Name : FH5VQ

B

C

D

E

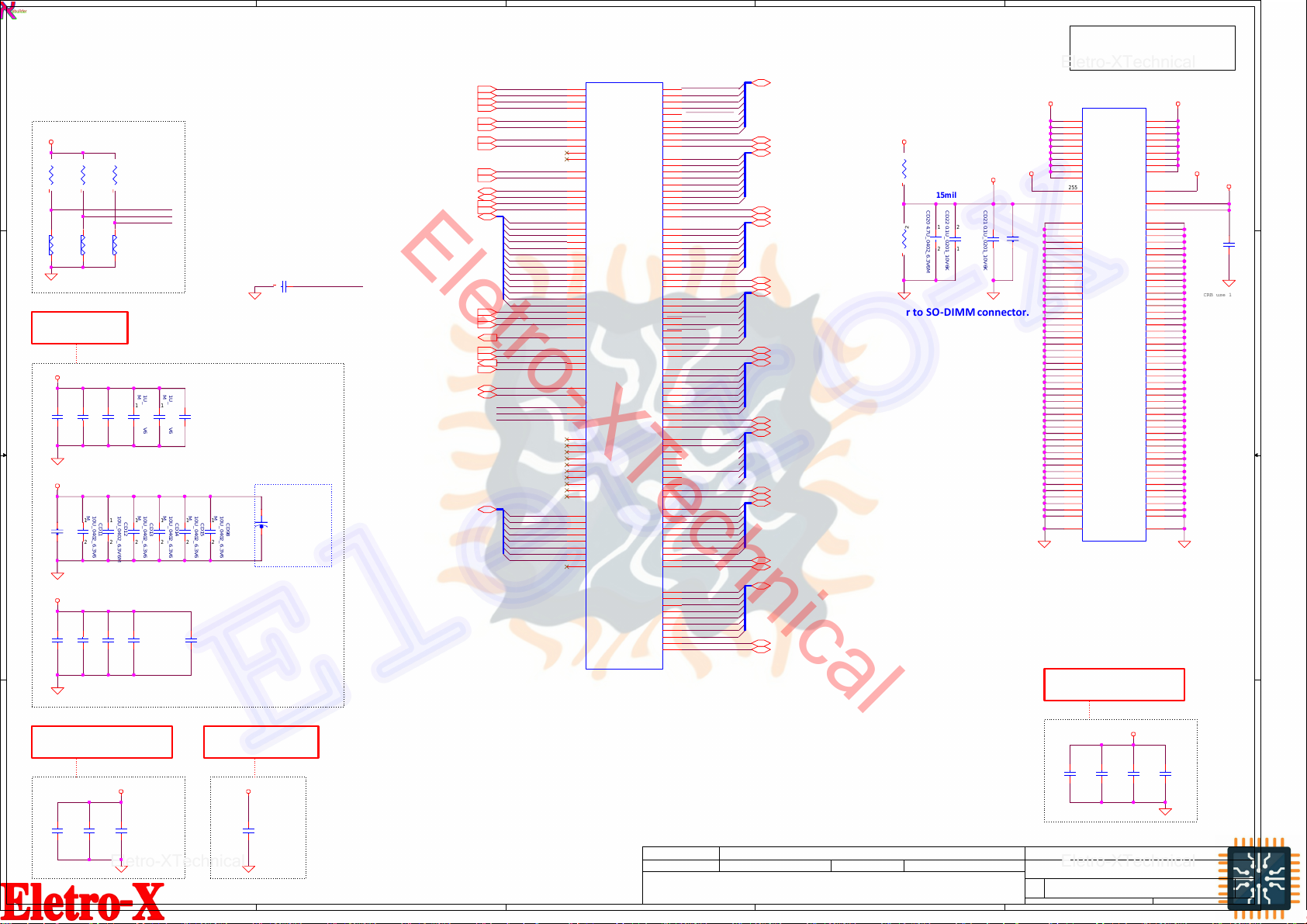

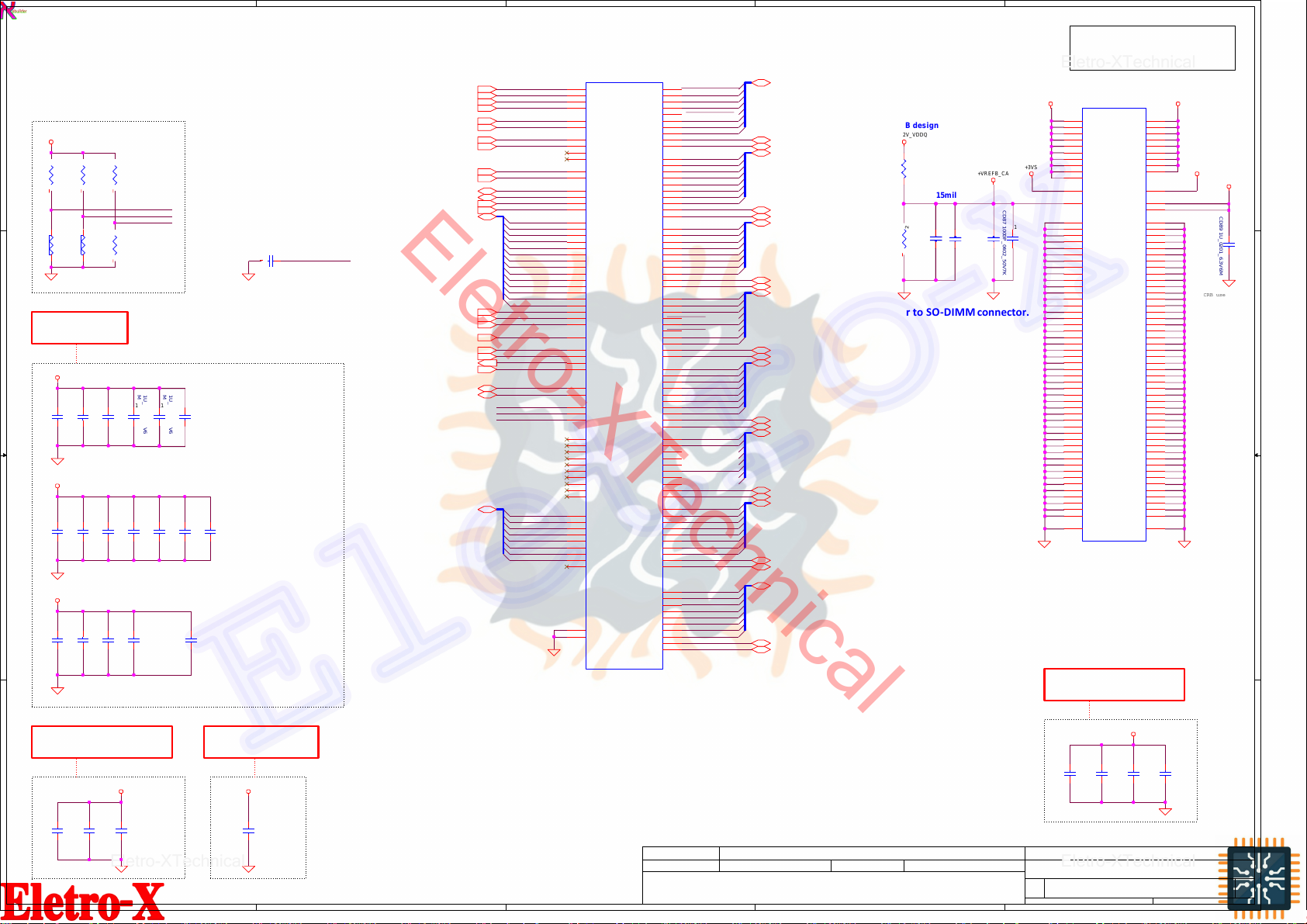

(Channel A) page 23

1 1

GPU

GDDR6 x4

128-bits

page 35~36

2 2

N18P-G61/G62

Port1

eDP Conn.

page 38

page 27~33

PEG x8

Display Port

Port0

HDMIConn.

page40

AMD

Picasso

Memory BUS(DDR4)

1.2V DDRIV

2400Mhz

USB2.0

USB3.0

260pin DDRIV SO-DIMM

Port1

Type-C

Conn.

page 42~43

Type-A (CHG)

Conn.

Port1

Port2Port3

Type-A

Conn.

page 71

Port2Port3

AMD FP5APU

PCIE

(BOM option)

SSD1

NGFFConn.

page 68

LAN

RTL8111H

Port4

page 51

Port5Port 0, 1, 2,3

WLAN/BT

NGFFConn.

page52

SPI

Transformer

RJ45

page51

3 3

page 10

BIOS (8M,1.8V)

Fan Control

page77

BGA1140-balls

page 6~12

LPC

ENE

KBC9022

page 58

page 63

Int.KBD

PS2

I2C

Port3

HD Audio

SATA III

PTP

page 63

Port0

(BOM option)

page 68

SSD1

NGFFConn.

(Channel B) page 24

260pin DDRIV SO-DIMM

Port4

Type-A

(SUB)

page 72

page 38

Int.DMIC

onCamera

page 73

Port0

Finger

Print

page66

Camera

Audio

ALC255

Port5

page38

Touch

Screen

page38

page 56

Int. Speaker

Conn.

page 56

USB2.0 Hub

page 75

WLAN/BT

NGFF Conn.

UAJ

onSub/B

Port1Port2Port3

page52

page 73

RTC CKT.

Power On/Off CKT.

4 4

DC/DC Interface CKT.

Power Circuit DC/DC

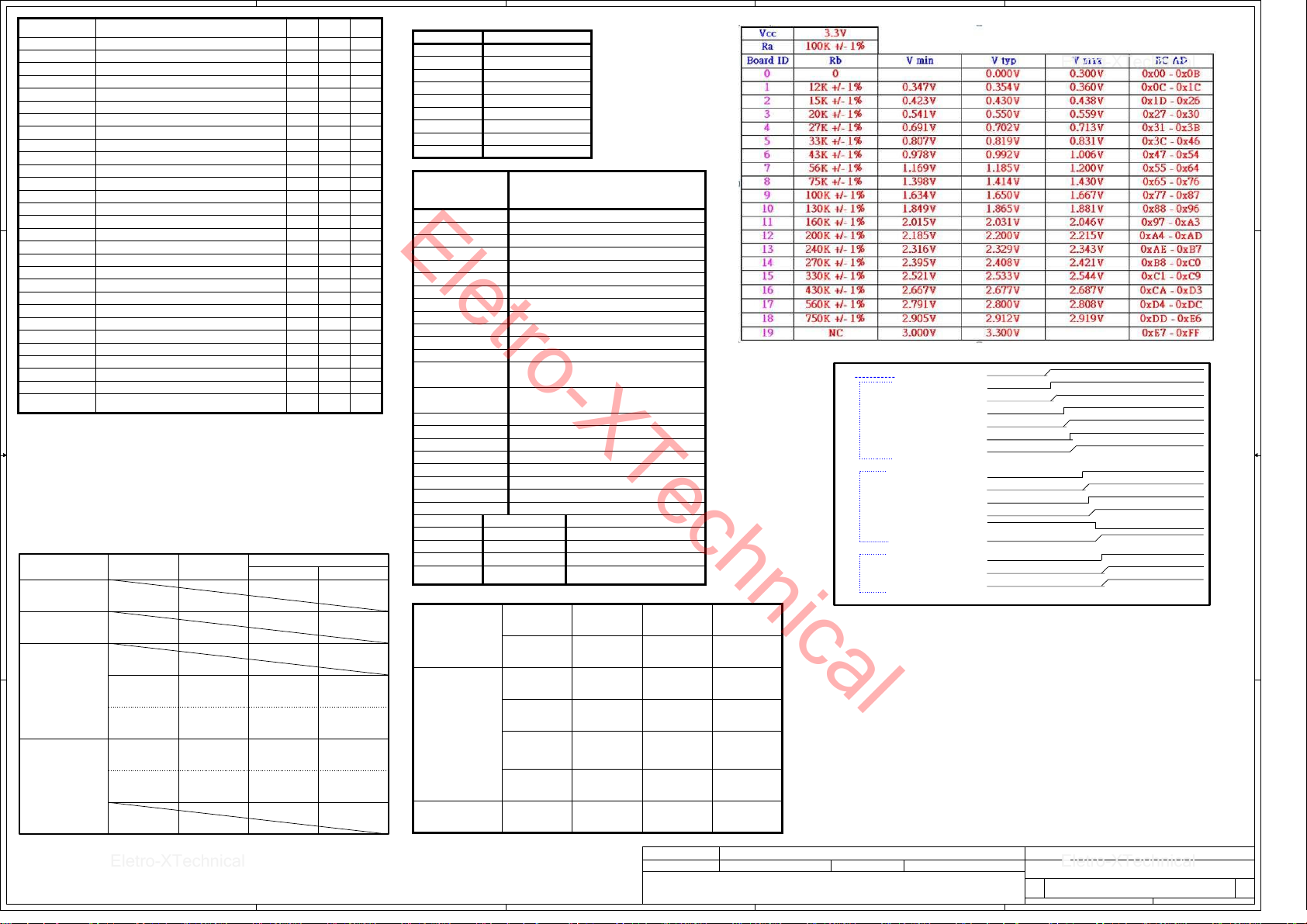

VRAM Config Table

page11

page63

page78

page 82~102

page29

A

Sub Board

LS-J812P IO/B

page 73

SecurityClassification

Issued Date

THIIIS S HE ET OF ENGIIINEERIIING DRA WIIING IIIS THE PR OPRIIIETARY P ROP ER TY OF COM PA L ELECTRONIIICS,,, IIINC... A ND CONTAIIINS CO NF IDE NT IAL

AN D T RA DE SE CRE T IIINFORMATION... THIIIS SHE ET MA Y NO T BE TR AN SF ERE D F ROM T HE CU ST ODY O F TH E C OM PE TEN T DIIIVIIISIIION OF R& D

DE PA RTM EN T E XC EP T AS AUTHOR IIIZED BY C OMP AL ELECTRONIIICS,,, IIINC... NEIIITHER THIIIS SH EE T NO R TH E IIINF ORMATION IIIT CONTAIIINS MA Y

B

BE U SE D BY OR DIIISCLOSE D TO ANY THIIIRD PART Y W IIITHOUT PRIIIOR W RIIITTEN C ONS EN T OF COM PA L ELECTRONIIICS,,, IIINC...

C

2019/ 08/30 2020/08/30

Compal Secret Data

DecipheredDate

Tiiitttllle

Siiize Documenttt Number

Custttom

D

Compal Electronics, Inc.

BLOCK DIAGRAMS

FH5VQ M/B LA-J812P

E

Rev

1A

112Dattte::: Friiiday,,, March 20,,, 2020 Sheettt 2 offf

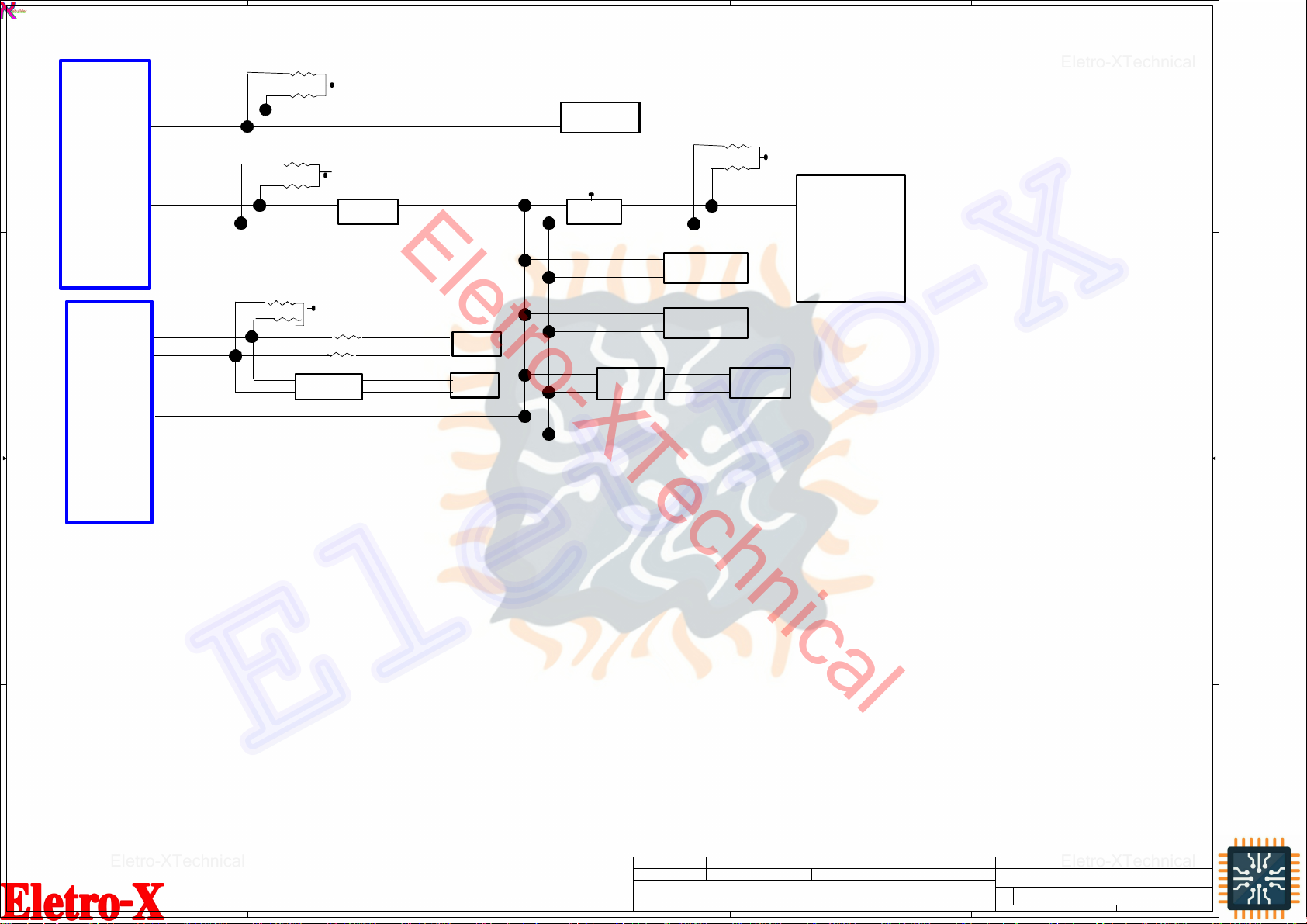

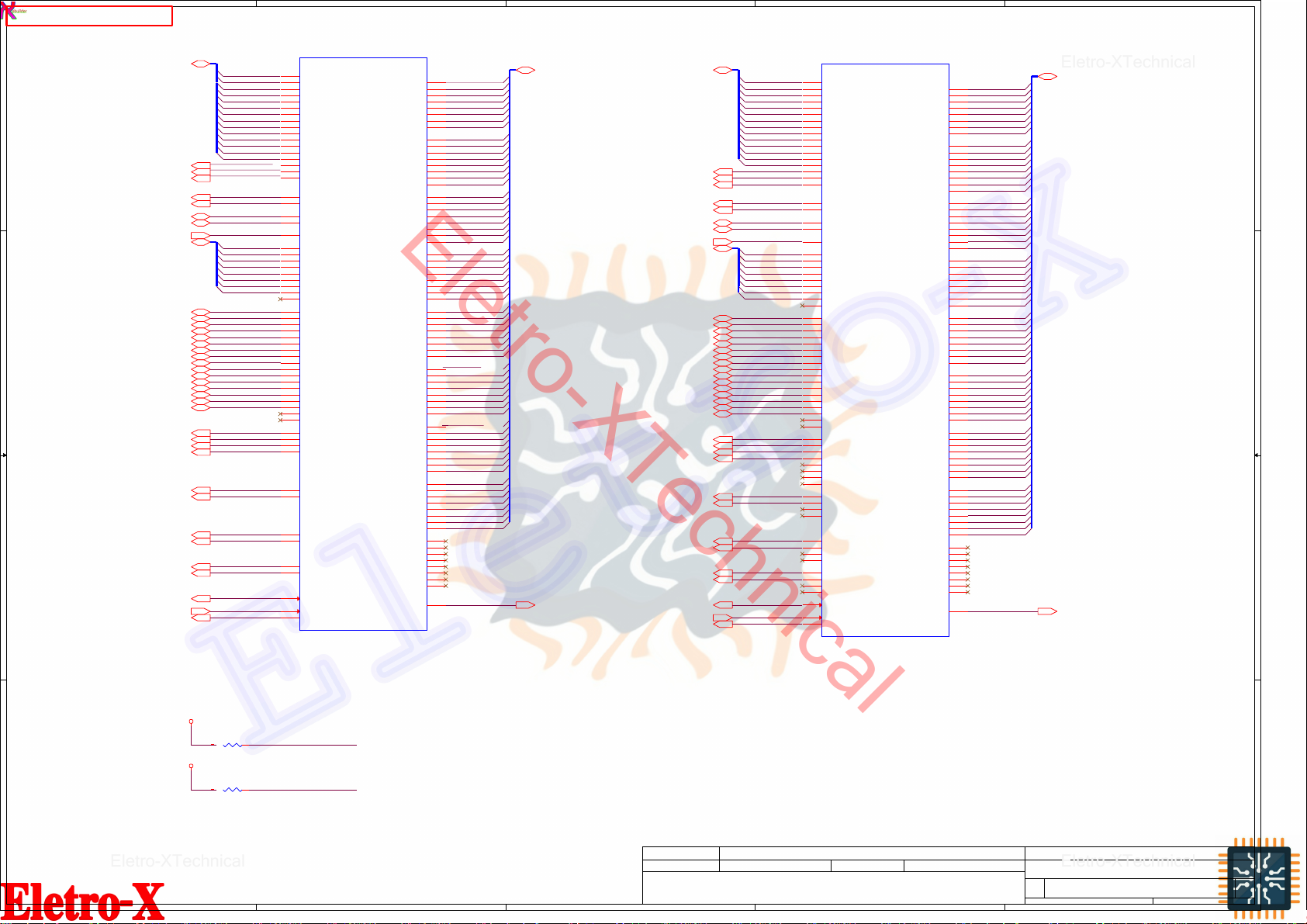

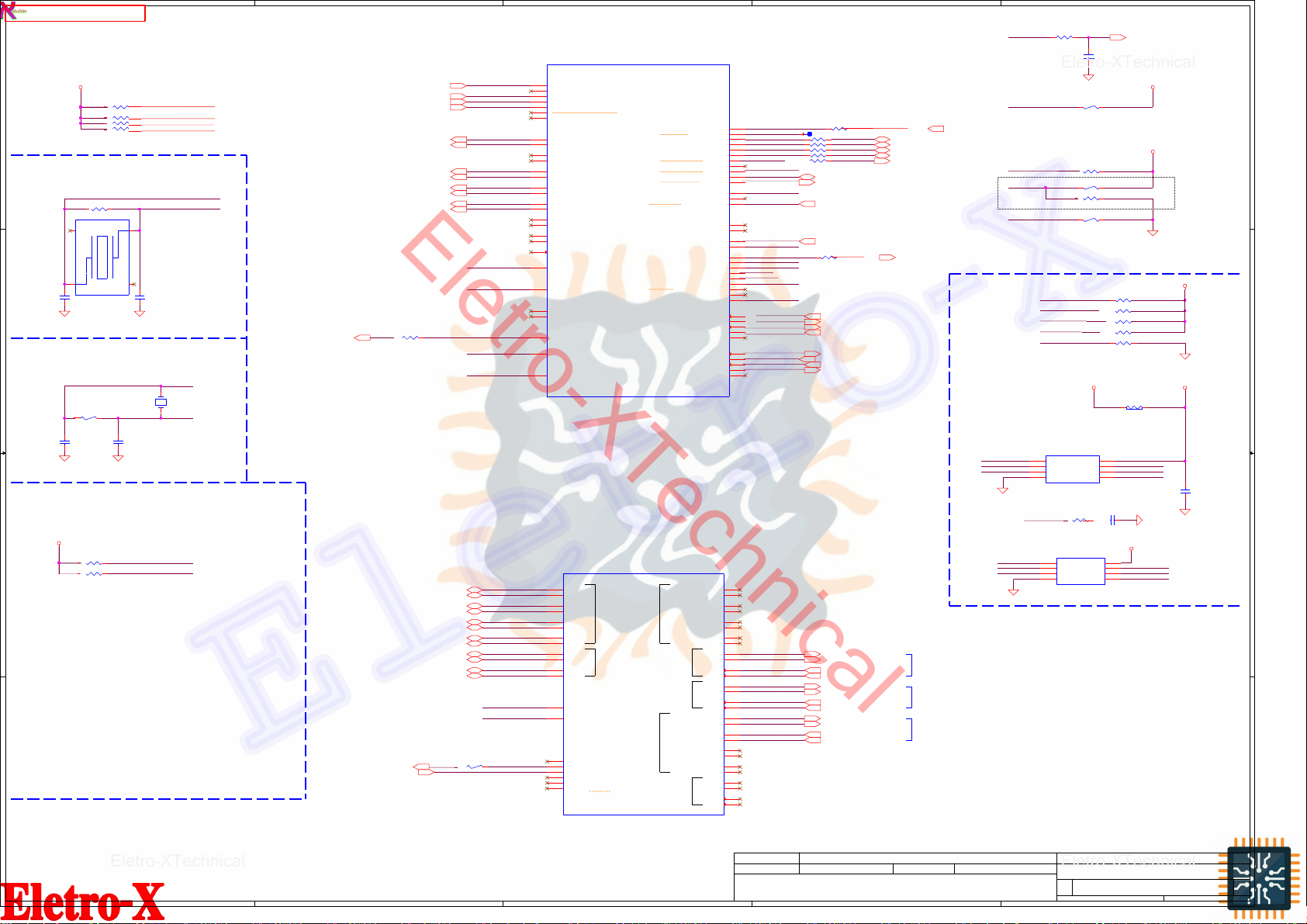

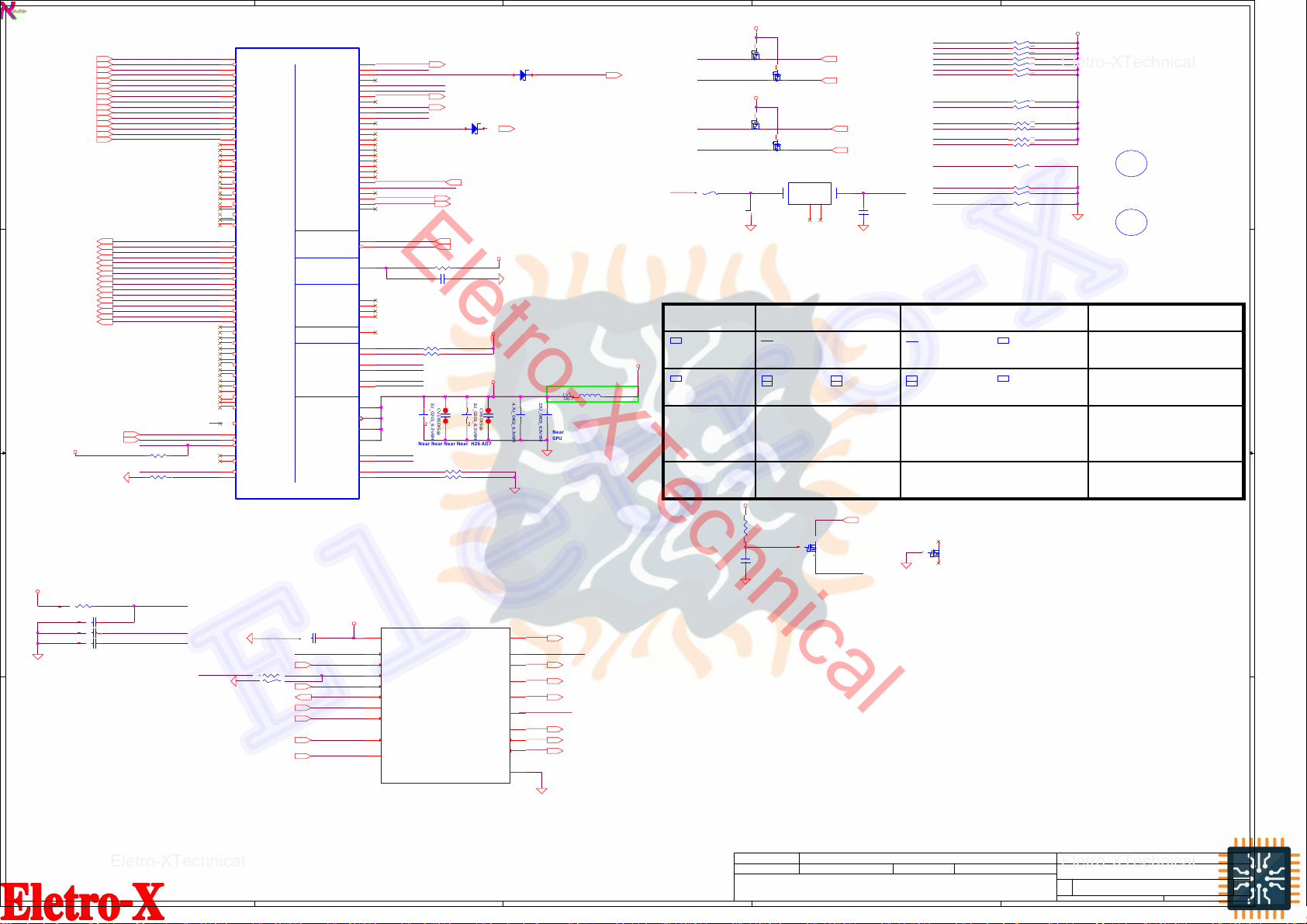

5

2.2K

I2C2_SCL/EGPIO113/SCL0

D D

I2C2_SDA/EGPIO114/SDA0

SMB_0_SCL

SMB_0_SDA

2.2K

+3VS

4

3

2

1

SO-DIMM A &B

1.8K

Picasso

APU

1K

+3VS

1K

APU_SIC

SIC

APU_SID

SID

(RC616,RC617)

R-short

EC_SMB_CK2

EC_SMB_DA2

+1.8VSDGPU_MAIN

(QV2)

PJT138KA2N

VGA_I2CS_SCL

VGA_I2CS_SDA

1.8K

+1.8VSDGPU_AON

nVidia

THERMALSENSOR

G781-1P8F

2.2K

2.2K

EC_SMB_CK1

C C

EC_SMB_DA1

KB9022

EC_SMB_CK2

EC_SMB_DA2

+EC_VCC

100 ohm

100 ohm

(PR317,PR315)

0 ohm_0402

EC_SMB_CK1-1

EC_SMB_DA1-1

EC_SMB_CK1_CHGR

EC_SMB_DA1_CHGR

BATTERY

CONN

Charger

(R4020,R4021)

0 ohm_0402

THERMALSENSOR

G753T11U

CSCL

CSDA

HDMIRetimer

PS8409A

2.2K

N18P-G61/

N18P-G62

B B

A A

Securiiity Clllassiiifiiicatiiion

Issued Date

THIIIS SHE ET OF ENGIIINEERIIING DRAWIIING IIIS THE PROPRIIIETARY PROPERT Y OF COMP AL ELECTRONIIICS,,, IIINC... AND CONTAIIINS CONFIIIDENTIIIAL AND

TRADE SECRE T IIINFORMATIIION... THIIIS SHE ET MAY NOT BE TRAN SFERED FROM THE CUSTO DY O F THE COMP ETENT DIIIVIIISIIION OF R &D

DEPAR TMENT EXCEP T AS AUTHORIIIZED BY COMPAL ELECTRONIIICS,,, IIINC...NEIIITHER THIIIS SH EET NOR THE IIINFORMATIIION IIIT CONTAIIINS

5

4

MAY B E USE D BY O R DIIISCLOSED TO AN Y THIIIRD PARTY WIIITHOUT PRIIIOR WRIIITTEN CON SENT OF COMPAL ELECTRONIIICS,,, IIINC...

3

2019/ 08/30 2020/08/30

Compal Secret Data

DeciiipheredDate

2

Tiiitttllle

Siiize DocumentttNumber

Compal Electronics, Inc.

SMBUS Diagram

FH5VQ M/B LA-J812P

Rev

1

61 offf 112Dattte::: Friiiday,,, March 20,,, 2020 Sheettt

1A

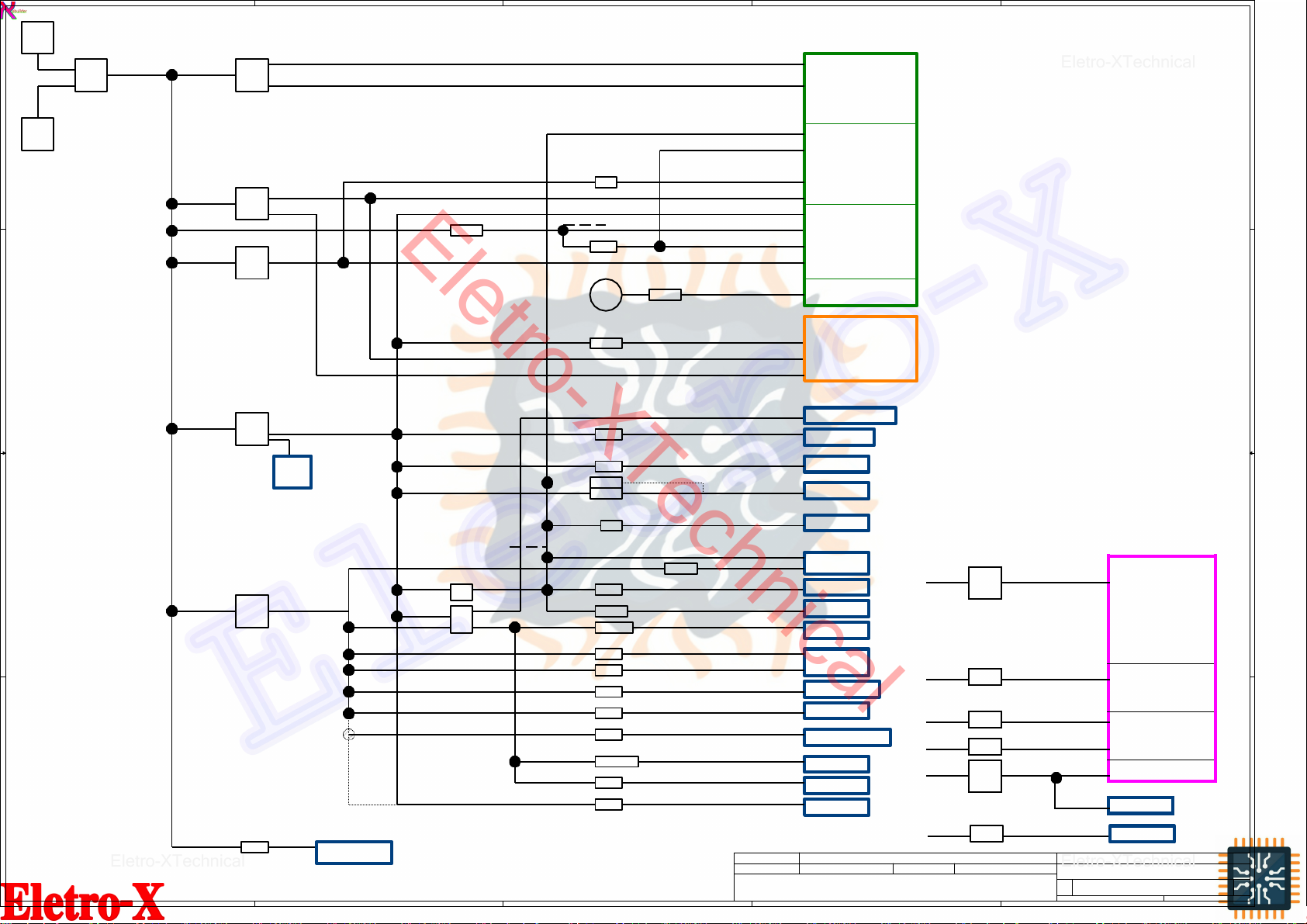

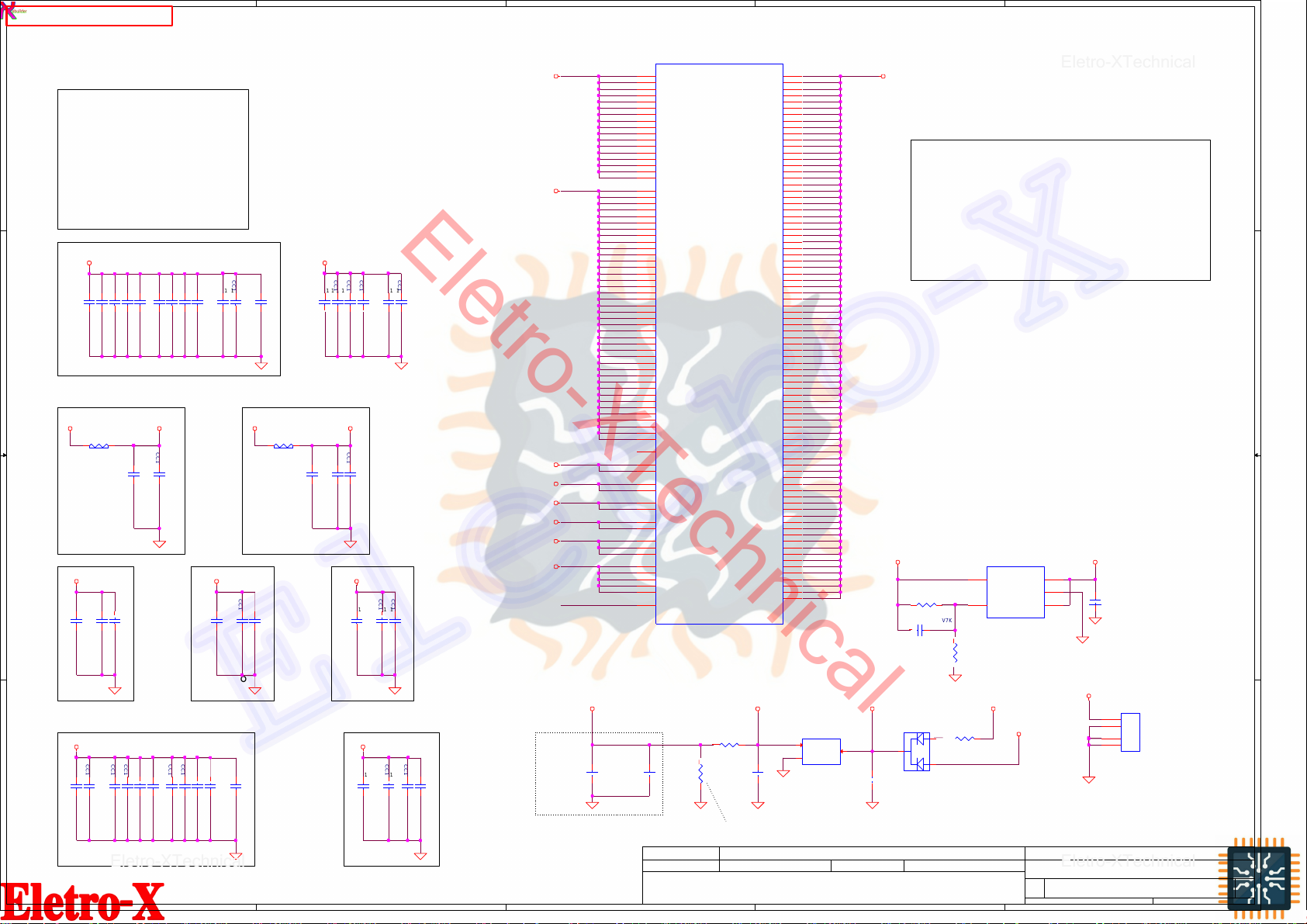

5

PJP101

AC-IN

PUB1

24810m A

+19VB

5243mA

638mA

237mA

+19V_V IN

+17.4V _BATT

D D

PJP201

DC-IN

PUZ1

PUM1

PUF1

+APU_C ORE

+APU_C ORE_SO C

+1.2V 9 500mA

+0.6VS 1200mA

5000mA

+0.9VA LW

4

4000mA

PU1802

+1.8VA LW

2660mA

2200mA

2026mA

U4

To VGA 1013mA

UG27

JRTC1

3

+0.9VS

+1.8VS

+RTCVC C

70000m A +A PU_COR E

13000m A +AP U_CORE _SOC

250mA

2000mA

4000mA

6000mA

250mA

500mA

200mA

1000mA

+RTC_A PU_R 0.045mA

+3VS

+1.8VS

+0.9VS

+1.2V

+3VALW

+1.8VA LW

+1.8VS

+0.9VA LW

+RTC_A PU_R

APU Power Rail

VDDCR_VDD @0.65-TBD

VDDCR_SOC @0.72-TBD

VDD_33 @0.25A

VDD_18 @2.0A

VDDP @4.0A

VDDIO_MEM_S3 @6.0A

VDD_33_S5 @0.25A

VDD_18_S5 @0.5A

VDDIO_AUDIO @0.2A

VDDP_S5 @1.0A

VDDBT_RTC_G @0.045mA

2

Group C, S0 d omain

Group B, S0 d omain

Group B, S3 domain

Group A, S5 domain

1

C C

2311mA

PU301

+3VLP

13347m A +3V ALW

528mA

KB9022

+2.5V

PU2501

UL1

U13

RM101

UM3 WLAN

UX1

10mA To VG A

B B

14700m A +5VALW3869mA

PU502

8330mA

4200mA

+3VS

U2

+3VS_S SD1

U3

+5VS

RX18

RX16

U2616

U1302

US14

US11

US12

JIO2

RF4/RF7

A A

LX1

+INVPW R_B+

Panel BackLight

4

2000mA

5

LA1

UK6

3

528mA

4160mA

1500mA

2790mA

300mA

30mA

1500mA

1500mA

+1.2V_ HDMI

200mA

200mA

100mA

200mA

250mA

+5VALW _MUX

3000mA

+USB3_ VCCC

2000mA

+USB3_ VCCA

2000mA +USB3_ VCCB

2500mA

1000mA

1500mA

100mA

Securiiity Clllassiiifiiicatiiion

Issued Date

THIS S HEET OF ENGIII NEERING DRAWIIING IIIS T HE P RO PRI ETARY PROP ERT Y OF CO MPAL ELECTRO NICS,,, IIINC. AND CONTAIIINS CONF IIIDENTIIIAL

AND TR ADE SE CRE T IIINFORMATIIION. T HIS SH EET MA Y NOT B E TR ANS FE RED FRO M T HE CUS TO DY O F THE CO MP ETE NT DIVIIISIIION O F R&D

DE PAR TME NT E XCE PT AS A UTH ORI ZE D B Y C OMP AL ELECTR ONICS,,, IIINC. NEIIITHER THI S SHE ET NOR TH E IIINFORMATIIION IIIT CONTAIIINS MA Y

BE US ED BY OR D IS CLO SED TO A NY T HIRD PAR TY WIIITHOUT PRI OR W RI TTE N CON SE NT OF CO MP AL EL ECTRONICS, ,, IIINC.

+2.5V

+1.2V

+0.6VS

+3VS_S SD1

+3V_LA N

+TP_VC C

+3VS_W LAN

+LCDVD D

+3VS_C AM

+TS_PW R

+5VS_B L

+VCC_F AN1

+VCC_F AN2

+5VS_P VDD

+FP_VC C

DDR4 SO-DIMM1/SO-DIMM2

+2.5V

+1.2V

+0.6VS

M.2 PCIE / SATA SSD

LAN RTL8118ASA

Touch Pad

Panel Logic

HDMI Retimer

Camera

+19VB

110000 mA +NVVDD 1

PUV1

Touch Screen

KB Light

Type C

RTS5441E

USB3.0(Charger)

USB3.0US13

IO/B (Sub Board)

FAN1/FAN2

Audio

+3VALW

+1.8VA LW

+1.8VA LW

+19VB

PU1002

UG27

UV45

PUW1

1900mA +1.0 VSDGPU

Finger Print

+3VS

U2

2019/ 08/30 2020/08/30 Tiiitttllle

Compal SecretData

Deciiiphered Date

2

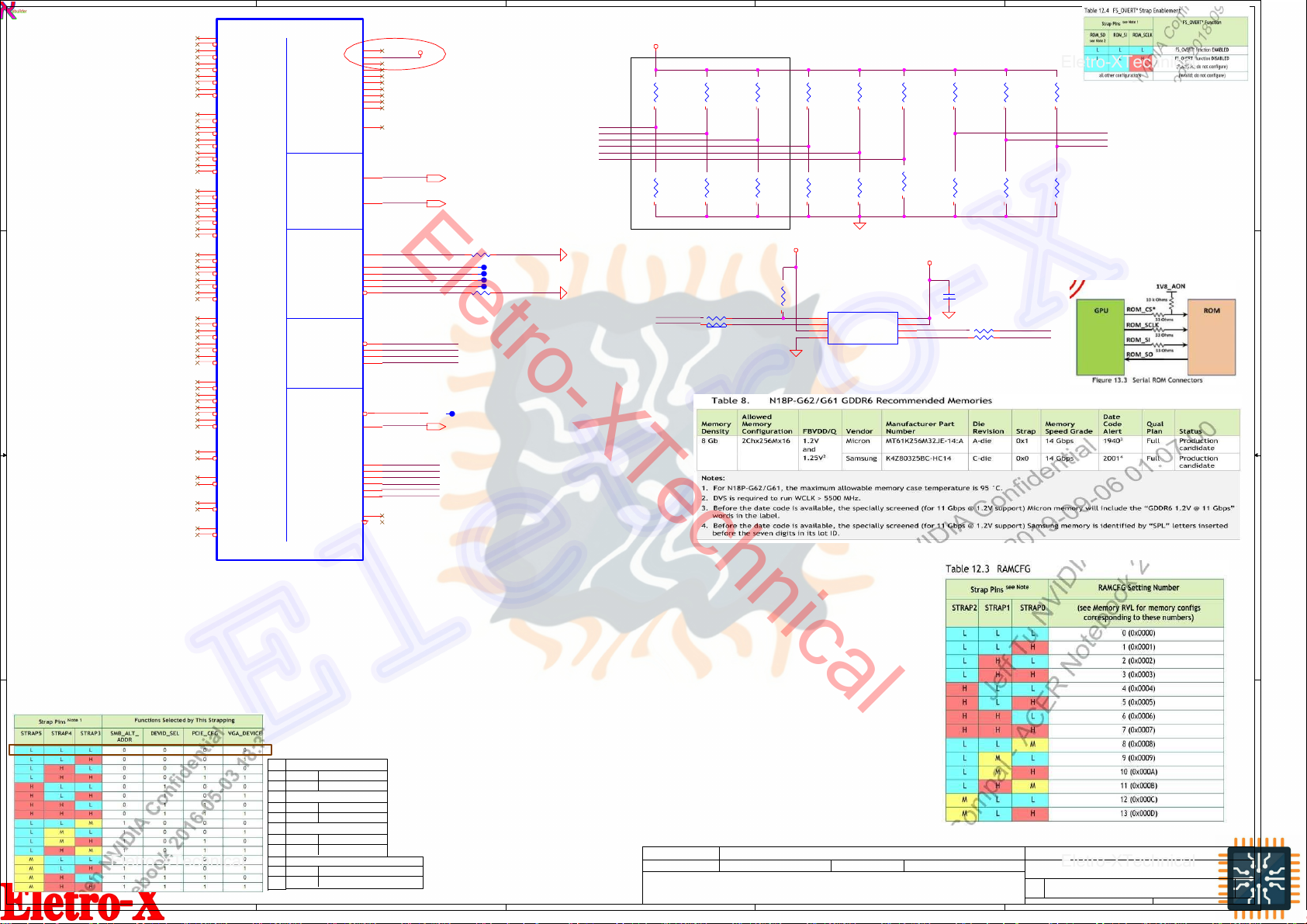

GPU Power Rail (N18P-G61/G62)

NVVDD @110A

PEX_DVDD @1.9A

+1.8VS DGPU_A ON

+1.8VS DGPU_M AIN

15000m A

+1.2VS DGPU

5160mA

+1.2VS DGPU

+3VSDG PU

PEX_HVDD @2A

FBVDDQ @15A

VRAM x4pcs

OVRM

Compal Electronics, Inc.

Siiize DocumentttNumberrr

Custttom

Dattte::: Friiirr day,,, Marcrr h 20,,, 2020 Sheettt 4 offf

POWER MAP

FH5VQ M/B LA-J812P

1

Rev

1A

112

VoltageRails

PowerPlane Description S0 S3 S5

+19V_VIN Adapter power supply (19V) ON ON ON

+19VB AC or battery power rail for powercircuit. ON ON ON

+APU_CORE Core voltage forAPU ON OFF OFF

+APU_CORE_SOC Core voltage forAPU ON OFF OFF

+1.8VALW 1.8V always on powerrail ON ON OFF

+1.8VS 1.8V switched powerrail ON OFF OFF

+2.5V 2.5V power rail for APU andDDR ON ON OFF

1 1

+1.2V 1.2V power rail for APU andDDR ON ON OFF

+0.6VS 0.6V switched power rail for DDRterminator ON OFF OFF

+3VALW 3.3V always on powerrail ON ON OFF

+3VS 3.3V switched powerrail ON OFF OFF

+5VALW 5V always on powerrail ON ON ON

+5VS 5V switched powerrail ON OFF OFF

+0.9VALW 0.9V always on powerrail ON ON ON

+0.9VS 0.9V switched powerrail ON OFF OFF

+RTC_APU RTC power ON ON ON

+3V_LAN 3.3V LAN ICpower ON ON OFF

+TP_VCC 3.3V Touch Pad power ON ON OFF

+FP_VCC 3.3V Finger Print power ON ON OFF

+3VSDGPU VGApower ON OFF OFF

2 2

+1.8VSDGPU_AON VGA power ON OFF OFF

+1.8VSDGPU_MAIN VGApower ON OFF OFF

+1.2VSDGPU VGApower ON OFF OFF

+1.0VSDGPU VGApower ON OFF OFF

+NVVDD1 VGApower ON OFF OFF

APU SMBus/I2C Address Table

Master Device

3 3

I2C Port0

(+1.8VS)

I2C Port1

(+1.8VS)

I2C Port2

(+3VS)

SBMus Port0

(+3VS)

I2C Port 3

(+3VALW)

4 4

SMBus Port1

(+3VALW)

A

JDIMM1

JDIMM2

PTP

(Synaptics)

PTP

(ELAN)

Address[7:1]

01010000b

50h

01010001b

51h

00101100b

2Ch

00011111b

15h

Address[7:0]

Write

10100000b

A0h

10100010b

A2h

01011000b

58h

00111110b

3Eh

10100001b

A1h

10100011b

A3h

01011001b

59h

00111111b

3Fh

Read

B

BOARD ID Table

Board ID PCB Revision

0 EVT

1 DVT

2 PVT

3 MP

BOM Structure

BOM Structure

@

EMC@/@EMC@

45@

CONN@

JP@

RS@

TP@

LDO@

R5/R7APU@

TMS@

TMSIEC@

EVT@/DVT@

PVT@/MP@

N18PG61@/

N18PG62@

N18P@

DIS@

GC6@

ON_X76@

uPI_X76@

Table

BTO Ite m

Unpop

EMI/ESD Pop/Unpop

HDMI Royalty

Mechanical Connector

Jump

R-Short

Test Point

RTL8111H LDO Mode only

APU PN Refer p.6

Thermal Sensor

Thermal Sensor for IEC safety

Test BOM for EVT/DVT/PVT/MP

N18P GPU

N18P Component

VGA Circuits

nVidia DGPU GC6 2.0 (Reserved)

OVRM-ON (For N18P Only)

OVRM-uPI (For N18P Only)

X76_M4G@

X76_S4G@

EC SMBus Address Table

SMBus Port1

(+3VALW)

SMBus Port2

(+3VS)

SmartBattery

Charger IC

(BQ24735)

APUTemp.

(TSI)

GPU Temp.

Thermal Sensor

G781-1

Thermal Sensor

IEC 62368-1

C

VRAM Config_Micro n

VRAM Config_Samsu ng

0000 1011b

0Bh

0000 1001b

09h

0100 1100b

4Ch

1001 1110b

9Eh

0001 0110b

16h

0001 0010b

12h

1001 1000b

98h

1001 1010b

9Ah

1001 0000b

90h

D

Board ID / SKU ID Table for AD channel

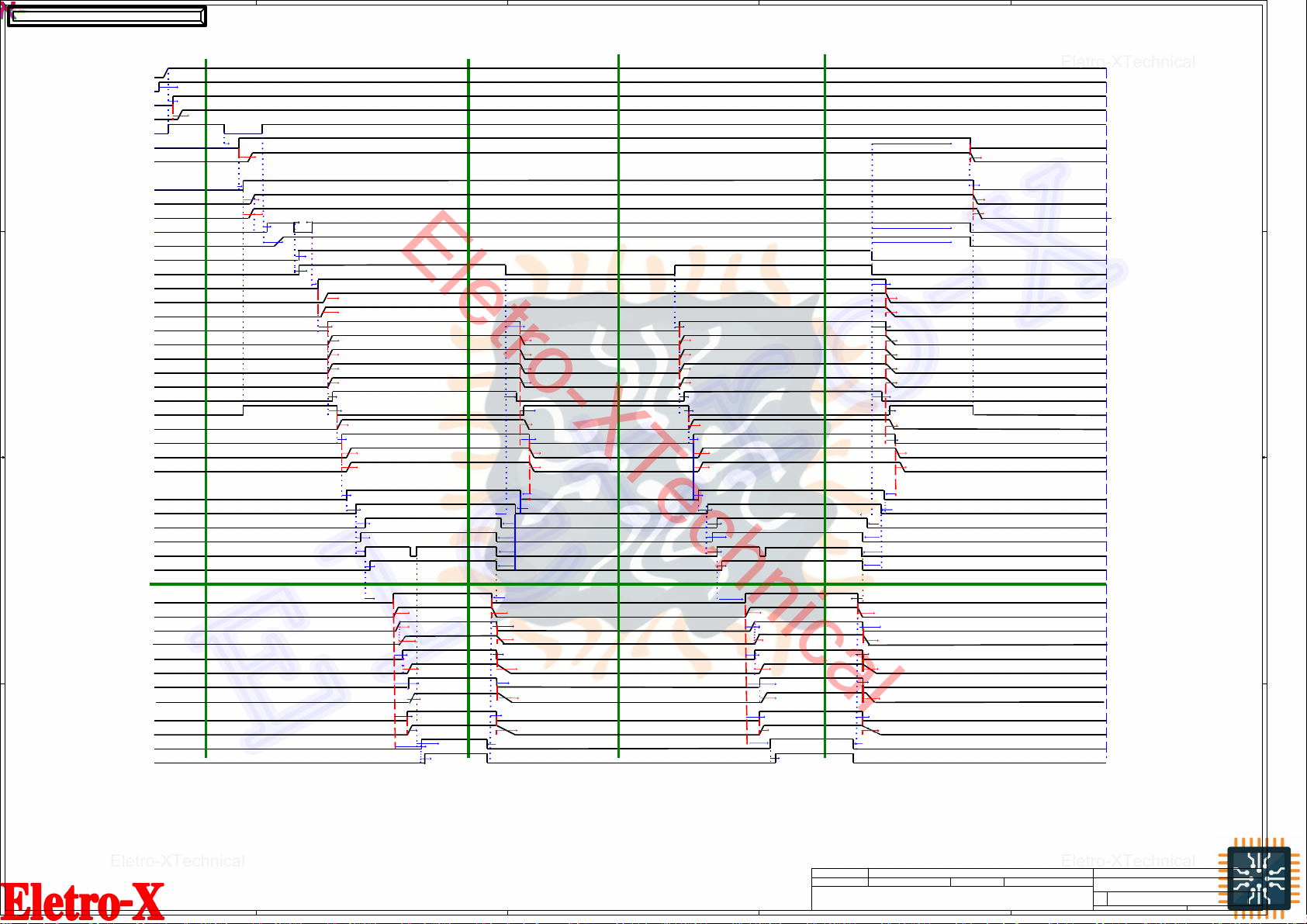

POWER SEQUENCE

+RTCBATT

EC_ON

+5VALW

3V_EN

+3VALW

0.9_1.8VALW_PWREN

+1.8VALW/+0.9VALW

SYSON

+1.2V/+2.5V

SUSP#

+5VS/+3VS/+1.8VS/+0.6VS

0.9VS_PWR_EN#

+0.9VS

VR_ON

+APU_CORE

+APU_CORE_SOC

0001 0111b

17h

0001 0011b

13h

1001 1001b

99h

1001 1011b

9Bh

1001 0001b

91h

G-A

G-B

G-C

G-D

E

SecurityClassification

Issued Date

THIIIS S HE ET OF ENGIIINEERIIING DRAWIIING IIIS THE PRO PRIIIETARY P ROPERTY OF COMP AL ELE CTRONIIICS,,, IIINC... AND CONTAIIINS CON FID ENTI AL

AN D T RA DE SE CRE T IIINFORMATION... THIIIS SHE ET MA Y NO T BE TR AN SF ERE D F ROM T HE CU ST ODY O F TH E C OM PE TEN T DIIIVIIISIIION OF R& D

DE PA RTM EN T E XC EP T AS AUTHOR IIIZED BY C OMP AL ELECTRONIIICS,,, IIINC... NEIIITHER THIIIS SH EE T NO R TH E IIINF ORMATION IIIT CONTAIIINS MA Y

A

B

BE U SE D BY OR DIIISCLOSE D TO ANY THIIIRD PART Y W IIITHOUT PRIIIOR W RIIITTEN C ONS EN T OF COM PA L ELECTRONIIICS,,, IIINC...

C

2019/ 08/30 2020/08/30

Compal Secret Data

DecipheredDate

Tiiitttllle

Siiize DocumentttNumber

Custttom

D

Date:::tt Friiiday,,, March 20,,, 2020 Sheettt

Compal Electronics, Inc.

NOTES LIST

FH5VQ M/B LA-J812P

E

3 offf 112

Rev

1A

AMD Picasso Platform Power Se quenc e

5 4 3 2 1

G3 --> S0AC-IN

+3VLP

ACIN

EC_ON

D D

+5VALW

ON/OFFBTN#

3V_EN

+3VALW

0.9_1.8VALW_PWREN

+1.8VALW

+0.9VALW

PBTN_OUT#

EC_RSMRST#

SLP_S5#

SLP_S3#

SYSON

+1.2V

+2.5V

SUSP#

C C

+5VS

+3VS

+1.8VS

+0.6VS

KBRST#

0.9VS_PWR_EN#

+0.9VS

VR_ON

+APU_CORE

+APU_CORE_SOC

VGATE

SYS_PWRGD_EC

APU_PWROK

LPC_RST#

APU_PCIE_RST#

B B

APU_RST#

VGA Sequence

PE_GPIO1(DGPU_PWR_EN)

+1.8VSDGPU_AON

1.8VSDGPU_MAIN_EN

+1.8VSDGPU_MAIN

NVVDD1_EN

+NVVDD1

1VSDGPU_EN

+1.0VSDGPU

1.35VSDGPU_EN

+1.2VSDGPU

PE_GPIO0(DGPU_HOLD_RST#)

PLTRST_VGA#_1V8

1.74ms

202.2us

2.421ms, Tr = 421.5us

40.45us

88.64ms

846.2us, Tr = 623.2us

245.1us, Tr = 261.4us

626.9us, Tr = 405.1us

197.9ms

98.68ms

384.7us

125ms

19.86ms

177.2us

177.2us

675.5us, Tr = 145us

1.708ms, Tr = 1.208ms

19.72ms

680.4us, Tr = 525.5us

758us, Tr = 586.1us

2.808ms, Tr = 1.874ms

14.71us, Tr = 13.87us

19.79ms

42.43ms

311.3us, Tr = 96.18us

19.14ms

12.62ms

2.380ms, Tr = 292.6us

2.402ms, Tr = 307.8us

2.606ms

41.19ms

14.94ms

10.31ms

600ms

8.959ms

475.5ms

10ms

213.6us, Tr = 125us

147.4u

1.277ms, Tr = 539.5us

749us

948.5us, Tr = 336.5us

1.648ms

1.429ms, Tr = 601.1us

3.137ms

376.2us, Tr = 81.86us 368.4us, Tr = 86.51us

9.996ms

128ms

1us

S0 --> S3 S3 --> S0

1.308ms

58.42ms

206us. Tf = 9.696ms

453us, Tf = 9.459ms

402.2us, Tf = 6.993ms

58.37ms

13.85us

145.3us, Tf = 2.726ms 302.1us, Tr =99.42us

29.72ms

53.02us, Tf = 337.6us

56.65us, Tf = 332us

29.15ms

32.74ms

29.34ms

32.88ms

35.71ms

35.71ms

375.09ms

4.142mss, Tf = 8.656ms

95.27ps

1.201ms, Tf = 39.13ms

608.4us

1.259ms, Tf = 1.047ms

408ns

729.1us, Tf = 1.187ms

3.002ms

469.8us, Tf = 6.681ms

1.906ms

21.82ms

651.9us, Tr = 509.1us

694.5us, Tr = 495.2us

2.495ms, Tr = 1.513ms

13.73us, Tr = 13.02us523.1us, Tf = 7.094ms

21.37ms

48.25ms

20ms

2.39ms, Tr = 294.1us

2.404ms, Tr = 303.4us

2.611ms

39.29ms

17.98ms

13.49ms

12.48ms

8.959ms

202.5ms

130.5us, Tr = 117.1us

141.5us

1.251ms, Tr = 511.9us

748.4us

980us, Tr = 353.8us

1.656ms

1.029ms, Tr = 498.1us

3.134ms

7.164ms

177.7ns

S0 --> S5

1.309ms

2.45s

606us

200.3ns

3.003ms

1.732ms

59.15ms

435.6s, Tf = 36.63ms

613.2us, Tf = 14.58ms

59.13ms

216.2us, Tf = 9.881ms

456us, Tf = 9.639ms

361us, Tf = 7.562ms

85.02us, Tf = 1.032ms

59.08ms

14.61us

142.9us, Tf = 2.653ms

28.32ms

29.48ms

32.59ms

38.74ms

3.532ms

28.2ms

28.19ms

4.139ms, Tf = 9.005ms

85.57ns

1.237ms, Tf = 37.96ms

1.208ms, Tf = 1.101ms

765.7us, Tf = 1.169ms

299.9us, Tf = 7.485ms

53.38us, Tf = 328.2us

61.13us, Tf = 329.2us

8.289s

8.518s

8.518s

1.836ms, Tf = 4.416ms

9ms

1.635ms, Tf = 2.995ms

1.617ms, Tf = 3.644ms

+3VLP

ACIN

EC_ON

+5VALW

ON/OFFBTN#

3V_EN

+3VALW

0.9_1.8VALW_PWREN

+1.8VALW

+0.9VALW

PBTN_OUT#

EC_RSMRST#

SLP_S5#

SLP_S3#

SYSON

+1.2V

+2.5V

SUSP#

+5VS

+3VS

+1.8VS

+0.6VS

KBRST#

0.9VS_PWR_EN#

+0.9VS

VR_ON

+APU_CORE

+APU_CORE_SOC

VGATE

SYS_PWRGD_EC

APU_PWROK

LPC_RST#

APU_PCIE_RST#

APU_RST#

VGA Sequence

PE_GPIO1(DGPU_PWR_EN)

+1.8VSDGPU_AON

1.8VSDGPU_MAIN_EN

+1.8VSDGPU_MAIN

NVVDD1_EN

+NVVDD1

1VSDGPU_EN

+1.0VSDGPU

1.35VSDGPU_EN

+1.2VSDGPU

PE_GPIO0(DGPU_HOLD_RST#)

PLTRST_VGA#_1V8

A A

SecurittyClassifficatttion

IIIssued Dattte

THIIIS SHEE T O F ENGIIINEERIIING DRAW IIIN G IIIS T HE PRO PRIIIETA RY PR O PE RT Y OF C OMP AL ELECTRONIIICS,,, IIINC... AND CON TAII INS CONFIIIDENTIIIASL

AN D T RA DE SEC RE T IIINFORMATIIION... THIIISS HE ET MAY NOT BE T RA NSF E RE D FRO M THE CU ST ODY OF T HE COM PE TE NT DIIIVIIISIIIONOF R &D

DE PA RT ME NT EX CEP T AS A UTHORI II ZED B Y CO MP AL E LECTRONII ICS,,, IIINC... NEIIITHER THIIIS S HEE T NOR TH E I IINFORMATIII ON IIIT CONTAIII NS

5 4 3 2 1

MAY BE USE D BY OR DIIISCLOSED TO ANY THIIIRD PARTY WIIITHOUT PRIIIOR WRIIITTEN C ONSENT OF COMPAL ELECTRONIIICS,,,IIINC...

2019/// 08///30

Compalll Secre t Da ta

Decip hered Dattte

2020///08///30

Compal Electronics, Inc.

Tiiitttllle

iiize DocumentttNumberrr

Custttom

Dattte::: Frrriiiday,,, Marrrch 20,,, 2020 Sheettt 5 offf112

POW ERSEQUENCE

FH5VQ M/B LA-J812P

Rev

1A

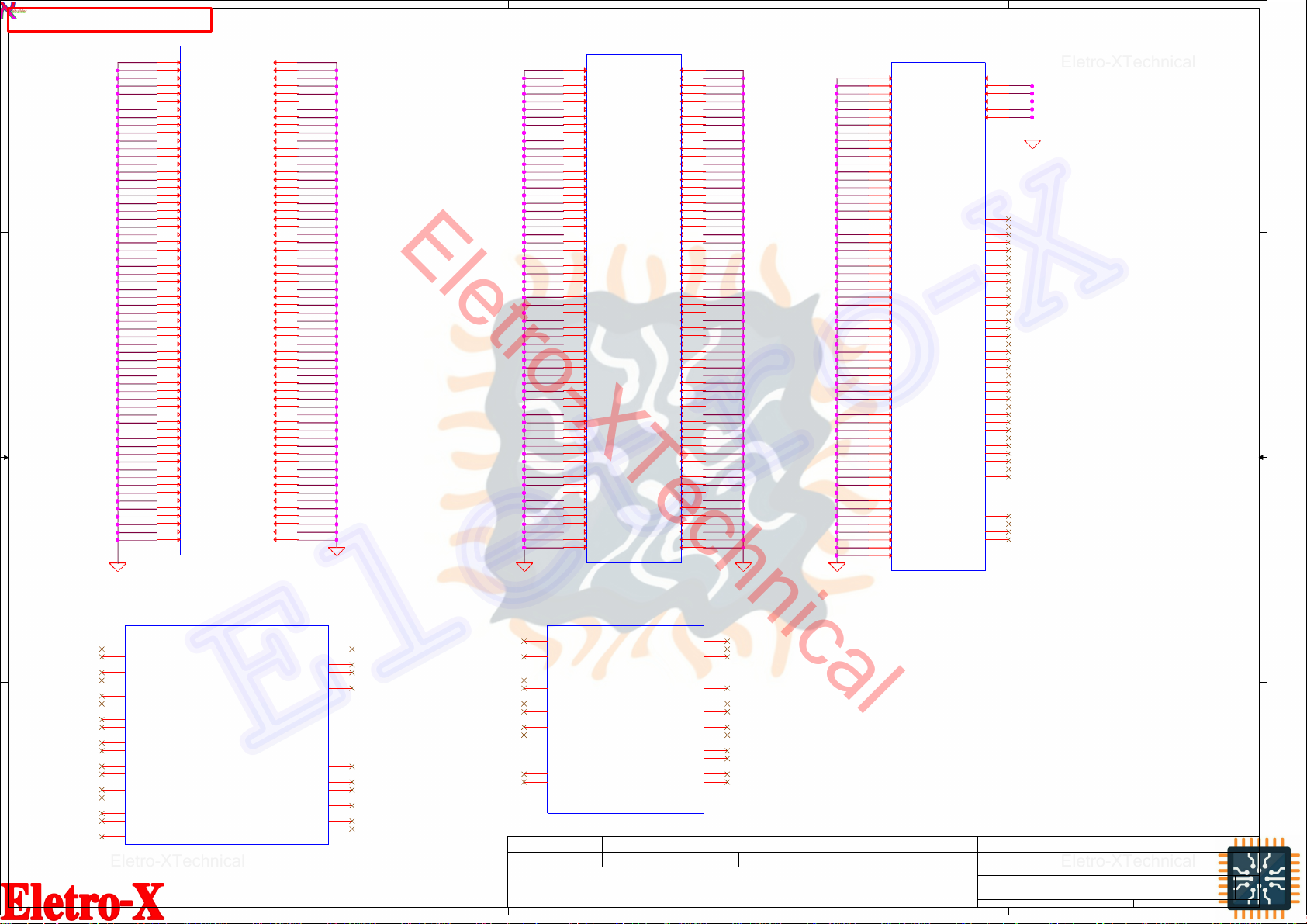

5 4 3 2 1

Main Func = CPU

UC1B

PEG

D D

27 PEG_ARX_C_GTX_P0

27 PEG_ARX_C_GTX_N0

27 PEG_ARX_C_GTX_P1

27 PEG_ARX_C_GTX_N1

27 PEG_ARX_C_GTX_P2

27 PEG_ARX_C_GTX_N2

27 PEG_ARX_C_GTX_P3

27 PEG_ARX_C_GTX_N3

27 PEG_ARX_C_GTX_P4

27 PEG_ARX_C_GTX_N4

27 PEG_ARX_C_GTX_P5

27 PEG_ARX_C_GTX_N5

27 PEG_ARX_C_GTX_P6

27 PEG_ARX_C_GTX_N6

27 PEG_ARX_C_GTX_P7

27 PEG_ARX_C_GTX_N7

C C

B B

PEG_ARX_C_GTX_P0 CC401 DIS@ 1

PEG_ARX_C_GTX_N0 CC402 DIS@1

PEG_ARX_C_GTX_P1

PEG_ARX_C_GTX_N1 CC404 DIS@1

PEG_ARX_C_GTX_P2

PEG_ARX_C_GTX_N2 CC406 DIS@1

PEG_ARX_C_GTX_P3

PEG_ARX_C_GTX_N3 CC408 DIS@1

PEG_ARX_C_GTX_P4

PEG_ARX_C_GTX_N4 CC410 TYPE1@1

PEG_ARX_C_GTX_P5

PEG_ARX_C_GTX_N5 CC412 TYPE1@1

PEG_ARX_C_GTX_P6

PEG_ARX_C_GTX_N6 CC414 TYPE1@1

PEG_ARX_C_GTX_P7

PEG_ARX_C_GTX_N7 CC416 TYPE1@1

LAN

WLAN

CC403 DIS@ 1

CC405 DIS@ 1

CC407 DIS@ 1

CC409 TYPE1@1

CC411 TYPE1@1

CC413 TYPE1@1

CC415 TYPE1@1

68 PCIE_ARX_DTX_P0

68 PCIE_ARX_DTX_N0

68 PCIE_ARX_DTX_P1

68 PCIE_ARX_DTX_N1

68 PCIE_ARX_DTX_P2

68 PCIE_ARX_DTX_N2

68 PCIE_ARX_DTX_P3

68 PCIE_ARX_DTX_N3

51 PCIE_ARX_DTX_P4

51 PCIE_ARX_DTX_N4

52 PCIE_ARX_DTX_P5

52 PCIE_ARX_DTX_N5

68 SATA_ARX_DTX_P0

68 SATA_ARX_DTX_N0

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

PCIE_ARX_DTX_P0

PCIE_ARX_DTX_N0

PCIE_ARX_DTX_P1

PCIE_ARX_DTX_N1

PCIE_ARX_DTX_P2

PCIE_ARX_DTX_N2

PCIE_ARX_DTX_P3

PCIE_ARX_DTX_N3

PCIE_ARX_DTX_P4

PCIE_ARX_DTX_N4

PCIE_ARX_DTX_P5

PCIE_ARX_DTX_N5

SATA_ARX_DTX_P0

SATA_ARX_DTX_N0

PEG_ARX_GTX_P0

PEG_ARX_GTX_N0

PEG_ARX_GTX_P1

PEG_ARX_GTX_N1

PEG_ARX_GTX_P2

PEG_ARX_GTX_N2

PEG_ARX_GTX_P3

PEG_ARX_GTX_N3

PEG_ARX_GTX_P4

PEG_ARX_GTX_N4

PEG_ARX_GTX_P5

PEG_ARX_GTX_N5

PEG_ARX_GTX_P6

PEG_ARX_GTX_N6

PEG_ARX_GTX_P7

PEG_ARX_GTX_N7

P8

P_GFX_ RXP0

P9

P_GFX_ RXN0

N6

P_GFX_ RXP1

N7

P_GFX_ RXN1

M8

P_GFX_ RXP2

M9

P_GFX_ RXN2

L6

P_GFX_ RXP3

L7

P_GFX_ RXN3

K11

P_GFX_ RXP4

J11

P_GFX_ RXN4

H6

P_GFX_ RXP5

H7

P_GFX_ RXN5

G6

P_GFX_ RXP6

F7

P_GFX_ RXN6

G8

P_GFX_ RXP7

F8

P_GFX_ RXN7

N10

P_GPP_ RXP0

N9

P_GPP_ RXN0

L10

P_GPP_ RXP1

L9

P_GPP_ RXN1

L12

P_GPP_ RXP2

M11

P_GPP_ RXN2

P12

P_GPP_ RXP3

P11

P_GPP_ RXN3

V6

P_GPP_ RXP4

V7

P_GPP_ RXN4

T8

P_GPP_ RXP5

T9

P_GPP_ RXN5

R6

P_GPP_ RXP6/SA TA_RXP0

R7

P_GPP_ RXN6/SA TA_RXN0

R9

P_GPP_ RXP7/SA TA_RXP1

R10

P_GPP_ RXN7/SA TA_RXN1

@

PCIE

FP5REV 0.90

PART2 OF13

FP5_BGA_1140P

P_GFX_ TXP0

P_GFX_ TXN0

P_GFX_ TXP1

P_GFX_ TXN1

P_GFX_ TXP2

P_GFX_ TXN2

P_GFX_ TXP3

P_GFX_ TXN3

P_GFX_ TXP4

P_GFX_ TXN4

P_GFX_ TXP5

P_GFX_ TXN5

P_GFX_ TXP6

P_GFX_ TXN6

P_GFX_ TXP7

P_GFX_ TXN7

P_GPP_ TXP0

P_GPP_ TXN0

P_GPP_ TXP1

P_GPP_ TXN1

P_GPP_ TXP2

P_GPP_ TXN2

P_GPP_ TXP3

P_GPP_ TXN3

P_GPP_ TXP4

P_GPP_ TXN4

P_GPP_ TXP5

P_GPP_ TXN5

P_GPP_ TXP6/S ATA_TXP0

P_GPP_ TXN6/SA TA_TXN0

P_GPP_ TXP7/S ATA_TXP1

P_GPP_ TXN7/SA TA_TXN1

PEG_ATX_GRX_P0

N1

PEG_ATX_GRX_N0

N3

PEG_ATX_GRX_P1

M2

PEG_ATX_GRX_N1

M4

PEG_ATX_GRX_P2

L2

PEG_ATX_GRX_N2

L4

PEG_ATX_GRX_P3

L1

PEG_ATX_GRX_N3

L3

PEG_ATX_GRX_P4

K2

PEG_ATX_GRX_N4

K4

PEG_ATX_GRX_P5

J2

PEG_ATX_GRX_N5

J4

PEG_ATX_GRX_P6

H1

PEG_ATX_GRX_N6

H3

PEG_ATX_GRX_P7

H2

PEG_ATX_GRX_N7

H4

PCIE_ATX_DRX_P0

N2

PCIE_ATX_DRX_N0

P3

PCIE_ATX_DRX_P1

P4

PCIE_ATX_DRX_N1

P2

PCIE_ATX_DRX_P2

R3

PCIE_ATX_DRX_N2

R1

PCIE_ATX_DRX_P3

T4

PCIE_ATX_DRX_N3

T2

PCIE_ATX_DRX_P4

W2

PCIE_ATX_DRX_N4

W4

PCIE_ATX_DRX_P5

W3

PCIE_ATX_DRX_N5

V2

SATA_ATX_DRX_P0

V1

SATA_ATX_DRX_N0

V3

U2

U4

CC417 DIS@ 1

CC418 DIS@ 1

CC419 DIS@ 1

CC420 DIS@ 1

CC422 DIS@ 1

CC421 DIS@ 1

CC423 DIS@ 1

CC424 DIS@ 1

CC425 TYPE1@

CC426 TYPE1@

CC427 TYPE1@

CC428 TYPE1@

CC429 TYPE1@

CC430 TYPE1@

CC431 TYPE1@

CC432 TYPE1@

CC1203, CC1204 place clost to JSSD1 for SATA co-

layout

MPCIE@ CC1204

MPCIE@ CC1203

MPCIE@ CC1206

MPCIE@ CC1205

MPCIET1@ CC1212

MPCIET1@ CC1211

MPCIET1@ CC1214

MPCIET1@ CC1213

CC1 1

CC2 1

CC3 1

CC4 1

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

2 0.22U_0201_6.3V6K

1 2

0.22U_0201_6.3V6K

1 2

0.22U_0201_6.3V6K

1 2

0.22U_0201_6.3V6K

1 2

0.22U_0201_6.3V6K

1 2

0.22U_0201_6.3V6K

1 2

0.22U_0201_6.3V6K

1 2

0.22U_0201_6.3V6K

1 2

0.22U_0201_6.3V6K

1 2

0.22U_0402_16V7K

1 2

0.22U_0402_16V7K

1 2

0.22U_0402_16V7K

1 2

0.22U_0402_16V7K

1 2

0.22U_0402_16V7K

1 2

0.22U_0402_16V7K

1 2

0.22U_0402_16V7K

1 2

0.22U_0402_16V7K

2 .1U_0402_16V7K

2 .1U_0402_16V7K

.1U_0402_16V7K

2

2 .1U_0402_16V7K

PEG_ATX_C_GRX_P0

PEG_ATX_C_GRX_N0

PEG_ATX_C_GRX_P1

PEG_ATX_C_GRX_N1

PEG_ATX_C_GRX_P2

PEG_ATX_C_GRX_N2

PEG_ATX_C_GRX_P3

PEG_ATX_C_GRX_N3

PEG_ATX_C_GRX_P4

PEG_ATX_C_GRX_N4

PEG_ATX_C_GRX_P5

PEG_ATX_C_GRX_N5

PEG_ATX_C_GRX_P6

PEG_ATX_C_GRX_N6

PEG_ATX_C_GRX_P7

PEG_ATX_C_GRX_N7

PCIE_ATX_C_DRX_P0 68

PCIE_ATX_C_DRX_N0 68

PCIE_ATX_C_DRX_P1 68

PCIE_ATX_C_DRX_N1 68

PCIE_ATX_C_DRX_P2 68

PCIE_ATX_C_DRX_N2 68

PCIE_ATX_C_DRX_P3 68

PCIE_ATX_C_DRX_N3 68

PCIE_ATX_C_DRX_P4 51

PCIE_ATX_C_DRX_N4 51

PCIE_ATX_C_DRX_P5 52

PCIE_ATX_C_DRX_N5 52

SATA_ATX_DRX_P0 68

SATA_ATX_DRX_N0 68

PEG_ATX_C_GRX_P0 27

PEG_ATX_C_GRX_N0 27

PEG_ATX_C_GRX_P1 27

PEG_ATX_C_GRX_N1 27

PEG_ATX_C_GRX_P2 27

PEG_ATX_C_GRX_N2 27

PEG_ATX_C_GRX_P3 27

PEG_ATX_C_GRX_N3 27

PEG_ATX_C_GRX_P4 27

PEG_ATX_C_GRX_N4 27

PEG_ATX_C_GRX_P5 27

PEG_ATX_C_GRX_N5 27

PEG_ATX_C_GRX_P6 27

PEG_ATX_C_GRX_N6 27

PEG_ATX_C_GRX_P7 27

PEG_ATX_C_GRX_N7 27

LAN

WLAN

HDDHDD

PEG

M.2SSD1M.2SSD1

APU PNTable

APUPlatform Customer PN Customer PN Customer PN Customer PN CompalPN Compal PN

UC1 R5APU@

Picasso

S IC RYZEN5 YM3500C4T4MFG 2.1G APU ABO!

SA0000CCR60

PCB Number

A A

ZZZ EVT@

PCB 2Y2 LA-J812P REV0 MB 1

DAA000N4000

ZZZ DVT@

PCB FH5VQ LA-J812PLS-J812P

DAZ2Y200100

MB: DAA000N4010 Rev1.0

IO/B: DAA000N5010 Rev1.0

5 4 3 2 1

ZZZ PVT@

PCB FH5VQ LA-J812P LS-J812P

DAZ2Y200101

MB: DAA000N401A Rev1A

IO/B: DAA000N5010 Rev1.0

ZZZ MP@

PCB FH5VQ LA-J812P LS-J812P

DAZ2Y200101

MB: DAA000N401A Rev1A

IO/B: DAA000N5010 Rev1.0

SecurityClassification

IssuedDate

THIS SHEET OF ENGINEERING DRAWING IS T HE PROPRIETARY PROPERTY OF COM PAL ELECTRONICS, INC. AND CONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPET ENT DIVISION OF R&D

DEPART MENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS MAY

BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN C ONS ENT OF C OMPAL ELECTRONICS, INC.

UC1 R7APU@

S IC RYZEN7 YM3700C4T4MFG 2.3G APUABO!

SA0000C7680

2019/ 08/30 2020/08/30

Compal Secret Data

DecipheredDate

Tiiitllle

Siiize Document Number

Custom

Date: of

Compal Electronics, Inc.

FP5_(1/7)_PEG/PCIE/SATA

FH5VQ M/B LA-J812P

Fridii ay, March 20, 2020 Sheet

6 112

Rev

1A

Main Func = CPU

5

4

3

2

1

UC1A

23 DDR_A_MA[13..0]

D D

23 DDR_A_MA14_WE#

23 DDR_A_MA15_CAS#

23 DDR_A_MA16_RAS#

23 DDR_A_BA0

23 DDR_A_BA1

23 DDR_A_BG0

23 DDR_A_BG1

23 DDR_A_ACT# 23

DDR_A_DM[7..0]

23 DDR_A_DQS0

23 DDR_A_DQS0#

23 DDR_A_DQS1

23 DDR_A_DQS1#

23 DDR_A_DQS2

C C

B B

23 DDR_A_DQS2#

23 DDR_A_DQS3

23 DDR_A_DQS3#

23 DDR_A_DQS4

23 DDR_A_DQS4#

23 DDR_A_DQS5

23 DDR_A_DQS5#

23 DDR_A_DQS6

23 DDR_A_DQS6#

23 DDR_A_DQS7

23 DDR_A_DQS7#

23 DDR_A_CLK0

23 DDR_A_CLK0#

23 DDR_A_CLK1

23 DDR_A_CLK1#

23 DDR_A_CS0#

23 DDR_A_CS1#

23 DDR_A_CKE0

23 DDR_A_CKE1

23 DDR_A_ODT0

23 DDR_A_ODT1

23 DDR_A_ALERT#

23 DDR_A_EVENT#

23 DDR_A_RST#

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14_WE#

DDR_A_MA15_CAS#

DDR_A_MA16_RAS#

DDR_A_BA0

DDR_A_BA1

DDR_A_BG0

DDR_A_BG1

DDR_A_ACT#

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS0#

DDR_A_DQS1

DDR_A_DQS1#

DDR_A_DQS2

DDR_A_DQS2#

DDR_A_DQS3

DDR_A_DQS3#

DDR_A_DQS4

DDR_A_DQS4#

DDR_A_DQS5

DDR_A_DQS5#

DDR_A_DQS6

DDR_A_DQS6#

DDR_A_DQS7

DDR_A_DQS7#

DDR_A_CLK0

DDR_A_CLK0#

DDR_A_CLK1

DDR_A_CLK1#

DDR_A_CS0#

DDR_A_CS1#

DDR_A_CKE0

DDR_A_CKE1

DDR_A_ODT0

DDR_A_ODT1

DDR_A_ALERT#

DDR_A_EVENT#

DDR_A_RST#

AG27

AG23

AG26

AW 25

AM26

AM27

AW 20

AG21

AG24

AF25

AE23

AD27

AE21

AC24

AC26

AD21

AC27

AD22

AC21

AF22

AA24

AC23

AJ25

MA _W E_ L _A DD 14

AF21

AF27

AA21

AA27

AA22

F21

G27

N24

N23

AL24

AN27

AT21

T27

F22

G22

H27

H26

N27

N26

R21

P21

AN24

AN25

AU23

AT23

AV20

V24

V23

AD25

AD24

AE26

AE27

AJ27

Y23

Y26

AJ22

AA25

AE24

Y24

MA _ADD0

MA _ADD1

MA _A DD 2

MA _A DD 3

MA _A DD 4

MA _A DD 5

MA _A DD 6

MA _A DD 7

MA _A DD 8

MA _A DD 9

MA_ AD D10

MA_ AD D11

MA_ AD D12

MA_ AD D13 _ BA NK 2

MA_ CA S_L _ ADD 1 5

MA_ RA S_L _ ADD 1 6

MA_ BA NK0

MA_ BA NK1

MA _B G0

MA _B G1

MA_ AC T_L

MA _D M0

MA _D M1

MA _D M2

MA _D M3

MA _D M4

MA _D M5

MA _D M6

MA _D M7

RSV D_ 36

MA _D QS _H 0

MA _D QS _L 0

MA _D QS _H 1

MA _D QS _L 1

MA _D QS _H 2

MA _D QS _L 2

MA _D QS _H 3

MA _D QS _L 3

MA _D QS _H 4

MA _D QS _L 4

MA _D QS _H 5

MA _D QS _L 5

MA _D QS _H 6

MA _D QS _L 6

MA _D QS _H 7

MA _D QS _L 7

RSV D_ 41

RSV D_ 40

MA_ CL K_H 0

MA_ CL K_L 0

MA_ CL K_H 1

MA_ CL K_L 1

MA_ CS _L0

MA_ CS _L 1

MA_CKE0

MA_CKE1

MA_ODT0

MA_ODT1

MA_ALERT_ L

MA_EVENT_L

MA_RESET _L

@

MEMORY A

FP5REV0.90

PART1OF13

FP5_BGA_1140P

MA_ DA TA0

MA_ DA TA1

MA_ DA TA2

MA_ DA TA3

MA_ DA TA4

MA_ DA TA5

MA_ DA TA6

MA_ DA TA7

MA_ DA TA8

MA_ DA TA9

MA_ DA TA1 0

MA_ DA TA1 1

MA_ DA TA1 2

MA_ DA TA1 3

MA_ DA TA1 4

MA_ DA TA1 5

MA_ DA TA1 6

MA_ DA TA1 7

MA_ DA TA1 8

MA_ DA TA1 9

MA_ DA TA2 0

MA_ DA TA2 1

MA_ DA TA2 2

MA_ DA TA2 3

MA_ DA TA2 4

MA_ DA TA2 5

MA_ DA TA2 6

MA_ DA TA2 7

MA_ DA TA2 8

MA_ DA TA2 9

MA_ DA TA3 0

MA_ DA TA3 1

MA_ DA TA3 2

MA_ DA TA3 3

MA_ DA TA3 4

MA_ DA TA3 5

MA_ DA TA3 6

MA_ DA TA3 7

MA_ DA TA3 8

MA_ DA TA3 9

MA_ DA TA4 0

MA_ DA TA4 1

MA_ DA TA4 2

MA_ DA TA4 3

MA_ DA TA4 4

MA_ DA TA4 5

MA_ DA TA4 6

MA_ DA TA4 7

MA_ DA TA4 8

MA_ DA TA4 9

MA_ DA TA5 0

MA_ DA TA5 1

MA_ DA TA5 2

MA_ DA TA5 3

MA_ DA TA5 4

MA_ DA TA5 5

MA_ DA TA5 6

MA_ DA TA5 7

MA_ DA TA5 8

MA_ DA TA5 9

MA_ DA TA6 0

MA_ DA TA6 1

MA_ DA TA6 2

MA_ DA TA6 3

RSVD_34

RSVD_35

RSVD_51

RSVD_52

RSVD_27

RSVD_28

RSVD_43

RSVD_42

MA_PAROUT

J21

H21

F23

H23

G20

F20

J22

J23

G25

F26

L24

L26

L23

F25

K25

K27

M25

M27

P27

R24

L27

M24

P24

P25

M22

N21

T22

V21

L21

M20

R23

T21

AL27

AL25

AP26

AR27

AK26

AK24

AM24

AP27

AM23

AM21

AR25

AU27

AL22

AL21

AP24

AP23

AW 26

AV25

AV22

AW 22

AU26

AV27

AW 23

AT22

AW 21

AU21

AP21

AN20

AR22

AN22

AT20

AR20

W25

W27

R26

R27

V27

V26

AF24

T24

T25

DDR_A_DQ0

DDR_A_DQ1

DDR_A_DQ2

DDR_A_DQ3

DDR_A_DQ4

DDR_A_DQ5

DDR_A_DQ6

DDR_A_DQ7

DDR_A_DQ8

DDR_A_DQ9

DDR_A_DQ10

DDR_A_DQ11

DDR_A_DQ12

DDR_A_DQ13

DDR_A_DQ14

DDR_A_DQ15

DDR_A_DQ16

DDR_A_DQ17

DDR_A_DQ18

DDR_A_DQ19

DDR_A_DQ20

DDR_A_DQ21

DDR_A_DQ22

DDR_A_DQ23

DDR_A_DQ24

DDR_A_DQ25

DDR_A_DQ26

DDR_A_DQ27

DDR_A_DQ28

DDR_A_DQ29

DDR_A_DQ30

DDR_A_DQ31

DDR_A_DQ32

DDR_A_DQ33

DDR_A_DQ34

DDR_A_DQ35

DDR_A_DQ36

DDR_A_DQ37

DDR_A_DQ38

DDR_A_DQ39

DDR_A_DQ40

DDR_A_DQ41

DDR_A_DQ42

DDR_A_DQ43

DDR_A_DQ44

DDR_A_DQ45

DDR_A_DQ46

DDR_A_DQ47

DDR_A_DQ48

DDR_A_DQ49

DDR_A_DQ50

DDR_A_DQ51

DDR_A_DQ52

DDR_A_DQ53

DDR_A_DQ54

DDR_A_DQ55

DDR_A_DQ56

DDR_A_DQ57

DDR_A_DQ58

DDR_A_DQ59

DDR_A_DQ60

DDR_A_DQ61

DDR_A_DQ62

DDR_A_DQ63

DDR_A_PAR

DDR_A_DQ[63..0] 23

DDR_A_PAR 23

24 DDR_B_MA[13..0]

24 DDR_B_MA14_WE#

24 DDR_B_MA15_CAS#

24 DDR_B_MA16_RAS#

24 DDR_B_BA0

24 DDR_B_BA1

24 DDR_B_BG0

24 DDR_B_BG1

24 DDR_B_ACT# 24

DDR_B_DM[7..0]

24 DDR_B_DQS0

24 DDR_B_DQS0#

24 DDR_B_DQS1

24 DDR_B_DQS1#

24 DDR_B_DQS2

24 DDR_B_DQS2#

24 DDR_B_DQS3

24 DDR_B_DQS3#

24 DDR_B_DQS4

24 DDR_B_DQS4#

24 DDR_B_DQS5

24 DDR_B_DQS5#

24 DDR_B_DQS6

24 DDR_B_DQS6#

24 DDR_B_DQS7

24 DDR_B_DQS7#

24 DDR_B_CLK0

24 DDR_B_CLK0#

24 DDR_B_CLK1

24 DDR_B_CLK1#

24 DDR_B_CS0#

24 DDR_B_CS1#

24 DDR_B_CKE0

24 DDR_B_CKE1

24 DDR_B_ODT0

24 DDR_B_ODT1

24 DDR_B_ALERT#

24 DDR_B_EVENT#

24 DDR_B_RST#

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14_WE#

DDR_B_MA15_CAS#

DDR_B_MA16_RAS#

DDR_B_BA0

DDR_B_BA1

DDR_B_BG0

DDR_B_BG1

DDR_B_ACT#

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS0#

DDR_B_DQS1

DDR_B_DQS1#

DDR_B_DQS2

DDR_B_DQS2#

DDR_B_DQS3

DDR_B_DQS3#

DDR_B_DQS4

DDR_B_DQS4#

DDR_B_DQS5

DDR_B_DQS5#

DDR_B_DQS6

DDR_B_DQS6#

DDR_B_DQS7

DDR_B_DQS7#

DDR_B_CLK0

DDR_B_CLK0#

DDR_B_CLK1

DDR_B_CLK1#

DDR_B_CS0#

DDR_B_CS1#

DDR_B_CKE0

DDR_B_CKE1

DDR_B_ODT0

DDR_B_ODT1

DDR_B_ALERT#

DDR_B_EVENT#

DDR_B_RST#

AK30

AG30

AC32

AC30

AB29

AB31

AA30

AA29

Y30

AA31

W2 9

AH29

Y32

W3 1

AL30

MB _W E_ L _A DD 14

AK32

AJ30

AH31

AG32

V31

V29

V30

C21

C25

E32

K30

AP30

AW 31

BB26

BD22

N32

D22

B22

D25

B25

F29

F30

K31

K29

AR29

AR31

AW 30

AW 29

BC25

BA25

BC22

BA22

N31

N29

AC31

AD30

AD29

AD31

AE30

AE32

AF29

AF31

AJ31

AM31

AJ29

AM29

U29

T30

V32

U31

AL31

AM32

AL29

AM30

W3 0

AG29

T31

MB _ADD0

MB _A DD 1

MB _A DD 2

MB _A DD 3

MB _A DD 4

MB _A DD 5

MB _A DD 6

MB _A DD 7

MB _A DD 8

MB _A DD 9

MB_ AD D1 0

MB_ AD D11

MB_ AD D12

MB_ AD D13 _ BA NK 2

MB_ CA S_ L_ AD D1 5

MB_ RA S_L _ AD D1 6

MB_ BA NK 0

MB_ BA NK1

MB _B G0

MB _B G1

MB_ AC T_L

MB _D M0

MB _D M1

MB _D M2

MB _D M3

MB _D M4

MB _D M5

MB _D M6

MB _D M7

RSV D_ 21

MB _D QS _H 0

MB _D QS _L 0

MB _D QS _H 1

MB _D QS _L 1

MB _D QS _H 2

MB _D QS _L 2

MB _D QS _H 3

MB _D QS _L 3

MB _D QS _H 4

MB _D QS _L 4

MB _D QS _H 5

MB _D QS _L 5

MB _D QS _H 6

MB _D QS _L 6

MB _D QS _H 7

MB _D QS _L 7

RSV D_ 20

RSV D_ 18

MB_ CL K_ H0

MB_ CL K_L 0

MB_ CL K_ H1

MB_ CL K_ L1

MB _C LK _H 2

MB_ C LK_ L 2

MB _C LK _H 3

MB_ CL K_L 3

MB0_ CS_ L0

MB0 _C S_L 1

MB1 _C S_L 0

MB1 _C S_L 1

MB0_CK E0

MB0_CK E1

MB1_CK E0

MB1_CK E1

MB0_ODT 0

MB0_ODT 1

MB1_ODT 0

MB1_ODT 1

MB_ALER T_L

MB_EVENT_ L

MB_RESET _L

@

UC1I

MEMORY B

FP5REV0.90

PART9OF13

FP5_BGA_1140P

MB_ DA TA0

MB_ DA TA1

MB_ DA TA2

MB_ DA TA3

MB_ DA TA4

MB_ DA TA5

MB_ DA TA6

MB_ DA TA7

MB_ DA TA8

MB_ DA TA9

MB_ DA TA1 0

MB_ DA TA1 1

MB_ DA TA1 2

MB_ DA TA1 3

MB_ DA TA1 4

MB_ DA TA1 5

MB_ DA TA1 6

MB_ DA TA1 7

MB_ DA TA1 8

MB_ DA TA1 9

MB_ DA TA2 0

MB_ DA TA2 1

MB_ DA TA2 2

MB_ DA TA2 3

MB_ DA TA2 4

MB_ DA TA2 5

MB_ DA TA2 6

MB_ DA TA2 7

MB_ DA TA2 8

MB_ DA TA2 9

MB_ DA TA3 0

MB_ DA TA3 1

MB_ DA TA3 2

MB_ DA TA3 3

MB_ DA TA3 4

MB_ DA TA3 5

MB_ DA TA3 6

MB_ DA TA3 7

MB_ DA TA3 8

MB_ DA TA3 9

MB_ DA TA4 0

MB_ DA TA4 1

MB_ DA TA4 2

MB_ DA TA4 3

MB_ DA TA4 4

MB_ DA TA4 5

MB_ DA TA4 6

MB_ DA TA4 7

MB_ DA TA4 8

MB_ DA TA4 9

MB_ DA TA5 0

MB_ DA TA5 1

MB_ DA TA5 2

MB_ DA TA5 3

MB_ DA TA5 4

MB_ DA TA5 5

MB_ DA TA5 6

MB_ DA TA5 7

MB_ DA TA5 8

MB_ DA TA5 9

MB_ DA TA6 0

MB_ DA TA6 1

MB_ DA TA6 2

MB_DATA63

RSVD_17

RSVD_19

RSVD_26

RSVD_29

RSVD_16

RSVD_15

RSVD_25

RSVD_24

MB_PAROUT

B21

D21

B23

D23

A20

C20

A22

C22

D24

A25

D27

C27

C23

B24

C26

B27

C30

E29

H29

H31

A28

D28

F31

G30

J29

J31

L29

L31

H30

H32

L30

L32

AP29

AP32

AT29

AU32

AN30

AP31

AR30

AT31

AU29

AV30

BB30

BA28

AU30

AU31

AY32

AY29

BA27

BC27

BA24

BC24

BD28

BB27

BB25

BD25

BC23

BB22

BC21

BD20

BB23

BA23

BB21

BA21

M31

P29

AG31

DDR_B_DQ0

DDR_B_DQ1

DDR_B_DQ2

DDR_B_DQ3

DDR_B_DQ4

DDR_B_DQ5

DDR_B_DQ6

DDR_B_DQ7

DDR_B_DQ8

DDR_B_DQ9

DDR_B_DQ10

DDR_B_DQ11

DDR_B_DQ12

DDR_B_DQ13

DDR_B_DQ14

DDR_B_DQ15

DDR_B_DQ16

DDR_B_DQ17

DDR_B_DQ18

DDR_B_DQ19

DDR_B_DQ20

DDR_B_DQ21

DDR_B_DQ22

DDR_B_DQ23

DDR_B_DQ24

DDR_B_DQ25

DDR_B_DQ26

DDR_B_DQ27

DDR_B_DQ28

DDR_B_DQ29

DDR_B_DQ30

DDR_B_DQ31

DDR_B_DQ32

DDR_B_DQ33

DDR_B_DQ34

DDR_B_DQ35

DDR_B_DQ36

DDR_B_DQ37

DDR_B_DQ38

DDR_B_DQ39

DDR_B_DQ40

DDR_B_DQ41

DDR_B_DQ42

DDR_B_DQ43

DDR_B_DQ44

DDR_B_DQ45

DDR_B_DQ46

DDR_B_DQ47

DDR_B_DQ48

DDR_B_DQ49

DDR_B_DQ50

DDR_B_DQ51

DDR_B_DQ52

DDR_B_DQ53

DDR_B_DQ54

DDR_B_DQ55

DDR_B_DQ56

DDR_B_DQ57

DDR_B_DQ58

DDR_B_DQ59

DDR_B_DQ60

DDR_B_DQ61

DDR_B_DQ62

DDR_B_DQ63

N30

P31

R32

M30

M29

P30

DDR_B_PAR

DDR_B_DQ[63..0] 24

DDR_B_PAR 24

EVENT# pullhigh

+1.2V_VDDQ

RC1 1 2 1K_0402 _5%

+1.2V_VDDQ

A A

5

RC2 1 2 1K_0402 _5%

DDR_B_EVENT#

DDR_A_EVENT#

SecurityClassification

Issued Date

THIIIS S HE ET OF ENGIIINEERIIING DRAWIIING IIIS THE PROPRIIIE TARY PROPER TY OF COMPA L ELECTRONIIICS,,, IIINC... AND CONTAIIINS CON FI DE NTI AL

AN D T RA DE SE CRE T IIINFORMATION... THIIIS SHE ET MA Y NO T BE TR AN SF ERE D F ROM T HE CU ST ODY O F TH E C OM PE TEN T DIIIVIIISIIION OF R& D

DE PA RTM EN T E XC EP T AS AUTHOR IIIZED BY C OMP AL ELECTRONIIICS,,, IIINC... NEIIITHER THIIIS SH EE T NO R TH E IIINF ORMATION IIIT CONTAIIINS MA Y

4

BE U SE D BY OR DIIISCLOSE D TO ANY THIIIRD PART Y W IIITHOUT PRIIIOR W RIIITTEN C ONS EN T OF COM PA L ELECTRONIIICS,,, IIINC...

3

2019/ 08/30 2020/08/30

Compal Secret Data

DecipheredDate

Tiiitttllle

Siiize Documenttt Number

Custttom

2

Compal Electronics, Inc.

FP5_(2/7)_DDR4

FH5VQ M/B LA-J812P

Rev

1A

1

112Dattte::: Friiiday,,, March 20,,, 2020 Sheettt 7 offf

Main Func = CPU

A

EC/THERM

+3VS

RC105 1 2 1K_0402_5%

RC106 1 2 1K_0402_5%

RC107 1 2 1K_0402_5%

RC108 1 2 1K_0402_5%

1 1

27,40,58,66 EC_SMB_CK2

27,40,58,66 EC_SMB_DA2

2 2

+3VS

RC6641

1 1

@EMC@

CC1202

.1U_0402_16V7K 33P_0402_5 0V8J

2 2

2 1K_0402_5% THERMTRIP#

EMC@

CC5

Close to APU

SVID

+1.8VS

3 3

RC109 1 @ 2 1K_0402_5%

RC110 1 @ 2 1K_0402_5%

2 1K_0402_5%

EC_SMB_CK2

EC_SMB_DA2

SVD_PWR_APU

APU_SID

APU_ALERT#

APU_SIC

APU_PROCHOT#

RC616 1 2 0_0402_5%

RC617 1 2 0_0402_5%

APU_PROCHOT#

APU_RST#

APU_PWROK

1

EMC@

CC6

33P_0402_50 V8J

2

SVT_PWR_APU_R

SVC_PWR_APU

RC111 1 @

APU_SIC

APU_SID

91 SVC_PWR_APU

91 SVD_PWR_APU

91 SVT_PWR_APU_R

HDMI

EDP

+1.8VS

+1.8VS

91 APU_PWROK

B

40 APU_DP0_P0

40 APU_DP0_N0

40 APU_DP0_P1

40 APU_DP0_N1

40 APU_DP0_P2

40 APU_DP0_N2

40 APU_DP0_P3

40 APU_DP0_N3

38 EDP_TXP0

38 EDP_TXN0

38 EDP_TXP1

38 EDP_TXN1

38 EDP_TXP2

38 EDP_TXN2

38 EDP_TXP3

38 EDP_TXN3

RC80 1 2 300_0402_5%

RC81 1 2 300_0402_5%

58 THERMTRIP#

58,85,91 APU_PROCHOT#

1 2

RC669

RC670

1 2

0_0402_5%

0_0402_5%

APU_DP0_P0

APU_DP0_N0

APU_DP0_P1

APU_DP0_N1

APU_DP0_P2

APU_DP0_N2

APU_DP0_P3

APU_DP0_N3

EDP_TXP0

EDP_TXN0

EDP_TXP1

EDP_TXN1

EDP_TXP2

EDP_TXN2

EDP_TXP3

EDP_TXN3

APU_TDI

APU_TDO

APU_TCK

APU_TMS

APU_TRST#

APU_DBREQ#

APU_RST#

APU_PWROK

APU_SIC

APU_SID

APU_ALERT#

THERMTRIP#

APU_PROCHOT#

SVC_PWR_APU_R

SVD_PWR_APU_R

SVT_PWR_APU_R

C

D

E

DISP

+1.8VALW

5

UC1C

C8

DP0 _TX P 0

A8

DP0 _T XN 0

D8

DP0 _TX P 1

B8

DP0 _T XN 1

B6

DP0 _TX P 2

C7

DP0 _TX N 2

C6

DP0 _TX P 3

D6

DP0 _T XN 3

E6

DP1 _T XP 0

D5

DP1 _T XN 0

E1

DP1 _T XP 1

C1

DP1 _TX N 1

F3

DP1 _TX P 2

E4

DP1 _T XN 2

F4

DP1 _TX P 3

F2

DP1 _TX N 3

DIS PLAY/ SVI 2/JTA G/TES T

DP3:

DP2:

DP1: eDP

DP0: HDMI

IO18

DP _S TE RE OS YN C

DP _B LO N

DP_ DI GON

DP_ VA RY _B L

DP0 _A UX P

DP0 _A UX N

DP0 _H PD

DP1 _A UX P

DP1 _A UX N

DP1 _H PD

DP2_ AU XP

DP2_ AU XN

DP2_H PD

DP3_ AU XP

DP3_ AU XN

DP3_H PD

RSV D_ 4

RSV D_ 3

RSV D_ 2

ENBKL_R

G15

ENVDD_R

F15

INVTPWM_R

L14

APU_DP0_CTRL_CLK

D9

APU_DP0_CTRL_DAT A

B9

APU_DP0_HPD

C10

EDP_AUXP

G11

EDP_AUXN

F11

EDP_HPD

G13

J12

H12

K13

J10

H10

K8

DP_STEREOSYNC

K15

F14

F12

F10

APU_DP0_CTRL_CLK 40

APU_DP0_CTRL_DAT A 40

APU_DP0_HPD 40

EDP_AUXP 38

EDP_AUXN 38

EDP_HPD 38

HDMI

EDP

ENBKL_R

ENVDD_R

ENVDD_R

INVTPWM_R

APU_TEST4

AP14

TES T4

AN14

TES T5

F13

TES T6

G18

TES T14

H19

TES T15

F18

TES T16

F19

TES T17

W2 4

TES T31

AR11

AU2

TDI

AU4

TD O

AU1

TC K

AU3

IO18S5

TMS

AV3

TRS T_ L

AW 3

DB RE Q_ L

AW 4

RES ET _L

AW 2

IO18

PW RO K

H14

SI C

J14

SI D

J15

ALE RT _L

AP16

IO33

THE RM TRI P _L

L19

PR OC HOT _L

F16

SVC0

H16

IO18

SVD0

J16

SVT0

FP5REV0.90

PART3OF13

FP5_BGA_1140P

@

TES T41

TES T47 0

TES T47 1

SM U_ ZV DD

CO RE TY PE

VDD P_ SE NS E

VDD CR _S OC _S EN SE

VDD CR _S EN SE

VSS _S EN SE _A

VSS_SENS E_B

AJ21

AK21

SMU_ZVDDP

V4

AW 11 CORETYPE

APU_VDDP_SEN_H

AN11

VCC_SENSE_APU_CORE_SOC

J1 9

VCC_SENSE_APU_CORE

K18

VSS_SEN_APU_CORE

J18

APU_VDDP_SEN_L

AM11

TP@

APU_TEST5

TP@

APU_TEST14

APU_TEST15

APU_TEST16

APU_TEST17

APU_TEST31

TP@

APU_TEST41

TP@

APU_TEST470

TP@

APU_TEST471

TP@

RC1682 1 2 196_0402_1%

RC1681 1 @ 2 1K_0402_5%

T4949

T4948

T4942

T4941

T4940

T4939

VSS_SEN_APU_CORE 91

APU_VDDP_SEN_L 89

+0.9VS

+3VALW

APU_VDDP_SEN_H 89

VCC_SENSE_APU_CORE_SOC 91

VCC_SENSE_APU_CORE 91

ENBKL

ENVDD

INVTPWM

ENBKL_R

ENVDD_R

INVTPWM_R

Leakage prevent from power side

UC66

1

P

NC

4 ENBKL

Y

2

A

G

NL17SZ07EDFT2G_SC70-5

SA0000BIO00

3

+1.8VALW

5

UC64

1

P

NC

4

Y

2

A

G

NL17SZ07EDFT2G_SC7 0-5

@ SA0000BIO00

3

RC6901 RS@ 2 0_0402_5% ENVDD

+1.8VALW

5

UC65

1

NC

4

INVTPWM

Y

2

A

G P

NL17SZ07EDFT2G_SC70-5

SA0000BIO00

3

RC3 1

RC4 1 @

RC5 1

RC6130 1 2 100K_0402_5%

RC6131 1 2 100K_0402_5%

RC6132 1 @ 2 100K_0402_5%

ENVDD

2 4.7K_0402_5%

2

4.7K_0402_5%

2

4.7K_0402_5%

ENBKL 58

ENVDD 38

INVTPWM 38

+3VS

HDT+

+1.8VALW

APU_TRST#

0.01U_0402_16 V7K

4 4

RH21 1

RH38 2

2

CH2

RH39 2

1

RH40 2

2 33_0402_5%

1 10K_0402_5%

1 10K_0402_5%

APU_TRST#_R

HDT_P11

HDT_P13

HDT_P15

JHDT1 CONN@

1

1 2

3

3 4

5

5 6

7

7 8

9

9 10

11

11 12

13

13 14

15

15 16

17

17 18

19

19 20

2

4

6

8

APU_PWROK

10

12

14

APU_DBREQ#_R

16

18

20

APU_TCK

APU_TMS

APU_TDI

APU_TDO

APU_RST#

APU_TCK

APU_TMS

APU_TDI

APU_DBREQ#

APU_TRST#

RH33 11 10K_0402_5%

2 33_0402_5%

APU_DBREQ#

RH34 1

RH35 1

RH36 1

RH37 1

RH26 1

Follow C5V08

2

1K_0402_5%

2 1K_0402_5%

2 1K_0402 _5%

2 1K_0402_5%

2 1K_0402_5%

+1.8VALW

TESTPOINT

DP_STEREOSYNC

APU_TEST14

APU_TEST15

APU_TEST16

APU_TEST17

RC1551

2 1K_0402_5%

RC1541 @ 2 1K_0402_5%

RC112 2 @ 1 10K_0402_ 5%

RC113 2 @ 1 10K_0402_5%

RC114 2 @ 1 10K_0402_5%

RC115 2 @ 1 10K_0402_ 5%

+1.8VS

+1.8VS

SAMTE_ASP-136446-07-B

Security Classification

Issued Date

THIIIS SH EE T OF ENGIIINEERIIING DRAWIIING IIIS THE PROPRIIIE TARY P RO PERTY O F C OMP AL ELECTRONIIICS,,, IIINC... AND CONTAIIINS CON FIDENTIA L

AN D T RA DE SE CRE T IIINFORMATION... THIIIS SHE ET MA Y NO T BE TR AN SF ERE D F ROM T HE CU ST ODY O F TH E C OM PE TEN T DIIIVIIISIIION OF R& D

DE PA RTM EN T E XC EP T AS AUTHOR IIIZED BY C OMP AL ELECTRONIIICS,,, IIINC... NEIIITHER THIIIS SH EE T NO R TH E IIINF ORMATION IIIT CONTAIIINS MA Y

A

B

BE U SE D BY OR DIIISCLOSE D TO ANY THIIIRD PART Y W IIITHOUT PRIIIOR W RIIITTEN C ONS EN T OF COM PA L ELECTRONIIICS,,, IIINC...

C

2019/ 08/30 2020/08/30

Compal Secret Data

DecipheredDate

Tiiitttllle

Siiize Documenttt Number

Custttom

D

Compal Electronics, Inc.

(3/7)_DISP/MISC/HDT

FH5VQ M/B LA-J812P

E

Rev

1A

112Dattte::: Friiiday,,, March 20,,, 2020 Sheettt 8 offf

Main Func = CPU

A B C D E

2 2.2K_0402_5%

2 2.2K_0402_5%

DIS

Type1

12

12

+1.8VALW

+3VS

+3VALW

12

12

RSV RSV

12

@

RC6135

12

RC6175

RC6174

@

@

+3VALW

12

12

UC1D

SW PU/PD

ACPI/AUDIO/I2C/GPIO/MISC

SW PU/PD

SW PU/PD1.8V_S5

SW PU/PD

SW PU/PD1.8V_S5

SW PU/PD

SW PU/PD 3.3V

FP5REV0.90

PART4OF13

FP5_BGA_1140P

I2C0_SCL/SFI0_I2C_SCL/EGPIO151

I2C0_SDA/SFI0_I2C_SDA/EGPIO152

I2C1_SCL/SFI1_I2C_SCL/EGPIO149

I2C1_SDA/SFI1_I2C_SDA/EGPIO150

SW PU/PD

3.3V_S5

SW PU/PD3.3VALW input

3.3VS input

3.3VS input

3.3VS Output

3.3VS input

3.3VS input

3.3VS input

3.3VS input

GPIO Table

AW1 2

EGPIO41/SFI_S5_EGPIO41

AU12

AGPIO39/SFI_S5_AGPIO39

AR13

AT13

AN8

AN9

BC20

I2C2_SCL/EGPIO113/SCL0

BA20

I2C2_SDA/EGPIO114/SDA0

AM9

I2C3_SCL/AGPIO19/SCL1

AM10

I2C3_SDA/AGPIO20/SDA1

L16

PSA_I2C_SCL

M16

PSA_I2C_SDA

AT15

AGPIO3

AW10 AGPIO4

AGPIO4/SATAE_IFDET

AP9 AGPIO5

AGPIO5/DEVSLP0

AU10

AGPIO6/DEVSLP1

AV15

SATA_ACT_L/AGPIO130

AU7 AGPIO9

AGPIO9

AU6 AGPIO40

AGPIO40

AW13 AGPIO69 RC6186 1 2 0_0402_5%

AGPIO69

AW1 5

AGPIO86

AU14

INTRUDER_ALERT

AU16

SPKR/AGPIO91

AV8 AGPIO11

BLINK/AGPIO11

AW1 6

GENINT1_L/AGPIO89

BD15

GENINT2_L/AGPIO90

AR18

FANIN0/AGPIO84

AT18

FANOUT0/AGPIO85

I2C_0_SCL

I2C_0_SDA

I2C_1_SCL

I2C_1_SDA

SMB_0_SCL

SMB_0_SDA

I2C_3_SCL

I2C_3_SDA

APU_BT_WAKE#

PANEL_OD#

APU_SPKR

TP_I2C_INT#_APU

SMB_0_SCL 23,24

SMB_0_SDA 23,24

I2C_3_SCL 63

I2C_3_SDA 63

APU_BT_WAKE# 52

AGPIO5 68

PANEL_OD# 38

APU_SPKR 56

TP_I2C_INT#_APU 63

DDR4

Touch Pad

AGPIO40 52,68

BT_ON 10,52

CC7 1 2 150P_0402_50V8J

1 1

APU_PCIE_RST#_C

APU_PCIE1_RST#_C

@ CC1001 2 150P_0402_50V8J

RC29 1 2 33_0402_5%

RC7041 @ 2 33_0402_5%

58 EC_RSMRST#

58 PBTN_OUT#

58 SYS_PWRGD_EC

58 SLP_S3#

58 SLP_S5#

ACPI

+3VALW

RC6133 1 @ 2 10K_0402_5%

+3VALW

12

RC6165

@ 10K_0402_1%

2 2

APU_PCIE_RST#_U

3 3

APU_PCIE_WAKE#

CRB use S0-rail

+3VS

12

RC28

10K_0402_1%

SYS_PWRGD_EC EC_RSMRST#

2

CC8

0.22U_0402_16V7K

1

APU_PCIE_RST#_C

RC7001 RS@ 2 0_0402_5%

APU_PCIE1_RST#_C

RC7011 @ 2 0_0402_5%

APU_PCIE_RST#_U

RC30 1 RS@ 2 0_0402_5%

1

2

RC6160

10K_0402_5%@

1 2

Reserve for MBDG/CRB

+1.8VALW

CC1210

10U_0402_6.3V6M

1 2

@

12

RC54

22K_0402_1%

1

CC16

1U_0201_6.3V6M

2

APU_PCIE_RST#_U

+3VALW

CC14

0.1U_0201_10V6K

1 2

@

5

IN1

APU_PCIE_RST#

4

O

IN2

G P

UC4 SA0000BIP00

@ MC74VHC1G08EDFT2G_SC70-5

3

APU_PCIE_RST#

APU_PCIE_RST# 27,51,52,68

52 BT_I2S_CLK_R

52 BT_I2S_DOUT_R

52 BT_I2S_DIN_R

52 BT_I2S_LRCLK_R

56 HDA_SDIN0

RC757 1@ 2 33_0402_5%

RC758 1@ 2 33_0402_5%

RC760 1@ 2 33_0402_5%

RC759 1@ 2 33_0402_5%

BT_I2S_CLK

BT_I2S_DOUT

BT_I2S_DIN

BT_I2S_LRCLK

APU_PCIE_RST#_R

APU_PCIE1_RST#_R

EC_RSMRST#

PBTN_OUT#

SYS_PWRGD_EC

SYS_RST#

APU_PCIE_WAKE#

SLP_S3#

SLP_S5#

AGPIO10

AGPIO23

AGPIO12

HDA_BIT_CLK

HDA_SDIN0

HDA_SDIN1

HDA_SDIN2

HDA_RST#

HDA_SYNC

HDA_SDOUT

BD5

PCIE_RST0_L/EGPIO26

BB6

PCIE_RST1_L/EGPIO27

AT16

RSMRST_L

AR15

PWR_BTN_L/AGPIO0

AV6

PWR_GOOD

AP10

SYS_RESET_L/AGPIO1

AV11

WAKE_L/AGPIO2

AV13

SLP_S3_L

AT14

SLP_S5_L

AR8

S0A3_GPIO/AGPIO10

AT10

AC_PRES/AGPIO23

AN6

LLB_L/AGPIO12

AW8

EGPIO42

AR2

AZ_BITCLK/TDM_BCLK_MIC

AP7

AZ_SDIN0/CODEC_GPI

AP1

AZ_SDIN1/SW_DATA1B/TDM_BCLK_PLAYBACK

AP4

AZ_SDIN2/SW_DATA2/TDM_DATA_PLAYBACK

AP3

AZ_RST_L/SW_DATA1A/SW_DATA3/TDM_DATA_MIC

AR4

AZ_SYNC/TDM_FRM_MIC

AR3

AZ_SDOUT/TDM_FRM_PLAYBACK

AT2

SW_MCLK/TDM_BCLK_BT

AT4

SW_DATA0/TDM_DOUT_BT

AR6

AGPIO7/FCH_ACP_I2S_SDIN_BT

AP6

AGPIO8/FCH_ACP_I2S_LRCLK_BT

@

SW PU/PD

I2C_0_SCL

I2C_0_SDA

I2C_1_SCL

I2C_1_SDA

SMB_0_SCL

SMB_0_SDA

I2C_3_SCL

I2C_3_SDA

RC6139 1 @ 2 2.2K_0402_5%

RC6140 1 @ 2 2.2K_0402_5%

RC6176 1 @ 2 2.2K_0402_5%

RC6177 1 @ 2 2.2K_0402_5%

RC6157 1 2 2.2K_0402_5%

RC6156 1 2 2.2K_0402_5%

RC6159 1

RC6158 1

AGPIO40 AGPIO9 AGPIO12 AGPIO23

RSV

H

RSV RSV DMIC x2 RSV

L

@

RC693 RC6147

10K_0402_5%10K_0402_5% 10K_0402_5% 10K_0402_5%

AGPIO40

AGPIO9

AGPIO12

AGPIO23

@ @

RC692 RC6148 RC6136

10K_0402_5%10K_0402_5% 10K_0402_5% 10K_0402_5%

AGPIO10 AGPIO11

HDA

Strap Pin

AGPIO5

AGPIO7

(BT_I2S_DIN

)

AGPIO3 AGPIO4

APU_SPI_CLK_R SYS_RST#

USE 48MHZ CRYSTAL

H

CLOCK

(Default)

USE 100MHZ PCIE

L

CLOCK AS

REFERENCE CLOCK

10 APU_SPI_CLK_R

HDA_SDIN1

HDA_SDIN2

HDA_RST#

HDA_BIT_CLK

HDA_SYNC

HDA_SDOUT

56 HDA_RST#_R

56 HDA_BIT_CLK_R

56 HDA_SYNC_R

56 HDA_SDOUT_R

4 4

RC1161 EMC@ 2 33_0402_5%

RC1171 EMC@ 2 33_0402_5%

RC1181 EMC@ 2 33_0402_5%

RC1191 EMC@ 2 33_0402_5%

RC1201 2 1K_0402_5%

RC1211 2 1K_0402_5%

RC122 1

2 1K_0402_5%

RC123 1

2 1K_0402_5%

RC695 1 @ 2 10K_0402_5%

RC696 1 @ 2 10K_0402_5%

RC703 1@ 2 10K_0402_5%

A B C D E

HDA_SDIN0

NORMAL RESET MODE

(Default)

SHORT RESET MODE

+1.8VS +1.8VALW +3VALW

12

RC622 RC47

10K_0402_5% @ 10K_0402_5%

APU_SPI_CLK_R

SYS_RST#

RC1703 RC929

2K_0402_5% @ 2K_0402_5%@

12

10K_0402_5%

12

RC951

+3VALW+3VALW

12

12

12

@

@

RC6137

RC6145

10K_0402_5%10K_0402_5%

12

12

AGPIO5

BT_I2S_DIN

@

RC6146

10K_0402_5%10K_0402_5%

Securiiity Clllassiiifiiicat iiion

Issued Date

THIS S HE ET O F E NGIIINEER ING DRAWI IING IIIS T HE PROP RIE TARY PR OP ERTY OF CO MPAL ELEC TRONICS,, , IIINC. A ND CONTAIII NS CONFIIIDENTIIIAL

AND TR ADE SE CRE T IIINFORMATIIION. T HIS SH EET MA Y NOT B E TR ANS FE RED FRO M T HE CUS TO DY O F THE CO MP ETE NT DIVIIISIIION O F R&D

DE PAR TME NT E XCE PT AS A UTH ORI ZE D B Y C OMP AL ELECTR ONICS,,, IIINC. NEIIITHER THI S SHE ET NOR TH E IIINFORMATIIION IIIT CONTAIIINS MA Y

BE US ED BY OR D IS CLO SED TO A NY T HIRD PAR TY WIIITHOUT PRI OR W RI TTE N CON SE NT OF CO MP AL EL ECTRONICS, ,, IIINC.

12

12

@

RC6138

2019/ 08/30 2020/08/30 Tiiitttllle

Compal SecretData

@

RC6170

10K_0402_5%10K_0402_5%

APU_BT_WAKE#

AGPIO4

@

RC6171

10K_0402_5%10K_0402_5%

Deciiiphered Date

12

@

RC6168

12

12

@

RC6169

@

RC619

10K_0402_5%10K_0402_5%

AGPIO10

AGPIO11

@

RC6134

10K_0402_5%10K_0402_5%

Compal Electronics, Inc.

FP5_(4/7)_GPIO/HDA/STRAP

Siiize DocumentttNumberrr

Custttom

Dattte::: Frrriiiday,,, Marrrch20,,, 2020 Sheettt 9 offf112

+3VALW

12

12

@

RC6172

12

12

@

RC6173

FH5VQ M/B LA-J812P

Rev

1A

Main Func = CPU

+3VS

1 1

48MHz CRYSTAL

2

2

3

3

1

C796

3.9P_0402_50V8C

2

2 2

32.768KHz CRYSTAL

(55597: FP5 32.768K +/-20ppm ESR <65K ohm)

32.768KHZ_9PF_X1A000141000200

2 1

RC914

20M_0402_5%

1

CC686

12P_0402_50V8J

2

USB Function

+1.8VALW

3 3

4 4

RC941 2 4.7K_0402_5%

RC951 2 4.7K_0402_5%

A B C D E

LPC_RST_A#

UC1E

CLK/LPC/EMMC/SD/SPI/eSPI/UART

SW PU/PD

EGPIO70/SD_CLK

SW PU/PD

LPC_PD_L/SD_CMD/AGPIO21

M.2 WLAN/BT

GBE LAN

M.2 WWAN

M.2 WLAN

PCIE X4 DT SLOT

M.2 PCIE SSD

EVAL GFX SLOT

FP5REV0.90

PART5OF13

SW PU/PD

SW PU/PD

SW PU/PD

SW PU/PD

LPC_PME_L/SD_PWR_CTRL/AGPIO22

ESPI_RESET_L/KBRST_L/AGPIO129

ESPI_ALERT_L/LDRQ0_L/EGPIO108

SW PU/PD

SPI_CS2_L/ESPI_CS_L/AGPIO30

UART0_RTS_L/UART2_RXD/EGPIO137

UART0_CTS_L/UART2_TXD/EGPIO135

EGPIO142/UART1_RTS_L/UART3_RXD

EGPIO140/UART1_CTS_L/UART3_TXD

LAD0/SD_DATA0/EGPIO104

LAD1/SD_DATA1/EGPIO105

LAD2/SD_DATA2/EGPIO106

LAD3/SD_DATA3/EGPIO107

LPCCLK0/EGPIO74

LPC_CLKRUN_L/AGPIO88

LPCCLK1/EGPIO75

SERIRQ/AGPIO87

LFRAME_L/EGPIO109

LPC_RST_L/SD_WP_L/AGPIO32

AGPIO68/SD_CD

SPI_ROM_REQ/EGPIO67

SPI_ROM_GNT/AGPIO76

SPI_CLK/ESPI_CLK

SPI_DI/ESPI_DATA

SPI_WP_L/ESPI_DAT2

SPI_HOLD_L/ESPI_DAT3

SPI_CS1_L/EGPIO118

SPI_CS3_L/AGPIO31

SPI_TPM_CS_L/AGPIO29

UART0_INTR/AGPIO139

EGPIO141/UART1_RXD

EGPIO143/UART1_TXD

AGPIO144/UART1_INTR

FP5_BGA_1140P

UC1J

USB

FP5REV0.90

PART10OF13

Port0

Port3

FP5_BGA_1140P

USBC0_A2/USB_0_TXP0/DP3_TXP2

USBC0_A3/USB_0_TXN0/DP3_TXN2

USBC0_B11/USB_0_RXP0/DP3_TXP3

USBC0_B10/USB_0_RXN0/DP3_TXN3

USBC0_B2/DP3_TXP1

USBC0_B3/DP3_TXN1

USBC0_A11/DP3_TXP0

USBC0_A10/DP3_TXN0

USB_0_TXP1

Port1

USB_0_TXN1

USB_0_RXP1

USB_0_RXN1

USB_0_TXP2

Port2

USB_0_TXN2

USB_0_RXP2

USB_0_RXN2

USBC1_A2/USB_0_TXP3/DP2_TXP2

USBC1_A3/USB_0_TXN3/DP2_TXN2

USBC1_B11/USB_0_RXP3/DP2_TXP3

USBC1_B10/USB_0_RXN3/DP2_TXN3

USBC1_B2/DP2_TXP1

USBC1_B3/DP2_TXN1

USB_1_TXP0

Port4

USB_1_TXN0

USB_1_RXP0

USB_1_RXN0

USB_0_DM0

USB_0_DP1

Controller0

USB_0_DP2

USB_0_DM2

USB_0_DP3

USB_0_DM3

USB_1_DP0

USB_1_DM0

Controller1

USB_1_DM1

USB_OC0_L/AGPIO16

USB_OC1_L/AGPIO17 USBC1_A11/DP2_TXP0

USB_OC2_L/AGPIO18 USBC1_A10/DP2_TXN0

USB_OC3_L/AGPIO24

AGPIO14/USB_OC4_L

SW PU/PD

@

BD13

BB14 LPCPD#

BB12

BC11

BB15

BA15

BC13

BC12 SERIRQ

BD11

BA11

BA13

BC8

BB8

BC6

BB7

BA9

BB10

SPI_DO

BA10

BC10

BC9

BA8

BA6

BD8

UART0_RXD/EGPIO136

UART0_TXD/EGPIO138

BD18

BB16

AD2

AD4

AC2

AC4

AF4

AF2

AE3

AE1

AG3

AG1

AJ9

AJ8

AG4

AG2

AG7

AG6

AA2

AA4

Y1

Y3

AC1

AC3

AB2

AB4

AH4

AH2

AK7

AK6

GC6_FB_EN

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

BC15

LPC_CLK0

LPC_CLK1

BB13

LPC_FRAME#

BA12

LPC_RST_A#

EC_SCI#

BB11 KBRST#

ESPI_ALERT_L

APU_SPI_CLK

APU_SPI_MISO

APU_SPI_MOSI

APU_SPI_WP#

APU_SPI_HOLD#

APU_SPI_CS#1

APU_SPI_TPMCS#

BA16

BB18

UART_0_RTS#

BC17

UART_0_CTS#

BA18

PE_GPIO1

BC18

NVVDD1_PG

BA17

GPU_EVENT#

BC16

PE_GPIO0

BB19

USB3_ATX_DRX_P1

USB3_ATX_DRX_N1

USB3_ARX_DTX_P1

USB3_ARX_DTX_N1

USB3_ATX_DRX_P2

USB3_ATX_DRX_N2

USB3_ARX_DTX_P2

USB3_ARX_DTX_N2

USB3_ATX_DRX_P3

USB3_ATX_DRX_N3

USB3_ARX_DTX_P3

USB3_ARX_DTX_N3

RC1011 2 10_0402_5%

RC1021 2 10_0402_5%

RC1031

RC1041

RC449 1

UART_0_ARXD_DTXD

UART_0_ATXD_DRXD

RC6182 1 GC6@ 2 0_0402_5%

TP@T103

2 10_0402_5%

2 10_0402_5%

2 22 _0402_5%

SERIRQ 58

LPC_FRAME# 58

EC_SCI# 58

KBRST# 58

RC74 1 EMC@ 2 10_0402_5%

UART_0_ARXD_DTXD 52

UART_0_ATXD_DRXD 52

UART_0_RTS# 52

UART_0_CTS# 52

PE_GPIO1 27

NVVDD1_PG 96

GPU_EVENT# 27

PE_GPIO0 27

USB3_ATX_DRX_P1 71

USB3_ATX_DRX_N1 71

USB3_ARX_DTX_P1 71

USB3_ARX_DTX_N1 71

USB3_ATX_DRX_P2 72

USB3_ATX_DRX_N2 72

USB3_ARX_DTX_P2 72

USB3_ARX_DTX_N2 72

USB3_ATX_DRX_P3 42

USB3_ATX_DRX_N3 42

USB3_ARX_DTX_P3 42

USB3_ARX_DTX_N3 42

GC6_FB_EN3V3

LPC_AD0_R 58

LPC_AD1_R 58

LPC_AD2_R 58

LPC_AD3_R 58

LPC_CLK0_EC58

APU_SPI_CLK_R 9

Type-A MB CHG

Type-A MB

Type-C MB

GC6_FB_EN3V327

8MB SPI ROM

APU_SPI_CS#1

APU_SPI_MISO

APU_SPI_WP#

EC_SCI#

ESPI_ALERT_L

PE_GPIO1

LPC_CLK1

APU_SPI_CS#1

APU_SPI_WP#

APU_SPI_HOLD#

RC6149 1

RC1696 1

RC1697 1

1 RC9392

1M_0402_5%

2 10K_0402_5%

2 10K_0402_5%

2 10K_0402_5%

2 10K_0402_5%

1

1

4

4

SJ10000PW00 YC3

1

CC682

10P_0402_50V8J

2

CLKREQ_PCIE#0

CLKREQ_PCIE#2

CLKREQ_PEG#4

CLKREQ_PCIE#3

48M_X2

48M_X1

YC2

48MHZ_8PF_7V48000010

SJ10000JP00

1

C797

3.9P_0402_50V8C

2

32K_X1

2 1

32K_X2

APU_USBC_SCL

APU_USBC_SDA

52 SUSCLK_WLAN

M.2 SSD1

M.2WLAN

LAN

DGPU

M.2 SSD1

WLAN

LAN

DGPU

RC762 1@ 2 22_0402_5%RTCCLK

CAMERA

Type-A MB CHG

Type-A MB

Type-C MB

Type-A SUB

USB Hub

9,52 BT_ON

52 APU_W LAN_WAKE#

68 CLKREQ_PCIE#0

52 CLKREQ_PCIE#2

51 CLKREQ_PCIE#3

27 CLKREQ_PEG#4

68 CLK_PCIE_P0

68 CLK_PCIE_N0

52 CLK_PCIE_P2

52 CLK_PCIE_N2

51 CLK_PCIE_P3

51 CLK_PCIE_N3

27 CLK_PEG_P4

27 CLK_PEG_N4

38 USB20_P0

38 USB20_N0

71 USB20_P1

71 USB20_N1

72 USB20_P2

72 USB20_N2

43 USB20_P3

43 USB20_N3

73 USB20_P4

73 USB20_N4

75 USB20_P5

75 USB20_N5

RC6187

0_0402_5% 2 @ 1

CLKREQ_PCIE#0

CLKREQ_PCIE#2

CLKREQ_PCIE#3

CLKREQ_PEG#4

CLK_PCIE_P0

CLK_PCIE_N0

CLK_PCIE_P2

CLK_PCIE_N2

CLK_PCIE_P3

CLK_PCIE_N3

CLK_PEG_P4

CLK_PEG_N4

48M_X1

48M_X2

32K_X1

32K_X2

USB20_P0

USB20_N0

USB20_P1

USB20_N1

USB20_P2

USB20_N2

USB20_P3

USB20_N3

USB20_P4

USB20_N4

USB20_P5

USB20_N5

APU_USBC_SCL

APU_USBC_SDA

AGPIO17 AK9

APU_WLAN_WAKE#

AV18

CLK_REQ0_L/SATA_IS0_L/SATA_ZP0_L/AGPIO92

AN19

CLK_REQ1_L/AGPIO115

AP19

CLK_REQ2_L/AGPIO116

AT19

CLK_REQ3_L/SATA_IS1_L/SATA_ZP1_L/EGPIO131

AU19

CLK_REQ4_L/OSCIN/EGPIO132

AW1 8

CLK_REQ5_L/EGPIO120

AW1 9

CLK_REQ6_L/EGPIO121

AK1

GPP_CLK0P

AK3

GPP_CLK0N

AM2

GPP_CLK1P

AM4

GPP_CLK1N

AM1

GPP_CLK2P

AM3

GPP_CLK2N

AL2

GPP_CLK3P

AL4

GPP_CLK3N

AN2

GPP_CLK4P

AN4

GPP_CLK4N

AN3

GPP_CLK5P

AP2

GPP_CLK5N

AJ2

GPP_CLK6P

AJ4

GPP_CLK6N

AJ3

48M_OSC

BB3

X48M_X1

BA5

X48M_X2

AF8

RSVD_76

AF9

RSVD_77

AW1 4

RTCCLK

AY1

X32K_X1

AY4

X32K_X2

@

AE7

USB_0_DP0

AE6

AG10

AG9

USB_0_DM1

AF12

AF11

AE10

AE9

AJ12

AJ11

AD9

USB_1_DP1

AD8

AM6

USBC_I2C_SCL

AM7

USBC_I2C_SDA

AK10

AL9

AL8

AW7

AT12

AGPIO13/USB_OC5_L

RC602

33_0402_5%

1 2

RC6181 2 1 10K_0402_5%

RC6166 2 @ 1 10K_0402_5%

RC6183 2 @ 1 10K_0402_5%

RC6180 2 @ 1 10K_0402_5%

APU_SPI_MISO

APU_SPI_WP#

APU_SPI_HOLD#

APU_SPI_CS#1

APU_SPI_TPMCS#

UC7

1

CS# VCC

2

DO(IO1) HOLD# (IO3)

3

WP #(IO2) CLK

4

GND DI(IO0)

GD25LB64CSIGR_SOIC_8P

SA00008K400

APU_SPI_CLK_R

JC1

1

CS#

3

WP#

7

HOLD# SI/SIO0

4

GND SO/S IO1

ACES_91960-0084N_MX25L3206EM2I

CONN@

LPC_RST# 58

1

CC615

150P_0402_50V8J

2

1 10K_0402_5%RC6154 2RC16951

2

8

7

6

5

@EMC@

8

6

5

2

2

2

2

RC1672

0_0603_5%

1 RS@ 2

+SPI_VCC

APU_SPI_HOLD#

APU_SPI_CLK_R

APU_SPI_MOSI

+SPI_VCC

APU_SPI_CLK_R

APU_SPI_MOSI

APU_SPI_MISO

10K_0402_5%

10K_0402_5%

10K_0402_5%

10K_0402_5%

RC1706 1 @

RC6401

RC642 1

RC6391

RC646 1 @ 210K_0402_5%

+1.8VALW +SPI_VCC

1 @EMC@2 1 2

RC680 CC636

10_0402_5%10P_0402_50V8J

VCC

SCLK

+3VALW

+3VS

+SPI_VCC

@

2

CC635

0.1U_0201_10V6K

1

Securiiity Clllassiiifiiicatiiion

Issued Date

THIS S HEE T O F ENG IIINEERI NG DRAWIIING IIIS THE PRO PRIET ARY PR OPE RTY OF COM PAL ELECTRONICS ,,, IIINC. AND CONTAIIINS CONFIIIDENTIIIAL

AND TR ADE SE CRE T IIINFORMATIIION. T HIS SH EET MA Y NOT B E TR ANS FE RED FRO M T HE CUS TO DY O F THE CO MP ETE NT DIVIIISIIION O F R&D

DE PAR TME NT E XCE PT AS A UTH ORI ZE D B Y C OMP AL ELECTR ONICS,,, IIINC. NEIIITHER THI S SHE ET NOR TH E IIINFORMATIIION IIIT CONTAIIINS MA Y

A B C D E

BE US ED BY OR D IS CLO SED TO A NY T HIRD PAR TY WIIITHOUT PRI OR W RI TTE N CON SE NT OF CO MP AL EL ECTRONICS, ,, IIINC.

2019/ 08/30 2020/08/30 Tiiitttllle

Compal SecretData

Deciiiphered Date

Compal Electronics, Inc.

Siiize DocumentttNumberrr

Dattte::: Frrriiiday,,, Marrrch20,,, 2020 Sheettt 10 offf 112

FP5_(5/7)_CLK/USB/SPI/LPC

Custttom

FH5VQ M/B LA-J812P

Rev

1A

A

B

C

D

E

Main Func = CPU

UC1F

TDC: 10A

+APU_CORE_SOC

SCL/MBDG:

7*22uF (BU)

1*1uF (BU)

1 1

1*180pF (BU)

EDC: 13A

+APU_CORE_SOC Cap

place at Power Side

+1.2V_VDDQ

SCL/MBDG:

9*22uF (BU)

+1.2V_VDDQ +1.2V_VDDQ

CC1057 22U_0603_6.3V6M

CC1058 22U_0603_6.3V6M

CC1008 22U_0603_6.3V6M

CC1060 22U_0603_6.3V6M

CC1059 22U_0603_6.3V6M

CC1163 22U_0603_6.3V6M

CC1063 22U_0603_6.3V6M

CC1062 22U_0603_6.3V6M

CC1061 22U_0603_6.3V6M

1 1 1 1 1 1 1 1 1

2 2 2 2 2 2 2 2 2

2 2

All BU(on bottom side under SOC)

SCL/MBDG:

1 *22uF (BO)

+1.8VS +3VS +3VS_APU

RC1677

0_0402_5%

1 RS@ 2

+VDDIO_AUDIO

CC1207 22U_0603_6.3V6M

1

2

1*1uF (BU)

CC1192 1U_0201_6.3V6M

1

2

CC1093 180P_0402_50V8J

CC1164 1U_0201_6.3V6M

CC1165 1U_0201_6.3V6M

1

1 1

2

2 2

CC1082 0.22U_0402_16V7K

1 1 1 1

2 2 2 2

CC1078 0.22U_0402_16V7K

CC1079 0.22U_0402_16V7K

CC1081 0.22U_0402_16V7K

ACROSS VDDIO AND VSS SPLIT

SCL/MBDG:

1 *22uF (BO)

RC1676

0_0402_5%

1 RS@ 2

CC1137 22U_0603_6.3V6M

1

2

2*1uF (BO+BU)

CC1209 1U_0201_6.3V6M

CC1208 1U_0201_6.3V6M

1 1

2 2

2*1uF (BU)

4*0.22uF

1*180pF (BU)

2*180pF

CC1167 180P_0402_50V8J

CC1166 180P_0402_50V8J

1 1

2 2

+3VS_APU

+1.8VALW

BO BU BO BO BU

3 3

+1.8VS +1.8VALW +3VALW

CC1189 22U_0603_6.3V6M

1

2

BO BO BU

SCL/MBDG:

1 *22uF (BO)

2*1uF (BO+BU)

CC1191 1U_0201_6.3V6M

CC1190 1U_0201_6.3V6M

1 1

2 2

CC1186 22U_0603_6.3V6M

1

2

BO BO BU

SCL/MBDG:

1 *22uF (BO)

2*1uF (BO+BU)

CC1187 1U_0201_6.3V6M

CC1188 1U_0201_6.3V6M

1 1

2 2

CC1183 22U_0603_6.3V6M

1

2

SCL/MBDG:

1 *22uF (BO)

2*1uF (BO+BU)

CC1184 1U_0201_6.3V6M

CC1185 1U_0201_6.3V6M

1 1

2 2

BO BO BU

+0.9VALW

TDC: 6A

TDC :0.2A

+VDDIO_AUDIO

TDC :0.25A

TDC :2A

+1.8VS

TDC :0.5A

TDC :0.25A

+3VALW

TDC :1A

TDC :4A

+0.9VS

TDC :4.5uA

+RTC_APU_R

RTC OF APU

AA20

AA23

AA26

AA28

AA32

AC20

AC22

AC25

AC28

AD23

AD26

AD28

AD32

AE20

AE22

AE25

AE28

AF23

AF26

AF28

AF32

AG20

AG22

AG25

AG28

AJ20

AJ23

AJ26

AJ28

AJ32

AK28

AL28

AL32

AP12

AL18

AM17

AL20

AM19

AL19

AM18

AL17

AM16

AL14

AL15

AM14

AL13

AM12

AM13

AN12

AN13

AT11

M15

M18

M19

N16

N18

N20

P17

P19

R18

R20

T19

U18

U20

V19

W1 8

W2 0

Y19

T32

V28

W2 8

W3 2

Y22

Y25

Y28

VDDCR_SOC _1

VDDCR_SOC _2

VDDCR_SOC _3

VDDCR_SOC _4

VDDCR_SOC _5

VDDCR_SOC _6

VDDCR_SO C_7

VDDCR_SO C_8

VDDCR_SOC _9

VDDCR_SO C_10

VDDCR_SO C_11

VDDCR_SO C_12

VDDCR_SO C_13

VDDCR_SO C_14

VDDCR_SO C_15

VDDCR_SO C_16

VDDCR_SO C_17

VDDIO_ME M_S3_1

VDDIO_ME M_S3_2

VDDIO_ME M_S3_3

VDDIO_ME M_S3_4

VDDIO_ME M_S3_5

VDDIO_ME M_S3_6

VDDIO_ME M_S3_7

VDDIO_ME M_S3_8

VDDIO_ME M_S3_9

VDDIO_ME M_S3_10

VDDIO_ME M_S3_11

VDDIO_ME M_S3_12