Acer A1-840 Schematic

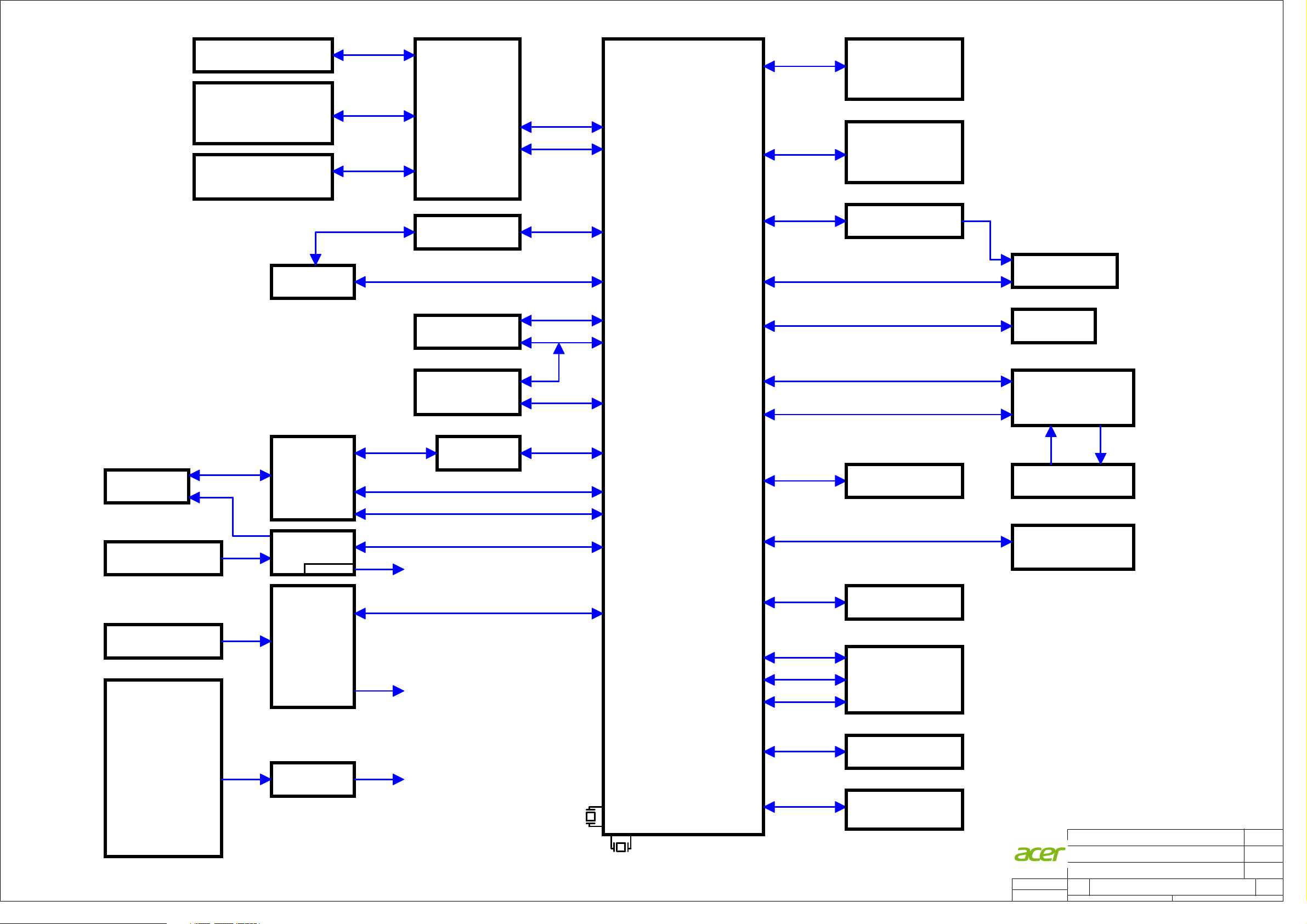

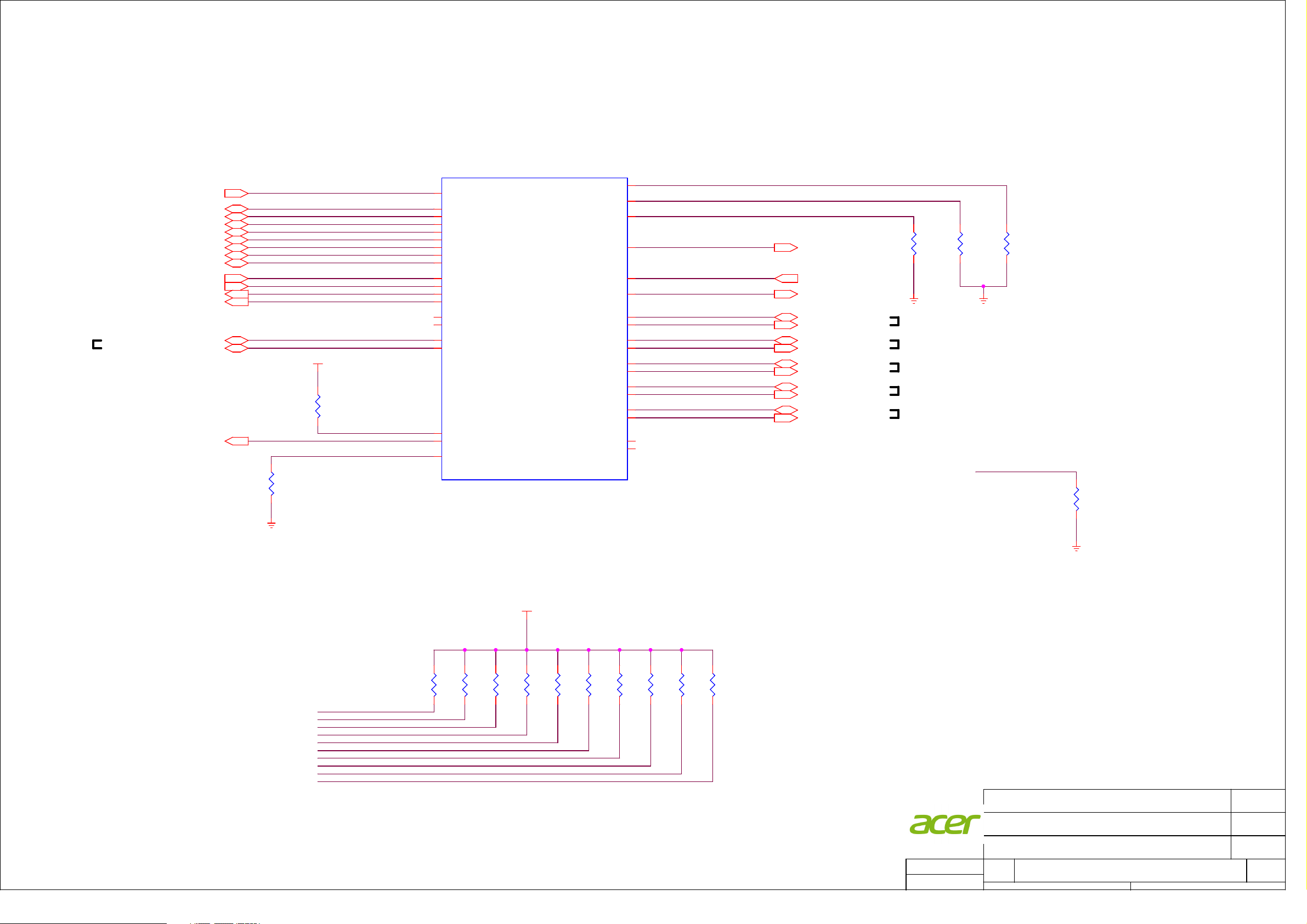

BLOCK DIAGRAM

Combo Jack

SPK CONN

Bei Ruier

XHB160905B08-01 x2

0.6W, 8ohm

DMIC

GoerTek

SD07OT263-010

uHDMI CONN

Audio Codec

ALC5640

Level Shift

Rear CAM

OV5693

Bay Trail-T CR

17mm x 17mm

Z3735F/G

I2S_0

I2C_1

DDIO_DDC_HPD

DDIO

MCSI_1

I2C_1

MMC1

XDP

UART3

I2C_1

SD3

DDR3L 4Gbit x4

D2516EC4BXGGB

H5TC4G63AFR-PBA

eMMC 16G

KE4CN4K6A-A58

H26M52103FMR

KLMAG2WEMB-B031

SPI (8MB)

W25Q64FWZPIG

Debug CONN

uSD CONN

uUSB CONN

BATTHERM Sensor

SYSTHERM Sensor

BAT CONN

LGC Polymer

Springpower

4600mAh

1S1P

USB SWITCH

AOZ6184

Charger

BQ24297

5V Boost

PMIC

Gauge

SND9039ABTRSK

HDMI 5V

TPS60151

Front CAM

GC2155 D2HD

OV2722 D2W

USB PHY

TUSB1210

+VBUS_CONN

SOC Rails &

Supply to all other IOs

To HDMI

25MHz

MCSI_2

USB_ULPI

USB2_P1

I2C_0

I2C_0

I2C_4

32.768KHz

MDSI_A

I2C_2

I2C_3

I2C_2

SD2

UART1

I2S_1

UART2

GPIOs

Vibrator

Gyro/G Combo

MPU-6515

WIFI/BT/FM

BCM43340 COB

GPS

BCM4752

PWR & Volume

Button x3

LCD CONN

K&D

KD080D10-31NA-A7

MIPI, 1280x800

22.8V

FB1~3

BKLT DRV

TPS61176

Touch CONN

FocalTech

FT5506

Project:

Project:

Project:

Title:

Title:

Title:

01_BLOC K DIAGRAM

01_BLOC K DIAGRAM

01_BLOC K DIAGRAM

Size:

Size:

Size:

Approved:

Approved:

Approved:

Designer:

Designer:

Designer:

Document Number:

Document Number:

Document Number:

Date:

Friday, July 25, 2014 391

Date:

Friday, July 25, 2014 391

Date:

Friday, July 25, 2014 391

Acer Inc.

Acer Inc.

Acer Inc.

Ducati2 BAYt_CR

Ducati2 BAYt_CR

Ducati2 BAYt_CR

{Doc} 0.1C

{Doc} 0.1C

{Doc} 0.1C

Sheet:

Sheet:

Sheet:

Drawing Rule

Drawing Rule

Drawing Rule

Allegro Lib Ver

Allegro Lib Ver

Allegro Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

Rev

Rev

Rev

of

of

of

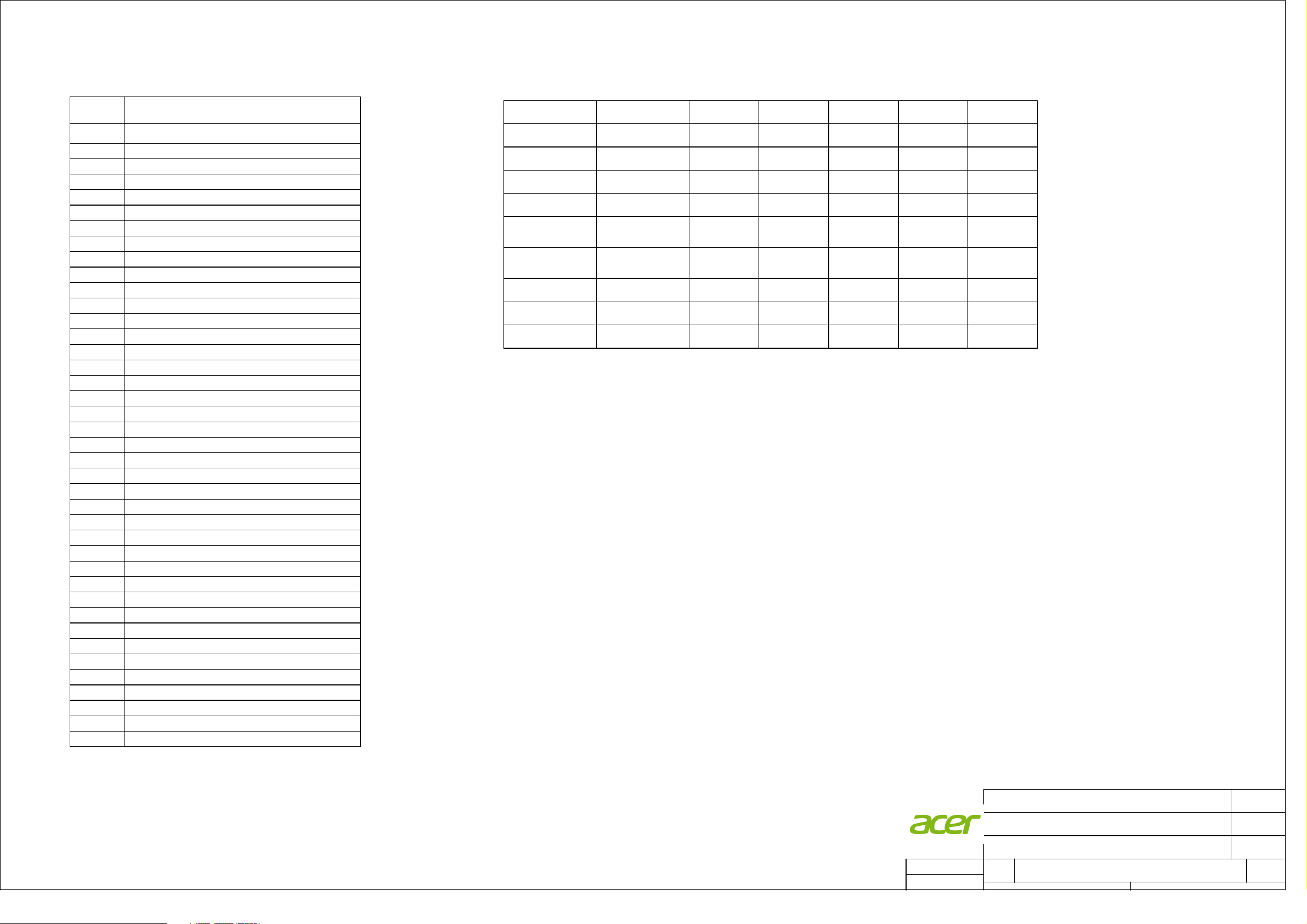

TABLE OF CONTENTS & NOTES

TABLE OF CONTENTS

SHEET NAMESHEET NO.

BLOCK DIAGRAM1

2

3

4

5

6

7

8

9

10

11

12

14

15

16

17

18

19

20

21

22

23

24

25

26 SENSORS

27

28

29

30

31

32

33

34

35

36

37

38

39

40

TABLE OF CONTENTS & NOTES

SOC: MEMORY

SOC: DISPLAY & CAMERA

SOC: STORAGE & I2S

SOC: USB & I2C

SOC: PMU/DFX/CLK/UART/SUS

SOC: POWER 1

SOC: POWER 2

SOC: GND

SOC: DECOUPLING

PMIC: SWITCHING REGULATORS

PMIC: LDOS13

PMIC: HOST & MISC INTERFACES

PMIC: EXTERNAL REGULATORS

MEMORY DEVICE 0 & 1

MEMORY DEVICE 2 & 3

MEMORY TERMINATION

SPI NOR FLASH

USB PHY & MUX

EMMC

BLANK PAGE

CAMERA CONNECTOR

TOUCH CONNCTOR & SHIELDS & HOLES

MIPI-DISPLAY CONNECTOR

AUDIO ALC5640

SPEAKER & DMIC & JACK

LCM LED BOOST

USB CONNECTOR

HDMI LEVEL SHIFTERS

HDMI CONNECTOR

MICRO-SD CONNECTOR

WIFI-BT

GPS

BATTERY & DEBUG CONNECTOR

POWER SEQUENCE

CHANGE LIST

POWER TREE

I2C MAP

INTERFACE PART I2C_0 I2C_1 I2C_2 I2C_3

TOUCH CONTROLLER

AUDIO CODEC

PMIC

GYRO/G SENSOR

FRONT CAMERA

REAR CAMERA

XDP CONNECTOR 0xXX

Charger BQ24297 0x6B

FT5506

ALC5640

SND9039ABTRSK

MPU-6515

GC2155 (D2HD)

OV2722 (D2W) 0x36/0x6D/0x6C

OV5693

0x38

0x3C/0x78/0x79

0x10/0x21/0x20

0x0C/0x19/0x18

0x70

0x69

0xXX LCD (NC in LCM) KD080D10-31NA-A7

I2C_4

0x5C~5F

Approved:

Approved:

Approved:

Designer:

Designer:

Designer:

Project:

Project:

Project:

Title:

Title:

Title:

Size:

Size:

Size:

Document Number:

Document Number:

Document Number:

Date:

Date:

Date:

Acer Inc.

Acer Inc.

Acer Inc.

Ducati2 BAYt_CR

Ducati2 BAYt_CR

Ducati2 BAYt_CR

02_TABLE OF CONTENTS & NOTES

02_TABLE OF CONTENTS & NOTES

02_TABLE OF CONTENTS & NOTES

{Doc} 0.1C

{Doc} 0.1C

{Doc} 0.1C

Friday, July 25, 2014 392

Friday, July 25, 2014 392

Friday, July 25, 2014 392

Sheet:

Sheet:

Sheet:

Drawing Rule

Drawing Rule

Drawing Rule

Allegro Lib Ver

Allegro Lib Ver

Allegro Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

Rev

Rev

Rev

of

of

of

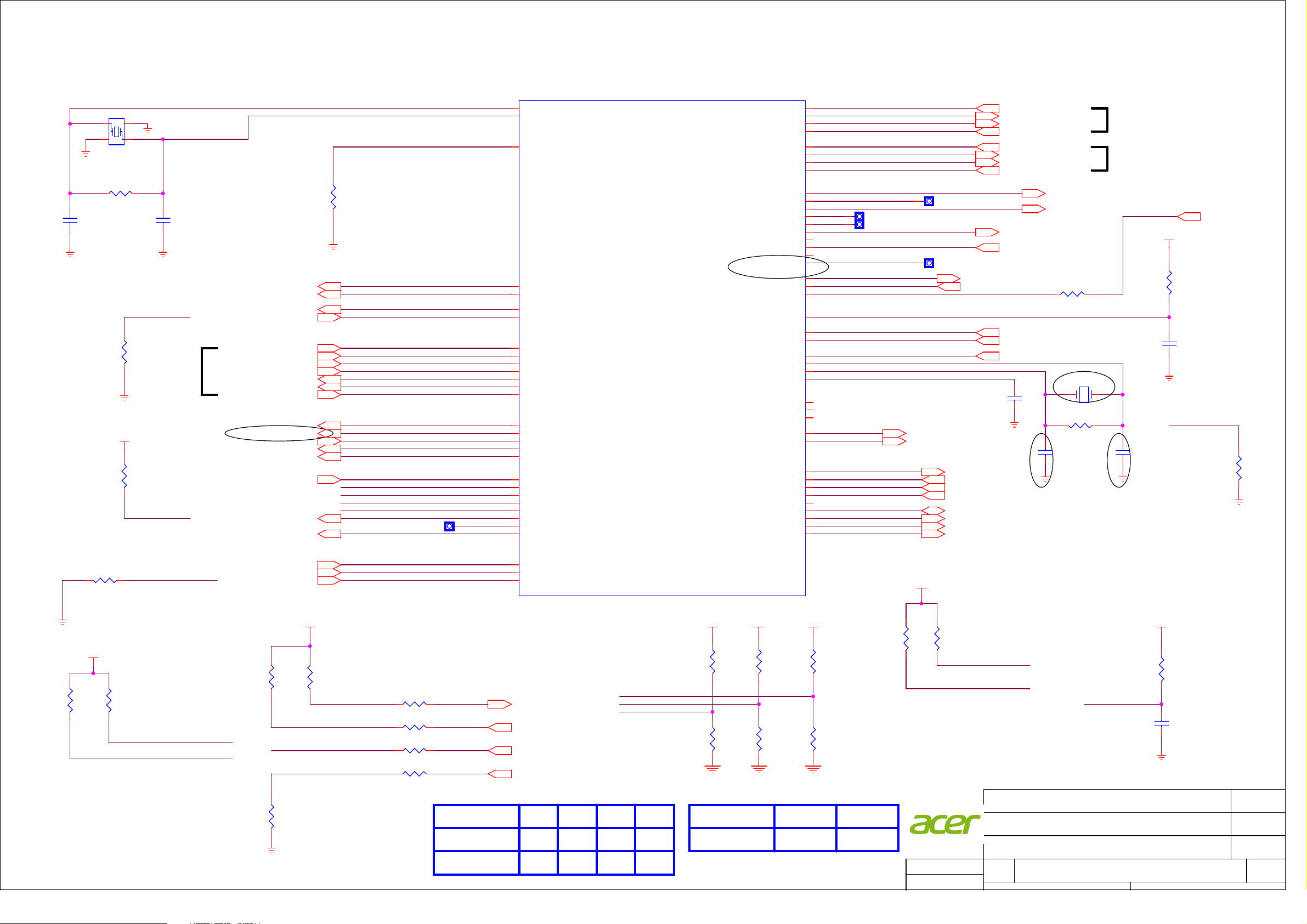

SOC: MEMORY

PLACE CLOSE TO SOC

+VDDQ_DDR

R301

4.7K PR 0402

R302

4.7K PR 0402

C301

0.1UF C 0402 10V

?

U1A

M0_MA016,18

M0_MA116,18

M0_MA216,18

M0_MA316,18

M0_MA416,18

M0_MA516,18

M0_MA616,18

M0_MA716,18

M0_MA816,18

M0_MA916,18

M0_MA1016,18

M0_MA1116,18

M0_MA1216,18

M0_MA1316,18

M0_MA1416,18

M0_DM016

M0_DM116

M0_DM216

M0_DM316

M0_DM417

M0_DM517

M0_DM617

M0_DM717

M0_RASB16,18

M0_CASB16,18

M0_WEB16,18

M0_BS016,18

M0_BS116,18

M0_BS216,18

M0_CS0_B16,18

M0_CKE016,18

M0_ODT016,18

M0_CLK0_DP16,18

M0_CLK0_DN16,18

M0_DRAMRSTB16,18

DDR3_DRAM_PWROK13

DDR3_VCCA_PW ROK13

DDR3_SOC_ODTPU

DDR3_SOC_DQPU

DDR3_SOC_CMDPU

R303

162ohm 1% R 0402

R304

R305

29.4ohm 1% R 0402

23.2ohm 1% R 0402

M24

DRAM0_MA[00]

L23

DRAM0_MA[01]

N23

DRAM0_MA[02]

M20

DRAM0_MA[03]

M22

DRAM0_MA[04]

L22

DRAM0_MA[05]

K24

DRAM0_MA[06]

N25

DRAM0_MA[07]

J25

DRAM0_MA[08]

H24

DRAM0_MA[09]

N20

DRAM0_MA[10]

K25

DRAM0_MA[11]

M25

DRAM0_MA[12]

M23

DRAM0_MA[13]

H25

DRAM0_MA[14]

K23

DRAM0_MA[15]

A20

DRAM0_DM[0]

D21

DRAM0_DM[1]

D25

DRAM0_DM[2]

F19

DRAM0_DM[3]

AC24

DRAM0_DM[4]

V24

DRAM0_DM[5]

Y22

DRAM0_DM[6]

T23

DRAM0_DM[7]

N22

DRAM0_RAS#

P20

DRAM0_CAS#

P21

DRAM0_WE#

M21

DRAM0_BS[0]

N19

DRAM0_BS[1]

K22

DRAM0_BS[2]

P22

DRAM0_CS[0]#

P23

DRAM0_CS[2]#

G22

DRAM0_CKE[0]

G23

DRAM0_CKE[1]

F23

DRAM0_CKE[2]

F22

DRAM0_CKE[3]

P24

DRAM0_ODT[0]

P25

DRAM0_ODT[2]

J23

DRAM0_CKP[0]

J22

DRAM0_CKN[0]

K20

DRAM0_CKP[2]

K21

DRAM0_CKN[2]

U19

DRAM0_DRAMRST#

AD20

DRAM_VREF

AC20

DRAM_VDD_S4_PWROK

AB20

DRAM_CORE_PWROK

AE22

DRAM_RCOMP[2]

AE20

DRAM_RCOMP[1]

AE21

DRAM_RCOMP[0]

Z3735F

REV = 2.0

1 OF 9

VLV2_CR

DRAM0_DQ[00]

DRAM0_DQ[01]

DRAM0_DQ[02]

DRAM0_DQ[03]

DRAM0_DQ[04]

DRAM0_DQ[05]

DRAM0_DQ[06]

DRAM0_DQ[07]

DRAM0_DQ[08]

DRAM0_DQ[09]

DRAM0_DQ[10]

DRAM0_DQ[11]

DRAM0_DQ[12]

DRAM0_DQ[13]

DRAM0_DQ[14]

DRAM0_DQ[15]

DRAM0_DQ[16]

DRAM0_DQ[17]

DRAM0_DQ[18]

DRAM0_DQ[19]

DRAM0_DQ[20]

DRAM0_DQ[21]

DRAM0_DQ[22]

DRAM0_DQ[23]

DRAM0_DQ[24]

DRAM0_DQ[25]

DRAM0_DQ[26]

DRAM0_DQ[27]

DRAM0_DQ[28]

DRAM0_DQ[29]

DRAM0_DQ[30]

DRAM0_DQ[31]

DRAM0_DQ[32]

DRAM0_DQ[33]

DRAM0_DQ[34]

DRAM0_DQ[35]

DRAM0_DQ[36]

DRAM0_DQ[37]

DRAM0_DQ[38]

DRAM0_DQ[39]

DRAM0_DQ[40]

DRAM0_DQ[41]

DRAM0_DQ[42]

DRAM0_DQ[43]

DRAM0_DQ[44]

DRAM0_DQ[45]

DRAM0_DQ[46]

DRAM0_DQ[47]

DRAM0_DQ[48]

DRAM0_DQ[49]

DRAM0_DQ[50]

DRAM0_DQ[51]

DRAM0_DQ[52]

DRAM0_DQ[53]

DRAM0_DQ[54]

DRAM0_DQ[55]

DRAM0_DQ[56]

DRAM0_DQ[57]

DRAM0_DQ[58]

DRAM0_DQ[59]

DRAM0_DQ[60]

DRAM0_DQ[61]

DRAM0_DQ[62]

DRAM0_DQ[63]

DRAM0_DQSP[0]

DRAM0_DQSN[0]

DRAM0_DQSP[1]

DRAM0_DQSN[1]

DRAM0_DQSP[2]

DRAM0_DQSN[2]

DRAM0_DQSP[3]

DRAM0_DQSN[3]

DRAM0_DQSP[4]

DRAM0_DQSN[4]

DRAM0_DQSP[5]

DRAM0_DQSN[5]

DRAM0_DQSP[6]

DRAM0_DQSN[6]

DRAM0_DQSP[7]

DRAM0_DQSN[7]

D18

B18

A21

C18

A22

B20

A18

B22

C20

D23

E19

E23

D22

E22

E20

D20

E25

A23

C23

F25

B24

D24

B23

F24

F20

F21

G20

H23

G21

J21

J20

H22

AD24

AB25

Y24

AE23

AA25

AC23

AD23

Y25

V23

T24

W22

W23

R23

R22

V22

T25

AB22

AC22

Y19

AD22

AA22

Y23

Y20

Y21

T22

T20

W20

V20

U21

W21

U20

T21

D19

C19

C22

C21

C24

C25

H20

H19

AC25

AB24

V25

U25

AB23

AA23

U22

U23

M0_DATA0 16

M0_DATA1 16

M0_DATA2 16

M0_DATA3 16

M0_DATA4 16

M0_DATA5 16

M0_DATA6 16

M0_DATA7 16

M0_DATA8 16

M0_DATA9 16

M0_DATA10 16

M0_DATA11 16

M0_DATA12 16

M0_DATA13 16

M0_DATA14 16

M0_DATA15 16

M0_DATA16 16

M0_DATA17 16

M0_DATA18 16

M0_DATA19 16

M0_DATA20 16

M0_DATA21 16

M0_DATA22 16

M0_DATA23 16

M0_DATA24 16

M0_DATA25 16

M0_DATA26 16

M0_DATA27 16

M0_DATA28 16

M0_DATA29 16

M0_DATA30 16

M0_DATA31 16

M0_DATA32 17

M0_DATA33 17

M0_DATA34 17

M0_DATA35 17

M0_DATA36 17

M0_DATA37 17

M0_DATA38 17

M0_DATA39 17

M0_DATA40 17

M0_DATA41 17

M0_DATA42 17

M0_DATA43 17

M0_DATA44 17

M0_DATA45 17

M0_DATA46 17

M0_DATA47 17

M0_DATA48 17

M0_DATA49 17

M0_DATA50 17

M0_DATA51 17

M0_DATA52 17

M0_DATA53 17

M0_DATA54 17

M0_DATA55 17

M0_DATA56 17

M0_DATA57 17

M0_DATA58 17

M0_DATA59 17

M0_DATA60 17

M0_DATA61 17

M0_DATA62 17

M0_DATA63 17

M0_DQS0_DP 16

M0_DQS0_DN 16

M0_DQS1_DP 16

M0_DQS1_DN 16

M0_DQS2_DP 16

M0_DQS2_DN 16

M0_DQS3_DP 16

M0_DQS3_DN 16

M0_DQS4_DP 17

M0_DQS4_DN 17

M0_DQS5_DP 17

M0_DQS5_DN 17

M0_DQS6_DP 17

M0_DQS6_DN 17

M0_DQS7_DP 17

M0_DQS7_DN 17

Approved:

Approved:

Approved:

Designer:

Designer:

Designer:

Project:

Project:

Project:

Title:

Title:

Title:

Size:

Size:

Size:

Document Number:

Document Number:

Document Number:

Date:

Date:

Date:

Acer Inc.

Acer Inc.

Acer Inc.

Ducati2 BAYt_CR

Ducati2 BAYt_CR

Ducati2 BAYt_CR

03_SOC_ MEMORY

03_SOC_ MEMORY

03_SOC_ MEMORY

{Doc} 0.1C

{Doc} 0.1C

{Doc} 0.1C

Friday, July 25, 2014 393

Friday, July 25, 2014 393

Friday, July 25, 2014 393

Sheet:

Sheet:

Sheet:

Drawing Rule

Drawing Rule

Drawing Rule

Allegro Lib Ver

Allegro Lib Ver

Allegro Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

Rev

Rev

Rev

of

of

of

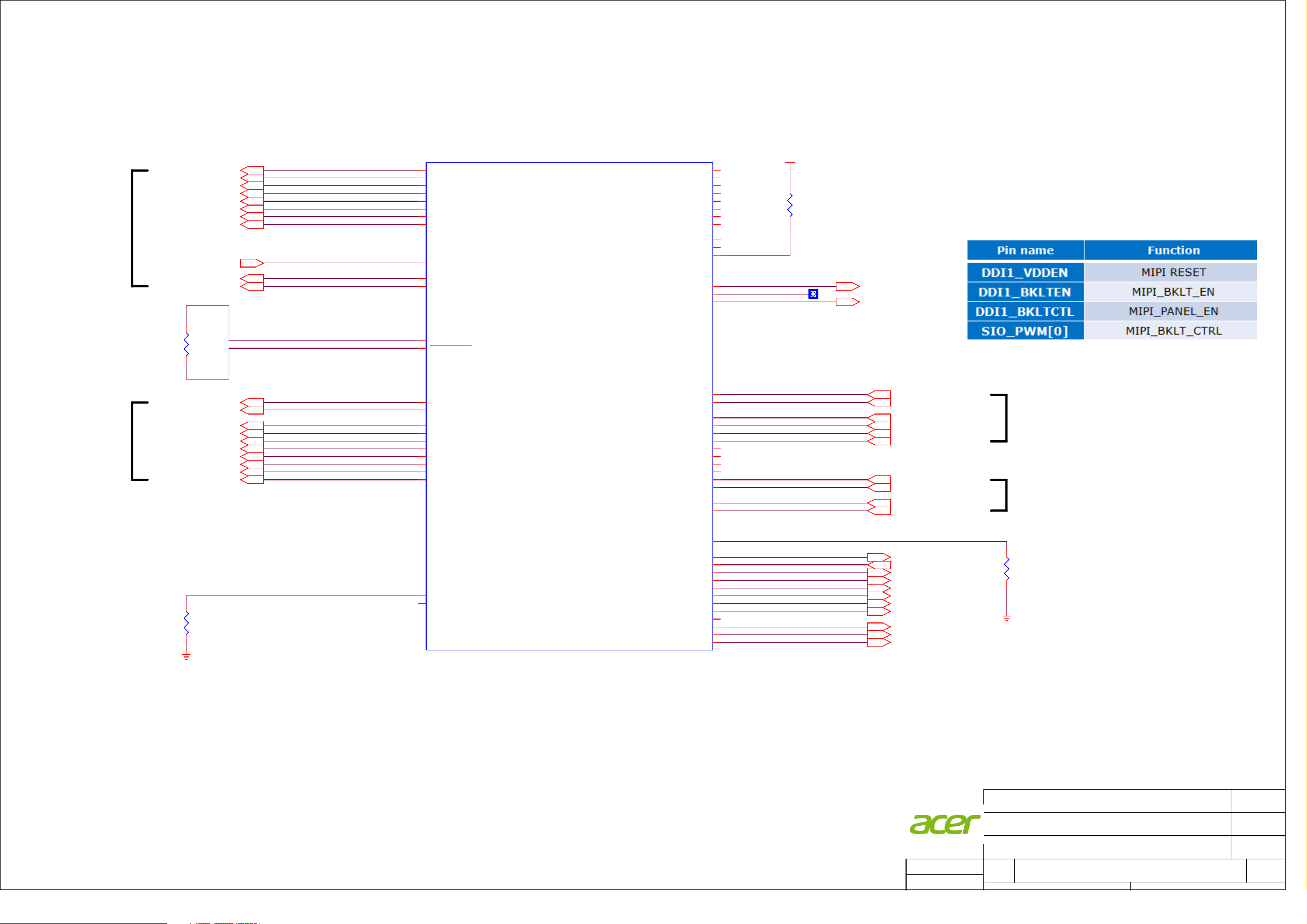

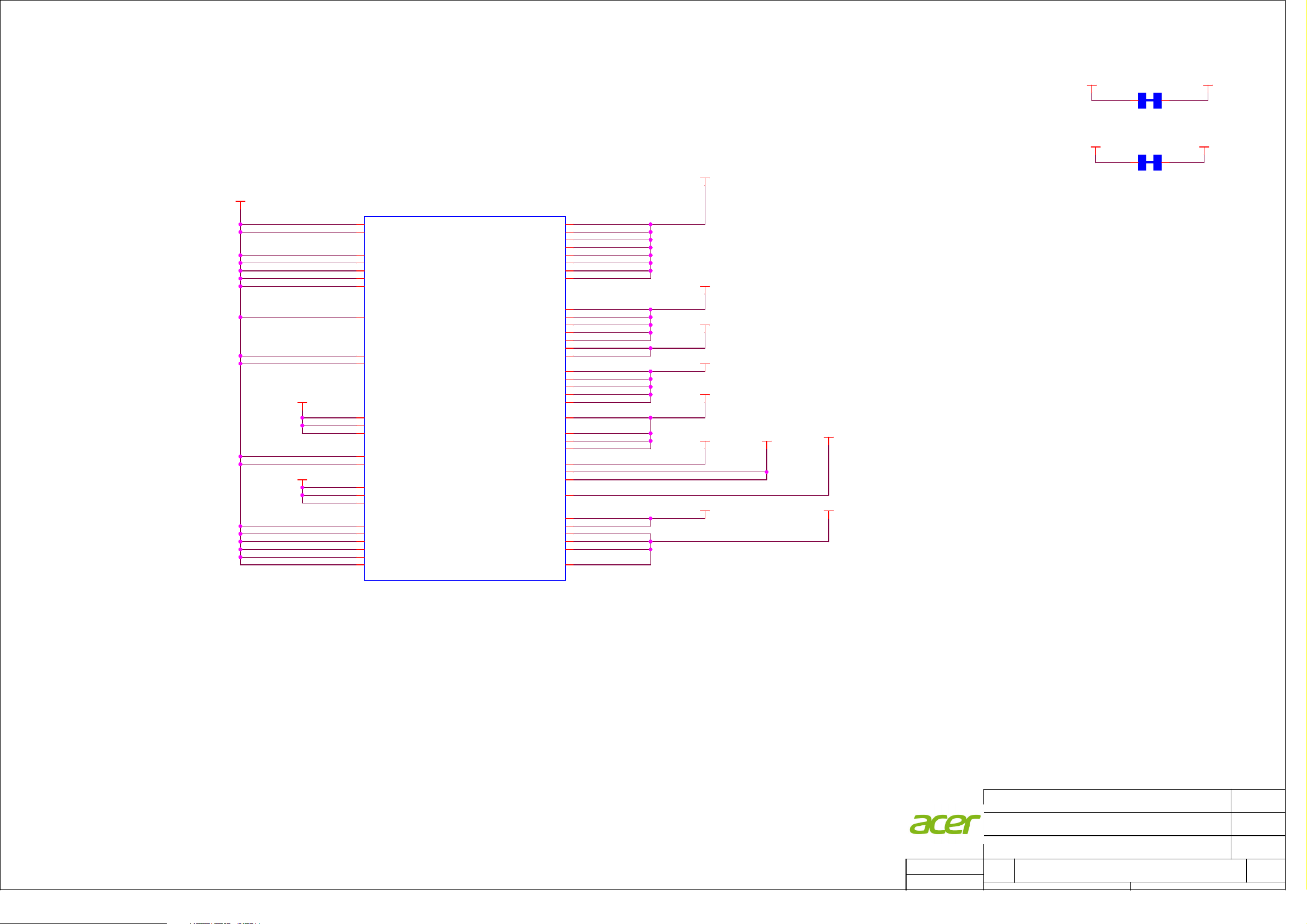

SOC: DISPLAY & CAMERA

HDMI

MIPI DSI

?

U1B

DDI0_TX0_DP32

DDI0_TX0_DN32

DDI0_TX1_DP32

DDI0_TX1_DN32

DDI0_TX2_DP32

DDI0_TX2_DN32

DDI0_TX3_DP32

DDI0_TX3_DN32

DDI0_HPD_N32

DDI0_DDC_SDA32

DDI0_DDC_SCL32

R401

DDI0_PLLOBS_DP

DDI0_PLLOBS_DN

402 PR 0402

MDSI_A_CLKN25

MDSI_A_CLKP25

MDSI_A_DN_025

MDSI_A_DP_025

MDSI_A_DN_125

MDSI_A_DP_125

MDSI_A_DN_225

MDSI_A_DP_225

MDSI_A_DN_325

MDSI_A_DP_325

AB4

DDI0_TXP[0]

AB3

DDI0_TXN[0]

AB2

DDI0_TXP[1]

AA1

DDI0_TXN[1]

Y2

DDI0_TXP[2]

Y1

DDI0_TXN[2]

Y4

DDI0_TXP[3]

Y3

DDI0_TXN[3]

E14

DDI0_HPD

D13

DDI0_DDCDATA

C13

DDI0_DDCCLK

AA3

DDI_RCOMP_P

AA4

DDI_RCOMP

P5

MDSI_A_CLKN

P4

MDSI_A_CLKP

T4

MDSI_A_DN[0]

T3

MDSI_A_DP[0]

R4

MDSI_A_DN[1]

R3

MDSI_A_DP[1]

T6

MDSI_A_DN[2]

T5

MDSI_A_DP[2]

P6

MDSI_A_DN[3]

N6

MDSI_A_DP[3]

2 OF 9

VLV2_CR

DDI1_TXP[0]

DDI1_TXN[0]

DDI1_TXP[1]

DDI1_TXN[1]

DDI1_TXP[2]

DDI1_TXN[2]

DDI1_TXP[3]

DDI1_TXN[3]

DDI1_AUXP

DDI1_AUXN

DDI1_HPD

DDI1_VDDEN

DDI1_BKLTEN

DDI1_BKLTCTL

MCSI1_CLKN

MCSI1_CLKP

MCSI1_DN[0]

MCSI1_DP[0]

MCSI1_DN[1]

MCSI1_DP[1]

MCSI1_DN[2]

MCSI1_DP[2]

MCSI1_DN[3]

MCSI1_DP[3]

MCSI2_CLKN

MCSI2_CLKP

MCSI2_DN[0]

MCSI2_DP[0]

U7

U6

V5

V4

T1

U1

U4

U5

Y5

W6

B12

B14

A14

A13

M5

M6

P3

P2

M1

N1

M4

M3

L3

L4

K4

K5

K6

J6

DDI1_HPD

+V1P8A_SOC

DDI1_BKLTEN

R402

100K R 0402

1

TP3650 TEST_POINT_20

LCM_RST_N 25

DDI1_BKLTCTL 25

MCSI_1_CLK_DN 23

MCSI_1_CLK_DP 23

MCSI_1_DATA0_DN 23

MCSI_1_DATA0_DP 23

MCSI_1_DATA1_DN 23

MCSI_1_DATA1_DP 23

MCSI_2_CLK_DN 23

MCSI_2_CLK_DP 23

MCSI_2_DATA_DN 23

MCSI_2_DATA_DP 23

5M CAMERA

2M CAMERA

R404

150 PR 0402

MDSI_COMP

F17

P1

MDSI_RCOMP

MDSI_A_TE

Z3735F

REV = 2.0

MCSI_RCOMP

GPIO_S0_NC[15]

GPIO_S0_NC[16]

GPIO_S0_NC[17]

GPIO_S0_NC[18]

GPIO_S0_NC[19]

GPIO_S0_NC[20]

GPIO_S0_NC[21]

GPIO_S0_NC[22]

GPIO_S0_NC[23]

GPIO_S0_NC[24]

GPIO_S0_NC[25]

GPIO_S0_NC[26]

K1

D17

B16

C15

C14

C17

C16

D16

D15

D14

F18

E17

E16

MCSI_COMP

CHG_DISABLE 14

MEMORY_SEL0 5

CAM1_RESET_N 23

CAM2_RESET_N 23

CODEC_RESET 27

CAMERA_1_VCM_PD_N 23

CAMERA_1_PD_N 23

CAMERA_2_PD 23

BT_DEV_WAKE 34

BT_REG_ON 34

TOUCH_RESET_N 24

Project:

Project:

Project:

Title:

Title:

Title:

Size:

Size:

Approved:

Approved:

Approved:

Designer:

Designer:

Designer:

Size:

Date:

Date:

Date:

R403

150 PR 0402

Acer Inc.

Acer Inc.

Acer Inc.

Ducati2 BAYt_CR

Ducati2 BAYt_CR

Ducati2 BAYt_CR

04_SOC_ DISPLAY & CAMERA

04_SOC_ DISPLAY & CAMERA

04_SOC_ DISPLAY & CAMERA

Document Number:

Document Number:

Document Number:

Friday, July 25, 2014 394

Friday, July 25, 2014 394

Friday, July 25, 2014 394

{Doc} 0.1C

{Doc} 0.1C

{Doc} 0.1C

Sheet:

Sheet:

Sheet:

Drawing Rule

Drawing Rule

Drawing Rule

Allegro Lib Ver

Allegro Lib Ver

Allegro Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

Rev

Rev

Rev

of

of

of

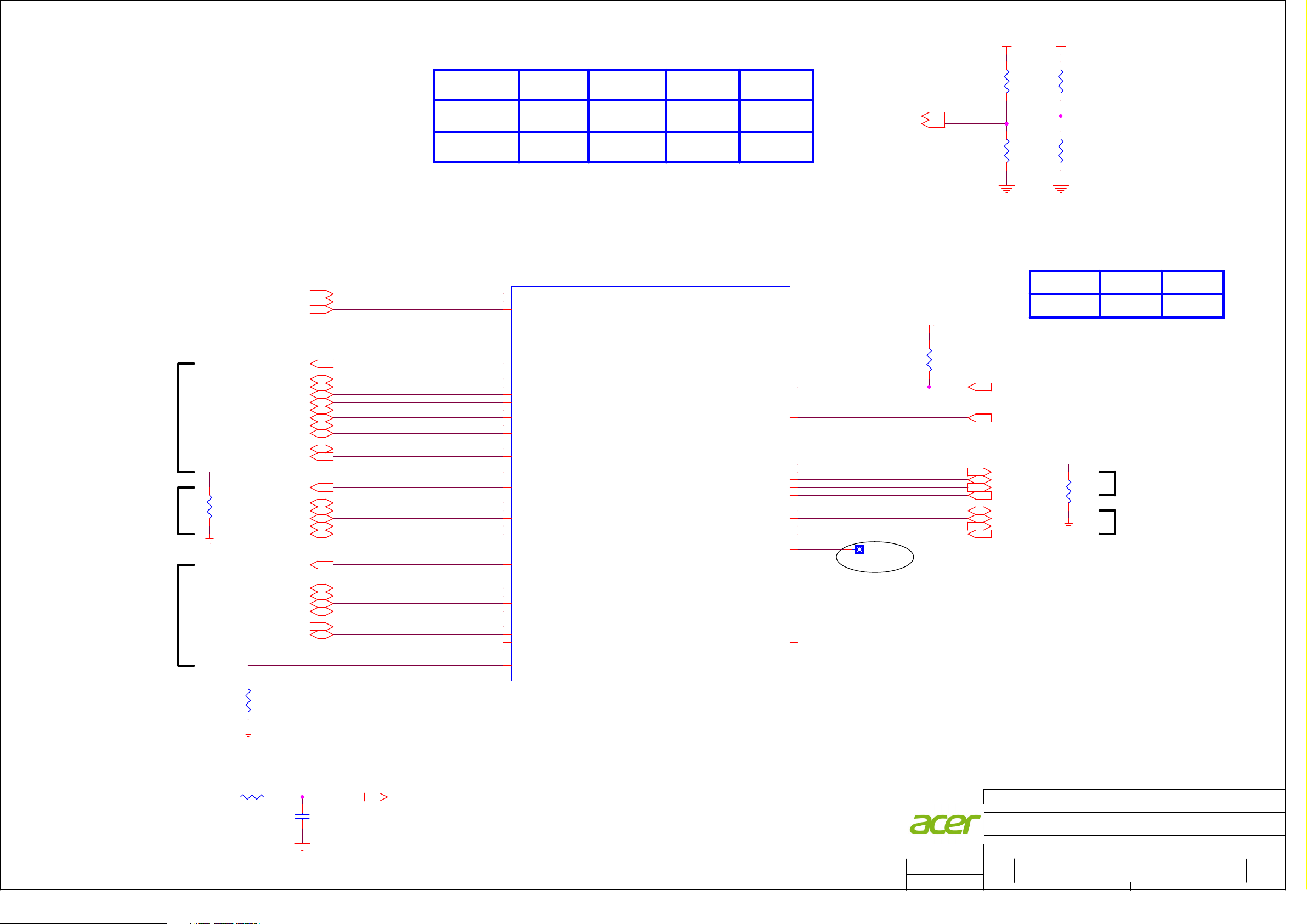

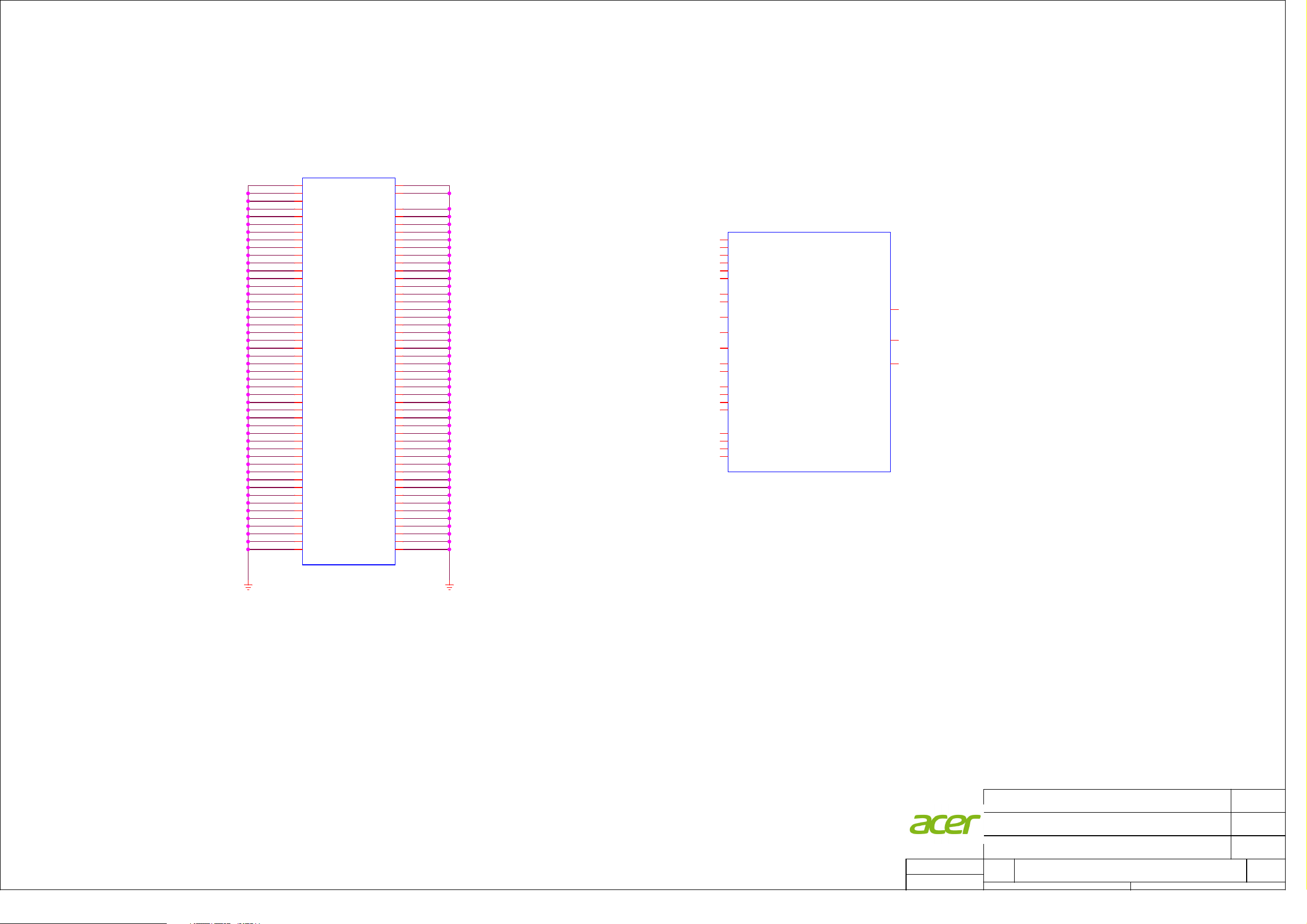

SOC: STORAGE & I2S

A Build: sku1 & sku4

B/C Build: sku1 & sku2

Pre-MP Build: sku1 & sku2

1G Hynix

(sku1)

1G Kingston

(sku2)

2G Hynix

(sku3)

2G Kingston

(sku4)

+V1P8A_SOC +V1P8A_SOC

R502

R503

@

eMMC

WLAN

SD CARD

R501

49.9 PR 0402

GPI_VOLUMEDOWN31

GPI_VOLUMEUP31

MEMORY_SEL15

EMMC_CLK21

EMMC_DATA_021

EMMC_DATA_121

EMMC_DATA_221

EMMC_DATA_321

EMMC_DATA_421

EMMC_DATA_521

EMMC_DATA_621

EMMC_DATA_721

EMMC_CMD21

EMMC_RESET_N21

SDIO2_CLK

SDIO2_DATA_034

SDIO2_DATA_134

SDIO2_DATA_234

SDIO2_DATA_334

SDIO2_CMD34

SDMMC3_CLK33

SDMMC3_D033

SDMMC3_D133

SDMMC3_D233

SDMMC3_D333

SDMMC3_CD_N5,33

SDMMC3_CMD33

R507

EMMC_RCOMP

SDMMC3_RCOMP

MEMORY_SEL0

AB6

AA6

Y6

AE8

AB7

AC7

AC8

AB9

AA9

AA8

Y8

Y7

AB8

AD8

AE6

AE9

AB11

AB10

AC10

AD10

AC9

AC12

AC11

AB13

AA12

AA13

Y12

AB12

Y9

AA10

AE10

Low

High

?

U1C

GPIO_S0_SC[00]

GPIO_S0_SC[01]

GPIO_S0_SC[02]

MMC1_CLK

MMC1_D[0]

MMC1_D[1]

MMC1_D[2]

MMC1_D[3]

MMC1_D[4]

MMC1_D[5]

MMC1_D[6]

MMC1_D[7]

MMC1_CMD

MMC1_RST#

MMC1_RCOMP

SD2_CLK

SD2_D[0]

SD2_D[1]

SD2_D[2]

SD2_D[3]_CD#

SD2_CMD

SD3_CLK

SD3_D[0]

SD3_D[1]

SD3_D[2]

SD3_D[3]

SD3_CD#

SD3_CMD

SD3_1P8EN

SD3_PWREN#

SD3_RCOMP

Z3735F

REV = 2.0

Low

Low

3 OF 9

VLV2_CR

High

HighMEMORY_SEL1

High

Low

GPIO_S0_SC[03]

GPIO_S0_SC[07]

AUDIO_RCOMP

I2S0_CLK

I2S0_L_R

I2S0_DATAOUT

I2S0_DATAIN

I2S1_CLK

I2S1_L_R

I2S1_DATAOUT

I2S1_DATAIN

GPIO_S0_SC[65]

PROCHOT#

AC5

AA5

AE14

Y16

Y14

AA14

Y13

AC13

AC14

AB14

Y10

U17

F16

MEMORY_SEL04

MEMORY_SEL15

TOUCH_ID

AUDIO_RCOMP

1

TP3642 TEST_POINT_20

TP on bottom side

+V1P8A_SOC

R3682

10K PR 0402

R504

@

10K PR 0402

Vendor

TOUCH_ID

100K PR 0402

TOUCH_ID 24

SDMMC3_CD_N 5,33

I2S_0_CLK 27

I2S_0_FS 27

I2S_0_TXD 27

I2S_0_RXD 27

I2S_1_CLK 34

I2S_1_FS 34

I2S_1_TXD 34

I2S_1_RXD 34

10K PR 0402

R505

10K PR 0402

SOE O-Film

1 0

R506

CODEC

49.9 PR 0402

WLAN

49.9 PR 0402

R3619 0 R 0402

SDIO2_CLK_SSDIO2_CLK

C3632

22pF C 0402 50V

SDIO2_CLK_S 34

Approved:

Approved:

Approved:

Designer:

Designer:

Designer:

Project:

Project:

Project:

Title:

Title:

Title:

Size:

Size:

Size:

Document Number:

Document Number:

Document Number:

Date:

Date:

Date:

Acer Inc.

Acer Inc.

Acer Inc.

Ducati2 BAYt_CR

Ducati2 BAYt_CR

Ducati2 BAYt_CR

05_SOC_ STORAGE & I2S

05_SOC_ STORAGE & I2S

05_SOC_ STORAGE & I2S

{Doc} 0.1C

{Doc} 0.1C

{Doc} 0.1C

Friday, July 25, 2014 395

Friday, July 25, 2014 395

Friday, July 25, 2014 395

Sheet:

Sheet:

Sheet:

Drawing Rule

Drawing Rule

Drawing Rule

Allegro Lib Ver

Allegro Lib Ver

Allegro Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

Rev

Rev

Rev

of

of

of

SOC: USB & I2C

Micro USB

?

U1D

USB_ULPI_0_CLK20

USB_ULPI_0_DATA020

USB_ULPI_0_DATA120

USB_ULPI_0_DATA220

USB_ULPI_0_DATA320

USB_ULPI_0_DATA420

USB_ULPI_0_DATA520

USB_ULPI_0_DATA620

USB_ULPI_0_DATA720

USB_ULPI_0_DIR20

USB_ULPI_0_NXT20

USB_ULPI_0_STP20

USB_ULPI_0_REFCLK20

USB2_P1_DP20

USB2_P1_DN20

WL_REG_ON34

+V1P8A_SOC

R3642

10K R 0402

USB_RCOMP

R601

N3

USB_ULPI_CLK

J5

USB_ULPI_DATA[0]

H5

USB_ULPI_DATA[1]

J4

USB_ULPI_DATA[2]

H1

USB_ULPI_DATA[3]

H2

USB_ULPI_DATA[4]

J3

USB_ULPI_DATA[5]

J1

USB_ULPI_DATA[6]

K2

USB_ULPI_DATA[7]

K3

USB_ULPI_DIR

N4

USB_ULPI_NXT

M2

USB_ULPI_STP

F10

USB_ULPI_REFCLK

G4

USB_DP[0]

G3

USB_DN[0]

H4

USB_DP[1]

H3

USB_DN[1]

F13

USB_OC[0]#

F14

USB_OC[1]#

F1

USB_RCOMPO

Z3735F

REV = 2.0

4 OF 9

VLV2_CR

USB_REXT[1]

USB_REXT[0]

GPIO_RCOMP

GPIO_S0_SC[57]

GPIO_S0_SC[61]

GPIO_S0_SC[54]

SIO_I2C0_DATA

SIO_I2C0_CLK

SIO_I2C1_DATA

SIO_I2C1_CLK

SIO_I2C2_DATA

SIO_I2C2_CLK

SIO_I2C3_DATA

SIO_I2C3_CLK

SIO_I2C4_DATA

SIO_I2C4_CLK

D1_I2C_DATA

D1_I2C_CLK

A8

C1

A4

AC6

AD6

AE5

AE12

AD12

AE13

AD14

AB15

AC15

AB16

AC16

AD16

AE16

AA17

AB17

USB3_REXT_P1

USB3_REXT_P0

GPIO_RCOMP

UART3_DEBUG_TXD 28,36

UART3_DEBUG_RXD 28,36

USB_ULPI_0_CS 20

I2C_0_SDA 14

I2C_0_SCL 14

I2C_1_SDA 23,27,36

I2C_1_SCL 23,27,36

I2C_2_SDA 25,26

I2C_2_SCL 25,26

I2C_3_SDA 24

I2C_3_SCL 24

I2C_4_SDA 13

I2C_4_SCL 13

R602

49.9 PR 0402

R603

1.24K PR 0402

R604

1.24K PR 0402

Charger, USB Switch

Codec, Front/Rear Camera, XDP

Gyro/G Sensor, LCD (reserved)

Touch

PMIC

USB_ULPI_0_CS

R605

45.3 PR 0402

RCOMP: PLACE AS CLOSE AS POSSIBLE TO SOC. PREFERABLY TRACE RESISTANCE < 0.5OHM

+V1P8A_SOC

R609

I2C_0_SCL

I2C_0_SDA

I2C_1_SCL

I2C_1_SDA

I2C_2_SCL

I2C_2_SDA

I2C_3_SCL

I2C_3_SDA

I2C_4_SCL

I2C_4_SDA

R606

2.2K PR 0402

R607

2.2K PR 0402

R608

2.2K PR 0402

R610

2.2K PR 0402

2.2K PR 0402

R611

2.2K PR 0402

R612

1K PR 0402

R613

1K PR 0402

R614

2.2K PR 0402

R615

2.2K PR 0402

Approved:

Approved:

Approved:

Designer:

Designer:

Designer:

Project:

Project:

Project:

Title:

Title:

Title:

Size:

Size:

Size:

Document Number:

Document Number:

Document Number:

Date:

Date:

Date:

10K R 0402

Acer Inc.

Acer Inc.

Acer Inc.

Ducati2 BAYt_CR

Ducati2 BAYt_CR

Ducati2 BAYt_CR

06_SOC_ USB & I2C

06_SOC_ USB & I2C

06_SOC_ USB & I2C

{Doc} 0.1C

{Doc} 0.1C

{Doc} 0.1C

Friday, July 25, 2014 396

Friday, July 25, 2014 396

Friday, July 25, 2014 396

Sheet:

Sheet:

Sheet:

Drawing Rule

Drawing Rule

Drawing Rule

Allegro Lib Ver

Allegro Lib Ver

Allegro Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

Rev

Rev

Rev

of

of

of

SOC: PMU & DFX & CLOCK & UART & SUS

1 4

G

32

G

X701

25MHz 10pF

R701 1M PR 0402

C701

15pF C 0402 50V

XDP_H_TRST_N

R705

+V1P8A_SOC

R707

@

PLACE WITHIN 0.25'

XDP

51 PR 0402

51 PR 0402

XDP_H_TDO

C3707

15pF C 0402 50V

PLT_CLK0_CAM123

PLT_CLK1_CAM223

CODEC_MCLK27

HW_BOARD_ID2

XDP_H_TCK36

XDP_H_TRST_N36

XDP_H_TMS36

XDP_H_TDI36

XDP_H_TDO36

XDP_H_PRDY_N36

XDP_H_PREQ_N36

SPI_NOR_CS0_N19

UART3_DEBUG_SW28

SPI_NOR_MISO19

SPI_NOR_MOSI19

SPI_NOR_CLK19

PMIC_INT13

WIFI_32K_CLK34

GPS_32K_CLK35

FROM XDP CONN

HW_BOARD_ID0

R708 51 PR 0402

XDP_H_TCK

HW_BOARD_ID1

CHG_STAT14

R702

4.02K PR 0402

XTAL25_IN

XTAL25_OUT

ICLK_ICOMP

GPIO_SUS1

GPIO_SUS2

GPIO_SUS3

GPIO_SUS4

?

U1E

V3

ICLK_OSCIN

V2

ICLK_OSCOUT

V1

ICLK_ICOMP

PMC_PWRBTN# must have internal pull-up

AB5

PMC_PLT_CLK[0]

AE4

PMC_PLT_CLK[1]

AD4

PMC_PLT_CLK[3]

AD2

PMC_PLT_CLK[4]

E5

TAP_TCK

G6

TAP_TRST#

H6

TAP_TMS

F4

TAP_TDI

F6

TAP_TDO

F7

TAP_PRDY#

F5

TAP_PREQ#

C12

PCU_SPI_CS[0]#

D12

PCU_SPI_CS[1]#

E13

PCU_SPI_MISO

E12

PCU_SPI_MOSI

F12

PCU_SPI_CLK

E9

GPIO_S5[00]

D7

GPIO_S5[01]

F9

GPIO_S5[02]

E8

GPIO_S5[03]

F8

GPIO_S5[04]

D6

TP3613TEST_POINT_20

1

D4

D5

D3

E6

C5

GPIO_S5[05]

GPIO_S5[06]

GPIO_S5[07]

GPIO_S5[08]

GPIO_S5[09]

GPIO_S5[10]

5 OF 9

VLV2_CR

SIO_UART1_RXD

SIO_UART1_TXD

SIO_UART1_RTS#

SIO_UART1_CTS#

SIO_UART2_RXD

SIO_UART2_TXD

SIO_UART2_RTS#

SIO_UART2_CTS#

PMC_SUSPWRDNACK

PMC_SUSCLK_0

PMC_SLP_S0IX#

PMC_SLP_S4#

PMC_SLP_S3#

USB_ULPI_RST#

PMC_ACPRESENT

GPIO_S5[15]

PMC_BATLOW#

PMC_PWRBTN#

PMC_PLTRST#

GPIO_S5[17]

PMC_SUS_STAT#

ILB_RTC_TEST#

PMC_RSMRST#

PMC_CORE_PWROK

ILB_RTC_RST#

ILB_RTC_X1

ILB_RTC_X2

ILB_RTC_EXTPAD

SVID_ALERT#

SVID_DATA

SVID_CLK

SIO_PWM[0]

SIO_PWM[1]

GPIO_S5[22]

GPIO_S5[23]

GPIO_S5[24]

GPIO_S5[25]

GPIO_S5[26]

GPIO_S5[27]

GPIO_S5[28]

GPIO_S5[29]

GPIO_S5[30]

AB19

AC19

AC18

AB18

AD18

AE18

AC17

AE17

D10

A9

C7

D8

C8

C6

B8

B10

C9

A10

B6

D9

E10

E3

F3

F2

E4

D1

E1

D2

C10

C11

D11

AA16

Y17

A6

B4

A3

B3

B2

C2

C3

C4

A5

1

TP706 TEST_POINT_20

1

TP707 TEST_POINT_20

PMC_SUS_STAT#

RTEST_N

RTC_X1

RTC_X2

BVCCRTC_EXTPAD

1

TP702 TEST_POINT_20

1

TP705 TEST_POINT_20

PLTRST_N 13,36

BT_HOST_WAKE 34

MIPI_PWM_BKLT_EN 29

SOC_VIBRA_PWM 31

Changed to 8pF (follow FHD)

GPS_WAKEUP 35

LCM_ID1 25

LCM_ID 25

GYRO_INT1 26

JACK_DET_N_R2 28

LCM_3P3V_EN 25

LCM_1P8V_EN 25

BUCK_3P3V_EN

+V1P8A_SOC

UART_1_BT_RXD 34

UART_1_BT_TXD 34

UART_1_BT_RTS 34

UART_1_BT_CTS 34

UART_2_GPS_RXD 35

UART_2_GPS_TXD 35

UART_2_GPS_RTS 35

UART_2_GPS_CTS 35

SUSPWRDNACK 13

PMU_SLP_S0IX_N 13,15,18,32

USB_ULPI_RESET_N 20

COMBO_WLAN_IRQ 34

R704 0 R 0402

RSMRST_N 13,36

COREPWROK 13,36

SRTCRST_N 36

C704

R706 10M PR 0402

0.1uF C 0402 16V

X702

32.768KHz 7pF

C706

8pF C 0402 50V

WLAN

GPS

+VRTC

12

Changed to Q-SC20S0322070AAAF

(follow FHD)

C705

7pF C 0402 50V

Changed to 7pF (follow FHD)

USB_ID_CONN 20,30

R703

20K PR 0402

C703

1uF C 0402 10V

RSMRST_N

R3644

100K R 0402

+V1P8A_SOC

R715

51 PR 0402

R716

51 PR 0402

+V1P8A_SOC

10K PR 0402

51 PR 0402

R712

10K R 0402

GPIO_SUS2

GPIO_SUS3

GPIO_SUS4

GPIO_SUS1

R3683

XDP_H_TDI

XDP_H_TMS

R723

@

POPOLATE ONLY FOR DEBUG VERSION

CHG_INT_N requires 10K pull-up

JTAG2_TMS

R717 0 R 0402

JTAG2_TDI

R718 0 R 0402

JTAG2_TDO

R721 0 R 0402

JTAG2_TCK

R722 0 R 0402

HW_Board_ID0

HW_Board_ID1

Z3735F

REV = 2.0

CHG_INT_N 14

TOUCH_INT_N 24

AUDIO_INT 27

USBMUX_SEL 20

V0.1

A/B C Pre-MP

Low High

Low

V0.2 V0.3 V0.4

Low High

Low

High High

HW_BOARD_ID0

HW_BOARD_ID1

HW_BOARD_ID2

R3680

@

10K PR 0402

R3681

@

10K PR 0402

HW_Board_ID2

+V1P8A_SOC+V1P8A_SOC+V1P8A_SOC

R709

10K PR 0402

R719

10K PR 0402

R710

@

10K PR 0402

R720

10K PR 0402

Android Windows

Low High

@

Approved:

Approved:

Approved:

Designer:

Designer:

Designer:

R730

100K PR 0402

R713

100K PR 0402

LCM_ID

LCM_ID1

Project:

Project:

Project:

Title:

Title:

Title:

Size:

Size:

Size:

Date:

Date:

Date:

SRTCRST_N

Acer Inc.

Acer Inc.

Acer Inc.

Ducati2 BAYt_CR

Ducati2 BAYt_CR

Ducati2 BAYt_CR

07_SOC_ PMU_DFX_CLK_UART_SUS

07_SOC_ PMU_DFX_CLK_UART_SUS

07_SOC_ PMU_DFX_CLK_UART_SUS

Document Number:

Document Number:

Document Number:

Friday, July 25, 2014 397

Friday, July 25, 2014 397

Friday, July 25, 2014 397

{Doc} 0.1C

{Doc} 0.1C

{Doc} 0.1C

Sheet:

Sheet:

Sheet:

+VRTC

R714

20K PR 0402

C707

1uF C 0402 10V

Drawing Rule

Drawing Rule

Drawing Rule

Allegro Lib Ver

Allegro Lib Ver

Allegro Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

Rev

Rev

Rev

of

of

of

SOC: POWER 1

+V1P2SX_SOC +VDDQ_SOC

+V_VCC

+VDDQ_SOC

?

U1F

A12

CORE_VCC_S0IX_1

G15

CORE_VCC_S0IX_3

H14

CORE_VCC_S0IX_4

H15

CORE_VCC_S0IX_5

H16

CORE_VCC_S0IX_6

K13

CORE_VCC_S0IX_8

K14

CORE_VCC_S0IX_9

K15

CORE_VCC_S0IX_10

K16

CORE_VCC_S0IX_11

L14

CORE_VCC_S0IX_12

L15

CORE_VCC_S0IX_13

L16

CORE_VCC_S0IX_14

M14

CORE_VCC_S0IX_15

F15

CORE_VCC_S0IX_2

M15

CORE_VCC_S0IX_16

N14

CORE_VCC_S0IX_17

N15

CORE_VCC_S0IX_18

P13

CORE_VCC_S0IX_19

P14

CORE_VCC_S0IX_20

P15

CORE_VCC_S0IX_21

P16

CORE_VCC_S0IX_22

J17

CORE_VCC_S0IX_7

W19

DRAM_VDD_S4_7

L18

DRAM_VDD_S4_2

L19

DRAM_VDD_S4_3

M19

DRAM_VDD_S4_5

L20

DRAM_VDD_S4_4

K18

DRAM_VDD_S4_1

T19

DRAM_VDD_S4_6

P19

DRAM_V1P24_S0IX_F1

6 OF 9

VLV2_CR

UNCORE_VNN_S4_26

UNCORE_VNN_S4_2

UNCORE_VNN_S4_3

UNCORE_VNN_S4_4

UNCORE_VNN_S4_5

UNCORE_VNN_S4_8

UNCORE_VNN_S4_9

UNCORE_VNN_S4_11

UNCORE_VNN_S4_12

UNCORE_VNN_S4_13

UNCORE_VNN_S4_14

UNCORE_VNN_S4_7

UNCORE_VNN_S4_15

UNCORE_VNN_S4_6

UNCORE_VNN_S4_17

UNCORE_VNN_S4_18

UNCORE_VNN_S4_19

UNCORE_VNN_S4_20

UNCORE_VNN_S4_21

UNCORE_VNN_S4_22

UNCORE_VNN_S4_23

UNCORE_VNN_S4_24

UNCORE_VNN_S4_25

UNCORE_VNN_S4_27

UNCORE_VNN_S4_28

UNCORE_VNN_S4_29

UNCORE_VNN_S4_30

UNCORE_VNN_S4_31

UNCORE_VNN_S4_32

UNCORE_VNN_S4_33

UNCORE_VNN_S4_34

UNCORE_VNN_S4_16

UNCORE_VNN_S4_35

UNCORE_VNN_S4_36

UNCORE_VNN_S4_1

UNCORE_VNN_S4_10

U12

K12

L11

L12

L13

M11

M12

M9

N10

N11

N12

M10

R13

L9

T11

T12

T13

T14

T15

T16

T17

U10

U11

U13

U14

U15

U16

V10

V11

V13

V17

R8

V18

W18

AB1

M8

+V_VNN

+V1P2SX +V1P2SX_SOC

SH701

1 2

SHORT-0402

+VDDQ +VDDQ_SOC

SH3636

1 2

SHORT-0603

Z3735F

REV = 2.0

Approved:

Approved:

Approved:

Designer:

Designer:

Designer:

Project:

Project:

Project:

Title:

Title:

Title:

Size:

Size:

Size:

Document Number:

Document Number:

Document Number:

Date:

Date:

Date:

Acer Inc.

Acer Inc.

Acer Inc.

Ducati2 BAYt_CR

Ducati2 BAYt_CR

Ducati2 BAYt_CR

08_SOC_ POWER 1

08_SOC_ POWER 1

08_SOC_ POWER 1

{Doc} 0.1C

{Doc} 0.1C

{Doc} 0.1C

Friday, July 25, 2014 398

Friday, July 25, 2014 398

Friday, July 25, 2014 398

Sheet:

Sheet:

Sheet:

Drawing Rule

Drawing Rule

Drawing Rule

Allegro Lib Ver

Allegro Lib Ver

Allegro Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

Rev

Rev

Rev

of

of

of

SOC: POWER 2

+V1P0A_SOC

+V1P0SX

+V1P0SX

?

U1G

J16

CORE_V1P05_S4_5

M16

CORE_V1P05_S4_8

J7

UNCORE_V1P0_G3_1

K8

UNCORE_V1P0_G3_4

L7

UNCORE_V1P0_G3_6

K7

UNCORE_V1P0_G3_3

W10

GPIO_V1P0_S4

G8

USB_V1P0_S4_1

H7

USB_V1P0_S4_2

H8

UNCORE_V1P0_S4

V15

UNCORE_V1P0_S0IX_6

W15

UNCORE_V1P0_S0IX_8

V16

UNCORE_V1P0_S0IX_7

K9

UNCORE_V1P0_G3_5

J9

UNCORE_V1P0_G3_2

T7

DDI_V1P0_S0IX_1

U8

DDI_V1P0_S0IX_3

T8

DDI_V1P0_S0IX_2

AE24

DRAM_V1P0_S4_1

H18

DRAM_V1P0_S4_3

G19

DRAM_V1P0_S4_2

U18

DRAM_V1P0_S4_6

N18

DRAM_V1P0_S4_5

M18

DRAM_V1P0_S4_4

CORE_V1P05_S4_7

CORE_V1P05_S4_6

CORE_V1P05_S4_4

CORE_V1P05_S4_10

CORE_V1P05_S4_9

CORE_V1P05_S4_2

CORE_V1P05_S4_3

7 OF 9

VLV2_CR

CORE_V1P05_S4_1

UNCORE_V1P0_S0IX_4

UNCORE_V1P0_S0IX_3

UNCORE_V1P0_S0IX_5

UNCORE_V1P0_S0IX_1

UNCORE_V1P0_S0IX_2

MIPI_V1P24_S4_1

MIPI_V1P24_S4_2

UNCORE_V1P8_S4_3

UNCORE_V1P8_S4_1

UNCORE_V1P8_S4_4

UNCORE_V1P8_S4_2

UNCORE_V1P8_G3

PMC_V1P8_G3_2

PMC_V1P8_G3_1

PMC_V1P8_G3_3

USB_V3P3_S0IX

PCU_V3P3_G3

SD3_V1P8V3P3_S4

ICLK_V1P24_S4_F1

ICLK_V1P24_S4_F2

UNCORE_V1P24_S0IX_F5

UNCORE_V1P24_S0IX_F4_2

UNCORE_V1P24_S0IX_F4_1

UNCORE_V1P24_S0IX_F1

MIPI_V1P8_S4

RTC_VCC

L17

K17

G18

R18

R17

A17

G17

A16

R11

R10

T10

H11

H12

N7

P7

W16

W12

Y15

W13

J15

G11

J10

H10

K10

F11

H9

G12

W14

M7

N8

P12

H13

G13

P9

+V1P0A_SOC

+V1P0SX

+V1P2A_SOC

+V1P8A_SOC

+V1P8A_SOC

+VRTC

+V1P2A_SOC

+V3P3A_SOC

+VSDIO

+V1P2SX_SOC

+V1P0A

+V1P2A

SH901

1 2

SHORT-0603

SH902

1 2

SHORT-0402

+V1P0A_SOC

+V1P2A_SOC

Z3735F

REV = 2.0

Approved:

Approved:

Approved:

Designer:

Designer:

Designer:

Project:

Project:

Project:

Title:

Title:

Title:

Size:

Size:

Size:

Document Number:

Document Number:

Document Number:

Date:

Date:

Date:

Acer Inc.

Acer Inc.

Acer Inc.

Ducati2 BAYt_CR

Ducati2 BAYt_CR

Ducati2 BAYt_CR

09_SOC_ POWER 2

09_SOC_ POWER 2

09_SOC_ POWER 2

{Doc} 0.1C

{Doc} 0.1C

{Doc} 0.1C

Friday, July 25, 2014 399

Friday, July 25, 2014 399

Friday, July 25, 2014 399

Sheet:

Sheet:

Sheet:

Drawing Rule

Drawing Rule

Drawing Rule

Allegro Lib Ver

Allegro Lib Ver

Allegro Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

Rev

Rev

Rev

of

of

of

SOC: GND & RESERVED PINS

E24

E21

E18

E15

E11

B21

B17

B13

AE2

AD9

AD5

AD21

AD17

AD13

AA7

AA24

AA21

AA2

AA18

AA15

AA11

W17

W11

J11

A24

V19

K11

K19

J19

AD25

R19

P17

G14

J12

V8

V7

E7

E2

B9

B5

B1

P8

G9

V9

N9

R7

?

U1H

VSS86

VSS85

VSS28

VSS27

VSS26

VSS25

VSS24

VSS23

VSS22

VSS21

VSS20

VSS19

VSS18

VSS17

VSS16

VSS15

VSS14

VSS13

VSS11

VSS10

VSS9

VSS8

VSS7

VSS6

VSS5

VSS4

VSS3

VSS2

VSS89

L8

VSS51

VSS88

VSS63

VSS36

J8

VSS44

VSS33

VSS87

VSS60

VSS73

VSS1

VSS82

VSS45

VSS46

VSS41

VSS12

VSS68

VSS61

VSS30

VSS37

8 OF 9

VLV2_CR

USB_VSSA

VSS92

VSS91

VSS93

VSS80

VSS94

VSS90

VSS84

VSS83

VSS81

VSS79

VSS78

VSS77

VSS76

VSS75

VSS74

VSS72

VSS71

VSS70

VSS69

VSS67

VSS65

VSS64

VSS62

VSS59

VSS58

VSS57

VSS56

VSS55

VSS54

VSS53

VSS52

VSS50

VSS49

VSS48

VSS47

VSS43

VSS42

VSS40

VSS39

VSS38

VSS35

VSS34

VSS32

VSS31

VSS29

VSS66

W8

W7

W9

V12

Y11

W5

V6

V21

V14

U9

U24

U2

T9

T18

R9

R6

R5

R21

R20

R16

R14

R12

P18

N24

N21

N2

N17

N16

N13

M17

M13

L6

L5

L21

L10

J24

J2

J18

J14

J13

H21

H17

G5

G16

G10

R15

G7

AC4

AC3

AE3

AD3

AC2

AC1

N5

A2

U3

Y18

P10

P11

AD1

AE1

W4

W3

AA19

AA20

AC21

AB21

T2

?

U1I

RESERVED9

RESERVED8

RESERVED13

RESERVED11

RESERVED6

RESERVED5

RESERVED17

RESERVED14

RESERVED1

RESERVED18

RESERVED21

RESERVED15

RESERVED16

RESERVED10

RESERVED12

RESERVED20

RESERVED19

RESERVED2

RESERVED3

RESERVED7

RESERVED4

Z3735F

REV = 2.0

9 OF 9

VLV2_CR

PWR_RSVD_OBS1

PWR_RSVD_OBS3

PWR_RSVD_OBS2

A25

B25

AE25

Z3735F

REV = 2.0

Approved:

Approved:

Approved:

Designer:

Designer:

Designer:

Project:

Project:

Project:

Title:

Title:

Title:

Size:

Size:

Size:

Document Number:

Document Number:

Document Number:

Date:

Date:

Date:

Acer Inc.

Acer Inc.

Acer Inc.

Ducati2 BAYt_CR

Ducati2 BAYt_CR

Ducati2 BAYt_CR

10_SOC_ GND & RESERVED PINS

10_SOC_ GND & RESERVED PINS

10_SOC_ GND & RESERVED PINS

{Doc} 0.1C

{Doc} 0.1C

{Doc} 0.1C

Friday, July 25, 2014 3910

Friday, July 25, 2014 3910

Friday, July 25, 2014 3910

Sheet:

Sheet:

Sheet:

Drawing Rule

Drawing Rule

Drawing Rule

Allegro Lib Ver

Allegro Lib Ver

Allegro Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

Rev

Rev

Rev

of

of

of

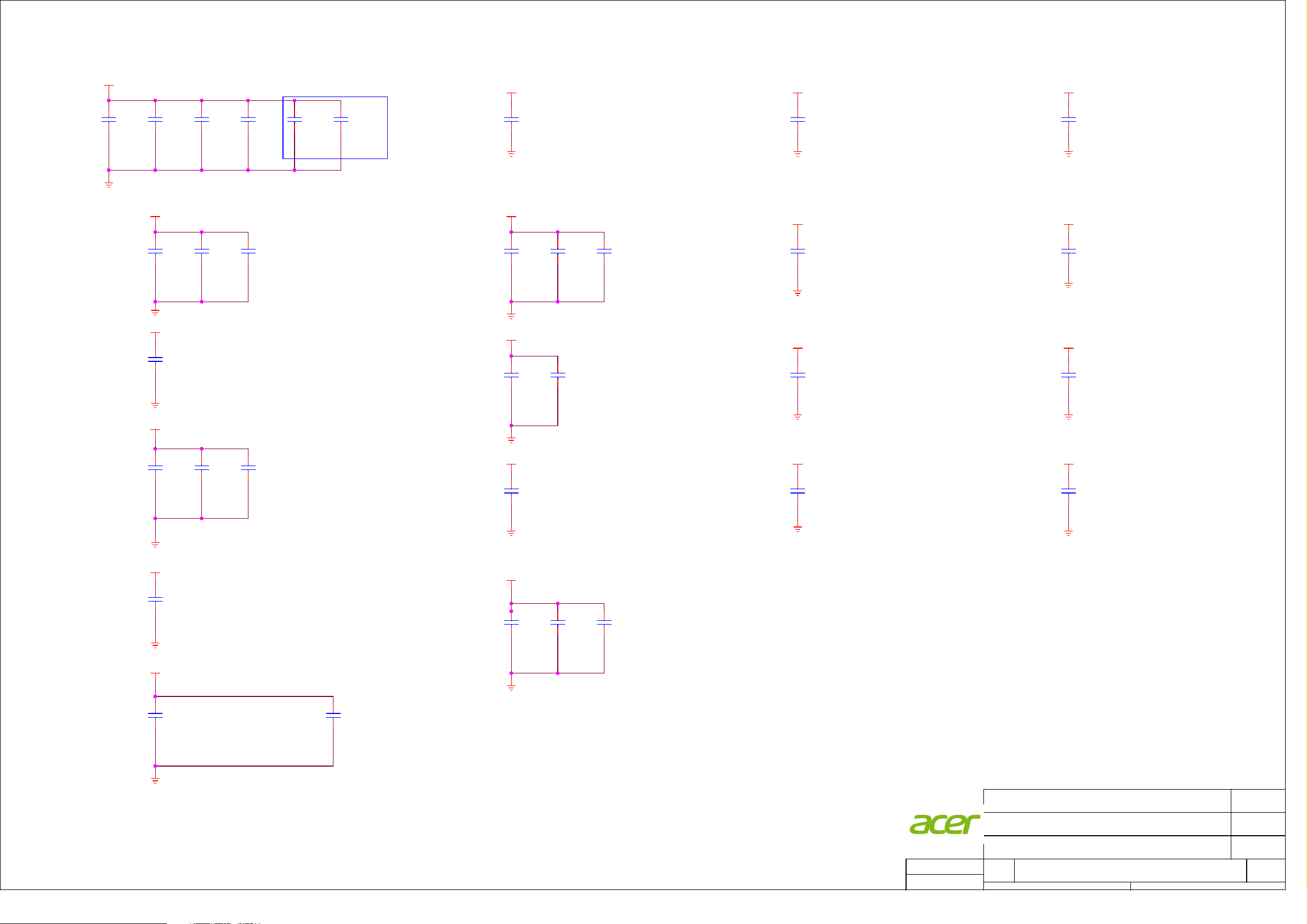

SOC: DECOUPLING

+V_VCC

C1101

1uF C 0402 10V

BSC

C1102

1uF C 0402 10V

BSC ESC ESC

+V_VNN

C1110

@

1uF C 0402 10V

+VDDQ_DDR

C1118

C1103

1uF C 0402 10V

C1104

1uF C 0402 10V

C1105

@

1uF C 0402 10V

ESC ESC ESC

C1106

@

1uF C 0402 10V

C1105 AND C1106 ARE STUFFED FOR

VALIDATION WHEN BSC'S ARE UNSTUFFED

C1111

1uF C 0402 10V

ESC

C1112

1uF C 0402 10V

ESCBSC

+V1P0SX

+V1P0A_SOC

@

+V1P0A_SOC

C1107

1uF C 0402 10V

C1113

1uF C 0402 10V

BSC

C1119

+V1P0A_SOC

C1108

ESC ESC

1uF C 0402 10V

+V1P0A_SOC

C1114

1uF C 0402 10V

C1120

@

C1115

@

ESC ESC

1uF C 0402 10V

+VSDIO

C1116

@

ESC

1uF C 0402 10V

C1121

+V1P2A_SOC

C1109

1uF C 0402 10V

+V1P2A_SOC

C1117

@

1uF C 0402 10V

+V1P8A_SOC

C1122

BSC

ESC

1uF C 0402 10V

+VDDQ_DDR

C1123

@

1uF C 0402 10V

BSC ESC

+V1P2SX_SOC

C1129

ESC

1uF C 0402 10V

+V1P0SX

C1133

@

C1124

1uF C 0402 10V

C1125

1uF C 0402 10V

ESC

C1134

1uF C 0402 10V

ESC ESC

+V1P0A_SOC

C1126

ESC

1uF C 0402 10V

+V1P0A_SOC

C1130

@

1uF C 0402 10V

BSC ESC ESC

C1131

1uF C 0402 10V

+V1P8A_SOC

C1132

1uF C 0402 10V

1uF C 0402 10V

1uF C 0402 10V

C1127

1uF C 0402 10V

ESC

+V3P3A_SOC

ESC

1uF C 0402 10V

C1128

1uF C 0402 10V

ESC

ESC

1uF C 0402 10V

1uF C 0402 10V

ESCBSC

Drawing Rule

Drawing Rule

Drawing Rule

Acer Inc.

Acer Inc.

Approved:

Approved:

Approved:

Designer:

Designer:

Designer:

Project:

Project:

Project:

Title:

Title:

Title:

Size:

Size:

Size:

Document Number:

Document Number:

Document Number:

Date:

Date:

Date:

Acer Inc.

Ducati2 BAYt_CR

Ducati2 BAYt_CR

Ducati2 BAYt_CR

11_SOC_ DECOUPLING

11_SOC_ DECOUPLING

11_SOC_ DECOUPLING

{Doc} 0.1C

{Doc} 0.1C

{Doc} 0.1C

Friday, July 25, 2014 3911

Friday, July 25, 2014 3911

Friday, July 25, 2014 3911

Sheet:

Sheet:

Sheet:

of

of

of

Allegro Lib Ver

Allegro Lib Ver

Allegro Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

Rev

Rev

Rev

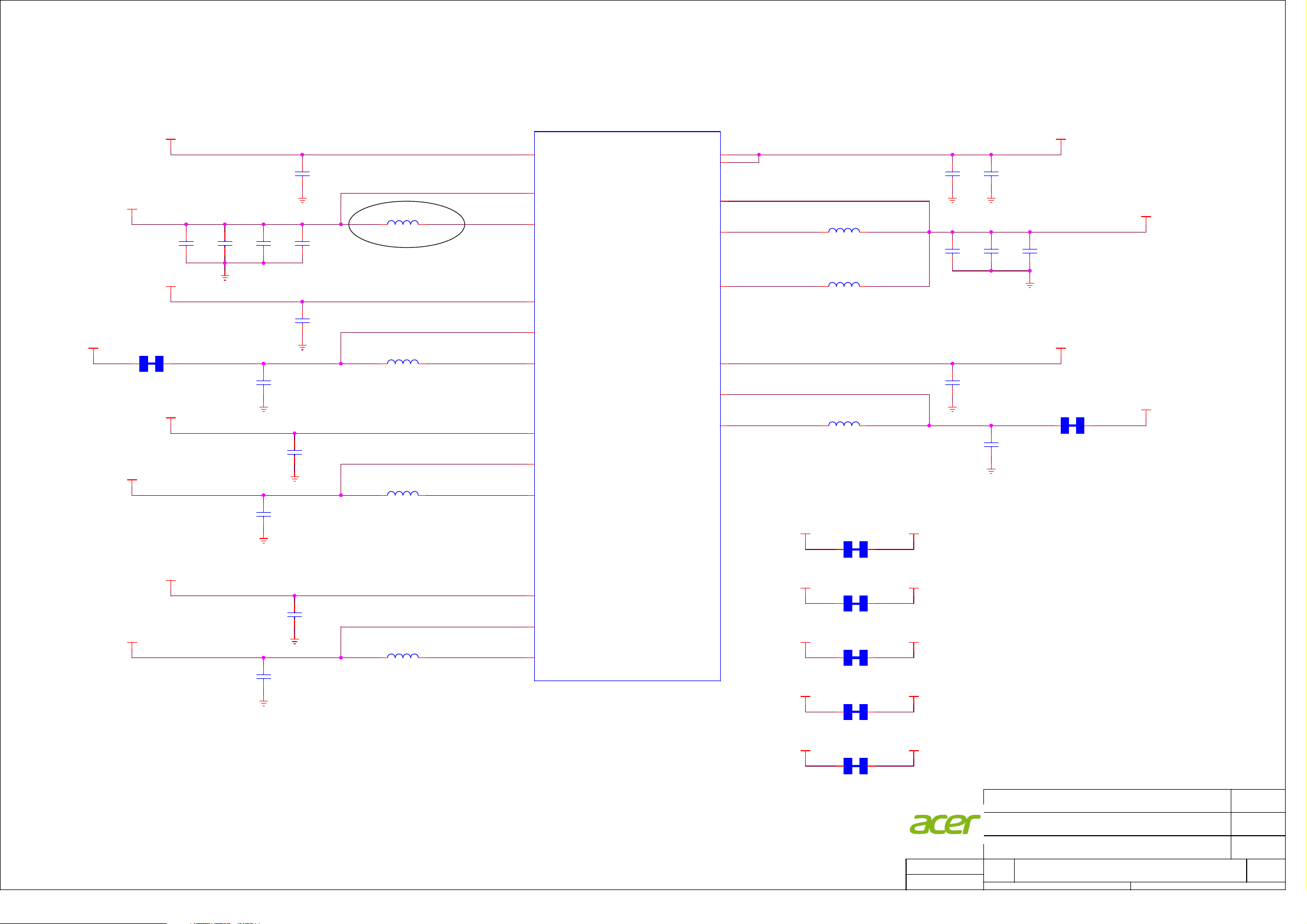

+V_VSYS_PMIC

U2A

+V_VSYS_PMIC

+V1P0SX

+V_VCC_PMIC

SH3616

1 2

SHORT-0603

+V1P0A

C3683

+V_VSYS_PMIC

+V_VSYS_PMIC

48

45

47

40

38

39

54

56

55

BUCK1VIN

BUCK1FB

BUCK1LX

(1V/3A)

BUCK2VIN

BUCK2FB

BUCK2LX

(1V/1.8A)

BUCK3VIN

BUCK3FB

BUCK3LX

(1.05V/2A)

C3679

C3680

22uF C 0603 6.3V

C3681

22uF C 0603 6.3V

+V1P0SX_BUCK2

22uF C 0603 6.3V

C3636

22uF C 0603 6.3V

C3639

10uF C 0603 6.3V

C3635

22uF C 0603 6.3V

C3637

4.7uF C 0603 6.3V

C3638

4.7uF C 0603 6.3V

L3214 1uH L 4040

1uH±20%, 4.2A, 43mohm

Changed to 4040 package in C build

L3215 1.5uH L 2520

1.5uH+/-20%, 3.1A, 66mohm

L3216 1.5uH L 2520

1.5uH+/-20%, 3.1A, 66mohm

+V_VCC_LX

+V1P0SX_LX

+V1P0A_LX

BUCK5VIN1

BUCK5VIN2

BUCK5FB1

BUCK5LX1

(1V, 5A)

BUCK5LX2

BUCK6VIN

BUCK6FB

BUCK6LX

(1.8V/1A)

27

28

31

26

29

19

18

20

+V_VNN_LX1

+V_VNN_LX2

+V1P8A_LX

L3218 0.47uH L 2520

0.47uH+/-20%, 3.9A, 30mohm

L3219 0.47uH L 2520

0.47uH+/-20%, 3.9A, 30mohm

L3220 1.5uH L 2520

1.5uH+/-20%, 3.1A, 66mohm

C3642

10uF C 0603 6.3V

C3644

22uF C 0603 6.3V

C3647

+V1P8A_BUCK6

4.7uF C 0603 6.3V

C3643

10uF C 0603 6.3V

C3645

22uF C 0603 6.3V

C3648

22uF C 0603 6.3V

C3646

22uF C 0603 6.3V

+V_VSYS_PMIC

SH3637

1 2

SHORT-0603

+V_VNN_PMIC

+V1P8A

+VDDQ

+V_VSYS_PMIC

22uF C 0603 6.3V

C3641

22uF C 0603 6.3V

C3640

4.7uF C 0603 6.3V

L3217 1.5uH L 2520

1.5uH+/-20%, 3.1A, 66mohm

+VDDQ_LX

61

63

62

BUCK4VIN

BUCK4FB

BUCK4LX

(1.25V/2A)

1/2

PSND9039ABTRSK

+V_VSYS

+VDDQ

+V_VNN_PMIC

+V_VCC_PMIC

SH1203

1 2

SHORT-0805

SH1202

1 2

SHORT-0603

SH1204

1 2

SHORT-0603

SH1206

1 2

SHORT-0805

SH1207

1 2

SHORT-0603

+V_VSYS_PMIC

+V1P8A_SOC+V1P8A

+VDDQ_DDR

+V_VNN

+V_VCC

Approved:

Approved:

Approved:

Designer:

Designer:

Designer:

PLACE AT V_SYS OUTPUT FROM PMIC TO MEASURE REST OF SYSTEM V_SYS PWR

PLACE RESISTOR FOR V1P8A RAIL TO SOC, CLOSE TO SOC (POWER #2)

PLACE RESISTOR AT INPUT TO MEMORY ICS

PLACE RESISTOR AT OUTPUT OF PMIC (PMIC #3)

PLACE RESISTOR AT OUTPUT OF PMIC (PMIC #3)

Drawing Rule

Drawing Rule

Drawing Rule

Acer Inc.

Acer Inc.

Project:

Project:

Project:

Title:

Title:

Title:

Size:

Size:

Size:

Document Number:

Document Number:

Document Number:

Date:

Date:

Date:

Acer Inc.

Ducati2 BAYt_CR

Ducati2 BAYt_CR

Ducati2 BAYt_CR

12_DOLLARCOVE TI_ SWITCHERS

12_DOLLARCOVE TI_ SWITCHERS

12_DOLLARCOVE TI_ SWITCHERS

{Doc} 0.1C

{Doc} 0.1C

{Doc} 0.1C

Friday, July 25, 2014 3912

Friday, July 25, 2014 3912

Friday, July 25, 2014 3912

Sheet:

Sheet:

Sheet:

of

of

of

Allegro Lib Ver

Allegro Lib Ver

Allegro Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

OrCAD Lib Ver

Rev

Rev

Rev

Loading...

Loading...