Page 1

DATASHEET

gen4 Display Module Series

2.4” Picaso Integrated Display Module

gen4-uLCD-24PT

Resistive touch

Document Date: 17th October 2017

Document Revision: 1.4

Please refer to the 4D Systems website for the latest Revision of this document

Uncontrolled Copy when printed or downloaded.

www.4dsystems.com.au

Page 2

gen

4 Display Module Series gen4-uLCD-24PT - 2.4”

Contents

1. Description ...................................................................................................................4

2. Features .......................................................................................................................4

3. Hardware Overview ......................................................................................................5

4. Hardware Interface - Pins ..............................................................................................7

4.1. Serial Ports – TTL Level Serial ........................................................................................ 7

4.2. General Purpose I/O ...................................................................................................... 7

4.3. System Pins .................................................................................................................... 8

4.4. I2C .................................................................................................................................. 8

5. Module Features ..........................................................................................................9

5.1. Picaso Processor ............................................................................................................ 9

5.2. Audio ............................................................................................................................. 9

5.3. SD/SDHC Memory Cards ................................................................................................ 9

5.4. FAT16 ............................................................................................................................. 9

5.5. Application PCB Support ................................................................................................ 10

5.6. RF / EMI Shielding Support ............................................................................................ 10

6. Display/Module Precautions ....................................................................................... 11

7. Hardware Tools .......................................................................................................... 11

7.1. 4D Programming Cable/Adaptor ................................................................................... 11

8. Software Overview - Language .................................................................................... 12

9. 4D Systems - Workshop 4 IDE ...................................................................................... 13

9.1. Workshop4 - Designer ................................................................................................... 13

9.2. Workshop4 – ViSi ........................................................................................................... 13

9.3. Workshop4 – ViSi Genie ................................................................................................ 14

9.4. Workshop4 – Serial ........................................................................................................ 14

9.5. PmmC/Firmware Programming ..................................................................................... 15

10. Starter Kit ................................................................................................................... 16

11. Display Module Part Numbers ..................................................................................... 16

12. Mechanical Details...................................................................................................... 17

13. Schematic Details ....................................................................................................... 18

14. Specifications ............................................................................................................. 19

© 2017 4D SYSTEMS Page 2 of 22 www.4dsystems.com.au

Page 3

gen

4 Display Module Series gen4-uLCD-24PT - 2.4”

15. Hardware Revision History .......................................................................................... 21

16. Legal Notice ................................................................................................................ 22

17. Contact Information ................................................................................................... 22

© 2017 4D SYSTEMS Page 3 of 22 www.4dsystems.com.au

Page 4

gen

4 Display Module Series gen4-uLCD-24PT - 2.4”

1. Description

The gen4 2.4” Picaso Integrated Display Module is

part of the latest gen4 series of modules Designed

and Manufactured by 4D Systems.

The gen4 series was designed specifically for ease of

integration and use, with careful consideration for

space requirements and functionality.

This specific gen4 module features a 2.4” colour TFT

LCD display, with resistive touch. It is powered by the

well-known 4D Systems Picaso Graphics Processor,

which offers an array of functionality and options for

any Designer / Integrator / User.

The Picaso processor features include 13

customisable GPIO, 2 Serial ports, and a Master I2C

interface.

The 2.4” Picaso Integrated Display Module features a

TFT LCD Display, is capable of Touch Detection,

microSD memory Storage, GPIO and

Communications, along with multiple millisecond

resolution timers, and Audio Generation.

The gen4 Series is 100% compatible with the

Workshop4 IDE and its 4 different development

environments, providing the User with a wealth of

options for programming and controlling their

system.

Anything designed to run on other 4D Systems

display modules featuring Picaso Graphic Processors

can be run on this gen4 Integrated Display Module,

with little or no required modifications. Please

contact 4D Systems Support Team for assistance if

migrating from a previous model.

The gen4 series of Integrated Display Modules

features a 30 pin ZIF socket, designed for a 30 pin FPC

cable, for easy and simple connection to an

application or mother board, or for connecting to

accessory boards for a range of functionality

advancements.

The gen4 series of modules has been designed to

minimise the impact of display related circuitry, and

provide a platform suitable for integration into a

product. Application boards can sit flush on the back

of the gen4 if required, as the display related

electronics sit inside the plastic mounting base,

leaving the application board surface clear for User

circuitry.

2. Features

• Universal 2.4” Intelligent LCD-TFT display module

powered by the Picaso Processor.

• 240 x 320 Resolution, RGB 65K true to life colours,

TFT Screen with integrated 4-wire Resistive Touch

Panel.

• 14KB of Flash memory for User Application Code

and Data.

• 14KB of SRAM for user variables, or 14KB shared

user code and program variables.

• 2 x Asynchronous hardware serial ports (COM0,

COM1), TTL interface, with 300 to 600K baud.

2

• 1 x I

• 8 x 16 bit timers with 1 millisecond resolution.

• 13 x General Purpose I/O pins. Supports fast 8-bit

• 30pin FPC connection, for all signals, power,

• On-board latch type micro-SD memory card

• DOS compatible file access (FAT16 format) as well

• Dedicated PWM Audio pin driven by WAV files

• Built in extensive 4DGL graphics and system library

• Display full colour images, animations, icons and

• Supports all available Windows fonts.

• 4.0V to 5.5V range operation (single supply).

• Module dimensions: 78.4 x 44.8 x 7.2mm.

• Weighing ~21 g.

• Display Viewing Area: 48.96 x 36.72mm.

• 4x mounting tabs with 3.2mm holes for mechanical

• RoHS and REACH compliant.

• CE Compliant – please ask for CE declarations from

C interface (Master).

parallel data transfer through Upper 8 bits.

communications, GPIO and programming.

connector for multimedia storage and data logging

purposes.

as low level access to card memory.

from micro-SD card, and for sound generation, for

an external amplifier.

functions.

video clips.

mounting using M3 screws.

our Support Team.

© 2017 4D SYSTEMS Page 4 of 22 www.4dsystems.com.au

Page 5

gen

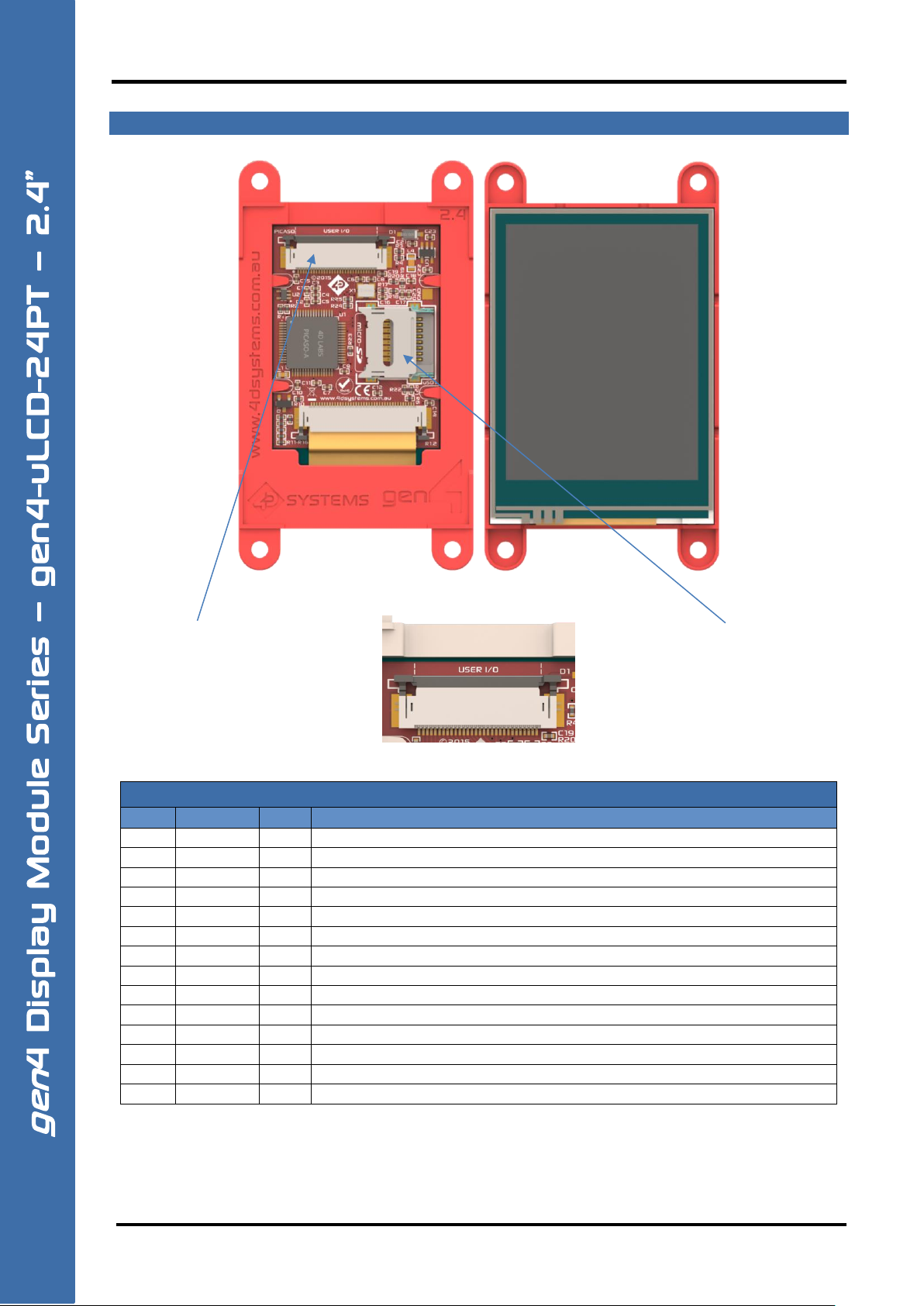

USER I/O – 30 Way FPC

Pin

Symbol

I/O

Description

1

GND

P

Supply Ground

2

IO1

I/O

General Purpose Input/Output, 3.3V Level - 5V Tolerant

3

IO2

I/O

General Purpose Input/Output, 3.3V Level - 5V Tolerant

4

IO3

I/O

General Purpose Input/Output, 3.3V Level - 5V Tolerant

5

IO4

I/O

General Purpose Input/Output, 3.3V Level - 5V Tolerant. Also used for Bus Read

6

BUS5

I/O

General Purpose Input/Output, 3.3V Level - 5V Tolerant

7

BUS4

I/O

General Purpose Input/Output, 3.3V Level - 5V Tolerant

8

BUS3

I/O

General Purpose Input/Output, 3.3V Level - 5V Tolerant

9

BUS2

I/O

General Purpose Input/Output, 3.3V Level - 5V Tolerant

10

BUS1

I/O

General Purpose Input/Output, 3.3V Level - 5V Tolerant

11

BUS0

I/O

General Purpose Input/Output, 3.3V Level - 5V Tolerant

12

BUS6

I/O

General Purpose Input/Output, 3.3V Level - 5V Tolerant

13

BUS7

I/O

General Purpose Input/Output, 3.3V Level - 5V Tolerant

14

IO5

I/O

General Purpose Input/Output, 3.3V Level - 5V Tolerant. Also Bus Write

PIN 1

PIN 30

USER I/O – 30 way ZIF Socket

0.5mm pitch Upper Contact

15.5mm wide FPC Cable

Latch Type microSD Socket

4 Display Module Series gen4-uLCD-24PT - 2.4”

3. Hardware Overview

© 2017 4D SYSTEMS Page 5 of 22 www.4dsystems.com.au

Continued overleaf…

Page 6

gen

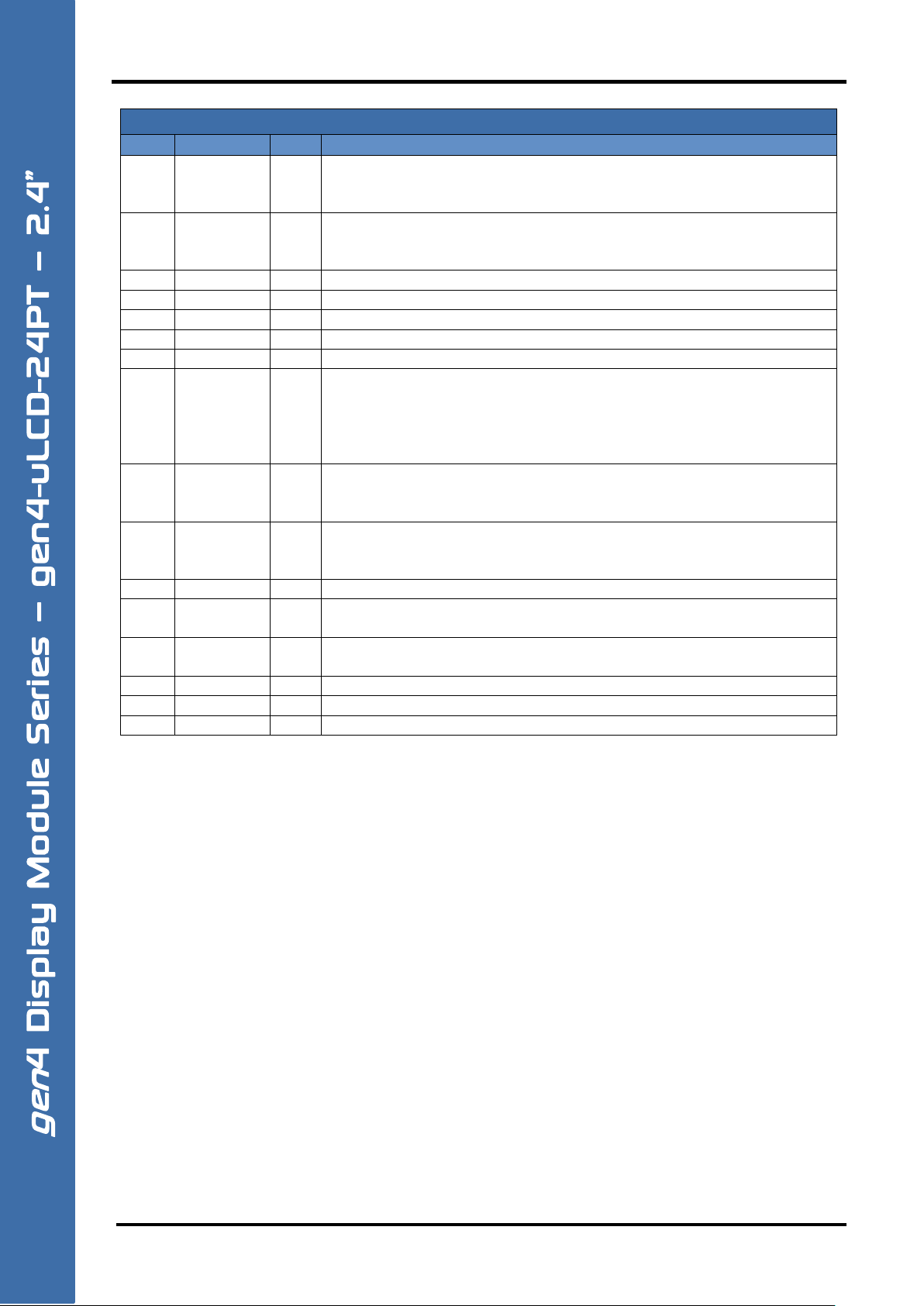

USER I/O – 30 Way FPC (continued)

Pin

Symbol

I/O

Description

15

RX1

I

Asynchronous Serial Receive COM1, TTL level. Connect this pin to the Transmit

(TX) signal of other serial devices. Used in conjunction with the TX1 pin. This

pin is tolerant up to 5.0V levels.

16

TX1

O

Asynchronous Serial Transmit COM1, TTL level. Connect this pin to the Receive

(RX) signal of other serial devices. Used in conjunction with the RX1 pin. This

pin has a 3.3V Level output.

17

I2C SCL

O

I2C Interface, SCL pin.

18

I2C SDA

I/O

I2C Interface, SDA pin.

19

AUDIO_OUT

O

Audio Output, PWM, to feed into external amplifier via filter network

20

AUDENB

O

Audio Amplifier Enable, to enable/disable external amplifier

21

GND

P

Supply Ground

22

RESET

I

Master Reset signal. Internally pulled up to 3.3V via a 10K resistor. An active

Low pulse greater than 2 micro-seconds will reset the module. If the module

needs to be reset externally, only use open collector type circuits. This pin is

not driven low by any internal conditions. The host should control this pin via

one of its port pins using an open collector/drain arrangement.

23

RX0

I

Asynchronous Serial Receive COM0, TTL level. Connect this pin to the Transmit

(TX) signal of other serial devices. Used in conjunction with the TX0 pin for

programming this module. This pin is tolerant up to 5.0V levels.

24

TX0

O

Asynchronous Serial Transmit COM0, TTL level. Connect this pin to the Receive

(RX) signal of other serial devices. Used in conjunction with the RX0 pin for

programming this module. This pin has a 3.3V Level output.

25

GND

P

Supply Ground

26

5V IN

P

Main Voltage Supply +ve input pin. Reverse polarity protected. Range is 4.0V

to 5.5V, nominal 5.0V.

27

5V IN

P

Main Voltage Supply +ve input pin. Reverse polarity protected. Range is 4.0V

to 5.5V, nominal 5.0V.

28

NC

-

Not Connected

29

NC

-

Not Connected

30

GND

P

Supply Ground

4 Display Module Series gen4-uLCD-24PT - 2.4”

I = Input, O = Output, P = Power

© 2017 4D SYSTEMS Page 6 of 22 www.4dsystems.com.au

Page 7

gen

4 Display Module Series gen4-uLCD-24PT - 2.4”

4. Hardware Interface - Pins

This section describes in detail the hardware interface

pins of the device.

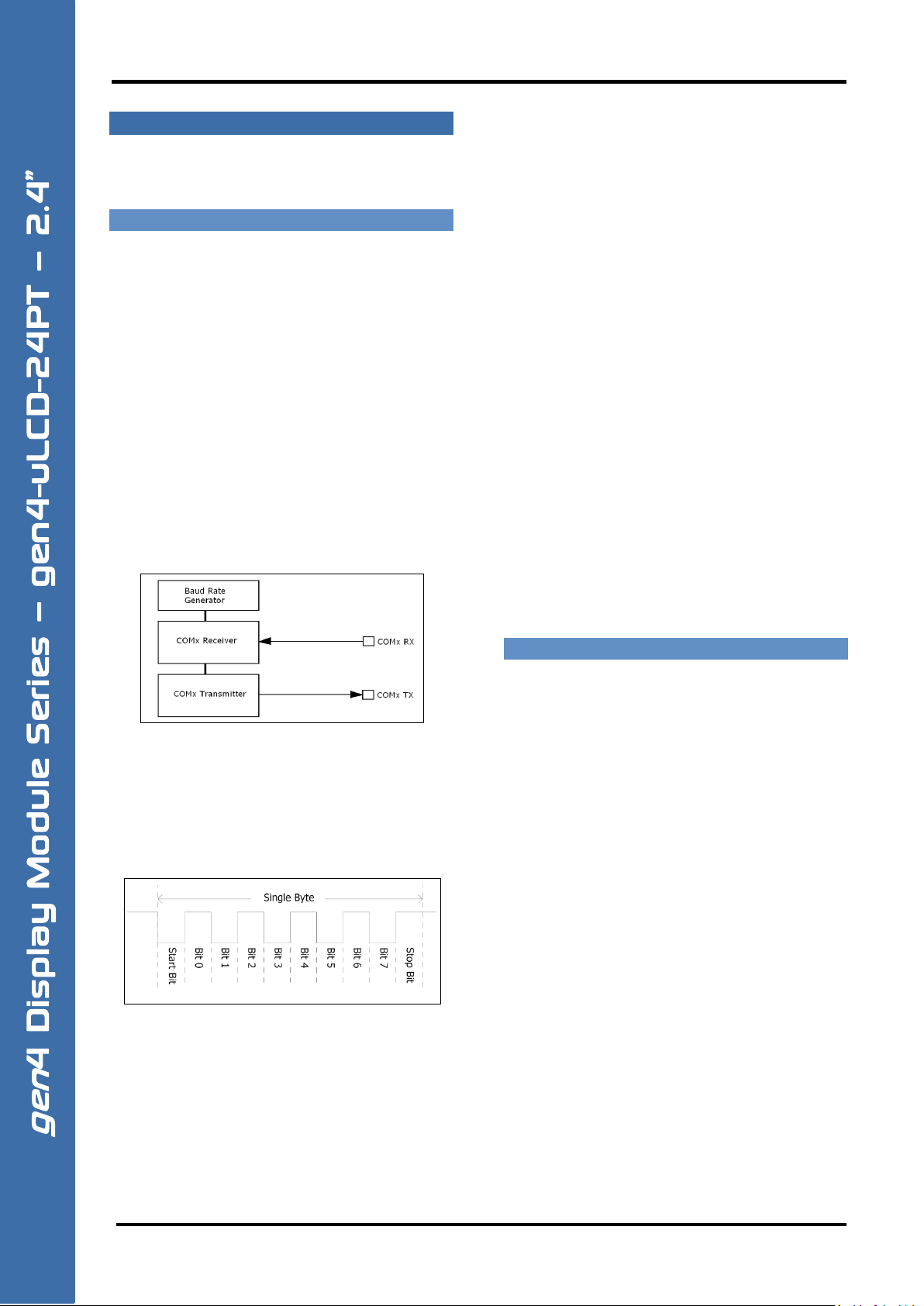

4.1. Serial Ports – TTL Level Serial

The Picaso Processor has two dedicated hardware

Asynchronous Serial ports that can communicate with

external serial devices. These are referred to as the

COM0 and the COM1 serial ports.

The primary features are:

• Full-Duplex 8 bit data transmission and

reception.

• Data format: 8 bits, No Parity, 1 Stop bit.

• Independent Baud rates from 300 baud up to

600K baud.

• Single byte transmits and receives or a fully

buffered service. The buffered service feature

runs in the background capturing and buffering

serial data without the user application having to

constantly poll any of the serial ports. This frees

up the application to service other tasks.

TX0 pin (Serial Transmit COM0):

Asynchronous Serial port COM0 transmit pin, TX0.

Connect this pin to external serial device receive (Rx)

signal. This pin outputs at 3.3V Level.

RX0 pin (Serial Receive COM0):

Asynchronous Serial port COM0 receive pin, RX0.

Connect this pin to external serial device transmit (Tx)

signal. This pin is native 3.3V level, but 5.0V tolerant.

TX1 pin (Serial Transmit COM1):

Asynchronous Serial port COM1 transmit pin, TX1.

Connect this pin to external serial device receive (Rx)

signal. This pin outputs at 3.3V Level.

RX1 pin (Serial Receive COM1):

Asynchronous Serial port COM1 receive pin, RX1.

Connect this pin to external serial device transmit (Tx)

signal. This pin is native 3.3V level, but 5.0V tolerant.

Please refer to the 'PICASO-4DGL-InternalFunctions.pdf' document for more information.

Serial ports output at the level of TTL 3.3V, however

are 5V tolerant, so can accept communications from

5V devices.

A single byte serial transmission consists of the start

bit, 8-bits of data followed by the stop bit. The start

bit is always 0, while a stop bit is always 1. The LSB

(Least Significant Bit, Bit 0) is sent out first following

the start bit. Figure below shows a single byte

transmission timing diagram.

COM0 is also the primary interface for 4DGL user

program downloads and chip configuration (PmmC

programming). Once the compiled 4DGL application

program (EVE byte-code) is downloaded and the user

code starts executing, the serial port is then available

to the user application. Refer to Section 5. ‘Firmware

/ PmmC Programming’ for more details on this

subject.

4.2. General Purpose I/O

There are 13 general purpose Input/Output (GPIO)

pins available to the user. These are grouped as IO1

IO5 and BUS0 BUS7. Power-Up Reset default is

all INPUTS.

The 5 I/O pins (IO1 IO5), provide flexibility of

individual bit operations while the 8 pins (BUS0

BUS7), known as GPIO BUS, serve collectively for byte

wise operations. The IO4 and IO5 also act as strobing

signals to control the GPIO Bus. GPIO Bus can be read

or written by strobing a low pulse (50ns duration or

greater) the IO4/BUS_RD or IO5/BUS_WR for read or

write respectively. For detailed usage refer to the

separate document titled:

“PICASO-4DGL-Internal-Functions.pdf”

IO1-IO5 pins:

General purpose I/O pins. Each pin can be

individually set for INPUT or an OUTPUT.

Power-Up Reset default is all INPUTS. Digital GPIO

can source/sink 4mA.

For more information see the Specifications section

of this datasheet.

© 2017 4D SYSTEMS Page 7 of 22 www.4dsystems.com.au

Page 8

gen

4 Display Module Series gen4-uLCD-24PT - 2.4”

IO4/BUS_RD pin (GPIO IO4 or BUS_RD pin):

General Purpose IO4 pin. Also used for BUS_RD signal

to read and latch the data in to the parallel GPIO

BUS0..BUS7.

IO5/BUS_WR pin (GPIO IO5 or BUS_WR pin):

General Purpose IO5 pin. Also used for BUS_WR

signal to write and latch the data to the parallel GPIO

BUS0..BUS7.

BUS0-BUS7 pins (GPIO 8-Bit Bus):

8-bit parallel General purpose I/O Bus.

Note: GPIO pins are 5.0V tolerant. All pins output at

3.3V levels.

4.3. System Pins

+5V IN (Module Voltage Input)

Module supply voltage input pins. Both of these pins

should be connected to a stable supply voltage in the

range of 4.0 Volts to 5.5 Volts DC. Nominal operating

voltage is 5.0 Volts. Note backlight brightness will be

lower for voltages under 5.0V.

GND (Module Ground)

Device ground pins. At least two pins should be

connected to ground.

RESET (Module Master Reset)

Module Master Reset pin. An active low pulse of

greater than 2μs will reset the module. Internally

pulled up to 3.3V via a 10K resistor. Only use open

collector type circuits to reset the device if an

external reset is required.

AUDENB (Audio Enable Output)

Output dedicated to enable or disable and external

amplifier, where required.

AUDIO (PWM Audio Output)

Output specifically for Audio. This pin is a PWM

output from the Picaso Processor. This pin is a 3.3V

level PWM output to drive an external amplifier with

Picaso generated Audio, via an external filtering

circuit to turn digital PWM into Analog. Note that

AUDENB must be enabled in Picaso for any input

signal to be heard.

4.4. I2C

There is one I2C Master Channel on the Picaso

processor. The I2C channel is Master only, and cannot

be configured to be a slave at this time.

To setup the I2C Channel the following 4DGL function

is used:

I2C_Open(Speed);

Where ‘Speed’ is the desired I2C Bus speed. There

are then an array of functions, typical of any I2C

capable processor, such as Close, Start, Stop, Restart,

Read, Write, Ack, Nack, etc…

Please refer to the separate document titled 'Picaso

4DGL Internal Functions’ for more information on

how to use the I2C functions, along with the separate

document titled ‘Picaso-Processor Datasheet’.

© 2017 4D SYSTEMS Page 8 of 22 www.4dsystems.com.au

Page 9

gen

4 Display Module Series gen4-uLCD-24PT - 2.4”

5. Module Features

The gen4 series of Integrated Display Modules are

designed to accommodate most applications. Some

of the main features of the module are listed below.

5.1. Picaso Processor

The module is designed around the Picaso Graphics

Controller from 4D-Labs.

The Picaso is a smart Controller and the interface to

the TFT- LCD displays is almost plug-n-play.

All of the data and control signals are provided by the

chip to interface directly to the display.

Powerful graphics, text, image, animation and

countless more features are built right inside the

chip.

The data sheet for the processor is available from the

http://www.4dsystems.com.au website:

“Picaso Processor Datasheet”

5.2. Audio

Audio playback support in the Picaso Processor

enables this module to play audio WAV files stored in

the micro-SD memory card. PWM audio is generated

and made available on the AUDIO pin of the 30 way

ZIF connector, ready to interface with an audio

amplifier on your application board.

A simple instruction enables the user to

play/pause/stop audio files while continuing the

execution of the user application code, such as

display updates, touch recognition, communications,

etc. The audio system also allows real time pitch

change of audio samples.

For a complete list of audio commands please refer

to the separate document titled:

“Picaso 4DGL Internal Functions”

5.3. SD/SDHC Memory Cards

The module supports micro-SD memory cards via the

on-board latch type micro-SD connector. The

memory card is used for all

multimedia file retrieval such as

images, animations and movie clips.

The memory card can also be used

as general purpose storage for data logging

applications. Support is available for off-the-shelf

micro-SD (< 4GB) and high capacity HC memory cards

(4GB and above). Memory cards up to 32GB is size

can be used, however it must be noted that only a

portion of this can be utilised by the FAT16 file

system. See section below for more details.

Note: A microSD card capable of SPI is a requirement

for all 4D Systems’ display modules powered by

Goldelox, Picaso or Diablo16 Processors. If a non-SPI

compatible card is used, it will simply fail to mount,

or may cause intermittent issues resulting in lock ups

and crashing of the application. Please refer to the

4D Systems website for microSD cards offered by 4D

Systems.

5.4. FAT16

All 4D Systems display modules featuring 4D Labs

processors use off-the-shelf standard

SDHC/SD/micro-SD memory cards (SPI Compatible

Only) with up to 4GB capacity usable with FAT16

formatting.

For any FAT file related operations, before the

memory card can be used it must first be formatted

correctly. Built into Workshop4 is a tool created by

4D, called RMPET (please refer to the Tools menu, in

any Environment, inside the Workshop4 IDE). RMPET

allows the User to easily partition and format

microSD cards, to make their file system ready to be

used with 4D Systems modules. The formatting of the

card can be done on any PC system with a card

reader.

The Picaso Processor also supports high capacity HC

memory cards (4GB and above). The available

capacity of SD-HC cards varies according to the way

the card is partitioned and the commands used to

access it. Refer to the 4D Systems RMPET tool in the

Workshop4 IDE.

A Max of 4GB can be utilised by the FAT16 file

system. The FAT partition is always first (if it exists).

Any space larger than 4GB will be RAW, and can still

be utilised by your 4D Systems module, using

different functions. Please refer to Application Notes.

© 2017 4D SYSTEMS Page 9 of 22 www.4dsystems.com.au

Page 10

gen

4 Display Module Series gen4-uLCD-24PT - 2.4”

5.5. Application PCB Support

The gen4 2.4” Picaso Integrated Display Module is

designed to accommodate a range of applications,

and therefore is suited for those wanting to make a

customised module, without the need for piggy-back

or daughter boards mounted on headers.

On the back of the gen4 module, the display related

circuitry will be found, which is recessed into the

plastic. The level of the plastic on the back of the

gen4 module is higher than the tallest component on

the display circuit PCB, meaning an Application PCB

can be mounted on the back of the gen4, without

affecting the display related circuitry.

The image below shows a mock Application PCB on

the back of the gen4 display (Blue area). It features a

cut-out in the PCB so access to the micro-SD socket

on the gen4’s display board is possible, however this

may or may not be required depending on the

application and if the micro-SD socket is utilised or

requiring access once the Application PCB is applied.

5.6. RF / EMI Shielding Support

As per what is written in section 5.5 (Application PCB

Support), there is an option for extended RF shielding

and EMI protection on this module.

On the back of the gen4’s display PCB, are grounded

plated ‘X pads’, which make contact with the metal

housing of the display.

Where the Application PCB is shown to sit in Section

5.5, can house a small metal shield of the same size.

This shield is used instead of, or underneath an

Application PCB, to aid the on-board electronics in

the prevention from potential RF or EMI signals.

On the top of the display PCB is another GND pad,

which can have a pogo pin or similar device mounted

on it, which can make contact with this metal shield.

The micro-SD socket is a latch type, so it is accessible

from the top, rather than a push/push or push/pull

style which is accessible from the side.

The display electronics are then sandwiched between

the display’s metal housing, and the metal shield, all

connected together with a common ground.

NOTE: There are no guarantees these steps will

increase chances or grant access to EMI related

certifications, however the gen4 has the capability to

utilise shielding of the modules electronics, should

the need arise. This may or may not assist the User

with protecting the device against EMI/EMF/RF type

noise, depending on the source, strength and type of

noise present, however should aid in the protection.

© 2017 4D SYSTEMS Page 10 of 22 www.4dsystems.com.au

Page 11

gen

4 Display Module Series gen4-uLCD-24PT - 2.4”

6. Display/Module Precautions

Avoid having to display the same image/object

on the screen for lengthy periods of time. This

can cause a burn-in which is a common problem

with all types of display technologies. Blank the

screen after a while or dim it very low by

adjusting the contrast. Better still; implement a

screen saver feature.

Moisture and water can damage the display.

Moisture on the surface of a powered display

should not cause any problems, however if water

is to enter the display either from the front or

from the rear, or come in contact with the PCB,

damage will certainly occur. Wipe off any

moisture gently or let the display dry before

usage. If using this display module in an

environment where it can get wet, ensure an

appropriate enclosure is used.

Dirt from fingerprint oil and fat can easily stain

the surface of the display. Gently wipe off any

stains with a soft lint-free cloth.

The performance of the display will degrade

under high temperature and humidity. Avoid

such conditions when storing.

Do not tamper with the display flex cable that is

connected to the control board. This may affect

the connection between the display and the

driving circuitry and cause failure.

Displays are susceptible to mechanical shock and

any force exerted on the module may result in

deformed zebra stripes, a cracked display cell

and broken backlight

Always use the mounting holes on the module's

corner plates to mount the display where

possible.

Display modules have a finite life, which is

typically dictated by the display itself, more

specifically the backlight. The backlight contains

LED’s, which fade over time. In the Specifications

section is a figure for the typical life of the

display, and the criteria are listed.

Resistive Touch model features a touch sensitive

film over the display which is sensitive to

pressure. Take note when mounting the display

module in an enclosure that pressure is not

applied to the surface of the display by the

enclosure, or false touches will occur, or the

touch will simply not function at all.

7. Hardware Tools

The following hardware tools are required for full

control of the gen4 Integrated Display Modules.

7.1. 4D Programming Cable/Adaptor

The 4D Programming Cable and uUSB-PA5

Programming Adaptor are essential hardware tools to

program, customise and test the Picaso Processor.

Either the 4D Programming Cable or the uUSB-PA5

Programming Adaptor can be used for the gen4

series of Display Modules.

The 4D programming interfaces are used to program

a new Firmware/PmmC and for downloading

compiled 4DGL code into the processor. They even

serve as an interface for communicating serial data to

the PC.

The 4D Programming Cable and uUSB-PA5

Programming Adaptor are available from 4D Systems,

www.4dsystems.com.au

Using a non-4D programming interface could damage

your processor, and void your Warranty.

4D Programming Cable

uUSB-PA5 Programming Adaptor

Please note, in conjunction with a Programming

Cable or a Programming Adaptor, the gen4 series of

Display Modules requires a simple interface board

(gen4-IB), as there is no 5 way male header on gen4

modules like other 4D Systems modules.

© 2017 4D SYSTEMS Page 11 of 22 www.4dsystems.com.au

Page 12

gen

4 Display Module Series gen4-uLCD-24PT - 2.4”

Gen4 Interface boards (Gen4-IB) ship with each gen4

Display Module unless otherwise stated. Simply

connect the supplied 30 way FPC cable into the ZIF

connector on the gen4 Interface Board, and connect

the Programming Cable or Adaptor into the 5-way

header on the Interface Board. You are now ready to

program using a 4D Programming Cable or 4D

Programming Adaptor (uUSB-PA5 or uUSB-PA5-II).

This can also be used to interface to other devices

such as a 4D Arduino Adaptor Shield, breadboard etc.

An alternative to using a Gen4-IB and a 4D

Programming Cable, or uUSB-PA5 Programming

Adaptor, is a single all in one board called the gen4PA (gen4 Programming Adaptor), which can be used

instead.

The gen4-PA incorporates the uUSB-PA5-II and gen4IB together essentially, creating a single module with

microUSB interface, and DIP style pads for GPIO

breakout of all the signals used on the gen4 Display

interface, which is useful for development or final

product use. Standard 2.54mm (0.1”) male pin

headers can be mounted so the module signals can

be interfaced to easily.

Please refer to the gen4-PA Datasheet for more

information.

8. Software Overview - Language

The Picaso processor belongs to a family of

processors powered by a highly optimised soft core

virtual engine called EVE (Extensible Virtual Engine).

EVE was designed and created by 4D Systems in the

early 2000’s, and should not be confused by FTDI’s

solution of EVE, which was developed a decent

decade or so later.

EVE is a proprietary, high performance virtualmachine with an extensive byte-code instruction set

optimised to execute compiled 4DGL programs.

4DGL (4D Graphics Language) was specifically

developed from ground up for the EVE engine core. It

is a high level language which is easy to learn and

simple to understand yet powerful enough to tackle

many embedded graphics applications.

4DGL is a graphics oriented language allowing rapid

application development, and the syntax structure

was designed using elements of popular languages

such as C, Basic, Pascal and others.

Programmers familiar with these languages will feel

right at home with 4DGL. It includes many familiar

instructions such as IF..ELSE..ENDIF, WHILE..WEND,

REPEAT..UNTIL, GOSUB..ENDSUB, GOTO, PRINT as

well as some specialised instructions SERIN, SEROUT,

GFX_LINE, GFX_CIRCLE and many more.

For detailed information pertaining to the 4DGL

language, please refer to the following documents:

“4DGL Programmers Reference Manual”

“Picaso 4DGL Internal Functions”

These are both available for download on the

Workshop4 Product Page of the 4D Systems website.

To assist with the development of 4DGL applications,

the Workshop4 IDE combines a full-featured editor, a

compiler, a linker and a downloader into a single PCbased application. It's all you need to code, test and

run your applications.

4DGL is available to be written in two of the four

environments offered by the Workshop 4 IDE,

Designer and ViSi. The other two environments, Serial

and ViSi-Genie do not directly use 4DGL by the User

(Except in Workshop4 Pro, for ViSi-Genie), however it

is present in the background. Serial is an application

which runs, and that is written in 4DGL. ViSi-Genie

automatically generates 4DGL itself based on what is

configured in the GUI. More information about each

follows.

© 2017 4D SYSTEMS Page 12 of 22 www.4dsystems.com.au

Page 13

gen

4 Display Module Series gen4-uLCD-24PT - 2.4”

9. 4D Systems - Workshop 4 IDE

Workshop 4 is a comprehensive software IDE that

provides an integrated software development

platform for all of the 4D family of processors and

modules. The IDE combines the Editor, Compiler,

Linker and Downloader to develop complete 4DGL

application code. All user application code is

developed within the Workshop 4 IDE.

The Workshop 4 IDE supports multiple development

environments for the user, to cater for different user

requirements and skill levels.

The Designer environment enables the user to

write 4DGL code in its natural form to program

the range of 4D Systems intelligent displays.

A visual programming experience, suitably called

ViSi, enables drag-and-drop type placement of

objects to assist with 4DGL code generation and

allows the user to visualise how the display will

look while being developed.

An advanced environment called ViSi-Genie

doesn’t require any 4DGL coding at all, it is all

done automatically for you. Simply lay the

display out with the objects you want, set the

events to drive them and the code is written for

you automatically. This can be extended with

additional features when a Workshop4 PRO

license is purchased from the 4D Systems

website. Extended Advanced features for VisiGenie are available in PRO version of WS4.

Further details explained in section 9.3.

A Serial environment is also provided to

transform the display module into a slave serial

module, allowing the user to control the display

from any host microcontroller or device with a

serial port.

The Workshop 4 IDE is available from the 4D Systems

website. www.4dsystems.com.au

For comprehensive manuals on the Workshop 4 IDE

Software, the language, and its environments, refer

to the documentation from the 4D Systems website,

on the Workshop 4 product page.

9.1. Workshop4 - Designer

Choose the Designer environment to write 4DGL code

in its raw form.

The Designer environment provides the user with a

simple yet effective programming environment

where pure 4DGL code can be written, compiled and

downloaded to the range of 4D Systems intelligent

display modules.

Designer is a very powerful environment, for those

use to developing without any form of GUI aid, or for

those developing complex systems where no aid is

required.

9.2. Workshop4 – ViSi

ViSi was designed to make the creation of graphical

displays a more visual experience.

ViSi is a great software tool that allows the user to

see the instant results of their desired graphical

layout. Additionally, there is a selection of inbuilt

dials, gauges and meters that can simply be placed

onto the simulated module display. From here each

object can have its properties edited, and at the click

of a button all relevant 4DGL code associated with

that object is produced in the user program. The user

can then write 4DGL code around these objects to

utilise them in the way they choose.

© 2017 4D SYSTEMS Page 13 of 22 www.4dsystems.com.au

Page 14

gen

4 Display Module Series gen4-uLCD-24PT - 2.4”

9.3. Workshop4 – ViSi Genie

ViSi-Genie is a breakthrough in the way 4D Systems’

graphic display modules are programmed. It is an

environment like no other, a code-less programming

environment that provides the user with a rapid

visual experience, enabling a simple GUI application

to be ‘written’ from scratch in literally seconds.

ViSi-Genie does all the background coding, no 4DGL

to learn, it does it all for you.

Pick and choose the relevant objects to place on the

display, much like the ViSi Environment yet without

having to write a single line of code. Each object has

parameters which can be set, and configurable

events to animate and drive other objects or

communicate with external devices.

Simply place an object on the screen, position and

size it to suit, set the parameters such as colour,

range, text, and finally select the event you wish the

object to be associated with, it is that simple.

In seconds you can transform a blank display into a

fully animated GUI with moving sliders, animated

press and release buttons, and much more. All

without writing a single line of code!

ViSi-Genie provides the user with a feature rich rapid

development environment, second to none.

with a fraction of the effort required by other

systems.

9.4. Workshop4 – Serial

The Serial environment in the Workshop 4 IDE

provides the user the ability to transform a 4D

Systems Intelligent Display, into a slave serial

graphics controller.

This enables the user to use their favourite

microcontroller or serial device as the Host, without

having to learn 4DGL or program in a separate IDE.

Once the display module is configured by the Serial

Environment (by downloading what is called the SPE

application to the module), commands can be sent

from the users host microcontroller to display

primitives, images, sound and video, and can even be

used to display ViSi generated graphics and widgets.

The Serial Environment should not be taken as being

basic in terms of its capabilities, as it has the full

4DGL command set behind it, but available from the

Host rather than from programming the display

module itself using the Workshop4 IDE.

Virtually anything created in Designer or ViSi, can be

designed or controlled from the Serial Environment.

Please refer to the “Picaso Serial Command Set

Reference Manual” from the Workshop 4 product

page on the 4D Systems website for a complete

listing of all the supported Serial commands

ViSi-Genie’s functionality can be extended with the

purchase of a Workshop4 PRO License.

Workshop4 PRO adds a professional set of features to

the Visi-Genie environment called Genie-Magic. The

added features allow the user to add in 4DGL scripts,

which can be activated from the display itself, from

an interfacing Host, or from an external sensor or

device.

These PRO set of features of Genie-Magic allow the

User to create an immensely powerful GUI system

© 2017 4D SYSTEMS Page 14 of 22 www.4dsystems.com.au

Page 15

gen

4 Display Module Series gen4-uLCD-24PT - 2.4”

9.5. PmmC/Firmware Programming

The Picaso processor is a custom graphics processor.

All functionality including the high level commands

are built into the chip. This chip level configuration is

available as a PmmC (Personality-module-microCode) file, which can be likened to traditional

Firmware..

A PmmC file contains all of the low level micro-code

information (analogy of that of a soft silicon) which

define the characteristics and functionality of the

device. The ability of programming the device with a

PmmC file provides an extremely flexible method of

customising as well as upgrading it with future

enhancements.

It also contains the initialisation and parameters

associated with the particular display that is to be

connected to the Picaso processor, along with

product specific settings and parameters.

The PmmC file can only be programmed into the

device via the COM0 serial port with the aid of

Workshop 4, the 4D Systems IDE software.

Solutions, which remove the need to use Workshop4

to program the display modules, are available for

commercial customers requiring batch programming

or production line programming. These solutions are

practical for production staff and minimize the

chance of unwanted or unauthorised modifications

on the production line.

Three solutions come with the Workshop4 IDE, which

can be separated out for production line computers if

required, ScriptC, PmmC Loader and Program

Loader.

ScriptC is a command line interface which can be

controlled from a Batch Script or similar, useful for

repetitive loading or when controlled from an

external application. Example scripts are provided,

showing how to load PmmC and Applications using a

batch script.

PmmC Loader is a GUI interface designed to

download PmmC’s in to a 4D Systems Processor. It

has the ability to automatically update existing

PmmC’s present on a module, or to manually change

or force download to a blank processor or module,

overwriting anything written in previously.

Program Loader is a GUI interface designed to

download Applications to either Flash or RAM, useful

for testing or production loading, without the need

for Workshop4 itself.

Please contact our Support Team for more

information on what we can provide. Some solutions

also exist for external processor based loading, if

there is a requirement for that. This solution is

available under NDA.

Using a non-4D programming interface could damage

your module, and void your Warranty.

© 2017 4D SYSTEMS Page 15 of 22 www.4dsystems.com.au

Page 16

gen

4 Display Module Series gen4-uLCD-24PT - 2.4”

10. Starter Kit

4D Systems highly recommends all first time buyers

of 4D Systems’ displays, to purchase the Starter Kit

when purchasing their first 4D Systems display

solution.

The Starter Kit provides all the hardware that is

required to get the User up and running.

Not all development environments and features will

be needed by every User. However, by purchasing

the display solution in a Starter Kit allows you to take

full advantage of all of the features of the 4D Systems

Display Solution and try out each of the 4D

Woskshop4 Environments prior to settling with the

preferred feature-set.

The Designer environment can utilise every feature

of the display, however depending on the user

requirements, a micro-SD (uSD) card may not be

required. The uSD card is used when displaying

images/video/sound, along with datalogging to uSD,

and a programming cable or adaptor is required for

downloading compiled code and PmmC/Firmware

updates.

The ViSi environment is the same as Designer in

terms of feature utilisation, but is image based so

requires a uSD card, along with a programming cable.

The ViSi-Genie environment is also image based, and

therefore requires a uSD card and programming cable

also.

The Serial environment does not require either a uSD

or Programming cable to be used once the module

has been configured as a Serial device, however can

utilise both depending on the user requirements. The

uSD card can be used for such things as storage and

display of multimedia files, datalogging, and the

Programming cable for PmmC/Firmware updates, or

changing to one of the other three programming

environments.

Starter Kits typically include:

Gen4 Integrated Display Module

Gen4 Interface Module (gen4-IB)

Gen4 Programming Adaptor (gen4-PA)

4GB micro-SD Card

150mm 30 way FFC Cable

150mm 5-way ribbon cable for easy

connection to a breadboard or host via the

gen4-IB

Quick Start Guide

Please refer to the 4D Systems website for current

components included in the Starter Kit.

Simply select the Starter Kit option when purchasing

the chosen display module on the 4D Systems

shopping cart, or from your local distributor.

11. Display Module Part Numbers

The following is a breakdown on the part

numbers and what they mean.

Example:

gen4-uLCD-24PT

gen4 - gen4 Display Range

uLCD - microLCD Display Family

24 - Display size (2.4”)

P - Picaso Processor

T - Resistive Touch.

© 2017 4D SYSTEMS Page 16 of 22 www.4dsystems.com.au

Page 17

gen

4 Display Module Series gen4-uLCD-24PT - 2.4”

12. Mechanical Details

© 2017 4D SYSTEMS Page 17 of 22 www.4dsystems.com.au

Page 18

gen

4 Display Module Series gen4-uLCD-24PT - 2.4”

13. Schematic Details

© 2017 4D SYSTEMS Page 18 of 22 www.4dsystems.com.au

Page 19

gen

ABSOLUTE MAXIMUM RATINGS

Operating ambient temperature ................................................................................................... -20°C to +70°C

Storage temperature ...................................................................................................................... -30°C to +80°C

Voltage on any digital input pin with respect to GND ....................................................................... -0.3V to 6.0V

Voltage on VCC with respect to GND ................................................................................................. -0.3V to 6.0V

Maximum current sunk/sourced by any pin ................................................................................................ 4.0mA

Maximum current sunk/sourced by all ports ........................................................................................... 200.0mA

NOTE: Stresses above those listed here may cause permanent damage to the device. This is a stress rating only

and functional operation of the device at those or any other conditions above those indicated in the

recommended operation listings of this specification is not implied. Exposure to maximum rating conditions

for extended periods may affect device reliability.

RECOMMENDED OPERATING CONDITIONS

Parameter

Conditions

Min

Typ

Max

Units

Supply Voltage (VCC)

Stable external supply required

4.0

5.0

5.5

V

Processor voltage (VP)

--

3.3

--

V

Operating Temperature

-10

--

+60

°C

Input Low Voltage (VIL)

all pins 0 --

0.2VP

V

Input High Voltage (VIH)

non 5V tolerant pins

0.8VP

--

3.3

V

Input High Voltage (VIH)

All GPIO pins, RX0 and TX0 pins

0.8VP

--

5.5

V

Reset Pulse

External Open Collector

2.0

--

--

µs

Operational Delay

Power-Up or External Reset

500

--

3000

ms

GLOBAL CHARACTERISTICS BASED ON OPERATING CONDITIONS

Parameter

Conditions

Min

Typ

Max

Units

Supply Current (ICC)

5V Supply

--

150

--

mA

Display Endurance

Hours of operation, measured to

when display is 50% original

brightness

30000

--

--

H

Touch Screen Endurance

Number of touches/hits with a

12.5mm tip at a rate of 2x per

second with 250gf force

--

1M

--

Touches

Slide stylus on screen, 100gf force,

60mm/s speed with a 0.8mm

polyacetal tip stylus pen

--

100K

--

Slides

Touch Screen Transparency

80

--

--

%

Touch Screen Operational

Force

Only use Finger or Stylus, do not

use anything sharp or metal

20

--

100

gf

4 Display Module Series gen4-uLCD-24PT - 2.4”

14. Specifications

© 2017 4D SYSTEMS Page 19 of 22 www.4dsystems.com.au

Page 20

gen

LCD DISPLAY INFORMATION

Parameter

Conditions

Specification

Display Type TFT Transmissive LCD

Display Size 2.4” Diagonal

Display Resolution

240 x 320 (Portrait View)

Display Brightness

5V Supply – Resistive-Touch

182 cd/m2

Display Contrast Ratio

Typical

250:1

Display Viewing Angles

Above Centre

35 Degrees

Below Centre

55 Degrees

Left of Centre

55 Degrees

Right of Centre

55 Degrees

Display Viewing Direction

6 o’clock Display

(Optimal viewing is from below when in

Portrait mode)

Display Backlighting

White LED Backlighting

1x4 Parallel LED’s

Pixel Pitch

0.153 x 0.153mm (Square pixels)

Pixel Density

Number of pixels in 1 row in

25.4mm

166 DPI/PPI

4 Display Module Series gen4-uLCD-24PT - 2.4”

© 2017 4D SYSTEMS Page 20 of 22 www.4dsystems.com.au

Page 21

gen

Revision

Number

Date

Description

0.1

xx/xx/2015

Internal Use Only

1.0

09/12/2015

Initial Public Release Version

1.1

22/12/2015

Cosmetic Changes to gen4 Datasheet range

1.2

13/06/2016

Final drawing added, and content reviewed prior to hardware release

4 Display Module Series gen4-uLCD-24PT - 2.4”

15. Hardware Revision History

© 2017 4D SYSTEMS Page 21 of 22 www.4dsystems.com.au

Page 22

gen

4 Display Module Series gen4-uLCD-24PT - 2.4”

16. Legal Notice

Proprietary Information

The information contained in this document is the property of 4D Systems Pty. Ltd. and may be the subject of

patents pending or granted, and must not be copied or disclosed without prior written permission.

4D Systems endeavours to ensure that the information in this document is correct and fairly stated but does not

accept liability for any error or omission. The development of 4D Systems products and services is continuous and

published information may not be up to date. It is important to check the current position with 4D Systems. 4D

Systems reserves the right to modify, update or makes changes to Specifications or written material without prior

notice at any time.

All trademarks belong to their respective owners and are recognised and acknowledged.

Disclaimer of Warranties & Limitation of Liability

4D Systems makes no warranty, either expressed or implied with respect to any product, and specifically disclaims

all other warranties, including, without limitation, warranties for merchantability, non-infringement and fitness for

any particular purpose.

Information contained in this publication regarding device applications and the like is provided only for your

convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with

your specifications.

Images and graphics used throughout this document are for illustrative purposes only. All images and graphics used

are possible to be displayed on the 4D Systems range of products, however the quality may vary.

In no event shall 4D Systems be liable to the buyer or to any third party for any indirect, incidental, special,

consequential, punitive or exemplary damages (including without limitation lost profits, lost savings, or loss of

business opportunity) arising out of or relating to any product or service provided or to be provided by 4D Systems,

or the use or inability to use the same, even if 4D Systems has been advised of the possibility of such damages.

4D Systems products are not fault tolerant nor designed, manufactured or intended for use or resale as on line

control equipment in hazardous environments requiring fail – safe performance, such as in the operation of nuclear

facilities, aircraft navigation or communication systems, air traffic control, direct life support machines or weapons

systems in which the failure of the product could lead directly to death, personal injury or severe physical or

environmental damage (‘High Risk Activities’). 4D Systems and its suppliers specifically disclaim any expressed or

implied warranty of fitness for High Risk Activities.

Use of 4D Systems’ products and devices in 'High Risk Activities' and in any other application is entirely at the

buyer’s risk, and the buyer agrees to defend, indemnify and hold harmless 4D Systems from any and all damages,

claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any 4D

Systems intellectual property rights.

17. Contact Information

For Technical Support: www.4dsystems.com.au/support

For Sales Support: sales@4dsystems.com.au

Website: www.4dsystems.com.au

Copyright 4D Systems Pty. Ltd. 2000-2017.

© 2017 4D SYSTEMS Page 22 of 22 www.4dsystems.com.au

Page 23

Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

4D Systems:

SK-gen4-24PT-AR SK-gen4-24PT gen4-uLCD-24PT-PI gen4-uLCD-24PT-AR SK-gen4-24PT-PI gen4-uLCD-24PT

Loading...

Loading...