UTMC 5962R0153501VXX, 5962R0153501VXC, 5962R0153501VXA, 5962R0153501QXX, 5962R0153501QXC Datasheet

...

Standard Products

UT54LVDS218 Deserializer

Data Sheet

October 2002

FEATURES

q15 to 50MHz shift clock support

q50% duty cycle on receiver output clock

qLow power consumption

qCold sparing all pins

q+1V common mode range (around +1.2V)

qNarrow bus reduces cable size and cost

qUp to 1.05 Gbps throughput

qUp to 132 Megabytes/sec bandwidth

q325 mV (typ) swing LVDS devices for low EMI

qPLL requires no external components

qRising edge strobe

qRadiation-hardened design; total dose irradiation testing to MIL-STD-883 Method 1019

-Total-dose: 300 krad(Si) and 1 Mrad(Si)

-Latchup immune (LET > 100 MeV-cm2 /mg)

qPackaging options:

-48-lead flatpack

qStandard Microcircuit Drawing 5962-01535

-QML Q and V compliant part

qCompatible with TIA/EIA-644 LVDS standard

INTRODUCTION

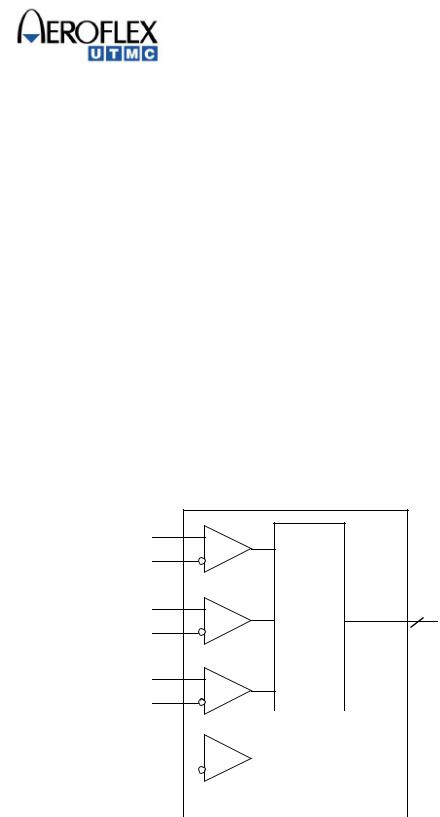

The UT54LVDS218 Deserializer converts the three LVDS data streams back into 21 bits of CMOS/TTL data. At a transmit clock frequency of 50MHz, 21 bits of TTL data are transmitted at a rate of 350 Mbps per LVDS data channel. Using a 50 MHz clock, the data throughput is 1.05 Gbit/s (132 Mbytes/sec).

The UT54LVDS218 Deserializer allows the use of wide, high speed TTL interfaces while reducing overall EMI and cable size.

All pins have Cold Spare buffers. These buffers will be high impedance when VDD is tied to VSS.

DATA (LVDS)

LVDS TO-PARALLEL TTL

21

CMOS/TTL OUTPUTS

CMOS/TTL OUTPUTS

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLOCK (LVDS) |

|

|

|

|

|

PLL |

|

|

|

|

|

RECEIVER CLOCK OUT |

||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

POWER DOWN |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 1. UT54LVDS218 Deserializer Block Diagram |

|||||||||||||

1

|

RxOUT 17 |

|

1 |

|

|

|

|

|

|

48 |

|

VDD |

PIN DESCRIPTION |

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

RxOUT 18 |

2 |

|

|

|

|

|

|

47 |

|

RxOUT 16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

GND |

3 |

|

|

|

|

|

|

46 |

|

RxOUT 15 |

|

Pin Name |

I/O |

|

No. |

|

|

|

|

Description |

||||||||||||||

|

RxOUT 19 |

4 |

|

|

|

|

|

|

45 |

|

RxOUT 14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

RxIN+ |

I |

|

3 |

Positive LVDS differential data inputs1 |

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

44 |

GND |

||||||||||||||||||||||||||

|

RxOUT 20 |

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

RxIN- |

I |

|

3 |

Negative LVDS differential data output 1 |

||||||||||||||||||||||||

|

|

N/C |

6 |

|

UT54LVDS218 |

43 |

|

RxOUT 13 |

|

|

||||||||||||||||||||||||||

LVDS GND |

7 |

|

42 |

|

VDD |

|

RxOUT |

O |

|

21 |

TTL level data outputs |

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

41 |

|

RxOUT 12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

RxIN0- |

8 |

|

|

|

|

|

|

|

|

RxCLK IN+ |

I |

|

1 |

Positive LVDS differential clock input |

||||||||||||||||||||

|

|

RxIN0+ |

|

9 |

|

|

|

|

|

|

40 |

|

RxOUT 11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

RxCLK IN- |

I |

|

1 |

Negative LVDS differential clock input |

|||||||||||||||||||||||

|

|

RxIN1- |

10 |

|

|

|

|

|

|

39 |

|

RxOUT 10 |

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

RxCLK OUT |

O |

|

1 |

TTL level clock output. The rising edge acts |

|||||||||||||||||||||||

|

|

RxIN1+ |

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

38 |

|

GND |

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

as data strobe. Pin name RxCLK OUT. |

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

LVDS V DD |

|

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

37 |

RxOUT 9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

PWR DWN |

I |

|

1 |

TTL level input. When asserted (low input) |

||||||||||||||||||||||||

|

13 |

|

|

|

|

|

|

|||||||||||||||||||||||||||||

LVDS GND |

|

|

|

|

|

|

36 |

|

VDD |

|

|

|

|

|

|

|

|

|

the receiver outputs are low |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

RxIN2- |

|

|

|

|

|

|

|

35 |

|

RxOUT 8 |

|

VDD |

I |

|

4 |

Power supply pins for TTL outputs and log- |

||||||||||||||||||

|

15 |

|

|

|

|

|

|

ic |

||||||||||||||||||||||||||||

|

|

RxIN2+ |

|

|

|

|

|

|

|

34 |

|

RxOUT 7 |

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

RxCLK IN- |

16 |

|

|

|

|

|

|

|

|

|

|

|

|

GND |

I |

|

5 |

Ground pins for TTL outputs and logic |

||||||||||||||||||

|

|

|

|

|

|

33 |

|

RxOUT 6 |

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

RxCLK IN+ |

17 |

|

|

|

|

|

|

32 |

GND |

|

PLL VDD |

I |

|

1 |

Power supply for PLL |

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

RxOUT 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

LVDS GND |

18 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

PLL GND |

I |

|

2 |

Ground pin for PLL |

|||||||||||||||||||||||||

|

|

|

|

|

|

|

RxOUT 4 |

|

|

|||||||||||||||||||||||||||

|

|

PLL GND |

19 |

|

|

|

|

|

|

30 |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

LVDS V DD |

I |

|

1 |

Power supply pin for LVDS pins |

||||||||||||||||||||||||

|

|

PLL V DD |

20 |

|

|

|

|

|

|

29 |

|

RxOUT 3 |

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LVDS GND |

I |

|

3 |

Ground pins for LVDS inputs |

|||||||||||||||||

|

|

PLL GND |

21 |

|

|

|

|

|

|

28 |

|

VDD |

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

PWR DWN |

22 |

|

|

|

|

|

|

27 |

RxOUT 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

Notes: |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

RxCLK OUT |

23 |

|

|

|

|

|

|

26 |

RxOUT 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

1. These receivers have input fail-safe bias circuitry to guarantee a stable receiver |

||||||||||||||||||||||||||||||

|

|

RxOUT0 |

24 |

|

|

|

|

|

|

25 |

|

GND |

output for floating or terminated receiver inputs. Under these conditions receiver |

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

inputs will be in a HIGH state. If a clock signal is present, outputs will all be |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HIGH; if the clock input is also floating/terminated outputs will remain in the |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

last valid state. A floating/terminated clock input will result in a LOW clock |

|||||||||||||||||

|

|

Figure 2. UT54LVDS218 Pinout |

|

|

|

|

output. |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

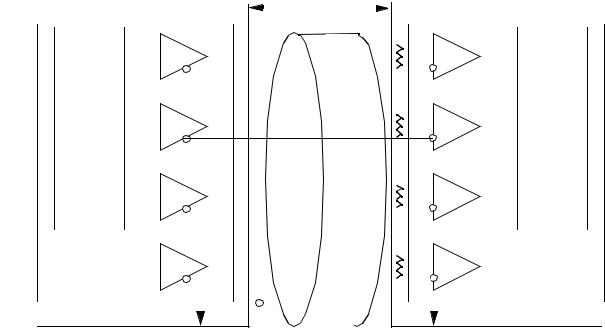

LVDS CABLE |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

TX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RX |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

MEDIA DEPENDENT DATA |

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

TxIN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(LVDS) |

|

|

|

|

|

|

|

|

|

|

|

RxOUT |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

||||

CMOS/ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

TTL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

18 |

|

|

|

|

|

|

|

|

|

18 |

||||||||||||

19 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

19 |

||

20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

20 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLOCK |

|

|

|||||||||

TxCLK |

|

|

|

|

|

|

|

|

(LVDS) |

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RxCLK |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

GND |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PCB |

|

|

|

|

|

|

|

|

|

PCB |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SHIELD

Figure 3. UT54LVDS218 Typical Application

2

ABSOLUTE MAXIMUM RATINGS1

(Referenced to VSS)

SYMBOL |

PARAMETER |

LIMITS |

|

|

|

VDD |

DC supply voltage |

-0.3 to 4.0V |

VI/O |

Voltage on any pin |

-0.3 to (VDD + 0.3V) |

TSTG |

Storage temperature |

-65 to +150°C |

PD |

Maximum power dissipation |

1.25 W |

|

|

|

TJ |

Maximum junction temperature2 |

+150°C |

|

|

|

ΘJC |

Thermal resistance, junction-to-case3 |

10°C/W |

II |

DC input current |

±10mA |

|

|

|

Notes:

1.Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions beyond limits indicated in the operational sections of this specification is not recommended. Exposure to absolute maximum rating conditions for extended periods may affect device reliability and performance.

2.Maximum junction temperature may be increased to +175°C during burn-in and steady-static life.

3.Test per MIL-STD-883, Method 1012.

4.For cold spare mode (VDD = VSS), VI/O may be -0.3V to the maximum recommended operating V DD +0.3V.

RECOMMENDED OPERATING CONDITIONS

SYMBOL |

PARAMETER |

LIMITS |

|

|

|

VDD |

Positive supply voltage |

3.0 to 3.6V |

TC |

Case temperature range |

-55 to +125°C |

VIN |

DC input voltage |

0V to VDD |

3

DC ELECTRICAL CHARACTERISTICS1

(VDD = 3.0V to 0.3V; -55°C < TC < +125°C)

SYMBOL |

PARAMETER |

|

|

CONDITION |

MIN |

MAX |

UNIT |

|||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

CMOS/TTL DC SPECIFICATIONS (PWR DWN, RXOUT) |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

||

VIH |

High-level input voltage |

|

|

|

|

2.0 |

VDD |

V |

||

VIL |

Low-level input voltage |

|

|

|

|

GND |

0.8 |

V |

||

VOL |

Low-level output voltage |

|

IOL = 2mA |

|

0.3 |

V |

||||

VOH |

High-level output voltage |

|

IOL = -0.4mA |

2.7 |

|

V |

||||

I |

|

High-level input current |

|

VIN=3.6V; VDD = 3.6V |

-10 |

+10 |

μA |

|||

IH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

IIL |

|

Low-level input current |

|

VIN=0V; VDD = 3.6V |

-10 |

+10 |

μA |

|||

VCL |

Input clamp voltage |

|

ICL = -18mA |

|

-1.5 |

V |

||||

ICS |

|

Cold spare leakage current |

|

VIN=3.6V; VDD = VSS |

-20 |

+20 |

μA |

|||

IOS |

|

Output short circuit current |

|

VOUT = 0V |

-15 |

-130 |

mA |

|||

2, 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

LVDS RECEIVER DC SPECIFICATIONS (IN+, IN-) |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|||

VΤΗ |

3 |

Differential input high threshold |

|

VCM = +1.2V |

|

+100 |

mV |

|||

V |

3 |

Differential input low threshold |

|

VCM = +1.2V |

-100 |

|

mV |

|||

ΤL |

|

|

|

|

|

|

|

|

|

|

VCMR |

Common mode voltage range |

|

VID=210mV |

0.2 |

2.00 |

V |

||||

IIN |

|

Input current |

|

VIN = +2.4V, VDD = 3.6V |

-10 |

+10 |

μA |

|||

|

|

|

|

|

VIN = 0V, VDD = 3.6V |

-10 |

+10 |

μA |

||

|

|

|

|

|

|

|

||||

ICSIN |

Cold spare leakage current |

|

VIN = 3.6V, VDD = VSS |

-20 |

+20 |

μA |

||||

Supply Current |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

||||

3 |

Active supply current |

|

CL=8pF (see Figure 4) |

|

105 |

mΑ |

||||

ICC |

|

|

|

|

|

|

|

|

|

|

ICCPD |

Power down supply current |

|

|

|

= Low, LVDS inputs = |

|

2.0 |

mA |

||

|

PWR DWN |

|

||||||||

|

|

|

|

|

logic low |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Notes:

1. Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenc ed to ground.

2.Output short circuit current (I OS) is specified as magnitude only, minus sign indicates direction only. Only one output should be shorted at a time, do not exceed maximum junction temperature specification.

3.Guaranteed by characterization.

4

Loading...

Loading...